# Advanced Transistors For Supply Voltage Reduction: Tunneling Field-Effect Transistors And High-Mobility Mosfets

**GUO PENGFEI**

NATIONAL UNIVERSITY OF SINGAPORE

2013

# Advanced Transistors For Supply Voltage Reduction: Tunneling Field-Effect Transistors And High-Mobility Mosfets

**GUO PENGFEI** (B. ENG. (HONS.)), NUS

**A THESIS SUBMITTED**

#### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

NUS GRADUATE SCHOOL FOR INTEGRATIVE SCIENCES

AND ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2013

### **Declaration**

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Guo Pengfei 28 Ang 2013

#### Acknowledgements

First and foremost, I would like to thank my research project supervisor, Prof. Yeo Yee-Chia, for his constructive criticism and invaluable suggestions throughout the completion of this research project. Prof. Yeo Yee-Chia is truly an outstanding academic professional and excellent supervisor in guiding the development of my work. My future career will benefit from the experience and knowledge that I gained by working with Prof. Yeo Yee-Chia. I am also grateful to my co-supervisor, Dr. Chia Ching Kean, for his advices and strong technical support to the project on Ge/In<sub>0.53</sub>Ga<sub>0.47</sub>As heterojunction tunneling field-effect transistors.

I owe special thanks to Dr. Han Genquan for his invaluable advices and generously sharing information, without whom the completion of the project is impossible. I would also like to thank Prof. Heng Chun-Huat, who has given me a lot of help and provided many useful discussions in the early stage of my research.

I am grateful to my fellow teammates in Silicon Nano Device Laboratory (SNDL): Yang Yue, Gong Xiao, Liu Bin, Zhou Qian, Huaxin, Xingui, Ivana, Cheng Ran, Lanxiang, Chunlei, Wang Wei, Tong Yi, Yinjie, Guo Cheng, Samuel, Eugene, Zhu Zhu, Tong Xin, Wenjuan, Kain Lu, Dong Yuan, Xu Xin, Sujith, Xinke, Fan Lu, Litao, Phyllis and many others for their useful discussions, assistance and friendships through the years.

In addition, I would like to express my sincere appreciation and gratitude to the technical staffs in SNDL, Mr. O Yan Wai Linn, Mr. Patrick Tang and Ms. Yu Yi, for providing technical and administrative support for my research work. Appreciation also goes out to staffs at Institute of Materials Research and Engineering (IMRE): Dr. Pan Jisheng, Dr. Zhang Zheng, Ms. Teo Siew Lang, Ms. Doreen Lai, and Ms. Hui Hui Kim, for their dedicated help and support in experimental works carried out at IMRE as well as data analysis and interpretation.

Finally, my deepest thanks and profound gratitude go to my family for their continuous encouragements and support. I am also grateful for the support and understanding of my wife, Chunyan, throughout my candidature. Thank you for your love and support over these years, without which my dream of completing my academic endeavors would not have been fulfilled. I would also like to thank my lovely daughter, Ruihan, for the joy and happiness that she brings to my life.

### **Table of Contents**

| Acknowledgements      | ii   |

|-----------------------|------|

| Table of Contents     | iv   |

| Abstract              | vii  |

| List of Tables        | ix   |

| List of Figures       | X    |

| List of Symbols       | XX   |

| List of Abbreviations | xxiv |

#### Chapter 1 Introduction

| 1.1 Background                                             | 1      |

|------------------------------------------------------------|--------|

| 1.2 Transistor with Steep Switching Characteristics        | 2      |

| 1.2.1 Development of Tunneling Field-Effect Transistor     | 5      |

| 1.2.2 Working Principle of TFET and Band-to-Band Tunneling | 7      |

| 1.2.3 Design Considerations of TFET                        | 9      |

| 1.3 Transistor with High-Mobility Channel Material         |        |

| 1.4 Objectives of Research                                 |        |

| 1.5 Outline of Thesis                                      |        |

| Chapter 2 Study of Strain and Temperature Depender         | nce of |

#### **Tunneling Current for Tunneling Field-Effect Transistor (TFET)**

| 2.1 | Introduction                                           | 19 |

|-----|--------------------------------------------------------|----|

| 2.2 | Strain Dependence of Tunneling Current                 | 20 |

| 2.3 | Temperature Dependence of Tunneling Current            | 28 |

| 2.4 | Temperature Independent Current Biasing Employing TFET | 34 |

| 2.5 | Summary                                                | 39 |

### Chapter 3 Source-Channel Interface Engineering for Tunneling Field-Effect Transistor (TFET) with p<sup>+</sup> Si<sub>0.5</sub>Ge<sub>0.5</sub> Source: Insertion of Strained Si<sub>0.989</sub>C<sub>0.011</sub> Layer for Enhancement of Tunneling Current and Subthreshold Swing

| 3.1 | Introduction                                                                                                 | . 40 |

|-----|--------------------------------------------------------------------------------------------------------------|------|

| 3.2 | Device Concept and Design                                                                                    | . 44 |

| 3.3 | Fabrication of TFETs with Si <sub>0.5</sub> Ge <sub>0.5</sub> /Si <sub>0.989</sub> C <sub>0.011</sub> Source | . 51 |

| 3.4 | Electrical Characterization of TFETs                                                                         | . 56 |

| 3.5 | Summary                                                                                                      | 61   |

|     |                                                                                                              |      |

### Chapter 4 Tunneling Field-Effect Transistor (TFET) with

#### Ge/In<sub>0.53</sub>Ga<sub>0.47</sub>As Heterostructure as Tunneling Junction

| 4.1 | Introduction                             | . 62 |

|-----|------------------------------------------|------|

| 4.2 | Device Concept and Design                | . 65 |

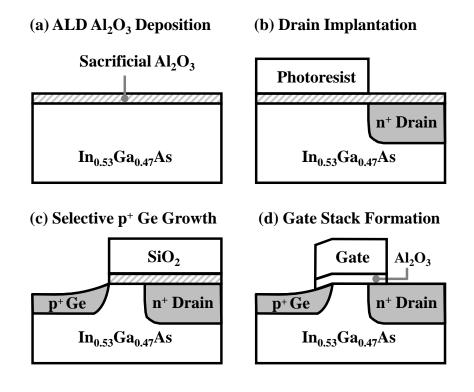

| 4.3 | Device Fabrication                       | . 69 |

| 4.4 | Results and Discussion                   | . 72 |

| 4.4 | 4.1 Material Analysis                    | 72   |

| 4.4 | 4.2 Band Alignment Study                 | 78   |

| 4.4 | 4.3 Electrical Characterization of TFETs | 85   |

| 4.5 | Summary                                  | . 92 |

### Chapter 5 Germanium-Tin $(Ge_{1-x}Sn_x)$ MOSFETs with Low-Temperature Silicon Surface Passivation

| 5.1 | Introduction                                 |     |

|-----|----------------------------------------------|-----|

| 5.2 | GeSn pMOSFETs with Si Surface Passivation    |     |

| 5.2 | 2.1 Fabrication of GeSn pMOSFETs             | 95  |

| 5.2 | 2.2 Impact of Si Passivation Layer Thickness | 98  |

| 5.2 | 2.3 Effects of Post Metal Annealing          | 107 |

| 5.3 | GeSn nMOSFETs with Si Surface Passivation    | 119 |

| 5.3 | 3.1 Fabrication of GeSn nMOSFETs             | 119 |

| 5.3 | 5.2 El | lectrica | al Cl | naracte | rizat | ion o | f GeSn nM0 | OSFETs          |    |      | 122   |

|-----|--------|----------|-------|---------|-------|-------|------------|-----------------|----|------|-------|

| 5.3 | .3 E   | ffects   | of    | FGA     | on    | the   | Electrical | Characteristics | of | GeSn |       |

| nN  | IOSFI  | ETs      |       |         |       |       |            |                 |    |      | 126   |

| 5.4 | Sum    | mary     |       |         |       |       |            |                 |    |      | . 131 |

### **Chapter 6 Conclusion and Future Work**

| 6.1 C     | onclusion                                                                                                 |     |

|-----------|-----------------------------------------------------------------------------------------------------------|-----|

| 6.2 C     | ontributions of This Thesis                                                                               | 133 |

| 6.2.1     | Strain and Temperature Dependence of Tunneling Current                                                    | 133 |

| 6.2.2     | TFET with Si <sub>0.5</sub> Ge <sub>0.5</sub> /Si <sub>0.989</sub> C <sub>0.011</sub> /Si Heterostructure | 134 |

| 6.2.3     | TFET with Ge/In <sub>0.53</sub> Ga <sub>0.47</sub> As Heterostructure                                     | 134 |

| 6.2.4     | Ge <sub>1-x</sub> Sn <sub>x</sub> MOSFET with Si Surface Passivation                                      | 134 |

| 6.3 Fi    | uture Directions                                                                                          | 135 |

| 6.3.1     | <i>I</i> <sub>ON</sub> Enhancement for TFETs                                                              | 135 |

| 6.3.2     | P-Channel TFETs                                                                                           | 135 |

| 6.3.3     | Surface Passivation for GeSn pMOSFETs                                                                     | 136 |

| 6.3.4     | Processing Technology of GeSn nMOSFETs                                                                    | 136 |

| Reference | ces                                                                                                       | 138 |

| Appendi   | X                                                                                                         |     |

| List of l | Publications                                                                                              |     |

#### Abstract

Due to the excellent scalability, low cost, and high performance, complementary metal-oxide-semiconductor (CMOS) transistors have been widely used in electronics for the past four decades. However, continuous scaling of CMOS devices causes serious power consumption issues as the leakage current and the operation frequency of an integrated circuit (IC) increase. To reduce the power consumption, supply voltage  $V_{DD}$  needs to be lowered. Tunneling field-effect transistors (TFETs) and high-mobility Ge<sub>1-x</sub>Sn<sub>x</sub> channel metal-oxide-semiconductor field-effect transistors (MOSFETs) are promising candidates to enable the reduction of  $V_{DD}$  and power consumption. In this thesis, TFETs with novel structures and high-mobility Ge<sub>1-x</sub>Sn<sub>x</sub> MOSFETs are explored.

In this thesis, we studied the TFET device physics by analyzing the temperature and strain dependence of the tunneling current, which has not been reported before. In general, bandgap  $E_G$  narrowing of silicon (Si) due to uniaxial tensile stress leads to drain current  $I_{DS}$  enhancement, while uniaxial compressive stress reduced  $I_{DS}$ . The positive temperature coefficient of  $I_{DS}$  at low drain bias  $V_{DS}$  is due to temperature-induced  $E_G$  reduction, and the negative temperature coefficient at higher  $V_{DS}$  is due to increased channel resistance which reduces the effective electrical field at the tunneling junction for a given  $V_{DS}$ . These results provide guidance for the design of strained TFETs and are also useful for understanding the band-to-band tunneling (BTBT) mechanism in TFETs.

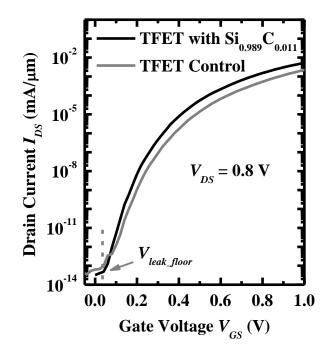

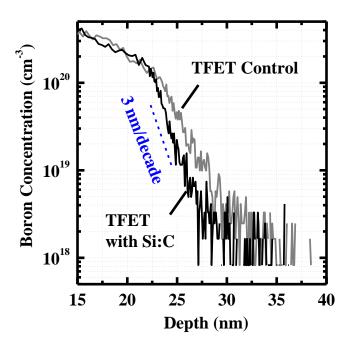

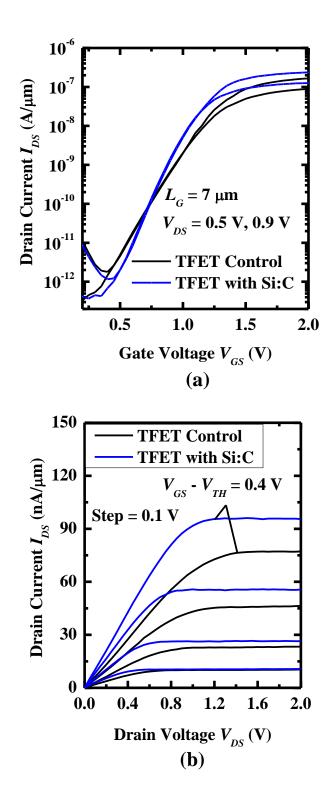

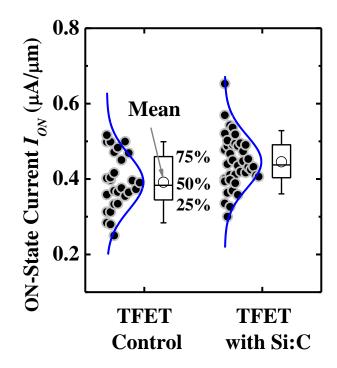

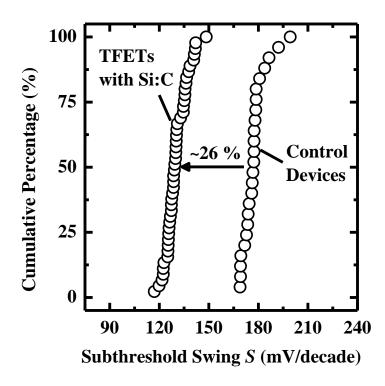

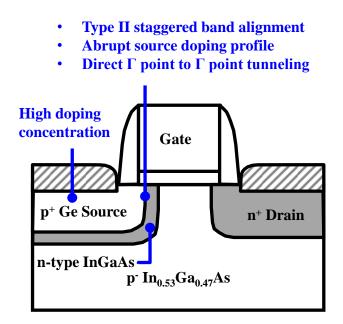

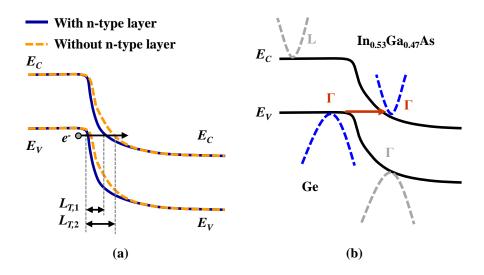

Exploiting heterostructure with staggered (or type II) band alignment at the tunneling junction is a promising approach to realize TFET with high on-state current  $I_{ON}$  and small subthreshold swing *S*. TFETs with two novel heterostructures (Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si<sub>0.989</sub>C<sub>0.011</sub>/Si and Ge/In<sub>0.53</sub>Ga<sub>0.47</sub>As) were demonstrated. In the TFET with Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si<sub>0.989</sub>C<sub>0.011</sub>/Si heterostructure, the strained Si<sub>0.989</sub>C<sub>0.011</sub> layer reduces the tunneling barrier width and contributes to a steep p<sup>+</sup> doping profile of 3 nm/decade, leading to a ~20% enhancement in  $I_{ON}$  and ~26% reduction in *S* as compared to TFET without the Si<sub>0.989</sub>C<sub>0.011</sub> layer. For TFET with Ge/In<sub>0.53</sub>Ga<sub>0.47</sub>As heterostructure, high source doping concentration ( $3 \times 10^{20}$  cm<sup>-3</sup>) with abrupt doping profile and direct BTBT were achieved, which are beneficial for  $I_{ON}$  and *S* of TFETs. Various process integration challenges for realizing such a TFET were identified and addressed.

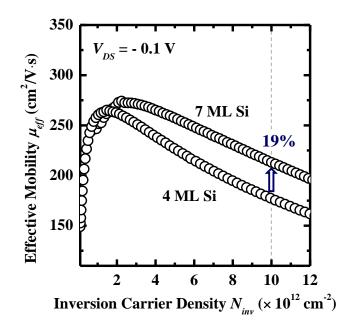

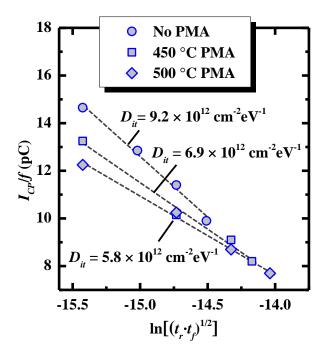

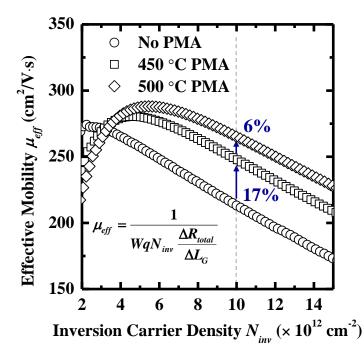

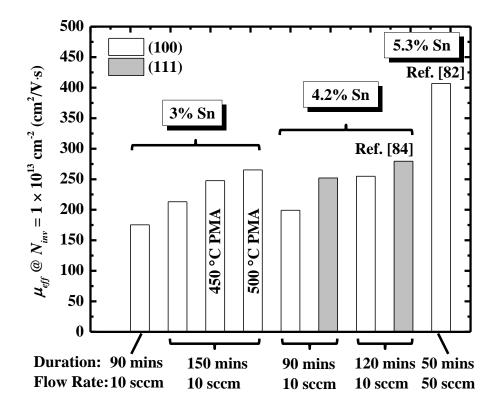

High-mobility  $\text{Ge}_{1-x}\text{Sn}_x$  MOSFET is another promising candidate for  $V_{DD}$  reduction in future technology nodes. To take full advantage of  $\text{Ge}_{1-x}\text{Sn}_x$  as a channel material, a high-quality and thermodynamically stable gate stack has to be realized. Surface passivation technique using low-temperature  $\text{Si}_2\text{H}_6$  treatment was investigated. By increasing the thickness of Si passivation layer from 4 to 7 monolayers, effective hole mobility  $\mu_{eff}$  at an inversion carrier density of  $1 \times 10^{13}$  cm<sup>-2</sup> was improved by ~19%. Ge<sub>0.97</sub>Sn<sub>0.03</sub> pMOSFETs with post metal annealing (PMA) show improved intrinsic transconductance  $G_{m,int}$ , S, and  $\mu_{eff}$  as compared to the control devices without PMA. In addition, Ge<sub>1-x</sub>Sn<sub>x</sub> n-channel MOSFETs with low-temperature Si passivation were demonstrated. This was the first demonstration of Si passivation for Ge<sub>1-x</sub>Sn<sub>x</sub> n-channel MOSFETs.

## **List of Tables**

| Table 1.1. | Electron and hole mobilities of some common semiconductors at room temperature.                                               | 14  |

|------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1. | Summary of device characteristics of Si-based TFETs                                                                           | 41  |

| Table 3.2. | Recipes used for Si <sub>0.5</sub> Ge <sub>0.5</sub> /Si <sub>0.989</sub> C <sub>0.011</sub> etch using a reactive ion etcher | 53  |

| Table 4.1. | Extraction of the Si layer thicknesses for 90 and 150 minutes Si passivation.                                                 | 101 |

## **List of Figures**

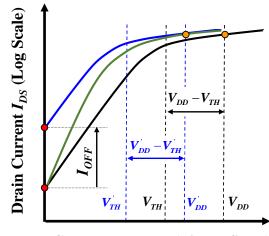

| Fig. 1.1. | The black curve shows the drain current - gate voltage $(I_{DS} - V_{GS})$<br>characteristics of an unscaled MOSFET. As $V_{DD}$ scales down, $V_{TH}$<br>needs to be reduced in order to maintain the on-state current $I_{ON}$ at<br>the same gate overdrive $(V_{DD} - V_{TH} = V_{DD} - V_{TH})$ . However,<br>scaling-down of $V_{DD}$ and $V_{TH}$ without reducing S will cause a high<br>$I_{OFF}$ as illustrated by the blue curve. The green curve indicates that<br>the S of the transistor has to be reduced to maintain a low $I_{OFF}$                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

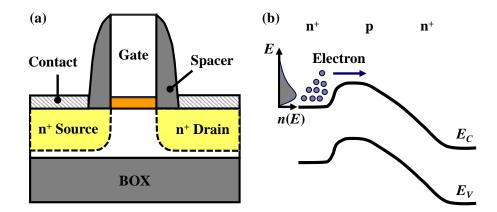

| Fig. 1.2. | (a) Schematic of a conventional n-channel MOSFET. (b) The energy band diagram along the source-to-drain direction when the MOSFET is at on-state. Fermi-Dirac distribution of the electron concentration in the energy scale $n(E)$ in the source region is illustrated. The electrons in the high energy tail can surmount the energy barrier between source and channel, causing the <i>S</i> of a MOSFET to be higher than 60 mV/decade at room temperature. $E_C$ and $E_V$ are the energies of conduction band edge and valence band edge, respectively                                               |

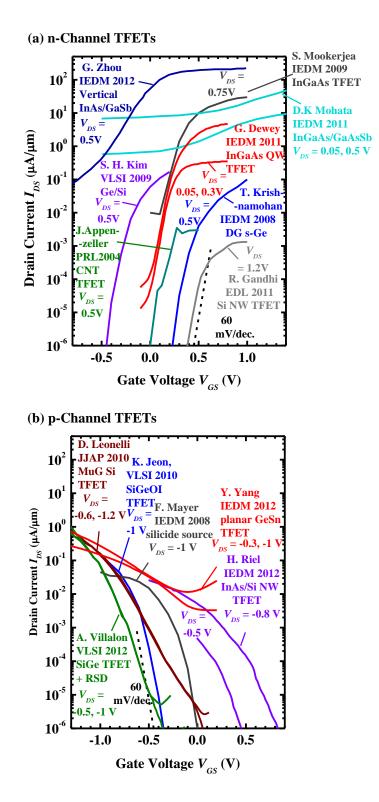

| Fig. 1.3. | The transfer characteristics of the key published experimental (a) n-<br>channel TFETs and (b) p-channel TFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

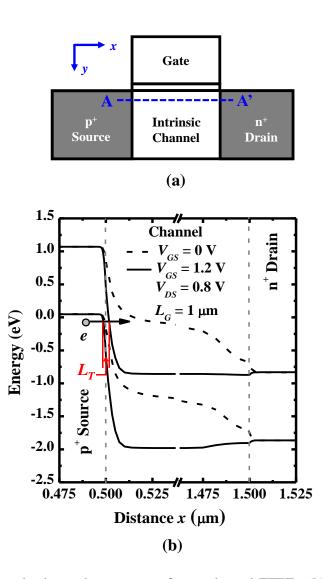

| Fig. 1.4. | (a) Schematic shows the structure of an n-channel TFET. (b)<br>Simulated energy band diagrams at on-state ( $V_{GS} = 1.2$ V) and off-<br>state ( $V_{GS} = 0$ V) along the source-to-drain direction as indicated by<br>the dashed line A-A' in (a). For this simulation, the device<br>parameters used were: acceptor concentration in the source $N_A = 1$<br>$\times 10^{20}$ cm <sup>-3</sup> , donor concentration in drain $N_D = 1 \times 10^{20}$ cm <sup>-3</sup> , body<br>doping $N_A = 1 \times 10^{16}$ cm <sup>-3</sup> , equivalent oxide thickness (EOT) = 0.8<br>nm, and $L_G = 1 \mu$ m |

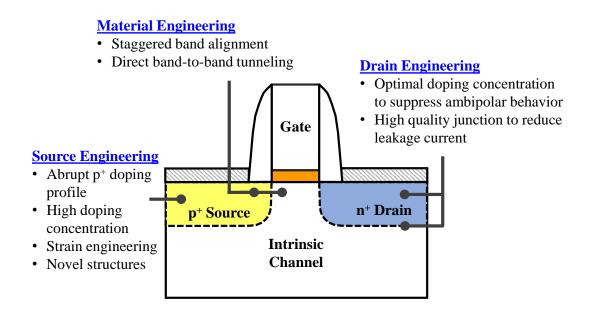

| Fig. 1.5. | Schematic illustrates the key challenges and design considerations for TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

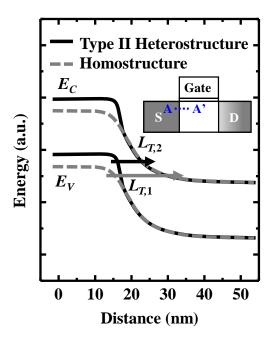

| Fig. 1.6. | Schematic of energy band diagrams along source-to-drain direction<br>at the tunneling junction regions in two TFETs. The first TFET has<br>a homojunction where the tunneling path length is $L_{T,1}$ . The second<br>TFET has a heterojunction with staggered band alignment, and the<br>tunneling path length $L_{T,2}$ is smaller than $L_{T,1}$ under the same bias<br>condition                                                                                                                                                                                                                      |

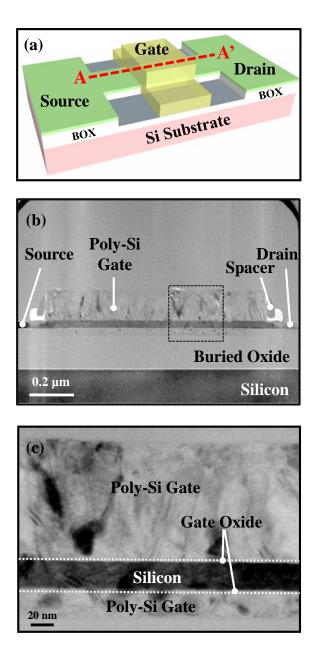

| Fig. 2.1. | (a) Schematic of a double-gate TFET. (b) TEM image of a TFET device with $L_G$ of 1 µm measured in this experiment. The source-to-drain orientation of the TFET is along [110] direction. Thickness of thermal SiO <sub>2</sub> gate dielectric $T_{OX}$ is 3 nm. 100 nm poly-Si gate electrode was formed by low-pressure chemical vapor                                                                                                                                                                                                                                                                  |

|           | deposition. (c) TEM image of the gate stack indicated by the dashed box in (b). The thickness of the body Si is 25 nm as measured from the TEM image. The top and bottom gates are connected together.                                                                                                                                                                                                                                          | 21 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

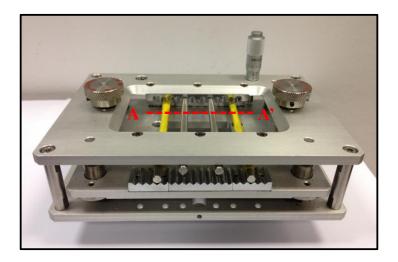

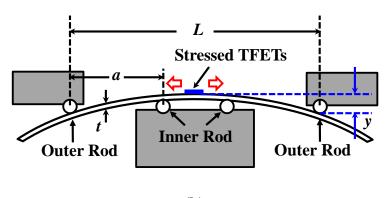

| Fig. 2.2. | (a) Image of the four-point wafer bending apparatus. (b) Schematic of the wafer bending apparatus along A-A' direction as indicated in (a). Tensile stress is applied to the wafer strip as illustrated. With the same setup, compressive stress can also be applied by bending the wafer strip in opposite direction. The dimension of the wafer strip that this setup can accommodate is $5 \sim 8$ cm in length and less than 2 cm in width. | 22 |

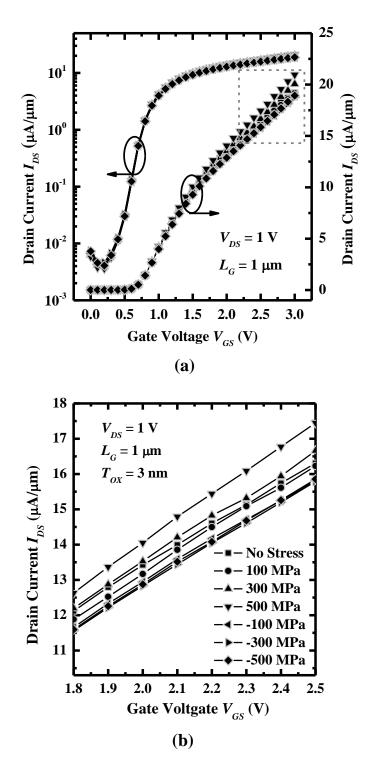

| Fig. 2.3. | (a) Linear and log-linear plot shows the $I_{DS} - V_{GS}$ characteristics of<br>a TFET at different strain conditions for $V_{DS} = 1$ V. (b) Zoomed-in<br>view of the $I_{DS} - V_{GS}$ curves indicated by the dashed box in (a). The<br>legend for each curve is shown in (b). Negative and positive signs<br>are used for compressive and tensile stress, respectively. (a) and<br>(b) have the same legend for each curve.                | 24 |

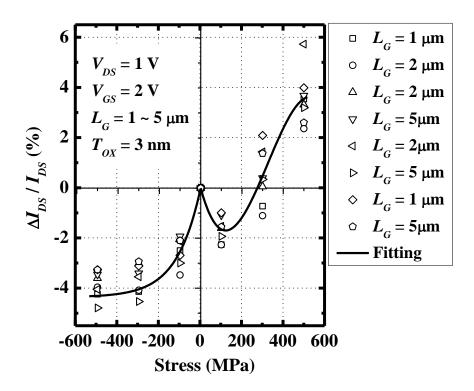

| Fig. 2.4. | Variation of $I_{DS}$ under uniaxial compressive or tensile stress. Each<br>symbol represents a single device under different stress conditions<br>and 8 devices are shown in this figure. Devices with $L_G$ from 1 µm<br>to 5 µm were characterized at room temperature. For each $L_G$ , the<br>same device was used for all stress values.                                                                                                  | 25 |

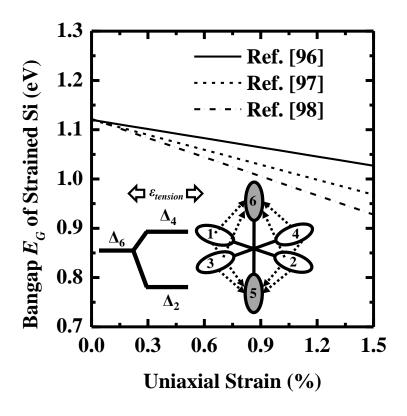

| Fig. 2.5. | Theoretical results indicate that uniaxial tensile strain reduces the $E_G$ of Si. The inset is a schematic illustration of strain induced conduction band splitting and carrier repopulation among six valleys in Si conduction band under uniaxial tensile strain ( $\varepsilon_{tension}$ ) along [110] direction. The strain makes the carriers preferentially populate in valley 5 and 6, where the effective mass is lower               | 27 |

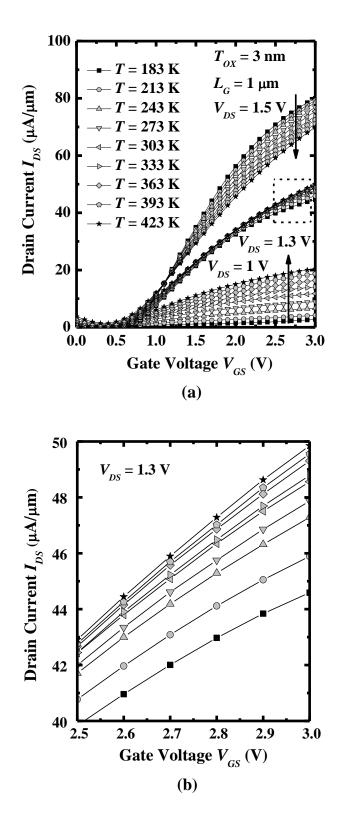

| Fig. 2.6. | (a) $I_{DS}$ - $V_{GS}$ curves at $V_{DS}$ of 1 V, 1.3 V and 1.5 V measured at temperatures from 183 to 423 K in steps of 30 K. The arrows indicate the direction of the change of $I_{DS}$ with increasing temperature. (b) The enlarged $I_{DS}$ - $V_{GS}$ curves in the dashed box in (a) for $V_{DS}$ of 1.3 V.                                                                                                                            | 29 |

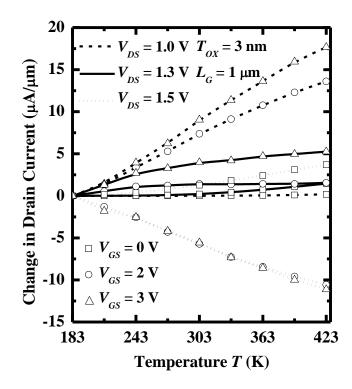

| Fig. 2.7. | Change in $I_{DS}$ as a function of temperature for $V_{GS}$ of 0 V, 2 V and 3 V. For each bias condition, $I_{DS}$ at 183 K was taken as reference for comparison. It is observed that $I_{DS}$ changes in different directions with different $V_{DS}$ when the temperature is increased                                                                                                                                                      | 30 |

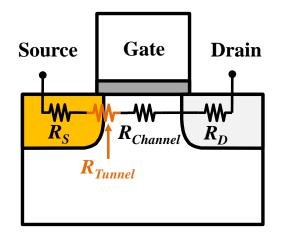

| Fig. 2.8. | Schematic of a TFET showing the resistance components between source and drain terminals: $R_{Tunnel}$ , $R_{Channel}$ , source resistance $R_S$ , and drain resistance $R_D$ . The temperature dependence of the tunneling current is mainly affected by the voltage drop on $R_{Tunnel}$ and $R_{Channel}$ .                                                                                                                                  | 32 |

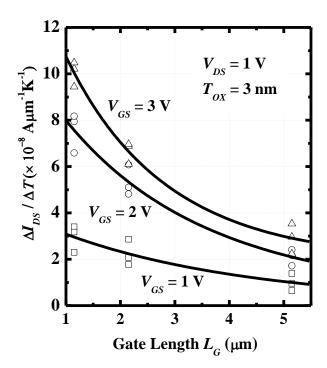

| Fig. 2.9.  | $\Delta I_{DS} / \Delta T$ as a function of $L_G$ at $V_{DS} = 1$ V. $\Delta I_{DS} / \Delta T$ decreases<br>with $L_G$ , and is attributed to an increased $R_{Channel}$ which reduces the<br>electric field at the tunneling junction for a given $V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

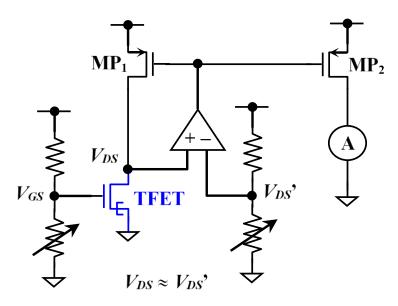

| Fig. 2.10. | Proposed temperature independent current biasing circuit. $V_{GS}$ of<br>the TFET is controlled by a voltage divider and $V_{DS}$ is<br>approximately equal to $V_{DS}$ '. The output current was measured<br>using a high-precision current meter at the drain terminal of MP <sub>2</sub> .<br>TFET device in this circuit has $L_G$ of 5.15 µm and width of 180 nm35                                                                                                                                                                                                                                                                                            |

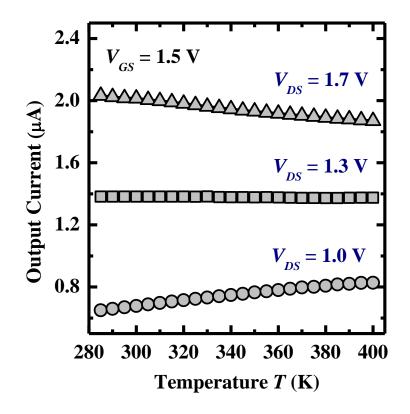

| Fig. 2.11. | Temperature dependency of the current biasing with various $V_{DS}$ at $V_{GS} = 1.5$ V. At $V_{DS} = 1.7$ V, the current biasing exhibits negative temperature coefficient, whereas it exhibits positive temperature coefficient at $V_{DS} = 1$ V. The output current is almost independent on temperature at $V_{DS} = 1.3$ V                                                                                                                                                                                                                                                                                                                                   |

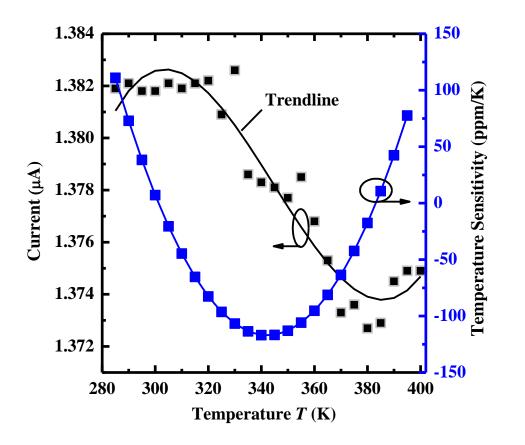

| Fig. 2.12. | Temperature dependency (left) and temperature sensitivity (right) of the current biasing at $V_{DS} = 1.3$ V and $V_{GS} = 1.5$ V. A low temperature sensitivity of $\pm 120$ ppm/K is achieved                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

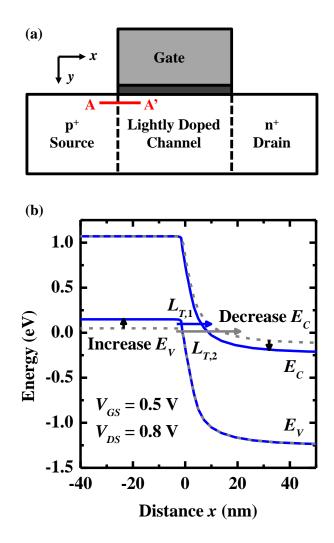

| Fig. 3.1.  | (a) Cross-sectional view of a TFET. (b) Energy band diagram along A-A' direction in the tunneling junction region of a TFET as indicated in (a). Increasing $E_V$ in the source and lowering $E_C$ in the channel can lead to a shorter tunneling path ( $L_{T,1} < L_{T,2}$ ), contributing to an improved drive current                                                                                                                                                                                                                                                                                                                                          |

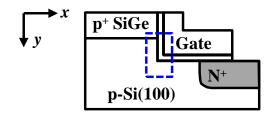

| Fig. 3.2.  | Schematics of (a) vertical TFET with $p^+$ Si <sub>0.5</sub> Ge <sub>0.5</sub> source and (b) TFET with Si <sub>0.5</sub> Ge <sub>0.5</sub> /Si <sub>0.989</sub> C <sub>0.011</sub> source. The thin Si <sub>0.989</sub> C <sub>0.011</sub> layer underneath the Si <sub>0.5</sub> Ge <sub>0.5</sub> is undoped                                                                                                                                                                                                                                                                                                                                                    |

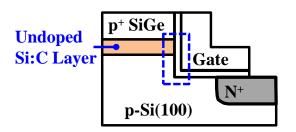

| Fig. 3.3.  | Lateral strain $\varepsilon_{xx}$ distribution for (a) TFET control device and (b)<br>TFET with Si <sub>0.5</sub> Ge <sub>0.5</sub> /Si <sub>0.989</sub> C <sub>0.011</sub> source for the dashed regions as<br>indicated in Fig. 3.2. The channel regions of these two structures<br>are highlighted in light yellow. Compressive strain is denoted by<br>negative sign. A higher tensile strain is induced in the Si <sub>0.989</sub> C <sub>0.011</sub><br>layer as compared to the Si channel in the TFET control device.<br>The tensile strain in Si <sub>0.989</sub> C <sub>0.011</sub> reduces the tunnel barrier and<br>enhances the tunneling probability |

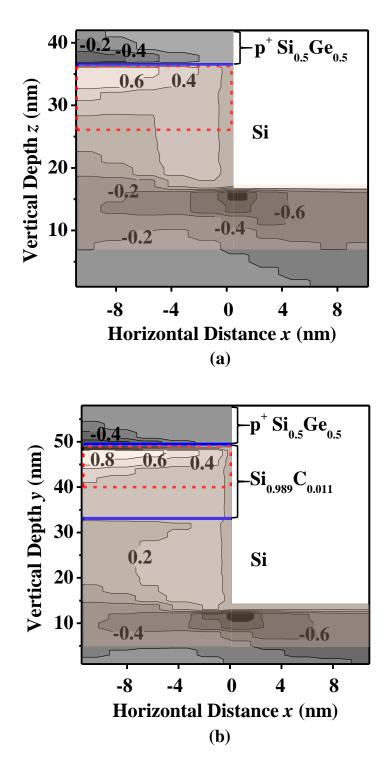

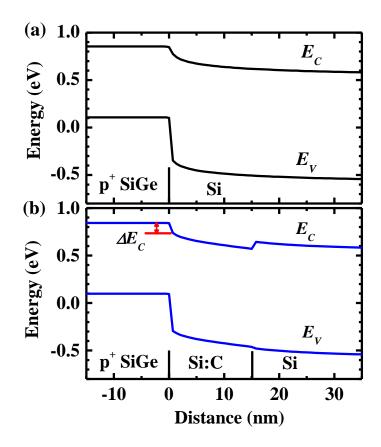

| Fig. 3.4.  | Energy band alignments of (a) $Si_{0.5}Ge_{0.5}/Si$ and (b) $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}/Si$ structures. The presence of substitutional C lowers the $E_C$ of $Si_{0.989}C_{0.011}$ by 79 meV by taking consideration of the ~0.5% biaxial tensile strain in the $Si_{0.989}C_{0.011}$ layer, which can contribute to $I_{ON}$ enhancement of TFET                                                                                                                                                                                                                                                                                                        |

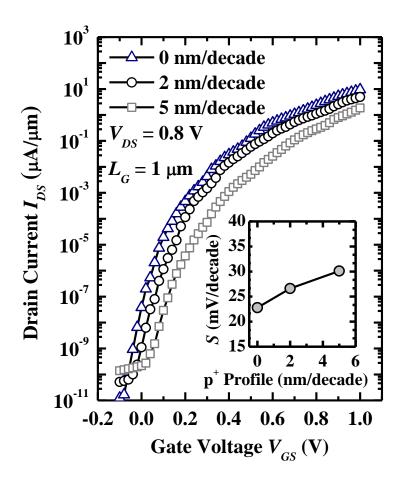

| Fig. 3.5.  | Simulated $I_{DS}$ - $V_{GS}$ curves of Si <sub>0.5</sub> Ge <sub>0.5</sub> source TFETs with different source doping profiles. The inset shows the minimum point <i>S</i> as a function of source doping profile. The diffusion of boron into the channel affects the $I_{ON}$ and <i>S</i> of the TFET                                                                                                                                                                                                                                                                                                                                                           |

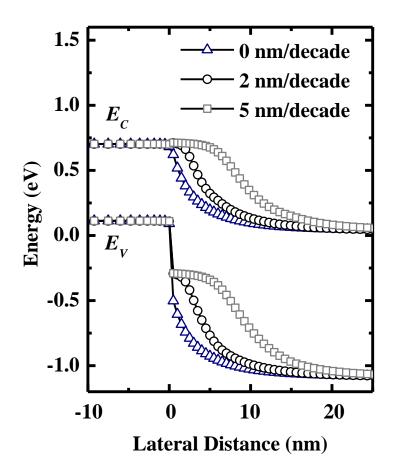

| Fig. 3.6.  | The energy band diagrams along source-to-channel direction for the devices in Fig. 3.5. As the source doping profile changes from 0 to 5 nm/decade, the tunneling width increases, which is responsible for the degradation of $I_{ON}$ and $S$                                                                                                                                                            | .49  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3.7.  | Simulated transfer characteristics of TFET control device and TFET with $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}$ source. A higher $I_{DS}$ is obtained by inserting a $Si_{0.989}C_{0.011}$ layer                                                                                                                                                                                                            | . 50 |

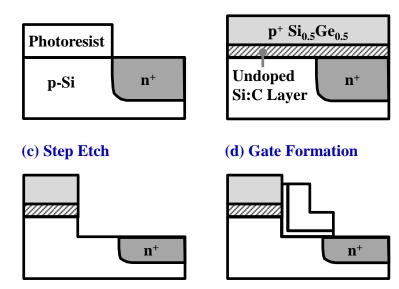

| Fig. 3.8.  | Key processing steps used to fabricate TFET with $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}$ source. TFET control device went through the same processing steps without the growth of the undoped $Si_{0.989}C_{0.011}$ layer.                                                                                                                                                                                  | .51  |

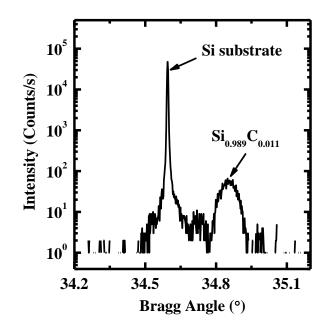

| Fig. 3.9.  | High-resolution XRD spectrum of a blanket Si sample with 40 nm thick Si:C layer. The substitutional carbon concentration was determined to be 1.1%. The well-defined $Si_{0.989}C_{0.011}$ peak indicates the high crystalline quality of the epitaxial $Si_{0.989}C_{0.011}$ film on Si.                                                                                                                  | .52  |

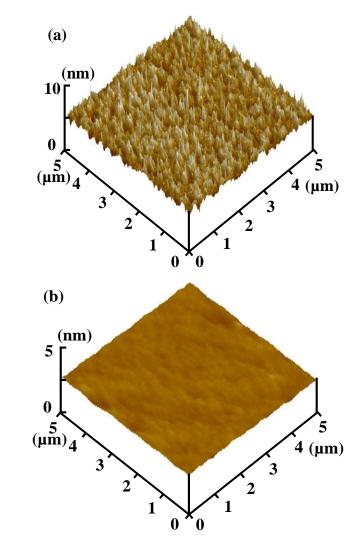

| Fig. 3.10. | AFM measurements of the Si surface roughness after the Cl <sub>2</sub> -based plasma etch that forms the elevated source. (a) RMS surface roughness for a 5 $\mu$ m × 5 $\mu$ m area is 2.46 nm using recipe A. (b) A smooth Si surface with RMS surface roughness of 0.19 nm was obtained by reducing the RF power and substrate bias.                                                                    | .53  |

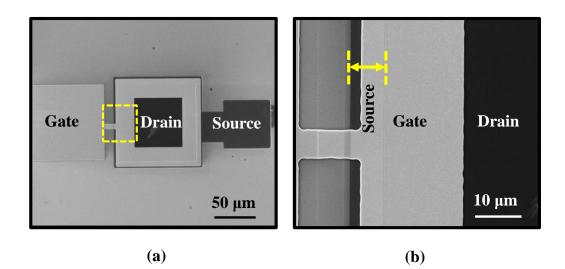

| Fig. 3.11. | (a) Top-view SEM image of a ring-type TFET with $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}$ source. (b) Zoomed-in view of the region highlighted by the dashed box in (a), which shows the source pattern of the TFET                                                                                                                                                                                           | .55  |

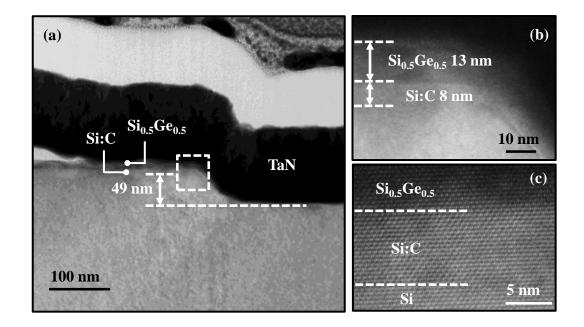

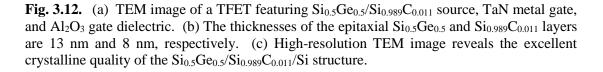

| Fig. 3.12. | (a) TEM image of a TFET featuring $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}$ source,<br>TaN metal gate, and $Al_2O_3$ gate dielectric. (b) The thicknesses of<br>the epitaxial $Si_{0.5}Ge_{0.5}$ and $Si_{0.989}C_{0.011}$ layers are 13 nm and 8 nm,<br>respectively. (c) High-resolution TEM image reveals the excellent<br>crystalline quality of the $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}/Si$ structure. | .55  |

| Fig. 3.13. | SIMS profiles for boron along the vertical direction in the source regions of TFETs with and without $Si_{0.989}C_{0.011}$ layer. TFET with $Si_{0.989}C_{0.011}$ layer achieves a steeper boron profile as compared to the TFET control device.                                                                                                                                                           | .56  |

| Fig. 3.14. | (a) Comparison of the transfer characteristics of TFET with $Si_{0.5}Ge_{0.5}/Si_{0.989}C_{0.011}$ source and TFET control device. Both devices have $L_G$ of 7 µm. (b) The output characteristics of the same pair of devices as shown in (a).                                                                                                                                                            | .57  |

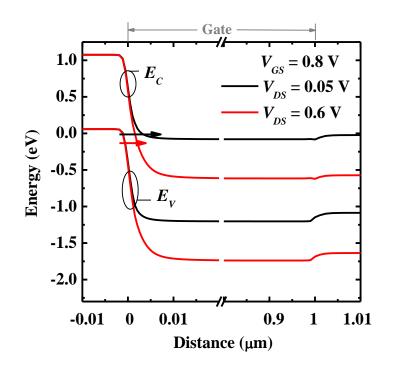

| Fig. 3.15. | Energy band diagram of a TFET along source-to-drain direction for $V_{DS} = 0.05$ V and $V_{DS} = 0.6$ V. The tunneling barrier width changes with $V_{DS}$ as shown by the black and red arrows.                                                                                                                                                                                                          | . 58 |

| Fig. 3.16. | Statistical plot of <i>I</i> <sub>ON</sub> for TFET with Si <sub>0.5</sub> Ge <sub>0.5</sub> /Si <sub>0.989</sub> C <sub>0.011</sub> source |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | and TFET control device. A ~20% enhancement of $I_{ON}$ is obtained                                                                         |    |

|            | due to the insertion of the $Si_{0.989}C_{0.011}$ layer between $p^+$ $Si_{0.5}Ge_{0.5}$                                                    |    |

|            | source and Si channel.                                                                                                                      | 59 |

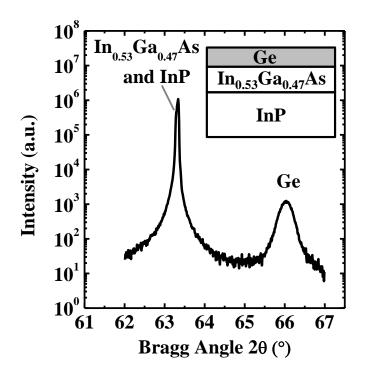

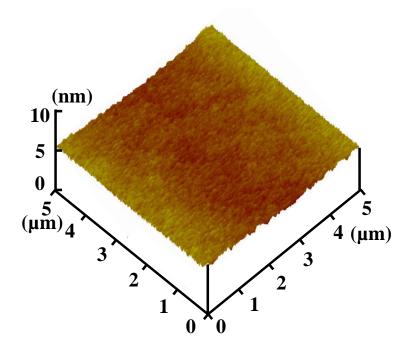

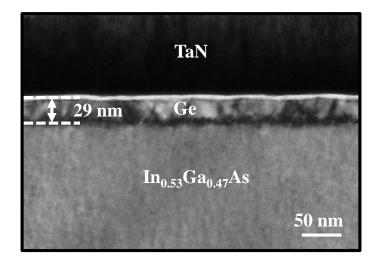

- **Fig. 4.6.** The RMS surface roughness for a 5  $\mu$ m × 5  $\mu$ m area is 0.54 nm, indicating that a smooth Ge surface was obtained......73

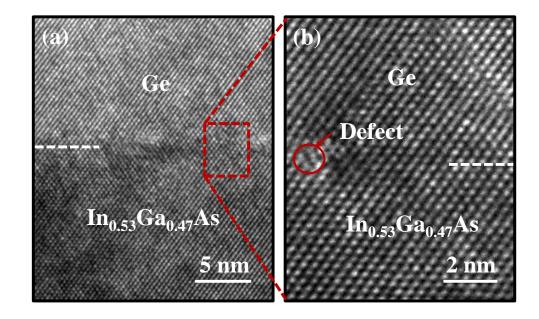

| Fig. 4.7.  | (a) High-resolution TEM image of 50 nm thick Ge epitaxially grown on $In_{0.53}Ga_{0.47}As$ substrate. (b) TEM image at the Ge/In_{0.53}Ga_{0.47}As interface indicated by the dashed box in (a). High quality Ge film was formed and defects were only observed at the interface                                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

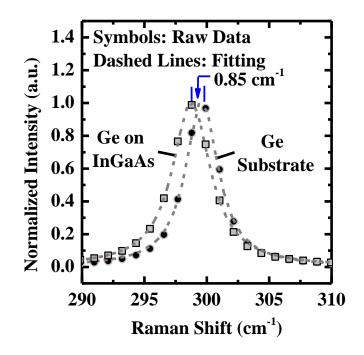

| Fig. 4.8.  | Raman spectra of a bulk Ge sample and an $In_{0.53}Ga_{0.47}As$ sample topped by 50 nm thick Ge film. Lorentzian functions were fitted to the spectra. The small shift of the Ge peak with respect to that of bulk Ge indicates the epitaxial Ge film is almost fully relaxed75                                                                                                                                                                           |

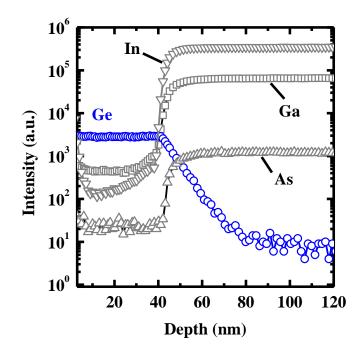

| Fig. 4.9.  | SIMS analysis of the Ge/In <sub>0.53</sub> Ga <sub>0.47</sub> As sample indicates that Ge atoms diffuse into In <sub>0.53</sub> Ga <sub>0.47</sub> As. As a result, an n-type In <sub>0.53</sub> Ga <sub>0.47</sub> As layer is formed at the Ge/In <sub>0.53</sub> Ga <sub>0.47</sub> As interface. This n-type layer enhances the lateral electric field at the tunneling junction, which can contribute to a higher TFET drive current75               |

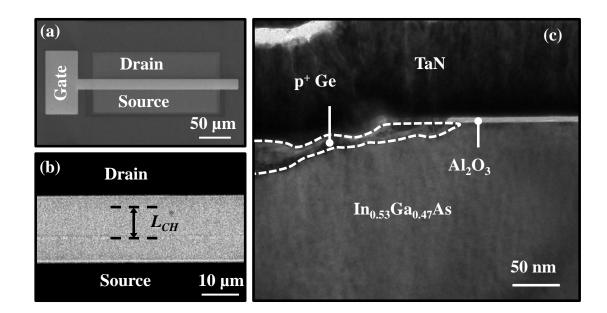

| Fig. 4.10. | (a) Top-view SEM image of a fabricated TFET. (b) Zoomed-in view of the same device in (a). The gate-to-source overlap $L_{OV,GS}$ of 5 µm is clearly observed. The channel length $L_{CH}$ is 8 µm. (c) TEM image of a fabricated TFET device showing the tunneling junction region                                                                                                                                                                       |

| Fig. 4.11. | TEM image of the gate-to-source overlap region. Ge film has a smooth surface on the etched In <sub>0.53</sub> Ga <sub>0.47</sub> As surface                                                                                                                                                                                                                                                                                                               |

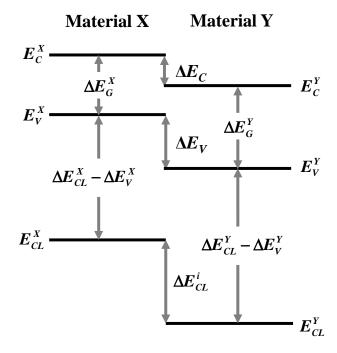

| Fig. 4.12. | Schematic illustrates the band alignment between material X and Y.<br>$\Delta E_V$ and $\Delta E_C$ between these two materials can be calculated using<br>the technique proposed by Kraut <i>et al.</i> [139]-[140]80                                                                                                                                                                                                                                    |

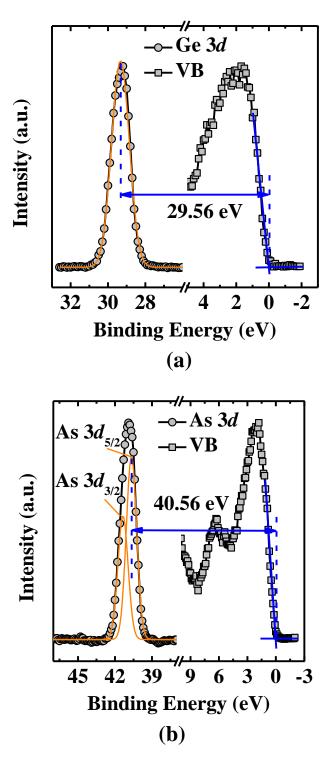

| Fig. 4.13. | (a) The Ge 3 <i>d</i> core-level and valence band spectra for 50 nm thick Ge on $In_{0.53}Ga_{0.47}As$ . (b) The As 3 <i>d</i> core-level and valence band spectra for $In_{0.53}Ga_{0.47}As$ reference sample. The valence band maximum is extrapolated from the intersection point between the leading edge of the valence band spectrum and the base line                                                                                              |

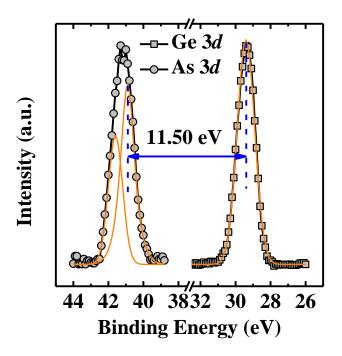

| Fig. 4.14. | The Ge 3 <i>d</i> and As 3 <i>d</i> core-level spectra from the Ge on $In_{0.53}Ga_{0.47}As$ sample after Ge was thinned down by Ar ion. Energy difference between the two core-levels is shown                                                                                                                                                                                                                                                           |

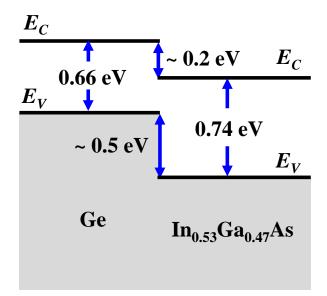

| Fig. 4.15. | The energy band alignment between Ge and $In_{0.53}Ga_{0.47}As$ is illustrated, showing the conduction band offset of $0.2 \pm 0.1$ eV and valence band offset of $0.5 \pm 0.1$ eV. The bandgap narrowing effect due to high doping concentration in Ge was taken into consideration                                                                                                                                                                      |

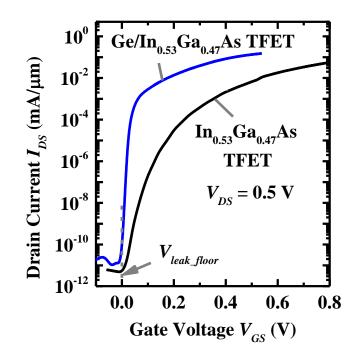

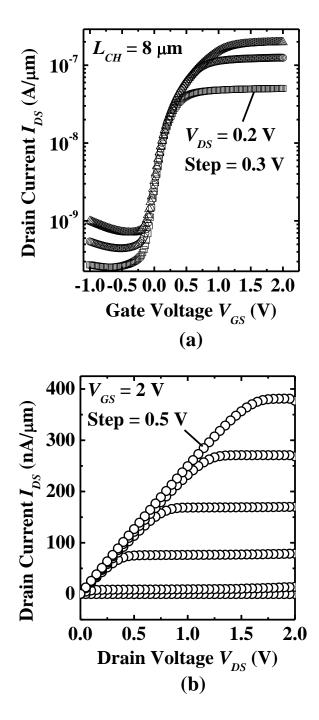

| Fig. 4.16. | $I_{DS}$ - $V_{GS}$ characteristics of a Ge-source In <sub>0.53</sub> Ga <sub>0.47</sub> As-channel<br>TFET with $L_{CH}$ of 8 µm. The $L_{OV,GS}$ and $L_{OV,GD}$ are 9 µm and 2 µm,<br>respectively. The minimum point S is ~177 mV/decade. (b) $I_{DS}$ -<br>$V_{DS}$ characteristics of the same device in (a). The device<br>performance can be further improved by optimizing the<br>Ge/In <sub>0.53</sub> Ga <sub>0.47</sub> As tunneling junction |

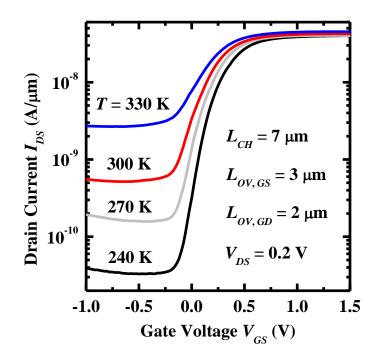

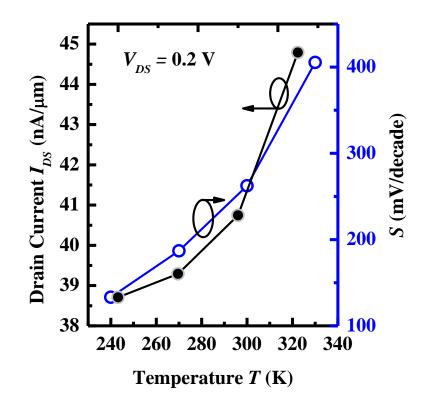

| Fig. 4.17. | $I_{DS}$ - $V_{GS}$ characteristics of a fabricated TFET under various temperatures ranging from 240 to 330 K in steps of 30 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

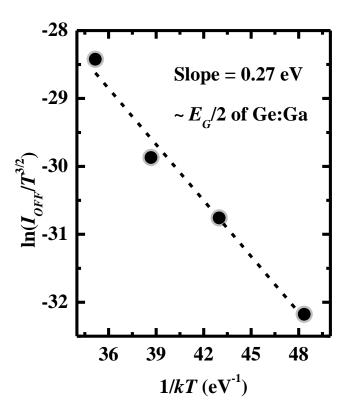

| Fig. 4.18. | Arrhenius plot of $\ln(I_{OFF}/T^{3/2})$ versus $1/kT$ . The slope of the fitted<br>line is ~0.27 eV, which corresponds to the half bandgap of Ge,<br>indicating the off-state leakage current floor is dominated by the<br>SRH generation-recombination current in the source side                                                                                                                                                                                                                                                                                                                                                                   |

| Fig. 4.19. | Plot of $I_{DS}$ and $S$ as a function of temperature. The $I_{DS}$ increases as temperature changes from 240 to 330 K, which is mainly due to the bandgap reduction. Due to the trap-assisted tunneling, $S$ has a positive temperature dependence. The discrepancy of the $S$ at room temperature between this transistor and the one in Fig. 4.16 is due to device-to-device variation.                                                                                                                                                                                                                                                            |

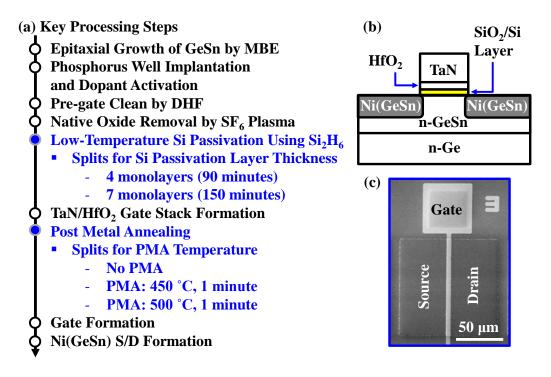

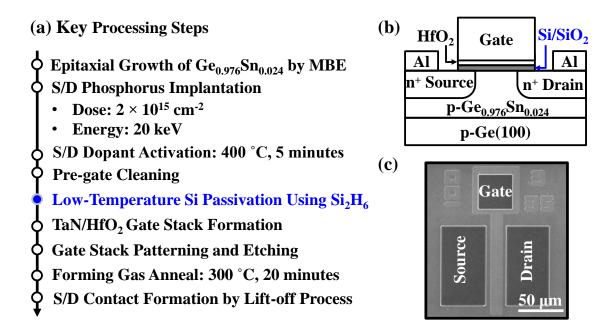

| Fig. 5.1.  | <ul> <li>(a) Key processing steps for the fabrication of a metallic S/D Ge<sub>0.97</sub>Sn<sub>0.03</sub> pMOSFET with low-temperature Si passivation. (b) Schematic shows the cross-sectional view of a GeSn pMOSFET.</li> <li>(c) Top-view SEM image of a fabricated GeSn pMOSFET with Si surface passivation</li></ul>                                                                                                                                                                                                                                                                                                                            |

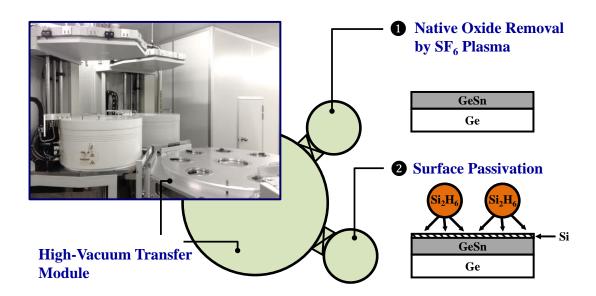

| Fig. 5.2.  | Schematic illustration of an UHVCVD system for Si surface<br>passivation. After pre-gate cleaning, wafers were quickly loaded<br>into the UHVCVD system. In the first chamber, the wafers were<br>cleaned in SF <sub>6</sub> plasma for native oxide removal and Si passivation<br>was performed in the second chamber. The high vacuum transfer<br>module serves to prevent native oxide formation during wafer<br>transfer                                                                                                                                                                                                                          |

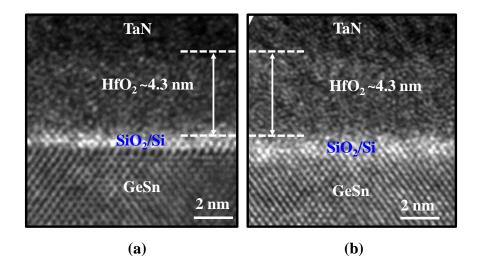

| Fig. 5.3.  | High-resolution cross-sectional TEM images of TaN/HfO <sub>2</sub> stack<br>formed on Si passivated $Ge_{0.97}Sn_{0.03}$ substrates with (a) 90 minutes<br>and (b) 150 minutes Si passivation. An ultrathin SiO <sub>2</sub> was formed<br>due to the partial oxidation of the Si passivation layer. The<br>thickness of the HfO <sub>2</sub> is ~4.3 nm                                                                                                                                                                                                                                                                                              |

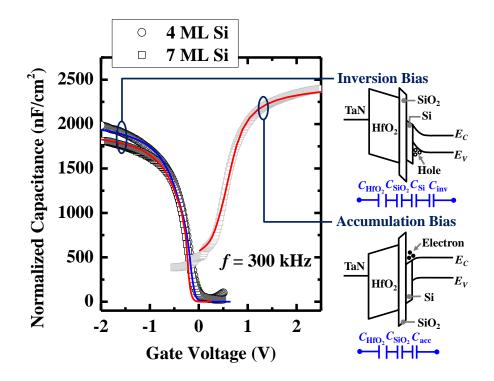

| Fig. 5.4.  | (a) Split <i>C</i> - <i>V</i> characteristics of the Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with 4<br>and 7 ML Si surface passivation layer. Characterization frequency<br><i>f</i> was 300 kHz. Measured data points are plotted as symbols. The<br>solid curves were obtained using a quantum-mechanical <i>C</i> - <i>V</i><br>simulator. The energy band diagrams along gate-to-channel<br>direction of a Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFET in the strong inversion and<br>accumulation regimes are shown. $E_C$ and $E_V$ in the energy band<br>diagrams are the conduction band edge and valence band edge,<br>respectively |

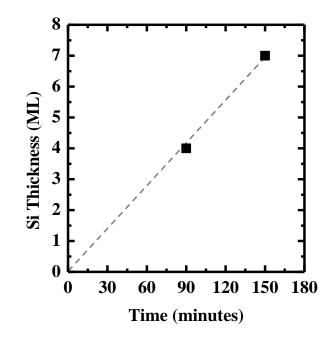

| Fig. 5.5.  | Plot of the Si layer thickness as a function of passivation time, from which the growth rate of the Si layer is calculated to be 2.7 ML per hour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

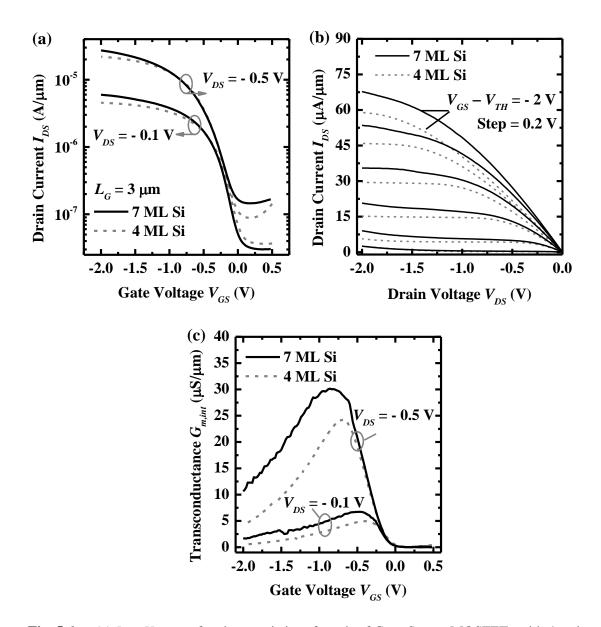

| Fig. 5.6.  | (a) $I_{DS}$ - $V_{GS}$ transfer characteristics of a pair of Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with 4 and 7 ML Si passivation layer. (b) $I_{DS}$ - $V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | characteristics of the same pair of devices in (a). Device with 7 ML<br>Si passivation layer exhibit a 10% enhancement in $I_{DS}$ at $V_{GS} - V_{TH}$<br>= $V_{DS} = -2$ V as compared to that with 4 ML Si passivation layer.<br>(c) $G_{m,int}$ versus $V_{GS}$ at $V_{DS}$ of $-0.1$ V and $-0.5$ V for the same<br>device in (a). Device with 7 ML Si passivation layer exhibits a<br>significant improvement in $G_{m,int}$ as compared to that with 4 ML Si<br>passivation layer                  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

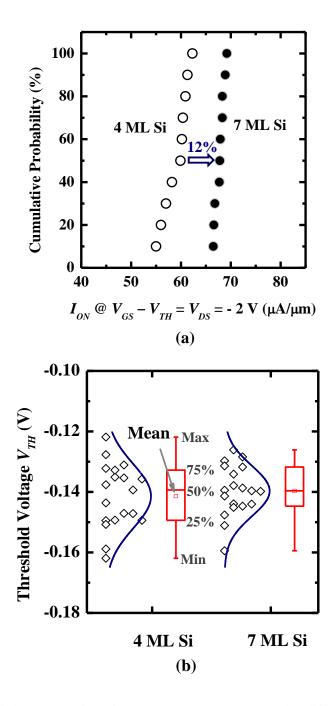

| Fig. 5.7.  | (a) Statistical plots of $I_{ON}$ for Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with different<br>Si passivation layer thicknesses. $I_{ON}$ is improved as the thickness<br>of Si passivation layer increases from 4 to 7 ML. 10 devices were<br>measured for each split. (b) $V_{TH}$ does not change with the Si<br>passivation layer thickness. This could possibly be explained by a<br>higher density of negative charges in the gate stack for devices with<br>7 ML Si passivation layer. 104 |

| Fig. 5.8.  | Plot of $\mu_{eff}$ versus $N_{inv}$ for Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs. Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with 7 ML Si passivation layer achieve 19% ± 4% enhancement in $\mu_{eff}$ at $N_{inv}$ of $1 \times 10^{13}$ cm <sup>-2</sup> as compared to devices with 4 ML Si passivation layer. The $\mu_{eff}$ was extracted using on a total resistance slope-based approach [179]. The mobility curves were extracted using a few pair of devices                        |

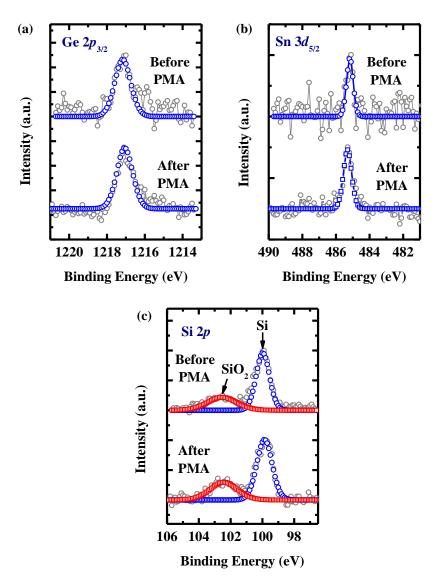

| Fig. 5.9.  | High-resolution XPS spectra reveal the bonding structure at the HfO <sub>2</sub> /SiO <sub>2</sub> /Si/GeSn interfaces. The grey circles show the raw data and the blue and red symbols are obtained by curve fitting. Ge $2p_{3/2}$ spectra in (a) and Sn $3d_{5/2}$ spectra in (b) show the suppression of Ge-O and Sn-O bonds, contributing to the improved interfacial quality. (c) The existence of both Si-Si and Si-O bonds indicates the Si passivation layer was partially oxidized              |

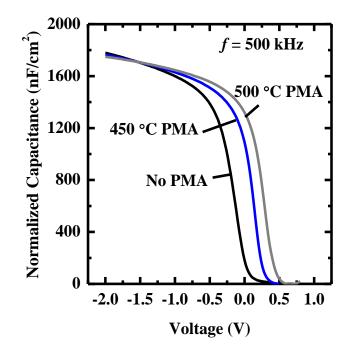

| Fig. 5.10. | Comparison of inversion $C$ - $V$ curves among the Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with and without PMA. Negligible differences in the gate capacitance in the inversion regime are observed110                                                                                                                                                                                                                                                                                            |

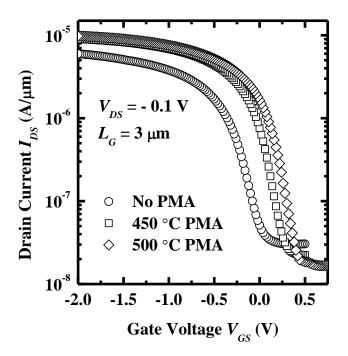

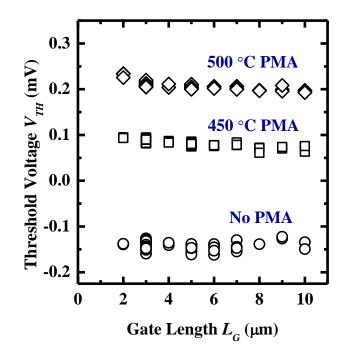

| Fig. 5.11. | $I_{DS}$ - $V_{GS}$ characteristics of the Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with no<br>PMA, 450 °C PMA, and 500 °C PMA. The $L_G$ and $W$ of these<br>devices are 3 µm and 100 µm, respectively. Both drive current and<br>S are improved for devices with PMA. In addition, PMA causes<br>$V_{TH}$ to shift towards positive direction                                                                                                                                                     |

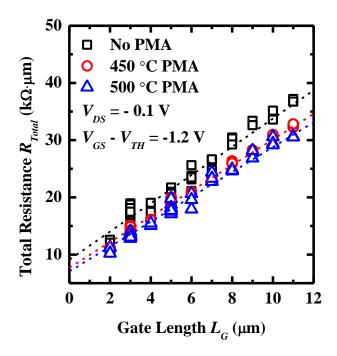

| Fig. 5.12. | $R_{Total}$ as a function of $L_G$ at $V_G - V_{TH}$ of - 1.2 V and $V_{DS}$ of - 0.1 V.<br>Experimental data points are plotted using symbols. Fitted lines are<br>drawn using dashed lines. The slight difference in the S/D series<br>resistance could be due to process variations                                                                                                                                                                                                                    |

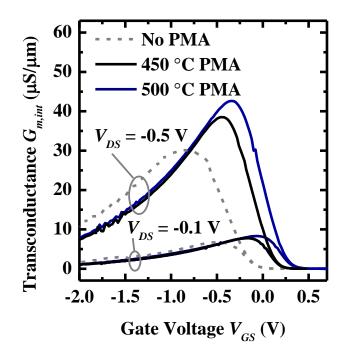

| Fig. 5.13. | $G_{m,int}$ for Ge <sub>0.97</sub> Sn <sub>0.03</sub> pMOSFETs with no PMA, 450 °C PMA, and 500 °C PMA. Peak $G_{m,int}$ was enhanced for the devices with PMA, indicating the improvement of the gate stack quality                                                                                                                                                                                                                                                                                      |

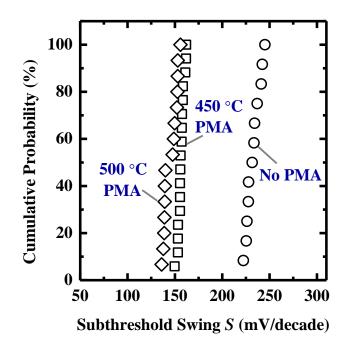

- Fig. 5.14. Statistical plot of *S* for  $Ge_{0.97}Sn_{0.03}$  pMOSFETs with and without PMA. The median *S* for the devices without PMA is 227 mV/decade. For the devices with 450 °C PMA, the median *S* reduces to 158 mV/decade and it further improves to 148 mV/decade when the PMA temperature increases to 500 °C. The reduction in *S* indicates that the mid-gap interface state density decreases due to PMA.

- Fig. 5.20. AFM image shows that the RMS surface roughness of the  $Ge_{0.976}Sn_{0.024}$  film is 0.37 nm over a 10 µm × 10 µm scanning area. .... 121

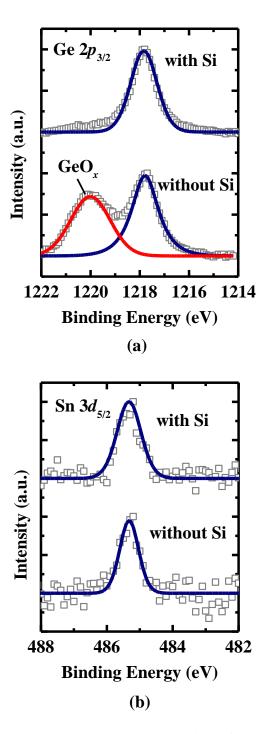

- **Fig. 5.22.** (a) Ge  $2p_{3/2}$  and (b) Sn  $3d_{5/2}$  spectra obtained from XPS to investigate the interfacial chemical bonding between high-*k* dielectric and Ge<sub>0.976</sub>Sn<sub>0.024</sub>. The open squares show the raw data and the solid lines are the fitting curves. Ge-O bonds are observed in the Ge  $2p_{3/2}$  spectrum from the sample without Si passivation, whereas no Ge-O is observed in the sample with Si passivation. This provides clear evidence that Si passivation eliminates the

|            | formation of Ge-O bond. No Sn-O peak is observed from the Sn $3d_{5/2}$ spectra for Ge <sub>0.976</sub> Sn <sub>0.024</sub> samples with and without Si passivation. 123                                                                                                                                                                                                                                                                                   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

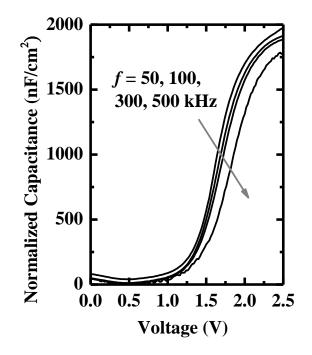

| Fig. 5.23. | Inversion <i>C</i> - <i>V</i> characteristics of a $Ge_{0.976}Sn_{0.024}$ nMOSFET. The large frequency dispersion indicates the existence of high density of fast trap charges in the gate stack                                                                                                                                                                                                                                                           |

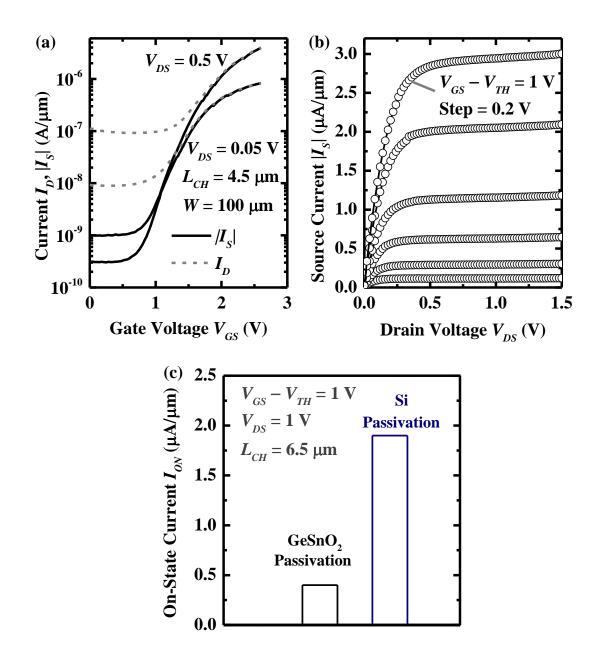

| Fig. 5.24. | (a) $I_D - V_{GS}$ and $ I_S  - V_{GS}$ transfer characteristics of a typical Ge <sub>0.976</sub> Sn <sub>0.024</sub> nMOSFET with $L_{CH}$ of 4.5 µm. The <i>S</i> of this device is ~230 mV/decade. (b) The $ I_S  - V_{DS}$ characteristics of the same device in (a). Good saturation behavior is observed. (c) Device with Si passivation shows a higher $I_{ON}$ as compared to that with GeSnO <sub>2</sub> passivation at the same bias conditions |

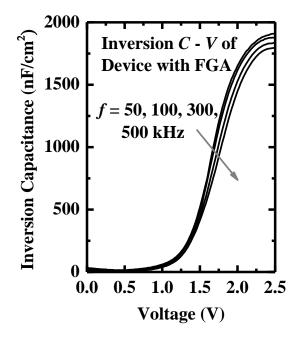

| Fig. 5.25. | Inversion <i>C</i> - <i>V</i> characteristics of a Ge <sub>0.976</sub> Sn <sub>0.024</sub> nMOSFET with FGA. Passivation of interfacial dangling bonds and bulk traps in HfO <sub>2</sub> by hydrogen during FGA contributes to a smaller frequency dispersion as compared to device without FGA (Fig. 5.23)                                                                                                                                               |

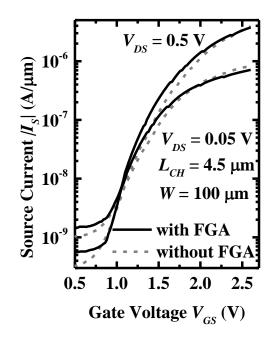

| Fig. 5.26. | The transfer characteristics of $Ge_{0.976}Sn_{0.024}$ nMOSFETs with and without FGA. It is observed that <i>S</i> improves from ~230 mV/decade to ~190 mV/decade by performing FGA                                                                                                                                                                                                                                                                        |

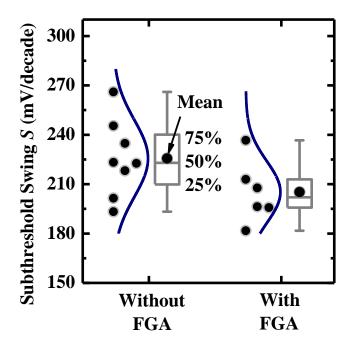

| Fig. 5.27. | Statistical plot shows the <i>S</i> enhancement due to FGA. The mean <i>S</i> of the $Ge_{0.976}Sn_{0.024}$ nMOSFETs with FGA is 200 mV/decade. This is 10% lower as compared to that of devices without FGA128                                                                                                                                                                                                                                            |

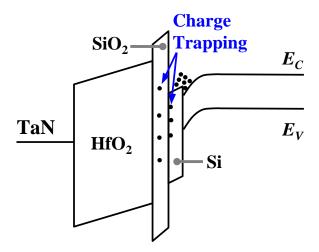

| Fig. 5.28. | Schematic of the energy band diagram along the gate-to-channel direction of a $Ge_{0.976}Sn_{0.024}$ nMOSFET in the strong inversion regime. The trapped charges can degrade the electron mobility due to Coulomb scattering                                                                                                                                                                                                                               |

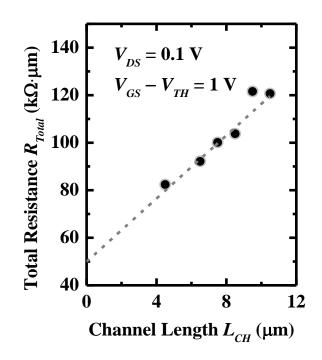

| Fig. 5.29. | Plot of $R_{total}$ versus $L_{CH}$ for Ge <sub>0.976</sub> Sn <sub>0.024</sub> nMOSFETs at $V_{DS} = 0.1$ V and $V_{GS} - V_{TH} = -1$ V. The high S/D resistance limits the drive current of the transistors                                                                                                                                                                                                                                             |

## List of Symbols

| Symbol           | Description                                    | Unit                              |

|------------------|------------------------------------------------|-----------------------------------|

| $A_G$            | Gate area                                      | cm <sup>2</sup>                   |

| а                | Distance between inner and outer rods          | cm                                |

| С                | Capacitance                                    | F/cm <sup>2</sup>                 |

| $C_{11}$         | Elastic constant                               | Pa                                |

| $C_{12}$         | Elastic constant                               | Pa                                |

| $C_{acc}$        | Capacitance in the accumulation layer          | F/cm <sup>2</sup>                 |

| $C_D$            | Depletion capacitance                          | F/cm <sup>2</sup>                 |

| $C_{ m HfO_2}$   | Capacitance due to HfO <sub>2</sub>            | F/cm <sup>2</sup>                 |

| $C_{inv}$        | Capacitance in the inversion layer             | F/cm <sup>2</sup>                 |

| $C_{it}$         | Capacitance associated with interface traps    | F/cm <sup>2</sup>                 |

| $C_{OX}$         | Gate oxide capacitance                         | F/cm <sup>2</sup>                 |

| $C_{ m Si}$      | Capacitance due to Si                          | F/cm <sup>2</sup>                 |

| $C_{{ m SiO}_2}$ | Capacitance due to SiO <sub>2</sub>            | F/cm <sup>2</sup>                 |

| $D_{it}$         | Interface trap density                         | cm <sup>-2</sup> eV <sup>-1</sup> |

| Ε                | Electron energy                                | eV                                |

| $E_C$            | Energy of conduction band edge                 | eV                                |

| $E_{CL}$         | Binding energy of the core-level electron      | eV                                |

| $E_G$            | Bandgap                                        | eV                                |

| $E_V$            | Energy of valence band edge                    | eV                                |

| f                | Frequency                                      | Hz                                |

| $F_C$            | Fermi-Dirac distribution function for electron | -                                 |

| $F_V$            | Fermi-Dirac distribution function for hole     | -                                 |

| GBTBT            | Band-to-band tunneling generation rate         | $\mathrm{cm}^{-3}\mathrm{s}^{-1}$ |

| $G_{m,int}$      | Intrinsic transconductance                     | S/µm                              |

| $g_c$            | Density of states in the conduction band       | eV <sup>-1</sup> cm <sup>-3</sup> |

| $g_{v}$          | Density of states in the valence band          | eV <sup>-1</sup> cm <sup>-3</sup> |

| ħ                           | Reduced Planck's constant                 | eV∙s             |

|-----------------------------|-------------------------------------------|------------------|

| I <sub>BTBT</sub>           | Band-to-band tunneling current            | А                |

| ICP                         | Charge pumping current                    | А                |

| $I_D$                       | Drain current                             | A/µm             |

| IDS                         | Drain-to-source current                   | A/µm             |

| I <sub>DSat</sub>           | Saturation drain current                  | A/µm             |

| I <sub>DS,max</sub>         | Largest output current                    | А                |

| I <sub>DS,min</sub>         | Smallest output current                   | А                |

| I <sub>DS,nom</sub>         | Nominal output current                    | А                |

| Ioff                        | Off-state current                         | A/µm             |

| $I_{ON}$                    | On-state current                          | A/µm             |

| $I_S$                       | Source current                            | A/µm             |

| k                           | Boltzmann constant                        | eV/K             |

| L                           | Distance between the two outer rods       | cm               |

| L <sub>CH</sub>             | Channel length                            | μm               |

| $L_G$                       | Gate length                               | μm               |

| Lov,gd                      | Length of gate-to-drain overlap           | μm               |

| Lov,GS                      | Length of gate-to-source overlap          | μm               |

| $L_T$                       | Length of tunneling path                  | nm               |

| $m_e^*$                     | Electron effective mass                   | kg               |

| $m_h^*$                     | Hole effective mass                       | kg               |

| m <sub>r</sub>              | Reduced tunneling mass                    | kg               |

| n                           | Electron concentration                    | cm <sup>-3</sup> |

| N <sub>A</sub>              | Acceptor concentration                    | cm <sup>-3</sup> |

| Ninv                        | Inversion carrier density                 | cm <sup>-2</sup> |

| $N_D$                       | Donor concentration                       | cm <sup>-3</sup> |

| ni                          | Intrinsic carrier concentration           | cm <sup>-3</sup> |

| $n_s$                       | Surface concentration of minority carrier | cm <sup>-3</sup> |

| PActive                     | Active Power                              | W                |

| P <sub>Passive</sub>        | Passive Power                             | W                |

| $Q_f$                       | Fixed oxide charge                        | С                |

| q                           | Elementary charge                         | С                |

| <b>R</b> <sub>Channel</sub> | Channel resistance                        | Ω                |

| $R_D$                       | Drain resistance                          | Ω                |

|                             |                                           |                  |

| $R_S$                     | Source resistance                                                                | Ω                |

|---------------------------|----------------------------------------------------------------------------------|------------------|

| <b>R</b> <sub>total</sub> | Total resistance                                                                 | Ω                |

| R <sub>Tunnel</sub>       | Tunneling junction resistance                                                    | Ω                |

| $r_c$                     | Backscattering coefficient                                                       | -                |

| S                         | Subthreshold swing                                                               | mV/decade        |

| $S_{T,eff}$               | Effective temperature sensitivity                                                | ppm/K            |

| t                         | Thickness                                                                        | μm               |

| Т                         | Temperature                                                                      | Κ                |

| $t_f$                     | Fall time                                                                        | S                |

| $T_{\rm max}$             | Maximum of the applied temperature                                               | Κ                |

| $T_{\min}$                | Minimum of the applied temperature                                               | Κ                |

| $T_{OX}$                  | Thickness of SiO <sub>2</sub>                                                    | nm               |

| $t_r$                     | Rise time                                                                        | S                |

| V                         | Voltage                                                                          | V                |

| $V_a$                     | Voltage amplitude                                                                | V                |

| $V_{base}$                | Base level voltage                                                               | V                |

| $V_{DD}$                  | Supply voltage                                                                   | V                |

| $V_{DS}$                  | Drain voltage                                                                    | V                |

| $V_{FB}$                  | Flatband voltage                                                                 | V                |

| $V_{GS}$                  | Gate voltage                                                                     | V                |

| $V_{leak\_floor}$         | Maximum gate voltage in the off-<br>state leakge floor region                    | V                |

| $V_{TH}$                  | Threshold voltage                                                                | V                |

| $\mathcal{V}_T$           | Thermal velocity                                                                 | m/s              |

| W                         | Gate width                                                                       | μm               |

| Y                         | Young's modulus                                                                  | Pa               |

| У                         | Vertical displacement                                                            | cm               |

| $\Delta \omega$           | Raman shift                                                                      | cm <sup>-1</sup> |

| $\Delta E_C$              | Conduction band offset                                                           | eV               |

| $\Delta E_G$              | Bandgap narrowing                                                                | eV               |

| $\Delta E_{CL}^{i}$       | Core-level binding energy different<br>between two materials at the<br>interface | eV               |

| $\Delta E_V$              | Valence band offset                                                              | eV               |

| $\Delta I_{DS}$           | Change in drain current                                                          | $\mu A/\mu m$    |

|                           |                                                                                  |                  |

| $\Delta L_G$       | Difference in the gate length      | μm               |

|--------------------|------------------------------------|------------------|

| $\Delta R_{total}$ | Difference in the total resistance | Ω                |

| Etension           | Uniaxial tensile strain            | -                |

| <i>E//</i>         | Biaxial tensile strain             | -                |

| $\mathcal{E}_{XX}$ | Lateral strain                     | -                |

| $\mu_{e\!f\!f}$    | Effective mobility                 | $cm^2/V \cdot s$ |

| ξ                  | Electric field                     | V/cm             |

| $\xi_{e\!f\!f}$    | Effective vertical electric field  | V/cm             |

| σ                  | Stress                             | Pa               |

| $\sigma_n$         | Capture cross section of electron  | cm <sup>-2</sup> |

| $\sigma_p$         | Capture cross section of hole      | cm <sup>-2</sup> |

| $	au_d$            | Time delay                         | S                |

| $\omega_o$         | Raman frequency in bulk sample     | $cm^{-1}$        |

|                    |                                    |                  |

## List of Abbreviations

| AFM              | Atomic force microscopy                     |

|------------------|---------------------------------------------|

| Ag               | Silver                                      |

| $Al_2O_3$        | Aluminum oxide                              |

| Al               | Aluminum                                    |

| ALD              | Atomic layer deposition                     |

| As               | Arsenic                                     |

| AsH <sub>3</sub> | Arsine                                      |

| Au               | Gold                                        |

| BJT              | Bipolar junction transistor                 |

| BOE              | Buffered oxide etch                         |

| BTBT             | Band-to-band tunneling                      |

| С                | Carbon                                      |

| CET              | Capacitance equivalent thickness            |

| $Cl_2$           | Chlorine                                    |

| CMOS             | Complementary metal-oxide-semiconductor     |

| Cu               | Copper                                      |

| DHF              | Dilute hydrofluoric acid                    |

| DOS              | Density-of-states                           |

| EOT              | Equivalent oxide thickness                  |

| FB-FET           | Feedback field-effect transistor            |

| FGA              | Forming gas annealing                       |

| Ga               | Gallium                                     |

| Ge               | Germanium                                   |

| GeH <sub>4</sub> | Germane                                     |

| GeSn             | Germanium-tin                               |

| $H_2O_2$         | Hydrogen peroxide                           |

| $H_2SO_4$        | Sulfuric acid                               |

| HCl              | Hydrochloric acid                           |

| HfO <sub>2</sub> | Hafnium dioxide                             |

| HH               | Heavy-hole                                  |

| IC               | Integrated circuit                          |

| I-MOS            | Impact-ionization metal-oxide-semiconductor |

|                  |                                             |

| ITRS                           | International Technology Roadmap for Semiconductors             |

|--------------------------------|-----------------------------------------------------------------|

| LH                             | Light-hole                                                      |

| MBE                            | Molecular beam epitaxy                                          |

| ML                             | Monolayer                                                       |

| MOCVD                          | Metal-organic chemical vapor deposition                         |

| MOSFET                         | Metal-oxide-semiconductor field-effect transistor               |

| $N_2$                          | Nitrogen                                                        |

| NH4OH                          | Ammonium hydroxide                                              |

| Ni                             | Nickel                                                          |

| Ni(GeSn)                       | Nickel stanogermanide                                           |

| nMOSFET                        | N-channel metal-oxide-semiconductor field-<br>effect transistor |

| nTFET                          | N-channel tunneling field-effect transistor                     |

| PECVD                          | Plasma enhanced chemical vapor deposition                       |

| PMA                            | Post metal annealing                                            |

| pMOSFET                        | P-channel metal-oxide-semiconductor field-<br>effect transistor |

| RMS                            | Root-mean-square                                                |

| RTA                            | Rapid thermal annealing                                         |

| sccm                           | Standard cubic centimeters per minute                           |

| SEM                            | Scanning electron microscope                                    |

| $SF_6$                         | Sulfuric hexafluoride                                           |

| Si                             | Silicon                                                         |

| Si <sub>2</sub> H <sub>6</sub> | Disilane                                                        |

| Si <sub>3</sub> H <sub>8</sub> | Trisilane                                                       |

| SiGe                           | Silicon-germanium                                               |

| SIMS                           | Secondary ion mass spectrometry                                 |

| SiO <sub>2</sub>               | Silicon dioxide                                                 |

| Sn                             | Tin                                                             |

| SO                             | Spin-orbit-split-hole                                           |

| SOI                            | Silicon-on-insulator                                            |

| SPM                            | Sulfuric peroxide mixture                                       |

| SRH                            | Shockley-Read-Hall                                              |

| STT                            | Surface tunnel transistor                                       |

| S/D                  | Source/drain                                |

|----------------------|---------------------------------------------|

| TaN                  | Tantalum nitride                            |

| TEM                  | Transmission electron microscope            |

| TFET                 | Tunneling field-effect transistor           |

| TMGa                 | Trimethylgallium                            |

| UHVCVD               | Ultra-high-vacuum chemical vapor deposition |

| VB                   | Valence band                                |

| XRD                  | X-ray diffraction                           |

| XPS                  | X-ray photoelectron spectroscopy            |

| (NH4) <sub>2</sub> S | Ammonia sulfide                             |

### **Chapter 1**

#### Introduction

#### 1.1 Background

Continuous scaling of the complementary metal-oxide-semiconductor (CMOS) devices has allowed the number of transistors in an integrated circuit (IC) to approximately double every two years [1]. While the scaling enables higher packaging density per unit chip area and increased circuit speed, it also causes high power consumption in an IC chip, which has become a serious issue as the technology advances [2]-[3]. The power consumption of an IC has two components, active power  $P_{Active}$  and passive power  $P_{Passive}$ , which are given by

$$P_{Active} \propto V_{DD}^2 \cdot f , \qquad (1.1)$$

$$P_{Passive} \propto I_{OFF} \cdot V_{DD}, \qquad (1.2)$$

where  $V_{DD}$  is the supply voltage, *f* is the frequency of the circuit, and  $I_{OFF}$  is the offstate current of a transistor. Because both  $P_{Active}$  and  $P_{Passive}$  strongly depend on  $V_{DD}$ , scaling-down of  $V_{DD}$  is the most effective approach to reduce the power consumption. However, it should be noted that the reduction of  $V_{DD}$  alone will cause a decrease in on-state current  $I_{ON}$ . As a result, the switching speed of the circuit will be lowered as the switching speed is inversely proportional to the time delay  $\tau_d$ , which is given by

$$\tau_d \propto \frac{V_{DD}}{I_{ON}}.$$

(1.3)

Therefore,  $V_{DD}$  reduction without compromising  $I_{ON}$  is compulsory for future low power logic applications. For this purpose, two promising technical approaches are explored in this thesis. The first one is to use novel transistors with steep switching characteristics. Another approach is to use devices with high-mobility channel materials. In the following sections, the technological relevance of these two approaches will be discussed in detail.

#### **1.2** Transistor with Steep Switching Characteristics