## **TOPOLOGY STUDIES AND CONTROL**

## OF MICROINVERTERS FOR PHOTOVOLTAIC

## APPLICATION

Li Yanlin

NATIONAL UNIVERSITY OF SINGAPORE

2013

# Topology Studies and Control of Microinverters for Photovoltaic Applications

### Li Yanlin

(B.Eng., University of Electronic Science & Technology of China, China)

#### A THESIS SUBMITTED

# FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### DEPARMENT OF ELECTRICAL AND COMPUTER ENGINEERING

#### NATIONAL UNIVERSITY OF SINGAPORE

2013

### DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

The thesis has also not been submitted for any degree in any university previously.

Janti

Li Yanlin 08 Jan. 2013

1.1.

### ACKNOWLEDGEMENTS

First of all, I would like to express my deepest gratitude to my supervisor Prof. Ramesh Oruganti for his constant guidance, sustaining encouragement and stimulating suggestions all through my doctoral research. This work will never come to an end without his continuous guidance and support. He was always there to help me when I was stopped by various research obstacles or when I got obsessed with problems but forgot to move on. I would also like to express my sincere thanks to him for his patience during my learning years. As an experienced advisor, he was always there to help me to reduce stress due to my challenging research, to advise research schedules and to provide opportunities for me to attend conferences and future career. I would like to thank for his considerateness and kindness to me. I learnt a lot from him not only to be a precise researcher but also to be a nice person.

I would also like to thank Prof. Liew Ah Choy for his support and help in setting up my research test.

Besides, I would like to express my gratitude to Prof. Panda, Prof. Ashwin M Khambadkone, Prof. Liang and Prof. Akshay Kumar Rathore for their valuable comment and suggestions.

I am grateful to lab officers Mr. Teo Thiam Teck, Mr. Woo Ying Chee, Mr. Chandra, Mr. Seow Hung Cheng and Mr. Looi for their kind help whenever I have troubles. Special thanks go to Mr. Abdul Jalil Bin Din for his prompt PCB fabrication services My stay in the Power Electronics Lab of NUS was made pleasant by many of my fellow research scholars. Foremost among them is Krishna Mainali, who not only shares with me his knowledge, but also his happiness. I would also like to thank Dr. Yin Bo, Dr. Deng Heng, Dr. Ravinder Pal Singh, Dr. Prasanna, Dr. Chen Yu, Dr. Zhou Haihua, Dr. Wu Xinhui, Dr. Viswanathan Kanakasabai, Dr. Sahoo S. K., Dr. Tanmoy, Htay, Yu Xiaoxiao and other friends who take care of me and support me. I treasured all precious moments we shared together and would like to thank them all.

Deep in my heart are special thanks to my parents for providing me a shelter from rain and storms. Their love has accompanied me through bad and good moments.

## **TABLE OF CONTENTS**

| CHAPTER 1:INTRODUCTION                                   | 1  |

|----------------------------------------------------------|----|

| 1.1 BACKGROUND                                           | 1  |

| 1.2 INTRODUCTION TO MICROINVERTER                        | 6  |

| 1.2.1. Power Processing Requirements                     | 8  |

| 1.2.2. Power Control Requirements                        | 10 |

| 1.3 MOTIVATION FOR THE PRESENT WORK                      | 16 |

| 1.4 Research Objectives & Thesis Contributions           | 20 |

| 1.4.1 Research Objectives                                | 20 |

| 1.4.2 Thesis Contributions                               | 21 |

| 1.5 Thesis Organization                                  | 23 |

| CHAPTER 2:LITERATURE SURVEY OF MICROINVERT               | ER |

| TOPOLOGIES                                               | 25 |

| 2.1 INTRODUCTION                                         | 25 |

| 2.2 LITERATURE SURVEY OF MICROINVERTER TOPOLOGIES        | 25 |

| 2.2.1. Transformerless Microinverter                     | 30 |

| 2.2.2. Microinverter with HF transformer                 | 34 |

| 2.2.3. Major Trends in Microinverter Research            | 51 |

| 2.3 LITERATURE SURVEY OF ACTIVE POWER DECOUPLING SCHEMES | 54 |

| 2.3.1. Power Decoupling Requirement                      | 57 |

| 2.3.2. APD solutions using DC link Capacitor             | 60 |

| 2.3.3. APD solutions using AC link Capacitor             | 66 |

| 2.3.4. Discussion of the APD Schemes                     | 68 |

| 2.4 Conclusions                                          | 69 |

| CHAPTER 3:AN IMPROVED SINGLE STAGE SCHEME:               | A  |

| FLYBACK-CCM INVERTER                                     | 71 |

| 3.1 INTRODUCTION                                         | 71 |

| 3.2 Overv                                                                                                                                                                                                                   | IEW – A POPULAR FLYBACK INVERTER                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3 Design                                                                                                                                                                                                                  | N OF INPUT CAPACITORS AT PV SIDE                                                                                                                                                                                                                                                                                                                                  |

| 3.3.1. M                                                                                                                                                                                                                    | PPT Requirement                                                                                                                                                                                                                                                                                                                                                   |

| 3.3.2. O                                                                                                                                                                                                                    | utput Power Quality Requirement                                                                                                                                                                                                                                                                                                                                   |

| 3.4 Analy                                                                                                                                                                                                                   | SIS AND DESIGN OF THE FLYBACK INVERTER                                                                                                                                                                                                                                                                                                                            |

| 3.4.1. Q                                                                                                                                                                                                                    | uasi-steady State Analysis                                                                                                                                                                                                                                                                                                                                        |

| 3.4.2. D                                                                                                                                                                                                                    | esign and Control of a Flyback-DCM Inverter                                                                                                                                                                                                                                                                                                                       |

| 3.4.3. D                                                                                                                                                                                                                    | esign of a Flyback-CCM Inverter                                                                                                                                                                                                                                                                                                                                   |

| 3.4.4. O                                                                                                                                                                                                                    | utput Current Power Factor                                                                                                                                                                                                                                                                                                                                        |

| 3.5 IMPLEN                                                                                                                                                                                                                  | MENTATIONS AND EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                                                               |

| 3.5.1. H                                                                                                                                                                                                                    | ardware Implementations103                                                                                                                                                                                                                                                                                                                                        |

| 3.5.2. D                                                                                                                                                                                                                    | C-DC Conversion with DC Voltage Load105                                                                                                                                                                                                                                                                                                                           |

| 3.5.3. D                                                                                                                                                                                                                    | C-AC Conversion with AC Voltage Load112                                                                                                                                                                                                                                                                                                                           |

| 3.6 CONCL                                                                                                                                                                                                                   | USIONS                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                   |

| CHAPTER 4                                                                                                                                                                                                                   | CONTROL STRATEGIES FOR THE FLYBACK-CCM                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                             | CONTROL STRATEGIES FOR THE FLYBACK-CCM                                                                                                                                                                                                                                                                                                                            |

| INVERTER                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                   |

| INVERTER<br>4.1 Introi                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                   |

| INVERTER<br>4.1 Introi<br>4.2 Poten                                                                                                                                                                                         | <b></b>                                                                                                                                                                                                                                                                                                                                                           |

| INVERTER<br>4.1 INTROI<br>4.2 POTEN<br>4.3 PROBL                                                                                                                                                                            | DUCTION                                                                                                                                                                                                                                                                                                                                                           |

| <b>INVERTER</b><br>4.1 INTROI<br>4.2 POTEN<br>4.3 PROBL<br><i>4.3.1. P</i>                                                                                                                                                  | 116<br>DUCTION                                                                                                                                                                                                                                                                                                                                                    |

| INVERTER<br>4.1 INTROI<br>4.2 POTEN<br>4.3 PROBL<br>4.3.1. Pr<br>4.3.2. Pr                                                                                                                                                  | 116DUCTION                                                                                                                                                                                                                                                                                                                                                        |

| INVERTER         4.1         INTROI         4.2         POTEN         4.3         PROBL         4.3.1.         4.3.2.         4.4         PROPO                                                                             | 116DUCTION                                                                                                                                                                                                                                                                                                                                                        |

| INVERTER<br>4.1 INTROI<br>4.2 POTEN<br>4.3 PROBL<br>4.3.1. PA<br>4.3.2. PA<br>4.4 PROPO<br>4.4.1. In                                                                                                                        | 116DUCTION116FIAL CURRENT CONTROL TECHNIQUES117EMS WITH DIRECT CONTROL OF OUTPUT CURRENT119roblem with Direct One Cycle Control (DOCC)119roblem with Direct Average Current Control (DACC)122SED INDIRECT CURRENT CONTROL STRATEGY124                                                                                                                             |

| INVERTER<br>4.1 INTROI<br>4.2 POTEN<br>4.3 PROBL<br>4.3.1. PA<br>4.3.2. PA<br>4.4 PROPO<br>4.4.1. In<br>4.4.2. In                                                                                                           | 116DUCTION116FIAL CURRENT CONTROL TECHNIQUES117EMS WITH DIRECT CONTROL OF OUTPUT CURRENT119roblem with Direct One Cycle Control (DOCC)119roblem with Direct Average Current Control (DACC)122SED INDIRECT CURRENT CONTROL STRATEGY124direct OCC Scheme125                                                                                                         |

| <ul> <li>INVERTER</li> <li>4.1 INTROI</li> <li>4.2 POTEN</li> <li>4.3 PROBL</li> <li>4.3.1. Pi</li> <li>4.3.2. Pi</li> <li>4.4 PROPO</li> <li>4.4.1. In</li> <li>4.4.2. In</li> <li>4.5 IMPROV</li> </ul>                   | 116DUCTION                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>INVERTER</li> <li>4.1 INTROI</li> <li>4.2 POTEN</li> <li>4.3 PROBL</li> <li>4.3.1. Pi</li> <li>4.3.2. Pi</li> <li>4.4 PROPO</li> <li>4.4.1. In</li> <li>4.4.2. In</li> <li>4.5 IMPROV</li> <li>4.5.1. C</li> </ul> | 116DUCTION                                                                                                                                                                                                                                                                                                                                                        |

| INVERTER<br>4.1 INTROI<br>4.2 POTEN<br>4.3 PROBL<br>4.3.1. PL<br>4.3.2. PL<br>4.4 PROPO<br>4.4.1. In<br>4.4.2. In<br>4.5 IMPROV<br>4.5.1. C.<br>4.5.2. C                                                                    | 116DUCTION116FIAL CURRENT CONTROL TECHNIQUES117EMS WITH DIRECT CONTROL OF OUTPUT CURRENT119Problem with Direct One Cycle Control (DOCC)119Problem with Direct Average Current Control (DACC)122SED INDIRECT CURRENT CONTROL STRATEGY124direct OCC Scheme125direct ACC Scheme127VED CURRENT SENSING USING CT137urrent Sensing Distortion with Unidirectional CT138 |

| 4.6.2. Verification of IACC Scheme                                 | 159           |

|--------------------------------------------------------------------|---------------|

| 4.7 Conclusion                                                     | 165           |

| CHAPTER 5:: A PARALLEL POWER PROCESSING (P3) SCHI                  | E <b>ME</b> – |

| TOPOLOGY STUDY AND DESIGN                                          | 168           |

| 5.1 INTRODUCTION                                                   | 168           |

| 5.2 System Concept and a Pilot Topology                            | 169           |

| 5.2.1. System Concept                                              | 169           |

| 5.2.2. A Pilot Power Topology for the P3 Scheme                    | 175           |

| 5.3 OPERATION AND DESIGN OF THE PILOT TOPOLOGY                     | 176           |

| 5.3.1. Design of Decoupling Capacitance                            | 177           |

| 5.3.2. Dual-Output Flyback Converter Design                        | 180           |

| 5.3.3. Buck Converter Design                                       | 193           |

| 5.4 VERIFICATION THROUGH SIMULATION                                | 195           |

| 5.4.1. A Flyback-DCM Inverter (without APD)                        | 196           |

| 5.4.2. The Pilot Topology (with APD)                               | 200           |

| 5.5 IMPLEMENTATION, RESULTS AND ANALYSIS                           | 205           |

| 5.5.1. Prototype Implementation                                    | 206           |

| 5.5.2. Dual-Output Flyback Converter in Scheme B: DC-DC Conversion | ı 208         |

| 5.5.3. Buck Converter Operation –DC-DC Conversion                  | 212           |

| 5.5.4. DC-AC Conversion                                            | 213           |

| 5.6 Conclusions                                                    | 215           |

| CHAPTER 6:: A PARRALLEL POWER PROCESSING (P3) SCHI                 | EME-          |

| CONTROL AND VERIFICATION                                           |               |

| 6.1 INTRODUCTION                                                   | 217           |

| 6.2 Power Stage Modeling                                           |               |

|                                                                    |               |

| 6.2.1. Input Stage Model for MPPT Control                          |               |

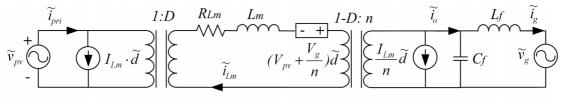

| 6.2.2. Pilot Topology Modeling                                     |               |

| 6.2.3. Model Discussion                                            | 231           |

| 6.3 Pro  | POSED CONTROL SCHEME                                                   |

|----------|------------------------------------------------------------------------|

| 6.3.1.   | A Dual Loop Voltage/Current Control                                    |

| 6.3.2.   | Current Control                                                        |

| 6.3.3.   | Voltage Control                                                        |

| 6.4 Res  | ULTS AND ANALYSIS                                                      |

| 6.4.1.   | Simulation Verification                                                |

| 6.4.2.   | Experimental Results                                                   |

| 6.5 CON  | ICLUSIONS                                                              |

| CHAPTER  | R 7: CONCLUSIONS AND FUTURE WORK 250                                   |

| 7.1 Sum  | IMARY OF CONCLUSIONS                                                   |

| 7.2 A L  | OW COST FLYBACK-CCM INVERTER                                           |

| 7.2.1.   | Study of the Power Decoupling Capacitance at PV side                   |

| 7.2.2.   | Analysis and Design of a Flyback CCM Inverer                           |

| 7.2.3.   | Verification of Efficiency Improvement of a Flyback CCM Inverter       |

| сотра    | red to a flyback-DCM Inverter                                          |

| 7.2.4.   | Output Current Shaping Control of Flyback-CCM Grid-Connected           |

| Inverte  | er                                                                     |

| 7.3 A P. | ARALLEL POWER PROCESSING SCHEME                                        |

| 7.3.1.   | Proposed Parallel Power Processing (P3) Scheme                         |

| 7.3.2.   | A Pilot Topology for Implementing the P3 Scheme                        |

| 7.3.3.   | Proposal of a Control System for the Pilot Topology                    |

| 7.4 Fut  | URE WORK                                                               |

| 7.4.1.   | Power Loss Distribution Analysis and Efficiency Improvement of the     |

| Flybac   | ck-CCM Inverter                                                        |

| 7.4.2.   | Solutions to dynamic response problem due to RHP zero in direct        |

| output   | current control of Flyback-CCM Inverter                                |

| 7.4.3.   | Identification and Solutions to bifurcation problem in IOCC Scheme 262 |

| 7.4.4.   | Complete Experimental Performance Verification of the P3 (Pilot        |

| Topolo   | ogy) Scheme                                                            |

| 7.4.5. | Explore other topologies under P3 Scheme                             | 263 |

|--------|----------------------------------------------------------------------|-----|

| 7.4.6. | Solutions to effective control of the P3 pilot topology in Switching |     |

| Schem  | е А                                                                  | 263 |

#### List of Publication Associated to the Research Work

#### Journal papers:

- L. Yanlin and R. Oruganti, "A Low Cost Flyback CCM Inverter for AC Module Application," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 1295-1303, 2012.

- Li, Y. and Oruganti, R. "A flyback-CCM inverter scheme for photovoltaic AC module application" Australian Journal of Electrical and Electronics Engineering, v6, n3, p301-309, 2009.

#### Conference papers:

- L. Yanlin and R. Oruganti, "A low cost high efficiency inverter for photovoltaic AC module application," in *Photovoltaic Specialists Conference (PVSC)*, 2010 35th IEEE, 2010, pp. 002853-002858

- L. Yanlin and R. Oruganti, "A flyback-CCM inverter scheme for photovoltaic AC module application," in *Power Engineering Conference*, 2008. AUPEC '08. Australasian Universities, 2008, pp. 1-6

# **List of Tables**

| Table 1.1: Panel specifications under STC (Standard Test Conditions: Irradiance             |

|---------------------------------------------------------------------------------------------|

| 1kW/m2, AM1.5 spectrum, module temperature 25 °C)9                                          |

| Table 1.2: Summary of Grid Connection Requirements (IEC61727)    15                         |

| Table 2.1: Candidate topologies for micro-inverters    30                                   |

| Table 2.2: Summary of Candidate Topologies for Transformerless Microinverter 34             |

| Table 2.3: Comparisons of Potential Low Cost Flyback Solutions    52                        |

| Table 2.4: Weighting Factors for European Efficiency and CEC efficiency                     |

| Table 2.5: Examples of APD schemes                                                          |

| Table 2.6: Comparison of APD schemes (at line frequency of 50Hz unless otherwise            |

| stated)                                                                                     |

| Table 3.1: Design of Input Capacitance under Different Conditions       80                  |

| Table 3.2: Design of flyback-DCM and CCM inverters for given specifications: 104            |

| Table 3.3: Snubber circuits parameters for Flyback-DCM and CCM inverters 109                |

| Table 3.4: Performance measurement at various power levels $(V_{pv} = 27V, P_r = 200W)$ 113 |

| Table 4.1: Theoretical Performance of the designed system at several key operating          |

| conditions                                                                                  |

| Table 4.2: Output power factor and THD at various power levels ( $V_{pv} = 27V$ , $P_r = 200W$ ) |

|--------------------------------------------------------------------------------------------------|

|                                                                                                  |

| Table 5.1: Voltage and Current Stresses of MOSFET and Diodes ( $L_m = 4\mu H$ ) 192              |

| Table 5.2: PV module KC200GT model parameters under STC    196                                   |

| Table 5.3: Circuit Parameters in Fig.5.12    197                                                 |

| Table 5.4: Circuit Parameters in Fig.5.16    201                                                 |

| Table 6.1: Circuit parameters at STC    225                                                      |

# **List of Figures**

| Fig.1.1: DC module and String Inverter                                                         |

|------------------------------------------------------------------------------------------------|

| Fig.1.2: AC module and micro-inverter                                                          |

| Fig.1.3: Quasi-AC module and unfolding inverter                                                |

| Fig.1.4: System diagram of a microinverter                                                     |

| Fig.1.5: Simple electrical model of (a) a PV cell and (b) a PV panel made up of <i>m</i> cells |

| in series                                                                                      |

| Fig.1.6: PV panel I-V curve (solid) and P-V curve (dashed) without shading                     |

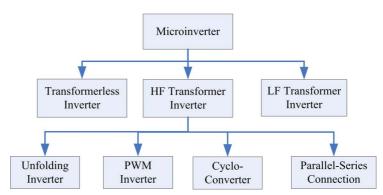

| Fig.2.1: Classification of basic microinverters based on 1) usage and type of                  |

| transformer and then 2) inverter operation mechanisms                                          |

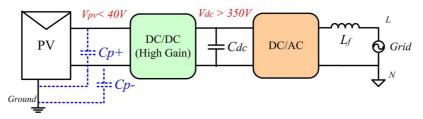

| Fig.2.2: Possible System diagram of transformerless microinverter                              |

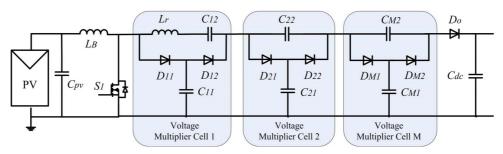

| Fig.2.3: High gain boost converter with voltage multiplying cells [44, 45]33                   |

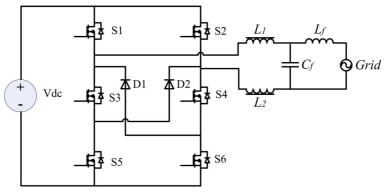

| Fig.2.4: H6 type inverter proposed in [46]                                                     |

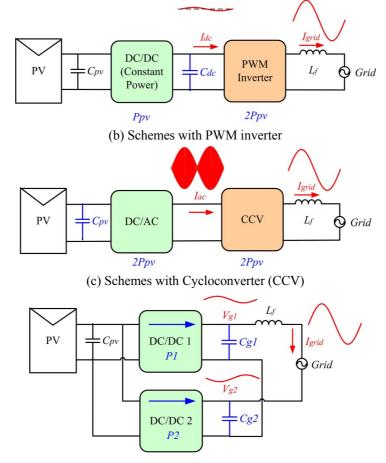

| Fig.2.5: System diagram of different types of HF transformer microinverters 35                 |

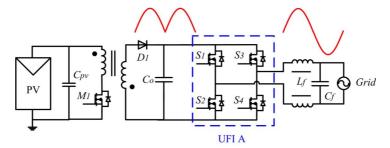

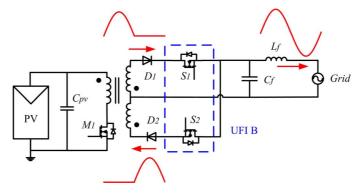

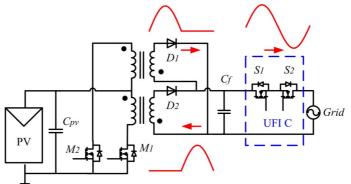

| Fig.2.6: Examples of microinverter with different types of UFI                                 |

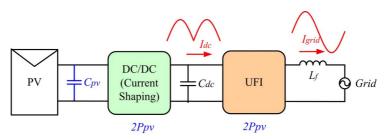

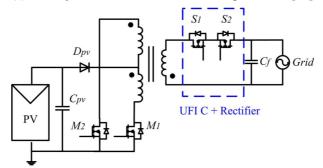

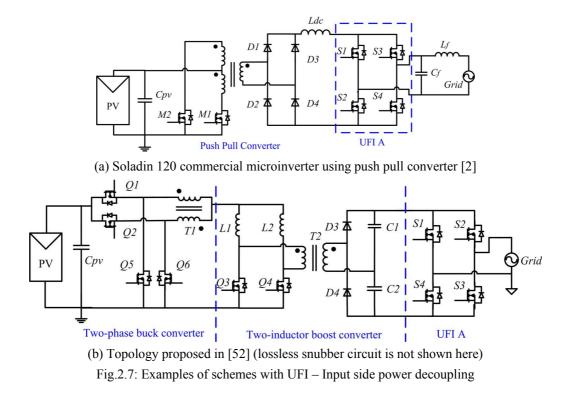

| Fig.2.7: Examples of schemes with UFI – Input side power decoupling 44                         |

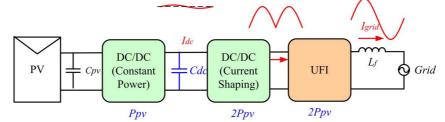

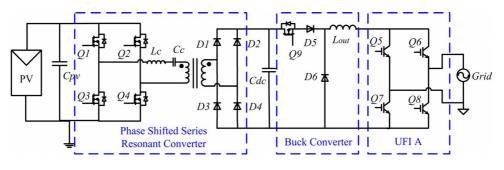

| Fig.2.8: Example of multiple-stage microinverter with UFI [53]                                 |

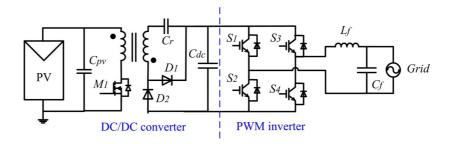

| Fig.2.9: Examples of Schemes using PWM Inverters                                               |

| Fig.2.10: Examples of schemes using CCV                                                 |

|-----------------------------------------------------------------------------------------|

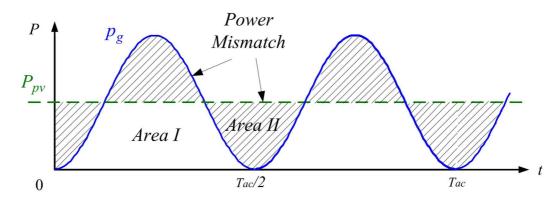

| Fig.2.11: Power decoupling requirement for single phase DC/AC inverter ( $P_{pv}$ : DC  |

| power from PV module; $P_g$ : switching average value of AC power to the grid) 57       |

| Fig.2. 12: Power Decoupling at PV side                                                  |

| Fig.2.13: System Diagram for APD solutions                                              |

| Fig.2.14: APD proposals for Flyback converter with UFI in Fig.2.7 (b)                   |

| Fig.2.15: Power decoupling scheme [93] for push pull microinverter in Fig.2.7 (b) 64    |

| Fig.2.16: Parallel Active Filter at PV side                                             |

| Fig.2.17: Power decoupling using AC link capacitor                                      |

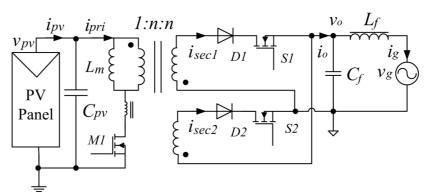

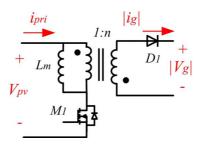

| Fig.3.1: A flyback-DCM microinverter                                                    |

| Fig.3.2: Circuit diagram for PV side capacitor                                          |

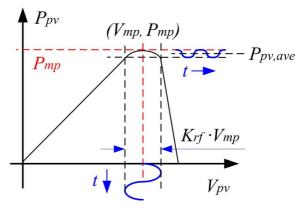

| Fig.3.3: The influence of PV voltage ripple to actual PV power                          |

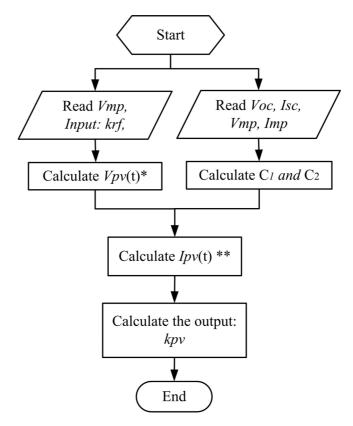

| Fig.3.4: Calculation flow chart of ripple factor's influence to PV utilization ratio (* |

| and ** indicates two assumptions for calculation)                                       |

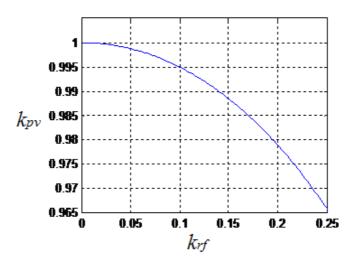

| Fig.3.5: PV utilization ratio vs. PV voltage ripple factor for KC200GT at NOCT          |

| (Nominal Operating Cell Temperature: 47°C)                                              |

| Fig.3.6: Simulation of KC200GT (STC) around MPPT point (Vmp=26.3V,                      |

| <i>Imp</i> =7.61A)                                                                      |

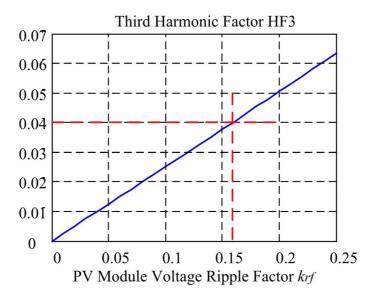

| Fig.3.8: Influence of PV voltage ripple factor to third harmonic factor of output               |

|-------------------------------------------------------------------------------------------------|

| current                                                                                         |

| Fig.3.9: Current waveforms of magnetizing inductance of flyback transformer 86                  |

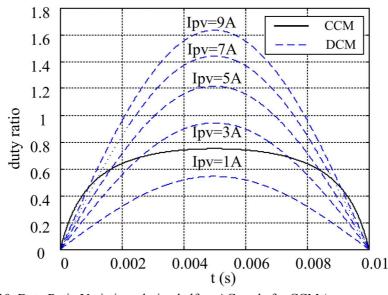

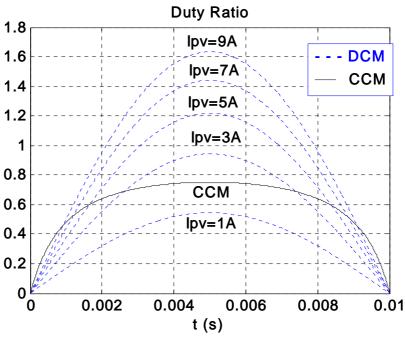

| Fig.3.10: Duty Ratio Variations during half an AC cycle for CCM ( $L_m = 20 \mu H$ ) and        |

| DCM ( $L_m = 4\mu H$ ) operations with $V_{pv} = 27V$ , $V_{rms} = 230V$ , $n = 4$              |

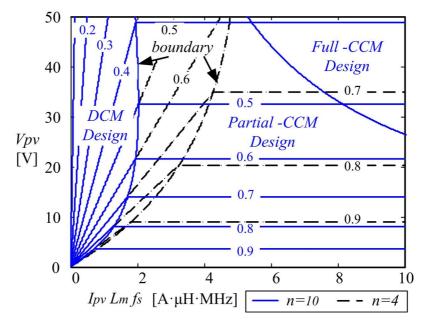

| Fig.3.11: Design aid diagram of flyback inverter $V_{rms} = 230$ V. (The numbers on the         |

| lines indicate the peak duty ratios)                                                            |

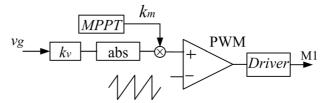

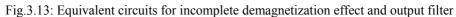

| Fig.3.12: Control Schemes for Flyback-DCM Inverter                                              |

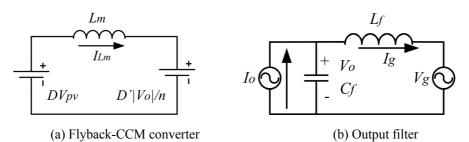

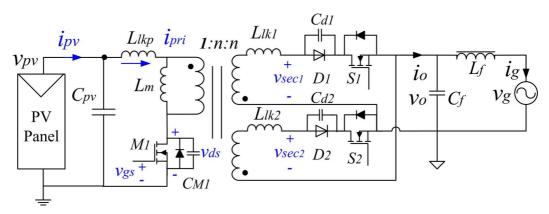

| Fig.3.13: Equivalent circuits for incomplete demagnetization effect and output filter99         |

| Fig.3.14: Flyback Inverter with parasitic components and measurement waveforms105               |

| Fig.3.15: Operation waveforms of flyback inverter without snubber circuit (positive             |

| leg) 107                                                                                        |

| Fig.3.16: Operation waveforms of flyback-CCM inverter with snubber circuits 111                 |

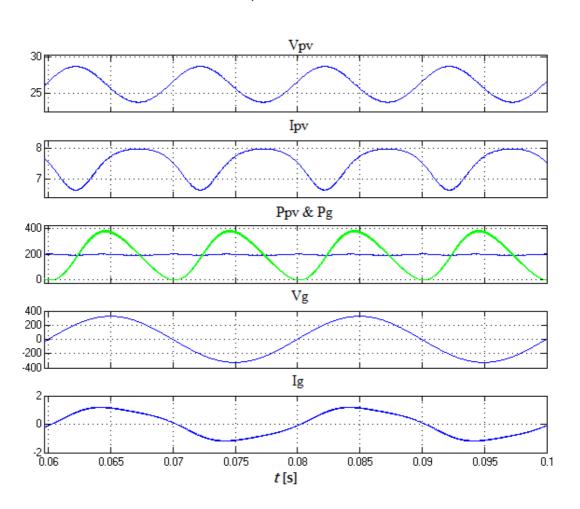

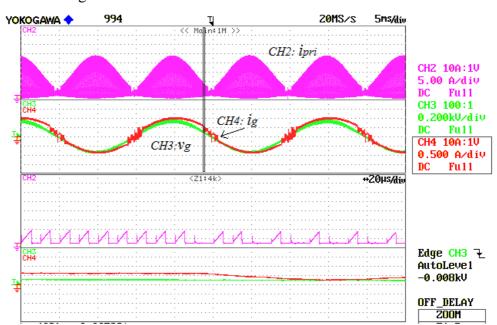

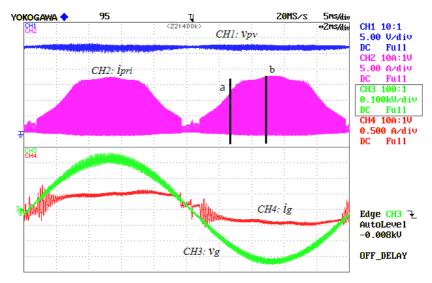

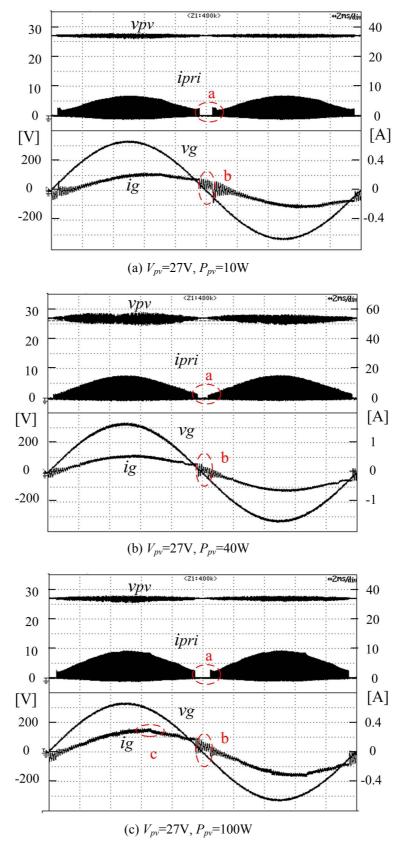

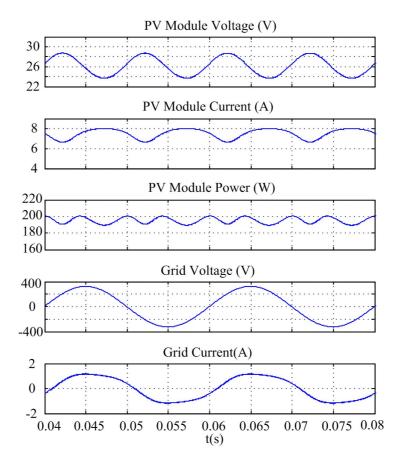

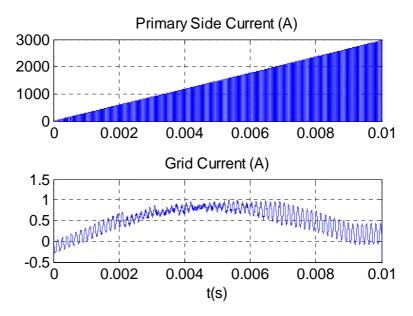

| Fig.3.17: PV side and grid side waveforms with $V_{pv}=27$ V, $P_{pv}=200$ W112                 |

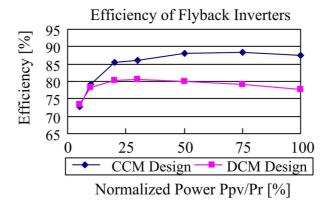

| Fig.3.18 Efficiency vs. normalized power (referred to rated power of 200W) for the              |

| DCM and CCM scheme                                                                              |

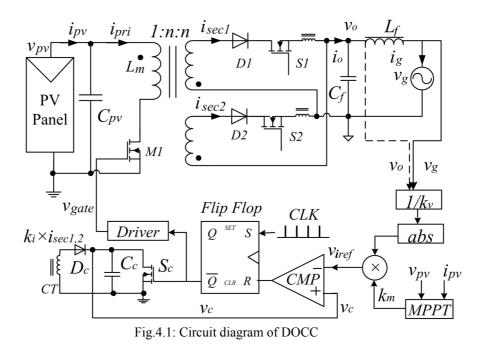

| Fig.4.1: Circuit diagram of DOCC 121                                                            |

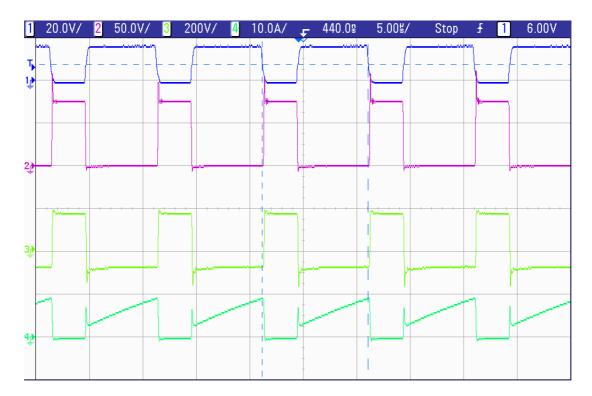

| Fig.4.2: Instability of DOCC ( $n = 4$ , $L_m = 20 \mu H$ , $V_{pv} = 27V$ , $V_{rms} = 230V$ ) |

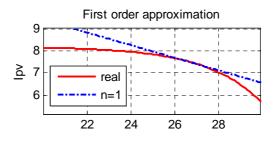

Fig.3.7: Linear (first order Taylor) approximation near MPP for KCT200GT (STD)82

| Fig.4.3: Control circuit diagram of DACC scheme                                                       | 22       |

|-------------------------------------------------------------------------------------------------------|----------|

| Fig.4.4: A typical waveform of DACC ( $n = 4$ , $L_m = 20\mu H$ , $V_{pv}=27V$ , $V_{rms}=230V$ ) 12  | 23       |

| Fig.4.5: Indirect Current Control Diagram 12                                                          | 24       |

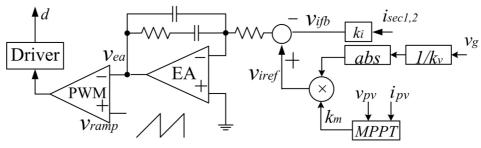

| Fig.4.6: Schematic diagram of the proposed IOCC scheme for flyback-CCM inverte                        | er126    |

| Fig.4.7: Equivalent Circuit of Flyback Inverter for Small Signal Modeling 12                          | 28       |

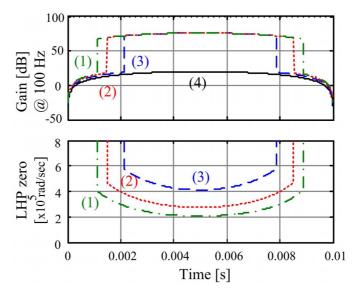

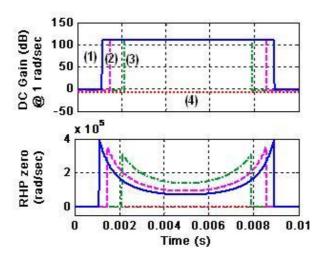

| Fig.4.8: Variation of gain (at $_{2f_{ac}} = 100Hz$ ) and LHP zero with power level of (1) 100%       | ,<br>0,  |

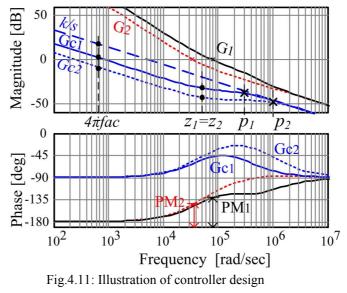

| (2) 75%, (3) 50% and (4) 25% (DCM-only, no LHP zero) at rated power $P_r = 200W$ 1                    | 31       |

| Fig.4.9: Plant references ('A': worst case in CCM at $P_c$ ; 'B': worst case in CCM at $P_c$          |          |

| 'C': DCM at $P_r$ and $V_g = 10V$ )                                                                   | 32       |

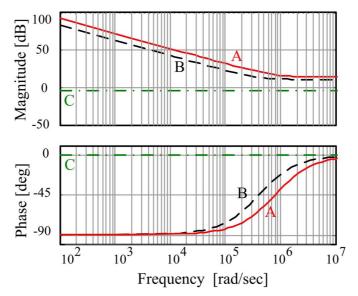

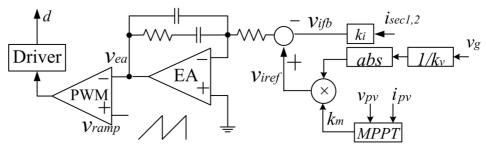

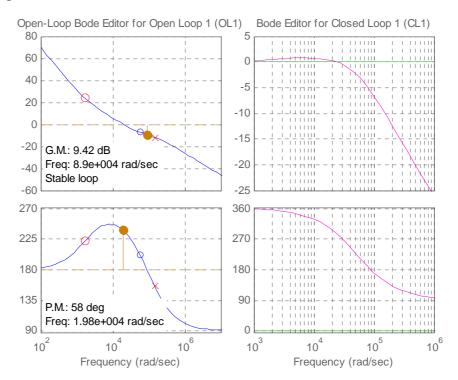

| Fig.4.10: Proposed CCM control scheme based on Indirect ACC                                           | 33       |

| Fig.4.11: Illustration of controller design                                                           | 35       |

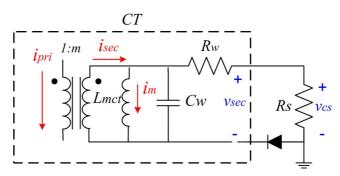

| Fig.4.12: Equivalent circuit of current sensing circuit using unidirectional CT 13                    | 39       |

| Fig.4.13: Unidirectional CT waveforms over an AC cycle: Ch1: $v_{cs}$ ; Ch2: $i_{pri}$ ; Ch3: $v_{d}$ | ;<br>ls; |

| Ch4: v <sub>sec</sub> (experiment)                                                                    | 40       |

| Fig.4.14: Cyclic waveforms of unidirectional CT sensing (zoom-in of Fig.4.13                          | 3,       |

| [5µs/div] )                                                                                           | 41       |

| Fig.4.15: Current sensing method using bidirectional CT with Sample & Hold [118]                      | 143      |

| Fig.4.16: Generation of Sample and Hold Signal                                                        | 13       |

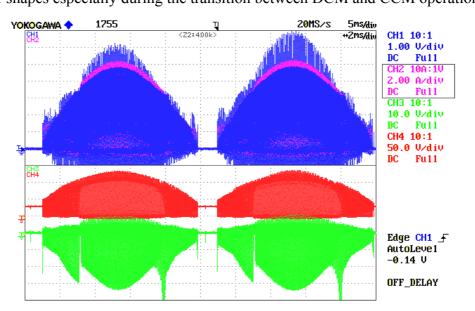

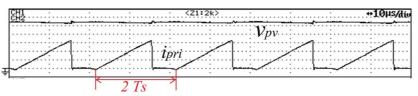

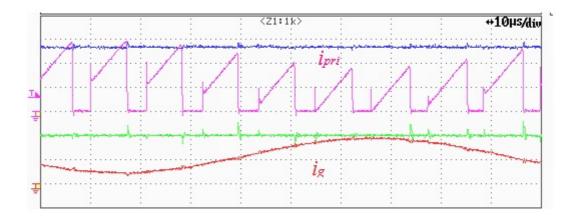

| Fig.4.17: Current Sensing Operating Waveforms (experiment)                                          |

|-----------------------------------------------------------------------------------------------------|

| Fig.4.18: Current Sensing Operating Waveforms over AC cycle with IACC                               |

| (experiment: with filter of 10 kHz)145                                                              |

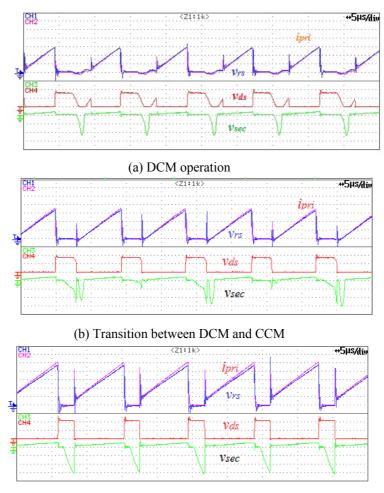

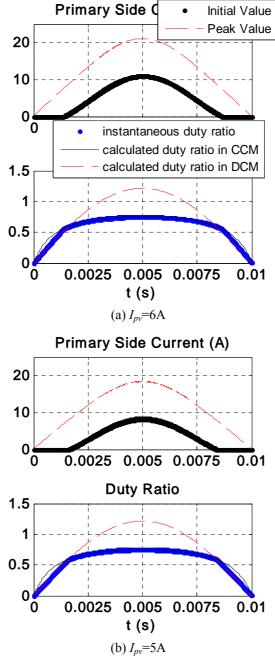

| Fig.4.19: Operating waveform at $V_{pv}$ =27V, $I_{pv}$ =9A, $V_{rms}$ =230V, (simulation, THD =    |

| 0.80%)                                                                                              |

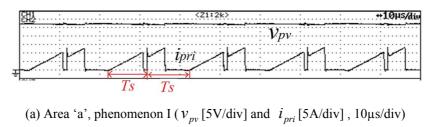

| Fig.4.20: Irregular operation waveforms at reduced power levels $V_{pv}$ =27V,                      |

| $V_{rms}$ =230V (simulation)                                                                        |

| Fig.4.21: Enlargemnt of two nonlinear dynamic phenomena in Fig.4.20 (simulation)148                 |

| Fig.4.22: Switched Integrator for OCC scheme                                                        |

| Fig.4.23: Input and output waveforms with IOCC: $V_{pv}=27V$ , $I_{pv}=6.7A$ , $V_{rms}=230V$       |

| (experiment)150                                                                                     |

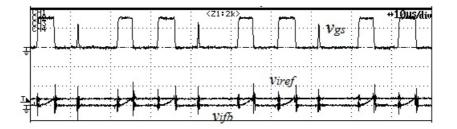

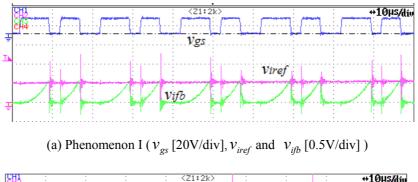

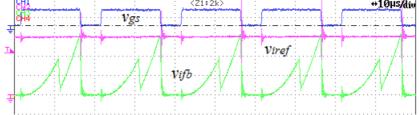

| Fig.4.24: Control signals around zero crossing points ( $v_{gs}$ [10V/div], $v_{iref}$ and          |

| <i>v<sub>ifb</sub></i> [0.5V/div] )                                                                 |

| Fig.4.25: Input and output waveforms $V_{pv}$ =27V, $I_{pv}$ =3.7A, $V_{rms}$ =230V (experiment)151 |

| Fig.4.26: Enlargement of two nonlinear dynamic phenomena in Fig.4.25 (experiment)                   |

|                                                                                                     |

| Fig.4.27: Control signals corresponding to Fig.4.26                                                 |

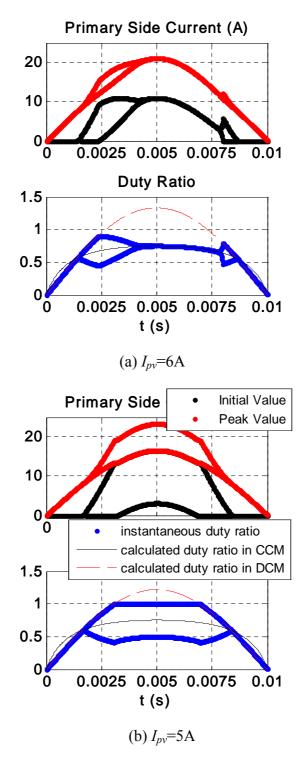

| Fig.4.28: Discrete-time mapping of primary side currents and duty ratio at $V_{pv}$ =27V154         |

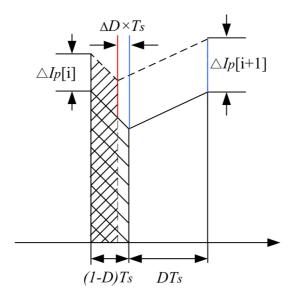

| Fig.4.29: Change of duty ratio in half AC cycle                                                     |

| Fig.4.30: Mitigation of bifurcation in Fig.4.28 $V_{pv}$ =27V                                      |

|----------------------------------------------------------------------------------------------------|

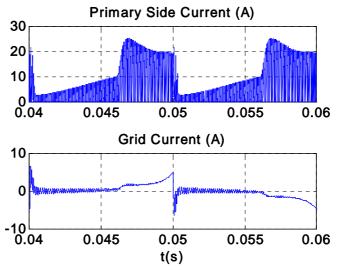

| Fig.4.31: Current tracking performance (Input and output waveforms) 160                            |

| Fig.4.32: Equivalent Circuit of flyback Inverter in CCM operation                                  |

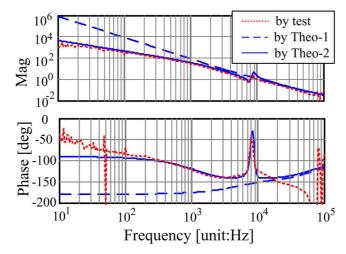

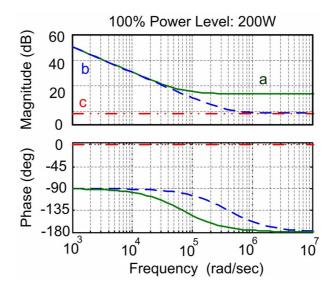

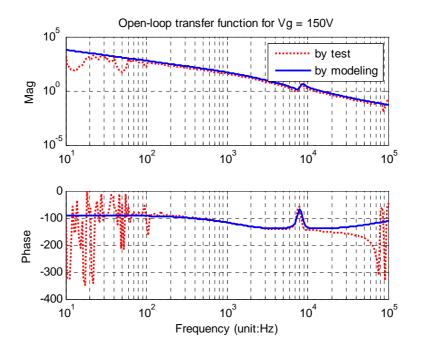

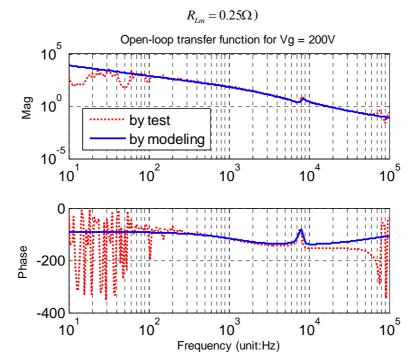

| Fig.4.33: Open loop Bode Plots verification with 200W and $V_{gb}=112$ V; $(R_{Lm}=0.25\Omega)$ in |

| Theo-2)                                                                                            |

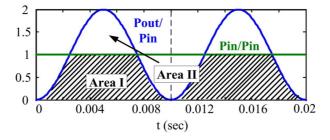

| Fig. 5.1: Input and output power mismatch                                                          |

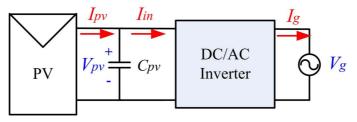

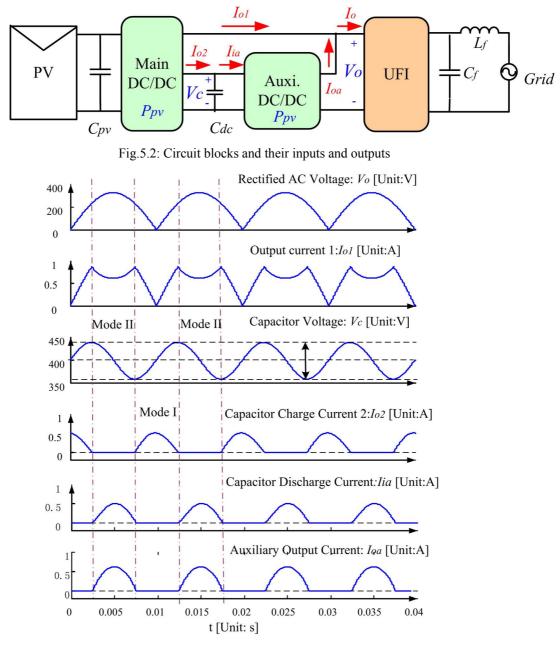

| Fig.5.2: Circuit blocks and their inputs and outputs                                               |

| Fig.5.3: Key Operation Waveforms of P3 Schemes                                                     |

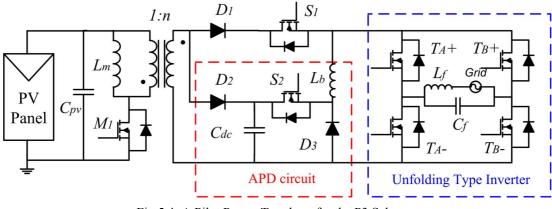

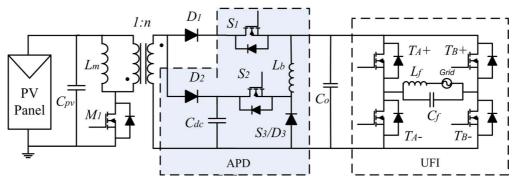

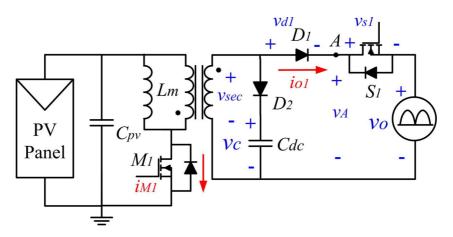

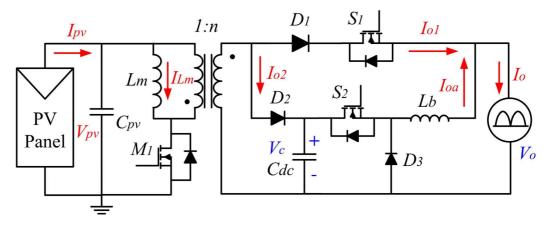

| Fig.5.4: A Pilot Power Topology for the P3 Scheme 175                                              |

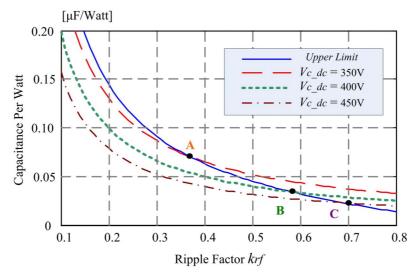

| Fig.5.5: Relationship between capacitance/watt and ripple factor for different DC link             |

| voltages                                                                                           |

| Fig.5.6: Dual Output Flyback Converter                                                             |

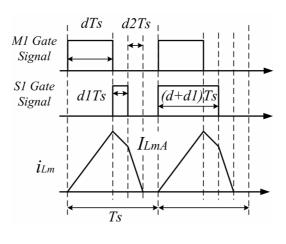

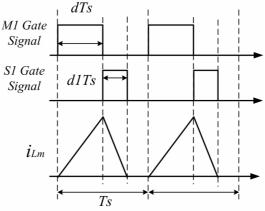

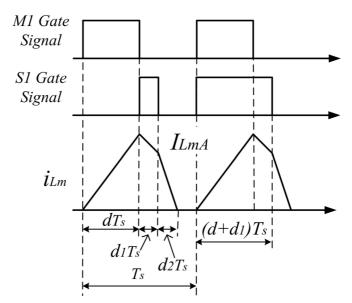

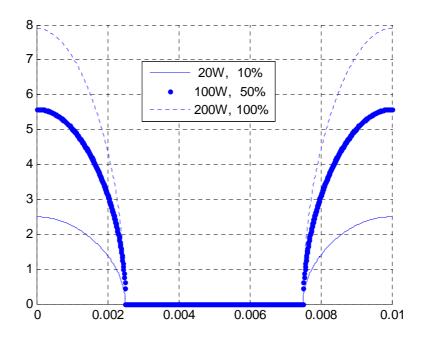

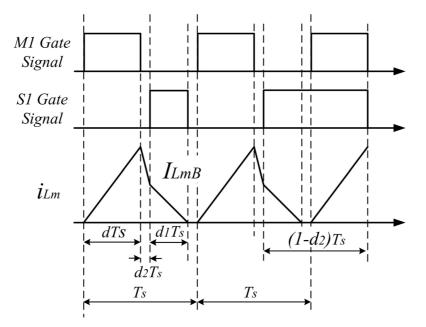

| Fig.5.7: Operating waveforms of the Dual-Output flyback converter                                  |

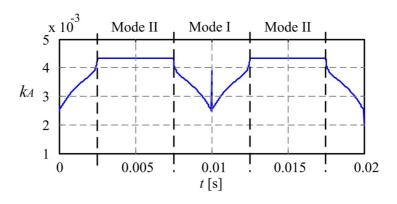

| Fig.5.8: Variation of $k_A$ over AC cycle                                                          |

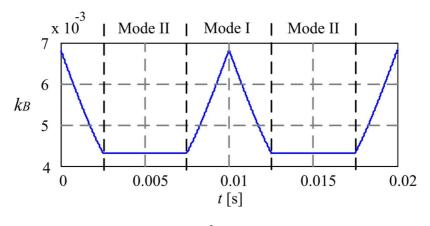

| Fig.5.9: Variation of $k_B$ over AC cycle                                                          |

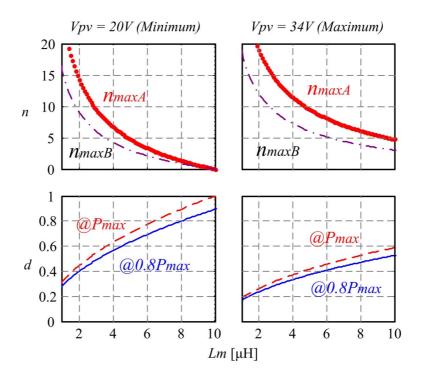

| Fig.5.10: Design of $L_m$ and $n$ for KC200GT at min. and max. PV MPPT voltage190                  |

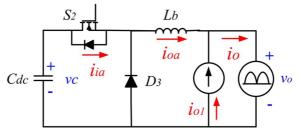

| Fig.5.11: Circuit diagram of the auxiliary buck converter                                          |

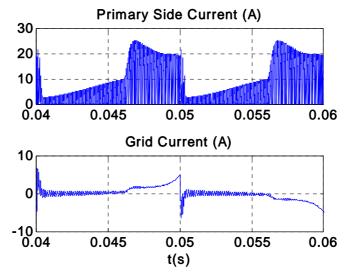

| Fig.5.12: Circuit diagram of a flyback-DCM inverter with UFI 197                                   |

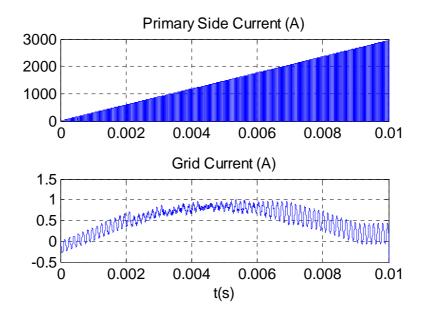

| Fig.5.13: Operating waveforms of a flyback-DCM inverter ( $C_{pv} = 4.7mF$ , $P_{pv} = 200W$ ,  |

|-------------------------------------------------------------------------------------------------|

| <i>THD</i> = 9.33%, simulation)                                                                 |

| Fig.5.14: Operating waveforms of a flyback-DCM inverter ( $C_{pv} = 11.6mF$ , $P_{pv} = 200W$ , |

| <i>THD</i> = 4.54%, simulation)                                                                 |

| Fig.5.15: Components voltage and current waveforms over AC cycles ( $C_{pv} = 11.6mF$ ,         |

| $P_{pv} = 200W$ , simulation)                                                                   |

| Fig.5.16: Circuit diagram of proposed topology (with APD) 200                                   |

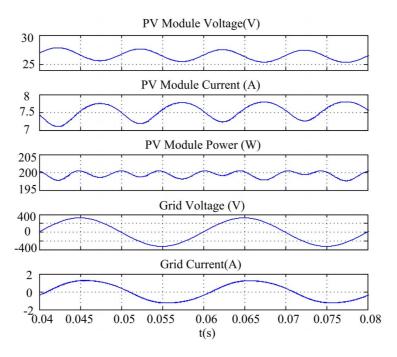

| Fig.5.17: Operating waveforms of a flyback-DCM inverter ( $P_{pv} = 200W$ , THD = 3.88%,        |

| Scheme B, Simulation)                                                                           |

| Fig.5.18: Component current and voltage waveforms over AC cycles                                |

| $(P_{pv} = 200W$ , Scheme B, Simulation)                                                        |

| Fig.5.19: Component current and voltage waveforms over AC cycles (with a filter of              |

| 1kHz, simulation)                                                                               |

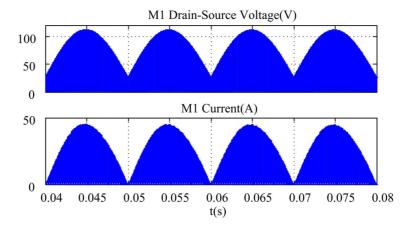

| Fig.5.20: Switching Waveforms (simulation)                                                      |

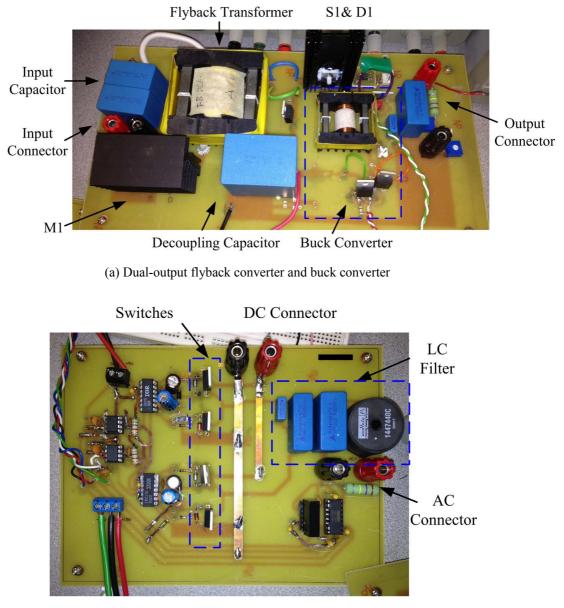

| Fig.5.21: Photos of experimental prototype                                                      |

| Fig.5.22: Measured Parameters of Flyback Converter in Experiment                                |

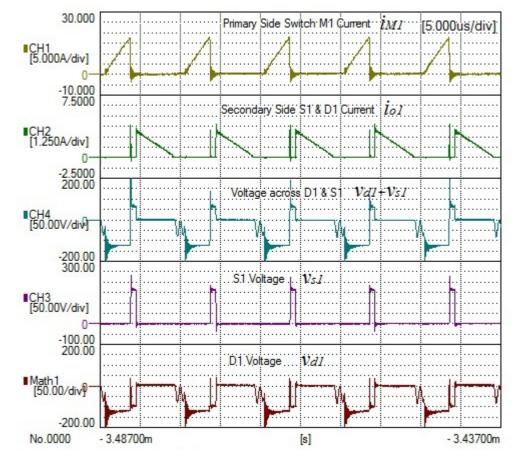

| Fig.5.23: Operating waveforms: S1 uses Cool MOS SPW24N60C3 (Scheme B,                           |

| Experiment, DC-DC Conversion)                                                                   |

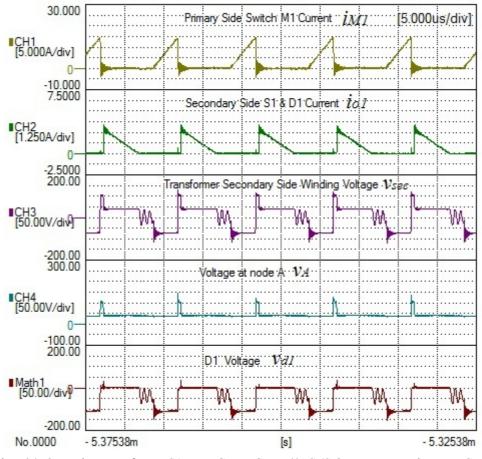

| Fig.5.24: Operating waveforms: S1 uses IGBT FGP5N60LS (Scheme B, Experiment,                    |

|-------------------------------------------------------------------------------------------------|

| DC-DC conversion)                                                                               |

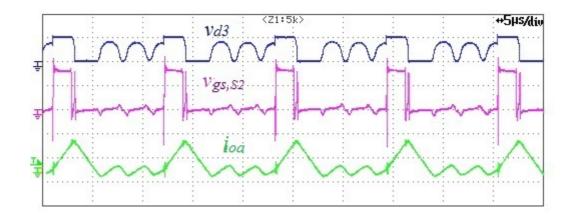

| Fig.5.25: Buck Converter Operating Waveforms ( $V_{ds,S2}$ [100V/div], $V_{gs,S2}$ [10V/div],   |

| <i>I<sub>oa</sub></i> [0.2A/div], Experiment, DC-DC conversion)                                 |

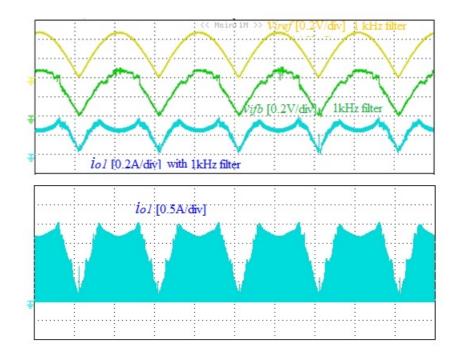

| Fig.5.26: DC-AC conversion waveforms ( $V_{pv} = 27V$ , $V_{rms} = 67.5V$ , $I_{rms} = 0.39A$ , |

| experiment)                                                                                     |

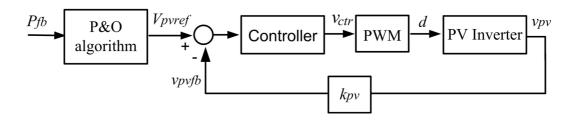

| Fig.6.1: A typical MPPT control diagram with voltage control                                    |

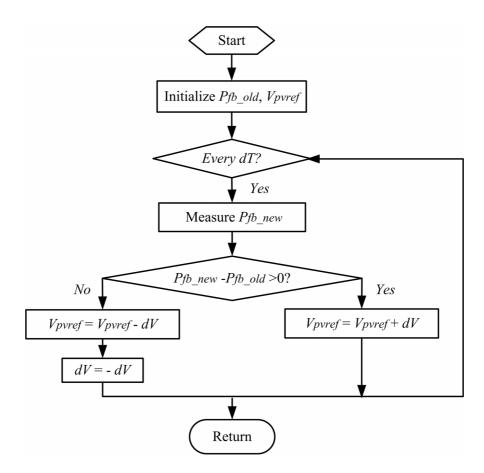

| Fig.6.2: A typical P&O flow chart with PV module voltage as reference value 219                 |

| Fig.6.3: Equivalent circuit diagram of the input stage (The secondary side power                |

| transfer parts are not shown)                                                                   |

| Fig.6.4: PV module model and input operation waveforms                                          |

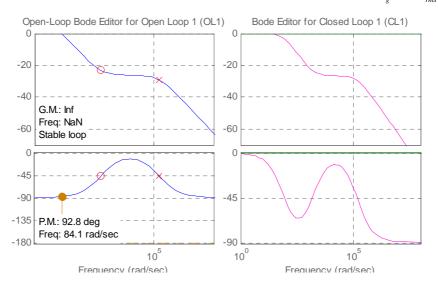

| Fig.6.5: Bode diagram of flyback in DCM under nominal operating condition (Duty                 |

| cycle to PV module voltage transfer function)                                                   |

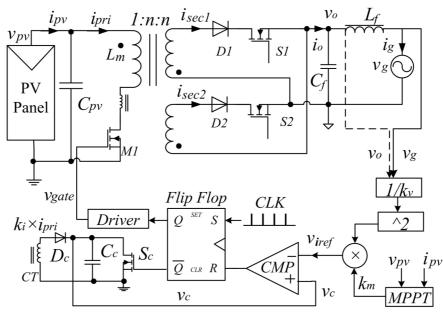

| Fig.6.6: Circuit diagram of the P3 pilot topology                                               |

| Fig.6.7: Illustration of Flyback converter waveforms in Scheme A 227                            |

| Fig.6.8: The transfer function of (6-9) over an AC cycle                                        |

| Fig.6.9: Illustration of Flyback converter waveforms in Scheme B 229                            |

| Fig.6.10: Current Transfer Function over an AC cycle (actual gain)                              |

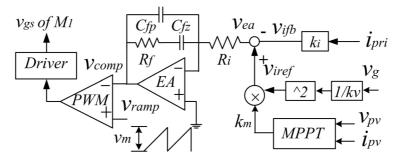

| Fig.6.11: Overall Control System for the P3 Pilot Topology                                      |

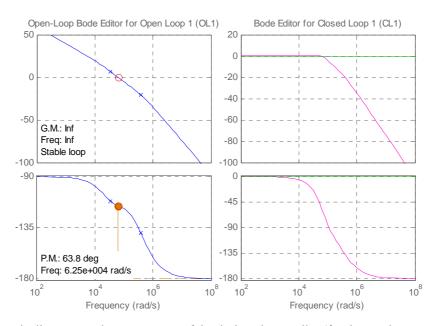

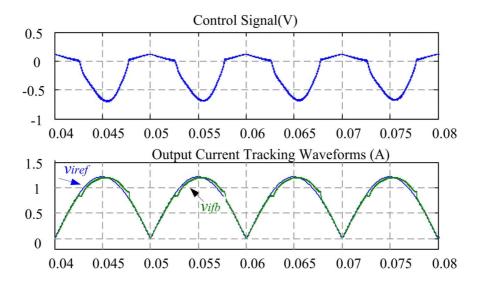

| Fig.6.12: Control diagram for dual-loop control                                                           |

|-----------------------------------------------------------------------------------------------------------|

| Fig.6.13: Plant transfer functions including current sensing circuit                                      |

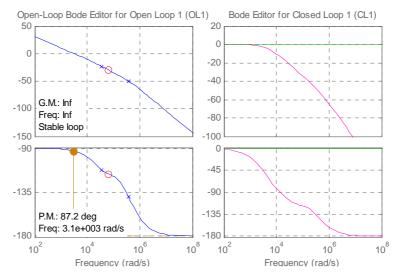

| Fig.6.14: Bode diagrams of the designed controller (for the minimum gain of 0.5)240                       |

| Fig.6.15: Bode diagrams and step response of the designed controller (for the                             |

| maximum gain of 15)                                                                                       |

| Fig.6.16: Block diagram of the external voltage loop                                                      |

| Fig.6.17: Steady State Control Signals ( $V_{pv} = 27V$ , $P_{pv} = 200W$ , Simulation)                   |

| Fig.6.18: Steady State Output Waveforms ( $V_{pv} = 27V$ , $P_{pv} = 200W$ , Simulation)                  |

| Fig.6.19: Start up waveforms of the P3 scheme with voltage control ( $V_{pv} = 27V$ , $P_{in} = P_{pv}$ , |

| Simulation)                                                                                               |

| Fig.6.20: Transient waveforms of the P3 scheme with voltage control (Step change of                       |

| 50W at input power, Simulation)                                                                           |

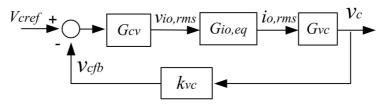

| Fig.6.21: Current controller implementation                                                               |

| Fig.6.22: Current tracking waveforms with flyback operation only ( $V_{pv} = 27V$ ,                       |

| $V_{rms} = 50V$ , experiment)                                                                             |

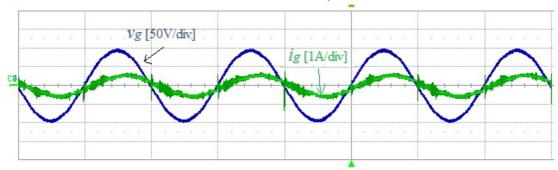

| Fig.6.23: Current tracking waveforms ( $V_{pv} = 27V$ , $V_{rms} = 100V$ , experiment)                    |

| Fig.6.24: Grid voltage and current waveforms ( $V_{pv} = 27V$ , $V_{rms} = 71V$ , $I_{rms} = 0.5A$ ,      |

| experiment)                                                                                               |

| Fig.6.25: Grid | voltage and | l current | waveforms | $\left(V_{pv}=27V\right),$ | $V_{rms} = 124.6V$ , $I_{rms} = 0.53A$ | , |

|----------------|-------------|-----------|-----------|----------------------------|----------------------------------------|---|

| experiment)    |             |           |           |                            |                                        | 8 |

# CHAPTER 1: INTRODUCTION 1.1 Background

In traditional electric grid system, the central plants to generate electricity are usually placed either close to the energy resources (such as hybroelectric plants) or purposely located far from city areas to prevent the heavy air pollution from affecting the populated areas (such as coal plants). This requires the bulk power to be distributed for a long distance through a transmission & distribution grid from central plants to where the load is connected.

However, due to the emerging oil shortage and increasing concerns on CO2 emission and global warming, various renewable energy resources with zero/negligible emission have been identified as attract alternatives to conventional energy resources.

Solar energy is one of the most promising renewable energy resources in use nowadays. Integration of renewable energy resources to traditional electric grid system brings both benefits and challenges.

On the one hand, because of the ubiquitousness of sunlight, ease of installation, as well as environment-friendly feature (no emission and no noise), PV generation system can be installed conveniently on the roof of buildings in towns and cities, where the major part of energy consumption occurs. In this way, the amount of energy loss in transmitting electricity can be reduced by the distributed power generation compared with the conventional centralized electricity generation. On the other hand, technical issues such as the power quality and system stability, caused by the interaction between the distributed PV system and grid need to be examined and additional protective devices may be required. Also the intermittency of solar energy resources would place requirement for better energy management through energy storage or additional capacity installation, especially for a large penetration of solar power into the grid.

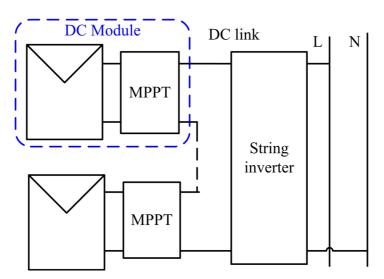

Fig.1.1: DC module and String Inverter

Compared to PV systems based on the processing of the energy output of several PV panels connected directly in series and parallel, power generation based on the processing of energy output of single PV modules individually has become a new trend [1-4]. Here, two major approaches have been noticed in both academic and industry work, viz., "DC module" [5-9] and "AC module" [10-13] based on their output features.

As shown in Fig.1.1, the term "DC module" refers to a PV module connected

to or integrated with an individual Maximum Power Point Tracking (MPPT) converter or "power optimizier" [5-9]. With the MPPT guaranteed by the local converter, the outputs of the DC modules are then connected in series and to a string inverter before feeding into grid.

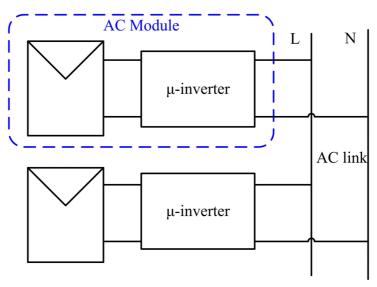

Fig.1.2: AC module and micro-inverter

The concept of an "AC module", which refers to a PV panel with an integrated "microinverter", was conceived 30 years ago by researchers at Caltech's Jet Propulsion Laboratory and Sandia National Lab [13]. As illustrated in Fig.1.2, their vision envisaged AC modules which "will be available at local hardware store and can be as easy to install as a string of light bulbs. [13]"

In both DC and AC module approaches, the maximum power point (MPP) of each panel can be tracked individually. Thus, the effects due to shading and module mismatches and orientation variations are almost totally eliminated and the utilization of the whole PV system is improved. This feature is vital in densely built areas where shading due to adjacent buildings or trees is inevitable. AC modules are especially suitable for Building Integrated PV (BIPV) systems, where PV panels are integrated with building materials and mounted on the building surfaces whose orientations are all not likely to be the same.

Besides, the AC module approach has its own unique advantages in terms of installation, maintenance and safety. Some of these are outlined below.

(1) According to NEC 690.11[14], "photovoltaic systems with DC source circuits, DC output circuits or both, on or penetrating a building operating at a PV system maximum system voltage of 80 volts or greater, shall be protected by a listed (DC) arc-fault circuit interrupter, PV type, or other system components listed to provide equivalent protection." Such a requirement, does not apply to AC modules with AC output only. Also, no special expertise for DC wiring is needed for installation and maintenance of AC module. This is an important advantage in the acceptance of PV systems among population.

(2) Secondly, the "plug and play" property allows the customers to install a small number of AC modules in the beginning and expand the system easily through paralleling of additional AC modules. There is no need to match the new AC modules with the existing ones in any manner. Different PV technologies can be mixed.

(3) Failure of one module will not influence other modules. The limitation imposed by the 'weakest link' on a PV array of serial/parallel connected modules is eliminated, which would improve system reliability.

(4) If failure of one AC module is detected, the removal and repair work can be carried out without influencing the other modules, again by a non-expert, safely.

All of the above features make the AC module approach, based on microinverters, a promising technology to improve PV penetration into the grid.

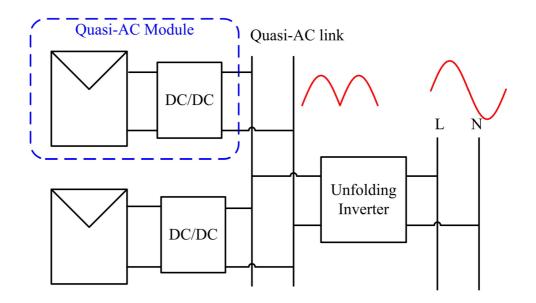

Fig.1.3: Quasi-AC module and unfolding inverter

Other than the above two popular approaches, an alternative "Quasi-AC module" approach has been proposed in [15] (Fig.1.3). A quasi-AC module supplies a unidirectional current but in the shape of a rectified sinusoid. These quasi-AC modules are connected to a quasi-AC link, which, in turn, feeds power to the centralized unfolding inverter. Although different in system structure, the DC/DC converter and its control is similar to that in AC module solution based on unfolding inverter, which will be studied in literature survey in Chapter 2.

### **1.2 Introduction to Microinverter**

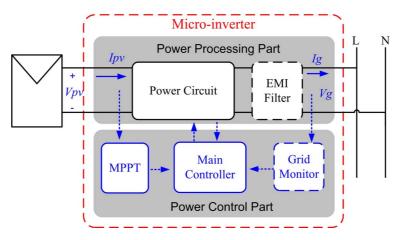

A microinverter, generally, refers to a low power inverter designed to handle the output of a single PV module (usually in the range of 100~300W). Its external connections and internal structure are shown in Fig.1.4.

Fig.1.4: System diagram of a microinverter

As illustrated in Fig.1.4, a microinverter consists of two major parts: a power processing part and a power control part.

The power processing part is connected to a PV module on the input side. The PV module converts the photon energy of light into Direct Current (DC) by photovoltaic effect. The PV module output is fed to the power circuit, which converts the DC into Alternating Current (AC) required by the utility. As the fast switching waveforms of the present day inverter technology would generate high frequency electromagnetic noise, an EMI filter is needed between the inverter and the utility to prevent high frequency noise currents from entering the grid and causing interference to other systems connected to the same utility.

The power control part is divided into three function blocks based on the requirements of the PV panel and grid connection.

Among them, MPPT (Maximum Power Point Tracking) is used to obtain the maximum power from the PV panel as the panel's output characteristics changes with environmental conditions.

Grid monitor is connected to the utility to detect its working condition and stop and restart the inverter as and when necessary. It also helps in synchronizing the inverter waveform with the grid voltage waveform. Detailed requirements and specifications are listed in several national and international standards concerning the interconnection of distributed generation systems with the grid and will be discussed later in this chapter.

Receiving the signals from MPPT and Grid monitor, the main controller directly controls the inverter to obtain a sinusoidal output current in phase with the grid voltage and with a low THD (Total Harmonics Distortion).

As an interface between a single PV module and the AC grid, the power circuit of a microinverter needs to cater to the requirements from both sides. Generally speaking, it needs to have 1) MPPT function to match with the PV module, and 2) high voltage boost and DC/AC conversion capability to match with the grid. These requirements are further explained below.

### 1.2.1. Power Processing Requirements

For the power processing part, the input side requirements are determined by the choice of the PV panel used. The developments in PV technologies focus on improving the conversion efficiency of the PV cell and on reducing the system cost. Various PV cell technologies, based on different materials and fabrication methods are currently under active research. These include silicon based technologies (in the mono-crystalline, poly-crystalline, amorphous and micro-crystalline forms), and technologies based on III-V compounds, organics, nanotechnology and multi-junctions [16, 17]. Despite all the exciting progress in the research laboratories around the world, most of the commercial PV products at present are still based on mono-crystalline and poly-crystalline silicon. It is believed that they would continue to dominate the PV market for at least another decade [18]. This belief is further strengthened by the recent plummeting of the cost of silicon PV modules.

The specifications of the applicable PV panels (above 100W) from several major global manufacturers [19] are listed in Table 1.1. This list, though not a complete list of all the panels available, gives a good idea of the voltage and current ranges of the normally available panels. As shown in Table 1.1, the number of cells per module is in the range of 36 to 72. Each PV cell is actually a p-n junction with a forward voltage around 0.5V, which makes the output voltage to be in the range of 18~36V at MPP.

In order to connect to the grid with AC voltage in the range of  $100 \sim 230$ Vrms, the low input voltage would need to be boosted by up to around  $10\sim20$  times. This variable and high step-up ratio needs to be considered in the selection and design of inverter topology.

| Manufacturer       | Module <sup>1</sup>         | MPP Voltage | MPP<br>Current | Number<br>of Cells |

|--------------------|-----------------------------|-------------|----------------|--------------------|

| Unit               |                             | V           | A              |                    |

| Kyocera KC130TM/GT |                             | 17.6        | 7.39           | 36                 |

| -                  | KD135GX-LP                  | 17.7        | 7.63           | 36                 |

|                    | KC175GT                     | 23.6        | 7.42           | 48                 |

|                    | KD180GX-LP                  | 23.6        | 7.63           | 48                 |

|                    | KC200GT                     | 26.3        | 7.61           | 54                 |

|                    | KD 205/210 GX-LP            | 26.6        | 7.71/7.9       | 54                 |

| Sharp              | NE-Q5E2U                    | 34.6        | 4.77           | 72                 |

|                    | NT-175U1                    | 35.4        | 4.95           | 72                 |

|                    | ND-187U1F                   | 25.8        | 7.25           | 54                 |

|                    | ND-200/ 216                 | 28.42~28.71 | 7.04~7.53      | 60                 |

| Shell              | SP150-P                     | 34          | 4.4            | 72                 |

|                    | Ultra 165/175 -PC           | 35/35.4     | 4.72/ 4.95     | 72                 |

| Solar World        | SW130/140/150 Poly          | 18.9~20.1   | 6.9~7.5        | 40                 |

|                    | SW155/165/175 Poly          | 34.8~36     | 4.5~4.9        | 72                 |

|                    | SW165/175 mono              | 34.4/35.7   | 4.8/4.9        | 72                 |

|                    | SW160~185 mono              | 35~36.3     | 4.58~5.1       | 72                 |

|                    | SW200/210/220 Poly          | 28.6~29.8   | 7~7.4          | 60                 |

| Sun Power          | SPR-205/215/220             | ~40.0       | 5.13~5.53      | 72                 |

| Sun Tech           | STP160/165/170/175/180S     | 34.4~35.6   | 4.65~5.05      | 72                 |

|                    | STP 190/200/210             | 26~26.4     | 7.31~7.95      | 54                 |

|                    | STP 260/270/280 S           | ~35         | 7.43~7.95      | 72                 |

| BP solar           | REW/ BP3-125/130            | 17.4/17.3   | 7.2/7.5        | 36                 |

|                    | REW/BP3-155/160/165/170/175 | 34.4~36     | 4.5~4.9        | 72                 |

|                    | REW/BP4-160/165/170/175     | 34.3~35.6   | 4.5~4.9        | 72                 |

|                    | BP3-210/220/230             | 28.9~29.2   | 7.3~7.9        | 60                 |

|                    | SX3-195/200                 | 24.4.24,5   | 7.96/8.16      | 50                 |

| Conergy            | SC170/175/180M              | 35.5~36     | 4.79~5         | 72                 |

|                    | S 190-210P                  | 26~26.4     | 7.31-7.95      | 54                 |

|                    | Powerplus 190-230 P/M       | 25~30       | 6.72~7.95      | 60                 |

|                    | YL 210/220 Wp               | 29/30       | 7.2/7.4        | 60                 |

Table 1.1: Panel specifications under STC (Standard Test Conditions: Irradiance 1kW/m2, AM1.5 spectrum, module temperature 25 °C)

<sup>1</sup> Usually, the number in the name of PV panel (for example the digits '130' in Kyocera KC130TM/GT) indicates the power level in W.

As each panel would need a separate inverter, a large enough power rating is preferred for AC module application so as to reduce the cost per watt. It is noted that with the increase of power level, the PV module current can reach as high as 8A at MPP in STC (Standard Testing Condition). The low voltage (18~40V) and high current (up to 8A) requirements at the PV side need to be considered in selecting a proper inverter topology.

One more factor to be considered is the voltage ripple seen by the PV panel which will affect its overall efficiency as discussed in the next section. The power topology selection and its design are also influenced by the need to keep this ripple small.

### 1.2.2. Power Control Requirements

Overall, the power control part is in charge of controlling the power processing part to ensure the requirement for operating at the MPP imposed by the PV module and requirements for the grid connection specified by international standards.

#### 1.2.2.1. Maximum Power Point Tracking (MPPT) Requirement

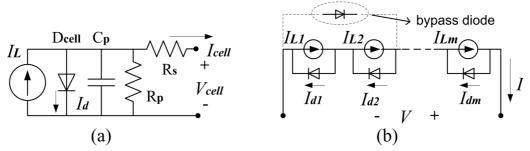

Fig.1.5: Simple electrical model of (a) a PV cell and (b) a PV panel made up of m cells in series

A PV cell is actually a large area p-n junction device with provision for external light to fall on the junction region to allow photovoltaic carrier generation. An electrical model that is commonly used to study its electrical characteristics is shown in Fig.1.5 (a). It is mainly composed of a light generated current source  $I_L$  and a diode in parallel. The generation of the current  $I_L$  involves two key processes [20]. The first is the absorption of incident photons resulting in the creation of electron-hole pairs. The second step is the separation of the electron and the hole by the action of the electric field existing in the p-n junction resulting in the generation of current. This p-n junction, however, also works as an internal load represented by the diode in Fig.1.5.

The parasitic elements shown in Fig. 1.5(a), such as the parallel capacitor  $C_p$ , is neglected in our simple analysis. The model of a PV panel made up of *m* cells in series is illustrated in Fig.1.5 (b). In an ideal case, assuming that all cells are perfectly matched, the equation for the I-V curve of the PV panel is obtained as:

$$I = I_L - I_d = I_L - I_o \left[ \exp(\frac{V}{m \times nV_t}) - 1 \right]$$

(1-1)

where,  $I_o$  is the reverse saturation current of the diode, *m* is the number of solar cells in series, *n* is the ideality factor, and  $V_t$  is the thermal voltage of a semiconductor, which is given by  $V_t = kT/q = 26mV$  at room temperature where k (=1.38×10<sup>-23</sup> J/K) is the Boltzmanns constant, T is the absolute temperature (in K) and q (=1.6×10<sup>-19</sup> C) is the electron charge.

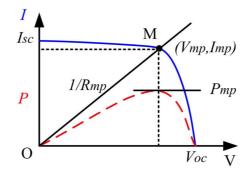

Fig.1.6: PV panel I-V curve (solid) and P-V curve (dashed) without shading

From the electrical model given by (1-1), the current-voltage (I-V) curve and power-voltage (P-V) curve of a PV panel can be obtained as illustrated in Fig.1.6. Here  $V_{oc}$  and  $I_{sc}$  refer to the open circuit voltage and short circuit current of the panel. The MPP is the point where the peak value of the P-V curve is reached, or the point on the I-V curve that defines the largest possible rectangle area (= $I_{mp} \times V_{mp}$ ) under it.

It may be noted that the idea behind the model is to reproduce the DC characteristic curve accurately and not the realization of an accurate physical model. An equation similar to the ideal PV equation is used to model the practical PV cell. Here,  $I_o$  and  $mnV_t$  are replaced with  $C_1$  and  $C_2$ . These constants are selected so that the resulting PV characteristics match reasonably with the manufacturer's data. Thus, the parameters of  $V_{oc}$ ,  $I_{sc}$ ,  $V_{mp}$  and  $I_{mp}$  given by the manufacturer's datasheet can be taken as inputs to calculate two unknown parameters  $C_1$  and  $C_2$ .

The characteristic resistance  $R_{mp}$ , of a PV panel is defined as the ratio of the voltage to current at MPP, equal to one over the slope of the line 'OM' through the MPP:

$$R_{mp} = \frac{V_{mp}}{I_{mp}} \tag{1-2}$$

If the effective load resistance seen by the panel is equal to this characteristic resistance, the maximum possible power is extracted from the panel. It is also noted that by increasing the illumination level, the current available at the MPP increases greatly. Though the MPP voltage does not change much with changing irradiance, it does increase significantly with reduction in temperature. Therefore, in order to make sure the maximum possible power is obtained under varying working conditions, an MPP tracking function must be included in the inverter control system.

The operating temperature of a PV panel will only change slowly due to the large thermal time constants involved, for example, 7~15 min for a BP Solar BP585 85W PV panel[21]. However, changes in irradiance can occur suddenly, e.g. caused by passing clouds [22]. The inverter should be capable of tracking the MPP fast enough during such changes in irradiation.

The maximum power obtainable also depends on the voltage ripple at the terminal of the PV panel. The ripple should be sufficiently small as any operating point deviation from MPP would result in power reduction. In [1], a second-order Taylor series approximation of the current has been used to calculate the average power from the panel when a sinusoidal voltage ripple is added upon the MPP voltage. The results show that the amplitude of the sinusoidal voltage ripple (usually at double the line frequency) should be below 8.5% of the MPP voltage in order to maintain

average operation at 98% of the MPP power. This also needs to be considered in any microinverter topology study.

### 1.2.2.2. Grid Connection Requirements

Traditionally, "utility electric power systems (grid or utility) were not intended to accommodate active generation at the distribution level [23]". Therefore, several standards have been evolved for dealing with the various issues involved in the interaction between the utility and the distributed generation systems. These standards have been developed by international organizations such as the IEEE (Institute of Electrical and Electronics Engineers) and IEC (International Electrotechnical Commission), and institutions and utilities local to individual countries such as the National Fire Protection Association, Inc, Underwriter Laboratories, Inc. (UL) in the U.S.A. and the European Committee for Electrotechnical Standardization (CENELEC). Some of the most widely accepted standards include IEEE 1741 [23, 24], IEC 61727 [25], IEC 62109 [26], UL1741 [27] and National Electrical Code (NEC) 690.

According to these standards, the interconnection requirements mainly involve the following: 1) power quality requirement, 2) fault detection and protection, and 3) synchronization and reconnection. We will mainly use IEC61727 in our work as it establishes a unified standard that is widely used in different countries with different grid systems. A summary of the most important requirements from the grid connection point of view is listed in Table 1.2.

| $\frac{1}{1000} = \frac{1}{1200} = \frac{1}{1000} = 1$ |                               |                                |                                      |                                |       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|--------------------------------------|--------------------------------|-------|--|--|--|

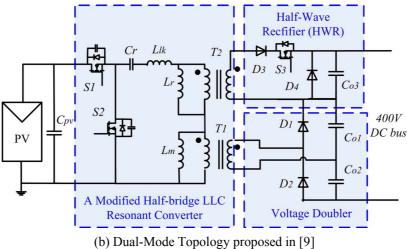

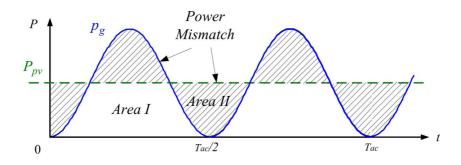

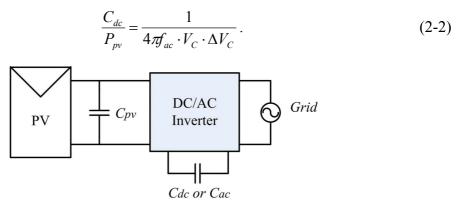

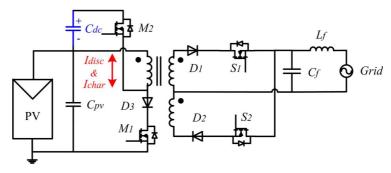

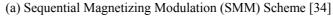

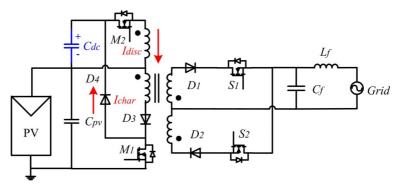

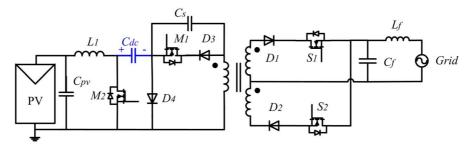

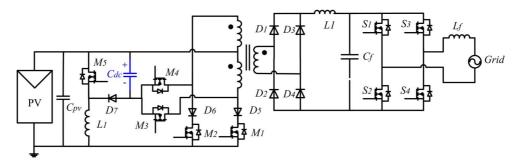

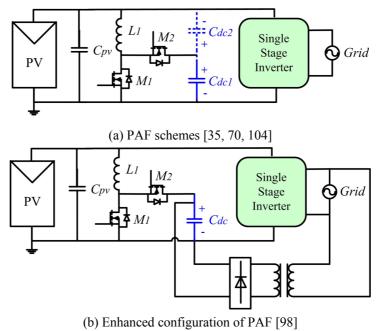

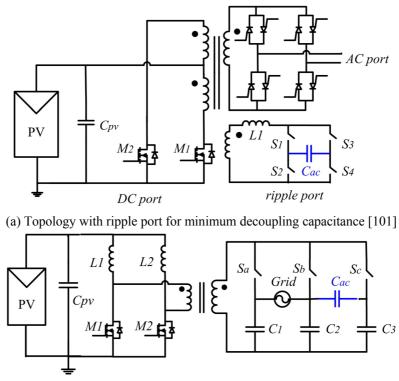

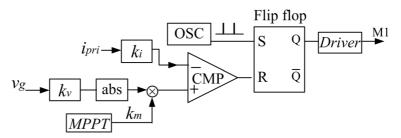

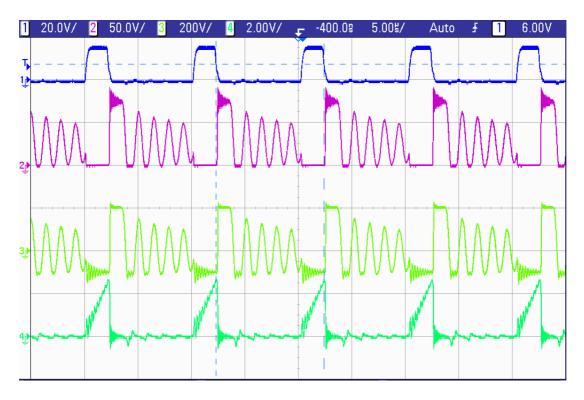

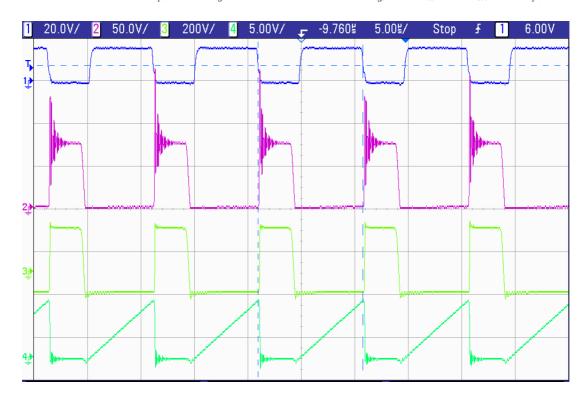

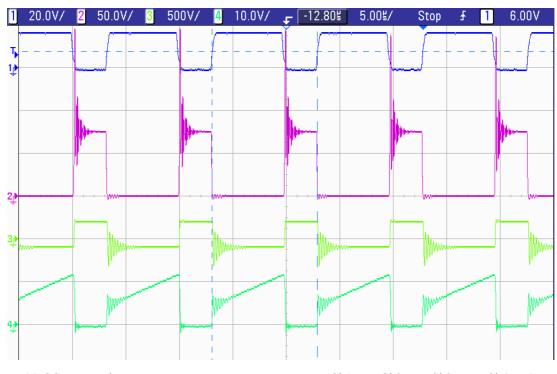

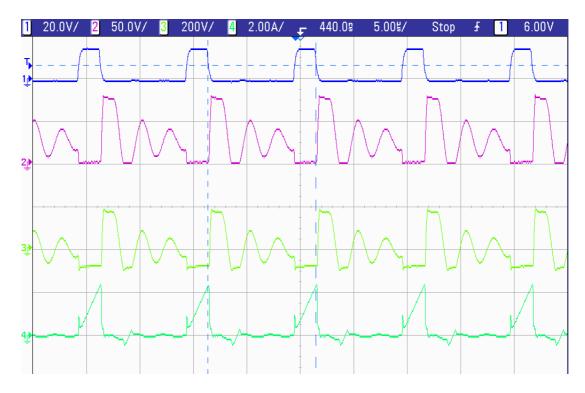

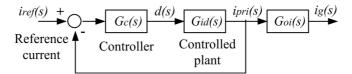

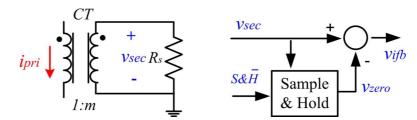

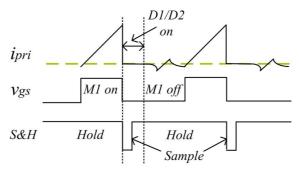

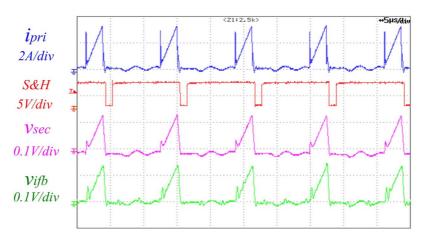

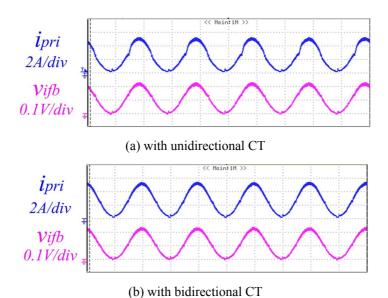

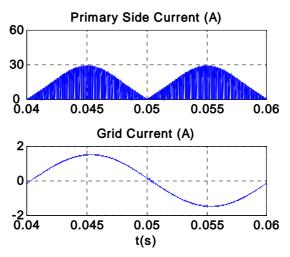

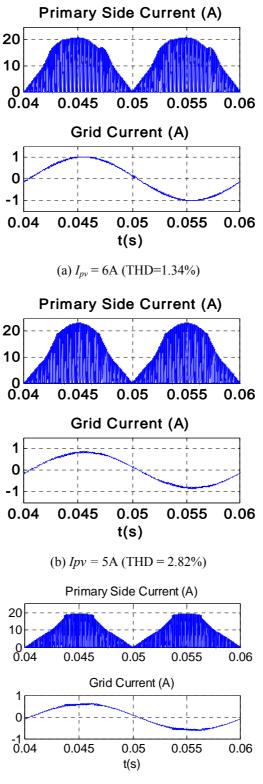

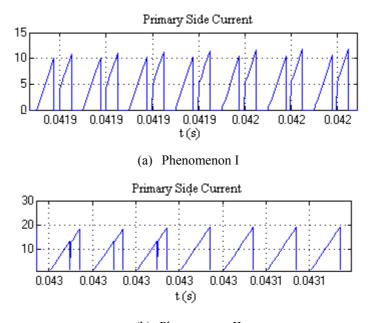

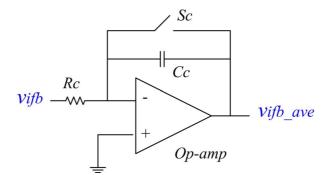

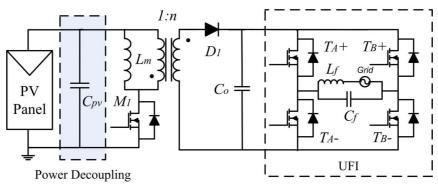

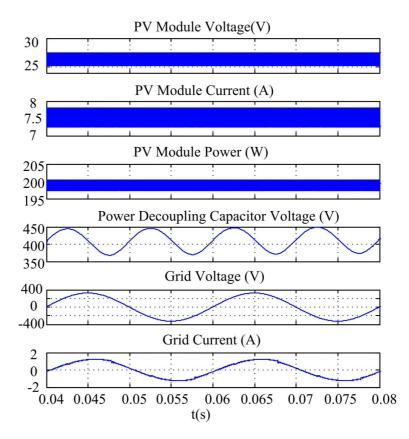

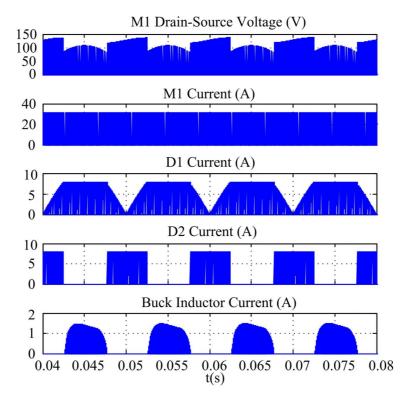

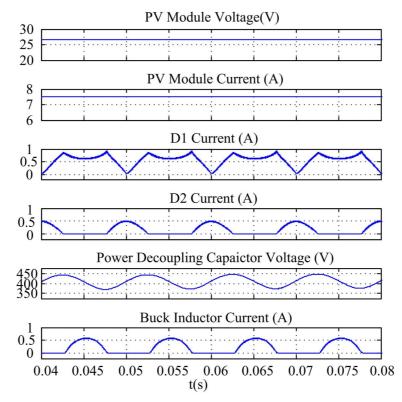

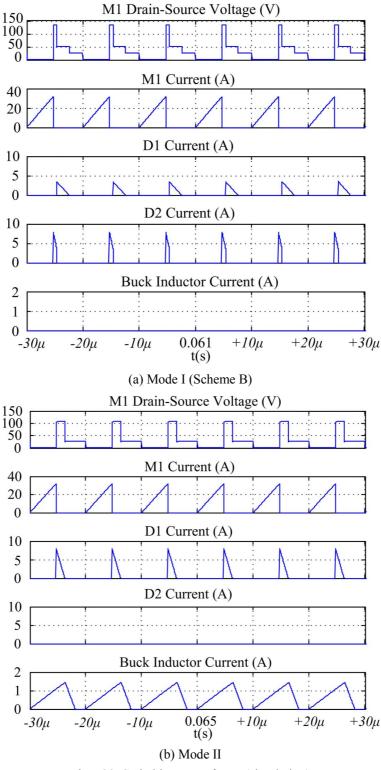

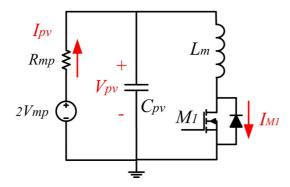

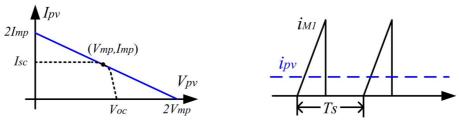

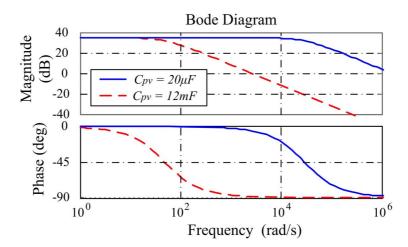

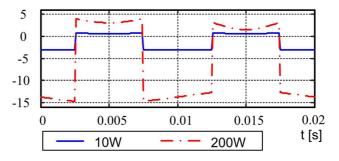

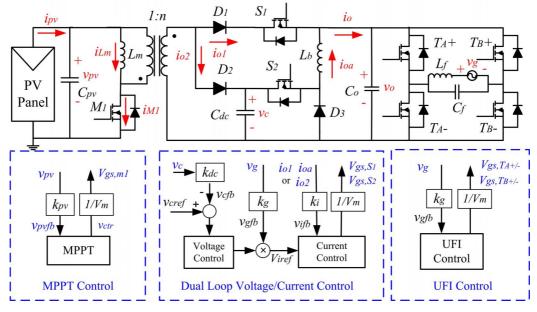

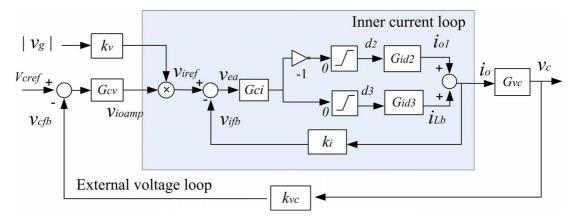

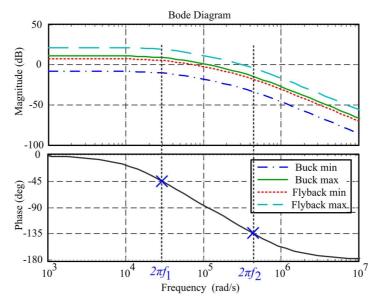

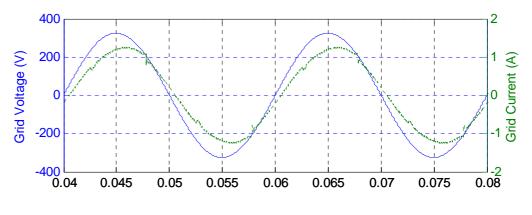

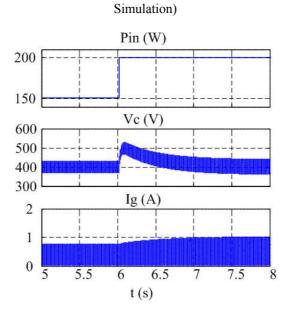

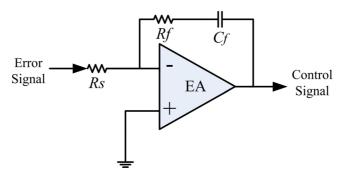

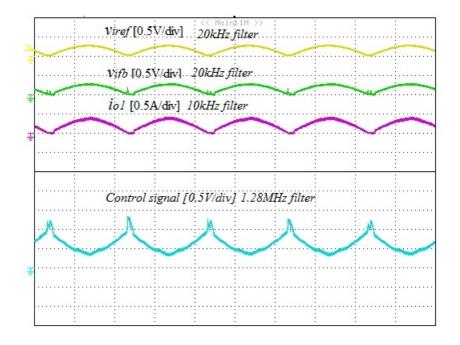

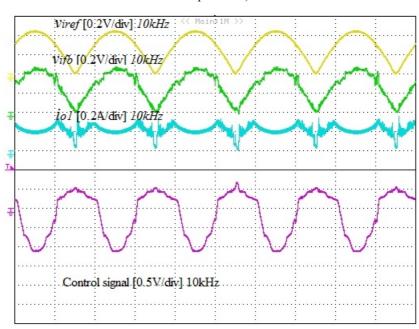

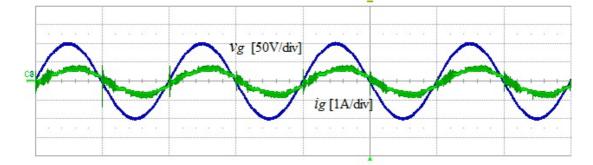

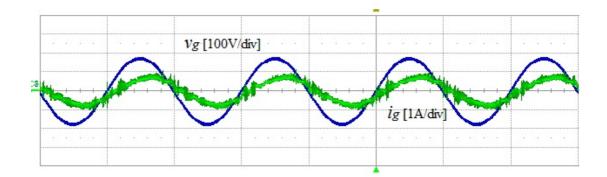

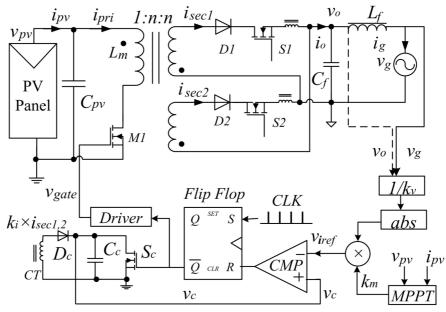

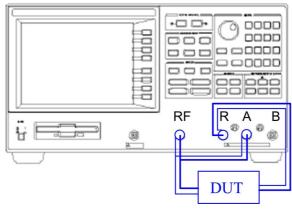

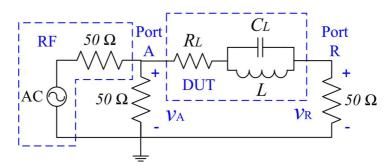

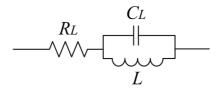

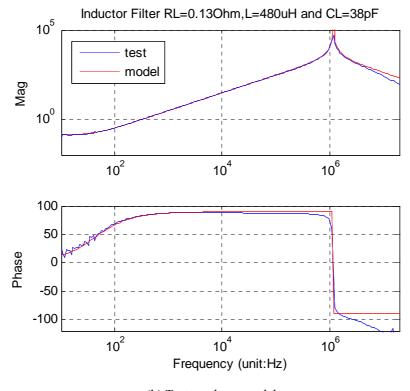

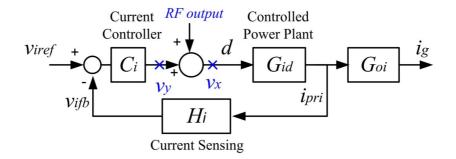

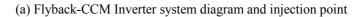

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1) Power Quality Requirements |                                |                                      |                                |       |  |  |  |