## **EXTENDING SI CMOS: INGAAS AND GESN**

## HIGH MOBILITY CHANNEL TRANSISTORS

### FOR FUTURE HIGH SPEED AND

## LOW POWER APPLICATIONS

GONG XIAO

NOTIONAL UNIVERSITY OF SINGAPORE

### **EXTENDING SI CMOS: INGAAS AND GESN**

### HIGH MOBILITY CHANNEL TRANSISTORS

### FOR FUTURE HIGH SPEED AND

### LOW POWER APPLICATIONS

**GONG XIAO**

## A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## NUS GRADUATE SCHOOL FOR INTEGRATIVE

### SCIENCES AND ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

### Declaration

# I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any

degree in any university previously.

Gong Xiao / May 17 2013

Gong Xiao

# Acknowledgements

This is perhaps the shortest but most important section of my thesis. First and foremost, I would like to express my earnest gratitude and appreciation to my research advisor, Dr. Yeo Yee Chia, for his encouragement, motivation, and trust throughout my graduate work. He has always been there to give insights into my research work, and I have greatly benefited from his vast knowledge and strong technical expertise. In addition, I have learnt from him how to achieve great things and be humble and nice at the same time. He is undoubtedly one of the most important and helpful people in my life. I am extremely fortunate to work with the finest advisor that one could possibly hope for.

I would like to thank Prof. Gengchiau Liang and Dr. Daniel Chua for serving as members of my Thesis Advisory Committee, and for their valuable guidance and suggestions during the course of my research work.

I am deeply grateful to Prof. Dimitri Antoniadis, who has been an excellent role model. Having discussion with him has been an extremely rewarding experience. He is always kind and generous in sharing his years of success and experience in the field of semiconductors and nanotechnology. This will be a continuous source of inspiration for me throughout my career. I am also grateful to Prof. Yoon Soon Fatt and Dr. Loke Wan Khai from Nanyang Technological University for valuable discussions on III-V epitaxy process.

I would like to thank Mr. Chum Chan Choy, Dr. Deng Jie, and Ms. Teo Siew Lang for their great help with my device fabrication work at the Institute of Materials Research and Engineering. During my PhD, I have been very fortunate to interact with many outstanding researchers and graduate students in SNDL. Special thanks to Dr. Chin Hock Chun for mentoring me on fabrication and characterization of InGaAs transistors during the initial phase of my research. Special thanks also to Dr. Han Genquan for being a mentor, friend, and great supporter for my research. I enjoyed all the technical and nontechnical discussions we had. I would also like to thank Zhou Qian, Wang Wei, Samuel, Phyllis, Shao Ming, Ivana, Yang Yue, Pengfei, Liu Bin, Xingui, Huaxin, Xinke, Chunlei, Tong Yi, Zhu Zhu, Cheng Ran, Wenjuan, Lanxiang, Eugene, Tong Xin, Yinjie, Sujith, Bai Fan, Guo Cheng, Kain Lu, Kian Hui, Dong Yuan, Xu Xin, and many others. Thank you all for enriching my life and making my years at NUS very enjoyable. I would also like to thank the technical staff of SNDL, namely Mr. O Yan Wai Linn, Mr. Patrick Tang, and Ms. Yu Yi for their support and help.

No words can ever adequately express my deepest thanks and gratitude to my family. To my dad, mum, sister and brother-in-law, thank you for your continuous love, sacrifice, support, and encouragement that have allowed me to pursue my academic dreams. I am eternally grateful to you for being there for me at all times.

| Table of | of Cont | tents |

|----------|---------|-------|

|----------|---------|-------|

| Acknowedgementsi                                                                        |  |  |

|-----------------------------------------------------------------------------------------|--|--|

| Table of Contentsiv                                                                     |  |  |

| Summaryix                                                                               |  |  |

| List of Tables xii                                                                      |  |  |

| List of Figuresxiii                                                                     |  |  |

| List of Symbols xxvii                                                                   |  |  |

| Chapter 1 Introduction1                                                                 |  |  |

| 1.1 Background 1                                                                        |  |  |

| 1.2 High Mobility Channel Materials for Future CMOS Applications                        |  |  |

| 1.3 Key Challenges and Issues to Be Addressed for InGaAs N-MOSFETs                      |  |  |

| and GeSn P-MOSFETs7                                                                     |  |  |

| 1.3.1 Formation of Low Resistance S/D Regions                                           |  |  |

| 1.3.2 Formation of High-Quality Gate Stack for InGaAs N-MOSFETs                         |  |  |

| 1.3.3 Formation of High-Quality Gate Stack for GeSn P-MOSFETs                           |  |  |

| 1.3.4 Surface Orientation Study for GeSn P-MOSFETs                                      |  |  |

| 1.3.5 Fabrication of Multi-Gate GeSn P-MOSFETs                                          |  |  |

| 1.4 Thesis Outline                                                                      |  |  |

| Chapter 2 Source/Drain Engineering for In <sub>0.7</sub> Ga <sub>0.3</sub> As N-Channel |  |  |

| Metal-Oxide-Semiconductor Field Effect Transistors:                                     |  |  |

| Raised Source/Drain with In Situ Doping for Series                                      |  |  |

| Resistance Reduction13                                                                  |  |  |

| 2.1 Introduction                                                                        |  |  |

| 2.2 Design Concept                                                                      |  |  |

| 2.3.  | 1 Selective Epitaxy of <i>In situ</i> Doped Raised S/D | 19 |

|-------|--------------------------------------------------------|----|

| 2.3.2 | 2 Process Flow and Device Fabrication                  | 22 |

| 2.3.  | 3 Device Characterization and Analysis                 | 27 |

| 2.4   | Summary                                                | 35 |

| Chapter 3 | <b>3</b> Advanced Gate Stack Technology for In <sub>0.7</sub> Ga <sub>0.3</sub> As N-       |

|-----------|---------------------------------------------------------------------------------------------|

|           | Channel Metal-Oxide-Semiconductor Field-Effect                                              |

|           | Transistors                                                                                 |

| 3.1 In    | ntroduction                                                                                 |

| 3.2 Se    | elf-Aligned Gate-First In <sub>0.7</sub> Ga <sub>0.3</sub> As N-MOSFETs with an InP Capping |

| L         | ayer for Performance Enhancement                                                            |

| 3.2.1     | Design Concept                                                                              |

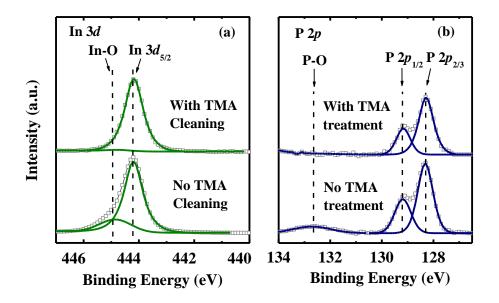

| 3.2.2     | High Quality and Thermally Stable Al <sub>2</sub> O <sub>3</sub> /InP Interface             |

| 3.2.3     | Fabrication and Electrical Characterization of Self-Aligned Gate-                           |

|           | First $In_{0.7}Ga_{0.3}As$ N-MOSFETs with an InP Capping Layer                              |

| 3.3 Se    | elf-Aligned Gate-First $In_{0.7}Ga_{0.3}As$ N-MOSFETs with Sub-400 °C                       |

| S         | i <sub>2</sub> H <sub>6</sub> Passivation and HfO <sub>2</sub> High-k Gate Dielectric       |

| 3.3.1     | Design Concept                                                                              |

| 3.3.2     | Device Fabrication and Characterization                                                     |

| 3.4 C     | omparison and Discussion of Two Advanced Gate Stack                                         |

| Т         | echniques: InP Capping and Si <sub>2</sub> H <sub>6</sub> Passivation                       |

| 3.4.1     | Benchmarking of Subthreshold Swing                                                          |

| 3.4.2     | Effect of InP or Si Thickness on the Drive Current of InGaAs N-                             |

|           | MOSFETs                                                                                     |

| 3.4.3     | Comparison of Integration Challenges and Options for InP Capping                            |

|           | and Si <sub>2</sub> H <sub>6</sub> Passivation                                              |

| 3.5 Si    | ummary                                                                                      |

| Chapter 4 | 4 Germanium-Tin (GeSn) P-Channel MOSFETs with                                               |

|-----------|---------------------------------------------------------------------------------------------|

|           | High Hole Mobility and Excellent NBTI Reliability                                           |

|           | <b>Realized by Low Temperature Si<sub>2</sub>H<sub>6</sub> Passivation 66</b>               |

| 4.1 In    | troduction                                                                                  |

| 4.2 Si    | $_{2}H_{6}$ and $(NH_{4})_{2}S$ Passivation Techniques and Effect on the Electrical         |

| C         | haracteristics of GeSn P-Channel MOSFETs                                                    |

| 4.2.1     | GeSn Growth and Material Characterization                                                   |

| 4.2.2     | Fabrication of Ge <sub>0.958</sub> Sn <sub>0.042</sub> P-MOSFETs                            |

| 4.2.3     | Results and Discussion                                                                      |

| 4.3 N     | egative Bias Temperature Instability Study of Si <sub>2</sub> H <sub>6</sub> Passivated     |

| G         | eSn P-MOSFETs                                                                               |

| 4.3.1     | NBTI Characterization Method                                                                |

| 4.3.2     | Results and Discussion                                                                      |

| 4.4 Te    | owards High Performance $Ge_{1-x}Sn_x$ and $In_{0.7}Ga_{0.3}As$ CMOS: Common                |

| G         | ate Stack Featuring Sub-400 °C Si <sub>2</sub> H <sub>6</sub> Passivation, Single TaN Metal |

| G         | ate, and Sub-1.75 nm CET                                                                    |

| 4.4.1     | Design Concept of TaN/HfO2/SiO2/Si Stack on InGaAs and GeSn 88                              |

| 4.4.2     | Device Fabrication                                                                          |

| 4.4.3     | Electrical Characterization                                                                 |

| 4.5 Su    | ummary                                                                                      |

| Chapte | r 5 Performance Enhancement for GeSn P-Channel                                          | Performance Enhancement for GeSn P-Channel<br>Metal-Oxide-Semiconductor Field-Effect Transistors: |  |

|--------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

|        | Metal-Oxide-Semiconductor Field-Effect Transist                                         |                                                                                                   |  |

|        | Surface Orientation and Gate Length Scaling                                             | 97                                                                                                |  |

| 5.1    | Introduction                                                                            |                                                                                                   |  |

| 5.2    | Ge <sub>0.958</sub> Sn <sub>0.042</sub> P-MOSFETs Fabricated on (100) and (111) Surface |                                                                                                   |  |

|        | Orientations with Sub-400 °C Si <sub>2</sub> H <sub>6</sub> Passivation                 |                                                                                                   |  |

| 5.2.1  | l Device Fabrication                                                                    |                                                                                                   |  |

| 5.2.2  | 2 Material Characterization                                                             | 100                                                                                               |  |

| 5.2.3  | Electrical Characterization                                                             |     |

|--------|-----------------------------------------------------------------------------------------|-----|

| 5.3 I  | Fabrication and Characterization of Short channel Ge <sub>0.95</sub> Sn <sub>0.05</sub> |     |

| ]      | P-MOSFETS                                                                               | 113 |

| 5.3.1  | Device Fabrication                                                                      |     |

| 5.3.2  | Electrical Characterization                                                             |     |

| 5.4 \$ | Summary                                                                                 |     |

##

| 6.1   | Introduction                                                                       | . 121 |

|-------|------------------------------------------------------------------------------------|-------|

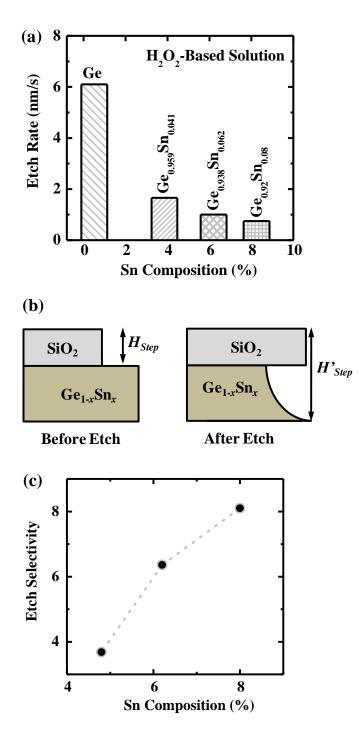

| 6.2   | Novel Process Technology for $Ge_{1-x}Sn_x$ Nanowire Formation                     | . 124 |

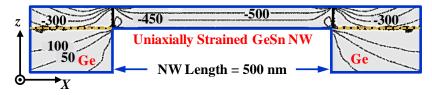

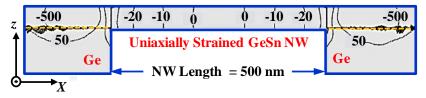

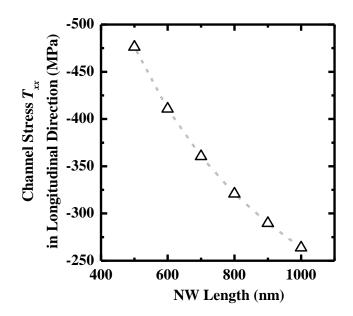

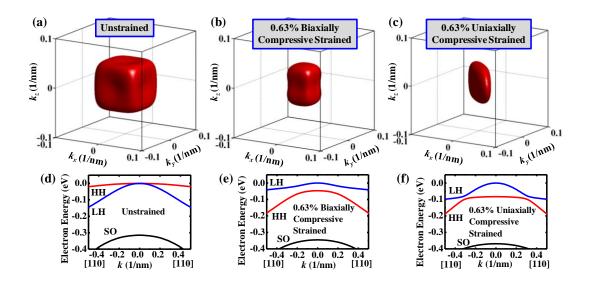

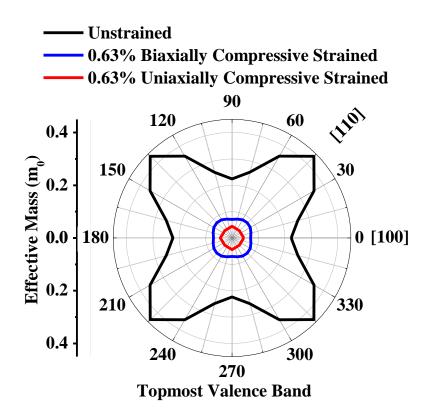

| 6.3   | Uniaxially Strained Germanium-Tin (GeSn) Nanowire                                  | . 128 |

| 6.4   | Reduction in Effective Mass and Interband Scattering by Uniaxial                   |       |

|       | Compressive Strain                                                                 | . 130 |

| 6.5   | Fabrication and Characterization of Ge <sub>0.959</sub> Sn <sub>0.041</sub> GAA NW |       |

|       | P-MOSFETs                                                                          | . 132 |

| 6.5.1 | 1 Device Fabrication                                                               | . 132 |

| 6.5.2 | 2 Electrical Characterization                                                      | . 136 |

| 6.6   | Summary                                                                            | . 140 |

### Chapter 7 Conclusion and Future Work......141

| 7.1 <b>(</b> | Conclusion and Contributions of This Thesis                                           | 141 |

|--------------|---------------------------------------------------------------------------------------|-----|

| 7.1.1        | Raised Source/Drain (S/D) with In situ Doping for Series                              |     |

|              | Resistance Reduction of In <sub>0.7</sub> Ga <sub>0.3</sub> As N-MOSFETs              | 141 |

| 7.1.2        | Advanced Gate Stack Technologies for In <sub>0.7</sub> Ga <sub>0.3</sub> As N-MOSFETs | 142 |

| 7.1.3 | GeSn P-MOSFETs with High Hole Mobility and Excellent Negative   | /e  |

|-------|-----------------------------------------------------------------|-----|

|       | Bias Temperature Instability (NBTI) Reliability Realized by Low |     |

|       | Temperature Si <sub>2</sub> H <sub>6</sub> Passivation          | 143 |

| 7.1.4 | Performance Enhancement for GeSn P-MOSFETs: Surface             |     |

|       | Orientation and Gate Length Scaling                             | 143 |

| 7.1.5 | Uniaxially Strained GeSn Gate-All-Around (GAA) Nanowire         |     |

|       | (NW) P-MOSFETs                                                  | 144 |

| 7.2 F | uture Directions                                                | 144 |

| 7.2.1 | Integration of InGaAs and GeSn on Silicon Substrates            | 144 |

| 7.2.2 | Novel Strain Techniques to Enhance the Hole Mobility of GeSn    |     |

|       | P-MOSFETs                                                       | 145 |

| 7.2.3 | Extremely Scaled GeSn P-MOSFETs                                 | 145 |

| 7.2.4 | Ultrathin body and NW GeSn P-MOSFETs                            | 145 |

| 7.2.5 | Gate Stack Technology and Strain Engineering for GeSn           |     |

|       | N-MOSFETs with High Electron Mobility                           | 146 |

| mondi | er en                       |     |

# Appendix

| List of Publications |  | . 17 | 14 | 1 |

|----------------------|--|------|----|---|

|----------------------|--|------|----|---|

# **Summary**

Extending Si CMOS: InGaAs and GeSn High Mobilty Channel Transistors for Future High Speed and Low Power Logic Application

by

GONG Xiao

Doctor of Philosophy – NUS Graduate School for Integrative Sciences and Engineering

National University of Singapore

As the semiconductor industry approaches the limits of traditional silicon CMOS scaling, the introduction of performance boosters such as novel materials and innovative device structures has become necessary for future high speed and low power logic applications. High mobility materials are being considered to replace Si as the channel materials, in order to achieve higher drive currents at lower operating voltages. In particular, InGaAs and Ge or GeSn have become of great interest due to their high electron and hole mobilities, respectively. This thesis work aims to address various challenges in taking full advantage of the high mobility channel materials for future CMOS logic applications.

For  $In_{0.7}Ga_{0.3}As$  N-MOSFETs, a selective epitaxy process using MOCVD was first developed to grow a high quality InGaAs film. The process module was then integrated into a self-aligned gate-first process to fabricate the  $In_{0.7}Ga_{0.3}As$  N-MOSFETs. Significant reduction in S/D series resistance was achieved due to combined contributions from the high S/D doping concentration as well as the structural improvement arising from the raised S/D structure.

Next, the concept and demonstration of two novel surface passivation techniques were exploited to realize high-quality metal gate/high-*k* dielectric stacks on InGaAs: InP capping and low-temperature  $Si_2H_6$  passivation. Introducing an InP capping layer in  $In_{0.7}Ga_{0.3}As$  N-MOSFETs was found to reduce the subthreshold swing *S* and increase the drive current. Low-temperature  $Si_2H_6$  passivation was developed to effectively passivate the  $In_{0.7}Ga_{0.3}As$  surface, enabling the realization of  $In_{0.7}Ga_{0.3}As$  N-MOSFETs with high drive current and *S* comparable to the best reported in the literature. Both interface engineering techniques are highly compatible with a matured high-*k* dielectric deposition process, and provide promising options for interface passivation to exploit the full potential of InGaAs N-MOSFETs.

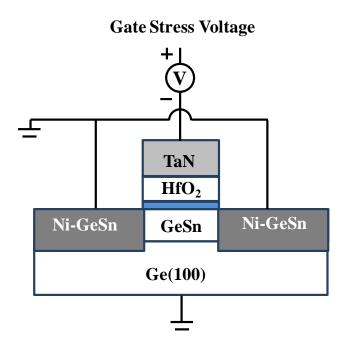

For GeSn P-MOSFETs, low-temperature  $Si_2H_6$  passivation was first developed to realize a high quality interface between the high-*k* dielectric and the GeSn, as well as excellent transistor NBTI reliability. For the first time, a common gate stack technology comprising 370 °C  $Si_2H_6$  passivation and TaN/HfO<sub>2</sub> gate stack was proposed and demonstrated for InGaAs and GeSn CMOS devices for costeffective integration.

Two approaches to further enhance the drive current of GeSn P-MOSFETs were then explored: choice of surface orientation and channel length scaling. The world's first short-channel GeSn P-MOSFETs with self-aligned NiGeSn metal S/D were realized using a gate-first process.

Х

In addition, the uniaxially compressive strained GeSn gate-all-around nanowire (NW) P-MOSFETs with the shortest reported channel length down to 100 nm were demonstrated for the first time using a CMOS-compatible top-down approach. This device structure takes advantage of uniaxial compressive strain for mobility enhancement by etching NWs from a biaxially strained layer, as well as a 3D device architecture for control of short channel effects at extremely scaled dimensions. The GeSn NW formation technology shows promise for integration in future high performance GeSn P-MOSFETs.

# **List of Tables**

| Table 1.1. | Key parameters of possible channel materials for future CMOS                        |     |

|------------|-------------------------------------------------------------------------------------|-----|

|            | applications [1.18]                                                                 | 4   |

| Table 3.1. | Comparison of InP capping and $\mathrm{Si}_2\mathrm{H}_6$ passivation techniques in |     |

|            | terms of the gate stack quality for higher drive current and better                 |     |

|            | subthreshold characteristics as well as the integration challenges and              |     |

|            | options                                                                             | .64 |

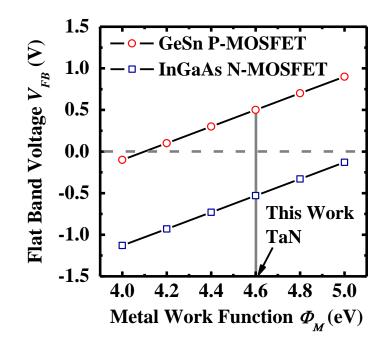

| Table 4.1. | Parameters used in the calculation of flat-band voltage $V_{FB}$ as a               |     |

|            | function of metal work function $\Phi_M$ shown in Fig. 4.19                         | .89 |

| Table 6.1. | Recipe used to etch the $Ge_{1-x}Sn_x$ film and the underneath Ge layer in          |     |

|            | the RIE tool.                                                                       | 124 |

# **List of Figures**

| Fig. 1.1. | Transistor scaling and manufacturing-development-research pipeline                       |

|-----------|------------------------------------------------------------------------------------------|

|           | of CMOS technology2                                                                      |

| Fig. 1.2. | Schematic of an ultimate CMOS structure using InGaAs N-                                  |

|           | MOSFET and Ge or GeSn P-MOSFET6                                                          |

| Fig. 2.1. | Schematic illustration of the channel resistance $(R_{CH})$ and the                      |

|           | source/drain resistance $(R_{SD})$ of a transistor in the linear region. The             |

|           | total resistance $(R_{Total})$ between the source contact and drain contact              |

|           | of the transistor is the summation of these resistance components.                       |

|           | The introduction of high mobility InGaAs channel reduces $R_{CH}$ . For                  |

|           | further enhancement of drive current, S/D engineering to reduce $R_{SD}$                 |

|           | is also important14                                                                      |

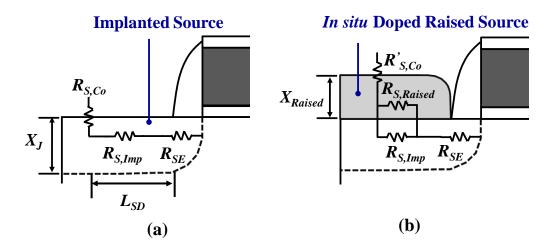

| Fig. 2.2. | Schematics of the source region of MOSFETs, (a) without in situ                          |

|           | doped raised source, and (b) with in situ doped raised source. The                       |

|           | dashed line represents the source-channel $n^+/p$ junction16                             |

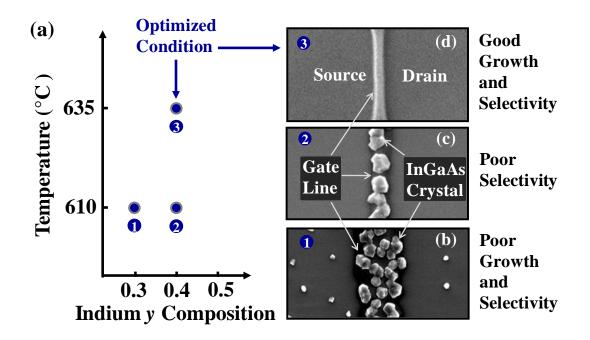

| Fig. 2.3. | (a) composition and MOCVD growth temperature are the two key                             |

|           | factors affecting the growth. SEM images show the $In_{0.4}Ga_{0.6}As$ film              |

|           | quality and selectivity over $SiO_2$ hardmask and SiON spacer regions:                   |

|           | (b) three dimensional growth due to huge lattice mismatch; (c) good                      |

|           | quality $In_{0.4}Ga_{0.6}As$ growth with poor selectivity; (d) selective                 |

|           | growth was achieved by increasing temperature to enable the                              |

|           | desorption of nucleated seeds on the gate lines and spacers20                            |

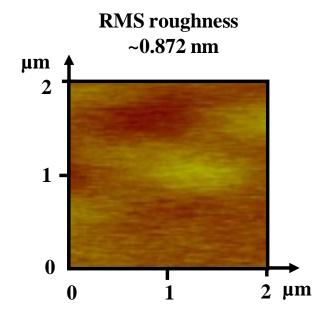

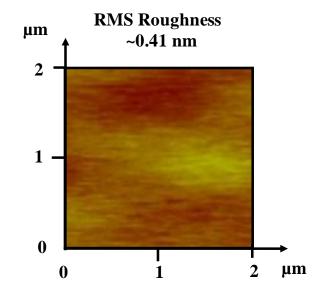

| Fig. 2.4. | AFM shows RMS surface roughness of the In <sub>0.7</sub> Ga <sub>0.3</sub> As surface in |

|           | the S/D regions after spacer etch, indicating a good growth starting                     |

|           | surface. The RMS surface roughness of the pristine $In_{0.7}Ga_{0.3}As/InP$              |

|           | starting substrate was ~0.32 nm                                                          |

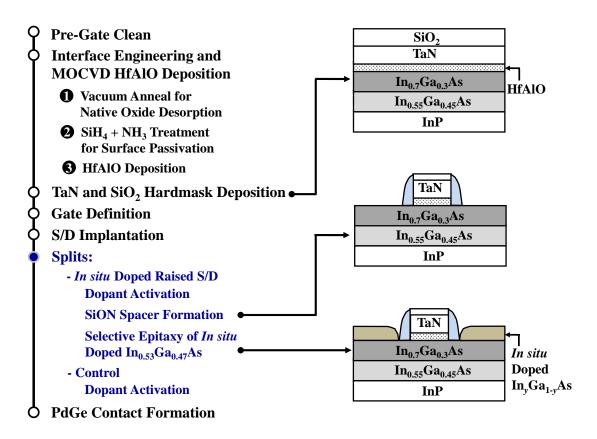

| Fig. 2.5. | (a) Process sequence employed in the fabrication of $In_{0.7}Ga_{0.3}As$                 |

|           | channel N-MOSFETs with in situ doped raised S/D, with cross-                             |

|           | section schematics after steps of (b) TaN and $SiO_2$ hardmask                           |

|            | deposition, (c) SiON spacer formation, and (d) selective epitaxy of in                                              |

|------------|---------------------------------------------------------------------------------------------------------------------|

|            | <i>situ</i> doped In <sub>y</sub> Ga <sub>1-y</sub> As                                                              |

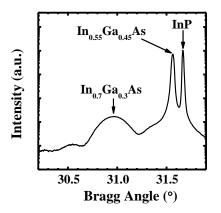

| Fig. 2.6.  | HRXRD shows well-defined In <sub>0.7</sub> Ga <sub>0.3</sub> As and In <sub>0.55</sub> Ga <sub>0.45</sub> As peaks, |

|            | indicating high crystalline quality of the epilayers                                                                |

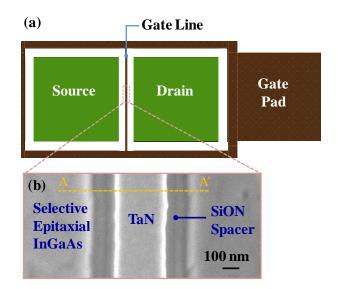

| Fig. 2.7.  | (a) Layout of a transistor structure. (b) SEM image showing the                                                     |

|            | zoomed-in view of the transistor gate line region with selective                                                    |

|            | epitaxial In <sub>0.53</sub> Ga <sub>0.47</sub> As, TaN metal gate and SiON spacers. The                            |

|            | SiON spacers prevent the raised S/D from electrically contacting the                                                |

|            | gate sidewalls. The cross-section TEM image across line A-A' is                                                     |

|            | shown in Fig. 2.825                                                                                                 |

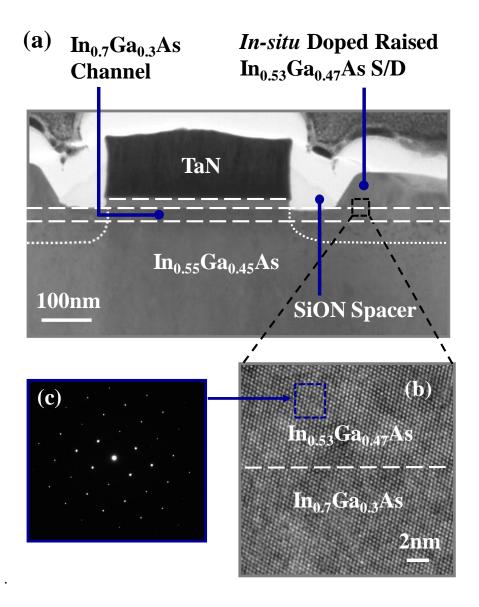

| Fig. 2.8.  | (a) TEM image of a completed In <sub>0.7</sub> Ga <sub>0.3</sub> As channel N-MOSFET                                |

|            | with selectively grown in situ doped raised S/D. (b) High resolution                                                |

|            | TEM and (c) Fast Fourier transform (FFT) diffractogram, revealing                                                   |

|            | the excellent crystalline quality of the $In_{0.53}Ga_{0.47}As$ epilayer26                                          |

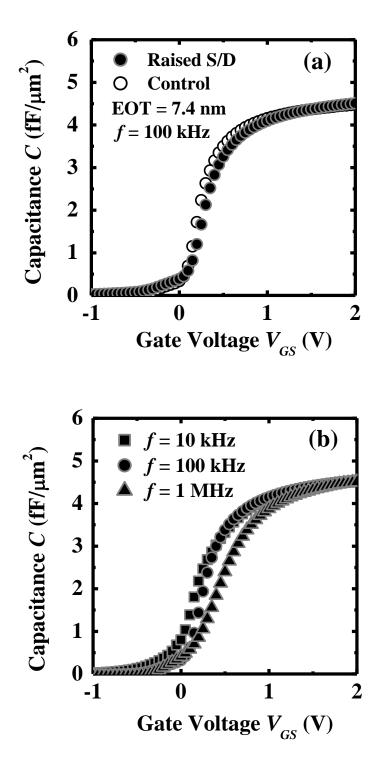

| Fig. 2.9.  | (a) Inversion $C-V$ curves measured at the frequency of 100 kHz show                                                |

|            | comparable equivalent oxide thickness EOT for control device and                                                    |

|            | device with raised S/D. (b) $C-V$ characteristics of the device with                                                |

|            | raised S/D measured from 10 kHz to1 MHz28                                                                           |

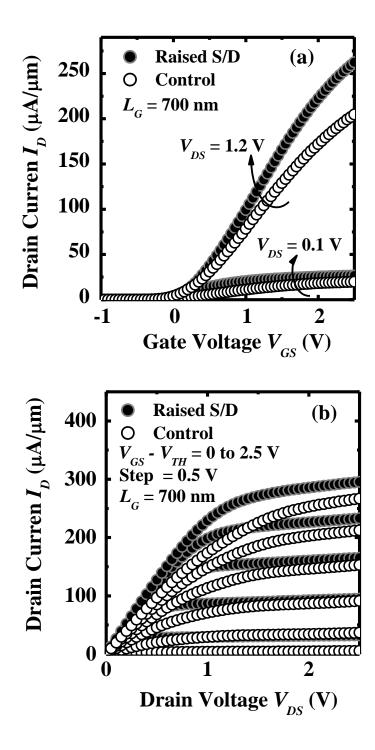

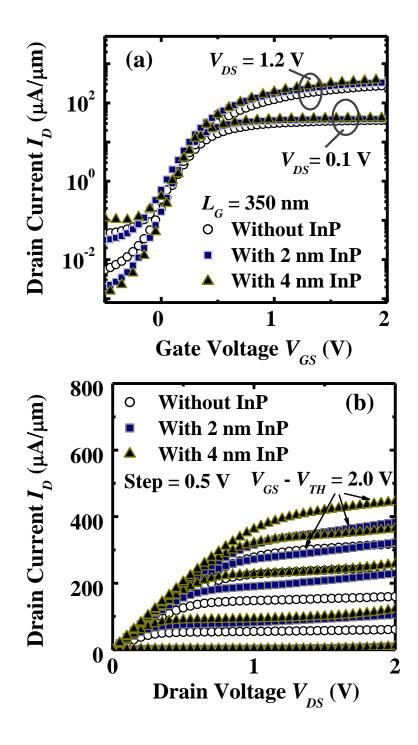

| Fig. 2.10. | (a) $I_D$ - $V_{GS}$ plot in the linear ( $V_{DS} = 0.1$ V) and saturation ( $V_{DS} = 1.2$ V)                      |

|            | regions. (b) $I_D$ - $V_{DS}$ curves of the same pair of devices, showing                                           |

|            | good saturation and pinch-off characteristics. Drive current is higher                                              |

|            | for the $In_{0.7}Ga_{0.3}As$ N-MOSFET with raised S/D as compared with                                              |

|            | the In <sub>0.7</sub> Ga <sub>0.3</sub> As N-MOSFET control                                                         |

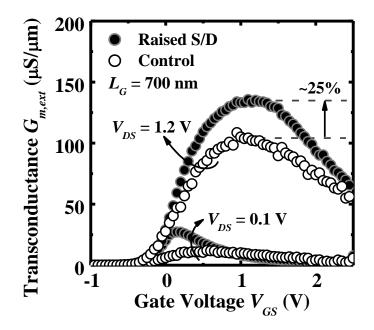

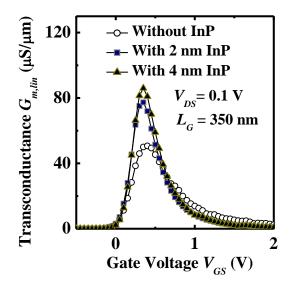

| Fig. 2.11. | $G_{m,ext}$ - $V_{GS}$ curves of the same pair of devices in Fig. 2.10. In situ                                     |

|            | doped raised S/D gives rise to a ~25% enhancement in saturation                                                     |

|            | $G_{m,ext}$ due to source and drain series resistance reduction                                                     |

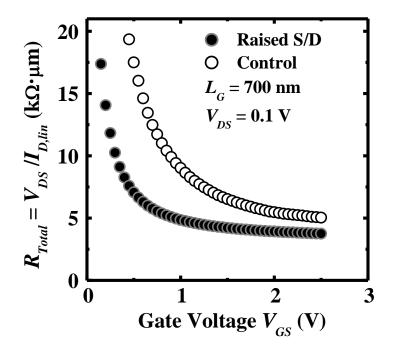

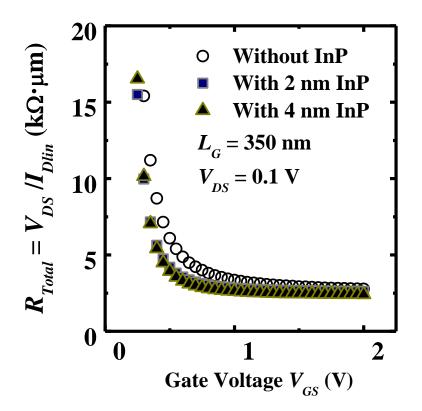

| Fig. 2.12. | Total resistance in linear regime ( $V_{DS} = 0.1$ ) at large $V_{GS}$ indicates                                    |

|            | smaller series resistance of the device with raised S/D than that of                                                |

|            | control                                                                                                             |

|            |                                                                                                                     |

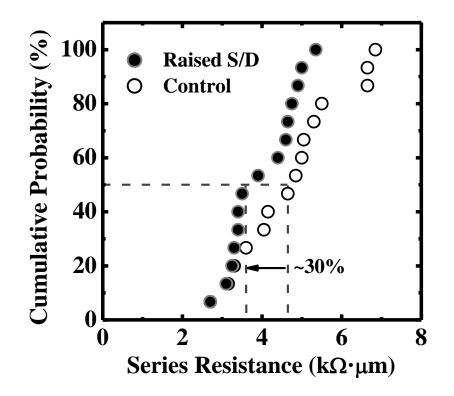

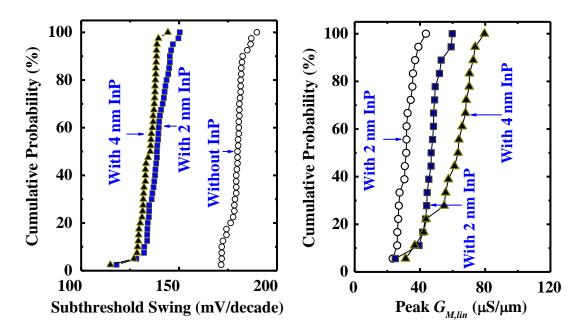

- Fig. 2.13. In situ doped raised S/D leads to ~30% reduction of the median series resistance. 15 devices for each split were measured. The gate lengths of the devices measured range from 350 to 1000 nm......32

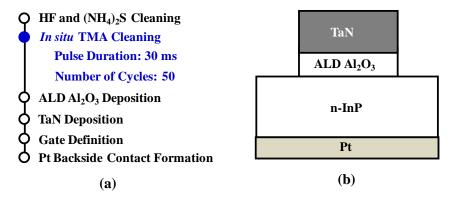

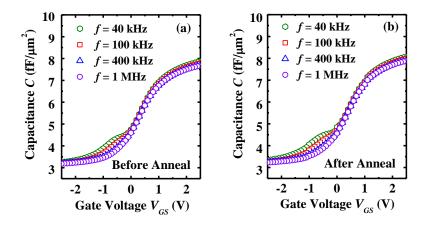

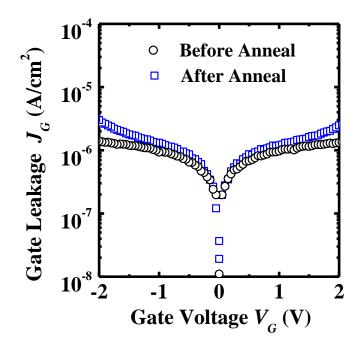

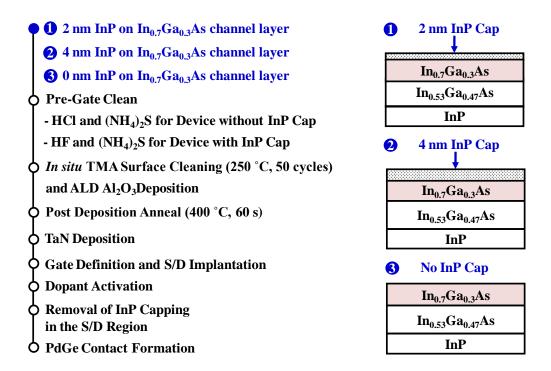

- Fig. 3.2. (a) The process flow for fabricating the InP capacitor, with the TMA cleaning step. (b) The schematic of a completed InP capacitor......40

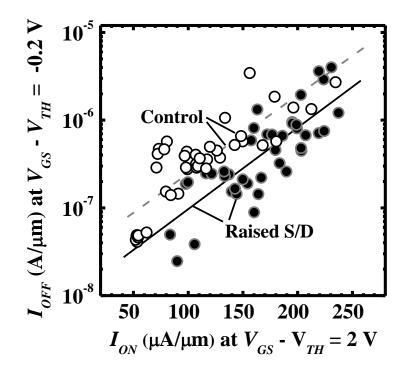

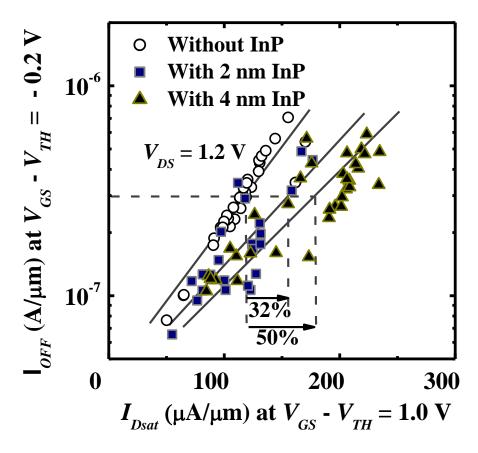

- Fig. 3.12. Plot of off-state leakage current  $I_{OFF}$  versus on-state drain current  $I_{Dsat}$  at  $V_{DS}$  of 1.2 V, showing  $I_{Dsat}$  enhancement of ~32% and ~50%

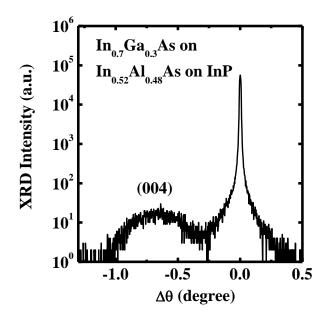

- Fig. 3.15. High-resolution XRD curves show an indium composition of 70% in InGaAs. The well-defined In<sub>0.7</sub>Ga<sub>0.3</sub>As peak indicates excellent crystalline quality of the channel material.

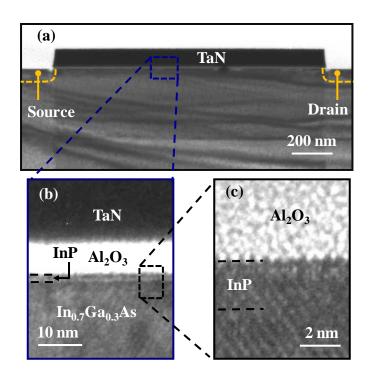

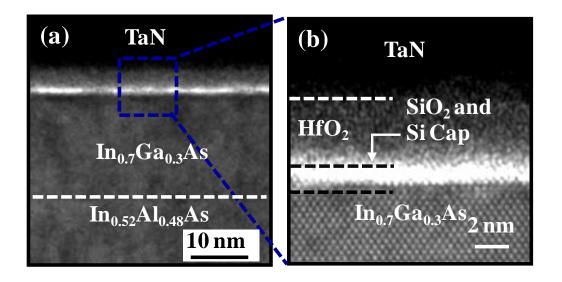

- Fig. 3.17. (a) The cross-sectional TEM image of the TaN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si gate stack on In<sub>0.7</sub>Ga<sub>0.3</sub>As showing the excellent interface quality. The high-resolution image in (b) reveals the existence of an ultra-thin

|            | SiO <sub>2</sub> /Si interfacial layer between the $HfO_2$ and the $In_{0.7}Ga_{0.3}As$             |

|------------|-----------------------------------------------------------------------------------------------------|

|            | channel material. HfO <sub>2</sub> is ~3.6 nm thick56                                               |

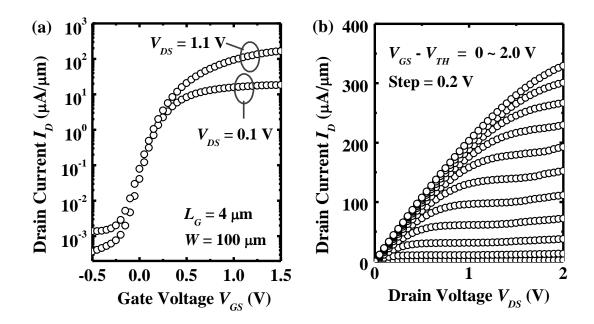

| Fig3.18.   | (a) $I_D$ - $V_{GS}$ curves showing excellent transfer characteristics of an                        |

|            | In <sub>0.7</sub> Ga <sub>0.3</sub> As N-MOSFET. (b) $I_D$ - $V_{DS}$ output characteristics of the |

|            | same transistor in (a). Very high drive current was achieved at a                                   |

|            | gate length $L_G$ of 4 µm, attributed to the excellent interface quality                            |

|            | due to $Si_2H_6$ passivation and the EOT scaling                                                    |

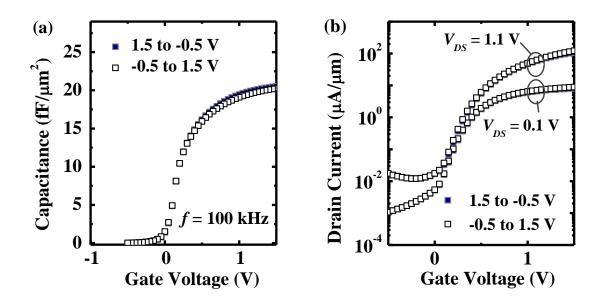

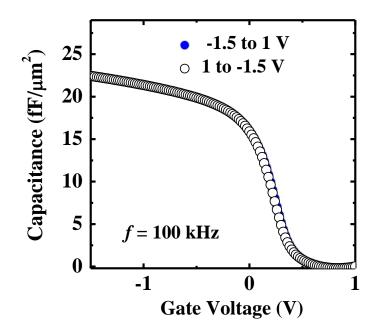

| Fig. 3.19. | (a) Inversion C-V curves measured at 100 kHz for InGaAs N-                                          |

|            | MOSFET yield a CET of ~1.6 nm. Forward and backward sweeps                                          |

|            | were applied to investigate the $C-V$ hysteresis, which is found to be                              |

|            | negligible. This indicates good interface and the gate dielectric                                   |

|            | quality and is consistent with the negligible hysteresis in the $I_D$ - $V_{GS}$                    |

|            | characteristics shown in (b)                                                                        |

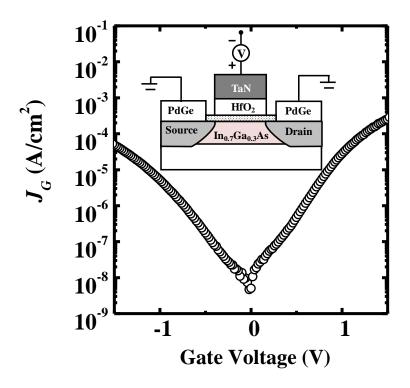

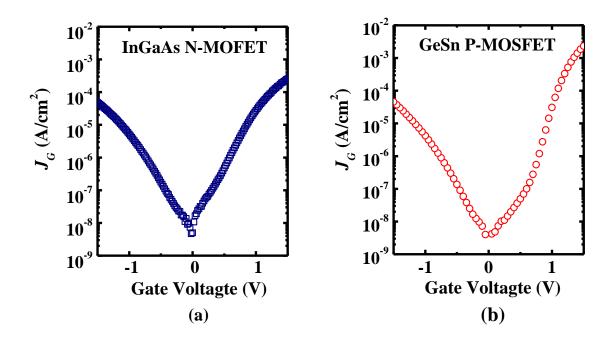

| Fig. 3.20. | Small gate leakage current density $J_G$ was measured. $J_G$ was                                    |

|            | normalized by gate area. There is potential for further scaling of the                              |

|            | ЕОТ                                                                                                 |

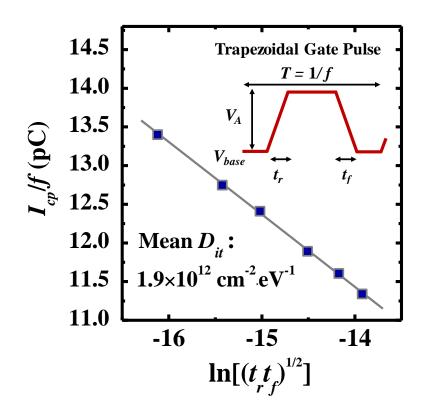

| Fig. 3.21. | Room temperature charge pumping measurement was performed to                                        |

|            | extract the mid-gap $D_{ii}$ . Constant-amplitude trapezoidal gate pulse                            |

|            | train was swept from accumulation to inversion level with rise and                                  |

|            | fall time of gate pulses ranging from 100 ns to 1000 ns. By                                         |

|            | extracting the slope in $I_{CP}/f$ as a function of $\ln[(t_r \cdot t_f)]$ , the mean $D_{it}$ of   |

|            | the InGaAs N-MOSFETs was obtained to be $1.9 \times 10^{12}$ cm <sup>-2</sup> ·eV <sup>-1</sup> 60  |

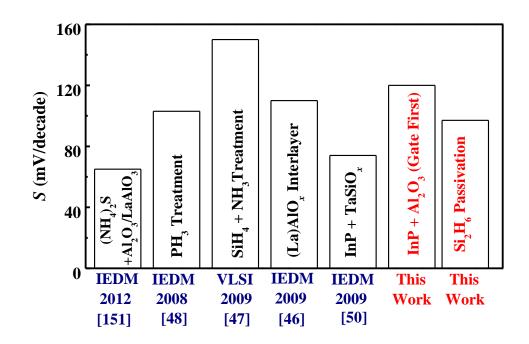

| Fig. 3.22. | Benchmarking of S of InGaAs N-MOSFETs achieved by different                                         |

|            | surface passivation techniques. Low-temperature Si <sub>2</sub> H <sub>6</sub> passivation          |

|            | demonstrated in this work leads to the realization of InGaAs N-                                     |

|            | MOSFETs with $S$ comparable to the best reported values. The $S$ of                                 |

|            | the transistors with InP cap can be reduced by reducing EOT61                                       |

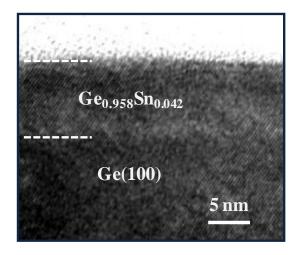

| Fig. 4.1.  | High-resolution TEM image of a 10 nm-thick Ge <sub>0.958</sub> Sn <sub>0.042</sub> film             |

|            | grown on (100)-oriented Ge substrate                                                                |

| E. 4.0     | High marchedian VDD (004) are the second shall defined CaSe much                                    |

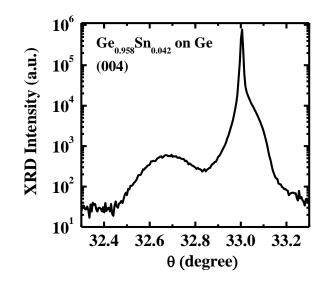

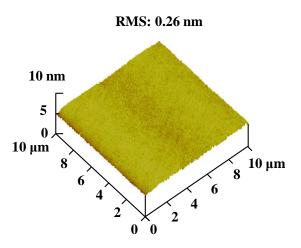

Fig. 4.2.High-resolution XRD (004) curve shows well-defined GeSn peak.The substitutional Sn composition of the GeSn film is ~4.2%......69

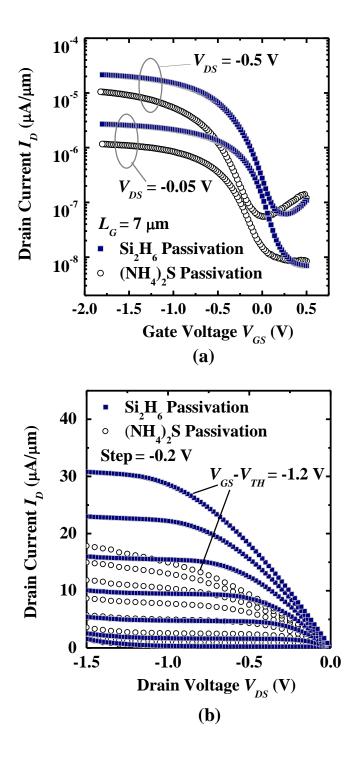

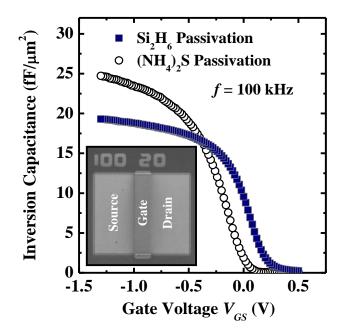

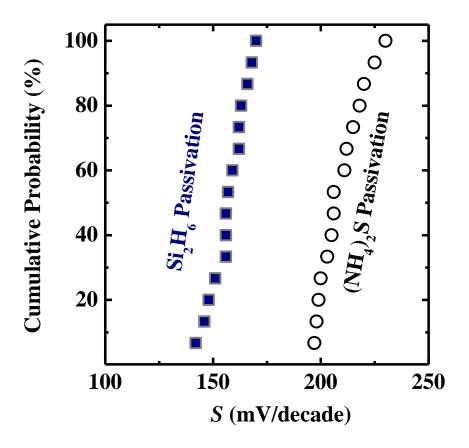

- Fig. 4.7. Despite a smaller  $C_{ox}$ , GeSn P-MOSFETs with Si<sub>2</sub>H<sub>6</sub> passivation have a median S that is ~50 mV/decade lower than that of transistors with (NH<sub>4</sub>)<sub>2</sub>S passivation. The S was extracted at  $V_{DS}$  of -50 mV......75

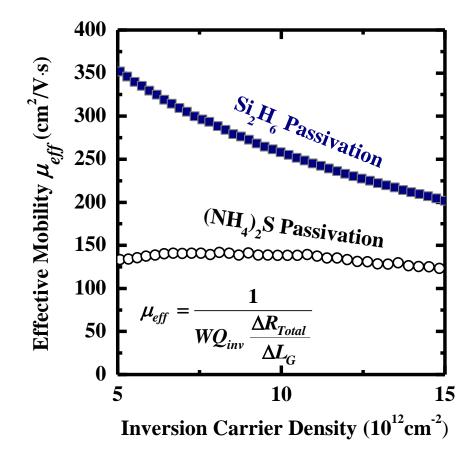

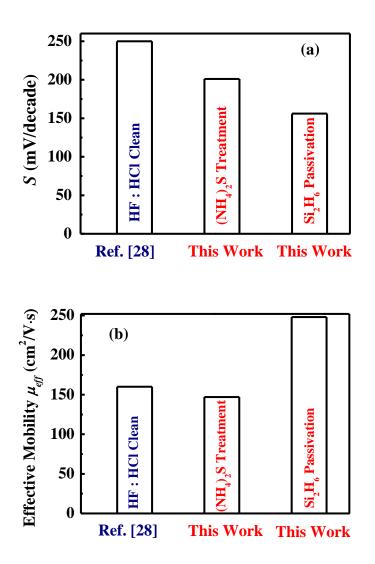

- Fig. 4.9. Low temperature  $Si_2H_6$  passivation in this work enables the realization of GeSn P-MOSFETs with (a) the smallest *S* and (b) highest hole mobility reported.......77

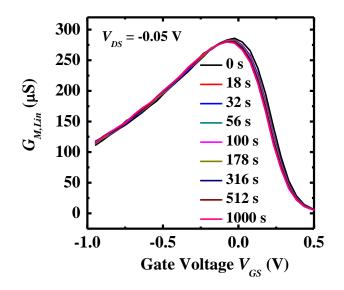

- Fig. 4.16. Very small degradation in peak  $G_{M, Lin}$  suggests that few interface traps were generated near the GeSn valence band under NBTI stress.....85

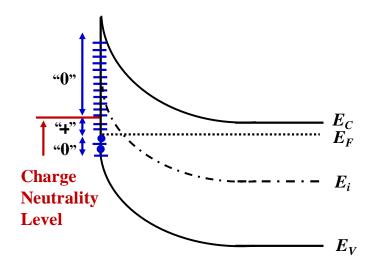

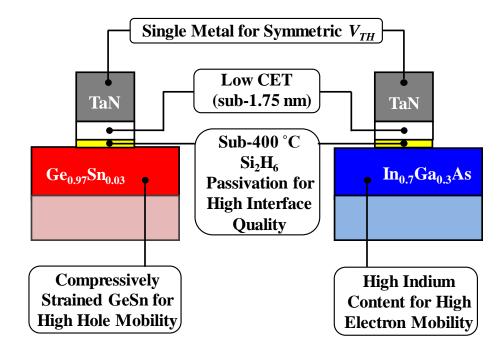

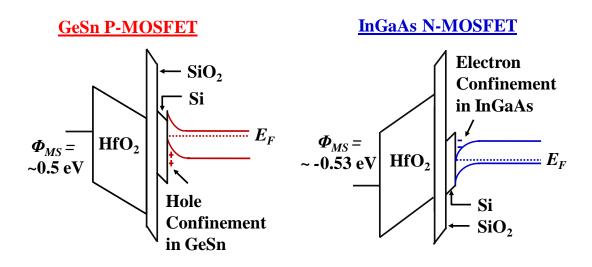

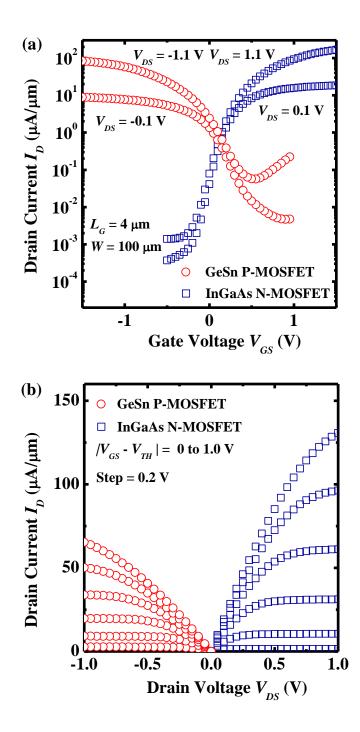

- Fig. 4.17. Key highlights of the common gate stack technology for  $Ge_{0.97}Sn_{0.03}$ P-MOSFETs and  $In_{0.7}Ga_{0.3}As$  N-MOSFETs. Channel materials were

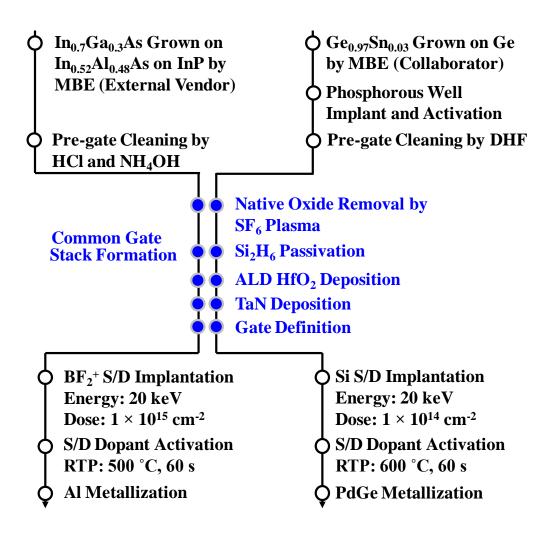

- Fig. 4.20. The process flow for fabricating GeSn P-MSOFETs and InGaAs N-MOSFETs. In all steps of common gate stack formation highlighted in blue, the GeSn and InGaAs wafers were process together.......91

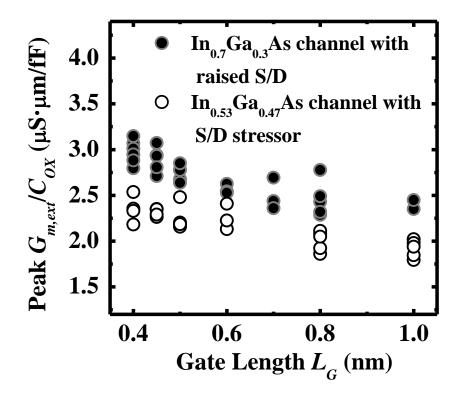

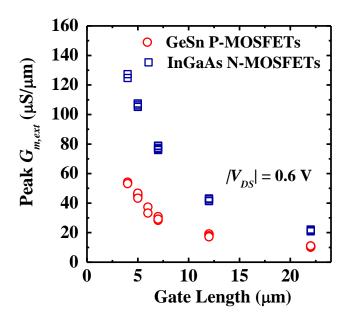

| Fig. 4.24. | The peak $G_{m,ext}$ values scale well with the gate length for both GeSn                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------|

|            | P-MOSFETs and InGaAs N-MOSFETs. InGaAs N-MOSFETs have                                                                     |

|            | 2 times higher peak $G_{m,ext}$ than GeSn P-MOSFETs due to the higher                                                     |

|            | effective carrier mobility95                                                                                              |

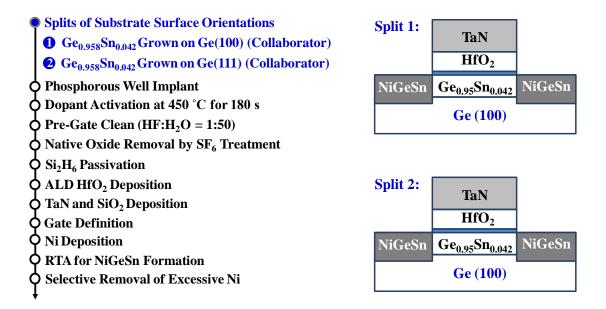

| Fig. 5.1.  | The process flow for fabricating $Ge_{0.958}Sn_{0.042}$ P-MOSFETs. Two                                                    |

|            | splits of substrate surface orientations were introduced: $Ge_{0.958}Sn_{0.042}$                                          |

|            | on Ge(100) or Ge(111). All steps were performed by the author                                                             |

|            | except for the $Ge_{0.958}Sn_{0.042}$ growth                                                                              |

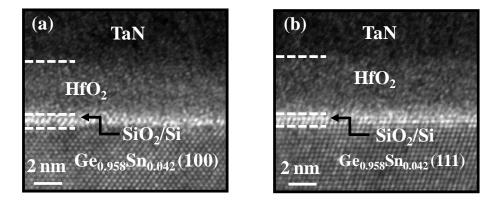

| Fig. 5.2.  | High resolution cross-sectional TEM images of the                                                                         |

|            | TaN/HfO <sub>2</sub> /SiO <sub>2</sub> /Si stack on (a) (100)-oriented and (b) (111)-oriented                             |

|            | $Ge_{0.958}Sn_{0.042}$ surfaces, respectively. An ultra-thin SiO <sub>2</sub> /Si interfacial                             |

|            | layer between the $HfO_2$ and $Ge_{0.958}Sn_{0.042}$ was formed and excellent                                             |

|            | interface quality was observed101                                                                                         |

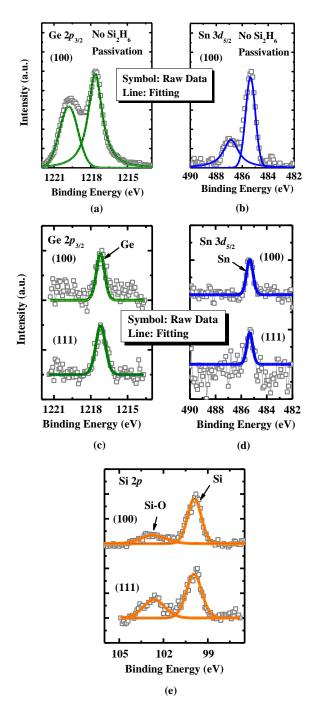

| Fig. 5.3.  | (a) Ge $2p_{3/2}$ and (b) Sn $3d_{5/2}$ core level spectra of (100)-oriented                                              |

|            | $Ge_{0.958}Sn_{0.042}$ sample without $Si_2H_6$ passivation show high intensity                                           |

|            | of Ge-O and Sn-O peaks. $Si_2H_6$ passivation can effectively suppress                                                    |

|            | the formation of Ge-O and Sn-O bonds for both (100)- and (111)-                                                           |

|            | oriented $Ge_{0.958}Sn_{0.042}$ surfaces, as shown in (c) and (d). Part of the                                            |

|            | Si layer was oxidized during the subsequent HfO2 dielectric                                                               |

|            | deposition process, as indicated by the existence of the Si-O peak in                                                     |

|            | the Si 2 <i>p</i> spectra shown in (e)102                                                                                 |

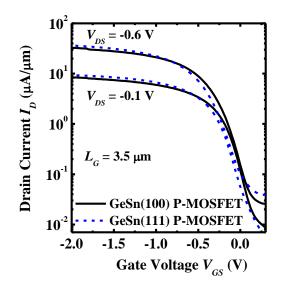

| Fig. 5.4.  | $I_D$ - $V_{GS}$ curves showing excellent transfer characteristics of                                                     |

|            | $Ge_{0.958}Sn_{0.042}$ P-MOSFETs with (100) and (111) surface orientations.                                               |

|            | Similar S was observed, indicating similar mid-gap interface trap                                                         |

|            | density103                                                                                                                |

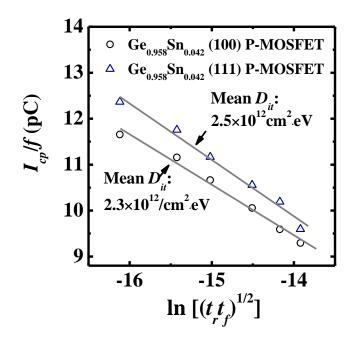

| Fig. 5.5.  | Mid-gap $D_{it}$ was extracted to be $2.3 \times 10^{12}$ and $2.5 \times 10^{12}$ cm <sup>-2</sup> ·eV <sup>-1</sup> for |

|            | (100)- and (111)-oriented $Ge_{0.958}Sn_{0.042}$ P-MOSFETs, respectively,                                                 |

|            | by room temperature charge pumping measurement104                                                                         |

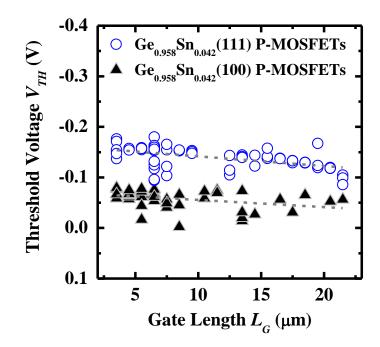

| Fig. 5.6.  | The $V_{TH}$ values of Ge <sub>0.958</sub> Sn <sub>0.042</sub> P-MOSFETs on the (111) substrate                           |

|            | are left-shifted as compared with those of transistors on the (100)                                                       |

xxii

substrate. This could be due to more positive fixed charges at the high-*k*/GeSn interface for the (111)-oriented devices......105

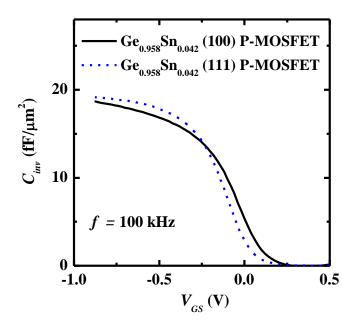

- Fig. 5.7. Inversion C-V characteristics measured at a frequency of 100 kHz. The CET is extracted to be ~1.8 nm based on the inversion capacitance value. Slightly larger inversion capacitance was observed for (111)-oriented transistor as compared with the (100)oriented one......105

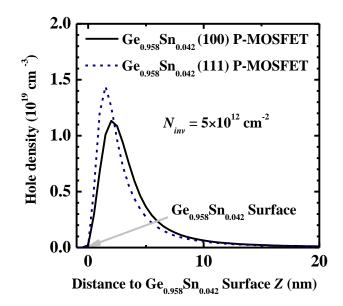

- Fig. 5.8. Simulation shows that  $Ge_{0.958}Sn_{0.042}$  P-MOSFET with (111) orientation has an inversion charge centroid closer to the  $Ge_{0.958}Sn_{0.042}$  surface at an inversion carrier density of  $5 \times 10^{12}$  cm<sup>-2</sup>. This is due to larger density of states for (111)-oriented  $Ge_{0.958}Sn_{0.042}$ .

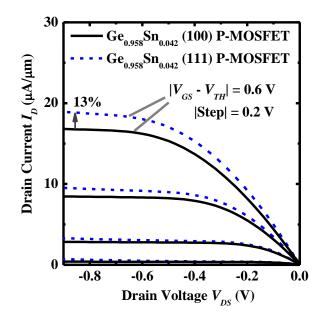

- Fig. 5.9.  $I_D$ - $V_{DS}$  characteristics show that (111)-oriented Ge<sub>0.958</sub>Sn<sub>0.042</sub> P-MOSFET has 13% enhancement in drive current over the (100)oriented device at a gate over drive of -0.6 V and  $V_{DS}$  of -0.9 V......107

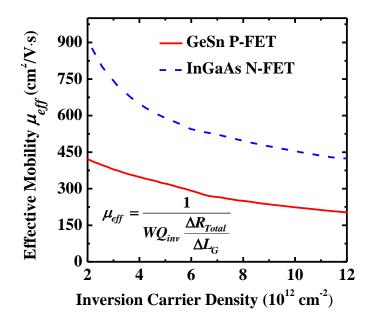

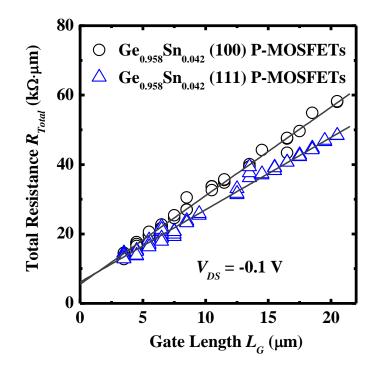

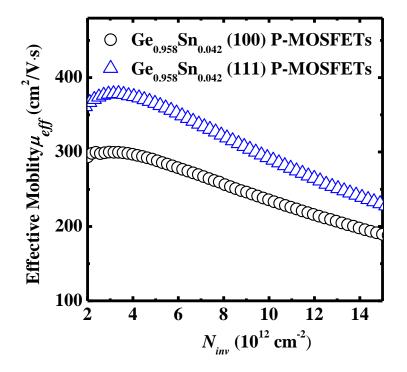

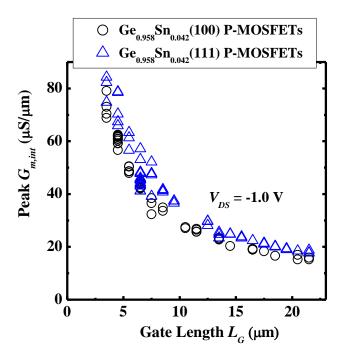

- Fig. 5.11.  $\mu_{eff}$  as a function of  $N_{inv}$  extracted by split C-V method. Higher  $\mu_{eff}$ was observed for the (111)-oriented Ge<sub>0.958</sub>Sn<sub>0.042</sub> P-MOSFET.  $\mu_{eff}$ values at  $N_{inv}$  of  $1.1 \times 10^{13}$  cm<sup>-2</sup> for (100)- and (111)-oriented Ge<sub>0.958</sub>Sn<sub>0.042</sub> P-MOSFETs are 226 and 270 cm<sup>2</sup>/V·s, respectively. This gives ~19 % higher mobility for Ge<sub>0.958</sub>Sn<sub>0.042</sub> P-MOSFETs with (111) surface orientation than with (100) surface orientation, constant with the result shown in Fig. 5. 10.............110

- Fig. 5.12. Monte Carlo simulation in Ref. 5.11 predicts ~15% increase of hole mobility for (111)-oriented Ge surface as compared with the (100)oriented one at 0.5 to 1.0% biaxial compressive strain (Data

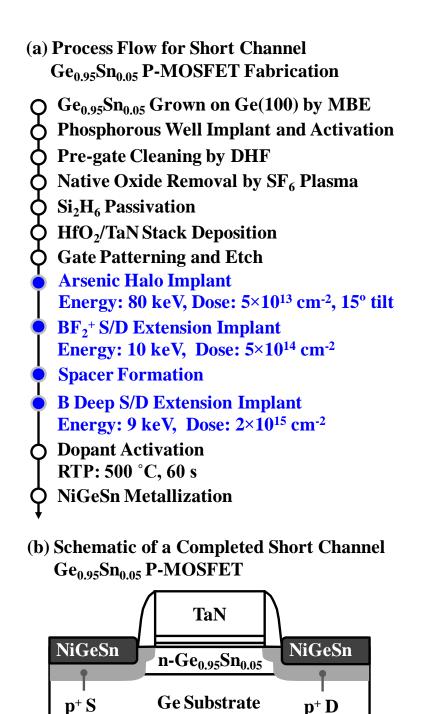

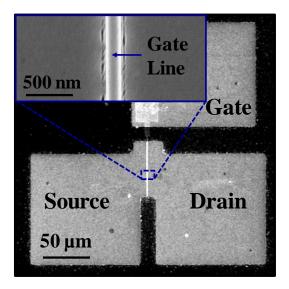

- Fig. 5.14. (a) Process flow for fabricating short channel Ge<sub>0.95</sub>Sn<sub>0.05</sub> P-MOSFET, with a schematic of the completed device structure shown in (b). Advanced modules, such as halo implant and S/D extension implant, were introduced to control the short channel effects......114

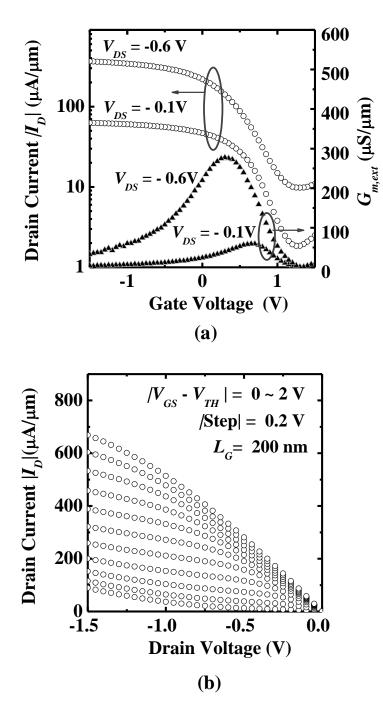

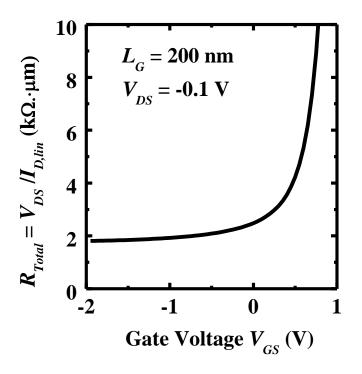

- Fig. 5.17.  $R_{Total}$  measured at  $V_{DS}$  of -0.1 V as a function of  $V_{GS}$  for a Ge<sub>0.95</sub>Sn<sub>0.05</sub> device with  $L_G$  of 200 nm.  $R_{SD}$  was extracted to be ~1.7 k $\Omega$ ·µm......117

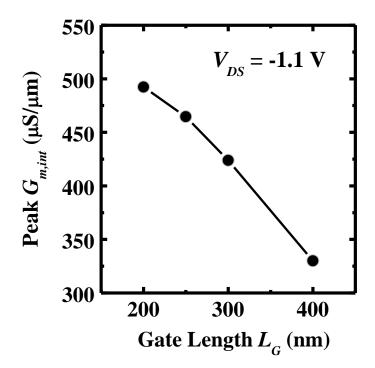

- Fig. 5.18. Peak  $G_{m,int}$  at  $V_{DS}$  of -1.1 V as a function of  $L_G$  shows the good scalability of Ge<sub>0.95</sub>Sn<sub>0.05</sub> short channel devices, with the highest peak  $G_{m,int}$  of ~492 µS/µm achieved at  $L_G$  of 200 nm......118

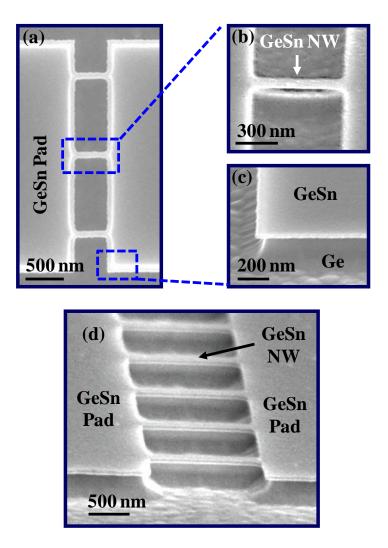

- Fig. 6.2. (a) Top-view SEM image of a GeSn NW test structure after selective wet etch and SiO<sub>2</sub> removal. (b) Tilt-view SEM confirms the GeSn NW release, with (c) very good selectivity achieved. (d) Tilt-view SEM image with multiple parallel GeSn NWs formed......127

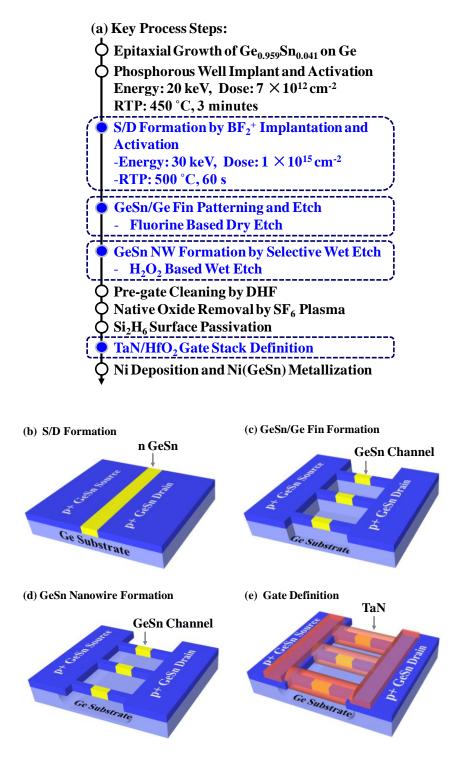

- Fig. 6.7. (a) Key process steps for fabricating GeSn GAA NW P-MOSFETs.The 3D schematics show the structures after the steps of (b) S/D formation, (c) GeSn fin definition, (d) removal of Ge under GeSn, and (e) gate definition.

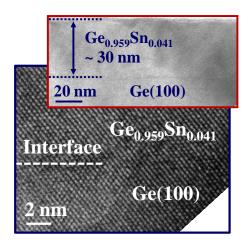

| Fig. 6.8.  | HRTEM images of epitaxial Ge <sub>0.959</sub> Sn <sub>0.041</sub> grown on Ge(100)             |

|------------|------------------------------------------------------------------------------------------------|

|            | substrate show the defect free interface and high quality                                      |

|            | Ge <sub>0.959</sub> Sn <sub>0.041</sub> film                                                   |

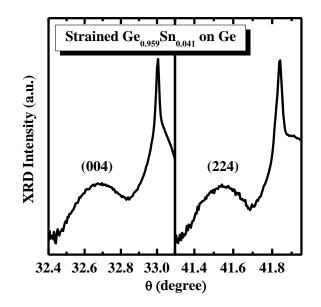

| Fig. 6.9.  | HRXRD (004) and (224) curves show that the GeSn film has a $4.2\%$                             |

|            | substitutional Sn. The well-defined peaks indicate excellent quality                           |

|            | of the $Ge_{0.959}Sn_{0.041}$ channel material                                                 |

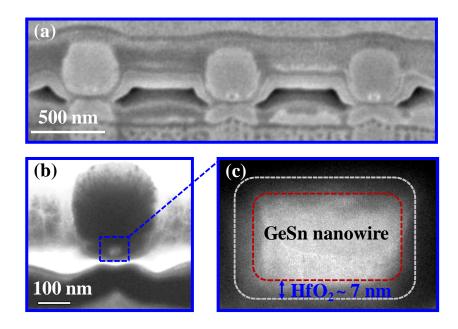

| Fig. 6.10. | (a) Cross-sectional SEM image shows GeSn GAA MOSFETs with 3                                    |

|            | parallel wires. (b) TEM image of one GeSn NW wrapped by high- $k$                              |

|            | $HfO_2$ and WN metal. The GeSn NWs were released and surrounded                                |

|            | by WN/HfO <sub>2</sub> . (c) HRTEM shows a GeSn NW with width of 50 nm                         |

|            | and height of ~35 nm                                                                           |

| Fig. 6.11. | (a) $I_D$ - $V_{GS}$ plot showing decent transfer characteristics of a GeSn                    |

|            | GAA NW MOSFET with $L_{CH}$ of 500 nm. (b) Output characteristics                              |

|            | of the same transistor shown in (a). The current is normalized by the                          |

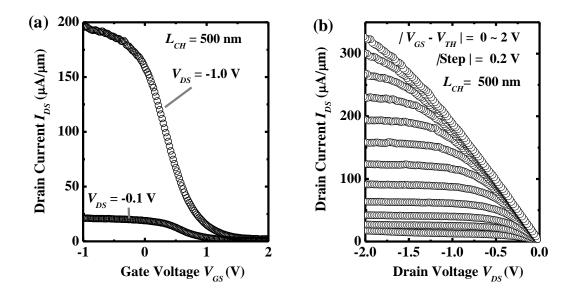

|            | total perimeter of 15 NWs                                                                      |

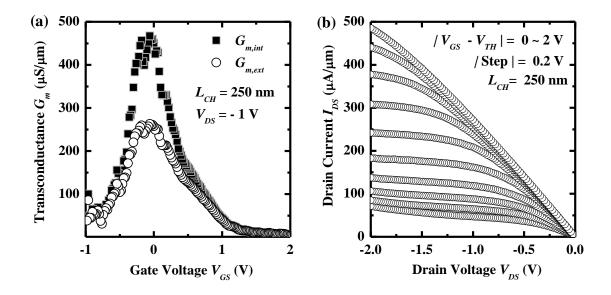

| Fig. 6.12. | (a) $G_m$ - $V_{GS}$ curves for a GeSn GAA NW P-MOSFET with $L_{CH}$ of                        |

|            | 250 nm show high peak $G_{m,int}$ of 465 $\mu$ S/ $\mu$ m at $V_{DS}$ of -1 V. Drive           |

|            | current of ~500 $\mu$ A/ $\mu$ m was achieved at $V_{GS}$ - $V_{TH}$ of -2 V and $V_{DS}$ of - |

|            | 2 V, as shown in the $I_D$ - $V_{DS}$ plot of the same transistor shown in (a)137              |

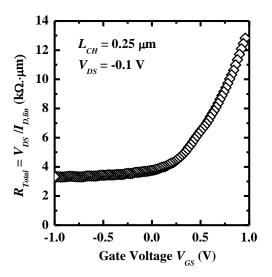

| Fig. 6.13. | $R_{Total}$ measured at $V_{DS}$ of -0.1 V as a function of $V_{GS}$ for a GeSn GAA            |

|            | NW MOSFET with $L_{CH}$ of 250 nm. $R_{SD}$ was extracted to be ~3.3                           |

|            | $k\Omega\cdot\mu m$                                                                            |

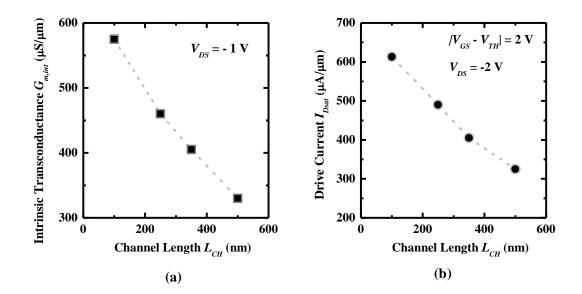

| Fig. 6.14. | (a) Peak $G_{m,int}$ at $V_{DS}$ of -1.1 V, and (b) $I_{Dsat}$ at an overdrive of -2 V         |

|            | and $V_{DS}$ of -2 V as a function of $L_{CH}$ . Degradation in carrier mobility               |

|            | was observed when the transistor scales to sub-350 nm                                          |

# List of Symbols

| Symbol              | Description                        | Unit                    |

|---------------------|------------------------------------|-------------------------|

| $A_G$               | Gate area                          | $\mu m^2$               |

| $C_D$               | Depletion capacitance              | F                       |

| $C_{it}$            | Capacitance due to interface traps | F                       |

| $C_{ox}$            | Gate oxide capacitance             | F                       |

| $D_{it}$            | Interface trap density             | $cm^{-2} \cdot eV^{-1}$ |

| $E_A$               | Activation energy                  | eV                      |

| $E_{CNL}$           | Charge neutrality level            | eV                      |

| $E_F$               | Fermi level                        | eV                      |

| $E_G$               | Bandgap                            | eV                      |

| $E_C$               | Conduction band edge               | eV                      |

| $\Delta E_C$        | Conduction band offset             | eV                      |

| $E_V$               | Valence band edge                  | eV                      |

| $\Delta E_V$        | Valence band offset                | eV                      |

| $E_{ox}$            | Oxide electric field               | V/cm                    |

| f                   | Frequency                          | Hz                      |

| $G_D$               | Drain conductance                  | S                       |

| $G_{m,ext}$         | Extrinsic transconductance         | S                       |

| $G_{m,int}$         | Intrinsic transconductance         | S                       |

| G <sub>M, Lin</sub> | Transconductance at linear region  | S                       |

| h                   | Planck's constant                  | eV·s                    |

| I <sub>CP</sub>     | Charge pumping current             | А                       |

| $I_D$               | Drive current (per unit width)     | μA/μm                   |

| I <sub>D,lin</sub>                 | Drain current at liner region (per unit width)                                                                                                                    | μA/μm                                                    |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| I <sub>Dsat</sub>                  | Saturation current (per unit width)                                                                                                                               | $\mu A/\mu m$                                            |

| $I_{ON}$                           | On-state current (per unit width)                                                                                                                                 | μA/μm                                                    |

| $I_{OFF}$                          | Off-state current (per unit width)                                                                                                                                | A/µm                                                     |

| $I_S$                              | Souce current (per unit width)                                                                                                                                    | A/µm                                                     |

| $J_{ m G}$                         | Gate leakage current density                                                                                                                                      | A/cm <sup>2</sup>                                        |

| k                                  | Boltzman's constant                                                                                                                                               | eV/K                                                     |

| L                                  | Contact length                                                                                                                                                    | μm                                                       |

| $L_{ m G}$                         | Gate length                                                                                                                                                       | nm                                                       |

| $L_T$                              | Transfer length                                                                                                                                                   | μm                                                       |

| L <sub>CH</sub>                    | Channel Length                                                                                                                                                    | nm                                                       |

| L <sub>SD</sub>                    | Separation between S/D and channel edge                                                                                                                           | μm                                                       |

| $m_n^*$                            | Effective mass                                                                                                                                                    | kg                                                       |

| n                                  | Time exponent                                                                                                                                                     | S                                                        |

| <i>n</i> <sub>i</sub>              | Intrinsic carrier concentraion                                                                                                                                    | cm <sup>-3</sup>                                         |

| n <sub>s</sub>                     | Surface concentraction of minority carriers                                                                                                                       | cm <sup>-3</sup>                                         |

| λI                                 |                                                                                                                                                                   |                                                          |

| $N_A$                              | Hole concentration                                                                                                                                                | cm <sup>-3</sup>                                         |

| $N_A$<br>$N_D$                     | Hole concentration<br>Electron concentration                                                                                                                      | cm <sup>-3</sup> cm <sup>-3</sup>                        |

|                                    |                                                                                                                                                                   |                                                          |

| $N_D$                              | Electron concentration                                                                                                                                            | cm <sup>-3</sup>                                         |

| N <sub>D</sub><br>N <sub>inv</sub> | Electron concentration<br>Inversion carrier density<br>Active doping concentration achieved                                                                       | cm <sup>-3</sup> cm <sup>-3</sup>                        |

| $N_D$<br>$N_{inv}$<br>$N_{D,Imp}$  | Electron concentration<br>Inversion carrier density<br>Active doping concentration achieved<br>by implantation and anneal<br>Active doping concentration achieved | cm <sup>-3</sup><br>cm <sup>-3</sup><br>cm <sup>-3</sup> |

| $Q_f$                     | Fixed charge density                                                            | C/cm <sup>2</sup> |

|---------------------------|---------------------------------------------------------------------------------|-------------------|

| $Q_{ox}$                  | positive oxide charge density                                                   | C/cm <sup>2</sup> |

| $Q_s$                     | Semiconductor charge density                                                    | C/cm <sup>2</sup> |

| $R_C$                     | Contact resistance                                                              | KΩ·µm             |

| R <sub>CH</sub>           | Channel resistance                                                              | KΩ·µm             |

| $R_{S,Co}$                | Contact resistance between the metal and the implantation-doped source          | KΩ·µm             |

| $\dot{R}_{S,Co}$          | Contact resistance between the metal and the <i>in situ</i> doped raised source | KΩ·µm             |

| $R_{S,Imp}$               | Resistance of the implantation-doped source                                     | KΩ·µm             |

| $R_{SE}$                  | Source extension resistance                                                     | KΩ·µm             |

| $R_{S,Raised}$            | Resistance of the <i>in situ</i> doped raised source region                     | KΩ·µm             |

| $R_{S,Total}$             | Total Source resistance                                                         | KΩ·µm             |

| $R_{SD}$                  | Source/drain series resistance                                                  | KΩ·µm             |

| $R_{sh}$                  | Sheet resistance                                                                | $\Omega$ /square  |

| <b>R</b> <sub>Total</sub> | Total resistance                                                                | KΩ·μm             |

| S                         | Subthreshold swing                                                              | mV/decade         |

| $t_f$                     | Trapezoidal pulse fall time                                                     | ns                |

| <i>t</i> <sub>r</sub>     | Trapezoidal pulse rise time                                                     | ns                |

| t                         | Time                                                                            | S                 |

| Т                         | Temperature                                                                     | °C                |

| $T_{xx}$                  | Stress in X direction                                                           | Ν                 |

| $V_A$                     | Amplitude of trapezoidal pulse                                                  | V                 |

| $V_{FB}$                  | Flatband voltage                                                                | V                 |

| $V_G$                     | Gate voltage                                                                    | V                 |

| $V_t$                     | Thermal voltage                                                                 | V                 |

| $V_{TH}$                       | Threshold voltage                                        | V                   |

|--------------------------------|----------------------------------------------------------|---------------------|

| $\Delta V_{TH}$                | Threshold voltage shift                                  | V                   |

| $W_{e\!f\!f}$                  | Gate or channel width                                    | μm                  |

| $X_J$                          | Implantation junction depth                              | nm                  |

| $X_{Raised}$                   | Height of the raised source                              | nm                  |

| $ ho_C$                        | Specific contact resistivity                             | $\Omega \cdot cm^2$ |

| $ ho_{\it imp}$                | Resistivity of the implantation-doped source             | KΩ·cm               |

| $\rho_{Raised}$                | Resistivity of the in situ doped source                  | KΩ·cm               |

| $\mu_{e\!f\!f}$                | Effective mobility                                       | $cm^2/V \cdot s$    |

| $\mu_e$                        | Electron mobility                                        | $cm^2/V \cdot s$    |

| $\mu_h$                        | Hole mobility                                            | $cm^2/V \cdot s$    |

| $\phi_{Bn}$                    | Electron Schottky barrier height                         | eV                  |

| r <sub>c</sub>                 | Backscattering coefficient                               |                     |

| $v_{inj}$                      | Thermal injection velocity                               | cm· s <sup>-1</sup> |

| $v_{th}$                       | Thermal velocity                                         | cm· s <sup>-1</sup> |

| $arPsi_F$                      | Fermi potential                                          | V                   |

| $arPhi_{\scriptscriptstyle M}$ | Metal work function                                      | V                   |

| $arPsi_{MS}$                   | Work function difference between metal and semicondcutor | eV                  |

| $\mathcal{E}_{s}$              | Permittivity                                             | F/m                 |

| $\sigma_n$                     | Capture cross sections of electrons                      | cm <sup>2</sup>     |

| $\sigma_h$                     | Capture cross sections of holes                          | cm <sup>2</sup>     |

| χ                              | Electron affinity                                        | eV                  |

|                                |                                                          |                     |

# **Chapter 1**

# Introduction

#### 1.1 Background

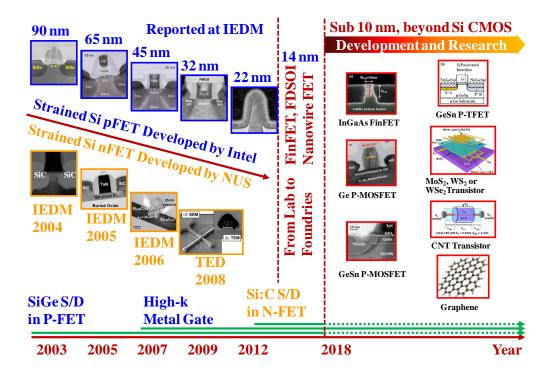

Over the past few decades, complementary metal-oxide-semiconductor (CMOS) technology based on Si has been driven by Moore's Law, i.e. device scaling to enhance performance, increase device density, and reduce cost and power consumption [1]. However, as the gate length  $L_G$  of the metal-oxide-semiconductor field-effect-transistor (MOSFET) scales beyond the 90 nm node, the performance gain using the traditional way of scaling becomes more and more difficult. The aggressively scaled gate dielectric sandwiched between the polysilicon (poly-Si) gate and the channel leads to higher and higher gate leakage current. As a result, novel technologies were explored to further enhance the device drive current. Fig. 1.1 shows the manufacturing-development-research pipeline for CMOS technology.

At the 90 nm technology node, SiGe source/drain (S/D) was introduced to induce uniaxial compressive strain in the Si channel of p-channel metal-oxidesemiconductor field-effect-transistors (P-MOSFETs) [2]. This changes the band structure of Si so that the hole mobility in the transport direction is improved. Since then, strain engineering has been adopted by Intel and other companies as an additional performance booster to further extend the CMOS roadmap below the 90 nm node [2]-[12]. At the 45 nm technology node, high-*k* materials were first introduced to replace SiO<sub>2</sub> as the gate dielectric to achieve higher capacitance and

Fig. 1.1.Transistor scaling and manufacturing-development-research pipeline ofCMOS technology.

reduce gate leakage current. In addition, metal gate was introduced to replace poly-Si gate to avoid the poly-Si depletion problem for small equivalent oxide thickness (CET) [13].

Although strain engineering has been able to provide the required performance boost after the 90 nm technology node, the continuous scaling of device dimensions and gate pitch pose new challenges to the conventional techniques and materials used for CMOS strain engineering, especially when the technology node reaches 11 nm and beyond [12]. Therefore, the advancement of future CMOS technology will rely increasingly on the innovative employment of materials, processes, and device architectures.

# 1.2 High Mobility Channel Materials for Future CMOS Applications

When the MOSFET is scaled down to the deep sub-100 nm regime, carrier transport in the extremely scaled device becomes quasi-ballistic. It has been theoretically and experimentally [14]-[17] shown that low-field mobility can still be a good indicator for the current drive in ultra-short-channel MOSFETs, where ballistic or quasi-ballistic transport, rather than saturation velocity, is important.

The drive current of a device operating in the quasi-ballistic regime is limited by the thermal injection velocity [15]-[16], instead of the saturation velocity which determines the performance of a long-channel device. The saturation current of a short channel device can be expressed as

$$I_{Dsat} = C_{ox} W_{eff} \upsilon_{inj} (\frac{1 - r_c}{1 + r_c}) (V_{GS} - V_{TH}),$$

(1.1)

where  $C_{ox}$  is the gate oxide capacitance,  $W_{eff}$  is the effective gate width,  $r_c$  is the backscattering coefficient which indicates the number of carriers backscattered to the source,  $V_{GS}$  is the voltage between the gate and the source,  $V_{TH}$  is the threshold voltage, and  $v_{inj}$  is the thermal injection velocity. Experimentally, it was found that  $v_{inj}$  is dependent on low-field mobility, while  $r_c$  is inversely proportional to low-field mobility [16]-[17]. For extremely scaled devices operating in the full ballistic regime,  $r_c$  is equal to zero. Therefore, incorporating channel materials with higher low-field mobility would achieve higher injection velocity near the source region of a transistor. This could lead to enhanced carrier transport, higher drive current, and shorter transistor delay.

|                                          | Si   | Ge   | GaAs | InAs  | InSb  |

|------------------------------------------|------|------|------|-------|-------|

| Band gap (eV)                            | 1.11 | 0.67 | 1.43 | 0.354 | 0.17  |

| Electron mobility (cm <sup>2</sup> /V·s) | 1350 | 3900 | 8500 | 40000 | 77000 |

| Hole mobility (cm <sup>2</sup> /V·s)     | 480  | 1900 | 400  | 500   | 850   |

| Dielectric constant                      | 11.8 | 16   | 12.4 | 14.8  | 17.7  |

| Lattice constant (Å)                     | 5.43 | 5.66 | 5.65 | 6.06  | 6.48  |

Table 1.1. Key parameters of possible channel materials for future CMOS applications [18]

Based on the information in Table 1.1, materials that have the potential to replace Si as the channel material for future high-speed and low-power logic applications can basically be grouped to give three promising options.

The first option is Ge or GeSn alloy for both N-MOSFETs and P-MOSFETs. Ge has substantially higher bulk electron and hole mobilities, approximately two and four times higher than those of Si, respectively. Very good progress has been made in realizing high-performance Ge P-MOSFETs [19]-[26]. Recently, GeSn channel P-MOSFETs were experimentally demonstrated to have higher hole mobility than Ge channel P-MOSFETs [27]-[29]. Simulation results also show that incorporation of Sn into Ge leads to an improvement in electron injection velocity for GeSn channel N-MSOFETs [30]. Ge or GeSn have an advantage over III-V compound semiconductors in terms of process compatibility and easy integration with Si technology. Integrating Ge or GeSn as the channel material in the current CMOS technology would be more straightforward, considering that SiGe has already been

integrated into the S/D regions of current MOSFETs. However, the electron mobility reported in Ge or GeSn N-MOSFETs is still lower than in strained Si N-MOSFETs despite the high electron mobility in bulk Ge or GeSn [30]-[39]. In addition, formation of very low resistance S/D is also very challenging for Ge or GeSn N-MOSFETs. Therefore, the drive current of the Ge or GeSn N-MOSFETs needs substantial improvement for them to be attractive.

The second option is III-V compound semiconductors for both N-MOSFETs III-V materials, such as As-based or Sb-based compound and P-MOSFETs. semiconductors, are particularly attractive for N-MOSFETs due to their very high electron mobility. In fact, high-performance devices based on III-V materials, such as high electron mobility transistors (HEMTs) and heterojunction bipolar transistors (HBTs), have been widely used in communications products for many years. However, due to the lack of a thermally stable and high-quality gate stack, III-Vbased MOSFET was demonstrated only a decade ago. Since then, extensive efforts and significant progress have been made in the development of III-V N-MOSFETs However, As-based compound semiconductors have hole mobilities [40]-[50]. similar to that of Si, which offers no advantage over Si for P-MOSFETs. Sb-based compound semiconductors offer the highest hole mobilities among all III-V semiconductor materials. Recently, peak hole mobilities of 620 and 910  $\text{cm}^2/\text{V}\cdot\text{s}$ were realized in surface and buried channel InGaSb P-MOSFETs, respectively [51]. However, these values are still much smaller than that of strained Ge P-MOSFETs, which can be as high as 1490  $\text{cm}^2/\text{V}$  s [52]. In addition, realizing nanoscale III-V transistors on a Si platform has many process, integration, and cost problems which may not have an easy solution. The success of any future CMOS technology will depend on its compatibility with the existing Si manufacturing infrastructure. The huge lattice mismatch between As-based or Sb-based compound semiconductors and Si makes it very challenging to integrate them on Si-based substrates with controllable strain levels and acceptable defect density.

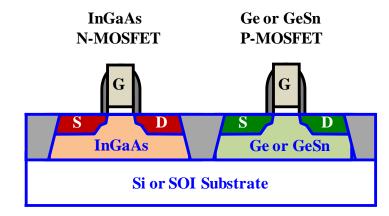

The third option is III-V semiconductor for N-MOSFETs and Ge or GeSn alloy for P-MOSFETs. Based on the discussion of the previous two options, Asbased or Sb-based compound semiconductors for N-MOSFETs and Ge or GeSn alloy for P-MOSFETs seem to be the most promising combination despite the fact that integrating these two strong contenders under a conventional CMOS process could further complicate the integration and cost issues. Shown in Fig. 1.2 is a simple schematic of an ultimate CMOS using InGaAs N-MOSFET and Ge or GeSn P-MOSFET. The objective of this thesis is to address some of the key front-end issues and develop various advanced technologies to unleash the potential of InGaAs and GeSn high-mobility channel materials for high drive current at scaled supply voltage.

**Fig. 1.2.** Schematic of an ultimate CMOS structure using InGaAs N-MOSFET and Ge or GeSn P-MOSFET.

## 1.3 Key Challenges and Issues to Be Addressed for InGaAs N-MOSFETs and GeSn P-MOSFETs

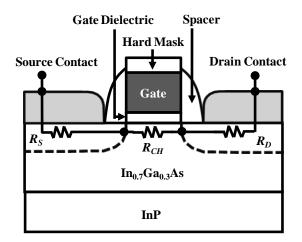

#### **1.3.1** Formation of Low Resistance S/D Regions

The S/D regions of conventional Si MOSFETs are formed by ion implantation, followed by dopant activation anneal. High doping concentration in the S/D reduces series resistance, leading to higher drain current. In III-V materials, such as GaAs and InGaAs, Si is the preferred impurity for obtaining N-type doping due to its moderately low dopant activation temperature, thermal stability, and low diffusivity. However, doping the InGaAs S/D regions by Si implantation and anneal does not achieve sufficiently high doping concentration (i.e. higher than  $5\times10^{19}$  cm<sup>-3</sup>). This is due to the Si solid solubility limit at ~8×10<sup>18</sup> cm<sup>-3</sup> [53]. Such a low doping level leads to high S/D series resistance and further limits the S/D junction depth scaling for better control of short channel effects. Although Si and P co-implantation was found to enhance the activation efficiency of the implanted Si in GaAs by 50% [54], the active doping concentration achieved is still not high enough for high-performance InGaAs N-MOSFETs [55]. Other innovative solutions are necessary to boost the S/D doping level to address the S/D series resistance issues.

#### 1.3.2 Formation of High-Quality Gate Stack for InGaAs N-MOSFETs

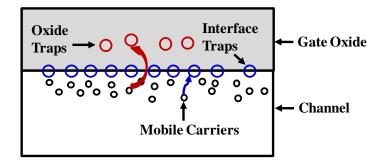

To realize high-performance InGaAs N-MOSFETs, a high-quality and thermodynamically stable gate stack on InGaAs is needed. When a III-V surface is oxidized, a high density of interface states can be generated, which may cause Fermilevel pinning, increase the subthreshold swing, degrade the electron mobility, and create reliability issues. Gate dielectrics on InGaAs channel have been extensively investigated, most of which involve high-*k* dielectric formed directly on the InGaAs channel. This usually leads to a high density of interface traps between the high-*k* dielectric and the InGaAs, resulting in significant carrier scattering and mobility degradation [56]. One strategy to mitigate the various interface states between the high-*k* dielectric and the InGaAs surface is to bury the channel beneath a large band gap material to reduce Coulombic scattering from the charged interface and bulk oxide states, as well as remote phonon scattering from oxide phonons.

#### **1.3.3** Formation of High-Quality Gate Stack for GeSn P-MOSFETs

As with InGaAs, one of the most critical issues for Ge P-MOSFETs is the poor quality of the native oxide compared to  $SiO_2$  on Si, which leads to rapid degradation in mobility with decreasing electrical oxide thickness. The solution to solve the problem is to create a high-quality interfacial layer with low interface state density between the gate dielectric and the Ge. The use of a thin Si cap is the most mature of the technologies under investigation, with significant progress over the last decade [57] and particularly in recent times [58]-[60].

Although GeSn has been shown to achieve enhanced hole mobility over Ge, the Sn was found to be segregated to the surface even right after the MBE GeSn growth at a high growth temperature [61]. The situation could be worsened by high process temperatures during the fabrication of GeSn MOSFETs. Segregation of Sn at the high-*k*/GeSn interface would degrade the interface quality between the high-*k* dielectric and the GeSn. This necessitates the use of a low thermal budget process to realize a high quality and thermodynamically stable high-*k*/GeSn interface for transistor fabrication.

#### 1.3.4 Surface Orientation Study for GeSn P-MOSFETs

Use of various surface and channel orientations has been extensively studied in Si CMOS to optimize transistor performance. The introduction of novel device structures, (i. e. FinFETs) enables the transistors to be fabricated on (110) and (111) Significant hole mobility enhancement of ~160% has been crystal orientations. observed for transistors made on a (110)-oriented surface compared to those on a (100)-oriented surface, for both oxynitride and  $HfO_2$  gate dielectrics [62]. It was also found that the low-field electron mobility of N-MOSFETs on (111) substrate is smaller than that on (100) substrate, and the low-field hole mobility of P-MOSFETs on (111) substrate is larger than that on (100) substrate [63]. The dependence of electron mobility on strain, channel direction and substrate orientation were studied for Ge N-MOSFETs [64]. The electron mobility of (111)-oriented Ge N-MOSFETs was calculated to be the highest, and the mobility can be enhanced further by introducing tensile strain into the Ge channel. Experimental results also demonstrate a 50% improvement in electron mobility for (111) substrate orientation compared to (100) orientation [65].

However, all reported GeSn channel N- and P-MOSFETs have so far been for (100) surface orientation [27]-[30],[39]. To explore the full potential of GeSn as a channel material for MOSFET application, it is necessary to investigate the performance of GeSn MOSFETs with other surface orientations.

#### 1.3.5 Fabrication of Multi-Gate GeSn P-MOSFETs

The larger permittivity of InGaAs and GeSn compared to Si leads to lower immunity to short-channel effects. As Si CMOS manufacturing enters a new era with the "tri-gate" design at the 22 nm node [66], a similar non-planar 3D approach needs to be explored for extremely scaled MOSFETs using InGaAs and GeSn. InGaAs N-MOSFETs [67]-[70] and Ge P-MOSFETs [71]-[77] with 3D structures have been extensively explored recently, with very promising results achieved. However, there has been no report of GeSn P-MOSFETs with similar advanced structures.

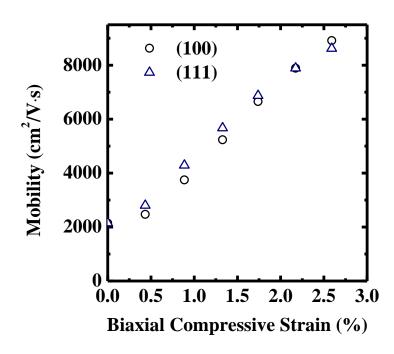

In addition, the hole mobility of GeSn is boosted by biaxial compressive strain. Uniaxial compressive strain has recently been experimentally shown to be even more effective in enhancing the hole mobility of Ge than biaxial compressive strain, and this was achieved by nanowire (NW) formation from biaxially strained Ge [77]. The ability to obtain uniaxial compressive strain by etching NWs from a biaxially strained layer, together with the need for 3D device architectures for control of SCEs at extremely scaled dimensions [78], makes it particularly attractive to form short channel GeSn NW P-MOSFETs from biaxially strained GeSn.

#### **1.4** Thesis Outline

The main technical contents discussed in this thesis are documented in five chapters.

In Chapter 2 of this thesis, we report the demonstration of  $R_{SD}$  reduction in In<sub>0.7</sub>Ga<sub>0.3</sub>As N-MOSFETs by *in situ* SiH<sub>4</sub> doping during the selective epitaxial growth of In<sub>0.53</sub>Ga<sub>0.47</sub>As to form the heavily doped raised S/D regions. A selective epitaxy process was first developed, and then integrated into a self-aligned gate-first process to fabricate the In<sub>0.7</sub>Ga<sub>0.3</sub>As N-MOSFETs. Significant  $R_{SD}$  reduction was achieved due to the combined contributions from the higher S/D doping concentration as well as the raised S/D structure.

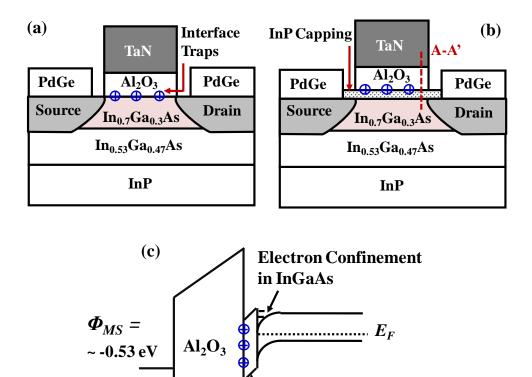

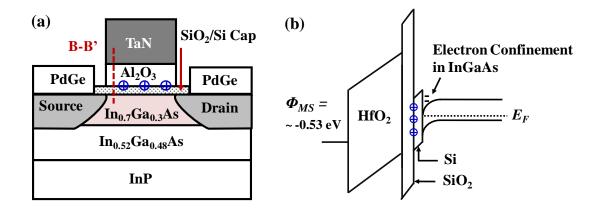

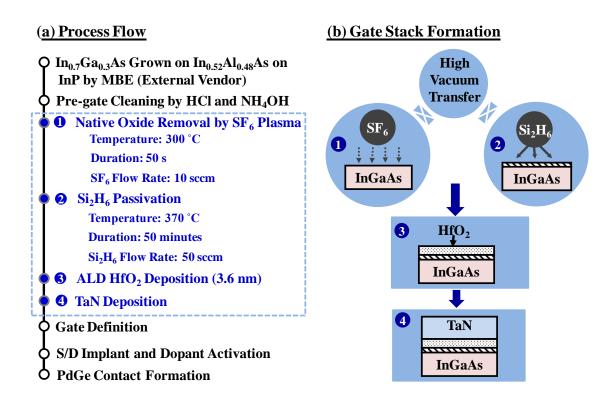

In Chapter 3, two advanced technology schemes were explored to realize high-quality gate stack for  $In_{0.7}Ga_{0.3}As$  N-MOSFETs. Section 3.2 discusses the realization of InP-capped  $In_{0.7}Ga_{0.3}As$  N-MOSFETs formed using a gate first process, in which self-aligned implant and anneal were used to form the S/D regions. The dependence of the electrical characteristics of the transistors on the thickness of the InP cap is investigated. Section 3.3 investigates a low-temperature Si<sub>2</sub>H<sub>6</sub> passivation technique, which forms an ultra-thin SiO<sub>2</sub>/Si interfacial layer between the high-*k* dielectric and the  $In_{0.7}Ga_{0.3}As$  channel.

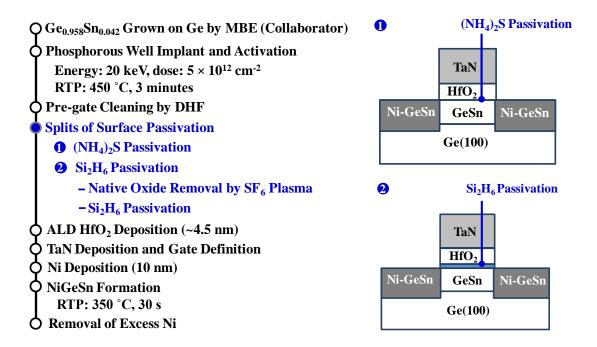

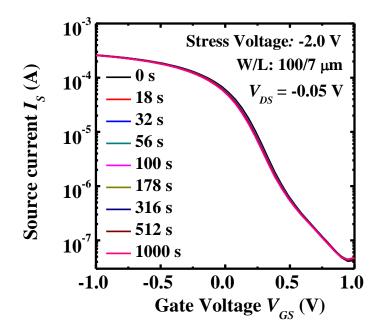

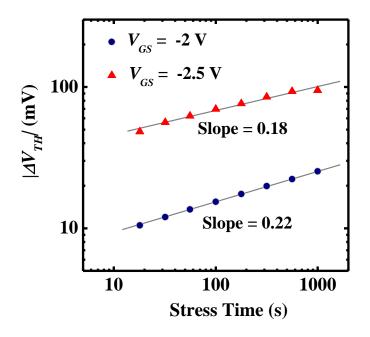

In Chapter 4, we first investigate and compare the dependence of the electrical characteristics of (100)-oriented  $Ge_{0.958}Sn_{0.042}$  P-MOSFETs on different surface passivation techniques (low-temperature  $Si_2H_6$  passivation or room temperature (NH<sub>4</sub>)<sub>2</sub>S treatment of GeSn) prior to HfO<sub>2</sub> deposition. The negative bias temperature instability (NBTI) of Si<sub>2</sub>H<sub>6</sub>-passivated GeSn P-MOSFETs is examined. For cost-effective integration in CMOS fabrication, a common gate stack solution for GeSn and InGaAs CMOS is then explored.

Chapter 5 investigates the dependence of the carrier mobility and drive current of  $Ge_{0.958}Sn_{0.042}$  P-MOSFETs on surface orientation. Fabrication and characterization of the world's first short-channel  $Ge_{0.95}Sn_{0.05}$  P-MOSFETs with  $L_G$  down to 200 nm are then discussed.