# UML-BASED CO-DESIGN FRAMEWORK FOR BODY SENSOR NETWORK APPLICATIONS

## **SUN ZHENXIN**

NATIONAL UNIVERSITY OF SINGAPORE

2011

# UML-based Co-design Framework for Body Sensor Network Applications

### Sun Zhenxin

(B. Computing(Hons), National University of Singapore, Singapore)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE

## Acknowledgement

First of all, I would like to express my deepest gratitude to my supervisor, Prof. Wong Weng-Fai, for his patience, support and help all these years. I have received immense support both in academics and life from him. Without his professional guidance and inspiration, this thesis would not even be possible.

I am deeply grateful to Prof P.S Thiagarajan, for his detailed and constructive comments on some of my works.

My sincere thanks are due to Kathy, Nguyen Dang for who have been collaborator of some initial works, and co-author of some of my papers. It was great pleasure to work with her.

I would like to thank my labmates in Embedded System Lab, who have been very kind and supportive in my research life: Joon, Edward Sim, Pan Yu, Andrei Hagiescu, Wang Chundong, Ge Zhiguo, Ankit Goel. My graduate life at NUS would not have been fun and interesting without them.

Special thanks go to National University of Singapore for funding me my research scholarship. My thanks also go to administration staff in School of Computing for their supports during my study.

My deepest appreciation goes to my family. My parents gave me much love, and their encouragements are my great source of power. I owe my loving thanks to my wife Wang Yulian, and my daughter, Sun Wanqing, and my son Sun Qichen, whose love

i

enables me to overcome the frustrations which occurred in the process of writing this these. This thesis dedicated to them.

Finally, I would like to thank all people who have helped and inspired me during my doctoral study.

# TABLE OF CONTENTS

| Chapter | 1 Introduction                                                | 10 |

|---------|---------------------------------------------------------------|----|

| 1.1     | Body Sensor Network                                           | 11 |

| 1.2     | Conventional Design Methods                                   | 12 |

| 1.3     | Challenges of Body Sensor Network Application Design          | 15 |

| 1.4     | Embedded System Design and UML                                | 17 |

| 1.5     | Level of Abstraction                                          | 20 |

| 1.6     | Our Contributions                                             | 24 |

| 1.7     | Thesis Structure                                              | 28 |

| Chapter | 2 Background and Related Works on our UML-based Framework     | 30 |

| 2.1     | UML                                                           | 31 |

| 2.2     | SystemC                                                       | 33 |

| 2.3     | UML-based SystemC Design Methodology                          | 35 |

| 2.3     | .1 Our previous works on UML to SystemC                       | 36 |

| 2.3     | .2 YAML                                                       | 36 |

| 2.3     | .3 Auto-generation of SystemC model from Extended Task Graphs | 38 |

| 2.3     | .4 RoseRT to SystemC translation                              | 38 |

| 2.4     | Summary                                                       | 40 |

| Chapter | 3 Heterogeneous IP Integration based on UML                   | 41 |

| 3.1     | Contribution of This Chapter                                  | 42 |

| 3.2     | Problem Description                                           | 46 |

| 3.3     | User Input                                                    | 47 |

| 3.4    | In   | terface Synthesis                                  | 52 |

|--------|------|----------------------------------------------------|----|

| 3.5    | Ex   | speriments and Results                             | 57 |

| 3.     | .5.1 | Simple-bus                                         | 57 |

| 3.     | .5.2 | MPEG-2 Decoder                                     | 58 |

| 3.6    | Su   | ımmary                                             | 63 |

| Chapte | er 4 | Analog and Mixed Signal System                     | 64 |

| 4.1    | Sy   | stemC-AMS Overview                                 | 68 |

| 4.2    | M    | odeling AMS Design Using UML Notations             | 70 |

| 4.     | .2.1 | Structural diagram and communication specification | 70 |

| 4.     | .2.2 | State chart diagram and behavior specification     | 72 |

| 4.3    | Im   | plementation                                       | 74 |

| 4.4    | Ca   | se Studies                                         | 77 |

| 4.     | .4.1 | Phase Loop Lock                                    | 77 |

| 4.     | .4.2 | Binary phase shift keying transmitter with noising | 79 |

| 4.5    | Su   | ımmary                                             | 82 |

| Chapte | er 5 | SystemC-based BSN Hardware Platform Simulator      | 84 |

| 5.1    | Pr   | evious Works on BSN Simulators                     | 86 |

| 5.2    | Sy   | stemC-based BSN hardware simulator                 | 89 |

| 5.     | .2.1 | Simulator                                          | 89 |

| 5.     | .2.2 | Application                                        | 90 |

| 5.     | .2.3 | Functionalities                                    | 91 |

| 5.     | .2.4 | Guideline to debug/optimize an application         | 94 |

| 5.3    | UI   | MI -modeled BSN hardware simulator                 | 97 |

| 5.3.1 UML-modeled BSN simulator                                     |

|---------------------------------------------------------------------|

| 5.3.2 Simulator customization                                       |

| 5.4 Summary                                                         |

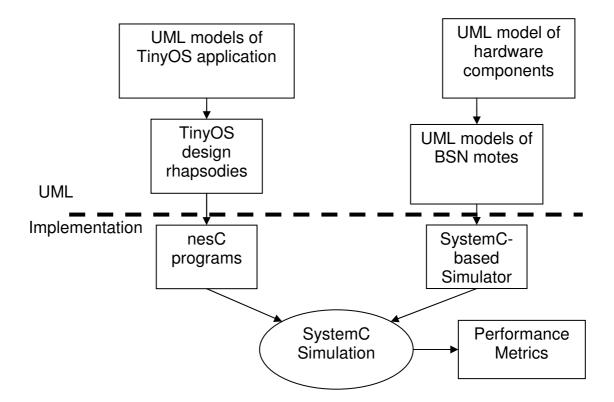

| Chapter 6 UML 2.0-based Co-Design Framework for Body Sensor Network |

| Application                                                         |

| 6.1 Previous Works on UML profile on TinyOS simulator               |

| 6.2 TinyOS and nesC                                                 |

| 6.3 UML-Based Framework                                             |

| 6.3.1 UML Profile                                                   |

| 6.4 Design Methodology                                              |

| 6.5 Case Studies                                                    |

| 6.5.1 Wheeze detection                                              |

| 6.5.2 ECG and SPO2 monitor                                          |

| 6.6 Experiment Results                                              |

| 6.7 Summary                                                         |

| Chapter 7 Conclusion                                                |

| 7.1 Future works                                                    |

| Bibliography136                                                     |

### **ABSTRACT**

A *body sensor network* (BSN) refers to a set of communicating, wearable computing devices. They are gaining popularity especially in bio-monitoring applications. In body sensor networks, the hardware and software often need to be co-designed specifically for an application. BSN applications are particularly sensitive to the tradeoff between performance and energy, both of which are also often severely constrained. However, often the hardware is still under development when the application running on it is being implemented. This makes any estimation of this tradeoff in the design of the hardware and the software inaccurate. In this thesis, we propose a unified design framework to manage the complex development of BSN application with the aims of enhancing modularity and reusability.

The proposed framework consists of a set of Unified Modeling Language (UML) 2.0 profiles for both software and hardware designs. For software portion, we have chosen to use nesC-TinyOS, the most popular programming language (nesC), and runtime system (TinyOS) platform for BSN applications. For hardware, we have chosen to use SystemC, the de facto standard specification language for hardware design. The proposed UML profiles abstract the low-level details of the application, and provide a higher level of description for application developers to graphically design, document and maintain their BSNs that consist of both hardware and software components. Using profiles for hardware platforms, we are able to customize a UML-based hardware simulator for BSNs. Our interface synthesis technique allows us to reuse existing design components (IPs) with a "plug-and-play" approach. This highly-

reconfigurable simulator acts as a fast and accurate performance evaluation tool to aid both software and hardware design.

With the aid of a UML profile for TinyOS and a pre-defined component repository, minimum knowledge about TinyOS is needed to construct a body sensor network application. The hardware simulation environment allows users to customize the hardware platform before a commitment is made to the real hardware. In our framework, we have also modeled our simulator in UML. Customized simulator can be automatically generated after refining system model or re-configuring the hardware parameters. Key design issues, such as timing and energy consumption can be tested on this automatically generated simulator. The framework ensures a separation of software and hardware development while maintaining the close connection between them.

The thesis will describe the design and implementation of the proposed framework, and how the framework is used in the development of nesC-TinyOS based body sensor network applications. Actual cases studies are used to show how the proposed framework can be used to adapt quickly to changes in the hardware while automatically morphing the software implementation quickly and efficiently to fit the changes.

# **LIST OF FIGURES**

| Figure 1: A typical Body Sensor Network design                                 | 13      |

|--------------------------------------------------------------------------------|---------|

| Figure 2: A traditional design flow of BSN applications                        | 14      |

| Figure 3: Recommended design flow for BSN application                          | 17      |

| Figure 4: Typical levels of abstraction in software/hardware design            | 21      |

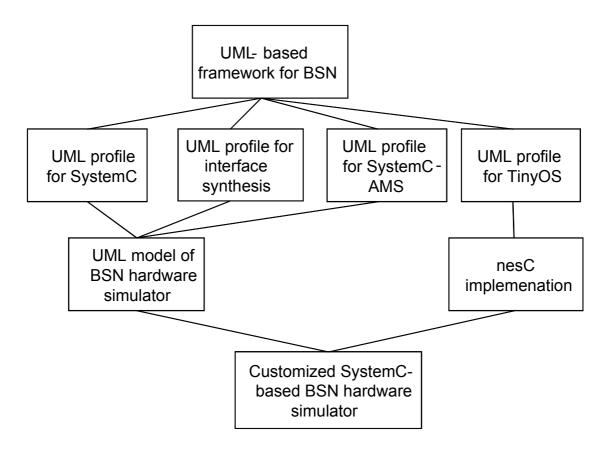

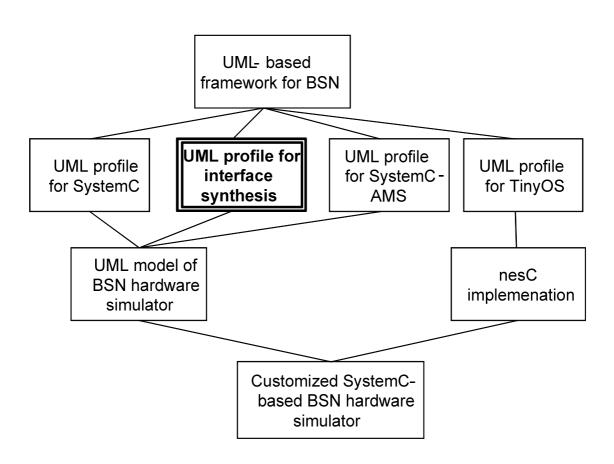

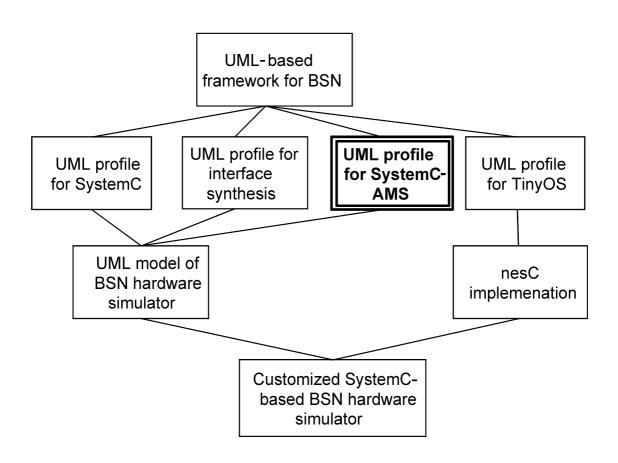

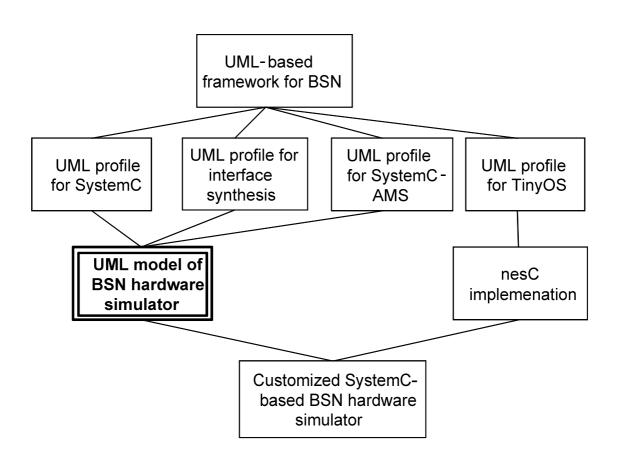

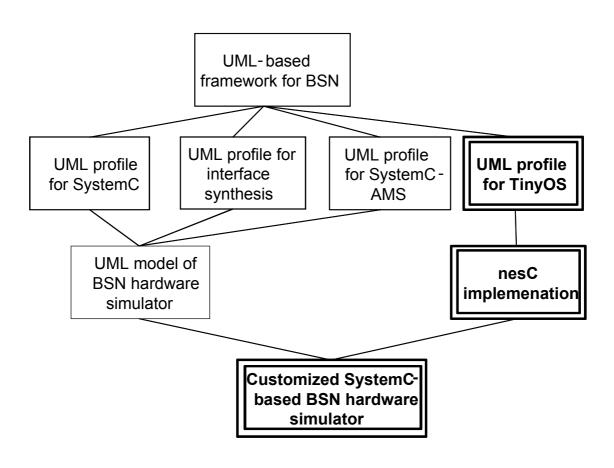

| Figure 5: Structural diagram of our BSN co-design framework                    | 28      |

| Figure 6: Different levels of SystemC model                                    | 34      |

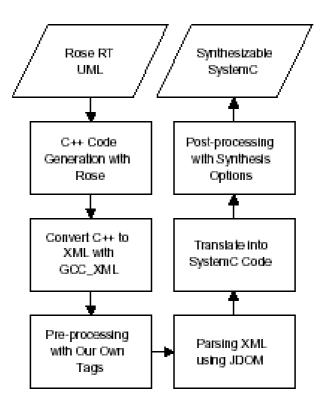

| Figure 7: Translation flow of RT2Code                                          | 39      |

| Figure 8: Design flow of UML based interface synthesis                         | 45      |

| Figure 9: Structural diagram of Simple-bus example                             | 51      |

| Figure 10: Work flow of wrapper generator                                      | 54      |

| Figure 11: Sequence diagram of OCP communication groups                        | 55      |

| Figure 12: State diagrams of glue logic between IDCT master and slave interfa- | aces at |

| of Figure 13                                                                   | 56      |

| Figure 13: Structural diagram of MPEG-2 decoder after wrapping                 | 60      |

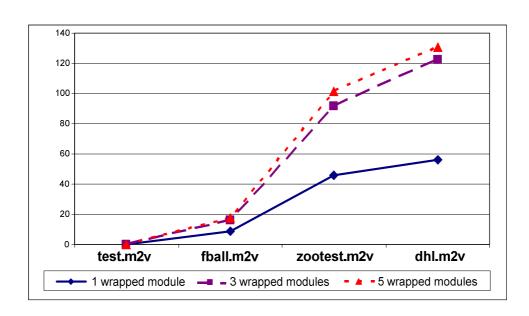

| Figure 14: Overhead with different number of wrappers                          | 61      |

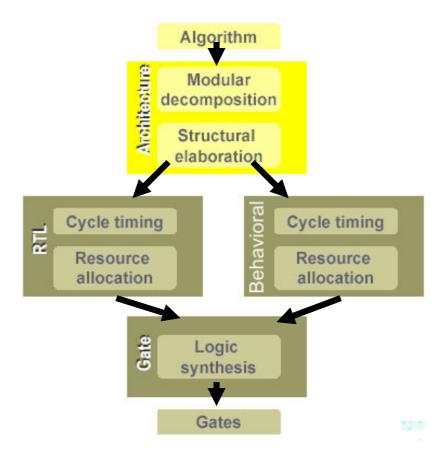

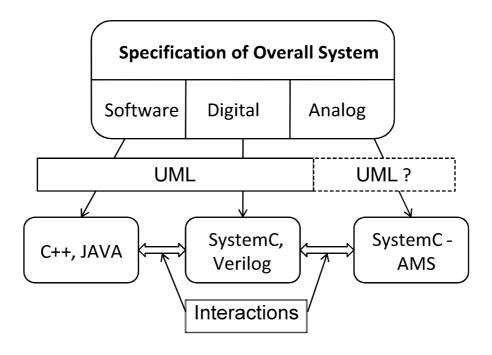

| Figure 15: Typical embedded system design and partitions                       | 67      |

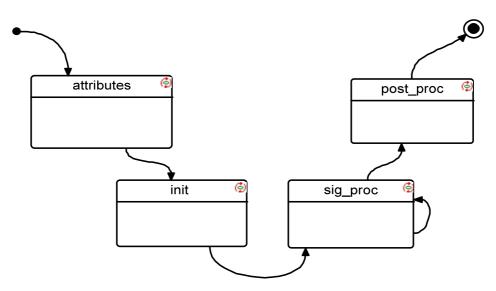

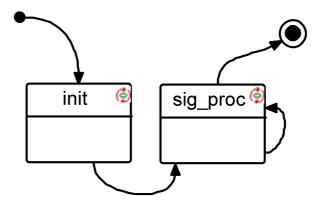

| Figure 16: Complete UML state chart of mixed signal components                 | 73      |

| Figure 17: UML Class and state chart diagrams of Low pass filter               | 74      |

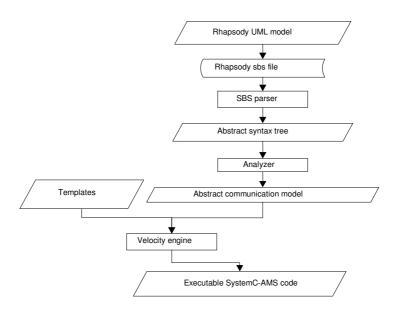

| Figure 18: Workflow of our implementation                                      | 76      |

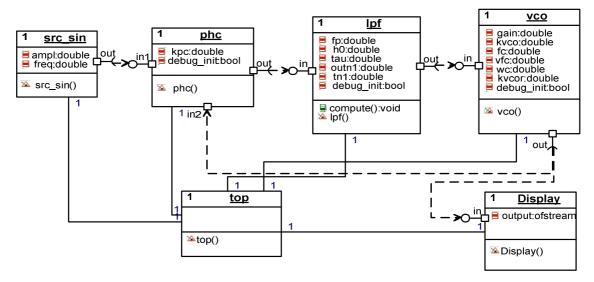

| Figure 19: UML structural diagram of PLL example                               | 78      |

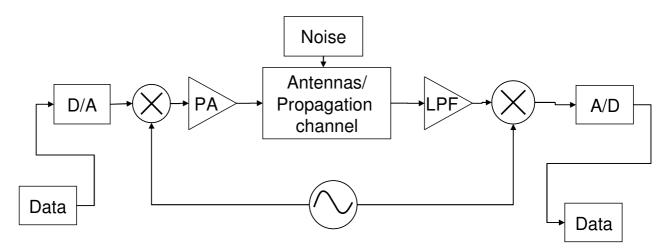

| Figure 20: Block diagram of BPSK example                                       | 80      |

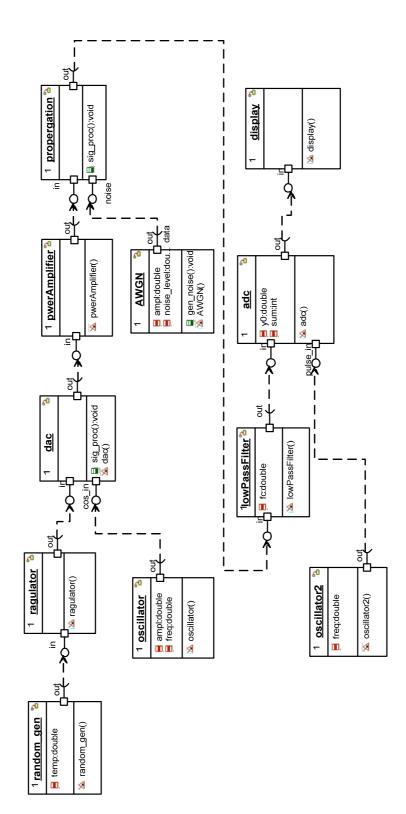

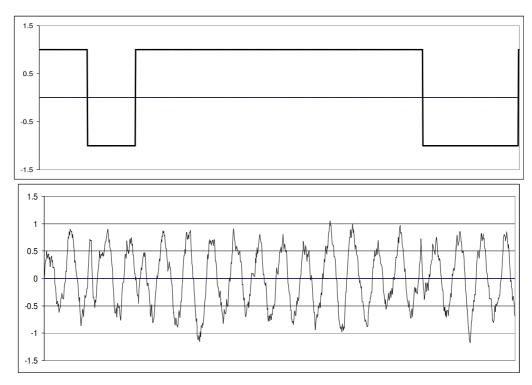

| Figure 21:UML Structural Diagram of BPSK transceiver                             | 81         |

|----------------------------------------------------------------------------------|------------|

| Figure 22: (a) Transmitted data stream (b) Samples after filtering               | 82         |

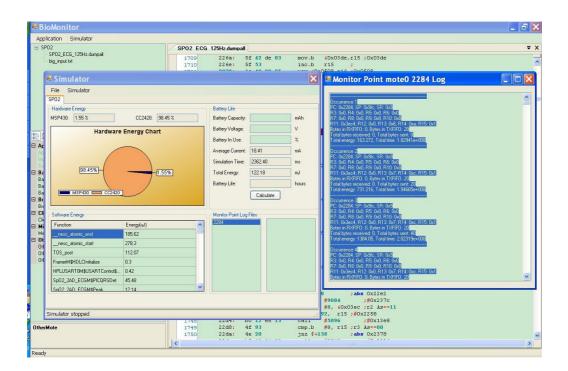

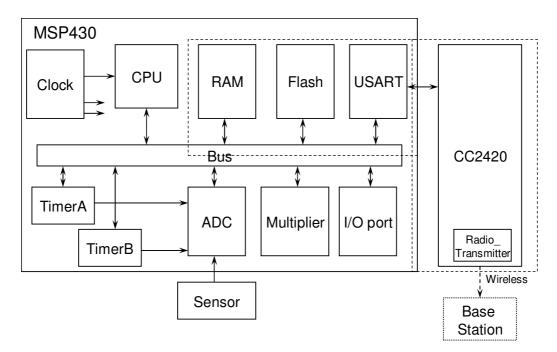

| Figure 23: Simulation data collected at monitor points.                          | 93         |

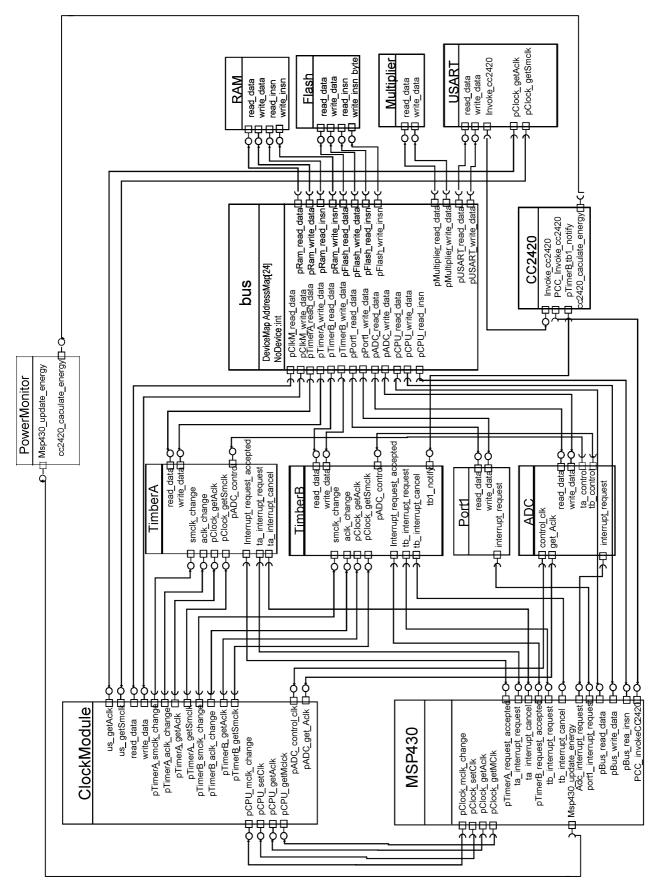

| Figure 24: Block diagram of BSN simulator                                        | 96         |

| Figure 25: Selected part of UML class diagram of the BSN simulator               | 99         |

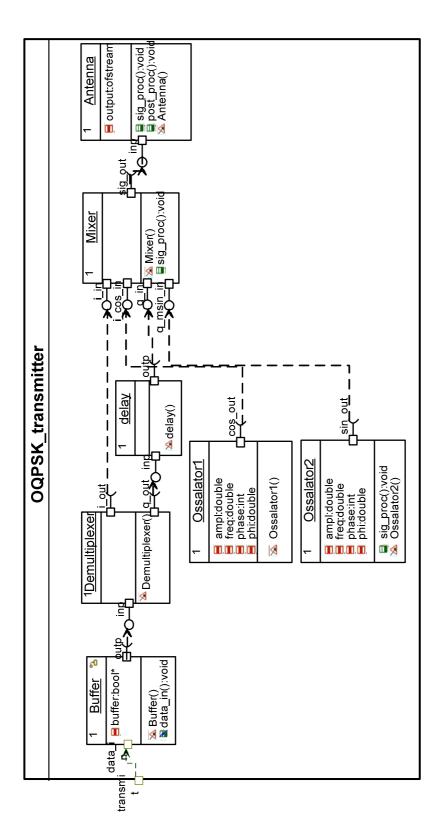

| Figure 26: UML class diagram of OQPSK transmitter                                | 102        |

| Figure 27: UML structural diagram (interfaces and communications) of BSN s       | simulator  |

|                                                                                  | 103        |

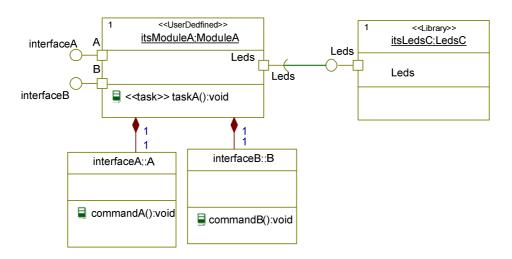

| Figure 28: An example class diagram of TinyOS application                        | 111        |

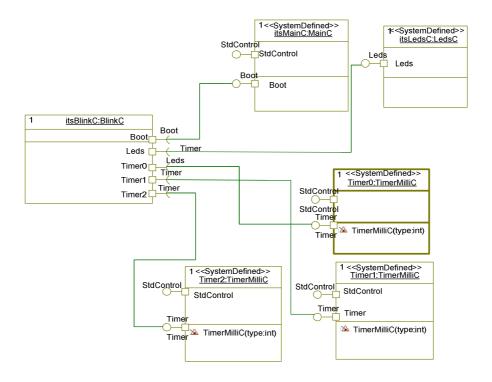

| Figure 29: Object model diagram of Blink example                                 | 113        |

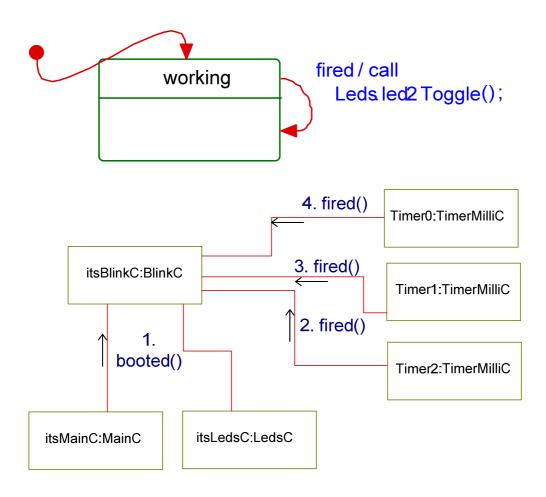

| Figure 30: Interface state chart for Timer2.fired() and Collaboration diagram of | of Blink   |

| example                                                                          | 115        |

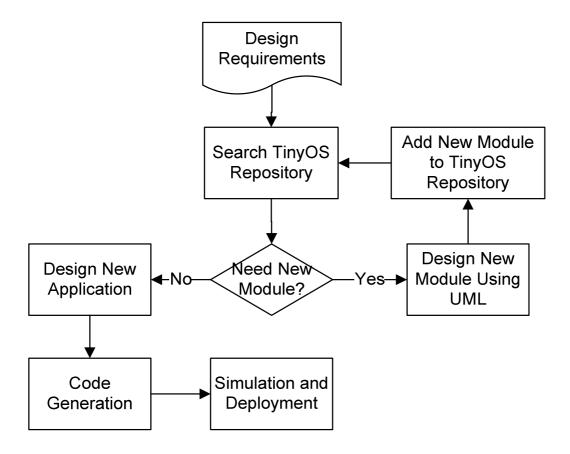

| Figure 31: Design a new TinyOS application using our proposed framework          | 119        |

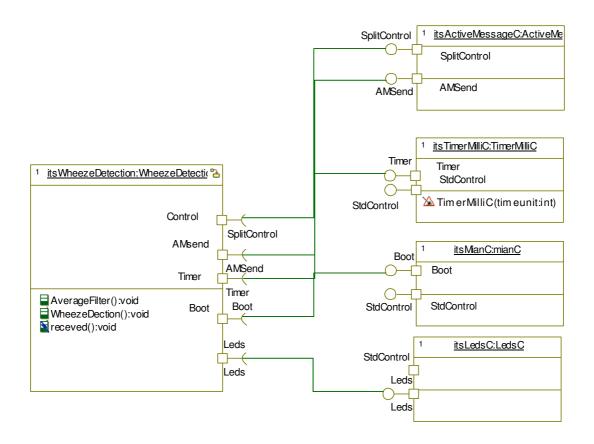

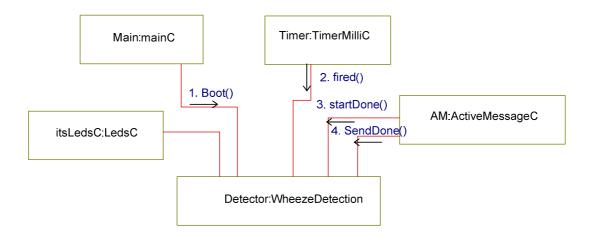

| Figure 32: Object diagram of wheeze detection module                             | 121        |

| Figure 33: Collaboration diagram of wheeze detection application                 | 122        |

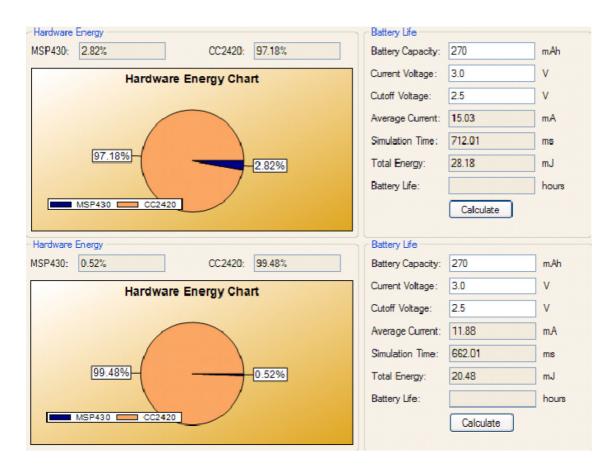

| Figure 34: Experiment result of power consumption of the ECGnSpO2 applica        | ation. (a) |

| hardware energy information of original design(top) (b) result after tuning (bo  | ttom) 125  |

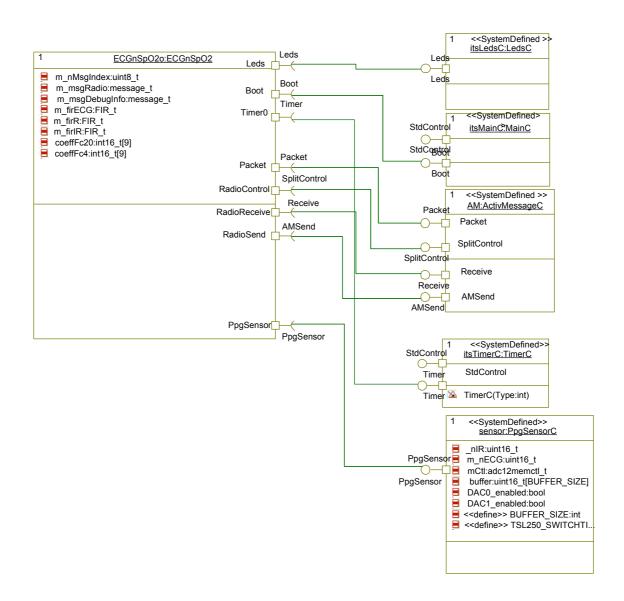

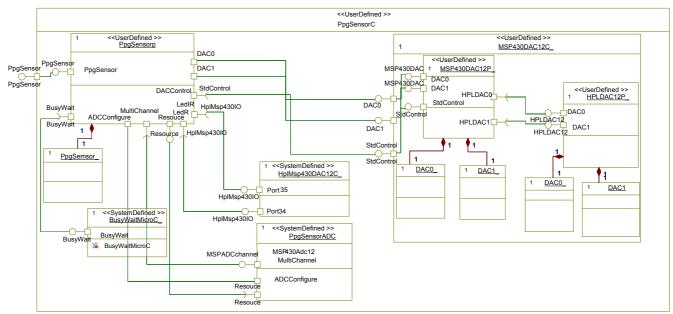

| Figure 35: Structure diagram for ECGnSPO2 application                            | 127        |

| Figure 36: Class diagram for PpgSensor module                                    | 128        |

| Figure 37: Summary of UML-based BSN design framework                             | 131        |

# **List of Tables**

| Table 1: Mapping between UML notations and design properties | 51  |

|--------------------------------------------------------------|-----|

| Table 2: Simulation results of decoders with F-IDCT          | 61  |

| Table 3: Simulation results of decoders with R-IDCT          | 61  |

| Table 4: Code size and execution time of code generator      | 125 |

| Table 5: Estimated implementation time                       | 126 |

### **List of Publications**

- 1. K.D. Nguyen, Z. Sun, P.S. Thiagarajan, and W.F. Wong, "Model-driven SoC Design Via Executable UML to SystemC", Proceedings of the 25th IEEE International Real-Time Systems Symposium (RTSS). pp. 459-468. Dec 2004 (Chapter 2)

- 2. Y. Zhu, Z. Sun, A. Maxiaguine, and W.F. Wong, "Using UML 2.0 for System Level Design of Real Time SoC Platforms for Stream Processing". Proceedings of the 11th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications. pp. 154-159. Hong Kong. Aug 2005. (Chapter 2)

- 3. Z. Sun, Y. Zhu, W.F. Wong, and S.K. Pilakkat, "Design of Clocked Circuits using UML". Proceedings of the Asia and South Pacific Design Automation Conference 2005 (ASP-DAC)." pp. 901-904. Jan 2005 (Chapter 2)

- 4. K.D. Nguyen, Z. Sun, P.S. Thiagarajan, and W.F. Wong, "Model-Driven SoC Design: The UML-SystemC Bridge" in "UML for SOC Design" edited by Grant Martin and Wolfgang Müller. pp. 175-197. ISBN 0-387-25744-6. Springer. July 2005 (Chapter 2)

- 5. Xianhui He, Yongxin Zhu, Zhenxin Sun, Yuzhuo Fu: UML Based Evaluation of Reconfigurable Shape Adaptive DCT for Embedded Stream Processing. EUC Workshops 2006: 898-907

- 6. Cutcutache, T.T.N. Dang, W.K. Leong, S. Liu, K.D. Nguyen, L.T.X. Phan, E.J. Sim, Z. Sun, T.B. Tok, L. Xu, F.E.H. Tay, and W.F. Wong, "BSN Simulator: Optimizing Application Using System Level Simulation", Proceedings of the 6th International Workshop on Wearable and Implantable Body Sensor Networks (BSN 2009), pp. 9-14. Berkeley, CA, U.S.A., Jun 2009. (Chapter 5)

- 7. Z. Sun, and W.F. Wong, "A UML-Based Approach for Heterogeneous IP Integration", Proceedings of the 14th Asia and South Pacific Design Automation Conference (ASP-DAC)." pp. 155-160. Yokohama, Japan. Jan 2009

(Chapter 3)

- 8. Z. Sun, C-T. Ye, and W.F. Wong, "A UML 2-based HW/SW Co-Design Framework for Body Sensor Network Applications". Proceedings of Design, Automation, and Test in Europe (DATE 11). pp. 1505-1508. Grenoble, France. Mar 2011 (Chapter 5 and 6)

# **Chapter 1 Introduction**

### 1.1 Body Sensor Network

With the recent advances in wireless sensor network and embedded computing technologies, wearable sensing devices have become feasible in meeting the demands for healthcare and bio-monitoring. There are now numerous examples of such body sensor network (BSN) applications [25][34]. Generally speaking, a BSN system collects, processes, and stores physiological (such as electrocardiogram (ECG), and blood pressure), activity (such as walking, running, and sleeping), and environmental (such as ambient temperature, humidity, and presence of allergens) data from a host's body and its immediate surroundings. It may even be able to perform actuation (such as in the form of drug delivery) based on the data collected[10]. BSNs can be very useful in assisting medical professionals to make informed decisions about the course of the patient's treatment by providing them with continuous information about the patient's condition.

Due to its reliability and the ability to detecting the onset of acute diseases, or monitoring chronic illnesses, BSNs have been used in a wide range of applications. The common and important applications of BSN include the monitoring of patients who have left hospital care, or the detection of the onset of different conditions such as asthma, or heart attacks. The following are two examples of sound BSN applications:

A BSN worn by a patient that automatically alerts the hospital at the critical moment just before the onset of a heart attack, through measuring changes in the patient's vital signs. A BSN on a diabetic patient that automatically injects insulin through a pump,

as soon as the level of insulin falls below a certain critical level.

Other applications of this technology include sports, military, and security where there is a need for the seamless exchange of information between individuals, or between individual and machines.

### 1.2 Conventional Design Methods

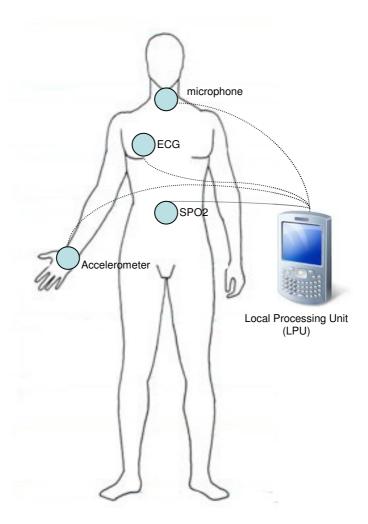

Given the wide variety of BSN applications, each with its own customized hardware and software, the design of these applications is attracting more concerns. The basic structure of a BSN is shown in Figure 1. As shown in the figure, wireless wearable sensors and a *local processing unit* (LPU) are attached to human body to measure the status of the patient. The latter is normally a PDA or a smart phone. The sensors collect information, and after doing some basic processing, they will send the results to the LPU via wireless communication channels. The LPU processes the data collected from sensors, and makes decisions such as sending alert, or making a call to the doctor in charge.

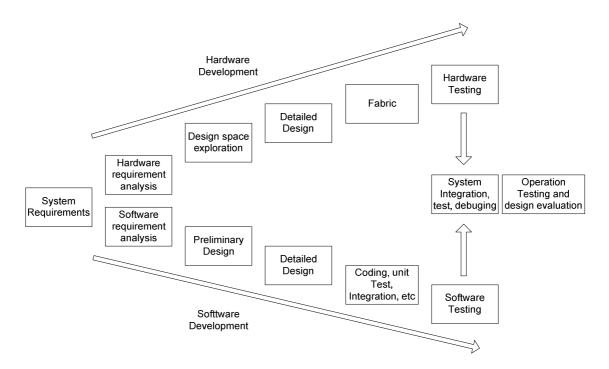

Figure 2 outlined the conventional design flow for BSN applications. It usually starts with some informal design specifications. These specifications include functional and performance requirements. Designers will then partition the BSN system into software and hardware portions, and assign them to different developers. The hardware and software designers will then work independently based on these specifications. Hardware components are refined from the specifications to the implementation.

Software components are subsequently implemented and integrated with the hardware components to complete the system. It is only after this integration, the functionality and performance metrics can be evaluated. If bugs are found at this stage, identifying and fixing the bugs is tedious and time-consuming. A large amount of effort generally needs to be spent at the post-developing stage.

Figure 1: A typical Body Sensor Network design

Integration puts together the separate software and hardware components to form the complete system. It is also a time consuming and error-prone process. The separate development of hardware and software restricts the ability to study the tradeoffs between hardware and software. A "hardware first" approach is often pursued with the following consequences:

- Hardware is specified without a full understanding the computational requirements of the software.

- Software development does not influence hardware development, and changes

made to hardware may not be reflected promptly in software.

Following this approach, any problem encountered as a result of late integration can cause costly modifications and schedule slippage.

Figure 2: A traditional design flow of BSN applications

### 1.3 Challenges of Body Sensor Network Application Design

Developing BSN systems is not easy. The nature of BSN system brings unique challenges to BSN designers. BSN applications have to operate in a continuous manner on the host body. Much of the theoretical foundation for general wireless sensors also applies to BSNs, with particular emphasis on issues such as power optimization, battery life performance, and radio design. There are also other issues, such as usability, durability, robustness, how well the sensor 'fits' in with the application, and the reliability and security of the data, that must be considered for a successful deployment of any BSN system. Sensor networks often suffer from the so-called 'reliability dilemma' -- the more reliable and secure is the data transmission, the higher is the overhead, and consequently more power is required. This leads to a reduction in battery life which is generally a bad thing for BSNs.

Another of the frequent issues that a BSN designer encounters is that hardware components have to be customized to meet any new design requirements. Continuous monitoring requires a lot of energy, and to give accurate and immediate detection result, a BSN node has to meet processing speed and transmission rate requirements that are often very energy consuming. On the other hand, BSN devices must be small enough to be wearable or even implanted, hence limiting its computational power and energy. This challenges the BSN designer to find an optimal design that can achieve the right balance of battery life and accuracy of measurement. The challenge for the designer would be how he can use these components in such a way that the stringent requirements of the application are met. There are also standard BSN devices available.

The designer also has the flexibility to customize the BSN hardware components, for example, increasing the bit width, or adjusting the clock's speed when trying to match the computational accuracies and energy requirements. Given the large design space, searching for the optimal solution may be very time-consuming.

To achieve the optimal solution, designers need to explore the different design alternatives and tune their application constantly. The often non-availability of real hardware is a particularly serious challenge. Because the target hardware and the software are being developed concurrently, BSN application designers have to rely on existing BSN platform to verify and test their implementation. However, differences in the hardware make the timing and energy analysis inaccurate, and the implementation will require another round of customization before the final integration with new hardware platform. A flexible and efficient tool for pre-integration testing would be useful.

In BSN application, hardware and software components have greater impact on each other than in other platforms. However, without actual integration, the exact nature of this dependence becomes very difficult to characterize. Continuous assessment of the overall performance metrics will help designer find the optimal solution more efficiently.

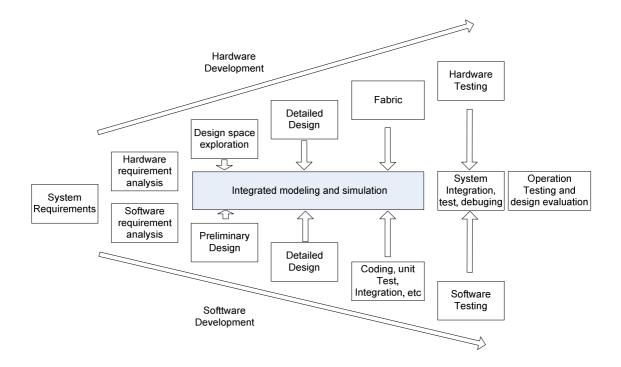

Moreover, the late integration also postpones the evaluation of design metrics and bug identification, such as bugs in communication channel which may only be found after integration. Identifying and fixing a bug after integration can be very difficult and expensive for both hardware and software designers. Figure 3 shows the

recommended design flow for BSN application designs is supported by our proposed framework.

Figure 3: Our recommended design flow for BSN application

### 1.4 Embedded System Design and UML

A BSN application is a kind of embedded system. Therefore the design techniques for embedded systems also apply to BSN. In this section, we will elaborate the design and co-design techniques using UML that is inherited from general embedded systems.

An *embedded system* is a *computer system* designed to perform specific functions often with real-time computing constraints. It is embedded as part of a more complete device typically including hardware and software parts. The uses of embedded systems are virtually limitless, because every day new products are introduced to the market that

utilizes embedded computers in novel ways. Products with embedded systems include computer parts, mobile phones, machine control units, automobile, etc, and they are closely related to our everyday life. All of these makes embedded system evolve very rapidly. On the other hand, embedded system designs are performed in a rather ad hoc way. Different types of algorithms (e.g. signal processing, communications, and controls) are implemented using a variety of technologies (e.g., digital signal processors, microcontrollers, field-programmable gate arrays, application-specific integrated circuits, and real-time operating systems). The complexity and scale of embedded systems bring many challenges to embedded system designers.

With advances in semiconductor technology, it is now possible to integrate most if not all the hardware modules required by an embedded systems into a single chip, giving rise to the so-called "system-on-a-chip" (SOC) platform. With complexities of SOCs rising rapidly following Moore's Law, the design community has been searching for new methodologies that can handle the complexities with increased productivity and decreased times-to-market. The obvious solution that comes to mind is increasing the levels of abstraction. In other words, using a modular approach to compose the overall system with increasing larger basic building blocks (or "intellectual property" (IP) blocks). However, it is not clear what these basic blocks should be beyond the available processors and memories. Furthermore, with multitude of processors and variety of IP blocks on the chip, the difference between software and hardware design has become indistinguishable. However, the existence of often incompatible tools for

utilizing and deploying the hardware and software components has prevented the creation of a comprehensive and integrated design flow.

Hardware and software essentially share the same development pattern. With dramatic increases in the size and complexity of both hardware and software, more user friendly and reusable design and development methodologies were introduced to cope with these issues.

Introducing the Unified Modeling Language (UML) into the design of system-on-chip has become an accepted solution to the ever increasing complexity. UML is a standardized general specification language which was originally created for software-based system. For decades, software designers have been applying it to every stage of software design and implementation. With the power of the UML, designers are able to model their application from different points of view, share their ideas with commonly understood notations.

A key strength of UML is its ability to be extended with domain-specific customizations, as so-called *profiles*. A profile in the Unified Modeling Language (UML) provides a generic extension mechanism for customizing UML models for particular domains and platforms. Extension mechanisms allow refining standard semantics in strictly additive manner, so that they can't contradict standard semantics. Profiles are defined using stereotypes, tag definitions, and constraints that are applied to specific model elements, such as Classes, Attributes, Operations, and Activities. A Profile is a collection of such extensions that collectively customize UML for a

particular domain. In this thesis, we will propose a few UML profiles to model BSN applications in different domains.

By decoupling the specification from implementation and using formal mathematical models of computation for specification, we gain the ability to perform fast simulation and efficient synthesis of complex heterogeneous systems. We model complex systems as a hierarchical composition of the simpler models of computation. Some of these simpler models of computation, such as types of finite state machines, dataflow models, and synchronous/reactive models, have finite state. Because they have finite state, all analyses of the system can be performed at compile-time. For example, memory usage and execution time can be determined without having to run the system. These models can be overlaid on an implementation technology (such as C or VHDL).

### 1.5 Levels of Abstractions

Design of anything, from a web application to an embedded software system to a hardware device, is done at some level of abstraction. Simply, a level of abstraction is the term that the designer uses to describe the thing being built. Level of abstraction usually refers to the level of complexity by which a system is viewed or programed. The higher the level, the less detail. The lower the level, the more detail. A level of abstraction is determined by the objects that can be manipulated and the operations that can be performed on them. In programming terms, the objects are data types and the operations are the operators that can be used in expressions and control constructs.

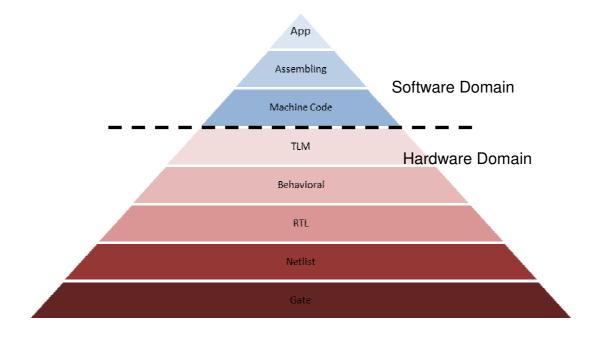

The notion of abstraction levels was introduced with software systems, since there were several obvious levels: machine code, assembly language, subroutine libraries, and eventually interpreted application languages like SQL. In hardware design, we are familiar with several low levels of abstraction: polygon, transistor, gate, and register-transfer (RTL). On top of these layers, hardware designers have introduced a few more levels to cope with the ever increasing complexity. Figure 4 gives a list of typical levels of abstraction being used in software/hardware design. The levels from top to bottom are: Application level, assembling level, machine code level, hardware level, transaction level(TLM), behavioral level, Register transfer level(RTL) and netlist level, and gate level.

Figure 4: Typical levels of abstraction in software/hardware design

### Gate level

At gate level, hardware is described as connected logic gates or transistors. The combinations of these gates will react at the edge of clock and perform the logic functionalities.

### **Netlist**

In Netlist level, hardware systems are described as directed graph with simple boolean gates as nodes.

### Register transfer level

RTL level code is characterized by arithmetic expressions, including conditionals and control constructs, which execute in a fixed schedule of cycles. The data objects, registers and wires, typically correspond to hardware objects. Low level details such as clock signals are also modeled. RTL simulation is normally defined as cycle accurate.

### **Behavioral**

Behavioral code looks like normal sequential code found in a general purpose programming language. It does, however, have structural information in the form of modules and ports. Simulation at behavior level can be defined as cycle accurate, and the simulation is faster than RTL level.

### **Transaction level**

A transaction object is an abstraction of an interface between modules (or more generally, concurrent processes). An example would be a FIFO buffer. The transaction object would take the place of several ports in the module port list. The operations done

on the object would be get and put, and perhaps query status. Another example would be an AMBA bus interface. Simulation at transaction level is usually faster than the previous levels and not cycle accurate.

These levels of abstractions are used in different stages of the hardware design process. Gate level and netlist level are very close to the real hardware, and they are used by circuit designers for physical designs. Hardware designers spend great effort on system level designs, which is at RTL and higher levels. Simulation speed varies in at great scare. For example, the RTL level simulation can be 100 time slower than the simulation at TLM level models. However, simulation at RTL level is defined as cycle-accurate, which is much more accurate comparing to the transaction level. The lower level simulation will take even more time. Our design framework will lift the abstraction level up to UML level, and designer will be able to focus on the relatively high abstraction levels, starting from UML level and evolves to the register transfer level. Our research is focusing on system level designs, although the produced implementations might require further optimization in physical design procedure. The main objective of the UML framework is to help the designers on refinement of codesign system with fast prototyping and integrated simulation models.

Our framework will focus on system level design procedures where simulation models are used to describe the design. In our framework, model simulation is the main method for the system analysis and validation. Transitions are made automatically from higher level to lower level with minimal user interaction. By working at a high level of abstraction, our framework can be used earlier in the design process than existing tools.

We automatically generate the working code which can be used directly for simulation, and through simulation, we can obtain accurate evaluation of the system, and therefore the designers can optimize their design based on the simulation result.

### 1.6 Our Contributions

This thesis summarizes our research on exploring usage of UML on BSN design.

The main contribution of this thesis is the unification of software and hardware design using a single design platform: UML, and subsequently applying it to the design of BSN applications. The detail contributions are as follows.

- We explored how UML can be used to design the digital components of the embedded system. We used UML to capture functional and behavioral specification of what are low level designs. A mapping was established between UML and a hardware description language, namely SystemC. Different levels of executable implementation can be automatically generated to perform simulation and verification. The semantics of chosen UML notations are then been extended to capture more design constraints such as clocking.

- We extended the UML profile for digital hardware to also handle analog and mixed signal systems. Many sensors are analog in nature, and their output need to be translated by mixed signal components for digital processing and communication. In order to express analog and mixed signal designs, we have chosen to use SystemC-AMS, a SystemC-complaint hardware description language for analog systems, as the implementation language. In a similar way,

UML is used to capture the specifications of mixed signal systems. Mappings are established between the design and its implementations. Using this novel approach, the analog part of the application can be seamlessly integrated with the digital components to capture hardware designs with a high degree of fidelity.

We introduced a UML-based interface synthesis technique that solves the problem of integration heterogeneous "intellectual property" (IP) blocks by reconfiguring their bus interfaces. An IP block refers to a pre-defined hardware or software functional component that has a well-defined interface. IP blocks may perform similar functionalities but their interfaces may differ, and are normally incompatible with the current design. Reusing existing IP blocks for a new design makes a lot of economic sense as they already have been purchased, or designed and tested. However, the incompatible interfaces make reuse technically challenging. To facilitate reuse, we chose the OCP (Open Core Protocol) as the standard bus interface. We use UML to model the IP communication interfaces, and automatically generate wrappers, so that the packaged IP cores can be easily assembled together using the OCP bus standard for simulation. In order to do this, we extracted the essential aspects of the bus communication, and modeled the interfaces using UML notations. UML notations are then used to produce wrapper code. The generated wrappers can be directly used to wrap up IP blocks for test and simulation.

- We developed a customizable simulator for BSN hardware platforms using the proposed hardware profiles and interface synthesis technique based on UML. Exiting IP blocks can be reconfigured and added in to the simulation platform, and our interface synthesis technique allows us to reuse existing design component (IPs) with a "plug-and-play" approach. The hardware simulation environment allows users to customize the hardware platform before a commitment is made to real hardware. In our framework, we have also modeled our simulator in UML. Implementations can be automatically generated by simply configuring some hardware parameters. Key performance issues, such as timing and energy consumption can be tested by simulating the generated implementation on this automatically generated simulator. This highly-reconfigurable simulator provides a fast and accurate performance evaluation tool to aid both software and hardware design.

- We proposed a UML profile for the software portion of BSN applications, and we have chosen TinyOS as our target platform. TinyOS is the most popular software platform of BSN application. The program running on TinyOS is written in nesC, a dialect of C. Using this UML profile, a designer can focus on the high level specifications rather than worry about the low level nesC implementation during the design stage. The models of the TinyOS components are kept in a repository. We find that the BSN applications often share similar structures, and these models are highly reusable. With the aid of a UML profile for TinyOS and a pre-defined component repository, minimum knowledge of TinyOS is needed to construct a body sensor network system.

• We proposed a novel co-design framework for BSN applications that is based on UML. The proposed UML profiles abstract the low-level details of the application and provide a higher level of description for application developers to graphically design, document and maintain their systems that consist of both hardware and software components. The framework ensures a separation of software and hardware development while maintaining the close connection between them.

The thesis will describe the design and implementation of the proposed framework, and how the framework is used in the development of nesC-TinyOS based body sensor network applications. Realistic cases studies are used to show how the proposed framework can be used to adapt quickly to changes in the hardware while automatically morphing the software implementation quickly and efficiently to fit the changes.

Figure 5: Structural diagram of our BSN co-design framework

### 1.7 Thesis Structure

Figure 5 shows the structural contents of the thesis. In the structures, several UML profiles are the directly contributions. Based on these profiles, we apply them to aid BSN software and hardware design and implementation.

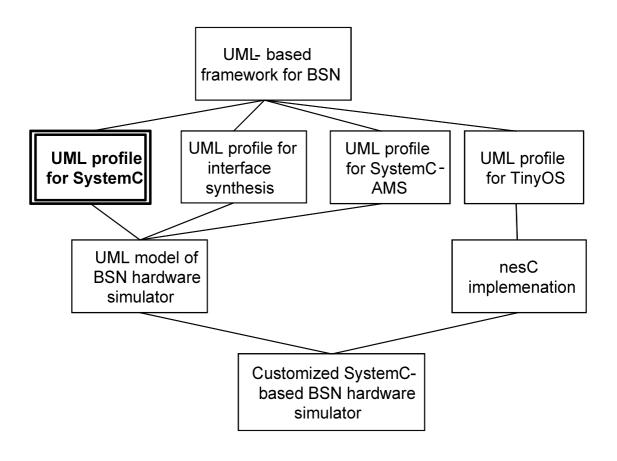

Reminder of thesis is organized as follows. In next chapter, we will present UML profile for SystemC which are used to model the digital portion of an application. Some related works, such as UML, SystemC, will also be introduced in chapter 2. UML-based interface synthesis technique is presented in chapter 3, which will be used to specify and generate glue logic between pre-defined hardware components. In chapter

4, we outline the UML profiles for SystemC AMS which can be used to model the analog portion of system. In Chapter 5, we will apply the profiles to a BSN hardware simulator, the details of UML profiled SystemC simulator for BSN hardware platform will be presented. In chapter 6, we first present the design framework for TinyOS, and then we will show how we can unify the software and hardware portion of BSN application by integrating the generated software code with the SystemC based simulator. Chapter 7 concludes the thesis and presents possible directions for future works.

# Chapter 2 Background and Related Works on our UML-based Framework

### 2.1 **UML**

With the increasing complexities of embedded systems, designers have been searching for new methodologies that can manage the complexity as well as yielding high productivity. The Unified Modeling Language (UML) is a proven modeling and specification language that has been used widely in development of complex software applications [80]. Embedded designer found that embedded system design can benefit from UML in similar way.

UML is an object-oriented modeling language standardized by the Object Management Group (OMG) mainly for software systems development[80]. It is a visual modeling tool for specifying, visualizing, constructing and documenting software systems and business processes. UML consists of a set of basic building blocks, rules that dictate the use and composition of these building blocks, and common mechanisms that enhance the quality of the UML models. Its rich notation set has made UML a popular modeling language in multiple application domains for system documentation and specification, for capturing user requirements and defining initial software architecture. It is considered the best understanding of system by designers and programmers.

While UML is well-suited for modeling software systems in general, it lacks support for some aspects important to embedded real-time systems, e.g. modeling of timing constraints, signals, and independent components[97]. Therefore, different proposals to extend the UML for modeling real-time systems have been made. The

Object Management Group (OMG) proposes to extend the UML by building UML "profiles" that contain the needed extensions[81]. However, this extension mechanism is currently not part of the standard and it is still discussed how to realize it. In parallel the leading CASE tool vendors implement proprietary extensions to the UML. Rational and Telelogic adapt UML for modeling embedded real-time systems by combining it with the modeling languages from the real-time (ROOM) and telecommunication domains (SDL), while I-Logix stays with Standard-UML, but provides a very powerful implementation of statecharts. [68]

The current version of UML called UML2, which is a large collection of diagrams and notations. It has 13 diagrams types. Here, we briefly introduce the diagrams we use in our framework. UML class diagram and state chart are chosen to capture the structure, behaviors and the deployment of the hardware components.

Class diagrams show the building blocks of the system, their inter-relationships, and the operations and attributes of the classes. We found that class diagram can represent the structural information of embedded system in a quite natural way. The individual components of the hardware components can be drawn as classes, and wiring among them can be modeled as relations or interfaces bindings via UML port. Stereotypes can be used to distinguish the difference types of hardware components. The composite classes enables designer to view the under design system from system level view down to detailed implementation of a building class. Each of the class in class diagram can be associated with a state chart diagram to specific its behaviors. State charts depict the dynamic behavior of an entity based on its response to events,

showing how the entity reacts to various events depending on the current state that. This event-triggered model is well-suited abstraction to the signal-triggered hardware components, where signals can be considered as events, and output signals are modeled as reactions. From practice, we found that these two types of diagrams are well-suited to our specification requirements.

## 2.2 SystemC

SystemC[75] is a system level modeling language based on C++. It provides library supporting system level design. It has become de facto standard for embedded hardware design language. SystemC has desirable properties for system level design. Besides, SystemC use most of C++ grammar, and this allows user to learn it in a very short time. Even those who have no experience with programming in SystemC can read and understand the code.

Figure 6: Different levels of SystemC model

Using the SystemC library, designer can model a system at various levels of abstraction as shown in Figure 6. At the highest level, only the functionality of system may be modeled. For hardware implementation, model can be written either in a functional (behavioral) style or RTL (register-transfer level) style. [40] The software part of a system can be naturally described in C++. Interfaces between software and hardware and between hardware blocks can be described either at the transaction-accurate level or at the cycle-accurate level. Moreover, different parts of the system can be modeled at different levels of abstraction and these models can co-exist during system simulation. C++ and SystemC classes can be used not only for the development

of the system, but also for the test-bench. SystemC consists of a set of header files describing the classes and a link library that contains the simulation kernel. Any ANSI C++ compliant compiler can compile SystemC, together with the program. During linking, the simulation kernel of the SystemC library is used. The resulting executable serves as a simulator for the system designed.

SystemC provides an ideal platform for developing embedded systems. Software and hardware parts can both be specified using the same language and verified using a common test-bench. The hardware parts may be refined up to RT level and implemented by using synthesis tools. The hierarchical modeling features of SystemC are supported by the hierarchical specification model. This facilitates not just a structured design, it also enable IP reuse. The FSMs can also be organized in a hierarchical manner, implementing a Hierarchical control flow.

SystemC-AMS[76] is an extension of SystemC[75] to describe mixed-signal design, and it has been popularly studied to model mixed signal systems such as an inertial navigation system [18], the I2C protocol communication [50], and wireless sensor network node [54]. We will focus on SystemC-AMS profile in chapter 3.

## 2.3 UML-based SystemC Design Methodology

This section briefly discusses other projects that have investigated integrating formal and informal approaches to systems development, where multiple modules are used to describe a system.

#### 2.3.1 Our previous works on UML to SystemC

Some of our previous works was focusing on the UML-based design technique on hardware[37][38][93][97]. In these works, we have proposed a UML profile for SystemC to capture the design specification of a system, including its architecture and behaviors. Two types of UML diagrams, namely class diagram and statechart diagrams are chosen as the modeling tool. With proposed profile, designers can leverage the design abstractions to UML level, and with the designed models can be translated into SystemC executable programs to do simulation so that designer can verify whether the design satisfies the requirements based on the simulation results. If the results are not satisfactory, designers can go back to UML model and modify it, re-generate SystemC code and check its behaviors again.

The UML models can be mapped into different levels of abstraction for different purposes. We have supported transaction level modeling(TLM), behavioral and register transfer level(RTL). TLM level offers faster simulation rate, and the BSN simulator presented in chapter 5 will employ this level of simulation. Designer can also target the code generation to RTL level, which describe the operation of a digital circuit with hardware registers and signals, the RTL level components can be considered the program running on the target platform.

#### 2.3.2 YAML

Most of the effort we have seen in the UML-SystemC translation was to generate skeleton SystemC code from, in particular, class diagrams and object diagrams. An

example of this kind of projects is YAML[84]. YAML uses UML notations to model hardware and allows user to input information about objects and relationships into a UML class diagram (for behavioral hierarchy) and object diagram(for structural modeling). YAML generates the C++ code for the design, using information input by the user to the UML class and object diagrams.

YAML provides a user friendly graphical interface to model systems under the guidelines of UML, using the SystemC and ICSP C++ class libraries. Users can specify the details of SystemC and ICSP classes into the UML front end. The code generated by YAML conforms to the syntax of ICSP and SystemC classes and can be directly compiled and simulated.

The major advantage of using YAML is the ability to avoid the complex syntactic details involved in using the C++ libraries. User can generate the SystemC + ICSP code from YAML, after specifying the various details in the class and object diagram. YAML has been used to model various designs including a DLX compatible processor pipleline. The DLX pipeline code consists of around 2000 lines of C++ code. Most of which was generated automatically by YAML. It raises good results in generating and simulating the models.

YAML gives some ideas of modeling the system functional and structural information. However, it lacks of the behavioral requirement support, and hence cannot capture the requirement of control information.

#### 2.3.3 Auto-generation of SystemC model from Extended Task Graphs

To model the behavior of hardware, Klaus proposed to use extended task graph[70]. Task graph gives an accurate definition of time and different model of computation are emphasized. Task graphs are a widely-spread means for the specification of embedded systems behavior. Task graphs have a well-defined execution semantic and a temporal order and other abstract modeling characteristics. A task graph represents operations and data dependencies between them. Its main features are both the modeling of control flow and a hierarchical structuring of functionality.

The methodology was successfully applied to complex specification consisting of more than 200 tasks. Besides scheduling, the complexity is linear in the number of tasks and allows handling such complex systems very easily. The produced code is quite readable using well-defined signal names derived from the specification and, as mentioned earlier, the code is synthesizable.

#### 2.3.4 RoseRT to SystemC translation

Another team in our department is exploring a similar method to translate from UML to SystemC.[88] A RoseRT wrapper of SystemC has been built to produce SystemC code from restricted RoseRT design. Despite its intention as a tool for general purpose software development, RoseRT has close similarities to SystemC. Capsules in Rose RT communicate via ports and protocols just as modules communicate via ports and channels in SystemC. A capsule undergoes a state transition when a specified trigger signal arrives whereas in SystemC this corresponds to an incoming signal on

one of the ports specified in the sensitivity list of an SC\_METHOD. RT2SystemC translator exploits these similarities to identify and extract important sections of the C++ code generated by the RoseRT tool.

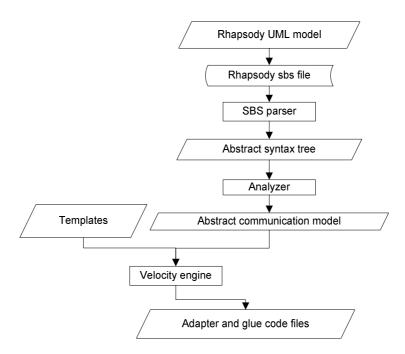

Figure 7: Translation flow of RT2Code

RT2Code translation starts from UML model in RoseRT, and then the rose generated C++ code are further compiled into XML documents. RT2SystemC generator uses the XML documents as input, and generated synthesizable SystemC code. There are interesting similarities as well as differences between their translation and our approach. (Figure 7)

There are still some limitations in the translation. Firstly, the generation is based on the generated code of RoseRT, and it is very software dependent. Furthermore, RoseRT lacks of complex statechart support, therefore, the behavioral functionalities of larger system may not be well captured. By studying their project, we can add in more value to our approach.

## 2.4 Summary

In this chapter, we have presented some background information on UML, SystemC, and they will be the essentials in the framework. We also presented some previous works on UML-based design framework targeting at SystemC implementation including our UML-profile for SystemC.

# Chapter 3 Heterogeneous IP Integration based on UML

In last chapter, we presented some background information on UML to SystemC transformation, which can be used to design a functional building block for embedded system. In this chapter, we focus on the customization of existing IP blocks. As the legacy IPs contribute to most of current SoC design usage, maximizing the reuse of them will greatly cut the design effort.

## 3.1 Contribution of This Chapter

With growth of embedded systems, systems are too large to be handled by single team, and a system has to be partitioned into smaller parts and designed by different engineers. One of the greatest design challenges for hardware developers today is to integrate different parts of hardware system together. IPs, or Intellectual Properties, are predefined functional blocks which have been tested for future integration. The use of pre-designed IP blocks to reduce the complexity of system integration has gained popularity lately. Using pre-designed IP blocks leads to the reduction of time and complexity of system level design. However, these IP blocks often have interfaces that are incompatible due to differences in protocol and/or unmatched I/Os. Integration suffers from these incompatibility issues which also hampers design exploration especially when there are many alternative solutions [65]. The problem of incompatible IP protocols is well-known, and efforts have been made to address it by standardizing the communication protocol. Several standards have been proposed. Among these, the Open Core Protocol (OCP) by OCP-IP [59] has gained wide industrial acceptance. Today, many IPs are OCP-compliant. However, for existing non OCP-compliant IP

cores, it is expensive to customize them to comply with the OCP standard. The process of IP integration also suffers from mis-matched I/O ports. For example, a 16-bit processor will have problems connecting to a 32-bit bus interface. These kinds of situations require logic to be introduced in between the interfaces. Design of such logic circuit is typically done manually and is therefore tedious and error prone. In chapter, we address the above problems by the automatic generation of OCP-compliant adapters for non-compliant components with fixed interfaces from UML structural and behavioral models.

With the shorten time and cost requirement, IP reuse becomes more important than ever. Interface synthesis consists of interface modeling and realization. The incompatible problem has been addressed by previous works in the literature. A common way to capture the system interface specification is the utilization of software programming language or an interface description language, such as variants of C, C++, or Java[32][67][79][94]. Such a specification has the advantage of being executable, and thereby facilitates early verification and simulation. However, for the purpose of system level specifications, the use of these programming languages does not satisfy all the requirements. One key issue is that the different phases of a system design flow — namely the requirement, design, implementation, and deployment — are not sufficiently separated. This can seriously confuse the issues that have to be addressed by each of these phases because of duplication or oversight.

Earlier efforts have also been made in context of timing analysis and verification. Interfaces synthesis tools based on specifying low level data port behaviors through timing diagrams have been proposed. In [21], a method to synthesize interface blocks

that consist of logic circuits and software routines were presented. Other works propose the use of control flow graph [61], event graphs [41], and signal transition graphs [6] to model interface behaviors. All these works address the interface synthesis problem for certain platform environment. However, there can be a large choice of IP. Therefore, the unified modeling for heterogeneous IP would benefit designers working through a top-down design process. UML-based approaches also have been studied [53][66][85]. However, these methods are not matured enough and the mapping rules to low level synthesis are usually too simple to handle realistic scenarios.

Our approach differs from others in the use of high level UML notations for heterogeneous IP integration. The following are features that are unique in our approach:

- To ensure correctness and reusability, we use UML structural and state diagrams to specify and formalize system interfaces. This single model is used consistently throughout the entire design process. It not only gives a system level view of the design but also allows for reuse in future designs.

- Automation is applied in every level of abstractions, and between different environments. Code is generated from the same source model, minimizing ambiguity.

- Our framework supports both interface protocol customization and glue logic generation, thereby maximizing IP integration.

- All changes are applied at the higher level, and user will only need to deal with the high level design decisions.

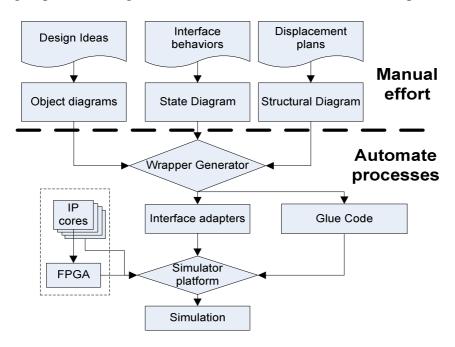

The main goal of this work is to generate the communication links between predefined blocks with minimal user inputs. In chapter, we present our solution which makes use of standards to enable transparency as well as the early validation of designs and the subsequent verification of resultant systems. Figure 8 shows the design flow of our approach. We built UML profiles to capture the system level communication interfaces. The solution is laid out using UML structural diagrams. State diagrams are added to customize functional behaviors of the interfaces. We built a software tool to automatically generate the interface and glue logic to connect the devices while meeting bandwidth and performance requirements. We experimented with our implementation under different scenarios including the "plug-and-play" of OCP-compliant, Verilog and PCI-compliant components into a SystemC simulation environment. The automatic generation of interfaces and glue code leads to the fast prototyping of possible design solutions. These can then be tested and optimized.

Figure 8: Design flow of UML based interface synthesis

## 3.2 **Problem Description**

To clearly explain our framework, we define following terms to represent different notations used in our system.

- *UMLport*: UML notation which called *port* in UML level, and it is presented in a small square with UML interface attached.

- *SLport*: System Level data port, and they can carry certain types of data.

- SystemC port: Port defined in SystemC, and they are usually defined as sc\_in, sc\_out, or sc\_inout.

- *Interface*: A point of interaction between system level components, and they are key component in system level designs.

- UML interface: A UML notation represents an interaction between UML modules.

We will define our problem scope first using the terminologies. IP blocks can be viewed as black boxes which communicate with each other through pre-defined interfaces. Each interface contains several *system level data ports* (SLport) that can send or receive certain type of data. Consider a scenario where an IP block is connected to an existing interface of a system. Let's assume that the IP block has only one exterior interface. A failure to perform the connection may be due to one of two possible reasons: (1) the interface protocol does not matched, or (2) the SLports of one interface are not sufficient to drive the other. We say that an IP core is *compatible* to an environment if all the output ports of each interface are able to drive the corresponding input port of the other interface while satisfying all timing constraints. For two

compatible interfaces that have different protocols, they form one of two types of compatible pair:

<u>Type 1 compatible pair</u>: There is a one-to-one correspondence between the SLports of the two interfaces.

<u>Type 2 compatible pair</u>: The output SLport of one interface can be made to drive the input SLport of the other through some runtime transformation of its data.

To establish a connection, signal mapping must be setup between the interfaces. For a type 1 compatible pair, a port-to-port mapping is specified through a *contract* associated with the connection. For a type 2 compatible pair, glue logic has to be introduced. We will synthesize both types of the connection from their descriptions specified in *wrapper classes*.

## 3.3 User Input

Graphical notations can give designers a direct view of the overall picture, and it can facilitate designers on adaptation and control of their designs. Unified Modeling Language (UML) from OMG is one of the most successful graphical formalisms[80]. It has been proven very successful and is widely used in software designs. In our framework, we chose UML to be our specification language for its user friendliness and wide adoption. UML provides a large set of notations. We carefully chose a subset for modeling the interface communications. In our framework, we will use structural diagram and statechart diagram to capture the interface models.

UML structural diagrams are predominantly used to describe the component structure of a system. IP blocks and their wrappers are treated as black-boxes and modeled as UML classes. We begin with modeling the communication interfaces of existing IP cores. Wrapper modules with interfaces adapters will then be modeled. After the classes are drawn, interfaces are added as UML ports to capture interface information. We shall use 'UMLport' to distinguish these ports from SLports. Communication channels are modeled as connections between the UML ports. To fix the inconsistency between unmatched interfaces, state charts are added to a wrapper's model to describe the behavior of the glue logic needed to drive the interface. The modeling procedure can be divided into following three steps:

#### Step 1: Formalize the IP interfaces using UML notations

IP cores are modeled as a UML class with UML ports attached. An UMLport is a real-time system elements introduced in UML 2.0. It is a property of classifiers that specifies a distinct interaction points between the classifier and its environment or between the classifiers. These UMLports will capture the module's communication interfaces. Each UMLport models a group of one or more SLports. The associated SLports will be described in the properties of the UMLport.

The details of an IP's interfaces are captured in the properties and contracts of its wrapper's UMLports. A contract specifies the services that a classifier provides (offers) to its environment as well as the services that a classifier expects (requires) of its environment [80]. If two UMLports have a port-to-port match in the communication path then they will share the same interface contract. A connection will be established

between them directly or indirectly (through other ports). The stereotype of an UMLport specifies the communication protocol. In our experiments, the default stereotype for UMLport is SystemC. However, we also used other stereotypes such as OCPSystemC, Verilog, and PCI. The communication parameters of interfaces are captured in the UMLport's attributes. For IPs with interfaces matched to each other, port-to-port communication paths are specified directly in their specification, and only external UMLports to the environment are used for generating the wrappers later on.

#### Step 2: Define the wrapper classes

To mask the interfaces, the internal UMLports of IP models are connected to the user defined UMLport in the outer class, i.e., a *wrapper class*. The diagrams capture two main aspects of the models: the structure of the model and the characteristics of the interfaces.

The links and blocks in the structure diagram lay out the structure of the model. The wrapped classes communicate with each other using defined channels, and the connections between the internal components are hidden. The adapters are defined using the exterior UMLports of the wrapper classes. We shall call these UMLports adapter ports. Each adapter port has a stereotype that indicates the protocol of the outgoing communication. Each wrapper class can hold one or more adapter ports, while each adapter port can have different protocol types and connects to different external modules. Table 1 summarizes the mapping between UML notations and the components of our model.

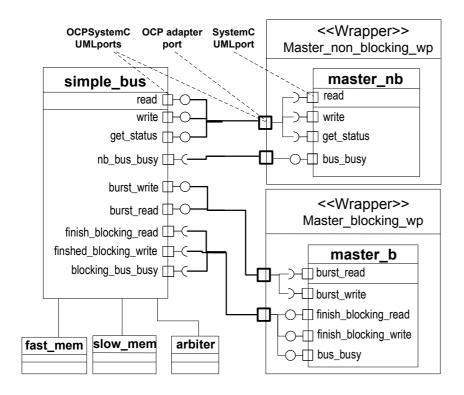

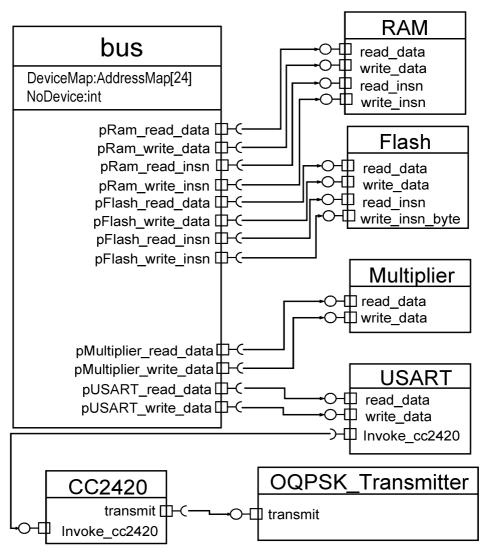

Figure 9 shows an example of a model after wrapping. The arbiter has 2 clients — one non-blocking and one blocking master. master\_nb is the UML model of a SystemC module. The UMLports (say read) of this UML module represent groups of SLports, of the underlying SystemC module. The interface of simple\_bus includes the interfaces to the arbiter as well as to the memory, because they have no compatibility problem, we will not model the details of these interfaces. In this example, the simple bus' SLports (and thus the encapsulating UMLports) are implemented in an OCP protocol, while the clients are not. Therefore, two wrapper classes were used to customize the interfaces of the clients. The clients will communicate with simple\_bus through the OCP adapter ports.

#### Step 3: Define the behavior for incompatible interfaces

Connections are made between adapter ports and the environment. For connections without port-to-port matchings, additional models have to be added to capture the logical relations between input and output SLports. As an example of a connection that requires glue logic, we consider the IDCT filter used in our MPEG-2 case study (see adapter port ① of Figure 13). To implement the 8X8 IDCT filter, some IP blocks take an address of two dimensional 8X8 array, while other takes 64 inputs in a linear array. To solve this problem, we introduce an *interface state machine* to transform the signals. Our framework allows the user to customize the predefined interface behaviors using such state charts.

Figure 9: Structural diagram of Simple-bus example

| <b>UML Notations</b> | <b>System Properties</b> |  |  |

|----------------------|--------------------------|--|--|

| Parent Class         | Wrapper module           |  |  |

| Name                 | Name                     |  |  |

| UMLport              | Interface adapter        |  |  |

| Subclasses           | IP cores                 |  |  |

| UMLPort of           | Interface                |  |  |

| subclass             |                          |  |  |

| Port name            | Name                     |  |  |

| port type            | Type                     |  |  |

| Interface type       | Direction                |  |  |

| Stereotype           | Protocol                 |  |  |

| Port properties      | Driving signals          |  |  |

| State chart          | Driving                  |  |  |

|                      | behaviors                |  |  |

| Contract Attributes  | Signals                  |  |  |

| Name                 | Name                     |  |  |

| Stereotype           | type                     |  |  |

| Tag                  | Width                    |  |  |

| UMLport State        | Adapter's control        |  |  |

| Chart                | code                     |  |  |

| States and           | Finite state             |  |  |

| transitions          | machine                  |  |  |

Table 1: Mapping between UML notations and design properties

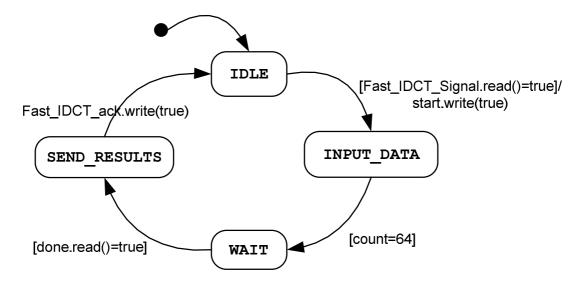

Figure 12 shows the state diagram of the IDCT example, where the master interface has three SLports: Fast\_IDCT\_signal, Fast\_IDCT\_addr, Fast\_IDCT\_ack, and slave interface has 4 SLports: start, datain, dataout and done. The diagram defines how the transformation needed for the output SLports to drive the input SLports across the connection.

## 3.4 Interface Synthesis

A key feature of our framework is the automatic code generation. In our experiments, we use IBM Rhapsody [68] to input the UML diagrams. The model is then fed into our code generator. The analyzer filters out the interfaces and produces abstract models of the design containing the communication specifications. The adapter code is generated from templates using Velocity [86], a template engine that generates code from predefined templates. The Velocity engine merges the code templates and the extracted wrapper models, and performs the final code generation. Figure 10 shows the work flow of our framework. The code generator reads the model and produces the interface synthesis code in 4 steps:

In the first step, models that have the stereotype Wrapper are extracted and the corresponding interface adapter code will be generated. For example, to integrate a module in the SystemC environment, each adapter will be generated as a SC\_MODULE, a primitive type of SystemC. On the other hand, to adapt a FPGA PCI module, an adapter file will be generated which contains the routines for checking and opening communication channels, as well as the communication routines for communicating

with the board. We assume that all the modules without stereotype are normal modules, and they will not be generated in the compilation process. The interfaces extracted from the models are also stored for future references.

In the next step, the code generator will extract and analyze the connections from the model. According to the stereotypes of the UMLports connected to each adapter port, the connections are classified into groups. Currently, we have generators for OCP-SystemC, OCP-Verilog, and OCP-PCI connections. After retrieving the type of each connection, we can now determine if a pair of connections is of Type 1 or Type 2. If a pair of interfaces connecting to the UMLport shares the same contract but has different protocol types, then they are classified as Type 1 incompatible pair. If the connections do not match up with each other but state diagrams were defined to fix the incompatibility, then they are classified as Type 2.

For Type 1 pairs, we build *adapters* (corresponding to the adapter ports) that forward the output source signals to the destination SLports through the desired protocol channel. We shall now explain how this is done for OCP compliant adapters.

An OCP compliant adapter is built to fit the OCP bus fabrics. There are three levels of SystemC OCP communication models: generic, OCP TL1, and OCP TL2. We chose to use OCP TL2 as our wrapper communication model. The advantage of OCP TL2 is that it allows for burst transfers and the communication is faster and more reliable.

When an adapter gets a message from an OCP channel via an OCP port, it first decodes the message, and then forwards the message to the corresponding interface using a SystemC signal. After the internal SystemC component has completed its

operation, a response message will be created and placed in the OCP channel. Correspondingly, when a wrapper gets signaled by an internal component that wants to communicate with the environment, the wrapper will create a message labeled with identifier number of the interface, and puts it on the OCP channel. After the response is received, it is decoded and a reply signal will be forwarded to the component in waiting.

Figure 10: Work flow of wrapper generator

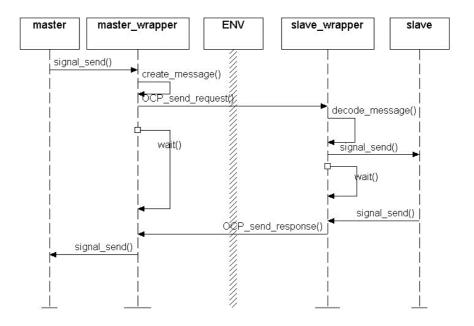

Figure 11: Sequence diagram of OCP communication groups

OCP master and slave ports are predefined OCP interfaces, and OCP communication is performed between them. The pair of master and slave ports forms a communication path. Each communication path starts with one OCP master port and ends with one OCP slave port. A 'provided' interface will be connected to OCP slave port, while a 'required' interface will be connected to an OCP master port. Each OCP port has three threads to control its actions. We call these a *communication group*. Communication groups are paired together and each pair controls an OCP channel. The channel is configured by reading the information extracted from the UML model.

Figure 11 shows the transactions of a communication group, where the *master* is a wrapped component of the master side object, and the *slave* is a wrapped component of slave side object. They communicate with each other using the services provided by

their wrappers, i.e., the communication is controlled by master\_wrapper and slave\_wrapper respectively.

Adapters for SystemC-Verilog, and SystemC-PCI are generated in a similar way. A SystemC-Verilog adapter is a SystemC header file that describes the SLport connection of the Verilog module. A SystemC-PCI adapter not only interprets incoming data but also needs to perform the access routines in accordance to the protocol. The wrapping is generic, therefore, multiple levels of wrapping is possible.

For a Type 2 pair, the state diagram shows how the outputs drive the inputs of the client program. A state machine is then generated. Code 1 shows the pseudo code for the state machine that drives IDCT interface using the Fast\_IDCT interfaces.

Figure 12: State diagrams of glue logic between IDCT master and slave interfaces at of Figure 13

```

while(true) {

switch (state) {

case IDLE: //in idle state

wait_until(Fast_IDCT_signal.read()=true);

//state is guarded by Fast_IDCT_signal

start.write(true); //drive driver port

state=INPUT_DATA; //change state

INPUT_DATA:

case

addr=Fast_IDCT_addr.read();

for i from 1 to 8, j from 1 to 8

din.write(addr[j*8+i];

state=WAIT;

case WAIT:

wait_until(done.read()=true);

state=SEND RESULTS;

case SEND_RESULTS:

for i from 1 to 8, j from 1 to 8

addr[j*8+i]=dout;

Fast_IDCT_ack.write(true);

state=IDLE;

```

Code 1: Pseudo code of glue logic generated from IDCT of Figure 12

## 3.5 Experiments and Results

#### 3.5.1 Simple-bus

Our first example, Simple-bus is taken from SystemC open source library. We have used it as our illustration example in previous sections. The system consists of a bus kernel, a bus arbiter, two memory slaves (fast\_mem, and slow\_mem), and two masters (master\_nb and master\_b). We wrapped the master\_b and master\_nb up and substituted the communication channels between the bus and the masters with OCP channels. Figure 9 shows the structural diagram of the Simple-bus example after wrapping. We then model the exterior SLports of the bus kernel and the masters,

and wrapped them up. The wrapper code is generated and assembled for the simulation. The unwrapped version of the simple bus SystemC code had 2,684 lines while the wrapped version had 3,743 lines of code. We measured the performance of the unwrapped and wrapped code on a Linux machine with a dual core AMD Opteron 280 CPU running at 2.4GHz. The unwrapped simple bus system finished a million bus transactions in 41.978 seconds, while the wrapped system took 52.188 seconds. Thus, the overall overhead caused by wrapping is 24.3%. Over head is caused by the additional the transactions between wrappers.

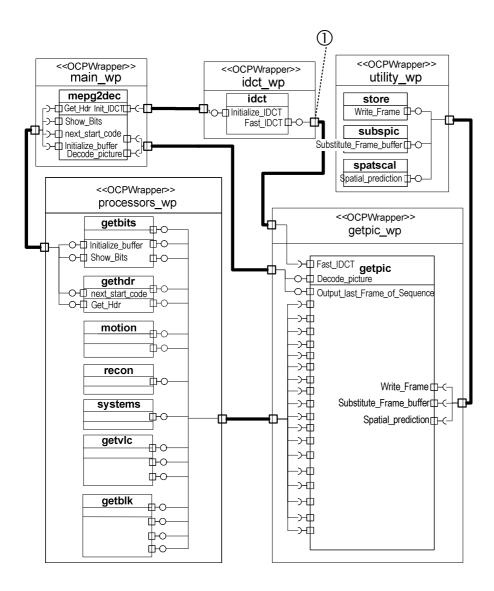

#### 3.5.2 MPEG-2 Decoder

MPEG is an encoding and compression system for digital multimedia content defined by the Motion Pictures Expert Group (MPEG) [56]. It is widely used in our audio/video system. MPEG-2 extends the basic MPEG system to provide compression support for TV quality transmission of digital video. We used an open source MPEG-2 decoder originally written in C. We analyzed the functionality and structure of the system, and made it SystemC-compliant.

To test the performance of our adapter code, we customized a SystemC version of MPEG-2 decoder and divided it into five groups. Five wrapper classes were created to wrap up the components. They communicate with each other using OCP channels which are highlighted using bold lines. Each wrapper consists of several OCP ports, and they are connected to other OCP ports as well as to interfaces of wrapped components. The MPEG-2 decoder is partitioned into five communication groups. The

SystemC code is generated and wrapped components are reconnected for simulation using the SystemC simulator.