# SELF-ALIGNED SOURCE AND DRAIN CONTACT

## **ENGINEERING FOR HIGH MOBILITY III-V**

## TRANSISTOR

ZHANG XIN GUI

## NATIONAL UNIVERSITY OF SINGAPORE

2012

## SELF-ALIGNED SOURCE AND DRAIN CONTACT

### **ENGINEERING FOR HIGH MOBILITY III-V**

### TRANSISTOR

### **ZHANG XIN GUI**

(B. Eng.), NUAA

#### A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# NUS GRADUATE SCHOOL FOR INTEGRATIVE SCIENCES AND ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2012

## **Declaration**

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Xingn

**Zhang Xin Gui**

7 March, 2013

### Acknowledgements

First and foremost, I would like to express my appreciation to my research advisor, Dr. Yeo Yee Chia for his patient guidance throughout these four years. I am thankful to him for sharing his knowledge and experiences, and have benefitted immensely from the regular discussions with him.

I would like to thank Dr. Moorthi Palaniapan and Dr. Daniel Shawn Pickard for their valuable discussion and suggestion during the course of my research work. I would also like to thank Associate Professor Ganesh S. Samudra and Zhu Chunxiang who have given me a lot of help and provided many useful discussions. Special thanks go to Dr. Lee Hock Koon for his guidance and support when I was performing my experiments at Data Storage Institute.

I am also grateful to Mr. Chum Chan Choy and Ms. Teo Siew Lang for their great help with a lot of process steps while I was doing device fabrication in Institute of Materials Research and Engineering. Thank you for sharing your valuable experiences with me and I have benefitted greatly.

To the friends I've met in Silicon Nano Device Lab, Shao-Ming, Hock-Chun, Genquan, Phyllis, Ivana, Pengfei, Yang Yue, Liu Bin, Gong Xiao, Tong Yi, Yinjie, Zhou Qian, Chunlei, Guo Cheng, Samuel, Sujith, Lanxiang, Eugene, Zhu Zhu, Cheng Ran, Tong Xin, Wenjuan, Zhu Zhu, Xinke and many others, I'm grateful that our paths have crossed and thank you for the assistance and friendship throughout the four years. Special thanks go to Huaxin for his contribution to this thesis and for those days we were rushing for conference deadlines together in the cleanroom. I would also like to thank the technical staff of SNDL, Mr. O Yan Wai Linn, Mr. Patrick Tang, and Ms. Yu Yi for their help in one way or another.

Last but not least, I would like to extend my deepest gratitude to my family. To my grandpa, grandma, dad, mum, and brother, thank you for your encouragement and support throughout this journey and your love will never be forgotten.

## **Table of Contents**

#### Abstract vii

| List of Tables  | ix   |

|-----------------|------|

| List of Figures | X    |

| List of Symbols | xxii |

#### Chapter 1 Introduction

| 1.1 | Silicon Transistor Scaling: Benefits and Challenges | . 1 |

|-----|-----------------------------------------------------|-----|

| 1.2 | High Electron Mobility of III-V Materials           | . 2 |

| 1.3 | Challenges of III-V CMOS Technology                 | . 3 |

| 1.3 | 3.1 Formation of High-Quality Gate Dielectric       | 4   |

| 1.3 | 3.2 III-V Integration on Si Substrates              | 4   |

| 1.3 | 3.3 Channel Material Engineering                    | 5   |

| 1.3 | 8.4 New Device Structure Engineering                | 6   |

| 1.3 | 3.5 Source/Drain Resistance Engineering             | 7   |

| 1.4 | Objectives of Research                              | 11  |

| 1.5 | Thesis Organization                                 | 12  |

| 1.6 | References                                          | 14  |

## Chapter 2 Self-Aligned NiGeSi Contacts for GaAs Channel n-MOSFETs

| 2. | 1 I   | ntroduction                                                   | 23 |

|----|-------|---------------------------------------------------------------|----|

| 2. | 2 I   | Development of Self-Aligned NiGeSi Contacts Technology        | 25 |

|    | 2.2.1 | Selective Epitaxy of Germanium-Silicon (GeSi) on GaAs         | 27 |

|    | 2.2.2 | Two-Step Metallization Process for NiGeSi Contacts Formation  | 30 |

|    | 2.2.3 | Electrical Characterization and Discussion                    | 34 |

| 2. | 3 I   | Device Integration and Characterization                       | 39 |

|    | 2.3.1 | Integration of Self-aligned NiGeSi Contacts on GaAs n-MOSFETs | 39 |

| 2.3.2 Device Characterization and Analysis                             | 42    |

|------------------------------------------------------------------------|-------|

| 2.4 Summary                                                            | 48    |

| 2.5 References                                                         | 49    |

| Chapter 3 Self-Aligned Ni-InGaAs Contacts for InGaAs Chan<br>n-MOSFETs | nnel  |

| 3.1 Introduction                                                       | 56    |

| 3.2 Development of Self-Aligned Ni-InGaAs Contact Technology           |       |

| 3.2.1 Reaction of Ni with InGaAs                                       | 58    |

| 3.2.2 Electrical Properties of Ni-InGaAs Contacts                      | 63    |

| 3.3 Device Integration and Characterization                            | 68    |

| 3.3.1 Integration of Self-aligned Ni-InGaAs Contacts on InGaAs n-      |       |

| MOSFETs                                                                | 68    |

| 3.3.2 Device Characterization and Analysis                             | 71    |

| 3.4 Summary                                                            | 82    |

| 3.5 References                                                         | 83    |

| Chapter 4 InGaAs FinFETs with Self-Aligned Ni-InGaAs Cont              | acts  |

| 4.1 Introduction                                                       | 93    |

| 4.2 Process Development for Fabrication of InGaAs FinFETs              | 96    |

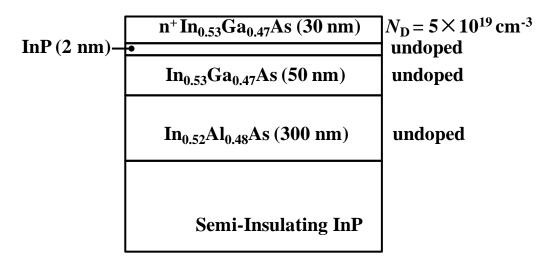

| 4.2.1 Design of III-V Layer Structure                                  | 96    |

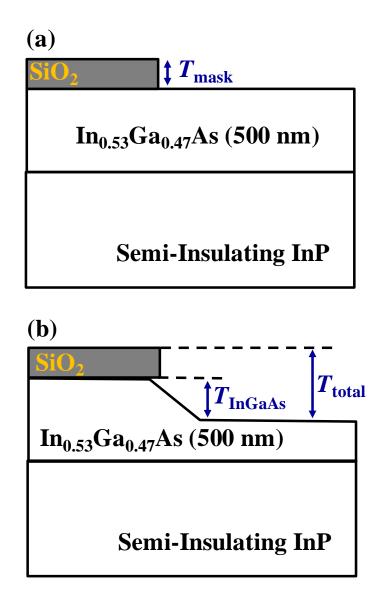

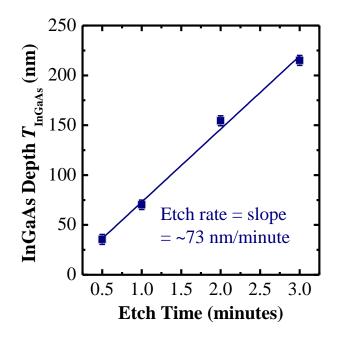

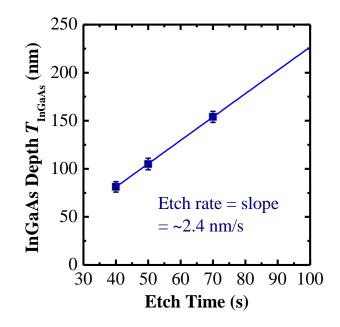

| 4.2.2 Selective Wet Etch of $n^+$ InGaAs                               | 97    |

| 4.2.3 Plasma Etch of InGaAs Fin                                        | 99    |

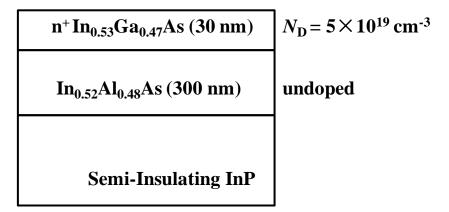

| 4.2.4 Electrical Properties of Ni-InGaAs Contacts                      | 102   |

| 4.3 Device Integration and Characterization                            | . 107 |

| 4.3.1 Integration of InGaAs FinFETs with Self-Aligned Ni-InGaAs        |       |

| Contacts                                                               | 107   |

| 4.3.2 Device Characterization and Analysis                             | 110   |

| A A Summary                                                            | 123   |

## Chapter 5 InGaAs FinFETs with Self-Aligned Non-Alloyed Molybdenum Contacts

| 5.1 | Introduction                                                                                       | . 131 |

|-----|----------------------------------------------------------------------------------------------------|-------|

| 5.2 | InGaAs FinFETs with Mo Contacts Self-Aligned to Channel                                            | . 135 |

| 5.2 | 2.1 Molybdenum Contacts on n <sup>+</sup> InGaAs                                                   | 135   |

| 5.2 | 2.2 Integration of InGaAs FinFETs with Mo Contacts Self-Aligned to                                 |       |

| Ch  | annel                                                                                              | 138   |

| 5.2 | 2.3 Device Characterization and Discussion                                                         | 141   |

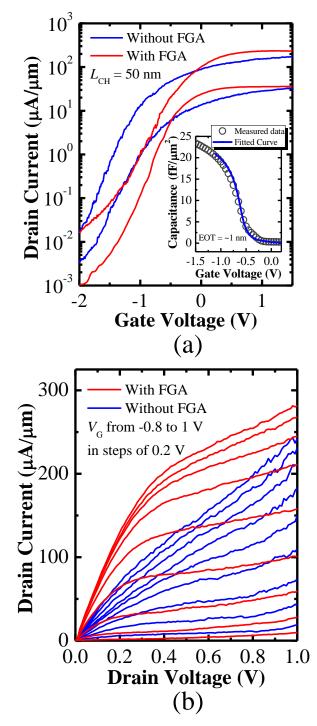

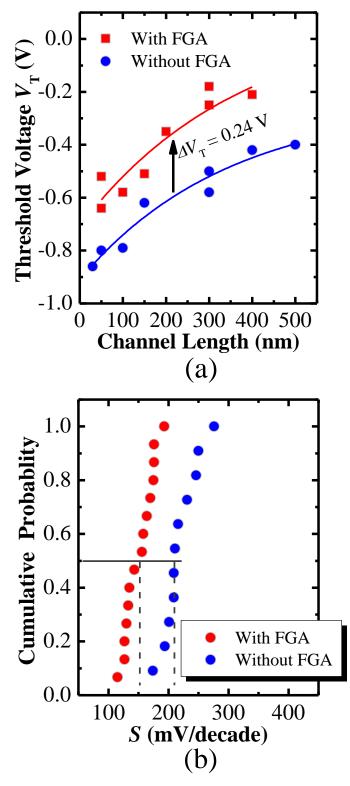

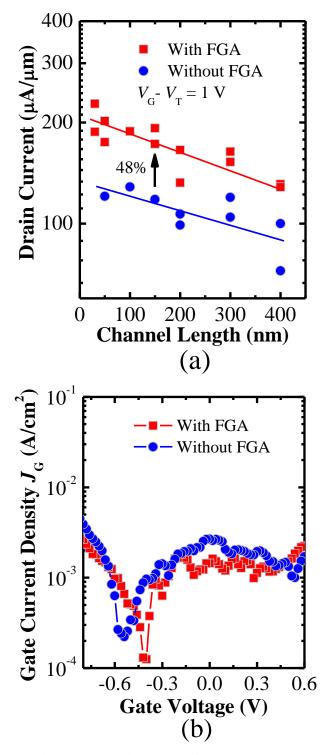

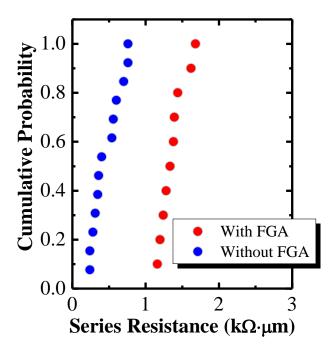

| 5.3 | InGaAs FinFETs with FGA Improved HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> Dielectric       | . 151 |

| 5.3 | 3.1 Integration of InGaAs FinFETs with HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> Dielectric | 151   |

| 5.3 | 3.2 Device Characterization and Discussion                                                         | 152   |

| 5.4 | Summary                                                                                            | . 159 |

| 5.5 | References                                                                                         | . 160 |

### Chapter 6 Conclusion and Future Work

| 6.1 Conclusion                                                    | 165 |

|-------------------------------------------------------------------|-----|

| 6.2 Contributions of This Thesis                                  | 166 |

| 6.2.1 Self-Aligned NiGeSi Metallization for GaAs Planar n-MOSFETs | 166 |

| 6.2.2 Self-Aligned Ni-InGaAs Contacts for InGaAs Planar n-MOSFETs | 166 |

| 6.2.3 InGaAs FinFETs with Self-Aligned Ni-InGaAs Contacts         | 166 |

| 6.2.4 InGaAs FinFETs with Self-Aligned Non-Alloyed Mo Contacts    | 167 |

| 6.2.5 InGaAs FinFETs with Forming Gas Annealing (FGA) Improved    |     |

| $HfO_2/Al_2O_3$                                                   | 167 |

| 6.3 Future Directions                                             | 168 |

| 6.3.1 Contact Resistance Reduction                                | 169 |

| 6.3.2 Thermal Stability of Contacts                               | 170 |

| 6.3.3 Reliability Study for III-V MOSFETs                         | 170 |

| 6.3.4 Self-Aligned Contacts for III-V p-MOSFETs                   | 170 |

| 6.4 References                                                    | 171 |

| Appendix List of Publications                                     | 174 |

### Abstract

Self-Aligned Source and Drain Contact Engineering

For High Mobility III-V Transistor

by

ZHANG Xin Gui

Doctor of Philosophy – Electrical and Computer Engineering National University of Singapore

Driven by tremendous advances in lithography the semiconductor industry has followed Moore's law by shrinking transistor dimensions continuously for the last 40 years. The big challenge going forward is that continued scaling of Si transistors will be more and more difficult because of both fundamental limitations and practical considerations as the transistor dimensions approach 10 nm. Among several emerging nanoscale devices, III-V MOSFETs are the most attractive devices due to their high electron mobility, low supply voltage, and potential heterogeneous integration on Si substrates. To take the full advantages of III-V MOSFETs, lowresistance source/drain (S/D) is required. However, III-V transistors currently have large S/D series resistance limiting the device drive current as they lack advanced S/D contact technologies. This thesis documents work performed on self-aligned S/D contact engineering for III-V n-MOSFETs.

In this thesis, novel self-aligned metallization, analogous to the salicidation process in Si CMOS, was developed for III-V n-MOSFETs to address the high S/D resistance issue. New contact materials such as NiGeSi, Ni-InGaAs were developed

and the key characteristics of these new contact materials were determined and identified. Various process integration challenges for realizing self-aligned S/D contacts were identified and addressed. Technology demonstrations of these new materials integrated as III-V S/D contacts in a self-aligned manner were also realized. In particular, NiGeSi and Ni-InGaAs were integrated in GaAs and InGaAs planar n-MOSFETs, respectively, using a salicide-like process and leading to reduced series resistance.

For achieving better electrostatic control than planar n-MOSFETs, novel III-V FinFETs were explored. S/D resistance engineering was also carried out for the FinFETs. With well designed FinFETs structure and metallization process, selfaligned contacts such as Ni-InGaAs and Mo were realized on *in-situ* heavily doped III-V S/D. The combination of heavily doped S/D and self-aligned contacts leads to low series resistance for InGaAs FinFETs. Series resistance as low as 250  $\Omega$ ·µm was obtained, and this is the lowest value reported-to-date for InGaAs non-planar n-MOSFETs. This affirms the effectiveness of the S/D resistance engineering concept of combining heavily doped S/D and self-aligned contacts. The availability of selfaligned contact technology is an important step towards realization of high performance III-V logic transistors.

# **List of Tables**

| Table 1.1.        | Carrier mobility, effective mass, bandgap and permittivity of                    |       |

|-------------------|----------------------------------------------------------------------------------|-------|

|                   | some commonly used semiconductors [1.7]                                          | 2     |

| Table 4.1.        | State-of-art S/D contact technologies for InGaAs non-planar n-                   |       |

|                   | MOSFETs                                                                          | 94    |

| <b>Table 4.2.</b> | Possible etch products and their volatilities for InGaAs etched in               |       |

|                   | Cl <sub>2</sub> -based plasma [4.23]                                             | . 100 |

| Table 4.3.        | Recipe that was used for InGaAs etch. Ar was introduced to $Cl_2$                |       |

|                   | to facilitate the etch process                                                   | . 100 |

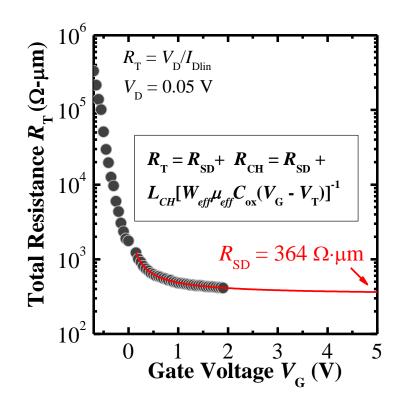

| Table 4.4.        | Contributions of series resistance $R_{SD}$ to device total resistance $R_{T}$ . |       |

|                   |                                                                                  | .118  |

| Table 5.1.        | State-of-art S/D contact technologies for InGaAs non-planar n-                   |       |

|                   | MOSFETs                                                                          | .131  |

| Table 5.2.        | State-of-art gate stack technologies for InGaAs non-planar n-                    |       |

|                   | MOSFETs.                                                                         | .133  |

# **List of Figures**

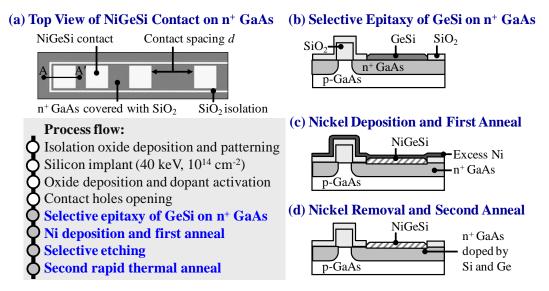

| Fig. 1.1. | Schematic illustration of the key technical challenges faced in the                  |

|-----------|--------------------------------------------------------------------------------------|

|           | realization and integration of high mobility III-V CMOS on Si                        |

|           | substrates for future logic applications                                             |

| Fig. 1.2. | Schematic of a transistor biased in the linear region, showing that                  |

|           | total resistance $R_{\rm T}$ between source and drain terminals includes             |

|           | channel resistance $R_{\rm CH}$ , source resistance $R_{\rm S}$ and drain resistance |

|           | <i>R</i> <sub>D</sub> 7                                                              |

| Fig. 1.3. | Schematic of a conventional III-V transistor showing various                         |

|           | resistance components that contribute to device $R_{SD}$ , where $R_{SD}$ =          |

|           | $2(R_{\rm C} + R_{\rm III-V})$                                                       |

| Fig. 2.1. | (a) The plan-view optical microscopy image of a TLM structure.                       |

|           | The self-aligned ohmic contact formation process comprises (b)                       |

|           | selective epitaxy of GeSi on n <sup>+</sup> GaAs in a contact hole, (c) Ni           |

|           | deposition and a first thermal annealing for NiGeSi formation, (d)                   |

|           | removal of excess Ni and a second thermal annealing to form the                      |

|           | NiGeSi ohmic contact25                                                               |

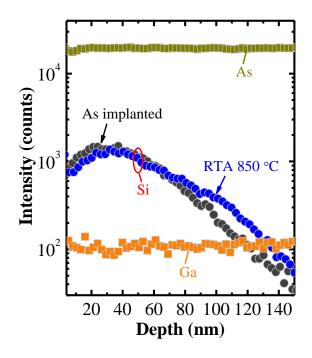

| Fig. 2.2. | SIMS analysis was performed to obtain the Si profiles (circles) of                   |

|           | the samples before and after dopant activation annealing. Si                         |

|           | dopants show negligible diffusion even after the dopant activation                   |

|           | annealing at 850 °C26                                                                |

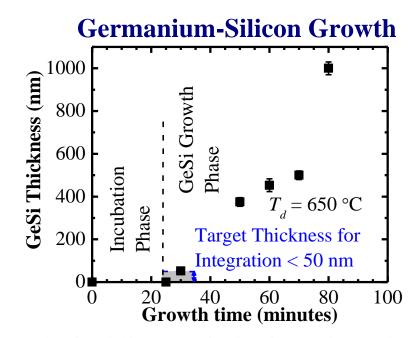

| Fig. 2.3. | Plot of GeSi thickness as a function of growth time. An                              |

|           | incubation phase with a very slow growth rate is observed in the                     |

|           | first 25 minutes. Once the growth enters into the growth phase,                      |

|           | the growth rate for GeSi is much faster (> 10 nm/minute)                             |

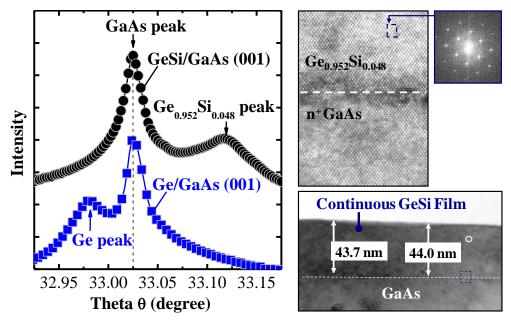

| Fig. 2.4. | (a) High resolution XRD shows that 4.8 atomic percent of Si was                      |

|           | incorporated in GeSi. GeSi formed on GaAs is under tensile                           |

|           | strain. (b) TEM images show the formed GeSi/GaAs                                     |

|           | heterostructure, and a diffractogram of a selected region enclosed                   |

|           | by the dashed box indicates the good crystalline quality of GeSi28                   |

Х

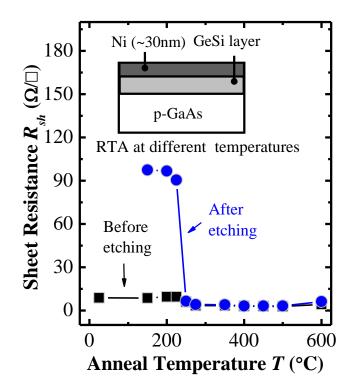

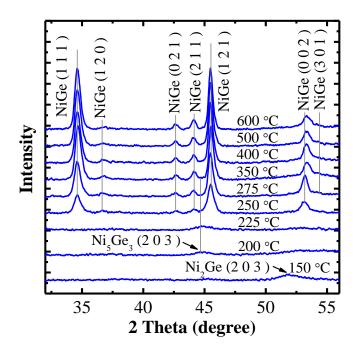

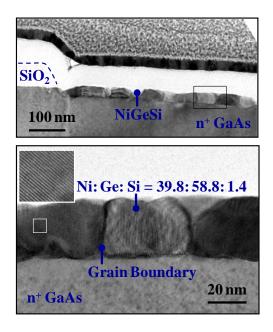

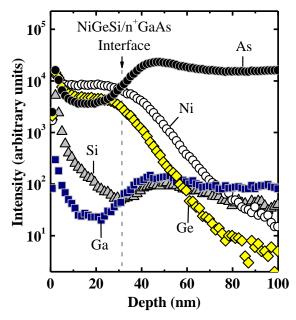

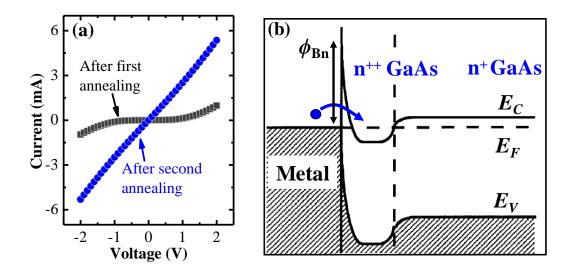

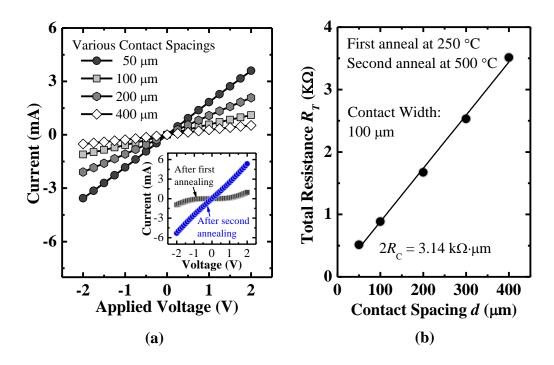

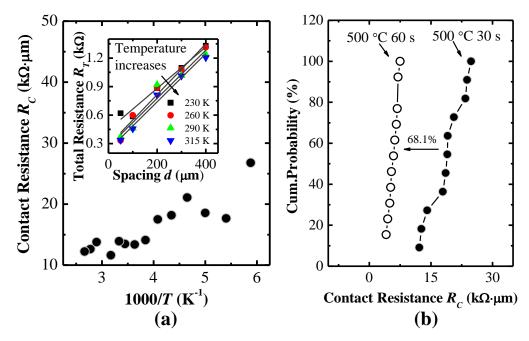

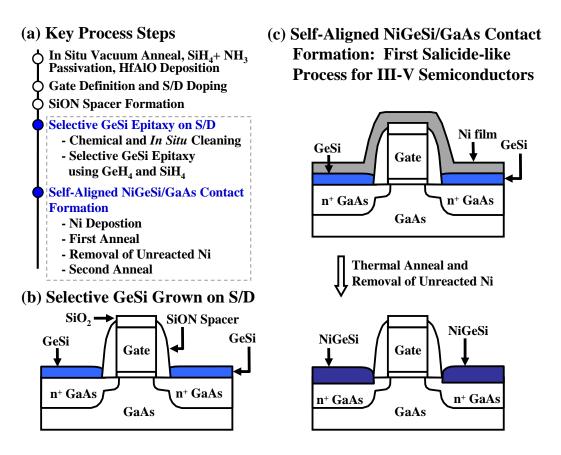

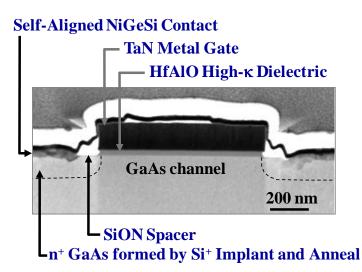

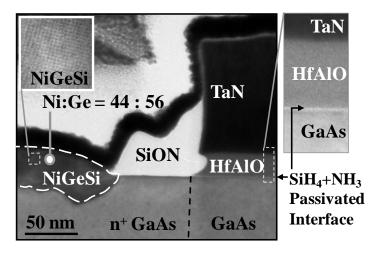

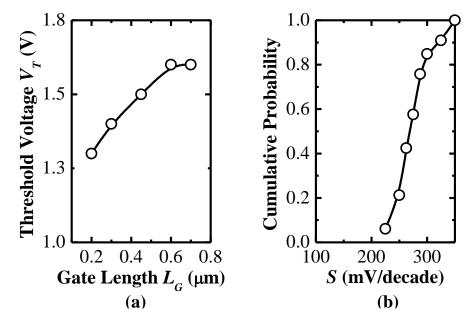

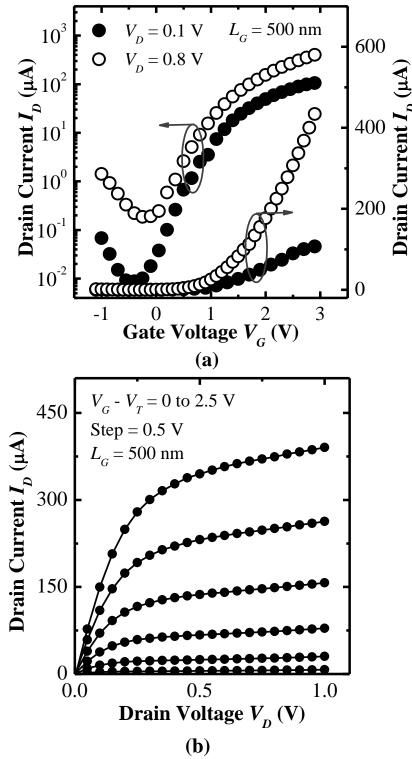

Fig. 2.5. Sheet resistance versus annealing temperature for ~30 nm Ni on blanket GeSi/GaAs sample. The annealing time was fixed at 60 s. The sheet resistance values of annealed samples with and without selective etching in HCl are indicated by square and circle symbols, respectively. Nickel germanosilicide formed at above 250  $^{\circ}$  C has a low sheet resistance. At temperatures below 225  $^{\circ}$  C, Fig. 2.6. XRD spectra shows nickel germanide phases formed from 150  $\,^{\circ}$ C and 600  $\,^{\circ}$ C. The spectra indicates that NiGe started to form at annealing temperature of 250 °C and confirms that only NiGe Fig. 2.7. Cross-sectional TEM image (top) of a TLM structure shows the formation of poly-crystalline NiGeSi on n<sup>+</sup> GaAs that is not covered by  $SiO_2$ . No Ge or NiGeSi was observed on the  $SiO_2$ region, which confirmed the selectivity of GeSi epitaxy. A zoomed-in view (bottom) showing several grains of NiGeSi. A high-resolution TEM image of a portion of a NiGeSi grain is SIMS analysis of NiGeSi contact on n<sup>+</sup> GaAs showing the Fig. 2.8. elemental distribution of Si, Ge, Ga, As, and Ni. The interface between NiGeSi and GaAs is indicated by the dashed vertical line. Fig. 2.9. (a) I-V characteristics of NiGeSi before and after the second annealing. (b) Band diagram shows that a heavily doped  $n^+$  GaAs layer can enhance the field emission of electrons through the (a) I-V curves measured between NiGeSi contacts with different Fig. 2.10. contact spacing d formed on  $n^+$  GaAs. Excellent ohmic behavior is observed. (b) Plot of total resistance  $R_T$  between two NiGeSi contacts as a function of the contact spacing d. The extracted  Fig. 2.11. (a) Reduction of  $R_{\rm C}$  with increasing measurement temperature was observed due to increased charge injection by thermionic Inset shows  $R_{\rm T}$  as a function of d at various emission. temperatures. (b) Cumulative distribution of contact resistance gives the statistical summary of  $R_{\rm C}$ . 68.1%  $R_{\rm C}$  reduction was achieved by extending the second annealing duration......37 Fig. 2.12. (a) Key process steps for first technology demonstration of III-V n-MOSFETs with 'salicide-like' self-aligned contact. (b) An epitaxy process for forming thin continuous GeSi layer on GaAs S/D regions was employed, followed by (c) Ni deposition and a novel two-step annealing process to form NiGeSi ohmic contacts on GaAs......40 Fig. 2.13. (a) TEM image of the world's first III-V n-MOSFET with 'salicide-like' self-aligned contacts. NiGeSi ohmic contacts were

formed adjacent to the gate. TaN metal-gate on HfAlO high-κ

dielectric stack was used. (b) Zoomed-in view of the NiGeSi

formed on the Si implanted and annealed n<sup>+</sup> GaAs S/D regions.

A SiH<sub>4</sub>+NH<sub>3</sub> passivation technique was used to form high-quality

gate dielectric on GaAs. Insets show high resolution TEM

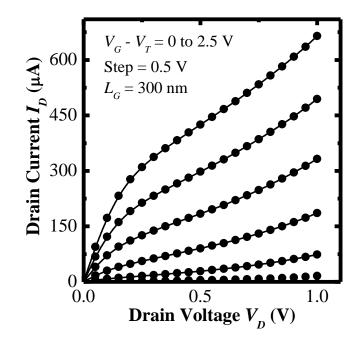

- Fig. 2.16.  $I_D$ - $V_D$  curves of another GaAs transistor with self-aligned NiGeSi contacts, showing good output characteristics. Device has a gate

|            | length of 300 nm, and a gate width of 100 $\mu$ m, showing higher                                       |

|------------|---------------------------------------------------------------------------------------------------------|

|            | drive current as compared with the device in Fig. 2.15                                                  |

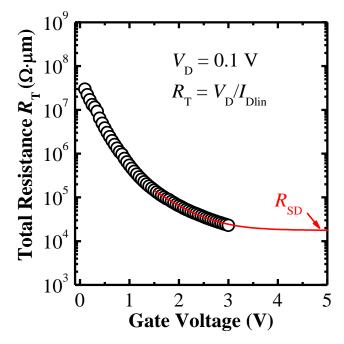

| Fig. 2.17. | Total resistance $R_{\rm T}$ as a function of gate voltage for the same                                 |

|            | device in Fig. 2.15. $R_{\rm T} = V_{\rm D}/I_{\rm Dlin}$ and $I_{\rm Dlin}$ is drain current at linear |

|            | regime ( $V_D = 0.1$ V). Device channel resistance was modulated                                        |

|            | by applied gate voltage, leading to reduction of device total                                           |

|            | resistance with increased gate voltage45                                                                |

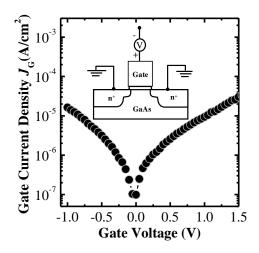

| Fig. 2.18. | Small gate leakage current density $J_{\rm G}$ was measured and                                         |

|            | normalized by gate area, indicating that the thermal steps of                                           |

|            | metallization are compatible with the TaN/HfAlO gate stack47                                            |

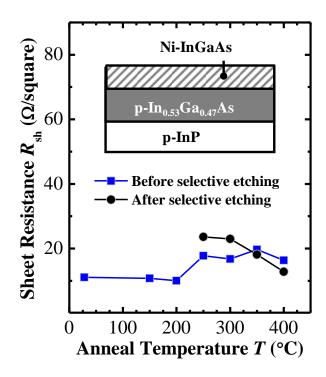

| Fig. 3.1.  | Sheet resistance of the Ni/InGaAs samples was measured right                                            |

|            | after annealing at different temperatures (squares) for 60 s. After                                     |

|            | selective etch, sheet resistance was also measured (circles). Ni-                                       |

|            | InGaAs is formed when the temperature is above 250 $^\circ\!\mathrm{C}$ and                             |

|            | shows a low sheet resistance even after the selective etching in                                        |

|            | concentrated HCl solution                                                                               |

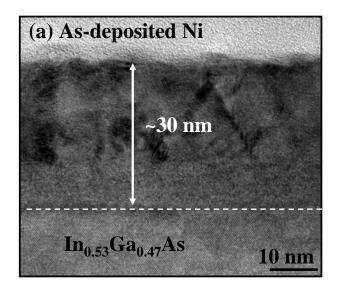

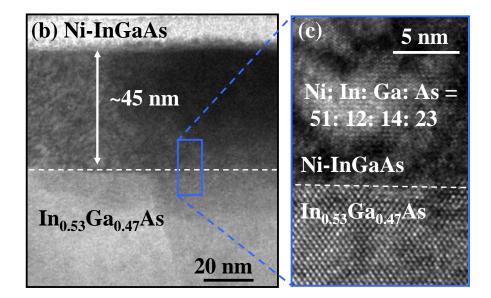

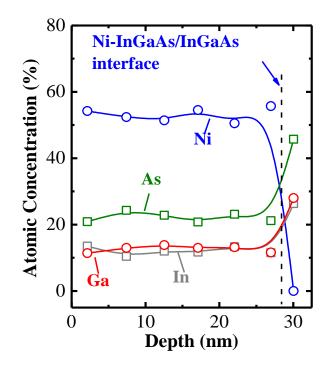

| Fig. 3.2.  | (a) A ~30 nm polycrystalline Ni film was deposited on InGaAs                                            |

|            | substrate. (b) After RTA at 250 $^{\circ}$ C for 60 s, a ~45 nm Ni-InGaAs                               |

|            | film was uniformly formed with darker contrast with respect to                                          |

|            | the substrate. (c) High resolution TEM shows the zoomed-in                                              |

|            | view of the Ni-InGaAs/InGaAs interface, featuring a very abrupt                                         |

|            | interface. Ni-InGaAs has a crystalline structure with an                                                |

|            | approximate atomic composition of Ni: In: Ga: As = 51: 12: 14:                                          |

|            | 23                                                                                                      |

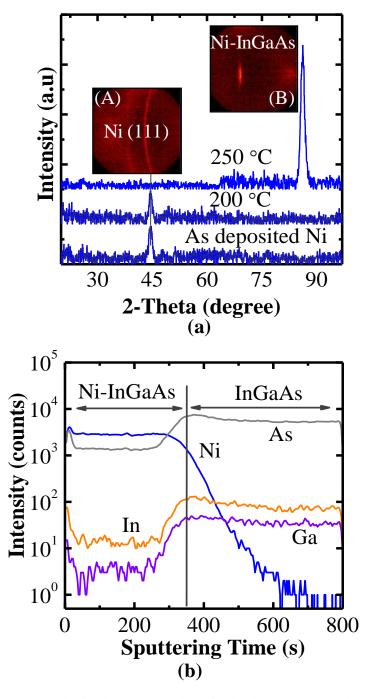

| Fig. 3.3.  | (a) XRD indicating that as-deposited Ni/InGaAs sample and                                               |

|            | Ni/InGaAs sample annealed at 200 °C for 60 s have ploy-                                                 |

|            | crystalline Ni and that Ni-InGaAs was formed after the sample                                           |

|            | was annealed at 250 $^{\circ}$ C. (b) SIMS profile shows the elemental                                  |

|            | distribution and confirms the formation of Ni-InGaAs                                                    |

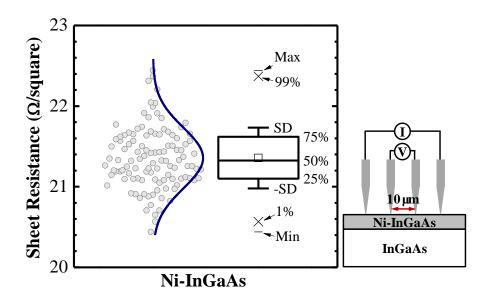

| Fig. 3.4.  | The cumulative plot shows $R_{\rm sh}$ distribution in area of 1 mm × 1                                 |

|            | mm for the Ni-InGaAs film. $R_{\rm sh}$ mapping was performed using                                     |

xiii

| microscopic  | 4-point   | probe.     | $R_{ m sh}$ | distribution   | ranges | from  |    |

|--------------|-----------|------------|-------------|----------------|--------|-------|----|

| 20.4–22.4 Ω/ | square, w | rith an av | erage o     | of 21.3 Ω/squa | are    | ••••• | 63 |

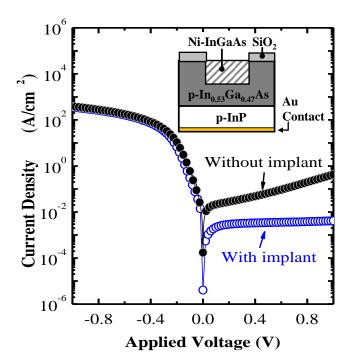

- Fig. 3.7. Process flow for fabricating InGaAs channel n-MOSFETs with self-aligned Ni-InGaAs contacts. S/D implant and dopant activation annealing were performed for one batch of devices (implanted devices), while the other batch of devices (control devices) skipped both the implant and activation annealing. (b) Ni was uniformly deposited on the gate and S/D regions of the device sample. (c) After thermal annealing, Ni diffuses into InGaAs and reacts with InGaAs by forming Ni-InGaAs. Ni-InGaAs formed on the surface of InGaAs shows a darker contrast with the InGaAs substrate. (d) Unreacted Ni over gate stack was selective removed by a selective wet etch using HCl solution. The cross-section TEM image shows the final structure of an InGaAs device with self-aligned Ni-InGaAs contacts. The Ni-InGaAs contact appears as a darker region formed on the surface

|            | of InGaAs, lying adjacent and well aligned to the TaN/Al <sub>2</sub> O <sub>3</sub> gate stack            |

|------------|------------------------------------------------------------------------------------------------------------|

| Fig. 3.8.  | EDX characterization at localized spots in the Ni-InGaAs region                                            |

|            | was performed to obtain the Ni-InGaAs composition. Atomic                                                  |

|            | concentration versus depth shows a uniform composition ratio of                                            |

|            | Ni: In: Ga: As = 51: 12: 14: 23 through the entire Ni-InGaAs                                               |

|            | layer                                                                                                      |

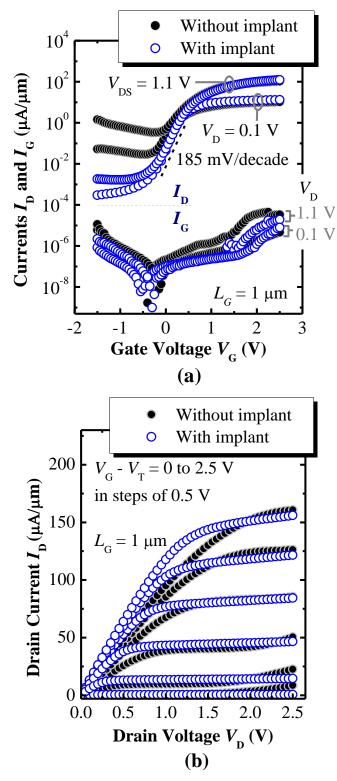

| Fig. 3.9.  | (a) $I_{\rm D}$ - $V_{\rm G}$ transfer characteristics of implanted and control                            |

|            | In <sub>0.7</sub> Ga <sub>0.3</sub> As channel n-MOSFETs with gate length of 1 $\mu$ m. $I_{OFF}$          |

|            | for the implanted device is significantly reduced as compared                                              |

|            | with the control device. Gate leakage current $I_{\rm G}$ is also plotted.                                 |

|            | (b) $I_{\rm D}$ - $V_{\rm D}$ output characteristics of the transistors at various gate                    |

|            | overdrives73                                                                                               |

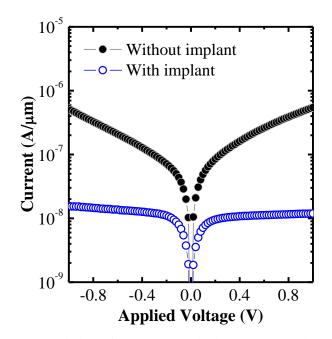

| Fig. 3.10. | I-V characteristics of source-to-drain back-to-back diodes for both                                        |

|            | devices. The current was normalized by gate width $W_{eff} = 100$                                          |

|            | $\mu$ m. Device with implanted S/D shows a much lower junction                                             |

|            | leakage current (reverse-saturation current)74                                                             |

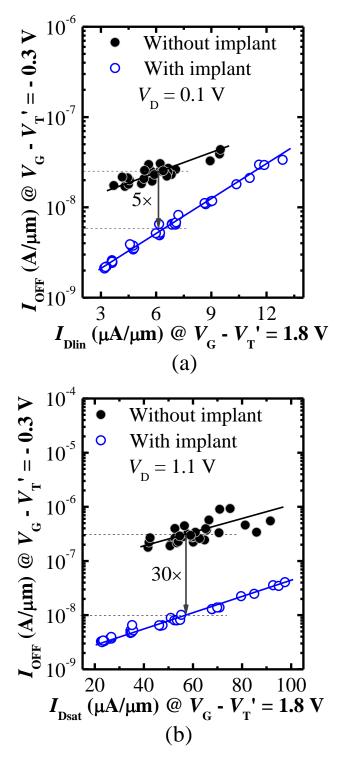

| Fig. 3.11. | (a) $I_{\text{ON}}$ - $I_{\text{OFF}}$ characteristics of implanted and control devices in the             |

|            | linear region ( $V_D = 0.1$ V). $I_{OFF}$ and $I_{ON}$ are defined at gate                                 |

|            | overdrives $V_{\rm G}$ - $V_{\rm T}$ ' of -0.3 V and 1.8 V, respectively. (b) $I_{\rm ON}$ - $I_{\rm OFF}$ |

|            | characteristics in the saturation region ( $V_D = 1.1$ V). $I_{OFF}$ was                                   |

|            | significantly suppressed for devices with $n^+$ S/D implant. Over 5                                        |

|            | times and 30 times reduction of $I_{\text{OFF}}$ was observed in the linear                                |

|            | and saturation region, respectively75                                                                      |

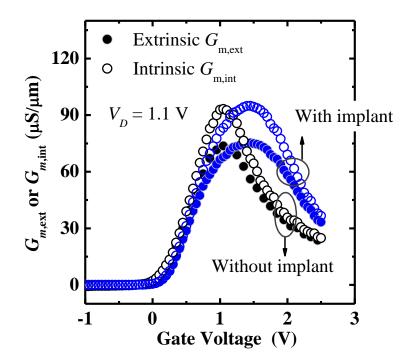

| Fig. 3.12. | $G_{\rm m,ext}$ (solid circles) and $G_{\rm m,int}$ (open circles) was plotted for                         |

|            | control and implanted devices. Both devices show comparable                                                |

|            | extrinsic and intrinsic transconductane at $V_{\rm D}$ of 1.1 V                                            |

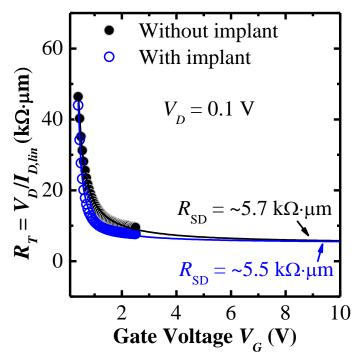

| Fig. 3.13. | Total resistance $R_T$ in the linear regime ( $V_D = 0.1$ V) as a function                                 |

|            | of gate voltage for the same pair of devices in Fig. 3.9. Equation                                         |

|            | (3.5) was used to fit the data points (circles). The fitted solid                                          |

|            | curves were extrapolated to $V_{\rm G} = 10$ V to obtain the value of $R_{\rm SD}$ 77                      |

|            |                                                                                                            |

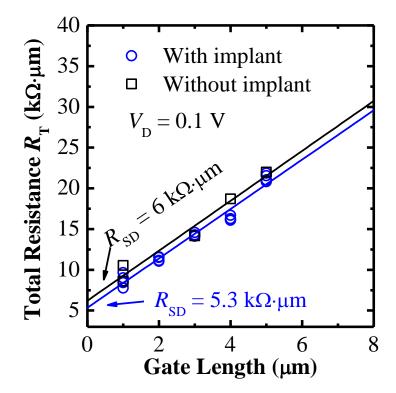

Fig. 3.14.  $R_{\rm T}$  in the linear regime ( $V_{\rm D} = 0.1$  V) as a function of  $L_{\rm G}$  at a specified gate overdrive  $V_{\rm G} - V_{\rm T}$  of 1.8 V. Equation (3.5) was used to fit the data points (circles and squares). The fitted curves were extrapolated to  $L_{\rm G} = 0$  to obtain the value of  $R_{\rm SD}$ . The obtained  $R_{SD}$  values for control and implanted device are ~6 and Fig. 3.15. (a) The device layout showing that the source or drain has an area of 100  $\mu$ m  $\times$  100  $\mu$ m. (b) The schematic of the device cross section (A-A') shows that series resistance  $R_{SD}$  includes Ni-Fig. 3.16. Ni-InGaAs resistance and Ni-InGaAs contact resistance are the main resistance components of the transistor  $R_{SD}$  and they lead to a contribution of 46% and 54 % to R<sub>SD</sub>, respectively......80 Fig. 3.17.  $R_{\rm SD}$  of this work is the lowest among the reported  $R_{\rm SD}$  values for transistors with implanted S/D. It is found that transistors with Fig. 4.1. Layer structure of III-V wafer for In<sub>0.53</sub>Ga<sub>0.47</sub>As FinFET fabrication. The III-V layers were grown on 2-inch semiinsulating InP substrate by molecular beam epitaxy......96 Fig. 4.2. (a) The wafer used in this etch experiment has a 500 nm thick InGaAs layer on InP substrate. SiO<sub>2</sub> layer with thickness  $T_{\text{mask}}$  of 35 nm was deposited by electron beam evaporation and was etched as an etch mask. (b) The sample was dipped in  $C_6H_8O_7/H_2O_2$  solution for different durations. The etch step Fig. 4.3.  $T_{\text{InGaAs}}$  as a function of etch time. The measured step height from a surface profiler has an error less than 10 nm. Multiple measurements were done at each etch time and the obtained step Fig. 4.4.  $T_{InGaAs}$  as a function of etch time. Surface profiler was used to measure the step height. Multiple measurements were performed

|           | at each etch time and the obtained step height shows small<br>standard deviation. The solid line is a linear line fit of the |

|-----------|------------------------------------------------------------------------------------------------------------------------------|

|           | measured data (squares)                                                                                                      |

| Fig. 4.5. | The layer structure of III-V substrate for TLM fabrication. This                                                             |

| 0         | is different from the sample used for FinFET fabrication. The                                                                |

|           | wafer has $n^+$ In <sub>0.53</sub> Ga <sub>0.47</sub> As (100 nm) with $N_D$ of $5 \times 10^{19}$ cm <sup>-3</sup> and      |

|           | undoped In <sub>0.52</sub> Al <sub>0.48</sub> As (300 nm) layers grown on 2-inch InP                                         |

|           | substrate                                                                                                                    |

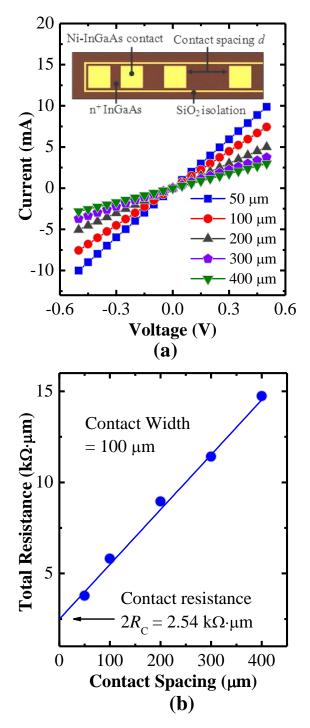

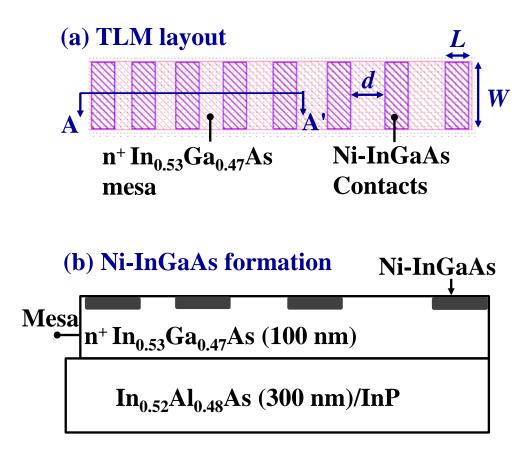

| Fig. 4.6. | (a) Layout of TLM test structure. Contact width and contact                                                                  |

|           | length are $W$ and $L$ , respectively. $d$ is contact spacing. Before                                                        |

|           | Ni-InGaAs formation, $n^+$ InGaAs mesa was formed by wet etch.                                                               |

|           | (b) Cross-section of the TLM structure along A-A' illustrates Ni-                                                            |

|           | InGaAs formation on top of $n^+$ InGaAs. (c) A thick Ni layer (300                                                           |

|           | nm) was deposited on top of Ni-InGaAs to reduce metal                                                                        |

|           | resistance103                                                                                                                |

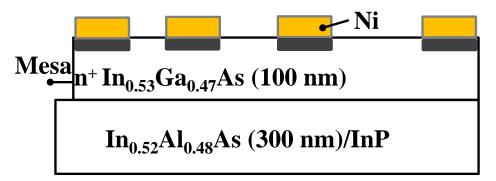

| Fig. 4.7. | (a) Plot of $R_{\rm T}$ between two Ni-InGaAs contacts as a function of                                                      |

|           | contact spacing d. d varies from 5 to 200 $\mu$ m. The solid line is                                                         |

|           | the linear fit of the data points. The current-voltage                                                                       |

|           | characteristics measured from adjacent Ni-InGaAs contacts is                                                                 |

|           | shown in the inset. (b) Cumulative plot showing a tight                                                                      |

|           | distribution of $\rho_{\rm C}$ measured from 10 TLM test structures. $\rho_{\rm C}$ is                                       |

|           | extracted to be in the order of $1 \times 10^{-6} \Omega \cdot cm^2$                                                         |

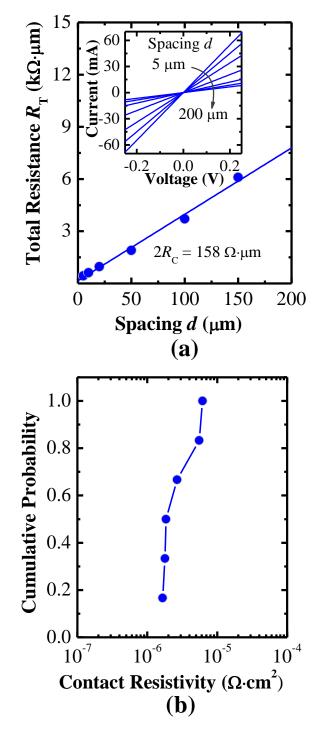

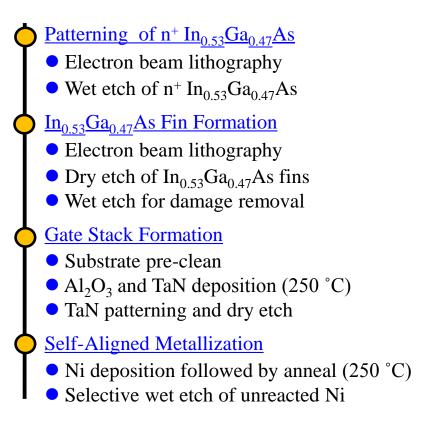

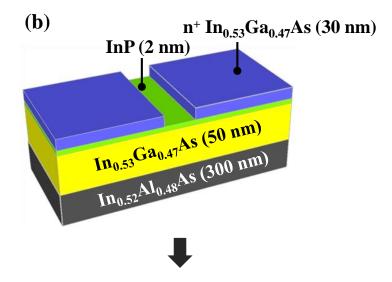

| Fig. 4.8. | (a) Process flow for fabricating InGaAs FinFETs with self-                                                                   |

|           | aligned Ni-InGaAs contacts. The key steps include (b) recess                                                                 |

|           | etch of $n^+$ InGaAs, (c) plasma etch of InGaAs fin, (d) gate stack                                                          |

|           | formation, and (e) self-aligned metallization109                                                                             |

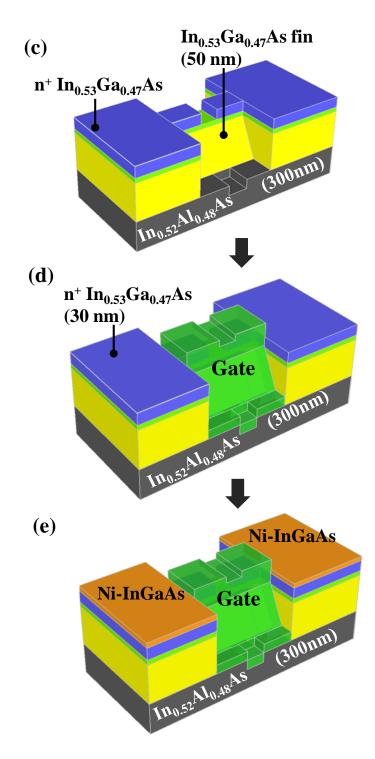

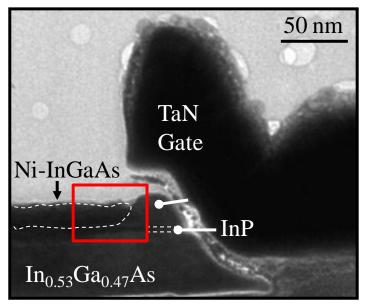

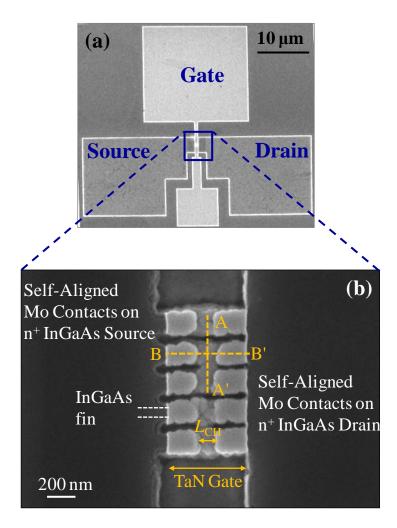

| Fig. 4.9. | (a) SEM image shows the zoomed-out view of a FinFET device.                                                                  |

|           | The gate line surrounding source and drain region is sitting on                                                              |

|           | InAlAs barrier layer. (b) Zoomed-in view of the device channel                                                               |

|           | region. The Ni-InGaAs contacts are formed on $\boldsymbol{n}^{\!\!+}$ InGaAs and                                             |

|           | aligned to the TaN gate. The n <sup>+</sup> InGaAs recess region defines the                                                 |

|           |                                                                                                                              |

|            | device channel. The InGaAs fin is oriented in the horizontal                                          |

|------------|-------------------------------------------------------------------------------------------------------|

|            | direction. The cross-section views along A - A' and B - B' are                                        |

|            | shown in Fig. 4.10 and Fig. 4.11, respectively                                                        |

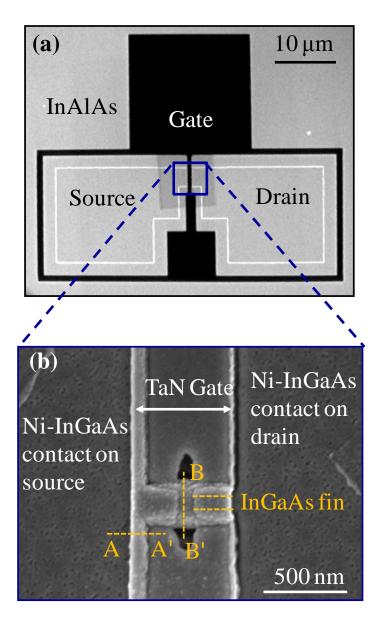

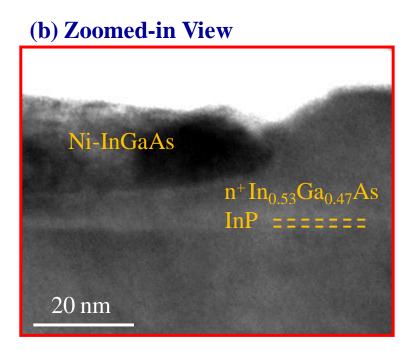

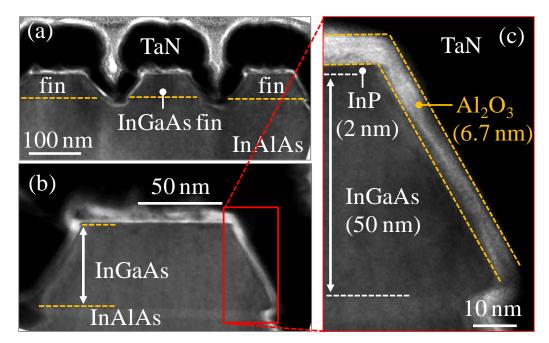

| Fig. 4.10. | (a) TEM image shows the device cross-section along A - A' in                                          |

|            | Fig. 4.9(b). Ni-InGaAs contact was uniformly formed on $n^+$                                          |

|            | InGaAs and well aligned to the TaN gate. (b) Zoomed-in view of                                        |

|            | the rectangular region shows that the Ni-InGaAs layer has clear                                       |

|            | interface and shows good contrast with respect to n <sup>+</sup> InGaAs112                            |

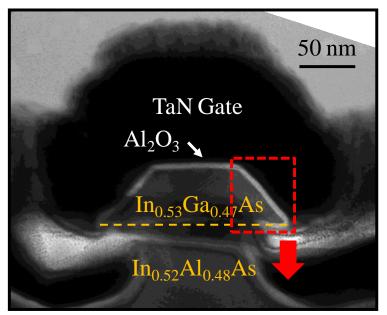

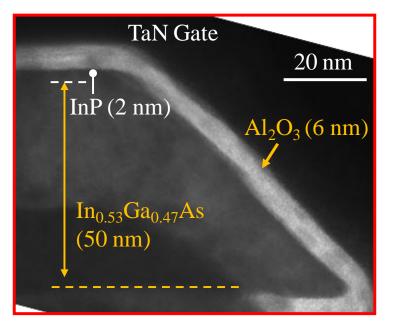

| Fig. 4.11. | (a) TEM shows the device cross-section along dashed line B - B'                                       |

|            | in Fig. 4.9(b). The InGaAs fin is in the shape of a trapezoid.                                        |

|            | Undercutting of the InAlAs layer beneath the InGaAs fin is                                            |

|            | observed due to the $C_6H_8O_7/H_2O_2$ dip after InGaAs fin etch [4.22].                              |

|            | (b) Zoomed-in view of the InGaAs fin sidewalls, showing that the                                      |

|            | $Al_2O_3$ and TaN were uniformly deposited on the top and                                             |

|            | sidewalls of the fin. The $Al_2O_3$ has a thickness of ~ 6 nm113                                      |

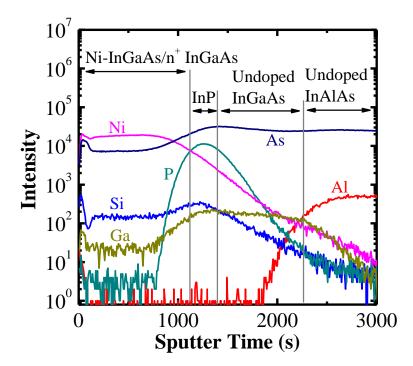

| Fig. 4.12. | SIMS profile shows the distribution of elements such as Ni, Si,                                       |

|            | Ga, As, Al, and P in the S/D regions. A uniform Ni-InGaAs layer                                       |

|            | on $n^+$ InGaAs was observed. The vertical gray lines are the                                         |

|            | estimated positions of materials interfaces                                                           |

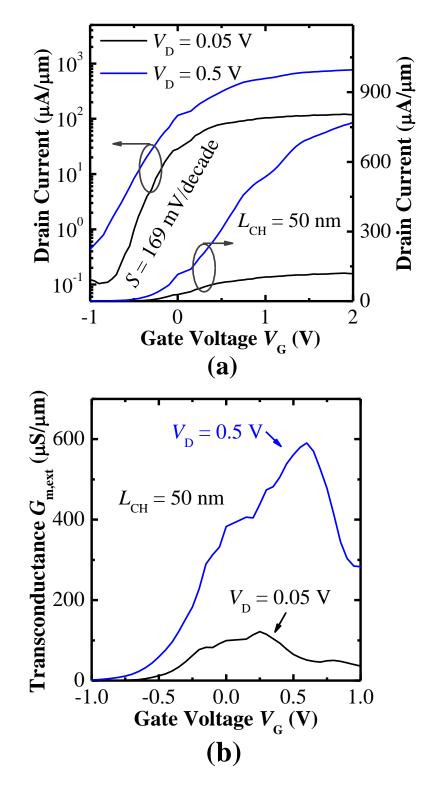

| Fig. 4.13. | (a) $I_{\rm D}$ - $V_{\rm G}$ curves of an InGaAs FinFET with channel length $L_{\rm CH}$             |

|            | of 50 nm. The device shows good transfer characteristics with                                         |

|            | subthreshold swing S of 169 mV/decade and on-state/off-state                                          |

|            | drain current ratio of ~10 <sup>3</sup> . (b) $G_{m,ext} - V_G$ of the device shows a                 |

|            | peak $G_{\rm m,ext}$ of 590 $\mu$ S/ $\mu$ m at $V_{\rm D}$ of 0.5 V                                  |

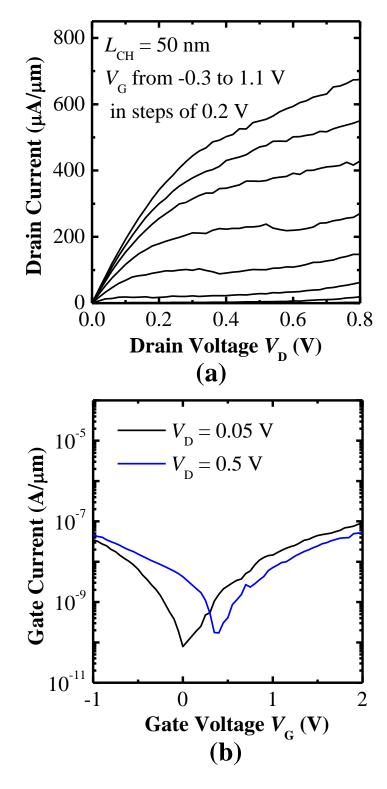

| Fig. 4.14. | (a) $I_D - V_D$ curves of the same device in Fig. 4.13 show good                                      |

|            | output characteristics. Drive current of 411 $\mu$ A/ $\mu$ m was obtained                            |

|            | at $V_{\rm D}$ of 0.7 V and $V_{\rm G}$ of 0.7 V. (b) $I_{\rm G}$ - $V_{\rm G}$ of the device shows   |

|            | low gate leakage current below the level of $1 \times 10^{-7}$ A/µm116                                |

| Fig. 4.15. | $R_{\rm T}$ in the linear regime ( $V_{\rm D} = 0.05$ V) as a function of $V_{\rm G}$ . $R_{\rm T} =$ |

|            | $V_{\rm D}/I_{\rm Dlin}$ , where $I_{\rm Dlin}$ is the drain current in linear regime. The solid      |

|            | curve is given by Equation (4.3), and was used to fit the data                                        |

|            |                                                                                                       |

|            | points (circles). The fitted curve was extrapolated to $V_{\rm G} = 5$ V to                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

|            | obtain <i>R</i> <sub>SD</sub> 117                                                                                |

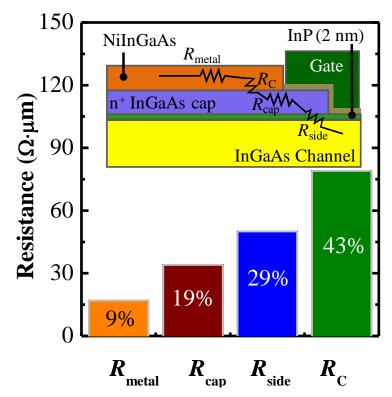

| Fig. 4.16. | Estimated resistance components of the source resistance $R_{\rm S}$ ( $R_{\rm SD}$                              |

|            | = $2R_{\rm S} = 2R_{\rm D} = 364 \ \Omega \cdot \mu m$ ). $R_{\rm C}$ and $R_{\rm side}$ are the dominant source |

|            | resistance in this self-aligned FinFET structure. The percentages                                                |

|            | shown are the percentage contributions of the various                                                            |

|            | components to $R_{\rm S}$                                                                                        |

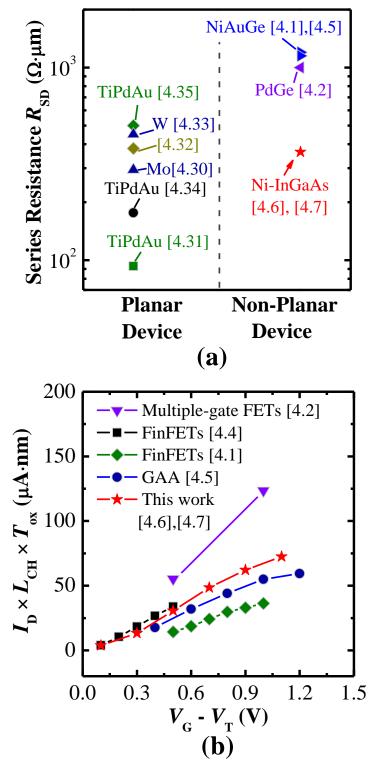

| Fig. 4.17. | (a) Much lower $R_{SD}$ was obtained in this Chapter as compared                                                 |

|            | with other reported $R_{SD}$ for InGaAs non-planar devices with non-                                             |

|            | self-aligned contacts. (b) Plot of $I_{\rm D} \times L_{\rm CH} \times T_{\rm ox}$ versus overdrive              |

|            | $V_{\rm G}$ - $V_{\rm T}$ for InGaAs non-planar n-MOSFETs reported in the                                        |

|            | literature and in this Chapter121                                                                                |

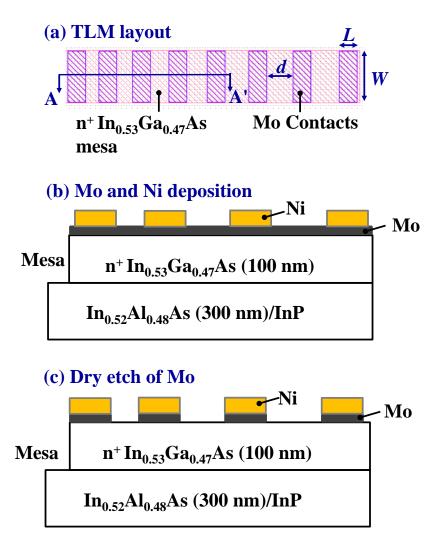

| Fig. 5.1.  | (a) Layout of TLM test structure. $L$ , $W$ , $d$ are contact length,                                            |

|            | width and spacing, respectively. (b) Cross-section of the TLM                                                    |

|            | structure along A-A'. Blanket Mo film was sputtered on the                                                       |

|            | substrate, followed by deposition of Ni pads (300 nm) using a                                                    |

|            | lift-off process. (c) Mo layer was etched in Cl <sub>2</sub> -based plasma                                       |

|            | using Ni as an etch mask. Finally, $n^+$ InGaAs mesa was formed                                                  |

|            | by wet etch in citric acid based solution135                                                                     |

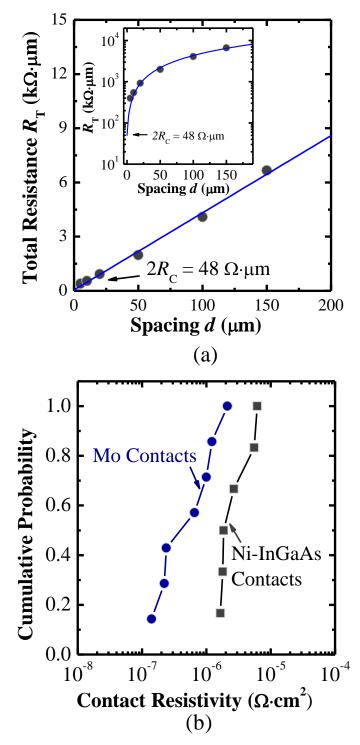

| Fig. 5.2.  | (a) Total resistance $R_{\rm T}$ versus contact spacing d of a TLM. Mo                                           |

|            | contact shows low $R_{\rm C}$ of ~24 $\Omega$ ·µm on n <sup>+</sup> InGaAs. The inset                            |

|            | shows $R_{\rm T}$ versus d in logarithm scale. (b) Statistical plot shows                                        |

|            | the distribution of $ ho_{ m C}$ for Mo and Ni-InGaAs contacts on $n^+$                                          |

|            | InGaAs. Mo contact has a $\rho_{\rm C} \sim 10$ times lower than that of Ni-                                     |

|            | InGaAs137                                                                                                        |

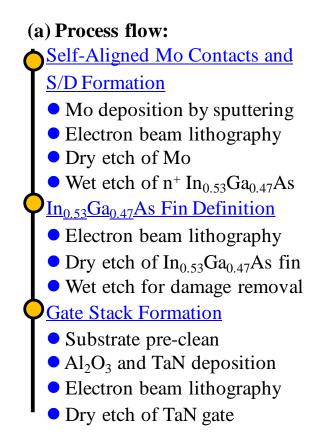

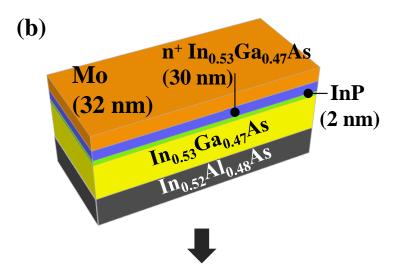

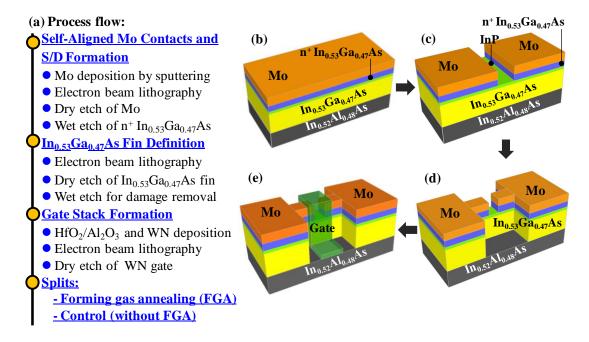

| Fig. 5.3.  | (a) Process flow for fabrication of a novel InGaAs FinFET with                                                   |

|            | Mo contacts self-aligned to channel. The key steps include (b)                                                   |

|            | blanket deposition of Mo, (c) dry etch of Mo and wet etch of $n^+$                                               |

|            | InGaAs, (d) dry etch of InGaAs fin, and (e) gate stack formation 140                                             |

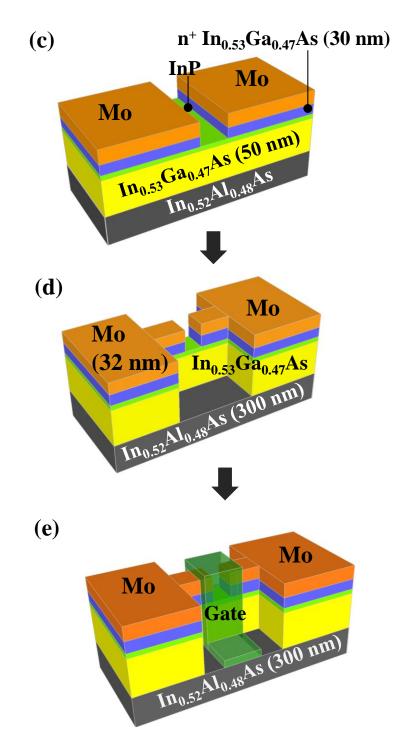

| Fig. 5.4.  | (a) SEM shows layout of an InGaAs FinFET with Mo contacts on                                                     |

|            | $n^+$ InGaAs S/D. The dimension of S/D big pads is about 15 $\mu m$                                              |

|            | $\times 15 \ \mu m.$ (b) A zoomed-in view shows the device channel region.                                    |

|------------|---------------------------------------------------------------------------------------------------------------|

|            | The width of recessed $n^+$ InGaAs defines $L_{CH}$ of the device                                             |

| Fig. 5.5.  | (a) Cross-section of an InGaAs FinFET across the fins [A - A' in                                              |

|            | Fig. 5.4(b)]. InGaAs fins sitting on InAlAs layer were observed.                                              |

|            | (b) Zoomed-in view of an InGaAs fin shows the fin structure and                                               |

|            | dimension. (c) Zoomed-in view of the rectangular region                                                       |

|            | indicates the conformally formed gate stack on the top and                                                    |

|            | sidewalls of the InGaAs fin142                                                                                |

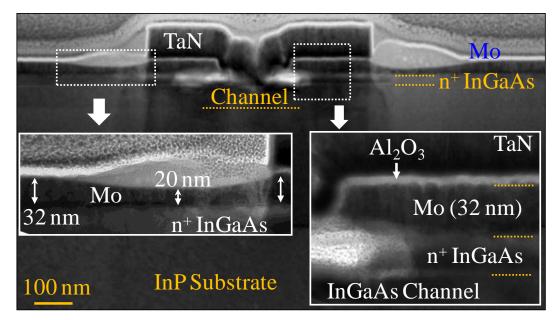

| Fig. 5.6.  | TEM images show the device cross-section along the fin [B - B'                                                |

|            | in Fig. 5.4(b)]. Mo contacts were observed on the surface of $n^+$                                            |

|            | InGaAs S/D and aligned to InGaAs channel. The zoomed-in                                                       |

|            | views of the S/D regions are shown by the insets142                                                           |

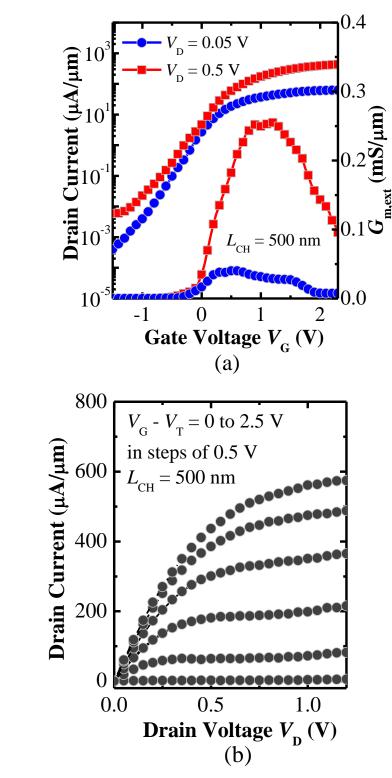

| Fig. 5.7.  | (a) $I_D - V_G$ and $G_{m,ext} - V_G$ of a single-fin InGaAs FinFET with $L_{CH}$                             |

|            | = 500 nm and $W_{\text{fin}}$ = 90 nm, showing $I_{\text{ON}}/I_{\text{OFF}}$ of over 10 <sup>5</sup> . Drain |

|            | voltage $V_{\rm D}$ of 0.05 and 0.5 V were applied. (b) $I_{\rm D}-V_{\rm D}$                                 |

|            | characteristics of the same device showing good saturation and                                                |

|            | pinch-off characteristics144                                                                                  |

| Fig. 5.8.  | (a) $J_{\rm G}$ as a function of $V_{\rm G}$ showing low gate leakage current                                 |

|            | density below $1 \times 10^{-2}$ A/cm <sup>2</sup> . (b) Peak $G_{m,ext}$ of FinFETs with                     |

|            | different $L_{CH}$ ( $W_{fin} = 90$ nm). The applied drain voltage is 0.5 V 146                               |

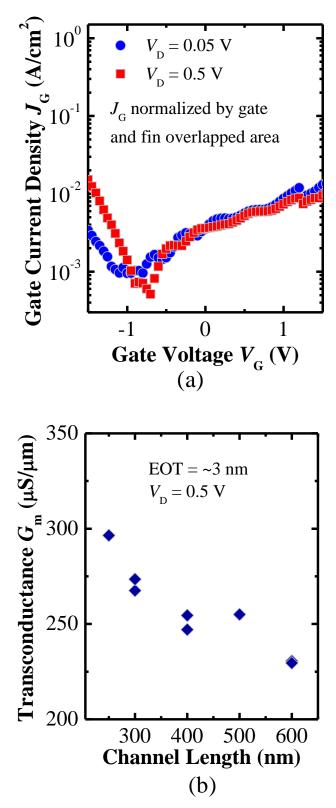

| Fig. 5.9.  | (a) $R_{\rm T}$ - $L_{\rm As-printed}$ of InGaAs FinFETs. $R_{\rm T}$ was obtained at a                       |

|            | specified $V_{\rm G}$ - $V_{\rm T}$ in the linear regime ( $V_{\rm D} = 0.05$ V). $R_{\rm SD}$ was            |

|            | extracted from the intersection of the fitted lines. (b) The plot                                             |

|            | indicates the estimated component elements ( $R_{\rm C}$ , $R_{\rm metal}$ , $R_{\rm side}$ ) of              |

|            | $R_{\rm S}$ . The percentages shown are the percentage contributions of                                       |

|            | the various components to $R_{\rm S}$                                                                         |

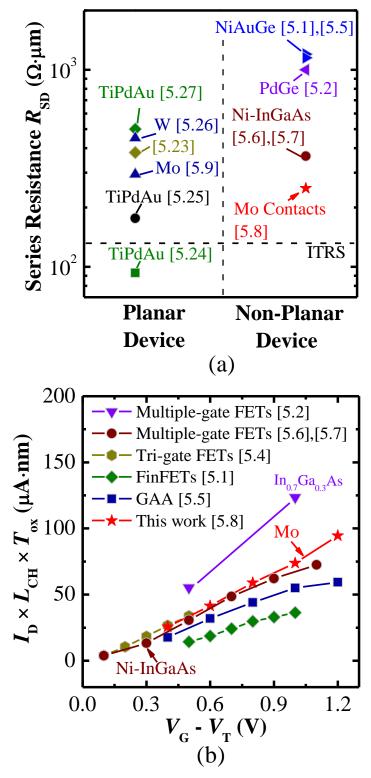

| Fig. 5.10. | (a) Lowest $R_{SD}$ of 250 $\Omega$ ·µm is obtained in this Chapter as                                        |

|            | compared with reported InGaAs non-planar devices with non-                                                    |

|            | self-aligned or self-aligned contacts. (b) Drive current                                                      |

|            | benchmarking by plotting $I_D \times L_{CH} \times T_{ox}$ versus $V_G - V_T$ of InGaAs                       |

|            |                                                                                                               |

### List of Symbols

| Symbol                           | Description                                                                        | Unit                              |  |

|----------------------------------|------------------------------------------------------------------------------------|-----------------------------------|--|

| $A^{*}$                          | Richardson constant                                                                | Acm <sup>-2</sup> K <sup>-2</sup> |  |

| $C_d$                            | Depletion capacitance                                                              | F                                 |  |

| $C_{\mathrm{ox}}$                | Gate oxide capacitance                                                             | F                                 |  |

| d                                | Contact spacing                                                                    | μm                                |  |

| $D_{ m sp}$                      | Spacing between probe and channel                                                  | μm                                |  |

| $D_{\mathrm{IT}}$                | Interface state density                                                            | $cm^{-2}eV^{-1}$                  |  |

| $D_{\rm n}$                      | Diffusion coefficient for electron                                                 | cm <sup>2</sup> s <sup>-1</sup>   |  |

| $D_{ m p}$                       | Diffusion coefficient for hole                                                     | cm <sup>2</sup> s <sup>-1</sup>   |  |

| $E_{ m F}$                       | Fermi level                                                                        | eV                                |  |

| $E_{\rm C}$                      | Conduction band edge                                                               | eV                                |  |

| $E_{ m V}$                       | Valence band edge                                                                  | eV                                |  |

| $G_{ m d}$                       | Drain conductance                                                                  | S                                 |  |

| $G_{\mathrm{m,ext}}$             | Extrinsic transconductance                                                         | S                                 |  |

| $G_{ m m,int}$                   | Intrinsic transconductance                                                         | S                                 |  |

| h                                | Planck's constant                                                                  | eVs                               |  |

| I <sub>D</sub>                   | Drive current (per unit width)                                                     | $\mu A/\mu m$                     |  |

| <i>I</i> <sub>Dlin</sub>         | Linear drain current (per unit width)                                              | $\mu A/\mu m$                     |  |

| $I_{ m G}$                       | Gate current (per unit width)                                                      | A/µm                              |  |

| I <sub>ON</sub>                  | On state current (per unit width)                                                  | μA/μm                             |  |

| $I_{ m OFF}$<br>$J_{S,Schottky}$ | Off state current (per unit width)<br>Reverse current density of Schottky<br>diode | A/μm<br>A/cm <sup>2</sup>         |  |

| $J_{S,PN}$                       | Reverse current density of PN diode                                                | A/cm <sup>2</sup>                 |  |

| $J_{ m G}$                       | Gate leakage current density                                                       | A/cm <sup>2</sup>                 |  |

| k                                | Boltzman's constant                                                                | eV/K                              |  |

| L                                | Contact length                                                                     | μm                                |  |

| $L_{ m G}$                       | Gate length                                                                        | nm                                |  |

| $L_{\mathrm{T}}$                 | Transfer length                                                                    | μm                                |  |

| $L_{\rm CH}$                     | Channel Length                                                                     | nm                                |  |

| $L_{\text{As-print}}$            | As-printed channel Length                                                          | nm                                |  |

| $L_{\rm SD}$                     | Spacing between contact and channel                                                | μm                                |  |

| Loverlap                         | Gate-to-source overlap length                                                      | nm                                |  |

| L <sub>n</sub>                   | Electron diffusion length                                                          | m                                 |  |

| $L_{\rm p}$                | Hole diffusion length            | m                 |  |  |

|----------------------------|----------------------------------|-------------------|--|--|

| $m_n^*$                    | Effective mass                   | kg                |  |  |

| $n_{ m po}$                | Minority electron concentration  | cm <sup>-3</sup>  |  |  |

| $N_{\rm A}$                | Hole concentration               | cm <sup>-3</sup>  |  |  |

| $N_{\rm D}$                | Electron concentration           | cm <sup>-3</sup>  |  |  |

| $p_{ m no}$                | Minority hole concentration      | cm <sup>-3</sup>  |  |  |

| q                          | Electronic charge                | С                 |  |  |

| $Q_f$                      | Fixed charge density             | C/cm <sup>2</sup> |  |  |

| $R_{\rm C}$                | Contact resistance               | Ω·μm              |  |  |

| R <sub>CH</sub>            | Channel resistance               | Ω·μm              |  |  |

| R <sub>S</sub>             | Source resistance                | Ω·μm              |  |  |

| $R_{\rm cap}$              | InGaAs cap resistance            | Ω·μm              |  |  |

| $R_{\rm D}$                | Drain resistance                 | Ω·μm              |  |  |

| $R_{\rm SD}$               | Source/drain series resistance   | Ω·μm              |  |  |

| <b>R</b> <sub>metal</sub>  | Metal resistance                 | Ω·μm              |  |  |

| $R_{\rm sh}$               | Sheet resistance                 | Ω/square          |  |  |

| R <sub>sh,InGaAs</sub>     | InGaAs sheet resistance          | $\Omega$ /square  |  |  |

| $R_{\rm III-V}$            | III-V resistance                 | Ω·μm              |  |  |

| R <sub>Ni-InGaAs</sub>     | Ni-InGaAs resistance             | Ω                 |  |  |

| R <sub>Ni-InGaAs</sub>     | Ni-InGaAs resistance             | Ω·μm              |  |  |

| R <sub>side</sub>          | Barrier and spreading resistance | Ω·μm              |  |  |

| $R_{\mathrm{T}}$           | Total resistance                 | Ω·μm              |  |  |

| S                          | Subthreshold swing               | mV/decade         |  |  |

| t <sub>Ni-InGaAs</sub>     | Ni-InGaAs thickness              | nm                |  |  |

| Т                          | Temperature                      | $^{\circ}$ C      |  |  |

| T <sub>d</sub>             | Desorption Temperature           | $^{\circ}$ C      |  |  |

| T <sub>InGaAs</sub>        | InGaAs step height               | nm                |  |  |

| $T_{\rm mask}$             | SiO <sub>2</sub> mask thickness  | nm                |  |  |

| $T_{\rm total}$            | Total step height                | nm                |  |  |

| $T_{\rm Mo}$               | Mo thickness                     | nm                |  |  |

| $T_{\rm ox}$               | Equivalent oxide thickness       | nm                |  |  |

| $V_{\mathrm{FB}}$          | Flatband voltage                 | V                 |  |  |

| $V_{ m G}$                 | Gate voltage                     | V                 |  |  |

| $V_{\rm T}$ or $V_{\rm T}$ | Threshold voltage                | V                 |  |  |

|                            |                                  |                   |  |  |

| $\Delta V_{ m T}$          | Threshold voltage shift                                  | V                                               |

|----------------------------|----------------------------------------------------------|-------------------------------------------------|

| W                          | Contact width                                            | μm                                              |

| W <sub>eff</sub>           | Channel width                                            | μm                                              |

| $W_{ m fin}$               | Fin width                                                | nm                                              |

| $W_{\rm top}$              | Fin top channel width                                    | nm                                              |

| W <sub>side</sub>          | Fin sidewall width                                       | nm                                              |

| $ ho_{ m C}$               | Specific contact resistivity                             | $\Omega \cdot cm^2$                             |

| $ ho_{ m III-V}$           | III-V resistivity                                        | μΩ·cm                                           |

| $ ho_{ m Ni-InGaAs}$       | Ni-InGaAs resistivity                                    | μΩ·cm                                           |

| $ ho_{ m Mo}$              | Mo resistivity                                           | μΩ·cm                                           |

| $\mu_{ m eff}$             | Effective mobility                                       | $cm^2 V^{-1}s^{-1}$                             |

| $\mu_{ m e}$               | Electron mobility                                        | $cm^2 V^{-1}s^{-1}$                             |

| $\mu_{ m h}$               | Hole mobility                                            | $\mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$ |

| $\phi_{ m S}$              | Surface potential                                        | eV                                              |

| $\phi_{ m Bn}$             | Schottky barrier height                                  | eV                                              |

| $\Phi_{ m MS}$             | Work function difference between metal and semicondcutor | eV                                              |

| $\mathcal{E}_{\mathrm{S}}$ | Permittivity                                             | F/m                                             |

## **Chapter 1**

## Introduction

#### **1.1** Silicon Transistor Scaling: Benefits and Challenges

The success of complementary metal-oxide-semiconductor (CMOS) technology is due to its scalability, which has enabled the number of transistors on integrated circuit (IC) chips to be increased exponentially during the past four decades [1.1],[1.2]. Continued scaling of the transistor dimension is required in order to achieve significantly higher packing density per unit chip area, reduction of cost per function, and improvement in circuit speed performance. A 45 nm process technology based on high-k, metal gate, and strained Silicon (Si) was introduced in 2007 [1.3]. Scaling of this technology continued to the 32 nm technology node in 2009 [1.4]. In the year of 2011, FinFET structure was also introduced to enable the scaling further down to the 22 nm technology node [1.5].

As transistors are aggressively scaled in accordance with Moore's law to sub-20 nm dimensions, it becomes increasingly difficult to maintain the required device performance. Currently, the increase in drive current for faster switching speed at lower supply voltage is largely at the expense of an exponentially growing leakage current, which leads to a large standby power dissipation [1.1]. If we look forward to the sub-10 nm node and beyond, the transistors are in the order of a few atoms across and continued shrinking of physical feature size will be imposed by fundamental limits of Si properties. Therefore, there is an important need to explore novel channel materials and device structures that would provide us with equivalent scaling for CMOS.

#### **1.2 High Electron Mobility of III-V Materials**

To address the scaling challenges, both industry and academia have been investigating alternative materials and device architectures, among which III-V compound semiconductors stand out as promising candidates for future logic applications. This is because their light electron effective mass lead to high electron mobility and high on-current, which would translate into high device performance at low supply voltage. As seen in Table 1.1, III-V compound semiconductors have significantly smaller electron effective mass and higher electron mobility compared to Si [1.7].

|                                               | Si   | Ge    | GaAs  | In <sub>0.53</sub> Ga <sub>0.47</sub> As | InAs  | InSb  |

|-----------------------------------------------|------|-------|-------|------------------------------------------|-------|-------|

| Electron mobility<br>(cm <sup>2</sup> /Vs)    | 1350 | 3900  | 8500  | 14000                                    | 33000 | 77000 |

| Hole mobility<br>(cm <sup>2</sup> /Vs)        | 460  | 1900  | 400   | 400                                      | 460   | 850   |

| Electron effective<br>mass (/m <sub>0</sub> ) | 0.19 | 0.082 | 0.067 | 0.05                                     | 0.027 | 0.013 |

| Bandgap<br>(eV)                               | 1.12 | 0.66  | 1.42  | 0.74                                     | 0.36  | 0.17  |

| Permitivity                                   | 11.8 | 16    | 12.4  | 13.9                                     | 14.8  | 17.7  |

Table 1.1. Carrier mobility, effective mass, bandgap and permittivity of some commonly used semiconductors [1.7].

#### 1.3 Challenges of III-V CMOS Technology

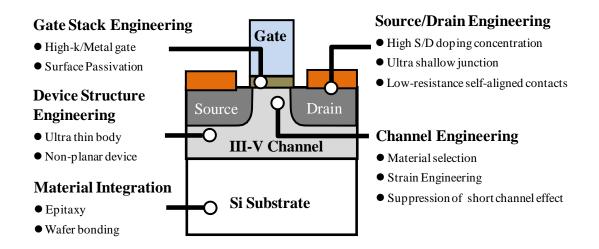

III-V compound semiconductors have been heavily researched since they have been widely used in communications and optoelectronics industries. There are still a lot of challenges to be overcome before III-V logic transistors manufacturing becomes viable [1.7]. The intrinsic properties of III-V materials may add to the challenge of successful device realization. The success of III-V in potential CMOS technology will mainly depend on: 1) heterogeneous integration of III-V on Si in a cost-effective way, 2) formation of low leakage and thermally stable gate dielectric with low interface state density, 3) realization of low-resistance source and drain, and 4) p-channel materials with reasonably high hole mobility. These technical challenges are illustrated in Fig. 1.1, discussed and summarized in the following Sections.

**Fig. 1.1.** Schematic illustration of the key technical challenges faced in the realization and integration of high mobility III-V CMOS on Si substrates for future logic applications.

#### 1.3.1 Formation of High-Quality Gate Dielectric

Native oxide surface of III-V, for instance GaAs, consists of several oxides such as  $As_2O_3$ ,  $As_2O_5$ ,  $Ga_2O_3$ ,  $Ga_2O_5$ , and  $Ga_2O$  [1.8],[1.9]. Unlike SiO<sub>2</sub> on Si, the native oxides of GaAs have very poor electrical properties and result in Fermi-level pinning and high interface state density ( $D_{TT}$ ) [1.10].

Deposition of gate dielectric on III-V is being studied using various *in-situ* and *ex-situ* deposition methods. Passivation techniques such as *in-situ* molecular beam epitaxy (MBE) growth of gallium-gadolinium oxide (GGO) [1.11], metal organic chemical vapor deposition (MOCVD) of HfAlO and HfO<sub>2</sub> with SiH<sub>4</sub>, NH<sub>3</sub>, or PH<sub>3</sub> plasma treatment [1.12],[1.13], atomic layer deposition (ALD) of Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, (La)AlO<sub>x</sub>/ZrO<sub>2</sub>, and TaSiO<sub>x</sub> [1.14]-[1.21] employing Si, or InP capping layer [1.22]-[1.25] have been developed to reduce interface trap density and to unpin the III-V interfaces. However, the reported  $D_{TT}$  values on various MOS devices are still higher than  $1 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> [1.7]. Further reduction of  $D_{TT}$  is still needed. In addition, thermally stable high-*k* dielectric is highly desirable to ensure that it remains high quality after subsequent thermal process steps such as S/D dopant activation anneal (600 - 800 °C).

#### 1.3.2 III-V Integration on Si Substrates

Bulk III-V substrates are costly, brittle, and difficult to make in large wafer sizes. Direct epitaxial growth of III-V materials on Si substrates is desirable for heterogeneous integration with Si CMOS technology. However, this poses serious challenges due to the large mismatch in lattice constant (e.g. 8% between  $In_{0.53}Ga_{0.47}As$  and Si), large mismatch in coefficient of thermal expansion, and the generation of polar/non-polar interfaces between III-V and Si. These challenges are being addressed by the use of III-V buffer layer growth, either on blanket or on patterned Si wafers, which reduces the number of defects reaching the active device layers [1.26]-[1.29].

Direct wafer bonding can be regarded as another promising technology to integrate III-V materials on Si, since the transfer of III-V semiconductor optical devices to Si wafers has been reported [1.7]. High quality III-V on insulator (III-V-OI) on Si was demonstrated recently using an electron-cyclotron-resonance (ECR) oxygen plasma-assisted direct wafer bonding process [1.30],[1.31]. Such III-V-OI substrates can provide process advantages for realizing new device structures such as III-V ultrathin body devices, FinFETs, and nanowire MOSFETs. However, the bonding of InGaAs on Si substrates is at the cost of sacrificing InP substrates [1.31] which are also costly. A cost-effective integration technology is still desired.

#### 1.3.3 Channel Material Engineering

In general, III-V materials have significantly smaller bandgap compared to Si (Table 1.1). Due to the small bandgap in these high mobility materials, the band-toband tunneling leakage current can become excessive and can ultimately limit the scalability of III-V MOSFETs. Therefore, ternary compound semiconductors such as InGaAs have received much attention due to their tunable and moderate bandgap. Another point to note is that most III-V materials suffer from low hole mobility (Table. 1.1), although GaSb and InGaSb offer slightly higher hole mobility [1.32]. There is lack of p-channel materials with reasonably good carrier transport properties and there is a need to explore new III-V channel materials for p-MOSFETs.

#### 1.3.4 New Device Structure Engineering

FinFET structure has been introduced for Si CMOS at the 22 nm technology node and would probably be extended to sub-20 nm technology nodes [1.5]. FinFET structure could provide improved short-channel effects (SCEs) control, enhanced volume inversion in the channel region, lower leakage current, and reduced device variability arising from random dopant fluctuation if low channel doping concentration is used. III-V FinFETs have been widely researched since the first III-V FinFET was experimentally demonstrated in 2009 [1.33]. III-V FinFETs are more scalable than III-V planar n-MOSFETs [1.33]-[1.39]. It is highly possible that III-V transistors will be used in the form of FinFETs in sub-10 nm nodes [1.1].

#### 1.3.5 Source/Drain Resistance Engineering

#### A. Concept of Source/Drain Resistance Engineering

The drive current of a transistor is determined by device total resistance ( $R_T$ ), which is the combination of transistor channel resistance ( $R_{CH}$ ) and source/drain (S/D) series resistance ( $R_{SD}$ ). To achieve high drive current, small  $R_T$  is desired and  $R_T$  can be express as:

$$R_{\rm T} = R_{\rm CH} + R_{\rm SD} \,. \tag{1.1}$$

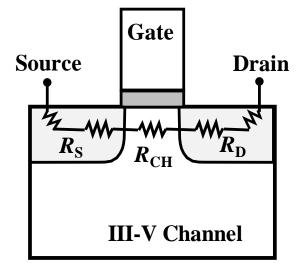

Schematic of a transistor in Fig. 1.2 shows the  $R_{\rm T}$  between source and drain terminals is the summation of  $R_{\rm CH}$ , source resistance ( $R_{\rm S}$ ), and drain resistance ( $R_{\rm D}$ ), where  $R_{\rm SD}$ =  $R_{\rm S} + R_{\rm D}$ .  $R_{\rm SD}$  will dominate  $R_{\rm T}$  of a transistor if  $R_{\rm CH}$  dramatically reduces with channel length scaling and channel mobility enhancement [1.40].  $R_{\rm SD}$  is projected to be comparable to  $R_{\rm CH}$  at the 22 nm technology node and this implies that device performance would ultimately be limited by  $R_{\rm SD}$  [1.41] beyond 22 nm technology node.

**Fig. 1.2.** Schematic of a transistor biased in the linear region, showing that total resistance  $R_{\rm T}$  between source and drain terminals includes channel resistance  $R_{\rm CH}$ , source resistance  $R_{\rm S}$  and drain resistance  $R_{\rm D}$ .

#### **B.** Components of Transistor Source/Drain Resistance

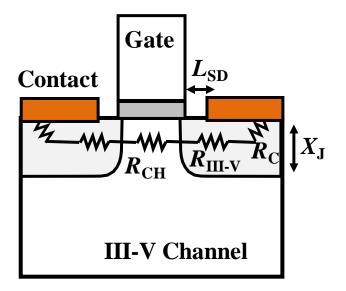

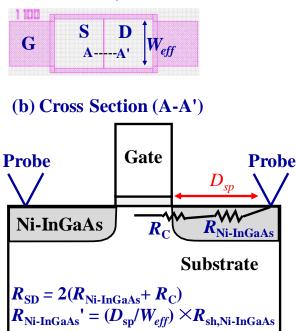

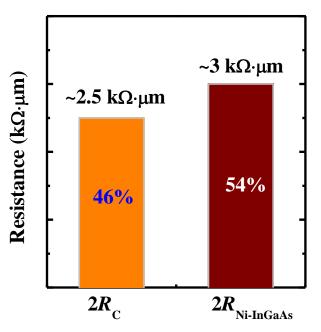

As illustrated in Fig. 1.3, the  $R_{SD}$  of a conventional III-V transistor can be mainly divided into two separate resistance components: 1) resistance of doped III-V S/D ( $R_{III-V}$ ), and 2) contact resistance ( $R_C$ ) between metal contact and III-V semiconductors. Assuming an ideal box-like doping profile, the resistance of the doped III-V S/D can be expressed as [1.42]:

$$R_{III-V} = \frac{\rho_{III-V} L_{SD}}{W_{eff} X_{J}},$$

(1.2)

and

$$\rho_{III-V} = \frac{1}{N_A q \mu_h + N_D q \mu_e} \approx \frac{1}{N_D q \mu_e}, \qquad (1.3)$$

where  $\rho_{\text{III-V}}$  is the resistivity of doped III-V S/D,  $L_{\text{SD}}$  is separation between S/D contacts and channel,  $W_{eff}$  is device width,  $X_{\text{J}}$  is S/D junction depth,  $N_{\text{D}}$  and  $N_{\text{A}}$  are electron and hole carrier concentration, respectively,  $\mu_{\text{e}}$  and  $\mu_{\text{h}}$  are electron and hole carrier mobility, respectively. It is noticed that  $R_{\text{III-V}}$  is strongly dependent on  $W_{\text{eff}}$ ,  $X_{\text{J}}$ ,  $L_{\text{SD}}$  and  $N_{\text{D}}$  (or  $N_{\text{A}}$ ).

**Fig. 1.3**. Schematic of a conventional III-V transistor showing various resistance components that contribute to device  $R_{SD}$ , where  $R_{SD} = 2(R_C + R_{III-V})$ .

$R_{\rm C}$  depends on the specific contact resistivity ( $\rho_{\rm C}$ ), the sheet resistance of semiconductor ( $R_{\rm sh}$ ), the width  $W_{eff}$ , length (L) of the contact hole, and transfer length ( $L_{\rm T}$ ).  $R_{\rm C}$  is given by [1.43]:

$$R_{C} = \frac{\sqrt{\rho_{C}R_{sh}}}{W_{eff}} \operatorname{coth}(\frac{L}{L_{T}}).$$

(1.4)

For a metal-semiconductor junction with a high impurity doping concentration, the tunneling process will dominate and  $\rho_{\rm C}$  is found to be [1.43]:

$$\rho_{c} \sim \exp\left[\frac{4\pi\sqrt{\varepsilon_{s}m_{n}^{*}}}{h}\frac{\phi_{Bn}}{\sqrt{N_{D}}}\right], \qquad (1.5)$$

where  $\pi$  is the ratio of a circle's circumference to its diameter,  $\varepsilon_s$  is permittivity of a semiconductor,  $m_n^*$  is effective mass,  $\phi_{Bn}$  is the schottky barrier height, *h* is Planck's constant, and  $N_D$  is semiconductor doping concentration. It is obvious that  $R_C$  is a strong function of  $N_D$ .

In summary,  $R_{\text{III-V}}$  and  $R_{\text{C}}$  are the two primary S/D resistance components of a typical III-V transistor and are strongly dependent on  $W_{\text{eff}}$ ,  $X_{\text{J}}$ ,  $N_{\text{D}}$  and  $L_{\text{SD}}$ . A small  $X_{\text{J}}$  is preferred to alleviate SCEs. In a FinFET,  $W_{\text{eff}}$  should also be kept small in order to achieve good control of SCEs. Small  $X_{\text{J}}$  and  $W_{\text{eff}}$  would lead to high  $R_{\text{III-V}}$  and  $R_{\text{C}}$ . Therefore, engineering the other parameters such as  $N_{\text{D}}$  and  $L_{\text{SD}}$  becomes important. Increased  $N_{\text{D}}$  and reduced  $L_{\text{SD}}$  could help reduce  $R_{\text{III-V}}$  as well as  $R_{\text{C}}$ , and thus reduce S/D series resistance.

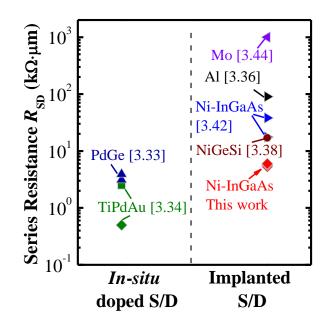

#### C. State-of-Art III-V n-MOSEFTs Contact Technology

High mobility III-V n-MOSFETs require the shallow (small  $X_1$ ), abrupt and highly doped (large  $N_{\rm D}$ ) n<sup>+</sup> source/drain. Si is widely used as the n-type dopant in III–V materials because of its negligible diffusivity which allows the realization of very abrupt junctions [1.44]. However, the maximum n-type carrier concentration in III-V materials, for instance InGaAs, with Si as dopants can only reach  $\sim 7 \times 10^{18}$  cm<sup>-3</sup> by direct Si implantation due to the low solid solubility limitation [1.45]. This doping level is far from the state-of-art doping concentration (in the order of  $10^{21}$  cm<sup>-3</sup>) achieved for Si. To obtain an active doping concentration over  $5 \times 10^{18}$  cm<sup>-3</sup> in InGaAs, an activation anneal temperature of  $\sim 700 \ ^{\circ}$  C is required [1.45]. However, in certain device processing schemes a limited thermal budget is imposed. As an example, in a gate-first processing flow, the thermal stability of the gate stack limits the maximum activation anneal temperature. It becomes obvious that III-V transistors will suffer more from  $R_{SD}$  as compared with Si transistors since low  $N_D$ would result in high  $R_{SD}$ . In-situ doping is required to boost the S/D doping level to reduce *R*<sub>SD</sub> [1.46],[1.47].

Gold-based contact materials such as TiPtAu and NiAuGe [1.12],[1.30], [1.33],[1.37],[1.48], [1.49] are commonly used for III-V MOSFETs. However, gold is a contaminant in Si CMOS technology and it may not be used for integration of III-V transistors in a Si CMOS process. Therefore, development of new contact materials which are low-resistance and CMOS compatible is highly desirable.

Unlike nickel salicide in Si CMOS process which is integrated based on a self-aligned technology [1.50], S/D contacts for III-V MOSFETs are non-self-aligned

and usually formed by direct deposition and patterning of metals using a lift-off process [1.12],[1.30],[1.33],[1.37],[1.48],[1.49]. Large spacing  $L_{SD}$  between the S/D contacts and the transistor channel is introduced and this gives a high  $R_{III-V}$  resulting from the sheet resistance of III-V S/D [Equation (1.2)].  $R_{III-V}$  would contribute a significant portion to  $R_{SD}$  considering the high  $\rho_{III-V}$  of III-V S/D due to the low  $N_D$ . Solutions to minimize this contribution will be even more crucial for the adoption of III-V FinFETs in the future technology generations. This is because device operation in a FinFET relies on the use of narrow fins (small  $W_{eff}$ ) to control SCEs and the narrow fins would result in increased  $R_{III-V}$  [Equation (1.2)]. The metallization of these narrow fins to maintain low sheet resistance at the S/D regions will be crucial for resistance reduction. Therefore, self-aligned S/D contacts which are adjacent to the gate stack could generate high conductivity path for local wiring and are desired to drastically reduce  $R_{SD}$ . A self-aligned contact technology would also reduce  $L_{SD}$ and provide better scalability for transistor footprint.

For the widespread adoption of the III-V MOSFETs in future CMOS technology generations, innovative S/D contact solutions for III-V planar MOSFETs or FinFETs must be developed to alleviate the concerns of high  $R_{SD}$ .

## **1.4 Objectives of Research**

The objectives of this research are to address the source/drain resistance issue in nanoscale III-V planar n-MOSFETs and FinFETs. The main focus of this thesis is placed on exploring low-resistance, CMOS compatible contact materials as well as developing new process technologies to realize self-aligned metallization for III-V n-MOSFETs. An extensive evaluation of contact technology options across various III-V n-MOSFETs such as GaAs planar transistors, InGaAs planar transistors, and InGaAs FinFETs is carried out to achieve low series resistance and high drive current. Ultimate motivation of realizing CMOS compatible, low-resistance self-aligned contacts for III-V n-MOSFETs was obtained. The results of this research will provide technology options for self-aligned metallization in III-V n-MOSFETs for the future technology generation nodes.

# **1.5** Thesis Organization