# Low-Pass Sigma Delta Modulator for High Temperature Operation

GONG XIAOHUI

(B.ENG.(Hons.), NUS)

# A THESIS SUBMITTED

# FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2012

# **Summary**

Low pass  $\Sigma\Delta$  modulators have been applied in many applications primarily for digitizing analog signals from environment. Compared to Nyquist rate ADCs (analog-to-digital converter),  $\Sigma\Delta$  ADCs have several advantages, such as high resolution and low process influence. On the other hand, in many industrial applications such as oil drilling process and hybrid vehicles, the electronic control circuits are required to operate at high temperature environment (typically above 200 °C), in which the commercial circuits are not capable of. This requires special design considerations dedicated for high temperature environment.

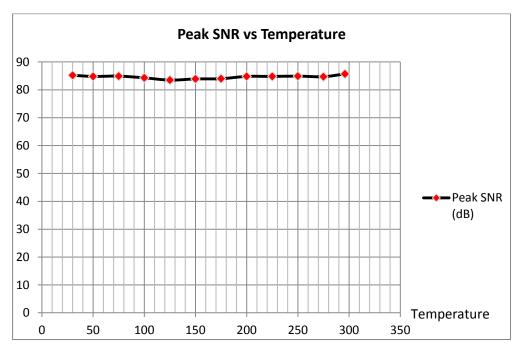

In this work, a design of  $3^{rd}$ -order  $\Sigma\Delta$  modulator has been presented in details. It is capable to operate in high temperature environment (above 200 °C). The input signal bandwidth is 250 Hz and sampling frequency is 128 kHz. It applies switched capacitor CIFB architecture with additional feed forward path to minimize the signal swing of internal stages. Meanwhile, by applying several high temperature design techniques, issues caused by the decrease of mobility and threshold voltage have been resolved. Over the temperature range from 0 °C to 300 °C, the designed fully differential amplifier shows a steady gain above 63dB and the overall system achieves a steady SNR of 87 dB.

# Acknowledgement

First of all, I would like to thank my supervisor, Professor Xu Yong Ping, for his valuable guidance and help during the course of this project. His expertise in circuit design and measure greatly helped me overcome the obstacles to accomplish this work. Thanks for all his effort in teaching and guiding me in the progress of this project.

I would also like to thank Ms. Zheng Huanqun for her effort in setting up the design tools and debugging for system errors. Thank Mr. Teo Seow Miang for his effort in maintaining and supporting the test equipment.

Besides, I would like to thank all the friends in VLSI lab for the inspiring discussions and sharing of knowledge. I really appreciate their help in their advice and effort for trouble-shooting.

# **Table of Contents**

| Summaryi                                                               |

|------------------------------------------------------------------------|

| Acknowledgementii                                                      |

| List of Figures                                                        |

| List of Tablesxii                                                      |

| Chapter 1 Introduction 1                                               |

| 1.1 Background                                                         |

| 1.2 Thesis Organization                                                |

| Chapter 2 Fundamentals of A/D Conversion and $\Sigma\Delta$ Modulation |

| 2.1 Concept of Sampling                                                |

| 2.2 Quantization                                                       |

| 2.3 Introduction to ADCs                                               |

| 2.3.1 Nyquist Rate ADC                                                 |

| 2.3.2 Oversampling ADCs                                                |

| 2.3.3 ΣΔ ADC                                                           |

| 2.4 Fundamentals of $\Sigma\Delta$ modulator                           |

| 2.5 Parameters and Classification of $\Sigma\Delta$ modulator          |

| 2.5.1 Design Parameters of $\Sigma\Delta$ modulator                    |

| 2.5.2 Classification of $\Sigma\Delta$ modulator                       |

| 2.6 Stability issue                                   |  |

|-------------------------------------------------------|--|

| 2.7 Noise analysis                                    |  |

| 2.7.1 Flicker Noise                                   |  |

| 2.7.2 Thermal noise                                   |  |

| 2.8 Performance Metrics                               |  |

| Chapter 3 High Temperature Circuit Design             |  |

| 3.1 Background                                        |  |

| 3.2 Temperature Effect on Threshold Voltage           |  |

| 3.3 Temperature Effect on Mobility                    |  |

| 3.4 Temperature Effect on Passive Components          |  |

| 3.6.1 Zero temperature coefficient biasing            |  |

| 3.6.2 Constant gm (transconductance) biasing circuit: |  |

| 3.6.3 Resistor Temperature Coefficients Cancelling    |  |

| Chapter 4 Switched Capacitor Circuit Fundamentals     |  |

| 4.1 Concept of Switched Capacitor Circuit             |  |

| 4.2 CMOS Switches                                     |  |

| 4.3 Non-Ideal Effects of CMOS Switches                |  |

| 4.3.1 Charge Injection                                |  |

| 4.3.2 Clock Feedthrough                               |  |

| 4.3.3 Bottom plate sampling technique                 |  |

| 4.4 Switched capacitor integrator                                             | 44 |

|-------------------------------------------------------------------------------|----|

| 4.4.1 Switched Capacitor Integrator Operation Principle                       | 44 |

| 4.4.2 Non-ideality due to finite gain of amplifier                            | 48 |

| Chapter 5 Design of High Temperature $\Sigma\Delta$ Modulator                 | 49 |

| 5.1 Review of Previously Published High Temperature $\Sigma\Delta$ Modulators | 49 |

| 5.2 System Level Design of Sigma Delta Modulator                              | 54 |

| 5.2.1 MatLab Model Construction and Simulation                                | 55 |

| 5.2.2 SimuLink Model Construction and Optimization                            | 58 |

| Chapter 6 Circuit Implementation                                              | 61 |

| 6.1 Top Level Circuit Schematic                                               | 61 |

| 6.2 Sizing the capacitor                                                      | 62 |

| 6.3 Design of Fully differential Amplifier                                    | 62 |

| 6.3.1 Analysis of Folded cascode amplifier                                    | 63 |

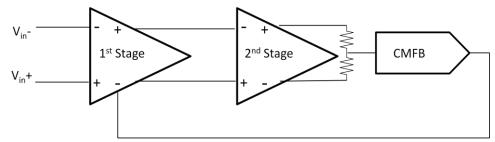

| 6.3.2 Two-Stage amplifier                                                     | 64 |

| 6.3.3 Common-Mode Feedback                                                    | 65 |

| 6.4 Clock generator                                                           | 79 |

| 6.4.1 Clock Scheme                                                            | 79 |

| 6.4.2 Clock generator                                                         | 81 |

| 6.4.3 Simulation Result of Clock generator                                    | 82 |

| 6.5 Comparator                                                                |    |

| 6.5.1 Comparator Circuit Schematic                       |     |

|----------------------------------------------------------|-----|

| 6.5.2 Simulation Result of Comparator                    | 85  |

| 6.5.3 Output Latch Schematic                             | 85  |

| 6.5.4 Simulation Results of Comparator with Output Latch | 86  |

| 6.6 Post-Layout Simulation result and discussion         | 87  |

| 6.7 Measurement Results                                  |     |

| 6.8 Result Analysis and Discussion                       |     |

| 6.8.1 SNDR drop                                          |     |

| 6.8.2 3 <sup>rd</sup> -Order Harmonics                   |     |

| 6.8.3 Comparison with previously reported works          | 101 |

| Chapter 7 Conclusion                                     |     |

| 7.1 Conclusion                                           |     |

| 7.2 Future work                                          |     |

| Bibliography                                             |     |

| Appendix A MatLab Scripts for Modeling the Modulator     |     |

| Appendix B Ocean Script                                  | 113 |

# List of Figures

| Figure 1-1 Electrical System                                                                               | 1 |

|------------------------------------------------------------------------------------------------------------|---|

| Figure 2-1 Nyquist Sampling Theorem                                                                        | 5 |

| Figure 2-2 Nyquist Rate ADC                                                                                | 5 |

| Figure 2-3 Concept of quantizer                                                                            | 7 |

| Figure 2-4 3-bit flash ADC schematic                                                                       | 8 |

| Figure 2-5 Oversampling ADC                                                                                | 9 |

| Figure 2-6 Quantization noise PSD of Nyquist rate (a) and oversampling (b) ADCs 1                          | 0 |

| Figure 2-7 $\Sigma\Delta$ ADC block diagram                                                                | 1 |

| Figure 2-8 Linear model of $\Sigma\Delta$ modulator                                                        | 1 |

| Figure 2-9 Comparison of Nyquist ADCs, oversampling ADCs and $\Sigma\Delta$ ADCs 1                         | 2 |

| Figure 2-10 1 <sup>st</sup> -order single loop $\Sigma\Delta$ modulator block diagram                      | 3 |

| Figure 2-11 $2^{nd}$ order $\Sigma\Delta$ modulator block diagram                                          | 4 |

| Figure 2-12 PSD of NTF (Z) for 1 <sup>st</sup> -order (MOD1) and 2 <sup>nd</sup> order (MOD2) modulators 1 | 6 |

| Figure 2-13 Empirical SNR limits for quantization bits =1 (a) and 2(b) 1                                   | 7 |

| Figure 2-14 Noise PSD profile1                                                                             | 9 |

| Figure 2-15 Thermal Noise Model of NMOS transistor                                                         | 1 |

| Figure 2-16 Definitions of maximum SNR and DR                                                              | 2 |

| Figure 2-17 Harmonic distortion                                                                            | 3 |

| Figure 3-1 Simulation of V <sub>th</sub> against temperature                                               | 6 |

| Figure 3-2 Simulation of mobility against temperature                                                      | 8 |

| Figure 3-3 Plot resistance against temperature                                                             | 9 |

| Figure 3-4 Cross section of bulk CMOS inverter (A) and SOI CMOS inverter (B)                               | 0 |

| Figure 3-5 Simulated drain current under DC sweep of gate voltage at different     |    |

|------------------------------------------------------------------------------------|----|

| temperatures                                                                       | 32 |

| Figure 3-6 Transistor biased at ZTC biasing point                                  | 33 |

| Figure 3-7 Constant gm biasing circuit                                             | 34 |

| Figure 3-8 Constant gm biasing circuit with start-up transistor                    | 36 |

| Figure 3-9 Series connection of two resistors with different TC                    | 37 |

| Figure 3-10 Simulation of R <sub>total</sub>                                       | 38 |

| Figure 4-1 Switched capacitor circuit                                              | 39 |

| Figure 4-2 NMOS switch (a) and transmission gate switch (b)                        | 41 |

| Figure 4-3 On-resistance of transmission gate switch                               | 42 |

| Figure 4-4 Charge injection of MOS switch                                          | 43 |

| Figure 4-5 Clock feed through of MOS switch                                        | 43 |

| Figure 4-6 Bottom plate sampling techniques                                        | 44 |

| Figure 4-7 RC integrator schematic                                                 | 45 |

| Figure 4-8 Switched capacitor integrator                                           | 46 |

| Figure 4-9 Clock phase 1                                                           | 46 |

| Figure 4-10 Clock phase 2                                                          | 47 |

| Figure 5-1 System schematic of a 2 <sup>nd</sup> order single stage modulator and  | 49 |

| Figure 5-2 System schematic of a 2 <sup>nd</sup> -order single stage modulator and | 52 |

| Figure 5-3 High temperature data acquisition system block diagram                  | 54 |

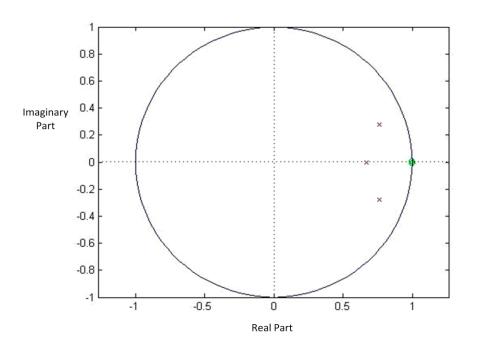

| Figure 5-4 Poles and zeros of NTF (Z)                                              | 56 |

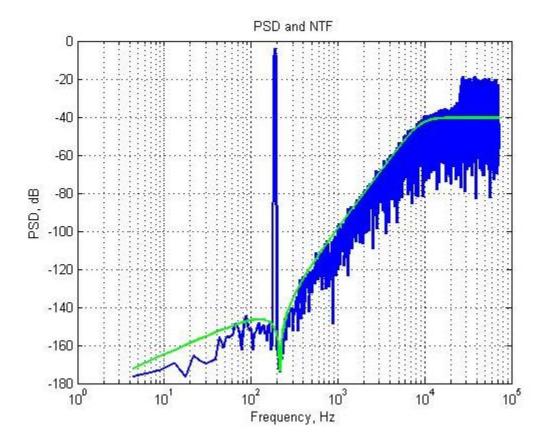

| Figure 5-5 NTF (green) and PSD (blue) of transfer function simulation              | 57 |

| Figure 5-6 Full CIFB architecture                                                  | 57 |

#### aumont un dan DC arrest a of acts welts as at diffs г. 2 5 Cimeralated duain

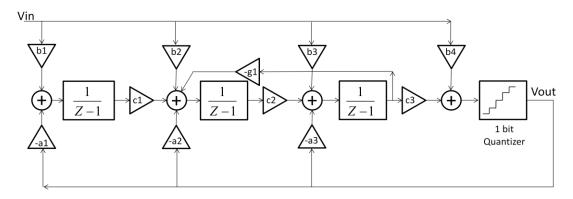

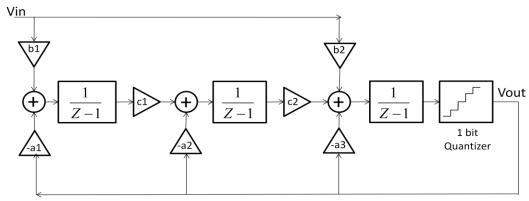

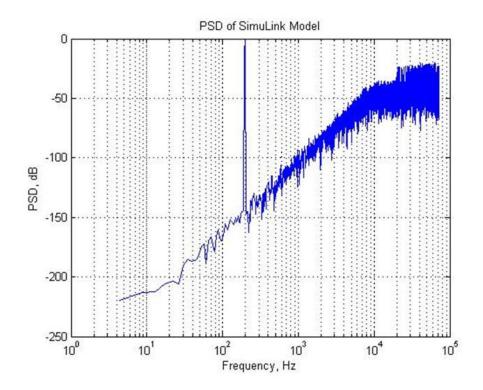

| Figure 5-7 Finalized modulator block diagram                                                         | . 59 |

|------------------------------------------------------------------------------------------------------|------|

| Figure 5-8 PSD of SimuLink model simulation                                                          | . 60 |

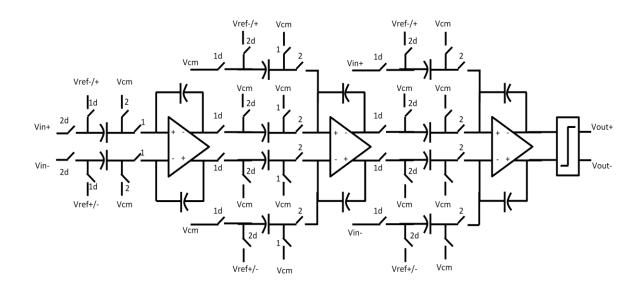

| Figure 6-1 Modulator schematic                                                                       | . 61 |

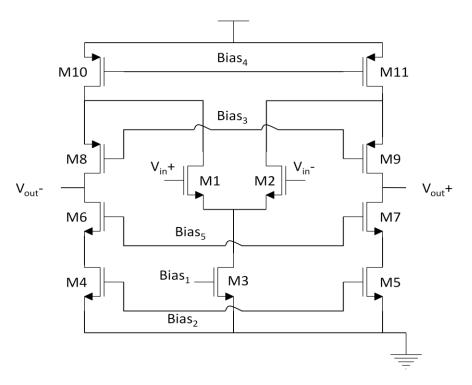

| Figure 6-2 Schematic of folded cascode fully differential amplifier                                  | . 63 |

| Figure 6-3 Schematic of two stage fully differential amplifier                                       | . 65 |

| Figure 6-4 Concept of common-mode (CM) feedback                                                      | . 66 |

| Figure 6-5 Circuit which calculates the output common-mode voltage                                   | . 66 |

| Figure 6-6 Switched capacitor based CMFB circuit                                                     | . 67 |

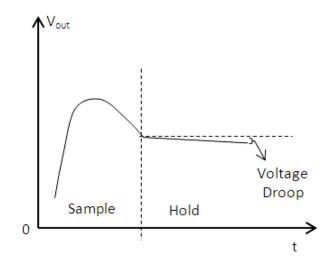

| Figure 6-7 Voltage droop of switched capacitor voltage                                               | . 68 |

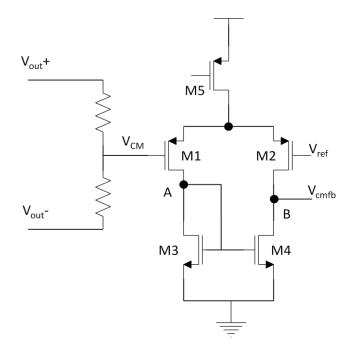

| Figure 6-8 Continuous-time CMFB circuit                                                              | . 69 |

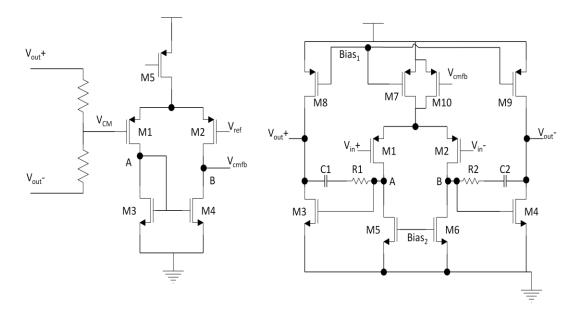

| Figure 6-9 Two stage fully differential amplifier with single CMFB loop                              | . 70 |

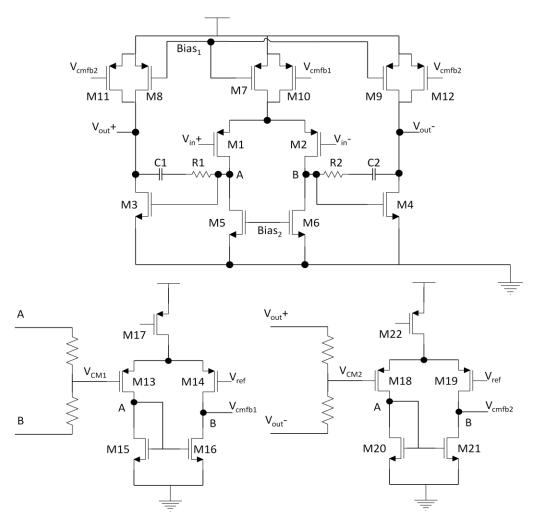

| Figure 6-10 Two stage fully differential amplifier with double CMFB loops                            | . 71 |

| Figure 6-11 Block diagram of single loop CMFB topology                                               | . 72 |

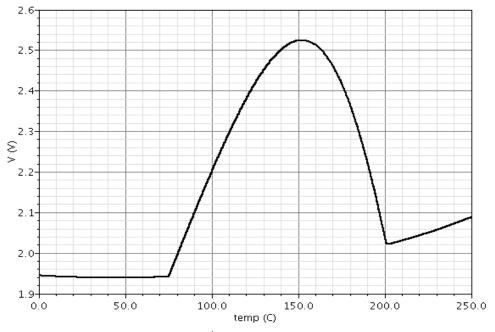

| Figure 6-12 DC level of 1 <sup>st</sup> stage output at different temperatures                       | . 72 |

| Figure 6-13 Biasing circuit                                                                          | . 73 |

| Figure 6-14 Simulated total resistance                                                               | . 74 |

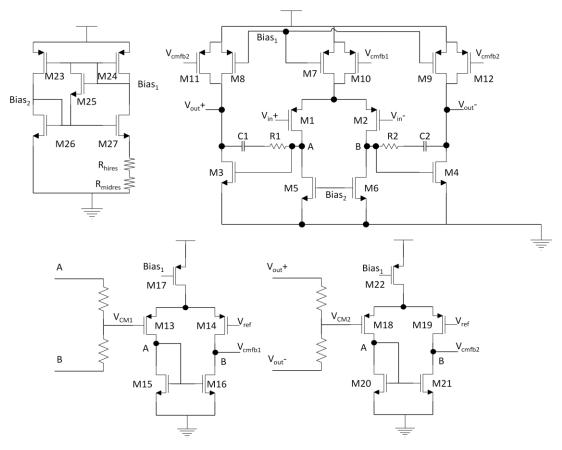

| Figure 6-15 Final schematic of amplifier                                                             | . 75 |

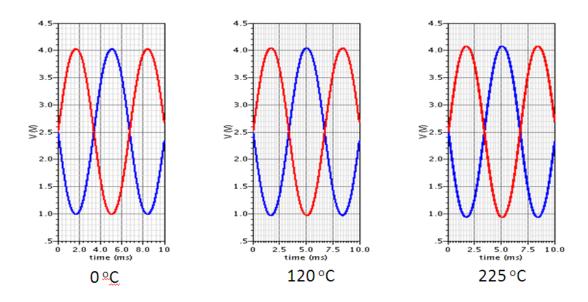

| Figure 6-16 Transient plot of amplifier at different temperatures                                    | . 76 |

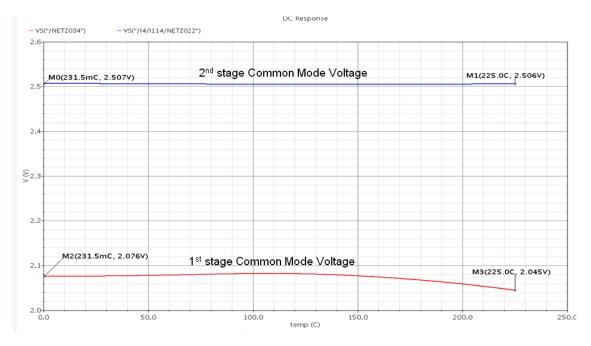

| Figure 6-17 Output DC levels of 1 <sup>st</sup> and 2 <sup>nd</sup> stages at different temperatures | . 76 |

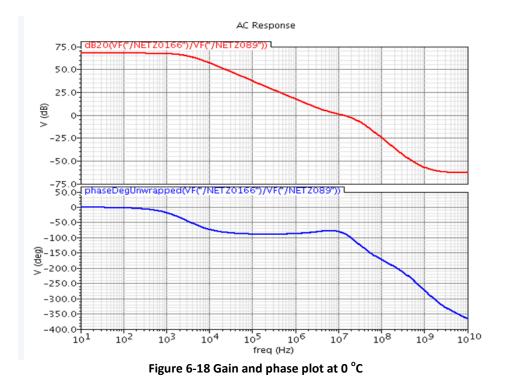

| Figure 6-18 Gain and phase plot at 0 °C                                                              | . 77 |

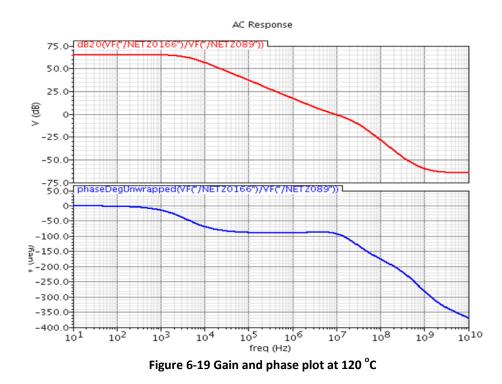

| Figure 6-19 Gain and phase plot at 120 °C                                                            | . 77 |

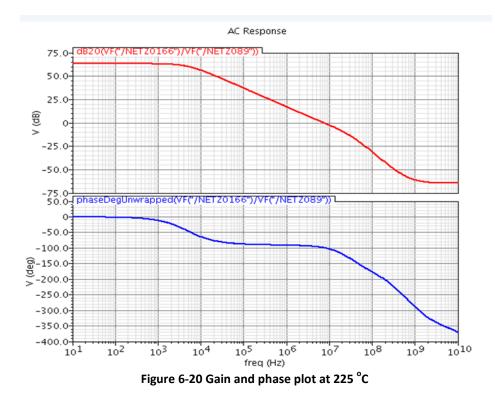

| Figure 6-20 Gain and phase plot at 225 °C                                                            | . 78 |

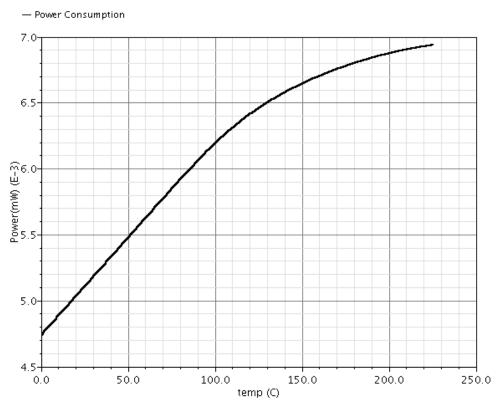

| Figure 6-21 Amplifier power consumption at different temperatures                                    | . 79 |

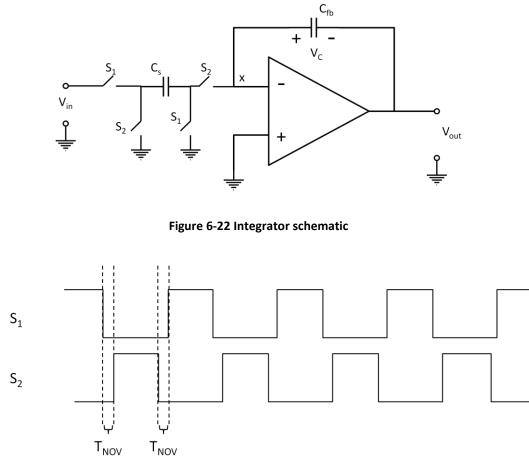

| Figure 6-22 Integrator schematic                                                  | . 80 |

|-----------------------------------------------------------------------------------|------|

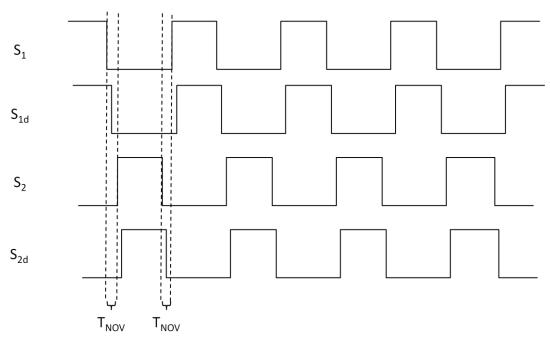

| Figure 6-23 Non-overlapping clock waveform                                        | . 80 |

| Figure 6-24 Non-overlapping with delayed clock waveform                           | . 81 |

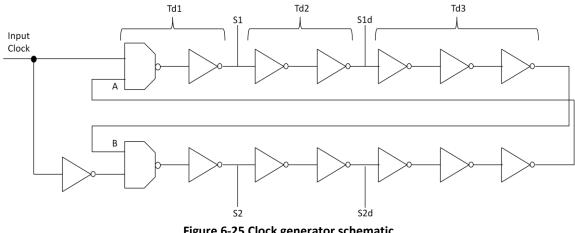

| Figure 6-25 Clock generator schematic                                             | . 81 |

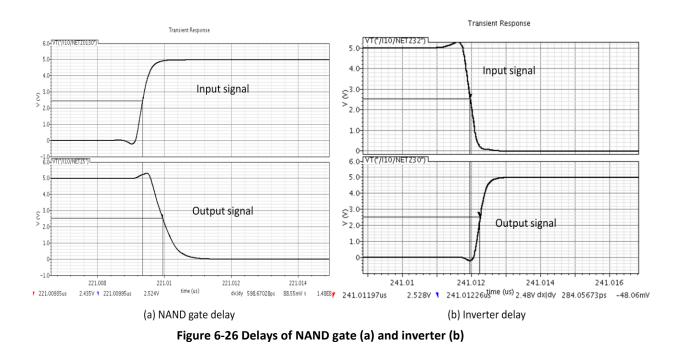

| Figure 6-26 Delays of NAND gate (a) and inverter (b)                              | . 83 |

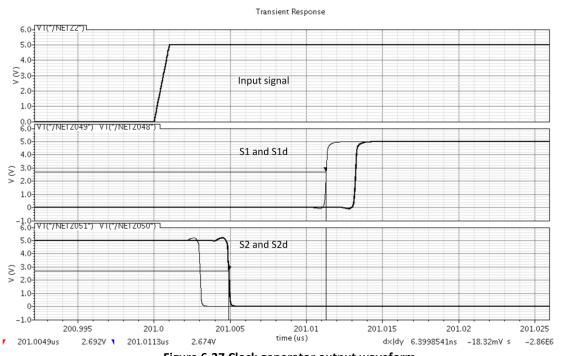

| Figure 6-27 Clock generator output waveform                                       | . 83 |

| Figure 6-28 Schematic of comparator                                               | . 84 |

| Figure 6-29 Comparator output waveform                                            | . 85 |

| Figure 6-30 Output latch schematic                                                | . 86 |

| Figure 6-31 Output waveform of comparator with output latch                       | . 87 |

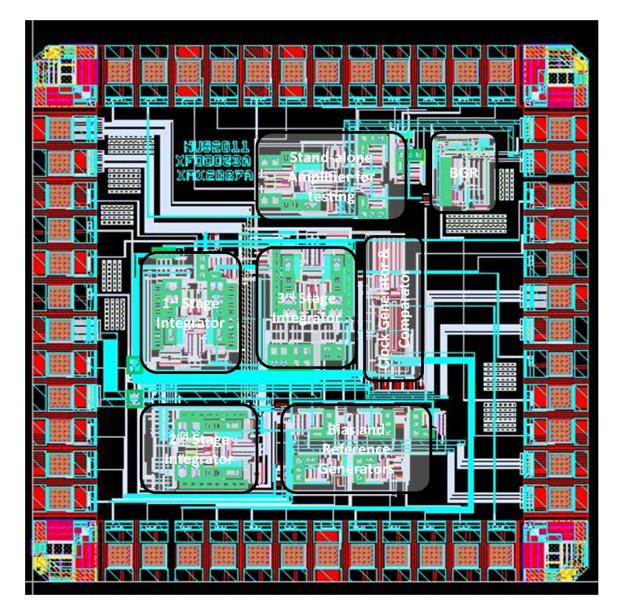

| Figure 6-32 Modulator layout                                                      | . 88 |

| Figure 6-33 PSD of post layout simulation at different temperatures               | . 89 |

| Figure 6-34 Dynamic range plot                                                    | . 89 |

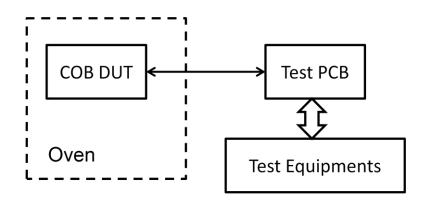

| Figure 6-35 Measurement Setup Diagram                                             | . 91 |

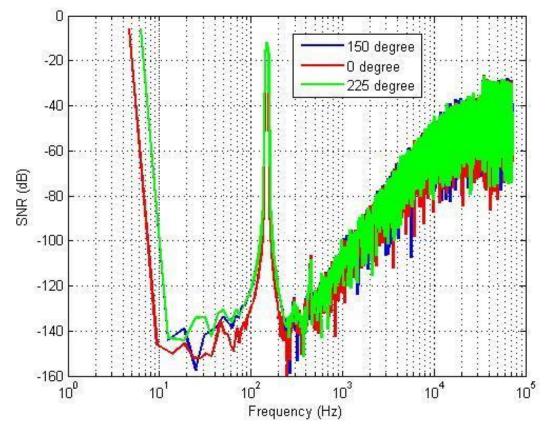

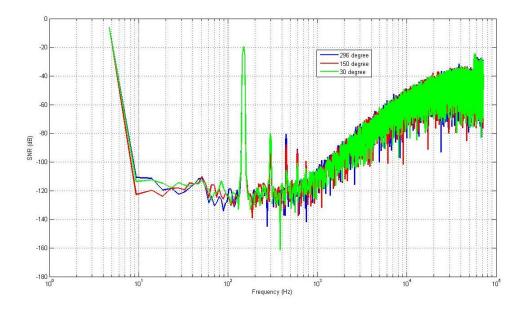

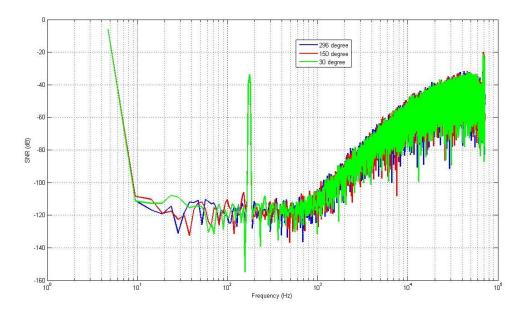

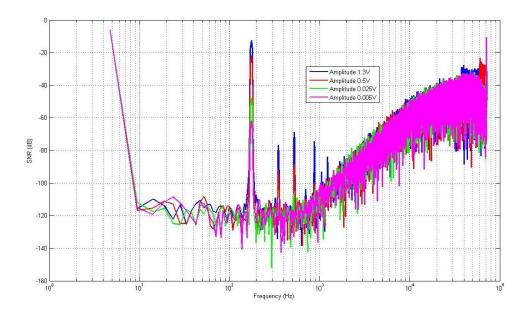

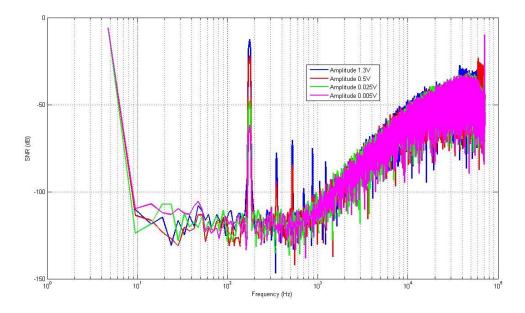

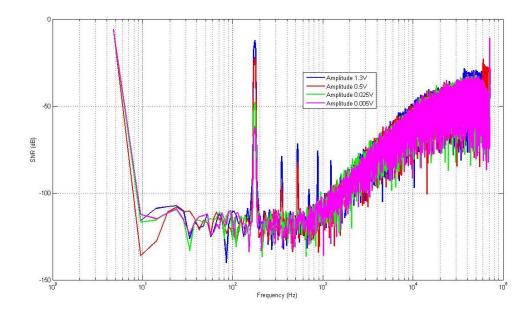

| Figure 6-36 Measured PSDs at different temperatures                               | . 92 |

| Figure 6-37 Measured PSDs at different temperatures for low input amplitude where |      |

| distortions are not seen                                                          | . 92 |

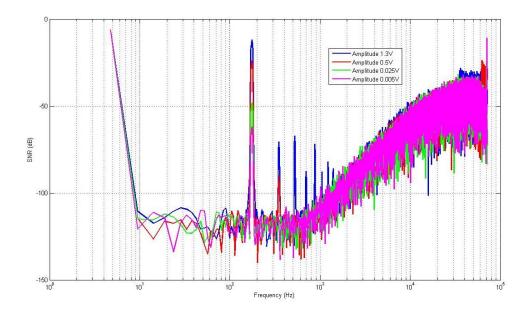

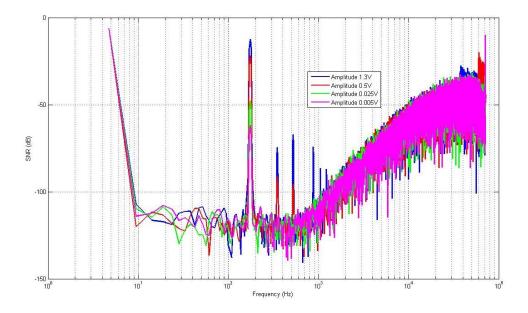

| Figure 6-38 Measured PSDs for different input amplitude at 25 °C                  | . 93 |

| Figure 6-39 Measured PSDs for different input amplitude at 150 °C                 | . 93 |

| Figure 6-40 Measured PSDs for different input amplitude at 200 °C                 | . 94 |

| Figure 6-41 Measured PSDs for different input amplitude at 250 °C                 | . 94 |

| Figure 6-42 Measured PSDs for different input amplitude at 300 °C                 | . 95 |

| Figure 6-43 Measured peak SNR at different temperatures                           | . 95 |

| Figure 6-44 Measured SNR against input amplitude at different temperatures | . 96 |

|----------------------------------------------------------------------------|------|

| Figure 6-45 PSD simulated with behavior model of amplifier                 | . 98 |

| Figure 6-46 PSD simulated with ideal capacitor                             | 100  |

# List of Tables

| Table 2-1 Classification of $\Sigma\Delta$ modulators                               |

|-------------------------------------------------------------------------------------|

| Table 5-1 Amplifier open-loop gain at different temperatures       50               |

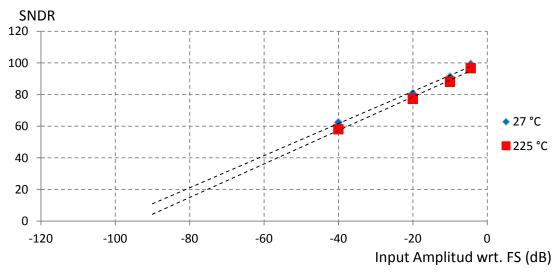

| Table 5-2 Experimental SNDR at different temperatures and input amplitudes       50 |

| Table 5-3 Summary of measurement results    52                                      |

| Table 5-4 Design Specification                                                      |

| Table 5-5 Calculated unscaled coefficients                                          |

| Table 5-6 Finalized coefficients after scaling    59                                |

| Table 6-1 Amplifier AC performace                                                   |

| Table 6-2 Clock generator timing table                                              |

| Table 6-3 Summary of key performance parameters    90                               |

| Table 6-4 Modulator Measurement Result Summary    96                                |

| Table 6-5 Performance Comparison between this work and reported works         101   |

# Chapter 1 Introduction

### 1.1 Background

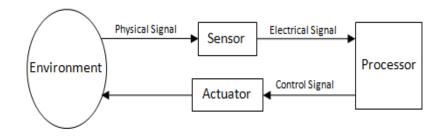

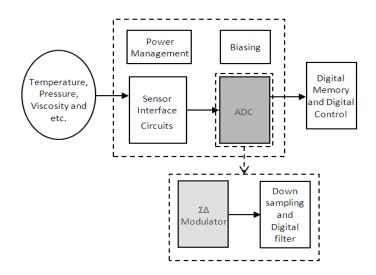

In recent years, following the rapid development of semiconductor industry, electronics have been adopted in various applications. For typical applications such as consumer electronic products, home appliances, bio-medical devices and automated manufacturing machines, functional specific electrical systems are designed to monitor and control the operation. Generally, such systems sense the physical signals using a sensor and feed the sensed electrical signals to the processor. The processor processes the sensed data based on application specific algorithms and sends control signal to the actuator which performs the operation back [1]. This is explained in Figure 1-1.

Figure 1-1 Electrical System

Among various steps in the process, sensing has always been a crucial step since the quality of the sensed data directly affects the system performance. Generally, for a sensor, the sensing quality is usually relied on an analog-to-digital converter(ADC), which converts the input signals(usually come in an analog format, such as sound, temperature, light and so on) into digital signals in order to be processed by the processor. In many applications, high resolution of A/D conversion is required, which leads to the promotion

of  $\Sigma\Delta$  ADC. It applies  $\Sigma\Delta$  modulation techniques and is able to achieve a resolution as high as above 16-bit ENOB [2].

On the other hand, operating temperature is a major limitation for the performance of electronic circuits that operate in harsh environments. This is because many physical parameters of silicon such as carrier concentrations and carrier mobilities, vary as temperature changes. This implies that electronic circuit is dedicated to operate within a pre-defined temperature range. Generally, for commercial electronic circuits, the operating temperature is within the range of 0 °C to 85 °C. For military applications, the operating temperature is within the range of -55 °C to 125 °C [3]. However, there is an increasing demand [4] [5] [6] of circuits which works in a wider temperature range. For example, in many industrial applications, such as oil drilling, aerospace and hybrid vehicles, circuits are required to operate in the temperature as high as above 200 °C [7], in which the available circuits are not capable of.

#### **<u>1.2 Thesis Organization</u>**

As motivated by the above mentioned demand of high temperature circuits, this work presents a switched capacitor based high temperature low pass  $\Sigma\Delta$  modulator. Chapter 2 introduces the fundamentals of A/D conversion and the operational principle of  $\Sigma\Delta$ modulator.

Chapter 3 studies the high temperature issues which may affect the circuit performance. Some effective high temperature design techniques are introduced to minimize the high temperature effects. In addition, a study of SOI CMOS process fundamentals is also presented.

Chapter 4 introduces the fundamental concepts of switched capacitor circuits. The issues associated with CMOS switch are studied in detail. Techniques such as bottom plate sampling are introduced in order to minimize the non-ideal effects. Moreover, a switched capacitor based integrator is studied in details and the transfer function is derived.

Chapter 5 firstly reviews some previously reported designs and analyzes the pros and cons of individual design. Subsequently, a top-level design of high temperature low pass  $\Sigma\Delta$ modulator is presented. With the proposed specification, the system level design and modeling is done using MatLab.

Chapter 6 presents the circuit level implementation of the low pass  $\Sigma\Delta$  modulator. The details of every circuit block are shown together with the simulation results. In addition, the post-layout simulation result is shown. Discussion and analysis of the performance are also presented.

Chapter 7 summarized the major achievements of this work. Some suggestions on future improvement have been proposed.

# Chapter 2 Fundamentals of A/D Conversion and ΣΔ Modulation

### 2.1 Concept of Sampling

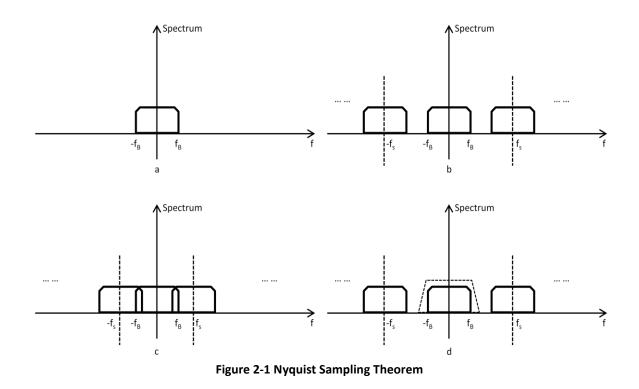

An analog-to-digital converter is a circuit block that converts the continues-time (analog) signal into discrete-time (digital) signal. According to the Nyquist sampling theory, in order to reconstruct the input signal with no error, the sampling frequency  $f_s$  must be at least twice of the input signal bandwidth  $f_B$ , which is given by

$$f_s > 2f_B$$

The sampling frequency  $f_s$ , which equals to twice of  $f_B$ , is called Nyquist sampling rate. The Nyquist sampling theory can be explained in Figure 2-1. Theoretically, the input signal spectrum with bandwidth of  $f_B$  is shown in Figure 2-1a, which is symmetric about the y axis. After being sampled, the spectrum is copied and shifted to be centered at  $f_s$ ,  $2f_s$ ,  $3f_s$  and so on as shown in Figure 2-1b. Therefore, for  $f_s$  less than twice of  $f_B$ , the two adjacent spectrums will overlap near the end of the band, which distorts the original signal spectrum. This is shown in Figure 2-1c. In this case, the original signal spectrum can never be reconstructed error-freely. This overlapping of spectrums is called aliasing. However, as shown in Figure 2-1d, when Nyquist sampling rate is used, there is an enough gap between two adjacent spectrums. It ensures that the signal spectrum is not distorted so that the original signal can be recovered by an anti-aliasing filter [8].

There are different types of ADCs. However, based on the sampling frequency, they can be divided into two categories, namely Nyquist rate ADCs and oversampling ADCs. For a Nyquist rate ADC, the sampling frequency is twice of the input single bandwidth. In real application, however, a sampling frequency slightly higher than Nyquist sampling rate is selected in order to ease the performance requirement of anti-aliasing filter. An example is shown in Figure 2-2.

Figure 2-2 Nyquist Rate ADC

### 2.2 Quantization

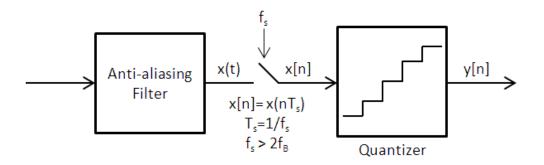

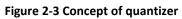

Quantization is a process to convert the analog signal into digital signal, as depicted in Figure 2-2. For an N bit quantizer, the output signal can have 2<sup>N</sup> levels as shown in Figure 2-3. However, since the quantization levels are discrete and finite, the quantization process is embedded with quantization noise. Generally, for an N bit quantizer, the step size can be expressed as equation (2.1) [9], which correspond to one LSB (Least Significant Bit). For large value of N, the step size can be approximated to FS/2<sup>N</sup>. As shown in Figure 2-3, when the input analog signal sweeps from the minimum value to maximum value, the instantaneous quantization error ranges from -0.5LSB to +0.5LSB. As shown in (2.2), by applying a linear model of the quantization process, with input of x, the quantization error e is a simple addition to the output y. Hence, the quantization error is approximated as white noise with zero mean [10]. Therefore, the variance, which corresponds to the power of the quantization error, can be expressed as equation (2.3) [11]. Furthermore, for a full scale sinusoidal input, the peak SNR (signal to noise ratio) can be expressed as equation (2.4). As a key performance parameter of ADC, a high SNR has been a challenge for ADC design [9].

$$\Delta = \frac{FS}{2^n - 1} \approx \frac{FS}{2^n} \qquad (2.1)$$

$$y = kx + e \tag{2.2}$$

Where

x is the input analog signal

k is the coefficient corresponding to the slope of line l as shown in Figure 2-3a

e is the quantization error

y is the output digital signal

$$P_n = \sigma_e^2 = \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} e^2 de = \frac{\Delta^2}{12}$$

(2.3)

$$SNR_{max} = 10 \log\left(\frac{FS/8}{P_n}\right) \cong 6.02N + 1.76 \ (dB)$$

(2.4)

# **2.3 Introduction to ADCs**

### 2.3.1 Nyquist Rate ADC

There are many types of Nyquist rate ADCs. For example, flash ADC, as shown in Figure 2-4 [12], uses resistors chain to divide the reference voltage  $V_{ref}$  into eight voltages (0V,  $V_{ref}/7, 2V_{ref}/7, 3V_{ref}/7 \dots V_{ref}$ ). If the input voltage is  $0.5V_{ref}$ , it is higher than  $3V_{ref}/7$  and lower than  $4V_{ref}/7$ . Those comparators which connect to  $V_{ref}/7, 2V_{ref}/7$  and  $3V_{ref}/7$  output 1 and the rest output 0. The encoder finally encodes the comparators output to binary code 3'b011.

Figure 2-4 3-bit flash ADC schematic

In a practical flash ADC as well as other Nyquist rate ADCs, in order to achieve a good linearity and high SNR, the matching of the circuit elements (resistors, capacitors or transistors) must be accurate. However, due to some conditions, such as process variation and parasitic, the inaccuracy is limited to above 0.02%. In another word, the maximum achievable SNR is less than 80 dB.

### 2.3.2 Oversampling ADCs

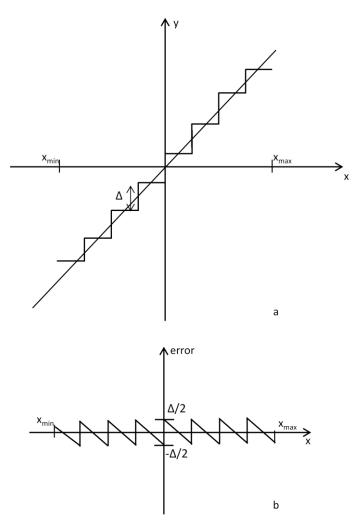

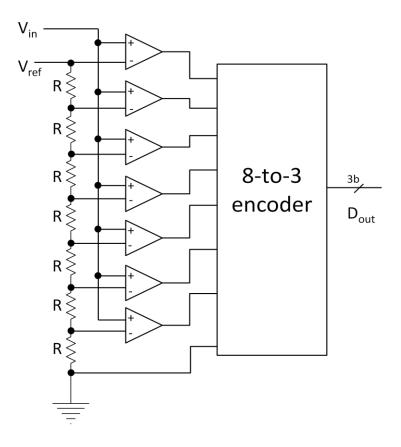

An oversampling ADC samples the input signal at a frequency much higher that the Nyquist sampling rate. The OSR (oversampling ratio) is defined as equation (2.5). As depicted in Figure 2-5, the ADC samples the input signal at a frequency of  $f_s$ . After quantization and filtering, the output digital signal goes through a down-sampling process to Nyquist rate.

$$OSR = \frac{f_s}{2f_b} \tag{2.5}$$

Figure 2-5 Oversampling ADC

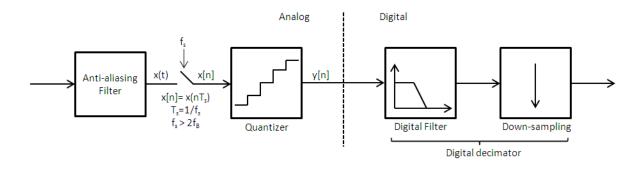

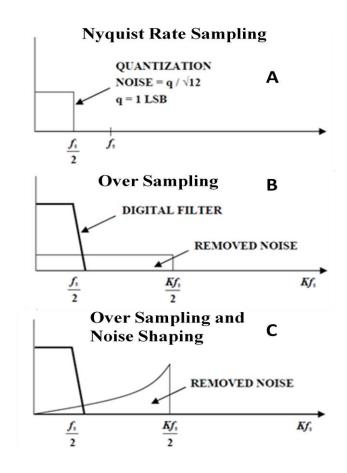

The oversampling ADC with N-bit quantizer contributes the same total quantization noise power as a Nyquist rate ADC with a same quantizer does. As explained in Figure 2-6a, the total quantization noise power is evenly distributed between  $-f_B$  and  $f_B$  for a Nyquist rate ADC. Therefore, the in-band quantization noise power is equivalent to the total quantization noise power. As shown in Figure 2-6b, for an oversampling ADC, since the sampling frequency is increased to  $f_s$ , the same amount of total quantization noise power spreads from  $-f_s$  to  $f_s$ . Therefore, the quantization noise level is lowered and the in-band quantization noise power is decreased. The in-band quantization noise power is expressed as equation (2.6). Hence, the SNR is derived as shown in (2.7). As a general rule of thumb, for every doubling of the OSR, the SNR increases by 3 dB (ENOB increases for 0.5b).

Figure 2-6 Quantization noise PSD of Nyquist rate (a) and oversampling (b) ADCs

$$P_{no} = \int_{-f_s}^{f_s} \frac{\sigma_e^2}{f_s} df = \sigma_e^2 \frac{2f_B}{f_s} = \frac{\Delta^2}{12} \frac{1}{OSR}$$

(2.6)

$$SNR_{max} = 10 \log\left(\frac{FS/8}{P_{no}}\right) \cong 6.02N + 1.76 + 10 \log OSR \ (dB)$$

(2.7)

### 2.3.3 ΣΔ ADC

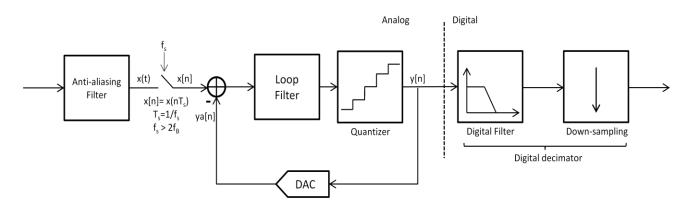

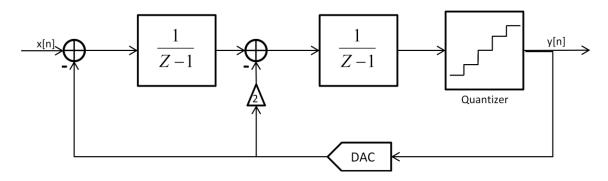

A  $\Sigma\Delta$  ADC is built on top of oversampling ADC. The main difference is that the original quantizer is replaced by a  $\Sigma\Delta$  modulator, as shown in Figure 2-7. Generally, a  $\Sigma\Delta$

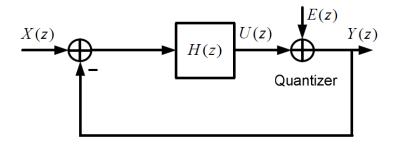

modulator consists of a loop filter, a quantizer and a DAC (digital-to-analog converter). Instead of digitizing the input signal directly, it integrates (low pass filtering) the error between the input and output signals, digitizes the integrated signal and feedbacks to input again. A linear model of discrete-time  $\Sigma\Delta$  modulator is shown in Figure 2-8.

Figure 2-7 ΣΔ ADC block diagram

Figure 2-8 Linear model of  $\Sigma\Delta$  modulator

$$Y(Z) = (X(Z) - Y(Z)) \times H(Z) + E(Z)$$

(2.8)

$$= Y(Z) = \frac{H(Z)}{1 + H(Z)} X(Z) + \frac{1}{1 + H(Z)} E(Z)$$

(2.9)

In this linear model, the loop filter's transfer function is H(Z). The quantizer is modeled as an ideal quantizer with quantization noise E(Z) as suggested in equation (2.1). The output Y(Z) can be derived as shown in equations (2.8) and (2.9). The input signal component is multiplied by an  $STF(Z) = \frac{H(Z)}{1+H(Z)}$  term, while the noise component is multiplied by an  $NTF(Z) = \frac{1}{1+H(Z)}$  term. STF(Z) is referred to signal transfer function and NTF(Z) is referred to noise transfer function. In ideal case, if the gain of H(Z) is designed to be a large value, STF(Z) is approximated to be one and NTF(Z) is approximated to be zero. Therefore, during  $\Sigma\Delta$  modulation, the noise component is suppressed and the signal component is maintained the same. This process is referred as noise shaping [13]. A comparison of Nyquist ADCs, oversampling ADCs and  $\Sigma\Delta$  ADCs is shown in Figure 2-9 [14].

Figure 2-9 Comparison of Nyquist ADCs, oversampling ADCs and ΣΔ ADCs [14]

### **2.4 Fundamentals of ΣΔ modulator**

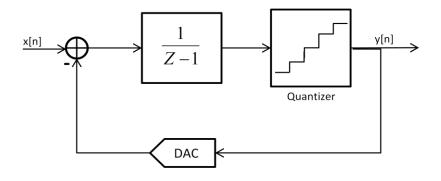

For a 1<sup>st</sup>-order single loop  $\Sigma\Delta$  modulator as shown in Figure 2-10, the loop filter H(Z) is simply an integrator with a pole at DC. By applying the linear model, the transfer function is shown in equation (2.10). For STF(Z) = Z<sup>-1</sup>, the resulting input signal is delayed by one clock cycle. For NTF(Z) = 1- Z<sup>-1</sup>(high pass filter), the low frequency noise is suppressed and the high frequency noise remains unchanged.

Figure 2-10  $1^{st}$ -order single loop  $\Sigma\Delta$  modulator block diagram

$$Y(Z) = X(Z)Z^{-1} + E(Z)(1 - Z^{-1})$$

(2.10)

with

$$STF(Z) = Z^{-1}$$

and  $NTF(Z) = 1 - Z^{-1}$

Noise shaping can be viewed as a process that transfers the low frequency band quantization noise into high frequency band, however, the total quantization noise power is maintained the same. Since the high frequency noise is out of signal band, after  $\Sigma\Delta$  modulation, a decimation filter can be added to remove the high frequency noise component. The signal and in-band noise (been greatly suppressed) is preserved.

### **2.5 Parameters and Classification of ΣΔ modulator**

#### **2.5.1 Design Parameters of \Sigma\Delta modulator**

In order to characterize different  $\Sigma\Delta$  modulators, several modulator-related parameters are proposed, namely OSR, order and quantization levels. OSR defines the sampling speed with respect to the input signal bandwidth. Intuitively,  $\Sigma\Delta$  modulator periodically corrects the output by feeding back the sampled error between input and output signals. As a result, the average value of the output bit stream is converging to the input signal level. Therefore, a higher OSR implies that a larger number of cycles the system takes to correct the input. Hence, a longer bit stream is generated and a more accurate result is achieved. As discussed previously in equation (2.7), for every doubling of the OSR, the SNR increases by 3 dB.

Figure 2-11  $2^{nd}$  order  $\Sigma\Delta$  modulator block diagram

The order of a  $\Sigma\Delta$  modulator corresponds to the order of NTF(Z). Figure 2-11 shows the block diagram of a 2<sup>nd</sup>-order  $\Sigma\Delta$  modulator. The modulator transfer function is derived as shown in equation (2.11). A higher order of NTF(Z) implies a higher order of high pass filter, which suppresses the in-band quantization noise to a lower lever. Generally, for a L-th order modulator with NTF(Z) of  $(1-Z^{-1})^{L}$ , the total power of in-band quantization noise can be expressed as equation (2.12).

$$Y(Z) = X(Z)Z^{-2} + E(Z)(1 - Z^{-1})^2$$

(2.11)

with

$$STF(Z) = Z^{-2}$$

and  $NTF(Z) = (1 - Z^{-1})^2$

$$P_{no} = \int_{-f_B}^{f_B} \frac{\sigma_e^2}{f_s} |1 - Z^{-1}|^{2L} df = \int_{-f_B}^{f_B} \frac{\sigma_e^2}{f_s} |2 \sin\left(\frac{\pi f}{f_s}\right)|^{2L} df$$

$$\approx \sigma_e^2 \frac{\pi^{2L}}{2L+1} \left(\frac{2f_B}{f_s}\right)^{2L+1} = \frac{\Delta^2}{12} \frac{\pi^{2L}}{2L+1} \frac{1}{OSR^{2L+1}}$$

(2.12)

Thus, the peak SNR can be obtained as

$$SNR_{max} \cong 6.02N + 1.76 + (2L+1)10 \log OSR - 10 \log \left(\frac{\pi^{2L}}{2L+1}\right) (dB) \qquad for N > 3$$

(2.13)

If a single-bit quantizer (N=1) is used, the peak SNR is

$$SNR_{peak} = 1.76 + (2L+1)10 \log OSR - 10 \log \left(\frac{\pi^{2L}}{2L+1}\right) (dB)$$

(2.14)

As shown in equation (2.13) and (2.14), for every doubling of OSR, the peak SNR increases by 3(2L+1) dB, corresponding to L+0.5 bit of resolution.

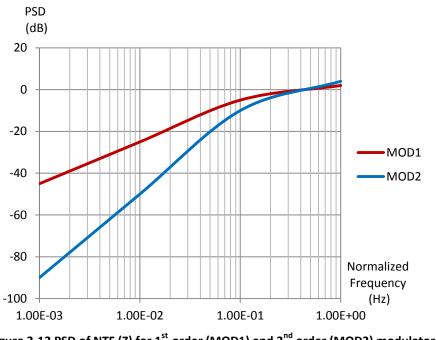

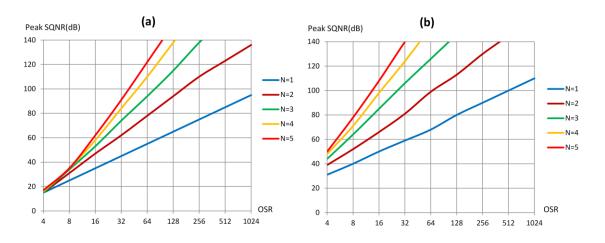

As shown in Figure 2-12 [15], for a 1<sup>st</sup> order  $\Sigma\Delta$  modulator, from high frequency to low frequency, the quantization noise level is decreasing in a slope of -20 dB/decade. For a 2<sup>nd</sup> order  $\Sigma\Delta$  modulator, the slope is -40 dB/decade. Generally, for an N-th order  $\Sigma\Delta$  modulator, the slope is -20N dB/decade.

Figure 2-12 PSD of NTF (Z) for 1<sup>st</sup>-order (MOD1) and 2<sup>nd</sup> order (MOD2) modulators [15]

The quantization level is defined by the quantizer. An N-bit quantizer has a quantization level of 2<sup>N</sup>. Generally, a quantizer with more quantization levels feeds back a more precise output to the input. Hence, the modulation is more efficient. As suggested by equation (2.13), an increase of 1 bit corresponds to 6 dB increase in the SNR. However, as the bit increased, the linearity of the quantizer may decrease, which results in a major trade off.

As shown in equation (2.13), different combinations of OSR, order and quantization level yield different SNRs. From system design point of view, the target SNR defines the requirement of OSR, order and quantization level. This can be explained in Figure 2-13 [16], which shows the limits of achievable SNR for various combinations of OSR, order and quantization level.

Figure 2-13 Empirical SNR limits for quantization bits =1 (a) and 2(b) [16]

### 2.5.2 Classification of $\Sigma\Delta$ modulator

$\Sigma\Delta$  modulators can be classified in many ways. Some commonly used criterions are listed

down as shown in Table 2-1.

| Criterion         | Classifications                      |           |

|-------------------|--------------------------------------|-----------|

| Sampling Method   | Discrete-Time Continuous-Time        |           |

| Order             | first order, second order n-th order |           |

| Quantization Bits | N=1, 1.5, 2 n                        |           |

| Loop Filter Type  | Low Pass                             | Band Pass |

Table 2-1 Classification of  $\Sigma\Delta$  modulators

# 2.6 Stability issue

In  $\Sigma\Delta$  modulator, the traditional BIBO (Bounded Input, Bounded Output) criterion does not applied. This is because for a practical quantizer, the output is bounded by the supply rails. In the case of an unstable loop, the output becomes clipped. Generally, the stability condition of a  $\Sigma\Delta$  modulator depends on both the input signal and the order of the modulator.

For an ideal modulator, if the linearity of the quantizer is ignored, for a large input signal when the input of the first integrator is positive at every cycle, the output of the integrator keeps increasing without bound and the system becomes unstable [17]. This is illustrated in Figure 2-8, if

$$X(Z) - Y(Z) > 0 (2.15)$$

Then

$$U(Z) = H(Z)[X(Z) - Y(Z)] \to \infty$$

(2.16)

Therefore, a stable system requires a limitation of input signal magnitude, which is called the stable input range. In normal modulator operation, the loop filter is required to remain linear and the quantizer is required to remain not severely overloaded. In practice, the stable input range is primarily determined by the NTF(Z) and the number of quantization levels.

On the other hand, the order of the modulator also affects the stability. For Figure 2-8, the loop filter's output U(Z) can be expressed as equation (2.17),

$$U(Z) = Y(Z) - E(Z) = STF(Z)X(Z) + [NTF(Z) - 1]E(Z)$$

(2.17)

As the order L of NTF(Z) increases, a large gain of [NTF(z)-1] may occur, which leads to a huge amplification of quantization noise. As a result, the internal signal may change rapidly and oscillation may happen. Therefore, in order to obtain a stable operation of modulator, the NTF(Z) should be carefully designed. To help determine the suitable NTF(Z) in order to meet the stability requirement, the Lee criterion [18] states

For a single bit  $\Sigma \Lambda$  modulator with an NTF(Z) is likely to be stable if

$$\max_{\omega} \left| NTF(e^{j\omega}) \right| < 1.5 \tag{2.18}$$

It is the most widely-used approximation criterion in determining the stability condition of the modulator. However, it is only an empirical conclusion which is neither necessary nor sufficient. It is used in the early modeling phase. The actually stable operating condition of the system requires to be verified by simulation.

# 2.7 Noise analysis

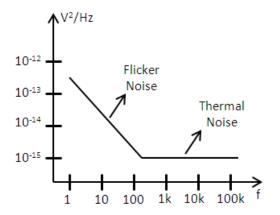

Noise is one of the major factors that affect the modulator's performance. In addition to the quantization noise introduced by quantizer, flicker noise and thermal noise are the primary sources of noise as shown in Figure 2-14.

Figure 2-14 Noise PSD profile

#### 2.7.1 Flicker Noise

Flicker noise is due to trapping and releasing of charge carriers when they move in the channel. It can be modeled as a voltage source connected in series at the gate. As shown in Figure 2-14 and equation (2.19) [19], the noise power is inversely proportional to frequency. It implies that most of the noise power is concentrated at low frequency [19].

$$S_{vf}(f) = \frac{K}{WLC_{ox}f} \left(\frac{V^2}{Hz}\right)$$

(2.19)

To reduce flicker noise, one option is to increase the area of the transistor since the noise power is inversely proportional to the product of width W and length L. In some technologies, K of PMOS is smaller than that of NMOS. Therefore, PMOS transistor is more preferable to be used as input device. To further suppress flicker noise, techniques like correlated double sampling (CDS) and chopper stabilization can be applied. In most of the cases, these methods can reduce the flicker noise to a point where thermal noise becomes dominate. Hence, thermal noise is resulted to be the major contribution of noise.

#### 2.7.2 Thermal noise

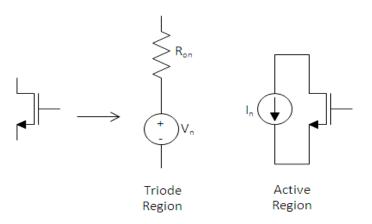

Thermal noise is resulted from the random fluctuation of current, which is caused by thermal motion of the charge carriers in the channel of devices. Thermal noise for a resistor or a MOSFET operating in triode region is approximately constant throughout the frequency spectrum. In practice, it can be modeled as a noise source in series of an ideal noise-free resistor as shown in Figure 2-15. The PSD of the noise voltage is expressed in equation (2.20) [19].

Figure 2-15 Thermal Noise Model of NMOS transistor

$$S_{vt}(f) = 4kTR_{on} \ (V^2/Hz)$$

(2.20)

For a MOSFET operating in active region, thermal noise can be modeled as a noise current source in parallel with a noise-free MOSFET as shown in Figure 2-15. The PSD of the noise voltage is expressed in (2.21) [19].

$$S_{it}(f) = \frac{8}{3}kTg_m \ (A^2/Hz)$$

(2.21)

### 2.8 Performance Metrics

SNR is one of the key performance parameters for all ADCs. The definition of SNR is shown in equation (2.22). This equation indicates that the peak SNR (highest achievable SNR) is achieved when the maximum input signal power is reached. However, the stability condition described in section 2.6 must be satisfied. In order to achieve a high SNR, the noise power must be reduced. This can be achieved by increasing the OSR and order of the loop filter as explained in section 2.5.

$$SNR = 10\log_{10}\left(\frac{P_{\text{signal}}}{P_{\text{noise}}}\right) (\text{dB})$$

(2.22)

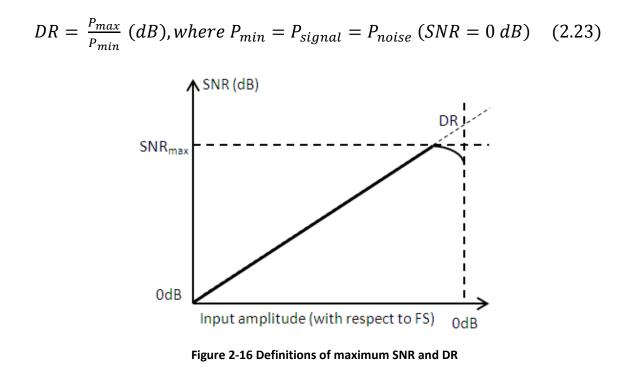

DR (dynamic range) measures the minimum detectable signal of an ADC. It is defined as the ratio of the largest achievable signal power to the smallest achievable signal power as shown in equation (2.23). The smallest achievable signal power is obtained when the signal level is the same as noise level. Furthermore, if the signal level is decreased below the noise floor, it is undetectable. Therefore, DR is directly related to the noise floor and hence the SNR. For an N-bit ideal ADC, DR is equal to SNR. In practical case, DR can be obtained from the plot in Figure 2-16.

ENOB (effective number of bits) measures the resolution of the ADC by specifying the output effective bits. It is defined as equation (2.24). This definition is applicable for all

types of ADCs. Hence, it is usually used to cross compare the resolution of Nyquist ADCs and  $\Sigma\Delta$  ADCs.

$$ENOB = \frac{SNR_{max} - 1.76}{6.02}$$

(bits) (2.24)

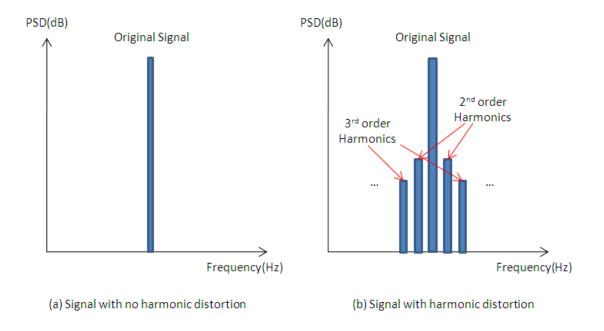

Harmonic distortion is known as those overtone signals with integer number multiples of signal frequency as shown in Figure 2-17. It is due to the non-ideality of the circuit blocks, such as the non-linear gain of amplifiers and insufficient settling time for the sampling capacitor.

Figure 2-17 Harmonic distortion

### Chapter 3 High Temperature Circuit Design

#### 3.1 Background

In industrial applications such as offshore oil drilling, the operational temperature can be ranged from 0 °C to above 200 °C. The device physical behavior over such wide temperature range varies significantly, which may lead to circuit malfunction. There are primarily two temperature-sensitive parameters that affect the circuits. They are studied in details in this section.

#### 3.2 Temperature Effect on Threshold Voltage

Threshold voltage is defined in equation (3.1) [20]. In this equation, many terms are related to temperature so that the relationship between threshold voltage and temperature is not clearly seen. A detailed analysis of every term is shown below [20]:

$$V_{th} = 2\phi_b + \frac{Q_b}{C_{ox}} + V_{fb}$$

(3.1)

$$V_{fb} = \phi_{ms} - \frac{Q_{fc}}{C_{ox}}$$

(3.2)

$Q_b$  is the total charge stored in depletion layer. It can be expressed as equation (3.3).

$$Q_b = \sqrt{2\varepsilon_{si} \times q \times N_A \times 2\phi_b} \tag{3.3}$$

$Q_{fc}$  is the fixed charge due to surface states which arises from the imperfection in silicon oxide interface and doping.  $C_{ox}$  is the gate oxide capacitance. Hence, the Qss/Cox does not vary with temperature once the device is made.

$\Phi$ ms is the work function difference between gate material and substrate. It is defined as (3.4). Eg can be expressed as equation (3.5) [21]. Moreover, from the empirical data, Eg can be simplified as 3.6. For temperature above 300 K, the temperature dependence of Eg can be ignored since the variation amount is too small [21].

$$\phi_{ms} = -\left(\frac{E_g}{2q} + \phi_b\right) \tag{3.4}$$

$$E_g(T) = E_g(0) - \frac{\alpha T^2}{T + \beta}$$

(3.5)

$$E_g(T) = 1.165 - 5 \times 10^{-7} T^2 \ (T < 300^{\circ}\text{C})$$

or  $1.205 - 2.829 \times 10^{-4} T \ (T > 300^{\circ}\text{C})$  (3.6)

$\Phi_{\rm b}$  is referred as Fermi potential, which is the potential difference between the Fermi level and the intrinsic level of the device channel. It can be expressed as (3.7). n<sub>i</sub> is the intrinsic carrier concentration which is expressed in (3.8). By substituting (3.8) into (3.7), a linear relationship between  $\Phi$ b and temperature can be obtained as (3.9).

$$\phi_b = \frac{kT}{q} \ln\left(\frac{N_A}{n_i}\right) \tag{3.7}$$

$$n_i = \sqrt{N_V N_C} e^{-E_g/2kT} \tag{3.8}$$

$$\phi_b = \frac{kT}{q} \ln\left(\frac{N_A}{\sqrt{N_V N_C}}\right) + \frac{kT}{q} \times \frac{E_g}{2kT} = \frac{kT}{q} \ln\left(\frac{N_A}{\sqrt{N_V N_C}}\right) + \frac{E_g}{2q}$$

(3.9)

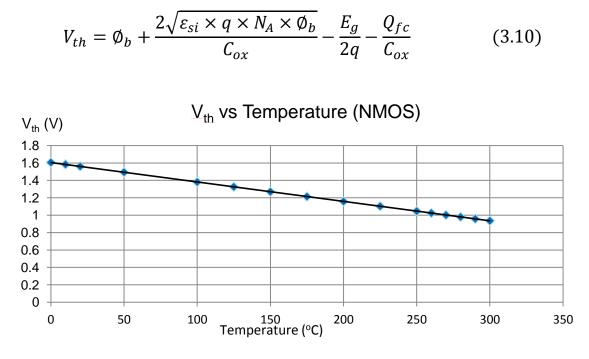

Subsequently, the equation (3.1) can be expanded to (3.10) [22]. As shown in (3.10), two terms are associated with temperature, namely  $\phi_b$  and  $\sqrt{\phi_b}$ . The term  $\sqrt{\phi_b}$  can be ignored due to the value of the coefficient. Therefore, only  $\phi_b$  term is associated with

temperature and hence a linear relationship between threshold voltage and temperature can be approximated. A simple simulation is carried out as shown in Figure 3-1. The plot matches with the approximation [22].

Figure 3-1 Simulation of V<sub>th</sub> against temperature

Practically, the threshold voltage changes in a slope of -2 mv/  $^{\circ}$ C to -4 mv/  $^{\circ}$ C when temperature increases linearly. Quantitatively, the threshold voltage can be extracted from curve and expressed as equation (3.11).

$$V_{thn} = 2.216 - 2.235 \times 10^{-3} T \quad (V) \tag{3.11}$$

#### **<u>3.3 Temperature Effect on Mobility</u>**

Theoretically, electrons (holes) in a doped semiconductor at a certain temperature have thermal energies which allow them to travel in any direction. However, if an electric field E is applied across the semiconductor, the free electrons (holes) are forced to move against (following) the direction of electric filed E. During the trip, the electrons (holes) accumulate momentum under a force F (F=-qE) during the mean free flight and loses momentum when they collide with an impurity atom or been scattered. By equating these two momentums, the drift velocity can be obtained as (3.12) [23].

$$-qE\tau_c = m_e v_d \tag{3.12}$$

$$\mu_e = \frac{v_d}{E} = \frac{q\tau_c}{m_e} \tag{3.13}$$

$$\mu_h = \frac{\nu_d}{E} = \frac{q\tau_c}{m_h} \tag{3.14}$$

$\tau_c$  is the mean free time, which is defined as the average distance that a charge carrier travels before been scattered. m<sub>e</sub> is the effective mass of electron. v<sub>d</sub> is the drift velocity. Mobility is defined by the ratio of the drift velocity to the applied electric field as shown in (3.13) and (3.14).  $\tau_c$  is primarily affected by two scattering mechanisms, namely the lattice scattering and impurity scattering.

Lattice scattering is the scattering of the charge carriers with atoms in a lattice. Theoretically, as temperature increases above 0 K, atoms which form the lattice start to vibrate and cause the variation of potential and emission of phonons. Phonons transfer energy between atoms and charge carriers. When temperature increases, the vibration becomes more intense. As a result, more phonons are emitted and the mobility is decreased. Impurity scattering results from the ionized impurities (donors and acceptors). As the charge carrier travels through the lattice, it is deflected by the donors and acceptors due to the Coulomb force. The scattering effect depends on the speed of the charge carrier and the impurity concentration (doping concentration). As temperature increases, the speed of the charge carrier increases and also the impurity atoms are ionized. When temperature is above a certain value, the effect of impurity scattering becomes insignificant compared to lattice scattering.

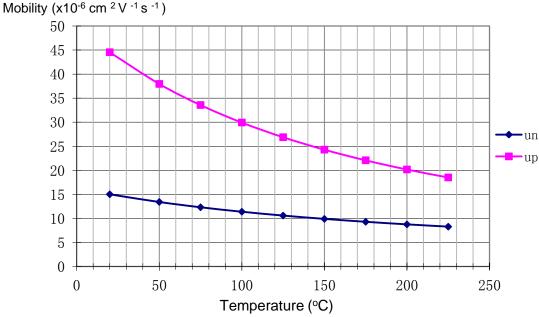

As an overall effect, mobility decreases as temperature increases. Experimentally, the relationship between mobility and temperature is shown in equation (3.15) [24]. A simulation of mobility change against temperature is shown in Figure 3-2.

$$\mu_{eff}(T) \approx \mu_{eff}(T_0) \times \left(\frac{T}{T_0}\right)^{-1.5}$$

(3.15)

Figure 3-2 Simulation of mobility against temperature

#### 3.4 Temperature Effect on Passive Components

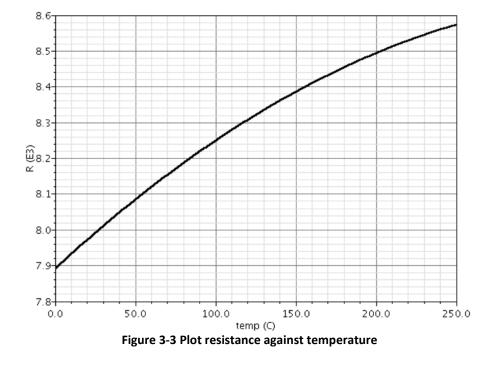

Passive components, namely resistors and capacitors, are subject to the variation of temperatures. Their relationships with temperature are modeled using temperature coefficients as shown in equation (3.16) and (3.17) [25]. The temperature coefficients are subject to processes. In most of the cases, the  $2^{nd}$ -order temperature coefficients are too small and can be neglected. This results in the approximation of a linear relationship with temperature. Figure 3-3 shows a simulation of resistance against temperature [25].

$$R_T = R_{T_0} \times [1 + TC1 \times (T - T_0) + TC2 \times (T - T_0)^2]$$

(3.16)

$$C_T = C_{T_0} \times [1 + TC1 \times (T - T_0) + TC2 \times (T - T_0)^2]$$

(3.17)

#### 3.5 SOI process

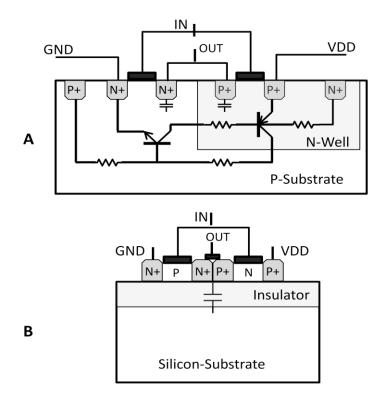

Silicon on Insulator (SOI) CMOS technology has been adopted from late 1990's. Unlike the conventional bulk CMOS process, SOI process employs a layer of electrical insulator between the substrate and the silicon device layer as shown in Figure 3-4B [26]. This structural difference introduces several advantages compared to bulk CMOS as shown in Figure 3-4A, which significantly improves the performance of the circuits. Due to the existence of the insulator layer, the junction capacitance is gradually reduced as well as the leakage current. As a result, the power dissipation is reduced significantly. Meanwhile, the SOI structure isolates the device not only from the substrate, but also from each other. On contrary, the latch up problem in bulk CMOS process is resolved in SOI process since the bottom of the device is fully covered by insulator. This eliminates the substrate noise and crosstalk and improves the circuit performance, especially for analog circuits. Moreover, since the junction leakage has been significantly reduced, SOI based circuit is reported to be capable of operating in high temperature environment. Therefore, in this work, SOI CMOS process is chosen for design and fabrication [27].

Figure 3-4 Cross section of bulk CMOS inverter (A) and SOI CMOS inverter (B) [23]

#### <u>3.6 High temperature design techniques</u>

As introduced in section 3.2 and 3.3, the decreases of threshold voltage and mobility are the major concerns for analog circuit design in high temperature environment. In Figure 3-1, when temperature changes from 0 °C to 200 °C, the threshold voltage decreases by over 60%. One challenge is that the biasing points of the transistors need to be carefully selected in order to maintain all transistors saturated. Moreover, as threshold voltage decreases, the overdrive voltage increases which leads to the quadratic increase of biasing current. On the other hand, the decrease of mobility against temperature increase is neither linear nor quadratic as shown in equation (3.15). This makes it difficult to develop compensation techniques. Since both threshold voltage and mobility change at the same time when temperature varies, it is difficult to eliminate the effects caused by the two parameters at the same time. Moreover, compared to threshold voltage which shows a linear dependence of temperature, the temperature dependence of mobility is neither linear nor quadratic. As a result, the compensation becomes difficult.

In this section, some high temperature design techniques are studied in details in order to resolve the high temperature issues.

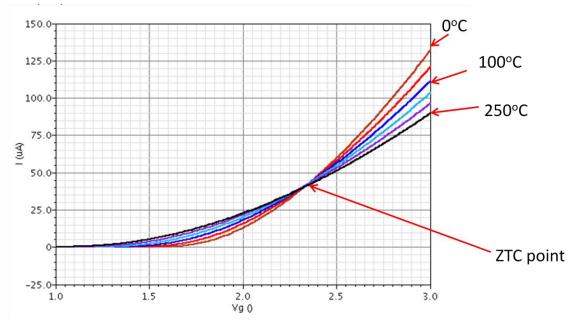

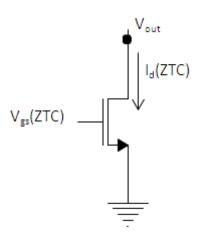

#### 3.6.1 Zero temperature coefficient biasing

As shown in Figure 3-1 and Figure 3-2, it is observed that, both the threshold voltage and mobility decrease while temperature increases. However, the decrease of  $V_{th}$  leads to the increase of drain current while the decrease of mobility leads to the decrease of drain current. Therefore, there should be a point where the two effects are cancelled and the drain current remains constant. Such a point is called ZTC (Zero Temperature Coefficient)

biasing point [28]. Figure 3-5 shows a plot from the simulation of the drain current by sweeping the gate voltage at different temperatures. The ZTC point is the intersection of all curves.

Figure 3-5 Simulated drain current under DC sweep of gate voltage at different temperatures

An analytical expression of ZTC biasing voltage is shown in equation (3.18). In this expression,  $p_0$  and  $q_0$  are the parameters extracted from equation (3.11). m denotes the power dependence of I<sub>d</sub> with Vgs – Vth. When m = 1, the resulted Vgs (ZTC) corresponds to the ZTC biasing voltage in linear region. When m = 2, the resulted Vgs (ZTC) corresponds to the ZTC biasing voltage in saturation region. T1 and T2 correspond to the minimum and maximum temperatures of the operational temperature range. This expression is as good as an approximation which involves a least squares minimization. In practice, the calculated value of V<sub>gs</sub> is accurate with maximum 10% error [28].

$$V_{gs}(ZTC) \approx -\frac{1}{6}p_0(T_1 + T_2) \times (2m - 3) + q_0$$

(3.18)

By applying ZTC biasing at gate, the estimated drain current can be expressed in equation (3.19) and (3.20) [28].

$$I_d(ZTC) \approx \mu_{eff}(T_0)C_{ox}\frac{W}{L} \times \frac{T_0}{1.5}p_0V_{DS} \quad (linear \ region) \qquad (3.19)$$

$$I_d(ZTC) \approx \frac{1}{2} \mu_{eff}(T_0) C_{ox} \frac{W}{L} \times (\frac{mT_0}{1.5} p_0)^2 \quad (saturation \ region) \quad (3.20)$$

Although ZTC biasing is effective in stabilizing the drain current against temperature variations, limitation has been found during applications. It is observed that the ZTC biasing voltage is usually much high than threshold voltage. For example, as shown in Figure 3-6, at room temperature,  $V_{th}$  is 1.5 V and the calculated  $V_{gs}$  (ZTC) is about 2.3 V. This leads to a large overdrive voltage and puts a limitation of high drain-source voltage  $V_{out}$  for saturation, which limits the output swing. Therefore, ZTC biasing technique is not applicable when large output swing for cascode stage amplifier is required.

Figure 3-6 Transistor biased at ZTC biasing point

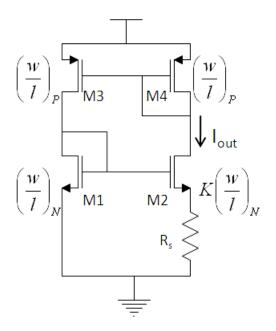

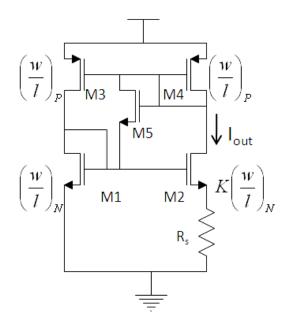

#### 3.6.2 Constant gm (transconductance) biasing circuit:

Besides the ZTC biasing technique which provides a constant current over the temperature range, constant gm biasing is another effective method in high temperature circuit design. In this technique, instead of generating a temperature independent current, a constant gm is more of the interest for stable amplifier AC performance over the temperature range.

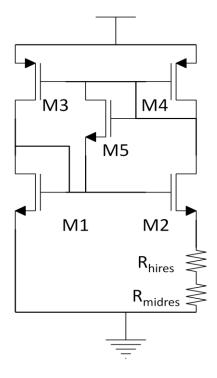

The constant gm biasing circuit is shown in Figure 3-7 [29]. It comprises of two PMOS transistors (M3 and M4) and two NMOS transistors (M1 and M2). M1 and M2 are connected in current-mirror configuration which gives (3.21).

Figure 3-7 Constant gm biasing circuit

$$V_{gs1} = V_{gs2} + I_{out}R_s (3.21)$$

$$\therefore \sqrt{\frac{2I_{out}}{\mu_n C_{ox}(W/L)_N}} + V_{th1} = \sqrt{\frac{2I_{out}}{\mu_n C_{ox} K(W/L)_N}} + V_{th2} + I_{out} R_s (3.22)$$

If body effect is ignored, the threshold voltages of M1 and M2 are the same. This leads to equation (3.23).

$$\sqrt{\frac{2I_{out}}{\mu_n C_{ox}(W/L)_N} \left(1 - \frac{1}{\sqrt{K}}\right)} = I_{out} R_s \tag{3.23}$$

$$\frac{2I_{out}}{\mu_n C_{ox} (W/L)_N} \left(1 - \frac{1}{\sqrt{K}}\right)^2 = I_{out}^2 R_s^2$$

(3.24)

After dividing both sides by I<sub>out</sub> and rearranging,

$$I_{out} = \frac{2}{\mu_n C_{ox} (W/L)_N {R_s}^2} \left(1 - \frac{1}{\sqrt{K}}\right)^2$$

(3.25)

For a normal transistor working in saturation, the gm is given by (3.26).

$$g_m = \sqrt{2\mu_n C_{ox} (W/L)_N} \tag{3.26}$$

Substitute (3.25) in (3.26),

$$g_m = \frac{2}{R_s} \left( 1 - \frac{1}{\sqrt{K}} \right) \tag{3.27}$$

The obtained gm as shown in equation (3.27) [29] is mobility and process independent. It only depends on K and  $R_s$ . K is the aspect ratio parameter which is only affected by mismatch.  $R_s$  is the resistor which is linearly dependent of temperature. The temperature compensation for resistor is covered in next section.

Constant gm biasing technique only keeps a constant transconductance but does not provide a constant current. Therefore, transistors which are not biased by constant gm biasing circuit should be designed to be saturated in different temperatures. Another issue of constant gm biasing circuit is that it may not be turned on during circuit start up. In equation (3.24), when both left hand side and right hand side are divided by I<sub>out</sub>, the I<sub>out</sub> is assumed to be non-zero. However, when the circuit is switched on, it may go to the state when no currents flow through M1 and M2, which could also be a stable state. In order to solve this issue, a start up circuit is added in as shown in Figure 3-8. It forces a small current to flow through path M5 and inject into the drain of M1. Once there is current in path M1, the double current-mirror feedback architecture forces I<sub>out</sub> to reach the desired current.

Figure 3-8 Constant gm biasing circuit with start-up transistor

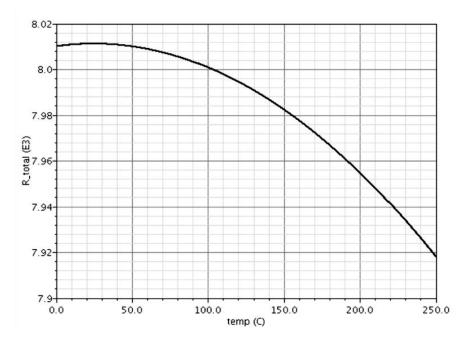

#### 3.6.3 Resistor Temperature Coefficients Cancelling

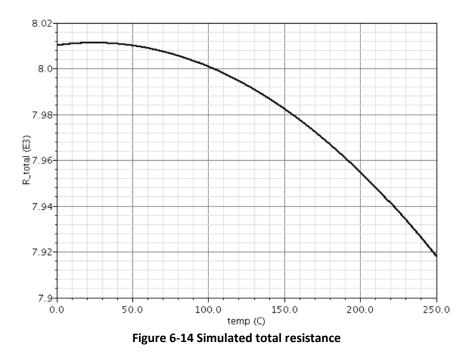

As introduced in section 3.4, the temperature dependence of resistor can be approximated as a linear equation with TC (temperature coefficients). In modern processes, materials can be of either negative or positive TC. With the series combination of the two materials and proper sizing, the overall resistance can be temperature independent. The concept is shown in Figure 3-9.

$$\begin{cases} R_{1} = R_{1T_{0}} \times [1 + TC_{1} \times (T - T_{0})] \\ R_{2} = R_{2T_{0}} \times [1 + TC_{2} \times (T - T_{0})] \end{cases}$$

Figure 3-9 Series connection of two resistors with different TC

If it is assumed that  $TC_1$  is positive and  $TC_2$  is negative, the total resistance  $R_{total}$  as shown in (3.26) is independent of temperature if the sizes of  $R_{1T0}$  and  $R_{2T0}$  satisfy equation (3.27). A simulation result of two serially connected resistors with opposite temperature coefficients is shown in Figure 3-10. The two resistors are properly sized to cancel temperature effect. The combined resistance shows a 1.13% variation from temperature range 0 °C to 250 °C. Compared to the resistance shown in Figure 3-3 (variation of 8.6%), the improvement is significant.

Figure 3-10 Simulation of R<sub>total</sub>

$R_{total} = R_1 + R_2 = R_{1T_0} + R_{2T_0} + (T - T_0) (R_{1T_0} T C_1 + R_{2T_0} T C_2)$ (3.26)  $R_{1T_0} T C_1 = -R_{2T_0} T C_2$ (3.27)

# Chapter 4 Switched Capacitor Circuit

### **Fundamentals**

#### 4.1 Concept of Switched Capacitor Circuit

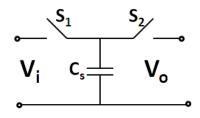

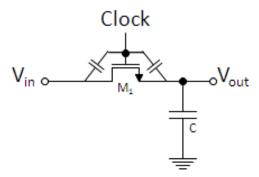

In many applications such as discrete-time filters and charge pumps, switched capacitor circuit is one of the major circuit elements. The fundamental operating concept is based on charge redistribution between capacitors [30]. As shown in Figure 4-1, at phase 1 when S1 is switched on and S2 is switched off, charges are stored at  $C_s$  as shown in equation (4.1).

Figure 4-1 Switched capacitor circuit

$$q_i = C_s V_i \tag{4.1}$$

At phase 2 when S1 is switched off and S2 is switched on, charges are transferred out. The remaining charges are expressed as (4.2).

$$q_o = C_s V_o \tag{4.2}$$

The transferred charges  $\Delta q$  is

$$\Delta q = q_o - q_i = C_s (V_o - V_i)$$

(4.3)

As current *I* can be expressed as equation (4.4)

$$I = \frac{\Delta q}{\Delta t} \tag{4.4}$$

39

Therefore,

$$I = \frac{C_s(V_o - V_i)}{\Delta t} = C_s(V_o - V_i) \times f$$

(4.5)

It means that if switches S1 and S2 are switched on/off in frequency of f, constant current *I* is generated. The equivalent resistance R is (4.6) [30].

$$R = \frac{V}{I} = \frac{V_o - V_i}{C_s (V_o - V_i) \times f} = \frac{1}{C_s f}$$

(4.6)

#### 4.2 CMOS Switches

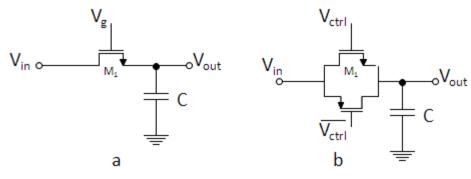

Simple switch is built on either PMOS or NMOS. For a simple NMOS switch as shown in Figure 4-2a, when  $V_g = V_{dd}$ , the switch is on. For  $V_{in} = V_{dd}$  and  $V_{out} = 0$ , C is charging. However, for the switch to be turned on,  $V_g$  must be larger than  $V_{th}$ . Therefore, the maximum value of  $V_{out}$  can only be  $V_{dd} - V_{th}$ . In addition, when body effect is considered,  $V_{th}$  is increased. This further decreases maximum value of  $V_{out}$ . For PMOS switch, the same analysis is applied. The result is that the minimum value of  $V_{out}$  is  $V_{th}$  when  $V_g = 0$  and  $V_{in} = 0$ . In order to achieve a full range of  $V_{out}$ , CMOS transmission gate is adopted. As shown in Figure 4-2b, it comprises of a PMOS and a NMOS. When  $V_{ctrl}$  is 0V, both transistors are switched off. When  $V_{ctrl}$  is 5V, the output voltage  $V_{out}$  follows input voltage  $V_{in}$ . For  $V_{in}$  larger than  $V_{dd} - V_{th}$ , NMOS is in cutoff region. PMOS is in saturation region. C is charged through PMOS and the maximum value can reach  $V_{dd}$ . Similarly for  $V_{in}$  smaller than  $V_{th}$ , PMOS is in cutoff region and NMOS is in saturation region, C is discharged through NMOS and the minimum value can reach 0V. Therefore, full range of  $V_{out}$  can be achieved by using transmission gate [29].

Figure 4-2 NMOS switch (a) and transmission gate switch (b)

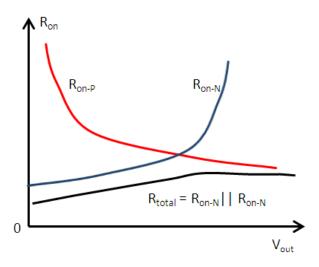

The on-resistance of NMOS switch and PMOS switch are defined in equations (4.7) and (4.8). Therefore, the total on-resistance of transmission gate is calculated using  $R_{on-N} \parallel R_{on-P}$ . Figure 4-3 shows the on-resistance of PMOS switch, NMOS switch and transmission gate as a function of input voltage. The maximum on-resistance of transmission gate is obtained when input voltage is at the center when both transistors are in saturation. To reduce the on-resistance, the aspect ratios of NMOS and PMOS are required to be increased. However, this will increase the area of the transistors and the increase of parasitic capacitance will lead to a reduction in bandwidth. In this work, since the sampling frequency is not very high, the requirement on-resistance is not stringent.

Linear Region:

$$R_{on} = \frac{2}{k[2(V_{dd} - |V_{th}| - (V_{dd} - V_{out}))]}$$

(4.7)

Saturation Region:

$$R_{on} = \frac{2(V_{dd} - V_{out})}{k(V_{dd} - V_{out} - |V_{th}|)^2}$$

(4.8)

Figure 4-3 On-resistance of transmission gate switch

#### 4.3 Non-Ideal Effects of CMOS Switches

#### 4.3.1 Charge Injection

Charge injection is one of the major error mechanisms in switched capacitor circuits. It is introduced by the non-ideality of the switch [31]. As shown in Figure 4-4, the switch is built by a single NMOS transistor. When the switch M1 is on, a channel is formed at the oxide-silicon interface. Charges are stored inside the inversion layer. When M1 is turned off, charges exit through the source and drain. The charge injection to  $V_{in}$  does not have much effect. However, the charge injection to capacitor introduces additional charges  $\Delta q$ which is considered as offset to the sampled output signal. Moreover, the amount of charges injected to the capacitor is too difficult to be determined since it depends on many parameters such as threshold, process variation and clock transition time. In switched capacitor circuit, charge injection is one of main sources of non-linearity.

Figure 4-4 Charge injection of MOS switch

#### 4.3.2 Clock Feedthrough

As shown in Figure 4-5, the clock signal is coupled with the sampling capacitor through the gate-source capacitor. Similar to charge injection, it introduces offset to the sampled output signal. The offset voltage can be express in equation (4.9), where  $C_{ov}$  is the overlap capacitance per unit width [31].

Figure 4-5 Clock feed through of MOS switch

$$\Delta V = V_{g_{M1}} \frac{WC_{ov}}{WC_{ov} + C} \tag{4.9}$$

Clock feedthrough is independent of the input level and embedded as a constant offset to the circuit. Its effect depends on the size of the switch as well as the size of the sampling capacitor.

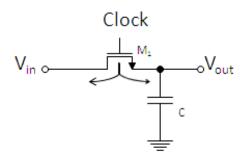

#### 4.3.3 Bottom plate sampling technique

The bottom plate sampling technique [32] is an effective way to reduce the effect of charge injection. As shown in Figure 4-6, two switches S1 and S2 are placed at the two plates of the capacitor. During the sampling phase, both switches are turned on, which is the same as phase one of Figure 4-1. However, at the transition to hold phase, there is a small delay between S1 and S2. As the bottom plate of C is connected to ground, when S2 is switched off first, a fixed amount of charge is injected on to C. After a small delay, switch S1 is switched off. Since the bottom plate of C is already opened, no charge will be injected on C. Therefore, compared to normal switched capacitor circuit as shown in Figure 4-1, bottom plate sampling technique samples a fixed amount of charges on C. It can be modeled as a DC offset to the output which does not affect the linearity. Moreover, such DC offset can be further reduced in a fully differential circuit topology.

Figure 4-6 Bottom plate sampling techniques

#### 4.4 Switched capacitor integrator

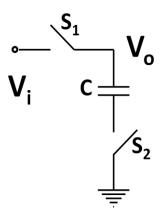

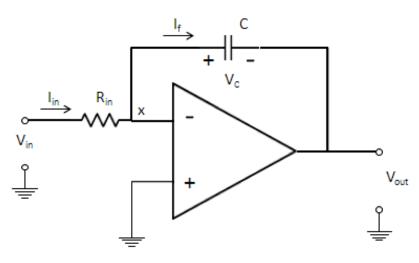

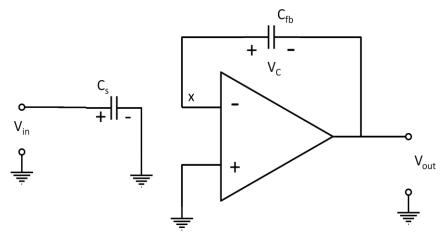

#### 4.4.1 Switched Capacitor Integrator Operation Principle

An integrator is a circuit block performing a time domain integration of input voltage. In frequency domain, the integration process is a form of 1<sup>st</sup>-order low pass filtering. A

traditional continuous-time RC integrator [33] is shown in 4-7. The derivation of transfer function is shown in equations (4.10), (4.11), (4.12) and (4.13). As shown in (4.13), the output voltage is an integration of the input voltage with a time constant  $R_{in}C$ .

Figure 4-7 RC integrator schematic

$$V_{c} = \frac{Q}{C} = V_{x} - V_{out} = -V_{out}$$

(4.10)

$$\therefore -\frac{dV_{out}}{dt} = \frac{dQ}{Cdt} \tag{4.11}$$

$$I_{in} = I_f = \frac{V_{in}}{R_{in}} = -\frac{CdV_{out}}{dt}$$

(4.12)

$$V_{out} = -\frac{1}{R_{in}C} \int_0^t V_{in} dt \qquad (4.13)$$

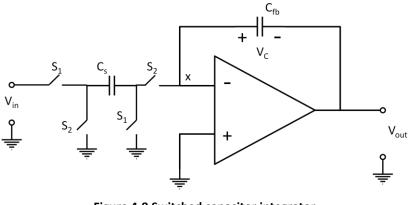

The switched capacitor based implementation of integrator is achieved by replacing the input resistor with a switched capacitor. Figure 4-8 shows the integrator architecture which replacing  $R_{in}$  with switched capacitor  $C_s$ . The fundamental concept is to sample and transfer charges from input to feedback capacitor  $C_{fb}$  through the median  $C_s[34]$ .

Figure 4-8 Switched capacitor integrator

At phase one (t= -T), switches S1 are switched on while switches S2 are switched off as shown in Figure 4-9. The capacitor  $C_s$  follows Vin and stores the charges. Capacitor keeps the previous charges at t= -1.5T. Therefore,

$$Q_{s}[(n-1)T_{s}] = C_{s}V_{in}[(n-1)T_{s}]$$

(4.14)

$$Q_{fb}[(n-1)T_s] = Q_{fb}[(n-1.5)T_s]$$

(4.15)

Figure 4-9 Clock phase 1

At phase two (t= -0.5T), switches S1 are switched off while S2 are switched on as shown in Figure 4-10. The capacitor  $C_s$  transfers the charges (previously stored in phase one) onto  $C_{fb}$ . Therefore,

$$Q_s[(n-0.5)T_s] = 0 (4.16)$$

$$Q_{fb}[(n-0.5)T_s] = Q_{fb}[(n-1)T_s] - C_s V_{in}[(n-1)T_s]$$

(4.17)

Figure 4-10 Clock phase 2

At the 2<sup>nd</sup> phase one,

$$Q_{s}[(n)T_{s}] = C_{s}V_{in}[(n)T_{s}]$$

(4.18)

$$Q_{fb}[(n)T_s] = Q_{fb}[(n-1)T_s] - C_s V_{in}[(n-1)T_s]$$

(4.19)

By substituting (4.20) and (4.21),

$$V_{out} = -\frac{Q_{fb}}{C_{fb}} \tag{4.20}$$

$$V_{out} = \frac{Q_s}{C_s} \tag{4.21}$$

Equation (4.22) can be obtained,

$$-V_{out}C_{fb}[(n)T_s] = -V_{out}C_{fb}[(n-1)T_s] - C_sV_{in}[(n-1)T_s]$$

(4.22)

After applying Z-transform, the transfer function of switched capacitor integrator is shown in (4.25). It is a form of 1<sup>st</sup> order digital low pass filter with gain of  $C_s/C_{fb}$  [34].

$$V_{out}[(n)T_s] - V_{out}[(n-1)T_s] = \frac{C_s}{C_{fb}} V_{in}[(n-1)T_s]$$

(4.23)

$$V_{out}(1 - Z^{-1}) = \frac{C_s}{C_{fb}} V_{in} Z^{-1}$$

(4.24)

$$\frac{V_{out}}{V_{in}} = \frac{C_s}{C_{fb}} \frac{Z^{-1}}{(1 - Z^{-1})} = \frac{C_s}{C_{fb}} \frac{1}{Z - 1}$$

(4.25)

#### 4.4.2 Non-ideality due to finite gain of amplifier

The transfer function (4.25) is derived based on the assumption of an ideal amplifier. In practice, however, the actual gain of the amplifier is finite. Therefore, equation (4.25) should be modified to (4.26) [35].

$$\frac{V_{out}}{V_{in}} = \frac{\beta}{Z - (1 - \alpha)} \tag{4.26}$$

with

$$\beta = \frac{C_s/C_{fb}}{1 + \frac{1}{A_0}(1 + \frac{C_s}{C_{fb}})}$$

$$\alpha = \frac{\beta}{A_0} \approx \frac{C_s/C_{fb}}{A_0}$$

The finite gain of amplifier  $A_0$  reduces the gain of the integrator (with factor of  $\beta$ ) and causes integrator leakage (with factor of  $\alpha$ ). In a switched capacitor modulator, such non-ideal effects will lead to the degradation of performance [35].

## Chapter 5 Design of High Temperature ΣΔ Modulator

#### **5.1 Review of Previously Published High Temperature ΣΔ Modulators**

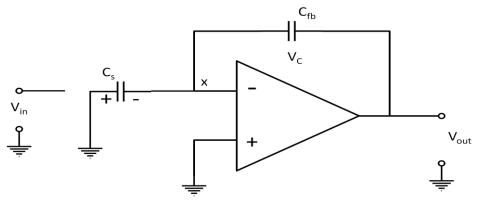

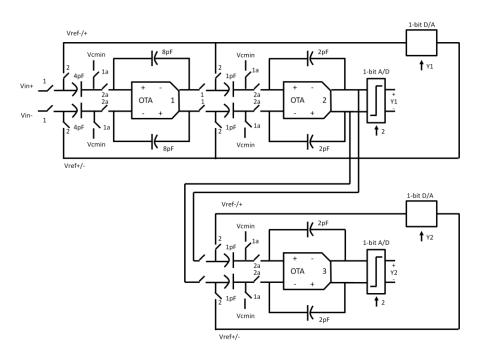

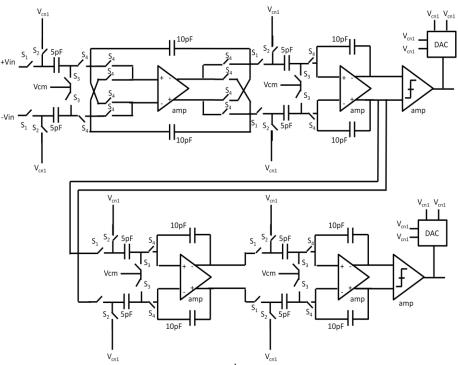

A 2<sup>nd</sup>-order single stage modulator and a 3<sup>rd</sup>-order 2-1 MASH cascaded  $\Sigma\Delta$  modulator were proposed in [36] as shown in Figure 5-1. Both modulators adopt switched capacitor architecture with single bit quantization and OSR of 256. The 3<sup>rd</sup>-order MASH modulator utilizes the 2<sup>nd</sup>-order modulator as its 1<sup>st</sup> stage. The 2<sup>nd</sup> stage comprises of a 1<sup>st</sup>-order  $\Sigma\Delta$ modulator. Besides, it also adopts a software based error cancellation block in 3<sup>rd</sup>-order MASH modulator. The chip is fabricated using 5V 1.5 µm double-poly standard CMOS process.

Figure 5-1 System schematic of a  $2^{nd}$  order single stage modulator and a  $3^{rd}$  order 2-1 MASH cascaded  $\Sigma\Delta$  modulator [36]

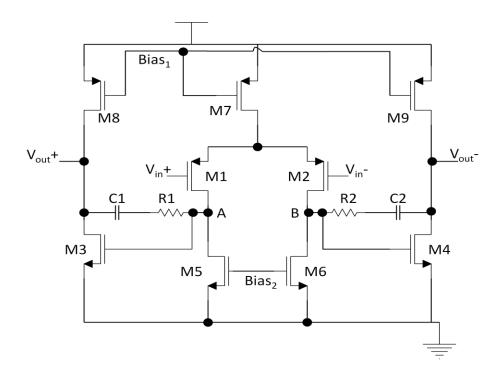

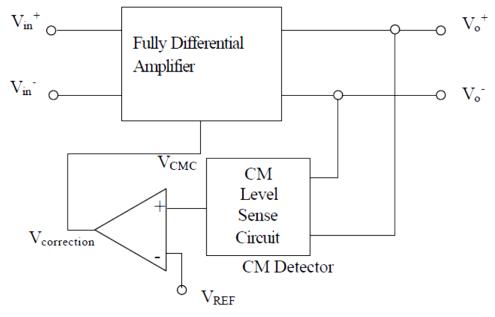

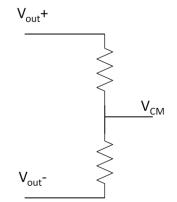

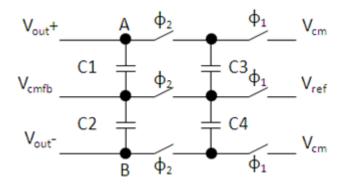

In the implementation of the integrator, a fully differential folded cascode amplifier is applied. The common-mode feedback circuit adopts switched capacitor architecture with minimum sized transmission gate switches in order to limit the high temperature leakage current. A latched comparator is used for the single bit quantizer. The circuit is tested at different temperatures. The result is shown in Table 5-1. The amplifier shows a gain of 64 dB at room temperature and 53 dB at 255 °C.

| Temperature | U1 Gain | CMFB Clock | Temperature | U2 Gain | CMFB Clock |

|-------------|---------|------------|-------------|---------|------------|

| (°C)        | (dB)    | Frequency  | (°C)        | (dB)    | Frequency  |

| 25          | 64      | 256KHz     | 26          | 63      | 256KHz     |

| 78          | 64      | 256KHz     | 79          | 62      | 256KHz     |

| 183         | 63      | 256KHz     | 163         | 55      | 256KHz     |

| 239         | 55      | 3.2MHz     | 230         | 54      | 3.2MHz     |

| 255         | 53      | 3.2MHz     | 251         | 53      | 3.2MHz     |

Table 5-1 Amplifier open-loop gain at different temperatures [36]

As shown in Table 5-2, the overall system shows a maximum SNDR of 88 dB at 223  $^{\circ}$ C and 80 dB at 255  $^{\circ}$ C. In room temperature, the SNDR decreased to around 75 dB.

| Temperature (oC) | Max SNDR (dB) |

|------------------|---------------|

| 25               | 75            |

| 100              | 79            |

| 166              | 83            |

| 223 | 88 |

|-----|----|

| 255 | 80 |

In this design, a 5V 1.5 µm standard CMOS process is chosen which brings some process related disadvantages such as high temperature leakage current and substrate latch up. Moreover, the chosen architecture does not have a feed forward path. This may lead to large swing of the internal nodes. The chosen architecture of amplifier is folded cascode which ensures the high DC gain and driving strength. However, the output swing is limited which may lead to the limitation of dynamic range. The switched capacitor based common-mode feedback circuit also suffers from the high temperature troop. As shown above, the gain of the amplifier varies about 11 dB from room temperature to 255 °C. The 3<sup>rd</sup>-order modulator does not show a superior performance over 2<sup>nd</sup>-order modulator since it is more sensitive to amplifier common-mode voltage drift. Some effective high temperature design techniques should be implemented to compensate the high temperature issues.

Another  $2^{nd}$ -order modulator and a  $4^{th}$ -order 2-2 cascade modulator were proposed in [37] as shown in Figure 5-2. Similar to [36], both modulators adopt switched capacitor architecture with single bit quantization and OSR of 256. The  $4^{th}$ -order modulator is built with a  $2^{nd}$ -order modulator as the first stage, followed by another  $2^{nd}$ -order modulator. The chip is fabricated using 0.5 µm SOS CMOS process.

Figure 5-2 System schematic of a 2<sup>nd</sup>-order single stage modulator and a 4<sup>th</sup> order 2-2c cascaded modulator [37]

In this implementation, it employs the chopper circuit configuration for the first stage integrator, which is helpful in reducing low frequency noises. Fully differential folded cascode amplifier architecture with a modified wide swing cascode biasing circuit is proposed. It applies a continuous-time common-mode feedback method to control the output common-mode voltage.

The circuit is tested at 25 °C, 150 °C and 200 °C. The result is shown in Table 5-1. The amplifier shows a gain of 2298 (67 dB) at 25 °C and 1117 (61 dB) at 200 °C. The peak SNDR achieved is 92.3 dB at 25 °C and 80.6 dB at 200 °C.

| Parameter                 | T= 25 °C | T= 150 °C | T= 200 °C |  |

|---------------------------|----------|-----------|-----------|--|

| Opamp Measurement Summary |          |           |           |  |

| Gain                      | 2298     | 1611      | 1117      |  |

| GBW                       | 7.85 MHz | 5.60 MHz  | 4.99 MHz  |  |

Table 5-3 Summary of measurement results [37]

| Slew Rate (V/us)      | 4.4  | 4.4  | 4.4  |  |

|-----------------------|------|------|------|--|

| Power(mW)             | 4.39 | 4.36 | 4.51 |  |

| Modulator Measurement |      |      |      |  |

| Peak SNR (dB)         | 92.7 | 86.9 | 81.1 |  |

| Resolution (bits)     | 15.5 | 14.9 | 13.5 |  |

| Peak SNDR (dB)        | 92.3 | 86.7 | 80.6 |  |

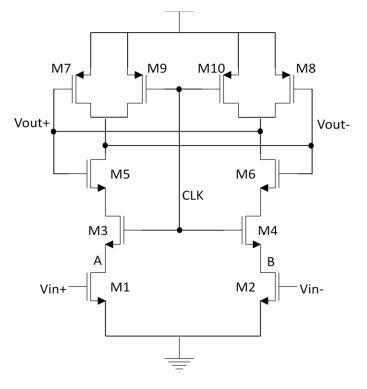

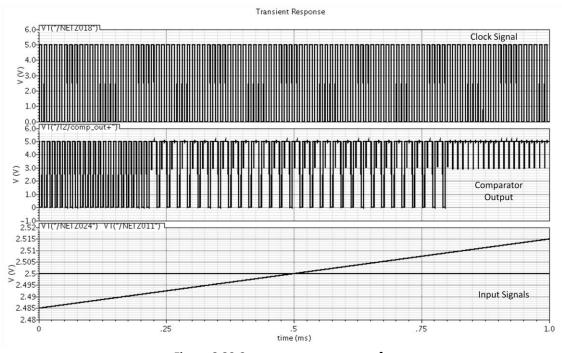

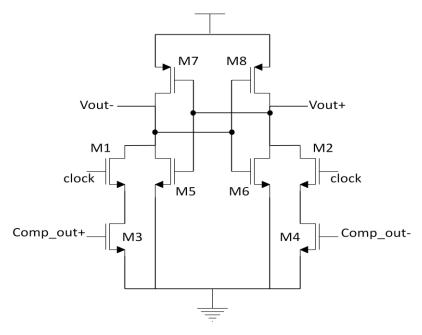

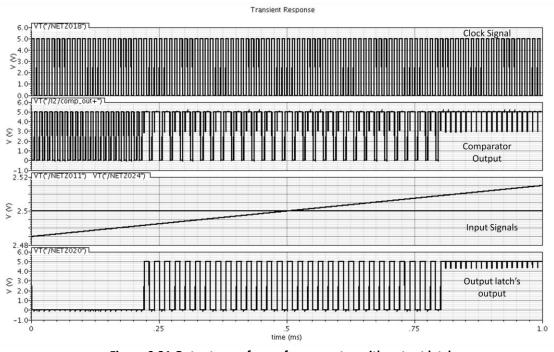

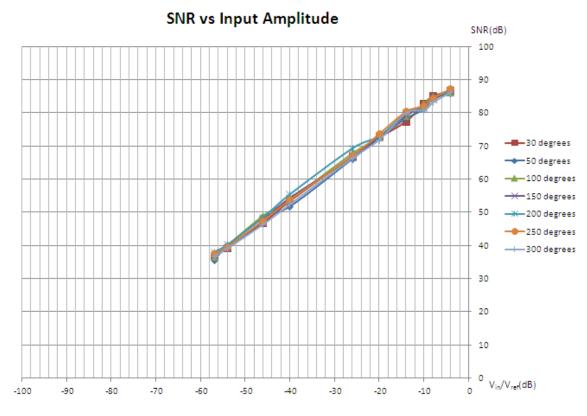

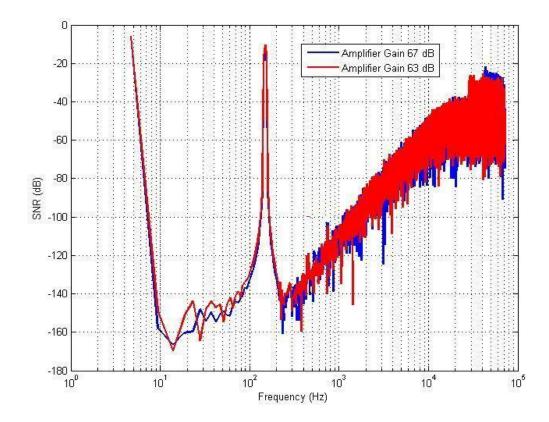

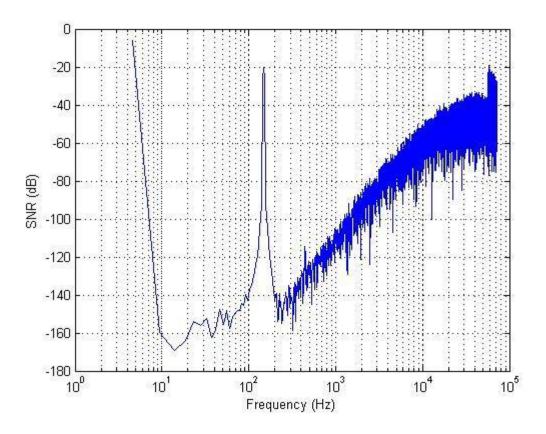

In this design, instead of standard CMOS process, a 0.5 µm SOS CMOS process is chosen. This reduces the substrate latch up as well as high temperature leakage current. Similar to [36], it adopts fully differential folded cascode architecture for integrator. Moreover, it uses a modified wide swing cascode biasing circuit and continues time common-mode feedback circuit. As a result, the amplifier shows a more consistent performance over the temperature range. However, the drawback of low output swing of folded cascode architecture still affects the performance of the overall system since the SNDR dropped about 12 dB from 25 °C to 200 °C. The 4th order modulator and 2<sup>nd</sup>-order modulator show similar performance for OSR larger than 128 due to the dominance of noises other than quantization noise. Some effective high temperature design techniques should be implemented to compensate the high temperature issues.