# TIME-MULTIPLEXED INTERCONNECTION NETWORK FOR FIELD-PROGRAMMABLE GATE ARRAYS

Xiaolei Chen

(B. Sc. University of Science & Technology of China)

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

February 2012

# Acknowledgements

I would like to thank my supervisor Dr. Ha Yajun for his support and guidance. He dedicated much time to consistently building up my background and patiently leading me to the right direction in my research. Also, he consistently shows great confidence on me, so that I have been able to come all the way through these six years. I would like to thank Dr. Vaugh Betz, the author of the VPR tool and the book *Architecture and CAD for Deep-Submicron FPGAs*. I have never met him personally, and the only one interaction between him and me was an Email exchange. I "got to know" and learned from him through my experiences with the source codes and the book, which have had a profound effect on my PhD studies and my life. I would like to express my sincere thanks to Dr. Akash Kumar. He has been keeping an eye on my project and consistently giving constructive suggestions and comments for the past years. He also kindly invited me to attend his weekly network-on-chip (NoC) seminars in academic year 2010 - 2011. In this seminar series, I had the opportunity to regularly present my work and get helpful feedbacks and comments from a group of bright and enthusiastic fellow students.

I would like to thank Mr. Hanyu Liu. In the Fall of 2008, he quickly completed the first version of a global router for FPGAs with time-division multiplexed (TDM) interconnects. That global router, for the first time, enabled me to get a sense of what the pros and cons of TDM interconnects are. Also I would like to thank Mr. Syed Rizwan, Mr. Loke Wei Ting, and Mr. Shakith Fernando. I have learned a lot from research discussions with them.

It has been a great pleasure to spend my PhD years at Signal Processing & VLSI Lab. I would like to acknowledge all in the Lab for your friendship. Thanks to Wei Ying, Tian Xiaohua, Li Yanhui, Yu Heng, Zhang Wenjuan, Shakith Fernando, Dong Bo, Pu Yu, He Lin, Chen Jiangzhong, Yang Zhenglin, Zhou Xiaodan, Tan Jun, Cheng Xiang, Zhang Xiaoyang, Wang Lei and Li Yong Fu. Since I take longer time to finish my PhD than most others, my thank-list is correspondingly longer than normal. My thanks also go to our dear lab officers: Mr. Teo Seow Miang and Ms. Zheng Huan Qun.

I would like to thank my parents and brother for their love and support. If humans had a second life, I wish that I could be their son and his brother for one more time. When I started on this project, I just got to know Ping. By today, I am almost convinced that she is *the one* with whom I want to spend the rest of my life. Thanks a lot for her accompany and love, which have proved to be crucial in the later stages of my PhD studies.

Last but not the least, my studies and research here are financially supported by National University of Singapore and Ministry of Education, Singapore. I would also like to thank Singapore people, numerous of which have displayed great friendship and kindness to me during the past six years.

# Summary

In FPGAs, interconnects account for a large part of the area and timing budget. Given the significant intra- clock cycle idleness of wire segments in conventional architecture, we in this work propose TM-ARCH, a time-multiplexed architecture for FPGA interconnects. In this architecture, a wire can be multiplexed among multiple nets within one clock cycle. Specially designed time-multiplexing switches (TM switches) are used to enable the multiplexing of wires. Correspondingly, we present a time-multiplexing -aware timing-driven routing algorithm. Based on the VPR 5 timing-driven routing algorithm, this algorithm actively identifies nets that can be scheduled to multiplex wires. This routing algorithm accepts placement results from conventional placement tool, and requires no changes to the upstream EDA tools in FPGA design flow. This is the first timing-driven routing algorithm that performs combined global and detailed routing on FPGA architectures with time-multiplexed interconnects.

Our experiments with MCNC 20 benchmark show that, average minimum channel width required by the proposed TM-ARCH architecture is 20% less than that of conventional island-style architectures. Also, the average circuit critical path delay is 1.7% smaller. However, these improvements come at the expense of a 46% increase in routing area. As a result, TM-ARCH exhibits 10% larger area-delay

product compared with conventional island-style architectures. The area overhead is largely due to TM switches.

Our further investigation finds that partial depopulation can reduce the number of TM switches required, hence mitigate the area overhead. Correspondingly, we propose TM-ARCH(a), a family of FPGA architectures with partially populated time-multiplexed interconnects. This architecture family is extended from TM-ARCH architecture. In this architecture, only a portion of tracks in routing channels can be time-multiplexed with the aid of TM switches. We define an architecture parameter, a, to parameterize this portion. Our experimental results show that, TM-ARCH(a) architecture with small a values can achieve up to 10% smaller area-delay product than conventional island-style architectures.

This thesis demonstrates that the technique of time-multiplex can be applied to FPGA interconnects. Our proposed architectures show that time-multiplexed interconnect reduces channel width and improves circuit critical path delay. Our architectures also show that FPGA architectures with time-multiplexed interconnects can have area-delay product advantages, if area overhead of time-multiplexing is controlled appropriately.

# Contents

| A             | ckno  | wledgements                                    | i   |

|---------------|-------|------------------------------------------------|-----|

| Su            | ımm   | ary                                            | iii |

| Co            | onter | nts                                            | v   |

| Li            | st of | Figures                                        | ix  |

| $\mathbf{Li}$ | st of | Tables                                         | xii |

| 1             | Intr  | roduction                                      | 1   |

|               | 1.1   | Overview of FPGAs                              | 3   |

|               | 1.2   | FPGA Interconnection Network                   | 4   |

|               | 1.3   | Time-Multiplexed Interconnects for FPGAs       | 5   |

|               | 1.4   | Approaches and Key Results                     | 6   |

|               | 1.5   | Contributions of This Thesis                   | 8   |

|               | 1.6   | Organization of This Thesis                    | 10  |

| <b>2</b>      | Bac   | kground and Previous Work                      | 12  |

|               | 2.1   | Island-Style FPGA Architecture                 | 12  |

|               |       | 2.1.1 Uni-Directional and Single Driver Wiring | 14  |

CONTENTS

|   |     | 2.1.2  | Direct Drive Mux Switch                          | 15 |

|---|-----|--------|--------------------------------------------------|----|

|   | 2.2 | VPR I  | Router                                           | 17 |

|   |     | 2.2.1  | Pathfinder Routing Algorithm                     | 17 |

|   |     | 2.2.2  | Delay Modeling of Routing Path                   | 19 |

|   |     | 2.2.3  | Static Timing Analysis                           | 20 |

|   | 2.3 | Previo | ous Work                                         | 22 |

|   |     | 2.3.1  | Pipelined Interconnect                           | 23 |

|   |     | 2.3.2  | Wave-Pipelined Interconnect                      | 27 |

|   |     | 2.3.3  | Three-Dimensional Architecture                   | 29 |

|   |     | 2.3.4  | Time-Multiplexed Interconnect                    | 33 |

| 3 | FPO | GAs w  | ith Time-Multiplexed Interconnects               | 37 |

|   | 3.1 | Overv  | iew                                              | 38 |

|   | 3.2 | User ( | Clock Cycle and Microcycle                       | 39 |

|   | 3.3 | Time-  | Multiplexed Wires                                | 40 |

|   | 3.4 | TM S   | witch                                            | 41 |

|   |     | 3.4.1  | Multiple Contexts                                | 41 |

|   |     | 3.4.2  | Latching Capability of TM Switch                 | 42 |

|   | 3.5 | TM S   | witch Design                                     | 43 |

|   |     | 3.5.1  | TM Pass Transistor                               | 43 |

|   |     | 3.5.2  | Design for Multiple Contexts                     | 45 |

|   |     | 3.5.3  | Design for Latching Ability                      | 47 |

| 4 | Tim | ne-Mul | tiplexing -Aware Timing-Driven Routing Algorithm | 49 |

|   | 4.1 | Proble | em Formulation                                   | 50 |

|   | 4.2 | Signal | 's Occupation Bitmap                             | 51 |

CONTENTS

|   |     | 4.2.1 Arrival Time and Leave Time                                                                                                                            |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 4.2.2 Occupation Bitmap                                                                                                                                      |

|   | 4.3 | Congestion Penalties at Microcycles                                                                                                                          |

|   |     | 4.3.1 Micro Occupancy                                                                                                                                        |

|   |     | 4.3.2 Present and Historical Congestion Penalty 58                                                                                                           |

|   | 4.4 | Multiplexing-aware Congestion Cost                                                                                                                           |

|   | 4.5 | Overall Cost Function                                                                                                                                        |

|   | 4.6 | Legal Routing Solution                                                                                                                                       |

|   | 4.7 | Pseudo Code                                                                                                                                                  |

|   | 4.8 | Further Details                                                                                                                                              |

|   |     | 4.8.1 Accuracy of $t_{arrival}$ and $t_{leave}$                                                                                                              |

|   |     | 4.8.2 Accuracy of $T_{crit}$                                                                                                                                 |

|   | 4.9 | Analysis of Algorithm                                                                                                                                        |

|   |     | 4.9.1 Time Complexity $\ldots \ldots \ldots$ |

|   |     | 4.9.2 Memory Requirement                                                                                                                                     |

|   |     | 4.9.3 Unroutability Detection                                                                                                                                |

| 5 | Arc | hitecture Evaluation 72                                                                                                                                      |

|   | 5.1 | Key Results from Related Work                                                                                                                                |

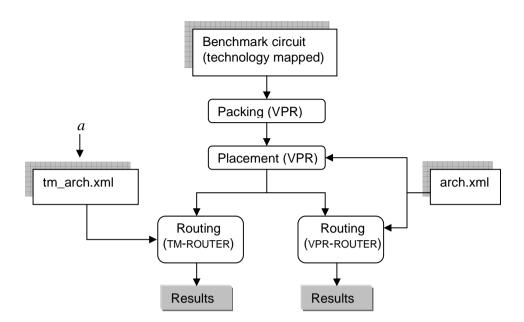

|   | 5.2 | Experimental Methodology                                                                                                                                     |

|   |     | 5.2.1 CAD Flow                                                                                                                                               |

|   |     | 5.2.2 FPGA Architectural Assumptions                                                                                                                         |

|   |     | 5.2.3 Evaluation Metrics                                                                                                                                     |

|   |     | 5.2.4 TM Switches Area and Delay Assumptions                                                                                                                 |

|   | 5.3 | Experimental Results: Minimum Channel Width                                                                                                                  |

#### List of Figures

|   | 5.4                   | Experimental Results: Routing Area                    | 88  |

|---|-----------------------|-------------------------------------------------------|-----|

|   | 5.5                   | Experimental Results: Circuit Critical Path Delay     | 90  |

|   | 5.6                   | Experimental Results: Area-Delay Product              | 93  |

| 6 | Part                  | tial Depopulation of Time-Multiplexed Interconnects   | 97  |

|   | 6.1                   | Motivation                                            | 97  |

|   | 6.2                   | Overview                                              | 98  |

|   | 6.3                   | Multiplex-able Track Population                       | 98  |

|   | 6.4                   | Co-Existence of TM Switches and Conventional Switches | 100 |

|   | 6.5                   | Architecture Evaluation                               | 102 |

|   |                       | 6.5.1 Key Results from Related Work                   | 102 |

|   |                       | 6.5.2 Experimental Methodology                        | 103 |

|   |                       | 6.5.3 Experimental Results                            | 105 |

| 7 | Con                   | clusion                                               | 118 |

|   | 7.1                   | Summary                                               | 118 |

|   | 7.2                   | Future Work                                           | 120 |

| A | $\operatorname{List}$ | of Publications                                       | 122 |

| в | Cur                   | riculum Vitae                                         | 124 |

# List of Figures

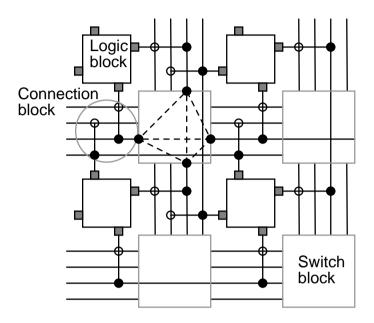

| 1.1 | A generic FPGA architecture (from [37])                                                                                                     | 4  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | An island-style FPGA (from [6]).                                                                                                            | 13 |

| 2.2 | Bi-directional wires with multiple drivers (adapted from $[19]$ )                                                                           | 15 |

| 2.3 | Uni-directional and single-driver wires (adapted from $[19]$ )                                                                              | 16 |

| 2.4 | A direct drive mux switch                                                                                                                   | 16 |

| 2.5 | A 4:1 multiplexer assuming the two-level hybrid topology. Each                                                                              |    |

|     | "MC" represents one-bit memory cell                                                                                                         | 16 |

| 2.6 | Pseudo-code of Pathfinder routing algorithm. From $[6]$                                                                                     | 18 |

| 2.7 | A simple circuit, and its timing graph (from $[6]$ )                                                                                        | 21 |

| 2.8 | Switch boxes with registers in HSRA architecture. From $[36]$                                                                               | 24 |

| 2.9 | Switch boxes with registers in Singh and Brown architecture. From                                                                           |    |

|     | $[32] \ldots \ldots$ | 25 |

| 3.1 | Proposed architecture of FPGAs with time-multiplexed interconnects                                                                          | 39 |

| 3.2 | (a) Signals of $N_1$ and $N_2$ time-multiplex a wire; (b) $N_1$ and $N_2$ do                                                                |    |

|     | not overlap in the time domain; (c) On/off state of the TM switches.                                                                        | 41 |

| 3.3 | A pass transistor controlled by a SRAM cell                                                                                                 | 44 |

| 3.4 | A TM pass transistor                                                                                                                        | 44 |

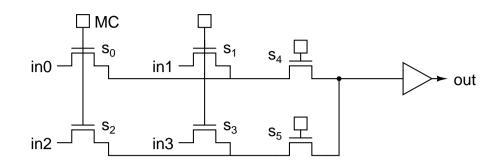

| 3.5 | A direct drive mux type switch. Its multiplexer selects one from four   |    |

|-----|-------------------------------------------------------------------------|----|

|     | input lines.                                                            | 46 |

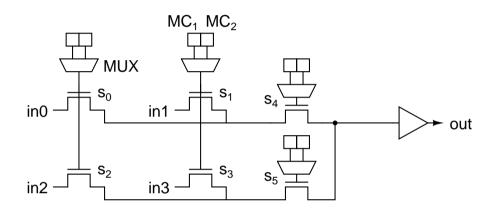

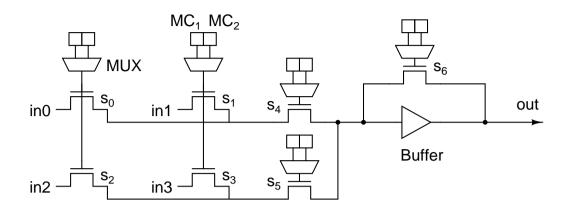

| 3.6 | A TM switch of direct drive mux type. For the sake of illustration,     |    |

|     | circular counters are not shown, and K is assumed to be 2. $\ldots$     | 46 |

| 3.7 | A TM switch of direct drive mux type. For the sake of illustration,     |    |

|     | circular counters are not shown, and K is assumed to be 2. Notice       |    |

|     | that this TM switch can latch data                                      | 48 |

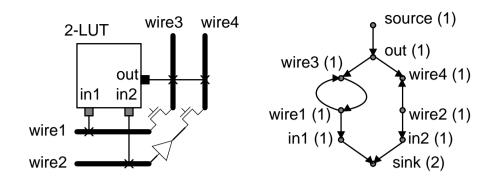

| 4.1 | Representing TM-ARCH architecture as a routing resource graph $\ . \ .$ | 51 |

| 4.2 | A linked list to record all the nets currently using the wire           | 54 |

| 4.3 | Pseudo code of our algorithm to compute occupation bitmaps              | 56 |

| 4.4 | A linked list to record all the nets currently using the wire           | 56 |

| 4.5 | Pseudo code of our algorithm to compute congestion cost. $\ldots$ .     | 61 |

| 4.6 | Time-multiplexing -aware timing-driven routing algorithm pseudo-        |    |

|     | code                                                                    | 64 |

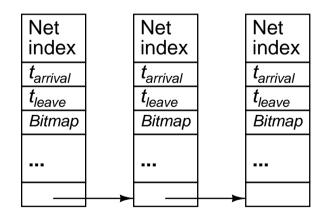

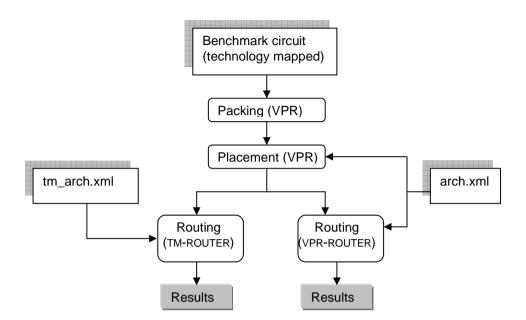

| 5.1 | Architecture evaluation flow                                            | 76 |

| 5.2 | Channel width values that are tried by TM-ROUTER during the bi-         |    |

|     | nary search                                                             | 86 |

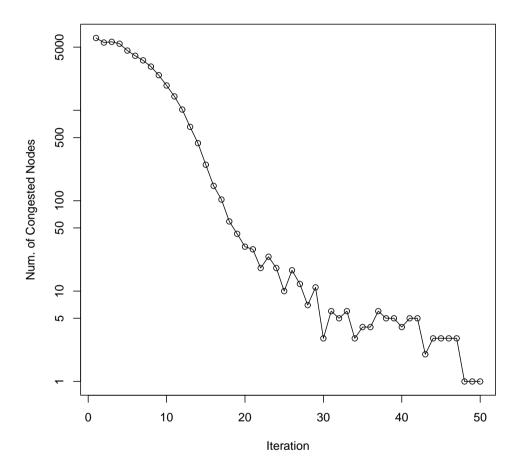

| 5.3 | Number of remaining congested nodes after each iteration. (Channel      |    |

|     | width $W = 136$ ; y-axis shown in logarithmic scale)                    | 87 |

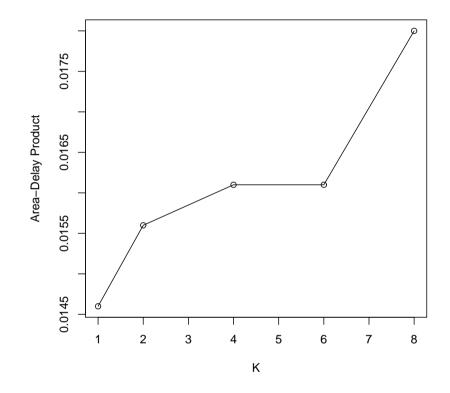

| 5.4 | Area-delay product results averaged over 20 MCNC benchmark cir-         |    |

|     | cuits versus $K$                                                        | 94 |

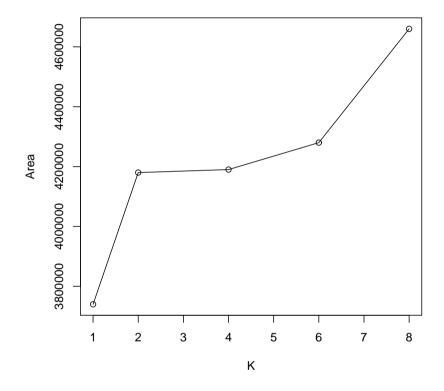

| 5.5 | Total area results averaged over 20 MCNC benchmark circuits versus      |    |

|     | <i>K</i>                                                                | 95 |

| 6.1 | Proposed architecture of FPGAs with partially depopulated time-                                                                         |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | multiplexed interconnects.                                                                                                              | 99  |

| 6.2 | A routing channel consisting of four conventional tracks and one                                                                        |     |

|     | multiplex-able tracks. All wire segments span four logic blocks $% \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A}$ | 99  |

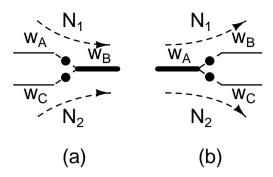

| 6.3 | A TM switch should be used for (a) a connection from a conventional                                                                     |     |

|     | wire $w_A$ to a multiplex-able wire $w_B$ , and (b) a connection from a                                                                 |     |

|     | multiplex-able wire $w_A$ to a conventional wire $w_B$                                                                                  | 101 |

| 6.4 | Architecture evaluation flow                                                                                                            | 104 |

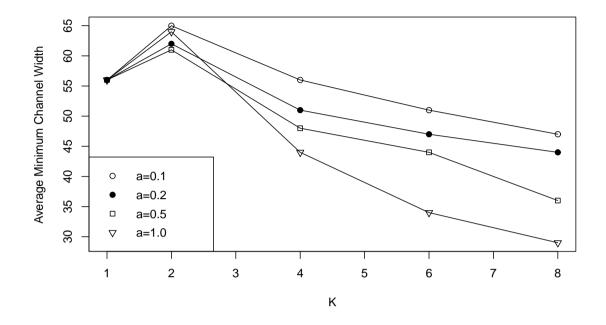

| 6.5 | Average minimum channel widths versus multiplex-able track pop-                                                                         |     |

|     | ulation, $a$ , and number of microcycles in a user clock cycle, $K$ 1                                                                   | 106 |

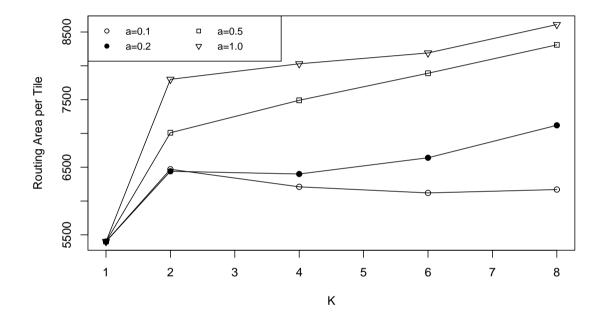

| 6.6 | Routing area per logic tile versus multiplex-able track population,                                                                     |     |

|     | a, and number of microcycles in a user clock cycle, $K$                                                                                 | 109 |

| 6.7 | Average circuit critical path delay versus multiplex-able track pop-                                                                    |     |

|     | ulation, $a$ , and number of microcycles in a user clock cycle, $K$ 1                                                                   | 112 |

| 6.8 | Area delay product versus multiplex-able track population, $a$ , and                                                                    |     |

|     | number of microcycles in a user clock cycle, $K$                                                                                        | 116 |

# List of Tables

| 3.1 | Pass transistor's on/off state in 1st and 2nd half cycles for different |    |

|-----|-------------------------------------------------------------------------|----|

|     | configurations                                                          | 45 |

| 3.2 | Configurations of TM pass transisotrs to achieve the time-multiplexing  |    |

|     | in Figure 3.2                                                           | 47 |

| 3.3 | Configurations of TM pass transisotrs to achieve the time-multiplexing  |    |

|     | in Figure 3.2                                                           | 48 |

| 4.1 | Routing schedule of our time-multiplexing -aware routing algorithm      | 59 |

| 5.1 | Channel width comparison between Trimberger's architecture and          |    |

|     | XC4000E architecture. Data of the former architecture is from [35]      |    |

|     | Table 1, and data of the later is from [38] Table 14                    | 73 |

| 5.2 | Key results from related architectures in the literature $\ldots$       | 75 |

| 5.3 | Main features of our used baseline FPGA architecture                    | 77 |

| 5.4 | Minimum channel width for different K values                            | 81 |

| 5.5 | Percentages of wire used in the 1st and the 2nd microcycle for MCNC     |    |

|     | 20 benchmark circuits. Assume that a user clock cycle is divided into   |    |

|     | two microcycles                                                         | 82 |

| 5.6 | Percentages of wire used in the 1st, the 2nd, the 3rd and the 4th            |

|-----|------------------------------------------------------------------------------|

|     | microcycle for MCNC 20 benchmark circuits. Assume that a user                |

|     | clock cycle is divided into four microcycles                                 |

| 5.7 | Routing area reported by routers, assuming minimum channel width.            |

|     | Unit is minimum-width transsitor area                                        |

| 5.8 | Channel width values used in low-stress routing                              |

| 5.9 | Circuit critical path delays reported from low-stress routing (In unit       |

|     | of nano-seconds)                                                             |

| 6.1 | Switch of choice to implement the configurable connection from wire          |

|     | segment $w_A$ to wire segment $w_B$                                          |

| 6.2 | Average minimum channel width reduction of architecture $TM-ARCH(a)$         |

|     | at different $K$ values                                                      |

| 6.3 | Routing area overhead of $TM-ARCH(a)$ at different K values 108              |

| 6.4 | Minimum channel width and low-stress channel width of circuit ${\bf alu4}$   |

|     | versus a and K. $W_{min}$ is determined from binary-search routing. $W_{ls}$ |

|     | is derived from $W_{min}$                                                    |

| 6.5 | Average low-stress channel widths versus multiplex-able track pop-           |

|     | ulation, $a$ , and number of microcycles in a user clock cycle, $K$ 114      |

## Chapter 1

# Introduction

Field-programmable gate arrays (FPGAs), as an important media to implement digital circuits, have been becoming increasingly popular. This trend is bound to continue, as the manufacturing technology of integrated circuits keeps on advancing. Although its programmability gives it some key advantages over application-specific integrated circuits (ASICs) technology, FPGA's programmability also causes significant timing, area, and power overhead compared with ASICs. If gaps between FPGAs and ASICs in these key metrics could be closer, FPGAs would be a more competitive technology.

It has been understood that FPGA interconnection network is a main contributor to the overall timing, area, and power budget. Hence, this thesis focuses on FPGA interconnection network exclusively. Traditionally, three factors are identified as determining the performance of an FPGA at large: quality of the FPGA architecture, quality of the computer-aided design (CAD) tools, and electrical design of the FPGA. This thesis attempts to examine and optimize the performance of FPGA interconnection network mainly by looking at the former two factors, i.e., architecture and CAD.

The technique of time-multiplex has been applied to FPGAs before. Originally this technique was applied to FPGA logic blocks so as to improve utilization of logic blocks. This is reasonable because logic resources used to be at a premium in early years of FPGAs. Given that nowadays FPGA interconnect resources are more costly than the logic, this thesis proposes that time-multiplex be applied to FPGA interconnects; hence the title of this thesis.

In this thesis, we present TM-ARCH, an FPGA architecture with fully populated time-multiplexed interconnects. This architecture is based on the classical island-style architecture [6]. All wires in routing channels can be time-multiplexed with the aid of specially designed switches. We also present TM-ARCH(a), a family of FPGA architectures with partially populated time-multiplexed interconnects. TM-ARCH(a) is extended from TM-ARCH architecture, and the parameter a is used to parameterize the portion of routing tracks that can be time-multiplexed. At CAD side, we present a time-multiplexing -aware timing-driven routing algorithm, which is based on VPR 5 timing-driven routing algorithm [20]. We implement this algorithm as our routing tool. With this routing tool, we employ a standard CAD flow and a set of benchmark circuits to experimentally evaluate TM-ARCH and TM-ARCH(a) architecture.

This thesis demonstrates that the technique of time-multiplex can be applied to FPGA interconnects. Our proposed architectures show that time-multiplexed interconnect reduces channel width and improves circuit critical path delay. Our architectures also show that FPGA architectures with time-multiplexed interconnects can have area-delay product advantages, if area overhead of time-multiplexing is controlled appropriately. The remainder of this chapter is organized as follows. Section 1.1 and 1.2 give an overview of FPGAs at large and FPGA interconnection network, respectively. Section 1.3 proposes the use of time-multiplex technique for FPGA interconnects. Section 1.4 briefly describes our approaches and some key results. Section 1.5 and 1.6 describes contributions and organizations of this thesis, respectively.

## 1.1 Overview of FPGAs

Since their introduction in 1980s, field-programmable gate arrays (FPGAs) have gained wide popularity. Some of the historical key application fields of FP-GAs include rapid prototyping, custom computing, and design emulation. Besides, with the technology scaling enabling high degree of integration, FPGAs nowadays contain rich logic, as well as a variety of customized functional blocks, such as block memory, digital signal processing (DSP) blocks, and Ethernet controller. Hence, FPGA has also become an important medium to implement user designs.

Compared with application-specific integrated circuits (ASICs), FPGAs have two desirable qualities: low non-recurring engineering (NRE) cost and fast turnaround time. While the IC technology is progressing towards 28nm technology node, it is expected that the cost and complexity of ASICs will skyrocket. This will make FPGA implementation more attractive for IC designers working on lowto-middle volume productions.

The above-mentioned advantages of FPGAs come with a price. It has been well known that, for the same user design, the FPGA implementation will consume more area and power, yet achieve lower performance than the ASIC implementation. A recent work [11] which measures the gap between FPGA implementation

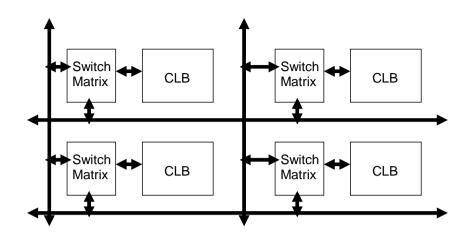

Fig. 1.1: A generic FPGA architecture (from [37])

and ASIC implementation points out that the required silicon area of the FPGA implementation is about 18 times that of ASIC implementation, the critical path delay about three to four times, and the dynamic power consumption about 14 times.

## 1.2 FPGA Interconnection Network

Resources in an FPGA device can be broadly divided into two parts: logic resources and interconnect resources. Logic resources are used to implement user logic. Logic resources in FPGAs are usually organized as arrays (or columns) of logic blocks. Interconnect resources are used to implement connections between different logic blocks. Interconnect resources usually include routing wires, grouped into channels, and routing switches. Figure 1.1 illustrates a generic FPGA architecture. FPGA interconnects (or interconnection network) can be defined as the programmable network of signal pathways between inputs and outputs of logic blocks within FPGA. Both analysis and measurements reveal that interconnection network is the main contributor to area, delay, and power. To achieve high routability leading to successful implementation of user design, and also to ease routing task for CAD tools leading to reduced compile time, FPGA vendors usually devote much silicon area to routing tracks and programmable switches used to connect tracks. This explains why interconnects out-weight logic in terms of area and power budget. Routing a net to connect pins at different logic blocks usually means traversing a series of tracks connected by switches. This explains why interconnects in FPGA implementation are slow. Given that the interconnection network has a profound effect on FPGA's overall performance, optimizing the interconnection network is essential.

#### **1.3** Time-Multiplexed Interconnects for FPGAs

Previous research [35] has shown that time-multiplexing can improve the utilization of logic resources in FPGA. In our work, we apply time-multiplexing to interconnection networks in FPGA. The idea is based on the observation that most interconnect wires are only used for a short period in a clock cycle. That is, the delay for a signal to propagate along a wire segment is only a small portion of the clock cycle. Take the 65nm FPGA architecture file n10k04l04.fc15.area1delay1.cmos65nm.bptmfrom iFAR [23]. The delay of a wire spanning four logic blocks (plus the delay of the switch driving the wire) is around 70ps. Assuming this same architecture file, the average post-route critical path delay of MCNC 20 benchmark circuits is around 4ns. Dividing 70ps by 4ns gives a percentage of 1.8%. This means that, in a clock cycle, a wire is effectively used to propagate a signal in only 1.8% of the time. In other words, a wire remains idle for more than 90% of the time. An intuitive way to understand this fact is that the circuit critical path usually spans a number of logic blocks and nets. If we examine one wire segment used along this critical path, we may find that its delay is far less than the whole critical path delay.

By time-multiplexing signals on interconnects, we can better utilize the interconnect resources. This could translate to area savings, as well as performance improvement, at the cost of routing circuitry complexity. As the FPGA architecture keeps evolving, time-multiplexed interconnection network could be a viable solution to the scalable FPGA architecture.

### **1.4** Approaches and Key Results

In this thesis, we first present TM-ARCH, an FPGA architecture with fully populated time-multiplexed interconnects. This architecture is based on the classical island-style architecture [6]. All wires in routing channels can be time-multiplexed. Specially designed switches, time-multiplexing switches (TM switches), replace conventional switches to enable time-multiplexing of wires. Following Trimberger *et* al's terminology, we define the architecture parameter, K, as the number of microcycles in a user clock cycle. That is, the number of time slots for time-multiplexing. It is worth to mention here that this architecture does not time-multiplex logic blocks.

We then present a time-multiplexing -aware timing-driven routing algorithm. This routing algorithm is based on VPR 5 timing-driven routing algorithm [20]. It employs a multiplexing-aware congestion cost function so as to identify nets for time-multiplexing. We implement this algorithm as our routing tool. By assuming standard FPGA CAD flow and replacing the conventional router with our router, we are able to implement circuits onto our proposed TM-ARCH FPGAs. More importantly we are able to evaluate experimentally TM-ARCH architecture by mapping a set of benchmark circuits to the architecture and measuring area and timing results.

In our evaluation of TM-ARCH, we use MCNC benchmark circuits and VPR flow, which are the common practices in the research community. We compare TM-ARCH with the conventional island-style architecture based on four metrics: minimum channel width, routing area, circuit critical path delay, and area-delay product. Our evaluation shows that TM-ARCH generally can achieve smaller minimum channel widths. For example, with K=4, TM-ARCH achieves average 20% reduction in minimum channel widths over 20 MCNC circuits. But TM-ARCH is also shown to exhibit significant routing area overhead although it reduces channel widths. In the case of K=4, TM-ARCH requires 46% larger routing area. This significant area overhead is mainly due to TM switches, which consume much more area than their conventional counterpart. Our evaluation shows that TM-ARCH can achieve similar or slightly better critical path delays with smaller channel widths than the conventional island-style architecture. In the case of K=4, TM-ARCH improves critical path delay by 1.7% while using 20% smaller channel widths. Finally, our evaluation shows that TM-ARCH generally has larger area-delay product. With K=4, TM-ARCH exhibits 10% larger area-delay product.

Our evaluation of TM-ARCH architecture reveals that area overhead of TM switches can be significant. This motivates us to propose a family of FPGA architectures with partially populated time-multiplexed interconnects. This architecture family is extended from TM-ARCH architecture. In this architecture, only a portion of tracks in routing channels can be time-multiplexed with the aid of TM switches. We define a second architecture parameter, a, to parameterize this portion. We denote this family of architecture by TM-ARCH(a). With a=1.0, TM-ARCH(a) is equivalent to TM-ARCH.

Again, we compare TM-ARCH(a) with the conventional island-style architecture. Our evaluation shows that TM-ARCH(a) architecture with small a values can achieve smaller area-delay product than the conventional island-style architecture. For example, with K=4 and a=0.1, TM-ARCH(a) achieves 10% smaller area-delay product.

### 1.5 Contributions of This Thesis

This thesis investigates two issues related to employing time-multiplexed interconnects for FPGAs. First, it investigates the proper FPGA interconnect architectures which support time-multiplexing. Second, it investigates the corresponding routing algorithm which schedules signals to achieve time-multiplexing. Main contributions of this thesis are:

1. An FPGA architecture with fully populated time-multiplexed interconnects is presented. This architecture is based on VPR island-style architecture. All the wires in the routing channels can be time-multiplexed with the aid of specially designed switches, TM switches. This architecture differs from existing FPGA architectures with time-multiplexed interconnects mainly in two aspects. First, only interconnect resources can be multiplexed, and logic blocks cannot be multiplexed (compared with [35]); Second, TM switches provide signal latching capability (compared with [18] and [10]). We believe that our work is the first to examine the feasibility of applying time-multiplexed interconnects to an academic island-style FPGA architecture.

This architecture is evaluated against and compared with island-style architecture experimentally. Our experimental results show that this architectural generally can achieve smaller channel widths. This acknowledges findings of related work in literature ([18] [10]). As part of the architecture evaluation, an important architectural parameter K, number of microcycles in a user clock cycle, is investigated. The investigation shows that K = 2 and  $K \ge 8$ , exhibiting significant area overhead, are inappropriate. This finding, to some extent, challenges practices in related work, which either use K = 2 ([18]) or  $K \ge 8$  ([35] [10]). The architecture evaluation also reveals that time-multiplexed interconnect could achieve comparable or slightly better timing and use smaller channel widths than its conventional counterpart. This finding is the first to demonstrate that, in terms of circuit timing, time-multiplexed interconnect is competitive with its conventional counterpart.

2. A time-multiplexing -ware timing-driven routing algorithm is presented. This algorithm is based on VPR 5 timing-driven routing algorithm. Multiplexingaware congestion cost function is used so as to identify signals for time-multiplexing. This routing algorithm is implemented as a routing tool, which is used for experimental evaluation of our proposed time-multiplexed interconnect architectures stated in contribution 1 and 3. This is the first timing-driven routing algorithm that performs combined global and detailed routing on FPGA architectures with time-multiplexed interconnects. This algorithm is important for us to demonstrate that time-multiplexed interconnect is competitive with its conventional counterpart in terms of circuit timing. 3. A family of FPGA architectures with partially populated time-multiplexed interconnects is presented. This architecture is also based on VPR island-style architecture, and extended from our proposed architecture stated in contribution 1. A portion of tracks in the routing channels can be time-multiplexed with the aid of TM switches, while the remaining tracks cannot be multiplexed. An architectural parameter a, multiplex-able track population, is used to parameterize this portion. This family of architectures is evaluated against and compared with island-style architecture experimentally. The experimental results demonstrate that small values for a help this architecture achieve good tradeoff between channel width reduction and area overhead. This finding, to some extent, acknowledges a previous finding in the literature ([10]). The results also show that our proposed architecture with small a values could achieve comparable or better area-delay product than the conventional island-style FPGA architecture. This finding is important, for it demonstrates that time-multiplexed interconnect is practical for FPGAs.

## **1.6** Organization of This Thesis

The remainder of this thesis is organized as follows. The next chapter provides background information and reviews some of the previous work in the area of FPGA interconnect architecture. Chapter 3 presents our proposed FPGA architecture with time-multiplexed interconnects. Chapter 4 presents our time-multiplexing aware timing-driven routing algorithm. Architecture and routing algorithm are the two facets of our work. Then the proposed architecture is evaluated, and experimental results are given in Chapter 5. Chapter 6 presents the proposed FPGA architecture with partially populated time-multiplexed interconnects. In this same chapter, we evaluate this partially populated architecture and give experimental results. Chapter 7 concludes this thesis and provides suggestions for future work.

## Chapter 2

# **Background and Previous Work**

The first half of this chapter gives background information about island-style FPGA architecture and VPR routing tool. The second half of this chapter reviews some of the previous research on FPGA interconnect architecture.

### 2.1 Island-Style FPGA Architecture

In their classical book Architecture and CAD for Deep-Submicron FPGAs [6], Betz et al classified FPGAs into three groups according to their routing architecture: island-style, row-based, and hierarchical. Lemieux and Lewis largely followed this classification in their book Design of Interconnection Networks for Programmable Logic [15]. The island-style architecture is certainly the most popular one. Almost all modern commercial FPGAs employ the island-style architecture. And in academia, research and literature on the island-style FPGA architecture also dominate.

In our work, we propose a new FPGA architecture by extending the classical

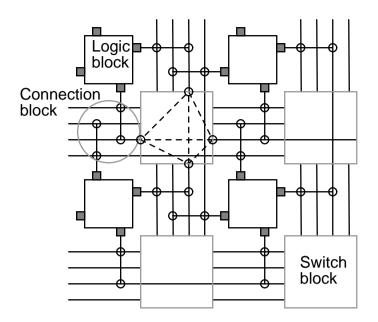

Fig. 2.1: An island-style FPGA (from [6]).

island-style FPGA architecture, as defined in Betz *et al*'s book. Hence, in the following, we give a short summary of key features of the island-style FPGA architecture. Readers are referred to Betz *et al*'s book for a detailed treatment of the island-style architecture.

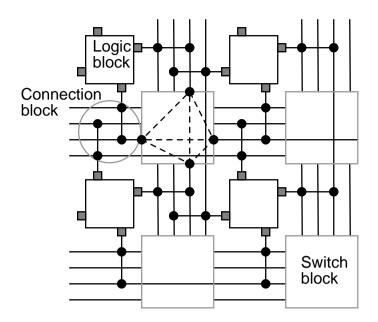

Island-style architecture is also called mesh architecture in Lemieux's book. In island-style FPGAs, logic resources are organized as a two dimensional array of logic blocks. Logic blocks are surrounded by routing channels on four sides. A routing channel, either horizontal or vertical, usually contains a number of routing tracks. A routing track usually consists of a series of wire segments. Figure 2.1 illustrates an island-style FPGA.

Input and output pins of a logic block can connect to the peripheral routing channels via connection blocks. And at the intersection of a horizontal channel and a vertical channel, there is a switch block. Both connection blocks and switch blocks are made up of routing switches. A routing switch contains a one-bit memory cell, and can be turned on or off by appropriately configuring the memory cell. It is the routing switches inside connection blocks and switch blocks that achieve programmable interconnections between logic blocks.

Logic blocks themselves are also programmable, thus allowing users to implement different logic functions. A logic block usually contains a cluster of look-up tables (LUTs) and registers. A k-input LUT can implement any Boolean function with k inputs and one output. Registers enable the implementation of sequential logic.

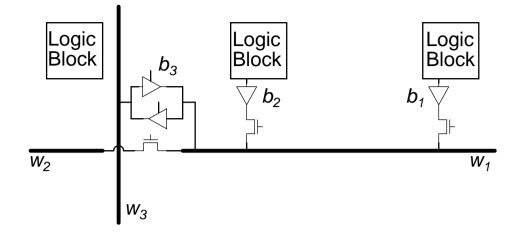

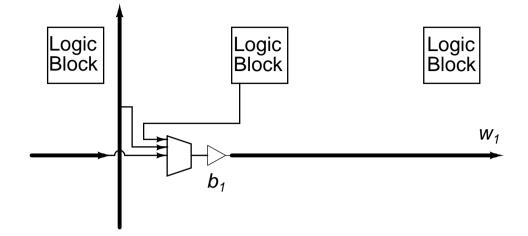

#### 2.1.1 Uni-Directional and Single Driver Wiring

Major commercial FPGAvendors have shifted away from using bi-directional and multiple-driver wires. They use uni-directional and single-driver wires, instead. Figure 2.2 and Figure 2.3 illustrate these two paradigms, respectively. In Figure 2.2, the horizontal wire  $w_1$  spanning two logic blocks can route a signal either from left to right or from right to left. Correspondingly, the switches used are bi-directional. A pass transistor switch connects wire  $w_1$  with another horizontal wire  $w_2$ , and two back-to-back tri-state buffers connect wire  $w_1$  with a vertical wire  $w_3$ . Also notice that wire  $w_1$  can be driven from multiple points: it can be driven via the tri-state buffer  $b_3$  by wire  $w_3$ , or via tri-state buffer  $b_1$  by a logic block, or via tri-state buffer  $b_2$  by a second logic block. But in Figure 2.3, the horizontal wire  $w_1$  can route a signal from left to right only. And it can only be driven via the buffer  $b_1$  from the left endpoint. A wide multiplexer is used to select from all possible sources.

It has been shown in [14] that uni-directional and single-driver wiring reduces

Fig. 2.2: Bi-directional wires with multiple drivers (adapted from [19]).

area and improves delay over bi-directional and multiple-driver wiring. This may explain the trend towards uni-directional and single-driver wiring in the industry.

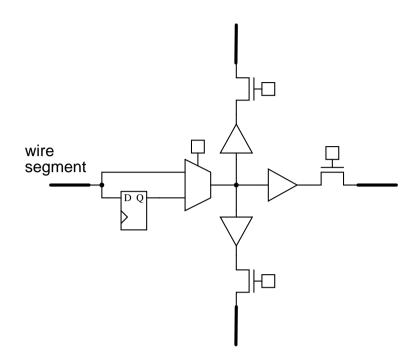

#### 2.1.2 Direct Drive Mux Switch

In the context of uni-directional and single-driver wiring, one switch widely used is direct drive mux switch [17].

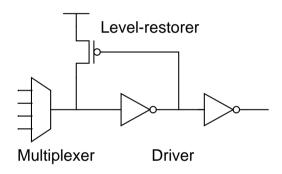

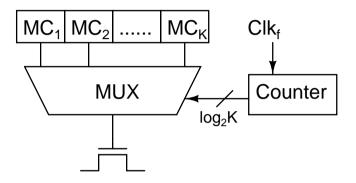

This type of switch consists of two parts: a multiplexer used to select input lines and a buffer to drive the wire. The multiplexer usually is constructed using NMOS pass transistors. As a result, a logic-1 signal at the selected input line will produce a weak-1 signal at the output of the multiplexer. A level-restoring PMOS transistor is integrated with the buffer to restore the voltage level of the weak-1 signal [25] [4]. Figure 2.4 illustrates a direct drive mux switch.

Assuming that we only use NMOS pass transistors to construct the multiplexer, there can be three kinds of topology: tree, flat, and two-level hybrid [12]. A comparison of these three topologies can be found at [12]. The two-level hybrid

Fig. 2.3: Uni-directional and single-driver wires (adapted from [19]).

Fig. 2.4: A direct drive mux switch.

Fig. 2.5: A 4:1 multiplexer assuming the two-level hybrid topology. Each "MC" represents one-bit memory cell.

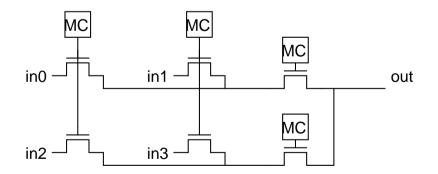

topology, which strikes a good balance between area and performance, is employed in [25] [4] [12] [16]. We also use the two-level hybrid topology in our work. Figure 2.5 shows a transistor-level implementation of a 4:1 multiplexer, which assumes the two-level hybrid topology.

#### 2.2 VPR Router

VPR (Versatile Pace and Route) CAD tool [5] was developed by the FPGA research group at University of Toronto. It has been well maintained and regularly updated by the same research group. Since its release in 1997, it has become the standard tool among the FPGA researchers, due to its free availability and high quality. In our work, we mainly use VPR version 5.0 [20], which we will refer to as "VPR 5" hereafter.

VPR 5 includes a timing-driven router, which is based on the Pathfinder negotiated congestion-delay algorithm [22]. Section 2.2.1 briefly introduces Pathfinder algorithm. In our work, we make extensive use of VPR 5 timing-driven router's capabilities of delay modeling and static timing analysis. Section 2.2.2 briefly describes how VPR router models the delay of a routing path. Section 2.2.3 gives background knowledge on static timing analysis.

#### 2.2.1 Pathfinder Routing Algorithm

Pathfinder negotiated congestion-delay routing algorithm is based on an iterative approach [22]. It rips-up and re-routes each net in each iteration. During each iteration, it finds the shortest path for each sink  $s_{ij}$  of each net  $N_i$  using directed search, and allows resource overuse. Figure 2.6 presents pseudo-code of Pathfinder routing algorithm.

|    | $Q(i)$ : Priority queue used while routing net $N_i$<br>$RT(i)$ : Routing tree of net $N_i$ |

|----|---------------------------------------------------------------------------------------------|

|    | $Source(i)$ : Source of net $N_i$                                                           |

| 1  | Crit(i, j) = 1.0 for all i and j;                                                           |

| 2  | while (overused resources exist) {                                                          |

| 3  | for (each net $N_i$ ) {                                                                     |

| 4  | Rip-up $RT(i)$ , and update $p(n)$ for all nodes $n$ in $RT(i)$ ;                           |

| 5  | RT(i) = Source(i);                                                                          |

| 6  | for (each sink j of net $N_i$ in decreasing $Crit(i, j)$ order) {                           |

| 7  | Q(i) = RT(i);                                                                               |

| 8  | while $(sink(i, j) \text{ not found}) \{ /* \text{ Wave expansion } */$                     |

| 9  | Remove lowest cost node, $m$ , from $Q(i)$ ;                                                |

| 10 | for (all fanout nodes $n$ of node $m$ ) {                                                   |

| 11 | Add $n$ to the $Q(i)$ ;                                                                     |

| 12 | }                                                                                           |

| 13 | $}/*$ Routing of one sink is finished. */                                                   |

| 14 | for (all nodes, $n$ , in path from $RT(i)$ to $sink(i, j)$ ) {                              |

| 15 | Update $p(n)$ ;                                                                             |

| 16 | Add $n$ to $RT(i)$ ;                                                                        |

| 17 | }                                                                                           |

| 18 | $}/*$ Routing of one net is finished. */                                                    |

| 19 | $} /*$ Routing of all nets are finished. */                                                 |

| 20 | Update $h(n)$ for all nodes $n$ ;                                                           |

| 21 | Update $Crit(i, j)$ ;                                                                       |

| 22 | } /* End of one routing iteration*/                                                         |

|    |                                                                                             |

Fig. 2.6: Pseudo-code of Pathfinder routing algorithm. From [6]

A key innovation of Pathfinder algorithm is its cost function. By using a cost function as shown by Eq. 2.1, it gradually resolves the overuse after multiple iterations, and at the same time optimizes the delay. The cost to include a node n into the routing path is

$$c(n) = Crit(i,j) \cdot d(n) + [1 - Crit(i,j)] \cdot b(n) \cdot h(n) \cdot p(n)$$

$$(2.1)$$

b(n), p(n) and h(n) are nodes *n*'s base cost, present congestion cost and historical congestion cost, respectively. p(n) and h(n) both increase as a node *n* is overused. d(n) is node *n*'s intrinsic delay. Crit(i, j), the criticality of the connection from net  $N_i$  source to sink  $s_{ij}$ , is defined as

$$Crit(i,j) = 1 - \frac{Slack(i,j)}{T_{crit}}$$

(2.2)

$T_{crit}$  is the circuit critical path delay, and Slack(i, j) the connection's timing slack.

The first term in right hand side of Eq. 2.1 is called *delay sensitive term*, and the second term *congestion sensitive term*. When a source-sink connection lies on a critical path, the congestion sensitive term becomes zero. This means that Pathfinder will ignore congestion and route this connection for minimum delay.

#### 2.2.2 Delay Modeling of Routing Path

VPR version 4.30 employs the Elmore delay model to compute the delay of a route from a net source to any of its sinks. Pass transistors and wires are modeled as RC trees. And a buffer is modeled by a constant delay and a resistor. The Elmore delay of a source-sink path is:

$$T_{path} = \sum_{i \in path} (R_i C_{ds,i} + d_i)$$

(2.3)

Basically, the Elmore delay of the path is a summation of the Elmore delay of each node over all the nodes along the path. A node i can be a wire, a pass transistor, or a buffer.  $R_i$  is node i's equivalent resistance, and  $d_i$  is node i's intrinsic delay.  $C_{ds,i}$  is the nodes i's downstream capacitance.

VPR 5 recommends that FPGAs assume uni-directional single driver wiring. As a result of that, it favors a constant delay model over the Elmore delay model [26]. Hence, the delay of a source-sink path now is:

$$T_{path} = \sum_{i \in path} d_i \tag{2.4}$$

Again, delay of the path is a summation of delay of each node over all the nodes along the path. A node i can be a wire, or a switch.  $d_i$  is a constant delay value specified in architecture files.

Note that VPR 5 can also compute Elmore delay for old-style VPR version 4.30 routing architectures. And it handles these two different cases transparently. In our research, we have worked with both the old-style routing architecture and the uni-directional single driver routing architecture. VPR 5 computes and reports delay values based on the Elmore delay model for old-style architectures; and it computes and reports delay values based on the constant delay model for uni-directional single driver architectures. Hereafter, we will simply use the same single word "delay" for routing path delay values computed based on both delay models.

VPR contains a delay extractor which can compute the delay of any routed net. The delay extractor can also incrementally compute the delay from the net source to a node in the current routing tree while a net is being routed.

#### 2.2.3 Static Timing Analysis

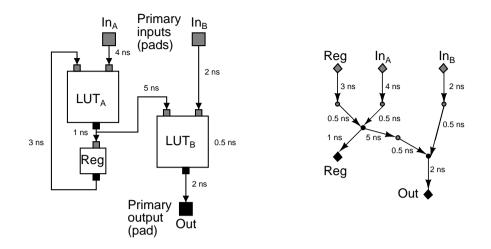

Usually a timing graph is used to perform static timing analysis. In a timing graph, nodes represent input and output pins of basic circuit elements. In the case of FPGAs, the basic circuit elements include LUTs, registers, and IO pads. Edges

Fig. 2.7: A simple circuit, and its timing graph (from [6]).

are added between input pins of combinational logic blocks (e.g., LUTs) and their outputs. Edges are also added between pins which the circuit netlist specifies are connected. Each edge is annotated with a delay value. This delay value specifies the delay required to pass through the circuit element or routing.

As explained in Section 2.2.2, VPR's delay extractor computes the delay of a net's routing path, after this net is routed. Delay values of all nets' routing paths will be annotated on the edges in the timing graph, after all nets are routed.

Figure 2.7 shows a simple circuit implemented with 2-input LUTs and registers, and its corresponding timing graph.

In sequential digital circuits, we usually assume that signal arrival times at primary inputs are 0. We can start from the primary inputs, breadth-first traverse the timing graph, and compute arrival time for each node in the graph.

$$T_{arrival}(i) = Max_{j \in fanin(i)} \{ T_{arrival}(j) + delay(j,i) \}$$

$$(2.5)$$

, where delay(j, i) is the delay value annotated on the edge joining node j to i.

The node with the largest arrival time defines the maximum delay  $T_{crit}$  through the circuit. The required clocked period of this circuit should be no less than  $T_{crit}$ .

We can do a backward breadth-first traversal of the timing graph, and determine required times at all nodes. Required times of all primary outputs we set to  $T_{crit}$ . The required time of any node with fanouts is

$$T_{required}(i) = Min_{j \in fanout(i)} \{ T_{required}(j) - delay(i,j) \}$$

(2.6)

Timing slack of the connection from node i to node j is then

$$Slack(i,j) = T_{required}(j) - T_{arrival}(i) - delay(i,j)$$

$$(2.7)$$

A connection with a slack of zero is said to be on the circuit critical path. Any delay increase of such a connection will result in increase of  $T_{crit}$ . It is easy to prove that the delay along the critical path equals to  $T_{crit}$ .

Note that one can find the circuit critical path by using a traceback method. The traceback starts from the node with the largest arrival time.

VPR contains a path-based static timing analyzer which can compute circuit critical path delay after all nets of a circuit have been routed.

## 2.3 Previous Work

The FPGA community have long realized that an optimized interconnect architecture is important to the overall performance of an FPGA. This can partly explain the extensive research activities on FPGA interconnect architecture. The remainder of this section reviews some of the previous work related to this thesis.

#### 2.3.1 Pipelined Interconnect

The idea of pipelined interconnect is mainly motivated by the fact that interconnect delay dominates logic delay and hence limits user designs' clock frequency. If interconnect between two logic blocks is pipelined and the delay of each interconnect pipeline stage is comparable to the delay inside logic blocks, interconnect delay will cease to be the bottleneck.

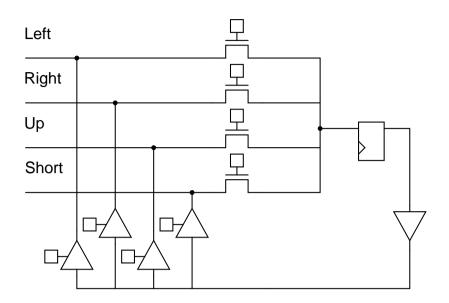

Architecture of pipelined interconnect has been reported in [36], [31], and [32]. HSRA [36] assumes a hierarchical routing architecture, instead of islandstyle architecture. Given a target clock frequency, the authors calculate (at HSRA design time) the length of interconnect that can be travelled within one clock cycle. At the end of this length, a register is placed. Figure 2.8 illustrates a switch block in this architecture. As can be observed, a register is present in the switch block. As a result of this register pipelined interconnect, signal route that consists of long interconnects takes more than one clock cycle. An HSRA prototype achieving 250MHz frequency was implemented with a 0.4um DRAM process. The authors have shown that HSRA architecture allows many pipelineable designs to run at frequencies of 2-17x the un-pipelined frequencies. However, HSRA architecture. The area overhead per logic block, compared with unpipelined architecture. The area overhead is due to pipeline registers in switch blocks and retiming registers in logic blocks.

In [32], Singh and Brown assume the island-style routing architecture. Figure 2.9 illustrates a registered switch in switch blocks. Note that this switch contains both a multiplexer and a register. Hence the route can be either pipelined or un-

Fig. 2.8: Switch boxes with registers in HSRA architecture. From [36]

pipelined. Also an extra input register per LUT is added for retiming purpose. A noticeable feature of Singh and Brown's architecture is that the number of registered tracks is parameterizable. All wire segments on a registered track have registered switches at their ends. For the architecture in which 25% of all tracks are registered, the authors reported 12% - 25% speedup for circuit critical path delay, at the price of around 10% area overhead.

Pipelined interconnect architecture poses implications on FPGA design flow. For example, a typical scenario in [36] is that there are more registers between some LUT pairs in the placed and routed design than there were in the original netlist. As a result, retiming the design is necessary to ensure the correct logical behavior. More specifically in [36] the authors retimed all LUTs such that the number of registers between any two LUTs is larger or equal to the number of registers required by the interconnects. In [32], the authors proposed a modified CAD flow in which

Fig. 2.9: Switch boxes with registers in Singh and Brown architecture. From [32]

the routing phase consists of two separate steps, namely, retiming aware routing and architecturally constrained retiming. In the first step, a conventional Pathfinderbased timing-driven routing algorithm routes all nets as if there were no registers in the connection network at all. Then long routes are shifted to registered tracks. In the second step, the actual retiming is performed.

A pipelining-aware router for FPGA called PipeRoute was presented in [30]. PipeRoute takes retimed netlist and pipelined FPGA architecture as inputs, and gives an assignment of nets (or signals) to routing resources as output. At the core of PipeRoute is an optimal one-delay router, which finds a lowest cost route between a source and a sink that goes through at least one registered switch-point. The registered switch-point is assumed to pick up either one clock cycle delay or no delay at all. This optimal one-delay router is then used to build a heuristic two-terminal N-delay router. This heuristic recursively builds an N-delay route from a (N-1)delay route by successively replacing each segment of the (N-1)-delay route with a one-delay route and then greedily selecting the lowest-cost N-delay route. Finally the two-terminal N-delay router is extended to a multi-terminal N-delay router. The multi-terminal router routes one sink at a time. All sinks are sorted in nondecreasing order of delay separation from the signal source. So the multi-terminal router first finds a route to the sink that is the least number of delays from the source, which is really a two-terminal N-delay routing problem. Then this partial routing tree connecting signal source and the first sink is expanded to include all remaining sinks. PipeRoute was employed for the design space exploration for the pipelined interconnect architecture in [29].

Armada, a timing-driven pipeline-aware router, was presented in [9]. In conventional FPGA routing, a link's timing criticality tends to be consistent between the routing iterations. This is so because the link's two endpoints are already fixed by the placement tool. However, in pipeline-aware routing, a link's criticality can change dramatically, depending on the route it takes. This happens because registers are discovered along the way during the routing. Authors of Armada tackled this problem by using *assumed criticality* breadth first search. To route from a source to a sink, N independent waves are started from the source, each assuming a different criticality from 1/N to 1.0. Each of these multiple simultaneous searches emphasizes delay versus congestion in a different way. The first wave exploration to reach the sink is the least expensive, representing a proper balance between congestion and delay. The actual value of N can be tuned to achieve tradeoff between runtime and timing accuracy. Experimental results presented in [9] showed that Armada produces significantly (as much as 60%) better critical path delays than non- timing-driven router (such as PipeRoute).

## 2.3.2 Wave-Pipelined Interconnect

Pipelining, which breaks logic gates into stages and inserts storage elements (for example, registers) between stages, is a commonly used technique to improve the system throughput. Wave-pipelining can be considered as a virtual pipelining, in which logic gates serve as the storage elements. Hence, wave-pipelining can achieve high throughput, while avoiding the timing overhead of the storage elements. But for wave-pipelining to operate correctly, additional constraints apply. This can partly explain why wave-pipelining has not gained wide popularity.

Recently, wave-pipelining technique has been applied to FPGA interconnects, and has been proved to be able to improve the bandwidth of interconnect links. Mak *et al* in [21] presented closed-form expressions for throughput of both registerbased pipelining and wave-pipelining in the context of FPGA interconnects. Their theoretic analysis showed that, in a 65nm technology and to achieve the same throughput, register-based pipelining requires 49% larger latency and 26% more power consumption than wave-pipelining. Their further SPICE modeling and simulation results confirmed advantages of wave-pipelining. For example, assuming PTM 65nm technology <sup>1</sup>, wave-pipelining claims about 22% latency improvement and around 9% power improvement over registered-based pipelining. And wavepipelining's improvement over register-based pipelining is expected to be even larger as technology scales down: at PTM 32nm technology, the latency and power improvement are shown to be 35% and 13%, respectively. Both the theoretical analysis and simulation results predicted that wave-pipelining could achieve 1.4

<sup>&</sup>lt;sup>1</sup>Predictive Technology Model. See http://ptm.asu.edu/

Gbps throughput for a data link spanning 75 tiles in 65nm FPGAs.

Teehan et al in [34] proposed using wave-pipelining as an on-chip serial signaling technique, especially for data-path FPGA designs which operate on words. Their architecture added dedicated serializer and de-serializer to each logic block. The serializer captures a data word from the logic block. The serialized data is then transmitted along the interconnect wires. At the receiving side, the de-serializer restores the data word. The reference clock signal for serializer and de-serializer is generated from user clock by a ring oscillator at the serializer side. And this reference serial clock is transmitted to the receiving side parallelly with data. This is called source-synchronous signaling. The authors' SPICE simulation results reported that wave-pipelining could achieve 2 to 4 Gbps throughput for a data link spanning 200 tiles in 65nm FPGAs. It is interesting to note that the authors predicted interconnect area saving in spite of the apparent area overhead of serializers and de-serializers. For example, almost 50% interconnect area saving can be achieved, if 512 length-4 channel wires are replaced with 8-to-1 bit-serial wires. The reasons, the authors argue, are that the number of wires is greatly reduced and connection block area shrinks significantly. One problem of Teehan's interconnect architecture is power consumption. The authors reported that wave-pipelined interconnect exhibits at least 6-8x power penalty compared with parallel-bus, due to increased data activity and high-frequency toggling of serial timing strobe. As for reliability, the authors showed that wave-pipelining is sensitive to PVT (process, temperature, and voltage) variations as well as clock jitter and skew. Although it could achieve throughput as high as 5Gbps for short links, wave-pipelined interconnect has to run much slower than that (2 - 4 Gbps) due to reliability issue.

Wave-pipelined interconnect requires neither new routing algorithm nor modi-

fications to conventional FPGA design flow. However, as put forward in [34], better supply noise modeling and accounting is essential to achieve robust communication over wave-pipelined interconnect. Hence, CAD tool support in this regard is valuable.

#### 2.3.3 Three-Dimensional Architecture

Three-dimensional architecture for FPGAs has been reported in [1], [13], and [24]. In these architectures, logic blocks are organized into a three-dimensional mesh array. These architectures have shorter average interconnect length than the conventional two-dimensional architecture. Also, they provide switch blocks with larger flexibilities. Besides, analytical results based on predicting models in [24] show that three-dimensional integration can improve interconnect delay by as much as 45% - 60%.

Alexander *et al* are possibly the first to propose a three-dimensional FPGA architecture [1]. Alexander's three-dimensional FPGA architecture is a generalization of the basic island-style architecture. In Alexander's architecture, each switch block has six immediate neighbors, as opposed to four in two-dimensional architecture. Three-dimensional switch blocks are analogous to their two-dimensional counterparts. They allow each channel segment to connect to a subset of channel segments incident on the other five faces of the switch block.

The authors' first-order analysis showed that, their proposed three-dimensional architecture achieves a shorter average interconnect length. For example, for FP-GAs with 525 switch blocks (a modest size at the time of their work), average interconnect length in three-dimensional architecture is only half of that in two-dimensional architectures.

The authors assumed the subset switch block generalized to three dimensions: a segment connects to a single segment in each of the five adjacent channels. That is,  $F_s = 5$ , while  $F_s = 3$  in two-dimensional architecture. As a result, a threedimensional switch block requires more transistors than its two-dimensional counterpart. A more refined analysis, which takes this overhead into account, showed that, for FPGAs with more than 250 switch blocks, the benefits from reduced interconnect length outweigh the overhead of three-dimensional switch block. Hence the authors concluded that an average net would consume less routing transistors in three-dimensional FPGAs.

Another early three-dimensional FPGA architecture is Rothko [13]. Rothko architecture is based on Triptych architecture: a layer of Rothko architecture is similar to Triptych, and inter-layer connections are provided. In Triptych architecture, the basic logic element is RLB (routing and logic block)<sup>2</sup> [7]. Rothko architecture extends the Triptych RLB by allowing an RLB receive outputs of the neighboring RLBs in adjacent layers. The authors' experimental results from manually mapping two designs to a two-layer Rothko architecture showed that Rothko mapping's footprint is about half of that of Triptych.

In spite of their claimed advantages, these three-dimensional architectures have not been adopted by major commercial vendors, possibly due to challenges involved in the fabrication of three-dimensional chips. Fabrication of 3D chips is usually complex, requiring additional process steps. Alexander *et al* proposed that multichip module (MCM) technology is used to vertically stack a number of 2D FPGA dies [2]. Solder bumps are used to bond dies to an underlying substrate containing wires. In this way vertical interconnections are established. A problem with this

$<sup>^2\</sup>mathrm{An}$  RLB in Triptych architecture can perform both logic implementation and signal routing. Hence the name.

vertical stacking technique is that there is a non-zero probability of defect when joining two dies. A second problem is heat dissipation. 3D architectures have a higher power-to-area ratio; hence the thermal issues are more challenging. Leeser *et al* proposed a thin film transfer approach for fabricating Rothko architecture [13]. Take a two-layer Rothko for example. First processed is a bulk silicon wafer containing half of the circuit. This is followed by the process of a second siliconon-insulator (SOI) wafer containing the other half of the circuit. Then the SOI circuit is transferred face-down onto the top of the bulk silicon wafer. An adhesive bonds the transferred circuit to the bulk. Vertical interconnections are enabled by 3D vias, which connect metals at both layers to a third common metal.

In [28], the concept of extra-dimensional FPGA, in which *logical* third and fourth dimension are mapped to standard two dimensional IC, is introduced. Logic blocks are grouped into xy planes. A conventional 2D FPGA can be considered as a xy plane. Logic blocks only connect to wires on the same xy plane. Extra dimensions are formed by interconnecting planes. The experiments demonstrated that a four-dimensional FPGA provides better scalability. For example, as the design size increases from 20 to 585 CLBs <sup>3</sup>, minimum channel width of 4D architecture remains constant, while that of 2D architecture needs to steadily increase.

Mostly, placement and routing algorithms for 2D FPGAs can be extended for 3D FPGAs. For example, the placement, global routing, and detailed routing algorithms used in [1] are extended from their 2D versions presented in [3]. More specifically, the 3D placement uses a 3D partitioning template (an m \* n \* r grid), while the 2D version uses a 2D template (an m \* n grid). Another example is the 3D FPGA design flow presented in [8], which extends VPR. The author modified the

<sup>&</sup>lt;sup>3</sup>This work assumes that a CLB consists of a four-input LUT and a bypass-able register.

VPR simulated annealing algorithm by introducing a non-adaptive schedule and a two-stage annealing. In fact, the first modification may not be strictly necessary, although the second modification is intended for optimizing circuit critical path delay. The author re-used VPR routing algorithm without any modification, as long as a routing resource graph can be generated from the 3D FPGA architecture description.

Stacked Silicon Interconnect (SSI) technology recently introduced by Xilinx represents another approach to achieve scalable interconnect for FPGAs [39]. SSI technology combines multiple FPGA die slices and a passive silicon interposer to create a die stack. The multiple die slices are placed side-by-side. This avoids the power and reliability issues that could result from stacking dies on top of each other. The passive silicon interposer interconnects the die slices by providing more than 10,000 traces between multiple die slices. Finally the die slices/ interposer stack is mounted on package substrate. Through-silicon vias (TSVs) are employed to prove connection between stack and package substrate. SSI technology is employed in Xilinx's Virtex-7 FPGAs.

FPGAs with SSI technology claim several advantages, compared with the traditional approach of connecting multiple conventional FPGAs to obtain a larger logic capacity. First, the interposer can provide as many as 10,000 connections, while IO pin count of a conventional FPGA is limited to around 1,200; Second, die-to-die latency of interposer is one fifth of pin-to-pin latency of standard IOs; Third, die-to-die connections implemented by interposer consume far less power.

Xilinx claims that, in terms of design flow, FPGAs with SSI technology can be treated like monolithic devices. There is no need of partitioning. And routing between die slices is transparent to users. Xilinx's ISE design tool supports the Virtex-7 family.

## 2.3.4 Time-Multiplexed Interconnect

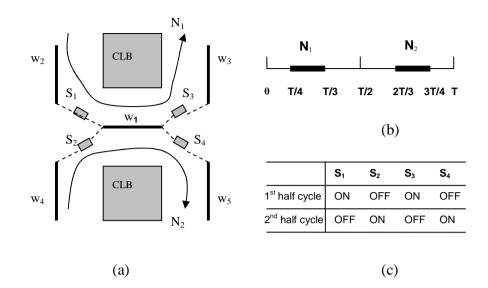

The seminal work on time-multiplexed FPGA is [35] by Trimberger et al. Based on the Xilinx XC4000E FPGA family, the introduced architecture features both time-multiplexed configurable logic blocks (CLBs) and time-multiplexed interconnects. The whole architecture is backed by one active configuration and eight inactive configurations. All the configuration bits of CLBs and interconnects can be flash reconfigured from one of the eight inactive configurations. Logic engine mode is one of the operation modes proposed by the authors for the time-multiplexed FPGA. In this mode, the FPGA sequences through multiple configurations. One configuration is called one *microcycle*. One pass through all the microcycles is called a *user cycle*. Therefore, the FPGA is reconfigured multiple times inside a user cycle. Our proposed FPGA architecture in this thesis is different from Trimberger's architecture, in that we time-multiplex interconnects only. We do not time-multiplex logic blocks. Our architecture is similar to Trimberger's architecture, in that we use the same concept of user cycle and microcycle. In particular, our architecture assumes that a user cycle is divided evenly into K microcycles. Kis an architecture parameter, which in our work is chosen to be 2, 4, 6, or 8.

Recently a commercial time-multiplexed FPGA architecture was introduced by a start-up vendor Tabula. The architecture is named Spacetime [33]. A user clock cycle is divided to eight *folds* (fold 0, fold 1, ..., and fold 7). The FPGA device starts from fold 0. In each fold, the FPGA device performs a portion of user logic, and stores results in place. Then the device gets re-configured, and moves to the next fold, in which it uses the locally stored data to perform another portion of user logic. At the completion of fold 7, the entire user logic has been performed, and a user clock cycle has been finished. After that, the device gets re-configured and starts again from fold 0, repeating the procedure described above. The reconfiguration between folds is ultra-rapid. In fact, the first generation of Tabula device employs a 1.6 GHz clock for this reconfiguration. This enables a user clock of 200 MHz divided into eight folds.

Advantages claimed by Spacetime architecture include greater logic density, higher performance, as well as greater memory density. The memory density advantage stems from the fact that Spacetime architecture uses single-port memory cells while still providing fold-based multi-port capability.

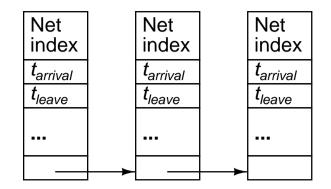

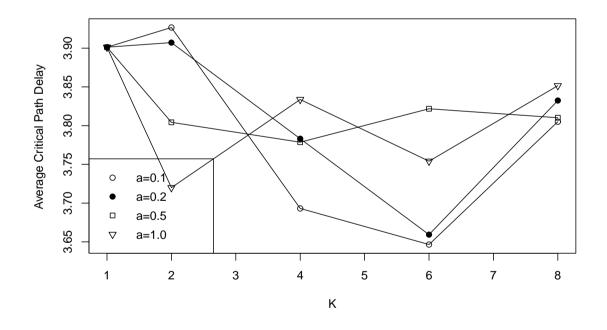

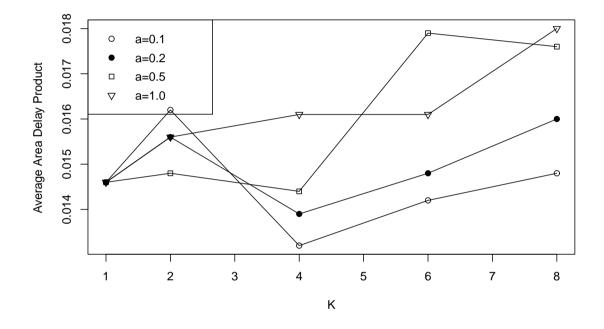

One can see that, in many ways, Spacetime architecture resembles Trimberger's time-multiplexed FPGA architecture. However, Spacetime architecture does have some unique features. For example, it allows tradeoff between speed and area. If a higher clock frequency is desired from user design, less number of folds should be used. Hence more area of the device is committed. Take a 200 MHz user design with eight folds for instance. To get higher performance, the user could run the design at 400 MHz with four folds (or, 800 MHz with two folds only) <sup>4</sup>.