# LOW-VOLTAGE LOW-POWER SWITCHED-CAPACITOR $\Delta\Sigma$ MODULATOR DESIGN

YANG ZHENGLIN

NATIONAL UNIVERSITY OF SINGAPORE

2012

### LOW- VOLTAGE LOW-POWER SWITCHED-CAPACITOR $\Delta\Sigma$ MODULATOR DESIGN

## YANG ZHENGLIN (B.Eng. M.Eng. XJTU, P.R.China)

### A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2012

## ACKNOWLEDGEMENT

I would like to express my sincere and deep appreciation to my supervisors Assistant Professor YAO Libin and Provost's Chair Professor LIAN Yong for giving me the opportunity to study in NUS, and also for their valuable guidance, continuous encouragement and financial support throughout the whole process of my research work. What I have learnt from them is not only about the study itself, their extensive knowledge and experiences have been of great value for me. Without their understanding, inspiration and guidance, I could not have been able to complete the study successfully. Also, I would like to thank our lab officers, Ms. ZHENG Huanqun and Mr. TEO Seow Miang for their supports and corporations in the arrangement of instruments and design tools.

I also appreciate all of my colleagues in the Signal Processing and VLSI Design Laboratory for their help and useful discussion during the past years.

Last, but not least I want to thank my parents for their love and support throughout my studies.

This page intentionally left blank

## **TABLE OF CONTENTS**

| CKNOWLEDGEMENTi                                  |

|--------------------------------------------------|

| ABLE OF CONTENTS iii                             |

| UMMARYvii                                        |

| IST OF TABLESix                                  |

| IST OF FIGURESxi                                 |

| IST OF ABBREVIATIONSxv                           |

| CHAPTER 1 INTRODUCTION1                          |

| 1.1 Overview of Analog-to-Digital Converters2    |

| 1.2 Motivation                                   |

| 1.3 Objectives and Significances                 |

| 1.4 List of Publications                         |

| 1.5 Organization of the Thesis                   |

| CHAPTER 2 BRIEF REVIEW OF Δ $\Sigma$ CONVERTERS9 |

| 2.1 Nyquist-Rate ADCs                            |

| 2.2 Oversampling ADCs                            |

| 2.3 $\Delta\Sigma$ Modulators                    |

| 2.4 $\Delta\Sigma$ ADC Topology                  |

| 2.4.1 Distributed Feedback Topology18            |

| 2.4.2 Input-Feedforward Topology19               |

| 2.4.3 Error Feedback Topology                    |

| 2.4.4 MASH Topology                              |

| 2.5 Circuit Implementation                       |

| CHAP  | TER 3   | DESIGN CONSIDERATION FOR LOW-VOLTAGE LOW-POWER        |    |

|-------|---------|-------------------------------------------------------|----|

| CIRCU | JITS    |                                                       | 23 |

| 3.1   | Low-V   | Voltage Low-Power Circuit Design Issues               | 23 |

|       | 3.1.1   | Floating Switch Problem                               | 23 |

|       | 3.1.2   | Intrinsic Noise                                       | 25 |

|       | 3.1.3   | Leakage Current                                       | 25 |

|       | 3.1.4   | Intrinsic Gain                                        | 26 |

| 3.2   | Low-V   | Voltage Circuit Design Techniques                     | 26 |

|       | 3.2.1   | Body-Driven Technique                                 | 26 |

|       | 3.2.2   | Charge Pump Technique                                 | 27 |

|       | 3.2.3   | Switched-Opamp Technique                              | 28 |

|       | 3.2.4   | Switched-RC Technique                                 | 29 |

| 3.3   | Low-P   | Power Circuit Design Techniques                       | 29 |

|       | 3.3.1   | Double Sampling Technique                             | 29 |

|       | 3.3.2   | Time-Sharing Technique                                | 30 |

| СНАР  | TER 4   | A 0.7-V 100-µW AUDIO MODULATOR WITH 92-dB DR IN 0.13- |    |

| µm CN | MOS     |                                                       | 33 |

| 4.1   | Introdu | uction                                                | 33 |

| 4.2   | System  | n Design                                              | 36 |

| 4.3   | Circui  | t Implementation <sup>2</sup>                         | 13 |

|       | 4.3.1   | Two-Tap FIR DAC                                       | 13 |

|       | 4.3.2   | Power-Efficient Rail-to-Rail Amplifier                | 14 |

|       | 4.3.3   | Multi-Input Comparator                                | 16 |

| 4.4   | Measu   | rement Results                                        | 18 |

|       | 4.4.1   | Measurement Setup                                     | 18 |

|       | 4.4.2  | Measurement Results and Discussions                                 | 50 |

|-------|--------|---------------------------------------------------------------------|----|

|       | 4.4.3  | Performance Comparison                                              | 52 |

| 4.5   | Conclu | usion                                                               | 53 |

| CHAP  | TER 5  | A 0.5-V 35- $\mu$ W 85-dB DR DOUBLE-SAMPLED $\Delta\Sigma$ MODULATO | R  |

| FOR A | AUDIO  | APPLICATIONS                                                        | 55 |

| 5.1   | Introd | uction                                                              | 55 |

| 5.2   | Existi | ng Double-Sampled Architecture                                      | 57 |

| 5.3   | Propos | sed Architecture                                                    | 63 |

|       | 5.3.1  | Proposed double-Sampled $\Delta\Sigma$ Architecture                 | 63 |

|       | 5.3.2  | Integrator Output Swings                                            | 67 |

|       | 5.3.3  | Mismatch Consideration                                              | 71 |

| 5.4   | Existi | ng Power-Efficient Low-Voltage Low-Power Amplifier                  | 73 |

|       | 5.4.1  | Current-Shunt Current Mirror Topology                               | 73 |

|       | 5.4.2  | Local Positive Feedback Current Mirror Topology                     | 73 |

| 5.5   | Circui | t Implementation                                                    | 74 |

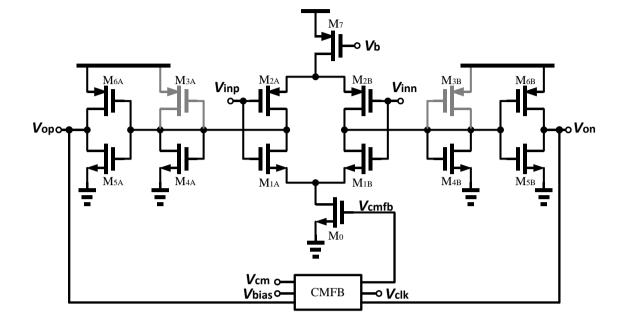

|       | 5.5.1  | Proposed Fully-Differential Amplifier with Inverter Output Stages.  | 75 |

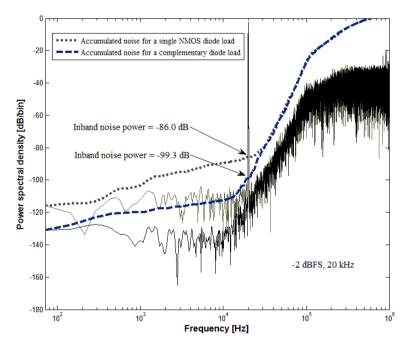

|       | 5.5.2  | Intrinsic Noise Analysis                                            | 77 |

|       | 5.5.3  | CMFB with Global Loop vs Local Loop                                 | 78 |

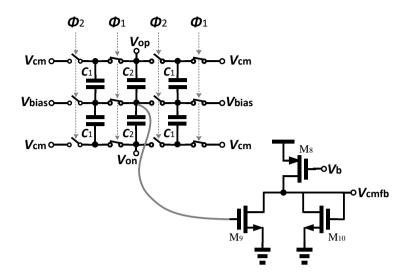

|       | 5.5.4  | Settling with Complimentary Diode Loading                           | 80 |

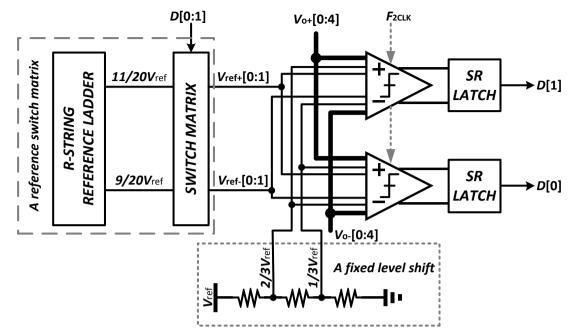

|       | 5.5.5  | Simple Reference Switch Matrix for Feedback Compensation            | 82 |

| 5.6   | Measu  | rement Results                                                      | 84 |

| 5.7   | Conclu | usion                                                               | 90 |

| CHAP  | TER 6  | CONCLUSION AND FUTURE WORKS                                         | 91 |

| 6.1   | Conclu | usion                                                               | 91 |

| 6.2   | Future | Works                                                               | 93 |

| BIBLIOGRAPHY95 |

|----------------|

|----------------|

## **SUMMARY**

As most of modern signal processing systems use digital signal instead of analog one, the interface between digital and real world becomes more crucial. ADC and DAC are two fundamental building blocks at these interfaces to convert data from one format to another. With the growing demand in portable and handheld devices, low-power ADC design attracts much research effort in the past few years, especially sub-1 V Delta-Sigma ( $\Delta\Sigma$ ) modulators. In this research, we proposed several techniques for low-voltage low-power  $\Delta\Sigma$  modulator designs.

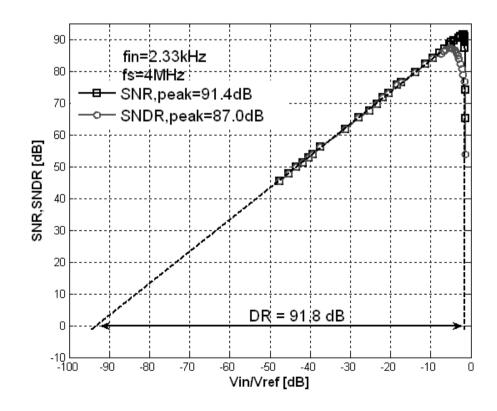

The first fabricated chip in the study is a fourth-order audio-band  $\Delta\Sigma$  modulator with a single-loop single-bit input-feedforward architecture which employs a finite impulse response (FIR) feedback DAC [1]. It has been implemented in a 0.13-µm CMOS process. Switch-free direct summation technique has been adopted to minimize the power consumption and reduce the supply voltage. Conventional switched-capacitor (SC) summation circuit for the feedforward paths is removed, and it is replaced by a multi-input comparator. A 2-tap FIR filter is inserted in the feedback loop to effectively attenuate the high frequency quantization noise, resulting 22% reduction in the maximum integration step of the first integrator and relaxing the slew rate requirement for the OTA to 9.5 V/µsec (diff). Clocked at 4 MHz, the modulator achieves 87.0 dB SNDR, 91.4 dB SNR, and 91.8 dB DR for a 20-kHz signal bandwidth while consuming 99.7 µW from a 0.7-V supply.

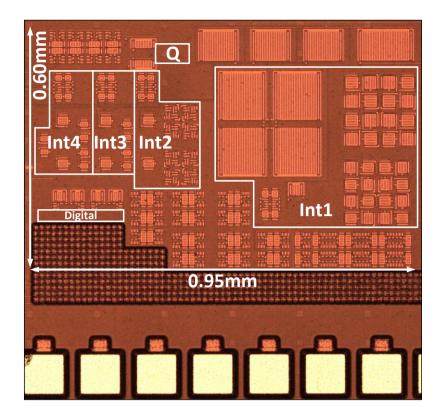

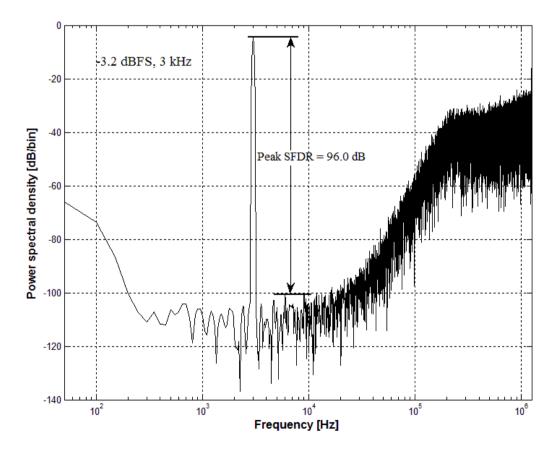

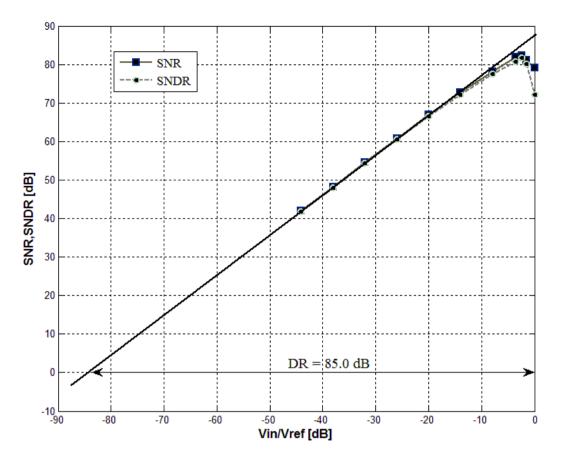

The second prototype presents a 0.5-V 1.5-bit double-sampled  $\Delta\Sigma$  modulator for audio codec. Unlike other existing double-sampled design, the proposed doublesampled  $\Delta\Sigma$  modulator employs input-feedforward topology, which reduces internal signal swings, hence relaxes design requirements for low-voltage amplifier and reduces distortion. Moreover, the proposed architecture with compensation loop restores noise transfer function to that of its single-sampled version and avoids performance degradation. It also employs a new fully-differential amplifier with a global common-mode feedback loop to minimize power, as well as a resistor-stringreference switch matrix based on direct summation quantizer to simplify compensation loop. The chip prototype has been fabricated in a 0.13-µm CMOS technology with a core area of 0.57 mm<sup>2</sup>. The measured results show that operated from a 0.5-V supply voltage with a clock frequency of 1.25 MHz, the modulator achieves a peak SNDR of 81.7 dB, a peak SNR of 82.4 dB and DR of 85.0 dB while consuming 35.2 µW for a 20-kHz signal bandwidth.

## LIST OF TABLES

| Table 4.1 Performance summary.   51                                                         |

|---------------------------------------------------------------------------------------------|

| Table 4.2 Performance comparison with state-of-the-art low-power low-voltage $\Delta\Sigma$ |

| audio modulators                                                                            |

| Table 5.1 Thermal noise comparison between classical current mirror and the                 |

| proposed OTA78                                                                              |

| Table 5.2 Comparison of output stage between conventional CM loop with a single             |

| NMOS and proposed CM loop80                                                                 |

| Table 5.3 Performance summary.    89                                                        |

| Table 5.4 Performance comparison with state-of-the-art sub-1V audio-band $\Delta\Sigma$     |

| modulators                                                                                  |

This page intentionally left blank

## **LIST OF FIGURES**

| Figure 2.1 Block diagram of Nyquist-rate ADC and operation of the different blocks                 |

|----------------------------------------------------------------------------------------------------|

| in time and frequency domain11                                                                     |

| Figure 2.2 Linear model of quantizer                                                               |

| Figure 2.3 Transfer characteristics of (a) single-bit quantizer and (b) multi-bit                  |

| quantizer12                                                                                        |

| Figure 2.4 Block diagram of oversampling ADC and operation of the different blocks                 |

| in time and frequency domain                                                                       |

| Figure 2.5 General block diagram of $\Delta\Sigma$ modulator15                                     |

| Figure 2.6 Linearized model for a first-order $\Delta\Sigma$ modulator16                           |

| Figure 2.7 Transfer functions of a second-order canonical $\Delta\Sigma$ modulator17               |

| Figure 2.8 General diagram of a <i>N</i> -th order single-loop feedback topology18                 |

| Figure 2.9 General diagram of a N-th order single-loop input-feedforward topology.19               |

| Figure 2.10 Second-order error feedback topology20                                                 |

| Figure 2.11 General block diagram of (a) DT and (b) CT $\Delta\Sigma$ modulator22                  |

| Figure 3.1 Floating switch in a typical SC integrator                                              |

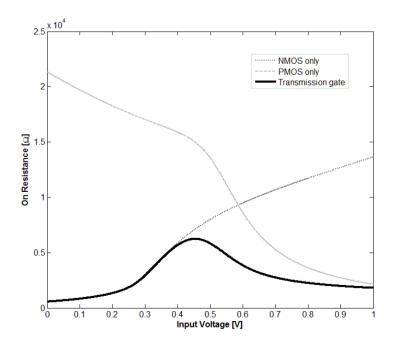

| Figure 3.2 Simulated on-resistance of a transmission gate under 1-V supply voltage                 |

| ( <i>Vth</i> , <i>n</i> =438.2m, <i>Vth</i> , <i>p</i> =578.7m, <i>W</i> / <i>L</i> =1.2u/0.12u)24 |

| Figure 3.3 Conceptual diagram of bootstrapped switch                                               |

| Figure 3.4 Two-stage miller-compensated switched opamp                                             |

| Figure 3.5 Switched-RC integrator                                                                  |

| Figure 3.6 Double-sampled SC integrator                                                            |

| Figure 4.1 Second-order single-loop feedforward topology                                           |

| Figure 4.2 Conceptual operation of a 2-tap FIR filter                                              |

| Figure 4.3 Output signal swings of the first integrator with/without a FIR filter40              |

|--------------------------------------------------------------------------------------------------|

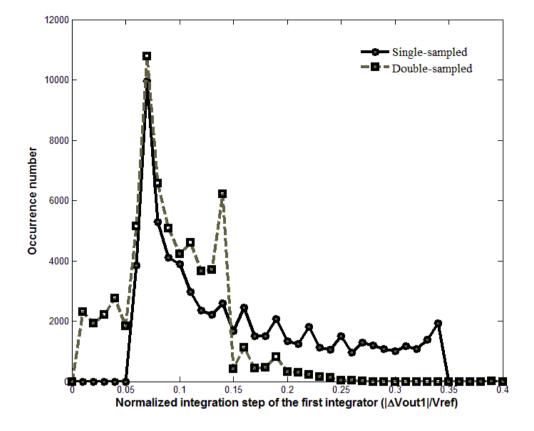

| Figure 4.4 Histogram of integration step of the first integrator with/without a FIR              |

| filter                                                                                           |

| Figure 4.5 System diagram of the $\Delta\Sigma$ modulator                                        |

| Figure 4.6 Percentage of noise leakage over total in-band quantization noise versus              |

| the first opamp's GBW41                                                                          |

| Figure 4.7 Signal timing diagram of the feedback signal and the first stage output44             |

| Figure 4.8 Gain-enhanced current mirror OTA45                                                    |

| Figure 4.9 Different implementation techniques of the feedforward paths47                        |

| Figure 4.10 Chip micrograph48                                                                    |

| Figure 4.11 Printed circuit board for the prototype chip testing                                 |

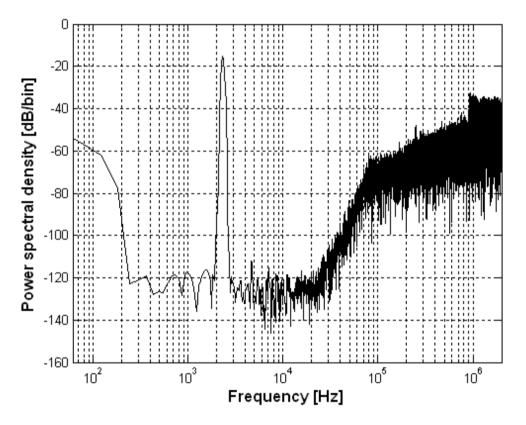

| Figure 4.12 Measured output spectrum with a 2.33-kHz sinusoidal input50                          |

| Figure 4.13 Measured SNR and SNDR versus input amplitude51                                       |

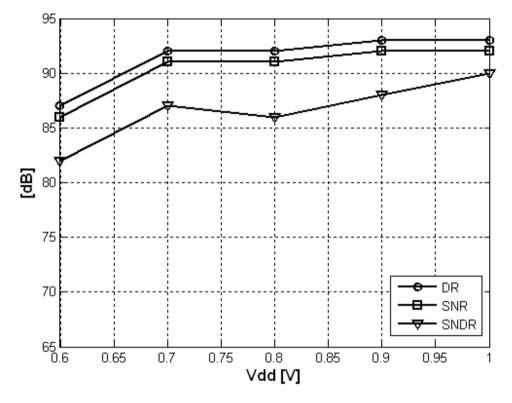

| Figure 4.14 Performance versus supply voltage                                                    |

| Figure 5.1 (a) Double-sampled switched-capacitor integrator. (b) Simplified model of             |

| double-sampled switched-capacitor integrator                                                     |

| Figure 5.2 Aliasing effect due to sampling process in a double-sampled $\Delta\Sigma$ modulaotr. |

|                                                                                                  |

| Figure 5.3 Fully-floating switched-capacitor integrator                                          |

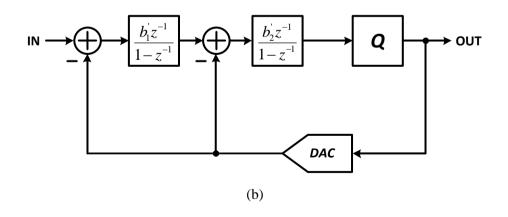

| Figure 5.4 (a) Second-order double-sampled architecture based on feedback topology.              |

| (b) Second-order single-sampled architecture based on feedback topology60                        |

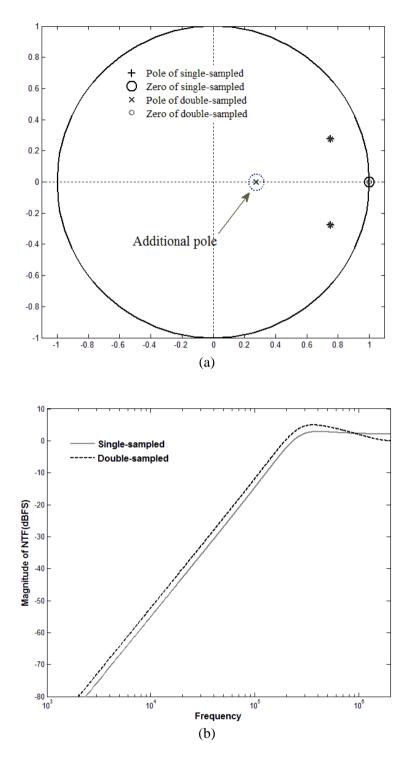

| Figure 5.5 (a) Pole-zero chart of single-sampled and double-sampled architecture. (b)            |

| NTF comparison between single-sampled and double-sampled architecture62                          |

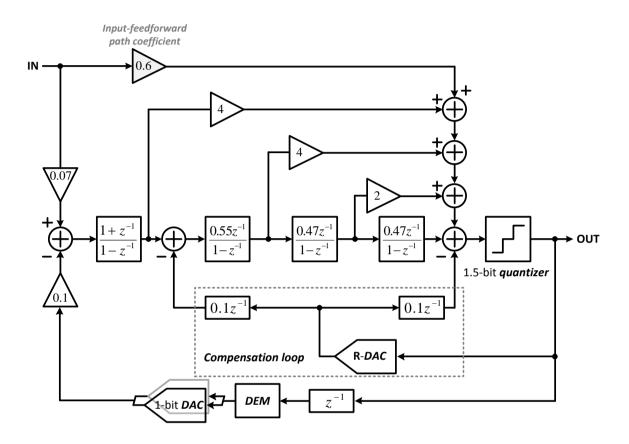

| Figure 5.6 Proposed fourth-order double-sampled $\Delta\Sigma$ modulator based on input-         |

| feedforward topology                                                                             |

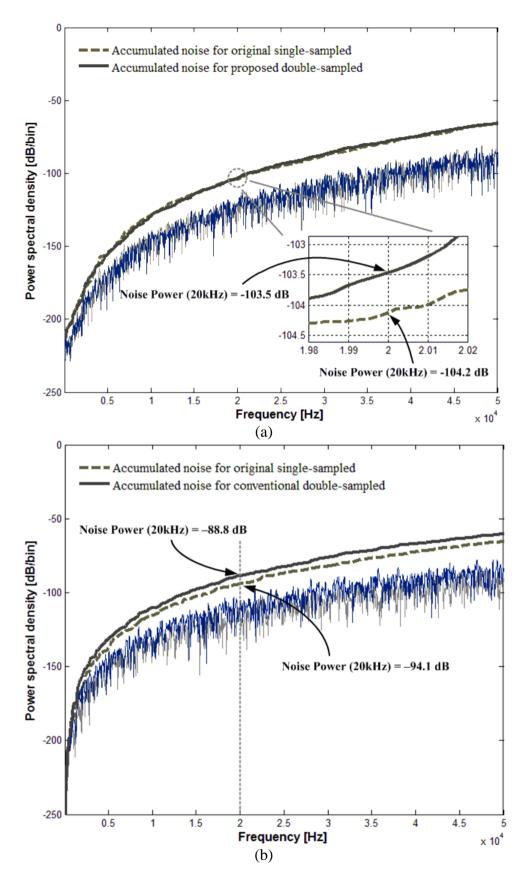

| Figure 5.7 (a) Noise-shaping comparison between proposed double-sampled and            |

|----------------------------------------------------------------------------------------|

| original single-sampled architecture. (b) Noise-shaping comparison between             |

| conventional double-sampled and original single-sampled architecture                   |

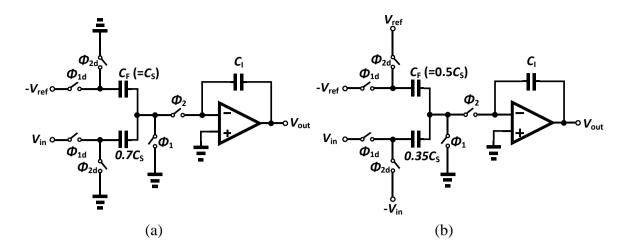

| Figure 5.8 (a) Sampling network with scaled input sampling capacitors and feedback     |

| reference sampling capacitor. (b) Proposed sampling network with scaled input          |

| sampling capacitors and feedback reference sampling capacitor                          |

| Figure 5.9 Reduced integration step of the first integrator of double-sampled          |

| architecture                                                                           |

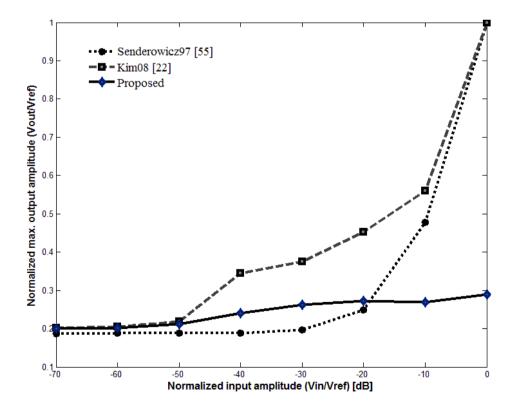

| Figure 5.10 Output voltage swing of the first integrator versus increased input signal |

| amplitude                                                                              |

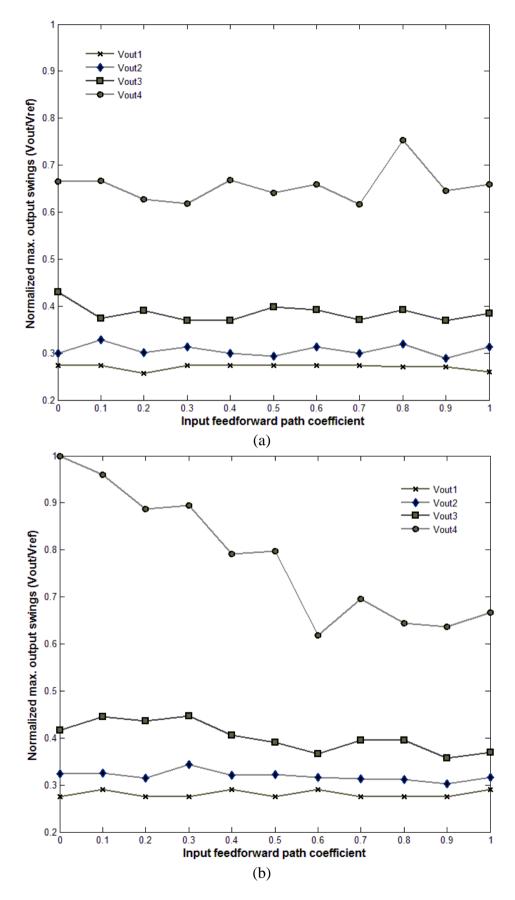

| Figure 5.11 Normalized output voltage swings versus input feedforward path             |

| coefficient (a) with -20 dBFS sinusoidal input. (b) with 0 dBFS sinusoidal input70     |

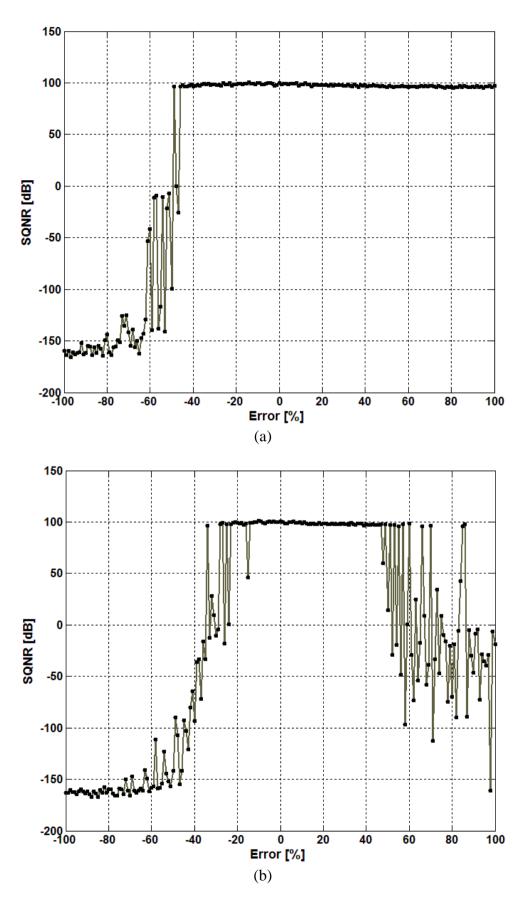

| Figure 5.12 Performance versus error (a) with -1 dBFS sinusoidal input. (b) with 0     |

| dBFS sinusoidal input72                                                                |

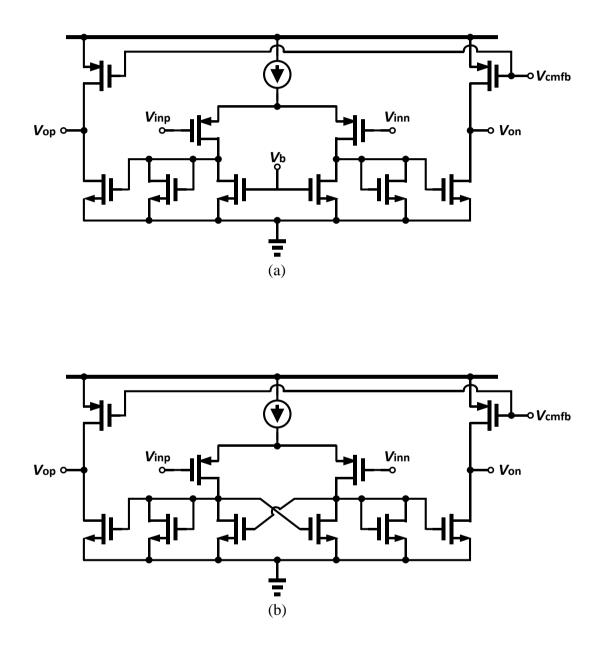

| Figure 5.13 (a) Current-shunt current mirror amplifier. (b) Current mirror amplifier   |

| employing a local positive feedback loop74                                             |

| Figure 5.14 Proposed fully-deferential amplifier with inverter output stages75         |

| Figure 5.15 Improved SC-CMFB circuits with an inverting stage76                        |

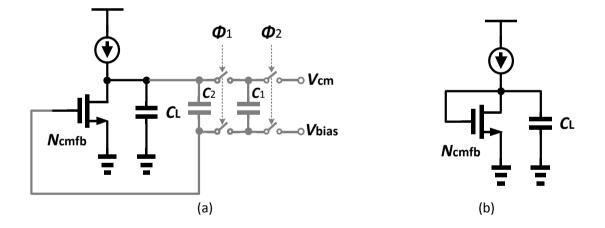

| Figure 5.16 (a) CMFB loop of conventional fully-differential amplifier (b) simplified  |

| model of (a)                                                                           |

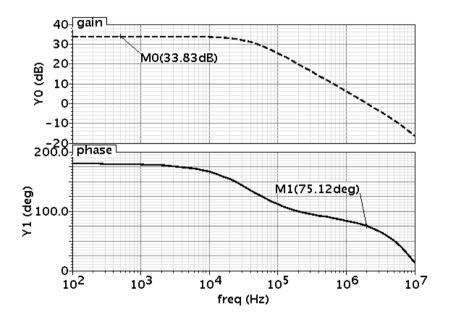

| Figure 5.17 CM loop gain and bandwidth of the proposed opamp                           |

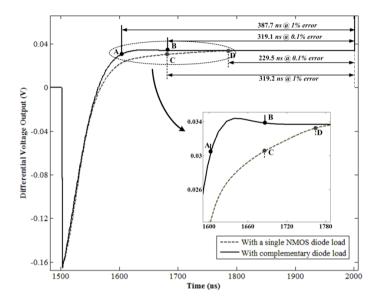

| Figure 5.18 Settling behavior comparison between a single diode load and               |

| complementary diode load82                                                             |

| Figure 5.19 Quantization noise leakage induced by settling error                       |

| Figure 5.21 Chip photograph85                                                       |

|-------------------------------------------------------------------------------------|

| Figure 5.22 Measured output spectrum with -3.2-dBFS 3 kHz sinusoidal input85        |

| Figure 5.23 Measured SNR and SNDR versus input amplitude for a 3-kHz sinusoid.      |

|                                                                                     |

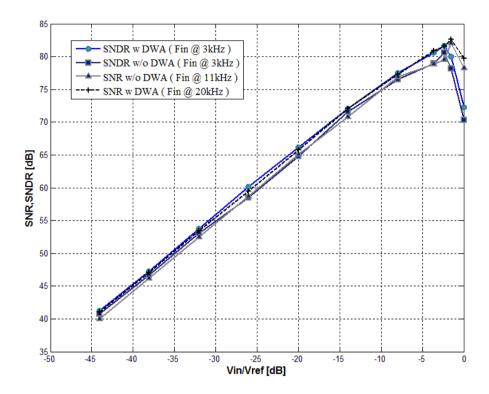

| Figure 5.24 Measured SNR/SNDR versus input amplitude w/wo DWA circuit87             |

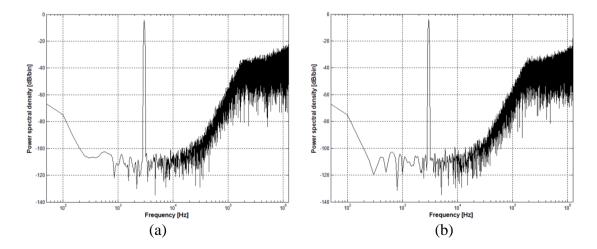

| Figure 5.25 Measured spectrum for a –3.4-dB, 3-kHz sinusoidal input signal (a) with |

| DWA circuit, (b) without DWA circuit                                                |

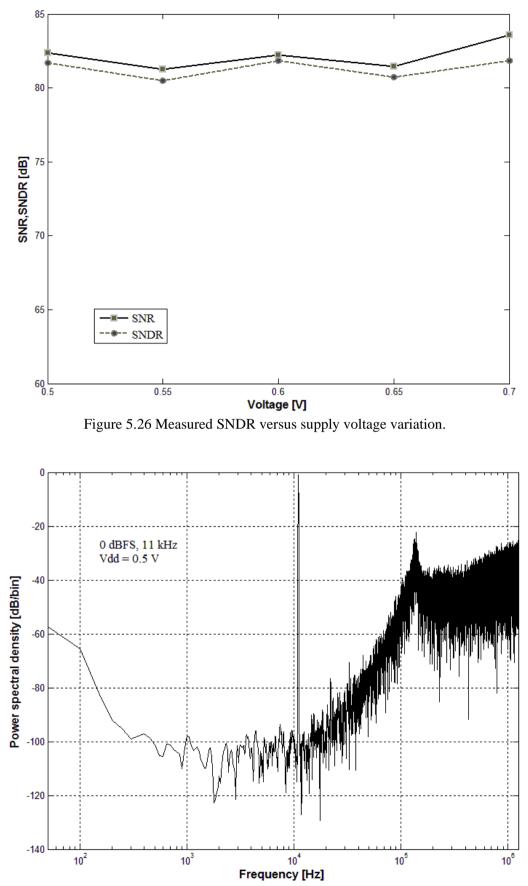

| Figure 5.26 Measured SNDR versus supply voltage variation                           |

| Figure 5.27 Measured spectrum for a 0-dB, 11-kHz sinusoidal input signal            |

Figure 5.20 Circuits blocks of feedback compensation based on the 1.5-bit quantizer.

## LIST OF ABBREVIATIONS

| Anti-Aliasing                          |

|----------------------------------------|

| Analog-to-Digital Converter            |

| Analog Signal Processing               |

| Common Mode Rejection Ratio            |

| Common-Mode Feedback                   |

| Continuous-Time                        |

| Digital-to-Analog Converter            |

| Digital Signal Processing              |

| Discrete-Time                          |

| Dynamic Range                          |

| Effective Number of Bits               |

| Figure-Of-Merits                       |

| Low-Pass                               |

| Noise Transfer Function                |

| Operational Transconductance Amplifier |

| OverSampling Ratio                     |

| Power Supply Rejection Ratio           |

| Printed Circuit Board                  |

| Power Spectral Density                 |

| Signal to Noise Ratio                  |

| Switched-Capacitor                     |

| Signal-to-Noise-and-Distortion Ratio   |

| Signal-to-Quantization Noise Ratio     |

|                                        |

| SOC | System-On-Chip            |

|-----|---------------------------|

| STF | Signal Transfer Function  |

| THD | Total Harmonic Distortion |

## CHAPTER 1 INTRODUCTION

Microelectronics technologies have changed our life by its rapidly improved products for more than four decades. The key ability of microelectronics is to reduce feature size of transistor for lowering fabrication cost. One of the most famous trends is geometrical scaling, which is usually expressed as Moore's Law. The scaling trend has guided targets for decades, and will continue in many aspects of chip manufacture.

Reduced transistor channel length and thickness of gate dielectrics have driven supply voltage to decline for reliability reasons. Since voltage difference is the most common used expression in today's mixed signal circuits, reduced supply voltage means decreasing the maximum achievable signal level. In order to keep the same dynamic range, analog circuits are likely to dissipate more power when the dynamic range is limited by thermal noise. This has a strong impact on mixed-signal product development for system-on-chip (SOC) solutions. Moreover, reduced supply voltage decreases voltage headroom of analog circuits, which limits the choices of circuit topologies. For example, the telescopic topology is seldom used in low-voltage design despite its high gain feature.

Impact of the voltage drop between drain and source upon effective channel length becomes more severe than ever as the effective channel length decreases. This results in reduced intrinsic gain of transistors. Reduced device intrinsic gain causes difficulty in building precision analog blocks. The accuracy of analog blocks is important to system in many aspects of performances, such as harmonic distortion, offset error, differential non-linearity, etc. This trend demands a robust system with relaxed requirement on analog blocks.

### 1.1 Overview of Analog-to-Digital Converters

Analog-to-digital converters (ADCs) are frequently required to interface digital processors to real signals such as radio, image and speech. Since quantization of continuous amplitude of information requires analog operations, ADCs often limit the throughput of digital signal processing (DSP) based systems. In general, ADCs can be categorized into Nyquist ADCs and oversampling ADCs based on sampling rate. Usually, the minimum required sampling rate of Nyquist ADCs is twice the bandwidth of input signal, thus signal bandwidth of this sort of ADCs could achieve several tenth Giga Hertz [2-4]. However, their accuracy is directly limited by quantization error and hence its resolution is restricted to approximate 15 bits of effective number of bit (ENOB) [5, 6]. Oversampling ADCs have their sampling frequency considerably higher than the bandwidth of input signal. Oversampling avoids aliasing, improves resolution and reduces in-band noise. Resolution of this sort of ADCs could achieve 24 bits [7-9], but the maximum bandwidth of the ADCs is limited by a few hundred Mega Hertz [10]. Survey data collected advanced ADCs [11], regardless of their architecture, over past fourteen years indicates that the power efficiency of ADCs, has improved on average by a factor of two every two years while the performance has doubled every four years. It also demonstrates that speed, power efficiency and resolutions are most important trade-off in design of state-ofthe-art advanced ADCs.

### **1.2 Motivation**

Usually, quantization noise is evenly spread over the whole bandwidth of converter at the Nyquist sampling rate. If an analog signal is sampled at a rate much higher than that of the Nyquist frequency during analog to digital conversion and then digitally filtered to limit it to the signal bandwidth, the resulting signal may have the following features.

- Due to better properties of digital filters a sharper anti-aliasing filter can be realized and hence the filtered signal could have better result.

- With oversampling technique, it is possible to obtain an effective resolution larger than that provided by the converter alone.

- The improvement in SNR is 3 dB per octave of oversampling which is not sufficient for many applications. Therefore, oversampling is usually associated with noise shaping. With noise shaping, the improvement is 6*L* + 3 dB per octave where *L* is the order of loop filter used for noise shaping. For example, a second-order loop filter provides an improvement of 15 dB per octave.

Therefore,  $\Delta\Sigma$  ADCs, which use both oversampling and noise shaping techniques, have a unique character that is suitable for nanometer-scale technologies. First, the design requirement for a front-end anti-alias filter is quite relaxed due to oversampling reasons. The roll-off frequency response needs not be too sharp as that for Nyquist ADCs. This results in simpler architecture of the anti-alias filter as well as less power consumption. Second, since noise shaping technique improves the effective resolution while high loop gain suppresses distortions induced by analog building blocks, stringent accuracy is not required in analog building blocks in most cases. For example, more than 100 dB DC gain is required for amplifier in first few stages of a pipeline structure which is desired to achieve 14 bit resolution if no digital calibration is used [12]. In contrast to pipeline ADCs, a single-loop high-order  $\Delta\Sigma$ modulator needs only 40 dB DC gain for the first amplifier to reach the same accuracy level [13, 14]. Since continuing down scaling of effective channel length makes the intrinsic gain of a transistor decrease to approximate 20 dB in sub-100 nm CMOS technologies [15],  $\Delta\Sigma$  ADCs demonstrate a great compatibility with state-ofthe-art CMOS technologies which is substantially optimized for digital circuitry.

Low-voltage low-power  $\Delta\Sigma$  ADCs have increasingly gained attentions not only because of the need for accompanying pace of down-scaling, but also due to the proliferated demand for portable or handheld applications. For past ten years, lowest supply voltage of this sort of ADCs for audio-band applications has declined from 1 V to approximate 0.25 V [16] while the power consumption has decreased from several milliwatts [17, 18] to several tenth microwatts [19, 20]. Although power consumption of this sort of ADCs has considerably decreased, the performance still remains as high as above 85 dB of dynamic range (DR), so that it is applicable in many cases such as image sensor, digital-audio codec [20-24].

#### **1.3 Objectives and Significances**

Research gaps for current study of low-voltage low-power SC  $\Delta\Sigma$  modulators are summarized below:

• Although single-loop multi-bit  $\Delta\Sigma$  modulators exhibit good robustness and could handle full input signal range, the quantizer suffers from mismatch

problem and hence the performance is degraded [25]. Moreover, dynamic element matching (DEM) circuit which is employed to suppress non-linearity of DAC tends to consume at least several hundred microwatts [14].

- Single-loop single-bit ΔΣ modulators tend to result in lower power consumption. However, low-order of this architecture suffers from idle tone while high-order architecture might encounter stability problem [26]. Moreover, SC implementation of this architecture usually fails to reach full referece range and hence is inferior to its multi-bit counterpart.

- Multi-stage noise shaping  $\Delta\Sigma$  modulators (MASH) avoid stability problem while restore high-order noise shaping character. Unfortunately, this architecture suffers from mismatch problem between stages and requires high accuracy of analog building blocks. Therefore, this architecture tends to result in higher power consumption [27].

The main aim of this study is to propose a low-voltage low-power SC  $\Delta\Sigma$  modulator. The specific objectives of this study are to:

- Develop a SC sampling network that could handle full available reference range for single-loop single-bit  $\Delta\Sigma$  modulators.

- Analyze and compare the noise performance of the proposed sampling network with conventional sampling network.

- Develop a power-efficient amplifier or system architecture that suitable for low-voltage low-power audio-band applications.

- Reduce supply voltage to the extent that could be comparable to sum of the threshold voltage of both PMOS and NMOS.

- Minimize the power consumption while maintaining high DR as before.

### **1.4 List of Publications**

The listed below are publications generated from this study.

**Zhenglin Yang**, Libin Yao, "A 1-V 190-μW Delta-Sigma Audio ADC in 0.13-μm full digital CMOS technology," *IEEE International Conference on Electron Devices and Solid-State Circuits*, pp.1-4, Dec., 2008.

**Zhenglin Yang,** Libin Yao, Yong Lian, "A 0.7-V 100-μW Audio Delta-Sigma Modulator with 92-dB DR in 0.13-μm CMOS," *Proc. IEEE Int. Symp. Circ. Syst.* (*ISCAS*), pp. 2011-2014, May, 2011.

**Zhenglin Yang,** Libin Yao, Yong Lian, "A 0.5-V 35- $\mu$ W 85-dB DR Double-Sampled  $\Delta\Sigma$  Modulator for Audio Applications," *IEEE Journal of Solid-State Circuits*, pp. 722-732, Mar., 2012.

### 1.5 Organization of the Thesis

The thesis is organized as follows:

**Chapter 2**: This chapter presents a brief review of  $\Delta\Sigma$  converter. Theoretical calculation of basic parameter is presented first, followed by an introduction of several architectures of  $\Delta\Sigma$  modulator and their implementation.

**Chapter 3**: This chapter discusses design considerations for low-voltage low-power circuits. The discussion starts from low-voltage circuit design issues. Then it is followed by low-voltage circuit design techniques. Collaborated with low-voltage application, low-power design technique is presented at the end.

**Chapter 4**: This chapter presents a low-voltage low-power  $\Delta\Sigma$  modulator for audioband applications. The Architecture of this modulator is based on input-feedforward topology. The modulator employs a 2-tap FIR DAC to reduce integration step of the first stage. The feedforward path is embedded in a multi-input comparator to simplify circuit implementation. The fabricated prototype operates from a 0.7-V supply voltage while consuming 99.7  $\mu$ W.

**Chapter 5**: This chapter presents a double-sampled 1.5-bit SC  $\Delta\Sigma$  modulator for audio-band applications. The modulator operates from a 0.5-V supply with a three level quantization. Compensated double sampling scheme and a proposed sampling network with an improved noise performance are employed in the work. The chip prototype has been fabricated in a 0.13-µm CMOS technology with a core area of 0.57 mm<sup>2</sup>.

**Chapter 6**: This chapter summarizes the study and draws conclusions. Future work of low-voltage low-power  $\Delta\Sigma$  converter is also presented here.

## This page intentionally left blank

### **CHAPTER 2**

## BRIEF REVIEW OF $\Delta\Sigma$ CONVERTERS

When modern signal processing extensively employ digital signal other than analog signal, the interface between digital domain and real world becomes more crucial. ADCs and DACs are fundamental building blocks of theses interfaces. Low-voltage low-power circuits are increasingly demanded for portable or handheld devices while their performances still expected to be high. These low-voltage low-power ADCs are the subject of this study.

Compared to classical Nyquist ADCs such as pipeline, successive approximation and flash type,  $\Delta\Sigma$  ADCs offer many unique advantages. First, the combination of oversampling and noise-shaping technique allows it to trade speed for accuracy. Therefore the converter is insensitive to circuit imperfections such as mismatch. Although  $\Delta\Sigma$  ADCs require an additional digital decimation filter to remove the outof-band quantization noise, modern CMOS technologies which substantially optimized for digital circuits make the implementation of this type of ADC easy. Second, due to inherently oversampling character of the ADCs, the complicated analog anti-aliasing filter with sharp transition is avoided. Third, one type of  $\Delta\Sigma$ ADCs which called frequency-to-digital  $\Delta\Sigma$  ADCs mostly implements all building blocks by digital circuits [28, 29], and hence is very compatible with state-of-the-art nano-scale technologies.

This chapter starts from Nyquist conversion, and then presents the quantization error

and the calculated signal-to-noise ratio of the converter. Next, the concepts of oversampling and noise-shaping are introduced. Finally, several architectures of  $\Delta\Sigma$  modulators as well as circuit implementations are presented.

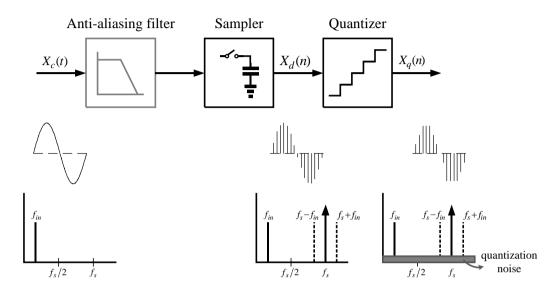

### 2.1 Nyquist-Rate ADCs

In a Nyquist conversion, the signal bandwidth  $f_b$  could reach up to  $\frac{f_s}{2}$ , where  $f_s$ represents the sampling frequency of the system. As illustrated in Figure. 2.1, a Nyquist-rate ADC usually consists of an anti-aliasing filter, a sampler and a quantizer. The input of the Nyquist conversion system is a continuous-time signal  $X_c(t)$ . A continuous time signal  $X_c(t)$  is converted into discrete data  $X_d(n)$  by the sampler. If the frequency of the input signal exceeds the band of interest, an anti-aliasing filter is required to remove the out-of-band signals because these parts can alias into the baseband because of sampling operation. The anti-aliasing filter has a low-pass filter character. In ideal case, the transition band is zero and hence the minimum sampling frequency without aliasing is  $2f_b$ . In practice however, the abrupt transition from passband to stopband cannot be implemented. Therefore, for a proper operation, the corner frequency is defined as  $\frac{f_s}{2}$ , which represents the sum of the signal band and the transition band. This implies that the practical Nyquist conversion is slightly oversampled. The quantizer converts the sampled data  $X_d(n)$  into quantized data  $X_q(n)$ . Meanwhile, the quantization error is introduced into signal band. The maximum amplitude of quantization error is dependent on the levels of the quantizer. If the sampled data varies random enough, the introduced quantization error can be regarded as a white noise. In time domain, the input signal is multiplied by a periodic

Dirac pulses spaced at  $\frac{1}{f_s}$ . This corresponds to a convolution with a periodic pulse spaced at  $f_s$  in the frequency domain. After the convolution, aliasing appears if the highest frequency of input signal exceeds  $\frac{f_s}{2}$ .

Figure 2.1 Block diagram of Nyquist-rate ADC and operation of the different blocks in time and frequency domain.

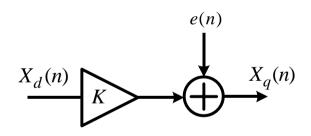

Figure 2.2 Linear model of quantizer.

Figure 2.2 shows a linear model of a quantizer, where  $X_d(n)$ ,  $X_q(n)$ , e(n), K represent the sampled data, the quantized data, the quantization error and the gain of the quantizer, respectively. This figure implies that even an ideal quantizer does introduce a degradation of the input signal. Since the input and output range are not necessarily equal, the quantizer can exhibit a gain different from one. Figure 2.3

shows transfer characteristics of single-bit and multi-bit quantizer, respectively. We can clearly see that the quantization gain of single-bit quantizer could vary arbitrarily while that of multi-bit quantizer might be regarded as constant. If the quantization error could be represented by a white noise source, the total quantization noise power can be calculated as [30]

$$e_q^2 = \int_{-\infty}^{\infty} e^2 de = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} e^2 de = \frac{\Delta^2}{12},$$

(1)

where  $\Delta$  is defined as the step size of the quantizer.

Figure 2.3 Transfer characteristics of (a) single-bit quantizer and (b) multi-bit quantizer.

In order to obtain signal-to-noise ratio (SNR) of the quantizer, the signal power also needs to be calculated. The maximum signal range of the quantizer [31] can be represented by

$$x_{max} = 2^m \frac{\Delta}{2k},\tag{2}$$

where m represents the number of bits of the quantizer, K represents the gain of the quantizer. Thus, the signal power through the quantizer is

$$Power = \frac{(kx_{max})^2}{2} = 2^{2m-3}\Delta^2.$$

(3)

From the ratio of (1) and (3), the peak SNR of an ideal m-bit quantizer can be expressed as

$$SNR_n = 1.76 + 6.02 \ m \ dB,$$

(4)

It should be noted that each additional bit in the quantizer results in approximate 6 dB improvement in SNR.

### 2.2 Oversampling ADCs

Besides classical Nyquist ADCs, an alternative type of ADCs is oversampling ADCs which have their input signal sampled at much higher frequency than the Nyquist sampling rate. And the oversampling ratio (OSR) is defined as the effective sampling frequency divided by the Nyquist rate, i.e.,

$$OSR = \frac{f_s}{f_N} = \frac{f_s}{2f_b}.$$

(5)

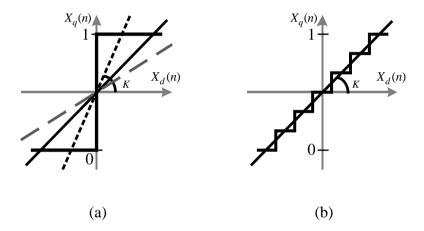

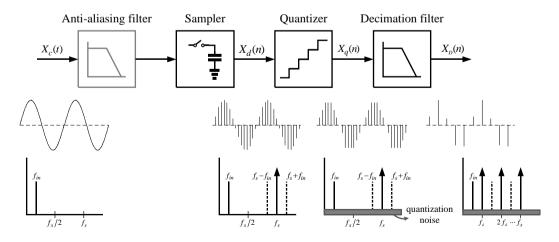

Figure 2.4 shows the operation of an oversampling ADC. Compared to Nyquist-Rate ADCs illustrated in Figure 2.1, a decimation filter is required in the post signal

Figure 2.4 Block diagram of oversampling ADC and operation of the different blocks in time and frequency domain.

processing. The function of the decimation filter is to down-sample the quantized result at a lower rate while convert the oversampled short-bit word to long-bit one.

Oversampling ADCs have an advantage that the high sampling rate significantly alleviates the design requirement for the analog anti-aliasing filter. This is because the signal bandwidth  $f_b$  is much lower than half of the sampling rate  $\frac{f_s}{2}$  and the spectrum between  $f_b$  and  $\frac{f_s}{2}$  cannot alias into the signal band, therefore, the large transition space from pass band to stop band eases implementation of the anti-aliasing.

Since all quantization noise appears at the band of  $-\frac{f_s}{2}$  to  $\frac{f_s}{2}$ , only a portion of them falls into the band of interest. Thus the total quantization noise power can be calculated as [30]

$$N_q = e_q \frac{f_b}{f_s/2} = \frac{\Delta^2}{120SR},\tag{6}$$

where  $\Delta$  is defined as the step size of the quantizer. Compared to a Nyquist-rate converter, the noise power of the signal band is reduced by OSR.

The equation to calculate the signal power is identical as that for a Nyquist-rate converter. The peak SNR of an oversampling converter results in:

$$SNR_n = 1.76 + 6.02 m + 10 \log(OSR) dB.$$

(7)

where m represents the number of bits of the quantizer.

### **2.3** $\Delta\Sigma$ Modulators

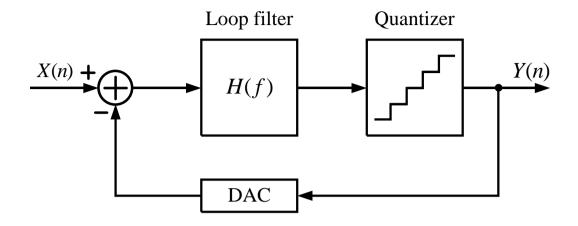

Figure 2.5 General block diagram of  $\Delta\Sigma$  modulator.

By applying a high-gain loop filter before the quantizer and forming a negative feedback loop, as shown in Figure 2.5, the spectrum of the quantization noise can be high-pass shaped, and resulting in a noise-shaped modulator which is a most important block of  $\Delta\Sigma$  converter. This type of modulator consists of a loop filter, an *m*-bit quantizer and an *m*-bit DAC. When noise-shaping and oversampling are combined, a significant improvement of SNR is achieved. A noised-shaped oversampled converter is called a  $\Delta\Sigma$  converter. Figure 2.5 shows a basic structure of a  $\Delta\Sigma$  modulator. By employing a linearized model for the quantizer and assuming the DAC is ideal, the linearized model for a first-order  $\Delta\Sigma$  modulator is illustrated in Figure 2.6.

The linear model has two inputs: the input signal and the negative quantization result. The output thus can be represented in *Z*-domain as

$$Y(z) = H_{\chi}(z)X(z) + H_{e}(z)E(z),$$

(8)

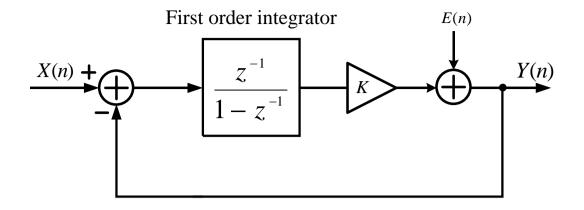

Figure 2.6 Linearized model for a first-order  $\Delta\Sigma$  modulator.

where Y(z), X(z) and E(z) are digital output, analog input signal and quantization error in Z-domain, respectively;  $H_x(z)$  and  $H_e(z)$  are the signal and noise transfer functions, respectively.

Suppose quantizer gain K is unity, the signal and noise transfer functions could be respectively represented as

$$H_{\chi}(z) = \frac{H(z)}{1+H(z)},\tag{9}$$

$$H_e(z) = \frac{1}{1 + H(z)},$$

(10)

For a first-order low-pass loop filter where transfer function  $H(z) = \frac{z^{-1}}{1-z^{-1}}$ , the signal transfer function  $H_x(z)$  and noise transfer function  $H_e(z)$  can be respectively calculated as

$$H_{\chi}(z) = z^{-1}, \tag{11}$$

$$H_e(z) = 1 - z^{-1}.$$

(12)

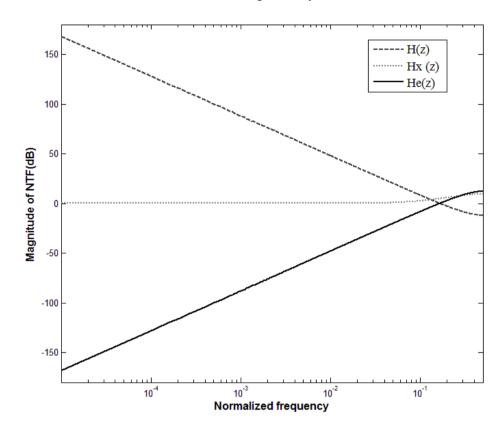

This linearized model implies that the input signal directly passes through the loop filter, as the quantization error is suppressed by the loop filter and hence high-pass shaped. Figure 2.7 shows simulated loop filter, signal and noise transfer functions of a second-order canonical  $\Delta\Sigma$  architecture, respectively.

Figure 2.7 Transfer functions of a second-order canonical  $\Delta\Sigma$  modulator.

# **2.4** $\Delta\Sigma$ ADC Topology

A number of alternative topologies exist which can perform noise shaping as discussed in the previous section. Single-loop topology reduces quantization noise by raising the order of the loop filter while cascade topology relies on the cancellation of quantization noise rather than aggressively shaping the quantization noise. This section is devoted to discuss several frequently used modulator topologies.

# 2.4.1 Distributed Feedback Topology

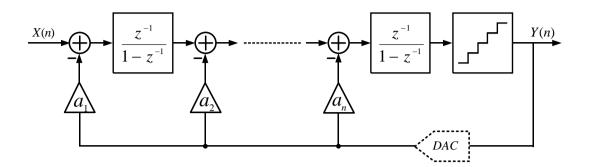

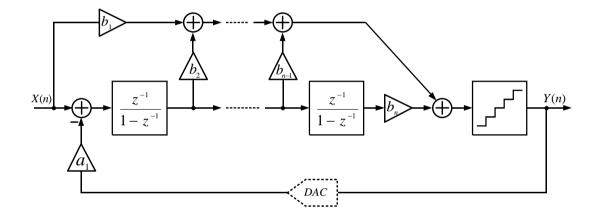

Figure 2.8 General diagram of a *N*-th order single-loop feedback topology.

Figure 2.8 shows a general block diagram of a *N*-th order single-loop  $\Delta\Sigma$  modulator with distributed feedback. Since there is only one loop in the whole modulator, the ability of the noise shaping could be improved only by increasing the order of the loop filter. However, the stability considerations limit the maximum input signal range for high-order loops. The reason is that the higher loop-gain of the high-order loop filter causes overload of the quantizer [32]. The internal swings of each stage of this topology are dependent on amplitude of the input signal. This is because the input signal exists in each output stage. For example, the transfer function of a second-order of feedback topology is as follows

$$Y(z) = z^{-2}X(z) + (1 - z^{-1})^2 E(z),$$

(13)

where Y(z), X(z) and E(z) are the digital output, the input signal, and the quantization noise in *z*-domain, respectively. The linearized model shows that the outputs at each stage are

$$y_1(z) = z^{-1}(1+z^{-1})X(z) - z^{-1}(1-z^{-1})E(z),$$

(14)

$$y_2(z) = z^{-2}X(z) - z^{-1}(2 - z^{-1})E(z),$$

(15)

where  $y_1(z)$  and  $y_2(z)$  are the output signals of the first and second stages, respectively. From the above equations, we can clearly see that the output signals of two stages are the functions of the input signal X(z). Signal swings at each stage exhibit large so that the implementation with low supply voltage is difficult. Moreover, the signal-dependent harmonics induced by the amplifier non-linearity reduce SNDR of the modulator.

#### 2.4.2 Input-Feedforward Topology

Figure 2.9 General diagram of a N-th order single-loop input-feedforward topology.

An alternative useful single-loop topology is input-feedforward, as illustrated in Figure 2.9. The distinguishing features of this topology are the direct feedforward path from the input to the quantizer and the single feedback path from the digital output. The transfer function of a second-order feedforward  $\Delta\Sigma$  modulator topology can be represented as

$$Y(z) = X(z) + (1 - z^{-1})^2 E(z),$$

(16)

where Y(z), X(z) and E(z) are the digital output, the input signal, and the quantization noise in z-domain, respectively. The output signals of each stage are as follows

$$y_1(z) = -z^{-1}(1 - z^{-1})E(z), \tag{17}$$

$$y_2(z) = -z^{-2}E(z),$$

(18)

where  $y_1(z)$  and  $y_2(z)$  are the output signals of the first and second stages, respectively. From equation (17) and (18), we can see that the  $y_1(z)$  and  $y_2(z)$  are free from the input signal X(z), which means that the loop filter does not process the signal, thus the requirements on linearity of the amplifier might be considerably relaxed. Furthermore, with reduced signal amplitudes this topology eases implementation of analog building blocks with reduced supply.

### 2.4.3 Error Feedback Topology

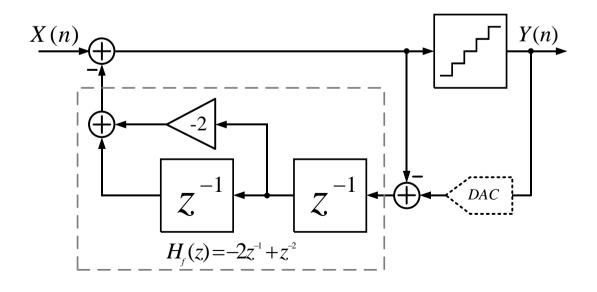

Figure 2.10 Second-order error feedback topology.

Figure 2.10 shows a second-order error feedback topology for simplicity. The key idea of the topology is to reconstruct quantization error. The topology subtracts the input of the quantizer from the output of DAC to obtain the quantization error in analog form. Then this error is fed back into a loop filter  $H_f(z)$ . Despite directly obtaining the quantization error, the topology is not practical for analog implementation, because it is very sensitive to variations of its parameters [33]. However, this topology can be used as the final stage combined with other topologies to enhance the noise shaping character [34].

#### 2.4.4 MASH Topology

The concept of multi-stage or MASH (Multi-stAge noise-Shaping) modulator is to extract the quantization error of the first stage for the input of the second stage, and then cancel it by employing digital filters at each stage. This topology has advantage that the stability character remains as that of low-order modulator while its shaping character exhibits like that of high-order modulator. However, the multi-stage topology suffers from match problem between stages. Therefore, it requires high accuracy for analog building block such as amplifier. For low-voltage application, this topology tends to result in higher power consumption [27, 35].

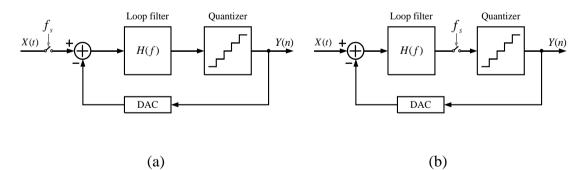

## 2.5 Circuit Implementation

As for circuit implementation of  $\Delta\Sigma$  modulator, we usually employ discrete-time or continuous-time circuits. Discrete-time modulator differs from continuous-time

modulator in the place where input signal is sampled. As illustrated in Figure 2.11, in a discrete-time modulator, input signal is sampled at the input of the loop filter while it is sampled at the output of the loop filter in a continuous-time modulator. This results in significant difference in many aspects. First, continuous-time is prone to be affected by nonidealities, especially, clock jitter. Because the uncertainty of acquisition time directly affects the length of feedback signal and the uneven length of feedback signal might cause quantization noise leakage in the band of interest. Second, design method for discrete-time modulator is mature. Behavioral or analytical simulation might well predict stability as well as performance of discrete-time modulator. Third, discrete-time modulator requires much more switches than continuous-time modulator. For a low-voltage application, each individual switch may need a booster to acquire sufficient overdrive voltage and hence consume more power. Final, settling requirement for discrete-time modulator is much stringent than that of continuous-time modulator. Usually, gain bandwidth (GBW) of amplifier used for integrator in a discrete-time modulator should be at least five times of clock frequency [36]. In practice however, for a continuous-time modulator, it only needs two times of clock frequency [37].

Figure 2.11 General block diagram of (a) DT and (b) CT  $\Delta\Sigma$  modulator.

# CHAPTER 3 DESIGN CONSIDERATION FOR LOW-VOLTAGE LOW-POWER CIRCUITS

Continuing down scaling of device geometry makes supply voltage declined. Reduced supply voltage with a relative higher threshold voltage has an important impact on circuits design. This chapter discusses low-voltage low-power issues related to switched-capacitor (SC) circuits and introduces low-voltage and low-power circuits design techniques.

# 3.1 Low-Voltage Low-Power Circuit Design Issues

#### 3.1.1 Floating Switch Problem

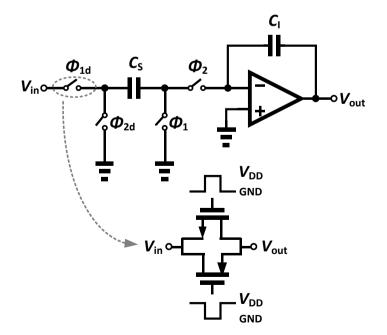

Figure 3.1 Floating switch in a typical SC integrator.

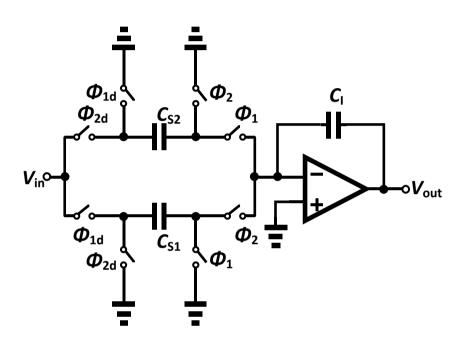

SC circuit is the most frequently used implementation for discrete-time system in CMOS technology. Figure 3.1 shows a typical SC integrator. The switch which connected between the input signal and the sampling capacitor is called floating switch. The operation of the SC integrator is as follows. During phase  $\phi$ 1, the input signal  $V_{in}$  is sampled into the sampling capacitor  $C_s$  through the floating switch. Ideally, the floating switch in the on-state should behave as a constant linear resistor. In practice however, the on-resistance of this switch varies with the input signal as shown in Figure 3.2. If supply voltage is large enough compared to the sum of the threshold voltages of PMOS and NMOS transistors, the on-resistance of the switch is approximately constant over the whole input signal range. However, if supply voltage approaches or less than the sum of the threshold voltages, both PMOS and NMOS transistors almost turn off in the mid-input signal range, and hence significantly increase resistance in this region. In order to have the on-resistance low enough, the gate-source voltage must be much larger than the sum of the input signal amplitude and the threshold voltage of the switch.

Figure 3.2 Simulated on-resistance of a transmission gate under 1-V supply voltage  $(V_{th,n}=438.2\text{m}, V_{th,p}=578.7\text{m}, W/L=1.2\text{u}/0.12\text{u}).$

#### 3.1.2 Intrinsic Noise

The most severe impact of reduced supply voltage is to limit input signal range, and hence reduce dynamic range. For SC circuits, in order to maintain dynamic range, we usually increase size of sampling capacitor to reduce thermal noise since the thermal noise does not related to supply voltage, i.e., KT/C. However, increased sampling capacitance dissipates more power. The trade-off between dynamic range and power consumption in a low-voltage design becomes more stringent. Besides thermal noise, for low-frequency applications such as biomedical and audio circuits, flicker noise with state-of-the-art CMOS technology becomes more important. This is because newer CMOS process employs thinner gate oxide and tends to have a higher corner frequency where flicker noise line and thermal noise line are crossed over in spectrum [38].

#### 3.1.3 Leakage Current

In general, leakage current can be categorized into off-state drain leakage and on-state gate leakage based on biasing condition of transistor. The continuous scaling down of CMOS technology results in increase of leakage current. First, reduction of threshold voltage exponentially increases subthreshold leakage. Second, reduced gate oxide thickness increases gate edge-direct-tunneling leakage and gate-induced drain-leakage. Third, lightly doped-drain also exponentially increases bulk band-to-band-tunneling leakage [39]. Leakage current, especially off-state drain leakage, can substantially increase total power consumption. Therefore, for low-power circuits such as memory and mobile system, leakage current reduction is very important technique in circuit

design [40, 41]. To prevent from leakage, state-of-the-art technologies may implement a low-power process which features relative higher threshold voltage.

#### 3.1.4 Intrinsic Gain

Reduced effective gate length makes the charge sharing between gate and source or drain more severe, and thus allow the voltage drop between drain and source  $V_{ds}$  control drain current apparently. The unexpected control of  $V_{ds}$  results in considerable reduction of output impedance  $r_o$  of transistor. Although transconductance  $g_m$  of each newer generation has been enhanced, the intrinsic gain of state-of-the-art transistor which equals to  $g_m r_o$  declines. Reduced supply voltage even makes this worse. This is because reduced supply voltage severely squeeze  $V_{ds}$ , so that push transistor move into linear region and thus reduce  $r_o$  further.

# 3.2 Low-Voltage Circuit Design Techniques

#### 3.2.1 Body-Driven Technique

Usually, body terminal is connected to source or ground to eliminate body effect which may increase threshold voltage. However, when gate input is substituted by body input, supply voltage can be substantially reduced due to the fact that the input range for body input is much larger than that for gate input. Body-driven technique demonstrates a possibility to work with very low supply voltage [42-44]. However, this technique suffers from several limitations compared to conventional gate-driven circuits. First, body input exhibits lower transconductance, DC gain, gain-bandwidth (GBW) and larger power for same load capacitance. Second, input impedance declines while body input may draw current from signal source. This fact tends to create parasitic bipolar transistor which might result in a latch-up problem. Third, due to low transconductance body-driven circuits may suffer from larger thermal noise and hence degrade system performance. Final, this technique is process related. For most cases, only PMOS transistor is applicable for body-driven technique because P-WELL is not available.

## 3.2.2 Charge Pump Technique

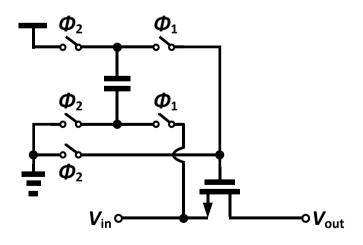

Due to low supply voltage the overdrive voltage for transistor is often insufficient to transmit signal. Therefore, charge pump technique is frequently employed in low-voltage circuit design. Boosted clock and bootstrapped switch [45-47] are two common used implementations. The former doubles amplitude of clock signal to increase the overdrive voltage for switch while the latter provides a constant gate-source voltage  $V_{gs}$  to gain better linearity. Figure 3.3 shows a conceptual diagram of bootstrapped switch.

Figure 3.3 Conceptual diagram of bootstrapped switch.

## 3.2.3 Switched-Opamp Technique

In order to solve floating switch problem, switched-opamp [48-52] is proposed to eliminate the floating switch, as illustrated in Figure 3.4. In preceding stage, output stage and bias of the miller-compensated opamp are switchable. When these switches are on, the opamp operates like a normal two-stage opamp. When these switches are off, the opamp stop to work and the output node is floating. This technique is compatible with SC circuits and might operate with low supply voltage. When the opamp stops to work, ideally, quiescent current declines to zero and power could be saved. However, switched-opamp might need a long time to recover from an idle state, and thus may be unsuitable for high speed applications.

Figure 3.4 Two-stage miller-compensated switched opamp.

#### 3.2.4 Switched-RC Technique

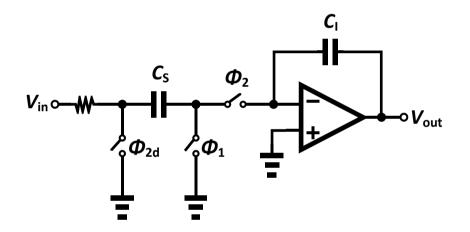

An alternative way to solve the floating switch problem is switched-RC technique [22, 27, 53, 54]. As shown in Figure 3.5, using a constant resistor to replace the floating switch not only improves linearity of the input sampling network, but also avoids insufficient overdrive voltage. This technique is also suitable for low supply voltage and very easy to realize. However, this constant resistor inevitably reduces output impedance of preceding stage and thus requires high DC gain for previous amplifier. Moreover, output load of the preceding stage is severely affected by the sampling state [27].

Figure 3.5 Switched-RC integrator.

# 3.3 Low-Power Circuit Design Techniques

#### **3.3.1 Double Sampling Technique**

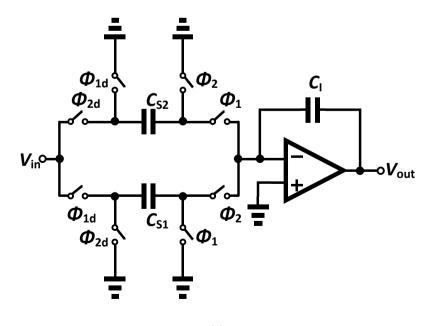

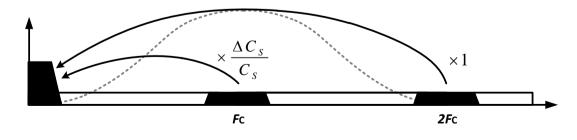

As illustrated in Figure 3.6, the amplifier in the double-sampled integrator is utilized in both phases and thus the effective sampling rate is twice of that of conventional single-sampled integrator. Double sampling technique has advantages that for a given sampling rate the clock frequency can be halved and hence power consumption of integrator is minimized [22, 55-58]. Another benefit of this technique is symmetrical equivalent load for the integrator. The same load avoids ringing in one phase. In practice however, due to mismatch between two sampling capacitor high frequency noise might easily fold down into baseband and hence increase noise floor [55].

Figure 3.6 Double-sampled SC integrator.

## 3.3.2 Time-Sharing Technique

In order to minimize power consumption, analog building blocks such as amplifier, comparator might be shared within different clock period [14, 59-61]. The time-sharing technique reduces the number of analog building blocks and hence total chip area. Since number of analog building block is significantly reduced, mismatch problem between each cell is alleviated. For example, using one comparator instead of

multi-comparator in a multi-bit quantizer avoids performance degradation due to mismatch between each comparator [14].

However, these remaining analog building blocks operated within reduced time space may need higher gain-bandwidth, slew rate. Moreover, control logic for the timeshared circuit might become more complicated.

# This page intentionally left blank

# **CHAPTER 4**

# A 0.7-V 100-μW AUDIO MODULATOR WITH 92dB DR IN 0.13-μm CMOS

This chapter demonstrates an example of low-voltage low-power  $\Delta\Sigma$  modulators for audio-band applications. This prototype is a fourth-order single-bit input-feedforward  $\Delta\Sigma$  modulator operated from a 0.7-V supply voltage while consuming 99.7 µW. The modulator has been fabricated in a 0.13-µm CMOS process and exhibits high figureof-merits among audio-band sub-1 V low-power  $\Delta\Sigma$  modulators based on measured results. The modulator utilizes a 2-tap finite-impulse-response (FIR) filter in the feedback path to reduce integration step of the first stage, resulting 22% reduction in the maximum integration step and relaxing the slew rate requirement for the first opamp to 9.5 V/µsec (diff). It also simplifies circuit implementation by embedding feedforward path in a multi-input comparator.

# 4.1 Introduction

The growing demands for fully integration of data converters and digital signal processing circuits make data converters migrating towards deep-submicron CMOS technologies. However, in contrast with digital circuits, which have gained higher power efficiency, higher area density and more powerful functions from smaller geometry of transistor size and lowered supply voltage, data converters are most likely to have its performance degraded due to the lowered supply voltage and worse

transistor characteristics. The first problem confronted is the lowered supply voltage. To ensure the reliability of transistor, the supply voltage is forced to decline in deepsubmicron technologies. However, the dynamic range of analog circuits is restricted by signal swing, which is limited by supply voltage. Thus, the reduced signal power makes the input network to have a larger sampling capacitor to reduce the noise floor in a discrete time system for a desired signal-to-noise ratio (SNR). Increasing capacitor size is most likely to raise power consumption. In terms of power consumption, analog building blocks tend to increase with the decrease of supply voltage for a given SNR. One method of keeping high available SNR accompanied with low level of the total power consumption is to separate the power line of analog and digital circuits, as in [62]. Since the rated supply voltage of state-of-the-art process already shrinks to around 1 volt, the supply voltage difference between these two parts is not very big to effectively reduce total power consumption, and it would be at the cost of more noise coupling and electromagnetic interface [22]. Besides lowered supply voltage, the impact of scaling down of CMOS technologies on analog building blocks is not ignorable; and the most prominent problem is DC gain degradation of amplifiers. Several multistage amplifiers topologies, such as threestage with nested  $g_m$ -C compensation [63], are employed to alleviate this degradation. However, multistage amplifiers in a low-voltage environment are difficult to design and most likely to be inferior to single-stage one in terms of power efficiency. Fortunately, the degradation of analog building blocks can be mitigated at the system level; and it will be discussed later.

A multi-bit single-loop  $\Delta\Sigma$  topology employed in low-voltage, low-power audio-band modulator with high precision is reported in [14]. However, the main drawback of multi-bit topology is the complicated digital circuits and its increased power dissipation. Flash ADC based quantizer doubles the number of comparators for each one bit increased of the quantizer, and appears power hungry. The more powerefficient successor, comparator-based tracking quantizer [59, 64], though save more power, but suffers from excessive loop delay [14]. Besides the multi-bit quantizer, the dynamic element matching (DEM) circuits, which used to suppress tone and nonlinearity induced by the capacitor mismatches of the feedback digital-to-analog converter, are also a power hungry part. As far as power efficiency is concerned, single-bit single-loop topology is proved to be more suitable for low-power applications.

Continuous-time  $\Delta\Sigma$  modulators are usually applied in wideband applications. Its attractive feature is low-power consumption and relaxed requirement of unity-gainbandwidth for amplifier compared with discrete-time counterpart. However, it is very prone to be affected by clock jitter and the jitter requirement is much stringent than that of discrete-time  $\Delta\Sigma$  modulators [65]. For high precision reasons, switched-capacitor circuitry is more popular and suitable in low-voltage audio band applications.

This section presents a fourth-order SC audio-band  $\Delta\Sigma$  modulator. To relax the design requirement for analog building blocks and reduce power consumption, single-loop single-bit feedforward topology with a 2-tap FIR filter is adopted in the work. A multi-input comparator is employed in the quantizer to fulfill the combined function of summation and quantization; hence the conventional feedforward capacitors can be removed. The section is organized as follows: section 4.2 describes the system architecture of the low-voltage low-power  $\Delta\Sigma$  modulator. The detailed circuit design of the analog building blocks is presented in sections 4.3. Section 4.4 reports the measurement results, and the conclusion is drawn in Section 4.5.

# 4.2 System Design

The second-order single-loop feedforward topology for broadband and low-distortion applications has been firstly presented in [66], as shown in Figure 4.1. Compared with the conventional feedback topology, the unique features make it a perfect candidate for low-voltage  $\Delta\Sigma$  analog-to-digital converters. Firstly, the signal transfer function of this topology is unity, which is less affected by the non-idealities of the building blocks. The quantization noise transfer function remains the same as the classic topology, a single loop topology without the feedforward. Secondly, the internal signal swing can be well controlled by optimizing the loop coefficients. Besides, there is only one feedback path to the first integrator, which simplifies the feedback circuit compared to the conventional topology.

Figure 4.1 Second-order single-loop feedforward topology.

For single-loop single-bit topology realized by switched-capacitor circuitry, the power consumption is mainly determined by the size of capacitors. Thanks to the noise suppression inside the loop, all capacitors with the exception of that in the first stage can be scaled down to save power [32]. Indeed, several low-voltage low-power  $\Delta\Sigma$  modulators show that the first stage dominates the total power dissipations [19, 22, 67]. However, the thermal noise induced by input switched-on resistance is also determined by the sampling capacitor of the first stage. Thus, there is a tradeoff between power consumption and SNR in a thermal noise dominant  $\Delta\Sigma$  system.

High power-efficient low-voltage low-power  $\Delta\Sigma$  modulators always exploit powerefficient amplifiers. Such amplifiers usually have class-AB output or simply consist of only a class-C inverter [20, 67, 68]. Both class-AB output and class-C inverter have similar attribute with digital circuits, which power consumption is proportionally to the switching activity. In terms of integrators, the power consumption is closely related to the integration step. From the linear model shown in the Figure 4.1, the output swing of the first stage and the integration step is derived as following:

$$y_1 = -a_1 z^{-1} (1 - z^{-1}) E(z), \tag{19}$$

$$\Delta_1 = \left| y_1(z) - y_1(z) z^{-1} \right| = \left| a_1 z^{-1} (1 - z^{-1})^2 E(z) \right|.$$

(20)

Equation (20) shows that either integration gain of the first stage, or quantization errors, or both can be minimized to reduce integration step.

From system perspective, the selection of the coefficient or the integration gain of the first stage is important to affect the power consumption of the first stage. When the integration gain increases, not only the integration step, but also the output signal

swings would increase proportionally. This would lead to penalty in terms of slew rate and DC gain of amplifier. However, too small integration gain would be at the cost of large capacitor spread. If a desired sampling capacitor is fixed or for a given SNR, the integration capacitor would be very large with small integration gain. Although several approaches have been reported to deal with the capacitor spread problem, such as T-network scheme [69] and charge-discharge-redistribution scheme [70], they are not likely chosen to serve for the sampling network. The main reason is the extra thermal noise induced by the additional switches and the added clock noise.

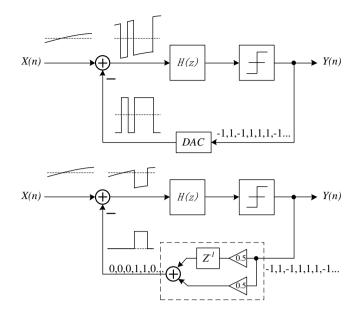

The quantization error is explicitly reduced by multi-bit topology, and is reversely proportional to the number of quantization level. But this is a power-hungry choice for low-power application for the reasons described above. An alternative way to reduce the impact of the quantization error is using a FIR filter to chop off the most power of the quantization errors centered at  $f_s/2$  [71, 72]. This method does not incur any non-linearity from the feedback DAC and requires no DEM circuits. Furthermore, the residual error at the input of the first stage is reduced. Thus, the integration step is reduced. Figure 4.2 illustrates a conceptual diagram of reduced residual error by a 2-tap comb FIR filter DAC. A 2-tap FIR filter raises the level of a 1-bit quantizer to that of a 1.5-bit quantizer, and minimizes the residual errors.

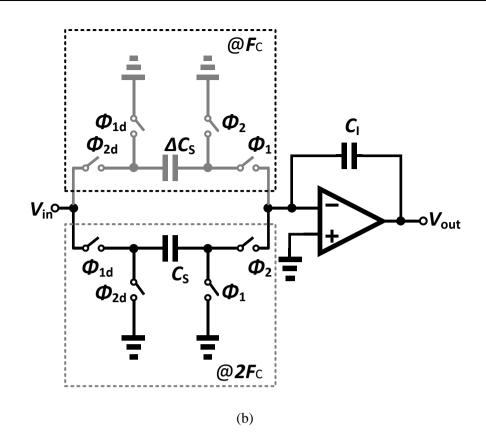

Figure 4.2 Conceptual operation of a 2-tap FIR filter.

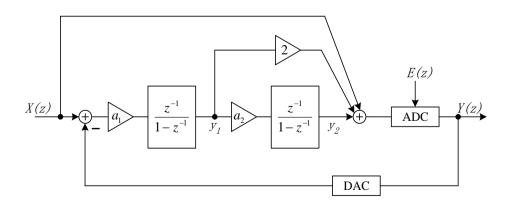

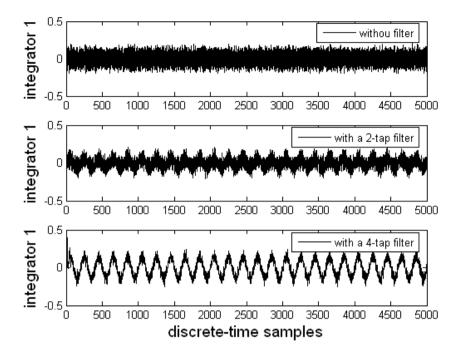

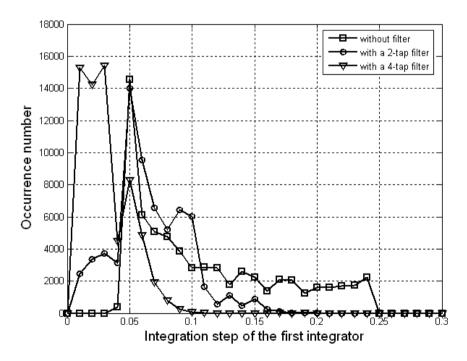

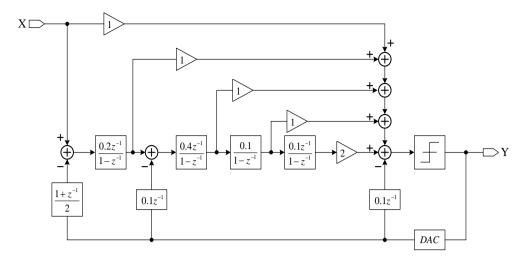

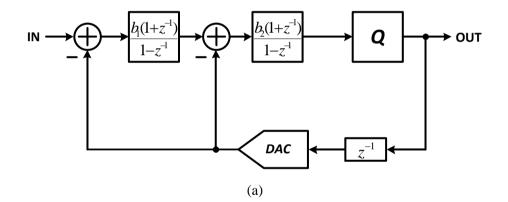

According to the behavior simulation, the output swings of the first stage are slightly affected by FIR filters, as shown in Figure 4.3. The integration step declined dramatically with the increase of length of tap of the filter, as shown in Figure 4.4. However, the increased length of tap would be at cost of complexity of compensation network. Thus, for simplicity reasons, a fourth-order single-bit feedforward architecture with a 2-tap comb FIR filter is adopted in the work, as shown in Figure 4.5. After introducing a FIR filter in the feedback path, two extra feedback paths are needed to be added to the input of the second integrator and the input of the quantizer to avoid stability problem or performance loss for the changes at the output of the first integrator. Behavior simulation result shows that the maximum integration step is reduced by 22% and the accumulated integration step is only 58% of that without the filter.

Figure 4.3 Output signal swings of the first integrator with/without a FIR filter.

Figure 4.4 Histogram of integration step of the first integrator with/without a FIR filter.

Figure 4.5 System diagram of the  $\Delta\Sigma$  modulator.

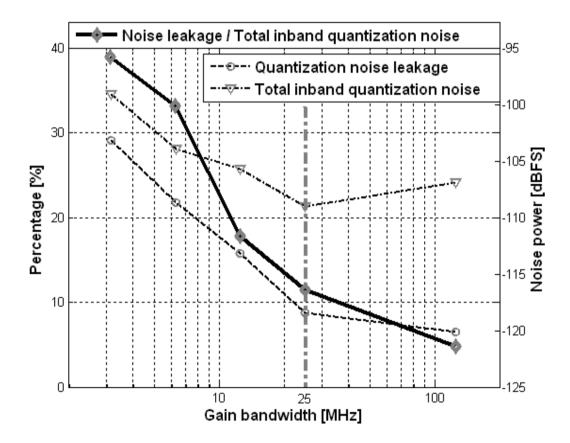

Figure 4.6 Percentage of noise leakage over total in-band quantization noise versus the first opamp's GBW.

Prediction of leakage of the quantization noise is important for achieving desired performance in low-voltage low-power  $\Delta\Sigma$  modulator design. Existing behavioral simulation does not provide a good prediction on the noise leakage while full

transistor level simulation prolongs entire design process. To address this issue, we use a mixed-mode simulation for leakage prediction, which is flexible and less time consuming. Under the mixed-mode simulation, all building blocks are based on transistor level design, except for opamps which are modeled by small signal models. For the first stage, the opamp is modeled as a fully differential one by voltage-controlcurrent-sources (VCCS) and resistors. For opamps in the downstream stages, they are modeled by voltage-control-voltage-sources (VCVS) to save simulation time since non-idealities of the downstream integrators have little effect on the leakage.

In order to estimate the quantization noise leakage, we separate the unshaped quantization noise from the shaped one for evaluating the leakage power. The leakage power is evaluated by accumulating the quantization noise spectrum within a half of signal band, i.e. 10 kHz, under different gain bandwidth (GBW) settings of the first stage opamp. Figure 4.6 shows the percentage of noise leakage over total in-band quantization noise versus the first opamp's GBW, where the DC gain is fixed at 35 dB. It can be seen that the noise leakage due to the opamp bandwidth contributes more than 30 % to the the total in-band quantization noise when the GBW is below 6 MHz. When the GBW is above 25 MHz the noise leakage declines slowly and occupies less than 12 % of the total. We can clearly see that the noise leakage degrades SQNR by more than 5 dB when the GBW is reduced from 25 MHz to 6 MHz. The DC gain does not have clear influence on the leakage. When the GBW is fixed at 25 MHz, the leakage is almost constant when DC gain increases from 29 dB to 41 dB. For achieving a better SNR, it is desirable to let GBW of the first opamp reasonably high so that the noise leakage can be minimized.

# 4.3 Circuit Implementation

Analog building block is a key element in low-voltage low-power  $\Delta\Sigma$  modulator. All switches are implemented with bootstrapped switches to increase linearity in a low-voltage environment. Two non-overlapped signals are generated from the on-chip clock generator.

#### 4.3.1 Two-Tap FIR DAC

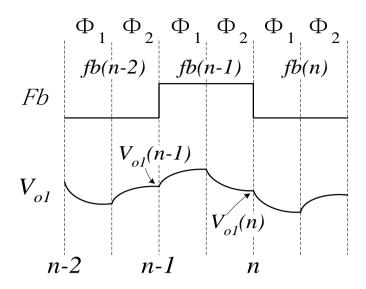

Figure 4.7 shows the signal timing diagram of the feedback signal and the first stage output. The quantizer resolves a comparison at the end of  $\phi_2$ . Within one clock period, the integration of the first stage occurs twice in both  $\phi_1$  and  $\phi_2$ , respectively. According to the time domain, at the end of  $\phi_1$ ,

$$V_{o1}\left(n-\frac{1}{2}\right) = V_{o1}(n-1) + \left[X\left(n-\frac{1}{2}\right) - fb(n-2)\right] \times 0.1.$$

(21)

At the end of  $\phi_2$ ,

$$V_{o1}(n) = V_{o1}\left(n - \frac{1}{2}\right) + \left[X\left(n - \frac{1}{2}\right) - fb(n-1)\right] \times 0.1,$$

(22)

where  $V_{o1}(n)$  is the output of the first stage, X(n) is the input signal, fb(n) is the feedback signal. Adding (4.3) to (4.4) and taking *z*-transfer transform on the sum, we have

$$V_{o1}(z) = V_{o1}(z)z^{-1} + X(z)z^{-0.5} - 0.2 \times fb(z)z^{-1}[\frac{1+z^{-1}}{2}].$$

(23)

We can clearly see from equation (23) that the feedback signal has been filtered.

Figure 4.7 Signal timing diagram of the feedback signal and the first stage output.

#### 4.3.2 Power-Efficient Rail-to-Rail Amplifier

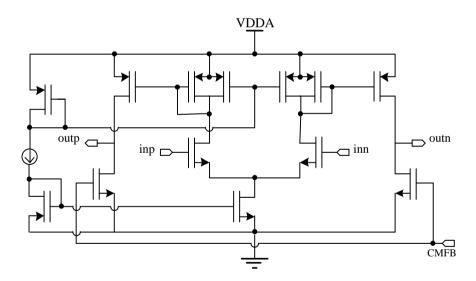

As CMOS technologies are migrating towards the deep-submicron, the intrinsic gain of a transistor shrinks dramatically. With lowered supply voltage this condition becomes even worse. However, high-gain amplifier which employed in a low-voltage environment is difficulty to design, and have to exploit two or three stages cascade topology. Thanks to the oversampling feature of  $\Delta\Sigma$  converters, the requirements of amplifier are not stringent as that of amplifiers which employed in Nyquist rate's converters, such as pipeline converters. Moreover, the reduced signal swings at the internal nodes of feedforward topology make the requirements relaxed much more. These two factors make even an inverter served as an amplifier [13]. As shown in Figure 4.8, this work exploits single-stage fully differential gain-enhanced current mirror OTA. It offers specific advantages in a low-voltage environment, such as low minimum required supply voltage, rail-to-rail output swing and high power efficiency. The process used provides the possibility of optimizing the threshold voltage of the transistors due to the reverse short-channel effect. The minimum required supply for the OTA is restricted by the input stage, which is  $3|V_{ds,sar}| + |V_{TH}|$ . By optimizing the threshold voltage of the PMOS diode-connected transistor to 0.2 V and designing  $|V_{ds,sar}|$  to be 0.1 V, the minimum supply voltage of the OTA is only 0.5 V. NMOS input differential pairs are used to increase the transconductance efficiency. To ensure good distortion suppression, the gain enhancement technique is adopted to increase the OTA DC gain while most parts of the current in the PMOS diode-connected transistors are shunted by a current source. The simulated DC gain and GBW for the OTA in the first integrator are 41 dB and 21 MHz with a 3-pF load capacitor, respectively. Switched-capacitor common-mode feedback circuit is used in the fully differential OTAs to set the output common-mode at the middle of the supply, while the input common-mode of the OTAs is set to 0.3 V.

Figure 4.8 Gain-enhanced current mirror OTA.

Flicker noise is a dominant noise in low frequency region. Several approaches have been reported to deal with this problem, such as chopper stabilization technique and correlated double sampling. However, both of them suffer some limitations. Chopper stabilization technique belongs to a modulation method; it might be at the risk to modulate shaped high-frequency quantization noise back down to the baseband, thus couples additional noise to the baseband [62]. Correlated double sampling belongs to a sampling method; it would lead a penalty of additional thermal noise and coupling clock noise induced by added switches in the sampling front-end. For simplicity reasons, we simply increase the geometric sizes of input transistors to suppress flicker noise.

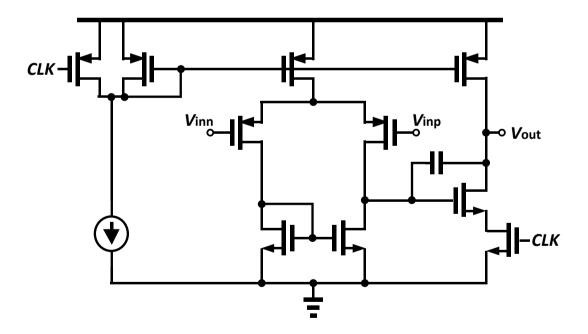

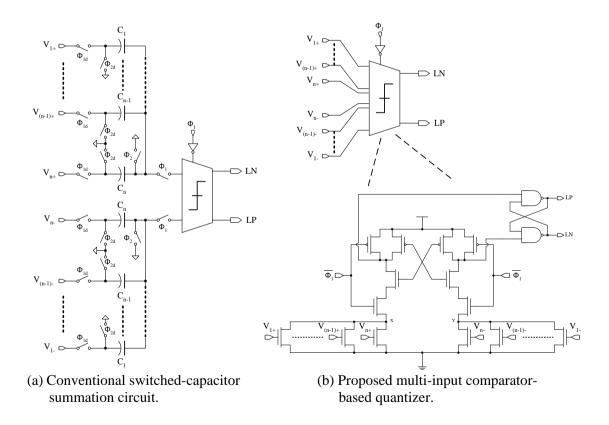

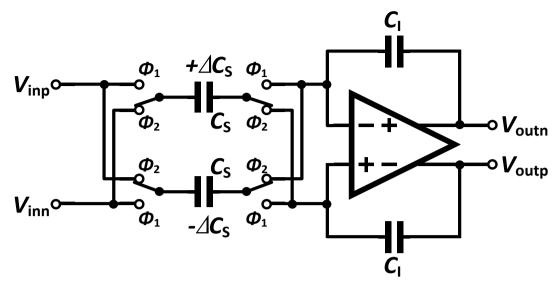

#### 4.3.3 Multi-Input Comparator

Conventionally, the summation of the feedforward paths is realized by a switchedcapacitor summation circuit shown in Figure 4.9a, which requires  $2 \times (N + 1)$ capacitors and extra switches for an Nth-order topology. In the proposed circuit implementation, the summation function is embedded in the quantizer [73]. The quantizer consists of a multi-input comparator and a SR latch. The feedforward paths are implemented by directly feeding the input signal and the output of each integrator to the comparator, as shown in Figure 4.9b. When CLK is low, the comparator is inactivated. The internal nodes X, Y are pulled down to GND, thus,  $V_X = V_Y \approx 0$ . And all input transistors are pushed into the linear region. Once  $V_{GS} > V_{THN}$  is validated for all input transistors. The current at X and Y is derived as:

$$I_X = \sum_{i=0}^4 I_i = \mu_n C_{ox} \sum_{i=0}^4 \left(\frac{W}{L}\right)_i \left(V_{oi+} - V_{THN} - \frac{V_X}{2}\right) \left(V_X\right), \quad (24)$$

$$I_{Y} = \sum_{i=0}^{4} I_{i} = \mu_{n} C_{ox} \sum_{i=0}^{4} \left(\frac{W}{L}\right)_{i} \left(V_{oi-} - V_{THN} - \frac{V_{Y}}{2}\right) \left(V_{Y}\right), \quad (25)$$

where  $V_{THN}$  is the threshold voltage of all input transistors.

When CLK is high, the comparator starts to sense the difference between *IX* and *IY*. Since all input transistors are initially operated in the linear region when the comparator is activated, the difference between *IX* and *IY* is linearly proportional to the difference between the sums of the input signals of both sides. That is

$$I_X - I_Y = \mu_n C_{ox} V_X \sum_{i=0}^4 \left(\frac{W}{L}\right)_i (V_{oi+} - V_{oi-})$$

(26)

The linear relationship between  $(I_x - I_y)$  and  $(V_{oi+} - V_{oi-})$  in equation (26) indicates that the ratio of  $\left(\frac{W}{L}\right)_i$  can be used to realize the feedforward coefficients in Figure 4.5. This difference is then amplified by the regenerative circuit to reach the level of the final outputs.

Figure 4.9 Different implementation techniques of the feedforward paths.

# 4.4 Measurement Results

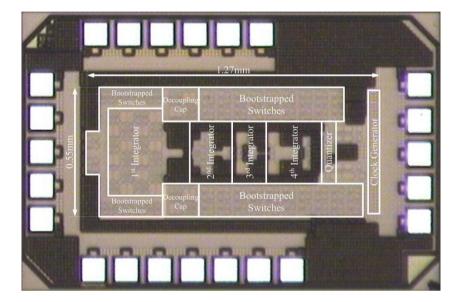

The prototype fourth-order feedforward  $\Delta\Sigma$  modulator is fabricated in a 1P8M 0.13µm CMOS process with MIM capacitor. The core area is  $1.27 \times 0.55$  mm<sup>2</sup>. Figure 4.10 shows the chip micrograph. And the chip is packaged in a 28-pin QFN package.

Figure 4.10 Chip micrograph.

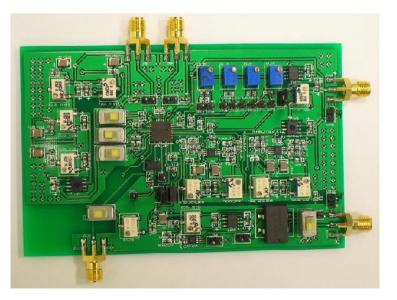

# 4.4.1 Measurement Setup

Low distortion function generator SRS DS360 is served for input signal. Unfortunately, the in-band rated noise power is slightly higher, and would affect the accuracy of the SNR measurement. The specifications details that the rated maximum white noise voltage is  $15 nV/\sqrt{Hz}$  for a 1 kHz sine wave into Hi-Z load with maximum 1.26 Vpp [74]. The maximum in-band noise power is calculated by

$$P_{no,in} = BW \times (Noise\_Voltage)^2 = 20kHz \times (15nV/\sqrt{Hz})^2 = 4.5(\mu V)^2,$$