### Status of Phase Change Memory in Memory Hierarchy and its impact on Relational Database

Masters Thesis

submitted by

### Suraj Pathak

suraj@comp.nus.edu.sg

under guidance of

Prof. Tay Yong Chiang

$\operatorname{to}$

### SCHOOL OF COMPUTING

NATIONAL UNIVERSITY OF SINGAPORE

December 2011

# Abstract

Phase Change Memory(PCM) is a new form of Non-volatile memory that has advantages like read access almost as close to a DRAM, write speed about 100 times faster than traditional hard disks and flash SSD, and cell density about 10 times better than any kind of storage devices available today. With these advantages, it is feasible that PCM could be the future of data storage as it has the potential to replace both secondary storage and main memory.

In this thesis, we study the current status of PCM in the memory hierarchy, its characteristics, advantages and challenges in implementing the technology. Specifically, we study how the byte-writeable PCM can be used as a buffer for flash SSD to improve its write efficiency. Then in the second part, we study how traditional relational database management should be altered for a database completely implemented in PCM. Specifically, we study this effect by choosing hash-join algorithm.

The experiments are carried out in a simulated environment, by modifying a DRAM to act as a PCM. We use postgreSQL database for relational database experiment. The results show that PCM has many benefits in the current memory hierarchy. First, if it is used in a small scale, it can be used as a buffer for flash to improve its write efficiency. Then, if PCM were to replace the DRAM as main memory, we can modify the traditional database algorithms marginally to accommodate the new PCM-based database.

# Acknowledgement

I owe my deepest gratitude to people around me without whose help and support I would not have been able to finish my thesis.

First of all, I would like to thank my principal supervisor Prof. Y.C. Tay for his continuous support, help and patience with me. I would also like to specially thank my co-supervisor from Data Storage Institute of A-Star, Dr. Wei Qingsong for his kind guidance and support throughout my study. It was a pleasure to work with him and learn valuable knowledge from him.

I would like to thank my colleague and one of my best friends Gong Bozhao for his support during my initial stage of research.

I would also like to thank my dearest parents who have endured their son being away from them for most of the time but have supported me in my every life decisions.

Last but not the least, I would like to thank all the supervisors involved in the evaluation of this thesis. For any errors or inadequacies that may remain in this work, of course, the responsibility is entirely my own.

# Contents

| $\mathbf{A}$ | bstra | $\mathbf{ct}$ |                                                      | i   |

|--------------|-------|---------------|------------------------------------------------------|-----|

| Li           | st of | Tables        | 5                                                    | vi  |

| Li           | st of | Figure        | es                                                   | vii |

| 1            | Intr  | oducti        | on                                                   | 1   |

|              | 1.1   | Our co        | ontribution                                          | 4   |

| <b>2</b>     | Pha   | se Cha        | ange Memory Technology                               | 7   |

|              | 2.1   | PCM           | in Memory Hierarchy                                  | 8   |

|              | 2.2   | Relate        | d work on PCM-based database                         | 11  |

|              |       | 2.2.1         | PCM as a secondary storage                           | 11  |

|              |       | 2.2.2         | PCM as a Main Memory                                 | 12  |

|              |       | 2.2.3         | B+-tree design                                       | 12  |

|              |       | 2.2.4         | Hash-join                                            | 13  |

|              |       | 2.2.5         | Star Schema Benchmark                                | 13  |

|              | 2.3   | PCM:          | Opportunity and Challenges                           | 15  |

| 3            | PC    | M as a        | buffer for flash                                     | 17  |

|              | 3.1   | Flash         | SSD Technology: FTL and Buffer Management $\ldots$ . | 17  |

|              |       | 3.1.1         | Flash Translation Layer                              | 18  |

|              |       | 3.1.2         | SSD buffer management                                | 19  |

|              |       | 3.1.3         | Duplicate writes present on workloads                | 20  |

|   | 3.2               | Syster                 | n Design                                                                                                                                                                                                                                                                                                                                                                         | 22                                                                                                                                 |

|---|-------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 3.2.1                  | Overview                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                 |

|   |                   | 3.2.2                  | Redundant Write Finder                                                                                                                                                                                                                                                                                                                                                           | 24                                                                                                                                 |

|   |                   |                        | Fingerprint Store                                                                                                                                                                                                                                                                                                                                                                | 24                                                                                                                                 |

|   |                   |                        | Bidirectional Mapping                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                 |

|   |                   | 3.2.3                  | Writing frequent updates on PCM cell $\hdots$                                                                                                                                                                                                                                                                                                                                    | 26                                                                                                                                 |

|   |                   |                        | F-Block to P-Block Mapping                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                                                 |

|   |                   |                        | Relative Address                                                                                                                                                                                                                                                                                                                                                                 | 29                                                                                                                                 |

|   |                   |                        | Replacement Policy                                                                                                                                                                                                                                                                                                                                                               | 29                                                                                                                                 |

|   |                   | 3.2.4                  | Merging Technology                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                                                                 |

|   |                   | 3.2.5                  | Endurance, Performance and Meta-data Management                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                 |

| 4 | Imp               | pact of                | PCM on database algorithms                                                                                                                                                                                                                                                                                                                                                       | 33                                                                                                                                 |

|   | 4.1               | PCM                    | based hash join Algorithms                                                                                                                                                                                                                                                                                                                                                       | 33                                                                                                                                 |

|   |                   | 4.1.1                  | Algorithm Analysis Parameters                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                                 |

|   |                   | 4.1.2                  | Row-stored Database                                                                                                                                                                                                                                                                                                                                                              | 34                                                                                                                                 |

|   |                   |                        |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                    |

|   |                   | 4.1.3                  | Column-stored Database                                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                                 |

| 5 | Exp               | -                      | Column-stored Database                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| 5 | <b>Exp</b><br>5.1 | perime                 |                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                                                                 |

| 5 |                   | perime                 | ntal Evaluation                                                                                                                                                                                                                                                                                                                                                                  | <b>38</b><br>38                                                                                                                    |

| 5 |                   | perime<br>PCM          | ntal Evaluation<br>as flash-Buffer                                                                                                                                                                                                                                                                                                                                               | <b>38</b><br>38<br>38                                                                                                              |

| 5 |                   | perime<br>PCM          | ntal Evaluation         as flash-Buffer         Experiment Setup                                                                                                                                                                                                                                                                                                                 | <b>38</b><br>38<br>38<br>38                                                                                                        |

| 5 |                   | perime<br>PCM          | ntal Evaluation         as flash-Buffer         Experiment Setup         Simulators                                                                                                                                                                                                                                                                                              | <b>38</b><br>38<br>38<br>38<br>38<br>39                                                                                            |

| 5 |                   | perime<br>PCM          | ntal Evaluation         as flash-Buffer         Experiment Setup         Simulators         Simulation of PCM Wear out                                                                                                                                                                                                                                                           | <b>38</b><br>38<br>38<br>38<br>39<br>39                                                                                            |

| 5 |                   | perime<br>PCM          | ntal Evaluation         as flash-Buffer         Experiment Setup         Simulators         Simulation of PCM Wear out         Simulation parameter Configurations                                                                                                                                                                                                               | <b>38</b><br>38<br>38<br>38<br>39<br>39<br>40                                                                                      |

| 5 |                   | PCM<br>5.1.1           | ntal Evaluation         as flash-Buffer                                                                                                                                                                                                                                                                                                                                          | <b>38</b><br>38<br>38<br>38<br>39<br>39                                                                                            |

| 5 |                   | PCM<br>5.1.1           | ntal Evaluation         as flash-Buffer         Experiment Setup         Simulators         Simulators         Simulation of PCM Wear out         Simulation parameter Configurations         Workloads and Trace Collection         Results                                                                                                                                     | <ul> <li>38</li> <li>38</li> <li>38</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>41</li> <li>41</li> </ul>             |

| 5 |                   | PCM<br>5.1.1           | ntal Evaluation         as flash-Buffer         Experiment Setup         Simulators         Simulators         Simulation of PCM Wear out         Simulation parameter Configurations         Workloads and Trace Collection         Results         Efficiency of duplication finder                                                                                            | <ul> <li>38</li> <li>38</li> <li>38</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>41</li> <li>41</li> <li>44</li> </ul> |

| 5 |                   | PCM<br>5.1.1           | ntal Evaluation         as flash-Buffer         Experiment Setup         Simulators         Simulators         Simulation of PCM Wear out         Simulation parameter Configurations         Workloads and Trace Collection         Results         Efficiency of duplication finder         Performance of flash buffer management                                             | <ul> <li>38</li> <li>38</li> <li>38</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>41</li> <li>41</li> <li>44</li> </ul> |

| 5 |                   | Derime<br>PCM<br>5.1.1 | Intal Evaluation         as flash-Buffer         Experiment Setup         Simulators         Simulators         Simulation of PCM Wear out         Simulation parameter Configurations         Workloads and Trace Collection         Results         Efficiency of duplication finder         Performance of flash buffer management         Making Sequential Flushes to flash | 41<br>44<br>47                                                                                                                     |

|    | 5.2.1      | Simulation Parameters                                     | 51   |

|----|------------|-----------------------------------------------------------|------|

|    | 5.2.2      | Modified Hash-join for Row-stored and Column-stored Datab | oase |

|    |            | 52                                                        |      |

|    | 5.2.3      | PCM as a Main Memory Extension                            | 56   |

| 6  | Conclusio  | n                                                         | 59   |

| Bi | bliography |                                                           | 60   |

# List of Tables

| 2.1 | Performance and Density comparison of different Memory devices | 10 |

|-----|----------------------------------------------------------------|----|

| 2.2 | Comparison of flash SSD and PCM                                | 10 |

| 4.1 | Terms used in analyzing hash join                              | 34 |

| 5.1 | Configurations of SSD simulator                                | 40 |

| 5.2 | Configuration of TPC-C Benchmarks for our experiment           | 40 |

| 5.3 | Simulation Parameters                                          | 51 |

# List of Figures

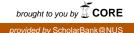

| 2.1 | Position of PCM in Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

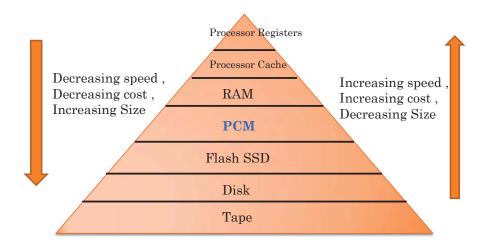

| 2.2 | Memory organization with PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9  |

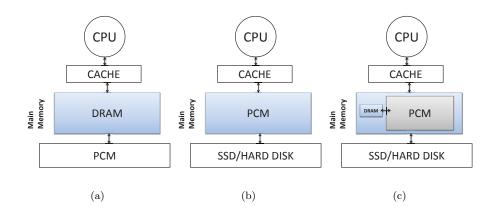

| 2.3 | Schema of the SSBM Benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14 |

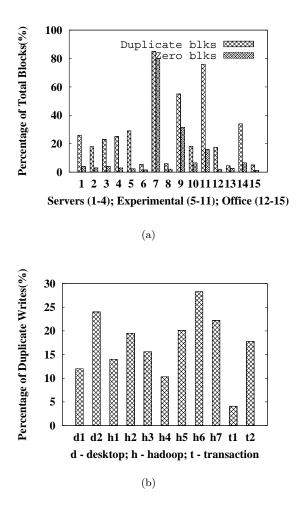

| 3.1 | The percentage of redundant data in (a) Data disk; (b) Workload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|     | , cited from [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

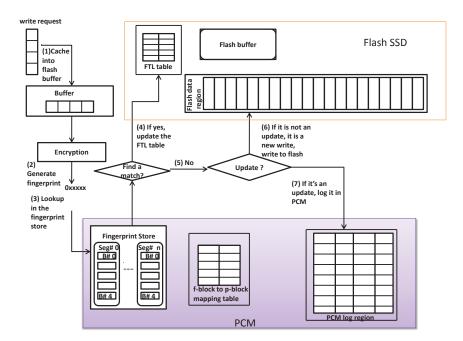

| 3.2 | Illustration of System design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23 |

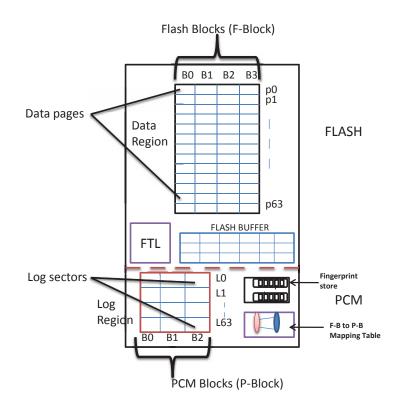

| 3.3 | Basic Layout of the proposed buffer management scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |

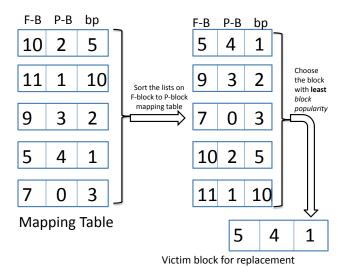

| 3.4 | Illustration of replacement policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30 |

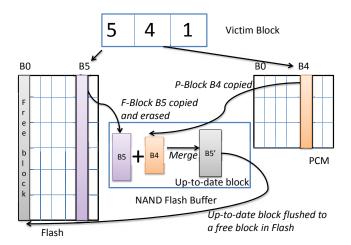

| 3.5 | Illustration of Merging and Flushing block after replacement $\ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31 |

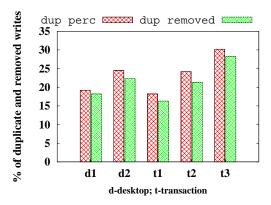

| 5.1 | The duplication data present in the workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |

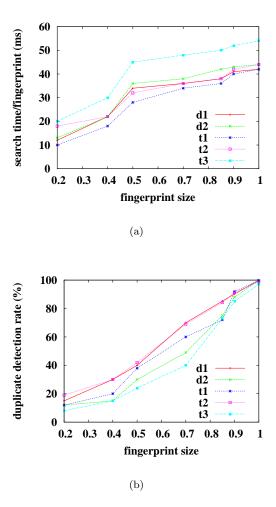

| 5.2 | The effect of fingerprint store size on (a) Search time per finger-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | print; (b) Duplication detection rate $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43 |

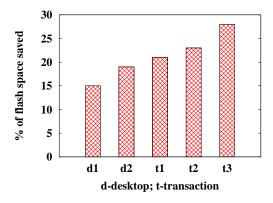

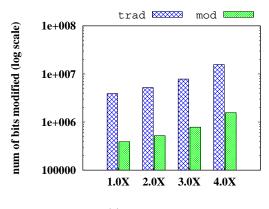

| 5.3 | flash space saved by duplicate finder $\hdots \hdots \hdo$ | 44 |

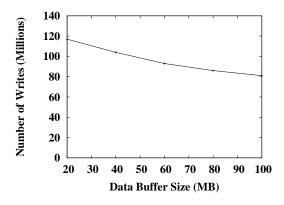

| 5.4 | The impact of data buffer size on write operations $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

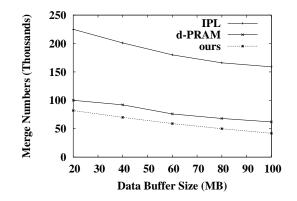

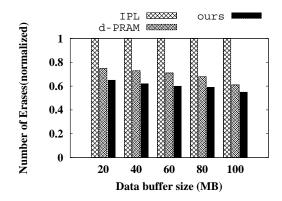

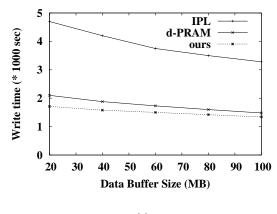

| 5.5 | The comparison of (a) Merge Numbers; (b) Erase Numbers; and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|     | (c) Write time for three techniques $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

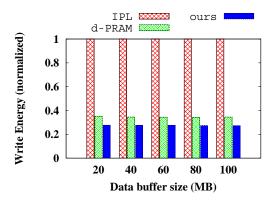

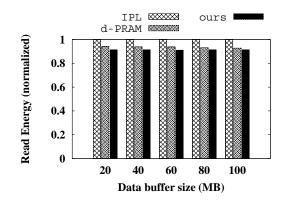

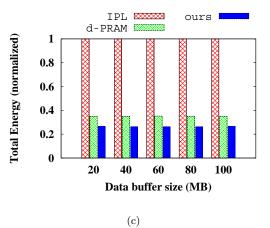

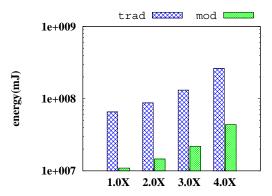

| 5.6 | The comparison of Energy consumption for (a) Write operation;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|     | (b) Read Operation; (c) Write + Read $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48 |

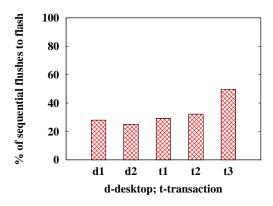

| 5.7 | Percent of sequential flush to flash due to PCM-based buffer man-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|     | agement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49 |

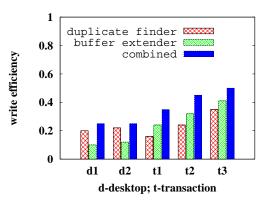

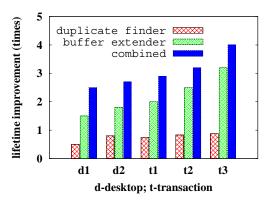

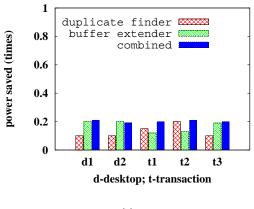

| 5.8  | Effect of duplication finder and pcm-based buffer extender on                |    |  |  |

|------|------------------------------------------------------------------------------|----|--|--|

|      | (a)<br>Write Efficiency; (b) Lifetime; (c) Power save $\ldots \ldots \ldots$ | 50 |  |  |

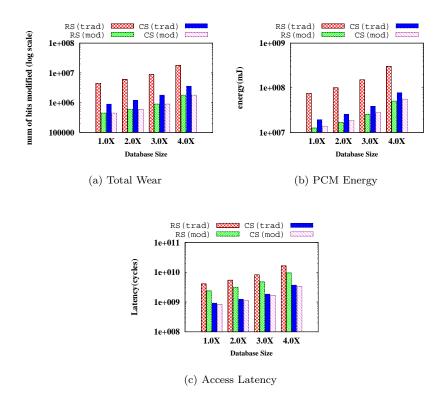

| 5.9  | Hash join Performance for various Database Size $\ . \ . \ . \ .$            | 54 |  |  |

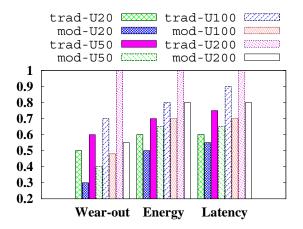

| 5.10 | Comparison of traditional and modified hash joins for R-S and                |    |  |  |

|      | C-S databases by increasing user size from 20 (U20) to $200(U200)$           | 55 |  |  |

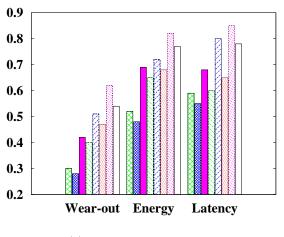

$5.11\,$  hash join Performance for a PCM-as-a-Main-Memory-Database . ~57

### Chapter 1

# Introduction

Non-volatile Memory (NVM) has a day-to-day impact in our life. NVM known as flash memory is there with us to store music on our smart phone, photographs on cameras, documents we carry on USB thumb drives, and as the electronics in cars.

Phase Change Memory (PCM) [25] is one of such emerging NVM that has many attractive features over traditional hard disks and flash SSD. For example PCM read is more than ten times faster than flash Solid State Disks(SSD), and more than hundred times faster than hard disks, while PCM write is also faster than both flash SSD and hard disks. Besides PCM supports '*in-memory update*'. And the most important features of all of them is the minimum cell density [41]. These attractive features make PCM a potential candidate to replace flash and hard disks as the primary storage in small and large scale computers and data centres. Besides, since the reads in PCM are almost comparable to that of DRAM, it is not too late to think that eventually we may have a computer with PCM as the only memory, replacing both hard disks and DRAM[34].

Despite the above positive features, PCM is relatively slow in hitting the memory world by storm, mainly, because of its two main drawbacks. The writes are relatively slow compared to reads, and specifically 100 times slower than that of DRAM [28]. And writes consume more energy, and causes wear-out of PCM cells. Over a lifetime of PCM, each cell can only be used for a limited number of times [29].

In the memory hierarchy, PCM falls in between flash SSD and DRAM main memory. As such, PCM could be a potential bridge between SSD and DRAM memory.

SSDs are gaining huge popularity as of late mainly because of their advantages over traditional hard disks, like faster read access, higher cell density and lower power consumption. Despite all these advantages, flash memory has not been able to completely take over the hard disks as a primary storage media in data centres because of their poor write performance and lifespan [9].

Even though SSD manufacturers claim that SSDs can sustain normal use for few to many years, there still exist three main technical concerns that inhibit data centers to use SSDs as the primary storage media. First concern is, as bit-density increases, flash memory chips become cheaper, but their reliability also decreases. In the last two years, for high-density flash memory, erase cycle number decreased from ten thousand to five thousand [7]. This could get even worse as the scaling goes up. Second concern is traditional redundancy solutions like RAID, which are effective in handling hard disk failures, are considered less effective for SSDS, because of the high probability of correlated device failures in SSD-based RAID [8]. The third concern is prior research on lifespan of flash memories and USB flash drives has shown both positive and negative reports [11, 22, 36]. And a recent Google report points out that endurance and retention of SSDs is yet to be proven [9].

Flash memory suffers from a random write issue when applied in enterprise environments where writes are frequent because of its 'erase-before-write' limitation. Because of this, it cannot update the data by directly overwriting it [24, 5]. While PCM has not this issue since it allows 'in-place-update' of data, PCM also has a finite write lifetime like the flash memory.

In flash memory, read and write operations are performed in a granularity of a page (typically 512 Bytes to 8 KB) [17]. But to update a page, the old page has to be erased, and to make matters worse, erase cannot be performed on a single page. Rather, a whole block (erase unit) has to be erased to do the update.

Some file systems called 'log-based file system' have been proposed to use logging to allow 'out-of-place-updating' for flash [43]. Some research shows that performance of these file system does not fit well for frequent and small random updates, like in database online transactions (OLTP) [10, 32]. Recently, In-Page Logging (IPL) approach was proposed to overcome the issue of frequent and small random updates [32]. It partitions the block of Flash memory into data pages and log pages, and further divide log pages into multiple log sectors. When a data page is updated, the change on this update (the change only, not the whole page) is reflected in the log sector corresponding to this data page. Later when the block runs out of memory, the log sectors and data pages are merged together to form an up-to-date data page.

Although IPL succeeds in limiting the number of erase and write operations, it cannot change the fact that the log region is still stored inside the flash, which has inherent limitations like no in-place-update, frequent updates of log regions, etc.

In PCM, the minimum write units are at byte-level, that means they can be written at more than 10 times finer granularity than the flash disk [45]. Furthermore, PCM allows the in-place-update of the data. Thus it is not that difficult to think that PCM may be used as a buffer for flash SSD.

By exploiting the advantages of PCM, a d-PRAM (d-Phase Change Random

Access Memory) technique was proposed where the log-region that was kept in flash is now kept in PCM [44]. This solves the issues of IPL, but it still cannot take full advantage of PCM technology. It has been well documented that flash performs poorly for random writes [5]. By properly managing the log region of PCM (or PCM buffer region), we can promise that every merge operation will invoke a sequential write flush to the flash.

### 1.1 Our contribution

This thesis mainly focuses on two contributions of PCM: using PCM as a SSDbuffer to increase its write efficiency, and impact of PCM on relational database.

As the first and main contribution, an encryption-based method to find and remove redundant data from SSD is purposed. PCM is used as a log to store smaller writes to flash because of it has the highest cell density among the emerging memory technologies [30]. Then, capacity of PCM is good enough to qualify as the buffer of flash that works as a massive storage [29]. Also previous works on combining PCM and flash [37, 26] to form hybrid storage have already shown that combining these two is feasible.

The main contributions of the first part can be summarized as:

- Since normal workloads all contain significant redundant data, we propose a hash-based encryption method to identify the redundant data that is headed to be written on flash pages, and maintain the finder in PCM.

- Considering the in-page update property of PCM, we propose the use of PCM as an extended buffer for flash memory.

- We emulate the PCM log region like the internal structure of flash memory, with blocks and log-sectors. Because of this, when the logs are merged

with data pages of flash, a sequential flush is carried out to the flash. This help increase the write performance of flash memory.

- We propose a replacement policy based on block popularity of PCM to ensure that the PCM log region wears out evenly.

- We modify the Microsoft SSD simulator extension [6] to include duplication checking mechanism. This SSD simulator is an extension of widelyused Disk simulator Disksim [12], and implements the major components of flash memory like FTL, mapping, garbage collection and wear-leveling policies, and others. The current version does not have buffer extension for flash, which we implemented. So when a new write request comes to SSD, it is first brought into this flash buffer space, and when its operation is completed, the host is notified of it.

- We also implement the two log-based buffer management techniques, namely IPL [32] and dPRAM [44] to compare our buffer management scheme against these.

- To include the PCM simulator, we wrote our own PCM simulator using C++, and implemented it as an extension of Disksim just like the SSD simulator. We implement a fingerprint store, F-block to P-block mapping table and a PCM log region as explained in above sections.

In the second part of the thesis, we ask the question: if PCM is to replace the entire primary and secondary storage, how a database system should be optimized for PCM. Primary design goal of new database algorithms should be minimizing the number of writes, and the writes should be evenly distributed over the PCM cells. Specifically, a modified hash-join Algorithm PCM-based database system is proposed.

Recent work has shown than column-stored database perform better for read-intensive queries [4] than the row-stored database. Even though, it is normally up to the database vendor to choose which type of database to use for their system, we do a comparative study of using PCM as a column-stored and row-stored database. We propose modified hash-join algorithms for these database systems and compare them with the traditional hash-join for columnstored and row-stored database systems.

Besides that, we also consider how database algorithms should be modified if PCM is used as a main memory extension, instead of secondary memory. We propose a modified hash-join algorithm for this database as well. All these hash-join algorithms re-organize the data structure for joins, and trade off an increase in PCM reads by reducing PCM writes.

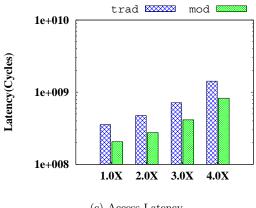

We measure the performance of these algorithms in terms of their impact on PCM Wear, PCM Energy, and Access Latency. We propose analytic metrics for measuring these parameters.

We use DRAM as an emulator for PCM. To emulate DRAM as a PCM, we change the read write time, and emulate the wear out behavior of PCM by introducing a counter on the DRAM cells that get written. We study PCM as a faster hard-disk as well as a DRAM extension. Simulation configurations for these two architectures are different. For PCM as a faster hard-disk, data would be required to brought into a DRAM to complete read or write, whereas in its use as a DRAM extension we suppose that data from PCM do not need to be brought into the DRAM to complete read/write operation. The experimental results show that the proposed new algorithms for hash-join significantly outperform traditional approaches in terms of time, energy and endurance (Section 4), supporting our analytical results. Moreover, experiment on multi-user environment shows that the results hold for a large database system with many transactions at the same time.

### Chapter 2

# Phase Change Memory Technology

Phase-Change memory (PCM) is a type of the next-generation storage-class memories (SCM) or Non-volatile Memories (NVM). PCM has read latency close to DRAM and high write endurance which makes it a promising technology for building large scale main memory system provided that one day it can have higher density than DRAM. The chalcogenide-based material used in making PCM allows it to switch between two states, amorphous and polycrystalline, by applying electrical pulses which control local heat generation inside a PCM cell [41].

Different from conventional RAM technologies, the information carrier in PCM is chalcogenide-based materials, such as  $Ge_2Sb_2Te_5$  and  $Ge_2Sb_2Te_4$  [25]. PCM exploits the property of these chalcogenide glasses which allows it to switch the material between two states, amorphous and polycrystalline, by applying electrical pulses which control local heat generation inside a PCM cell. Different heat-time profiles can be used to switch from one phase to another. The amorphous phase is characterized by high electrical resistivity, whereas the poly-

Figure 2.1: Position of PCM in Memory Hierarchy

crystalline phase exhibits low resistivity. The difference in resistivity between the two states can be 3 to 4 orders of magnitude [41].

### 2.1 PCM in Memory Hierarchy

PCM is a byte-addressable memory that has many features similar to that of DRAM except the life-time limitation [25]. In today's memory PCM falls in between DRAM and flash SSD in terms of read/write latency. Figure 2.1 shows the memory hierarchy.

Compared to DRAM, PCM's read latency is close to that of DRAM, while write latency is an order of magnitude slower. But PCM has a density advantage over DRAM. Also PCM is potentially cheaper, and more energy-efficient than DRAM in idle mode.

Compared to flash SSD, PCM can be programmed in any state, i.e. it supports the '*in-page update*', and does not have the expensive '*erase*' operation that flash SSD has [33]. PCM has higher sequential and random read speed

Figure 2.2: Memory organization with PCM

than SSD. And PCM's write endurance is also better.

Figure 2.2 shows three ways in which PCM can be incorporated in memory system [31, 39]. Proposal (a) uses PCM just as a plane replacement of SSD and hard disks. Proposal (b) replaces DRAM with PCM to achiever higher main memory capacity. Even though PCM is slower than DRAM, execution time on PCM can be reduced with clever optimizations.

Proposal (c) includes a small amount of DRAM in addition to PCM so that frequently accessed data can be kept in the DRAM buffer to improve performance and reduce PCM wear. It has been shown that a relatively small DRAM buffer (3% the size of PCM) can bridge the latency gap between DRAM and PCM[39].

As PCM technology evolves, it has shown more potential to replace NAND flash memory with advantages of in-place updates, fast read/write access, etc. Table 2.1 compares the performance and density characteristics of DRAM, PCM, NAND flash memory and hard disks. Table 2.2 compares the read/write characteristics of Flash SSD and PCM. Units of write and read operations for flash and PCM are different. While flash is written or read in units of page, PCM can be accessed in finer granularity (byte-based). This advantage makes PCM a viable option, in compared to traditional IPL [32] method, to use as a log region to store the updated contents of Flash.