Verification of Timed Process Algebra and Beyond

Zhang Xian (B.Sc. (Hons.), NUS)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE

2011

### Acknowledgement

First and foremost, I am deeply indebted to my supervisor, Dr. Dong Jin Song, for his guidance, advice and encouragement throughout the course of my doctoral program. He has given me immense support both in various ways, and have also helped me stay on the track of doing research.

I am grateful to Dr. Joxan Jaffar and Dr. Andrew Santosa for their valuable suggestions and comments on my research works. I have special thanks to Dr. Sun Jun, Dr. Liu Yang, Dr. Hao Ping, Dr. Zhang Daqing, Dr. Qin Shengchao, Dr. Mikhail Auguston, Dr. Kenji Taguchi, etc for their research collaborations.

To my seniors, Dr. Li Yuanfang, Dr. Chen Chunqing, Dr. Sun Jing, Dr. Wang H. Hai and Feng Yuzhang - Thank you for your support and friendships through my Ph.D. study.

This study was in part funded by the project "Rigorous Design Methods and Tools for Intelligent Autonomous Multi-Agent Systems" and "Advanced Modeling Checking Systems" supported by Ministry of Education of Singapore and the project "Reliable Software Design and Development for Sensor Network Systems" supported by National University of Singapore Academic Research Fund and project "Model Checking System of Systems" supported by Temasek Defence Systems Institute and the project "Activity Monitoring and User interface Plasticity for supporting Ageing with mild Dementia at Home (AMUPADH)" supported by Agency for Science, Technology and Research (A\*Star) Institute. The School of Computing also provided the finance for me to present papers in several conferences overseas.

Lastly, I wish to thank sincerely and deeply my parents Zhang Qiusheng and Li Yixia, who have taken care of me with great love in these years.

# Contents

| 1 | Intr | roduction                                       | 1  |

|---|------|-------------------------------------------------|----|

|   | 1.1  | Motivation and Goals                            | 1  |

|   |      | 1.1.1 Modeling Real-time systems                | 2  |

|   | 1.2  | Summary of Contributions                        | 4  |

|   | 1.3  | Thesis Outline and Overview                     | 8  |

|   | 1.4  | Publications from the Thesis                    | 9  |

| 2 | Bac  | kground Introduction                            | 11 |

|   | 2.1  | Communicating Sequential Processes (CSP)        | 12 |

|   | 2.2  | Timed CSP                                       | 14 |

|   |      | 2.2.1 Syntax of Timed CSP                       | 14 |

|   |      | 2.2.2 Semantics of Timed CSP                    | 15 |

|   | 2.3  | Constraint Logic Programming                    | 16 |

|   |      | 2.3.1 CLP and Reasoning                         | 18 |

|   | 2.4  | Verification and Process Analysis Toolkit (PAT) | 18 |

# CONTENTS ii

| 3 | Enc | oding   | Timed CSP in CLP                                | 23 |

|---|-----|---------|-------------------------------------------------|----|

|   | 3.1 | Timed   | d CSP Specification in CLP                      | 24 |

|   |     | 3.1.1   | Syntax Encoding                                 | 24 |

|   |     | 3.1.2   | Laws and Simplification                         | 25 |

|   | 3.2 | Mode    | ling Operational Semantics of Timed CSP in CLP  | 29 |

|   |     | 3.2.1   | Primitive process                               | 30 |

|   |     | 3.2.2   | Choice                                          | 31 |

|   |     | 3.2.3   | Concurrency                                     | 34 |

|   |     | 3.2.4   | Flow of control                                 | 36 |

|   | 3.3 | Mode    | ling Denotational Semantics of Timed CSP in CLP | 40 |

|   |     | 3.3.1   | Handling Extensions to Timed CSP                | 41 |

|   | 3.4 | Verific | cation of Timed CSP                             | 43 |

|   |     | 3.4.1   | Safety and Liveness Properties                  | 44 |

|   |     | 3.4.2   | Trace-based Properties                          | 46 |

|   |     | 3.4.3   | Time Related Checking                           | 47 |

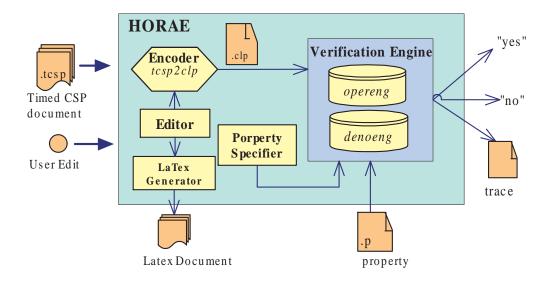

|   | 3.5 | HORA    | AE                                              | 48 |

|   |     | 3.5.1   | Building Timed CSP Models                       | 49 |

|   |     | 3.5.2   | Verifying Models                                | 50 |

|   | 3.6 | Case S  | Studies and Experiments                         | 51 |

|   |     | 3.6.1   | Timed Vending Machine                           | 51 |

# CONTENTS iii

|   |       | 3.6.2   | Dining Philosopher                  | 52 |

|---|-------|---------|-------------------------------------|----|

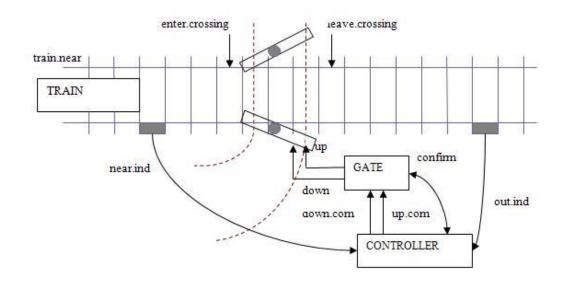

|   |       | 3.6.3   | The Railway Crossing                | 52 |

|   | 3.7   | Summ    | ary                                 | 55 |

| 4 | l Tin | ned Pla | nning                               | 57 |

|   | 4.1   | Syntax  | c of Extended Timed CSP             | 58 |

|   |       | 4.1.1   | Timed Variables                     | 58 |

|   |       | 4.1.2   | Syntax of Timed Planning            | 61 |

|   |       | 4.1.3   | Healthiness Conditions              | 63 |

|   | 4.2   | Operat  | tional Semantics                    | 64 |

|   | 4.3   | Modeli  | ing Timed Planning in CLP           | 71 |

|   |       | 4.3.1   | Encoding Extended Timed CSP in CLP  | 71 |

|   |       | 4.3.2   | Encoding Semantics in CLP           | 72 |

|   | 4.4   | Verific | ation of Extended Timed CSP         | 75 |

|   |       | 4.4.1   | Feasibility Checking                | 75 |

|   |       | 4.4.2   | Reasoning about Safety and Liveness | 76 |

|   | 4.5   | Case S  | Studies                             | 78 |

|   |       | 4.5.1   | Extended Railway Crossing System    | 78 |

|   |       | 4.5.2   | Real Time Multi-lift System         | 79 |

|   | 4.6   | Summ    | ary                                 | 82 |

# CONTENTS iv

| 5 | Job                               | Iob-shop Scheduling Problems         83                                                                                                                                       |                                       |  |

|---|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

|   | 5.1                               | Deterministic Job-Shop Scheduling Problem                                                                                                                                     | 84                                    |  |

|   |                                   | 5.1.1 Formal Definition of Deterministic Job-shop Scheduling Problem $\ldots$                                                                                                 | 84                                    |  |

|   |                                   | 5.1.2 Modeling with Timed Planning                                                                                                                                            | 85                                    |  |

|   |                                   | 5.1.3 Optimal Schedulers                                                                                                                                                      | 87                                    |  |

|   | 5.2                               | Preemptive Job-Shop Scheduling Problem                                                                                                                                        | 91                                    |  |

|   |                                   | 5.2.1 Solving Preemptive Job-shop Scheduling Problems                                                                                                                         | 92                                    |  |

|   | 5.3                               | Extended Job-shop Scheduling                                                                                                                                                  | 94                                    |  |

|   | 5.4                               | Experiments                                                                                                                                                                   | 95                                    |  |

|   | 5.5                               | Summary                                                                                                                                                                       | 96                                    |  |

| 6 | Mo                                | deling and Verification of Timed Security Protocols                                                                                                                           | 99                                    |  |

|   | 6.1                               |                                                                                                                                                                               |                                       |  |

|   |                                   | Formal Specification of Timed Security Protocols                                                                                                                              | .00                                   |  |

|   | 6.2                               | Formal Specification of Timed Security Protocols       1         Verification of Authentication       1                                                                       |                                       |  |

|   | 6.2                               |                                                                                                                                                                               | 105                                   |  |

|   | 6.2                               | Verification of Authentication                                                                                                                                                | 105<br>105                            |  |

|   | <ul><li>6.2</li><li>6.3</li></ul> | Verification of Authentication                                                                                                                                                | 105<br>105<br>108                     |  |

| 7 | 6.3                               | Verification of Authentication       1         6.2.1       Timed Authentication Property       1         6.2.2       Using Timing Information       1         Summary       1 | 105<br>105<br>108                     |  |

| 7 | 6.3                               | Verification of Authentication       1         6.2.1       Timed Authentication Property       1         6.2.2       Using Timing Information       1         Summary       1 | 105<br>105<br>108<br>109<br><b>11</b> |  |

|   |     | 7.1.2   | Modeling using Timed Planning             | 114 |

|---|-----|---------|-------------------------------------------|-----|

|   |     | 7.1.3   | Medication Planner                        | 120 |

|   |     | 7.1.4   | Specific domain: Elderly Reminding System | 122 |

|   | 7.2 | Smart   | Nursing Home for Mild Dementia Elderly    | 124 |

|   |     | 7.2.1   | System Design                             | 125 |

|   |     | 7.2.2   | Verification                              | 133 |

|   |     | 7.2.3   | Modeling with PAT                         | 135 |

|   | 7.3 | Summ    | ary                                       | 136 |

| 8 | Con | clusio  | n                                         | 137 |

|   | 8.1 | Summ    | ary of the Thesis                         | 137 |

|   | 8.2 | Future  | e Works                                   | 140 |

|   |     | 8.2.1   | Reduction and Optimization Techniques     | 140 |

|   |     | 8.2.2   | New Application Domains                   | 141 |

|   |     | 8.2.3   | Tool Development                          | 141 |

| A | Hea | lthines | ss Conditions for Timed Planning          | 153 |

| в | Rea | l-time  | Multi-lift System                         | 155 |

| С | Con | nplete  | Model of Smart Nursing Home               | 157 |

| D | Con | nplete  | PAT Model of Smart Nursing Home           | 163 |

### Summary

The design and verification of real-time systems are notoriously difficult problems. In this thesis, we study the modeling and verification of real-time systems using timed process algebra, particularly Timed CSP.

Timed CSP is an elegant and intuitive modeling language for real-time systems. It has been widely accepted and applied to a wide arrange of systems. However the verification support for Timed CSP is limited. The first part of the thesis is to develop a reasoning mechanism for Timed CSP by using Constraint Logic Programming (CLP) as underlying reasoning engine. Our approach starts with a systematic translation of the syntax of Timed CSP into CLP. Powerful constraint solver like  $\text{CLP}(\mathcal{R})$  is then used to prove traditional safety properties and beyond, e.g., reachability, deadlock-freeness, timewise refinement relationship, lower or upper bound of a time interval, etc. Counterexamples are generated when properties are not satisfied. Based on this translation, an interactive tool, named HORAE, which provides composing and reasoning of Timed CSP process descriptions is developed.

The second contribution of this thesis is the proposal of a formal language, named Timed Planning, for modeling real-time systems. Timed Planning extends Timed CSP with the capability of stating complicated timing behaviors. A Timed Planning model is made up of a hierarchical timed process and a set of constraints over processes, events and the data variables which are the requirements that the process should satisfy. Particularly, each process is associated with a set of localized timing/untiming requirements with keyword WHERE which can be specified in a compositional way. The full syntax and operational semantics of Timed Planning are formally defined. A reasoning mechanism for the Timed Planning is hence developed based on CLP by extending our reasoning engine HORAE. Feasibility checking and various property verification can be applied to check systems modeled in Timed Planning.

To show the usefulness of Timed Planning, we apply Timed Planning and HORAE to solve three different application domains. Firstly, we use Timed Planning to model classical jobshop scheduling problems, in order to find a shortest execution in terms of elapsed time. In this case, the job-shop scheduling problem can be reduced to a problem of finding a complete execution (an execution that terminates) with the minimum execution time. In our work, Both deterministic and preemptive job-shop scheduling problems can be solved.

Secondly, security protocols are widely used for secure application-level data transport crossing distributed systems. Designing security protocols is notoriously difficult and error-prone. The new challenges raise when different timing aspects are required in the security protocol design, such as timestamps, delays, timeout and a set of timing constraints. We focus on using Timed Planning to accomplish the modeling and analyzing of timed security protocols. The use of explicit timing information allows us to specify security protocols with timestamps, timeout and retransmissions which can be naturally modeled using Timed Planning specification. In the timing analysis, we could verify timed non-injective agreement authentication property which can be easily extended to other authentication property verification. Besides, we can model timing requirements/constraints and verify other timed sensitive properties such as execution time of a protocol which is beyond the capability of existing approaches.

Thirdly, pervasive computing environments encompass a spectrum of computation and communication devices that seamlessly augment human thoughts and activities. They have been used to assist elders with mild dementia to improve their level of independence and quality of life through cognitive reinforcement. To support formal analysis, we propose to build a context-aware reminding framework for elders living at home using Timed Planning specification. Then we demonstrate the effectiveness of formal methods via modeling and verifying an integrated smart space reminding system for monitoring and assisting people with mild dementia in the nursing home.

Key words: Timed Process Algebra, Formal Verification, Concurrent and Realtime Systems, Constraint Logic Programming, Refinement, Job-shop Scheduling Problem, Security Protocol, Dementia

# List of Figures

| 2.1 | Architecture Design                                                  |

|-----|----------------------------------------------------------------------|

| 3.1 | Timed Vending Machine in CLP                                         |

| 3.2 | Overview of HORAE                                                    |

| 3.3 | The Rail Way Control System                                          |

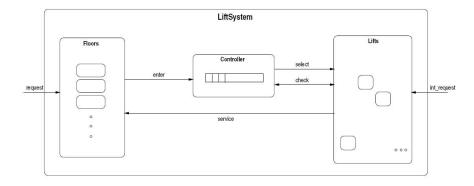

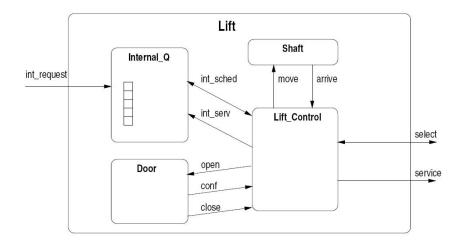

| 4.1 | The Multi-Lift System Communication Diagram                          |

| 4.2 | Internal Lift Communication Diagram                                  |

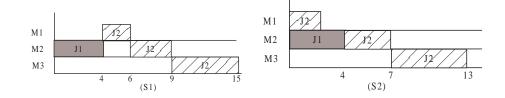

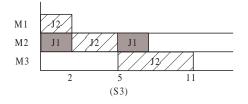

| 5.1 | The Gantt-Chart representations of two schedules                     |

| 5.2 | The Gantt-Chart representations of a preemptive schedules 91         |

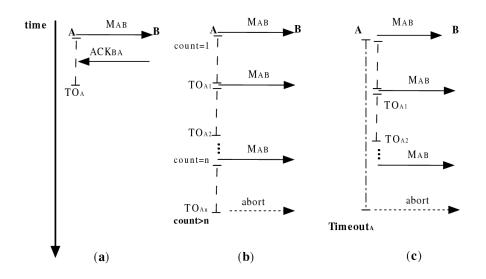

| 6.1 | Timeout patterns: (a) typical (b) count-bounded (c) time-bounded 101 |

| 6.2 | Analysis of Wide Mouth Frog protocols                                |

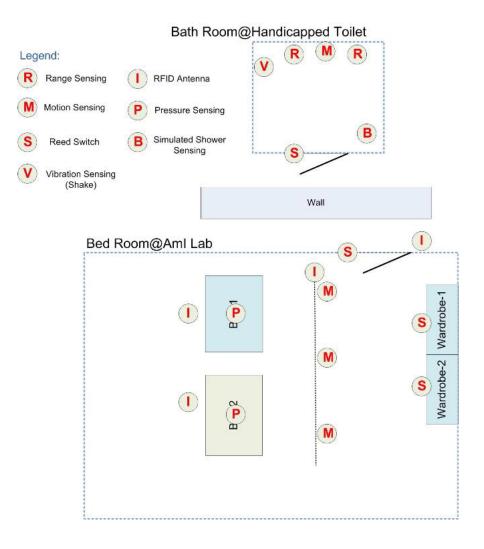

| 7.1 | The Sensor Setup for Bedroom and Bath Room                           |

# List of Tables

| 3.1 | Library of Timed CSP processes in CLP                                                                                                                                | 25  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Properties Verification                                                                                                                                              | 54  |

| 3.3 | Experiment Results                                                                                                                                                   | 55  |

| 5.1 | The result for $n$ jobs with 4 machines, where $n = 2,, 6$ . $\sharp j, \sharp states, time$ represents number of jobs, number of state space and the execution time | 96  |

| 5.2 | The result for the ten hard bench marks deterministic job-shop scheduling                                                                                            |     |

|     | problems. The first three columns give the problem name, no. of jobs and                                                                                             |     |

|     | no. of machines                                                                                                                                                      | 97  |

| 7.1 | Summary of needs and wants for mild dementia people living at home $\ldots \ldots 1$                                                                                 | 13  |

| 7.2 | Results of Experiment                                                                                                                                                | .34 |

# Chapter 1

# Introduction

The design and verification of real-time systems are notoriously difficult problems, especially when systems often depend on quantitative timing. Modeling and verification of real-time systems are research topics which have important practical implication. Formal modeling and analysis of real-time systems are the trend to systematic and automatic detecting the design or implementation errors for complex systems.

# 1.1 Motivation and Goals

The correctness of many systems and devices in our modern society depends not only on the effects or results they produce but also on the time at which these results are produced. These real-time systems range from the anti-lock braking controller in automobiles to the vital-sign monitor in hospital intensive-care units. For example, when the driver of a car applies the brake, the anti-lock braking controller analyzes the environment in which the controller is embedded (car speed, road surface, direction of travel) and activates the brake with the appropriate frequency within fractions of a second. Both the result (brake activation) and the time at which the result is produced are important in ensuring the safety of the car, its driver, and passengers.

Recently, computer hardware and software are increasingly embedded in a majority of these real-time systems to monitor and control their operations. These computer systems are called real-time computer systems, or simply real-time systems. Unlike conventional, nonreal-time systems, real-time systems are closely coupled with the environment being monitored and controlled. Examples of real-time systems include computerized versions of the braking controller and the vital-sign monitor, the new generation of airplane and spacecraft avionics, the planned Space Station control software, high-performance network and telephone switching systems, multimedia tools, virtual reality systems, robotic controllers, battery-powered instruments, wireless communication devices (such as cellular phones and PDAs), astronomical telescopes with adaptive-optics systems, and many safety-critical industrial applications. These real-time systems must satisfy stringent timing and reliability constraints in addition of functional correctness requirements.

In this thesis, our research focuses on the modeling and verification of real-time systems. In particular, we have tried to address four issues related to real-time systems: (i) proposing a formal language to model real-time systems, (ii) exploring efficient verification techniques to perform formal analysis of the models, (iii) implementing a toolkit to support effective real-time verification, and (iv) applying the proposed techniques in different domains.

#### 1.1.1 Modeling Real-time systems

Real-time system modeling is of great importance and highly non-trivial. The choice of modeling language is an important factor in the success of the entire system analysis or development. The language should cover several facets of the requirements and the model should reflect exactly (up to abstraction of irrelevant details) an existing system or a system to be built. The language should have a semantic model suitable to study the behaviors of the system and to establish the validity of desired properties. Many languages have been proposed to model real-time systems, e.g., algebra of timed processes [79], timed CCS [108], timed CSP [88, 18], etc. The most popular language is timed automata [5, 71]. Timed automata are finite state automata equipped with clocks. They are powerful in de-

signing real-time models by explicitly manipulating clock variables. Real-time constraints are captured by explicitly setting or resetting clocks. A number of automatic verification support for timed automata based models have proven to be successful, e.g., UPPAAL [62], KRONOS [10].

Models based on timed automata often have a simple structure. For instance, the input models of the UPPAAL checker take the form of a network of timed automata with no hierarchy [62]. The advantage of a simple structure is that efficient verification is made feasible. Nonetheless, designing and verifying compositional real-time systems is becoming an increasingly important task due to the widespread applications and increasing complexity of real-time systems. High-level requirements for real-time systems are often stated in terms of *deadline*, *time out*, and *timed interrupt* [60, 32, 63]. In industrial case studies of realtime system verification, system requirements are often structured into phases, which are then composed in many different ways. Unlike Statecharts equipped with clocks [49] or timed process algebras [79, 108, 88], timed automata lack high-level compositional patterns for hierarchical design. Users often need to manually cast those terms into a set of clock variables with carefully calculated clock constraints. This process is tedious and error-prone. On the other hands, real-time system modeling based on timed process algebras often suffers from lack of language features (e.g., shared variables) or automated tool support.

One goal of this thesis is to design a modeling language for hierarchical real-time systems, which is sufficiently expressive, but is still subject to automatic verification.

#### **Requirement Specification and Verification**

Critical system requirements like safety, liveness and fairness play important roles in system specification, verification and development. Safety properties ensure that something undesirable never happens. Liveness properties state that something desirable must eventually happen.

In order to verify hierarchical real-time systems, more general specifications like refinement

relation are needed. In these cases, the requirement is modeled using an abstract model rather than a logic formula, which gives more expressive power. FDR (Failures-Divergence Refinement) [84] is the *de facto* refinement analyzer for CSP, which has been successfully applied in various domains. Based on the model checking algorithm presented in [84] and later improved with other reduction techniques presented in [86], FDR is capable of handling large systems. Nonetheless, when the system contains real-time constraints, new verification techniques and tools are required.

There are a few verification support for Timed CSP, e.g. the theorem proving approach documented in [11, 47], and the translation to UPPAAL models [25, 26]. The PAT model checker [1] is the first dedicated verification tool support for Timed CSP models by using dynamic zone abstraction. However, Timed CSP lacks support for stating system requirements which constrain all behavioral traces of given processes, for example, *deadline* and execution time of a process, time-related constraints among events which are common requirements for many real time systems. To increase the expressiveness of Timed CSP, current verification support becomes inadequate.

In this thesis, we want to explore the new approach for verification of powerful real-time system modeling language. To add to our understanding of the field, we aim to develop efficient model checker with the consideration of the above points.

### **1.2 Summary of Contributions**

The main result of this thesis is a powerful modeling language for real-time systems together with the complete verification support. Several cases studies demonstrate the usefulness of our approach. The contributions of this thesis can be summarized as follows:

Event-based specification languages like the classic Communicating Sequential Process (C-SP) of Hoare's [51] and its timed extension Timed CSP [82, 18], have been proposed for decades. Such specification languages are elegant and intuitive as well as precise. They have

been widely accepted and applied to a wide arrange of systems, including communication protocols, embedded systems, etc [85]. It is important that system specified using CSP or Timed CSP can be proved formally and even better if the proving is fully automated.

The first part of the thesis is building a reasoning mechanism for Timed CSP. Instead of building a specialized reasoning engine for Timed CSP from scratch, we choose one of powerful reasoning mechanisms, Constraint Logic Programming (CLP) [53, 54], as underlying reasoning engine. CLP has been successfully applied to model programs and transition systems for the purpose of verification [48, 56], showing that their approach outperforms the well-known state-of-art systems with higher efficiency. The XMC/RT system [37, 45] showed how a Timed Safety Automata (TSA) represented in CLP can be comparable in efficiency, by using a tabling logic programming framework. [4] employs a logic program transformation based approach for inductive verification of real-life parameterized protocols. Our approach starts with a systematic translation of the syntax of Timed CSP into CLP. Operational semantics are encoded into CLP in a systematic way. Powerful constraint solver like  $\text{CLP}(\mathcal{R})$  [55] is then used to prove traditional safety properties and beyond, e.g., reachability, deadlock-freeness, lower or upper bound of a time interval, etc. Counterexamples are generated when properties are not satisfied. Based on this translation, an interactive tool, named HORAE, which provides composing and reasoning of Timed CSP process descriptions is developed.

One of the main contribution of this thesis is the proposal of a formal language for modeling real-time systems, which is an extension of Timed CSP. We name this extension as Timed Planning. Timed Planning specification extends Timed CSP with the capability of stating complicated timing behaviors for processes and events to model and verify complex compositional real-time systems. A Timed Planning model is made up of a hierarchical timed process and a set of constraints over processes, events and the data variables which are the requirements that the process should satisfy. In this approach each process is associated with a set of localized timing/untiming requirements with keyword WHERE which can be specified in a compositional way. The full syntax and operational semantics of Timed Planning language are formally defined. A reasoning mechanism for the Timed Planning is hence developed based on CLP by extending our reasoning engine HORAE. Both syntax and semantics of Timed Planning are formally translated into CLP. The operational semantics is encoded to CLP, where a set of global and local variables need to be captured during the execution. Feasibility checking and various property verification can be applied to check systems modeled in Timed Planning. Feasibility checking is necessary which helps users to debug the conflicts of the set of timing constraints specified in the systems.

In many application domains, we are interested in selecting, among all possible behaviors, one that *optimizes* some sophisticated performance measurement. We apply Timed Planning and HORAE to solve classical job-shop scheduling problems, where finding an optimal schedule corresponds to finding a shortest execution (in terms of elapsed time) in the Timed Planning. The observation underlying is that classical scheduling and resource allocation problems can be modeled naturally using Timed Planning whose runs correspond to feasible schedules. In this case, the job-shop scheduling problem can be reduced to a problem of finding a complete execution (an execution that terminates) with the minimum execution time. In our work, Both deterministic [58] and preemptive job-shop scheduling problems can be solved. We also apply our approach to handle the extended job-shop scheduling problems, where jobs can have more complex relations, such as a composition of operational behaviors with communications, and jobs with deadlines and relative timing constraints, which no other current work are able to support.

Another application of Timed Planning is to model and verify timed security protocols. Security protocols are widely used for secure application-level data transport crossing distributed systems. In general, designing security protocols is notoriously difficult and error-prone. Many protocols proposed in the literature and exploited in practice turned out to be awed, or their well-functioning was found to be based on implicit assumptions. Since the late 80s various approaches have been put forward for the formal verification of security protocols to overcome the problems of faulty implementations and hidden requirements. The new challenges raise when different timing aspects are required in the security protocol design, such as timestamps, delays, timeout and a set of timing constraints. In the past years, there has been an increasing interest in the formal analysis of timed cryptographic protocols. However, there are few tool supports for modeling and analyzing security protocols with the capability of capturing various timing features. A particularly successful approach to analyze untimed security protocols is modeled using CSP [51] and verified by FDR model checker [87, 70]. Motivated by this approach, we focus on using Timed Planning to accomplish the modeling and analyzing of timed security protocols. Our approach is different from the previous approaches by taking the timing information into account. The use of explicit timing information allows us to specify security protocols with timestamps, timeout and retransmissions which can be naturally modeled using Timed Planning specification. In the timing analysis, we could verify timed non-injective agreement authentication property which can be easily extended to other authentication property verification [46]. We also propose to use the capability of Timed Planning to avoid such attacks without changing the original specifications of the protocols. Besides, we can model timing requirements/constraints and verify other timed sensitive properties such as execution time of a protocol which is beyond the capability of existing approaches.

Pervasive computing environments encompass a spectrum of computation and communication devices that seamlessly augment human thoughts and activities. Applications in this type of environments are often context-aware, using various kinds of context such as location and time to adapt to the evolving environments and provide smarter services. As the fast development of context-aware systems (e.g. new sensors, new application domains), critical system requirements like safety and liveness properties start to play more important roles. For example, smart system deployed in hospital shall never reach a state which hazards patients' lives. Therefore, formal methods are desirable in the design and development context-aware systems.

Pervasive computing techniques have been proposed to assist elders with mild dementia to improve their level of independence and quality of life through cognitive reinforcement. To support formal analysis, we propose to build a context-aware reminding framework for elders living at home using Timed Planning specification. Then we demonstrate the effectiveness of formal methods via modeling and verifying an integrated smart space reminding system for monitoring and assisting people with mild dementia in the nursing home.

# 1.3 Thesis Outline and Overview

In this section, we briefly present the outline of the thesis and overview of each chapter.

Chapter 2 introduces background information on specification languages and tools used in the presented work. We firstly review CSP and Timed CSP with their syntax and semantics. Next we briefly introduce Constraint Logic Programming (CLP) and its related works in formal method domain.

Chapter 3 illustrates the verification system for Timed CSP using Constraint Logic Programming as underlying reasoning engine. We firstly show how the syntax of Timed CSP is formally translated into CLP. The operational semantics of each and every operator of Timed CSP are formally encoded into CLP. A reasoning tool for Timed CSP is presented in Section 3.5. Last but not least, we demonstrate the effectiveness of our approach through benchmark real-time systems.

Chapter 4 introduces an extended Timed CSP language, namely Timed Planning. We firstly define the syntax and operational semantics of Timed Planning formally. We further extend the verification system of Timed CSP to support Timed Planning using Constraint Logic Programming.

Chapters 5, 6 and 7 are devoted to applying Timed Planning in various applications to solve different problems. Chapter 5 applies Timed Planning in Job-shop scheduling problems where using underlying reasoning engine to find optimal scheduler for both preemptive and non-preemptive job-shop scheduling problems. Another piece of work has been done is that we apply Timed Planning to model and verify timed security protocols, which is demonstrated in Chapter 6. In Chapter 7, we apply Timed Planning in pervasive computing, more specifically, the mild dementia care for elderly at both home and nursing home.

Lastly, Chapter 8 concludes this thesis, summarizes the main contributions and discusses possible future work directions.

### **1.4** Publications from the Thesis

Most of the work presented in this thesis has been published or accepted in international conference proceedings or journals.

The work in Chapter 3 was presented at The 8<sup>th</sup> International Conference on Formal Engineering Methods ICFEM'06 (December 2006) [28]. The tool horae in Section 3.8 is published as a tool paper on The 13<sup>th</sup> International Symposium on Formal Methods FM'06 (November 2006) [27]. The work in Chapter 4 was the basis for the paper published at The 4<sup>th</sup> International Conference on Secure Software Integration and Reliability Improvement (June 2010) [112]. The work in Chapter 5 was presented at The 1<sup>st</sup> Workshop on International Conference on Secure Software Integration and Reliability Improvement (April 2010) [111]. The work in Chapter 6 was accepted at The 4<sup>th</sup> International Conference on Secure Software Integration and Reliability Improvement (September 2010) [112].

A paper including the modeling smart reminding system presented in Section 7 has been submitted for publication [98]. I also made contributions to other publications [24, 30, 31, 33, 99] which are remotely related this thesis.

For all the publications mentioned above, I have contributed substantially in both theory development and tool implementation.

A full list of the publications on which the thesis is based is included in the bibliography.

# Chapter 2

# **Background Introduction**

Real-time systems exhibit complex behaviors. System simulation and verification become more and more demanding as the complexity grows. It is highly desirable to have formal modeling languages to describe the real-time system rigourously. Compared with Timed Automata (with a flatten structure), timed process algebra is a more powerful way to modeling hierarchical real-times systems. Timed process algebra has a long history with various proposed formalisms. Examples include Timed CCS [108], Timed Communicating Sequential Processes (Timed CSP) [89], Timed petri nets [77] and so on. In this thesis, we focus on Timed CSP for its expressive power and wide usage.

Constraint logic programming (CLP) [54] is a form of constraint programming, in which logic programming is extended to include concepts from constraint satisfaction. In this chapter, we briefly introduce the basic concepts and conventions of CLP, which are used in the rest of the thesis.

The remainder of the chapter is organized as follows. Section 2.1 gives an introduction to CSP. The timed extension of CSP is explained in Section 2.2 with formal syntax and semantics. Section 2.3 presents the fundamental concepts of CLP. Section 2.4 introduces the model checker PAT.

### 2.1 Communicating Sequential Processes (CSP)

In computer science, Communicating Sequential Processes (CSP) [52] is a formal language for describing patterns of interaction in concurrent systems. It is a member of the family of mathematical theories of concurrency known as process algebras, or process calculi. CSP was first described in [51] by C. A. R. Hoare, but has evolved substantially since then. FDR (Failures-Divergence Refinement) [84] is the *de facto* refinement analyzer for CSP, which has been successfully applied in industry as a tool for specifying and verifying the concurrent aspects of a variety of different systems. The theory of CSP is still the subject of active research, including work to increase its range of practical applicability. CSP has passed the test of time. It has been widely accepted and influenced the design of many recent programming and specification languages including Ada [40], occam [75], Concurrent ML [83], BPEL4WS [81], TCOZ [74, 72, 25, 73], OZTA [24, 30] etc.

As its name suggested, CSP allows the description of systems in terms of component processes that operate independently, and interact with each other solely through message-passing communication. However, the "Sequential" part of the CSP name is now something of a misnomer, since modern CSP allows component processes to be defined both as sequential processes, and as the parallel composition of more primitive processes. The relationships between different processes, and the way each process communicates with its environment, are described using various process algebraic operators. Using this algebraic approach, quite complex process descriptions can be easily constructed from a few primitive elements.

CSP is a formal specification language where processes proceed from one state to another by engaging in events. Processes may be composed by using operators which require synchronization on events, i.e., each component must be willing to participate in a given event before the whole system makes the transition. Synchronous communication, rather than assignments to shared state variables, is the fundamental means of interaction between agents. In the following, we present the syntax of CSP process and informal semantics. For any process P in CSP language, it can be defined using following syntax.

| $P = Stop \mid Skip$                          | – primitives             |

|-----------------------------------------------|--------------------------|

| $  e \rightarrow P$                           | – event prefixing        |

| $  ch!exp \rightarrow P   ch?x \rightarrow P$ | – channel communications |

| $  P \setminus X$                             | - hiding                 |

| P; Q                                          | – sequential composition |

| $  P \Box Q   P \sqcap Q$                     | – choice operators       |

| $\mid [b]P$                                   | – state guard            |

| $  P \parallel Q$                             | – parallel composition   |

| $\mid P \mid \mid \mid Q$                     | – interleave composition |

| $  P \bigtriangledown Q$                      | - interrupt              |

| $\mid ref(Q)$                                 | – process reference      |

where P, Q are processes, e is a name representing an event with an optional sequential program<sup>1</sup> prog, X is a set of event names (e.g.,  $\{e_1, e_2\}$ ), b is a Boolean expression, ch is a channel, exp is an expression, and x is a variable.

Stop is the process that communicates nothing, also called deadlock.  $Skip = \checkmark \rightarrow Stop$ , where  $\checkmark$  is the special event of termination. Event prefixing  $e \rightarrow P$  performs e and afterwards behaves as process P. Hiding process  $P \setminus X$  makes all occurrences of events in Xnot to be observed or controlled by the environment of the process. Sequential composition, P; Q, behaves as P until its termination and then behaves as Q. External choice  $P \square Q$ is solved only by the occurrence of a visible event<sup>2</sup>. On the contrast, internal choice  $P \sqcap Q$ is solved non-deterministically. Process [b]P waits until condition b becomes true and then behaves as P. Note that [b]P does not block and will be dropped in choice operators if other choices are selected. Notice that it is different from if b  $\{P\}$  else  $\{Q\}$ . One distinguishing feature of CSP is alphabetized multi-processes parallel composition. Let P's alphabet, written as  $\alpha P$ , be the events in P excluding the special invisible event  $\tau$ . Process  $P \parallel Q$ synchronizes common events in the alphabets of P and Q excluding non-communicating events. In contrast, process  $P \parallel || Q$  runs all processes independently (except for communication through shared variables and synchronous channels<sup>3</sup>). Process  $P \lor Q$  behaves as P

<sup>&</sup>lt;sup>1</sup>The grammar rules for the sequential program can be found in PAT user manual.

<sup>&</sup>lt;sup>2</sup>In CSP, symbol  $\tau$  is introduced as the internal action in the operational semantics only. Any event other than  $\tau$  is called visible event.

<sup>&</sup>lt;sup>3</sup>Note that in original CSP,  $P \parallel \mid Q$  does not allow communication through shared channels.

until the first occurrence of a visible event from Q. A process expression may be given a name for referencing. Recursion is supported by process referencing.

# 2.2 Timed CSP

#### 2.2.1 Syntax of Timed CSP

Hoare's CSP [51] is an event based notation primarily aimed at describing the sequencing of behavior within a process and the synchronization of behavior (or *communication*) between processes. Timed CSP extends CSP by introducing a capability to quantify temporal aspects of sequencing and synchronization. Inherited from CSP, Timed CSP adopts a symmetric view of process and environment. Events represent a cooperative synchronization between process and environment. Both process and environment may control the behavior of the other by *enabling* or *refusing* certain events and sequences of events.

**Definition 1 (Timed CSP)** A Timed CSP process is defined by the following syntax,

$$\begin{array}{rcl} P & ::= & \operatorname{STOP} \mid \operatorname{SKIP} \mid \operatorname{RUN} \mid e \xrightarrow{t} P \mid e : E \to P(e) \mid e @t \to P(t) \\ & \mid & P_1 \Box P_2 \mid P_1 \sqcap P_2 \mid P_1 |_X \mid \mid_Y P_2 \mid P_1 \mid \mid [X] \mid P_2 \mid P_1 \mid \mid \mid P_2 \\ & \mid & P_1; \ P_2 \mid P_1 \bigtriangledown P_2 \mid P_1 \stackrel{d}{\rhd} P2 \mid \operatorname{WAIT} d \mid P_1 \lor_d P_2 \\ & \mid & \mu X \bullet P(X) \end{array}$$

RUN<sub> $\Sigma$ </sub> is a process always willing to engage any event in  $\Sigma$ . STOP denotes a process that deadlocks and does nothing. A process that terminates is written as SKIP. A process which may participate in event e then act according to process description P is written as  $e@t \rightarrow P(t)$ . The (optional) timing parameter t records the time, relative to the start of the process, at which the event e occurs and allows the subsequent behavior P to depend on its value. The process  $e \xrightarrow{t} P$  delays process P by t time units after engaging event e. The external choice operator, written as  $P \square Q$ , allows a process of choice of behavior according to what events are requested by its environment. Internal choice represents variation in behavior determined by the internal state of the process. The parallel composition of processes  $P_1$  and  $P_2$ , synchronized on common events of their alphabets X, Y (or a common set of events A) is written as  $P_1 |_X ||_Y P_2$  (or  $P_1 |[A]| P_2$ ). The sequential composition of  $P_1$  and  $P_2$ , written as  $P_1$ ;  $P_2$ , acts as  $P_1$  until  $P_1$  terminates by communicating a distinguished event  $\checkmark$  and then proceeds to act as  $P_2$ . The interrupt process  $P_1 \bigtriangledown P_2$  behaves as  $P_1$  until the first occurrence of event in  $P_2$ , then the control passes to  $P_2$ . The timed interrupt process  $P_1 \bigtriangledown P_2$  behaves similarly except  $P_1$  is interrupted as soon as d time units have elapsed. A process which allows no communications for period d time units then terminates is written as WAIT d. The timeout construct written as  $P_1 \bowtie^d P_2$  passes control to an exception handler  $P_2$  if no event has occurred in the primary process  $P_1$  by some deadline d. Recursion is used to give finite representation of non-terminating processes. The process expression  $\mu X \bullet P(X)$  describes processes which repeatedly act as P(X). The detailed illustration of each process can be found in [89].

#### 2.2.2 Semantics of Timed CSP

The semantics of a Timed CSP process is precisely defined either by identifying how the process may evolve through time or by engaging in events (i.e., the operational semantics defined in [90]) or by stating the set of observations, e.g., traces, failures and timed failures (i.e., the denotational semantics as defined in [17]). In this work, Timed CSP is used to specify interactive timed tasks.

In general, the behavior of a process at any point in time may be dependent on its internal state and this may conceivably take an infinite range of values. It is often not possible to provide a finite representation of a process without introducing some notation for representing this internal state. The approach adopted by Timed CSP is to allow a process definition to be parameterized by state variables. Thus a definition of the form P(x) represents a family of definitions, one for each possible value of x.

**Example 2.2.1 (Timed Vending Machine)** A user may insert some coins and then make a choice between coffee or tea. Once the choice is made, the vending machine dispatches the

corresponding drink. Or the user may ask the machine to release the coins and walk away. If the user idles more than 10 seconds after the coin is inserted, the machine will release the coins.

$$TVM \stackrel{\widehat{=}}{=} \mu X \bullet coin \rightarrow ((reqrelease \rightarrow release \stackrel{2}{\rightarrow} X)$$

$$\square (coffee \stackrel{3}{\rightarrow} dispatch coffee \rightarrow X) \square (tea \stackrel{2}{\rightarrow} dispatch tea \rightarrow X))$$

$$\stackrel{10}{\triangleright} (release \rightarrow X)$$

$\Box$ end

### 2.3 Constraint Logic Programming

Constraint Logic Programming (CLP) [54] began as a natural merger of two declarative paradigms: constraint solving and logic programming. This combination helps to make CLP programs both expressive and flexible, and in some cases, more efficient than other kinds of logic programs. The CLP scheme defines a class of languages based upon the paradigm of rule-based constraint programming.  $\text{CLP}(\mathcal{R})$  [55] is an instance of this class, which is used in this thesis. We present some preliminary definitions about CLP in this section.

**Definition 2 (Atom, Rule and Goal)** An atom is of the form  $p(\tilde{t})$ , where p is a user defined predicate symbol and  $\tilde{t}$  is a sequence of terms  $t_1, t_2, \ldots, t_n$ . A rule is of the form  $A: -\tilde{B}, \Psi$  where the atom A is the head of the rule, and the sequence of atoms  $\tilde{B}$  and the constraint  $\Psi$  constitute the body of the rule. A goal has exactly the same format as the body of the rule of the form  $? - \tilde{B}, \Psi$ . If  $\tilde{B}$  is an empty sequence of atoms, we call this a (constrained) fact. All goals, rules and facts are terms.

The universe of discourse  $\mathcal{D}$  of CLP program is a set of terms, integers, and lists of integers. A constraint is written using a language of functions and relations. They are used in two ways, in the basic programming language to describe expressions and conditions, and in user assertions, as defined below. In this work, we will not define the constraint language explicitly, but invent them on demand in accordance with our examples. Thus the terms of our CLP programs include the function symbols of the constraint language. A ground instance of a constraint, atom and rule is defined in obvious way. A ground instance of a constraint is obtained by instantiating variables therein from  $\mathcal{D}$ . The ground instances of a goal G, written [G] is the set of ground atoms obtained by taking all the true ground instances of G and then assembling the ground atoms therein into a set. We write  $G_1 \models G_2$ to mean that for all groundings  $\theta$  of  $G_1$  and  $G_2$ , each ground atom in  $G_1\theta$  appears in  $G_2\theta$ .

Let  $G = (B_1, ..., B_n, \Psi)$  and P denote a goal and program respectively. Let R = A:  $-C_1, ..., C_m, \Psi_1$  denote a rule in P, written so as none of its variables appear in G. Let A = B, where A and B are atoms, be shorthand for equations between their corresponding arguments. A *reduct* of G using R is of the form

$(B_1, ..., B_{i-1}, C_1, ..., C_m, B_{i+1}, ..., B_n, B_i = A \land \Psi \land \Psi_1)$

provided  $B_i = A \wedge \Psi \wedge \Psi_1$  is satisfiable. A *derivation sequence* is a possibly infinite sequence of goals  $G_0, G_1, \ldots$  where  $G_i, i > 0$  is a reduct of  $G_{i-1}$ . If there is a last goal  $G_n$ with no atoms, notationally  $(\Box, \Psi)$  and called a *terminal goal*, we say that the derivation is a *successful* and that the *answer constraint* is  $\Psi$ . A derivation is ground if every reduction therein is ground.

**Example 2.3.1 (Fibonacci)** The following is typical CLP program:

$$\begin{array}{l} fib(0,1). \ fib(1,1). \\ fib(N,X1+X2): -N>1, fib(N-1,X1), fib(N-2,X2) \end{array}$$

A relation fib(N, X) is defined, where X is the factorial of N, denoted as X = N!. There are three atoms for the relation fib(N, X), where the first two atoms are *facts* and the last one is a *rule*. We want to find the number whose fibonacci is greater than 3 but less than 8, by executing the goal ? - F > 3, F < 8, fib(N, F). which returns N = 4, F = 5.  $\Box$  end

CLP has been successful as a programming language, and more recently, as a model of executable specifications. There have been numerous works which use CLP to model system modeling or programs and which use an adaptation of the CLP proof system for proving certain properties [57, 29]. In this work, we follow this trend and use existing powerful constraint solvers for mechanized Timed Planning.

#### 2.3.1 CLP and Reasoning

Constraint Logic Programming has been used to model programs and transitions systems for purpose of verification problems. In particular, it has been used to model Timed Safety Automata (TSA) [50]. The main advantage of using CLP pertain to expressiveness. For example, [48] demonstrates the proof of some standard properties, as well as properties such timed bounds between important events, on a CLP representation of TSA.

[56] presented a CLP proof method for well-known state-of-art systems - Timed Automata. They started with a systematic translation of TSA into CLP and then use a new CLP inference method for proving assertions. They claimed that their assertion language can specify important properties beyond traditional safety properties, one important of which is the *symmetric*. They also gave a demonstration showing that their improvements over the Timed Automata model checker - UPPAAL [62].

Moreover, (Constraint) Logic Programming has been used in formal methods area, for example, [106] uses Logic Programming Techniques for animating Z which could be used for detecting errors in a formal specification.

# 2.4 Verification and Process Analysis Toolkit (PAT)

In this section, we introduce the verification tool for Timed CSP. Due to the expressive power, verification of Timed CSP is a difficult task with minimum tool support. To the best of our knowledge, there are few verification support for Timed CSP, e.g. the theorem proving approach documented in [11, 47], the translation to UPPAAL models [25, 26] and the approach based on constraint solving [28]. Among them, the most established tool is Process Analysis Toolkit (PAT) [1, 66, 95, 68, 64, 101, 113, 103]. PAT is a self-contained toolkit to analyze real-time systems, which supports system modeling, animated simulation and automatic verification (based on advanced model checking techniques like dynamic zone abstraction [99]).

PAT's modeling language [99, 94, 102, 69, 97] is an extension of Timed CSP with mutable variables and data structures (e.g., arrays, stacks or arbitrary data types), synchronous or asynchronous channels, etc. The language adopts a dense-time semantics, where the clock values are rational numbers. Hence, there may be infinitely many transitions between any two time points. To offer efficient verification support, a fully automated abstraction technique is developed to build an abstract finite state system from the (infinite) model. It has been prove that the abstraction has finite state and is subject to model checking [99]. Further, it weakly bi-simulates the concrete model and, therefore, it may perform sound and complete safety property checking, Linear Temporal Logic (LTL) [91] model checking, refinement checking upon the abstraction.

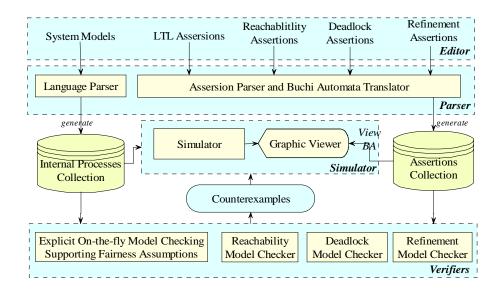

Figure 2.1 shows the architecture design of PAT with four components, namely the editor, the parser, the simulator and verifiers. The editor is featured with powerful text editing, syntax highlighting and multi-documents environment. The parser compiles the system models and the properties into internal representation. Due to infinite timed transitions, abstraction is applied to the input models so that a finite state abstract model is yielded internally. The simulator allows users to perform various simulation tasks on the models: complete states generation of execution graph, automatic simulation, user interactive simulation, trace replay and etc. The simulator is also used to visualize Büchi automata generated from the negation of LTL assertions. Most importantly, PAT implements several verifiers catering for checking deadlock-freeness, reachability, LTL properties with fairness assumptions [], refinement checking [23, 65] and etc. To achieve good performance, advanced optimization techniques are implemented, e.g., partial order reduction, process counter abstraction [100], parallel model checking [67], etc. All the verification algorithms perform on-the-fly exploration of the state space [110]. If any counterexample is identified during the exploration,

Figure 2.1: Architecture Design

then it can be animated in the simulator for the purpose of debugging. The correctness of PAT is established by using various test cases and user feedback. In additional, PAT is verified by performing model checking on its source code [93].

#### **Real-Time System Modeling in PAT**

In PAT, a system model is composed of multiple elements, i.e. constants, global variables/channels, a set of timed process definitions, a set of assertions, etc. The process definitions identify the computational logic of a system. A timed process P (hereafter process) can be defined using a rich set of process constructs (similar to CSP processes). Furthermore, a number of timed process constructs (similar to Timed CSP processes) can be used to capture common real-time system behavior patterns. For example, let d be an rational number. Process Wait[d] idles for d time units. In process P timeout[d] Q, the first observable event of P shall occur before d time units elapse. Otherwise, Q takes over control after exactly d time units elapse. Process P interrupt[d] Q behaves exactly as P(which may engage in multiple observable events) until d time units elapse, and then Q takes over control. Process P waituntil[d] is constrained to finish only after d time units have elapsed since the process starts. If P terminates early, then it idles until exactly dtime units have elapsed. Process P deadline[d] constrains P to terminate before d time units. In this setting, clock variables are made implicit and hence they cannot be compared with each other directly, which potentially allows efficient clock manipulation and hence system verification. In real-time systems, requirements are often structured into phases, which is hierarchical in nature [78]. PAT modeling language is hierarchical and uses implicit clocks, hence the modeling process is much simpler without complicated clock calculations. The complete language syntax can be found in PAT's user manual. The formal operational semantics can be found in [99].

#### Abstraction and Verification

Model checking requires a finite state system model. Hence, we assume that all variables have finite domains and the process forbids unbounded non-tail recursion. However, the number of system states (and hence the transition system) is still infinite because of our dense-time semantics. PAT adopts a zone abstraction [99] to build an abstract system. Different from zone abstraction applied to Timed Automata [21], PAT dynamically creates/deletes a set of clocks to precisely encode the timing requirements. A *zone* is the maximal set of clock valuations satisfying a set of primitive clock constraints. A primitive constraint on a clock is of the form  $tm \sim d$  where tm is a timer, d is a constant and  $\sim$  is  $\geq$ , =, or  $\leq$ . Because clocks are implicit, clock readings cannot be compared directly. In order to support efficient verification, PAT uses difference bound matrices (DBM) [21] as an equivalent representation for the zone.

To perform verification on the original systems, PAT shows that the abstract transition system is equivalent to the original transition system. It is shown that our zone abstraction is sound and complete with respect to the following three properties using a specialized bi-simulation relationship [99]. LTL Model Checking In this setting, the properties are linear temporal logic (LTL) formulae, constituted by propositions on global variables and events. Notice that no clocks are allowed in the property. In order to reflect model checking results on the abstract transition system to the original system with respect to LTL formulae, it is need to establish that the abstract transition system is equivalent to the concrete one with respect to LTL-X formulae. The idea is to show stutter equivalence between traces of the abstract system and the original system [99]. To verify the LTL formulae, PAT adopts the automata-based on-the-fly verification algorithm [96], i.e., by firstly translating a formula to a Büchi automaton and then check emptiness of the product of the system and the automaton.

**Refinement Checking** In this setting, PAT investigates an alternative verification approach. That is, to verify whether the system satisfies the property by showing a refinement relationship between the system and a model which models the property. In order to check refinement between two (timed) models, zone abstraction must be applied to both models. In [99], it proves that it is sound and complete to show stable failures refinement between the two abstraction transition systems in order to show failures refinement between the two corresponding original models. The refinement relationship is verified using an on-the-fly simulation checking approach.

# Chapter 3

# Encoding Timed CSP in CLP

Timed CSP is a powerful modeling language for real-time systems. However the verification support is limited. The first piece of work we have done is building a reasoning mechanism for Timed CSP. We choose CLP as the underlying reasoning support for Timed CSP, which can provide a simple and intuitive way of representing real timing aspects of Timed CSP and a flexible way of specifying interesting properties, such as deadlock-freeness, trace related properties, time related properties, and etc.

This chapter is organized as follows. In Section 3.1, we start with translating syntax of Timed CSP into CLP. Section 3.2 encodes the operational semantics of Timed CSP into CLP, by capturing both event transition and timed transition of every operator defined in Timed CSP (refer to Section 2.2). Section 3.3 encodes the denotational semantics of Timed CSP into CLP. In Section 3.4, we demonstrate how to verify the properties of the Timed CSP processes encoded in CLP based on the operational semantics. In Section 3.5, a prototype tool HORAE is developed to support the verification of the Timed CSP with the techniques we developed in this chapter. Section 3.6 demonstrate our approaches using three examples with experimental results. Section 3.7 concludes this chapter.

# 3.1 Timed CSP Specification in CLP

#### 3.1.1 Syntax Encoding

In this section, we show how to encode every operator of Timed CSP defined in Section 2.2 into CLP terms. All operators of the extended specification which inherited from Timed CSP are encoded into CLP rules in a compositional way. A translation library for all operators is built. For example:

- $a \rightarrow \text{SKIP}$  : eventprefix(a, skip)

- $a \xrightarrow{t} SKIP$  : delay(a, skip, t)

- $P_1 \mid\mid\mid P_2$ : interleaving(P1,P2)

- $P_1$ ;  $P_2$ : sequential(P1,P2)

In our library, eventprefix(A, P) is defined to denote a process  $A \to P$ . delay(A, P, T)is the CLP form of operator  $A \xrightarrow{T} P$  in Timed CSP. interleaving(P1, P2) is to represent operator  $P_1 \parallel P_2$  where P1 and P2 are the CLP formate of process  $P_1$  and  $P_2$ . Relations  $sequential/2^1$  is to represent a sequential operator ";". We define a library of rules for all Timed CSP processes in CLP, which is shown in Table 3.1.1.

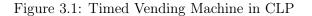

The very initial step of our work is the syntax encoding of Timed CSP process in CLP syntax, which can be automated easily by syntax rewriting. A relation of the form proc(N, P) is used to present a process P with name N. For instance, Figure 3.1 is the syntax encoding of process TVM (Example 2.2.1) in CLP, which is a recursive process with name tvm.

<sup>&</sup>lt;sup>1</sup>2 means predicate "sequential" has two parameters.

| Timed CSP Process                    | CLP presentation       |

|--------------------------------------|------------------------|

| Skip                                 | skip                   |

| Stop                                 | $\operatorname{stop}$  |

| Run                                  | run                    |

| $\mathbf{a} \to \mathbf{P}$          | eventprefix(a, P)      |

| $a \xrightarrow{t} P$                | delay(a, t, p)         |

| $P1 \square P2$                      | extchoice(P1, P2)      |

| $P1 \sqcap P2$                       | intchoice(P1, P2)      |

| P1 $_X   _Y$ P2                      | parallel(P1, P2, X, Y) |

| P1 $ [X] $ P2                        | parallel(P1, P2, X)    |

| P1     P2                            | interleave(P1, P2)     |

| P1; P2                               | sequential(P1, P2)     |

| P1 $\forall$ P2                      | interrupt(P1, P2)      |

| $P1 \stackrel{d}{\triangleright} P2$ | timeout(P1, P2, d)     |

| WAIT d                               | wait(d)                |

| P1 $\bigtriangledown_d$ P2           | tinterrupt(P1, P2, d)  |

| $\mu \ge P(X)$                       | recursion(P)           |

Table 3.1: Library of Timed CSP processes in CLP

### 3.1.2 Laws and Simplification

[89] introduces the concept of process equivalence  $P_1 = P_2$  when  $P_1 = _T P_2$ ,  $P_1 =_{SF} P_2$  and  $P_1 = FDIP_2$  hold.

A set of laws are defined associated with each operator, where some of them can be used for process simplification. For example,  $\Box$ -idem law  $P \Box P = P$ , which states that offering a choice between two copies of the same process is identical to the process itself, can simplify process  $P \Box P$  to P. A set of such laws are selected and implemented in the reasoning engine to fulfil this purpose, which are shown below.

$\begin{array}{l} proc(c1, delay(coffee, eventprefix(dispatchcoffee, tvm), 3)).\\ proc(c2, delay(tea, eventprefix(dispatchtea, tvm), 2)).\\ proc(c3, eventprefixc(reqrelease, delay(release, tvm, 2))).\\ proc(choices, extchoice(extchoice(C, T), R))\\ &: -proc(c1, C), proc(c2, T), proc(c3, R).\\ proc(to, timeout(C, eventprefix(release, tvm), 10))\\ &: -proc(choices, C).\\ proc(tvm, eventprefix(coin, tvm)))\\ &: -proc(to, P). \end{array}$

| $P \Box P = P$                                | $\langle \Box$ -idem $\rangle$                 |

|-----------------------------------------------|------------------------------------------------|

| $P_1 \Box P_2 = P_2 \Box P_1$                 | $\langle \Box$ -sym $\rangle$                  |

| $P \square \text{Stop} = P$                   | $\langle \Box$ - $unit \rangle$                |

| $P \sqcap P = P$                              | $\langle \sqcap -idem \rangle$                 |

| $P_1 \sqcap P_2 = P_2 \sqcap P_1$             | $\langle \Box -sym \rangle$                    |

| SKIP $_A   _B$ SKIP = SKIP                    | $\langle \ $ -term1 $\rangle$                  |

| $P_A   _A P = P$ if $\alpha(P) \subseteq A$   | $\langle \ $ -idem $\rangle$                   |

| SKIP $   $ SKIP = SKIP                        | $\langle    $ -term $1 \rangle$                |

| $P \parallel \parallel \text{Skip} = P$       | $\langle    $ - $unit \rangle$                 |

| $P_1 \mid\mid\mid P_2 = P_2 \mid\mid\mid P_1$ | $\langle    $ -sym $\rangle$                   |

| SKIP; $P = P$                                 | $\langle ; -unit - I \rangle$                  |

| $P; \text{ Skip} =_T P$                       | $\langle ; -unit - r_T \rangle$                |

| Stop; $P = $ Stop                             | $\langle ; -zero - I \rangle$                  |

| Stop $\forall P = P$                          | $\langle \nabla$ -unit-I $\rangle$             |

| $P \bigtriangledown \text{Stop} = P$          | $\langle \nabla \text{-}unit\text{-}r \rangle$ |

| $SKIP \lor P = SKIP \Box P$                   | $\langle \bigtriangledown$ -term $\rangle$     |

|                                               |                                                |

Laws for timed operators timeout  $P_1 \stackrel{d}{\triangleright} P_2$ , delay  $a \stackrel{d}{\rightarrow} P$ , wait WAIT and timed interrupt

$P_1 \bigtriangledown_d P_2$  as shown as follows.

| Stop $\stackrel{d}{\triangleright} Q_1 = \text{Wait } d; \ Q_1$                                                                                         | $\langle \triangleright - delay \rangle$              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| $Q_1 \stackrel{d}{\triangleright} (Q_2 \stackrel{d'}{\triangleright} Q_3) = (Q_1 \stackrel{d}{\triangleright} Q_2) \stackrel{d+d'}{\triangleright} Q_3$ | $\langle \triangleright \text{-}assoc \rangle$        |

| (WAIT $d; Q_1$ ) $\stackrel{d+d'}{\triangleright} Q_2$ ) = WAIT $d; (Q_1 \stackrel{d'}{\triangleright} Q_2)$                                            | $\left< \triangleright\text{-}delay\text{-}1 \right>$ |

| $(\text{WAIT}(d+d'); Q_1) \stackrel{d}{\triangleright} Q_2) = \text{WAIT} d; Q_2$                                                                       | $\langle \triangleright - delay - 2 \rangle$          |

| WAIT $d$ ; WAIT $d' = WAIT(d + d')$                                                                                                                     | $\langle delay\text{-}sum \rangle$                    |

| $a \stackrel{d}{\to} P = a \to \text{Wait} d; P$                                                                                                        | $\langle delay$ -prefix $\rangle$                     |

| (WAIT $d; Q_1$ ) $_A   _B$ (WAIT $d; Q_2$ ) = WAIT $d; (Q_1 _A   _B Q_2)$                                                                               | $\langle delay$ -  - $dist \rangle$                   |

| (WAIT $d; Q_1$ )     (WAIT $d; Q_2$ ) = WAIT $d; (Q_1     Q_2)$                                                                                         | $\langle delay$ -   - $dist \rangle$                  |

| (WAIT $d; Q_1$ ) $ [A] $ (WAIT $d; Q_2$ ) = WAIT $d; (Q_1   [A]   Q_2)$                                                                                 | $\langle delay -  [A]  - dist \rangle$                |

| $Q_1 \triangledown_d (Q_2 \triangledown_{d'} Q_3) = (Q_1 \triangledown_d Q_2) \triangledown_{d+d'} Q_3$                                                 | $\langle \nabla_d \text{-}assoc \rangle$              |

| STOP $\nabla_d P = \text{WAIT } d; \ Q_1$                                                                                                               | $\langle stop- \bigtriangledown_d - delay \rangle$    |

| $(\text{WAIT } d; \ Q_1) \ \nabla_{d+d'} \ Q_2) = \text{WAIT } d; \ (Q_1 \ \nabla_{d'} \ Q_2)$                                                          | $\langle \nabla \text{-} delay \text{-} 1 \rangle$    |

| $(\operatorname{WAIT}(d+d'); \ Q_1) \ \nabla_d \ Q_2) = \operatorname{WAIT} d; \ Q_2$                                                                   | $\langle \nabla - delay - 2 \rangle$                  |

For the purpose of simplification, we encode the laws described above into CLP clauses in a structured way. A CLP relation law(P, Q) is introduced to find the simplified version of process Q of P. law/2 rules for each operator are defined recursively which is illustrated as follows.

law(extchoice(P, P), P) : -!.law(extchoice(P, stop), P) : -!.law(extchoice(stop, P), P) : -!.law(intchoice(P, P), P) : -!.law(parallel(skip, skip, -), skip) : -!.law(parallel(P, P, A, B), P) : -setequal(A, B), !. $law(parallel(skip, skip, \_), skip) : -!.$  $law(parallel(P, P, \_), P) : -!.$ law(interleave(P, stop), P) : -!.law(interleave(stop, P), P) : -!.law(interleave(P, skip), P) : -!.law(interleave(skip, P), P) : -!.law(sequential(skip, P), P) : -!.law(sequential(P, skip), P) : -!. $law(sequential(stop, \_), stop) : -!.$ law(interrupt(stop, P), P) : -!.law(interrupt(P, stop), P) : -!.law(extchoice(P, Q), S) : -not(P = stop; Q = stop, P = Q),law(P, P1), law(Q, Q1), (P1 = P, Q1 = Q) >S = extchoice(P, Q); law(extchoice(P1, Q1), S), !.law(intchoice(P, Q), S) : -not(P = Q), law(P, P1), law(Q, Q1), $(P1 = P, Q1 = Q) \rightarrow S = intchoice(P, Q); law(intchoice(P1, Q1), S).$ law(parallel(P, Q, A, B), parallel(P, Q, A, B)) : not(P = skip, setequal(A, B)), !.law(parallel(P, Q, A, B), P) : -setequal(A, B), not(P = Q),law(P, P1), law(Q, Q1), (P1 = P, Q1 = Q)-> S = parallel(P, Q, A, B); law(parallel(P1, Q1, A, A), S).law(parallel(P, Q, A), S) : -not(P = Q), law(P, P1), law(Q, Q1),(P1 = P, Q1 = Q) - > S = parallel(P, Q, A); law(parallel(P1, Q1, ...), S).law(interleave(P, Q), S) : -not(P = skip; Q = skip),law(P, P1), law(Q, Q1), (P1 = P, Q1 = Q)-> S = interleave(P, Q); law(interleave(P1, Q1), S).law(sequential(P, Q), S) : -not(P = skip; P = stop; Q = skip),law(P, P1), law(Q, Q1), (P1 = P, Q1 = Q)-> S = sequential(P, Q); law(sequential(P1, Q1), S).law(interrupt(skip, P), extchoice(skip, P)) : -!.law(interrupt(P, Q), S) : -not(P = skip; P = stop; Q = stop),law(P, P1), law(Q, Q1), (P1 = P, Q1 = Q) $-> S = interrupt(P, Q); \ law(interrupt(P1, Q1), S).$

# 3.2 Modeling Operational Semantics of Timed CSP in CLP

Operational semantics provides a way of interpreting a language - of stepping through executions of programs written in that language. It therefore offers a direct intuition of how program constructs are intended to behave, in contrast with denotational semantics which often abstract away from such considerations, and with algebraic approaches, where operators are defined in terms of the algebraic laws when satisfy.

This section is devoted to an encoding of the semantics of Timed CSP in CLP. The practical implication is that we may then use powerful constraint solver like  $\text{CLP}(\mathcal{R})$  [55] to do various proving over systems modelled using Timed CSP. Both the operational semantics and denotational semantics are encoded. The encoding of operational semantics serves most of our purposes.

The operational semantics of Timed CSP is precisely defined by Schneider [90] using two relations: an evolution relation and a timed event transition relation. It is straightforward to verify that our encoding conforms the two relations in [90].

A relation of the form tos(P1, T1, E, P2, T2) is used to denote the timed operational semantics, by capturing both evolution relations and timed event transition relations. Predicate tos(P1, T1, E, P2, T2)is true if the process P1 may evolve to P2 through either a timed transition, i.e., let T2-T1 time units pass, or an event transition by engaging an abstract event instantly<sup>2</sup>. The relation tos defines a transition system interpretation of a Timed CSP process, where the state is identified by the combination of the process expression and the time variable. Using tabling mechanism offered in some of the constraint solvers like  $CLP(\mathcal{R})$  [55] or XSB [105], the termination of the derivation sequence based on relation tos depends on the finiteness of the reachable process expressions from the initial one. Therefore, if a process is irregular, proving of goals which need to explore all reachable process expressions is not feasible.

<sup>&</sup>lt;sup>2</sup>Or both at the same time by engaging an nontrivial action which takes time (necessary for only extensions to Timed CSP like TCOZ [74] where E could be a complicated computation)

However, even for irregular processes, interesting proving like existence of a trace is still possible.

We define the *tos* relation in terms of each and every operator of Timed CSP. For the moment, we assume the process is not parameterized and we shall handle parameterized processes uniformly in Section 3.3.1.

## 3.2.1 Primitive process

## STOP, SKIPand RUN

The operational semantics of the primitive process expressions in Timed CSP are defined through the following transitions:

$\frac{d}{SKIP} \xrightarrow{d} STOP$   $\frac{d}{SKIP} \xrightarrow{d} SKIP$

The rules associated with the SKIP, STOP and RUN processes are as the following: