# DESIGN OF A BROAD-BAND DISTRIBUTED AMPLIFIER AND DESIGN OF CMOS PASSIVE AND ACTIVE FILTERS

# DALPATADU K. RADIKE SAMANTHA

Beng (Hons), NUS

NATIONAL UNIVERSITY OF SINGAPORE

2011

# DESIGN OF A BROAD-BAND DISTRIBUTED AMPLIFIER AND DESIGN OF CMOS PASSIVE AND ACTIVE FILTERS

# DALPATADU K. RADIKE SAMANTHA

Beng (Hons), NUS

# A THESIS SUBMITTED

# FOR THE DEGREE OF MASTER OF ENGINEERING

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# NATIONAL UNIVERSITY OF SINGAPORE

2011

#### ACKNOWLEDGEMENTS

The work described in this thesis could not have been accomplished without the help and support of many individuals.

First of all I would like to give my deepest gratitude to my supervisor, Assistant Professor Koen Mouthaan, for his guidance and encouragement throughout the two years. He helped me to overcome difficult problems whenever I got stuck during this period of time. Other than the academic progress he also helped me in my personal growth during the past two years.

I would also like to thank Mdm Lee Siew Choo, Mdm Guo Lin and Mr Sing for their help in the fabrication and the measurement of the microwave circuits during the past two years. Also I would like to thank Mdm Zheng for her technical support.

I am also thankful to all the friends in the MMIC lab who helped me during the last two years. I am truly grateful to Li Yong Fu, Hu Zijie, Azadeh Taslimi and Hu Feng for their help and technical support at various stages of the project. Also I would like to thank my brother Sandun Dalpatadu for providing support during the thesis writing.

Last but not the least I wish to thank my parents for bringing me up and for their forever love. I have always been learning to be more kind-hearted, patient, and optimistic from them.

# TABLE OF CONTENTS

| CHAPTER 1: Introduction1 |                                                                |  |

|--------------------------|----------------------------------------------------------------|--|

| 1.1                      | Broad-Band Amplifiers for RF Communication Systems1            |  |

| 1.2                      | Broadband Amplification Techniques                             |  |

| 1.2.1                    | Reactively matched circuit                                     |  |

| 1.2.2                    | Feedback Amplifier Configuration                               |  |

| 1.2.3                    | Lossy Matched Amplifier Circuit                                |  |

| 1.2.4                    | Distributed Amplifier Circuit5                                 |  |

| 1.3                      | CMOS Technology for RF and Microwave Applications7             |  |

| 1.4                      | Motivation, Scope and Thesis Organization                      |  |

| CHAPTI                   | ER 2: Distributed Amplification Technique11                    |  |

| 2.1                      | Introduction11                                                 |  |

| 2.2                      | Gain Bandwidth Product of an Amplifier12                       |  |

| 2.3                      | Principle of Distributed Amplification                         |  |

| 2.3.1                    | Power Performance of a Distributed Amplifier17                 |  |

| 2.3.2                    | Noise Performance of Distributed Amplifiers                    |  |

| 2.3.3                    | Stability of Distributed Amplifiers                            |  |

| 2.4                      | Theoretical Analysis on Distributed Amplifiers                 |  |

| 2.4.1                    | Amplifier with periodically loaded transmission lines          |  |

| 2.4.2                    | Analysis of a distributed amplifier with discrete inductors    |  |

| 2.4.3                    | Cascaded four-ports formulation                                |  |

| 2.5                      | Effect of FET Parasitics on Distributed Amplifier Performances |  |

| 2.5.1                    | Effect of Gate-to-Source Capacitance                           |  |

| 2.5.2                    | Effect of Series Resistance $R_i$ when $C_{gs} = 100$ fF       |  |

| 2.5.3                    | Effect of Series Resistance $R_i$ when $C_{gs} = 200$ fF       |  |

| 2.5.4                    | Effect of gate-to-drain capacitance when $C_{gs} = 10$ fF      |  |

| 2.5.  | 5 Effect of Drain-to-Source Capacitance when $C_{gs} = 10$ fF and $C_{gd} = 1.5$ fF |    |

|-------|-------------------------------------------------------------------------------------|----|

| 2.6   | Conclusions and Recommendations                                                     |    |

| СНАРТ | TER 3: TRL Calibration and Measurement                                              |    |

| 3.1   | Introduction                                                                        |    |

| 3.2   | S – Parameter measurement                                                           |    |

| 3.2.  | 1 Vector Network Analyzer                                                           |    |

| 3.2.  | 2 TRL ( <b>T</b> HRU – <b>R</b> FLECT – <b>L</b> INE) Calibration                   |    |

| 3.3   | Measurement of Active and Passive devices                                           | 47 |

| 3.3.  | 1 Measurement of the transistor                                                     | 47 |

| 3.3.  | 2 Measurement of the passive devices                                                |    |

| 3.4   | Conclusions and Recommendations                                                     |    |

| СНАРТ | TER 4: Design of a Distributed Amplifier                                            |    |

| 4.1   | Introduction                                                                        | 53 |

| 4.2   | Circuit Realization                                                                 | 54 |

| 4.2.  | 1 Bends, Meander Lines and T-Junctions                                              |    |

| 4.2.  | 2 Stability Analysis                                                                |    |

| 4.2.  | 3 Schematic Design and Simulation                                                   | 56 |

| 4.2.  | 4 Electromagnetic Simulation Results                                                | 60 |

| 4.3   | Measurement and Discussion                                                          | 62 |

| 4.3.  | 1 DC Measurement and Check for Oscillations                                         | 62 |

| 4.3.  | 2 S – Parameter Measurement Results                                                 | 63 |

| 4.3.  | 3 Input 1-dB Compression point of the amplifier                                     | 69 |

| 4.4   | Conclusions and Recommendations                                                     | 69 |

| СНАРТ | TER 5: CMOS Active Filter Design                                                    |    |

| 5.1   | Introduction                                                                        | 71 |

| 5.2   | Microwave transversal Filtering                                                     | 72 |

|   | 5.3   | Design of a CMOS lumped and transversal element filter | 75  |

|---|-------|--------------------------------------------------------|-----|

|   | 5.3.  | 1 Filter Schematic Design                              | 75  |

|   | 5.3.2 | 2 Schematic Simulation Results                         | 77  |

|   | 5.3.3 | 3 Gain Compression of the Filter                       | 79  |

|   | 5.3.4 | 4 Monte-Carlo Simulation Results                       | 80  |

|   | 5.4   | Layout Design and Post Layout Simulation Results       |     |

|   | 5.4.  | 1 Standard 0.13 µm CMOS process                        | 80  |

|   | 5.4.2 | 2 Layout Design                                        |     |

|   | 5.4.3 | 3 Post Layout Simulation                               | 84  |

|   | 5.5   | Measurement Results                                    |     |

|   | 5.6   | Conclusions                                            |     |

| ( | СНАРТ | ER 6: Microwave CMOS Passive Filter Design             | 90  |

|   | 6.1   | Introduction                                           | 90  |

|   | 6.2   | CMOS Lumped Element Filter Design                      | 91  |

|   | 6.3   | Filter Design                                          | 92  |

|   | 6.3.  | 1 Calculation of Filter Element Values                 | 92  |

|   | 6.3.2 | 2 CMOS MIM Capacitor Design                            | 96  |

|   | 6.3.3 | 3 Filter Layout Design                                 | 97  |

|   | 6.4   | Conclusions                                            |     |

| ( | СНАРТ | ER 7: Conclusions and Recommendations                  | 103 |

|   | 7.1   | Distributed Amplifier Design                           |     |

|   | 7.2   | CMOS Active and Passive Filter Design                  |     |

|   |       | Appendix A                                             |     |

|   |       | Appendix B                                             | 115 |

### Summary

Broadband amplifiers are an important component in multiband radio systems and in optical receiver systems. Out of many existing topologies, the distributed amplification technique is an ingenious way of obtaining high bandwidths even greater than 100 GHz with good gain and return loss. Out of the two parts of this thesis, the first part addresses the design and implementation of a distributed amplifier on PCB. The concept of distributed amplification was deeply investigated and some of the limitations which degraded the performance of such amplifiers have been presented. The designed amplifier has a bandwidth of more than 3.0 GHz with a return loss better than 15 dB and a gain of 15 dB. Several issues encountered during design and measurement have also been addressed.

The second part of this thesis is mainly concerned with the design of CMOS passive and active filters. Due to the lossy nature of the silicon substrate the design of filters with a good return loss and a good pass band rejection is a challenge. The first design of the second project is related to the design of an active filter in 2-4 GHz. The proposed topology is based on lumped and transversal element filter topology, in which transversal elements are used to compensate the losses due to the substrate. In addition, these transversal elements are also used to improve the pass band rejection of the filter.

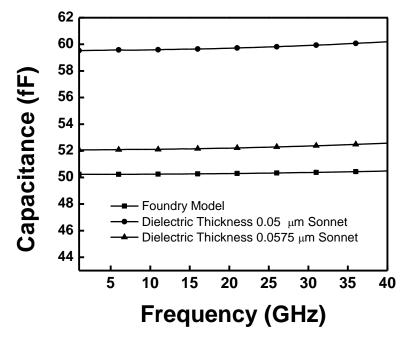

The second design addresses the design of a microwave passive filter at a centre frequency of 27.5 GHz. The proposed topology is based on the inverse Chebyshev filter prototype elements, in which inductors are designed using simple transmission lines. MIM capacitors are used to obtain the necessary capacitance values and, due to the inaccuracies of foundry provided models, capacitors were simulated in Sonnet EM simulator. The designed filter has a bandwidth of 7% at a centre frequency 27.5 GHz and a return loss of 8 dB.

# LIST OF TABLES

| Table 3.1: Calculated length of the TRL calibration kit                          | 44 |

|----------------------------------------------------------------------------------|----|

| Table 4.1: Amplifier Design Specifications                                       | 56 |

| Table 4.2: Optimized lengths and widths of gate and drain lines of the amplifier | 57 |

| Table 5.1: Active filter specifications                                          | 75 |

| Table 5.2: 8th Order Chebyshev filter element values                             | 75 |

| Table 5.3: Low pass and high pass element values                                 | 76 |

| Table 6.1: Passive filter design specifications                                  | 92 |

| Table 6.2: Element values for the band pass filter structure                     | 94 |

| Table 6.3: Series parallel section element values                                | 95 |

# LIST OF FIGURES

| Fig. 1.1 Multi-band and software defined radio systems.                                                         | 2   |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Fig. 1.2 Fibre optic receiver system.                                                                           | 3   |

| Fig. 1.3 Reactively matched amplifier.                                                                          | 3   |

| Fig. 1.4 Feedback amplifier                                                                                     | 4   |

| Fig. 1.5 Lossy matched amplifier circuit                                                                        | 5   |

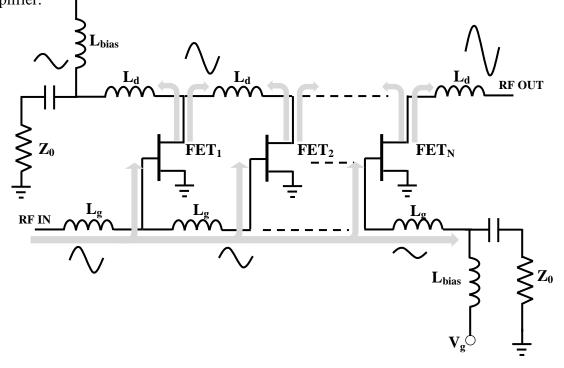

| Fig. 1.6 Schematic diagram of a distributed amplifier circuit                                                   | 6   |

| Fig. 1.7 Microwave transversal filter circuit.                                                                  | 8   |

| Fig. 2.1 Simple band pass amplifier structure.                                                                  | .12 |

| Fig. 2.2 Schematic representation of a FET distributed amplifier                                                | .13 |

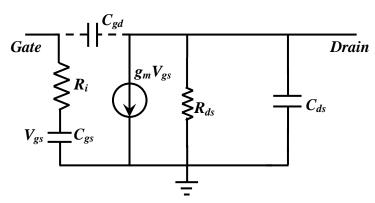

| Fig. 2.3 Small signal equivalent circuit of a FET                                                               | .14 |

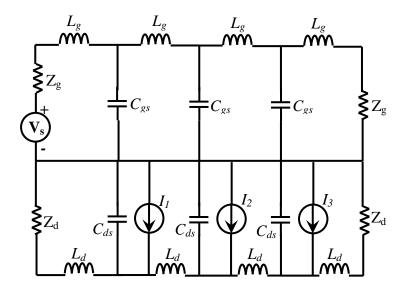

| Fig. 2.4 Equivalent circuit of a distributed amplifier.                                                         | .14 |

| Fig. 2.5 Schematic diagram of a traveling wave amplifier.                                                       | .17 |

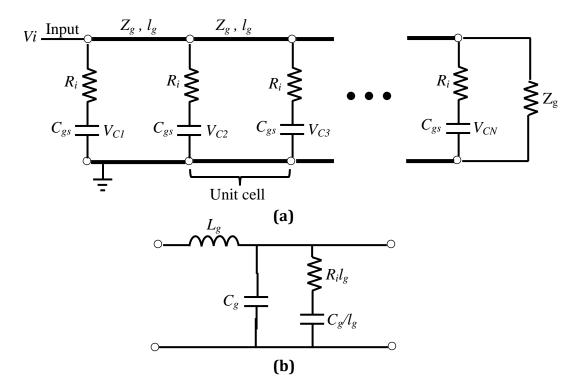

| Fig. 2.6 Equivalent circuit of (a) gate line; (b) single unit cell of the gate line                             | .20 |

| Fig. 2.7 Equivalent circuit of (a) drain line; (b) single unit cell of the drain line                           | .20 |

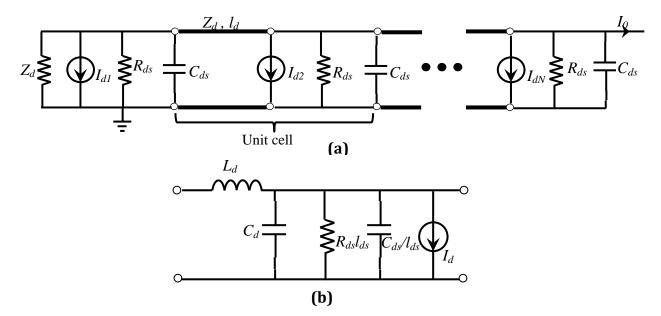

| Fig. 2.8 Equivalent circuit of a DA with discrete components (a) gate line; (b) drain line.                     | .25 |

| Fig. 2.9 A cross section of the distributed amplifier circuit                                                   | .28 |

| Fig. 2.10 Internal components of the four ports                                                                 | .28 |

| Fig. 2.11 Individual components of the four port section (a) Transmission lines; (b) Y                          |     |

| parameters of the FET; (c) transmission lines                                                                   | .29 |

| Fig. 2.12 Small signal equivalent circuit of a FET                                                              | .31 |

| Fig. 2.13 Effect of gate-to-source capacitance (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB); (c) $ S_{22} $ (dB)    | .32 |

| Fig. 2.14 Effect of Series Resistance $R_i$ when $C_{gs} = 100$ fF (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB);    |     |

| (c) $ S_{22} $ (dB)                                                                                             | .33 |

| Fig. 2.15 Effect of Series Resistance $R_i$ when $C_{gs} = 200$ fF (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB);    |     |

| (c) $ S_{22} $ (dB)                                                                                             | .34 |

| Fig. 2.16 Effect of gate-to-drain capacitance when $C_{gs} = 10$ fF (a) $ S_{21} $ (dB); (b) $ S_{12} $ (dB)    | );  |

| (c) $ S_{11} $ (dB); $ S_{22} $ (dB)                                                                            | .35 |

| Fig. 2.17 Effect of Drain-to-Source Capacitance when $C_{gs} = 10$ fF and $C_{gd} = 1.5$ fF (a)  S <sub>2</sub> | 21  |

| (dB); (b) $ S_{12} $ (dB); (c) $ S_{11} $ (dB); (d) $ S_{22} $ (dB)                                             | .36 |

| Fig. 3.1 Block diagram of a N-port vector network analyzer [59]                                                 | .39 |

| Fig. 3.2 Microstrip test fixture structure                                                                      | .41 |

| Fig. 3.3 THRU standard.                                                                                         | .41 |

| Fig. 3.4 REFLECT standard                                                                             | 42  |

|-------------------------------------------------------------------------------------------------------|-----|

| Fig. 3.5 LINE standard.                                                                               | 42  |

| Fig. 3.6 Substrate definition                                                                         | 43  |

| Fig. 3.7 Fabricated TRL calibration kit.                                                              | 45  |

| Fig. 3.8 S-parameters of the THRU standard (a) $ S_{21} $ (dB); $ S_{12} $ (dB); (c) $ S_{11} $ (dB); |     |

| (d)  S <sub>22</sub>   (dB).                                                                          | 46  |

| Fig. 3.9 S-parameters of the THRU line with bias tees (a) $ S_{21} $ (dB); (b) $ S_{12} $ (dB);       |     |

| (c) $S_{11} $ (dB); (d) $ S_{22} $ (dB)                                                               | 47  |

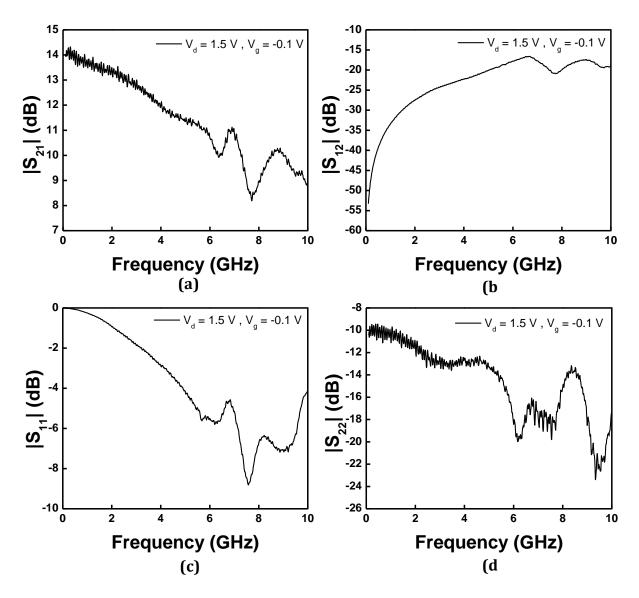

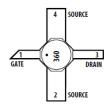

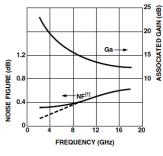

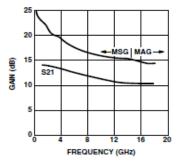

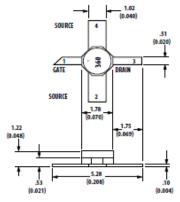

| Fig. 3.10 Measured S-parameters of the ATF-36077 transistor (a) $ S_{21} $ (dB); (b) $ S_{12} $ (dB   | ;); |

| (c) $ S_{11} $ (dB); (d) $ S_{22} $ (dB)                                                              | 48  |

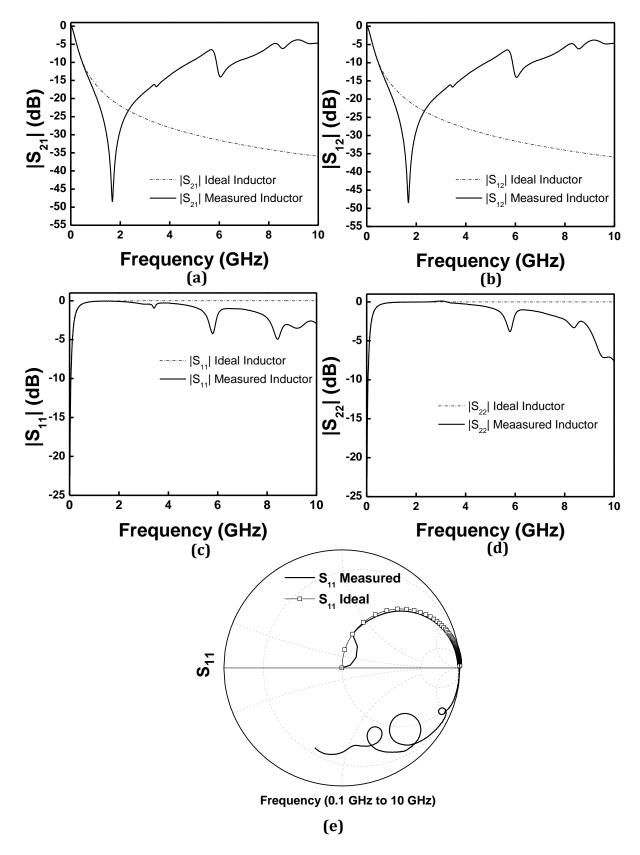

| Fig. 3.11 Measured S-parameters of a 100 nH Inductor (a) $ S_{21} (dB)$ ; (b) $ S_{12} (dB)$ ;        |     |

| (c) $ S_{11} $ (dB); (d) $ S_{22} $ (dB); (e) $ S_{11} $ Smith chart.                                 | 49  |

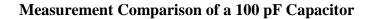

| Fig. 3.12 Measured S-parameters of a 100 pF Capacitor (a) $ S_{21} $ (dB); (b) $ S_{12} $ (dB);       |     |

| (c) $ S_{11} $ (dB); (d) $ S_{22} $ (dB); (e) $ S_{11} $ Smith chart.                                 | 50  |

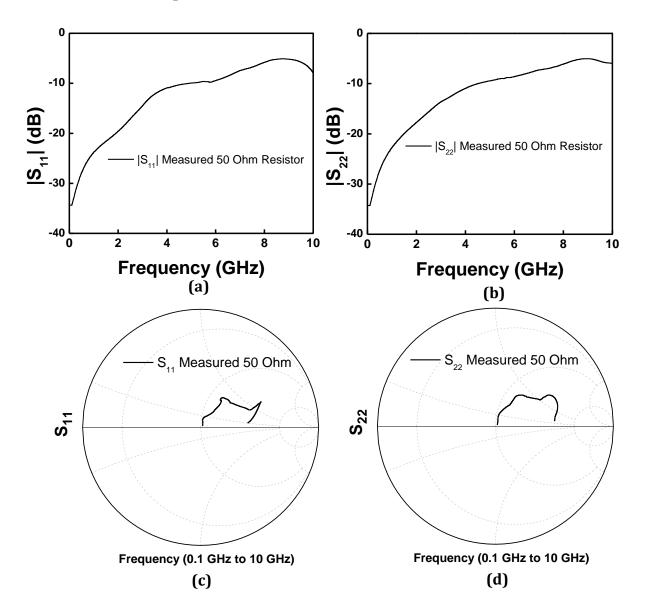

| Fig. 3.13 S-parameter measurement of a 50 Ohm resistor (a) $ S_{11} $ (dB); (b) $ S_{22} $ (dB);      |     |

| (c) $ S_{11} $ Smith Chart; (d) $ S_{22} $ Smith Chart.                                               | 51  |

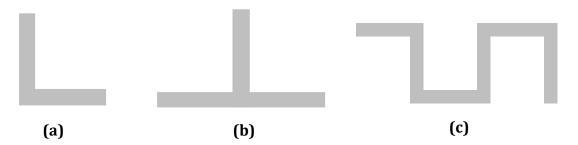

| Fig. 4.1 Microstrip discontinuities (a) Bend; (b) T - junction; (c) Meander line                      | 54  |

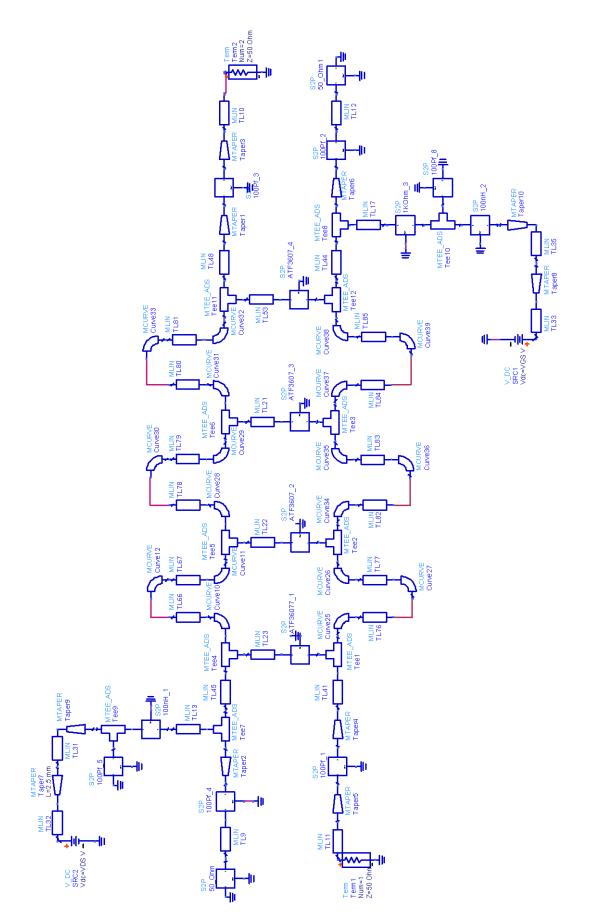

| Fig. 4.2 Schematic Diagram of the amplifier                                                           | 58  |

| Fig. 4.3 Schematic simulation results of the amplifier                                                | 59  |

| Fig. 4.4 Layout of the distributed amplifier.                                                         | 60  |

| Fig. 4.5 Comparison between schematic simulation and EM simulation.                                   | 61  |

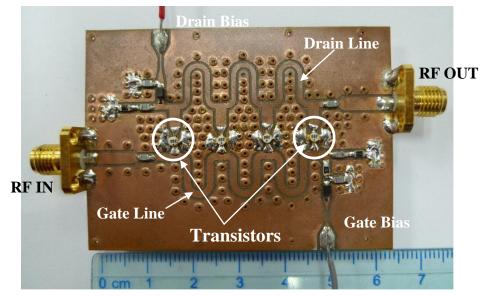

| Fig. 4.6 Fabricated amplifier                                                                         | 62  |

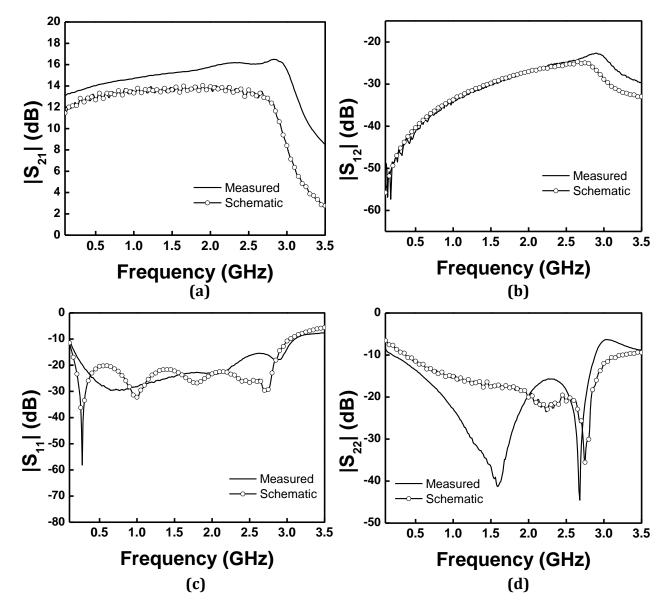

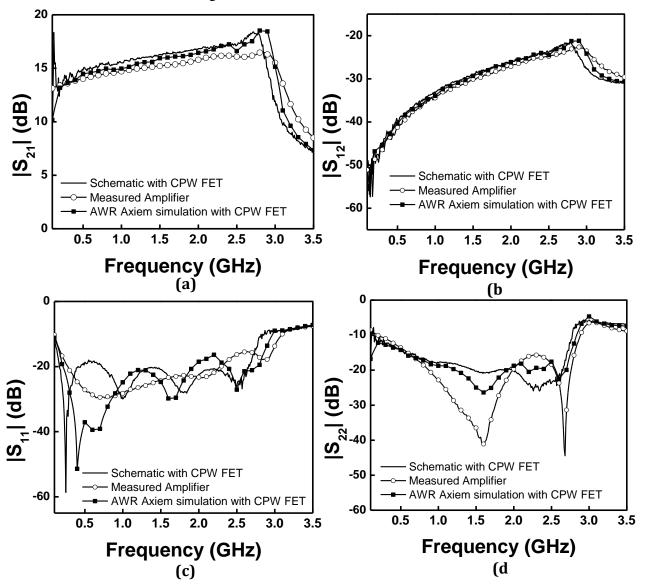

| Fig. 4.7 Measured and simulated S –parameters                                                         | 63  |

| Fig. 4.8 Comparison between measured S-parameters of the transistor using                             |     |

| Agilent VNA and R&S VNA                                                                               | 64  |

| Fig. 4.9 Comparison between measurement and schematic simulations using transistor                    |     |

| measured in HP VNA                                                                                    | 65  |

| Fig. 4.10 S-parameter measurement results for different input power levels                            | 67  |

| Fig. 4.11 Fabricated TRL calibration kit with CPW.                                                    | 68  |

| Fig. 4.12 S-parameter comparison between the measured amplifier and the simulations                   |     |

| conducted using the transistor measured with the CPW calibration kit                                  | 68  |

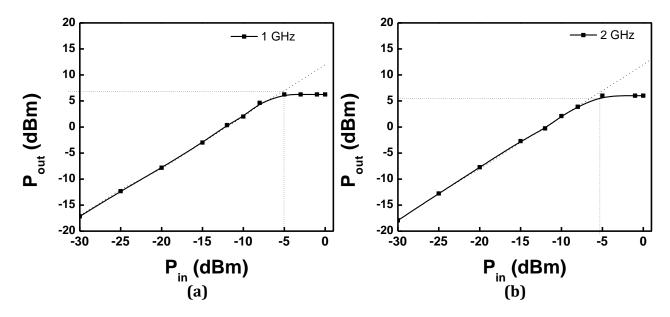

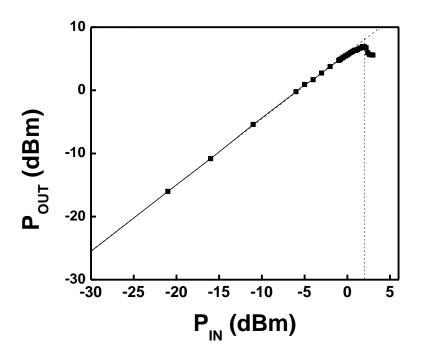

| Fig. 4.13 Measured input 1dB compression point (a) 1 GHz; (b) 2 GHz.                                  | 69  |

| Fig. 5.1 Digital transversal filtering.                                                               | 72  |

| Fig. 5.2 Typical microwave transversal filter structure                                               | 73  |

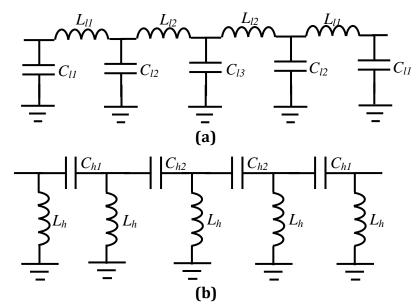

| Fig. 5.3 Microwave lumped and transversal element filter topology                                               | 74  |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.4 (a) Low pass filter; (b) High pass filter                                                              | 76  |

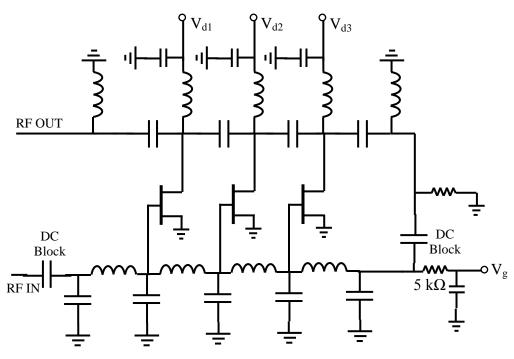

| Fig. 5.5 Schematic diagram of the designed filter                                                               | 78  |

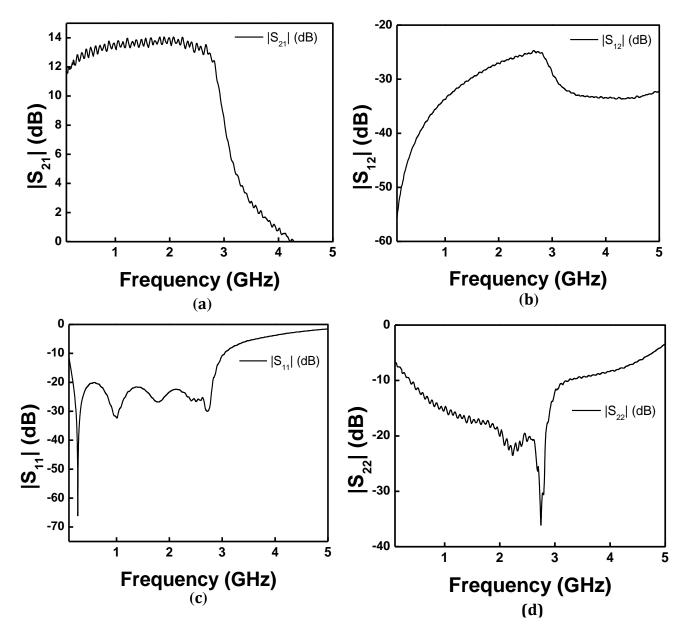

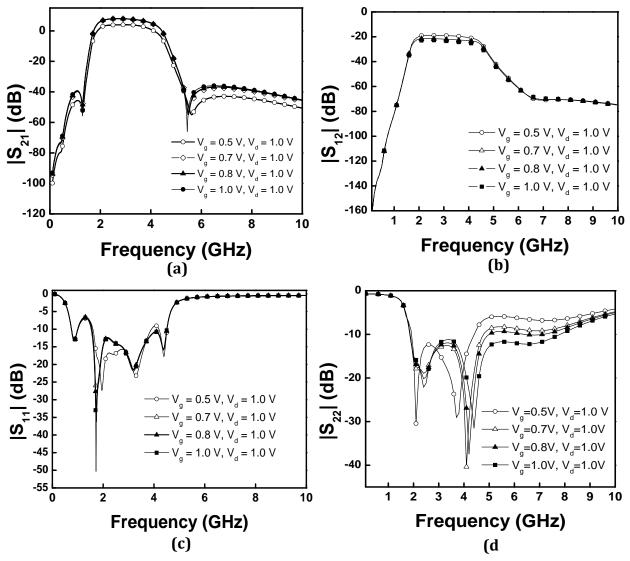

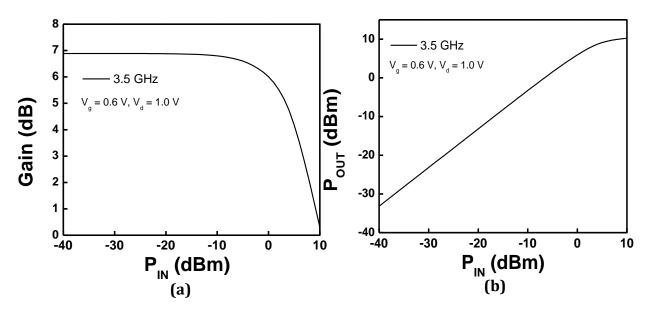

| Fig. 5.6 Simulation results (a) $ S_{21} $ (dB); (b) $ S_{12} $ (dB); (c) $ S_{11} $ (dB); (d) $ S_{22} $ (dB); |     |

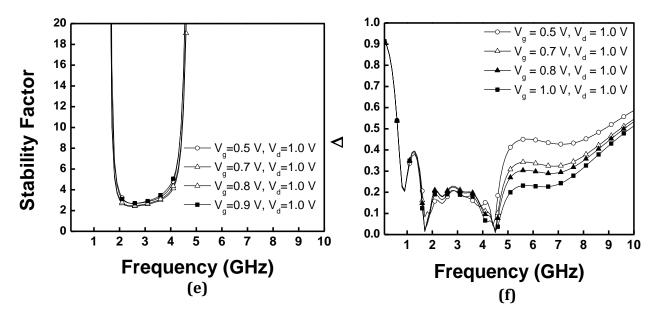

| (e) Stability factor K; (f) Delta factor                                                                        | 79  |

| Fig. 5.7 (a) Gain VS input power; (b) Output power VS Input power                                               | 79  |

| Fig. 5.8 Monte Carlo simulation (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB)                                        | 80  |

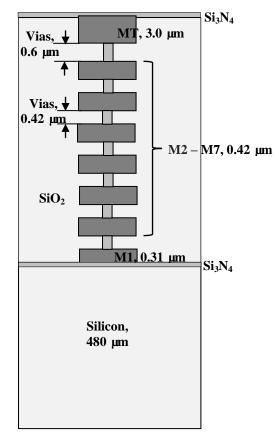

| Fig. 5.9 CMOS 0.13-um layer configuration                                                                       | 81  |

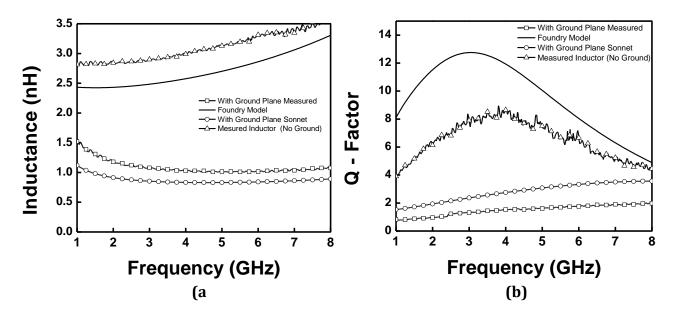

| Fig. 5.10 Effect of ground plane on (a) Inductance; (b) Q factor                                                | 82  |

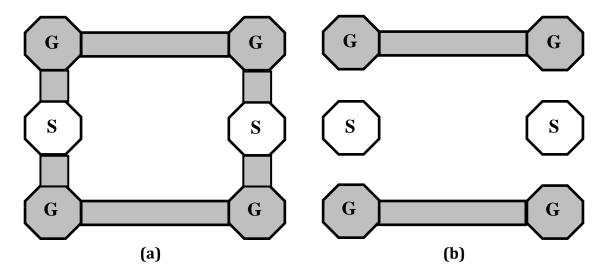

| Fig. 5.11 Pad de-embedding (a) Short; (b) Open                                                                  | 82  |

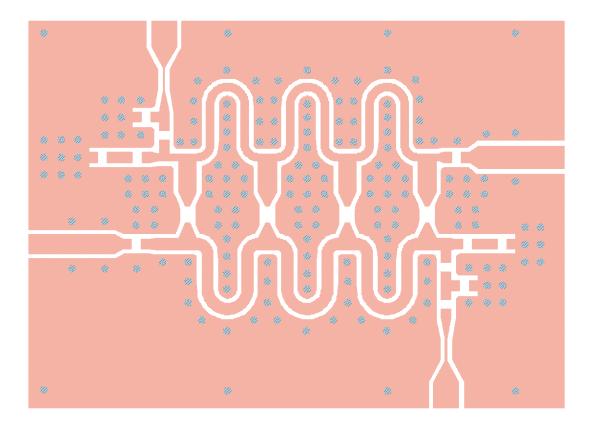

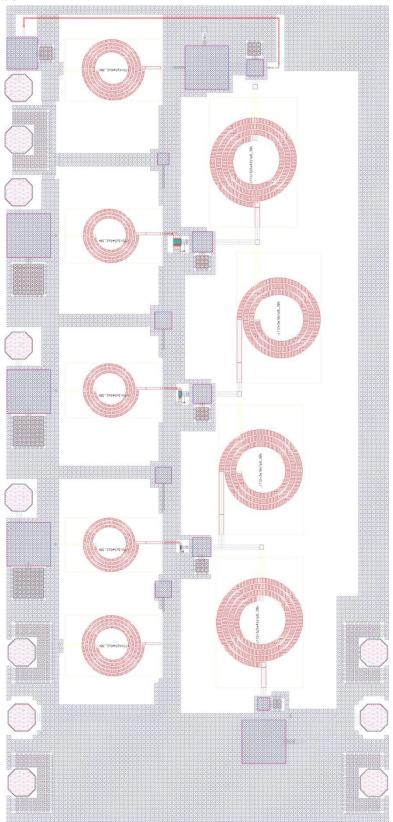

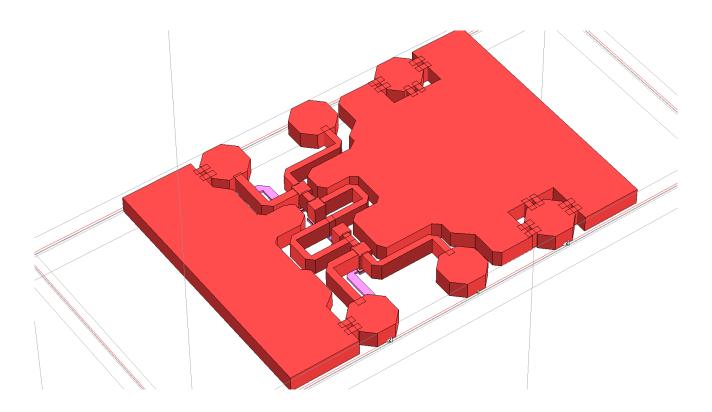

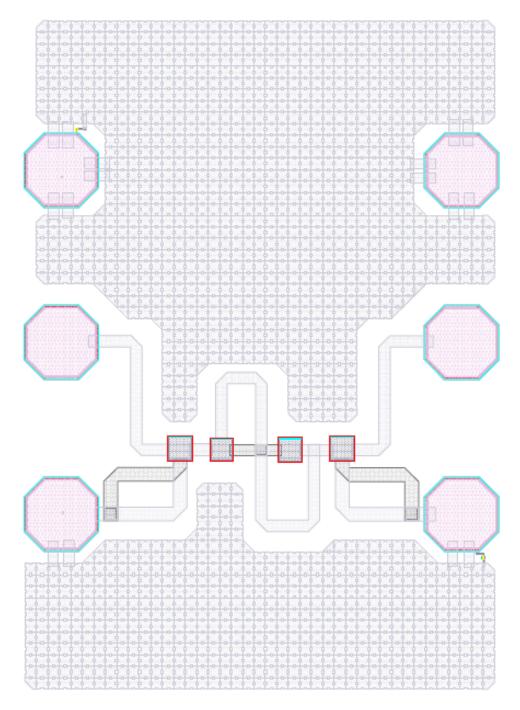

| Fig. 5.12 Layout of the designed filter                                                                         | 83  |

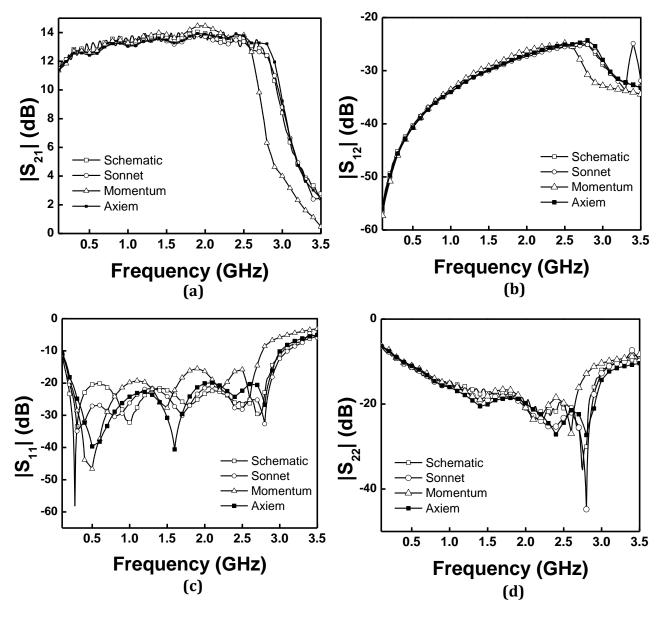

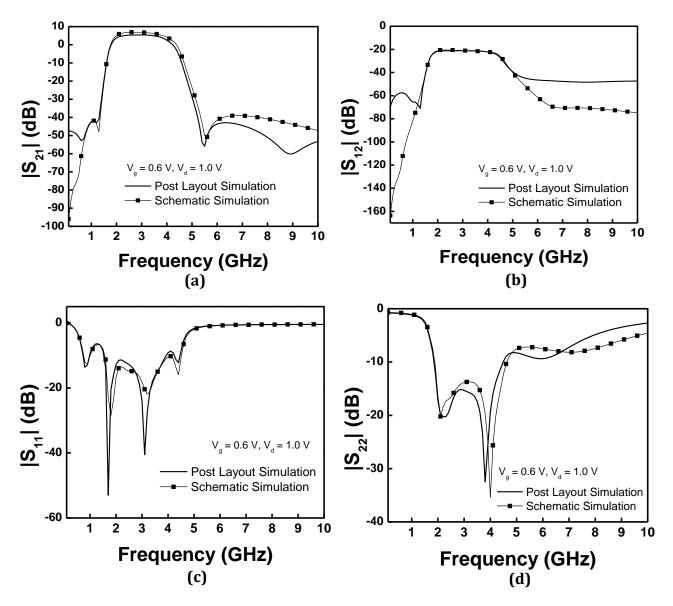

| Fig. 5.13 Schematic simulation VS post layout simulation (a) $ S_{21} $ (dB); (b) $ S_{12} $ (dB);              | (c) |

| $ S_{11} $ (dB); (d) $ S_{22} $ (dB)                                                                            | 84  |

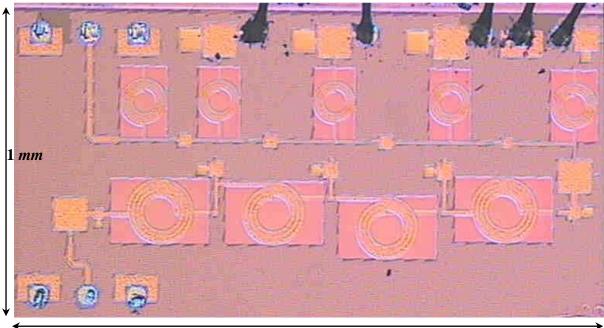

| Fig. 5.14 Fabricated filter                                                                                     | 85  |

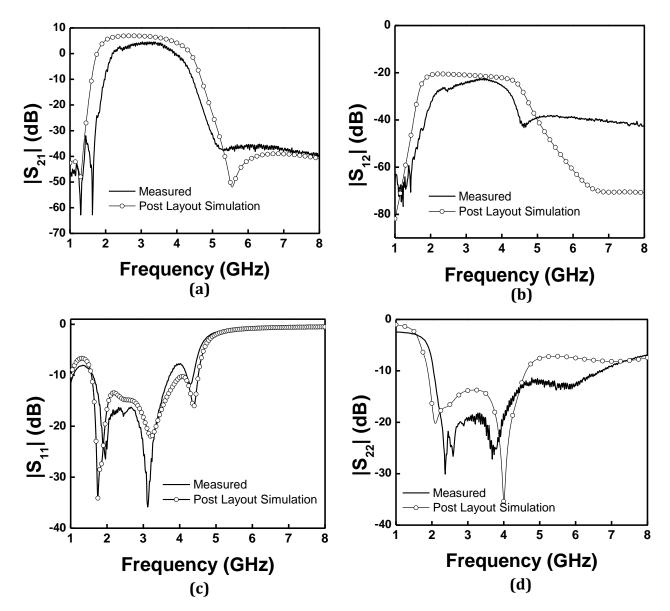

| Fig. 5.15 Measured first IC (a) $ S_{11} $ (dB) (b) $ S_{12} $ (dB) (c) $ S_{11} $ (dB) (d) $ S_{22} $ (dB)     | 86  |

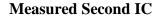

| Fig. 5.16 Measured second IC                                                                                    | 87  |

| Fig. 5.17 Measured input 1 dB compression point                                                                 | 88  |

| Fig. 6.1 Low pass inverse Chebyshev filter structure.                                                           | 92  |

| Fig. 6.2 Low pass to band pass conversion.                                                                      | 93  |

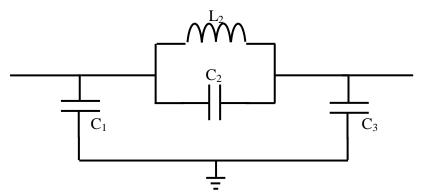

| Fig. 6.3 Band pass filter structure                                                                             | 94  |

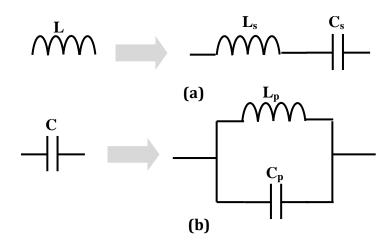

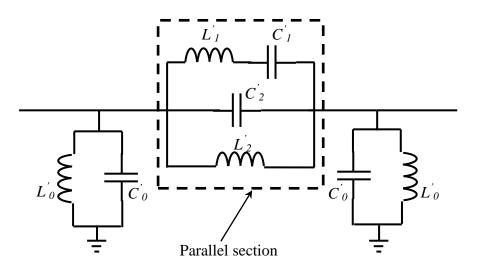

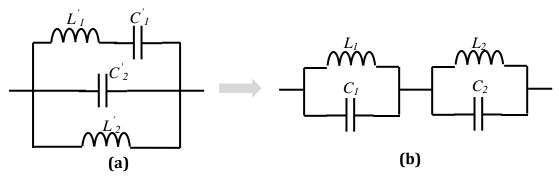

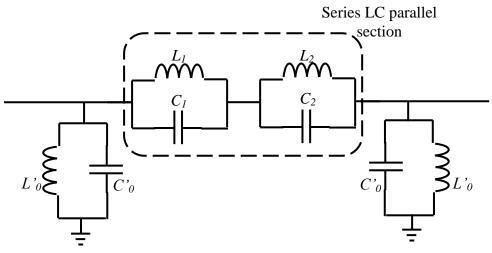

| Fig. 6.4 Conversion of parallel section in to two series parallel sections                                      | 95  |

| Fig. 6.5 Final inverse Chebyshev band pass filter structure                                                     | 95  |

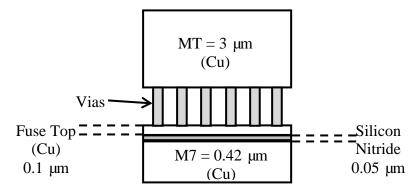

| Fig. 6.6 Cross section view of an MIM capacitor structure                                                       | 96  |

| Fig. 6.7 Comparison between MIM capacitor foundry model with Sonnet simulation                                  | 97  |

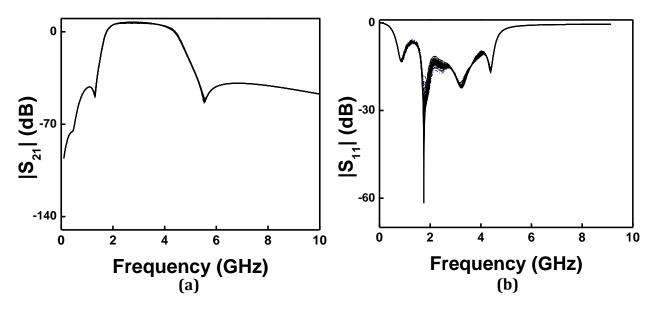

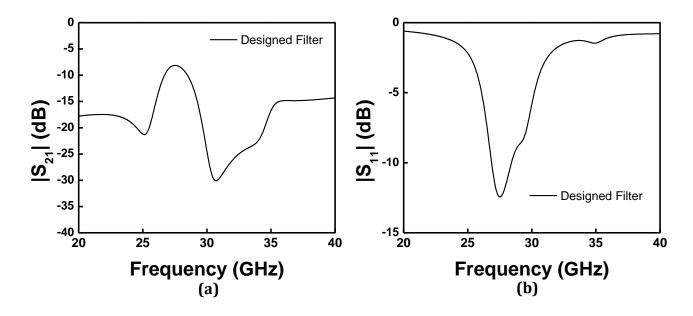

| Fig. 6.8 Sonnet simulation results (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB).                                    | 98  |

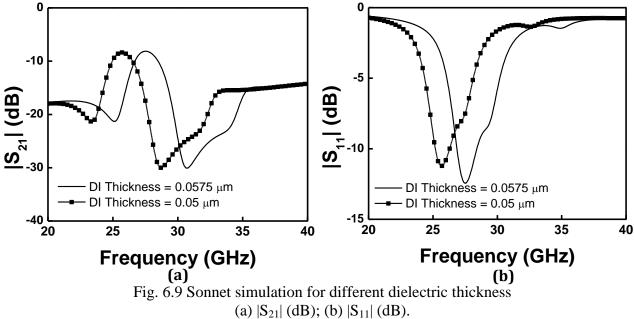

| Fig. 6.9 Sonnet simulation for different dielectric thickness                                                   |     |

| (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB).                                                                       | 98  |

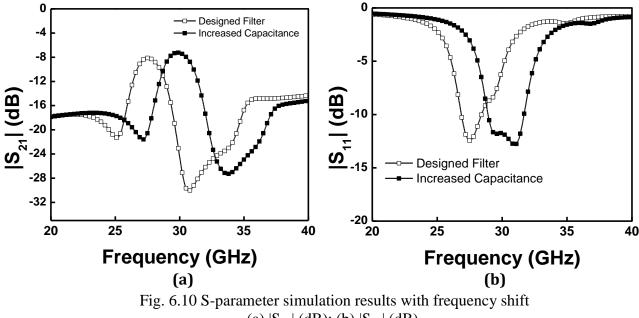

| Fig. 6.10 S-parameter simulation results with frequency shift                                                   |     |

| (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB).                                                                       | 99  |

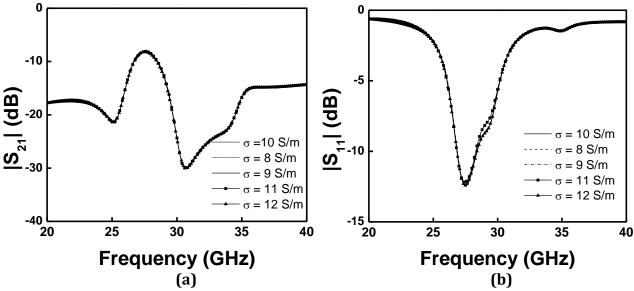

| Fig. 6.11 S-parameter simulation results of different substrate conductivities                                  |     |

| (a) $ S_{21} $ (dB); (b) $ S_{11} $ (dB).                                                                       | 99  |

| Fig. 6.12 3D view of the designed filter                                                                        | 100 |

| Fig. 6.13 Layout of the lumped element filter                                                                   | 101 |

Х

## CHAPTER 1

### Introduction

### 1.1 Broad-Band Amplifiers for RF Communication Systems

Broadband amplifiers are one of the main building blocks in modern communication systems. Some of the applications that employ broadband amplifiers include electronic warfare, radar and high-data-rate fibre optic communication systems. The interest for this type of devices has grown rapidly due to the availability of various mobile communication standards and increasing demand for high data rate communication systems.

As various mobile communication standards are available, it is important to develop mobile terminals that can be used as multi-mode transceivers. One main solution for realizing multi-mode mobile communication standards is the "software defined radio architecture" [1].

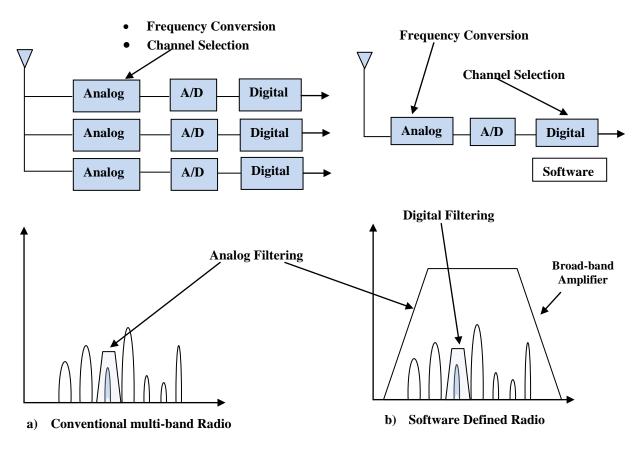

Fig 1.1 shows a comparison between the conventional multi-band radio systems and software defined radio systems. In the conventional multi-band radio architecture of Fig 1.1 (a), each standard consists of one receiver chain. Each receiver chain selects the channel according to the required carrier frequency. The analog section consists of fixed analog filters which select corresponding the carrier frequency and bandwidth. In software defined radio systems the received signal is first fed into a broadband amplifier. Next, the channels

are converted to the digital domain using a high speed A/D converter. The desired channel is next selected with the software defined channel selection filters in the digital domain. Hence, broadband amplifiers play a key role in software defined radio architectures.

Fig. 1.1 Multi-band and software defined radio systems.

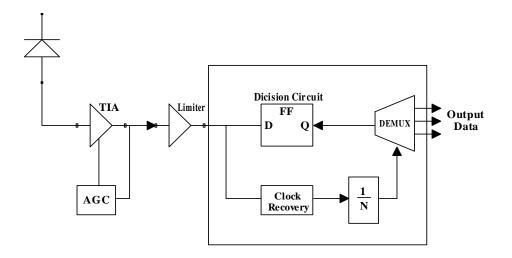

In optical communication systems the carrier frequency is around 200 THz, with high speeds of data transfer. Fig 1.2 shows a fiber optic receiver system. In such a system, optical signals are converted to electrical signals by using a photodetector. Converted signals are amplified by a TIA (Trans-Impedance Amplifier), which is a broadband amplifier.

Fig. 1.2 Fibre optic receiver system.

# 1.2 Broadband Amplification Techniques

To realize a broad bandwidth amplifier, conventional narrowband matching techniques are not suitable. Hence, special techniques need to be incorporated in order to achieve wide bandwidths. Some of the well-established techniques are:

- Reactively matched circuit;

- Feedback circuit;

- Lossy matched circuit;

- Distributed amplifier circuit;

### 1.2.1 Reactively matched circuit

This is also known as the lossless matched amplifier due to the reactively matched input and output circuit. Fig 1.3 shows a block diagram of a conventional reactively matched amplifier [2].

Fig. 1.3 Reactively matched amplifier.

The matching circuit in this topology uses gain compensation by creating reflections between the matching circuits and the FET. In this topology the poor impedance matching is a disadvantage. The first reactively matched circuit was reported in 1981 by Tserng, et al. [3]. He was able to achieve a bandwidth of 16 GHz from 2 - 18 GHz with a gain of 5 dB. However, the return loss is less than 10 dB throughout the bandwidth.

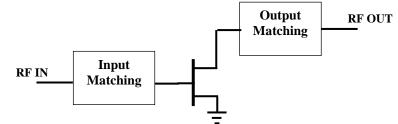

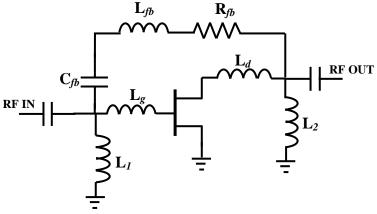

#### 1.2.2 Feedback Amplifier Configuration

Figure 1.4 shows the circuit diagram of a feedback amplifier. In this circuit, a shunt feedback is incorporated between gate and the drain in-order to obtain a broader bandwidth. This feedback contains three elements. The value of the resistor  $R_{fb}$  controls the gain of the amplifier. Gate inductance  $L_g$ , drain inductance  $L_d$ , and feedback inductance  $L_{fb}$  controls the bandwidth of the amplifier [4]. The capacitance  $C_{fb}$  acts as a DC block from the drain biasing.

Fig. 1.4 Feedback amplifier

Some of the advantages of this topology include: less complexity, ability to provide higher power added efficiency, flat gain and better stability. The main disadvantage of this configuration is the poor noise figure due to the feedback resistance used. Also, it is very sensitive to frequency in hybrid circuits due to the parasitic and hence more suitable for MMIC design. Niclas, et al. first proposed the concept of the feedback amplifier in 1980 [4]. The concept of negative feedback was available before Niclas publication. However, in his design he incorporated both negative and positive feedback to obtain a broader bandwidth. He was able to obtain a gain of 4 dB from 350 MHz to 14 GHz with an output power of 13 dBm.

#### 1.2.3 Lossy Matched Amplifier Circuit

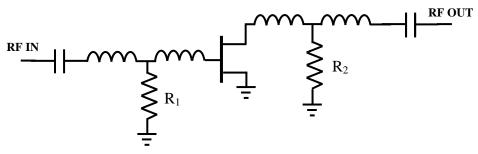

In this topology, two resistors  $R_1$  and  $R_2$  are employed for the input and output matching respectively as illustrated in Fig 1.5. These resistors are used to obtain flat gain by maintaining an input and output match throughout the desired bandwidth. It has a broader bandwidth at the expense of low power added efficiency. Moreover, due to the resistor  $R_1$ and  $R_2$ , it consists of a poor noise figure. This was first reported in the paper published by K. Honjo [5]. He was able to obtain a bandwidth of 13.5 octaves and 8.6 dB of gain using GaAs FETs.

Fig. 1.5 Lossy matched amplifier circuit.

#### 1.2.4 Distributed Amplifier Circuit

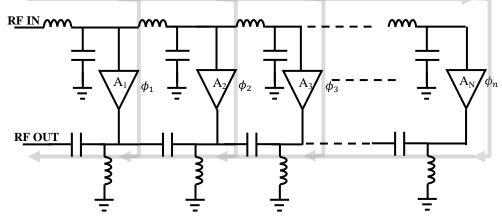

This is a well-known technique used in microwave amplifier design. This concept can be used to realize microwave amplifiers with multi octave bandwidths. In a conventional distributed amplifier topology, several numbers of transistors are connected between the input and output lines as shown in Fig 1.6.

Fig. 1.6 Schematic diagram of a distributed amplifier circuit.

The gate and drain impedance of the FETs are absorbed in these lossy artificial transmission lines. These lines are referred to as gate and drain transmission lines and they are coupled by the transconducatnce of the FETs. The principle of distributed amplification was first proposed by W. S. Percival in 1937 [6]. However, his work was not widely known until after E. L. Ginzton et al. reported the analysis of distributed amplifiers using valves in 1948 [7].

The first part of this thesis concentrates on the designing of such a distributed amplifier in PCB. A detailed discussion of this particular topology is provided in later chapters.

### 1.3 CMOS Technology for RF and Microwave Applications

Conventionally, RF and microwave ICs were very often realized in III-V technologies. Such as GaAs and InP. MESFETs and HFETs, which are available in these technologies, are able to operate at high frequencies and are superior in their performance. However, these technologies are not suitable for consumer products due to the high cost.

Silicon based technologies, such as CMOS, SiGe and BiCMOS are more suitable for consumer products, due to their high yield and low cost. Out of these technologies CMOS is relatively cheaper and more suitable for integrating digital circuits and data storage devices on the same chip.

However, designing RFICs in CMOS is challenging due to the lossy substrate. In a typical CMOS substrate, the Silicon conductivity is ~ 10 S/m, which is very lossy. Hence, realizing inductors with a high quality factor is challenging in this technology, especially at microwave frequencies due to the ohmic losses in the metal traces and substrate resistance and eddy currents. There are techniques used in CMOS RFIC in order to improve the quality factor of these inductors. Some of the techniques include; increasing the number of metal layers so that the inductor can be realized on the top most layer by increasing the distance between the lossy substrate and the microstrip lines, use lowest metal layer as a ground to provide an excellent isolation, choose thickened metal for the top most layer signal lines to reduce metal loses [8]. On the other hand, research interest on using active inductors and active filters has increased in recent years.

#### **CMOS Active and Passive Filters**

Traditionally, CMOS active filters were realized using transconductance amplifiers [9]. However, this type of filters is most suitable for low frequency range applications only [10]. Nowadays, research is conducted to implement inductors using active components [11]-[14]. Such active inductors are suitable for CMOS, because of reduced size and high quality factor. However, these circuits exhibit poor linearity and high noise figure due to the active components.

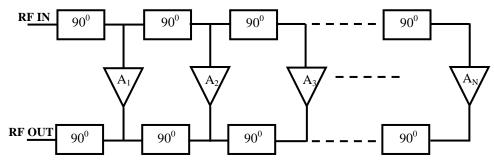

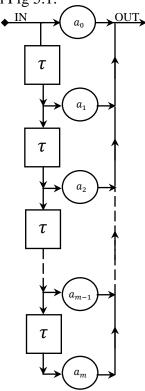

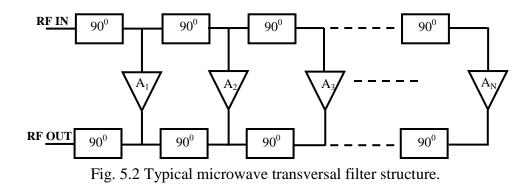

Various methods have been researched in the past to implement active filters in MMIC. Some of the research works consider active gyrators [15]. The transversal and recursive principle is another concept used in GaAs to implement active filters [16]. This was a concept used in discrete time filtering and adopted in the microwave frequency range later by Rauscher [16]. Later Schindler et al. modified this concept to reduce the circuit size and they proposed lumped and transversal element filters to realize an active filter [17] as shown in Fig 1.7. The concept of transversal filtering is somewhat similar to the distributed amplifier concept. The fundamental difference between the two types of filtering is that, in the case of the distributed amplifier, the signals are combined together in phase. And in the case of filtering, the filtering is done by combining different amplitudes and frequency dependent phase delays.

Fig. 1.7 Microwave transversal filter circuit.

The interest in the design of microwave and millimeter wave passive filters has recently increased. This is mainly because at higher operating frequencies the wavelengths are comparable with on-chip component dimensions. Therefore distributed elements can be used to design filters at higher frequencies such as millimeter wave. Using lumped elements in CMOS, microwave filter design is a challenging task due to the low quality factor of inductors and capacitors.

### 1.4 Motivation, Scope and Thesis Organization

The main objective of this thesis is the design of a broadband amplifier in 0.1-3.0 GHz and active and passive filters for RF and microwave front end systems. Frequency range in 0.1-3.0 GHz is chosen as it covers most of the commercial application bands such as UHF, VHF, ZigBee, GSM, Bluetooth and wireless LAN etc. This project has been divided into two subprojects. In the first project, a detailed description of the distributed amplification technique has been discussed. Some of the characteristics of this type of amplifiers have been simulated and verified. Next, a detailed explanation of the design and fabrication of a distributed amplifier from 0.1-3.0 GHz in PCB is reported.

The second project consisted of two designs. The first design is a lumped and transversal element band pass filter and the second is a passive lumped element filter using the Global Foundries CMOS 0.13-µm process. The simulation results have been verified by measuring the fabricated device. The organizations of the thesis is as follows:

Chapter 2: In this chapter the theory of distributed amplification is presented. Also, the effect of FET parasitics on distributed amplifier performance is discussed and verified through simulation.

Chapter 3: Measurement of active and passive components using TRL calibration technique is reported.

Chapter 4: A design of a distributed amplifier on PCB is presented. Schematic simulation results and comparison between electromagnetic and measurement results are provided.

Chapter 5: This chapter presents the second project which is the design of a lumped and transversal element filter in a 0.13-µm CMOS process. Simulation results of the designed filter are presented. Next, on wafer measurement results of the filter are compared with simulations.

Chapter 6: The design of a passive filter in 0.13-µm CMOS process at Ka band is presented. Chapter 7: The work presented in this thesis is summarized and recommendations are provided.

# CHAPTER 2

## **Distributed Amplification Technique**

### 2.1 Introduction

Microwave amplifiers always have benefited from new developments in device technology. Out of many characteristics of an amplifier, gain, frequency are the most important. After the invention of the triode, it was found that the gain bandwidth product of an amplifier is highly affected by the shunt capacitance. Hence, realizing a wide bandwidth amplifier was a challenging task. Distributed amplification is a well-known technique to overcome this challenge.

In this chapter we discuss the concept of distributed amplification. First, the gain bandwidth product of an amplifier is introduced. Next the principle of distributed amplification is discussed, followed by the explanation of several theoretical analysis methods. Finally, simulation verification of the effect of the FET intrinsic parasitics on a distributed amplifier is reported.

### 2.2 Gain Bandwidth Product of an Amplifier

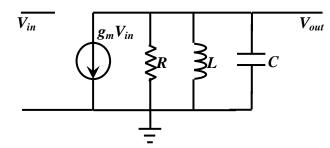

It has been shown by Wheeler [18] that the gain and bandwidth of an amplifier cannot be increased simultaneously beyond a certain limit. This limit is determined by a factor which is proportional to the ratio of tube transconductance  $g_m$  to the square root of the product of input and output plate capacitance. Hence, the gain bandwidth product cannot be increased indefinitely by connecting tubes in parallel because an increase in gain due to  $g_m$  is compensated by the total of input and output plate capacitance. Therefore, these two quantities are trade-offs when designing an amplifier. The concept illustrated by Wheeler [18] for tubes also applies to modern FET transistors as well. Thomas Wong [19] illustrated this concept by considering a simple transistor combined with coupling circuit as shown in figure 2.1.

Fig. 2.1 Simple band pass amplifier structure.

The transfer function of the above circuit can be obtained as:

$$A_{\nu}(\omega) = \frac{-g_m}{1 + jQ\left(\frac{\omega}{\omega_0} - \frac{\omega_0}{\omega}\right)}$$

(2.1)

Where  $\omega_0 = \frac{1}{\sqrt{LC}}$  and  $Q = \omega_0 RC$

The maximum gain occurs at midband and is given by  $g_m R$ . The -3 dB bandwidth *B* is given by  $1/_{2\pi RC}$ . Hence the gain-bandwidth product is

$$A_{\nu o}B = \frac{g_m}{2\pi C} \tag{2.2}$$

From equation 2.2 it can be seen that, if we are interested in obtaining the maximum gainbandwidth product from a given active device, then we should keep C close to the intrinsic contribution from the input and output capacitance of the active device.

### 2.3 Principle of Distributed Amplification

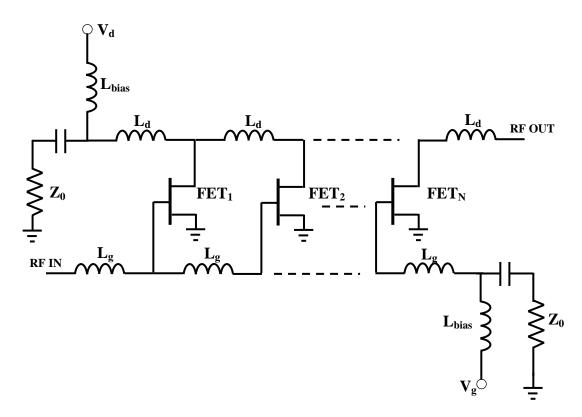

To overcome the difficulty of increasing the gain-bandwidth product of an amplifier, an arrangement should be made so that we can connect transistors in parallel without increasing up the input and output parasitic capacitances. The distributed amplification technique enables us to increase the gain-bandwidth product without adding shunt capacitance. This concept was first proposed by W. S. Percival's patent in 1937 [6]. In his design, he made the electrodes of the tubes in a helical coil form, which combined with the inter electrode capacitors to form an artificial transmission line. Percival's invention did not gain widespread attention until Ginzton et al. [7] published a paper on distributed amplification in 1948. Figure 2.2 shows a schematic representation of a FET distributed amplifier.

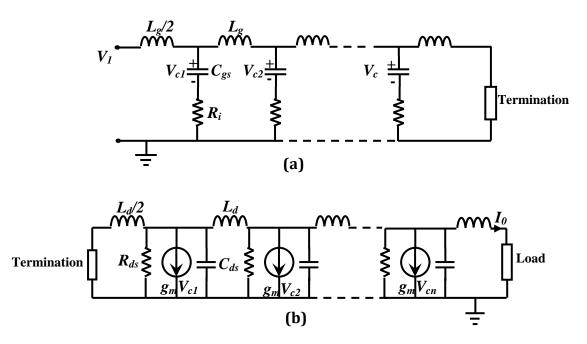

Fig. 2.2 Schematic representation of a FET distributed amplifier.

As shown in Fig. 2.2, the gates of the FETs are connected to a series of inductors  $L_g$  which is known as gate-line inductors. Similarly, drains of the FETs are connected to a series of inductors  $L_d$  which is known as the drain-line. Fig. 2.3 shows the small signal equivalent circuit of a FET.  $C_{gs}$  and  $C_{ds}$  are the input and output capacitance of the FET respectively.  $C_{gd}$  is the capacitance between gate and drain. In this case, we assume the unilateral case. Hence,  $C_{gd}$  is neglected. These input and output capacitors are absorbed into the gate line inductors and drain line inductors to form a constant k LC low-pass ladder filter structure as shown in Fig 2.4. One end of both lines has been terminated with the appropriate characteristic impedance  $Z_g$  and  $Z_d$ .

Fig. 2.3 Small signal equivalent circuit of a FET.

Fig. 2.4 Equivalent circuit of a distributed amplifier.

When an RF signal is applied at the input of the gate line, the signal travels down the gate line and will be absorbed at the termination end. As the signal travels down the gate line, the transistors are excited by the traveling voltages and will be coupled into the drain line through the transconductance of each transistor. At each node in the drain line the signal will travel away in opposite directions. Signals traveling to the left will be absorbed by the network termination impedance. Only the signals that travel to the right will appear as useful output. To produce sufficient gain, it is important that the drain currents add in phase as the signal propagates along the drain line. This is achieved by making the phase shift per section of the gate line equal to the phase shift per section of the drain line. This is possible under the assumption that all the transistors are identical.

For a typical FET,  $C_{gs}$  is larger than  $C_{ds}$ . Hence, in order to equalize the phase shift per section in both lines, an additional capacitance has to be added as shown in Fig. 2.4.

Hence,

$$C_{gs} = C_{ds} + C_{add} \tag{2.3}$$

Next we choose

$$L_g = L_d = L \tag{2.4}$$

There for cut-off frequency of the line is given by:

$$\omega_c = \frac{2}{\sqrt{LC_{gs}}} = \frac{2}{\sqrt{L(C_{ds} + (C_{add}))}}$$

(2.5)

The characteristics impedance of the lines is given by:

$$Z_0 = \sqrt{\frac{L}{C_{gs}}} = \sqrt{\frac{L}{C_{ds} + C_{add}}}$$

(2.6)

From the equivalent circuit of the distributed amplifier, it can be seen that inductors and capacitors form a distributed low pass filter structure, whose bandwidth is determined by

the amount of inductance and capacitance in one period. Hence, it is possible to increase the gain by introducing more transistors without compromising the bandwidth. However, this is possible only if the transistors and transmission networks are not dissipative. In a practical system, increasing the number of sections will not increase the gain per section beyond a certain limit and it might even become negative.

Ginzton addressed some of the techniques to improve the flatness of gain and delay by incorporating m-derived networks with *m* greater than unity. He also suggested that by connecting together the adjacent anodes or grids in pairs, a constant gain can be obtained throughout the pass-band. Soon after Ginzton's publication in 1948, Horton et al. published a paper in 1950 addressing some of the practical considerations in distributed amplifiers [20]. In their paper, they considered effects not considered in the first order theory such as, coil losses, grid losses, grid and plate inductors and coil winding capacitance. He also suggested corrective methods to counteract the limitations. In 1954 Bassett reported a way to improve the gain fluctuation at the cut-off frequency of a distributed amplifier by incorporating resistors into the m-derived low pass filter structure [21].

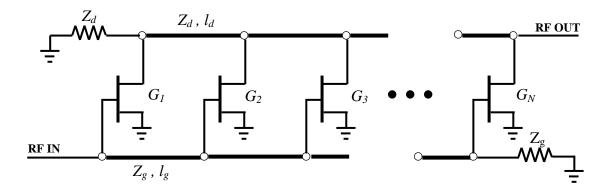

The research in distributed amplifiers using vacuum tubes continued [20]-[24] until the first solid-state GaAs MESFET distributed amplifier investigated by Moser in 1967 [25] and Jutzi in 1969 [26]. The first monolithic GaAs distributed amplifier was successfully built and tested by Ayasli et al. in 1981 [27] and 1982 [28], which was a vital point in the evolution of the distributed amplifiers. Ayasli et. al. used a new approach to obtain a wideband performance using distributed amplifiers. In their approach they used GaAs FETs as the active elements and instead of using inductors, gate and drain lines were implemented with transmission lines, which are truly distributed. Fig 2.5 shows a schematic diagram of such amplifier. Since the gate and drain lines are implemented using transmission lines, it is also known as "*Traveling-Wave amplifier*". With this approach it is possible to avoid many

difficulties occurring in the conventional approach such as capacitive and inductive coupling, loading due to grid and coil losses, parasitic inductance and capacitance in coil windings.

Fig. 2.5 Schematic diagram of a traveling wave amplifier.

Ayasli et al. also showed a theoretical analysis for the traveling-wave amplifier constructed with periodically loaded transmission lines, which will be discussed later in this chapter. As described earlier, the bandwidth of a distributed amplifier depends on the cut-off frequency of the artificial transmission line. Engineers were able to obtain several hundreds of GHz bandwidth using this technique [29]-[33]. A special technique used to improve the bandwidth of the distributed amplifier is capacitive division [33]-[36]. In this technique a capacitor is connected in series with the FET gate-source capacitor which acts as a voltage divider. The reduction in gain was recovered by increasing the number of stages in the amplifier. Introducing such capacitive division helps in increasing the amplifier bandwidth equal to  $f_{max}$  of the FET [33]. On-the-other hand, it also helps to increase the total device periphery per gain stage and this helps to bring the optimum as load line of the FET closer to the output drain line impedance.

### 2.3.1 Power Performance of a Distributed Amplifier

Since the invention of the transistor, the distributed amplifier was a main research area in the RF and microwave field. Much research has been conducted to improve the performance of this topology. Improving the power performance of a distributed amplifier was a main research area [37]-[46]. A conventional distributed amplifier's power performance is limited due to several reasons such as breakdown voltage of the transistor; unequal contributions from the transistors to the output power, and none-optimum load impedance seen by the transistors [43]. Capacitive drain coupling is one proposed technique to increase the power capabilities of a distributed amplifier [38]. In this case, an additional capacitor is added between the drain line and the drain of the last FET to reduce the drain line loading and increase the impedance seen by the FET. Schindler et al. was able to obtain an output power of 20 dBm up to 33 GHz. Using GaN devices also can help to improve power handling capabilities of distributed amplifiers due to its superior thermal and breakdown voltage properties [44]. By using GaN devices, they were able to obtain an output power of 37 dBm and a power added efficiency of 27 % in the frequency range 0.002 - 3.0 GHz.

#### 2.3.2 Noise Performance of Distributed Amplifiers

In terms of noise, distributed amplifiers have a medium noise figure. It typically varies from 4 - 8 dB [47-54]. Formulas for the intrinsic noise figure of a distributed amplifier was first formulated by Niclas [47] in 1983. Based on his formulation, the minimum noise figure of a distributed amplifier can be reduced by increasing the number of sections.

#### 2.3.3 Stability of Distributed Amplifiers

The analysis on oscillation conditions in distributed amplifiers has been done by Gamand et al. in 1989 [55]. Based on their analysis, the instability for a given transistor with width W, increases with  $g_m$ ,  $C_{gd}$  and the parasitic resistances  $r_{ds}$  and  $R_i$  tend to moderate the oscillations. In addition, he found that oscillations occur at high frequencies and they are mainly due to the internal loops formed by the transconductance and the feedback capacitance  $C_{gd}$  of the transistor combined with the transmission lines.

### 2.4 Theoretical Analysis on Distributed Amplifiers

In this section three types of analysis methods available in the literature are presented. The first two types are based on the unilateral ( $C_{gd} = 0$ ) version of the FET and will analyze an amplifier with loaded gate and drain transmission lines and an amplifier with inductors as gate and drain lines. The third analysis considers the effect of gate to drain capacitor ( $C_{gd}$ ).

#### 2.4.1 Amplifier with periodically loaded transmission lines

This analysis was first proposed by Ayasli et al. in 1982 [28]. Fig. 2.5 shows a distributed amplifier with periodically loaded transmission lines. By considering the unilateral figure of the FET, the above circuit can be separated into two sections each, for gate and drain lines, as shown in Figures 2.6 and 2.7 [56]. Hence, the circuit can be analyzed separately. The gate and drain lines are connected via the coupling through the current source  $I_{dn} = g_m V_{cn}$ . Fig. 2.6 (b) and 2.7 (b) shows a single unit cell of gate and drain lines respectively.

Fig. 2.6 Equivalent circuit of (a) gate line; (b) single unit cell of the gate line.

Fig. 2.7 Equivalent circuit of (a) drain line; (b) single unit cell of the drain line.

$L_g$  and  $C_g$  are the per unit inductance and capacitance of the gate transmission lines.  $R_i l_g$  and  $C_{gs} \mathcal{A}_g$  are the per unit length loading due to the FET input resistance  $R_i$  and gate to source capacitance  $C_{gs}$ . Similarly,  $L_d$  and  $C_d$  are the inductance and capacitance per unit length of

the drain line and  $R_{ds}l_d$  and  $C_{ds}/l_d$  are the per unit length loading due to the FET output resistance  $R_{ds}$  and drain to source capacitance  $C_{ds}$ .

Since the transmission line properties change due to the FET input and output capacitances, we need to obtain the characteristic impedance of the modified lines. For the gate line, the series and parallel admittance per unit length are given by

$$Z = j\omega L_g \tag{2.7}$$

$$Y = j\omega C_g + \left[ R_i l_g + \frac{1}{j\omega C_{gs}/l_g} \right]$$

$$\Rightarrow Y = j\omega C_g + \frac{j\omega C_{gs}/l_g}{1 + j\omega C_{gs}R_i}$$

(2.8)

Where Z is the series impedance and Y is the shunt admittance. Next, using transmission line theory, characteristic impedance of the gate line is obtained as

$$Z_g = \sqrt{\frac{Z}{Y}} = \sqrt{j\omega L_g \left\{ j\omega C_g + \frac{j\omega C_{gs}/l_g}{1 + j\omega C_{gs}R_i} \right\}^{-1}}$$

$$Z_g = \sqrt{\frac{L_g}{C_g + C_{gs}/l_g}}, \qquad R_i \approx 0$$

(2.9)

In the above calculation, we have assumed that the loss due to the resistance  $R_i$  is negligible. By definition, the propagation constant of the transmission line is given by

$$\gamma_g = \alpha_g + j\beta_g = \sqrt{ZY} \tag{2.10}$$

Where,  $\alpha_g$  is the gate line attenuation constant and  $\beta_g$  is the phase shift per section of the gate line.

Assuming small loss, such that  $\omega R_i C_{gs} \ll 1$ ,  $\omega^2 C_{gs}^2 R_i^2 \approx 0$ , the gate-line propagation constant is calculated as:

$$\gamma_g = \frac{\omega^2 R_i C_{gs}^2 / l_g}{2} Z_g + j \omega \sqrt{L_g (C_g + C_{gs} / l_g)}$$

(2.11)

A similar analysis is used to obtain the characteristic impedance and propagation constant of the drain line. Hence, the series impedance Z and shunt admittance Y of the drain line are found as:

$$Z = j\omega L_d \tag{2.12}$$

$$Y = \frac{1}{R_{ds}l_d} + j\omega(C_d + C_{ds}/l_d)$$

(2.13)

Next, the characteristic impedance of the drain line is found as:

$$Z_d = \sqrt{\frac{Z}{Y}} = \sqrt{\frac{L_d}{C_d + C_{ds}/l_d}}$$

(2.14)

And by using the small loss approximation, the propagation constant can be calculated as:

$$\gamma_d = \alpha_d + j\beta_d = \sqrt{ZY} \tag{2.15}$$

$$\gamma_d = \sqrt{j\omega L_d \left[\frac{1}{R_{ds}l_d} + j\omega(C_d + C_{ds}/l_d)\right]}$$

(2.16)

$$\approx \frac{Z_d}{2R_{ds}l_d} + j\omega\sqrt{L_d(C_d + C_{ds}/l_d)}$$

(2.17)

The amplifier gain can be calculated by considering an incident input voltage of  $V_i$ . Hence, the voltage across the gate-to-source capacitance of the nth FET can be written as:

$$V_{cn} = V_i e^{-(n-1)\gamma_g l_g} \left\{ \frac{1/j\omega C_{gs}}{R_i + 1/j\omega C_{gs}} \right\}$$

$$\Rightarrow V_{cn} = V_i e^{-(n-1)\gamma_g l_g} \left\{ \frac{1}{1 + j\omega C_{gs} R_i} \right\}$$

(2.18)

For a typical FET we assume that,  $\omega R_i C_{gs} \ll 1$ . Hence, the factor  $\frac{1}{1+j\omega C_{gs}R_i}$  can be

approximated as unity throughout the bandwidth.

Each current generator in the drain line contributes waves in the form of  $-\frac{1}{2}I_{dn}e^{\pm\gamma_d Z}$  in each direction. Also  $I_{dn}$  is given by

$$I_{dn} = g_m V_{cn} \tag{2.19}$$

Therefore, the total output current  $I_0$  at the N<sup>th</sup> terminal of the drain line is

$$I_0 = -\frac{1}{2} \sum_{n=1}^{N} I_{dn} e^{-(N-n)\gamma_d l_d} = -\frac{g_m V_i}{2} e^{-N\gamma_d l_d} e^{\gamma_g l_g} \sum_{n=1}^{N} e^{-n(\gamma_g l_g - \gamma_d l_d)}$$

(2.20)

Equation (2.20) can be simplified by using the identity

$$\sum_{n=1}^{N} x^n = \frac{x^{N+1} - x}{x - 1}$$

(2.21)

Thus, the total output current can be calculated as:

$$I_{0} = \frac{-g_{m}}{2} V_{i} e^{-N\gamma_{d} l_{d}} e^{\gamma_{g} l_{g}} \left[ \frac{\left\{ e^{-(\gamma_{g} l_{g} - \gamma_{d} l_{d})} \right\}^{N+1} - e^{-(\gamma_{g} l_{g} - \gamma_{d} l_{d})}}{e^{-(\gamma_{g} l_{g} - \gamma_{d} l_{d})} - 1} \right]$$

$$I_{0} = \frac{-g_{m}}{2} V_{i} \left[ \frac{e^{-N\gamma_{g}l_{g}} - e^{-N\gamma_{d}l_{d}}}{e^{-\gamma_{g}l_{g}} - e^{-\gamma_{d}l_{d}}} \right]$$

(2.22)

23

Next the amplifier gain is calculated as:

$$G = \frac{P_{out}}{P_{in}} = \frac{\frac{1}{2}I_0^2 Z_d}{\frac{1}{2}|V_i|^2/Z_g} = \frac{g_m^2 Z_d Z_g}{4} \left| \frac{e^{-N\gamma_g l_g} - e^{-N\gamma_d l_d}}{e^{-\gamma_g l_g} - e^{-\gamma_d l_d}} \right|^2$$

(2.23)

As explained in section 2.3, to obtain useful gain, waves contributed by each generator in the drain line must be added in phase. To ensure phase addition,  $\beta_g l_g = \beta_d l_d$ .

Hence, the gain in (2.23) can be simplified to

$$G = \frac{g_m^2 Z_g Z_d}{4} \frac{\left(e^{-N\gamma_g l_g} - e^{-N\gamma_d l_d}\right)^2}{\left(e^{-\alpha_g l_g} - e^{-\alpha_d l_d}\right)^2}$$

(2.24)

If we assume losses to be negligible, the term  $e^{-\alpha_g l_g} - e^{-\alpha_d l_d}$  can be approximated as:  $\alpha_g l_g = \alpha_d l_d$

Hence, for the ideal lossless case, the expression of the gain is found as

$$G = \frac{g_m^2 Z_g Z_d N^2}{4}$$

(2.25)

From equation (2.25), it can be seen that for an ideal distributed amplifier, the gain increases as  $N^2$ . However, in a conventional cascaded stage, gain increases with  $(G_0)^N$  [56]. If we include losses, equation (2.24) explains that when  $N \to \infty$  the gain of the distributed amplifier approaches zero. This is because that, the wave traveling along the lossy gate line decays exponentially. Hence, the FET at the end of the amplifier receives less input signal. On the other hand, amplified signals at the beginning of the drain line decay exponentially. However, an increase in the number of sections N is not enough to compensate for an exponential decay of signals. Therefore, we cannot increase the number of sections in a distributed amplifier indefinitely for a real lossy case. Which implies that there is an optimum number for *N* for a given FET. To obtain the optimum *N*, which gives maximum gain, we need to differentiate equation (2.24) with respect to *N*. Hence  $N_{opt}$  is given as:

$$N_{opt} = \frac{\ln(\alpha_g l_g / \alpha_d l_d)}{\alpha_g l_g - \alpha_d l_d}$$

(2.26)

## 2.4.2 Analysis of a distributed amplifier with discrete inductors

In 1984 Bayer et al. [57] presented the analysis and reported a systematic graphical approach to design a distributed amplifier. For simplicity they used the unilateral model of the FET.

Fig. 2.8 Equivalent circuit of a DA with discrete components (a) gate line; (b) drain line.

Figure 2.8 shows the equivalent circuit for the gate and drain lines of the distributed amplifier. These lines are considered as constant-k lines and resistances  $R_i$  and  $R_{ds}$  introduce losses. In the analysis, they assumed that the lines are terminated with the image impedance. Hence, current delivered to the load of the amplifier is given by

$$I_0 = \frac{1}{2} g_m e^{-\theta_d/2} \left[ \sum_{k=1}^n V_{ck} e^{-(n-k)\theta_d} \right]$$

(2.27)

Where,  $V_{ck}$  is the voltage across the gate-to-source capacitance of the  $k^{th}$  FET,

$\theta_d = A_d + j\phi_d$  is the propagation constant of the drain line,

$A_d$  and  $\phi_d$  are the attenuation and the phase shift per section of the drain line respectively, *n* is the number of FETS in the amplifier.

Next  $V_{ck}$  is expressed in terms of the voltage at the gate terminal of the  $k^{th}$  FET and is given by:

$$V_{ck} = \frac{V_i e^{-(2k-1)\theta_g/2 - j \tan^{-1}(\omega/\omega_g)}}{\left[1 + \left(\frac{\omega}{\omega_g}\right)^2\right]^{1/2} \left[1 - \left(\frac{\omega}{\omega_c}\right)^2\right]^{1/2}}$$

(2.28)

Where,

$V_i$  is the input voltage of the amplifier,

$\theta_g = A_g + j\phi_g$  is the propagation function of the gate line,

$A_g$  and  $\phi_g$  are the attenuation and the phase shift per section of the gate line respectively,

$\omega_g = 1/R_t C_{gs}$  is the radian gate line cut-off frequency and

$\omega_c = 2\pi f_c$  is the radian cut-off frequency of the lines.

As before, in order to obtain a useful gain, the phase velocities of both lines must be the same. Therefore,  $\phi_g \cong \phi_d = \phi$ , and by using equations (2.27) and (2.28),  $I_o$  can be rewritten as

$$I_{0} = \frac{g_{m}V_{i}\sinh\left[\frac{n}{2}(A_{d} - A_{g})\right]e^{-n(A_{d} + A_{g})/2}e^{-jn\phi - j\tan^{-1}(\omega/\omega_{g})}}{2\left[1 + \left(\frac{\omega}{\omega_{g}}\right)^{2}\right]^{1/2}\left[1 + \left(\frac{\omega}{\omega_{c}}\right)^{2}\right]\sinh\left[\frac{1}{2}(A_{d} - A_{g})\right]}$$

(2.29)

Power delivered to the load is given by:

$$P_0 = \frac{1}{2} |I_0|^2 Re[Z_{ID}] \cong \frac{1}{2} |I_0|^2 \sqrt{L_d / C_d [1 - (\omega/\omega_c)^2]}$$

(2.30)

Input power of the amplifier is given by:

$$P_{i} = \frac{|V_{i}|^{2}}{2|Z_{IG}|^{2}} Re[Z_{IG}] \cong \frac{1}{2} |V_{i}|^{2} / \sqrt{L_{g}/C_{g}[1 - (\omega/\omega_{c})^{2}]}$$

(2.31)

Where  $Z_{IG}$  and  $Z_{ID}$  are the image impedance of the gate and drain lines respectively. The power gain of the amplifier is given by:

$$G = \frac{g_m^2 R_{01} R_{02} \sinh^2 \left[ \frac{n}{2} (A_d - A_g) \right] e^{-n(A_d + A_g)}}{4 \left[ 1 + \left( \frac{\omega}{\omega_g} \right)^2 \right] [1 - (\omega/\omega_c)^2] \sinh^2 \left[ \frac{1}{2} (A_d - A_g) \right]}$$

(2.32)

$R_{01} = \sqrt{L_g/C_g}$  and  $R_{02} = \sqrt{L_d/C_d}$  are the characteristic impedance of gate and drain lines respectively. The voltage gain of the amplifier is given by

$$A = \frac{g_m (R_{01} R_{02})^{1/2} \sinh\left[\frac{n}{2} (A_d - A_g)\right] e^{-n(A_d + A_g)/2}}{2\left[1 + \left(\frac{\omega}{\omega_g}\right)^2\right]^{1/2} \left[1 + \left(\frac{\omega}{\omega_c}\right)^2\right]^{1/2} \sinh\left[\frac{1}{2} (A_d - A_g)\right]}$$

(2.33)

The optimum number of stages of the amplifier can be obtained using equation (2.33) and is given by:

$$N_{opt} = \frac{\ln(A_d/A_g)}{A_d - A_g} \tag{2.34}$$

#### 2.4.3 Cascaded four-ports formulation

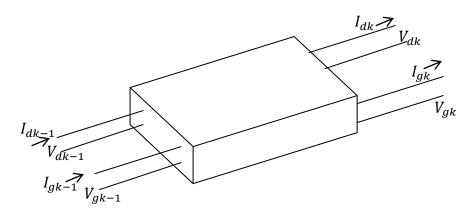

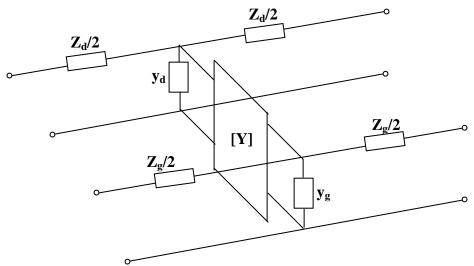

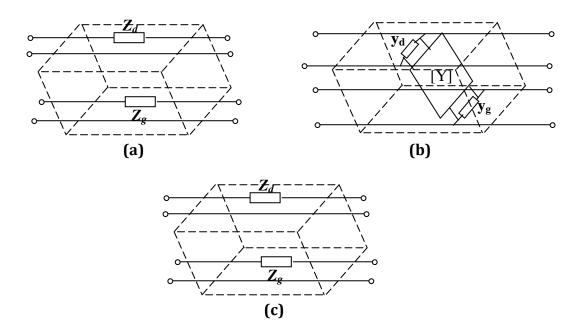

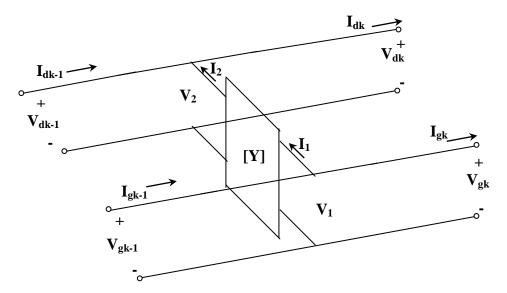

In the previous two analyses, the unilateral case for the FET is assumed for simplicity. However, this ignores the finite isolation of the FET. To describe these effects we need to account for the gate-to-drain capacitance of the FET. Such analysis will lead to more complicated formulations and may not give any closed form results. Hence, we need to employ numerical methods in order to solve these equations. Cascaded four port formulation is a well-known method which includes the effect of gateto-drain capacitor [58]. In this formulation, a cross section of the amplifier is considered with four ports as shown in Fig. 2.9.

Fig. 2.9 A cross section of the distributed amplifier circuit

By considering Fig.2.9, a chain matrix for a four port can be defined in parallel with the ABCD matrix for a two port. Such a chain matrix can be written as

$$\begin{bmatrix} V_{dk-1} \\ I_{dk-1} \\ V_{gk-1} \\ I_{gk-1} \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} & A_{13} & A_{14} \\ A_{21} & A_{22} & A_{23} & A_{24} \\ A_{31} & A_{32} & A_{33} & A_{34} \\ A_{41} & A_{42} & A_{43} & A_{44} \end{bmatrix} \begin{bmatrix} V_{dk} \\ I_{dk} \\ V_{gk} \\ I_{gk} \end{bmatrix}$$

(2.35)

Fig. 2.10 shows the internal components of the four ports. The active device is represented

by a two port with admittance matrix [Y].

Fig. 2.10 Internal components of the four ports

To obtain a chain matrix for this section, we first separate the above circuit into several sections consisting of an active device, shunt elements and transmission lines. The chain matrix of the series elements is obtained by augmenting the ABCD matrices of the two ports and is given by

$$A_{l} = \begin{bmatrix} 1 & Z_{d} & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{g} \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(2.36)

Fig. 2.11 Individual components of the four port section (a) Transmission lines; (b) Y parameters of the FET; (c) transmission lines

The chain matrix of the middle subsection is obtained by applying Kirchhoff's current law (a detailed derivation is provided in Appendix A) and is given by:

$$A_{t} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ y_{22} + y_{d} & 1 & y_{21} & 0 \\ 0 & 0 & 1 & 0 \\ y_{12} & 0 & y_{11} + y_{g} & 1 \end{bmatrix}$$

(2.37)

If we use transmission lines instead of lumped elements equation (2.36) can be written as

$$A_{l} = \begin{bmatrix} \cosh \theta_{d} & Z_{0d} \sinh \theta_{d} & 0 & 0 \\ Z_{od}^{-1} \sinh \theta_{d} & \cosh \theta_{d} & 0 & 0 \\ 0 & 0 & \cosh \theta_{g} & Z_{0g} \sinh \theta_{g} \\ 0 & 0 & Z_{og}^{-1} \sinh \theta_{g} & \cosh \theta_{g} \end{bmatrix}$$

(2.38)

And equation (2.37) can be written as:

$$A_t = \begin{bmatrix} 1 & 0 & 0 & 0 \\ y_{22} & 1 & y_{21} & 0 \\ 0 & 0 & 1 & 0 \\ y_{12} & 0 & y_{11} & 1 \end{bmatrix}$$

(2.39)

The final chain matrix for this section, assuming that the network is symmetrical, is written as:

$$A_k = A_l A_t A_l \tag{2.40}$$

For a distributed amplifier with N sections, the overall chain matrix can be written as:

$$B = \prod_{k=1}^{N} A_k = \begin{bmatrix} \beta_{11} & | & \beta_{12} \\ - & - & - & - \\ \beta_{21} & | & \beta_{22} \end{bmatrix}$$

(2.41)

Where,  $\beta_{jj}$  represents a 2 x 2 sub-matrix. Hence, the input and output relation of the amplifier can be written as:

$$\begin{bmatrix} V_{do} \\ -V_{od}/Z_L^d \\ V_{go} \\ I_{go} \end{bmatrix} = B \begin{bmatrix} V_{dN} \\ V_{dN}/Z_L^d \\ V_{gN} \\ V_{gn}/Z_L^g \end{bmatrix}$$

(2.42)

Equation (2.42) can be used to obtain closed form formulas for  $S_{11}$ . However, the analytical results are cumbersome. Niclas et al. showed some of their numerical simulation results for the above formulations and some optimization methods for distributed amplifiers [58].

### 2.5 Effect of FET Parasitics on Distributed Amplifier Performances

The theoretical analysis performed in the previous section is based on a simple FET model and this type of analysis does not provide any insight into how the individual parasitics affect the distributed amplifier performance. In this section we explore how these parasitics affect the gain  $|S_{21}|$ , input return loss  $|S_{11}|$ , output return loss  $|S_{22}|$  and isolation  $|S_{12}|$  of a distributed amplifier.

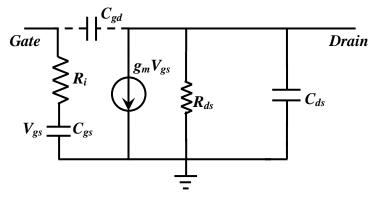

To investigate the effect of parasitics, commercially available circuit simulator Agilent's Advanced Designed System (ADS) was used. Equivalent circuit model shown in Fig. 2.12 was used for the transistor model. Next, a three stage distributed (traveling-wave) amplifier incorporating ideal 50 Ohm transmission lines is designed. Gate and drain lines are terminated with a 50 Ohm resistor.

Fig. 2.12 Small signal equivalent circuit of a FET.

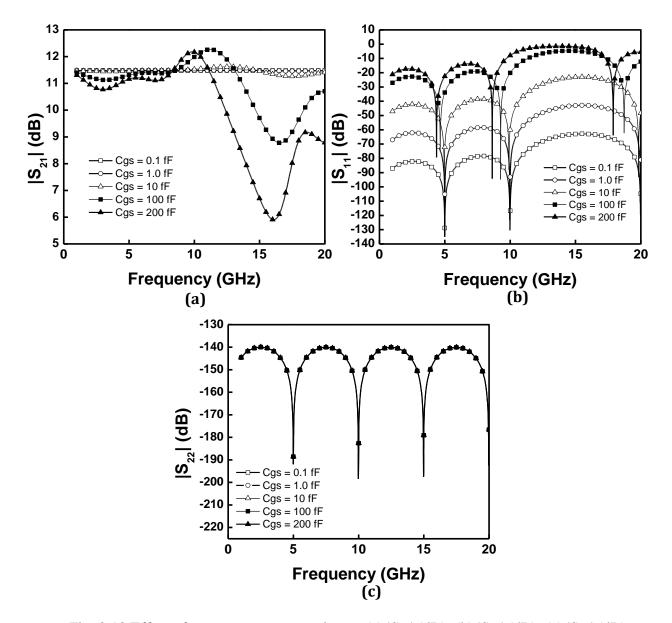

Several simulations are performed in order to investigate the effect of the parasitics. First we explore the effects of the gate-to-source capacitance ( $C_{gs}$ ) by considering other parasitics negligible. Values of 0.1 fF, 1.0 fF, 10 fF, 100 fF and 200 fF were considered. Next, we explore the effect on series gate resistance  $R_i$  on the performance of a distributed amplifier. In this simulation  $R_i$  was varied for two different values of gate-to-source capacitance. Finally we explore the effect of gate-to-drain capacitance ( $C_{gd}$ ) of a distributed amplifier when  $C_{gs} = 10$  fF. The simulated results are shown in the subsection below.

Fig. 2.13 Effect of gate-to-source capacitance (a)  $|S_{21}|$  (dB); (b)  $|S_{11}|$  (dB); (c)  $|S_{22}|$  (dB)

Based on the simulated results it is seen that the value of  $C_{gs}$  can affect the return loss significantly. For a distributed amplifier with loaded transmission lines, increasing  $C_{gs}$ changes the characteristic impedance of the artificial transmission line. If the value of  $C_{gs}$  is very small, the characteristic impedance of the transmission line will be close to 50 Ohm and, hence, good input matching is achieved. From the above graphs, it can also be seen that increasing  $C_{gs}$  reduces the cut-off frequency of the amplifier and it increases the ripples in the gain. However, an increase in  $C_{gs}$  does not affect the output return loss of the amplifier. This is because in this simulation we have assumed  $C_{gd}$  to be negligible.

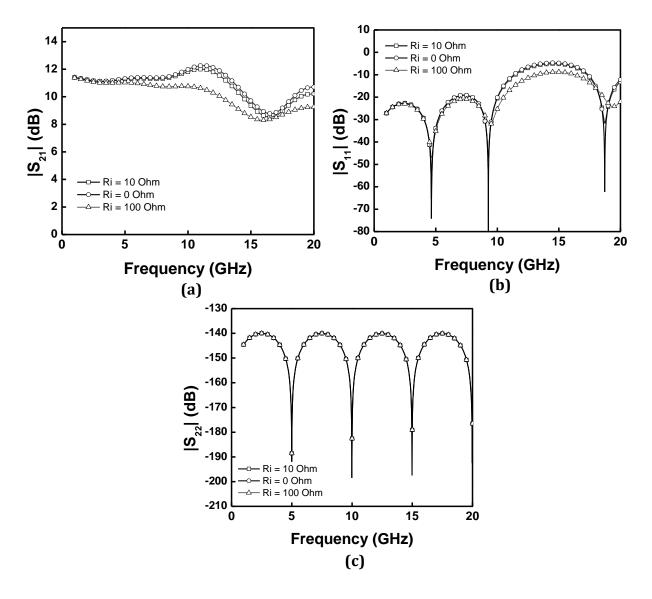

2.5.2 Effect of Series Resistance  $R_i$  when  $C_{gs} = 100$  fF

Fig. 2.14 Effect of Series Resistance  $R_i$  when  $C_{gs} = 100$  fF (a)  $|S_{21}|$  (dB); (b)  $|S_{11}|$  (dB); (c)  $|S_{22}|$  (dB)

Fig. 2.15 Effect of Series Resistance  $R_i$  when  $C_{gs} = 200$  fF (a)  $|S_{21}|$  (dB); (b)  $|S_{11}|$  (dB); (c)  $|S_{22}|$  (dB)

Based on the above simulations, it can be seen that increasing  $R_i$  significantly affects the gain of the amplifier. This is due to the losses introduced by the resistance. On the other hand, it is also clear that this impact is more pronounced when  $C_{gs}$  is increased from 100 fF to 200 fF.

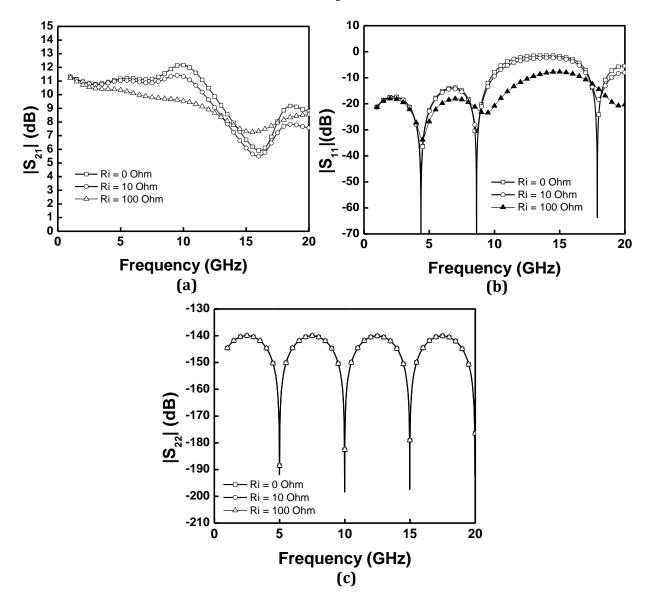

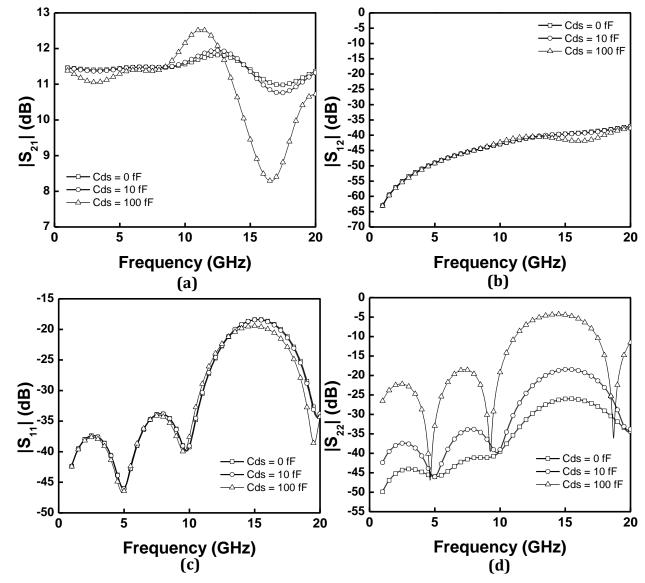

Fig. 2.16 Effect of gate-to-drain capacitance when  $C_{gs} = 10$  fF (a)  $|S_{21}|$  (dB); (b)  $|S_{12}|$  (dB); (c)  $|S_{11}|$  (dB);  $|S_{22}|$  (dB)

For a typical discrete transistor,  $C_{gd}$  is around one tenth of  $C_{gs}$ . Hence, we have chosen values from 1.0 fF – 5.0 fF for  $C_{gd}$ . From the above graphs it is clear that  $C_{gd}$  affects the return loss, gain and output return loss.

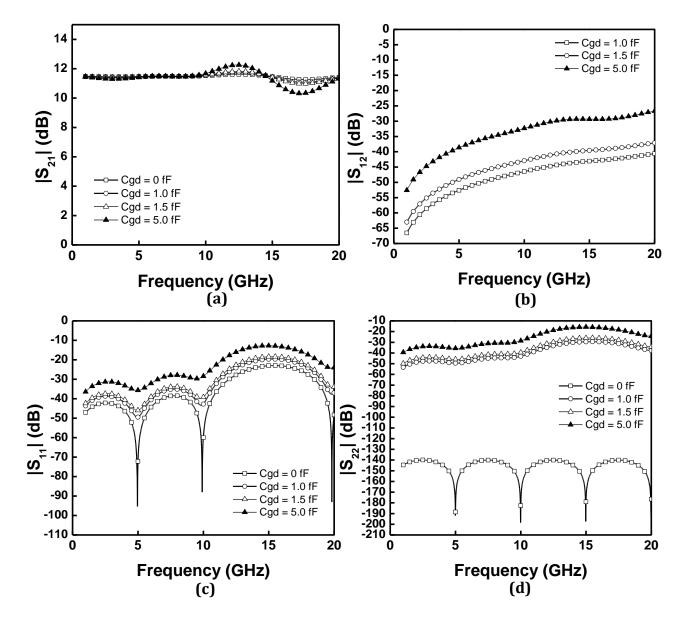

2.5.5 Effect of Drain-to-Source Capacitance when  $C_{gs} = 10$  fF and  $C_{gd} = 1.5$  fF

Fig. 2.17 Effect of Drain-to-Source Capacitance when  $C_{gs} = 10$  fF and  $C_{gd} = 1.5$  fF (a)  $|S_{21}|$  (dB); (b)  $|S_{12}|$  (dB); (c)  $|S_{11}|$  (dB); (d)  $|S_{22}|$  (dB)

Based on the simulations, output return loss is mostly affected by the value of  $C_{ds}$ . Because, when  $C_{ds}$  is present, the characteristics impedance of the drain-line is not equal to 50 Ohms. From the above simulations it is clear that parasitics introduced by the transistor tend to degrade the performance of distributed amplifiers. These parasitics are only contributions from the intrinsic part of a transistor. However, transistors with packages consist of many other parasitics due to the package itself. Therefore, designer needs to take account these contributions in order to design a working distributed amplifier.

## 2.6 Conclusions and Recommendations

In this chapter, the principle of distributed amplification is presented. Some of the performances such as power, noise and stability, are discussed and theoretical expressions are formulated based on previous research work. Agilent's ADS simulator is used to obtain insight into how the transistor intrinsic parasitics effect the distributed amplifier performance. Based on the simulation results, it is concluded that the amplifier return loss is mostly affected by the transistor gate-to-source capacitance ( $C_{gs}$ ). Increasing  $C_{gs}$  also caused an increase in the ripples in the gain of the amplifier. An increase in the gate-to-drain capacitance ( $C_{gd}$ ) also degrades the performance of the amplifier. The presence of  $C_{gd}$  also causes unnecessary oscillations due to the internal loops formed. To design a successful working amplifier it is recommended to include all the parasitic effects of the amplifier as well as the package parasitics.

# **CHAPTER 3**

# **TRL Calibration and Measurement**

# 3.1 Introduction

As described in the previous chapter, package parasitics degrade the performance of distributed amplifiers. In order to design a distributed amplifier by considering these effects, we measured the S-parameters of the transistors and used these results in our design. Passive components, such as inductors and capacitors, may not have a very high self-resonant frequency. Hence, we had to consider the behavior at higher frequencies of these components to design a broadband amplifier as well.

In this work, the TRL calibration technique for accurate measurement of active and passive components is discussed. Measurement results of measured components are presented, which were used in the design of a distributed amplifier.

## 3.2 S – Parameter measurement

#### 3.2.1 Vector Network Analyzer

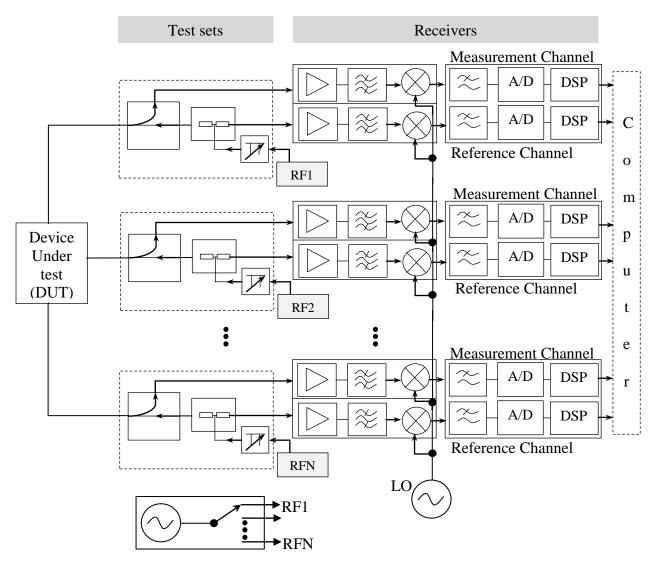

The vector network analyzer (VNA) is one of the most important instruments used to measure S-parameters of active and passive components. It generates a sinusoidal test signal that is applied to the DUT as a stimulus. Considering the DUT to be linear, the analyzer measures the response of the DUT, which is also sinusoidal. Fig 3.1 shows a block diagram of an N-port vector network analyzer which is based on a heterodyne principle [59].

Fig. 3.1 Block diagram of a N-port vector network analyzer [59].

The test set separates incident and reflected waves by using directional couplers. The generator provides the RF signal which referred to as the stimulus.

Each test set combines with two separate receivers for the measurement channel and reference channel. They consist of a RF section, which down converts to IF signals, and a digital signal processing unit.

The computer is used to do the system error correction and displaying measurement data.

A VNA can perform full system error correction to compensate the systematic measurement error of the test instrument.

Before processing with measurement of components, we need to account for the systematic errors in the instrument and losses in the cables, and we also shifted the reference plane of the measurement. This was done by using the calibration process in which a network analyzer measures precisely known calibration standards and stores the vector differences between the measured and the actual values. Some of the calibration standards mostly used are short (S), open (O), load (L), match (M), through (T), reflect (R) and line (L).

The required calibration standard depend on the method of calibration used. There are many calibration methods available. Some of the techniques are TOM, TRM, TRL, TNA, SOLT and UOSM [60]-[62]. In this work we concentrate on the TRL calibration technique in order to measure the active and passive devices.

#### 3.2.2 TRL (THRU – **R**FLECT – **L**INE) Calibration

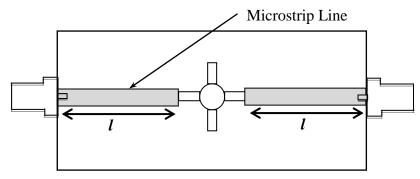

One of the major issues faced when making network analyzer measurements is the need to separate the effects of the transmission medium in which the device is embedded and testing [63]. Also in a microstrip test fixture there is a discontinuity at the coaxial to microstrip transition and also signal can be attenuated along the microstrip line, Fig 3.2. These effects can significantly change the measured data.

Fig. 3.2 Microstrip test fixture structure.

TRL calibration is a commonly used approach in which the calibration can be done until a specified reference plane. It is a THRU – RFLECT – LINE approach which is a 2 - port calibration that relies on transmission lines.

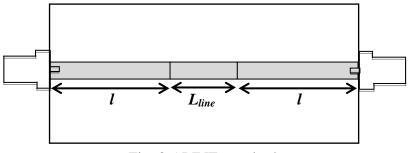

**THRU** – This refers to the connection of port 1 and port 2 directly or with a microstrip line. If a non-zero line is used, the mid-section of the microstrip line will be considered as the reference plane. The characteristic impedance  $Z_0$  of the THRU line should be the same as the line standard. For a test structure similar to Fig 3.2, the THRU line is fabricated by connecting line  $l_1$  and  $l_2$  together as shown in Fig 3.3.

Fig. 3.3 THRU standard.

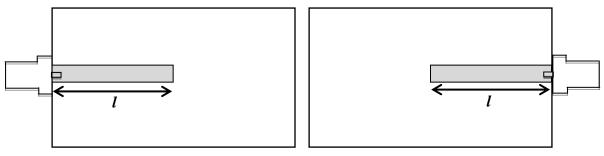

**REFLECT** – This one port standard exhibits a reflection coefficient  $|\Gamma| > 0$ , optimally 1.0. The exact reflection value is not required to know, however, it must be identical at both test ports. The diagram of a REFLECT line is shown in Fig 3.4.

Fig. 3.4 REFLECT standard.

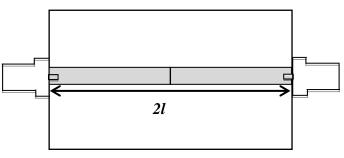

**LINE** – This is a two port standard in which the characteristic impedance of the line needs to be matched precisely possible to the reference impedance. In this standard a line is inserted between the fixture halves as illustrated in Fig 3.5.

Fig. 3.5 LINE standard.

The electrical length of the  $L_{line}$  must be different than the length of the THRU standard used and also the length difference of these lines should not be equal to an integral multiple of half wavelengths since it will increase the measurement uncertainty significantly. Therefore, the frequency range for the calibration standard is restricted, because the phase difference between the two lines must be sufficiently different from 0° and 180° (e.g. it must be between 20° and 180° or the ratio of the stop and start frequencies must have a maximum ratio of 8:1). However, the frequency range of the calibration can be further increased by using multiple line standards.

### Design of the calibration kit

In this work we designed a calibration kit for a frequency range 0.1 - 25 GHz. The length of the THRU line was 5.0 *cm*. Hence, the length of a reflect line was 2.5 *cm*. The substrate definition is shown in Fig 3.6, which is the same substrate used to measure the passive and active elements.

Fig. 3.6 Substrate definition

First, equation (3.1) was used to calculate a LINE with <sup>1</sup>/<sub>4</sub> wavelength at centre frequency and is given by:

$$l = \frac{c}{4f\sqrt{\epsilon_{eff}}} \tag{3.1}$$

Where, c is the speed of light at free space,  $\epsilon_{eff}$  is the effective dielectric constant of the substrate, f is the frequency.

At the centre frequency f = 12.55 GHz, the effective dielectric constant is  $\epsilon_{eff} = 1.915$ . Hence <sup>1</sup>/<sub>4</sub> wavelength is calculated as  $l_{\lambda/4} = 4.32$  mm.

It is necessary to check whether the LINE meets the acceptable insertion phase requirement. The insertion phase of each line is given by

$$\frac{360 \times f \times l}{c} \tag{3.2}$$

Therefore at 0.1 GHz the insertion phase was =  $5.1^{\circ}$ . And at 25 GHz the insertion phase was =  $129.6^{\circ}$

From the above calculation it can be seen that a 4.32 mm line does not meet the required insertion phase which is between  $20^{\circ}$  and  $160^{\circ}$ . This can also be verified by taking the ratio of 0.1 GHz to 25 GHz which is greater than 8. Therefore, the desired frequency span must be divided in to several sections.

Three frequency ranges were selected such that each span has a ratio less than 8. The selected frequency ranges are 0.1 GHz – 0.7 GHz, 0.7 GHz – 4.9 GHz and 4.9 GHz – 25 GHz. Hence, for this calibration kit we have used three lines. The total length of each line was obtained by adding the length of the THRU standard.

For LINE 1, the quarter wavelength at the centre frequency 0.4 GHz was calculated using (3.1) and it is equal to 13.682 *cm*. Therefore, the total length of LINE 1 is 5 *cm* + 13.682 *cm* = 18.682 *cm*.

Similar method is used to calculate the lengths of the other two lines. Table 3.1 below shows a summary of each of the lines calculated.

| Calibration Standard | Frequency Range<br>(GHz) | Length (cm) | Delay (ps) |

|----------------------|--------------------------|-------------|------------|

| THRU                 | 0.1 - 25                 | 5           | 230.6      |

| REFLECT              | 0.1 - 25                 | 2.5         |            |

| LINE 1               | 0.1 - 0.7                | 18.682      | 624.5      |

| LINE 2               | 0.7 - 4.9                | 6.953       | 89.67      |

| LINE 3               | 4.9 - 25                 | 5.361       | 16.7       |

Table 3.1: Calculated length of the TRL calibration kit

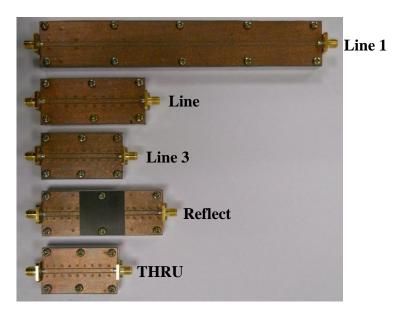

Fig 3.7 shows the fabricated calibration standards.

Fig. 3.7 Fabricated TRL calibration kit.

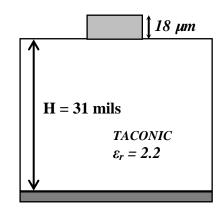

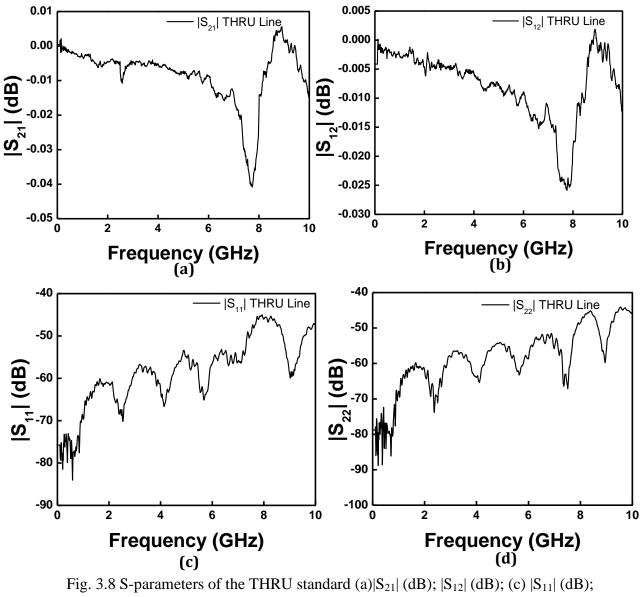

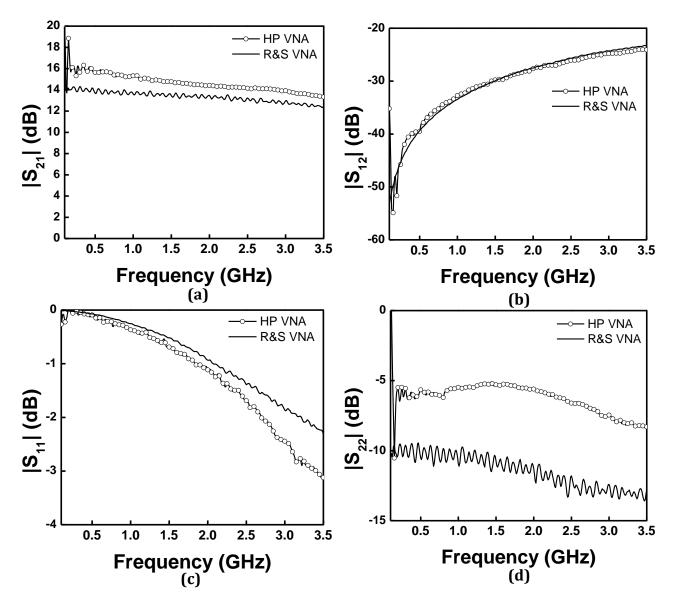

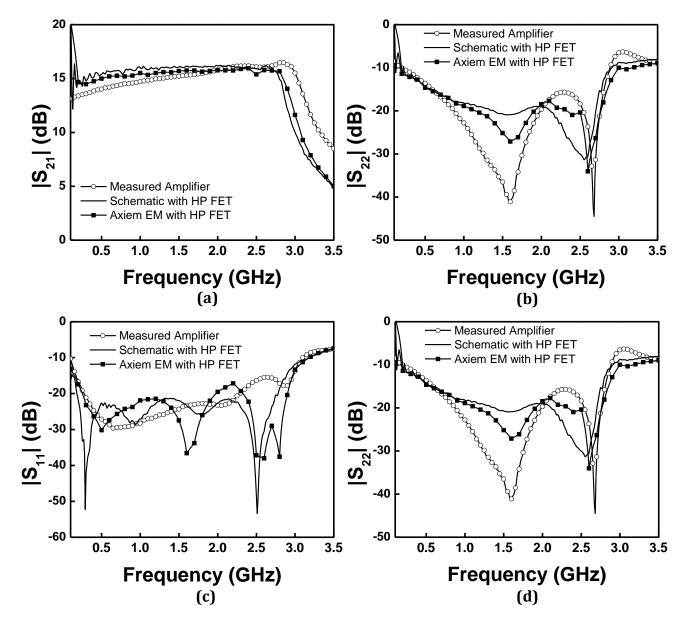

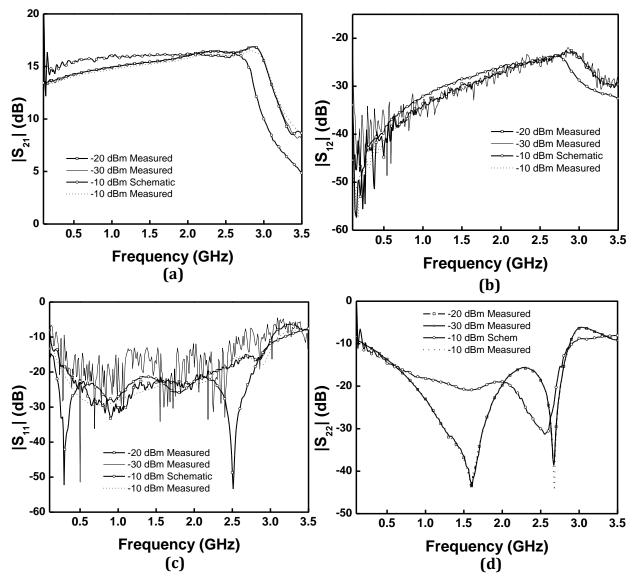

In order to measure the transistor we need to bias it using bias tees. Therefore, calibration was done by adding bias tees in between the test fixture and the coaxial cable. To verify that the calibration was done accurately, we measured the S-parameters of the THRU standard. Fig 3.8 and Fig 3.9 show the measured S-parameters for the THRU standard with and without bias tees respectively. The calibration was conducted using the Rohde & Schwarz ZVA 50 vector network analyzer.

(d)  $|S_{22}|$  (dB).

Theoretically  $|S_{21}|$  and  $|S_{12}|$  of the THRU line should be 0 dB since the effects of the transmission lines are removed after calibration. From the above figure it can be seen that  $|S_{21}|$  and  $|S_{12}|$  of the THRU standard are close to 0 dB between 0.1 GHz and 10 GHz. Furthermore, the input and output reflection coefficients should be as small as possible. In this calibration, the return loss of the THRU standard is better than 45 dB, which is a good input match. Similar results were obtained for the calibration with bias tees.