# A COMPUTING ORIGAMI: OPTIMIZED CODE GENERATION FOR EMERGING PARALLEL PLATFORMS

#### ANDREI MIHAI HAGIESCU MIRISTE

(Dipl.-Eng., Politehnica University of Bucharest, Romania)

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE

NATIONAL UNIVERSITY OF SINGAPORE

## ACKNOWLEDGEMENTS

I am grateful to all the people who have helped me through my PhD candidature. First of all, I would like to extend my deep appreciation to Assoc. Prof. Weng-Fai Wong, who has guided me with enthusiasm in the world of research. Numerous hours of late work, discussions and brainstorming sessions had always been offered when I needed them more.

I have had much to learn from several other professors at the National University of Singapore, including Assoc. Prof. Tulika Mitra, Prof. P. S. Thiagarajan and Prof. Samarjit Chakraborty. Prof. Saman Amarasinghe graciously agreed to be my external examiner, and his feedback was much appreciated. I am also grateful to Prof. Nicolae Tapus from the Politehnica University of Bucharest, who initiated me to academic research.

I would like to mention my closest collaborators from whom I learnt a great amount during these last years. In no specific order, I would like to thank Rodric Rabbah, Huynh Phung Huynh and Unmesh Bordoloi.

Several friends participating in the research program of the university have provided their support, and it will be only fair to mention them here: Cristian, Narcisa, Dorin, Hossein, Ioana, Bogdan, Cristina, Mihai and Chi-Tsai.

On the personal side, I am grateful to my parents Anca and Bogdan, my sister Ioana and my uncle Cristian Lupu for their constant support in pursuing this academic quest. Before I conclude, I would like to thank and wai my wife, who has never let me down, no matter the distance, Hathairat Chanphao.

# TABLE OF CONTENTS

| AC            | KNO         | OWLEDGEMENTS ii                              |

|---------------|-------------|----------------------------------------------|

| $\mathbf{SU}$ | MM          | ARY is                                       |

| LIS           | <b>ST O</b> | F TABLES                                     |

| LIS           | <b>ST O</b> | F FIGURES xii                                |

| 1             | INT         | TRODUCTION                                   |

|               | 1.1         | Code generation                              |

|               | 1.2         | Problem Description                          |

|               | 1.3         | Thesis Overview                              |

|               | 1.4         | Contributions                                |

|               | 1.5         | Outline                                      |

| 2             | BAG         | CKGROUND AND RELATED WORK                    |

|               | 2.1         | StreamIt: A Parallel Programming Environment |

|               |             | 2.1.1 Language Background                    |

|               |             | 2.1.2 Related Work on StreamIt               |

|               |             | 2.1.3 Benchmark Suite                        |

|               | 2.2         | FPGA Architecture                            |

|               |             | 2.2.1 Related Work on FPGA code generation   |

|               | 2.3         | The GPU Architecture                         |

|               |             | 2.3.1 Related Work on GPU code generation    |

| 3             | STF         | REAMIT CODE GENERATION FOR FPGAS 25          |

|               | 3.1         | Rationale                                    |

|               | 3.2         | Code Generation Method                       |

|               |             | 3.2.1 Calculating Throughput                 |

|               |             | 3.2.2 Calculating Latency                    |

|               |             | 3.2.3 HDL Generation                         |

|               | 3.3         | Results                                      |

|               | 3.4         | Summary                                      |

| 4             | STF         | REAMIT CODE GENERATION FOR GPUS 45           |

|               | 4.1         | Rationale                                    |

|               | 4.2         | Code Generation Method                       |

|   |     | 4.2.1 Mapping Stream Graph Executions 51            |

|---|-----|-----------------------------------------------------|

|   |     | 4.2.2 Parallel Execution Orchestration              |

|   |     | 4.2.3 Working Set Layout                            |

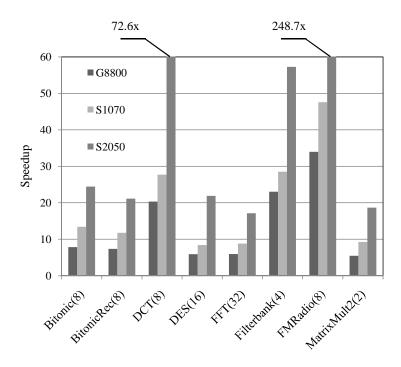

|   | 4.3 | Design Space Characterization for Different GPUs 63 |

|   | 4.4 | Results                                             |

|   | 4.5 | Summary                                             |

| 5 | STI | REAMIT CODE GENERATION FOR MULTIPLE GPUS 73         |

|   | 5.1 | Code Generation Method                              |

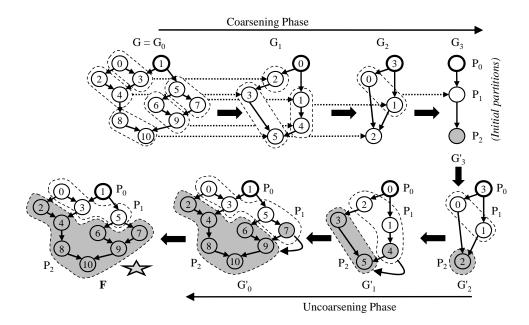

|   | 5.2 | Partitioning of the Stream Graph                    |

|   |     | 5.2.1 Coarsening Phase                              |

|   |     | 5.2.2 Uncoarsening Phase                            |

|   | 5.3 | Execution on Multiple GPUs                          |

|   |     | 5.3.1 Communication Channels 82                     |

|   |     | 5.3.2 Mapping Parameters Selection                  |

|   | 5.4 | Results                                             |

|   | 5.5 | Summary                                             |

| 6 | FLO | OATING-POINT SIMD COPROCESSORS ON FPGAS 93          |

|   | 6.1 | Rationale                                           |

|   | 6.2 | Co-design Method                                    |

|   | 6.3 | Customizable SIMD Coprocessor Architecture 103      |

|   |     | 6.3.1 Instruction Handling                          |

|   |     | 6.3.2 Folding of SIMD Operations                    |

|   |     | 6.3.3 Memory Access                                 |

|   | 6.4 | Performance Projection Model                        |

|   | 6.5 | Configuration Selection and Code Generation         |

|   | 6.6 | Results                                             |

|   | 6.7 | Summary                                             |

| 7 | FIN | NE-GRAINED CODE GENERATION FOR GPUS 121             |

|   | 7.1 | Rationale                                           |

|   | 7.2 | Application Description                             |

|   | 7.3 | Code Generation Method                              |

|   | 7.4 | Results                                             |

|   | 7.5 | Summary                                             |

| 8              | $\mathbf{CO}$ | NCLU   | SIO | NS  |              |    |    |              |          |   |          |   |   |    |    |    |    |    |    |    |              |  |  |  | • | 135        |  |

|----------------|---------------|--------|-----|-----|--------------|----|----|--------------|----------|---|----------|---|---|----|----|----|----|----|----|----|--------------|--|--|--|---|------------|--|

|                | 8.1           | Future | Wo  | k . |              |    |    |              |          |   |          |   |   |    |    |    |    |    |    |    |              |  |  |  |   | 137        |  |

|                |               | 8.1.1  | FPO | GΑ  |              |    |    |              |          |   |          |   |   |    |    |    |    |    |    |    |              |  |  |  |   | 137        |  |

|                |               | 8.1.2  | GP  | U.  |              |    |    |              |          |   |          |   |   |    |    |    |    |    |    |    |              |  |  |  |   | 138        |  |

| $\mathbf{Bib}$ | liogr         | aphy   |     |     |              |    |    |              |          |   |          |   |   |    |    |    |    |    |    |    |              |  |  |  |   | 139        |  |

| $\mathbf{AP}$  | PEN           | DIX A  |     |     | $\mathbf{A}$ | DΙ | ΟI | $\mathbf{T}$ | <b>O</b> | N | <b>A</b> | L | B | Εľ | V( | CF | IN | ΊA | 4I | RK | $\mathbf{S}$ |  |  |  |   | <b>153</b> |  |

# **PUBLICATIONS**

Publications related to this thesis:

- A Computing Origami: Folding Streams in FPGAs. Andrei Hagiescu, Weng-Fai Wong, David F. Bacon and Rodric Rabbah. Design Automation Conference (DAC), 2009

- Co-synthesis of FPGA-Based Application-Specific Floating Point SIMD Accelerators. Andrei Hagiescu and Weng-Fai Wong. International Symposium on Field Programmable Gate Arrays (FPGA), 2011

- Automated architecture-aware mapping of streaming applications onto GPUs. Andrei Hagiescu, Huynh Phung Huynh, Weng-Fai Wong and Rick Siow Mong Goh.

International Parallel and Distributed Processing Symposium (IPDPS), 2011

- Scalable Framework for Mapping Streaming Applications onto Multi-GPU Systems. Huynh Phung Huynh, Andrei Hagiescu, Weng-Fai Wong and Rick Siow Mong Goh. Symposium on Principles and Practice of Parallel Programming (PPoPP), 2012

#### Other publications:

- Performance analysis of FlexRay-based ECU networks. Andrei Hagiescu, Unmesh

D. Bordoloi, Samarjit Chakraborty et al. Design Automation Conference (DAC),

2007

- Performance Debugging of Heterogeneous Real-Time Systems. Unmesh D. Bordoloi, Samarjit Chakraborty and Andrei Hagiescu. Next Generation Design and Verification Methodologies for Distributed Embedded Control Systems, 2007

## **SUMMARY**

This thesis deals with code generation for parallel applications on emerging platforms, in particular FPGA and GPU-based platforms. These platforms expose a large

design space, throughout which performance is affected by significant architectural idiosyncrasies. In this context, generating efficient code is a global optimization problem.

The code generation methods described in this thesis apply to applications which expose

a flexible parallel structure that is not bound to the target platform. The application is

restructured in a way which can be intuitively visualized as *Origami* (the Japanese art

of paper folding).

The thesis makes three significant contributions:

- It provides code generation methods starting from a general stream processing language (StreamIt) for both FPGA and GPU platforms.

- It describes how the code generation methods can be extended beyond streaming applications to finer-grained parallel computation. On FPGAs, this is illustrated by a method that generates configurable floating-point SIMD coprocessors for vectorizable code. On GPUs, the method is extended to applications which expose fine-grained parallel code accompanied by a significant amount of read sharing.

- It shows how these methods can be used on a platform which consists of multiple GPU devices connected to a host CPU.

The methods can be applied to a broad range of applications. They go beyond mapping and provide tightly integrated *code generation* tools that handle together high-level mapping, code rewriting, optimizations and modular compilation. These methods target FPGA and GPU platforms without requiring user-added annotations. The results indicate the efficiency of the methods described.

# LIST OF TABLES

| 2.1 | Benchmark characterization                                                                                                  | 17  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Example latency calculation                                                                                                 | 37  |

| 3.2 | Design points generated for maximum throughput and under resource and latency constraints                                   | 42  |

| 4.1 | The versatility of the code generation method                                                                               | 71  |

| 6.1 | Characteristics of execution units                                                                                          | 109 |

| 6.2 | Execution time and energy                                                                                                   | 118 |

| 7.1 | Biopathway models                                                                                                           | 130 |

| 7.2 | Comparative performance of a cluster of CPU to multiple GPUs.                                                               | 132 |

| 7.3 | Performance of the fine-grained method, compared to a naïve GPU implementation, for trajectories generated on a single GPU. | 132 |

| 7.4 | Optimized SM configuration for the presented models                                                                         | 133 |

# LIST OF FIGURES

| 1.1  | Improving code generation under resource constraints. The resource utilization is suggested by the area of the corresponding boxes                                                                                                                                                              | 3  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Thesis road map                                                                                                                                                                                                                                                                                 | 7  |

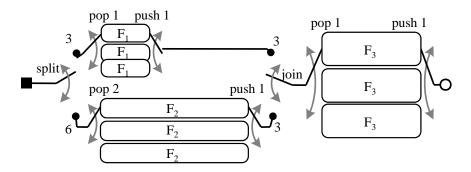

| 3.1  | An example stream graph                                                                                                                                                                                                                                                                         | 28 |

| 3.2  | A stream graph with replicated filters that achieves maximum throughput, subject to resource constraints                                                                                                                                                                                        | 29 |

| 3.3  | Reducing the latency for the graph in Figure 3.2 under the same resource constraints                                                                                                                                                                                                            | 31 |

| 3.4  | Schedule used to determine latency. Six data tokens arrive every interval $p.$ With two replicas, computation occurs in parallel                                                                                                                                                                | 37 |

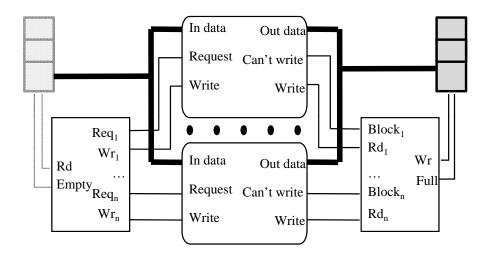

| 3.5  | Hardware structure of the replication mechanism                                                                                                                                                                                                                                                 | 38 |

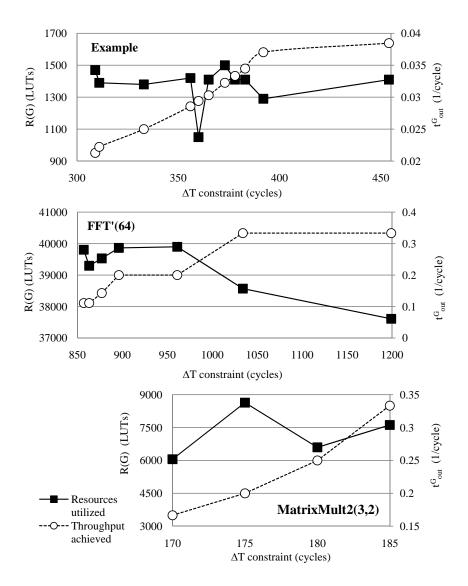

| 3.6  | Design space exploration with a maximum resource constraint. The latency constraint is relaxed, hence the throughput can increase. The actual resource usage is influenced by both throughput and latency.                                                                                      | 40 |

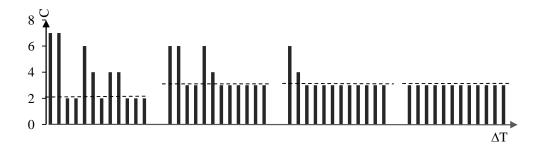

| 3.7  | FFT design points with increasing latency. Sets of bars represent replication factors for instances of filter $CombineDFT$ belonging to each design point. The dotted line separates the replication that ensures a specific throughput (below) from that necessary to decrease latency (above) | 41 |

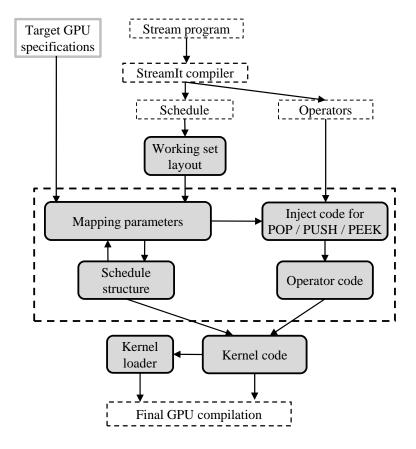

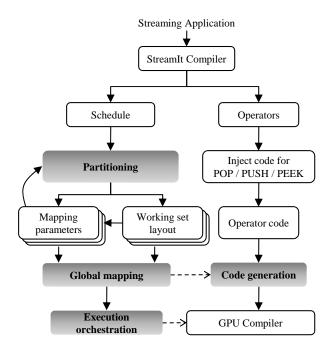

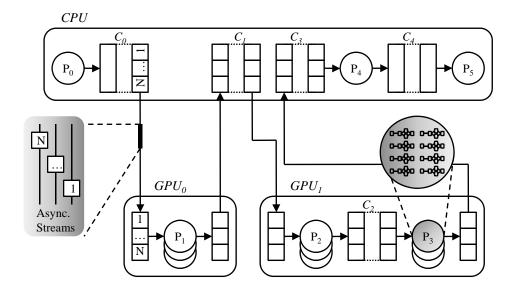

| 4.1  | The code generation method                                                                                                                                                                                                                                                                      | 50 |

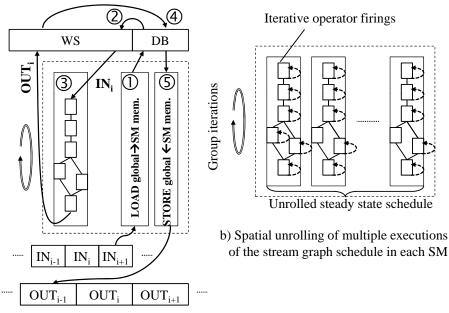

| 4.2  | Parallel memory access and orchestration of the stream graph                                                                                                                                                                                                                                    | 51 |

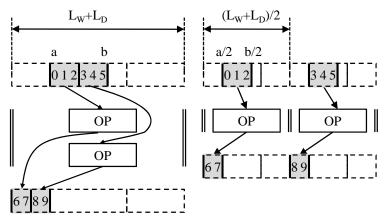

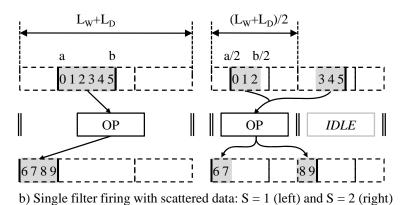

| 4.3  | Memory layout transformation examples                                                                                                                                                                                                                                                           | 54 |

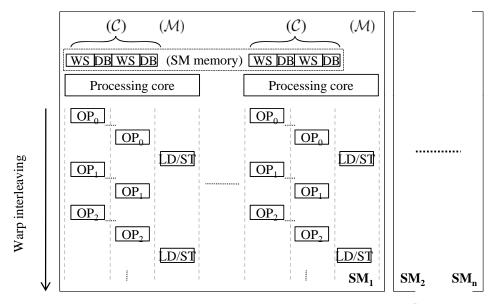

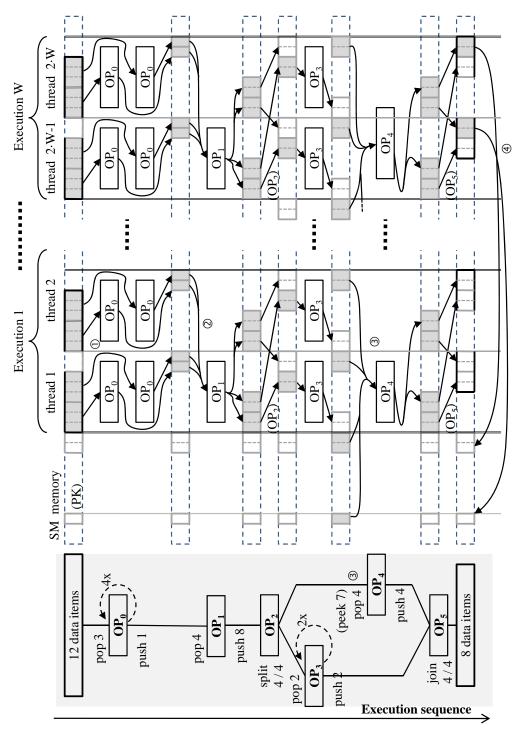

| 4.4  | Example of the orchestration for a single group iteration. Two $\mathcal{C}$ threads are assigned to each of the $W$ parallel executions of the stream graph                                                                                                                                    | 56 |

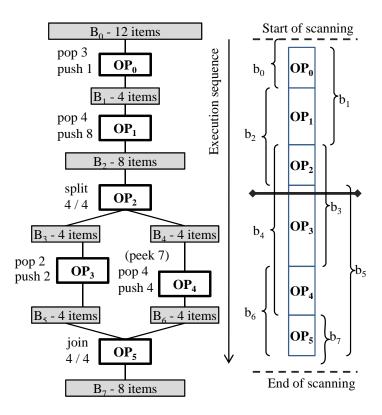

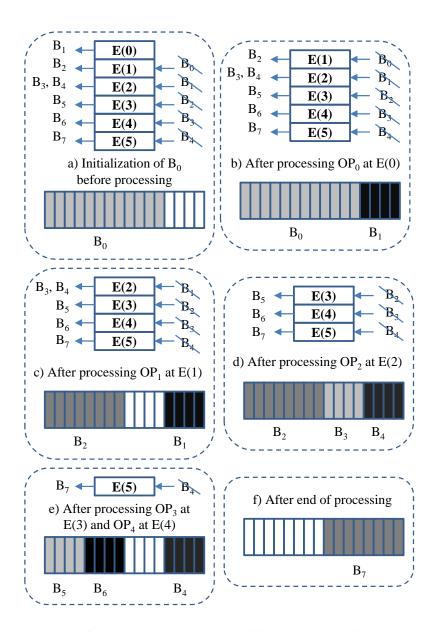

| 4.5  | Liveness and lower bound analysis on working set size                                                                                                                                                                                                                                           | 59 |

| 4.6  | Working set allocation example                                                                                                                                                                                                                                                                  | 61 |

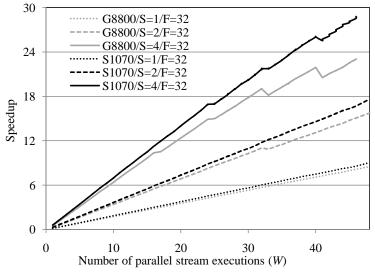

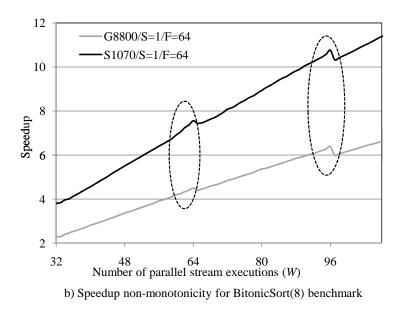

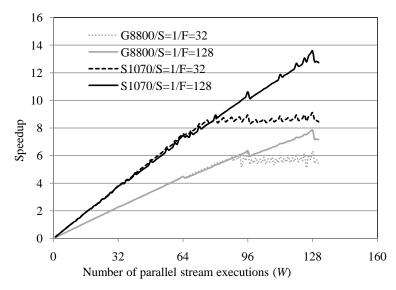

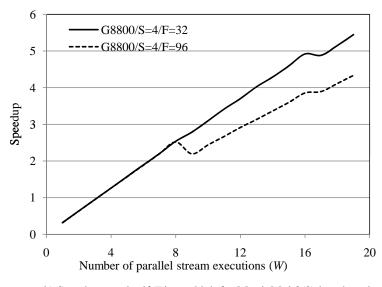

| 4.7  | Characterizing the design space                                                                                                                                                                                                                                                                 | 65 |

| 4.8  | The trade-offs for $F$ , the number of $\mathcal M$ threads                                                                                                                                                                                                                                     | 66 |

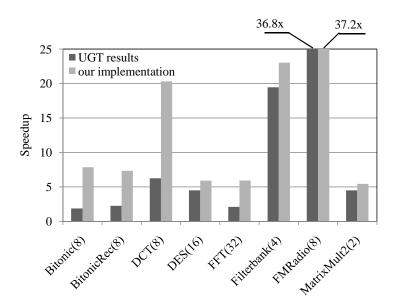

| 4.9  | The comparison between $UGT$ and this method                                                                                                                                                                                                                                                    | 68 |

| 4.10 | The versatility of the code generation method                                                                                                                                                                                                                                                   | 70 |

| 5.1  | Scalable code generation method                                                                                                                                                                                                                                                                 | 75 |

| 5.2 | Illustration of Multi-Level Graph Partitioning. The dashed lines show the projection of a vertex from a coarser graph to a finer graph                                                                                                                                                        | 78   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.3 | Execution and data transfer among partitions on a multi-GPU system                                                                                                                                                                                                                            | 83   |

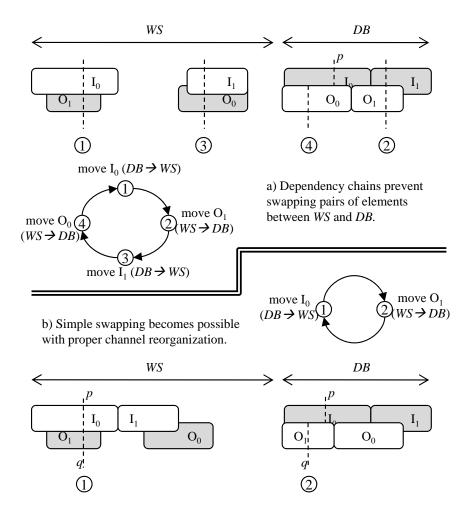

| 5.4 | Execution snapshot showing the challenges of partition I/O handling. The inputs for the next iteration have to swap with the outputs of the previous iteration                                                                                                                                | 86   |

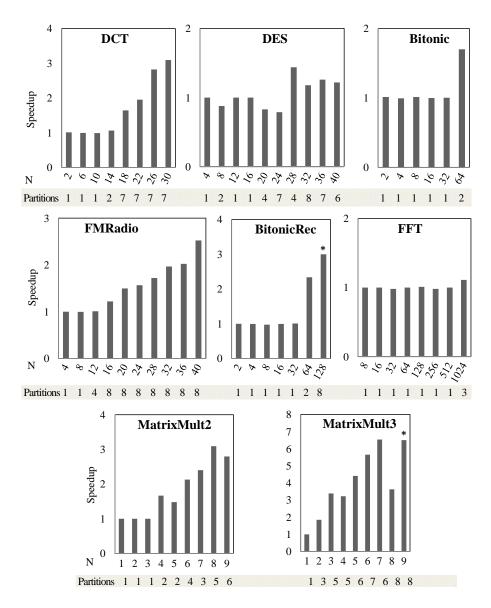

| 5.5 | Mapping to a single partition and to multiple partitions (the number of partitions is listed under the graphs) on a single GPU. The speedup is the execution time ratio between the two. Design points marked with (*) were not supported by the single partition implementation in Chapter 4 | 88   |

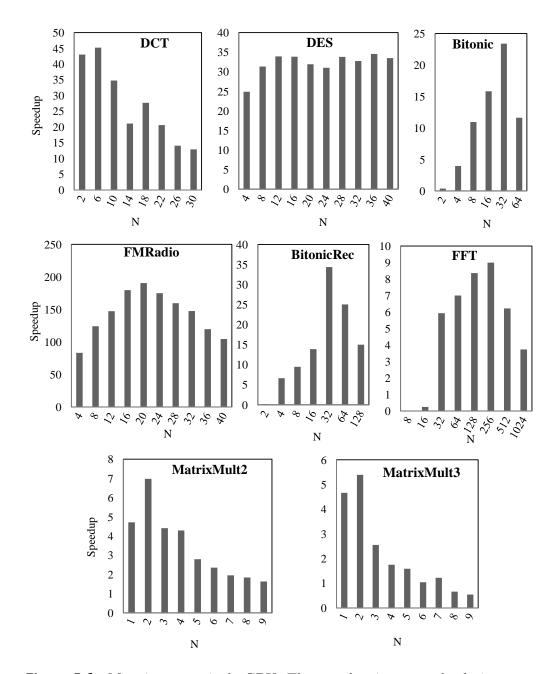

| 5.6 | Mapping to a single GPU. The speedup is reported relative to a CPU implementation                                                                                                                                                                                                             | 90   |

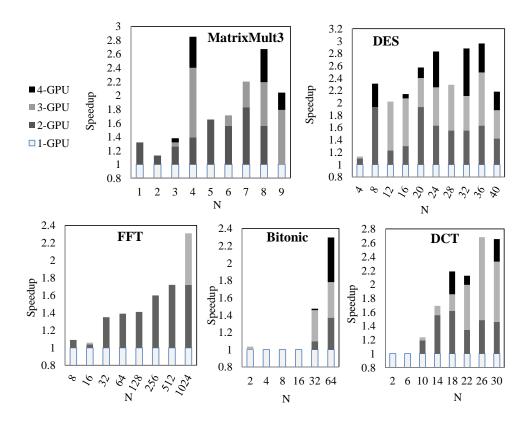

| 5.7 | Additional speedup resulted from the mapping to multiple GPUs compared to a single GPU                                                                                                                                                                                                        | 91   |

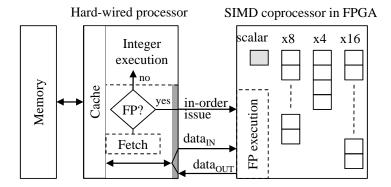

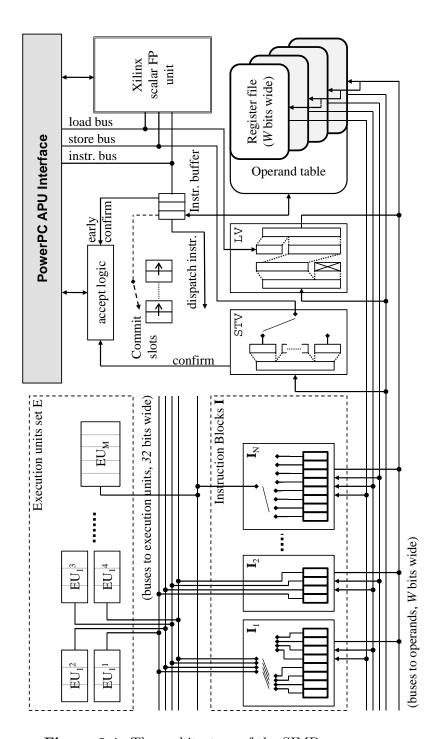

| 6.1 | The target architecture configuration                                                                                                                                                                                                                                                         | 95   |

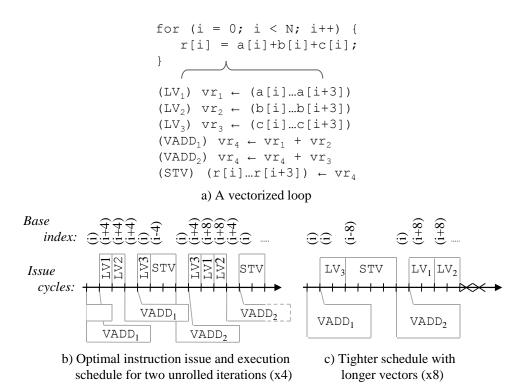

| 6.2 | Executing a loop using x4 and x8 vector instructions                                                                                                                                                                                                                                          | 99   |

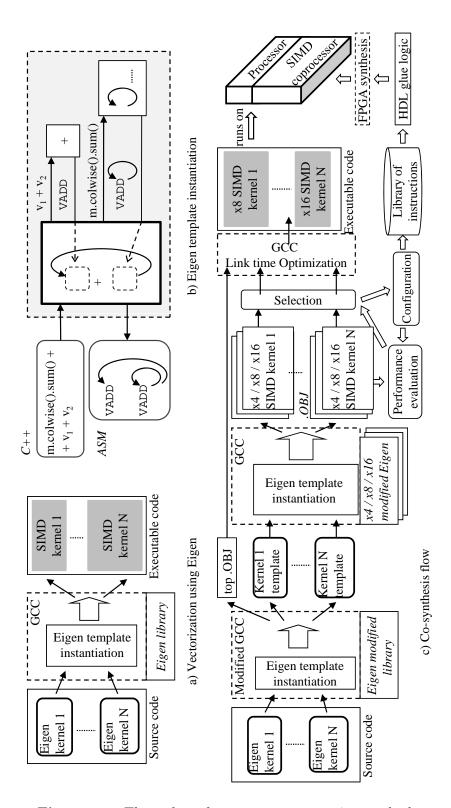

| 6.3 | The code and coprocessor generation method                                                                                                                                                                                                                                                    | 102  |

| 6.4 | The architecture of the SIMD coprocessor                                                                                                                                                                                                                                                      | 105  |

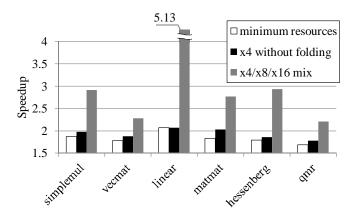

| 6.5 | Speedup of different design points compared to scalar FP execution                                                                                                                                                                                                                            | .115 |

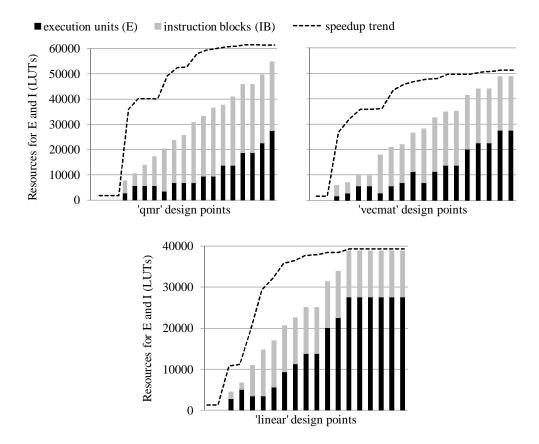

| 6.6 | Resources used by execution units vs. instructions throughout the design space                                                                                                                                                                                                                | 116  |

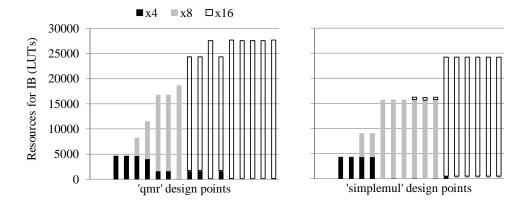

| 6.7 | Distribution of resources among x4, x8 and x16 instructions for 'qmr'                                                                                                                                                                                                                         | 117  |

| 7.1 | Computation flow                                                                                                                                                                                                                                                                              | 125  |

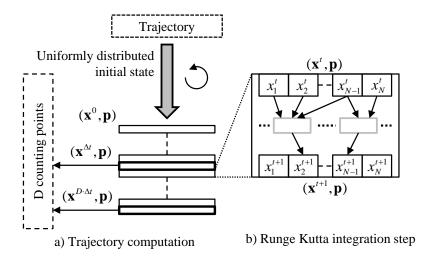

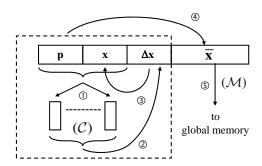

| 7.2 | Data movement during trajectory generation and counting steps.                                                                                                                                                                                                                                | 126  |

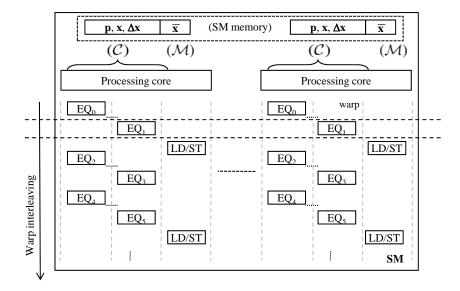

| 7.3 | Concurrent execution of trajectories inside an SM                                                                                                                                                                                                                                             | 127  |

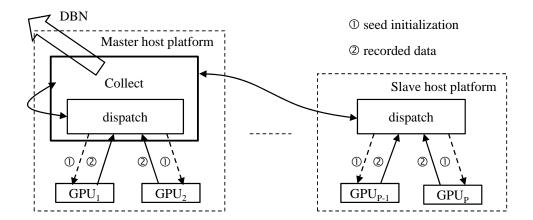

| 7.4 | Distributed execution among multiple GPUs                                                                                                                                                                                                                                                     | 129  |

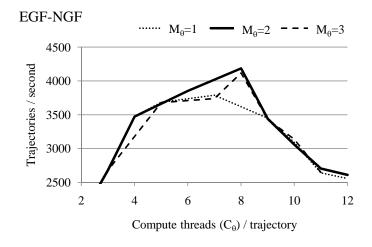

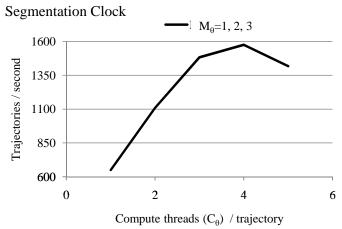

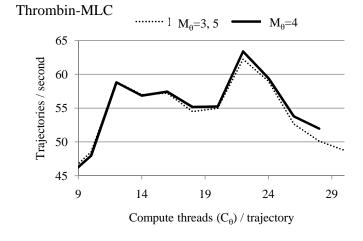

| 7.5 | Design space exploration on the S2050 GPU                                                                                                                                                                                                                                                     | 131  |

# CHAPTER 1

## INTRODUCTION

This thesis describes high-level code generation methods which connect mapping, code rewriting, optimizations and modular compilation in an integrated approach. In particular, it describes code generation methods for two promising parallel platforms that have emerged in mainstream computing: Field Programmable Gate Arrays (FPGAs) and Graphic Processing Units (GPUs).

Both FPGA and GPU platforms tightly integrate a large number of parallel processing units. This results in lower communication overhead [2, 39], which favors the execution of a broader spectrum of parallel applications [15, 71]. However, complex architectural constraints, inherent in these platforms, prevent the mapping of the parallel computation expressed through the application code, in a straight-forward manner, to the processing units.

This thesis shows that it is beneficial to combine the mapping step with the subsequent compilation step in an integrated approach. The thesis describes code generation methods for applications that expose a flexible program structure. The methods use either the coarse-grained parallel structure exposed by the StreamIt language, or the fine-grained parallel structure derived from the application code. In both cases, the experiments show the suitability of the proposed methods.

# 1.1 Code generation

In general, code generation consists of a series of sequential transformation steps. The first step is to map the application structure to the platform. Then, the application undergoes an intermediate code rewriting step which commits the mapping results and converts the application code to a program representation supported by the platform compiler. Eventually, the rewritten application

undergoes the final *compilation*. During each step, additional *optimizing* transformations are applied, based on the projected effect of these transformations. Some of the high-level application structure is likely to be discarded during the optimization process. Mapping and optimization decisions can not be unrolled thereafter, even if it becomes obvious, after compilation, that the application would benefit from them.

This problem becomes increasingly relevant, as the parallel platforms evolve, because the level of application abstraction is rising steadily. In order to cover a larger number of alternative platforms, the code representation tends to abstract more platform details and eventually to become platform independent [64]. Therefore, good execution performance relies heavily on the decisions taken during the mapping step, and how this step closes the gap between the abstract code structure exposed by the programmer and the target platform architecture.

FPGAs and GPUs have emerged as lead competitors in the parallel application domain. Both are characterized by shortened development cycles and increased platform variability [7]. Therefore, mapping on these platforms can not benefit from comprehensive performance projection models, similar to more matured architectures [86, 87]. This impedes application portability and clutters the accuracy of the mapping decisions.

As a workaround, current mapping tools often rely on a significant amount of user-added annotations [48, 66, 67, 72, 102] that drive the solution selection for each target platform. Using annotations reduces the inherent complexity of the mapping step for these platforms. As the platform architecture may handle hundreds of parallel threads with complex resource constraints, the annotations complement the mapping algorithms and provide guidelines for global decisions spanning the entire design space. However, the annotations are platform specific and nontrivial to assert.

Also, because mapping precedes compilation, the mapping decisions can not always capture the side effects of compilation on the performance and resource utilization of the mapped application. For example, resource sharing during compilation can decrease total resource usage, while it may introduce inter-task

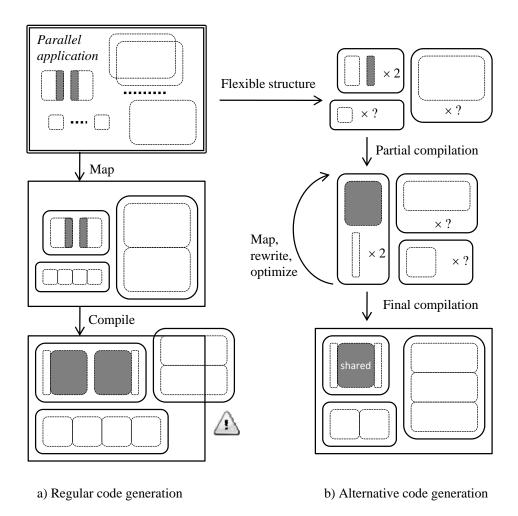

**Figure 1.1:** Improving code generation under resource constraints. The resource utilization is suggested by the area of the corresponding boxes.

dependencies, which lead to serial execution. Significant effort has been invested in developing new programming models and compilation methods, which can expose the platform structure and steer developers to write their code in a way that improves mapping [26, 48, 79, 90]. Usually, the developer is encouraged to write modular code that corresponds to parallel tasks which can be compiled independently. In addition, the programming models may structure data placement, often separating the computation from communication. Using these dedicated models eases the mapping to particular platforms and hides many of the platform idiosyncrasies from the user.

Consequently, current mapping tools seldom modify the structure of the program parallelism expressed by the user through the programming model. This is based on the assumptions that: (1) the programmer has gone the extra step to

ensure that all the available parallel computation is exposed, and (2) exactly that parallel structure was determined by the user to be beneficial. Unfortunately, applications are often ported to different platforms, and a certain amount of design restructuring and application tuning [67] is usually apparent after compilation, once the resource usage becomes evident, either to match the platform resources, or to match the actual degree of parallelism that maximizes the performance of the compiled application on the target parallel platform. However, after compilation, the application representation is usually flattened, and it is beyond the ability of the current code generation methods to modify the parallel structure of the application without user intervention.

While multiple design points can be manually or semi-automatically explored, large performance variability prevents proper pruning of the design space. Therefore, the adequate set of mapping and optimization decisions taken during the high-level stages of the compilation leads to a challenging problem, which affects the outcome of the entire compilation process.

# 1.2 Problem Description

The mapping of applications to FPGAs and GPUs is dictated by the availability of certain key resources. However, the resource usage is commonly available only as a result of the compilation step. Attempts to model resource consumption have only limited success due to the complexity of the platforms involved. In this context, disjoint mapping and compilation may lead to sub-optimal performance of the automatically generated code. Specific architectural and resource constraints on these platforms exacerbate this problem. Hence, it is important to identify methods to generate optimized code while considering these constraints.

Figure 1.1a illustrates an intuitive perspective of the problem described above, as it appears in regular code generation methods. The resources utilized by the code blocks, as well as the resources made available by the platform, are indicated by the area of the corresponding boxes. The parallel application is first mapped using a model of the target platform. Because the mapping is

done as a separate step, at the beginning of code generation, further optimization, code rewriting and compilation can lead to an entirely different outcome, in terms of resource usage, than the one predicted by the mapping decisions. The model may lack accuracy or may not capture the complete interactions between parallel compute blocks (i.e. resources shared between FPGA blocks, or serialization of parallel threads on GPU). After compilation, any inaccuracy of the original mapping model leads to a mismatch in terms of resource usage, which translates to infeasible or poor performance designs.

On FPGAs [1, 61], a common instance of this problem is related to the resource usage of each code block when implemented in reconfigurable hardware. To achieve the greatest performance, it is desirable to use most of the reconfigurable resources. However, mapping is usually overly conservative in terms of resources, because the compilation outcome can not be easily predicted, and exceeding the number of available resources leads to infeasible solutions.

On GPUs [3, 67], this problem is related to the size of fast on-chip memories. Because these memories are small, the size of the working set of each thread determines the feasibility of its placement in these memories. As this size is determined only during compilation, mapping may conservatively confine it to a large long-latency memory. The mapping then determines that an increased number of threads is necessary to offset the memory access delay, but this often leads to memory bandwidth saturation. Faster but small memories could be used if the total memory requirement of all threads is known.

#### 1.3 Thesis Overview

This thesis describes code generation methods leading to design points that maximize performance subject to platform constraints. As previously explained, it is often too late to restructure the application after the compilation step. Hence, it is beneficial to preserve the flexibility exposed initially through the program structure, especially the information that captures the parallel structure of the computation. During code generation, the original computation blocks can be compiled separately. The resource information from each block can be further

utilized to adequately map the pre-compiled blocks of the application, in order to match the constraints of the underlying architecture.

Throughout this thesis, the code generation steps are reorganized as shown in Figure 1.1b. The flexibility in the application structure is preserved beyond an initial partial compilation. Consequently, the application structure can be modified during the iterative mapping and optimization steps. Finalizing the mapping decisions and committing the application structure are deferred until the final compilation. These additional restructuring opportunities can enhance the accuracy of resource utilisation. Including the mapping step into an integrated code generation method is a major departure from the traditional code generation, where mapping precedes compilation.

Data flow computing or streaming programming models are suitable to express applications in a platform independent manner [12, 84]. These models also expose a tremendous amount of parallel code structure. For both GPUs and FPGAs, there are significant opportunities for performance improvement if the code generation starts from a streaming programming model which exposes a flexible application structure. StreamIt [84], a recent hierarchical streaming language, has been selected as an input programming model, without loss of generality. Among the major advantages of using this language, the most relevant are its high level of abstraction, its finer granularity, expressiveness and possibility to use complex structured communication primitives. Its hierarchical structure naturally augments the flexibility in reorganizing the application.

Alternative stream programming models capture an increasing range of applications [73]. A relevant, recent example is the OpenCL programming model [48], which was originally designed for CPU-GPU platforms, and which is now extended to target FPGAs. If this succeeds, it will provide an alternative streaming model which supports the same target platforms as the methods described in this thesis. However, OpenCL provides a weaker semantics for communication between computation blocks, and this penalizes global transformations of the application structure.

This thesis describes code generation methods that start from the StreamIt

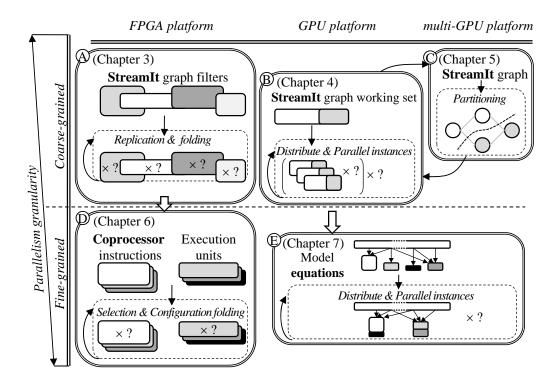

Figure 1.2: Thesis road map.

parallel application representation and target FPGA and GPU devices. The GPU code generation method also supports multiple GPU devices connected to a host CPU. Large amounts of *coarse-grained* parallelism is extracted from the StreamIt programming language. This parallelism is exposed through parallel and pipelined filters in the stream graph representation, and also extracted from the execution model.

The methods described in this thesis are extended to finer-grained parallelism usually exposed by specialized models and libraries. Fine-grained parallelism can be identified by the processor at run-time, or it may be exposed by the compiler, through SIMD or VLIW instructions. Significant hardware resources are required to identify parallel instructions in the former case, and yet the amount of parallel operations identified at run-time is affected by how the compiler schedules the code instructions. Usually a mix of platform and compiler support is required to fully utilize this type of parallelism. Based on this observation, this thesis employs an algebra library to expose fine-grained parallelism in vectorizable code, and describes an FPGA-based code generation method that generates custom floating-point SIMD coprocessors which utilise

the exposed parallelism. Complementary, on GPU, the thesis shows how to utilise the fine-grained parallelism exposed by a set of equations backed by a shared working set, and describes a method that generates code to support the parallel execution of these equations.

Although seemingly unrelated, FPGAs and GPUs share a number of similar characteristics from the point of view of this thesis. The most noteworthy of these is their ability to support broad parallelism with tightly coupled threads. The granularity of these threads also covers a large spectrum of applications. For both platforms, these advantages are throttled by tight resource constraints which have to be accounted during code generation.

## 1.4 Contributions

This thesis proposes a novel approach to integrate mapping and platform-specific compilation to maximize performance for FPGAs and GPUs. Figure 1.2 indicates how the code generation strategy described in Figure 1.1b is projected to the target platforms. It also indicates the parallel granularity of each contribution. The following is a list of contributions included in this thesis:

- (A) a novel code generation method for FPGA platforms [38], which starts from a StreamIt graph, and determines the amount of *replication* and *folding* for the graph filters, such that it maximizes the throughput of the application under global resource and latency constraints; this approach utilises coarsegrained parallelism exposed by the StreamIt graph.

- (B) the first code generation method for GPU platforms [36] which introduces heterogeneous threads in order to cope with resource limitations. This method takes into account the tight memory constraints of the platform and determines how many parallel instances of the StreamIt graph can store their working set in memory, and how to distribute the execution of these instances, as well as their working set, in order to increase the throughput.

- (C) a scalable extension of the above method, which targets a platform containing multiple GPUs connected to a host CPU [43]; this extension relies

1.5. Outline 9

on the single GPU method to determine a feasible set of *partitions*; this method lifts most of the limitations that appear in the single GPU version.

- (D) a novel co-design method which analyses the fine-grained parallelism available in vectorizable code, and generates a configurable SIMD floating-point coprocessor that boosts application performance. The customization is the first to allow coexisting vectors with different lengths. The proposed method selects which vector instructions are supported, and how their operations are folded onto a custom configuration of execution units [37].

- (E) an improved code generation method that analyses both the coarse-grained as well as the fine-grained parallelism exposed by a systems biology application, maps *parallel instances* of this application, and *distributes* fine-grained code blocks to a set of threads which share a common working set.

# 1.5 Outline

Chapter 2 provides a detailed background of existing code generation solutions for the platforms of interest. This chapter also includes details regarding the StreamIt language. Chapter 3 presents the first method that applies to StreamIt code generation for FPGA platforms. The next chapter presents a method that generates GPU code for StreamIt. This method can be extended to a multi-GPU platform as described in Chapter 5, with emphasis on scalability. This is followed in Chapter 6 by a FPGA contribution, complementary to that in Chapter 3, for finer-grained parallelism, that generates SIMD coprocessors for the FPGA platform. To justify the generality of the method introduced in Chapter 4, Chapter 7 presents code generation for a model exposing finer-grained parallelism. Chapter 8 concludes this thesis.

# CHAPTER 2

## BACKGROUND AND RELATED WORK

Chapter 1 indicated that the streaming programming model exposes a significant amount of parallelism that can be used for efficient code generation. Indeed, previous research shows that streaming programming languages [9, 12, 27] have been successfully utilized to describe applications for parallel platforms. This chapter presents relevant work related to code generation for StreamIt applications. Background regarding the StreamIt language and previous code generation attempts are described in Section 2.1.

This thesis describes code generation methods for the FPGA and GPU platforms. Therefore, this background chapter provides a description of the architecture of each of these platforms. Exposing a reconfigurable structure, the FPGA architecture has been actively used by the research community in application acceleration, by implementing either custom processors or dedicated computation blocks. FPGA circuits are prone to implement applications with a high degree of parallelism, but are subject to tight capacity (resource utilisation) constraints. Relevant work on automatically generated code for FPGAs is presented in Section 2.2.

The GPU architecture follows a different paradigm. It can also handle applications with a high degree of parallelism, but it imposes tight constraints on the resources shared by the parallel threads. Due to the complexity involved, modeling and experimentation have been the norm in writing efficient applications. Because actual GPU code performance is difficult to estimate, automatic generation of efficient code has raised increased interest in the research community, as shown in Section 2.3.

# 2.1 StreamIt: A Parallel Programming Environment

Stream processing is a data-centric execution model which represents an important class of applications that spans telecommunications, multimedia and the Internet. The compilation of the streaming programs has attracted significant attention because of the parallelism they expose. Languages, tools, and even custom hardware for streaming have been proposed, some of which are commercially available.

The StreamIt language [84] is a hierarchical streaming programming language and infrastructure built upon the experience of a large spectrum of previous streaming languages such as Lustre [14], Esterel [9], Brook [12], Streams-C [27], etc. StreamIt is built on top of the synchronous data flow model [52].

#### 2.1.1 Language Background

StreamIt was designed to expose the parallel and pipelined nature of the streaming applications. The high-level structure of a StreamIt program is a hierarchical graph whose leaf nodes are *filters* which communicate through data channels. Filters can be combined to execute in *pipelines*. The flow of data can be distributed using *splitters* and *joiners* that describe parallel execution paths in the application. These constructs expose coarse-grained parallelism in the application.

Filters are written in C-like code with special constructs to access their input and output channels. A filter consumes data from an input channel using pop constructs and produces data on the output channel using push constructs. An example filter declaration, with different input and output data rates, is filter F1 in the example below.

This example includes a pipeline P1 which connects the output of filter F1 to a subsequent splitter. This splitter and a joiner are encapsulated in a *splitjoin* construct. The splitter is instructed to route alternative elements, using a roundrobin scheme, to the pipelines P2 and P3 which it encapsulates. The results of the pipelines are combined, in the same order, to form the output of the splitjoin construct. An alternative splitter policy exists, where all the paths duplicate the same data.

```

int->int filter F1(int N) {

work pop N push N/2 {

for (int i = 0; i < N/2; i++) {

int x = pop(); // read/dequeue from input FIFO

int y = pop();

push(x-y);

// write/enqueue to output FIFO

}

}

}

int->float pipeline P1() {

add F1(2);

add splitjoin {

split roundrobin(1,1);

add P2();

add P3();

join roundrobin(1,1);

}

}

```

The StreamIt compiler flattens the hierarchical stream program to a set of base operators (filters, splitters and joiners). It produces a schedule that consists of a sequence of operators, and the number of times they are executed (fired). Note that multiple firings may be necessary, because filters are allowed to have non-matching input and output rates and hence the elements produced by one filter's firing may require multiple firings of the consumer filter. These multiple firings describe data parallelism in the streaming application. In the above example, as F1 produces a single element, the derived execution schedule must include pairs of executions of F1, in order to produce one element for each of the two subsequent pipelines P2 and P3.

The schedule may require an initialization part which is executed once when

the program is launched. Apart from the initialization part, the resulting schedule consists of a steady-state component that can be executed as many times as required to process all the given input.

Dependencies between filters are made explicit by the communication channels. Each filter has its own control logic and an independent address space, and it executes repeatedly as long as a sufficient number of tokens are available on its input channels. However, the filters have the capability to *peek* data from the input channel beyond what they are going to consume. This feature allows structured data dependencies between consecutive filter firings. Peeking is useful for sliding-window computations, and provides an opportunity to rewrite filters that otherwise require internal state to preserve previous values.

A few features in StreamIt may introduce unstructured data dependencies which would prevent parallel code generation. Their usage is not supported by the code generation methods described in this thesis. These features include feedback loops and portals, which create cycles in the stream graph. If these constructs are eliminated, the stream graph can always be flattened to an acyclic directed graph. The code generation methods also require filters with statically defined rates in order to derive the schedules statically.

#### 2.1.2 Related Work on StreamIt

Since its introduction [84], StreamIt has been ported to several distinct platforms. The parallelism it exposes makes it a natural candidate for programming parallel platforms. Each filter in StreamIt declares its data input and output rates. This explicit information enables many optimizations that can yield efficient implementations of the stream computation onto platforms with a high degree of parallelism.

The Raw platform back-end [31] introduces several load balancing optimizations. *Fission* is utilized to split a filter's contents into a pipeline of finer-grained filters. Such a pipeline may achieve better load distribution between parallel threads. In the opposite direction, too fine-grained filters are *fused* together. This optimization also assists with load balancing, as it removes some of the synchronization overhead, if several filters are to be grouped on the same processing unit.

As a special type of fission, a filter can be replicated [31, 63] in order to expose more parallel instances to the compiler. If the number of filters is smaller than the number of processing cores, the compiler replicates the filters with the highest computation requirements. While this strategy works well when generating code for a platform with a finite number of compute engines, it is not clear how to adapt it for platforms where the number of independent processing cores can not be modelled independently from the application. This thesis relies on an extended version of this optimization. Replication appears in different methods throughout this thesis, and is backed up by special orchestration, which allows structured usage of arbitrary replication factors. The reverse, where replication has to be rolled back is called folding.

Later, StreamIt has been ported to multi-core processors [30]. This back-end emphasizes on additional challenges of the code generation problem. Despite exposing a significant amount of task and data parallelism, optimizations are often hindered by communication costs. In this context, careful consideration has been given to match the cache size of the underlying processors to prevent performance degradation of operators executed on the same processor.

This back-end has described other trade-offs involved in the execution of the derived stream schedule among multiple cores. It differentiates between *soft-ware pipelining*, which pre-encodes a static schedule on each execution core and *hardware pipelining* which relies on computation driven by dynamic data arrival. Software pipelining is found to be suitable on the shared memory architectures utilized. In contrast, Chapter 3 shows that hardware pipelining can significantly reduce latency for the FPGA architecture, where communication is implemented with dedicated channels.

With the emergence of new parallel platforms, a StreamIt back-end has been proposed for the Cell platform [51]. The integer linear programming solution employed to map StreamIt to this platform targets maximum throughput based on the modelled computation and communication overhead. It generates a software

pipelined schedule which attempts to overlap communication with computation.

The architectures of all the platforms presented above share a common characteristic. They utilize a fixed number of cores capable of executing threads independently. However, both the FPGAs and GPUs diverge from this characterisation and introduce global interrelations between the implemented threads. An FPGA mapping can vary the number of parallel computation blocks based on the size of the reconfigurable resources they utilise, while a GPU mapping has to consider the complex relations between parallel threads that impact their performance. Prior implementations of StreamIt to FPGAs and GPUs are discussed in Section 2.2.1 and 2.3.1.

#### 2.1.3 Benchmark Suite

The StreamIt compiler provides a suite of standard benchmarks [80]. These benchmarks describe realistic stream graphs and have been utilized throughout this thesis. To adjust the workload included in the benchmarks, the benchmarks allow parameterization. Table 2.1 describes the benchmarks and how they were parameterized.

#### 2.2 FPGA Architecture

FPGA platforms expose a parallel architecture that consists of a large number of reconfigurable gates that can be reprogrammed to accelerate application-specific code. A broad class of applications, including multimedia, networking, graphics, and security codes, provide ample opportunities to exploit FPGA-based acceleration.

FPGA performance is drawn from the flexibility of its reconfigurable gates, called Look-Up Tables (LUTs)<sup>1</sup>. The LUTs are generic multiple input logic functions with 5 or recently 6 inputs, and 1 or 2 outputs. The configuration of the LUTs can be changed at run-time through FPGA reconfiguration. These gates are connected to each other through a reconfigurable interconnect. Together, the LUTs and the interconnect form a fully reconfigurable architecture which can provide operating frequencies up to 400 MHz.

<sup>&</sup>lt;sup>1</sup>Xilinx terminology is used throughout this thesis.

Table 2.1: Benchmark characterization.

| Benchmark                      | Description                                                              |

|--------------------------------|--------------------------------------------------------------------------|

| $\operatorname{Bitonic}(N)$    | Sorting algorithm for $N$ float elements applying the                    |

|                                | bitonic algorithm                                                        |

| $\operatorname{BitonicRec}(N)$ | Same as above, recursive method                                          |

| DCT(N)                         | Discrete cosine transform followed by the inverse trans-                 |

|                                | form for a matrix of $N \times N$ floats                                 |

| iDCT(N)                        | Inverse discrete cosine transform for a matrix of $N \times N$           |

|                                | floats                                                                   |

| DES                            | DES encryption algorithm with $N$ rounds, input 8                        |

|                                | bytes, output as 16 hex digits                                           |

| Serpent(N)                     | Serpent encryption algorithm with $N$ rounds, it in-                     |

|                                | cludes a bit level linear transform                                      |

| FFT(N)                         | Fine grained FFT transform on $N$ float elements                         |

| FFT'(N)                        | Very fine grained FFT transform on $N$ float elements                    |

|                                | described in Appendix A                                                  |

| FilterBank(N)                  | Instantiates $N$ filter banks to process multirate signals               |

| $\operatorname{FMRadio}(N)$    | (N+3)-band equalizer radio                                               |

| MatrixMult2(N)                 | Blocked matrix multiplication algorithm for $2N \times 2N$               |

|                                | matrices, split into blocks of $2 \times 2$                              |

| MatrixMult2(N, M)              | Blocked matrix multiplication algorithm for $(2N \times  $               |

|                                | $(2N) \times (2M \times 2N)$ matrices, split into blocks of $2 \times 2$ |

| MatrixMult3(N)                 | Same as above for $((3N+3)\times(3N+3))\times(3N\times(3N+3))$           |

|                                | matrices, with blocks of $3 \times 3$                                    |

The configuration of an FPGA is usually determined through hardware synthesis. The circuit is described in a high-level hardware description language (HDL) such as Verilog or VHDL [79] and further processed by vendor-specific tools. It is first synthesized into a netlist, which matches the characteristics of the LUTs and other reconfigurable resources in the target FPGA, and further fitted to the actual circuit layout, which fixes the placement and routing of each resource. Both steps take a large amount of time, in the range of hours, and they are often seen as the most significant factor limiting the popularity of FPGA technology.

Besides LUTs, the FPGA architecture now contains other reconfigurable resources, such as memories, DSP blocks, clock generators and even hard-wired processor cores, all of which can be included in user designs. Utilising these pre-defined hard-wired resources increases the performance of the synthesized application.

Various strategies are employed to reduce the design synthesis time. Among

these strategies, manually added annotations are the most frequently utilised, as they allow the circuit designer to fine tune the implementation. However, in the context of automatic HDL generation, such an option is infeasible. Instead, HDL generation tools often utilise libraries of pre-synthesized components which can be combined in larger designs, and which rely exclusively on the capabilities of the vendor synthesis tools in order to improve the performance of the resulting design.

In this context, applying automatic replication or folding strategies, as described in Chapters 3 and 6, exploits the possibility of duplicating or sharing not only the HDL code, but also the synthesized version of the code. As the parallel granularity of the FPGA resources is fully customizable, the applicability of the folding strategy is possible for several levels of parallelism. Replicating synthesized modules ensures balanced circuits capable of higher performance. The size and performance of the application which can run on the FPGA are only limited by the total available resources.

#### 2.2.1 Related Work on FPGA code generation

There are several platforms that integrate FPGAs with hard-wired processor cores [1, 29, 61, 81], and recent announcements [21] from leading vendors suggest that FPGAs are likely to become widely available as programmable coprocessors. Sequential parts of the applications can be assigned to run on the host processor, while those parts with abundant parallelism can pass through code generation methods that lead to FPGA implementations. These application parts can expose parallel computation, which is fine-grained (i.e. data parallel paths), or coarse-grained (i.e. parallel tasks).

#### 2.2.1.1 Fine-grained Parallel Computation on FPGAs

Fine-grained parallel computation is usually implemented as *custom instructions* that extend a given processor core. Previous research has shown how custom instructions can be added to an existing processor in a systematic approach. A number of commercial products are available, such as those developed by Tensilica [29] and Stretch [81].

The typical approach, used to automatically generate custom instructions, involves the analysis of the data flow graph obtained as a result of compilation, followed by the enumeration and selection of sub-graphs as candidates for custom instruction implementation [20, 100]. While the selected sub-graphs are identified during application compilation, resource usage is only estimated [10], and it may be affected by optimizations during HDL synthesis. This phase dependency prevents code generation tools from controlling accurately the reconfigurable resource count of the sub-graphs that would be synthesised. This is particularly important if the size of the custom instructions is large.

Previous research has usually focused on integer custom instructions [29, 100], which are lightweight and must be tightly integrated in the processor pipeline to achieve high performance. However, the overhead of such an approach is small only if the processor core resides in the FPGA reconfigurable resources, as well. If this is the case, the performance of the entire processor is offset by the implementation of the processor core in reconfigurable resources.

An alternative option becomes viable for floating point instructions. Because floating-point operations are usually supported by a bulkier implementation, their integration in the main processor pipeline can be less tightly coupled [97]. In this case, the processor core may be hard-wired, and only the floating-point instructions are implemented in FPGA. However, the number of floating-point pipelines that can be implemented in hardware is small, and resource sharing can certainly improve the designs. Therefore, the code generation for custom coprocessors, described in Chapter 6, combines custom instructions with resource sharing into folding methods. These methods exploit the regular structure of the vector instructions in order to generate automatically resource-constrained implementations.

While sharing methods have been previously applied to custom instructions [10, 83], the regular structure exposed by vector integer instructions is not suitable for sharing, due to the considerable cost of the multiplexers required for sharing purposes, compared to the size of the fine-grained integer operations. Indeed, the custom integer vector instructions offered by Tensilica [29] do not share the operations, hence they exhibit only limited resemblance with the method described in this thesis.

However, there are also a number of customized floating-point SIMD processor architectures [29, 85, 92, 99]. They provide a rich set of reconfigurable parameters. However, the final result is a monolithic processor instance with all instructions tightly integrated into the base pipeline. As such, these processors can not take advantage from fine-grained application-specific parallelism, and they are suitable to be implemented either in silicon or entirely as soft-cores [58].

Lastly, some vendors already offered hard-wired SIMD floating point coprocessors for their embedded processors [57]. The iPhone, for example, includes such a core [45]. This is additional evidence for the growing importance of floating point computation in a design domain characterized by tight resource and performance constraints. However, these coprocessors are silicon-based, and hence do not possess the flexibility of the solution presented in Chapter 6.

#### 2.2.1.2 Coarse-grained Parallel Computation on FPGAs

As discussed in the previous section, there is some overhead associated with the attachment of fine-grained FPGA computation to a hard-wired processor core. Coarser blocks, such as hardware loop accelerators [77, 104] have been proposed, relieving the processor of the steady issue of instructions and operands. Using this method, loop specific optimizations such as unrolling and pipelining can be used to improve the efficiency and utilization of the hardware execution units. Several tools [19, 34] are capable of deriving dedicated loop accelerators from the application code by applying static transformations to extract the necessary data parallelism. These methods, however, do not support irregular loop structures or complex control flow. In addition, dedicated memory connections are required to provide data for the loops. The method presented in Chapter 6, on the other hand, relies on the core processor to resolve all dynamic control flow and the data transfers, issuing scheduled vector instructions and operands in the proper order to the hardware.

Exploiting data parallelism through replication can increase the throughput

of the computation blocks [13, 18]. The replication applied to StreamIt operators in Chapters 3 addresses this issue in the context of the FPGA platforms. A method is described that performs maximal replication of the operators bound only by the size of the FPGA, then folds back those that do not improve throughput.

This replication method does not address the synthesis of the actual computation from stream operators to HDL. The emphasis is on the composition of the synthesized operators into an overall space-time efficient design. Recent work [41] specifically addressed the issue of hardware generation from StreamIt, and this method is orthogonal to it. Similarly, many of the existing state of the art C-to-hardware compiler technologies can be used to complement this method. Hence the method described is complementary to most of the ongoing research in the community that address sequential code high-level synthesis.

The replication strategy improves the accuracy in modelling the communication overhead. Because the replicas are identical, the data routing is simplified and the associated overhead is more accurately accounted for. This improves the global performance of the generated code. The modularity and composability of this method distinguishes it from global optimization of loop nests [103].

#### 2.3 The GPU Architecture

The GPU platforms have a massively parallel architecture that allows the concurrent execution of thousands of threads. The architecture consists of a number of streaming multiprocessors (SM), which in turn contain a number of processing cores. The number of processing cores in each of the streaming multiprocessors continues to increase with each new generation of GPUs(up to 48 cores per SM in the most recent nVidia GPU, compared to S2050's 32 cores and S1070's 16 cores).

The processing cores are running in lockstep, similar to SIMD execution. Blocks of parallel software threads run on each of the available SM. Typically, there are much more software threads than there are processing cores. In order to schedule the many threads on SM, they are statically grouped into scheduling units called warps<sup>2</sup>. For the current generation of nVidia GPU, a warp consists of 32 threads. Because threads in a warp execute in lockstep on the processing cores, any intra-warp control flow discrepancies will lead to serialized execution. However, threads that belong to different warps are independent of any divergent control flow penalty.

A hardware scheduler typically selects one warp and issues the current instruction from all its threads onto the pipeline of the processing cores in 2 - 4 consecutive cycles [94]. Afterwards, this warp becomes unavailable for a number of cycles until its instructions clear the pipeline. The scheduler switches to execute a different warp with zero overhead. As a result, though a large number of parallel threads can be spawned, their executions are actually *interleaved* on the processing cores. As opposed to CPU, where advanced compiler and run-time support is necessary to extract the fine-grained parallel operations, the GPU scheduler can simply issue, in parallel, independent instructions from inherently parallel threads.

The GPU architecture benefits from an exposed memory hierarchy where threads explicitly specify which memory they access. All threads can access off-chip global memory. However, the latency of accessing this memory is high. In addition, each SM in a GPU contains a small but very fast on-chip memory that is shared among all the threads in the SM. This *SM memory*<sup>3</sup> has close to register latency.

The register file is distributed among all the threads of the GPU. Hence, instantiating more threads leads to fewer registers allocated to each thread. This may lead to spills, which are directed to a *local memory*. Unfortunately, local memory is backed by private areas in the long-latency global memory, and performance is again significantly affected.

The long stalls affecting a warp that accesses global and local memory can be partially hidden if the scheduler can launch enough alternative warps. However, the architecture is not able to sustain execution without stalls when all warps

<sup>&</sup>lt;sup>2</sup>nVidia terminology is used throughout this thesis.

<sup>&</sup>lt;sup>3</sup>The nVidia way of referring to this as shared memory is potentially confusing.

access the memory simultaneously. This observation suggests that the GPU scheduler would benefit from a mix of threads with different execution patterns and from reduced memory access rate.

In this context, the methods described in Chapters 4, 5 and 7 show how the parallelism extracted from the application can be utilized to provide a steady number of stall-free warps to the scheduler, hence hiding most of the global memory latency. It also shows how the finer-grained parallelism in the code can be utilized to reduce the ratio of computation to memory access.

### 2.3.1 Related Work on GPU code generation

Computing on GPU platforms involves kernels that usually communicate to each other through global memory. Therefore, the overall performance is limited by the high latency of memory access. Hence, memory latency hiding is one of the most significant concerns in GPU programming. Basic strategies that enhance the memory access for a variety of GPU applications are detailed in [69].

Selecting the right number of parallel threads and the location of frequently used data is not trivial [75]. One well-known approach that boosts performance is to prefetch data from global memory to SM memory [98]. This is the approach taken by other high-level language translations [8, 74, 93] to CUDA and OpenCL.

The method presented in Chapter 4 uses two classes of dedicated threads for:

(1) loading / storing data from global memory to SM memory and (2) computing using data preloaded in SM memory. A recently proposed method [42] exploited efficiently only the coarse-grained task parallelism exposed by StreamIt, while the method presented in this thesis also takes advantage of finer-grained data parallelism when generating code for the stream graph. Therefore, a single instance of the stream graph spans several computing threads.

Because the amount of SM memory is limited, it is necessary to reduce the working set footprint. When generating GPU code for StreamIt, two complementary methods are possible. One relies on caching transformations for StreamIt that have included narrowing the memory requirement through modulation or copy-shift [78]. The other is to use a scratchpad memory, as optimal algorithms

have been proposed for its management [53]. The method in Chapter 4 is based on the copy-shift method, adapted to the way the stream graph executions share a common memory.

StreamIt applications have been previously executed on GPU platforms [42, 89]. The stream graph is usually mapped directly to kernels encapsulating operators that communicate via global memory. Mapping communication to global memory penalizes performance and eventually saturates the memory bandwidth. In order to reduce run-time overhead, communication between SM executing different kernels has to be deferred until a large amount of data is processed locally. As a result, the latency of executing the stream graph is large, while the throughput is limited by the memory bandwidth, despite the use of pipelining.

The methods described in this thesis generate code encapsulating stream graph partitions. Instead of mapping each operator separately, they execute multiple instances of larger stream graph partitions in parallel on each SM, taking care to adjust the number of parallel instances to match the resource constraints. The aim is to achieve a balance between the number of GPU threads, the layout of the SM memory, and the memory bandwidth consumption, such that performance is maximized.

A promising solution to deal with scalability issues is the utilization of multi-GPU platforms. Such systems are well-suited to process large data set applications [82]. Performance modeling for GPU architectures was comprehensively investigated by analytic and quantitative approaches [4, 101, 40] which highlighted the important balance between computation and memory access, as well as the utilization of SM memory. It is possible to estimate statically the performance of an application running on multiple GPUs based on characterizing computation and different communication costs [76].

On the other hand, efficient run-time systems for multiple GPUs have been proposed to explore speculative execution [22] and to investigate load balancing [17]. None of these works has attempted to generate code automatically, nor to provide an execution model for streaming languages onto multiple GPUs.

## CHAPTER 3

# STREAMIT CODE GENERATION FOR FPGAS

The first contribution described in this thesis tackles the optimized code generation of StreamIt applications to FPGA platforms. The architecture of these platforms does not directly constrain the degree of parallelism that can be derived from the application code. However, there are several other significant challenges to FPGA code generation for streaming applications. Since FPGA platforms have finite reconfigurable resources, there are many non-trivial trade-offs between the performance achieved and the number of reconfigurable resources utilized.

In addition, the performance of such an application is not reflected only by its throughput. Different design domains may trade throughput for the overall latency of the computation. The latency, defined as the time lapsed between the moment when an input appears at the input of the FPGA, until the moment when a corresponding output is produced, is an important constraint in application domains such as real-time control [88], network and media applications [101] as well as in the financial domain, for high frequency algorithmic trading [96].

This chapter describes a code generation method that takes StreamIt programs and generates HDL code suitable for FPGA implementation, with focus on the improvement of the high-level mapping steps. The optimized code generation method includes an algorithm that assists with the refinement of the stream graph applications. The design points processed are further refined for the highest achievable throughput subject to user-specified latency constraints and target FPGA resource bounds.

Starting with an application represented in StreamIt, ample parallelism is available due to the stream-oriented programming model. This chapter addresses the following question: is there a refinement of the flexible input stream graph that can maximize the processing throughput of the overall graph? Furthermore, because FPGA reconfigurable resources are finite, and latency is typically an important consideration in this application domain, the optimization goal is extended to consider both resources and latency constraints. The throughput improvement algorithm described is the first tackling the combined constraint.

The intuition behind the algorithm is the following. The filters that may cause bottlenecks in the stream graph are identified and inspected. If the filters do not maintain a history of their past execution, then their throughput can be boosted by exploiting automatically the data parallel properties they expose. This is achieved by judiciously *replicating* the bottleneck filters.

Replicating the filters has several advantages. The replicated filter instances do not require to be synthesised again as they are all instances of the same filter, and the synthesis results are reusable. This is in contrast to prior work on global optimization of loop nests on FPGAs [103] which requires recompilation and evaluation of the recompiled designs based on heuristics. Such an approach will not scale for large designs.

The algorithm operates on a stream graph and relies on a previously synthesized set of filters. It determines how to assemble the pre-synthesized filters in order to achieve the best possible throughput. If a filter is replicated, additional code is automatically generated for specific hardware circuitry required to route the data flow to and from the replicated filters. This method makes the issue of filter synthesis orthogonal to design assembly and generation. Hence, this method is complementary to a lot of the ongoing research in the community that addresses high-level synthesis of the filter code itself.

The algorithm can be briefly described as first aggressively replicating candidate filters, then folding back the graph to reduce the number of replicas if they are not profitable given the constraints. The next section provides a motivating example that shows some of the trade offs considered by the code generation method. Subsequently, the details of the replication and folding algorithm are discussed, together with the evaluation results.

3.1. Rationale 27

## 3.1 Rationale

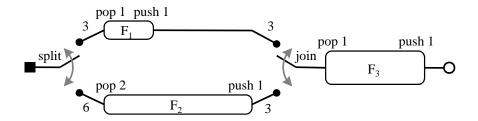

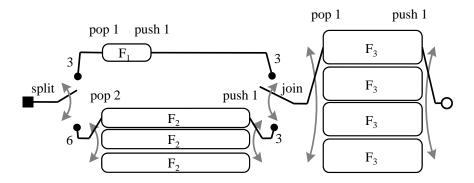

A stream graph example is shown in Figure 3.1. In this figure,  $F_i$  are filters, and the hardware footprint (R(i)), reconfigurable resources utilized) of each filter is correlated to the area of its corresponding rectangle, while the execution time T(i) of a filter firing is correlated to the length of the rectangle. The figure represents the number of input tokens popped and pushed by each filter. The edges in the graph describe channels routing the data flow between operators. The splitter and joiner are illustrated using arched double-headed arrows. Section 2.1.1 provides a complete description of the StreamIt language.

The data flow is split between  $F_1$  and  $F_2$  in a periodic and round-robin manner, with 3 tokens dispatched to  $F_1$  and 6 to  $F_2$ . This information is annotated on the edges that fan-out from the splitter. Similarly, the joiner collects data from the input streams in a round-robin manner. The weight annotations on each edge describe how the data is aggregated from the streams: 3 tokens from  $F_1$  and 3 from  $F_2$ .

This example contains a pipeline stream container, connecting a splitjoin to  $F_3$ . The splitjoin is a stream container, with a splitter at the source, a joiner at the sink, and filters  $F_1$  and  $F_2$  between them. The stream graph in the figure can be described as follows in StreamIt:

```

int->int pipeline Example() {

add pipeline {

add splitjoin {

split roundrobin(3, 6);

add F1();

add F2(2); // instantiating parameterized filter