# STRAINED MULTIPLE-GATE TRANSISTORS WITH SI/SIC AND SI/SIGE HETEROJUNCTIONS

LIOW TSUNG-YANG

NATIONAL UNIVERSITY OF SINGAPORE

2008

# STRAINED MULTIPLE-GATE TRANSISTORS WITH SI/SIC AND SI/SIGE HETEROJUNCTIONS

LIOW TSUNG-YANG B.Eng (Hons.), NUS

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Acknowledgements

First of all, I would like to express my utmost gratitude to my advisors, Dr Narayanan Balasubramanian and Dr Yeo Yee-Chia, for their invaluable guidance during the course of my Ph.D. candidature. I am thankful for their sharing of knowledge and ideas, their patience, the inspiring discussions with them, and the autonomy in research that they have given me. I would also like to thank Dr Lee Sungjoo for sitting on my thesis advisory committee. I am also glad that I was given the opportunity of being a member of two laboratories at the same time – the Semiconductor Processing Technology (SPT) Lab at the Institute of Microelectronics (IME), and the Silicon Nano Device Lab (SNDL) at the National University of Singapore (NUS).

I wish to express sincere thanks to the members of the SPT lab at IME for their help, in one way or another. I would especially like to thank Dr Ajay Agarwal and Mr Ranganathan Nagarajan for their help and for sharing of semiconductor processing knowledge with me during the initial stages of my candidature. I truly appreciate being given the opportunity to extensively use the advanced device fabrication facilities at IME.

I would also like to thank the members of the SNDL at NUS. I also wish to thank Associate Professor Ganesh S Samudra for his valuable comments and ideas during our research group meetings. I am also grateful for the friendship of many members of our research group, especially King Jien, Kah Wee, Kian Ming, Rinus Lee, Andy Lim, Hoong Shing and Zhu Ming. I will never forget the countless hours spent in the cleanroom with Kian Ming developing the FinFET process flow, without which many of the experiments in this work would not have been possible. I really appreciate the care and concern that my parents and brother have given me. Most of all, I would like to thank Julia, the love of my life, for her support, encouragement and love during this wonderful chapter of my life.

# **Table of Contents**

1.3

1.4

1.5

1.4.1

1.4.2

| Acknowledgements  | i   |

|-------------------|-----|

| Table of Contents | iii |

| Summary           | ix  |

| List of Tables    | xi  |

| List of Figures   | xii |

| Chapter 1                         |   |

|-----------------------------------|---|

| 1. Introduction                   | 1 |

| 1.1 Current Issues and Motivation | 1 |

| 1.2 Background                    | 3 |

| 1.2.1 Multiple-Gate Transistors   | 3 |

| 1.2.2 Strained-Silicon            | 5 |

| 1.2.2.1 Strain Techniques         | 5 |

| 1.2.2.2 Physics of Strained-Si    | 8 |

SiC S/D Technologies for N-Channel Multiple-Gate Transistors......9

| Ch | apter 2  |                                                                       | 20      |

|----|----------|-----------------------------------------------------------------------|---------|

| 2. | Silicon  | Carbon $(Si_{1-y}C_y)$ Source and Drain Technology for N-             |         |

|    | Channe   | el Multiple-Gate FETs                                                 | 20      |

| -  | 2.1 Intr | roduction                                                             | 20      |

| -  | 2.2 Lat  | ttice Strain Effects with Silicon Carbon Source and Drain Stressors   | 20      |

|    | 2.2.1 I  | Device Fabrication                                                    | 20      |

|    | 2.2.2    | Selective Epitaxial Growth of $Si_{1-y}C_y$                           | 22      |

|    | 2.2.2.   | 1 Cyclic Growth/Etch Process Details                                  | 22      |

|    | 2.2.2.2  | 2 Si migration and SOI agglomeration during Pre-epitaxy UHV Anne      | al 24   |

|    | 2.2.2.3  | 3 Epitaxial growth on FinFET devices with different channel orientati | ions.25 |

|    | 2.2.2.4  | 4 Stress effect of Π-shaped stressors compared to embedded stressors  | 27      |

|    | 2.2.3 I  | Device Characterization                                               | 28      |

|    | 2.2.3.   | 1 <100>-oriented devices (45°)                                        | 28      |

|    | 2.2.3.2  | 2 <110>-oriented devices $(0^\circ)$                                  | 31      |

|    | 2.2.3.3  | 3 Comparison between <100> and <110> oriented SiC S/D FinFETs.        | 35      |

| 4  | 2.3 Co-  | -integration with High-stress Etch Stop Layer Stressors               |         |

|    | 2.3.1 I  | Introduction                                                          |         |

|    | 2.3.2 I  | Device Fabrication                                                    |         |

|    | 2.3.3 I  | Device Characterization                                               |         |

|    | 2.3.3.   | 1 <100>-oriented devices (45°)                                        | 39      |

|    | 2.3.3.2  | 2 <110>-oriented devices $(0^\circ)$                                  | 41      |

|    | 2.3.3.3  | 3 Summary                                                             | 44      |

| -  | 2.4 Car  | rrier Backscattering Characterization                                 | 45      |

|    | 2.4.1 H  | Backscattering Theory                                                 | 45      |

|    | 2.4.2 I  | Device Backscattering Characterization                                | 47      |

| 4  | 2.5 Geo  | cometrical Approaches to Further Stress Enhancement                   | 51      |

| 2.5.1     | Introduction                                                | 51 |

|-----------|-------------------------------------------------------------|----|

| 2.5.2     | Effect of Increasing Stressor Thickness                     | 51 |

| 2.5.3     | Effect of Increasing Stressor-to-channel Proximity          | 54 |

| 2.5.4     | Summary                                                     | 59 |

| 2.6       | References                                                  | 60 |

|           |                                                             |    |

| Chapter 3 | 3                                                           | 63 |

| L         |                                                             |    |

| 3. Nove   | el Techniques for Further Improving N-Channel Multiple      | -  |

| Gate      | e FETs with Silicon Carbon $(Si_{1-y}C_y)$ Source and Drain | 1  |

| Tech      | nnology                                                     | 63 |

| 3.1       | Introduction                                                | 63 |

| 3.2       | Spacer Removal Technique for Further Strain Enhancement     | 64 |

| 3.2.1     | Introduction                                                | 64 |

| 3.2.2     | Device Fabrication                                          | 65 |

| 3.2.3     | Device Characterization                                     | 67 |

| 3.2.4     | Summary                                                     | 74 |

| 3.3       | Contact Silicide-Induced Strain                             | 75 |

| 3.3.1     | Introduction                                                | 75 |

| 3.3.2     | High stress Nickel-Silicide Carbon (NiSi:C)                 | 76 |

| 3.3.3     | Device Fabrication                                          | 79 |

| 3.3.4     | Device Characterization                                     |    |

| 3.3.5     | Compatibility with FUSI Metal-gate                          |    |

| 3.3       | 3.5.1 Introduction                                          |    |

| 3.3       | 3.5.2 Device Fabrication                                    |    |

| 3.3       | 3.5.3 Device Characterization                               |    |

| 3.3.0 | 6 Summary                                                        | 88  |

|-------|------------------------------------------------------------------|-----|

| 3.4   | Scaling up Carbon Substitutionality with In-situ doped Si:CP S/D |     |

|       | Stressors                                                        | 89  |

| 3.4.  | 1 Introduction                                                   | 89  |

| 3.4.2 | 2 In-situ Phosphorus Doped Silicon-Carbon (Si:CP) Films          | 90  |

| 3.4.3 | 3 Device Fabrication                                             | 93  |

| 3.4.4 | 4 Device Characterization                                        | 98  |

| 3.4.  | 5 Summary                                                        | 105 |

| 3.5   | Summary                                                          | 106 |

| 3.6   | References                                                       | 107 |

| Chapter | 4 |  |

|---------|---|--|

|---------|---|--|

| 4. Germanium Condensation on SiGe Fin Structures: Ge enrichment |                                 |     |

|-----------------------------------------------------------------|---------------------------------|-----|

| aı                                                              | nd Substrate Compliance Effects |     |

| 4.1                                                             | Introduction                    |     |

| 4.2                                                             | Experiment                      |     |

| 4.3                                                             | Results and Discussion          | 116 |

| 4.4                                                             | Summary                         |     |

| 4.5                                                             | References                      |     |

|  | Chapter 5 |  | 126 |

|--|-----------|--|-----|

|--|-----------|--|-----|

| 5.  | P-Channel FinFETs with Embedded SiGe stressors Fabricated |     |

|-----|-----------------------------------------------------------|-----|

|     | using Ge condensation                                     | 126 |

| 5.1 | 1 Introduction                                            | 126 |

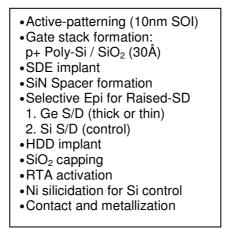

| 5.2 | Device Fabrication      | 127 |

|-----|-------------------------|-----|

| 5.3 | Device Characterization | 131 |

| 5.4 | Summary                 | 134 |

| 5.5 | References              | 135 |

| Chapter 6 |  | 138 |

|-----------|--|-----|

|-----------|--|-----|

####

| 6.1   | Introduction                                                       | 138 |

|-------|--------------------------------------------------------------------|-----|

| 6.2   | Device Fabrication                                                 | 139 |

| 6.3   | Device Characterization                                            | 141 |

| 6.4   | Melt-enhanced Dopant Diffusion and Activation Technique for Ge S/D |     |

|       | Stressors                                                          | 146 |

| 6.4.  | 1 Introduction                                                     | 146 |

| 6.4.2 | 2 Devices with MeltED Ge S/D Stressors                             | 146 |

| 6.4.  | 3 Device Characterization of MeltED Ge S/D devices                 | 148 |

| 6.5   | Summary                                                            | 154 |

| 6.6   | References                                                         | 155 |

| Chapter 7 |                                                                          | 158 |  |

|-----------|--------------------------------------------------------------------------|-----|--|

| 7. Con    | clusions and Future Work                                                 | 158 |  |

| 7.1       | Conclusions                                                              | 158 |  |

| 7.1.1     | Silicon Carbon $(Si_{1-y}C_y)$ Source and Drain Technology for N-Channel |     |  |

|           | Multiple-Gate FETs                                                       | 158 |  |

| 7.1.2 | 2 Novel Techniques for Further Improving N-Channel Multiple-Gate        |

|-------|-------------------------------------------------------------------------|

|       | FETs with Silicon Carbon $(Si_{1-y}C_y)$ Source and Drain Technology159 |

| 7.1.3 | 3 Germanium Condensation on SiGe Fin Structures: Ge enrichment and      |

|       | Substrate Compliance Effects                                            |

| 7.1.4 | P-Channel FinFETs with Embedded SiGe stressors Fabricated using Ge      |

|       | condensation161                                                         |

| 7.1.5 | 5 Multiple-gate UTB and Nanowire-FETs with Ge S/D stressors             |

| 7.2   | Future Work                                                             |

| <b>Appendix A: Publication</b> | List | 165 |

|--------------------------------|------|-----|

|--------------------------------|------|-----|

## Summary

High performance multiple-gate transistors such as FinFETs are likely to be required beyond the 32 nm technology node. Process-induced strain techniques can significantly enhance the carrier mobility in the channels of such transistors. In this dissertation work, complementary lattice mismatched source and drain stressors are studied for both n and p-channel multiple-gate transistors. Si<sub>1-y</sub>C<sub>y</sub> (or SiC), which has a lattice constant smaller than that of Si, is employed to induce uniaxial tensile strain in the channel regions of n-channel devices. Si<sub>1-x</sub>Ge<sub>x</sub> (or SiGe), which has a lattice constant larger than that of Si, is employed to induce uniaxial compressive strain in the channel regions of p-channel devices.

For n-channel devices, various integration challenges pertaining to SiC S/D stressors were identified and addressed. Evaluation of the electrical performance of such strained devices was also performed, showing that significant drive current enhancement can indeed be achieved. Backscattering characterization was also performed to clarify the carrier transport behaviour of strained FinFETs with SiC S/D stressors. The compatibility of the SiC stressor with high stress tensile SiN capping layer was also shown.

Further enhancement of devices with SiC S/D stressors was also investigated. A novel technique involving spacer removal prior to backend passivation layer (or contact etch-stop layer) deposition was proposed and experimentally shown to increase the influence of the S/D stressor on the channel regions, allowing greater performance benefits to be obtained at very low cost. It was also shown that the contact silicide (NiSi:C) can be tuned for higher intrinsic tensile stress, so as to induce further tensile strain in the channel. This will be of great importance in achieving low parasitic series resistances as well as high channel stress.

For further scalability of SiC S/D stressor technology, in-situ doped SiC films were explored as an alternative to implantation doped SiC films. In-situ doping makes a high temperature S/D activation anneal unnecessary. This has the effect of suppressing the loss of carbon substitutionality, preserving it in its as-grown state. This makes it easier to control the final substitutional carbon percentage in the film as it is now solely controlled by the epitaxial growth process conditions.

For p-channel devices, enhancements to the conventional embedded SiGe S/D stressors were sought. The Ge condensation technique was investigated for vertically standing fins. The results show that up to 90% Ge content can be obtained using the condensation technique. It was also observed that substrate compliance suppresses dislocation formation. Applying this technique to the SiGe S/D regions of p-channel devices resulted in simultaneous Ge enrichment and embedding of the S/D stressors. The enrichment of Ge content as well as the increased proximity of the stressors to the channel resulted in further performance enhancement.

Ge S/D stressors were evaluated with ultra-thin body SOI planar and nanowire FETs. Enhanced substrate compliance in ultra-thin SOI and narrow structures resulted in dramatic performance enhancement from the Ge S/D stressors. A Ge melting technique for enhanced dopant diffusion and activation in the S/D stressors was also introduced. This technique resulted in further strain enhancement as a result of the simultaneous embedding effect.

# List of Tables

# **List of Figures**

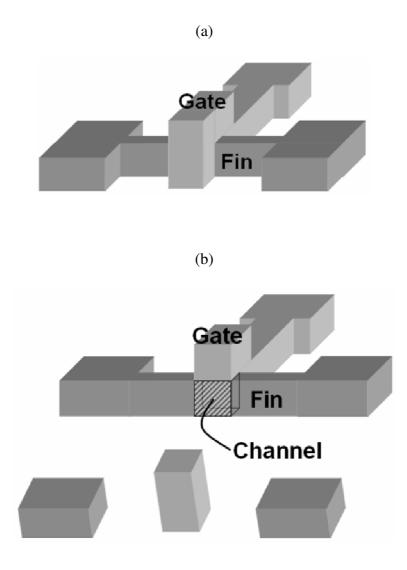

|   | (a) Schematic illustrating the structure of a double-gate FinFET. (b) Schematic of the same structure which has been sliced vertically to reveal one of the two side channels of the device, which would otherwise be obscured by the gate which runs over the fin. (For the double-gate FinFET, the top of the fin is covered with a thick dielectric hardmask which prevents inversion of the top channel. In the tri-gate FinFET, this top hardmask is removed prior to gatestack formation, resulting in a total of 3 channel surfaces.). | 4  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

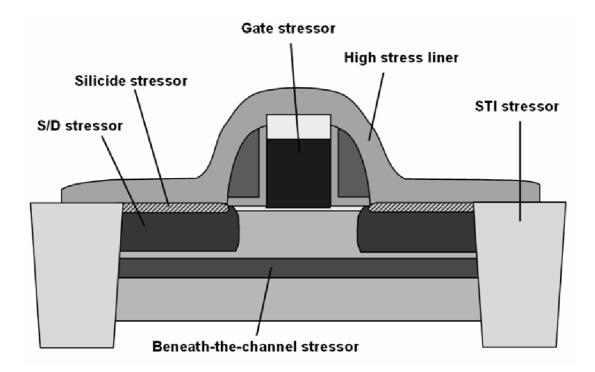

|   | Schematic illustrating the various process-induced strain techniques for introducing stress in the channel                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7  |

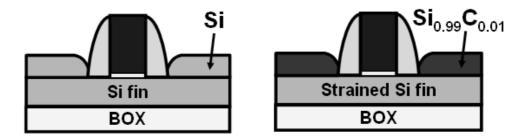

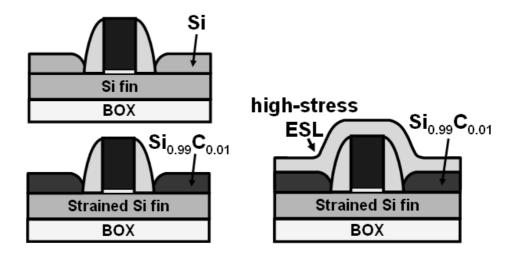

| 1 | Schematic showing the difference between Si S/D control and the SiC S/D strained devices. SiC S/D strained devices have $Si_{0.99}C_{0.01}$ films grown in the S/D regions. The lattice mismatched SiC S/D stressors induce uniaxial tensile strain in the transistor's channel regions.                                                                                                                                                                                                                                                      | 21 |

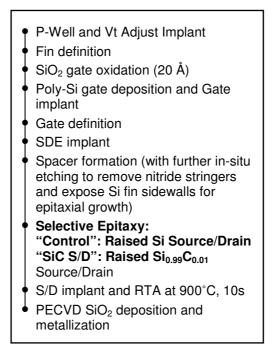

|   | Process flow schematic showing the key steps in the fabrication of FinFETs with SiC S/D stressors and control devices.                                                                                                                                                                                                                                                                                                                                                                                                                        | 22 |

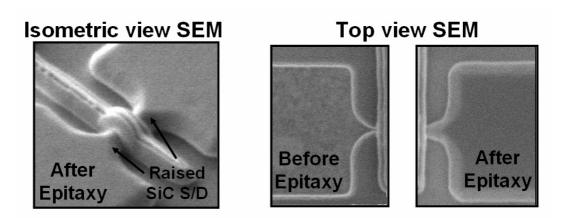

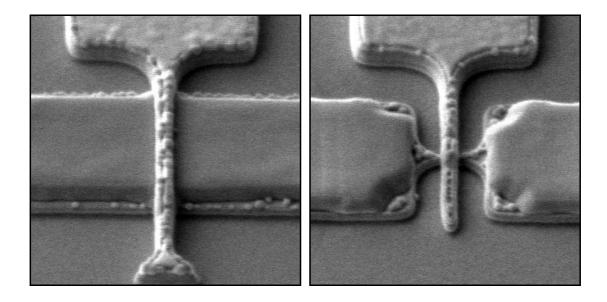

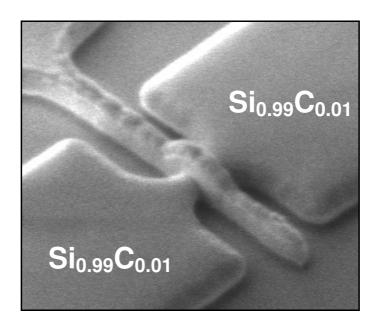

|   | SEM images showing the successful growth of $Si_{0.99}C_{0.01}$ in the S/D regions of FinFET transistors. Excellent selectivity to the SiN gate spacers and isolation $SiO_2$ was achieved.                                                                                                                                                                                                                                                                                                                                                   | 23 |

| ] | SEM images showing (a) agglomeration at edges of the S/D area in SOI planar FETs and (b) agglomeration at the fin extensions between the gate and the.                                                                                                                                                                                                                                                                                                                                                                                        | 24 |

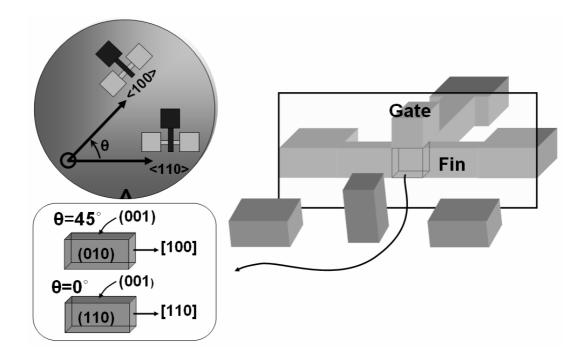

| ( | Schematic showing the channel direction and surface orientations of 0 and 45 degree oriented devices. The effect of strain on different channel surface orientations and directions are different, as can be inferred from piezoresistivity coefficients.                                                                                                                                                                                                                                                                                     | 26 |

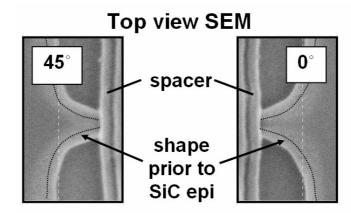

| 1 | Top view SEM images showing the epitaxial growth of $Si_{0.99}C_{0.01}$ in the S/D regions of 0 and 45 degree oriented devices. The thicknesses of the epitaxial films grown in the S/D regions are quite comparable.                                                                                                                                                                                                                                                                                                                         | 26 |

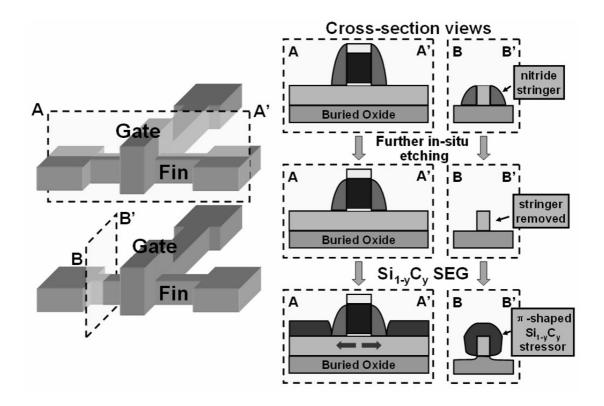

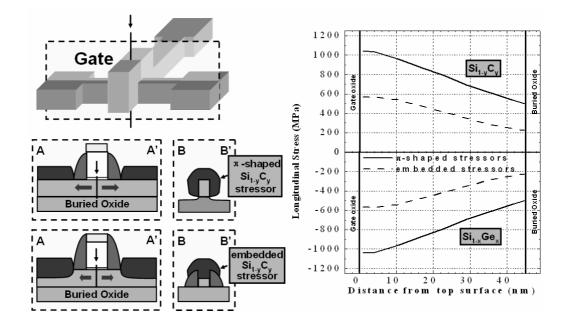

| j | Process flow schematic showing how pi-shaped SiC S/D stressors can be integrated with multiple-gate FinFETs. An extra in-situ over-etch during the spacer formation step removes the nitride spacer stringers from around the S/D regions, allowing the epitaxial growth of $Si_{1-y}C_y$ on the top surface as well as the side surfaces of the S/D regions.                                                                                                                                                                                 | 27 |

|   | TCAD stress simulation provides a rough gauge of the enhancement in channel stress in FinFET devices with the proposed pi-shaped S/D stressors as compared to a device with 50% S/D embedding of the S/D stressors. The cut-line along which the stress is plotted is shown in the schematic                                                                                                                                                                                                                                                  | 28 |

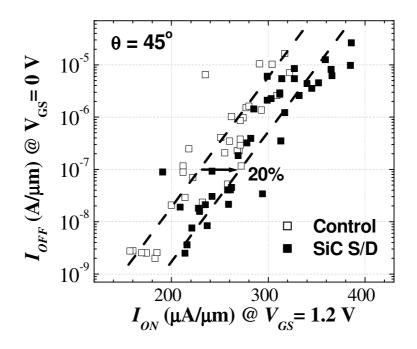

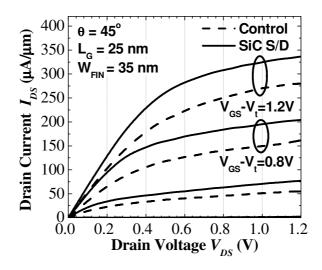

| Figure 2-9 $I_{OFF}$ - $I_{ON}$ plot comparing SiC S/D devices and raised Si S/D control devices<br>( $\theta = 45^{\circ}$ for all devices), showing 20% improvement at $I_{OFF} = 10^{-7}$ A/µm2                                                                                                                                                                                                                                                                    | 9  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

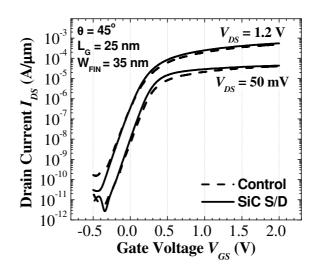

| Figure 2-10 $I_D$ - $V_G$ characteristics of SiC S/D device and raised Si S/D control device<br>with the same off-state current, comparable DIBL and subthreshold swing<br>( $\theta = 45^\circ$ for both devices)                                                                                                                                                                                                                                                    | 0  |

| Figure 2-11 $I_D$ - $V_D$ showing 20% saturation drive current enhancement of SiC S/D device over the raised Si S/D control device ( $\theta = 45^\circ$ for both devices)                                                                                                                                                                                                                                                                                            | 0  |

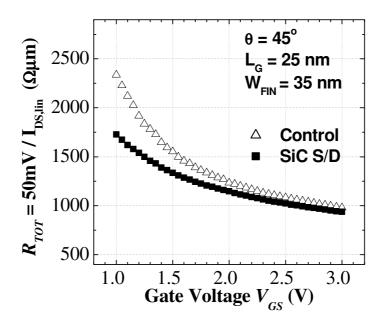

| Figure 2-12 Estimation of series resistance by examining the value of total resistance, given the asymptotic behavior of total resistance at large gate bias. The series resistances for both SiC S/D and raised Si S/D control devices are closely matched to within 5% ( $\theta$ =45° for both devices)                                                                                                                                                            | 1  |

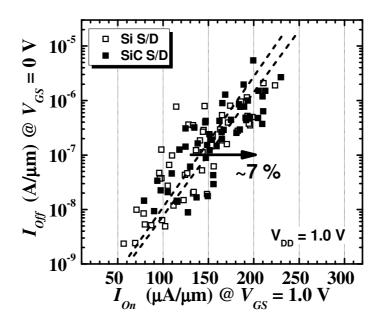

| Figure 2-13 $I_{OFF}$ - $I_{ON}$ plot comparing SiC S/D devices and raised Si S/D control devices<br>( $\theta = 0^{\circ}$ for all devices), showing 7% improvement at $I_{OFF} = 10^{-7}$ A/µm3                                                                                                                                                                                                                                                                     | 3  |

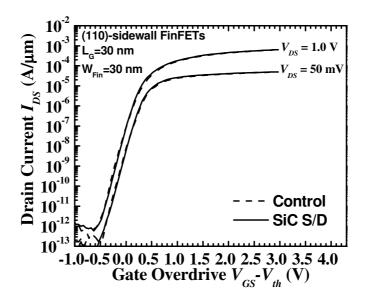

| Figure 2-14 $I_D$ - $V_G$ transfer characteristics of SiC S/D device and raised Si S/D control device with the same off-state current, comparable DIBL and subthreshold swing ( $\theta = 0^\circ$ for both devices)                                                                                                                                                                                                                                                  | 3  |

| Figure 2-15 $I_D$ - $V_D$ showing 7% saturation drive current enhancement of SiC S/D device<br>over the raised Si S/D control device ( $\theta = 0^\circ$ for both devices)                                                                                                                                                                                                                                                                                           | 4  |

| Figure 2-16 Extraction of series resistance by examining the asymptotic behavior of total resistance at large gate bias. ( $\theta$ =0° for both devices). A simplified linear region drain current equation that includes a source/drain series resistance parameter was used to generate curves which fit each set of measured data points. The series resistances were estimated to be comparable, 594 and 614 $\Omega$ µm for "Si S/D" and "SiC S/D" respectively | 54 |

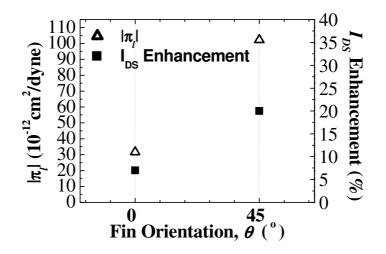

| Figure 2-17 $I_{DSat}$ enhancement of SiC S/D over Control for the 45°-oriented FinFETs is<br>larger compared to the 0°-oriented FinFETs. This is expected due to the<br>larger magnitude of longitudinal piezoresistance coefficient, $ \Pi_l $ for the<br>channels in the 45°-oriented FinFETs                                                                                                                                                                      | 6  |

| Figure 2-18 Process flow schematic showing the key steps in the fabrication of<br>FinFETs with SiC S/D stressors and control devices                                                                                                                                                                                                                                                                                                                                  | 7  |

| Figure 2-19 Schematic showing difference between Si S/D+ESL devices from the Si S/D control and the SiC S/D strained devices. SiC S/D+ESL devices are similar to SiC S/D devices, with the sole exception that a high-stress SiN capping layer (+1.1 GPa) was added as a contact etch-stop layer. This high-stress liner induces further stress in the device channel                                                                                                 | 8  |

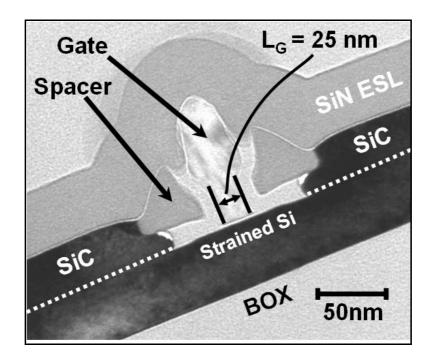

| Figure 2-20 Cross-section TEM image showing the transistor structure of SiC S/D+ESL devices. Like SiC S/D devices, Si <sub>0.99</sub> C <sub>0.01</sub> is grown in the S/D regions. After S/D implantation and activation, the high stress SiN ESL is deposited as a second stressor                                                                                                                                                                                 | 8  |

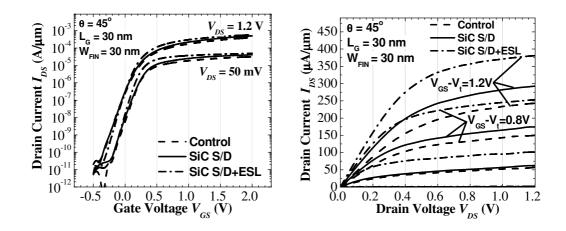

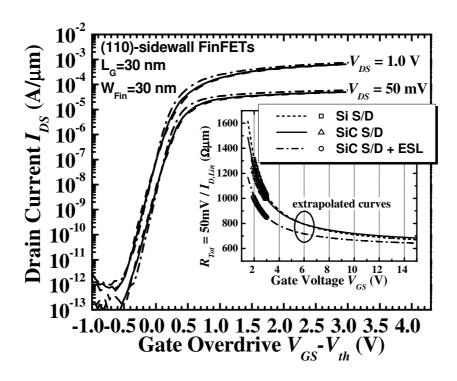

| Figure 2-21 From the $I_D$ - $V_G$ transfer characteristics, it is clear that the SiC S/D+ESL                                                                                                                                                                                                                                                                                                                                                                         |    |

gure 2-21 From the  $I_D$ - $V_G$  transfer characteristics, it is clear that the SiC S/D+ESL device does not show any sign of short channel degradation as a result of

| the added thermal budget experienced during the LPCVD SiN liner deposition. The $I_D$ - $V_D$ curves for the same devices show 20% enhancement of the SiC S/D device over the control. A 30% further enhancement in $I_{Dsat}$ is observed for the SiC S/D+ESL device over the SiC S/D device                                                                                                                                                                                                                                                                                        | 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

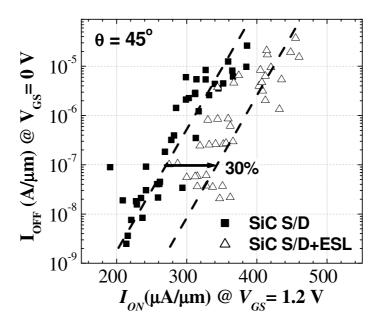

| Figure 2-22 $I_{On}$ - $I_{Off}$ plot statistically confirms the additional 30% enhancement in $I_{Dsat}$ that was gained by co-integrating a high-stress SiN ESL with SiC S/D devices.                                                                                                                                                                                                                                                                                                                                                                                              | 0 |

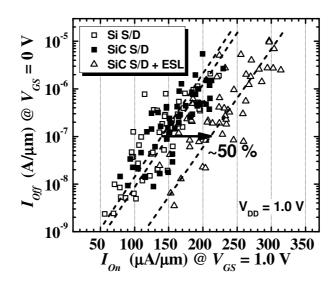

| Figure 2-23 $I_{Off}$ - $I_{On}$ characteristics of FinFETs with Si S/D, SiC S/D, and SiC S/D and ESL. For <110>-oriented (110)-sidewall FinFETs, incorporating Si <sub>1-y</sub> C <sub>y</sub> S/D stressors alone results in modest performance enhancement. However, further addition of a tensile SiN ESL results in significant performance enhancement of about 50%.                                                                                                                                                                                                          | 2 |

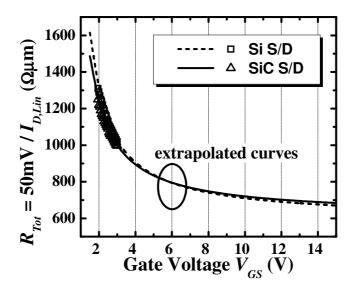

| Figure 2-24 Subthreshold characteristics of FinFETs with Si S/D, SiC S/D, and SiC S/D and ESL, showing similar values of DIBL and subthreshold slope. The inset shows total resistance ( $R_{Tot} = 50 \text{ mV} / I_{D,lin}$ ) plotted against gate voltage. A simplified linear region drain current equation that includes a source/drain series resistance parameter was used to generate curves which fit each set of measured data points.                                                                                                                                    | 2 |

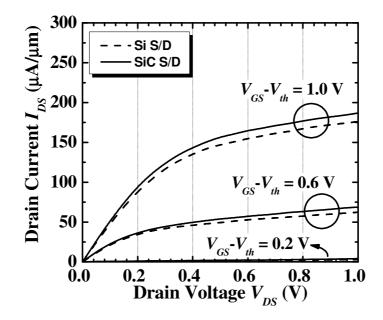

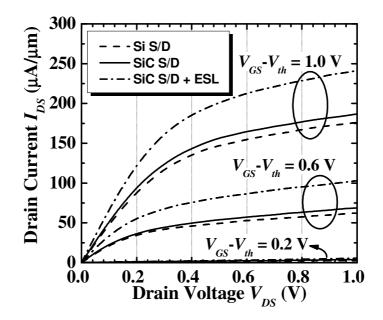

| Figure 2-25 $I_{DS}$ - $V_{DS}$ characteristics of the FinFETs at various gate over-drives, $V_{GS}$ - $V_{th}$ .<br>$I_{Dsat}$ enhancement of about 6 % was obtained by incorporating Si <sub>1-y</sub> C <sub>y</sub> S/D<br>stressors alone, while a further 29 % enhancement can be obtained by<br>adding a tensile SiN ESL, bringing the total enhancement to ~37%. $V_{th}$ is<br>defined as $V_{GS}$ when $I_{DS} = 100$ nA/µm and $V_{DS} = 1.0$ V                                                                                                                           | 3 |

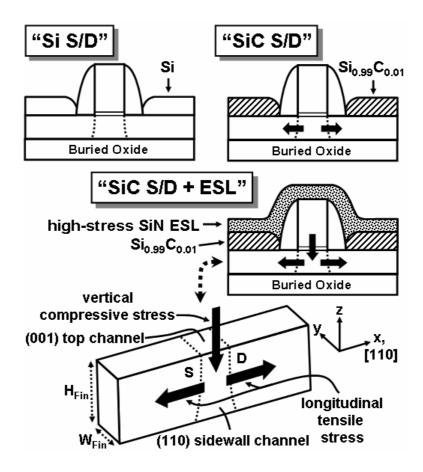

| Figure 2-26 Schematic showing the three experiment splits or device structures comprising "Si S/D", "SiC S/D" and "SiC S/D + ESL". In the "Si S/D" control split, the devices have raised Si S/D regions. In both the "SiC S/D" and "SiC S/D + ESL" splits, the devices have raised Si <sub>1-y</sub> C <sub>y</sub> S/D regions. In the "SiC S/D + ESL" split, an additional tensile SiN ESL was deposited. A 3-D schematic of the fin is also shown for the "SiC S/D + ESL" split, in which the stress components acting on the (110) sidewall channel surface are also indicated. | 4 |

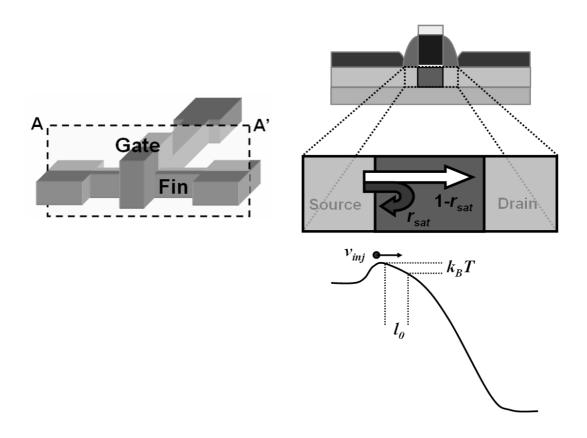

| Figure 2-27 Schematic representation of an n-channel transistor showing the conduction band profile across the channel from source to drain. $r_{sat}$ represents the fraction of electrons that are backscattered from the channel to the source size. The electrons are injected in the channel with an injection velocity $v_{inj}$                                                                                                                                                                                                                                               | 6 |

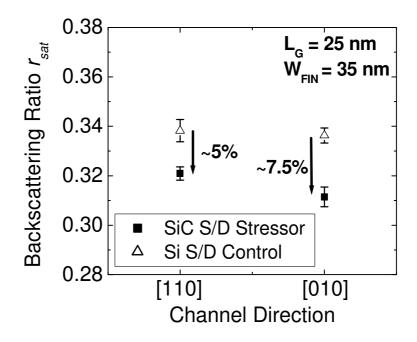

| Figure 2-28 SiC S/D FinFETs show improvement (reduction) in backscattering ratio $r_{sat}$ over control Si S/D FinFETs. This could possibly be due to a reduced critical length for backscattering $\ell_o$ as a result of conduction band barrier modulation                                                                                                                                                                                                                                                                                                                        | 9 |

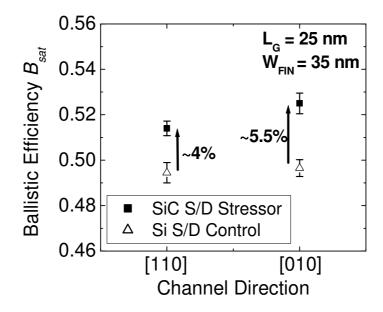

| Figure 2-29 SiC S/D FinFETs show improvement (increase) in ballistic efficency $B_{sat}$ over control Si S/D FinFETs. It is observed that the dependence of $\Delta B_{sat}$ on channel direction is not very prominent                                                                                                                                                                                                                                                                                                                                                              | 9 |

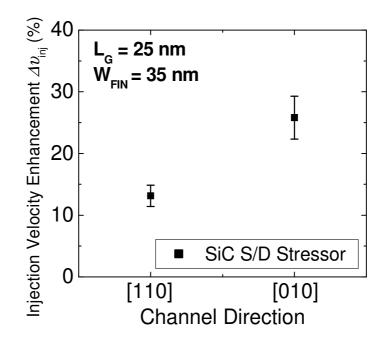

| Figure 2-30 Injection velocity $v_{inj}$ enhancement in the strained SiC S/D FinFETs is<br>higher for [010] channel direction than for the [110] channel direction50                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

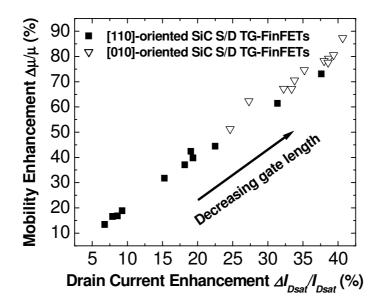

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-31 Significant $I_{Dsat}$ enhancement observed in strained n-channel FinFETs is<br>attributed to the large gain in electron mobility. The mobility enhancement<br>is approximately 2 times the $I_{Dsat}$ enhancement. $I_{Dsat}$ enhancement for<br>[010]-oriented FinFETs is higher than that for [110]-oriented FinFETs, as<br>can be expected by examining the piezoresistance coefficients of the<br>channel surfaces                                                                                                                                                                                     |

| Figure 2-32 SEM image showing thick Si <sub>0.99</sub> C <sub>0.01</sub> S/D stressors of 45 nm grown selectively in the S/D regions of a FinFET device                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

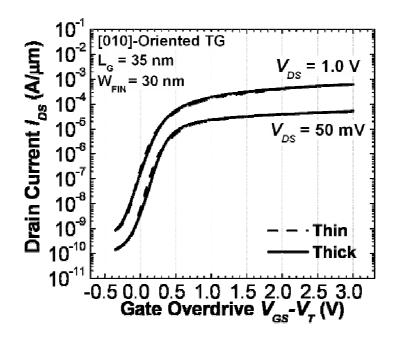

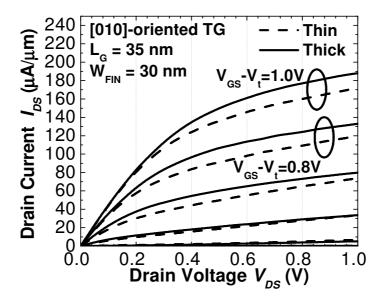

| Figure 2-33 Subthreshold characteristics of a matched pair of TG FinFETs of 2 SiC S/D stressor thicknesses having similar DIBL and subthreshold swing. The estimated series resistances are also very similar                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 2-34 <i>I</i> <sub>DS</sub> - <i>V</i> <sub>DS</sub> characteristics of the same matched pair of devices show ~9% <i>I</i> <sub>Dsat</sub> enhancement of "Thick" SiC S/D FinFETs over "Thin" SiC S/D FinFETs                                                                                                                                                                                                                                                                                                                                                                                                    |

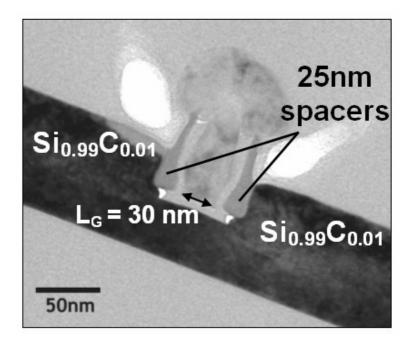

| Figure 2-35 Cross-section TEM of a "Spacer-2" device with 30 nm gate length, 25 nm spacer width and 45 nm $Si_{0.99}C_{0.01}$ stressors. "Spacer-1" device (not shown here) has a 40 nm spacer. The narrower spacer width in a "Spacer-2" device allows closer proximity between the $Si_{0.99}C_{0.01}$ S/D stressors and the channel. An oxide hardmask of ~10 nm SiO <sub>2</sub> on top of the fin allows the devices to function as DG FinFETs                                                                                                                                                                     |

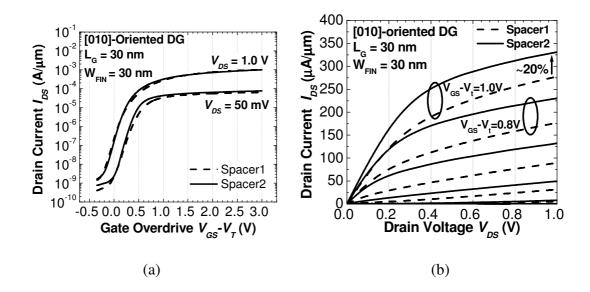

| Figure 2-36 (a) Subthreshold characteristics of a pair of DG FinFETs with similar DIBL and subthreshold swing. "Spacer1" and "Spacer2" have spacer widths of ~40 nm and ~25 nm respectively. (b) $I_{DS}$ - $V_{DS}$ characteristics of the same pair of devices show ~20% $I_{Dsat}$ enhancement of "Spacer-2" SiC S/D FinFETs over "Spacer-1" SiC S/D FinFETs. A small fraction of this enhancement is attributed to series resistance reduction                                                                                                                                                                      |

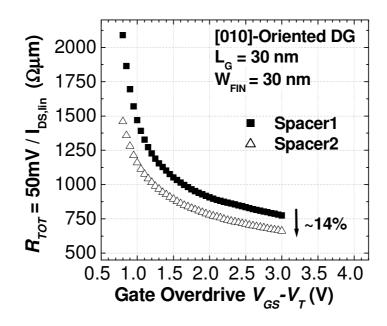

| Figure 2-37 Series resistance extraction by examining the asymptotic behaviour of total resistance at large gate bias estimates 14% reduction in series resistance for this pair of devices                                                                                                                                                                                                                                                                                                                                                                                                                             |

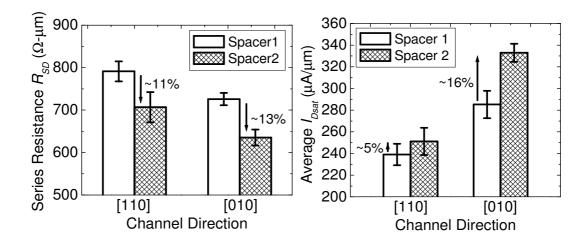

| Figure 2-38 (a) Average estimated series resistances are shown for the 2 channel directions. The reduction in series resistances for both channel directions is comparable. This suggests similar contributions to $I_{Dsat}$ enhancement from series resistance reduction for both channel directions. (b) Average $I_{Dsat}$ enhancement is much higher for [010]-oriented devices than for [110]-oriented devices. Hence, increased strain effects from closer proximity between the Si <sub>0.99</sub> C <sub>0.01</sub> S/D stressors and the channel accounts for a large fraction of the $I_{Dsat}$ enhancement. |

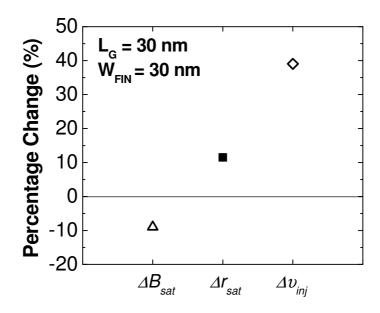

| Figure 2-39 Both $B_{sat}$ and $r_{sat}$ of the "Spacer-2" device are degraded over that of "Spacer-1". However, $v_{inj}$ is significantly enhanced by almost 40%. Hence, the $I_{Dsat}$ enhancement of the "Spacer-2" device over the "Spacer-1" device is likely to come primarily from the injection velocity enhancement                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

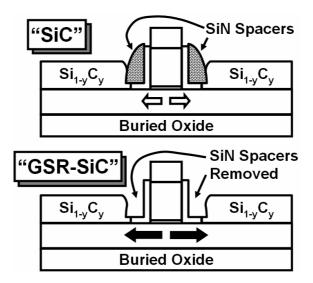

| Figure 3-1 Schematic illustrating that the device structure for both "SiC" and "GSR-<br>SiC" FinFETs are exactly the same, except for the removal of the gate<br>spacers in "GSR-SiC" devices just prior to ILD deposition                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-2 Process sequence showing key steps employed in FinFET device fabrication.<br>For Gate-Spacer-Removed-SiC or "GSR-SiC" devices, the SiN gate spacers<br>were removed by selective wet etching after S/D implant activation                                                                                                                                                                                                                                             |

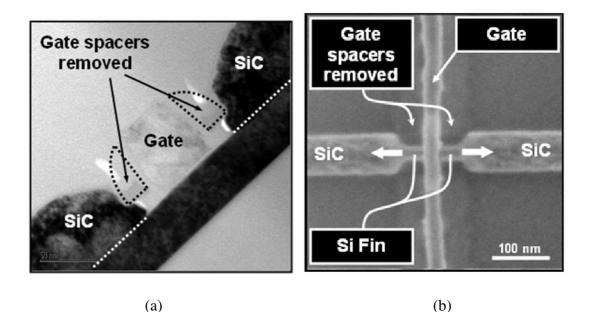

| <ul> <li>Figure 3-3 (a) Cross-section TEM image showing a spacerless device with raised SiC S/D regions. The gate spacers have been selectively etched away after S/D activation. (b) Top-view SEM image of a spacerless FinFET with raised SiC S/D regions. Removing the gate spacers enhances the stress coupling to the channel, resulting in an increase in longitudinal tensile channel stress</li></ul>                                                                    |

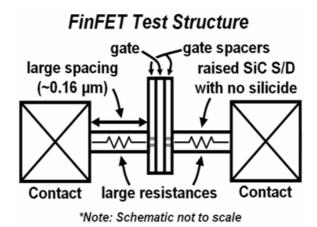

| Figure 3-4 Schematic of the FinFET test structure                                                                                                                                                                                                                                                                                                                                                                                                                                |

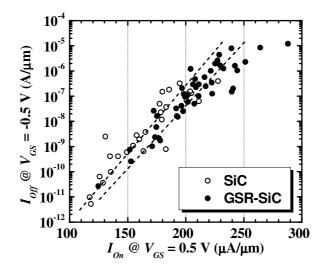

| Figure 3-5 $I_{Off}$ - $I_{On}$ plot showing enhancement in $I_{On}$ of GSR-SiC devices over conventional SiC devices at a given $I_{Off}$                                                                                                                                                                                                                                                                                                                                       |

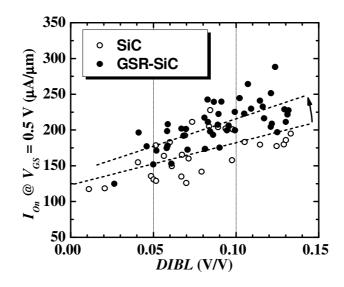

| Figure 3-6 $I_{On}$ -DIBL plot showing improvement in $I_{On}$ at a given value of DIBL. It is observed that the enhancement in $I_{On}$ increases with DIBL                                                                                                                                                                                                                                                                                                                     |

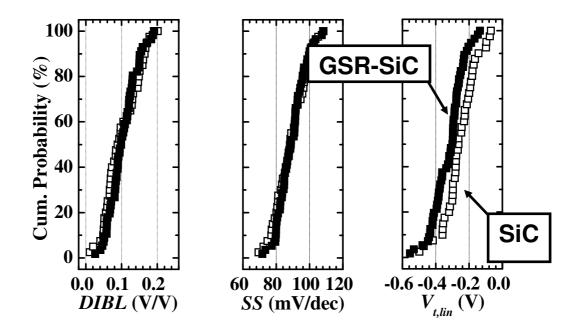

| Figure 3-7 Cumulative probability plots of <i>DIBL</i> , SS and $V_{t,lin}$                                                                                                                                                                                                                                                                                                                                                                                                      |

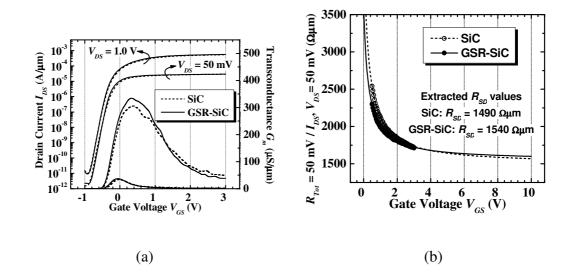

| Figure 3-8 Electrical results for a pair of SiC and GSR-SiC FinFETs ( $W_{Fin} = 40 \text{ nm}$ , $L_G = 70 \text{ nm}$ ). (a) $I_{DS}$ - $V_{GS}$ and $G_m$ - $V_{GS}$ characteristics. Values of DIBL and subthreshold swing in this pair of devices are closely matched. Improved transconductance is observed in the GSR-SiC FinFET. (b) $R_{Tot}$ - $V_{GS}$ characteristics. S/D series resistances were estimated to be quite similar, which allows for a fair comparison |

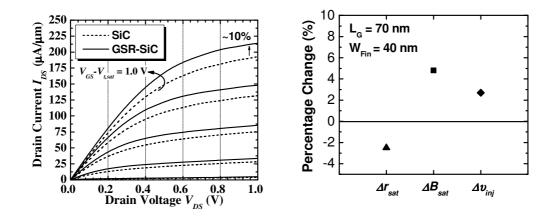

| Figure 3-9 (a) $I_{DS}$ - $V_{DS}$ family of curves ( $V_{GS}$ - $V_{t,sat} = 0$ to 1.0 V in steps of 0.2 V). At $V_{GS}$ - $V_{t,sat}$ =1.0 V, $I_{Dsat}$ of the GSR-SiC FinFET was enhanced by 10% over that of the SiC FinFET. (b) Extraction of backscattering parameters shows improvement in backscattering ratio $r_{sat}$ , ballistic efficiency $B_{sat}$ , and injection velocity $v_{inj}$                                                                            |

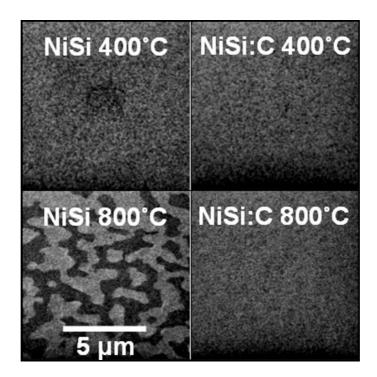

| Figure 3-10 SEM images showing good thermal stability of NiSi:C compared to NiSi77                                                                                                                                                                                                                                                                                                                                                                                               |

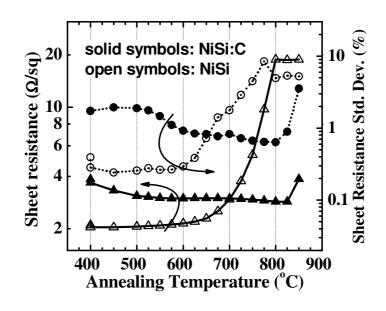

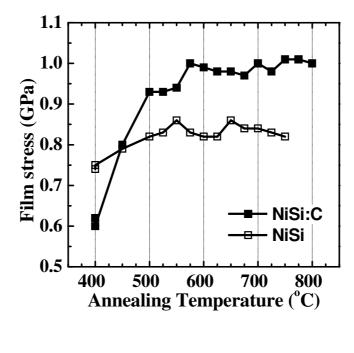

| Figure 3-11 Evolution of (a) sheet resistance and its uniformity across a 200 mm wafer<br>in NiSi and NiSi:C films and (b) stress evolution in NiSi and NiSi:C films,<br>with cumulative isochronal anneals at increasing temperatures. In NiSi:C,<br>stress increases from ~0.6 GPa to ~1 GPa with annealing at temperatures up<br>to about 575°C, after which the stress levels appear to saturate                                                                             |

| Figure 3-12 FinFET fabrication process flow. A post-silicidation anneal enhances silicide stress                                                                                                                                                                                                                                                                                                                                                                                 |

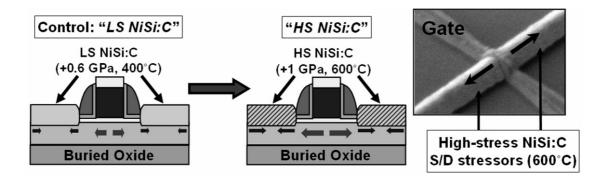

| Figure 3-13 Schematic showing the experiment splits. In "HS NiSi:C" split, a post-<br>silicidation stress enhancing anneal was performed                                                                                                                                                                                                                                                                                                                                         |

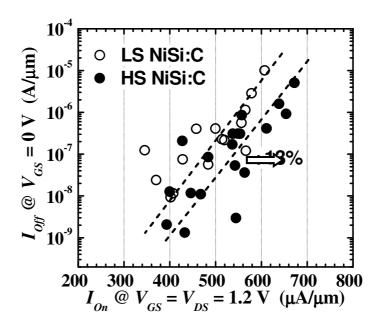

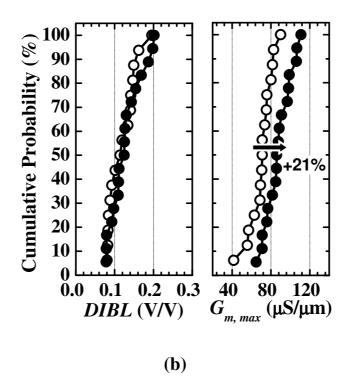

| Figure 3-14 (a) $I_{Off}$ - $I_{On}$ characteristics showing ~13% $I_{On}$ enhancement at a given $I_{Off}$ of $10^{-7}$ A/µm. (b) Cumulative distribution for <i>DIBL</i> and peak linear $G_m$ for the                                                                                                                                                                                                                                                                         |

|        | same set of devices. Open circles are for low-stress NiSi:C contacts (LS NiSi:C) and closed circles are for high-stress NiSi:C contacts (HS NiSi:C). <i>DIBL</i> values are comparable for this set of devices. Devices with HS NiSi:C show a median peak $G_m$ enhancement of about 21% over devices with LS NiSi:C.                                                                                                                                                     | 81 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

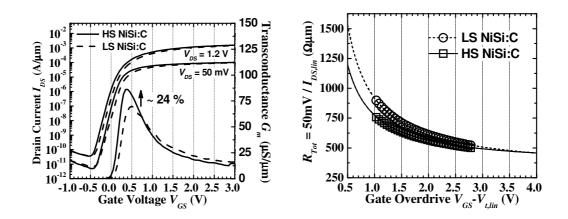

| Figure | 3-15 (a) $I_{DS}$ - $V_{GS}$ and $G_m$ - $V_{GS}$ characteristics of a pair of "LS NiSi:C" and "HS NiSi:C" devices. (b) $R_{Tot}$ is plotted against gate overdrive $V_{GS}$ - $V_{t,lin}$ for the same pair of matched devices. The gate length is ~40 nm. S/D series resistances are estimated to be comparable in both devices.                                                                                                                                        | 82 |

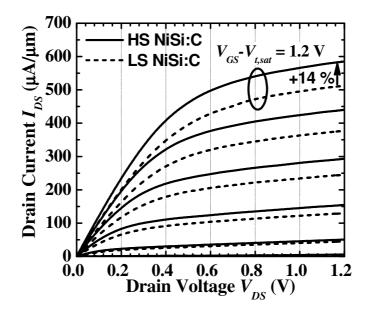

| Figure | 3-16 $I_{DS}$ - $V_{DS}$ family of curves ( $V_{GS}$ - $V_{t,sat} = 0$ to 1.2 V in steps of 0.2 V, $V_{t,sat} = V_{GS}$<br>where $I_{DS} = 10^{-7}$ A/µm when $V_{DS} = 1.2$ V). A ~14% $I_{Dsat}$ or $I_{On}$ enhancement<br>due to increased silicide-induced stress effects is observed                                                                                                                                                                                | 83 |

| Figure | 3-17 FinFET fabrication process flow showing a single additional step of gate<br>hardmask removal for the "HS NiSi:C + FUSI Gate" split. A post-<br>silicidation anneal enhances silicide stress for both "HS NiSi:C" and "HS<br>NiSi:C + FUSI Gate" splits.                                                                                                                                                                                                              | 84 |

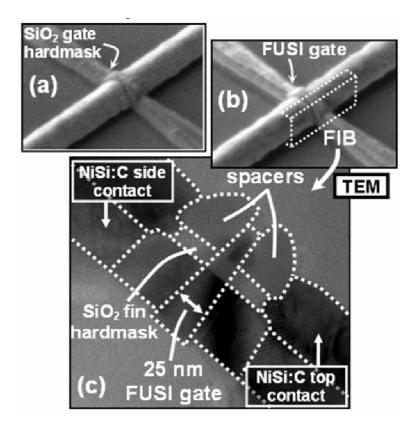

| Figure | 3-18 Isometric-view SEM images showing (a) a poly-Si gate FinFET with HS<br>NiSi:C contacts (poly-Si gate is capped by a gate hardmask), and (b) a FUSI<br>gate FinFET with HS NiSi:C contacts. (c) TEM image of a device as shown<br>in (b). One of the FUSI side-gates is captured within the FIB sample                                                                                                                                                                | 85 |

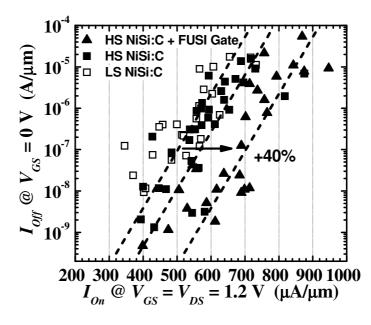

| Figure | 3-19 Integrating HS NiSi:C contacts with FUSI metal gate gives a combined enhancement of ~40 %.                                                                                                                                                                                                                                                                                                                                                                           | 86 |

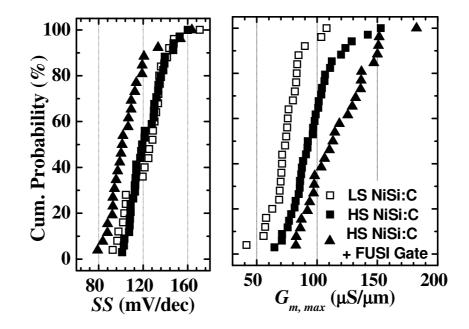

| Figure | 3-20 Cumulative distributions of SS and $G_m$ of the same sets of devices used for<br>the $I_{Off}$ - $I_{On}$ plot. A clear improvement in SS is obtained for FUSI devices<br>due to improved gate control. $G_m$ enhancement is due to stress effects in<br>"HS NiSi:C" devices. In "HS NiSi:C+FUSI Gate" devices, the<br>enhancement is due to the elimination of the poly-depletion effect, as well<br>as gate-induced channel stress effects.                        | 87 |

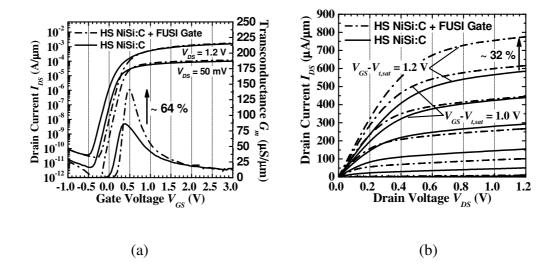

| Figure | 3-21 (a) $I_{DS}$ - $V_{GS}$ and $G_m$ - $V_{GS}$ characteristics of a pair of "HS NiSi:C" and "HS NiSi:C + FUSI gate" devices. With FUSI, gate stress effects and increase in $C_{ox}$ results in significant peak $G_m$ enhancement. (b) Integration with a high-stress FUSI metal gate results in a further 32 % $I_{Dsat}$ enhancement at $V_{GS}$ - $V_{t,sat} = 1.2$ V, where $V_{t,sat} = V_{GS}$ at which $I_{DS} = 1 \times 10^{-7}$ A/µm when $V_{DS} = 1.2$ V. | 87 |

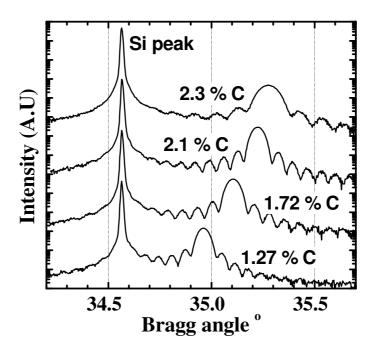

| Figure | 3-22 HRXRD rocking curve of Si:CP films with various substitutional carbon percentages showing excellent crystallinity in the films despite the high carbon content.                                                                                                                                                                                                                                                                                                      | 92 |

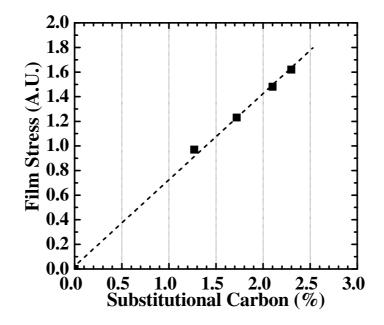

| Figure | 3-23 Wafer curvature measurements indicate a linear relationship between film stress and substitutional carbon percentage in the Si:CP films. This implies that higher stress can be obtained in the FinFET channel regions by incorporating Si:CP S/D stressors of higher substitutional carbon percentages.                                                                                                                                                             | 93 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

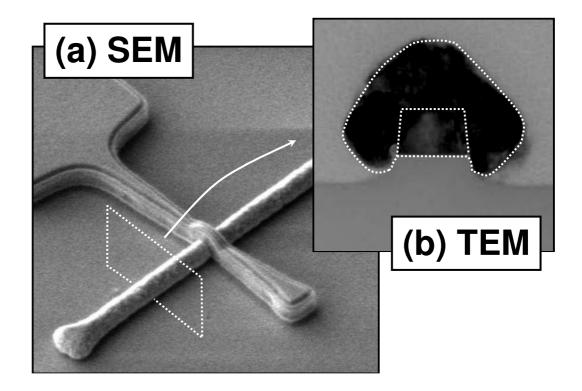

|     | Figure 3-24 (a) Isometric-view SEM image showing selective epitaxial growth of<br>Si:CP with 1.7 atomic percent of substitutional carbon concentration (also<br>denoted as "Si:CP 1.7%" in subsequent figures) in the S/D regions of the<br>FinFET test structure. (b) Cross-section TEM of the indicated S/D regions<br>shows Si:CP growth on both the top and side surfaces of the fin, forming an<br>extended Π-shaped S/D stressor that wraps around the Si fin for maximum<br>lattice interaction.                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Figure 3-25 Process sequence showing key steps employed in FinFET device fabrication. Double-gate (DG) FinFETs were fabricated. The gate spacer formation scheme involves an extra in-situ etch to remove fin spacers, allowing the formation of extended Π-shaped S/D stressors                                                                                                                                                                                                                                                                         |

|     | Figure 3-26 Schematic showing the three splits fabricated. They are structurally similar except for the selectively-grown S/D epitaxial film. Si:CP with substitutional carbon percentages of 1.7% and 2.1% were grown in the S/D regions of the strained FinFETs. Si:P was grown in the S/D regions of the control FinFETs.                                                                                                                                                                                                                             |

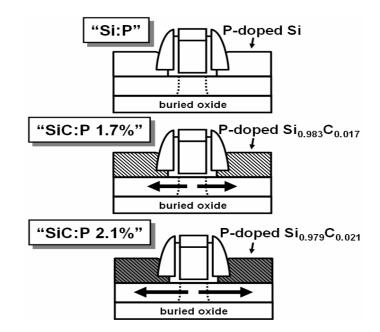

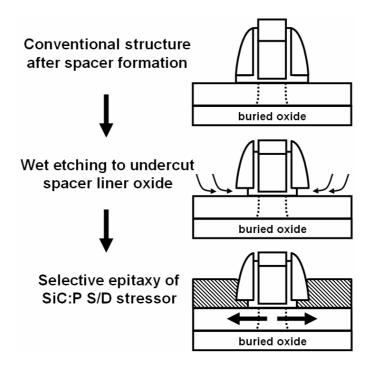

|     | Figure 3-27 Schematic showing the key steps for forming the Si:CP S/D stressors for strained devices or Si:P S/D for control devices. Wet etching with HF is performed to undercut the SiO <sub>2</sub> liner oxide underneath the SiN spacer. This enables the epitaxial growth of Si:CP or Si:P in the S/D extension regions. Extension resistance is also reduced since the films are <i>in-situ</i> doped. For FinFETs with Si:CP S/D, closer proximity of S/D stressors to the channel leads to enhanced stress coupling for larger stress benefits |

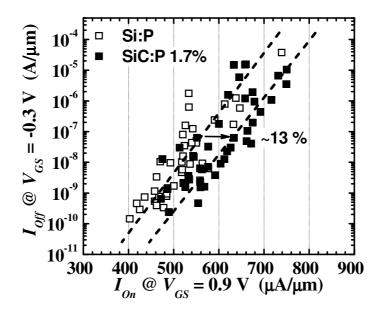

|     | Figure 3-28 $I_{Off}$ - $I_{On}$ plot shows ~13% enhancement in $I_{On}$ at a fixed $I_{Off}$ of $1 \times 10^{-7}$ A/µm due to the incorporation of Si:CP S/D stressors with 1.7% substitutional carbon.                                                                                                                                                                                                                                                                                                                                                |

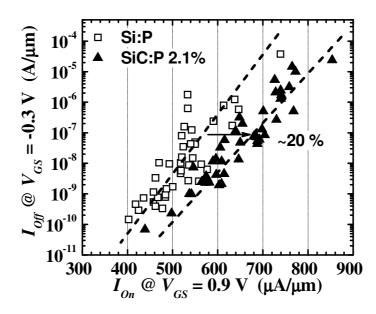

|     | Figure 3-29 $I_{Off}$ - $I_{On}$ plot shows ~20% enhancement in $I_{On}$ at a fixed $I_{Off}$ of $1 \times 10^{-7}$ A/µm due to the incorporation of Si:CP S/D stressors with 2.1% substitutional carbon.                                                                                                                                                                                                                                                                                                                                                |

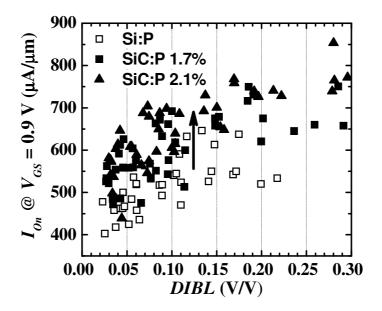

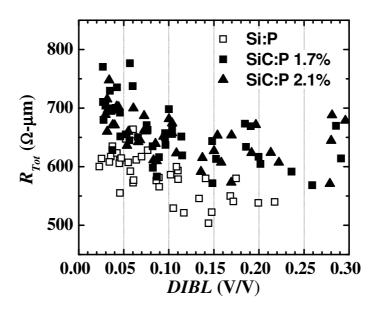

| 100 | Figure 3-30 Up to ~20% enhancement in $I_{On}$ can be obtained by incorporating Si:CP S/D stressors with 2.1% substitutional carbon at a fixed value of drain-<br>induced barrier lowering (DIBL). For the split with Si:CP 1.7%, an enhancement of ~15% can be obtained.                                                                                                                                                                                                                                                                                |

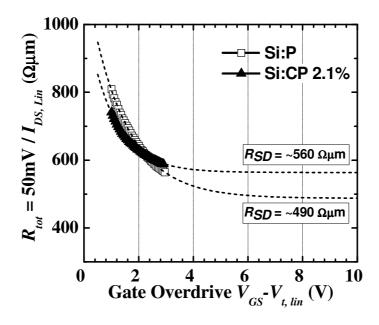

| 101 | Figure 3-31 $R_{Tot}$ at high gate overdrive is indicative of the S/D series resistances of the various types of devices ( $R_{Tot} = 50 \text{ mV} / I_{DS} @ V_{GS}-V_{t,lin} = 2.7 \text{ V}, V_{DS} = 50 \text{ mV}$ ). It was found that Si:P devices have generally lower series resistances                                                                                                                                                                                                                                                       |

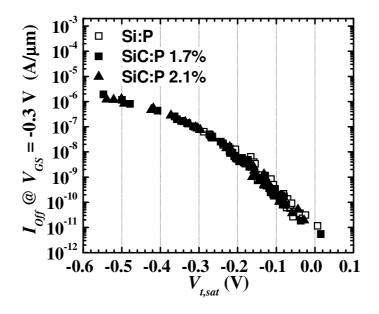

| 102 | Figure 3-32 Excellent match in control of short channel effects for both Si:P and Si:CP devices is evident from the comparable $I_{Off}$ for devices with different values $V_{t,sat}$ . Threshold voltage is lower than usual due to the use of n <sup>+</sup> poly-Si gate with a relatively low channel doping concentration.                                                                                                                                                                                                                         |

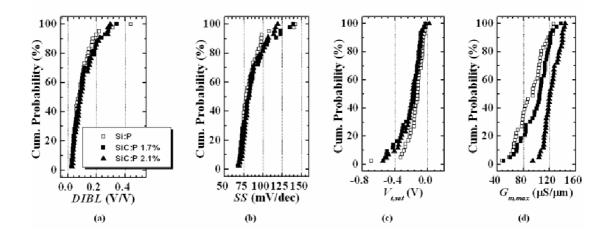

|     | Figure 3-33 Cumulative distributions of (a) <i>DIBL</i> , (b) <i>SS</i> , (c) $V_{t,sat}$ ( $V_{t,sat} = V_{GS} @ I_{DS} = 1\mu A/\mu m$ , $V_{DS} = 1.2$ V) and (d) $G_{m,max}$ of all the FinFET devices employed in the $I_{Off}$ - $I_{On}$ plots. All three splits have comparable <i>SS</i> and <i>DIBL</i> , suggesting similar short channel control in devices from all three splits. $V_{t,sat}$ is lower                                                                                                                                      |

| for the strained devices than for the control, possibly due to conduction band lowering. $G_{m,max}$ of both Si:CP splits show enhancement over the Si:P control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

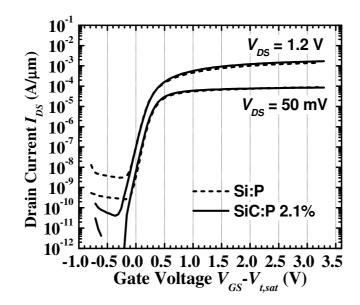

| Figure 3-34 Transfer characteristics of a pair of matched FinFET devices showing comparable <i>DIBL</i> and <i>SS</i> . The <i>DIBL</i> is 85 mV/V and the <i>SS</i> is 80 mV/decade ( $V_{t,sat} = V_{GS} @ I_{DS} = 100$ nA/ µm, $V_{DS} = 1.2$ V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 3-35 S/D series resistances of the matched devices were estimated by extrapolating $R_{Tot}$ to high gate overdrive voltages using a first-order exponential decay fit. The Si:P device has a slightly lower series resistance then the Si:CP 2.1% device. 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

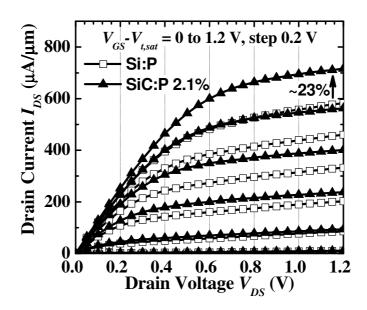

| Figure 3-36 $I_{DS}$ - $V_{DS}$ curves showing 23% $I_{Dsat}$ enhancement for this pair of matched devices ( $V_{t,sat} = V_{GS} @ I_{DS} = 100 \text{ nA}/ \mu\text{m}, V_{DS} = 1.2 \text{ V}$ ). This enhancement is mainly attributed to strain effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

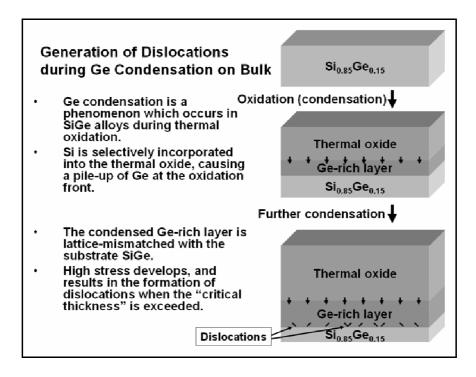

| Figure 4-1 Schematic illustrating the phenomenon of Ge condensation of SiGe (eg. Si <sub>0.85</sub> Ge <sub>0.15</sub> ) bulk substrates. Ge enrichment in the Ge-rich layer results in a large lattice mismatch with the Si <sub>0.85</sub> Ge <sub>0.15</sub> substrate. This results in dislocation-mediated strain relaxation. 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

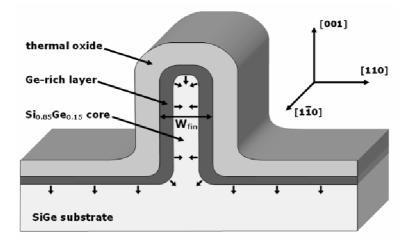

| Figure 4-2 Cross-sectional schematic of a SiGe fin heterostructure during Ge condensation. The piling up of Ge at the oxidation front to form a Ge-rich layer is shown. As oxidation proceeds, the Ge-rich layer increases in thickness and the fin width ( $W_{fin}$ ) decreases. This also results in decreasing $Si_{0.85}Ge_{0.15}$ core thickness ( $T_{core}$ ). 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

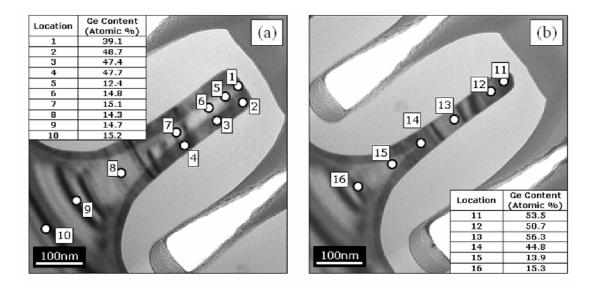

| Figure 4-3 Cross-sectional TEM images of 2 SiGe fins after 12 hours of Ge condensation. The oxidation temperature of $875^{\circ}$ C is below the viscous flow temperature of thermal oxide of about $950^{\circ}$ C, resulting in the unique geometry of the thermal oxide encapsulating the fin. The vertical sidewall surfaces of the SiGe fins also appear to be very smooth, making them suitable for FinFET applications where sidewall surface roughness would degrade carrier mobility dramatically at high electric field. The Ge atomic concentration values obtained by EDS at several locations in each fin are shown. (a) A wider fin ( $W_{fin}$ =100 nm) showing the Ge-rich layer and the sandwiched Si <sub>0.85</sub> Ge <sub>0.15</sub> core. (b) A narrower fin ( $W_{fin}$ =45 nm) in which the Ge-rich layers have merged from opposite sides of the fin |

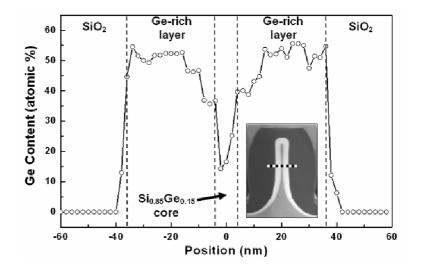

| Figure 4-4 Ge concentration profile across a medium-width SiGe fin ( $W_{fin}$ =70nm, see inset) that has undergone 18 hours of Ge condensation. The Ge concentration within the Ge-rich layer is quite uniform. The Ge concentration profile is observed to be rather abrupt at the interface between the Ge-rich layer and the Si <sub>0.85</sub> Ge <sub>0.15</sub> substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

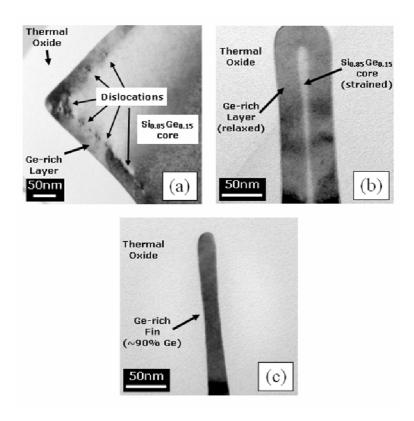

| Figure 4-5 Cross-sectional TEM images highlighting dislocations in 3 SiGe fins of different fin widths ( $W_{fin}$ ) after 18 hours of Ge condensation. (a) A wide fin ( $W_{fin}$ =480nm) with a high dislocation density at the interface between the Ge-rich layer and the Si <sub>0.85</sub> Ge <sub>0.15</sub> core. (b) A medium-width ( $W_{fin}$ =70nm) fin with a much lower dislocation density. (c) A narrow homogenous Ge-rich                                                                                                                                                                                                                                                                                                                                                                                                                                     |

xix

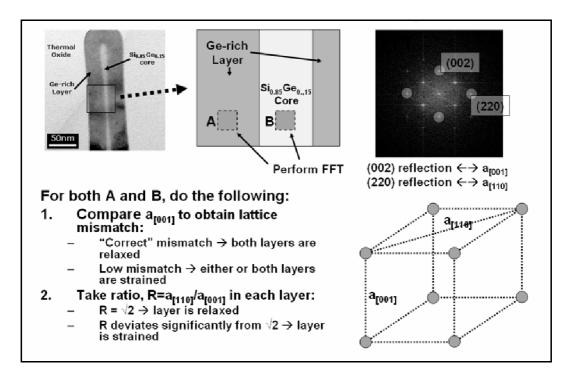

| Figure 4-6 | A schematic explaining how the estimation of strain using HRTEM FFT diffractogram analysis is performed                                                                                                                                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

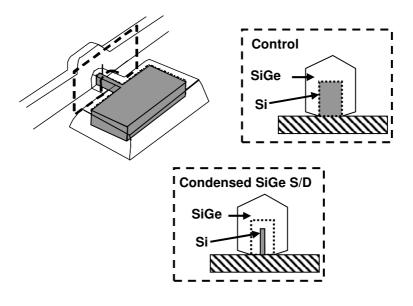

| Figure 5-1 | Schematic of device structures fabricated in this work showing the selectively grown SiGe on the S/D regions. The schematic also shows the difference in the Ge distribution in the fin at the S/D region for a control FinFET and a FinFET with condensed SiGe S/D. Si region is shown in grey and SiGe region is shown in white |

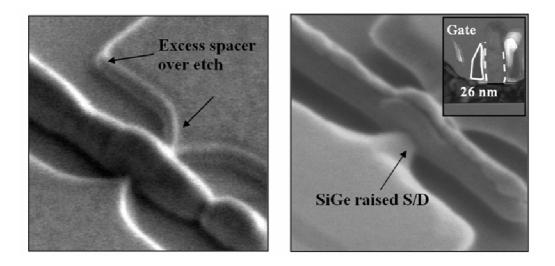

| Figure 5-2 | 2 (a) SEM images of the FinFET structure after SiN spacer etch. An excessive over-etch step was used for the removal of spacer stringers (b) SEM image of FinFET with SiGe S/D after Ge condensation and oxide removal. The inset shows the TEM image of the gate stack, having a gate length of 26 nm                            |

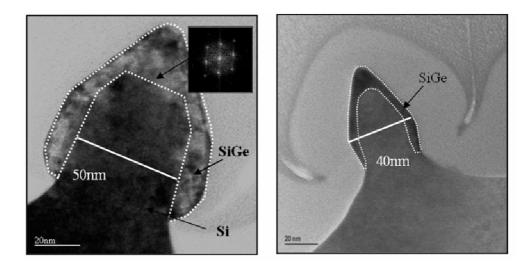

| Figure 5-3 | (a) TEM image of a fin structure with SiGe grown on the top (100) and the sidewall (110) surfaces. (b) Ge diffuses into the fin after condensation at $950^{\circ}$ C for 20 min in an oxygen ambient as indicated by the reduction of Si fin width                                                                               |

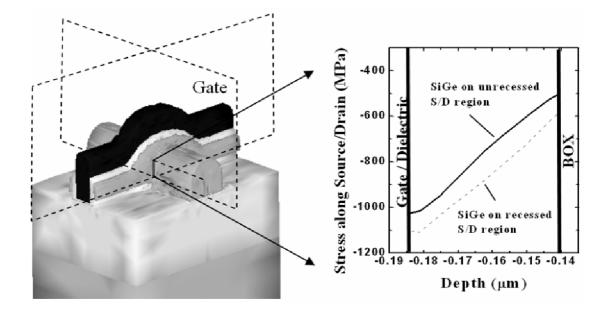

| Figure 5-4 | Stress simulation for FinFET (fin width = 20 nm) with recessed profile shows a larger compressive strain                                                                                                                                                                                                                          |

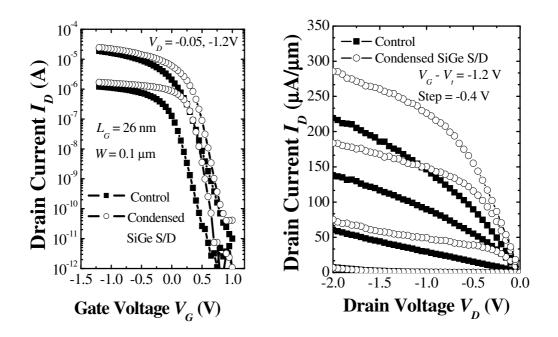

| Figure 5-5 | (a) $I_D$ - $V_G$ characteristics of FinFET devices having an $L_G$ of 26nm. (b) $I_D$ - $V_D$ characteristics of FinFET devices at various gate overdrives ( $V_G$ - $V_t$ ).<br>FinFET with condensed SiGe S/D shows a higher drive current                                                                                     |

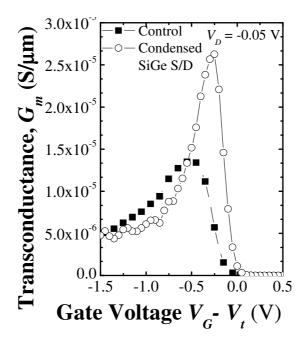

| Figure 5-6 | Comparison of transconductance $G_m$ at the same gate overdrive, illustrating<br>an enhancement of 91% for the FinFET with condensed SiGe S/D over the<br>control device                                                                                                                                                          |

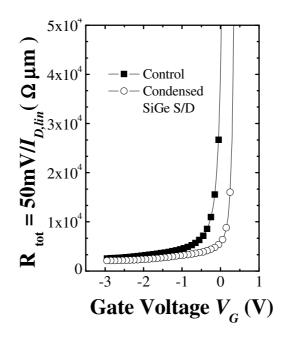

| Figure 5-7 | Extraction of series resistance by examining the the total resistance, which asymptotically approaches the value of the S/D series resistance at large gate bias                                                                                                                                                                  |

| Figure 6-1 | Process flow schematic which summarizes key steps in the device fabrication process                                                                                                                                                                                                                                               |

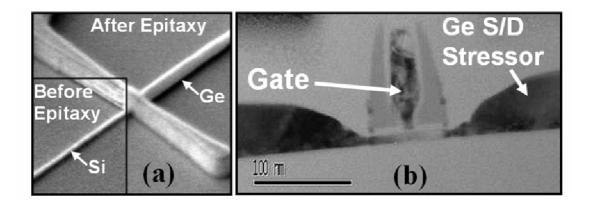

| Figure 6-2 | <ul> <li>(a) SEM images taken at a 45° tilt, showing the S/D regions of a nanowire-FET before and after Ge epitaxial growth. Excellent selectivity is achieved</li> <li>(b) TEM image showing a cross-section of the gate structure and Ge S/D stressors.</li> </ul>                                                              |

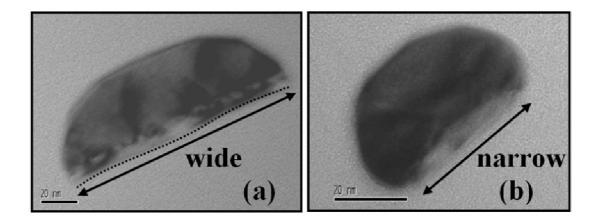

| Figure 6-3 | TEM images of Ge grown on ultra-thin SOI showing (a) a wide active region with multiple dislocations at the Ge-Si interface, and (b) a narrow active region with a greatly reduced dislocation density                                                                                                                            |

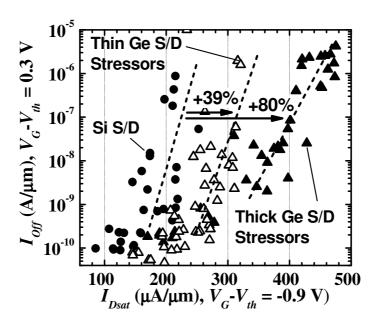

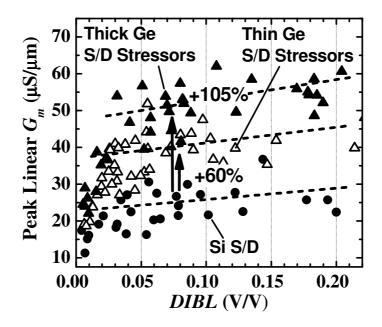

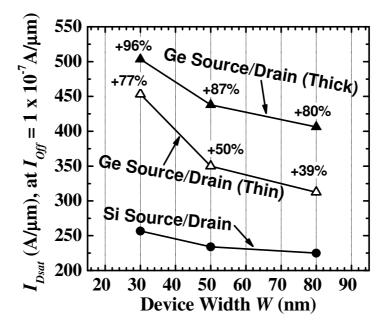

| Figure 6-4 | Thin and Thick Ge S/D stressors result in 39% and 80% $I_{Dsat}$ enhancement, respectively, at a fixed $I_{Off}$ of 1×10 <sup>-7</sup> A/µm. (W = 80 nm)                                                                                                                                                                          |

| Figure 6-5 | Hole mobility is very significantly enhanced by large compressive stress due to Ge S/D stressors. Peak transconductance is increased by 60% and 105%, respectively, at a DIBL of 75 mV/V                                                                                                                                          |

| Figure 6-6 $I_{Dsat}$ enhancement (indicated in %) for 2 different Ge S/D stressor<br>thicknesses, compared to a control with raised Si S/D. UTB-FETs with<br>small width <i>W</i> have larger enhancement. For <i>W</i> of 30 nm, $I_{Dsat}$ enhancement<br>due to Thin Ge S/D stressor approaches that of Thick Ge S/D stressor                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

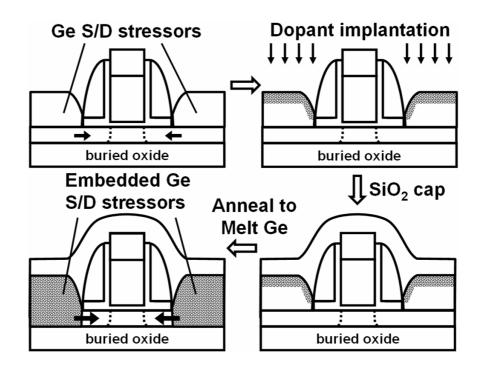

| Figure 6-7 New Melt-Enhanced Dopant (MeltED) diffusion and activation process.<br>After shallow S/D implant and SiO <sub>2</sub> capping, a 950°C spike anneal melts<br>the Ge-rich region, and achieves these key objectives: Interface inter-<br>diffusion <i>embeds</i> the Ge stressor; Dopant diffuses, redistributes uniformly,<br>and is substitutionally incorporated as Ge recrystallizes |

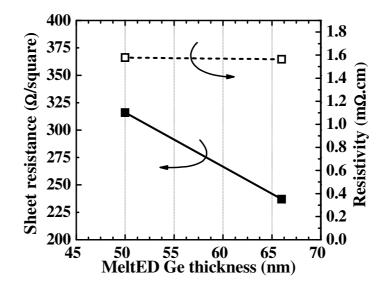

| Figure 6-8 Sheet resistance measurements of MeltED Ge with 2 thicknesses. Both received surface $BF_2^+$ implants only. Both films have near identical resistivity values, which confirms that Boron is uniformly diffused in the liquid Ge and is substitutionally incorporated as Ge re-crystallizes                                                                                             |

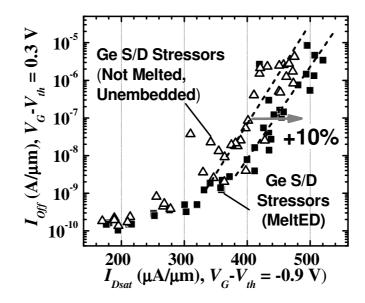

| Figure 6-9 MeltED Ge S/D stressors are embedded, and gives a further 10% $I_{Dsat}$ enhancement at $I_{Off}$ of $1 \times 10^{-7}$ A/µm, as compared to the unembedded Ge S/D stressors (also plotted in Fig. 4). Greater strain effects come with S/D stressor embedding                                                                                                                          |

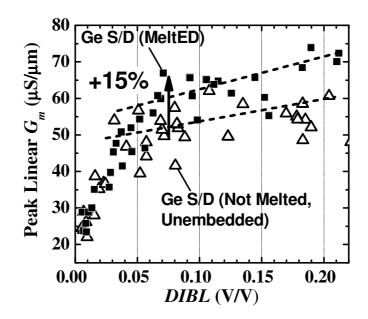

| Figure 6-10 An additional 15% enhancement in peak transconductance was obtained at a DIBL of 75 mV/V as a result of increased channel strain                                                                                                                                                                                                                                                       |

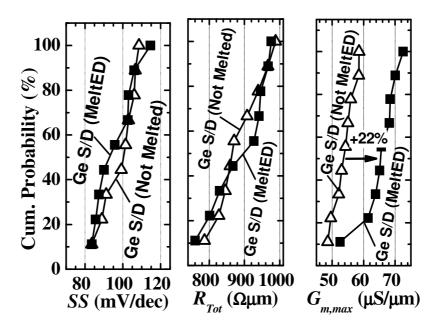

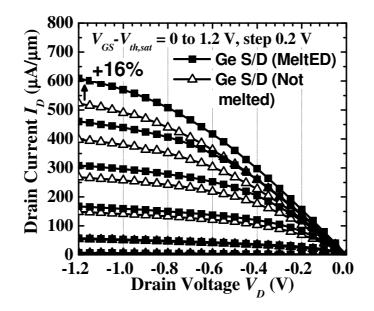

| Figure 6-11 P-FETs with MeltED/Embedded Ge S/D have 22% higher $G_{m,max}$ than<br>those with unembedded Ge S/D (not melted). All p-FETs have the same<br>short channel control and $L_G$ (35nm). $R_{Tot}$ at high gate overdrive ( $V_G$ - $V_{th}$ =<br>2.5V) estimates $R_{SD}$ to be comparable                                                                                               |

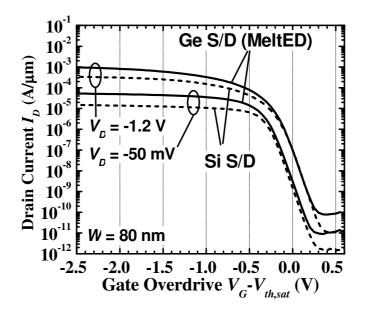

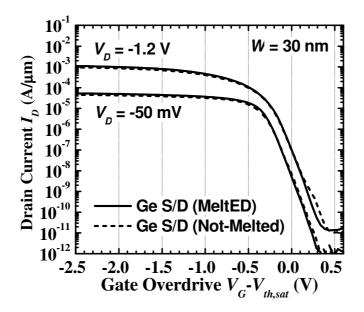

| Figure 6-12 $I_D$ - $V_G$ plot showing comparable DIBL and SS for a p-FET with Raised Si Control and a p-FET with Embedded Ge S/D (MeltED)150                                                                                                                                                                                                                                                      |

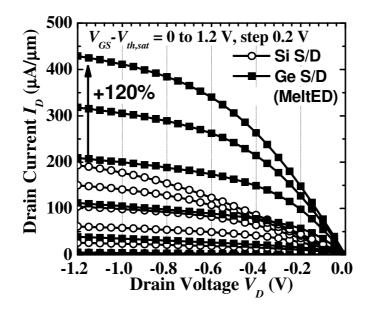

| Figure 6-13 $I_D$ - $V_D$ plot of same pair of devices in Fig. 14. Embedded Ge S/D (MeltED) gives a 120% $I_{Dsat}$ enhancement over a p-FET with Si S/D                                                                                                                                                                                                                                           |

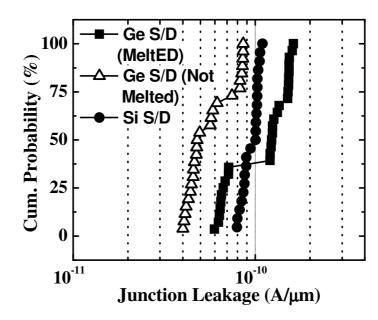

| Figure 6-14 Ge S/D stressors does not significantly impact junction leakage, indicating that defects are well-confined outside the extension regions                                                                                                                                                                                                                                               |

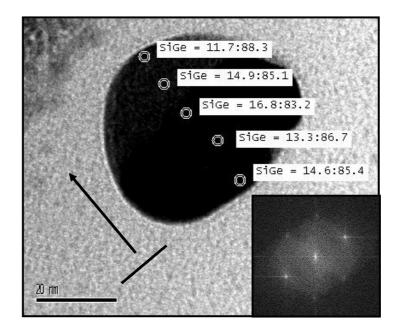

| Figure 6-15 EDS analysis of MeltED Ge nanowire S/D shows uniform ~85% Ge concentration from top to bottom. Reciprocal space diffractogram (inset) shows single crystallinity                                                                                                                                                                                                                       |