### APPLICATION OF PEEC MODELING FOR THE DEVELOPMENT OF A NOVEL MULTI-GIGAHERTZ TEST INTERFACE WITH FINE PITCH WAFER LEVEL PACKAGE

JAYASANKER JAYABALAN

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2005

### APPLICATION OF PEEC MODELING FOR THE DEVELOPMENT OF A NOVEL MULTI-GIGAHERTZ TEST INTERFACE WITH FINE PITCH WAFER LEVEL PACKAGE

BY

JAYASANKER JAYABALAN M.Sc.(Engg), National University of Singapore

A THESIS SUBMITTED FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2005

#### ACKNOWLEDGMENTS

I like to thank my research supervisors, Professor Leong Mook Seng, Dr. Ooi Ban Leong and Dr. Mahadevan Krishna Iyer for the invaluable advice and guidance throughout the course of this research. Their emphasis on independent and multidisciplinary research has given me opportunities to explore many aspects of electromagnetic modeling, measurements and electronic packaging.

The National University of Singapore and Institute of Microelectronics provided many facilities without which this work would not have materialized. In particular, the readily available literature and computing resources in NUS and the assembly, measurement and analysis equipment facilities in IME have greatly helped me in completing this work successfully. I am also honored to be awarded the Nano-Wafer Level Packaging Program research fellowship provided by Singapore's Agency for Science, Technology and Research during my candidature.

My appreciation to Dr. Mihai of IME for his help on microwave modeling and measurements; Dr. Albert Ruehli of IBM for clarifications on PEEC modeling via email; Prof. M. S. Nakhla of Carleton University for clarifications on circuit solvers for delay differential equations when he visited the Institute for Mathematical Sciences; Prof. Andrew Tay and my NUS laboratory colleagues Dr. Xu, Ms. Guo Lin, Mr. Wu Bin, Mr. Song and Mr. Sing for the numerous discussions and help which have contributed to this work; my IME colleagues Mr. Sivakumar and Mr. Ranjan for help in test sample preparations.

I am grateful to my wife Padmalatha, my parents and in-laws for their kind understanding and support throughout my studies. I thank my daughters Manneyaa and Yahavi who sacrificed my company on many holidays and weekends.

This thesis is dedicated to my Divine Mother.

i

# **TABLE OF CONTENTS**

| ACKNOWLEDGMENT    | i   |

|-------------------|-----|

| TABLE OF CONTENTS | ii  |

| ABSTRACT          | vii |

| LIST OF FIGURES   | ix  |

| LIST OF TABLES    | xiv |

| LIST OF SYMBOLS   | XV  |

| CHAPTER 1                                                                     | 1  |

|-------------------------------------------------------------------------------|----|

| INTRODUCTION                                                                  | 1  |

| 1.1 Background and Motivation                                                 | 1  |

| 1.2 Partial Element Equivalent Circuit Modeling                               | 3  |

| 1.3 Solving Delay Differential Equation Systems                               | 4  |

| 1.3.1 DDE Example with Two Nodes                                              | 4  |

| 1.3.2 Time Stepping Algorithm for Solving Delay Differential Equation Systems | 6  |

| 1.4 Scattering Parameter Analysis of Circuits                                 | 8  |

| 1.5 Scope and Organization of This Thesis                                     | 10 |

| 1.6 Original Contributions                                                    | 13 |

| 1.6.1 Journals                                                                | 14 |

| 1.6.2 Journal Submissions under Review                                        | 15 |

| 1.6.3 Conferences                                                             | 15 |

| 1.6.4 Patents                                                                 | 16 |

| CHAPTER 2                                 |        |

|-------------------------------------------|--------|

| MODELING OF HOMOGENEOUS LOSSLESS MEDIA BY | Y PEEC |

| МЕТНОД                                    | 17     |

| 2.1 Introduction                          | 17     |

| 2.2 Deriving the PEEC Model in Homogeneous Media      | 18 |

|-------------------------------------------------------|----|

| 2.3 Baker-Campbell-Hausdorff-Dynkin Series Expression | 22 |

| 2.4 Scaling the System Matrix                         | 24 |

| 2.5 Numerical Example                                 | 27 |

| 2.6 Results and Discussions                           | 29 |

#

### PEEC AND LUMPED CIRCUIT MODELING OF HOMOGENEOUS LOSSY

| MEDIA                                        | 38 |

|----------------------------------------------|----|

| 3.1 Introduction                             | 38 |

| 3.2 PEEC Model Extension to Lossy Substrates | 38 |

| 3.3 Lumped Circuit Model in Lossy Substrates | 40 |

| 3.3.1 Equivalent Circuit Description         | 41 |

| 3.3.2 Modeling Methodology                   | 42 |

| 3.3.3 Minimizing the Residual Trace Function | 44 |

| 3.4 Results and Discussions                  | 45 |

#

| CHAPTER 5                           | 65 |

|-------------------------------------|----|

| PEEC MODELING OF MULTILAYERED MEDIA | 65 |

| 5.1 Introduction                    | 65 |

| 5.2 Interface Function              | 66 |

| 5.2.1 Example A: Inductive Open Wire Loop                   | 72 |

|-------------------------------------------------------------|----|

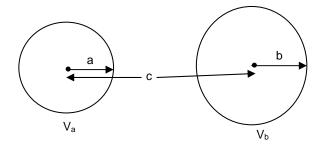

| 5.2.2 Example B: Insulated Capacitive Spheres               | 73 |

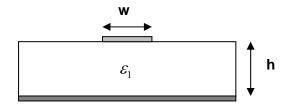

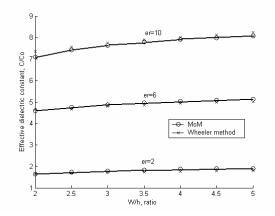

| 5.3 Two Layer System: Microstrip Capacitance                | 75 |

| 5.4 Extension to PEEC Model                                 | 77 |

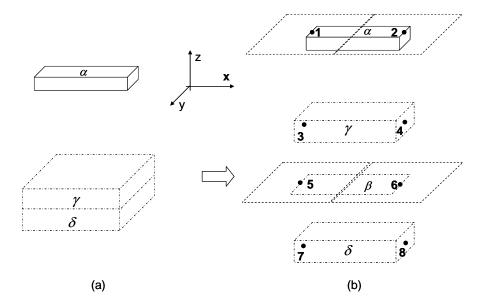

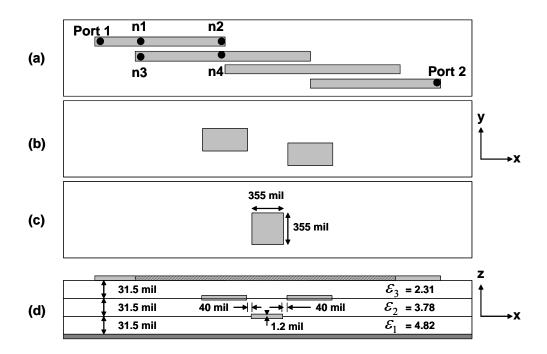

| 5.5 Multilayer PEEC Example: Coupled Microstrip Line Filter | 83 |

| 5.5.1 Three Layer Geometry                                  | 83 |

| 5.2.2 Four Layer Geometry                                   | 86 |

| 5.6 Discussion                                              | 88 |

|                                                             |    |

| CHAPTER 6                                                      | 89     |

|----------------------------------------------------------------|--------|

| DEVELOPMENT OF A NOVEL MULTIGIGAHERTZ TEST INT                 | ERFACE |

| FOR FINE PITCH WAFER LEVEL PACKAGES : AN APPLCAT               | ION OF |

| PEEC MODELING                                                  | 89     |

| 6.1 Introduction                                               | 89     |

| 6.1.1 Significance of Wafer Level Packaging                    | 89     |

| 6.1.2 WLP Test Concept                                         | 90     |

| 6.1.3 Limitations of Conventional Test Approaches for WLPs     | 91     |

| 6.1.4 Test Solution                                            |        |

| 6.2 Structure of Prototype and Fabrication                     | 93     |

| 6.2.1 Test Fixture                                             | 93     |

| 6.2.2 Device under Test                                        | 99     |

| 6.3. Model of Prototype Components                             | 101    |

| 6.3.1 WLP                                                      | 101    |

| 6.3.2 WLP Off-chip Interconnect                                | 101    |

| 6.3.3 Elastomer Mesh                                           | 103    |

| 6.3.4 Multilayer Substrate                                     | 105    |

| 6.3.5 System Level Model                                       | 108    |

| 6.4. Test Results                                              |        |

| 6.5. Adaptation of Hardware for Functional and Structural Test | 119    |

| 6.5.1 Functional versus Structural Test                        | 119    |

| 6.5.2 High Speed Signal Generation and Detection for Functional Test of Fine Pitch |

|------------------------------------------------------------------------------------|

| and Large Pin Count WLP Devices                                                    |

| 6.5.3 Eye Diagrams122                                                              |

| 6.6. Discussions                                                                   |

# CHAPTER 7......126

# CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORKS......126

| 7.1 Concluding Remarks                            | 126 |

|---------------------------------------------------|-----|

| 7.2 Suggestions for Future Works                  | 129 |

| 7.2.1 Modeling Intermediate and Far Field Effects | 130 |

| 7.2.2 Modeling Nano-Scale Size Effects            | 131 |

| REFERENCES | <br> |

|------------|------|

|            |      |

| APPENDIX A                                          | .144 |

|-----------------------------------------------------|------|

| DELAY DIFFERENTIAL EQUATION CODING EXAMPLE FOR PEEC |      |

| WITH 2 NODES                                        | 144  |

| APPENDIX B14                                                                |     |

|-----------------------------------------------------------------------------|-----|

| COMPUTATION OF GREEN'S FUNCTION INTEGRALS                                   | 149 |

| B.1 Numerical Evaluation                                                    | 149 |

| B.2 Analytical Evaluation                                                   | 152 |

| B.2.1 Approximate Forms for Removing Singularity                            | 152 |

| B.2.2 Approximate Evaluation of Self Terms from Variational Considerations. | 153 |

| APPENDIX C                                                 |     |

|------------------------------------------------------------|-----|

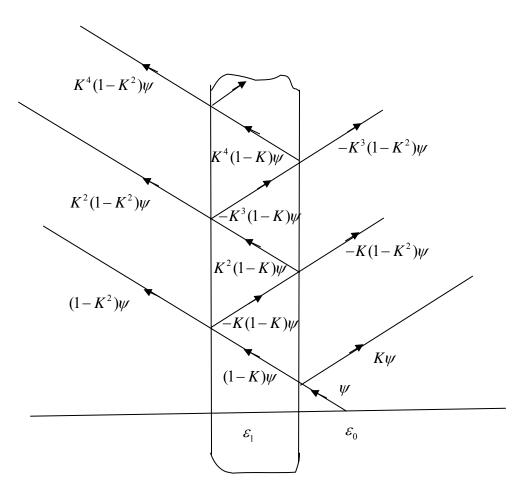

| THE METHOD OF IMAGES IN MULTILAYERS                        | 155 |

| C.1 On the Use of Image Method in Representing Multilayers | 155 |

| C.2 Multilayer Problem as a Multi-body Problem             | 156 |

| C.3 Silvester's Image Model of Spatial Green's Function | 158 |

|---------------------------------------------------------|-----|

### MODEL CONSIDERATIONS AS CIRCUIT SIZES APPROACH NANO-

### SCALE......164

| D.1 Introduction           | 164  |

|----------------------------|------|

| D.2 Modeling               | 166  |

| D.3 Results and Discussion | .169 |

| APPENDIX E1' | 72 |

|--------------|----|

|--------------|----|

## SPICE EXAMPLE CODE FOR PEEC IMPLEMENTATION......172

| APPENDIX F                                   |  |

|----------------------------------------------|--|

| OPTIMIZATION: MINIMUM, CONVERGENCE AND NOISE |  |

| SENSITIVITY                                  |  |

#### ABSTRACT

This thesis derives efficient partial element equivalent circuit (PEEC) models in homogeneous media, dielectric mesh media, inhomogeneous media with multilayered composites and applies the models for the development of a novel test interface for wafer level packages (WLP) operating at multi-gigahertz frequencies given the tight geometrical constraints of fine pitch (of the order of 100 micron) offchip interconnects and large device pin counts (of the order of thousands).

PEEC scaling technique incorporating Baker-Campbell-Hausdorff-Dynkin series for the analysis of fine pitch geometries has been proposed. An improved PEEC model is derived for homogeneous media through the scaling of circuit elements. The model is verified with a stripline geometry. Relatively good agreements between the Method of Moments simulation data and the results generated from the scaled circuit model are obtained. PEEC modeling is then extended to lossy silicon substrates using the theory of complex images. The model is verified with a measurement based lumped circuit model. The model is found to agree with measured data over a wide frequency range for coplanar waveguides fabricated on a high resistivity silicon substrate.

For wafer level package test application, there is a need for using elastomer mesh probes due to vertical and lateral compliance requirements. A novel circuit model is developed for treating the dielectric-metal composite mixture that the probe is built with. The local interaction between the dielectric and metal is factored into the Electric Field Integral equation for accurate representation of the circuit element. The model is verified with measurements. PEEC model of multilayer dielectric geometry is next developed to address the signal redistribution in WLP test hardware. To do this, the concept of mutual interactions between circuit elements is extended to an interface function. Isolation of the self and mutual components lends itself to separate treatment of the interface from the bulk substrate. This formulation was first tested in a quasi-static capacitance problem in a micro-strip. The per unit length capacitance was evaluated for different geometries and material properties. Then, transmission characteristics of a multilayered coupled micro-strip filter were analyzed. The treatment of the dielectric interface in terms of the convolution of the interface function and source function in pulse basis is found to give satisfactory results compared to other independent studies.

This thesis combines the modeling techniques derived above for developing a prototype test interface comprising of a compliant elastomer mesh for probing fine pitch wafer level packaged devices. The prototype has been built to handle multigigahertz signal propagation using 100 micron pitch GSG mesh-coplanar probes. The components of the prototype namely multilayer PCB with connectors, elastomer mesh probe, WLP interconnect and coplanar transmission lines have all been modeled. A complete system level model has been developed. The validity of the modeling as well as the efficacy of the prototype system for WLP test is demonstrated with model simulation and measurement results.

## LIST OF FIGURES

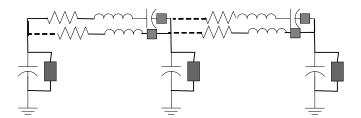

| Fig. 1.1: DDE network with two nodes                                                                |

|-----------------------------------------------------------------------------------------------------|

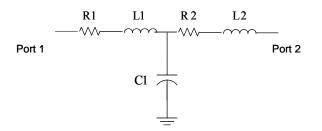

| <b>Fig. 1.2:</b> Simulation setup for S <sub>11</sub> and S <sub>21</sub>                           |

| Fig. 1.3: Simulation setup for S <sub>22</sub> and S <sub>12</sub>                                  |

| <b>Fig. 2.1:</b> PEEC model                                                                         |

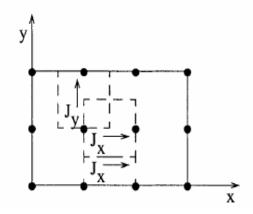

| Fig. 2.2: Sectioning the object geometry into inductance partitions                                 |

| <b>Fig. 2.3:</b> Sectioning the object geometry into capacitive partitions                          |

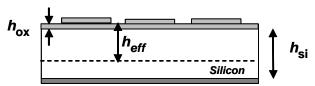

| Fig. 2.4: Cross-section of strip transmission line                                                  |

| <b>Fig. 2.5:</b> .S <sub>21</sub> magnitude (linear) versus frequency                               |

| <b>Fig. 2.6:</b> .S <sub>21</sub> phase (Degrees) versus frequency                                  |

| <b>Fig. 2.7:</b> .S <sub>21</sub> magnitude and phase error versus frequency                        |

| <b>Fig. 2.8:</b> .S <sub>11</sub> magnitude and phase error versus frequency                        |

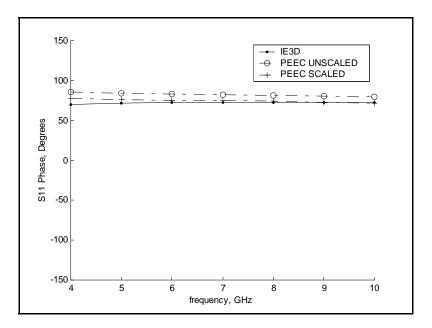

| <b>Fig. 2.9:</b> .S <sub>11</sub> phase (Degrees) versus frequency                                  |

| <b>Fig. 2.10:</b> .S <sub>11</sub> magnitude and phase error versus frequency                       |

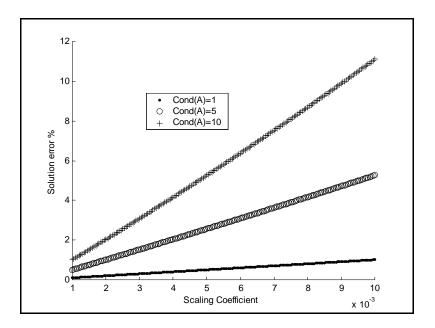

| Fig. 2.11: .Scaling coefficient versus solution error                                               |

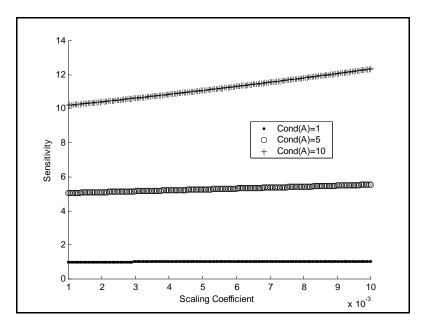

| Fig. 2.12: .Scling coefficient versus sensitivity                                                   |

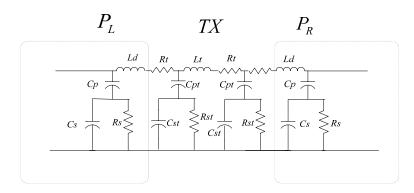

| <b>Fig. 3.1:</b> Image ground plane for a coplanar transmission line on a lossy silicon substrate39 |

| Fig. 3.2: PEEC model of transmission line on lossy substrate40                                      |

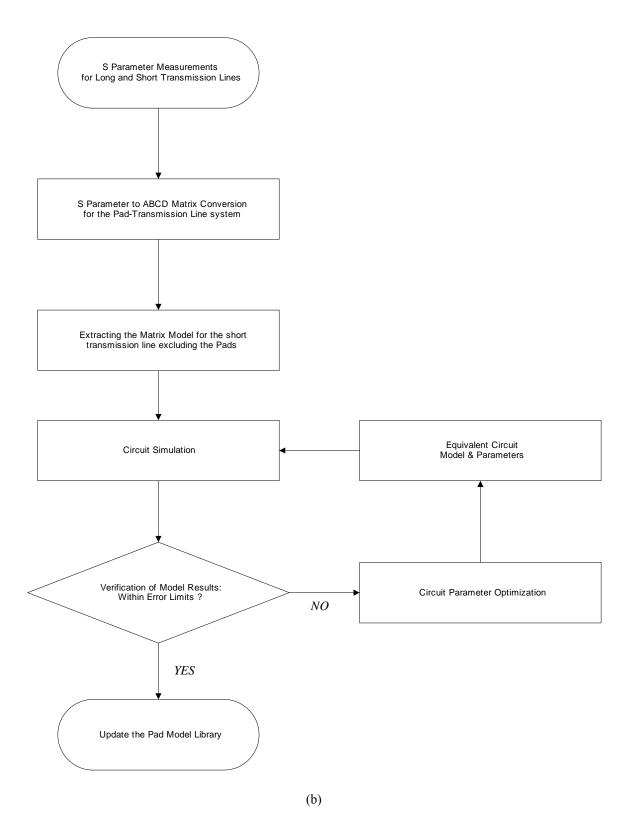

| <b>Fig. 3.3:</b> (a) Equivalent circuit and (b) flowchart showing the lump model approach           |

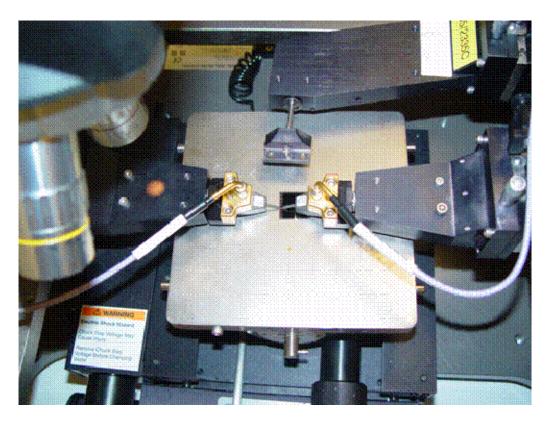

| Fig. 3.4: Measurement setup                                                                         |

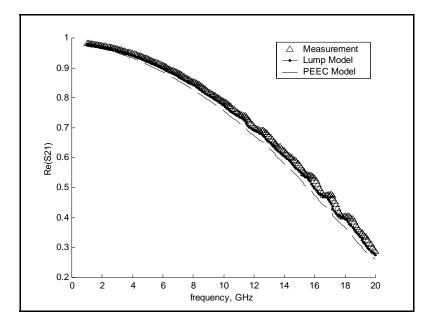

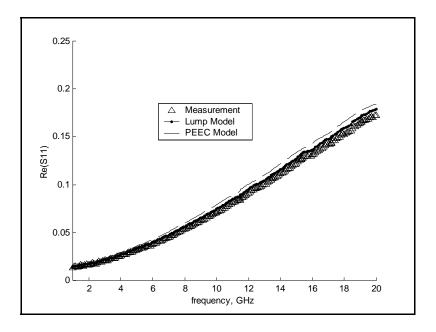

| <b>Fig. 3.5:</b> Re(S <sub>21</sub> ) measurement versus simulation                                 |

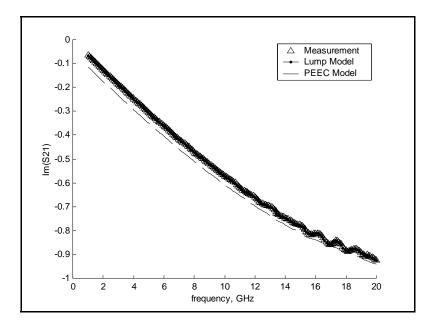

| <b>Fig. 3.6:</b> Im(S <sub>21</sub> ) measurement versus simulation                                 |

| <b>Fig. 3.7:</b> Re(S <sub>11</sub> ) measurement versus simulation                                 |

| <b>Fig. 3.8:</b> Im(S <sub>11</sub> ) measurement versus simulation                                 |

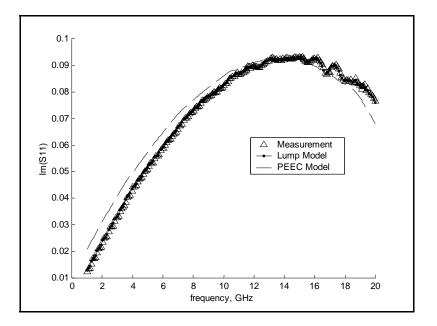

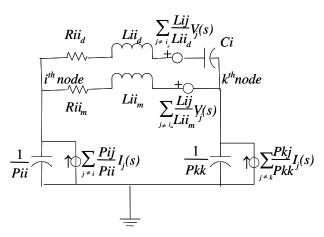

| Fig. 4.1: Elastomer dielectric mesh without metallization                                           |

| <b>Fig. 4.2:</b> Elastomer dielectric mesh with metallization                                       |

| Fig. 4.3: PEEC model of a dielectric mesh cell with metallic inclusion                              |

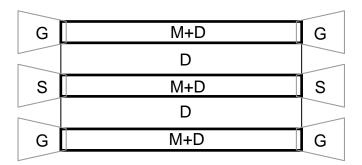

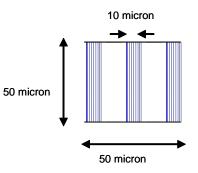

| Fig. 4.4: Elastomer coplanar probe layout. M+D represents the mixture of metal and polymer mesh              |

|--------------------------------------------------------------------------------------------------------------|

| material. D represents the polymer mesh alone. GSG represents air coplanar probe used for VNA                |

| measurements                                                                                                 |

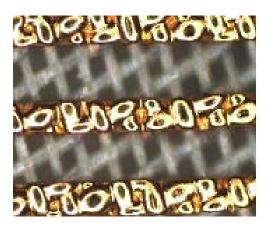

| Fig. 4.5: Physical test sample of Elastomer probe (a) Top view (b) Cross-section                             |

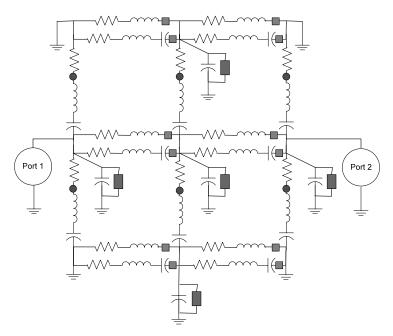

| Fig. 4.6: PEEC for Elastomer mesh coplanar line                                                              |

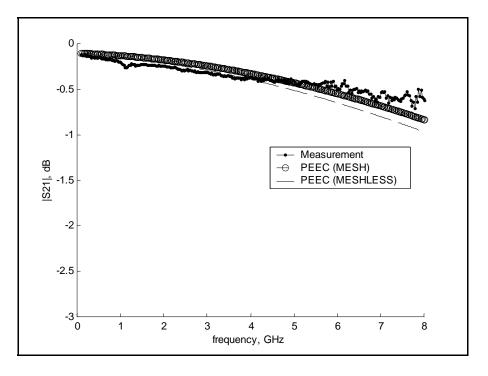

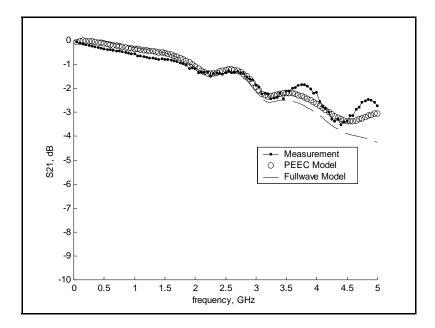

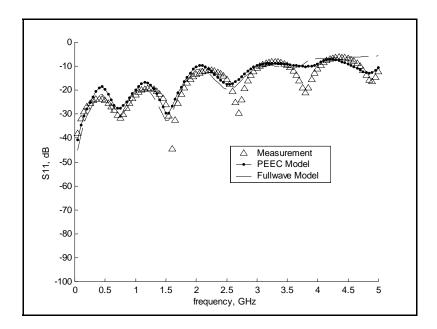

| Fig. 4.7: Insertion Loss (S <sub>21</sub> ) measurement versus PEEC model60                                  |

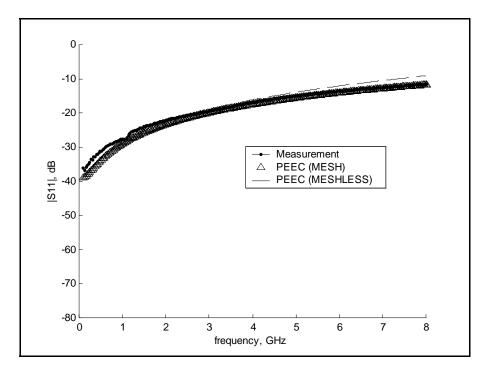

| Fig. 4.8: Return Loss (S <sub>11</sub> ) measurement versus PEEC model                                       |

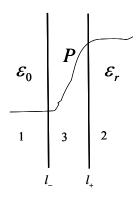

| Fig. 5.1: Interface between two dielectrics                                                                  |

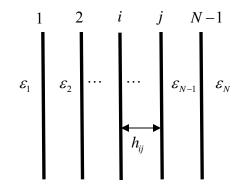

| <b>Fig. 5.2:</b> Interfaces within multilayer dielectrics                                                    |

| Fig. 5.3: Open wire loop of two conducting bars in series                                                    |

| Fig. 5.4: System of two insulated spheres                                                                    |

| Fig. 5.5: Microstrip geometry76                                                                              |

| Fig. 5.6: Effective permittivity versus w/h76                                                                |

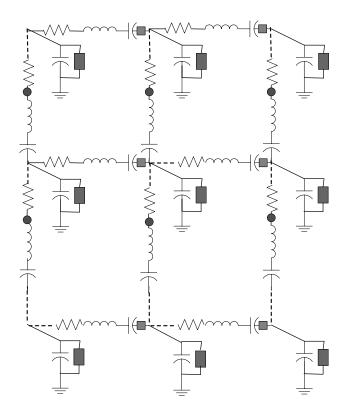

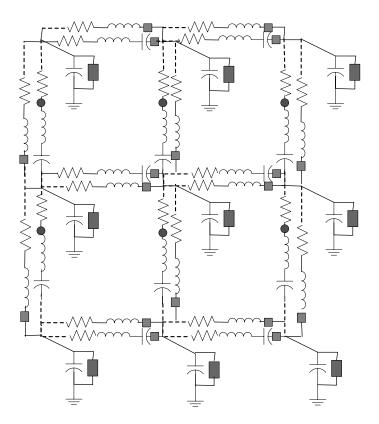

| Fig. 5.7: Cell structure for finite conductor including (a) multilayer dielectrics (a) with multilayer split |

| into two bulk layers and an interface layer                                                                  |

| Fig. 5.8: PEEC model at metal and dielectric interface                                                       |

| Fig. 5.9: PEEC model at dielectric interior                                                                  |

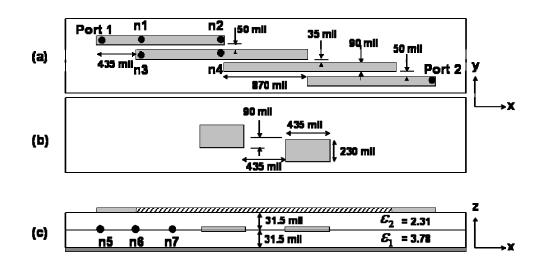

| Fig. 5.10: Coupled microstrip filter geometry (a) Top metal layer (b) Intermediate metal layer (c)           |

| Multilayer cross section backed by ground plane (hashed segment represents coupled line; solid               |

| segments represent single transmission line / metal patch)                                                   |

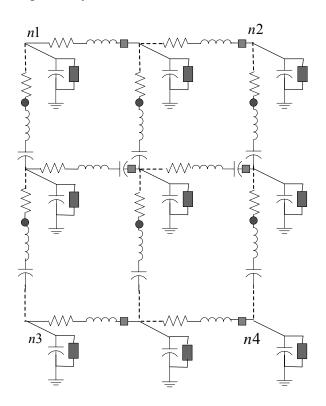

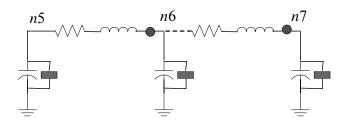

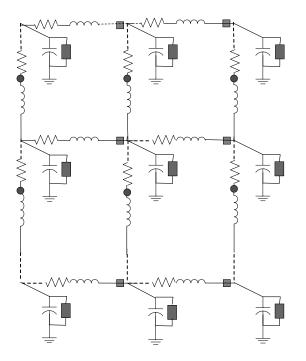

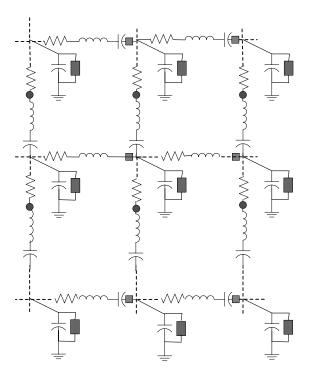

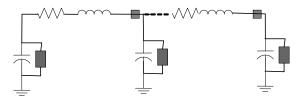

| Fig. 5.11: Equivalent circuit for a coupled microstrip                                                       |

| Fig. 5.12: Equivalent circuit at the interface layer nodes                                                   |

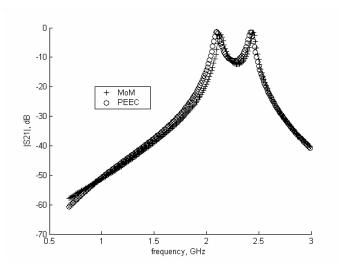

| <b>Fig. 5.13:</b> S <sub>21</sub> magnitude response of three layer coupled line filter                      |

| Fig.5.14: Four layer coupled microstrip filter geometry. (a) Top metal layer, (b) Second metal layer, (c)    |

| Third metal layer and (d) Multilayer cross section backed by ground plane (hashed segment represents         |

| coupled line; solid segments represent single transmission line / metal patch)                               |

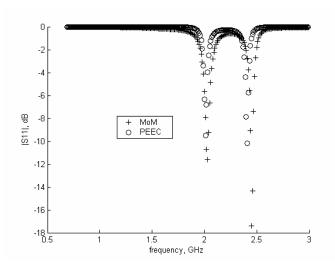

| <b>Fig. 5.15:</b> S <sub>11</sub> magnitude response of four layer coupled line filter                       |

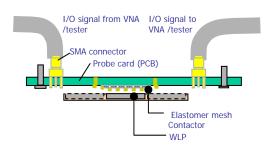

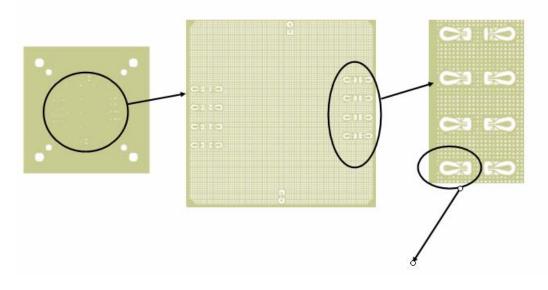

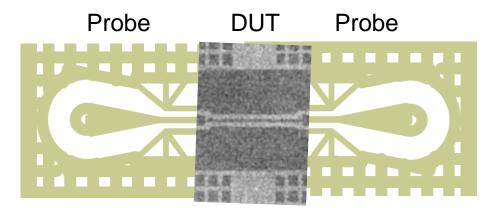

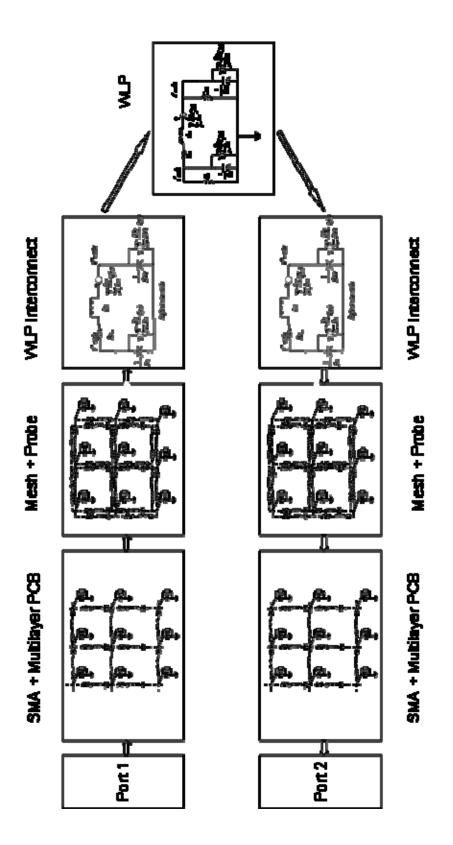

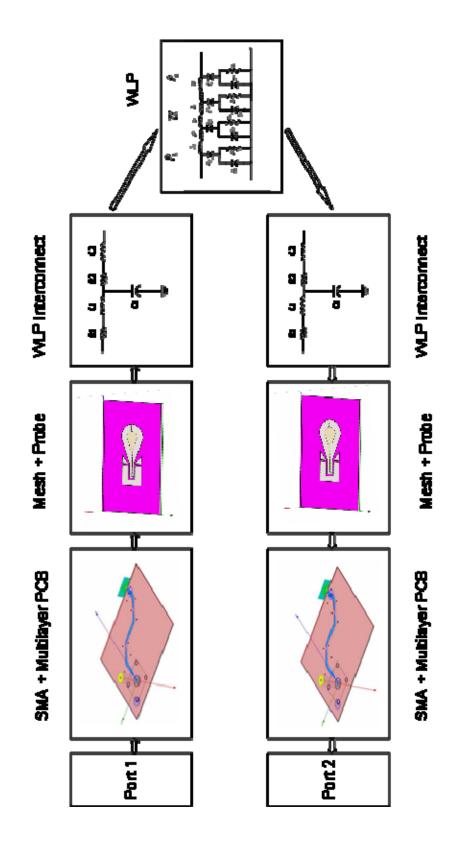

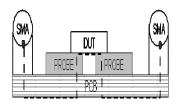

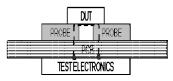

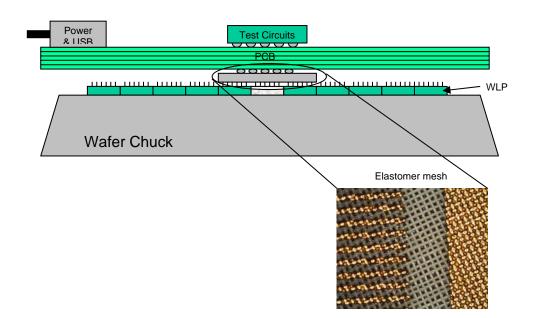

| Fig. 6.1: Test hardware for WLP device under test                                                            |

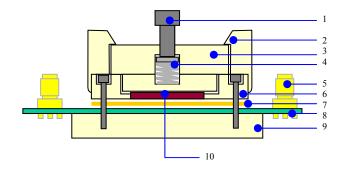

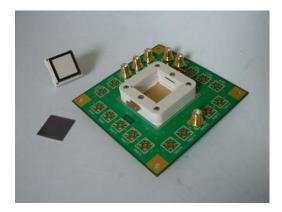

| Fig. 6.2: Prototype test fixture                                                                             |

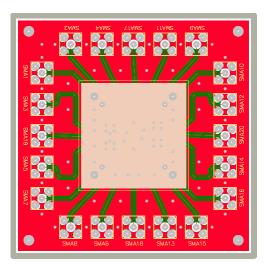

| Fig. 6.3:  | PCB top layer with SMA connector footprints. Elastomer mesh is the square sheet in the |

|------------|----------------------------------------------------------------------------------------|

| centre     |                                                                                        |

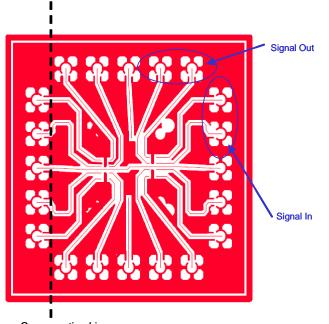

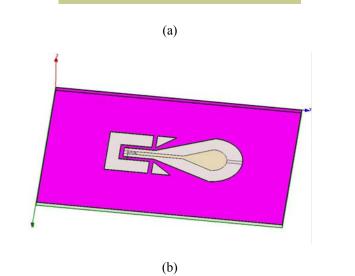

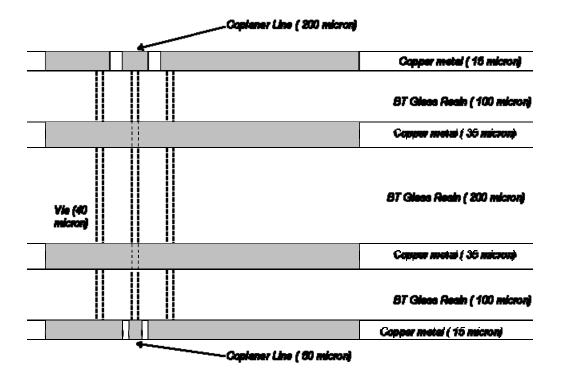

| Fig. 6.4:  | PCB. (a) Signal layer and (b) Cross-Section95                                          |

| Fig. 6.5:  | Elastomer mesh Sheet shown with a magnified probe. (a) Physical structure and (b) Full |

| wave mod   | lel                                                                                    |

| Fig. 6.6:  | Elastomer mesh with device under test97                                                |

| Fig. 6.7:  | Fabricated prototype test fixture                                                      |

| Fig. 6.8:  | Prototype test fixture components (mesh exposed)98                                     |

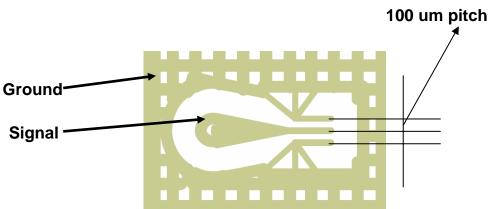

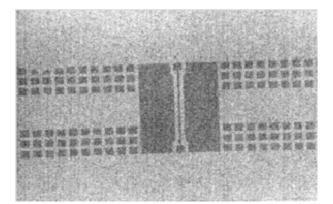

| Fig. 6.9:  | X-Ray image of the DUT coplanar structure (top view)                                   |

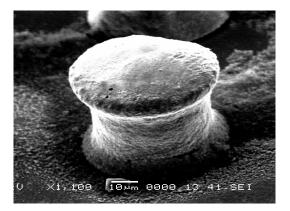

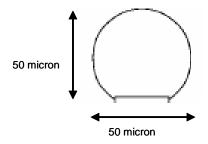

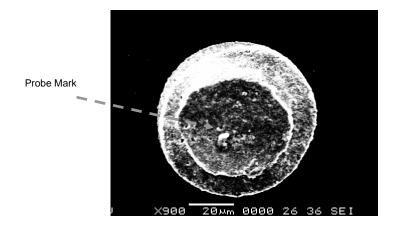

| Fig. 6.10: | SEM image of a fabricated copper column interconnect100                                |

| Fig. 6.11: | Equivalent circuit of the WLP transmission and pads101                                 |

| Fig. 6.12: | Copper column interconnect geometry103                                                 |

| Fig. 6.13: | Equivalent circuit of WLP interconnect Copper column                                   |

| Fig. 6.14: | Equivalent circuit model of Elastomer mesh plane104                                    |

| Fig. 6.15: | Equivalent circuit for Elastomer mesh plane with metallization105                      |

| Fig. 6.16: | Equivalent circuit for the mesh probe105                                               |

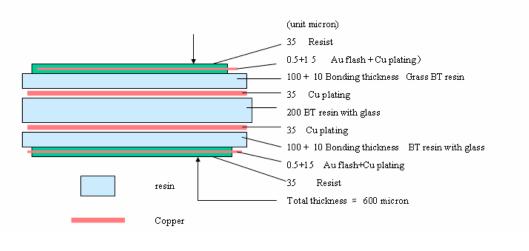

| Fig. 6.17: | Multilayer substrate geometry. (a) Cross-section and (b) Full wave model107            |

| Fig. 6.18: | Equivalent circuit for the PCB ground plane107                                         |

| Fig. 6.19: | Equivalent circuit at the multilayer interface                                         |

| Fig. 6.20: | Equivalent circuit for the PCB and coaxial via108                                      |

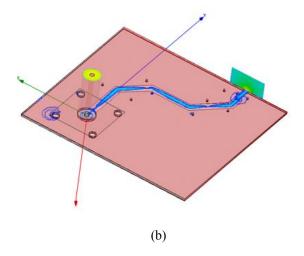

| Fig. 6.21: | System level (a) PEEC model and (b) Full wave model111                                 |

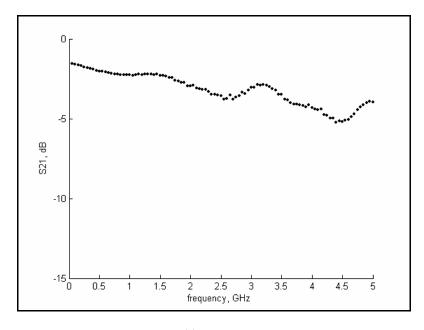

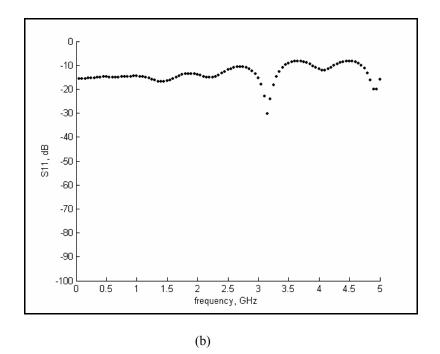

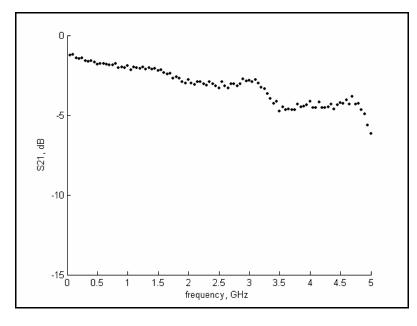

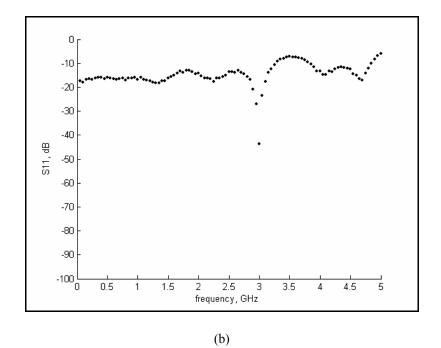

| Fig. 6.22: | Insertion loss measurement of WLP with single copper column113                         |

| Fig. 6.23: | Return loss measurement of WLP with single copper column                               |

| Fig. 6.24: | Multiple copper column schematic                                                       |

| Fig. 6.25: (a) Insertion loss and (b) return loss measurement of WLP with multiple copper                            |

|----------------------------------------------------------------------------------------------------------------------|

| column                                                                                                               |

| Fig. 6.26: Solder bump schematic116                                                                                  |

| <b>Fig. 6.27:</b> (a) Insertion loss and (b) return loss measurement of WLP with solder bump117                      |

| Fig. 6.28:       SEM image of copper column interconnect: Before probing                                             |

| Fig. 6.29:       SEM image of copper column interconnect: After probing                                              |

| Fig. 6.30: Test hardware for VNA measurement (with dashed lines indicating signal path120                            |

| <b>Fig. 6.31:</b> Functional test hardware (with dashed lines indicating signal path)                                |

| Fig. 6.32: Wafer probe setup with functional test hardware                                                           |

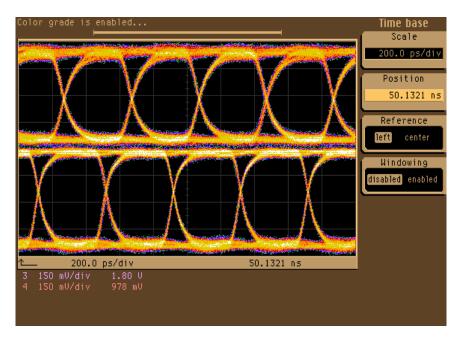

| <b>Fig. 6.33:</b> Eye diagram at 2.5 Gbps                                                                            |

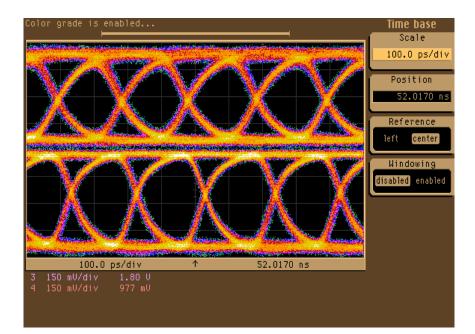

| <b>Fig. 6.34:</b> Eye diagram at 5 Gbps                                                                              |

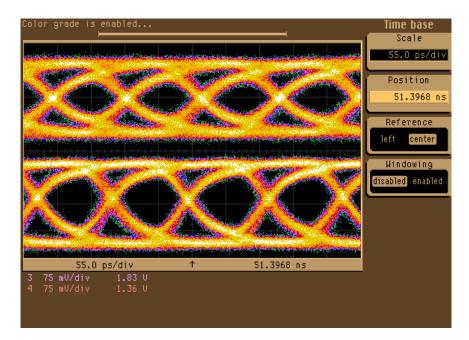

| <b>Fig. 6.35:</b> Eye diagram at 8 Gbps                                                                              |

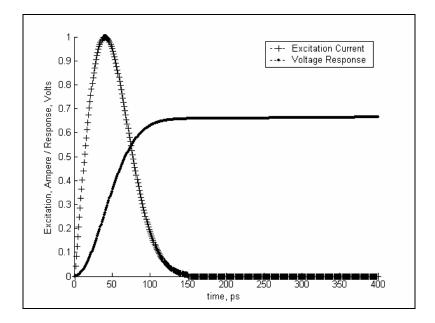

| Fig. A.1: Response of a two node DDE system to a Gaussian excitation                                                 |

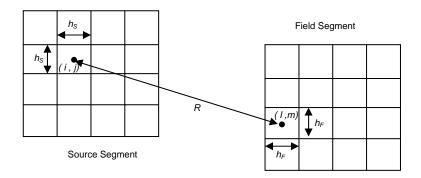

| Fig. B.1: Segmentation of source and field surface elements                                                          |

| <b>Fig. B.2:</b> Circular approximation of a square patch for self term evaluation152                                |

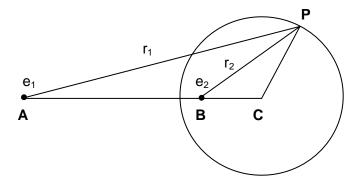

| Fig. C.1: Equipotential spherical surface P due to point charges at A and B155                                       |

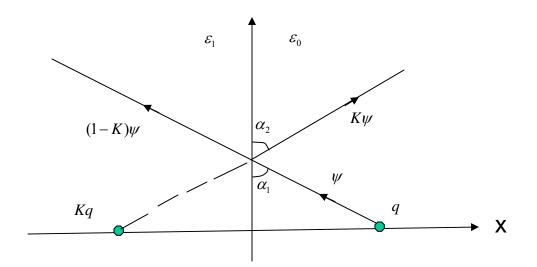

| Fig. C.2: Equipotential flux lines associated with a line charge near a semi-infinite dielectric half-               |

| space158                                                                                                             |

| Fig. C.3: Flux lines due to a line charge near a dielectric slab                                                     |

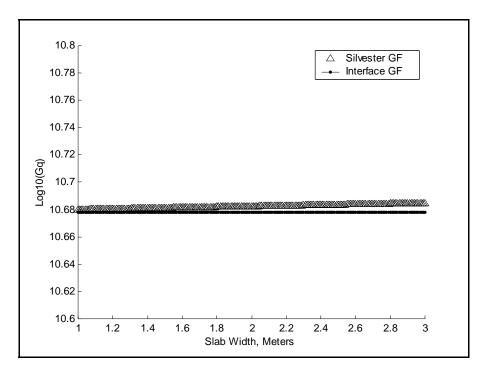

| <b>Fig. C.4:</b> Green's function for the dielectric slab at the field distance of $x=5$ m, $y=7m$ and source        |

| distance of x'=75m, y'=0m161                                                                                         |

| Fig. C.5: Relative difference in Green's function for the dielectric slab at the field distance of                   |

| x=5 m, y= 7m and source distance of x'=75m, y'=0m161                                                                 |

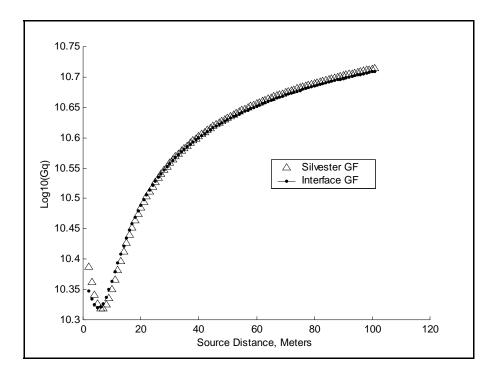

| <b>Fig. C.6:</b> Green's function for the dielectric slab at the field distance of $x=5$ m, $y=7$ m, source distance |

| of y'=0m and slab width of 2m162                                                                                     |

|                                                                                                                      |

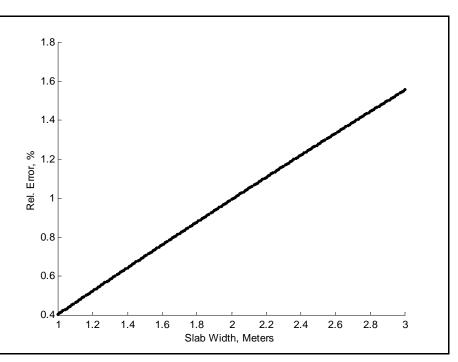

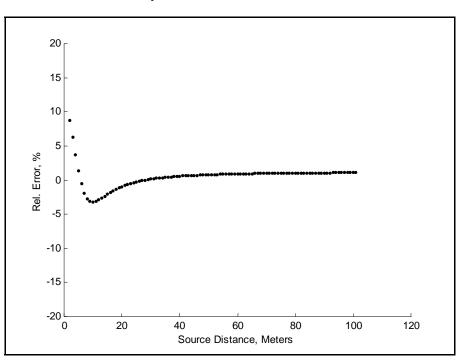

Fig. C.7: Relative difference in Green's function for the dielectric slab at the field distance of

| x=5m, y=  | 7m, source distance of y'=0m and slab width of 2m    | .162 |

|-----------|------------------------------------------------------|------|

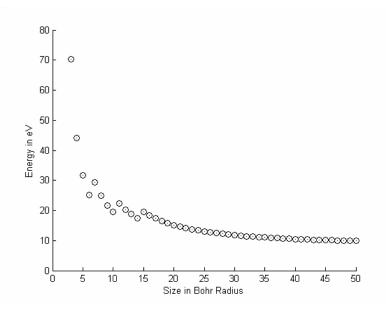

| Fig. D.1: | Fermi energy versus width of copper nanowire.        | 169  |

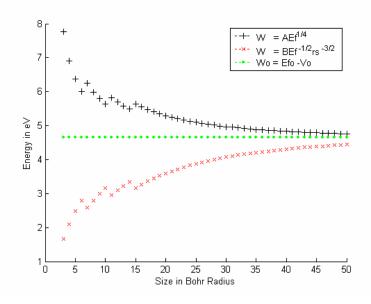

| Fig. D.2: | Work function versus size of copper nanowire.        | .170 |

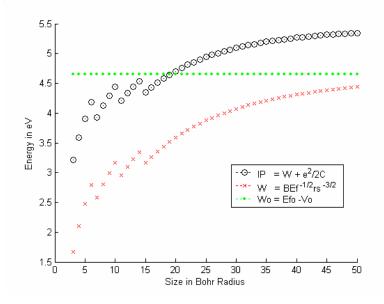

| Fig. D.3: | Ionization potential versus size of copper nanowire. | 171  |

# LIST OF TABLES

| Table 2.1: S <sub>11</sub> Magnitude error (percentage) and Phase error(degrees). | 32  |

|-----------------------------------------------------------------------------------|-----|

| Table 2.2: S <sub>11</sub> Magnitude error (percentage) and Phase error(degrees). |     |

| Table 2.3: Number of terms versus convergence error of BCHD series.               | 36  |

| Table 4.1: Insertion loss Model versus Measurement relative error                 | 62  |

| Table 4.2: Return loss Model versus Measurement relative error                    | 63  |

| Table 4.3: Comparison of different probing technologies                           | 64  |

| Table 6.1:: Test Fixture Part Details                                             | 94  |

| Table 6.2: S <sub>21</sub> Measurement and Model Data                             | 114 |

# LIST OF SYMBOLS

| A                                 | Magnetic vector potential                                              |

|-----------------------------------|------------------------------------------------------------------------|

| В                                 | Magnetic displacement vector                                           |

| D                                 | Electric displacement vector                                           |

| Ε                                 | Electric field vector                                                  |

| <b>G</b> ( <b>r</b> , <b>r</b> ') | Green's function for the field at <b>r</b> due to source at <b>r</b> ' |

| Н                                 | Magnetic field vector                                                  |

| J                                 | Electric current density                                               |

| ρ                                 | Electric charge density                                                |

| i                                 | Electric current                                                       |

| q                                 | Electric Charge                                                        |

| $V_{j}$                           | Voltage across the $j^{th}$ circuit element                            |

| $I_{j}$                           | Current along the $j^{th}$ circuit element                             |

| $L_P$                             | Partial inductance                                                     |

| $C_P$                             | Partial capacitance                                                    |

| $P_{P}$                           | Partial coefficient of potential                                       |

| $R_{P}$                           | Partial resistance                                                     |

| ${\cal E}_0$                      | Permittivity of free space                                             |

| Е                                 | Permittivity of a medium                                               |

| Φ                                     | Electrostatic potential                                                                             |

|---------------------------------------|-----------------------------------------------------------------------------------------------------|

| $\mu_0$                               | Permeability of free space                                                                          |

| $\lambda_{0}$                         | Wavelength in free space                                                                            |

| k                                     | Wave number                                                                                         |

| f                                     | Linear frequency                                                                                    |

| ω                                     | Angular frequency                                                                                   |

| $\sigma$                              | Conductivity                                                                                        |

| t <sub>d</sub>                        | Retardation time                                                                                    |

| $\nabla_{\mathbf{v}} R(\mathbf{v})$   | Vector of the first partial derivative of a scalar function $R$ with respect to vector <b>v</b>     |

| $\nabla_{\mathbf{v}}^2 R(\mathbf{v})$ | Matrix of the second partial derivatives of a scalar function R with respect to vector $\mathbf{v}$ |

### CHAPTER 1

#### **INTRODUCTION**

#### **1.1 Background and Motivation**

In conventional integrated circuit (IC) packaging, test and burn-in are done after the IC is packaged using package formats such as Quad Flat Package (QFP), Ball Grid Array (BGA), or Chip Scale Package (CSP). But this singulated device test and burn-in at the packaged IC level is very expensive.

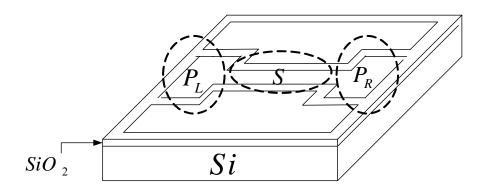

Wafer Level Packaging (WLP) is a new paradigm in microelectronic packaging which provides solution, to arrest cost escalation, through miniaturization [1]. WLP offers batch processing capability at the wafer level. Since test and burn-in can be performed in one go with many devices in parallel, test productivity is multiplied while test cost is significantly reduced. But the need to make electrical contacts to the large number of I/O pins with fine pitches of the order of 100 microns presents new problems to the conventional wafer level test system. Furthermore, the bandwidth requirements present difficulties in the selection of materials as well as integration and fabrication methods necessitating efficient modeling of test system interface to avoid costs of multiple prototyping cycles.

Fine pitch WLPs with large number of input / output pins pose tremendous test challenges at multi-gigahertz frequencies for several reasons. The test probes need to be packed with high I/O density. They need to be mechanically compliant in the vertical direction to accommodate thickness variations in the wafer and interconnects. They also

need to be compliant in the lateral direction to accommodate thermal expansion and contraction. At the same time, they should offer good electrical contact for efficient signal transmission and integrity over several gigahertz frequency ranges.

There are many test probes available currently that meets some but not all of the test needs of WLP semiconductor devices. Coaxial probes and air-coplanar probes, for instance, provide high frequency operation but they are too bulky and so they are suited for low pin count device testing only. The cantilever beam probes have been used traditionally in the industry for testing chips with pin counts of the order of hundreds but they are very bad for high frequency testing due to huge inductance of long lead length. There are Cobra probes, membrane and DoD (die-on-die) probes from various sources but their problem is that they are not providing reliable contacts and are not scalable to very high pin counts (beyond a thousand or two). Thus the motivation behind this thesis is to provide a new solution to testing WLPs using a novel elastomer mesh material based probe geometry with a fine pitch of 100 micron and a multilayer PCB for multi-gigahertz signal distribution. The partial element equivalent circuit (PEEC) method [2] is used for modeling and physical realization of such a test interface. The content of this thesis is, therefore, (a) the derivation of efficient PEEC model in homogeneous media from the Green's function [3] and from the scattering parameter measurements, (b) derivation of efficient PEEC model in inhomogeneous media with dielectric mesh [4], (c) derivation of efficient PEEC model in inhomogeneous media with multilayered composites and (d) application of the PEEC models for the development and analysis of test interface for wafer level package operation at multi-gigahertz frequencies (about 2.5 to 5 GHz) given the tight geometrical constraints of fine pitch (of the order of 100 micron) and large device pin counts (of the order of thousands). In the following section, a review of the literature on PEEC method which has been developed over the past decades for modeling multi-conductor systems in homogeneous dielectric media is given.

#### **1.2 Partial Element Equivalent Circuit Modeling**

In typical device applications, we are not interested in knowing the field values at every point in the domain of the problem. We are only interested in the terminal or nodal voltages and currents. There is the possibility to condense the field information into the circuit information that is good enough for most VLSI applications. PEEC modeling suits the purpose due to the popularity and efficiency of circuit solvers like SPICE among VLSI design community for many decades. The challenges are not only the complexity of the 3D structures, but also an ever growing number of interconnects that must be modeled accurately. PEEC provides an efficient option to handle the VLSI circuit complexity through its ability to reduce the problem order by condensing the field information at innumerable points into circuit element information over a more manageable number of area and volume elements. PEEC method is similar to the moment method with pulse function used for weight as well as basis. The interaction between capacitive displacement currents and the inductive conductor currents are to be considered for getting accurate results.

The PEEC method is applicable in both time and frequency domain [5]-[6]. Fast implementations of the method have been shown using fast multipoles and wavelets [7]-[9]. Non-orthogonal versions of the method have been proposed to handle arbitrary geometries [10]-[12]. Ruehli and Garrett [13]-[16] have made accuracy and stability

3

improvements. Model order reduction has been addressed by Antonini, Cullum and Cangellaris [17]-[24]. Numerous applications of PEEC has been demonstrated for the case of interconnects, vias, power-ground planes, LTCC circuits, spiral inductors, accurate treatment of crosstalk, skin effect and dielectric loss [19]-[55].

The availability of better CAD tools for the extraction of inductances and capacitances makes the PEEC models attractive. PEECs are equivalent to Maxwell's equations in the limit of an infinite lattice of partial elements and when retardation field is neglected. PEECs can be combined with other models, like transistors, for a circuit simulator like SPICE.

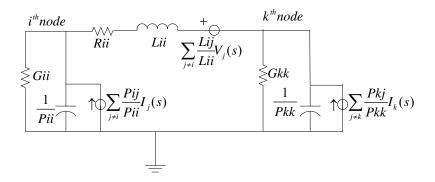

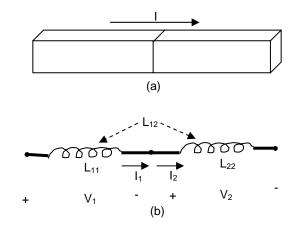

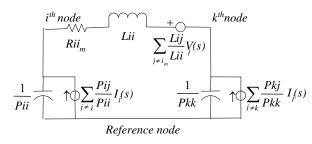

Unlike differential equation RLC lump model, PEEC includes cross-coupling terms. The mutual components are represented by delayed interaction. The circuit equation thus obtained, which is actually a delay differential circuit equation (DDE), is solved by an implicit time stepping algorithm [56]. The time domain solution of DDEs by time stepping algorithms is discussed in the next section. The method for frequency domain solution of DDE system in circuit solver is detailed in section 1.4.

#### **1.3 Solving Delay Differential Equation (DDE) Systems**

**1.3.1 DDE Example with Two Nodes**

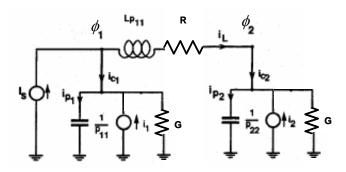

Fig. 1.1: DDE network with two nodes.

Let  $\phi_1$  and  $\phi_2$  be the potentials of a network shown in Fig. 1.1, with two nodes, which is typical of the PEEC topology. The nodes are separated by the partial inductance  $L_{p11}$  and partial resistance R. The excitation and the load currents are  $I_s$  and  $I_L$ respectively. The partial coefficients of potentials (reciprocal capacitances) corresponding to the two nodes are  $p_{11}$  and  $p_{22}$  with the conductance component G. Let  $\tau$  be the interaction time delay between the two capacitances. Then, the MNA (modified nodal analysis) equations of the equivalent circuit can be written as

$$\frac{1}{p_{11}}\frac{\partial\phi_1}{\partial t} + G\phi_1 + I_L - \frac{p_{12}}{p_{11}}I_L(t-\tau) = I_S, \qquad (1.1)$$

$$\frac{1}{p_{22}}\frac{\partial\phi_2}{\partial t} + G\phi_2 - I_L + \frac{p_{12}}{p_{22}}I_L(t-\tau) = \frac{p_{12}}{p_{22}}I_S(t-\tau), \qquad (1.2)$$

$$(\phi_2 - \phi_1) + L_{p11} \frac{\partial I_L}{\partial t} + I_L R = 0.$$

(1.3)

The time factor *t* is implicit for all the state variables and is suppressed for brevity except where delays are involved. In matrix operator form, the MNA equations are,

$$\begin{pmatrix} \frac{1}{p_{11}} \frac{\partial}{\partial t} + G & 0 & 1 - \frac{p_{12}}{p_{11}} \\ 0 & \frac{1}{p_{22}} \frac{\partial}{\partial t} + G & -1 + \frac{p_{12}}{p_{22}} \\ -1 & +1 & L_{p11} \frac{\partial}{\partial t} + R \end{pmatrix} \begin{pmatrix} \phi_1 \\ \phi_2 \\ I_L \end{pmatrix} = \begin{pmatrix} I_s \\ \frac{p_{12}}{p_{22}} I_s \\ 0 \end{pmatrix} ,$$

(1.4)

where the ' is used to symbolize time delays. Upon re-arranging equation (1.4), we obtain

$$\begin{pmatrix} \frac{\partial}{\partial t} \phi_{1} \\ \frac{\partial}{\partial t} \phi_{2} \\ \frac{\partial}{\partial t} I_{L} \end{pmatrix} = \begin{pmatrix} p_{11} & 0 & 0 \\ 0 & p_{22} & 0 \\ 0 & 0 & \frac{1}{L_{p11}} \end{pmatrix} \begin{pmatrix} G & 0 & +1 \\ 0 & G & -1 \\ -1 & +1 & R \end{pmatrix} \begin{pmatrix} \phi_{1} \\ \phi_{2} \\ I_{L} \end{pmatrix}$$

$$- \begin{pmatrix} p_{11} & 0 & 0 \\ 0 & p_{22} & 0 \\ 0 & 0 & \frac{1}{L_{p11}} \end{pmatrix} \begin{pmatrix} 0 & 0 & \frac{p_{12}}{P_{11}} \\ 0 & 0 & \frac{p_{12}}{P_{22}} \\ 0 & 0 & 0 \end{pmatrix} \begin{pmatrix} \phi_{1}(t-\tau) \\ \phi_{2}(t-\tau) \\ I_{L}(t-\tau) \end{pmatrix}.$$

(1.5)

Now expression (1.5) is in a form suitable for performing the time stepping with backward Euler since the delay differential equation can be written as a delay difference equation. This example is a simple case where the matrix inversion is trivial due to the diagonal nature of the system matrix. In the most general case, however, an LU decomposition would be performed for solving the system. The solution of an example of the DDE system is illustrated with Matlab codes in Appendix A.

#### **1.3.2 Time Stepping Algorithm for Solving Delay Differential Equation Systems**

Both explicit [57] and implicit [58] schemes are available in the literature to solve the delay differential equations. Since implicit scheme is known to be stable, we use backward Euler method for the time domain solution [56].

Let **A** be the system matrix, and **x**' be the state variables and **w** the input stimuli. Then the system is represented as

$$\mathbf{x'} = \mathbf{A}\mathbf{x} + \mathbf{w} \,. \tag{1.6}$$

In backward Euler method, we have

$$\mathbf{x}_{n+1} = \mathbf{x}_n + h\mathbf{x'}_{n+1}, \tag{1.7}$$

where h is the time step. Using equation (1.6) in equation (1.7), we have

$$\mathbf{x}_{n+1} = \mathbf{x}_n + h(\mathbf{A}\mathbf{x}_{n+1} + \mathbf{w}_{n+1}).$$

(1.8)

Rewriting equation (1.8), we get

$$(\mathbf{I} - h\mathbf{A})\mathbf{x}_{n+1} = \mathbf{x}_n + h\mathbf{w}_{n+1}.$$

(1.9)

If the step size is not changed during the simulation, then the matrix (I - hA) remains constant. So we need to do LU factorization only once for the matrix inversion. This makes the process very efficient.

Time domain solutions have sometimes been found to diverge after a sufficient number of time steps, because of the accumulation of numerical noise. The source of the noise could be numerical round-off errors or from the analytical and numerical approximations made in developing the circuit model. The approximation errors are said to introduce low-amplitude, right-half-plane, nonphysical poles into the model.

Many techniques for solving late-time instabilities have been reported [59]. Tijhuis [60] investigated using an improved time-interpolation scheme to increase the accuracy of time derivatives. Rao *et al.* [61] used a conjugate gradient technique to control error accumulation over time. Smith [62] describes a procedure that considers the fact that late-time instabilities, generally being of a high-frequency nature relative to the correct response, can be filtered from the solution by averaging techniques.

### **1.4 Scattering Parameter Analysis of Circuits**

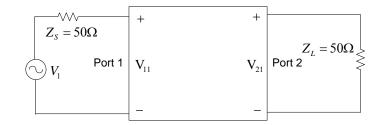

First each port is represented by a resistor in series with a voltage source. The value of resistance is set to the reference resistance of the port, typically 50 Ohms. The magnitude of the source voltage is initially set to zero at all the ports.

Fig. 1.2: Simulation setup for  $S_{11}$  and  $S_{21}$ .

**Fig. 1.3:** Simulation setup for  $S_{12}$  and  $S_{22}$ .

The scattering parameters are related by

$$V_1^- = S_{11}V_1^+ + S_{12}V_2^+, \qquad (1.10)$$

$$V_2^- = S_{21}V_1^+ + S_{22}V_2^+, (1.11)$$

where  $V_1^-$ ,  $V_2^-$  are the reflected waves and  $V_1^+$ ,  $V_2^+$  are the transmitted waves at the ports 1 and 2 respectively. Also, in Fig. 1.1  $V_{11}$  is the sum of the transmitted and reflected waves at port 1 and  $V_{21}$  is the sum of the transmitted and reflected waves at port 2. Thus,

$$V_{11} = V_1^+ + V_1^-, \qquad (1.12a)$$

$$V_{21} = V_2^+ + V_2^-, \tag{1.12b}$$

and

$$V_1 = V_1^+ - V_1^- + V_{11}. (1.13)$$

Using equation (1.12a), equation (1.13) becomes

$$V_1 = 2V_1^+ \,. \tag{1.14}$$

Using equations (1.10), (1.12a) and (1.14),  $S_{11}$  is given by

$$S_{11} = \frac{V_1^-}{V_1^+} \bigg|_{V_1^+ \to 0} = \frac{V_{11} - V_1^+}{V_1^+} = V_{11} - 1, \qquad (1.15)$$

since the input source  $V_1$  is excited with an amplitude of 2 volts. Using equations (1.11),

(1.12b) and (1.14),  $S_{21}$  is given by

$$S_{21} = \frac{V_2^-}{V_1^+} \bigg|_{V_2^+ \to 0} = \frac{V_{21} - V_2^+}{V_1^+} \bigg|_{V_2^+ \to 0} = V_{21}.$$

(1.16)

Fig. 1.2 shows the circuit arrangement for the computations. For computing  $S_{11}$  and  $S_{21}$ , the magnitude of the voltage source on the first port is set to 2Volts and the alternating current (AC) analysis [63] is run over the frequency range of interest. For automatically performing subtraction, a 1Volt source is installed to obtain  $S_{11}$ .

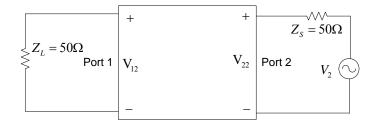

Similarly, as shown in Fig. 1.3,  $S_{22}$  and  $S_{12}$  are obtained from

$$S_{22} = V_{22} - 1, \tag{1.17}$$

$$S_{12} = V_{12} \,. \tag{1.18}$$

For convenience, the model simulation results are presented in the thesis in the form of scattering parameter (S parameter) data since it is easier to compare with the results of full-wave EM solvers without having to do FFT. Example SPICE codes for S parameter analysis are given in Appendix E.

#### 1.5 Scope and Organization of this Thesis

This thesis presents the derivation and application of PEEC modeling for the development of a multi-gigahertz test interface for fine pitch wafer level packages. First, efficient PEEC models for homogeneous media are derived from a new scaling technique based on Baker-Campbell-Hausdorff-Dynkin series [64]. This technique leads to an order of improvement in relative accuracy for predicting small quantities such as return loss. Secondly, the PEEC models are extended to lossy silicon substrates and compared with lumped circuit model derived, by mapping the physical geometry to circuit elements and by applying symmetry properties of ABCD matrix elements, from scattering parameter measurements. The lump circuit approach has practical value when it is harder to derive Green's function integral terms due to singularity problem in small geometry scales and

due to material inhomogeneity and geometric discontinuity. Thirdly, PEEC models for inhomogeneous media with dielectric mesh are derived. The dielectric mesh substrate with metallization suits the need for test probes for wafer level packages. Fourthly, PEEC model for multi-layer geometry is developed by considering additional interaction terms arising from multilayer interfaces. Current generation of high speed devices and the hardware used for testing such devices are built with multi-layer substrates and boards to redistribute power and signal lines. Hence, multilayer PEEC has practical significance in the design and test of devices operating at RF and microwave frequencies. Finally, PEEC models derived above are combined and applied towards development of a complete test interface for fine pitch wafer level package for multi-gigahertz operation at probe pitch of the order of 100 micron.

Chapter 2 derives a novel PEEC model based on a perturbation technique for scaling of circuit elements in homogeneous media. Baker-Campbell-Hausdorff-Dynkin series [64] is used to scale the circuit derived from the geometry. Circuit scaling is shown to provide an order of magnitude of accuracy improvement in the prediction of return loss from PEEC models. A strip line geometry is taken as a test case. The results of the circuit model simulation are compared with that from Method of Moments (MoM). Relatively good agreements between the scaled circuit model simulation data and the MoM are obtained.

PEEC modeling derived in Chapter 2 is extended to lossy substrates using the theory of images. The extended model is compared with a measurement based lumped circuit model. The lumped circuit model is optimized in a least squares sense using the measured data. Congruent property of the geometry and the resultant symmetry of the

11

ABCD matrix structure are used to derive the optimization algorithm. A sample device having coplanar waveguide structure fabricated on high resistivity silicon substrate (2 kilo-ohm cm) is used as a test case. The models and measurements are well matched over 100 MHz to 20 GHz range.

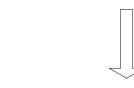

For wafer level package test applications, there is a need to use elastomer mesh substrate based probes due to vertical and lateral compliance requirements. A novel PEEC model is developed in Chapter 4 for treating the dielectric-metal composite mixture that the probe is built with. The local interaction between the dielectric and metal is factored into the electric field integral equation for accurate representation of the circuit elements. The model is verified with measurements in a coplanar GSG (Ground Signal Ground) probe structure.

In Chapter 5, PEEC method for multilayer dielectric geometry is presented. To do this, the concept of mutual interactions between circuit elements is extended to an interface function. Isolation of the self and mutual components lends itself to separate treatment of the interface from the bulk substrate. This formulation is first tested in a quasi-static capacitance problem in a micro-strip. The per unit length capacitance is evaluated for different geometries and material properties. Then transmission characteristics of a multilayered coupled micro-strip filter are analyzed. The treatment of the dielectric interface in terms of the convolution of the interface function with source function in pulse basis in the time domain is found to give satisfactory results compared to other studies based on the method of moments.

Application of PEEC modeling for WLP test interface prototype development is discussed in Chapter 6. The details of modeling a prototype test hardware comprising of a

12

compliant elastomer mesh, a multilayer printed circuit board substrate with coplanar transmission lines and coaxial connectors are presented. The test hardware is built to handle multi-gigahertz signal propagation using 100 micron pitch GSG mesh-coplanar probes. The components of the test hardware such as the SMA connectors, coplanar transmission lines on the PCB, off-chip and on-chip interconnect of the WLP and elastomer mesh probe have all been modeled. Two cases of system level model containing the above sub-systems, one based on PEEC and the other from full-wave solver, has been developed and compared. The numerical results of scattering parameters from both modeling and the measurements on the prototype are found to be in good agreement over the frequency range from DC to 5 GHz.

#### **1.6 Original Contributions**

As a result of this research, the following contains the original contributions made by the author of this thesis:

A new perturbation technique based on Baker-Campbell-Hausdorff-Dynkin [64] series for PEEC scaling is presented. This technique effectively reduces the stiffness of the differential equation system. Consequently, an order of improvement in the prediction accuracy of small quantities such as return loss is achieved.

PEEC model is extended to lossy substrates and verified with a measurement based lumped circuit modeling methodology. The lumped circuit modeling method is valuable where Green's function approach fares poorly due to its singular behaviour and due to the material inhomogeneity and geometric discontinuity in the small region. The congruent symmetry of the model and the consequent simplicity of the ABCD matrices are used to develop this method.

PEEC method for modeling dielectric mesh medium including metallization is derived. The mesh has novel electrical and mechanical properties that make it attractive for applications such as wafer level package test.

Interface function coefficients based on the method of images is derived. This method takes into account the effect of multiple stacks of dielectrics, which are common in current CMOS, LTCC and other integrated circuit and package fabrication technologies. Multilayer PEEC modeling method is derived using the interface function. This method makes it possible to represent multilayer objects in terms of circuit elements without the need to rely on full-wave field solvers.

A test methodology is demonstrated for fine pitch (of the order of 100 micron), high pin count (of the order of thousands) wafer level packages at high frequencies (of the order of gigahertz) using elastomer mesh probes.

The contributions made in this research are reported in the following publications:

#### **1.6.1 Journals**

1. J. Jayabalan, B.L. Ooi, M.S. Leong and M.K. Iyer, "A scaling technique for partial element equivalent circuit analysis using SPICE," *Microwave and Wireless Components Letters, IEEE*, Vol. 14, Issue: 5, pp. 216 – 218, March 2004.

2. J. Jayabalan, W. Bin, D. X. Xu, B.L. Ooi, M. S. Leong and M. K. Iyer, "A methodology for accurate modeling of pad structure from S-Parameter

measurements," *Microwave and Optical Technology Letters*, Vol.45, Issue 2, pp. 115-118, Wiley Interscience, April 2005.

3. J. Jayabalan, B.L. Ooi, M.K. Iyer and M.S. Leong, "Modeling and application of elastomer mesh for microwave probing," *IEE proceedings on Microwaves, Antennas and Propagation*, Vol.153, No. 1, pp.83-88, Feb 2006.

J. Jayabalan, R. Jayaganthan, A.A.O. Andrew Tay and B.L. Ooi., "Energetics of Copper Nanowires," *International Journal of NanoScience*, World Scientific, Singapore, Vol. 4, No. 4, pp 717-724, Aug. 2005.

5. J. Jayabalan, B.L. Ooi, M.S. Leong and M.K. Iyer, "Novel Circuit Model for Three-Dimensional Geometries with Multilayer Dielectrics," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 54, Issue 4, Part 1, pp. 1331 – 1339, Jun 2006.

#### **1.6.2** Journal Submissions under Review

6. J. Jayabalan, M.K.Iyer, M.D. Rotaru, V.S. Rao. V. Kripesh, B.L. Ooi and M.S. Leong, "A novel test strategy for fine pitch wafer level packaged devices," to appear in *IEEE CPMT Transactions on Advanced Packaging*.

#### 1.6.3 Conferences

J. Jayabalan, M.D. Rotaru, D. Chun, H.H. Feng, M.K. Iyer, B.L. Ooi, M.S. Leong, S. Ang, A.A.O. Tay, D. Keezer and T. Rao, "Test strategies for fine pitch wafer level packaged devices;" *Electronics Packaging Technology Conference Proceedings*, pp. 397 – 400, 10-12 Dec. 2003.

2. J. Jayabalan, C.K. Goh, B.L. Ooi, M.S. Leong, M.K. Iyer and A.A.O. Tay, "PLL based high speed functional testing, "*IEEE Proceedings Asian Test Symposium*, pp. 116 – 119, ATS 2003.

3. J. Jayabalan, W. Bin, D. X. Xu, B.L. Ooi, M. S. Leong and M. K. Iyer," Pad modeling from S-Parameter measurements," in *Progress in electromagnetic research symposium proceedings, Nanjing, China, PIERS,* Aug. 2004.

4. J.Jayabalan, M.D.Rotaru, Jimmy PH Tan, M.K.Iyer, B.L.Ooi and M.S. Leong, "Test Bench modeling and characterization for fine pitch wafer level packaged devices, *IEEE Electronics Packaging Technology Conference Proceedings*, pp. 502 – 505, Dec. 2004.

5. J. Jayabalan, B.L. Ooi, and M. S. Leong, "PEEC Model for Multiconductor Systems Including Dielectric Mesh," *Asia Pacific Microwave Conference proceedings, Suzhou, China*, Vol. 2, Dec. 2005.

6. J. Jayabalan and M.D. Rotaru, "High Frequency Characterizaion of 100 micron pitch wafer level package interconnects," to appear in *IEEE Electronics Packaging Technology Conference Proceedings*, Vol. 1, pp 171-174, Dec. 2005.

#### 1.6.4 Patents

1. J. Jayabalan, M.D. Rotaru, M.K. Iyer, and A.A.O. Tay, "Compliant Probes and Test Methodology for Fine Pitch Wafer Level Devices and Interconnects," filed in US Patents and Trademarks Office, No. 11/207336, August, 2005.

#### CHAPTER 2

# MODELING OF HOMOGENEOUS LOSSLESS MEDIA BY PEEC METHOD

#### 2.1 Introduction

A scaling technique for Partial Element Equivalent Circuit analysis using SPICE is presented in this Chapter. The conventional PEEC model in homogeneous medium is first reviewed. The Baker-Campbell-Hausdorff-Dynkin (BCHD) series [64] for exponential matrices is then derived. Then BCHD series approximation based matrix transformation and scaling is applied to the component values extracted by the standard PEEC method to get up to an order of magnitude improvement in relative accuracy of scattering parameters with SPICE simulation. The effectiveness of the technique is verified by using the numerical example of a stripline structure and comparing the results with that of the Method of Moments (IE3D).

In PEEC modeling of micron size multi-conductor geometries, the resistance values are quite small, while the reactance values are relatively large at GHz frequencies. This huge spread in the network component values leads to poor results or ill-conditioned matrices in circuit simulation using SPICE. For example, in a microstrip structure, the transmission parameter values ( $S_{21}$ ) from circuit simulation are accurate to within 5% of the expected reference value from the full-wave solution while the errors in reflection parameter values ( $S_{11}$ ) are as high as 50%. Conventional linear techniques like impedance scaling and frequency scaling [56] are not enough to handle this problem

since this does not improve the matrix condition. A scaling technique based on the approximation of BCHD series [65]-[66] is applied to alleviate this problem.

#### 2.2 Deriving the PEEC Model in Homogeneous Media

The PEEC model in Fig. 2.1 comes from mapping the field problem into a circuit problem. The Maxwell equations are represented in the form of an Electric Field Integral Equation (EFIE) in terms of scalar and vector potentials.

Fig. 2.1: PEEC model

Starting with the Maxwell equation,

$$\nabla \cdot \mathbf{B} = 0, \qquad (2.1)$$

which means that **B** could be considered as a curl of some term **A** called vector potential, we have,

$$\mathbf{B} = \nabla \times \mathbf{A} \,. \tag{2.2}$$

Again, from Faraday's Law

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t}, \qquad (2.3)$$

$$\nabla \times \mathbf{E} = -\frac{\partial}{\partial t} (\nabla \times \mathbf{A}), \qquad (2.4)$$

$$\nabla \times \left( \mathbf{E} + \frac{\partial \mathbf{A}}{\partial t} \right) = 0.$$

(2.5)

$\mathbf{E} + \frac{\partial \mathbf{A}}{\partial t}$  is a vector whose curl is zero. This means that the vector is equivalent to the

gradient of a scalar called the scalar potential. That is

$$\mathbf{E} + \frac{\partial \mathbf{A}}{\partial t} = -\nabla\phi, \qquad (2.6)$$

$$\mathbf{E} = -\frac{\partial \mathbf{A}}{\partial t} - \nabla \phi \,. \tag{2.7}$$

If the loss term due to conductivity were added, equation (2.7) would become

$$\mathbf{E} = -\frac{\partial \mathbf{A}}{\partial t} - \nabla \phi - \frac{\mathbf{J}}{\sigma}.$$

(2.8)

where **E** is the incident field. In general,  $\mathbf{E} = \mathbf{E}^{i} + \mathbf{E}_{s}$  contains both incident ( $\mathbf{E}^{i}$ ) and scattered ( $\mathbf{E}_{s}$ ) components. For representing the scattered term, **E=0** for a conservative system gives

$$\mathbf{E}_{s}(\mathbf{r},t) = \frac{\partial \mathbf{A}(\mathbf{r},t)}{\partial t} + \nabla \phi(\mathbf{r},t) + \frac{\mathbf{J}(\mathbf{r},t)}{\sigma}.$$

(2.9)

Here, **r** is the distance vector between source and field points, and *t* is time.

Integrating the above equation over the volume, we arrive at the macroscopic Kirchoff's voltage equation. Since the voltage around the closed loop is zero, we have

$$\frac{\mathbf{J}(\mathbf{r},t)}{\sigma} + \frac{\mu}{4\pi} \int_{v'} G(\mathbf{r},\mathbf{r'}) \frac{\partial \mathbf{J}(\mathbf{r'},t_d)}{\partial t} dv' + \frac{\nabla}{4\pi\varepsilon_0} \int_{v'} G(\mathbf{r},\mathbf{r'}) q(\mathbf{r'},t_d) dv' = 0, \qquad (2.10)$$

where  $G(\mathbf{r}, \mathbf{r'})$  and  $t_d$  are the kernel function and time retardation respectively, given by

$$G(\mathbf{r},\mathbf{r'}) = \frac{1}{|\mathbf{r} - \mathbf{r'}|},\tag{2.11}$$

$$t_d = t - \frac{|\mathbf{r} - \mathbf{r'}|}{c}.$$

(2.12)

For the inclusion of stratified dielectric region, we note that

$$\nabla \times \mathbf{H} = \mathbf{J} + \varepsilon_0 (\varepsilon_r - 1) \frac{\partial \mathbf{E}}{\partial t} + \varepsilon_0 \frac{\partial \mathbf{E}}{\partial t}.$$

(2.13)

Here, we consider the total current as

$$\mathbf{J}_{tot} = \mathbf{J}(\mathbf{r}, t) + \varepsilon_0 (\varepsilon_r - 1) \frac{\partial \mathbf{E}}{\partial t}, \qquad (2.14)$$

which is a combination of conduction current and displacement current, to formulate the integral equation. The integral equation for a conductor cell then becomes,

$$\frac{\mathbf{J}(\mathbf{r},t)}{\sigma} + \frac{\mu}{4\pi} \int_{v'} G(\mathbf{r},\mathbf{r'}) \left[ \frac{\partial \mathbf{J}(\mathbf{r'},t_d)}{\partial t} + \varepsilon_0 (\varepsilon_r - 1) \frac{\partial^2 \mathbf{E}(\mathbf{r'},t_d)}{\partial t^2} \right] dv' + \frac{\nabla}{4\pi\varepsilon_0} \int_{v'} G(\mathbf{r},\mathbf{r'}) q(\mathbf{r'},t_d) dv' = 0.$$

(2.15)

In the above equation, the first term is the resistance term, the second term is the inductance term and the third term is the capacitance term respectively.

When the source and the field are spread in different volume regions, we can generalize the above equation by converting the single volume integral into double integrals where the interaction terms are respectively called mutual partial inductance and mutual partial capacitance. We need to extract the lumped circuit parameters (partial inductance L, coefficient of potential P and patch resistance R) from the kernel function representation of scalar and vector potentials.

The partitioning of geometry is done such that the Inductance patches (current elements) and the capacitance patches (charge elements) are orthogonal and are placed

half a cell away from each other. This partitioning is clearly depicted in Figs. 2.2-2.3 for the case of two dimensional object such as a thin conducting microstrip.

Fig. 2.2: Sectioning the object geometry into inductance partitions.

Fig. 2.3. Sectioning the object geometry into capacitive partitions.

The integral of quasi-static free space Green's function kernel which represents the circuit components is evaluated by numerical quadrature or using approximate analytical and closed form expressions [19], [67]-[69] for quick evaluation of component values. The evaluation of the Green's function kernel leads to the PEEC model with self- and partial- inductance and capacitance terms. The calculations of Green's function integral kernels are detailed in Appendix B.

#### 2.3 Baker-Campbell-Hausdorff-Dynkin Series Expression

Given two  $n \times n$  matrices namely x and y, the objective is to find a power series z = C(x, y) such that the equation

$$e^{x}e^{y} = e^{z}, \quad e^{x} = \sum_{n=0}^{\infty} \frac{x^{n}}{n!},$$

(2.16)

holds. The solution of the matrix problem could be obtained by treating x and y as variable elements that obey certain non-commutative algebra rules. It is assumed that the matrices x and y are close to zero matrices to ensure the convergence of the series.

To proceed with the derivation, a Hausdorff derivative operator is defined as

$$u\frac{\partial}{\partial x}(x^{k}yx^{m}) = ux^{k-1}yx^{m} + xux^{k-2}yx^{m} + x^{2}ux^{k-3}yx^{m} + \cdots + x^{k-1}uyx^{m} + x^{k}yux^{m-1} + \cdots + x^{k}yx^{m-1}u$$

. (2.17)

For the case of  $e^x$ , the relation

$$u\frac{\partial}{\partial x}e^{x} = u + \frac{1}{2!}(ux + xu) + \frac{1}{3!}(ux^{2} + xux + x^{2}u) + \cdots$$

(2.18)

is obtained. This results in the expression for  $e^{x+\alpha u}$  as

$$e^{x+\alpha u} = e^x + \alpha u \frac{\partial}{\partial x} e^x + \alpha^2(.) + \cdots, \qquad (2.19)$$

where  $\alpha$  is a real or complex parameter. To derive the coefficients of the series C(*x*,*y*) explicitly, a deformation of *x* and *y* in terms of a special series with variables *u* and *v* gives

$$e^{x}e^{y} = e^{x} [1 + \alpha \varphi(u, x) + \cdots] [1 - \alpha \psi(v, y) + \cdots] e^{y}.$$

(2.20)

The vanishing of the term corresponding to  $\alpha$  implies that

$$\varphi(u, x) = \psi(v, y), \qquad (2.21)$$

and

$$u_{\uparrow x} \frac{\partial}{\partial x} z = v_{\uparrow \omega(x,y)} \frac{\partial}{\partial y} z, \qquad (2.22)$$

where the symbol  $\uparrow$  is used to mean that the substitutions of u = x (as a convenient choice) and  $v = \omega(x, y)$  are made.

In order to calculate  $\omega(x, y)$ , an alternating series of the type

$$x = v \frac{1 - e^{-y}}{y} = v - \frac{1}{2!}vy + \frac{1}{3!}vy^2 - \dots + \frac{(-1)^n}{(n+1)!}vy^n + \dots,$$

(2.23)

is considered. Using the standard expansion form of  $\frac{y}{1-e^{-y}}$ , the  $v = \omega(x, y)$  series is

found to be

$$v = x \frac{y}{1 - e^{-y}} = x + \frac{1}{2}xy + \frac{B_1}{2!}xy^2 - \frac{B_2}{4!}xy^4 + \dots + (-1)^{n-1}\frac{B_n}{(2n)!}xy^{2n} + \dots, \quad (2.24)$$

where  $B_1, B_2, \dots, B_n$  are the Bernoulli numbers defined by

$$B_n = \frac{2(2n)!}{(2\pi)^{2n}} \sum_{k=1}^{\infty} \frac{1}{k^{2n}}.$$

(2.25)

Expansion on both sides of equation (2.22) leads to

$$u_{\uparrow_x}\frac{\partial}{\partial x}C(x,y) = C_1(\cdot) + 2C_2(\cdot) + 3C_3(\cdot) + \dots = v_{\uparrow_{\omega(x,y)}}\frac{\partial}{\partial y}\left[C_0(\cdot) + C_1(\cdot) + C_2(\cdot) + \dots\right], \quad (2.26)$$

where  $C_n = C_n(x, y)$  is the term of the n<sup>th</sup> order.

Equating the coefficients on both sides of equation (2.26) gives  $C_0(x, y) = y$  (by virtue of (2.16)) and

$$C_1(x, y) = v_{\uparrow \omega(x, y)} \frac{\partial}{\partial y} C_0(x, y), \qquad (2.27)$$

$$2C_2(x, y) = v_{\uparrow \omega(x, y)} \frac{\partial}{\partial y} C_1(x, y).$$

(2.28)

$$3C_3(x, y) = v_{\uparrow_{\omega(x,y)}} \frac{\partial}{\partial y} C_2(x, y), \qquad (2.29)$$

and similarly for the following coefficient terms. Thus, the desired series C(x, y) up to  $(2n+1)^{\text{th}}$  order is constructed by recursion of terms in equations (2.27), (2.28) up to the  $C_{n-1}^{\text{th}}$  term.

In particular, the series expansion up to five orders is

$$C(x, y) = x + y + \frac{1}{2} [xy] + \frac{1}{12} [yx^{2}] + \frac{1}{12} [xy^{2}] + \frac{1}{24} [yx^{2}y] - \frac{1}{720} [xy^{4}] - \frac{1}{720} [yx^{4}] + \frac{1}{360} [xy^{3}x] + \frac{1}{360} [yx^{3}y] - \frac{1}{120} [xy^{2}xy] - \frac{1}{120} [yx^{2}yx] + \cdots, \quad (2.30a)$$

where the symbol ^ is defined such that [xy] := [x, y] = xy - yx and

$[abc \cdots xyz] := [[abc \cdots xy], z]$ . The series is known to be convergent around the zero point. This property is of significance in applications such as the circuit solution for reflection coefficients (return loss) which are typically two orders of magnitude smaller than transmission coefficients (insertion loss).

A dual formula to the BCHD series, due to Zassenhaus [70], exists and is given by

$$e^{t(x+y)} = e^{tx}e^{ty}e^{t^2\frac{1}{2}[y,x]}\cdots$$

(2.30b)

# 2.4 Scaling the System Matrix

Let **A** be the system matrix, consisting of memory-less elements **G**, memory elements **C** and complex frequency  $s = j2\pi f$ , given as

$$\mathbf{A} = \mathbf{G} + s\mathbf{C} \tag{2.31}$$

Let **G**' be the perturbation matrix of resistive elements. Then the resulting exponent can be written as

$$e^{\mathbf{A}}e^{\mathbf{G}'} = e^{\mathbf{A}+\mathbf{G}'+\frac{1}{2}[\mathbf{A},\mathbf{G}']+\frac{1}{12}[\mathbf{A},[\mathbf{A},\mathbf{G}']]+\frac{1}{12}[\mathbf{G}',[\mathbf{A},\mathbf{G}']]+\frac{1}{24}[[\mathbf{A},[\mathbf{A},\mathbf{G}'],\mathbf{G}']+\cdots}{.}$$

(2.32)

This is the Baker-Campbell-Hausdorff-Dynkin series in which

$$[\mathbf{A},\mathbf{G'}] = \mathbf{A}\mathbf{G'} - \mathbf{G'}\mathbf{A} \tag{2.33}$$

is the Jacobi bracket of matrix commutation. Approximation of the convergent series by removing the higher order terms

$$[\mathbf{A}, [\mathbf{A}, \mathbf{G'}]] = [\mathbf{G'}, [\mathbf{A}, \mathbf{G'}]] = 0, \qquad (2.34)$$

which are negligible, results in

$$e^{\mathbf{A}}e^{\mathbf{G}'} \approx e^{\mathbf{A}+\mathbf{G}'+\frac{1}{2}[\mathbf{A},\mathbf{G}']}$$

(2.35)

A compensation matrix C' defined as

$$e^{s\mathbf{C}'} \approx e^{-\mathbf{G}' - \frac{1}{2}[\mathbf{A}, \mathbf{G}']}, \qquad (2.36)$$

is now introduced so that the product

$$e^{\mathbf{A}}e^{\mathbf{G}'}e^{s\mathbf{C}'} \approx e^{\mathbf{A}+\mathbf{G}'+\frac{1}{2}[\mathbf{A},\mathbf{G}']-\mathbf{G}'-\frac{1}{2}[\mathbf{A},\mathbf{G}']} \approx e^{\mathbf{A}},$$

(2.37)

is equivalent to the actual system matrix. The rate of change of energy and hence the perturbation of the system states is proportional to the frequency and the size of the memory elements. Thus the commutator can be represented as

$$[\mathbf{A}, \mathbf{G'}] \approx s\mathbf{C} \tag{2.38}$$

Substitution of equation (2.38) in equation (2.36) gives,

$$\mathbf{C'} \approx -\frac{1}{2}\mathbf{C} - \frac{1}{s}\mathbf{G'}$$

(2.39)

The matrix C' is the memory element compensation necessary, due to the perturbation of memory-less element matrix G', to preserve the system The choice of G' is governed by the circuit element spread.

System matrix scaling through the perturbation described above has the effect of improving its condition number which is quantified as follows [71]:

Let the system matrix A be scaled as A+E due to small perturbation E=G'+sC'. Let x be the solution of the linear system

$$\mathbf{A}\mathbf{x} = \mathbf{b} \,. \tag{2.40}$$

Let  $\mathbf{x}^*$  be the solution of the perturbed system such that

$$(\mathbf{A} + \mathbf{E})(\mathbf{x} + \boldsymbol{\delta}) = \mathbf{b}, \qquad (2.41)$$

where  $\delta = \mathbf{x}^* - \mathbf{x}$ . Subtracting equation (2.40) from equation (2,41), we get

$$(\mathbf{A} + \mathbf{E})\boldsymbol{\delta} = -\mathbf{E}\mathbf{x}, \qquad (2.42)$$

which implies that

$$\boldsymbol{\delta} = -\mathbf{A}^{-1}\mathbf{E}(\mathbf{x} + \boldsymbol{\delta}). \tag{2.43}$$

Therefore

$$\|\boldsymbol{\delta}\| \leq \|\mathbf{A}^{-1}\| \cdot \|\mathbf{E}\| \left( \|\mathbf{x}\| + \|\boldsymbol{\delta}\| \right) = \frac{Cond(\mathbf{A})}{\|\mathbf{A}\|} \|\mathbf{E}\| \left( \|\mathbf{x}\| + \|\boldsymbol{\delta}\| \right),$$

(2.44)

where  $Cond(\mathbf{A})$  refers to the condition number of  $\mathbf{A}$  and the matrix norm  $\|\mathbf{A}\|$  is given by

$$\|\mathbf{A}\| = \max_{\mathbf{x}\neq 0} \frac{\|\mathbf{A}\mathbf{x}\|}{\|\mathbf{x}\|}.$$

(2.45)

Solving the inequality (2.44) for  $\|\boldsymbol{\delta}\|$ , we get

$$\left\|\boldsymbol{\delta}\right\| \leq \frac{Cond(\mathbf{A}) \frac{\left\|\mathbf{E}\right\|}{\left\|\mathbf{A}\right\|} \left\|\mathbf{x}\right\|}{1 - Cond(\mathbf{A}) \frac{\left\|\mathbf{E}\right\|}{\left\|\mathbf{A}\right\|}},$$

(2.46)

where the assumption that

$$Cond(\mathbf{A}) \frac{\|\mathbf{E}\|}{\|\mathbf{A}\|} = \|\mathbf{A}^{-1}\| \cdot \|\mathbf{E}\| < 1$$

(2.47)

has been made. From the inequality (2.46), we conclude that

$$\frac{\|\mathbf{\delta}\|}{\|\mathbf{x}\|} \le \frac{Cond(\mathbf{A})\frac{\|\mathbf{E}\|}{\|\mathbf{A}\|}}{1 - Cond(\mathbf{A})\frac{\|\mathbf{E}\|}{\|\mathbf{A}\|}}.$$

(2.48)

The inequality (2.48) shows that small Cond(A) indicates a small relative change in the solution. When Cond(A) is large, introduction of small perturbation in  $||\mathbf{E}||$  helps to reduce the error in the solution.

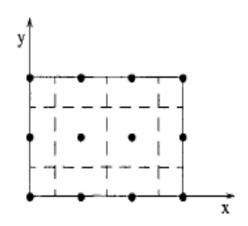

### **2.5 Numerical Example**

A symmetric stripline geometry with the size of length =500  $\mu m$ , width =25  $\mu m$  and thickness = 0.5  $\mu m$  of copper with dielectric permittivity = 1 and ground plane spacing of 20  $\mu m$  as shown in Fig. 2.4, is chosen as a test example. The conductor loss is governed by the finite conductivity of copper which is taken as  $5.8 \times 10^7$  Siemens/m. The dielectric loss is absent since free space is taken as a dielectric medium. The geometry is specifically chosen to obtain a characteristic impedance of 50 ohms. This helps to

simplify the treatment of PEEC boundary with the source and load terminal nodes to be 50 ohms each.

Fig. 2.4: Cross-section of stripline transmission line

The thin geometry allows for 2-dimensional basis functions to be used in the PEEC model. The pulse functions are used as the basis and weights. By sub-sectioning the geometry, it ( $<\lambda/10$ ) results in 9+8=17 inductors, 17 resistors and 12 capacitors. The ground planes are replaced by the image elements. The partial inductance, partial potential coefficient (reciprocal of capacitance) and resistance values are obtained through

$$L_{p} = \frac{\mu}{4\pi ll'} \iint_{s \ s'} K(r, r') ds ds', \qquad (2.49)$$

$$P_{P} = \frac{1}{C_{P}} = \frac{1}{4\pi\varepsilon a} \int_{s'} K(r, r') ds', \qquad (2.50)$$

$$R_P = \frac{L}{\sigma W t},\tag{2.51}$$

where K(r,r') is the inverse distance kernel with r and r' representing distances, ds and ds' area segments and l and l' length segments (perpendicular to the direction of current flow) of the observation and source cells respectively; a is the surface area of the

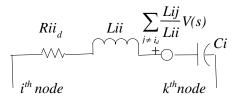

capacitive partition segment and *L*, *W*, *t* and  $\sigma$  are the segment length (along the direction of current flow), width, thickness and conductivity respectively. We have used the surface integrals instead of the volume integrals for inductance calculations, which significantly reduce the computational overhead while keeping the required accuracy. Only the self-inductances and self-capacitances and resistances are scaled. The mutual inductance and mutual capacitance ratios need not be scaled. The scaling factor of the *Lp* and *Pp* are determined by equation (2.39). i.e. the new circuit element values are scaled as

$$Rii = R_p \to R_p + \varepsilon R_p, \qquad (2.52)$$

$$Lii = L_p \rightarrow \left[\frac{L_p}{2} - \frac{\varepsilon R_p}{s}\right], \qquad (2.53)$$

$$Cii = C_p \to \left[\frac{C_p}{2} - \frac{\varepsilon R_p}{s}\right]. \tag{2.54}$$

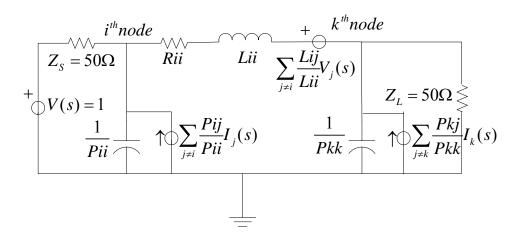

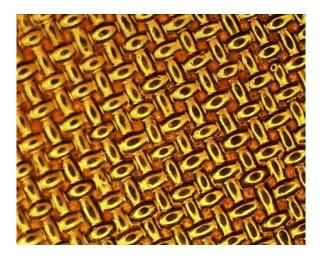

where  $\varepsilon$  is the scaling coefficient determined from the system matrix condition. The equivalent circuit with the scaled circuit elements is given in Fig. 2.1 where mutual  $(i \neq j)$ inductance couplings are represented by voltage sources  $V_j$  and capacitive couplings by current sources  $I_K$ .

## 2.6 Results and Discussions

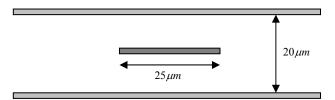

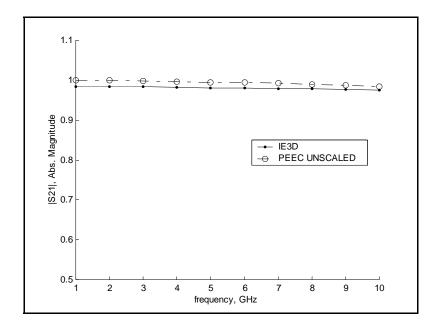

The unscaled and scaled PEEC models were simulated in SPICE and compared with the full-wave solver IE3D [72] results in terms of scattering parameter magnitude and phase.

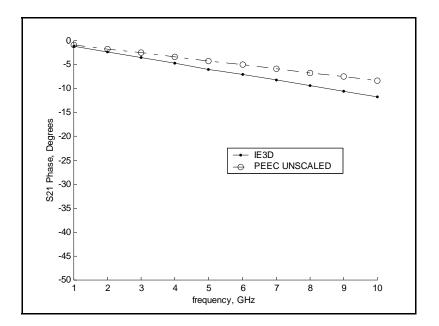

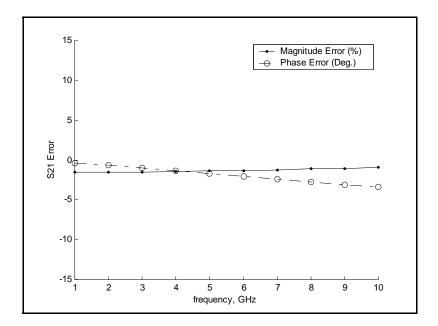

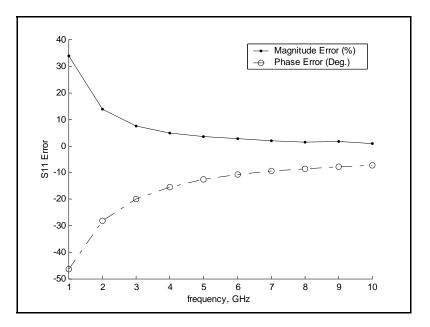

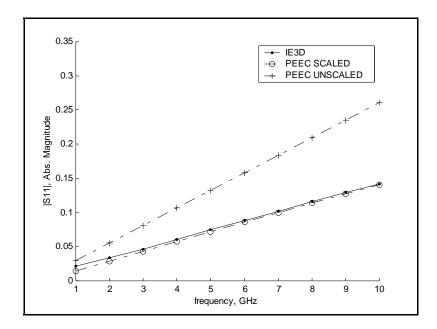

IE3D is chosen for its accuracy and efficiency in handling rectangular geometries. Also, simulation of the structure with Ansoft HFSS shows agreement with IE3D results within 1% relative magnitude and 3 degrees phase difference. The  $S_{21}$  results of the unscaled model are in good agreement within 2% of relative magnitude error and 3 degrees of relative phase error at frequency range of 1 to 10 GHz as shown in Figs. 2.5, 2.6 and 2.7. But  $S_{11}$  results of unscaled model have errors as high as 34% in magnitude and 46 degrees in phase as shown in Fig. 2.8, and Tables 2.1 and 2.2.  $S_{11}$  results of the scaled model are in good agreement at high frequencies over 5 GHz as shown in Figs. 2.9 and 2.10.

Fig. 2.5: S<sub>21</sub> magnitude (linear) versus frequency.

**Fig. 2.6:**  $S_{21}$  phase versus frequency.

Fig. 2.7:  $S_{21}$  magnitude and phase error versus frequency

**Fig. 2.8:**  $S_{11}$  magnitude and phase error versus frequency

| Frequency<br>GHz | IE3D<br>Abs. mag | PEEC<br>Abs. mag | IE3D Angle<br>Degrees | PEEC Angle<br>Degrees | Mag. Error<br>Rel. (%) | Phase Error<br>Degrees |

|------------------|------------------|------------------|-----------------------|-----------------------|------------------------|------------------------|

| 1.00E+00         | 2.17E-02         | 1.44E-02         | 4.13E+01              | 8.76E+01              | 3.38E+01               | -4.63E+01              |

| 2.00E+00         | 3.34E-02         | 2.88E-02         | 5.90E+01              | 8.72E+01              | 1.38E+01               | -2.82E+01              |

| 3.00E+00         | 4.67E-02         | 4.32E-02         | 6.64E+01              | 8.63E+01              | 7.55E+00               | -1.99E+01              |

| 4.00E+00         | 6.05E-02         | 5.75E-02         | 7.00E+01              | 8.54E+01              | 5.00E+00               | -1.54E+01              |

| 5.00E+00         | 7.45E-02         | 7.18E-02         | 7.18E+01              | 8.44E+01              | 3.57E+00               | -1.26E+01              |

| 6.00E+00         | 8.84E-02         | 8.59E-02         | 7.26E+01              | 8.34E+01              | 2.79E+00               | -1.08E+01              |

| 7.00E+00         | 1.02E-01         | 1.00E-01         | 7.29E+01              | 8.24E+01              | 2.11E+00               | -9.48E+00              |

| 8.00E+00         | 1.16E-01         | 1.14E-01         | 7.29E+01              | 8.14E+01              | 1.53E+00               | -8.51E+00              |

| 9.00E+00         | 1.29E-01         | 1.27E-01         | 7.26E+01              | 8.04E+01              | 1.69E+00               | -7.78E+00              |

| 1.00E+01         | 1.42E-01         | 1.41E-01         | 7.22E+01              | 7.94E+01              | 9.40E-01               | -7.21E+00              |

Table 2.1: S<sub>11</sub> magnitude error (percentage) and Phase error (degrees).

| Frequency<br>GHz | IE3D<br>Abs. mag | PEEC<br>Abs. mag | IE3D Angle<br>Degrees | PEEC Angle<br>Degrees | Mag.Error<br>Rel. (%) | Phase Error<br>Degrees |