# TWO CONCRETE PROBLEMS IN TIMING ANALYSIS OF EMBEDDED SOFTWARE

## **HEMENDRA SINGH NEGI**

(B.Tech., IIT Bombay)

A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF SCIENCE SCHOOL OF COMPUTING NATIONAL UNIVERSITY OF SINGAPORE

2004

# Acknowledgement

I would like to thank my supervisors **Dr. Tulika Mitra** and **Dr. Abhik Roychoudhury**, for their invaluable guidance and support. Without their help, it was almost impossible for me to complete this work.

I would also like to thank my lab-mate Pan Yu for his help in getting me various tools and softwares required. I would also like to thank all my friends for their consistent support and encouragement.

Finally, I would like to thank my parents who stood by me during the hardest time in my life and provided me with encouragement and confidence to complete the work.

#### Hemendra Singh Negi

# Contents

| 1 | Intr | oduction                                    | 1  |

|---|------|---------------------------------------------|----|

|   | 1.1  | Design Issues For Real-Time Systems         | 1  |

|   | 1.2  | Overview Of The Report                      | 3  |

| 2 | Esti | mation of Cache Related Preemption Delay    | 4  |

|   | 2.1  | Introduction                                | 4  |

|   | 2.2  | Related Work                                | 5  |

|   |      | 2.2.1 Set Based Approach of Lee et. al      | 7  |

|   | 2.3  | Our Technique                               | 8  |

|   |      | 2.3.1 Motivation                            | 9  |

|   |      | 2.3.2 Approach                              | 10 |

|   | 2.4  | An Example                                  | 14 |

|   | 2.5  | Experimental Results                        | 17 |

|   | 2.6  | Optimization Using Binary Decision Diagrams | 19 |

|   | 2.7  | Conclusion                                  | 23 |

| 3 | Tim  | ing Analysis of Loop Behaviors              | 24 |

|   | 3.1  | Introduction                                | 24 |

|   |      | 3.1.1 Types of Infeasible Paths             | 25 |

|   | 3.2  | Infeasible Path Detection Technique         | 27 |

|   |      | 3.2.1 Technique                             | 27 |

|   |      | 3.2.2 Example                               | 28 |

|   |      | 3.2.3 Implementation And Results            | 28 |

|   | 3.3                                                       | WCET                                                                                | Calculation Technique                                                                                                                                 | 29                                                                                                         |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   |                                                           | 3.3.1                                                                               | Basic Technique                                                                                                                                       | 29                                                                                                         |

|   |                                                           | 3.3.2                                                                               | Refined Approach                                                                                                                                      | 33                                                                                                         |

|   |                                                           | 3.3.3                                                                               | Problem Statement                                                                                                                                     | 34                                                                                                         |

|   |                                                           | 3.3.4                                                                               | Method                                                                                                                                                | 34                                                                                                         |

|   |                                                           | 3.3.5                                                                               | Creating Nodes                                                                                                                                        | 35                                                                                                         |

|   |                                                           | 3.3.6                                                                               | Creating Transitions                                                                                                                                  | 36                                                                                                         |

|   |                                                           | 3.3.7                                                                               | Dynamic Programming Algorithm                                                                                                                         | 37                                                                                                         |

|   | 3.4                                                       | Impler                                                                              | nentation And Illustration By Examples                                                                                                                | 39                                                                                                         |

|   |                                                           | 3.4.1                                                                               | Example 1: Iteration Based Constraints                                                                                                                | 40                                                                                                         |

|   |                                                           | 3.4.2                                                                               | Example 2: Effect Based Constraints                                                                                                                   | 41                                                                                                         |

|   |                                                           | 3.4.3                                                                               | Example 3: Combination of Effect Based And Iteration Based Constraints                                                                                | 44                                                                                                         |

|   |                                                           | 3.4.4                                                                               | Results                                                                                                                                               | 44                                                                                                         |

|   | 3.5                                                       | Relate                                                                              | d Work                                                                                                                                                | 48                                                                                                         |

|   | 3.6                                                       | Discus                                                                              | sion                                                                                                                                                  | 51                                                                                                         |

|   |                                                           |                                                                                     |                                                                                                                                                       |                                                                                                            |

| 4 | Sim                                                       | plifying                                                                            | WCET Analysis by Code Transformations                                                                                                                 | 52                                                                                                         |

| 4 | <b>Sim</b> ]<br>4.1                                       |                                                                                     | WCET Analysis by Code Transformations                                                                                                                 | <b>52</b><br>53                                                                                            |

| 4 | -                                                         |                                                                                     |                                                                                                                                                       |                                                                                                            |

| 4 | -                                                         | Our Te                                                                              | chnique                                                                                                                                               | 53                                                                                                         |

| 4 | -                                                         | Our Te<br>4.1.1<br>4.1.2                                                            | cchnique                                                                                                                                              | 53<br>54                                                                                                   |

| 4 | 4.1                                                       | Our Te<br>4.1.1<br>4.1.2<br>Conclu                                                  | cchnique                                                                                                                                              | 53<br>54<br>55                                                                                             |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Our Te<br>4.1.1<br>4.1.2<br>Conclu<br>Discus                                        | echnique                                                                                                                                              | 53<br>54<br>55<br>58                                                                                       |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Our Te<br>4.1.1<br>4.1.2<br>Conclu<br>Discus<br>clusion                             | acchnique                                                                                                                                             | 53<br>54<br>55<br>58<br>58                                                                                 |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>Con</li></ul> | Our Te<br>4.1.1<br>4.1.2<br>Conclu<br>Discus<br>clusion                             | achnique   Reducing number of loop paths   Equalizing path lengths   Ision   Sion & Future Work                                                       | <ul> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>58</li> <li>61</li> </ul>                         |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>Con</li></ul> | Our Te<br>4.1.1<br>4.1.2<br>Conclu<br>Discus<br>clusion<br>A Tigh                   | achnique   Reducing number of loop paths   Equalizing path lengths   Ision   Ision & Future Work <b>&amp; Future Work</b>                             | <ul> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>58</li> <li>61</li> <li>61</li> </ul>             |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>Con</li></ul> | Our Te<br>4.1.1<br>4.1.2<br>Conclu<br>Discus<br>clusion<br>A Tigh<br>5.1.1<br>5.1.2 | achnique   Reducing number of loop paths   Equalizing path lengths   Ision   sion & Future Work <b>&amp; Future Work</b> Iter Bound on CRPD   Example | <ul> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>58</li> <li>61</li> <li>61</li> <li>62</li> </ul> |

#### Summary

The design of real-time systems requires a timing guarantee to be given on the execution time of the tasks running in the system. The timing guarantees for the tasks can be given in the form of worst case execution time (WCET) of a program. An upper bound on the WCET of a program can be given by static analysis methods. The problem of determining WCET of a program by static analysis methods has to be solved at the following two levels (1) Programming language level, to determine the longest path in the program and (2) Micro-architectural level, to take into account the effect of features such as pipeline, cache and branch prediction. At the programming language level it is required to detect the infeasible paths in the program and use that information for giving a tight bound on the WCET of the program. At the micro-architectural level, the presence of caches in a real-time system with multiple tasks, results in additional delay in the execution time of the task due to preemption by a higher priority task. Such delays are called as cache related preemption delay (CRPD). It is important to derive an upper bound on the CRPD for the schedulability analysis of tasks running in a real-time system.

In our work we have targeted static analysis both at the programming language level and microarchitectural level. At the programming language level, we have proposed a constraint propagation based technique to determine certain infeasible paths present in a loop in the program. We have also proposed a WCET Analysis technique which uses the infeasible path information to give a tight upper bound on the worst case execution time of a loop. Our experimental results show that our infeasible path detection technique could even detect some of the infeasible paths which are hard to detect from existing infeasible path detection techniques and our WCET computation technique gives tight bounds on the WCET of a program. Further, we have proposed a code transformation based idea for reducing the number of paths in a program that has to be considered during the WCET analysis. Reducing the number of paths is very advantageous for path based WCET analysis techniques which in general are exponential on the number of paths in a program.

We have also proposed a technique to model caches in order to determine a tight bound on the CRPD of tasks. Our technique performs path analysis of both high priority and low priority tasks. Furthermore, we compute all possible states of cache, when the lower priority task gets preempted by the higher priority tasks and when the higher priority task is completed. This is more accurate than the existing set based analysis techniques which estimate the cache states by inferring the set of memory blocks which may exist in each cache block, and thus leading to over-estimations.

# **List of Tables**

| 2.1 | Computation of $RCS_B$ for the CFG in Figure 2.3                                              | 15 |

|-----|-----------------------------------------------------------------------------------------------|----|

| 2.2 | Description of benchmark programs.                                                            | 17 |

| 2.3 | Accuracy of CRPD analysis for a 32-block cache. A stands for actual value(by sim-             |    |

|     | ulation), C stands for combined analysis of all cache blocks and S stands for separate        |    |

|     | analysis of each cache block.                                                                 | 18 |

| 2.4 | Maximum number of cache blocks used by high priority task for a 32-block cache                | 18 |

| 2.5 | Maximum number of useful cache blocks of the low-priority task at any program point           |    |

|     | for different cache sizes. A stands for actual value(by simulation), C stands for combined    |    |

|     | analysis of all cache blocks and S stands for separate analysis of each cache block. $\ldots$ | 18 |

| 2.6 | Comparison of combined and separate analysis for low-priority task. BB denotes the            |    |

|     | number of basic blocks at which useful cache block count differs and Diff denotes the         |    |

|     | maximum of these differences.                                                                 | 19 |

| 2.7 | Time to compute useful cache blocks for low-priority task in sec                              | 19 |

| 2.8 | Possible encoding of memory blocks into boolean form                                          | 20 |

| 2.9 | Comparison of memory usage between normal and BDD representation of cache states .            | 23 |

| 2 1 | Description of benchmarks used                                                                | 17 |

| 3.1 |                                                                                               | 47 |

| 3.2 | Results showing WCET prediction                                                               | 48 |

# **List of Figures**

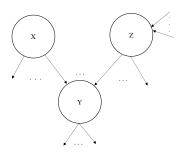

| 2.1  | RMB, LMB and Useful states at program point P                        | 9  |

|------|----------------------------------------------------------------------|----|

| 2.2  | Two paths to P from X, only one of it is possible                    | 10 |

| 2.3  | An example control flow graph                                        | 14 |

| 3.1  | Infeasible paths due to branch correlation                           | 25 |

| 3.2  | Infeasible paths due to effect of assignment on branch               | 25 |

| 3.3  | Correlation of a branch outcome with a conjunction of other branches | 26 |

| 3.4  | Infeasible paths across iteration                                    | 26 |

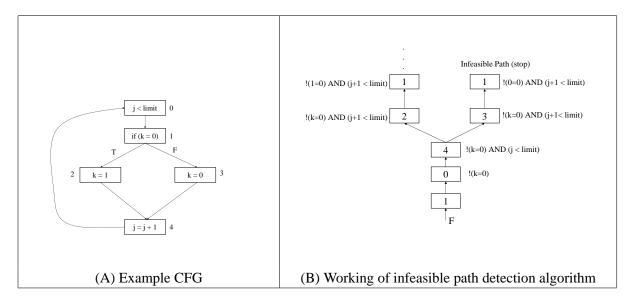

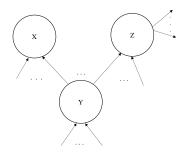

| 3.5  | Example CFG and working of infeasible path detection algorithm       | 28 |

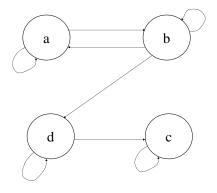

| 3.6  | X has no incoming edge                                               | 32 |

| 3.7  | X has no outgoing edge                                               | 32 |

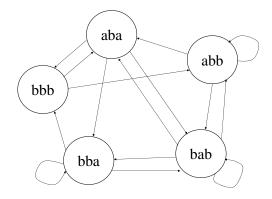

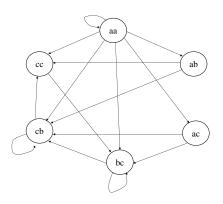

| 3.8  | <i>ba</i> is an infeasible sequence of paths                         | 35 |

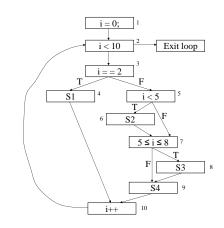

| 3.9  | Example 1: Illustrating iteration based constraints                  | 40 |

| 3.10 | Control Flow Graph for Example 1                                     | 40 |

| 3.11 | Paths and their corresponding sequence of blocks executed            | 41 |

| 3.12 | Transition graph for Example 1                                       | 41 |

| 3.13 | Working of DP algorithm for Example 1                                | 42 |

| 3.14 | Example 2: Illustrating effect based constraints                     | 42 |

| 3.15 | Possible paths for Example 2                                         | 43 |

| 3.16 | Transition graph for Example 2                                       | 43 |

| 3.17 | Working of DP algorithm for Example 2                                | 44 |

| 3.18 | Example 3: Combining effect and iteration based constraints          | 45 |

| 3.19 | Possible paths for Example 3                                         | 45 |

| 3.20 | Nodes and their corresponding start and end for Example 3 | 45 |

|------|-----------------------------------------------------------|----|

| 3.21 | Transition graph for Example 3                            | 46 |

| 3.22 | Working of DP algorithm for Example 3                     | 46 |

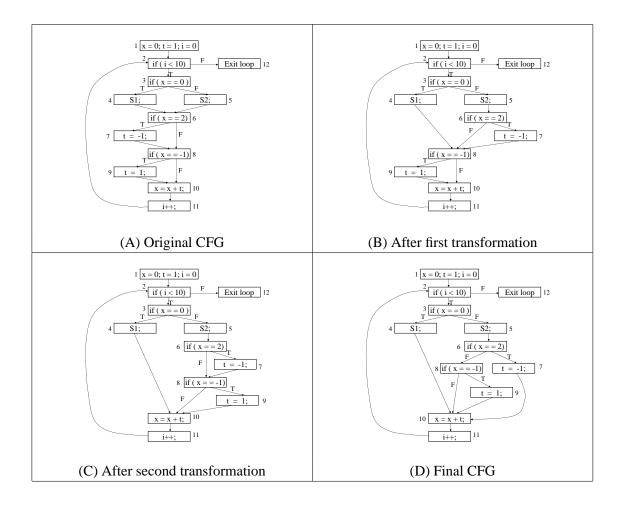

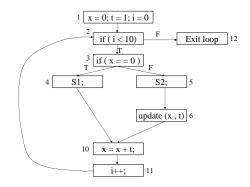

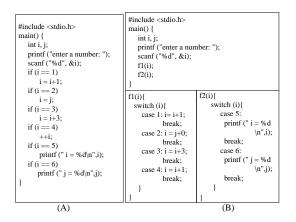

| 4.1  | Example code to illustrate our technique                  | 54 |

| 4.2  | Reduction of number of loop paths in Control Flow Graph   | 55 |

| 4.3  | Possible paths for original loop                          | 56 |

| 4.4  | Example code after loop path reduction                    | 56 |

| 4.5  | Example code after path length equalization               | 57 |

| 4.6  | Control Flow Graph after path equalization                | 57 |

| 4.7  | Example Code: Toy6                                        | 59 |

# **Chapter 1**

# Introduction

The world is moving fast towards embedded systems. A lot of equipments used in the day to day life for e.g. washing machine, mobile phones etc. are embedded systems. An embedded system is classified as *real-time embedded system* if the correctness of the system depends not only on the logical result of the computation, but also on the time at which the results are produced [46]. Further, a real-time system can be divided into two classes: 1) *Hard Real-Time System:* which has to meet strict deadlines. 2) *Soft Real-Time System:* which do not require the same degree of determinism and the task running in it retain some diminished value after its deadline so it should still be executed. Predictability of hard real-time systems is very important as missing of deadline by a task in hard real-time system may cause havocs. In this report we concentrate upon the predictability of real-time system in reference to hard real-time systems.

#### **1.1 Design Issues For Real-Time Systems**

The two main issues <sup>1</sup> in the design of real-time systems are: (i) *predictability:* it should be possible to give an upper bound on the execution time of a task, and (ii) *performance:* the real-time system should be fast.

One of the main issue in the design of real time system is: providing a timing guarantee (predictability) for the tasks running in it. The obstacles to the predictability of real-time systems are:

<sup>&</sup>lt;sup>1</sup>Note that another important issue in the design of real-time system is *power* i.e. a real-time system should consume less power. Detail description of this issue is beyond the scope of this report

- Large set of inputs: since in most of the cases the set of inputs to an application program in realtime systems could be very large, hence it is not feasible to test all the input cases to determine how much time the application will take to execute in the system.

- 2. Unpredictable hardware: In the presence of unpredictable components such as caches and pipeline it is hard to derive the exact amount of time taken by a task to run in the system (In this report, we will only concentrate on predictability issues related to caches).

Predictability for real-time system can be achieved either by *static analysis techniques* or by *hard-ware/software approaches*. Since, it is very difficult and time consuming and in some cases almost impossible to test all the input cases to determine the time taken by a task running in a system. There-fore, static analysis methods which analyze the program statically to give an upper bound on the time taken by a task are very beneficial [31, 23, 36, 32, 29]. On the other hand, hardware/software approaches try to model the system in a way such that it is inherently predictable.

One of the hindrance to the predictability of real-time system is the use of unpredictable hardware such as caches. The performance gain achieved by caches in a system makes their use in real-time system inevitable. Although caches are very effective means of speeding up the memory accesses in the average case. However, the worst case behavior of applications, which is of prime importance in hard real-time systems, is hard to predict in a safe and precise way in the presence of caches, due to the presence of *intra-task* and *inter-task* interferences. Intra-task interferences occur when a task overrides its own blocks in the cache due to conflicts for cache blocks. Inter-task interferences arise in multitasking systems because of the preemptions. The modelling of caches via static analysis methods include worst case execution time (WCET) analysis in case of intra-task interferences. Caches can also be modelled for real-time system by various hardware/software approaches which include cache partitioning [25, 33], cache locking [12, 52, 43] etc. In this report we present our technique to determine a tight upper bound on the cache related preemption delay.

Another issue in the design of real-time embedded system is that it should be fast in performance. A real-time system can be tuned for optimal performance with respect to caches, either by analysis of programs' memory performance [20, 13] and applying code transformation accordingly or by design and optimization of cache parameters such as line size, cache size and associativity [24, 35, 49, 30].

## **1.2** Overview Of The Report

In this report two techniques for the timing analysis of real-time embedded systems are presented. Chapter 2 discusses a technique to determine a tight bound on the cache related preemption delay. Chapter 3 presents a method to determine a bound on time for the execution of loops in a program. Chapter 4 discusses a code transformation based technique which could be used as a pre-processing step to other WCET calculation techniques for reducing their complexity. Finally the last chapter presents conclusion and future work prospects.

# Chapter 2

# **Estimation of Cache Related Preemption Delay**

#### 2.1 Introduction

The running of multiple tasks in a real time system with cache results in interferences in the cache, due to the replacement of memory blocks of one task by another task at the time of preemption. Such type of interferences as said before are known as inter-task interferences. Due to the preemption of a lower priority task by a higher priority task some memory blocks belonging to lower priority task might get replaced, therefore when the lower priority task resumes its execution it has to incur some extra cost by bringing back the replaced memory blocks (if they are required) from the memory to the cache. This additional cost incurred by the lower priority task is known as Cache Related Preemption Delay (CRPD) and it occurs when the useful cache blocks of the lower priority task get replaced by the higher priority task. The useful cache blocks at any point in the program are those cache blocks whose contents would be used again later in the program before being replaced.

The estimation of CRPD is very important for the schedulability analysis of tasks. In particular, [27, 28] reports how CRPD can be used to derive accurate response times of multiple periodic tasks running on a single processor for fixed-priority preemptive scheduling. There exists other ways such as cache partitioning (for e.g. [25, 54]) to avoid the analysis of CRPD. However, such an approach results in severe degradation of performance and might also require changes to hardware or software depending upon how the partitioning is controlled. Thus, for multi-tasked real-time systems with caches, CRPD

estimation is necessary to evaluate task preemption costs.

To determine a tight bound on CRPD, it is important to consider the effects of both high and low priority tasks. When a task  $\tau_0$  is preempted by task  $\tau_1$  it is necessary to consider the following:

- All the memory blocks of  $\tau_0$  which are in the cache when  $\tau_0$  is preempted may not be re-referenced after resumption.

- All the memory blocks of  $\tau_0$  which are in the cache when  $\tau_0$  is preempted may not be replaced by  $\tau_1$ .

- There are several possible cache contents when  $\tau_0$  is preempted (resulting from the different paths of  $\tau_0$ ).

- There are several possible cache contents when  $\tau_0$  resumes (resulting from the different paths of  $\tau_1$ .)

- There are several possible memory reference patterns after  $\tau_0$  resumes execution (due to different paths of  $\tau_0$ ).

The importance of some of these factors on CRPD is mentioned in [17]. However, no estimation technique is given and only simulation results are presented.

#### 2.2 Related Work

In [3], Basumallick and Nilsen extended the rate monotonic analysis to take into account inter-task interferences in the the form of cache related preemption delay. Some of the works on estimating the CRPD are presented in [51, 27, 28, 17]. Tomiyama and Dutt in their approach [51] have assumed that all the cache blocks are useful at the time of preemption, thus reducing the CRPD calculation to finding out the maximum number of cache blocks used by high priority task. They have also shown that it is not necessary that the longest path in the program uses the largest number of cache blocks too. They have used an integer linear programming based approach to determine the program execution path which uses the maximum number of cache blocks. They have shown that by solving the ILP problem, it is possible to achieve a tighter upper bound on CRPD. Lee at. el. in [27] have performed a set based analysis of the cache blocks used by the preempted task. In their approach they try to find out the set

of all possible memory blocks that could be present in a cache block at any program point. For their analysis they consider only the low priority tasks. The work of [27] has been extended in [28] to include the high priority task also. Dwyer and Fernando in [17] have given a simulation based approach to calculate the CRPD. They generate a live cache frame <sup>1</sup> distribution of an application by running it under different circumstances and thus find out the maximum number of live cache frames reached at any instant. This gives an upper bound on the CRPD. A caveat to their approach is that it must be possible to find the maximum number of live frames coexistent during the execution of an application under all possible circumstances. They have also proposed refinements to include the effect of high priority task. Busquets-Mataix has proposed an approach to analyze cache eviction cost in a multi-tasking system [11]. However, they also conservatively assume that all the cache lines used by the preempting task need to be reloaded by the preempted task when the preempted task is resumed. In a recent work by Yudong and Mooney [50], the authors have proposed a method to analyze the preemption cost caused by cache eviction in a multi-tasking real-time system. They analyzes the inter-task cache eviction behavior by calculating the intersection set of cache lines used by the preempting task and the preempted task. The authors also do a path analysis to eliminate cache lines that will not be accessed in a task from being used in the estimate. In another recent work [48], Staschulat and Ernst have presented a CRPD analysis approach which considers multiple process activations and preemption scenarios. The authors have proposed a technique which extends the CRPD approach of [38], by propagating replaced cache blocks in the control flow graph. Multiple process activations are modelled by inserting an edge from the last to the first node.

Our approach is similar to the set based approach of Lee et. al. [27]. However, with our approach we are able to compute a tighter bound on CRPD, as we store the relative occurrences of memory blocks in cache. We have later compared our results with the set based approach of [27], to show that our approach gives a tighter bound on the CRPD. Therefore, to realize the usefulness and power of our approach it is important to have a basic understanding of the set based approach of [27]. The description of the set based approach follows.

<sup>&</sup>lt;sup>1</sup>A 'live cache frame' is a cache frame that contains a block that is accessed in the future and without an intervening eviction

#### 2.2.1 Set Based Approach of Lee et. al

Lee at. el. in [27] have performed a set based analysis of the cache blocks used by the preempted task  $\tau_0$  before and after preemption. Some of the definitions given by them are as follows.

**Definition 2.2.1 (REACHING MEMORY BLOCKS(RMBs))** The set of reaching memory blocks of cache block c at program point p, denoted by  $RMB_p^c$ , contains all possible states of cache block c at program point p, where a possible state corresponds to a memory block that may reside in the cache block at the point. For a memory block to reside in cache block c, first, it should be mapped to cache block c. Furthermore, it should be the last reference to the cache block in some execution path reaching p.

**Definition 2.2.2 (LIVE MEMORY BLOCKS(LMBs))** The set of live memory blocks of cache block c at a program point p, denoted by  $LMB_p^c$ , contains all possible states of cache block c at program point p, where a possible state corresponds to a memory block that may be the first reference to cache block c after p.

The iterative equations for calculating the RMBs at various basic blocks of the program are as follows.

$$RMB_{IN}^{c}[B] = \bigcup_{X \text{ a predecessor of } B} RMB_{OUT}^{c}[X]$$

$$RMB_{OUT}^{c}[B] = \begin{cases} gen^{c}[B] & \text{if } gen^{c}[B] \text{ is not null;} \\ RMB_{IN}^{c}[B] & \text{otherwise.} \end{cases}$$

B, X are the basic blocks (note that a program point is taken as an exit or entry of a basic block).  $RMB_{IN}^c$  and  $RMB_{OUT}^c$  are the RMBs at the beginning and end of the basic block *B*, respectively.  $gen^c[B]$  contains as its unique element the memory block that is the last reference to the cache block *c* in the basic block.  $gen^c[B]$  is null if basic block *B* does not have any reference to memory blocks mapped to cache block *c*. The equations for LMB is given in a similar manner. The LMBs at various basic blocks of the program can be calculated using the following equations.

$$LMB_{OUT}^{c}[B] = \bigcup_{S \text{ a successor of } B} LMB_{IN}^{c}[S]$$

$$LMB_{IN}^{c}[B] = \begin{cases} gen^{c}[B] & \text{if } gen^{c}[B] \text{ is not null;} \\ LMB_{OUT}^{c}[B] & \text{otherwise.} \end{cases}$$

where  $gen^{c}[B]$  is null if basic block *B* does not have any reference to memory blocks mapped to cache block *c*, otherwise contains an unique element, the memory block that is the first reference to the cache block *c* in the basic block.

A fixed point iteration algorithm is used to calculate the sets of RMB and LMB at various program points, as per the above equations. The initial conditions for RMB calculation via fixed point iteration algorithm are

$$RMB_{IN}^{c}[B] = \phi$$

$$RMB_{OUT}^{c}[B] = gen^{c}[B]$$

and the initial conditions for LMB calculation via fixed point iteration algorithm are

$$LMB_{OUT}^{c}[B] = \phi$$

$$LMB_{IN}^{c}[B] = gen^{c}[B]$$

Once the sets of RMBs and LMBs are calculated at various program points, the set of *useful cache blocks* are calculated from the intersection of RMB and LMB at various program points. A cache block c is useful at a program point P if the intersection of sets RMB and LMB for cache block c is not null at point P. The CRPD incurred, if the interrupt point is P would be given by the total number of useful cache blocks at point P.

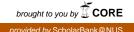

Figure 2.1 from [27] shows an example of the set of RMB and LMB calculated at program point P. The cache blocks *i* and *j* are useful at point P, as the intersection of sets LMB and RMB is not null.

#### 2.3 Our Technique

In our approach [38], we have refined the existing set based approach [27] to calculate a more accurate bound on the CRPD. Our technique performs path analysis of both high priority and low priority tasks. Furthermore, we compute all possible states of cache, when the lower priority task gets preempted by

Figure 2.1: RMB, LMB and Useful states at program point P

the higher priority tasks and when the higher priority task is completed. This is more accurate than the existing set based analysis techniques [27] which estimate the cache states by inferring the set of memory blocks which may exist in each cache block.

#### 2.3.1 Motivation

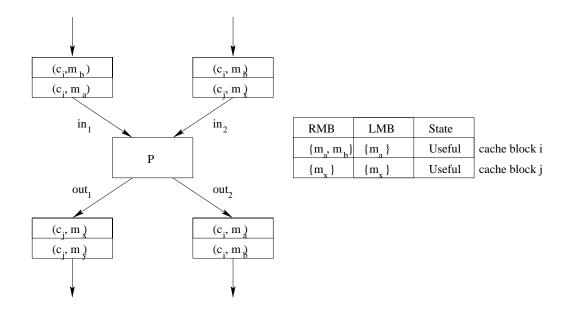

The existing set based approach [27] suffers with an overestimation as they calculate the different possible states of the cache blocks at any instant independently. Therefore, at any instant for each cache block, they give all possible memory blocks those can be present at that instant in that cache block. For example consider Figure 2.2. In Figure 2.2, there are two possible paths to P from X, but only one is possible at any time. Consider a direct mapped cache with two cache blocks. Taking the left path would result in cache state  $\{< M_a, M_c >\}$  and taking the right path will result in state  $\{< M_b, M_d >\}$  for the cache. [27] will represent the cache state individually as  $\{M_a, M_b\}$  and  $\{M_c, M_d\}$  for the cache blocks  $c_i$  and  $c_j$ , respectively. This will actually be counted as cache states  $\{< M_a, M_c >\}$ ,  $\{< M_a, M_d >\}$ , later while calculating the useful cache blocks, since they do not store the relative occurrences of memory blocks in cache. In our approach at each point we actually store the different possible cache states, thus maintaining the relative occurrences of memory blocks in cache. For example, in the above case we will store the cache states as  $\{< M_a, M_c >\}$  and  $\{< M_b, M_d >\}$ , hence

Figure 2.2: Two paths to P from X, only one of it is possible

later while calculating the useful cache blocks, we get accurate and better results than [27].

#### 2.3.2 Approach

Let us define some of the notions first, before giving the description of our approach.

**Definition 2.3.1 (Cache State)** A cache state represents the contents of cache at any instant. A cache state of null for any cache block denotes an empty cache block. A cache state can be imagined as a vector of size equal to maximum number of cache blocks and containing the memory addresses mapping to the cache blocks.

In all our calculations we have assumed a direct mapped cache. For a direct mapped cache with n blocks, a cache state can be represented as a vector of n elements c[0, ..., n-1] where c[i] = m if cache block i holds memory block m. Otherwise, if the ith cache block does not hold any memory block we denote this as  $c[i] = \bot$ . At each program point we try to calculate the different possible cache states, which are called as the *set* of cache states.

**Definition 2.3.2 (REACHING CACHE STATES)** The Reaching Cache States at a basic block B of a program, denoted as  $RCS_B$ , is the set of possible cache states when B is reached via any incoming program path.

**Definition 2.3.3 (LIVE CACHE STATES)** The Live Cache States at a basic block B of a program, denoted as  $LCS_B$ , is the set of possible first memory references to cache blocks via any outgoing program path from B.

The idea is: for the low priority task, we try to calculate different possible reaching and live cache states of the whole cache, at different program point and then combining each cache state in any set (reaching/live) with every cache state in the other set (live/reaching), we get a set of useful cache states at each program point. We then report the useful cache states which has the maximum number of useful cache blocks. A cache block is useful at any program point if it will be used again during the execution of the program without its content getting replaced. At any program point P, an element R in the set of reaching cache states represent the memory blocks present in cache when the program point P is reached via some path say p1. And an element L in the set of live cache states represent the memory blocks which will be the first memory references via some path say p2 after the program point P. Hence, for any cache block if the value in R and L is same, then it represents that the content of the cache block will be used again without being replaced in the path p1 followed by p2. The maximum number of useful cache blocks obtained from our approach is lesser than that obtained from [27]. Further, we consider the high priority task and calculates the reaching cache states at the exit of high priority task. Then, by combining the different possible useful cache states at any program point in the low priority task, with the reaching cache states at the exit of the high priority task, we get the set of replaced cache states at any program point. This set of replaced cache states determines the CRPD. The maximum number of replaced cache blocks in the set of replaced cache states at any program point, gives the CRPD.

The equations for the reaching cache states and live cache states are given by.

$$\begin{split} RCS^{IN}_B &= \bigcup_{p \in predecessor(B)} RCS^{OUT}_p \\ RCS^{OUT}_B &= \{r \odot gen_B | r \in RCS^{IN}_B \} \end{split}$$

$RCS_B^{IN}$  and  $RCS_B^{OUT}$  are the reaching cache states at the entry and exit of basic block *B*, respectively.  $gen_B = [m_0,...,m_{n-1}]$  where  $m_i = m$  if m is the *last* memory block in *B* mapping to cache block *i* in *B* and  $\perp$  if no memory block in *B* maps to cache block *i*. The operation  $\odot$  is defined over memory blocks as:  $m \odot m' = \begin{cases} m' & \text{if } m' \neq \perp; \\ m & \text{otherwise.} \end{cases}$

and we assume that any operation  $\odot$  over memory blocks can be applied to cache states (by applying the operation pointwise to its elements).

The equations for calculating the live cache states are given by:

$$\begin{split} LCS_B^{OUT} &= \bigcup_{s \in successor(B)} LCS_s^{IN} \\ LCS_B^{IN} &= \{l \odot gen_B | l \in LCS_B^{OUT} \} \end{split}$$

$LCS_B^{IN}$  and  $LCS_B^{OUT}$  are the live cache states at the entry and exit of basic block *B*, respectively.  $gen_B = [m_0, ..., m_{n-1}]$  where  $m_i = m$  if m is the *first* memory block in *B* mapping to cache block *i* in *B* and  $\perp$  if no memory block in *B* maps to cache block *i*. The  $\odot$  operation is the same as given above.

A fixed point iteration algorithm (as given in [40]) can be used to solve the above sets of equations, to get the reaching/live cache states at each program point. Once the fixed point is reached we set  $RCS_B = RCS_B^{OUT}$  and  $LCS_B = LCS_B^{OUT}$ . The initial assignments of variables in the two cases (reaching/live), is as follows.

$$RCS_B^{IN} = \phi$$

$$RCS_B^{OUT} = gen_B$$

$$LCS_B^{OUT} = \phi$$

$$LCS_B^{IN} = gen_B$$

**Calculating useful cache blocks.** Solving the above equations would results in two sets (reaching and live) at different program points. From the intersection of each element in one set with every element in another set, we obtain a new set, called useful cache set, denoted as  $UCS_B$ . Every element of this set is an array of size equal to total number of cache blocks, and is calculated as follows. If L is a cache state in  $LCS_B$  and R is a cache state in  $RCS_B$  and combination of L and R results in an array U, in  $UCS_B$ , then U is given by:

For cache block  $c_i$  if  $ml_i$  is the memory block in  $c_i$  in L and  $mr_i$  is the memory block in  $c_i$  in R, then U[i] is given by:

$U[i] = \begin{cases} 1 & \text{if } ml_i = mr_i; \\ 0 & \text{otherwise.} \end{cases}$

This way at each program point P, we can get a set, representing the useful cache blocks for different possible program paths through P.

The memory space of high priority task and low priority task are disjoint hence the execution of high priority task after preemption at any program point P might replace the useful cache blocks of low priority task at P. However, it may happen that not all of these useful blocks are replaced by the high priority task. Therefore it is also necessary to know the cache state at the finish of the high priority task. Hence, a set of final cache state (*FCS*) is calculated for the high priority task. The FCS is obtained from the RCS of high priority task, at the last block (exit block). If R is a cache state in  $RCS_{exit}$  then a state F in FCS corresponding to R can be calculated as below.

$F[i] = \begin{cases} 1 & \text{if cache block } c_i \text{ in } \mathbf{R} \text{ is nonempty }; \\ 0 & \text{otherwise.} \end{cases}$

Once we have both the UCS (at every point of low priority task) and FCS (RCS at exit of high priority task), we can calculate the CRPD at any point P in low priority task in the following way:

For every U in  $UCS_B$  at program point P and from every F in FCS find the number of useful cache blocks in U replaced by F, and report the maximum number of replaced useful cache blocks achieved through any combination of U and F. A useful cache block  $c_i$  is replaced, if both U[i] and F[i] are equal to one.

Hence by finding the maximum number of replaced useful cache blocks at any program point in low priority task, we can achieve a tight bound on CRPD.

It may appear that our approach can face exponential blowup of cache states. But this is not common in general case, because due to the limited size of the cache, different paths get merge at various basic blocks. A naive example to show this would be to assume that there is a basic block B, which has instructions mapping to all the cache blocks. Thus even if  $RCS_B^{IN}$  has more than one elements but  $RCS_B^{OUT}$  would only have a single element. This results in reduction of the exponential nature of the approach. In fact our results prove this fact and the execution time of the fixed point algorithm in general is not so high in all our test cases.

### 2.4 An Example

For better understanding, let us work out an example to calculate the CRPD with our technique. Consider the control flow graph (CFG) shown in Figure 2.3. The CFG consists of four basic blocks (B1-B4) and six memory blocks (m0-m6) within a loop with single if-then-else. A direct mapped cache with four cache blocks (c0-c3) is assumed. As per the CFG the  $gen_B$  of various basic blocks are as follows.

Figure 2.3: An example control flow graph

```

gen_{B1} = [m0, \bot, \bot, \bot]

gen_{B2} = [\bot, m1, m2, m3]

gen_{B3} = [m4, m5, \bot, \bot]

gen_{B4} = [\bot, \bot, m6, \bot]

```

The various iterations of the fixed-point iteration algorithm to calculate the  $RCS_B$  are shown in Table 2.1. It is important to note here that some cache states might get subsumed by other cache states and are avoided for further consideration in the fixed point iteration algorithm. A cache state c' is subsumed by another cache state c if  $\forall i \ c'[i] = c[i] \ or \ c'[i] = \bot$ . Thus, in iteration 4 for basic block B3,

$$RCS_{B3}^{IN} = \{[m0, m1, m6, m3], [m0, m5, m6, \bot]\}$$

| Iteration | Basic Block | RCS <sup>IN</sup>                          | $RCS^{OUT}$                                |

|-----------|-------------|--------------------------------------------|--------------------------------------------|

| 1         | B1          | Ø                                          | $[m0, \bot, \bot, \bot]$                   |

|           | B2          | Ø                                          | $[\perp, m1, m2, m3]$                      |

|           | B3          | Ø                                          | $[m4, m5, \bot, \bot]$                     |

|           | B4          | Ø                                          | $[\perp, \perp, m6, \perp]$                |

| 2         | B1          | $[\perp, \perp, m6, \perp]$                | $[m0, \bot, m6, \bot]$                     |

|           | B2          | $[m0, \bot, \bot, \bot]$                   | [m0, m1, m2, m3]                           |

|           | B3          | $[m0, \bot, \bot, \bot]$                   | $[m4, m5, \bot, \bot]$                     |

|           | B4          | $[\bot, m1, m2, m3], [m4, m5, \bot, \bot]$ | $[\perp, m1, m6, m3], [m4, m5, m6, \perp]$ |

| 3         | B1          | $[\perp, m1, m6, m3], [m4, m5, m6, \perp]$ | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     |

|           | B2          | $[m0, \bot, m6, \bot]$                     | [m0, m1, m2, m3]                           |

|           | B3          | $[m0, \bot, m6, \bot]$                     | $[m4, m5, m6, \bot]$                       |

|           | B4          | $[m0, m1, m2, m3], [m4, m5, \bot, \bot]$   | $[m0, m1, m6, m3], [m4, m5, m6, \bot]$     |

| 4         | B1          | $[m0, m1, m6, m3], [m4, m5, m6, \bot]$     | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     |

|           | B2          | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     | [m0, m1, m2, m3]                           |

|           | B3          | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     | [m4, m5, m6, m3]                           |

|           | B4          | $[m0, m1, m2, m3], [m4, m5, m6, \bot]$     | $[m0, m1, m6, m3], [m4, m5, m6, \bot]$     |

| 5         | B1          | $[m0, m1, m6, m3], [m4, m5, m6, \bot]$     | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     |

|           | B2          | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     | [m0, m1, m2, m3]                           |

|           | B3          | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     | [m4, m5, m6, m3]                           |

|           | B4          | [m0, m1, m2, m3], [m4, m5, m6, m3]         | [m0, m1, m6, m3], [m4, m5, m6, m3]         |

| 6         | B1          | [m0, m1, m6, m3], [m4, m5, m6, m3]         | [m0, m1, m6, m3], [m0, m5, m6, m3]         |

|           | B2          | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     | [m0, m1, m2, m3]                           |

|           | B3          | $[m0, m1, m6, m3], [m0, m5, m6, \bot]$     | $\left[m4, m5, m6, m3\right]$              |

|           | B4          | [m0, m1, m2, m3], [m4, m5, m6, m3]         | [m0, m1, m6, m3], [m4, m5, m6, m3]         |

| 7         | B1          | [m0, m1, m6, m3], [m4, m5, m6, m3]         | [m0, m1, m6, m3], [m0, m5, m6, m3]         |

|           | B2          | [m0, m1, m6, m3], [m0, m5, m6, m3]         | [m0, m1, m2, m3]                           |

|           | B3          | [m0, m1, m6, m3], [m0, m5, m6, m3]         | [m4, m5, m6, m3]                           |

|           | B4          | [m0, m1, m2, m3], [m4, m5, m6, m3]         | [m0, m1, m6, m3], [m4, m5, m6, m3]         |

Table 2.1: Computation of  $RCS_B$  for the CFG in Figure 2.3.

and  $gen_{B3} = [m4, m5, \bot, \bot]$ . Therefore,

$$RCS_{B3}^{OUT} = \{ [m4, m5, m6, m3], [m4, m5, m6, \bot] \}$$

However,  $[m4, m5, m6, \bot]$  is subsumed by [m4, m5, m6, m3] and hence  $RCS_{B3}^{OUT} = \{[m4, m5, m6, m3]\}$ . The  $LCS_B$  can also be calculated in the similar fashion and are as follows at the fixed point.

$$LCS_{B1} = \{[m0, m1, m2, m3], [m4, m5, m6, m3]\}$$

$$LCS_{B2} = \{[m0, m1, m6, m3], [m0, m5, m6, m3]\}$$

$$LCS_{B3} = \{[m0, m1, m6, m3], [m0, m5, m6, m3]\}$$

$$LCS_{B4} = \{[m0, m1, m2, m3], [m0, m5, m6, m3]\}$$

Given LCS and RCS for each basic block, the useful cache sets (UCS) can be computed.

$$UCS_{B1} = \{[1, 1, 0, 1], [0, 0, 1, 1], [0, 1, 1, 1], [1, 0, 0, 1]\}$$

$$UCS_{B2} = \{[1, 1, 0, 1], [1, 0, 0, 1]\}$$

$$UCS_{B3} = \{[0, 1, 1, 1], [0, 0, 1, 1]\}$$

$$UCS_{B4} = \{[1, 1, 0, 1], [1, 0, 1, 1], [0, 1, 1, 1], [0, 0, 0, 1]\}$$

Now let us illustrate the advantage of our technique over separate analysis of each cache block [27, 28]. In that case,  $RCS_B$  and  $LCS_B$  have a set of reaching memory blocks for each cache block as shown in the following.

$$RCS_{B1} = [\{m0\}, \{m1, m5\}, \{m6\}, \{m3\}]$$

$$RCS_{B2} = [\{m0\}, \{m1\}, \{m2\}, \{m3\}]$$

$$RCS_{B3} = [\{m4\}, \{m5\}, \{m6\}, \{m3\}]$$

$$RCS_{B4} = [\{m0, m4\}, \{m1, m5\}, \{m6\}, \{m3\}]$$

$$LCS_{B1} = [\{m0, m4\}, \{m1, m5\}, \{m2, m6\}, \{m3\}]$$

$$LCS_{B2} = [\{m0\}, \{m1, m5\}, \{m6\}, \{m3\}]$$

$$LCS_{B3} = [\{m0\}, \{m1, m5\}, \{m6\}, \{m3\}]$$

$$LCS_{B4} = [\{m0\}, \{m1, m5\}, \{m2, m6\}, \{m3\}]$$

Let us consider  $RCS_{B4}$ . From separate analysis of cache blocks, we infer that  $RCS_{B4}$  can have four possible cache states: [m0, m1, m6, m3], [m0, m5, m6, m3], [m4, m1, m6, m3], and [m4, m5, m6, m3]. However, our combined analysis of cache blocks infers that only two of these cache states are feasible. The identification of these infeasible cache states leads to decrease in the number of useful cache blocks (computed via intersection of  $RCS_B$  and  $LCS_B$ ) at each program point. For example, our analysis infers at most 3 useful cache blocks for both B1 and B4 (Even though each of the cache blocks is useful along some path, all 4 of them are not useful along any path). Whereas, with separate analysis of cache blocks, we get 4 useful cache blocks for B1 and B4.

Note that we also maintain the Final Cache States (FCS) of the high priority task as a set of boolean

| Program | Description                                |

|---------|--------------------------------------------|

| matsum  | Summation of two $100 \times 100$ matrices |

| qsort   | Non-recursive quick sort algorithm         |

| crc     | Cyclic redundancy check program            |

| sqrt    | Square root calculation                    |

| eqntott | Drawn from SPEC'92 integer benchmarks      |

| des     | Data Encryption Standard                   |

| whet    | Whetstone benchmark                        |

| ssearch | Pratt-Boyer-Moore string search            |

| math    | Basic math within nested loop              |

Table 2.2: Description of benchmark programs.

vectors. This leads to further accuracy in CRPD analysis. For example, suppose we compute  $FCS = \{[1, 0, 1, 0], [1, 1, 0, 0]\}$ . This will allow our analysis to estimate the number of replaced cache blocks to be 2 leading to even tighter CRPD estimation.

### 2.5 Experimental Results

In our experiments we used nine different benchmarks (mostly from [32] and [22]) to present the accuracy and performance of our technique. Table 2.2 gives the description of benchmarks used by us. We used the Simplescalar architectural simulation platform [10] in the experiments. All the benchmarks are compiled to Simplescalar assembly language with modified *gcc*. A CRPD analyzer written by us accepts the assembly language code, identifies the basic blocks out of it and constructs the control flow graph (CFG) from it. Given the CFG for the low-priority and high-priority task, our analyzer implements a fixed point iteration algorithm to calculate the RCS and LCS at various program points taken at the exit of each basic block. The calculated RCS and LCS are used to compute the useful cache states (UCS) at various program points and finally the intersection of UCS and final cache states (FCS from high-priority task) is used to determine the CRPD.

We present three types of results to present the accuracy and performance of our technique, and at the same time comparing it with the set based approach.

First we present the results for CRPD analysis. Table 2.3 shows the CRPD values in terms of number of cache blocks for a direct mapped instruction cache with 32 cache blocks. matsum, eqntott, and sqrt are used as higher priority tasks and all others as low priority tasks. The results for actual (A in Table 2.3), set based or separate [27] (S in Table 2.3), and combined or our (C in Table 2.3), analysis of

| LP Task | HP Task |    |    |    |       |    |      |    |    |  |

|---------|---------|----|----|----|-------|----|------|----|----|--|

|         | matsum  |    |    | e  | qntot | t  | sqrt |    |    |  |

|         | Α       | C  | S  | Α  | C     | S  | Α    | C  | S  |  |

| qsort   | 19      | 20 | 24 | 16 | 22    | 28 | 18   | 19 | 26 |  |

| crc     | 17      | 17 | 18 | 17 | 21    | 22 | 18   | 19 | 20 |  |

| ssearch | 19      | 22 | 23 | 19 | 25    | 27 | 21   | 22 | 25 |  |

| des     | 22      | 23 | 24 | 21 | 24    | 26 | 22   | 22 | 25 |  |

| whet    | 20      | 21 | 22 | 20 | 25    | 25 | 23   | 23 | 24 |  |

| math    | 18      | 22 | 23 | 20 | 25    | 27 | 20   | 22 | 25 |  |

Table 2.3: Accuracy of CRPD analysis for a 32-block cache. A stands for actual value(by simulation), C stands for combined analysis of all cache blocks and S stands for separate analysis of each cache block.

| Task    | Combined | Separate |

|---------|----------|----------|

| matsum  | 23       | 24       |

| eqntott | 26       | 28       |

| sqrt    | 23       | 26       |

Table 2.4: Maximum number of cache blocks used by high priority task for a 32-block cache.

all cache blocks are presented. The maximum number of cache blocks used by high-priority tasks are shown in Table 2.4. Our analysis produces much tighter bound on CRPD, with improvement as high as 37% for some benchmarks.

Second we show the maximum number of useful cache blocks of the low-priority task at any program point in Table 2.5. In Table 2.5, A, C and S have their usual meaning as described above. Again our technique results in tighter values for useful cache blocks than the separate analysis of [27].

Third in Table 2.6 we show the number of preemption points (basic blocks) at which useful cache block count differs in our combined and separate analysis as well as the maximum of these differences. It should be noted that even though the maximum number of useful cache blocks over all preemption points

| Task    | # of Cache Blocks |   |    |    |    |    |    |    |    |    |    |    |

|---------|-------------------|---|----|----|----|----|----|----|----|----|----|----|

|         | 8                 |   | 16 |    | 32 |    |    | 64 |    |    |    |    |

|         | Α                 | С | S  | Α  | C  | S  | Α  | C  | S  | Α  | C  | S  |

| qsort   | 1                 | 1 | 1  | 14 | 14 | 14 | 26 | 28 | 32 | 51 | 62 | 63 |

| crc     | 2                 | 2 | 2  | 12 | 12 | 12 | 22 | 26 | 26 | 47 | 48 | 48 |

| ssearch | 2                 | 6 | 6  | 14 | 15 | 16 | 29 | 31 | 31 | 59 | 59 | 59 |

| des     | 0                 | 0 | 0  | 6  | 12 | 12 | 30 | 30 | 30 | 60 | 60 | 64 |

| whet    | 0                 | 1 | 2  | 10 | 11 | 14 | 29 | 29 | 29 | 59 | 59 | 59 |

| math    | 3                 | 4 | 5  | 10 | 14 | 16 | 27 | 30 | 31 | 63 | 63 | 64 |

Table 2.5: Maximum number of useful cache blocks of the low-priority task at any program point for different cache sizes. A stands for actual value(by simulation), C stands for combined analysis of all cache blocks and S stands for separate analysis of each cache block.

| Task    | # of Cache Blocks |      |    |      |    |      |    |      |  |  |

|---------|-------------------|------|----|------|----|------|----|------|--|--|

|         | 8                 |      | 1  | 6    | 3  | 32   | 6  | 64   |  |  |

|         | BB                | Diff | BB | Diff | BB | Diff | BB | Diff |  |  |

| qsort   | 0                 | 0    | 1  | 1    | 2  | 4    | 1  | 1    |  |  |

| crc     | 2                 | 1    | 0  | 0    | 0  | 0    | 0  | 0    |  |  |

| ssearch | 0                 | 0    | 2  | 2    | 0  | 0    | 0  | 0    |  |  |

| des     | 0                 | 0    | 0  | 0    | 9  | 2    | 47 | 15   |  |  |

| whet    | 7                 | 1    | 11 | 4    | 0  | 0    | 0  | 0    |  |  |

| math    | 2                 | 1    | 4  | 5    | 2  | 3    | 1  | 1    |  |  |

Table 2.6: Comparison of combined and separate analysis for low-priority task. BB denotes the number of basic blocks at which useful cache block count differs and Diff denotes the maximum of these differences.

| Task    | # of Cache Blocks |       |       |        |  |  |  |  |  |  |

|---------|-------------------|-------|-------|--------|--|--|--|--|--|--|

|         | 8                 | 16    | 32    | 64     |  |  |  |  |  |  |

| qsort   | 0.003             | 0.004 | 0.022 | 0.082  |  |  |  |  |  |  |

| crc     | 0.016             | 0.015 | 0.164 | 65.663 |  |  |  |  |  |  |

| ssearch | 0.007             | 0.025 | 1.613 | 16.168 |  |  |  |  |  |  |

| des     | 0.010             | 0.022 | 0.525 | 55.329 |  |  |  |  |  |  |

| whet    | 0.005             | 0.023 | 4.189 | 89.858 |  |  |  |  |  |  |

| math    | 0.013             | 0.059 | 1.061 | 8.414  |  |  |  |  |  |  |

Table 2.7: Time to compute useful cache blocks for low-priority task in sec.

of low-priority task (shown in Table 2.5) might be the same in both analysis techniques, the estimated number of useful cache blocks in individual preemption points of low-priority task may be different.

We have used pentium 4, 1.7 GHz CPU with 1 GB memory for our experiments. For all benchmarks it takes less than 1.5 minute, to calculate the useful cache states. Also, the cache states are quite less as compared to expected exponential blow up of cache states. For e.g., for qsort with 40 basic blocks and 490 memory blocks and 8 cache blocks, the total number of live cache states are 68 and reaching cache states are 69. Table 2.7 shows the time taken by our analyzer to compute the UCS for all basic blocks in the low-priority task.

### 2.6 Optimization Using Binary Decision Diagrams

In our approach, we represent the cache states at a program point in a task as a set of tuples (where each tuple denotes an assignment of memory blocks to the cache blocks). To avoid an exponential blow-up in the space consumption we can represent the possible cache states at any program point implicitly as a Binary Decision Diagram (BDD) [9, 8]. A BDD is an efficient data structure for representing

| 0        | <b>;</b> 1 | $c_2$    |          |  |  |

|----------|------------|----------|----------|--|--|

|          | $x_1 x_2$  |          | $y_1y_2$ |  |  |

| $M_{a1}$ | 01         | $M_{a2}$ | 01       |  |  |

| $M_{b1}$ | 10         | $M_{b2}$ | 10       |  |  |

| $M_{c1}$ | 11         | $M_{c2}$ | 11       |  |  |

Table 2.8: Possible encoding of memory blocks into boolean form.

a propositional logic formula. In this section we show how to translate our approach to use BDD. Although we have implemented our approach using BDD but not much gain was obtained in terms of memory usage. The possible factors for this are discussed later in the section.

#### **Binary Decision Diagram (BDD)**

Binary decision diagrams(BDD) [9, 8] are an abstract representation of boolean functions. An Ordered BDD (OBDD) can be obtained from a BDD, by imposing some of the restriction on the ordering of the variables used by the boolean function, such that the resulting form is canonical. An OBDD is a directed acyclic graph with internal nodes corresponding to the variables over which the function is defined and the terminal nodes labelled by the function values 0 and 1.

#### Encoding of our approach into boolean Form

For the purpose of using OBDD we first have to encode our variables and structures into boolean form. Let us assume we have two cache blocks say  $c_1$  and  $c_2$ , and let the memory blocks (only these are mapped)  $M_{a1}$ ,  $M_{b1}$  and  $M_{c1}$  gets mapped to cache block  $c_1$  and memory blocks (only these are mapped)  $M_{a2}$ ,  $M_{b2}$  and  $M_{c2}$  gets mapped to cache block  $c_2$ . We can encode the mapping of memory blocks to cache block in boolean form. For eg. let us have two boolean variables representing the memory block residing in each cache block, further assume  $x_1$  and  $x_2$  represent the memory block residing in cache block  $c_2$ . We can encode the memory block residing in cache block in boolean values. A possible set of encoding is shown in Table 2.8.

The 00 encoding is used to represent an empty cache state. Now for instance at any program point P, let the set of cache states is  $\{ < M_{a1}, M_{a2} >, < M_{c1}, M_{a2} > \}$ . Hence this set of cache states can be represented as a boolean function F (which is a disjoint sum of product cover) of the form.

$$F = \bar{x_1} x_2 \bar{y_1} y_2 + x_1 x_2 \bar{y_1} y_2 \tag{2.1}$$

where each product term represents the possible cache state at the program point P. The function F can then be reduced to

$$F = x_2 \bar{y_1} y_2 \tag{2.2}$$

Thus the representation of cache states as boolean function can be used for a more compact representation.

#### **Our representation**

For our purpose we assign each basic block with four boolean functions corresponding to  $RCS_B^{IN}$ ,  $RCS_B^{OUT}$ ,  $LCS_B^{IN}$  and  $LCS_B^{OUT}$ , which are stored as BDDs. The previously described LCS and RCS analysis can then be done by manipulating these boolean functions. The initial values for  $RCS_B^{OUT}$  and  $LCS_B^{IN}$  can be obtained by just encoding the cache state  $gen_B$  in the same way as shown above. The recursive equations for the RCS and LCS analysis can then be modified in the following way.

- The union operation (∪) for RCS or LCS analysis would just become the + (boolean OR) operations over various boolean functions representing the different RCS<sub>p</sub><sup>OUT</sup> or the LCS<sub>s</sub><sup>IN</sup> respectively.

- The  $\odot$  operation for RCS analysis can be represented in boolean form in the following way.  $RCS_B^{OUT} = f \odot gen_B \mid f$  is a boolean function for  $RCS_B^{IN}$

$f \odot gen_B$  can be calculated as follows: Let  $gen_B = \{c_1, c_2, ..., c_i\}$  and let each memory block mapping to a cache block  $c_i$  is encoded with j variables  $x_{i1}, ..., x_{ij}$ , hence  $c_i$  would have a particular set of values(0 or 1) coming from each boolean variable, depending upon the encoding of memory block which is present in the cache block. Now for each non-empty cache block  $c_i$  (i.e. at least one of  $x_{i1}, ..., x_{ij}$  has a non-zero value), do the following:

For each variable  $x_{ik}$  first convert all the instances of  $x_{ik}$  in f into don't-care and then do the boolean "and" of f with  $x_{ik}$  if  $x_{ik}=1$  in  $c_i$ , otherwise do the boolean "and" of f with  $x_{ik}$  if  $x_{ik}=0$  in  $c_i$ . To reduce a variable x into don't-care in a boolean function f, first f is projected with x=0 and then it is projected with x=1. A boolean "Or" for the two projection results in a new function f" from f with x reduced to don't-care.

Let us consider an example with two cache blocks to show this.

Let at any instance  $f = \bar{x_1}x_2y_1\bar{y_2} + x_1\bar{x_2}y_1y_2$  and let the  $gen_B$  be  $\{<01,00>\}$ , this means that the

cache block 2 is empty, therefore the  $f \odot gen_B$  can be calculated in the following way: first take  $x_1$ , convert all instances of  $x_1$  in f into don't-care, hence f will become;

$f = x_2 y_1 \bar{y_2} + \bar{x_2} \bar{y_1} y_2$

and now do boolean "and" of f with  $\bar{x_1}$  as the value of  $x_1$  in  $gen_B$  is 0. hence the f would become  $f = \bar{x_1}x_2y_1\bar{y_2} + \bar{x_1}\bar{x_2}\bar{y_1}y_2$

following the same terminology for  $x_2$  the resulting f would be

$f = \bar{x_1} x_2 y_1 \bar{y_2} + \bar{x_1} x_2 \bar{y_1} y_2$

The  $\odot$  operation for the LCS analysis can also be represented in the same way as in RCS analysis as shown above.

#### How does BDD serves us

The above manipulation of boolean functions is done through OBDD. For this purpose the boolean functions used by us are represented as nodes of OBDD and the transformation functions applied to the boolean functions are then treated as manipulation of the subtree, rooted at the node representing those functions, in a OBDD. Although the OBDD representation of the boolean function may have size exponential in the number of variables, many useful functions have more compact representation. Since, in our approach we store all possible cache states (corresponding to different paths) at a program point, therefore our technique might possibly suffer from exponential blow up. The use of OBDDs to represent intermediate functions representing various cache states might prove helpful as OBDD could represent many functions compactly.

We have used the CUDD package (Release 2.3.1)[15] by University of Colorado in our implementation. The CUDD package provides a large set of functions to manipulate Binary Decision Diagrams. The CUDD package is used as a black box i.e. only the exported functions of the package are used. Although our implementation proves the accuracy of encoding our approach using OBDD but the memory usage can not be compared directly, as the CUDD package itself uses a large amount of memory to maintain its various data structures. Table 2.9 compares the maximum number of Reaching and Live cache states obtained via normal implementation with the maximum number of nodes in the BDDs during the execution of fixed point iteration algorithm using CUDD, for 8 and 16 cache blocks. The columns *LCS* and *RCS* represent the maximum number of Live and Reaching cache state obtained in normal implementation. And the columns *LCS nodes* and *RCS nodes* represent the maximum number of nodes used in BDD

| Benchmark | Basic Blocks | LCS |     | RCS |     | LCS Nodes |       | RCS Nodes |       |

|-----------|--------------|-----|-----|-----|-----|-----------|-------|-----------|-------|

|           |              | 8   | 16  | 8   | 16  | 8         | 16    | 8         | 16    |

| qsort     | 40           | 68  | 95  | 69  | 109 | 2661      | 5363  | 2505      | 5171  |

| des       | 117          | 236 | 411 | 257 | 469 | 11796     | 42434 | 12239     | 29653 |

| whet      | 52           | 175 | 506 | 136 | 367 | 5763      | 14676 | 4889      | 11081 |

| ssearch   | 76           | 202 | 479 | 247 | 467 | 6366      | 14995 | 7079      | 17101 |

| crc       | 66           | 219 | 356 | 186 | 306 | 6253      | 14755 | 5643      | 14008 |

| math      | 22           | 99  | 702 | 81  | 869 | 1773      | 8015  | 1681      | 9526  |

Table 2.9: Comparison of memory usage between normal and BDD representation of cache states

during the execution of fixed point iteration algorithm. It can be observed that a large number of nodes in BDD are maintained. The size of BDD depends upon a lot on number of variables and their ordering, hence a proper encoding of memory blocks into boolean variables and their ordering can help in better performance of OBDDs.

### 2.7 Conclusion

The determination of Cache Related Preemption Delay (CRPD) is important for the schedulability of tasks in real-time system. CRPD is the additional delay incurred by the low-priority task owing to additional cache misses introduced by preemption. We have provided an accurate analysis of CRPD by maintaining the cache states possible at any program point via various paths in a program. Further we have considered both low and high priority tasks in our approach. Our experiments show that our approach results in tighter bound on CRPD than the existing approaches.

One possible concern regarding our analysis technique is a blow-up in space consumption. As observed in the previous section, none of our benchmarks suffered from an exponential space blow-up due to our decision to represent cache states (instead of the content of each cache block separately).

BDD can be used to reduce the space consumption. To use BDD we have to encode our approach into a boolean form (a way to do this is presented in previous sections). A proper encoding and ordering of boolean variables is very important to derive full advantage from BDD. Although we have implemented our approach using BDD but we have not tried optimization using various encodings and orderings, since none of our benchmarks suffered with space blow ups.

# **Chapter 3**

# **Timing Analysis of Loop Behaviors**

### 3.1 Introduction

A real-time system requires that some timing guarantee should be given for the tasks running in it. A bound on the time, taken by an application can be provided by static analysis of programs in the form of worst case execution time (WCET) of the program. The problem of determining WCET of a program by static analysis methods has to be solved at the following two levels [53]: (1) Programming language level, and (2) Micro-architectural level, to take into account the effect of features such as pipeline, cache and branch prediction [36, 32, 29]. There are three main approaches for calculation of WCET at the programming language level: *path based, tree based* and *implicit path enumeration technique (IPET)*. In *path based* approach, the longest path is discovered from the start to end of a program. In a *tree-based approach* the final WCET is generated by a bottom-up traversal of a tree, generally corresponding to a parse tree of the program, using rules defined for each type of compound program statement to determine the execution time of the statement. In *IPET*, program flow and low-level execution time are modelled using arithmetic constraints

The previous chapter presented an analysis of caches to determine the delay caused in the execution of a task due to preemption (by higher priority task). In this chapter we present a program path analysis technique to determine the WCET of loops in a task. In particular, we try to identify certain infeasible paths <sup>1</sup> spanning across loop iterations, which are hard to detect via existing path analysis techniques and

<sup>&</sup>lt;sup>1</sup>A path (from start to end) in a program is referred as infeasible (or false) if it can never be executed regardless of the input data [34].

then use the infeasible path information to get a tight bound on the WCET of a loop. We first describe the types of infeasible paths along with some techniques on how to detect them. We then present our technique to detect infeasible paths and use the infeasible path information to give a bound on the WCET of a loop in a program.

#### **3.1.1** Types of Infeasible Paths

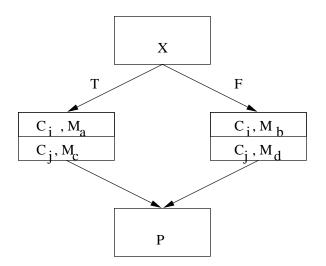

Figure 3.1: Infeasible paths due to branch correlation

The knowledge about infeasible paths in a program can be used to give a tighter bound on WCET. There could be various types of infeasible paths possible in a program. There could be infeasible paths because of the correlation between branches. For example, in Figure 3.1,  $\langle 3, 4, 5, 6 \rangle$  is an infeasible path because  $\langle 3, 4 \rangle$  implies that the outcome of branch at line number 3 is true therefore the outcome of branch at line number 5 can not be true, hence  $\langle 5, 6 \rangle$  can not be executed. The idea in such types of infeasible paths is to detect the effect of outcome of a branch on the outcome of another branch. Another type of infeasible paths can occur due to the effect of assignment of a variable on a branch. For e.g. Figure 3.2 shows how the assignment of variable *v* to value 5 makes  $\langle 3, 4, 6 \rangle$  an infeasible path. Detection of such types of branch correlation and assignment effect based infeasible paths has been studied in [6, 23].

Figure 3.2: Infeasible paths due to effect of assignment on branch

There could exists a different type of branch correlated infeasible paths where the outcome of a

```

1 if u = 0 then

2 v := 1;

3 if w = 0 then

4 x := 1;

5 if (u = 0 and w = 0) then

6 y := 1

7 else y := 2;

```

Figure 3.3: Correlation of a branch outcome with a conjunction of other branches

```

1 sumeven := 0;

2 for (j:=0; j <= limit; j++)

3 {

4 if (j % 2 == 0) then

5 sumeven = sumeven + j;

6 }

```

Figure 3.4: Infeasible paths across iteration

branch is dependent upon outcome of more than one branch visited earlier in the program flow. For example in Figure 3.3 the outcome of the branch at line 5 depends upon the outcome of branches at lines 1 and 3. Therefore,  $\langle 1, 2, 3, 4, 5, 7 \rangle$  is an infeasible path. However, such types of infeasible paths are hard to detect because they can not be obtained by considering the direct effect of one branch on another, rather they require the combined knowledge about the outcomes of several branches. In Figure 3.3 it is easy to determine the infeasible path  $\langle 1, 2, 3, 5, 6 \rangle$  because it could be easily reasoned out that the falsehood of the branch condition in line 3 forces the condition in line 5 to be false.

Other type of infeasible paths which can be present in a program include ones that span over multiple iterations of a loop. For example consider the code to calculate the sum of even numbers, as shown in Figure 3.4. If the path  $\langle 3, 4, 5, 6 \rangle$  is taken in some iteration of the loop then it is not possible to take it again in the consecutive iteration. Information about such types of infeasible paths (which span over multiple iterations) can be utilized to give a tighter bound on the timing of the loops. In this chapter we present our technique which uses information about such types of *iteration-spanning* infeasible paths to get a tight bound on the WCET of a loop. From now on we will use the term *iteration-spanning infeasible paths*.

#### **3.2 Infeasible Path Detection Technique**