# FABRICATION OF ULTRA-SHALLOW JUNCTIONS AND ADVANCED GATE STACKS FOR ULSI TECHNOLOGIES USING LASER THERMAL PROCESSING

CHONG YUNG FU

NATIONAL UNIVERSITY OF SINGAPORE 2003

# FABRICATION OF ULTRA-SHALLOW JUNCTIONS AND ADVANCED GATE STACKS FOR ULSI TECHNOLOGIES USING LASER THERMAL PROCESSING

#### CHONG YUNG FU

(B. A. Sc. (First Class Hons.), NTU)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2003

#### **ACKNOWLEDGEMENTS**

The author hereby wishes to express his utmost gratitude to the following people, without whom the completion of this project would not be possible. They are:

- 1. Dr. Pey Kin Leong, project supervisor. He is greatly indebted to Dr. Pey for his patience, encouragement and invaluable guidance throughout the course of this work.

- A/Prof. Andrew Wee Thye Shen of the Department of Physics, National University of Singapore (NUS), project co-supervisor. He is especially grateful to Dr. Wee for his continuous support and interest in this project.

- Dr. Lap Chan and Dr. Alex See of Chartered Semiconductor Manufacturing Ltd., industrial project advisors. He is most thankful to Dr. Chan and Dr. See for the support and training that they had provided.

- 4. Dr. Hans J. Gossmann of Axcelis Technologies, USA. He would like to express his deepest appreciation to Dr. Gossmann for his invaluable advice and helpful discussions.

- A/Prof. Michael O. Thompson of Cornell University, USA. He wishes to express his

most sincere gratitude to Dr. Thompson for his invaluable advice and rewarding

discussions.

- 6. Dr. Lu Yong Feng and Dr. Song Wen Dong of Data Storage Institute (DSI), Singapore, who had provided the resources and knowledge for conducting experiments using the 248 nm excimer laser.

- 7. Mr. Liu Rong of the Department of Physics, NUS. He acknowledges Mr. Liu for his help in the secondary ion mass spectrometric analysis.

- 8. Mr. Tung Chih Hang and Dr. Gopal Krishnan of the Institute of Microelectronics (IME),

- Singapore, who had provided technical support on transmission electron microscopy.

- 9. Dr. T. Osipowicz for his support on Rutherford backscattering spectrometry.

- 10. Dr. Somit Talwar of Verdant Technologies, USA, who had provided the resources for the laser thermal processing of device wafers.

- 11. Dr. G. Hobler of Vienna University of Technology, who had provided the software on the binary collision code implant simulator (IMSIL).

- 12. Dr. Rajiv K. Singh of the University of Florida, who had provided the software on the simulation of laser interaction with materials (SLIM).

Last but not least, the author would also like to thank all those people (whose names are not listed above) that have contributed to this work in one way or another.

## TABLE OF CONTENTS

|     |         | Section                                                      | Page |

|-----|---------|--------------------------------------------------------------|------|

| AC  | KNOW    | LEDGEMENTS                                                   | i    |

| SUI | MMAR    | Y                                                            | vii  |

| LIS | T OF T  | ABLES                                                        | ix   |

| LIS | T OF F  | IGURES                                                       | X    |

|     |         |                                                              |      |

| CH  | APTER   | 1 INTRODUCTION                                               | 1    |

| 1.1 | Backg   | round                                                        | 1    |

| 1.2 | Scope   | of the Project                                               | 4    |

| 1.3 | Object  | tives                                                        | 5    |

| 1.4 | Organi  | ization of the Thesis                                        | 6    |

|     |         |                                                              |      |

| CH  | APTER   | 2 LITERATURE REVIEW                                          | 8    |

| 2.1 | Introdu | uction                                                       | 8    |

| 2.2 | Ion Im  | plantation                                                   | 8    |

| 2.3 | Rapid   | Thermal Annealing                                            | 11   |

|     | 2.3.1   | Transient enhanced diffusion                                 | 12   |

| 2.4 | Laser'  | Thermal Processing                                           | 14   |

|     | 2.4.1   | Excimer lasers                                               | 14   |

|     | 2.4.2   | Light absorption mechanism and optical properties of silicon | 14   |

|     | 2.4.3   | Heat flow calculations                                       | 17   |

|     | 2.4.4   | Laser irradiation of an a-Si overlayer on c-Si               | 22   |

|     | 2.4.5   | Dopant incorporation during rapid solidification             | 24   |

| 2.5 | Altern  | ative Approaches to Form Ultra-shallow Junctions             | 26   |

| 2.6 | Carrie  | r Depletion in Polycrystalline Silicon Gates                 | 27   |

| 2.7 | Summ    | ary                                                          | 30   |

| CHA | APTER   | 3 EXPERIMENTAL                                                           | 31 |

|-----|---------|--------------------------------------------------------------------------|----|

| 3.1 | Introdu | uction                                                                   | 31 |

| 3.2 | Simula  | ntion Studies                                                            | 31 |

| 3.3 | Forma   | tion of Ultra-shallow Junctions                                          | 32 |

|     | 3.3.1   | Ion implantation                                                         | 32 |

|     | 3.3.2   | Dopant activation                                                        | 32 |

| 3.4 | Gate S  | stacks With a TiN/Ti Capping Layer                                       | 33 |

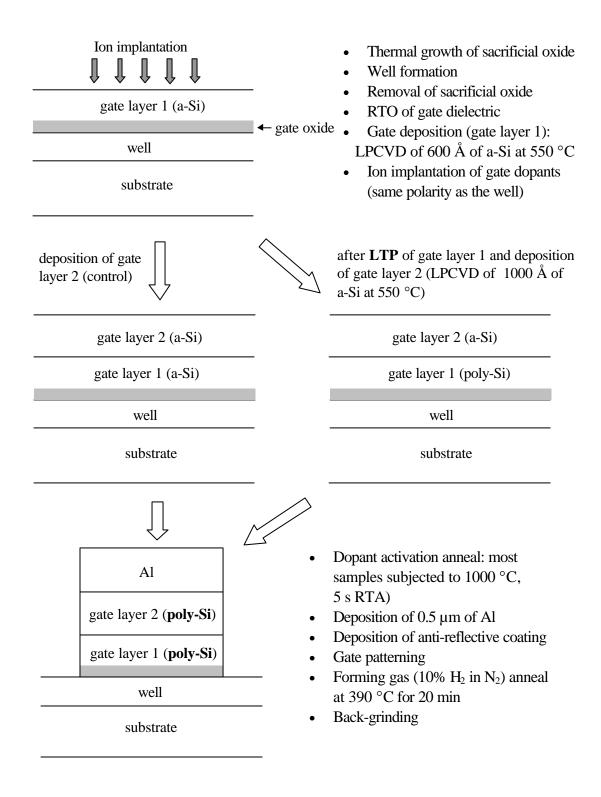

| 3.5 | Advan   | aced Gate Stacks/Capacitor Structures                                    | 34 |

| 3.6 | Materi  | als Characterization                                                     | 37 |

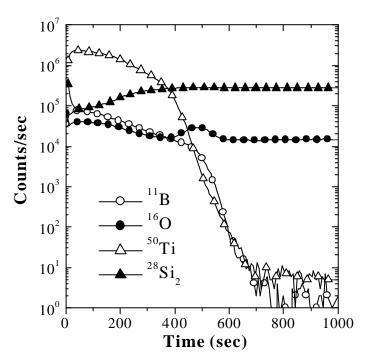

|     | 3.6.1   | Secondary ion mass spectrometry                                          | 37 |

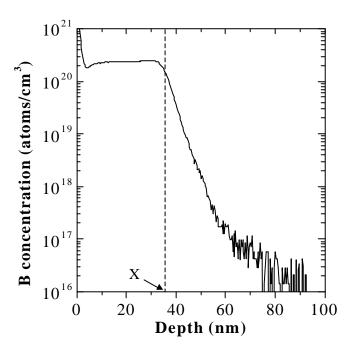

|     |         | 3.6.1.1 Determination of junction depth (from SIMS) after LTP            | 37 |

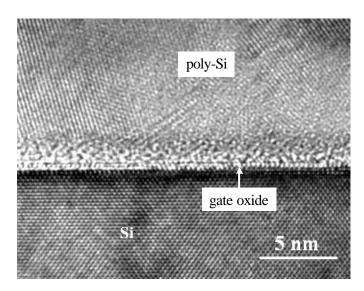

|     | 3.6.2   | Transmission electron microscopy                                         | 39 |

|     | 3.6.3   | Rutherford backscattering spectrometry                                   | 40 |

|     | 3.6.4   | Atomic force microscopy                                                  | 40 |

| 3.7 | Electri | cal Characterization                                                     | 41 |

|     | 3.7.1   | Characterization of poly-depletion                                       | 41 |

| CH  | APTER   | 4 SIMULATION OF LASER IRRADIATION ON SILICON                             | 43 |

| 4.1 | Introdu | uction                                                                   | 43 |

| 4.2 | Interac | tion of Laser with Crystalline Silicon                                   | 43 |

| 4.3 | Interac | ction of Laser with an a-Si Overlayer on c-Si                            | 47 |

| 4.4 | Summ    | ary                                                                      | 50 |

| CH  | APTER   | 5 FORMATION OF ULTRA-SHALLOW JUNCTIONS<br>USING LASER THERMAL PROCESSING | 51 |

| 5.1 | Introdu | uction                                                                   | 51 |

| 5.2 | Effect  | of Surface Treatment on Channeling                                       | 51 |

| 5.3 | Effect  | of RTA Temperature on Sheet Resistance                                   | 52 |

| 5.4 | Compa   | arison of Spike Anneal with Soak RTA                                     | 53 |

| 5.5 | Ultra-s | shallow P <sup>+</sup> /n Junctions Formed By LTP                        | 55 |

|     | 5.5.1  | Effect of different fluence conditions                        | 55  |

|-----|--------|---------------------------------------------------------------|-----|

|     | 5.5.2  | Lattice Strain                                                | 58  |

|     | 5.5.3  | Effect of multiple laser pulses at a high fluence             | 60  |

| 5.6 | Modif  | ication of Surface Morphology by LTP                          | 62  |

| 5.7 | Summ   | ary                                                           | 68  |

| CH  | APTER  | 6 ANNEALING OF CRYSTAL DEFECTS BY<br>LASER THERMAL PROCESSING | 69  |

| 6.1 | Introd | uction                                                        | 69  |

| 6.2 | RBS S  | Studies of Si Samples With Ge PAI                             | 69  |

| 6.3 | TEM    | Studies of Si Samples With Ge PAI                             | 73  |

| 6.4 | TED o  | of Boron During Post-LTP Anneal                               | 77  |

|     | 6.4.1  | Validation of the implant simulator, IMSIL                    | 77  |

|     | 6.4.2  | Simulation of implantation cascades                           | 79  |

|     | 6.4.3  | Enhanced diffusion of boron during post-LTP RTA               | 81  |

|     | 6.4.4  | Recrystallization of the pre-amorphized layer                 | 83  |

|     | 6.4.5  | Control of boron TED during post-LTP anneal                   | 85  |

| 6.5 | Summ   | ary                                                           | 91  |

| CH  | APTER  | 7 PHASE TRANSFORMATIONS DURING LTP OF<br>GATE STACKS          | 92  |

| 7.1 | Introd | uction                                                        | 92  |

| 7.2 | Effect | of a TiN/Ti Capping Layer on Melt Characteristics of Poly-Si  | 92  |

| 7.3 | Result | s From TRR Measurements                                       | 103 |

|     | 7.3.1  | Arsenic-doped single-layer a-Si gates                         | 104 |

|     | 7.3.2  | Boron-doped single-layer a-Si gates                           | 108 |

| 7.4 | TEM :  | Studies of B-doped Single-layer a-Si Gates                    | 114 |

| 7.5 | Summ   | ary                                                           | 118 |

| CH  | APTER  | 8 REDUCTION OF POLY-DEPLETION USING LASER THERMAL PROCESSING  | 119 |

| 8.1 | Introd |                                                               | 119 |

| 8.2                               | Result   | ts From P <sup>+</sup> -gated Capacitors (PCAP) | 119 |

|-----------------------------------|----------|-------------------------------------------------|-----|

|                                   | 8.2.1    | LTP of single-layer PCAP                        | 119 |

|                                   | 8.2.2    | Reduction of PDE in dual-layer PCAP             | 122 |

|                                   | 8.2.3    | TEM studies of dual-layer PCAP                  | 125 |

|                                   | 8.2.4    | Boron penetration in dual-layer PCAP            | 128 |

| 8.3                               | Result   | ts From N <sup>+</sup> -gated Capacitors (NCAP) | 131 |

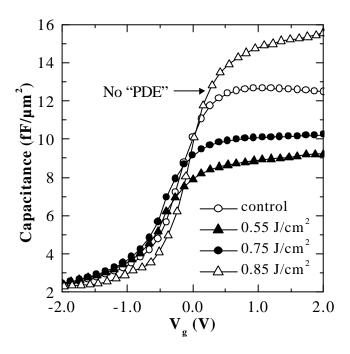

|                                   | 8.3.1    | LTP of single-layer NCAP                        | 131 |

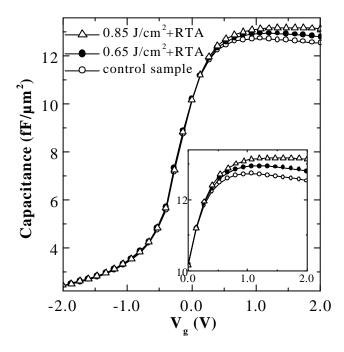

|                                   | 8.3.2    | Reduction of PDE in dual-layer NCAP             | 133 |

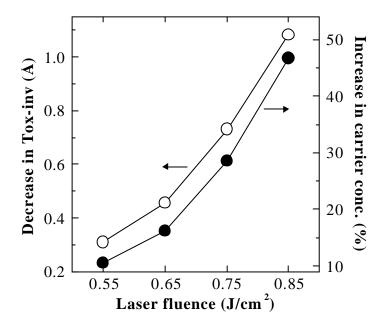

| 8.4                               | Effect   | of LTP on Electrical Oxide Thickness            | 134 |

| 8.5                               | Effect   | of LTP on Gate Oxide Integrity                  | 135 |

| 8.6                               | Summ     | nary                                            | 138 |

|                                   |          |                                                 |     |

| CH                                | APTER    | R 9 CONCLUSIONS                                 | 139 |

| 9.1                               | Introd   | luction                                         | 139 |

| 9.2                               | Forma    | ation of Ultra-shallow Junctions                | 139 |

| 9.3                               | Laser    | Thermal Processing of Gate Stacks               | 141 |

| 9.4                               | Future   | e Work                                          | 142 |

|                                   |          |                                                 |     |

| REI                               | FEREN    | ICES                                            | 144 |

| PUE                               | BLICA    | TIONS AND PATENTS                               | 155 |

| Publ                              | ications |                                                 | 155 |

| Pate                              | nts      |                                                 | 156 |

| Other publications as a Co-author |          | 157                                             |     |

#### **SUMMARY**

With the continual scaling of the channel length and the gate dielectric thickness of conventional metal oxide semiconductor (MOS) transistors, it has become increasingly difficult or complex to form highly activated ultra-shallow junctions and near depletion-free polycrystalline silicon (poly-Si) gates that meet the stringent requirements of the international technology roadmap for semiconductors. This is in spite of extensive development work in the ion implantation and dopant activation technologies. In this project, a novel technique known as laser thermal processing (LTP) was employed to fabricate ultra-shallow p<sup>+</sup>/n junctions and advanced poly-Si gate stacks for ultra-large scale integration technologies. LTP of ultra-shallow junctions typically involves the pre-amorphization of the silicon surface, followed by the melting of the amorphized regions (and the substrate) using a pulsed excimer laser. The extent of dopant diffusion is controlled by the melt depth and an extremely high degree of dopant activation is achieved upon recrystallization. To study the impact of LTP on the depletion of carriers at the poly-Si gate/gate oxide interface (poly-depletion), single or dual-layer capacitors with ultra-thin gate dielectrics were fabricated by subjecting asdeposited amorphous silicon gates to laser irradiation.

In this work, the dopant profiles were analyzed by secondary ion mass spectrometry (SIMS). Microstructural information was provided using transmission electron microscopy (TEM) and crystal defects were studied by Rutherford backscattering spectrometry (RBS). Capacitance-voltage (C-V) measurements and time-dependent dielectric breakdown (TDDB) studies were conducted to investigate the degree of gate-depletion and gate oxide reliability after LTP. The results show that LTP can form highly activated ultra-shallow p<sup>+</sup>/n junctions with step-like dopant profiles. These characteristics are in sharp contrast

compared to the junctions formed by spike rapid thermal annealing (RTA). In addition, as evident from RBS and TEM results, LTP can virtually anneal all the crystal damage that is created by the pre-amorphization implant. It is further demonstrated that transient enhanced diffusion of boron occurs during a post-LTP anneal due to a supersaturation of excess interstitials in the end-of-range region. This enhanced diffusion can be significantly suppressed when the melt depth is extended beyond the amorphous layer.

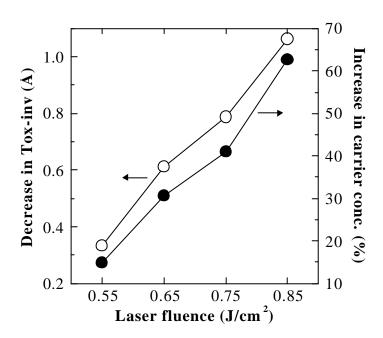

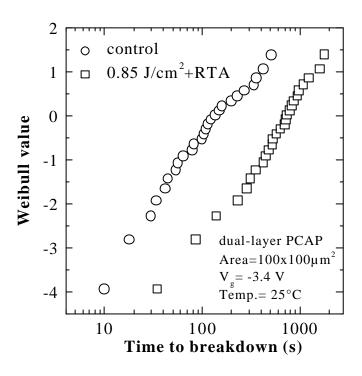

The electrical data indicate that LTP, when combined with a post-LTP anneal, increases the carrier concentration (up to ~63% for arsenic-doped gates) at the poly-Si gate/gate oxide interface. Thus, the LTP + RTA process readily reduces the poly-depletion effect. SIMS depth profiles clearly show an increase in dopant concentration near the gate/gate oxide interface for samples that were subjected to LTP prior to the gate activation anneal. For p<sup>+</sup>-gated capacitors, a reduction in poly-depletion is achieved without observable boron penetration. TDDB studies show an improvement in gate oxide reliability after LTP at high fluences. It is thus concluded that LTP, with a near-zero thermal budget, is a promising technique to fabricate ultra-shallow junctions as well as to process advanced poly-Si gate stacks for future generations of semiconductor devices.

# LIST OF TABLES

| Table |                                                                                                                                                      | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Optical (at $\lambda = 248$ nm) and thermophysical properties of c-Si.                                                                               | 20   |

| 2.2   | Optical (at $\lambda = 248$ nm) and thermophysical properties of a-Si.                                                                               | 21   |

| 5.1   | Tetrahedral radius and misfit factors of various atoms in Si.                                                                                        | 60   |

| 5.2   | Roughness measurements of the as-implanted sample and the samples annealed under different conditions.                                               | 65   |

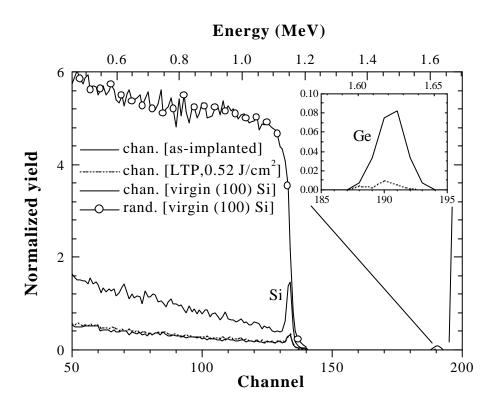

| 6.1   | Calculated $\chi_{min}$ values of the reference sample and the Ge <sup>+</sup> preamorphized sample before and after LTP at 0.52 J/cm <sup>2</sup> . | 72   |

| 7.1   | Comparison of the optical properties and net energy absorbed in TiN and Si.                                                                          | 97   |

Y. F. Chong ix

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                  | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Schematic showing the components of the total series resistance.                                                                                                                                                 | 2    |

| 2.1    | Schematic band diagram of an indirect band gap material. The heavy arrows symbolize (a) indirect and (b) direct transition [45].                                                                                 | 15   |

| 2.2    | Reflectivity and absorption coefficient of c-Si at room temperature.                                                                                                                                             | 17   |

| 2.3    | Illustration of the structural changes induced by laser irradiation of an a-Si overlayer on c-Si.                                                                                                                | 23   |

| 2.4    | Schematic showing the components of the total gate capacitance.                                                                                                                                                  | 28   |

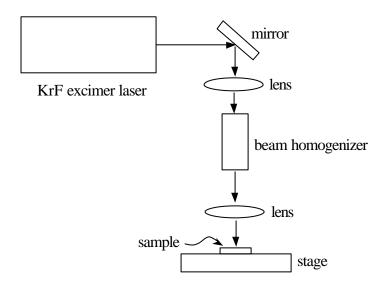

| 3.1    | A schematic diagram of the apparatus setup for laser thermal processing.                                                                                                                                         | 33   |

| 3.2    | Schematic diagrams of the cross-sections of the gate stacks and the associated process flow.                                                                                                                     | 35   |

| 3.3    | Determination of the metallurgical junction depth (from SIMS) after laser melting.                                                                                                                               | 39   |

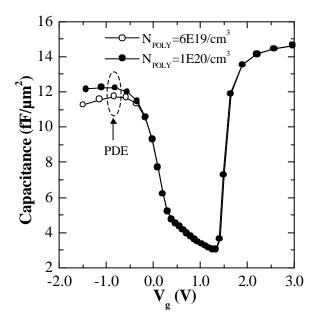

| 3.4    | Simulated C-V plots of PCAP of different gate doping concentrations, $N_{\text{POLY}}$ for the same gate oxide thickness.                                                                                        | 42   |

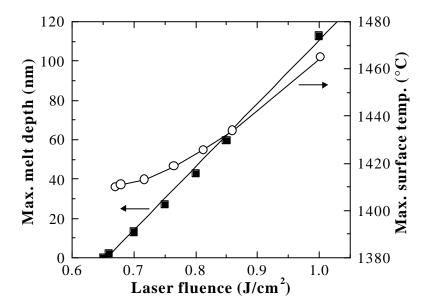

| 4.1    | Correlation between laser fluence, maximum melt depth and maximum surface temperature for c-Si (obtained from SLIM).                                                                                             | 44   |

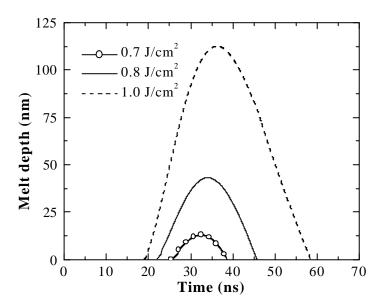

| 4.2    | Simulated melt front profiles for c-Si during laser irradiation with various fluences.                                                                                                                           | 45   |

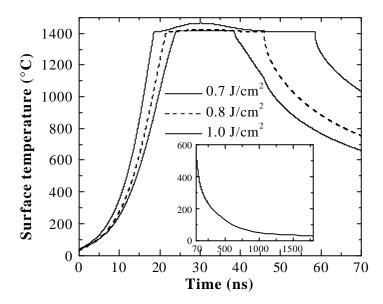

| 4.3    | Effect of laser fluence on the surface temperature of c-Si during irradiation. Inset shows that the surface temperature of Si (for a fluence of $0.7 \text{ J/cm}^2$ ) falls to room temperature after ~1800 ns. | 46   |

| 4.4    | Simulated melt front profiles for a 280 $\hbox{Å}$ a-Si overlayer on c-Si during laser irradiation at various fluences.                                                                                          | 48   |

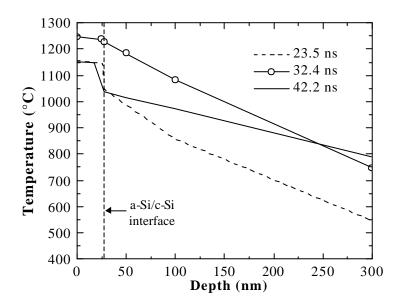

| 4.5    | Simulated temperature distribution profiles in the a-Si/c-Si sample at different times during irradiation with a fluence of $0.58~\rm J/cm^2$ .                                                                  | 50   |

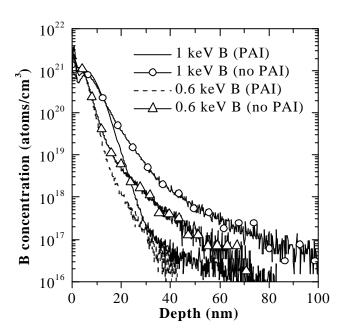

| 5.1    | Comparison of as-implanted boron SIMS profiles in pre-amorphized and c-Si samples.                                                                                                                               | 52   |

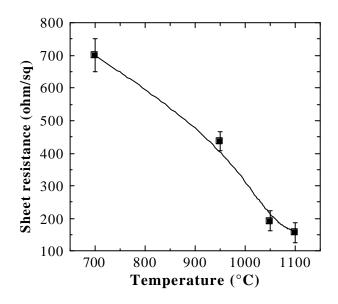

| 5.2    | Effect of annealing temperature (at a soak time of $10 \text{ s}$ ) on sheet resistance. Samples were pre-amorphized with $10 \text{ keV}$ , $2x10^{15}/\text{cm}^2 \text{ Si}^+$ PAI.                           | 53   |

| Figure |                                                                                                                                                                                                                  | Pag |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

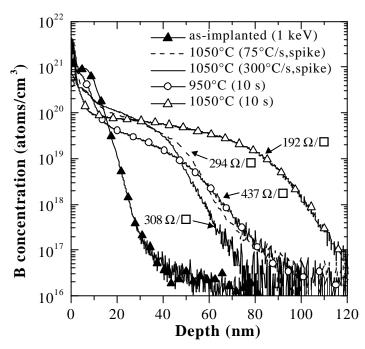

| 5.3    | Boron SIMS profiles of the pre-amorphized samples before and after RTA under various conditions.                                                                                                                 | 54  |

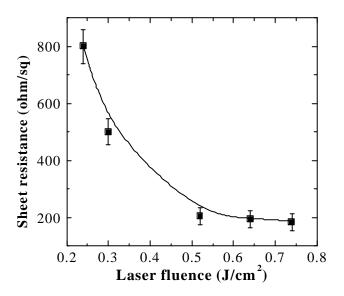

| 5.4    | Sheet resistance of a 1 keV boron-implanted sample as a function of laser fluence.                                                                                                                               | 56  |

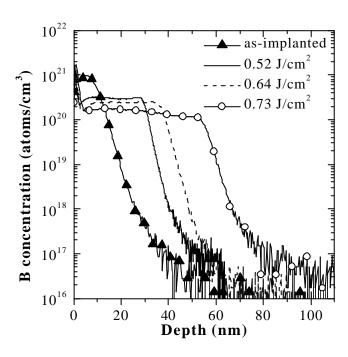

| 5.5    | SIMS depth profiles showing the effect of single-pulsed 248 nm laser irradiation on the redistribution of boron atoms.                                                                                           | 57  |

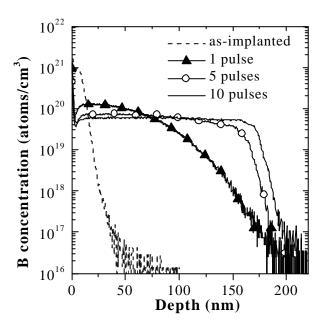

| 5.6    | Comparison of boron concentration profiles after LTP with successive pulses at 1.1 J/cm <sup>2</sup> .                                                                                                           | 61  |

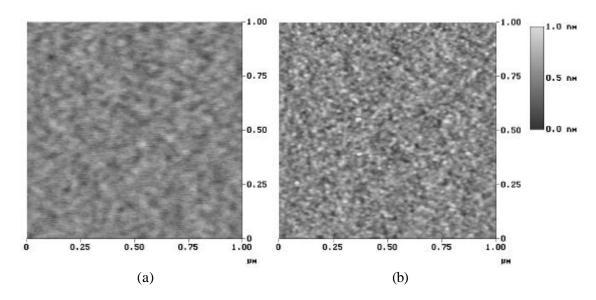

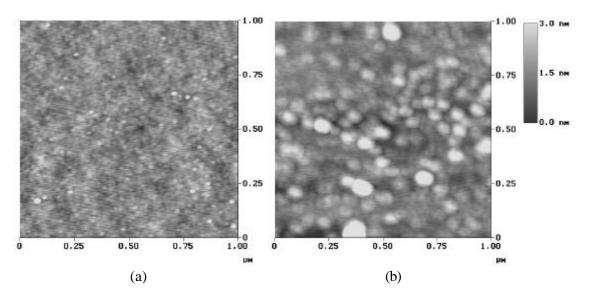

| 5.7    | Top-view AFM images recorded from the (a) as-implanted sample (pre-amorphized silicon) and (b) sample after RTA.                                                                                                 | 62  |

| 5.8    | Effect of laser irradiation on surface morphology. AFM image of a sample (a) after LTP at 0.52 J/cm <sup>2</sup> and (b) after LTP at 0.74 J/cm <sup>2</sup> .                                                   | 64  |

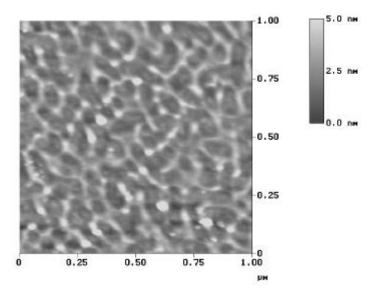

| 5.9    | Top-view AFM image obtained from a sample after laser annealing at a high fluence of $1.1\ \mathrm{J/cm^2}$ .                                                                                                    | 66  |

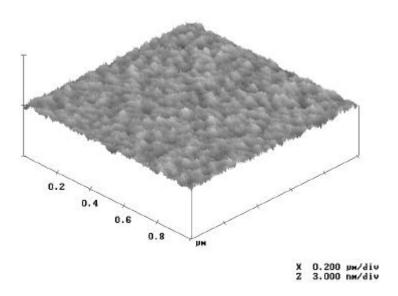

| 5.10   | Three-dimensional AFM topographic plots of the as-implanted sample.                                                                                                                                              | 67  |

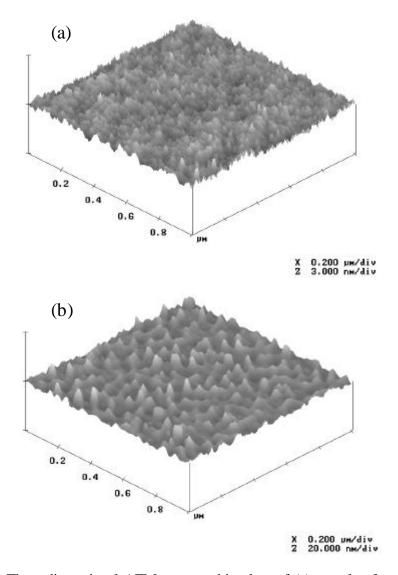

| 5.11   | Three-dimensional AFM topographic plots of (a) sample after LTP at $0.52~\mathrm{J/cm^2}$ and (b) sample after LTP at $1.1~\mathrm{J/cm^2}$ .                                                                    | 68  |

| 6.1    | RBS spectra of a virgin (100) silicon substrate and the $\mathrm{Ge^+}$ preamorphized sample before and after laser annealing at $0.52~\mathrm{J/cm^2}$ .                                                        | 70  |

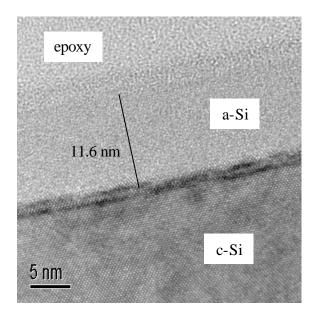

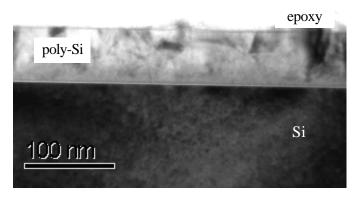

| 6.2    | Cross-sectional transmission electron micrograph of the $B^{\!\scriptscriptstyle +}$ as-implanted sample, pre-amorphized with $Ge^{\scriptscriptstyle +}$ implantation.                                          | 74  |

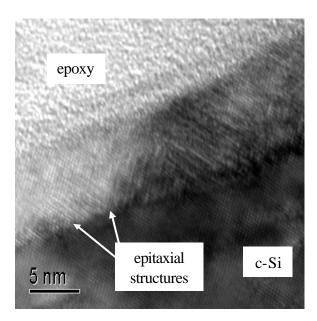

| 6.3    | High-resolution XTEM image of a sample that was not completely annealed by the $0.3~\mathrm{J/cm^2}$ laser irradiation. It is observed that some epitaxial structures have grown from the crystalline substrate. | 75  |

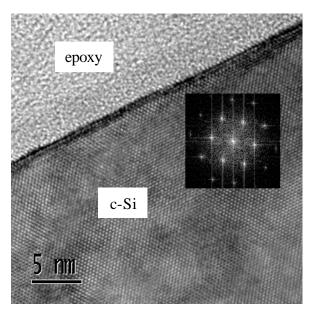

| 6.4    | Lattice image of the pre-amorphized sample after laser annealing at 0.52 J/cm². Recrystallization has occurred throughout the region of the originally amorphous layer.                                          | 76  |

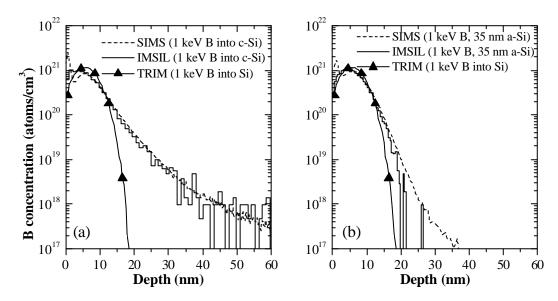

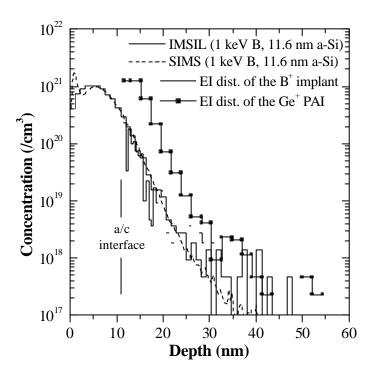

| 6.5    | Comparison of as-implanted 1 keV B profiles obtained from SIMS with simulated profiles from IMSIL and TRIM. (a) in c-Si and (b) in a-Si.                                                                         | 78  |

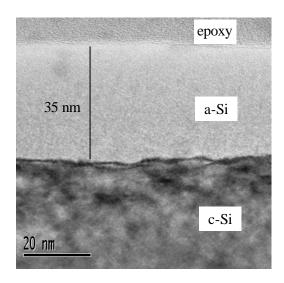

| 6.6    | Cross-sectional transmission electron micrograph of a sample that was pre-amorphized with $3x10^{15}/cm^2$ , $10~keV~Si^+$ .                                                                                     | 79  |

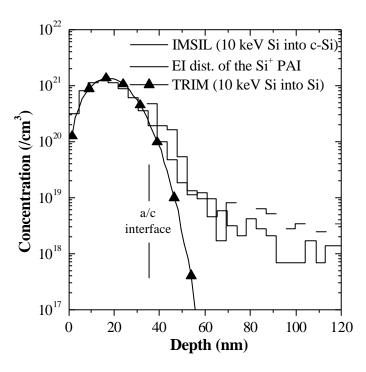

| 6.7    | Simulated profiles of the distribution of ions and excess interstitials for the $3x10^{15}$ /cm <sup>2</sup> , 10 keV Si <sup>+</sup> PAI (as obtained from IMSIL and TRIM).                                     | 80  |

| Figure |                                                                                                                                                                                                                                          | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

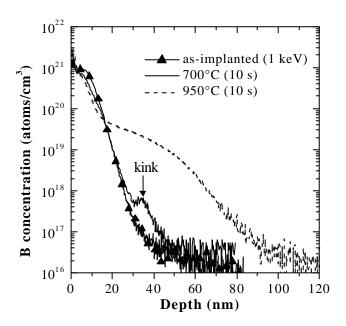

| 6.8    | SIMS profiles of 1 keV boron implanted into silicon (pre-amorphized with $10\text{keV Si}^+$ ). The presence of a kink at a depth of ~36 nm is clearly observed for a sample that was annealed at $700^\circ\text{C}$ for $10\text{s}$ . | 81   |

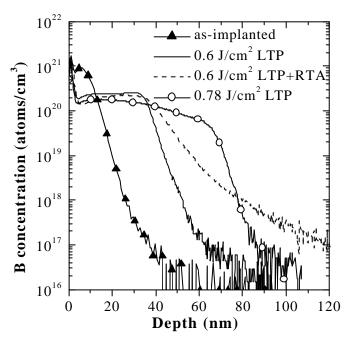

| 6.9    | SIMS depth profiles of boron after LTP at different fluence and after a post-LTP (at $0.6~\rm J/cm^2$ ) anneal. The PAI condition was $3x10^{15}/cm^2$ , $10~\rm keV~Si^+$ .                                                             | 82   |

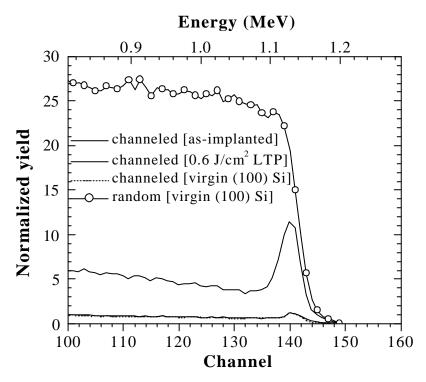

| 6.10   | Random and channeled backscattering spectra of a virgin (100) silicon sample and the $\mathrm{Si}^{\scriptscriptstyle +}$ pre-amorphized sample before and after LTP at 0.6 $\mathrm{J/cm^2}.$                                           | 84   |

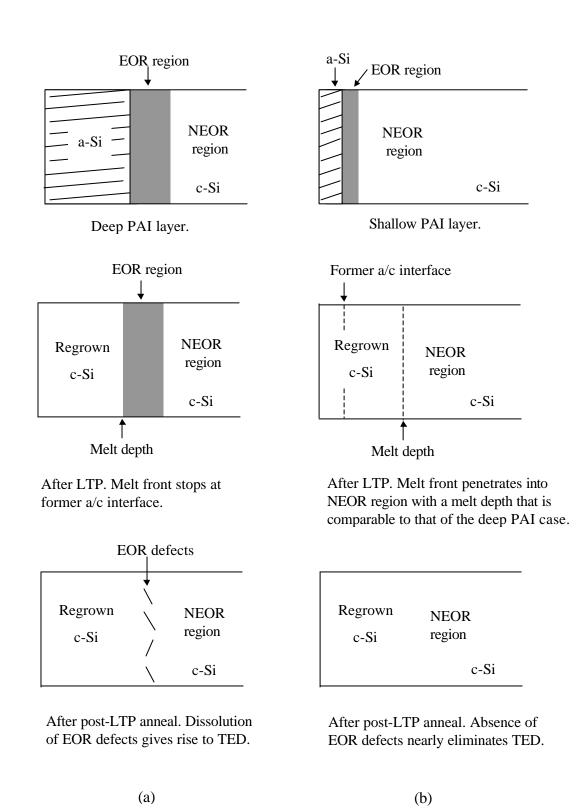

| 6.11   | Schematics showing the effect of melt front position on TED caused by EOR defects. (a) Melt front stops at former a/c interface. (b) Melt front penetrates into the NEOR region.                                                         | 86   |

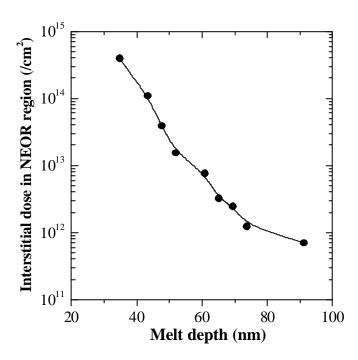

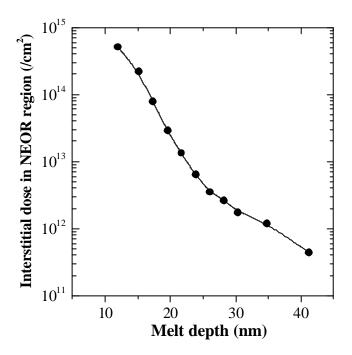

| 6.12   | Plot of the simulated interstitial dose in the NEOR region (for the $10 $ keV $\mathrm{Si}^+$ PAI sample) as a function of melt depth.                                                                                                   | 87   |

| 6.13   | SIMS profile of boron and simulated profiles of boron ions and excess interstitials that were generated by a 1 keV B <sup>+</sup> implant and a 5 keV Ge <sup>+</sup> PAI.                                                               | 88   |

| 6.14   | Plot of the simulated interstitial dose in the NEOR region (for the 5 keV Ge <sup>+</sup> PAI sample) as a function of melt depth.                                                                                                       | 89   |

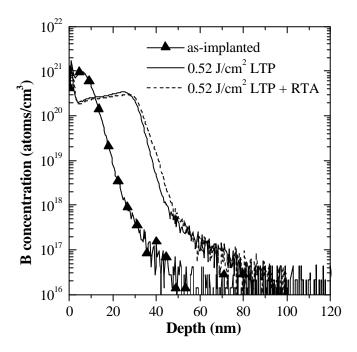

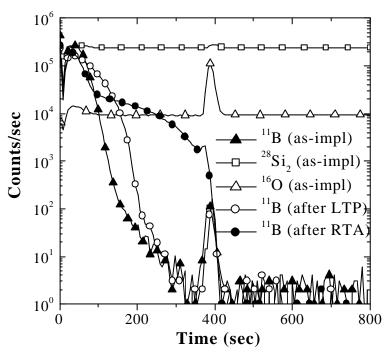

| 6.15   | Boron SIMS profiles (in the $Ge^+$ PAI sample) after LTP at $0.52~\text{J/cm}^2$ and after a post- $0.52~\text{J/cm}^2$ LTP RTA. Over-melting into the substrate nearly eliminate boron TED.                                             | 90   |

| 7.1    | Comparison of SIMS depth profiles of an as-implanted sample, a sample after LTP at $0.68~\rm J/cm^2$ and a sample after RTA at $925~\rm ^{\circ}C$ for $30~\rm s$ (all without metal capping layers).                                    | 93   |

| 7.2    | Effect of using a TiN/Ti capping layer on the distribution of boron and titanium atoms in silicon after laser irradiation at 0.68 J/cm². Extensive diffusion of B and Ti had occurred.                                                   | 95   |

| 7.3    | Schematic of the optical path of the laser light upon impinging a homogeneous surface.                                                                                                                                                   | 96   |

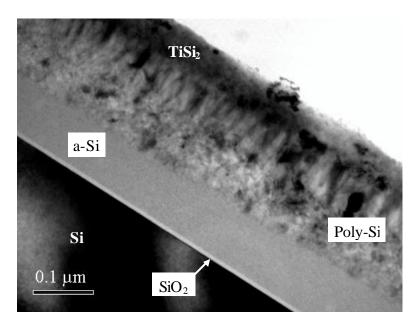

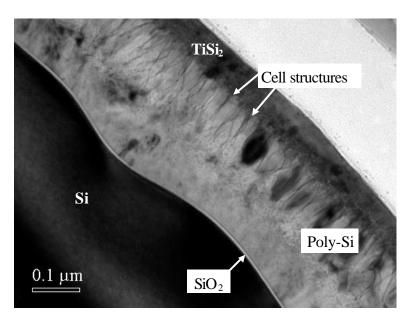

| 7.4    | Cross-sectional transmission electron micrograph obtained from a TiN/Ti capped sample after irradiating at $0.68~\mathrm{J/cm^2}$ .                                                                                                      | 98   |

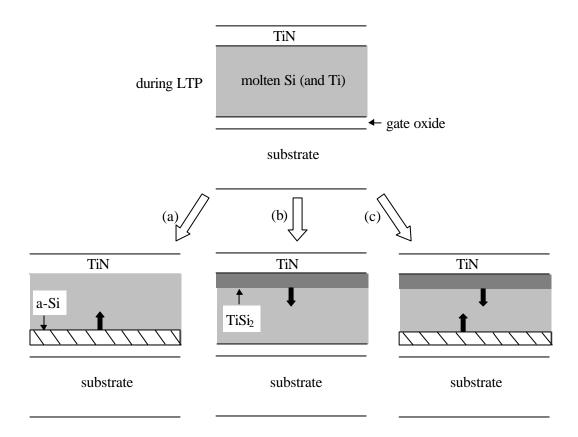

| 7.5    | Schematics illustrating the three possible scenarios for solidification. (a) conventional growth mode. (b) reverse growth mode. (c) combination of both modes. Dark arrows indicate the direction of solidification.                     | 100  |

| Figure |                                                                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.6    | XTEM image of a TiN/Ti capped sample after laser irradiation at 0.92 J/cm². The TEM micrograph shows that the oxide layer is severely deformed.                     | 102  |

| 7.7    | Plan-view TEM image of the TiN/Ti capped sample after laser irradiation at $0.92~\mathrm{J/cm^2}$ .                                                                 | 103  |

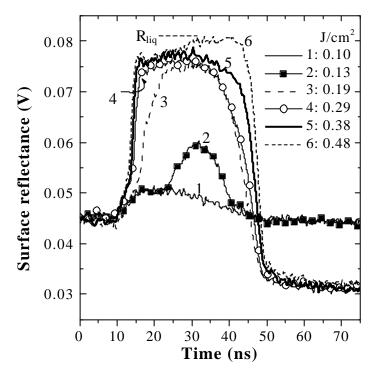

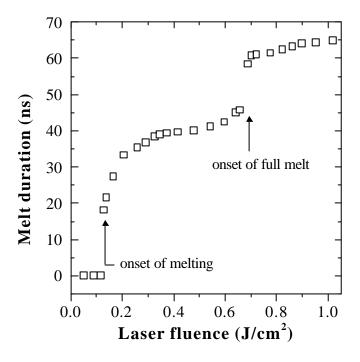

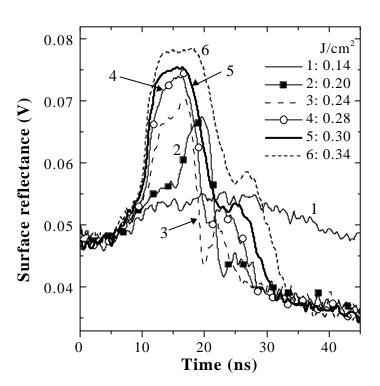

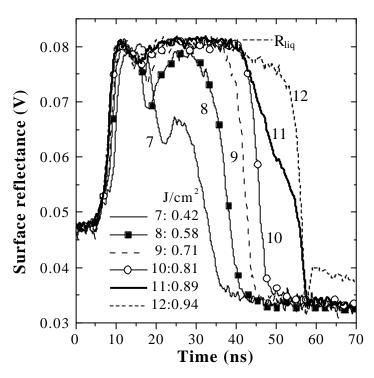

| 7.8    | Typical TRR traces obtained during LTP of arsenic-implanted a-Si at various fluences (0.10 J/cm <sup>2</sup> $\leq$ E <sub>l</sub> $\leq$ 0.48 J/cm <sup>2</sup> ). | 104  |

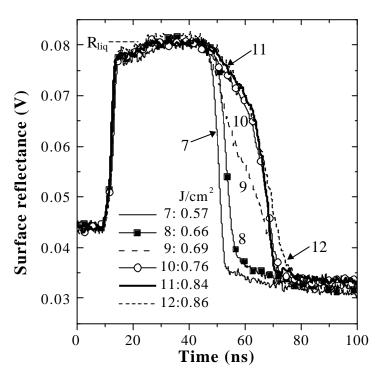

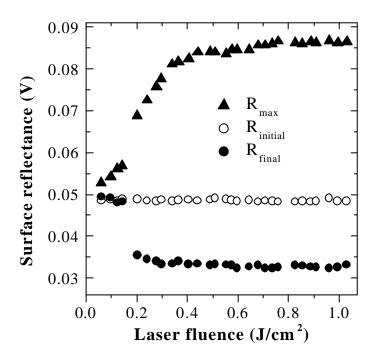

| 7.9    | Plots of the transient surface reflectance obtained during LTP of arsenic-implanted a-Si at various energy densities.                                               | 106  |

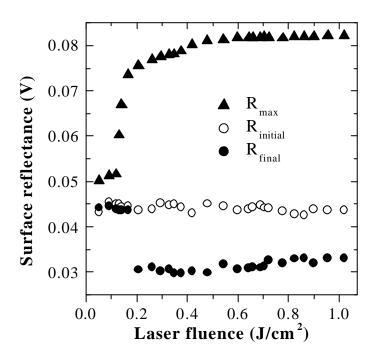

| 7.10   | Plot of the characteristic reflectance values as a function of laser fluence for arsenic-implanted a-Si.                                                            | 107  |

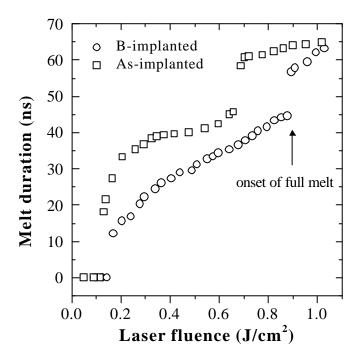

| 7.11   | Plot of the melt duration as a function of laser fluence for an arsenic-implanted a-Si film.                                                                        | 107  |

| 7.12   | Typical TRR traces obtained during LTP of boron-implanted a-Si at low energy densities (0.14 $\leq$ E $_l$ $\leq$ 0.34 J/cm $^2$ ).                                 | 108  |

| 7.13   | Temporal evolution of the reflectance of boron-implanted a-Si under laser irradiation at various fluences ( $0.42 \le E_l \le 0.94 \text{ J/cm}^2$ ).               | 109  |

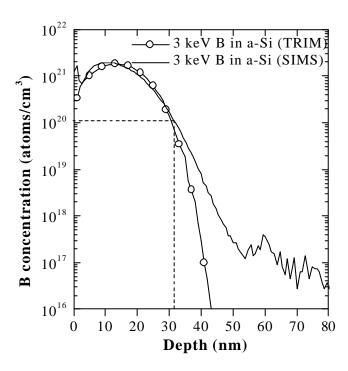

| 7.14   | Comparison of an as-implanted 3 keV B profile obtained from SIMS with a simulated profile from TRIM.                                                                | 111  |

| 7.15   | Plot of the characteristic reflectance values as a function of laser fluence for a boron-implanted a-Si film.                                                       | 113  |

| 7.16   | Plot of the melt duration as a function of laser fluence for a boron-implanted a-Si film. The plot for the As doped sample is overlaid as a comparison.             | 114  |

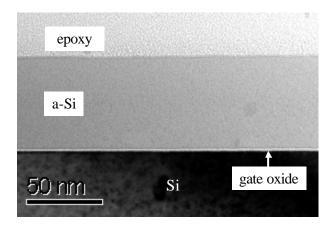

| 7.17   | Cross-sectional transmission electron micrograph of a boron-implanted a-Si sample prior to LTP.                                                                     | 115  |

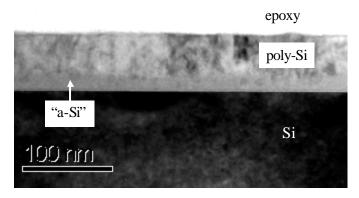

| 7.18   | Bright-field TEM image of a cross-section of the boron-doped sample that was irradiated at a fluence of 0.45 J/cm <sup>2</sup> .                                    | 115  |

| 7.19   | Bright-field TEM image of a cross-section of the boron-doped sample that was irradiated at a fluence of 0.55 J/cm <sup>2</sup> .                                    | 116  |

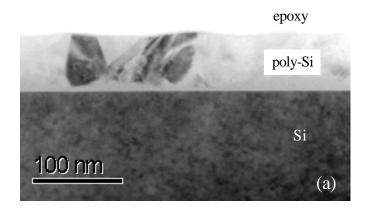

| 7.20   | XTEM image of a cross-section of the boron-doped sample after LTP at (a) 0.75 J/cm², (b) 0.85 J/cm² and (c) 0.94 J/cm².                                             | 117  |

| 7.21   | HRTEM image of a cross-section of the boron-implanted a-Si sample upon LTP at 0.94 J/cm <sup>2</sup> .                                                              | 118  |

| Figure |                                                                                                                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

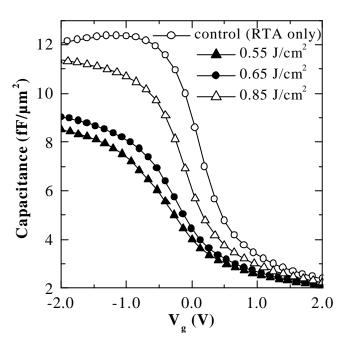

| 8.1    | Comparison of high frequency C-V plots of single-layer PCAP after RTA (control sample) and after LTP alone.                                                                                                         | 120  |

| 8.2    | SIMS depth profiles of boron in single-layer PCAP after LTP at different fluences.                                                                                                                                  | 121  |

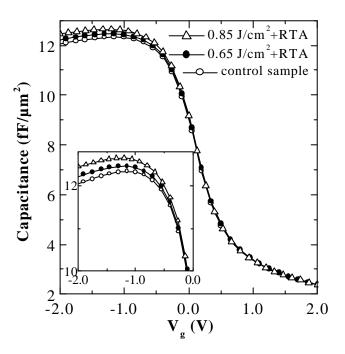

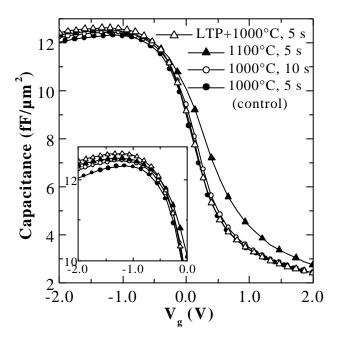

| 8.3    | HF C-V plots of the dual-layer PCAP after the standard RTA or after a post-LTP RTA. Inset is the enlarged view showing a reduction in PDE for the laser-processed samples.                                          | 122  |

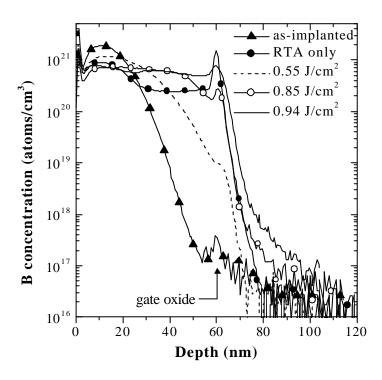

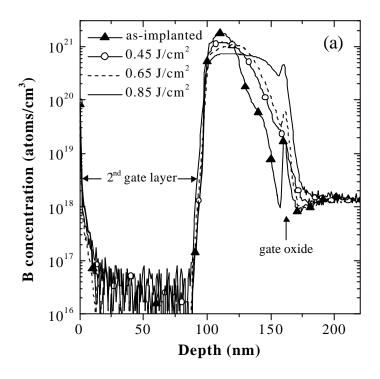

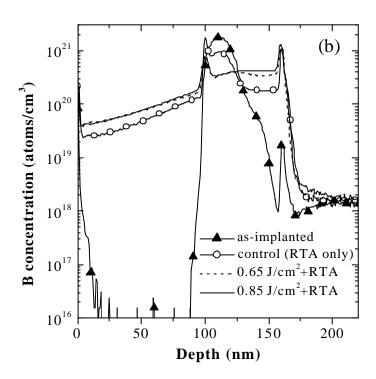

| 8.4    | Boron SIMS profiles in the dual-layer PCAP (a) after LTP of the first gate layer and (b) after RTA alone or LTP + RTA.                                                                                              | 124  |

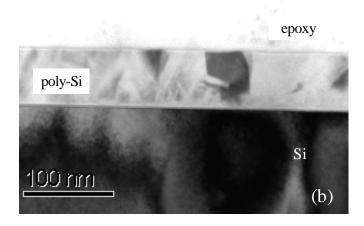

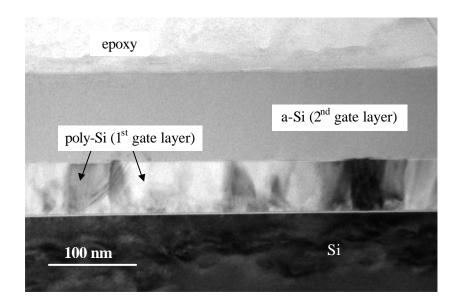

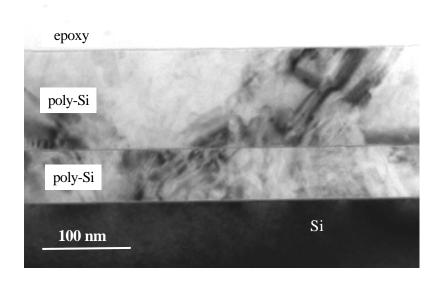

| 8.5    | Bright-field TEM image of a cross-section of the dual-layer PCAP before it was subjected to RTA. The first gate layer was exposed to LTP at $0.85 \text{ J/cm}^2$ prior to the deposition of the second gate layer. | 126  |

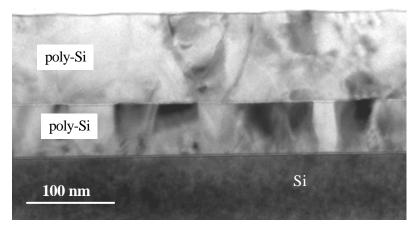

| 8.6    | XTEM image of the dual-layer p+ poly-Si gate stack after 0.85 $\ensuremath{\text{J/cm}^2}$ LTP + RTA.                                                                                                               | 127  |

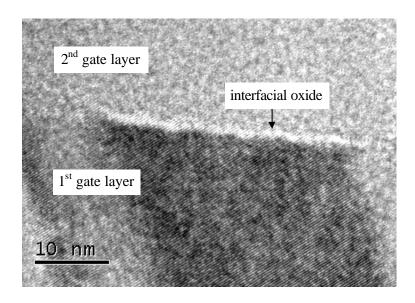

| 8.7    | HRTEM image of a cross-section of the dual-layer PCAP after 0.85 J/cm² LTP+RTA, focussing on the interface between the first and the second gate layer.                                                             | 127  |

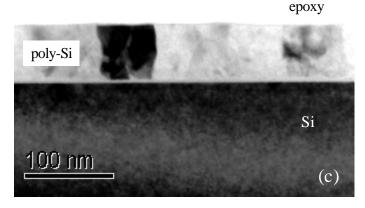

| 8.8    | Cross-sectional transmission electron micrograph of the dual-layer PCAP after RTA alone (control sample).                                                                                                           | 128  |

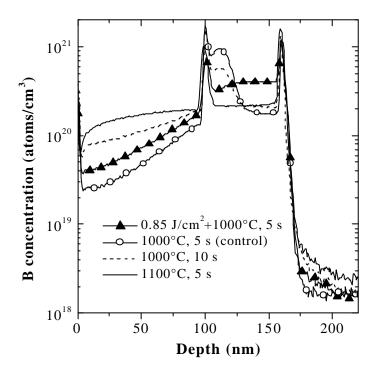

| 8.9    | C-V plots of dual-layer PCAP annealed under different conditions. RTA at 1100 $^{\circ}\text{C}$ , 5 s causes a large positive $V_{FB}$ shift, indicating severe boron penetration.                                 | 129  |

| 8.10   | Boron SIMS profiles of the dual-layer PCAP after various annealing conditions.                                                                                                                                      | 130  |

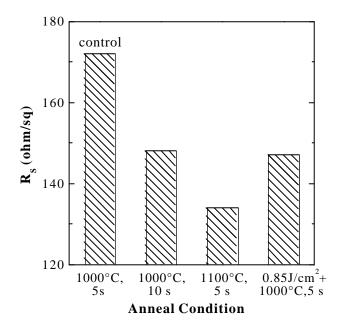

| 8.11   | Sheet resistance of the dual-layer PCAP annealed under different conditions.                                                                                                                                        | 131  |

| 8.12   | HF C-V plots of the single-layer NCAP after LTP at different fluences.                                                                                                                                              | 132  |

| 8.13   | C-V plots of the dual-layer NCAP after RTA or after a post-LTP anneal. Inset is the enlarged view showing a reduction in PDE for the laser-processed samples.                                                       | 133  |

| 8.14   | Effect of a pre-RTA LTP on $T_{\rm ox}\mbox{-inv}$ and $N_{\rm POLY}$ for a p-MOSFET.                                                                                                                               | 134  |

| 8.15   | Effect of a pre-RTA LTP on $T_{\rm ox}$ -inv and $N_{\rm POLY}$ for a n-MOSFET.                                                                                                                                     | 135  |

Y. F. Chong xiv

| Figure |                                                                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|------|

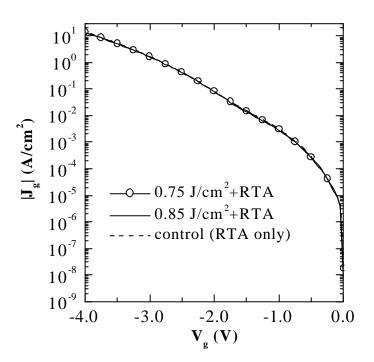

| 8.16   | Comparison of $J_{\rm g}\mbox{-}V$ plots of dual-layer PCAP processed under different conditions.                                      | 136  |

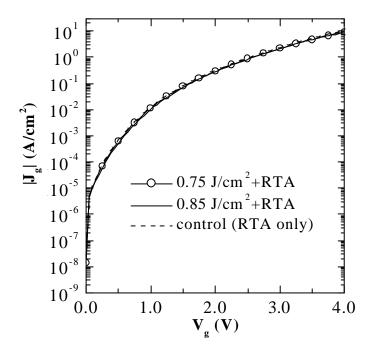

| 8.17   | Comparison of $J_{\rm g}\mbox{-}V$ plots of dual-layer NCAP processed under different conditions.                                      | 136  |

| 8.18   | Weibull plots of TDDB data for the control sample and the sample after $0.85~\text{J/cm}^2~\text{LTP} + \text{RTA}$ (dual-layer PCAP). | 137  |

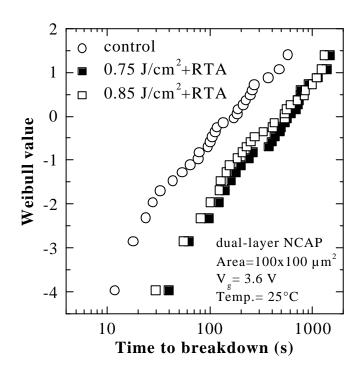

| 8.19   | Comparison of Weibull plots of TDDB data for the control and LTP + RTA samples (dual-layer NCAP).                                      | 138  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background

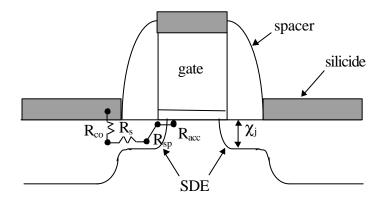

The 2001 international technology roadmap for semiconductors (ITRS) projects source/drain extension (SDE) junctions to be 22-36 nm, with sheet resistance, R<sub>s</sub> of less than 460  $\Omega/\Box$  for advanced (< 75 nm printed gate length) complementary metal oxide semiconductor field effect transistors (MOSFETs) [1]. Reducing the channel length of a MOSFET is the most appropriate way to increase the drive current and circuit density. However, this is often accompanied by a reduction in threshold voltage and an increase in the sub-threshold leakage current [2]. Hence, in order to minimize short channel effects and to confine the electric field profile in the channel region, the vertical junction depth  $(\chi_i)$ should be scaled down appropriately [2]. The main challenge in the formation of ultrashallow SDE junctions is the optimization of  $\chi_j$  to achieve low series resistance with good transistor turn-off performance [2, 3]. Referring to Fig. 1.1, the total series resistance, R<sub>tot</sub> comprises the contact resistance due to the silicide (R<sub>co</sub>), sheet resistance of the doped layer (R<sub>s</sub>), spreading resistance where the carrier path turns toward the channel (R<sub>sp</sub>) and the voltage dependent accumulation resistance where the gate overlaps the junction, Racc [see Eqn. (1.1)]. These parameters are in turn dependent on the doping profile, degree of dopant activation and  $\chi_j$  [2]. A reduction in  $R_{tot}$  will lead to an increase in the drive current.

$$R_{\text{tot}} = R_{\text{co}} + R_{\text{s}} + R_{\text{sp}} + R_{\text{acc}} \tag{1.1}$$

**Figure 1.1** Schematic showing the components of the total series resistance.

However, it has become increasingly difficult and complex for the conventional ion implantation and dopant activation technologies to fabricate junctions with the desired characteristics due to the well-known tradeoff between  $\chi_j$  and  $R_s$  [2-4]. This tradeoff is a direct consequence of the physical limits imposed by the diffusion and solid solubility of the dopant atoms in silicon. Furthermore, these technologies do not produce junctions with the ideal "box-shaped" profiles that meet the requirements of ITRS [1]. Such constraints have led a recent study [5] to conclude that continual junction scaling of  $\,\chi_{j}$  to less than 40 nm would result in little to no performance gain. This is because any improvement in short channel effects due to reduced charge sharing is offset by a large increase in external resistance. Compared to n<sup>+</sup>/p junctions, ultra-shallow p<sup>+</sup>/n junctions using boron ion implantation are more difficult to form due to channeling of boron ions and transient enhanced diffusion (TED) of boron during post-implantation annealing [2-4, 6, 7]. TED is mainly caused by the interaction of boron atoms with the excess interstitials generated during ion implantation. It has been demonstrated that TED is significantly suppressed by reducing the implantation energy to sub-keV energies [6-8]. Besides reducing the energy of the ion implantation, TED can also be minimized by performing an optimized sub-amorphizing

implant and by reducing the thermal budget of the post-implantation anneal [3, 6, 9]. The function of the sub-amorphizing implant is to reduce channeling of the dopant ion (such as B<sup>+</sup>), and to create a vacancy-rich region for the provision of vacancies to recombine with the interstitials produced by the dopant ion implantation, thereby resulting in less excess interstitials that can contribute to TED [9].

Previous studies have shown that when the ion implantation energy is low enough for TED to be almost negligible, a diffusivity enhancement factor of approximately four still exists [10]. In this case, boron enhanced diffusion (BED) is believed to be responsible for the diffusion enhancement. Agarwal *et al.* [10] have shown that BED is driven by the interstitials produced in the boron-containing silicon layer during the annealing process when the boron concentration exceeds a threshold of a few atomic percent. The importance of the control of annealing ambient is emphasized by the observation of oxygen enhanced diffusion (OED). The presence of oxygen during annealing will lead to oxide growth on the silicon substrate. During oxide growth, interstitial defects are injected into Si, resulting in increased boron diffusion into bulk silicon [11]. The need for ultra-shallow junction fabrication has led to the development of new processes such as ultra-low energy ion implantation, spike rapid thermal annealing (RTA), gas immersion laser doping (GILD) and laser thermal processing (LTP) [2, 12-14]. Among these, LTP is the most promising technique because it produces abrupt, highly activated and ultra-shallow junctions.

The advantages of LTP are (i) "near-zero" thermal budget (since laser pulses last only for tens of nanoseconds), (ii) extent of dopant diffusion is controlled by the melt depth (with negligible diffusion in the adjacent solid substrate), and (iii) rapid quench rate (metastable process). This allows active dopant concentrations to exceed the solid solubility limit [13,

14]. The disadvantages associated with LTP are (i) low throughout, (ii) differential absorption of laser light across patterned structures, and (iii) deactivation/diffusion of the dopants during post-LTP anneal steps.

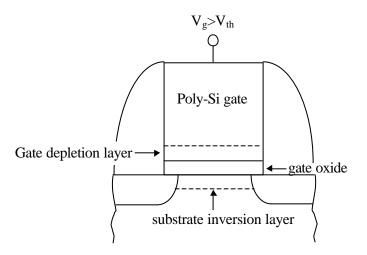

Another critical aspect of MOSFET scaling is the depletion of carriers at the polycrystalline silicon (poly-Si) gate/gate oxide interface [15-18]. After doping the poly-Si gate, a RTA is usually performed to activate the gate dopants. However, the anneal may be insufficient to drive the implanted impurities down the entire depth of the gate. Consequently, a portion of the poly-Si gate nearest to the gate oxide will be depleted of carriers (poly-depletion), which degrades the device performance [16]. With reference to p-MOSFETs, although the temperature and/or time of the gate activation anneal can be increased to reduce the poly-depletion effect (PDE), extensive diffusion of boron may occur such that boron diffuses through the thin gate oxide into the channel. This phenomenon is known as boron penetration. It is well known that boron penetration causes threshold voltage instabilities and deteriorates gate oxide reliability [16-18].

#### 1.2 Scope of the Project

This project involves the fabrication (using LTP) and characterization of ultra-shallow p<sup>+</sup>/n junctions and advanced poly-Si gate stacks for ultra-large scale integration technologies. For the formation of ultra-shallow junctions, silicon substrates were first pre-amorphized by Si<sup>+</sup> or Ge<sup>+</sup>. Boron ions were then implanted using ultra-low energy ion implantation. Comparisons were made between the dopant profiles of laser-processed and spike rapid thermal annealed samples. Further work was done to investigate the crystal quality after LTP, and how residual defects affect the enhanced boron diffusion during a

post-LTP anneal. The ultra-shallow junctions were mainly characterized using secondary ion mass spectrometry (SIMS), transmission electron microscopy (TEM) and Rutherford backscattering spectrometry (RBS). To study the impact of laser irradiation on PDE, MOS capacitors with ultra-thin gate oxides were fabricated using LTP. Single or dual-layer poly-Si gated capacitors were processed after the as-deposited amorphous silicon (a-Si) gates were exposed to laser irradiation. Detailed characterizations of the gate stacks/capacitors were carried out using capacitance-voltage (C-V) measurements, SIMS, TEM and time-resolved reflectance (TRR) measurements. The mechanism of the improvement in PDE after LTP (for both n<sup>+</sup> and p<sup>+</sup>-gated capacitors) is elucidated based on the results.

#### 1.3 Objectives

- 1. To determine the effect of ramp-up rates of spike RTA on dopant redistribution and compare the dopant profiles with those obtained after conventional RTA.

- 2. To investigate the effect of different laser fluence on junction depth after LTP and compare the dopant profiles with those obtained after spike RTA.

- 3. To examine the crystal quality or residual defects after LTP and check the effect of these defects on the boron diffusivity enhancement during a post-LTP anneal.

- 4. To investigate the effect of a metal capping layer on the melt characteristics of a gate stack during LTP.

- 5. To study the effect of LTP on dopant activation at the poly-Si gate/gate oxide interface, with and without an additional rapid thermal anneal.

#### 1.4 Organization of the Thesis

The organization of the thesis and a brief synopsis of the various chapters of this thesis are provided as follows:

#### • Chapter 1: Introduction

This chapter covers some introductory information pertaining to the subject matter of this study. It also describes the scope and objectives of this project.

#### • Chapter 2: Literature Review

This chapter provides the background and relevant theories of ultra-shallow junction formation, laser interaction with materials and the poly-depletion effect. It also gives a detailed review on the subject matters of this study based on earlier works.

#### • Chapter 3: Experimental

This chapter describes the experimental setup and the sample preparation methods. It also includes the test methodologies and the simulation procedures used in this work.

#### • Chapter 4: Simulation of Laser Irradiation on Silicon

This chapter shows the results from the simulation of the laser interaction with silicon using the SLIM software. These results (e.g. melt depth vs. time, heating and cooling rates) provide some basic understanding of the LTP and the melt phenomenon.

### Chapter 5: Formation of Ultra-shallow Junctions Using Laser Thermal Processing

This chapter describes and compares the two most promising techniques that can be

employed to form ultra-shallow p<sup>+</sup>/n junctions. For each technique, the discussion will include the analyses of the junction depth, the abruptness of the junction, and the sheet resistance of the boron-doped layer.

#### • Chapter 6: Annealing of Crystal Defects by Laser Thermal Processing

This chapter discusses the effect of LTP on the annealing of crystal defects. The role of the excess interstitials in the EOR region in the enhanced diffusion of boron during a post-LTP RTA is also reported.

#### • Chapter 7: Phase Transformations During LTP of Gate Stacks

This chapter presents the results and relevant discussions pertaining to the phase transformations during LTP of gate stacks. It begins with the determination of the effect of a TiN/Ti cap layer on the melt characteristics of poly-Si. The second part of the chapter discusses in detail the data obtained from TRR measurements.

#### • Chapter 8: Reduction of Poly-depletion Using Laser Thermal Processing

This chapter reports the electrical results obtained from single or dual-layer poly-Si gated capacitors. The effect of LTP on reducing poly-depletion is interpreted from C-V data and SIMS profiles. In addition, the effect of LTP on the gate oxide reliability is presented.

#### • Chapter 9: Conclusions

This chapter summarizes the major results and findings, and provides conclusions based on these findings in the light of the objectives of this project. Recommendations for further experimental work are also given.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Introduction

This chapter begins with an overview on the formation of ultra-shallow junctions and transient enhanced diffusion, and proceeds to cover the relevant theories on laser interaction with materials. It also covers the poly-depletion effect and ways to prevent boron penetration. In general, the chapter gives a detailed review on the subject matter of this study based on earlier works.

#### **2.2 Ion Implantation**

For more than 15 years, ion implantation has been the method of choice for doping semiconductor devices [2, 7]. One of the complications that can arise during ion implantation is channeling, and this occurs when the ion velocity vector is parallel to a major crystal orientation [7, 19]. In this situation, some ions may travel considerable distances with little energy loss since nuclear stopping is not very effective, and the electron density in a channel is low. Once in a channel, the ion will continue in that direction, making many internal collisions that are nearly elastic until it comes to rest or de-channels.

Channeling is more pronounced when implanting light atoms on axis into a heavy matrix and can produce a significant tail on the dopant distributions [6, 7]. Thus, off-axis implantation with a typical tilt angle of  $7^{\circ}$  is performed to avoid this tail. However, the effect of tilt angle is found to be almost negligible for ultra-low energy ion implantation [6]. In fact, Foad *et al.* [6] have demonstrated that channeling of  $B^{+}$  still occurs when the implantation

energy decreases to as low as 1 keV.

Owing to the larger molecular weight of BF<sub>2</sub> as compared to boron, BF<sub>2</sub><sup>+</sup> may also be used for ion implantation to form shallow junctions. This method decreases the depth to which the B atoms are implanted because the fluorine atoms damage the surface and reduce boron channeling. Moreover, since the B<sup>+</sup> ion only acquires 11/49 (ratio of the mass of <sup>11</sup>B over  ${}^{11}B^{19}F_2$ ) of the energy of  $BF_2^+$ , it does not penetrate deeply into the silicon substrate [7, 19]. However, this technique has several disadvantages. For instance, it was found that the fluorine atoms retard boron activation and also reduce the rate of recrystallization of the amorphous region [20, 21]. Furthermore, the use of BF<sub>2</sub><sup>+</sup> for the SDE implantation would imply that BF<sub>2</sub><sup>+</sup> is also implanted into the gate. It follows that the presence of fluorine in the gate would enhance boron penetration into the channel as compared to pure boron implants. This was explained by the increase in boron diffusivity through the poly-Si gate and gate oxide [18, 22]. Another method to minimize channeling is to disorder the crystal lattice prior to implantation. This is achieved by pre-amorphizing the Si surface with ions such as Si<sup>+</sup> or Ge<sup>+</sup> [21, 23]. One major drawback of this technique is that the amorphous region must be recrystallized, and residual defects such as end-of-range (EOR) loops may remain after annealing [23, 24]. In order to remove these defects completely, it is necessary to anneal at a higher temperature; this however will cause undesirable dopant diffusion into the silicon substrate [25].

Germanium is normally preferred over silicon for the pre-amorphizing implant (PAI) because a lower dose is required for Ge<sup>+</sup> implantation to form a continuous amorphous layer. In addition, Ge<sup>+</sup> implantation is known to produce a sharper amorphous/crystalline (a/c) interface. This helps to inhibit the nucleation of hairpin dislocations during annealing and

thus results in less extended defects and less leakage [21, 24]. Recent studies have shown that the degree of boron activation is greater for Ge<sup>+</sup> PAI as compared to Si<sup>+</sup> PAI [26, 27]. This is largely due to the strain compensation provided by the larger Ge atoms in the silicon matrix. Hence, more boron atoms (which are smaller than Si) are able to move into substitutional sites during annealing [26] and become activated. The conditions for ideal shallow junction formation are that the implanted boron profile should be confined within the amorphous region, and that the final junction should completely contain the defects formed at the previous a/c interface [25, 28].

The junction depth can also be reduced by implanting the dopants through a thin ( $\sim$ 20 nm) screen layer such as silicon dioxide [7, 19]. It has been proposed that this sacrificial layer randomizes or reduces the ion velocities before entering the crystal, thus minimizing channeling effects. Another reason for using a screen oxide layer is that the implanted dopant profile can be moved closer to the Si surface [7]. The problems associated with this method are: (i) oxygen may be "knocked on" into the substrate and (ii) some dopants will be trapped in the oxide film resulting in dose loss [23]. Alternatively, ultra-shallow junctions can be obtained by using polyatomic (such as decaborane,  $B_{10}H_{14}$ ) cluster ion implantation [29, 30]. This technique produces ions with low equivalent energies because the kinetic energy of the cluster is shared between the constituent atoms. The concept used in  $B_{10}H_{14}$  cluster ion implantation is similar to that of the BF<sub>2</sub> ion implantation except that it does not include the fluorine molecule that is deleterious to the gate oxide.

#### 2.3 Rapid Thermal Annealing

Rapid thermal annealing (RTA) is often employed to anneal the primary crystalline damage caused by ion implantation as well as to activate the implanted dopants, i.e., to move the dopants to substitutional lattice sites [2]. If the Si substrate was pre-amorphized, RTA is also used to recrystallize the amorphous layer that normally extends up to the surface [7]. This recrystallization process initiates from the underlying substrate and regrowth proceeds toward the surface via solid phase epitaxy (SPE). Dopant activation is obtained by the conventional "soak" or the "spike" anneal method. A typical soak anneal profile involves ramping up to a target temperature of 1000 °C, with a soak time of about 10 s, then ramping down at a rate of ~75 °C/s [2, 6]. On the other hand, spike RTA utilizes much higher ramp-up rates (as high as ~400 °C/s) and reduces the soak time to << 1 s [12, 14]. In this way, higher temperatures can be reached while maintaining a low thermal budget. Earlier works have shown that spike anneals produce shallower junctions with superior dopant activation efficiency [3, 31] as compared to soak RTA. It has been reported that shallow junctions with extremely low leakage currents can be formed by a two-step anneal process [2]. Firstly, a low temperature (~500-600 °C) furnace anneal is used to anneal the implantation-induced defects. This is followed by a high temperature RTA to activate the dopants [32].

Previously, "thermal budget" was represented by the product of time, t and the temperature, T. More precisely, in present non-isothermal systems, the thermal budget should denote the area under the t-T curve [33]. Although several thermal budgets can be used to describe the same time-at-temperature to produce shallow junctions, ideally we should anneal at the highest temperature possible for the shortest duration [25].

#### 2.3.1 Transient enhanced diffusion

In recent years, significant progress has been made in quantifying the physical processes involved in transient enhanced diffusion (TED) [4, 34-38]. During TED, the diffusivity of boron may be thousands of times greater than the intrinsic value for a short period of time [36]. The following gives a brief account on TED: when a dopant is introduced into the silicon substrate via ion implantation, the process will inevitably result in implantation-induced damage (Frenkel pairs consisting of vacancies and interstitials) in the silicon substrate. During the initial phase of annealing, as the implanted dopant atoms begin to occupy substitutional sites, most of the vacancies and interstitials recombine, leaving behind a net excess of interstitials with a dose approximately equal to that of the implant [4, 35, 39]. These excess interstitials (EI) quickly coalesce into metastable clusters/extended defects. This is the well-known "+1" model of Giles [39] and has been shown to be an useful approximation for modeling dopant diffusion. Upon further annealing, the extended defects dissolve and release excess interstitials that cause the enhanced diffusivity of dopant atoms (such as B and P) which diffuse either principally or in part by an interstitial(cy) mechanism in silicon [40]. Since the enhanced diffusion is driven by excess interstitials, it is therefore a "transient" process that lasts until the defects dissolve or are annihilated at a defect-sink such as the surface [2].

Based on theoretical calculations, the activation energy of the increase in junction depth is found to be negative when boron diffusion is dominated by the dissolution of interstitial-type defects [34, 35]. This implies that if TED is allowed to run to completion (i.e. complete dissolution of extended defects) at 750 °C, the resulting junction will be deeper than if it was formed at 1000 °C [3, 34]. This is the primary reason why high-temperature

spike anneals with fast ramp-up rates are being adopted for ultra-shallow junction formation.

For the range of implantation dose and energies required to fabricate SDE, Agarwal et al. [3] have illustrated that a point of diminishing return is quickly reached as ramp-up rate increases. This means that when the ramp-up rate is increased to above a certain value, further reduction in junction depth is insignificant. This is due to the limited practical rampdown rate (~70-90 °C/s) of the anneal. Also, for spike anneals with ultra-fast ramp-up rates, the implant damage may not be annealed out during the ramp-up portion, hence TED is delayed from the ramp-up to the ramp-down portion of the thermal cycle [3]. After short, or low-temperature anneals (e.g. 750 °C at 15 s) following implantation of doses greater than  $10^{12}$ /cm<sup>2</sup> but less than the amorphization threshold, extended defects are observed to be primarily of the {311} type. These consist of interstitial agglomerates located on the {311} habit plane and elongated in the <110> direction [4]. This indicates that the source of interstitials for TED is the dissolution of the {311} defects that were formed during the initial stage of annealing. However, it was found that boron TED can also occur in the absence of {311} defects, suggesting that there may be more than one source of interstitials [37]. For high-dose boron ion implantation, it is believed that boron-interstitial clusters (BIC) are the source of interstitials for the enhanced diffusion [38].

In the case where Si was pre-amorphized, a different kind of defect evolution occurs [36, 40]. It is well established that after PAI, there exists a highly damaged region in the crystalline material just beyond the a/c interface [4]. This EOR damaged region contains a supersaturation of interstitial point defects generated during implantation. During the early stage of annealing, EOR loops (with a small fraction of {311} defects) are formed and they continue to grow at the expense of the {311} defects. Upon further annealing (at sufficiently

high temperatures), these EOR loops dissolve and release excess interstitials that induce boron TED [2, 41]. An excellent review on the mechanism of transient enhanced diffusion has been treated in details by Stolk *et al.* [4].

#### 2.4 Laser Thermal Processing

#### 2.4.1 Excimer lasers

Excimer lasers are a family of lasers in which light is emitted by a short-lived molecule that consists of one rare gas atom (e.g. Argon, Krypton or Xenon) and one halogen atom (e.g. fluorine or chlorine). In practice, excimer lasers are excited by passing a short, intense electrical pulse through a mixture of gases containing the desired elements. Normally, more than 90 % of the mixture is a buffer gas (e.g. neon) that does not take part in the reaction [42]. Electrons in the discharge transfer energy to the gases, breaking up halogen molecules and results in the formation of electronically excited molecules. These molecules remain excited for a few nanoseconds and drop to the ground state, emitting a photon in the process. The most developed class of excimer lasers is the rare gas-halide lasers such as ArF, KrF and XeCl with wavelengths of 193, 248 and 308 nm, respectively [42].

#### 2.4.2 Light absorption mechanism and optical properties of silicon

There are a few mechanisms whereby light can be absorbed by semiconductors [43-45]. The absorption (and the heating) mechanism of the lattice depends greatly on the energy of the photon (hv) and the band gap energy ( $E_g$ ) of the semiconductor (e.g. Si). In general, photons with energies larger than the band gap are readily absorbed into the surface regions of the semiconductor. The energy of these photons is transferred to the electronic

system of the substrate, which in turn is transferred to the lattice in a time much shorter than the pulse duration [43]. The resultant energy is then utilized to heat (or even melt) the surface layer such that the temperature of the underlying material is not significantly raised. Since the lasers (XeCl and KrF laser) used in this work produce photons with energies (hv  $\sim$ 4 eV and  $\sim$ 5 eV, respectively) larger than the band gap energy of Si (E<sub>g</sub>  $\sim$ 1.12 eV), we will only consider the absorption mechanism in the case when hv > E<sub>g</sub>.

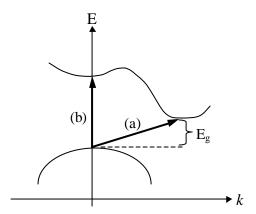

For silicon, the edge of the valence and conduction band is located at different points in momentum, k space. An electronic transition (by optical excitation) between them usually requires the assistance of a phonon to supply the additional momentum. Such a process is known as indirect transition and may occur in two ways [46]: (a) An electron in the valence band absorbs a photon and make a transition to an intermediate state in the conduction band of essentially the same wave vector [45]. Subsequently, a phonon from the lattice is absorbed and the electron transits to the conduction band (refer to Fig. 2.1). (b) The photon may excite an electron from a valence band state directly below the conduction band minimum, with the hole being transferred to the valence band maximum by phonon absorption. The final state is the same in both cases [46].

**Figure 2.1** Schematic band diagram of an indirect band gap material. The heavy arrows symbolize (a) indirect and (b) direct transition [45].

Upon relaxation from a higher energy state in the conduction band, an electron transits back to the valence band and causes a multi-phonon cascade to be emitted in the process [46]. According to the thermal model, the phonon emission process results in the transfer of energy to the lattice and raises its temperature [43, 44]. It should be noted that direct transitions are also possible in indirect band gap materials [45], provided that the photon energy is sufficiently high [47].

In general, since optical wavelengths,  $\lambda$  are considered large compared to atomic distances, the response of a homogenous material to the light wave can be described in terms of averaged macroscopic quantities such as the complex refractive index, m = n + ik [44, 45]. The real part n (refractive index) gives the ratio of the phase velocities in vacuum and in the material, and the imaginary part k (also known as the extinction coefficient) describes the damping of the light wave. A useful measure of the thickness required for the occurrence of significant attenuation of the incident radiation is the optical absorption length,  $\alpha^{-1}$  where  $\alpha$  is the absorption coefficient of the material. For normal beam incidence, the reflectivity, R and  $\alpha$  are related to n and k by [44, 45]:

$$R = \frac{(n-1)^2 + k^2}{(n+1)^2 + k^2}$$

(2.1)

$$a = \frac{4pk}{l} \tag{2.2}$$

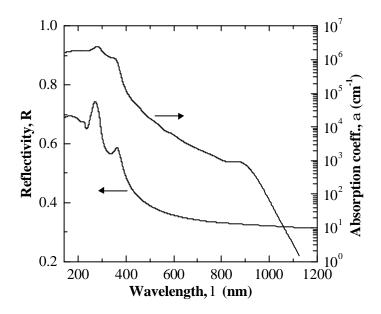

Figure 2.2 shows the room temperature reflectivity and absorption coefficient of crystalline silicon (c-Si) as a function of wavelength. These are computed from the n and k values at various photon energies from the literature [48, 49]. It can be seen that for  $\lambda < Y$ . F. Chong

360 nm,  $\alpha$  is in the order of  $10^6$  cm<sup>-1</sup>, which is several orders of magnitude greater than that at  $\lambda > 540$  nm. Hence, it is desirable to use lasers with  $\lambda < 360$  nm for efficient heating of the substrate by optical absorption such that the laser energy density (fluence) needed to melt the Si surface is not extremely high and can be easily achieved in practice.

Figure 2.2 Reflectivity and absorption coefficient of c-Si at room temperature.

#### 2.4.3 Heat flow calculations

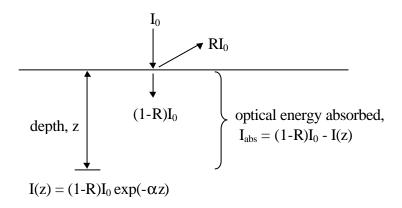

The transformation of electronic excitation into heat energy has been well established for the laser irradiation on metals and semiconductors. It is generally accepted that the absorbed light is instantaneously converted into heat that diffuses according to the conventional heat diffusion equation [43, 50]. For simplicity, it is assumed that the laser beam travels along the z-axis and the target composition is homogenous in this plane. After adding a source term that depends on space and time, t to the conventional heat equation, the one-dimensional heat transfer equation becomes:

$$\mathbf{r}(T)C(T)\frac{\partial T(z,t)}{\partial t} = \frac{\partial}{\partial z} \left[ K(T)\frac{\partial T(z,t)}{\partial z} \right] + \mathbf{a}(1-R)I_0(t)\exp(-\mathbf{a}z)$$

(2.3)

where T = temperature,  $\rho(T)$  = density, C(T) = specific heat capacity, K(T) = thermal conductivity, R = reflectivity of the substrate,  $\alpha$  = absorption coefficient of the substrate material, and  $I_0(t)$  = laser intensity upon reaching the substrate surface.

As shown in Eqn. (2.3), the interaction of lasers with materials is a complex phenomenon and can be affected by a variety of parameters. A lot of effort has been made to obtain numerical solutions to Eqn. (2.3) to determine the temperature distribution profiles and the melt kinetics during laser processing [43, 45]. The surface thermal field induced by pulsed laser irradiation of Si is not due to heat diffusion alone, but also depends on the penetration depth of the laser light [45, 51]. The laser heating process is affected by the absorption length,  $\alpha^{-1}$  and the heat diffusion length,  $L_T = \sqrt{2D_h t_p}$  where  $t_p$  is the laser pulse duration and  $D_h = \frac{K(T)}{\mathbf{r}(T)C(T)}$  is the thermal diffusivity. There are two limiting cases, depending on whether  $L_T > \alpha^{-1}$  or  $L_T < \alpha^{-1}$ . For  $L_T > \alpha^{-1}$ , the laser pulse behaves like a surface source such that the average increase in the surface temperature as a function of time is given by [51]:

$$\Delta T(t) \approx \frac{(1-R)I_0(t)}{K} \sqrt{\frac{D_h t_p}{2}}$$

(2.4)

When  $L_T < \alpha^{-1}$ ,

$$\Delta T(t) \approx \frac{(1 - R)I_0(t)\mathbf{a} \exp(-\mathbf{a}z)t_p}{\mathbf{r}C}$$

(2.5)

For a 248 nm laser irradiation on c-Si with  $t_p = 23$  ns at T = 300 K,  $L_T \sim 2$  µm and  $\alpha^{-1} \sim 5.6 \times 10^{-3}$  µm. This indicates that the conduction of heat into the substrate after surface absorption plays an important role during LTP. The optical (at  $\lambda = 248$  nm) and thermophysical properties of c-Si and amorphous silicon (a-Si) are shown in Tables 2.1 and 2.2, respectively. These are obtained either directly from the literature or through a best-fit procedure of literature experimental data [48-57]. In order to simplify the heat-flow calculations, the solid-state reflectivity and absorption coefficient are typically assumed to be constant with temperature. The simplification for  $\alpha$  is justified because the absorption coefficient of Si at a wavelength of 248 nm is so high ( $\alpha > 10^6$  cm<sup>-1</sup>) that it is believed that any changes in  $\alpha$  with temperature is insignificant [50]. It is noted that the absorption coefficient of silicon at  $\lambda = 308$  nm is within the same magnitude to that at  $\lambda = 248$  nm.

**Table 2.1** Optical (at  $\lambda = 248$  nm) and thermophysical properties of c-Si.

| Properties                                           | c-Si                                                                                                 | Comments                               |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------|

| Melting point, T <sub>c</sub> (K)                    | 1683                                                                                                 | From [48, 51, 52]                      |

| Boiling point (K)                                    | 3538                                                                                                 | From [48]                              |

| Thermal conductivity,                                | 1585/T <sup>1.229</sup> (for T<1371 K)                                                               | From [53, 54] and derived              |

| K <sub>c</sub> (W/cm K)                              | 0.221 (1371 < T < 1683 K)                                                                            | from [48, 55]                          |

|                                                      | 1.4 (T > 1683 K)                                                                                     | From [53]                              |

| Volume heat capacity (J/cm³ K)                       | $1.99 + 2.54 \times 10^{-4} \text{T} -$ $3.68 \times 10^{4} / \text{T}^{2} \text{ (for T < 1683 K)}$ | From [54] and derived from [48]        |

|                                                      | 2.49 (T > 1683 K)                                                                                    | Calculated from [56]                   |

| Reflectivity, R                                      | 0.67 (T < 1683 K)                                                                                    | From [48, 54] and calculated from [49] |

|                                                      | 0.70 (T > 1683 K)                                                                                    | From [45, 57]                          |

| Absorption coefficient, $\alpha$ (cm <sup>-1</sup> ) | $1.81 \times 10^6  (T < 1683  K)$                                                                    | From [54] and calculated from [48, 49] |

|                                                      | $1.93 \times 10^6  (T > 1683  \text{K})$                                                             | Calculated from [57]                   |

| Latent heat of melting, $L_{c}  (\text{J/cm}^{3})$   | 4192                                                                                                 | From [53] and derived from [51, 52]    |

**Table 2.2** Optical (at  $\lambda = 248$  nm) and thermophysical properties of a-Si.

| Properties                                       | a-Si                                                                                                  | Comments                                                                             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Melting point, T <sub>a</sub> (K)                | 1420                                                                                                  | From [52, 58, 59]. A range of values can be found.                                   |

| Thermal conductivity,  K <sub>a</sub> (W/cm K)   | 0.018 (T < 1420 K)                                                                                    | Average value from room temperature to melting point [51, 52].                       |

|                                                  | 1.4 (T > 1420 K)                                                                                      | From [53]                                                                            |

| Volume heat capacity (J/cm <sup>3</sup> K)       | $2.06 + 2.64 \times 10^{-4} \text{T} - $ $3.82 \times 10^{4} / \text{T}^{2} \text{ (for T < 1420 K)}$ | Assuming C and p of a-Si is 10% greater and 6% less than c-Si respectively [51, 60]. |

|                                                  | 2.49 (T > 1420 K)                                                                                     | Calculated from [56]                                                                 |

| Reflectivity, R                                  | 0.55 (T < 1420 K)<br>0.70 (T > 1420 K)                                                                | Calculated from [49] From [45, 57]                                                   |

| Absorption coefficient,<br>α (cm <sup>-1</sup> ) | $1.40 \times 10^6 \text{ (T < 1420 K)}$<br>$1.93 \times 10^6 \text{ (T > 1420 K)}$                    | Calculated from [49] Calculated from [57]                                            |

| Latent heat of melting, $L_a$ (J/cm $^3$ )       | 3076                                                                                                  | Derived from [51, 52]                                                                |

One important property of a-Si is that it exists as a unique phase and melts at a discrete temperature that is  $225 \pm 50$  °C lower than the melting point of crystalline Si [58, 59, 61]. This is due to the fact that a-Si is in a higher free energy state compared to c-Si and that the transformation from the amorphous to liquid state is a first-order phase transition [58, 62]. It was further suggested that this transition is possible because it involves a change in bonding from the covalent, amorphous phase with four-fold coordination to the metallic

liquid phase with (11 to 12)- fold coordination [58]. It should be recognized that this kind of phase transition will only occur during very rapid heating conditions, otherwise the amorphous phase will recrystallize directly in the solid phase [50]. Another important property of a-Si is that its thermal conductivity (K<sub>a</sub>) in the solid state is very low, with an average value (from room temperature to melting point, T<sub>a</sub>) of 0.018 W/cm K. This value is between one and two orders of magnitude smaller than the temperature dependent (K<sub>c</sub>) of c-Si for temperatures below 1420 K [51, 52].

### 2.4.4 Laser irradiation of an a-Si overlayer on c-Si

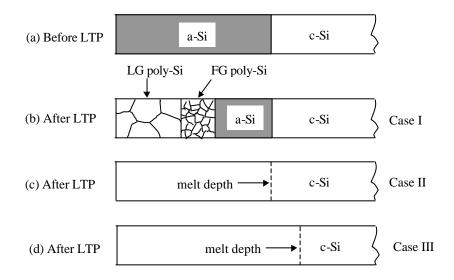

Important insight into the kinetics and thermodynamics of the phase transformations involved in LTP has been obtained from earlier investigations on laser irradiation of a-Si [43, 59, 61-64]. In general, the structural changes induced by laser irradiation of an a-Si layer on c-Si can be characterized by three cases. Case I: the laser fluence, E<sub>i</sub> is only slightly greater than the threshold fluence, E<sub>h</sub> for melting a-Si. In this case, the primary melt (molten layer produced directly by laser irradiation) does not penetrate through the entire a-Si layer. Typically, large-grained (LG) poly-Si will be formed at the near surface region followed by fine-grained (FG) poly-Si in the underlying region [Fig. 2.3 (b)]. The fraction of the LG region will increase at the expense of FG region with increasing fluence - a result of explosive crystallization [50, 59]. Explosive crystallization is a complex solidification process whereby the decay of the amorphous phase is accelerated by the feedback of the latent heat that is released during crystallization. At low energy densities where the laser does not melt the entire amorphous layer, the liquid Si (l-Si) will solidify as poly-Si and releases latent heat in the process [50, 59].

**Figure 2.3** Illustration of the structural changes induced by laser irradiation of an a-Si overlayer on c-Si.