# DEVELOPMENT OF HIGH MOBILITY CHANNEL LAYER FORMATION TECHNOLOGY FOR HIGH SPEED CMOS DEVICES

**OH Hoon Jung**

NATIONAL UNIVERSITY OF SINGAPORE 2010

# DEVELOPMENT OF HIGH MOBILITY CHANNEL LAYER FORMATION TECHNOLOGY FOR HIGH SPEED CMOS DEVICES

**OH Hoon Jung**

(B. Sc., Ewha Womans University, Korea) (M. Sc., Ewha Womans University, Korea)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2010

## **ACKNOWLEDGEMENTS**

Growth means change and change involves risk, stepping from the known to the unknown. - Author unknown

I chose NUS to pursue a Ph.D. in 2005 with luck when I had worked for 11 years and become an effective being in the company regardless of my will. Because, studying abroad has been one of my lifelong dreams. At least, I made the decision then because of that. However, at this moment when I am at the end of the course, I come to know that the journey was prepared only for me to grow along the way by the God. The Ph.D. course was so different from my expectations, but it was full of changes and thanks that I had never imagined. During my time at Silicon Nano Device Laboratory (SNDL), NUS in Singapore, I have learned so many things not only about the MOSFETs and semiconductor engineering but also about the values of spiritual virtues such as love, passion, patience, faith, and truth again. I will never forget the happiest moments when the unknown suddenly changes to the known in the lecture theater, in front of the Jusung Gate Cluster, in the seat of #151 bus, and so on... And there are so many people whom I thank for their kind help, insightful discussion, teaching, and shaping me during the past five years.

I would like to begin to acknowledge my supervisors, Prof. Lee Sungjoo and Prof. Chua Soo Jin for their insightful guidance and sincere concern throught my graduate course. I would especially like to thank Prof. Lee Sungjoo for his time, concern, and giving me the opportunity to research this interesting field.

I am also grateful to Prof. Cho Byung Jin for offering me the opportunity to join SNDL as a staff and his heartful supervision as my advisor before his leaving NUS. In addition, I would like to thank SNDL academic staffs, Prof. Samudra, Prof, Zhu, Prof. Yeo, Prof. Daniel Chan, Prof. Tan, and Prof. Albert Liang for their support and help for me to work in SNDL. My special thanks go to Mr. Yong, Mr. O Yan, Patrick, Boon Teck, and Mr. Sun for their kind help and sharing their invaluable experiences in frequent collaborations.

It was definitely a privilege to work with Wan Sik, Sung Jin, and Kyu Jin. I cannot imagine how I worked and pursued Ph.D simultaneously, if they were not there and then. I am also grateful to their wives, Hae Hyun, Mi Hea, and Soo Hyung.

I would like to thank my SNDL collegues, Sumarlina, Jian Qiang, Goutam, Gao Fei, Li Rui, Weifeng, Aadi, Wangjian, Tong Yi, Wei Yip, Zang Hui, He Wei, Pu Jing, Lina, Andy, Rinus, Hock Chun, Xinke, Shen Chen, Wu Nan, Xinpeng, Dr. Zhu Ming, Dr. Han, Jianjun, Chunfu, Ruilong, Manu, Hoong Shing, Zhang Lu, Eric, Jingde, Jiang Yu, Chia Ching, and Dr. Samanta for sharing their knowledge and hearts.

I met many kind and competent people in NUS. I am greateful to Thwin Htoo, Musni, Jade, Jane, Dr. Zhang, Kelly, Dr. Yuan, and Samantha not only for help in my research work but also for the earnest conversations. In addition, I would like to thank IMRE staffs, Mona, Dr. Chi, Dr. Debbie, Doreen, Yi Fan, and Siew Lang for their obliging support on my experiments in IMRE.

My very special thanks go to Ryan, who is my special cousin, for his care, the endless discussion about our lives, and, above all, being with me.

Lastly, but not the least, I would like to give my big thanks to my parents and sisters, Hoon Young and Hun Kyeong, who have been always supportive and encouraging throughout the Ph. D. course. Any words of acknowledgement are not enough to express my deepest gratitude to my parents. Their continuous love, sacrifice, support, encouragement, and prayer have allowed me to pursue my way...! Thank God.

## **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS             | i    |

|------------------------------|------|

| TABLE OF CONTENTS            | iii  |

| ABSTRACT                     | vi   |

| LIST OF TABLES               | viii |

| LIST OF FIGURES              | ix   |

| LIST OF SYMBOLS AND ACRONYMS | XV   |

### **CHAPTER 1** INTRODUCTION

| 1.1    | CMOS S   | Scaling Beyond the 10 nm Node               | 3  |

|--------|----------|---------------------------------------------|----|

|        | 1.1.1    | Overview of MOSFET Scaling                  | 3  |

|        | 1.1.2    | ITRS Projections                            | 8  |

|        | 1.1.3    | Challenges for Further Scaling              | 8  |

| 1.2    | Approac  | whes for Scaling Beyond the 10 nm Node      | 13 |

|        | 1.2.1    | High-k Gate Dielectrics and Metal Gate      | 13 |

|        | 1.2.2    | Non-planar MOSFET Structure                 | 16 |

|        | 1.2.3    | Mobility Enhancement Techniques             | 20 |

|        | 1.2.4    | Advanced Channel Material Engineering       | 23 |

| 1.3    | Motivat  | ion and Objectives                          | 28 |

| 1.4    | Thesis ( | Dutline and Original Research Contributions | 31 |

| Refere | nces     |                                             | 33 |

### CHAPTER 2 INTEGRATION OF GaAs EPITAXIAL LAYER ONTO Si-BASED SUBSTRATE

| 2.1 | Introdu | action                                                      | 43 |

|-----|---------|-------------------------------------------------------------|----|

|     | 2.1.1   | Background and Motivation                                   | 44 |

|     | 2.1.2   | Approaches for Heteroepitaxy of High Mobility Channel on Si | 45 |

|     | 2.1.3   | Objective                                                   | 48 |

| 2.2 | GaAs ]  | MBE growth on Si(100) via Strained SiGe                     | 48 |

|     | 2.2.1   | Introduction                                                | 48 |

|        | 2.2.2    | Experiment                                               | 49 |

|--------|----------|----------------------------------------------------------|----|

|        | 2.2.3    | Results and Discussion                                   | 50 |

|        | 2.2.4    | Conclusion                                               | 52 |

| 2.3    | Concept  | t of GaAs Heteroepitaxy on a Compositionally Graded SGOI | 52 |

| 2.4    | Fabricat | tion of Graded SGOI substrate for GaAs Heteroepitaxy     | 54 |

|        | 2.4.1    | Introduction                                             | 54 |

|        | 2.4.2    | Modified Two-step Ge Condensation Method                 | 54 |

|        | 2.4.3    | Results and Discussion                                   | 57 |

|        | 2.4.4    | Conclusion                                               | 59 |

| 2.5    | GaAs H   | eteroepitaxy on the Graded SGOI                          | 60 |

|        | 2.5.1    | MBE Heteroepitaxy Technique                              | 60 |

|        | 2.5.2    | Experiment                                               | 63 |

|        | 2.5.3    | Results and Discussion                                   | 63 |

|        | 2.5.4    | Conclusion                                               | 68 |

| 2.6    | Summa    | ry                                                       | 68 |

| Refere | ences    |                                                          | 70 |

### CHAPTER 3 HIGH MOBILITY CHANNEL NMOSFET INTEGRATED WITH HIGH-*K*/METAL GATE

| 3.1 | Introdu | ction      |                                                       | 74    |

|-----|---------|------------|-------------------------------------------------------|-------|

|     | 3.1.1   | Motivatio  | on                                                    | 74    |

|     | 3.1.2   | GaAs-bas   | sed III-V MOSFET and Fermi Level Pinning              | 76    |

|     | 3.1.3   | Objective  |                                                       | 79    |

| 3.2 | Process | Optimizat  | ion by Material Characterization                      | 80    |

|     | 3.2.1   | MOCVD      | High-k Deposition                                     | 80    |

|     |         | 3.2.1.1    | HfO <sub>2</sub>                                      | 81    |

|     |         | 3.2.1.2    | HfAlO                                                 | 84    |

|     | 3.2.2   | GaAs-bas   | sed III-V/Hf-based High-k Interface                   | 87    |

|     |         | 3.2.2.1    | Chemical and Physical Properties of Interfaces        | 88    |

|     |         | 3.2.2.2    | Band Alignment of Hf-based High-k on GaAs-based III-V | ' 92  |

| 3.3 | Process | Optimizat  | ion by Electrical Characterization                    | 96    |

|     | 3.3.1   | Fabricatio | on Procedure of MOSFET                                | 97    |

|     | 3.3.2   | S/D Char   | acteristics                                           | 99    |

|     | 3.3.3   | Surface C  | Cleaning Effect                                       | . 101 |

|       | 3.3.4   | III-V Substrate Effect                                 | 103           |

|-------|---------|--------------------------------------------------------|---------------|

| 3.4   | High N  | Mobility III-V NMOSFET Integrated with High-k/Metal Ga | te in A Self- |

|       | alignee | d Scheme                                               | 105           |

|       | 3.4.1   | Gate Stack                                             | 106           |

|       | 3.4.2   | Performance of MOSFET                                  | 106           |

| 3.5   | Conclu  | usion                                                  | 110           |

| Refer | ences   |                                                        | 112           |

### CHAPTER 4 NOVEL SURFACE PASSIVATION FOR FUTURE HIGH-SPEED CMOS DEVICE APPLICATION

| 4.1   | Introdu | iction                                                                                     | 119 |

|-------|---------|--------------------------------------------------------------------------------------------|-----|

|       | 4.1.1   | Surface Passivation for InGaAs/High-k Interface                                            | 119 |

|       | 4.1.2   | Overview of Passivation Techniques                                                         | 121 |

|       | 4.1.3   | Concept of Approach and Objective                                                          | 124 |

| 4.2   | Experin | ment                                                                                       | 125 |

|       | 4.2.1   | PH <sub>3</sub> -based Passivation Conditions                                              | 125 |

|       | 4.2.2   | In situ High-k Integration and Device Fabrication                                          | 128 |

| 4.3   | Results | s and Discussion                                                                           | 129 |

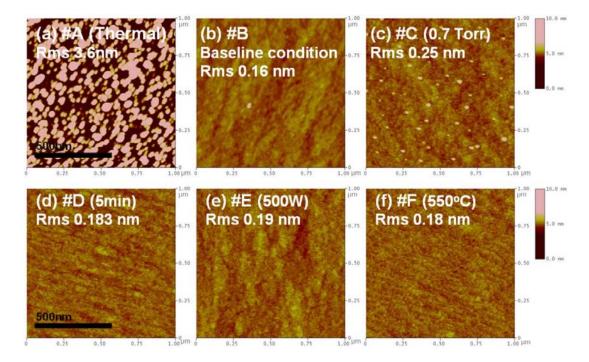

|       | 4.3.1   | Morphology of the Passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As                      | 129 |

|       | 4.3.2   | Chemistry of the PH3-based Passivation Layer on In0.53Ga0.47                               | 7As |

|       |         | Surface                                                                                    | 130 |

|       | 4.3.3   | Chemistry of the $P_x N_y$ Passivation Layer on $In_{0.53}Ga_{0.47}As$ Surface             | 137 |

|       | 4.3.4   | MOSFET Characteristics of the Passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As/High-k/T | 'aN |

|       |         | Gate Stack                                                                                 | 147 |

|       | 4.3.5   | Thermal Stability of Phosphorus Nitride Passivated Gate Stack                              | 156 |

| 4.4   | Conclu  | ision                                                                                      | 161 |

| Refer | ences   |                                                                                            | 163 |

### CHAPTER 5 CONCLUSIONS AND FUTURE RESEARCHES

| 5.1     | Conclusion                        | 170 |

|---------|-----------------------------------|-----|

| 5.2     | Suggestions for Future Researches | 174 |

| Referen | nces                              | 177 |

### ABSTRACT

As the gate length of complementary metal-oxide-semiconductor field-effect transistor (CMOSFET) approaches ~10 nm regime, the traditional Si CMOS scaling faces its fundamental limits. Among the proposed technical solutions, GaAs-based III-V compound semiconductors are actively being studied as a possible alternative for a high speed n-channel MOSFET (NMOSFET) due to their low effective electron masses, high electron mobilities, the accumulated knowledge, and the difficulty in Ge NMOSFET realization. However, the III-V MOSFET technology should address several critical issues with the device realization. The challenges include how to integrate a high quality III-V channel layer into Si platform and how to achieve the thermally stable III-V/high-*k* interface without Fermi level pinning.

In the first part of this thesis, novel approaches for GaAs-on-insulator (GaAs-OI) fabrication technology were explored to overcome the physical and technical challenges in growing the GaAs heteroepitaxial layer in Si platform. The cost-effective Ge-condensation technique was developed to provide a compositionally graded SiGeon-insulator (SGOI) as a virtual substrate for the GaAs heteroepitaxy on Silicon-oninsulator (SOI). A modified two-step Ge-condensation resulted in 42 nm thick SGOI with 71 % Ge concentration on top of the SGOI with an excellent crystalline quality. For the first time, a device quality GaAs-OI structure has been realized on a Si wafer through the graded SGOI virtual substrate using molecular beam epitaxy with introduction of migration-enhanced epitaxy technique.

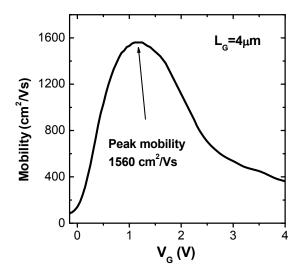

In the second part of this thesis, fabrication processes were developed to realize the NMOSFET integrated with metal-organic chemical vapor deposited (MOCVD) Hf-based high-*k*/metal gate stack on a GaAs-based III-V channel in a self-aligned gatefirst fabrication scheme. The main process steps included pre-deposition cleaning,  $HfO_2$  and HfAlO MOCVDs, and Si implanted n<sup>+</sup> S/D formation processes. The focus was on improving III-V/high-*k* interface quality to mitigate Fermi level pinning issue. Electrical properties were investigated to optimize the material combinations and processes further. Consequently, enhancement mode NMOSFET with ~3 times higher peak mobility over the universal mobility of Si has been demonstrated with MOCVD HfAlO/TaN gate stack on  $In_{0.53}Ga_{0.47}As$  channel.

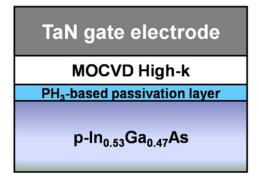

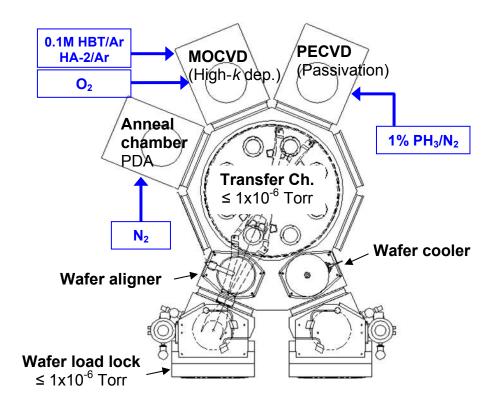

Finally, a Si-compatible passivation technique using *in situ* PH<sub>3</sub> treatment is proposed, explored and investigated to improve the InGaAs NMOSFET performance. It was found that at low pressure PH<sub>3</sub>-N<sub>2</sub> plasma condition, a 1 monolayer thick phosphorus nitride ( $P_xN_y$ ) layer is formed with an underlying P-for-As exchanged layer as a minor product on InGaAs substrate in a wide range of process window. The improved interface quality of the  $P_xN_y$ -passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As is identified and compared with the non-passivated InGaAs and PH<sub>3</sub>-based passivated InGaAs without  $P_xN_y$  layer with chemical and physical properties. The  $P_xN_y$  passivation greatly improved electrical properties of the InGaAs MOSFET devices. Technology demonstration with this novel  $P_xN_y$  passivation achieved the low subthreshold slope approaching the ideal value of 60 mV/dec as well as the significantly enhanced peak mobility in the inversion layer of ~5 times the universal Si mobility at the corresponding low field. Thermal stability of the  $P_xN_y$ -passivated interface was examined up to 750 °C with the self-aligned InGaAs/HfO<sub>2</sub> MOSFET devices by activating the S/D at different temperatures.

## LIST OF TABLES

| Table 1.1 | High-performance (HP), low-operating power (LOP), and low<br>standby power (LSTP) logic technology requirements where the                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | transistor type is a planar bulk CMOSFET. [10]9                                                                                                                                                               |

| Table 1.2 | High-performance (HP) logic technology requirements where the transistor types include the UTB FDSOI and multiple-gate                                                                                        |

|           | CMOSFET as well as the planar bulk structure. [10]                                                                                                                                                            |

| Table 1.2 | 1 6 3                                                                                                                                                                                                         |

| Table 1.5 | Physical and electrical parameters of selected semiconductors [56]25                                                                                                                                          |

| Table 2.1 | Material properties of Si, Ge, and GaAs at room temperature [13]47                                                                                                                                            |

| 14010 2.1 |                                                                                                                                                                                                               |

| Table 3.1 | Fabrication process and condition for long channel GaAs NMOSFET 98                                                                                                                                            |

| Table 4.1 | In <sub>0.53</sub> Ga <sub>0.47</sub> As surface passivation conditions using 1% PH <sub>3</sub> /N <sub>2</sub> treatment                                                                                    |

| Table 4.2 | Summary of relative intensities of different XPS core level emissions from substrate elements and the binding types of As at the passivated $In_{0.53}Ga_{0.47}As$ surfaces. The As 3d and Ga 3d peaks were   |

|           | decomposed into different binding types and core levels without<br>spin-orbit splitting. The number in parenthesis refers to the chemical<br>shift from a main As-Ga/In component and the difference of BE of |

|           | the decomposed emissions for As 3d and Ga 3d, respectively                                                                                                                                                    |

| Table4.3  | Interface state density $(D_{it})$ estimated by Hill's conductance method                                                                                                                                     |

| 1 00104.3 | for $In_{0.53}Ga_{0.47}As$ /HfO <sub>2</sub> /TaN MOSFET with different PH <sub>3</sub> -based                                                                                                                |

|           |                                                                                                                                                                                                               |

|           | passivations154                                                                                                                                                                                               |

## **LIST OF FIGURES**

| Fig. 1.1  | Schematic of a Si NMOSFET structure. Gate dimension is defined by the gate length, $L_G$ , the gate width, $W_G$ , and the thickness of gate |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

|           | dielectric, $d$ . If a large positive voltage is applied to $V_G$ , the p-type Si                                                            |

|           | surface under the gate $(W_G \times L_G)$ is inverted and a conductive n-type                                                                |

|           | channel is induced connecting the source and the drain2                                                                                      |

| Fig. 1.2  | Illustration of Moore's Law: The number of microprocessor transistors                                                                        |

|           | by year. [5]4                                                                                                                                |

| Fig. 1.3  | (a) Gate length, $L_G$ and (b) gate oxide thickness, $T_{ox}$ changes in                                                                     |

|           | production MOSFET by year [5]                                                                                                                |

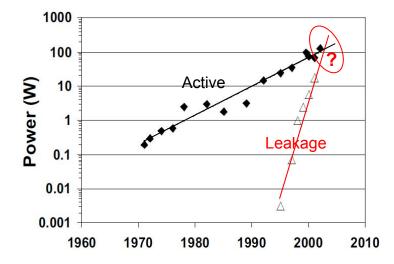

| Fig. 1.4  | Increasing power dissipation trend, which is illustrated from active                                                                         |

|           | power and standby power, i.e. leakage by production year from                                                                                |

|           | industry data. Traditional scaling will not be valid near the cross over                                                                     |

|           | point drawn by the extrapolations. [5]                                                                                                       |

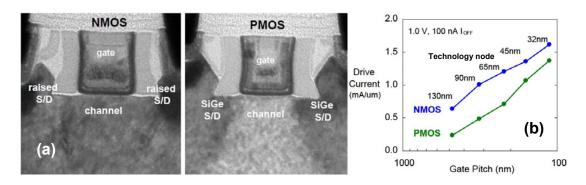

| Fig. 1.5  | (a) Cross section of NMOS and PMOS transistors showing high-                                                                                 |

|           | <i>k</i> /metal gate, raised and embedded S/D regions in 32 nm logic                                                                         |

|           | technology. (b) $I_D$ as a function of gate pitch (length for one gate and                                                                   |

|           | one S/D contact). [8]7                                                                                                                       |

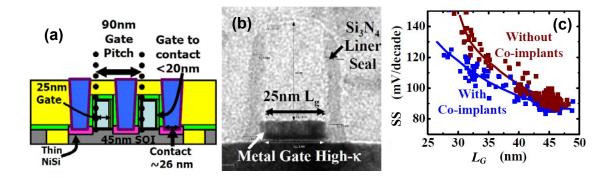

| Fig. 1.6  | (a) Cross section view of a MOSFET at 22 nm node dimensions. (b)                                                                             |

|           | TEM image of the gate stack (c) SS measurement showing gate length                                                                           |

|           | scaling with S/D engineering effect [9]7                                                                                                     |

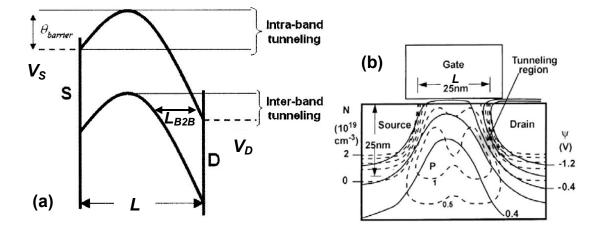

| Fig. 1.7  | (a) Band diagram in the off-state of an extremely scaled MOSFET                                                                              |

|           | indicating quantum mechanical tunneling mechanism. [12] (b)                                                                                  |

|           | Advanced 25 nm gate-length FET structure showing the BTBT                                                                                    |

|           | tunneling region. Solid contours are electrostatic potential, in 0.2 V                                                                       |

|           | intervals, and dashed contours indicate doping, in 5x10 <sup>18</sup> cm <sup>-3</sup> intervals                                             |

|           | with open contours being n- type and closed contours p-type. Region                                                                          |

|           | of the shortest tunneling distance is shaded. [13]11                                                                                         |

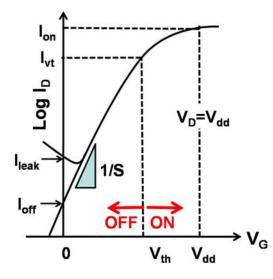

| Fig. 1.8  | Schematic $I_D$ - $V_G$ characteristic in log scale showing the factors                                                                      |

|           | affecting electrical parameter requirements                                                                                                  |

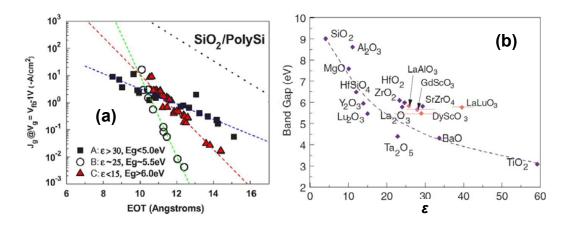

| Fig. 1.9  | (a) $J_G$ as a function of EOT for three different high-k layers with                                                                        |

|           | various dielectric constants (shown as $\varepsilon$ ) and $E_g$ [18]. (b) $E_g$ vs $\varepsilon$ for                                        |

|           | candidate high-k oxides for MOSFET scaling [20]14                                                                                            |

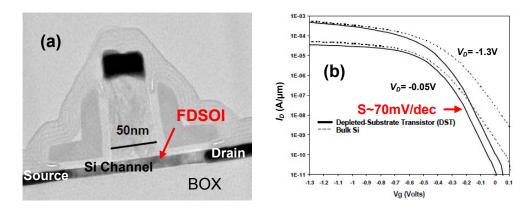

| Fig. 1.10 | (a) TEM image of UTB FDSOI transistor (b) $I_D$ - $V_G$ characteristics of                                                                   |

|           | the UTB FDSOI PMOSFET with the gate length of 70 nm in                                                                                       |

|           | comparison with bulk Si PMOSFET. [35]                                                                                                        |

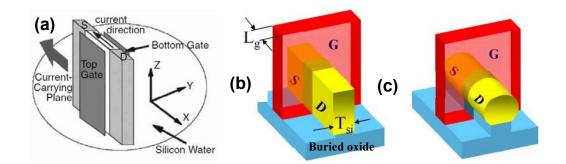

| Fig. 1.11 | 1 6 ()                                                                                                                                       |

|           | FET [11], (b) triple-gate, and (c) nanowire FinFET structure. [47]18                                                                         |

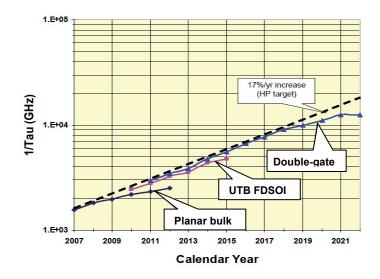

| Fig. 1.12 |                                                                                                                                              |

|           | different MOSFET structures. [10]                                                                                                            |

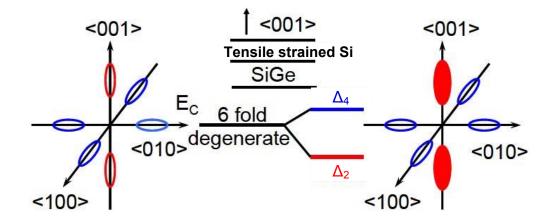

| Fig. 1.13 | Strain effect on conduction sub-bands of (001)Si21                                                                                           |

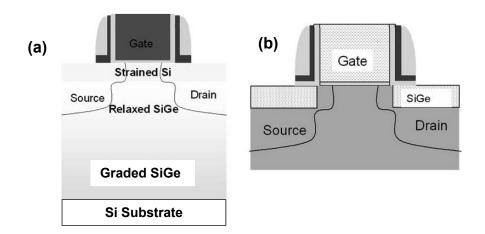

| Fig. 1.14 |                                                                                                                                              |

|           | channel transistor and (b) local SiGe stressor next to gate. [47] 22                                                                         |

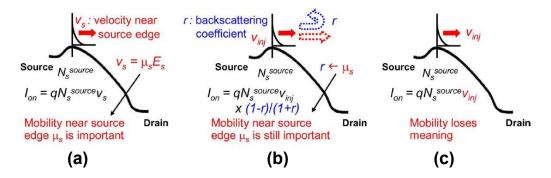

| Fig. 1.15 | Illustrations of carrier transport models to determine $I_{on}$ ( $I_{Dsat}$ ) as                                                            |

|           | varying the channel length based on the scattering theory [55]. (a)                                                                          |

|           | Conventional transport in a long channel MOSFET. (b) Quasi-ballistic                                                                         |

|           | transport model for a short channel MOSFET. (c) Full ballistic                                                                               |

|           | transport model for an extremely short channel MOSFET [46]24                                                                                 |

| - |   | ü | , |  |

|---|---|---|---|--|

|   | l |   | • |  |

|   |   |   |   |  |

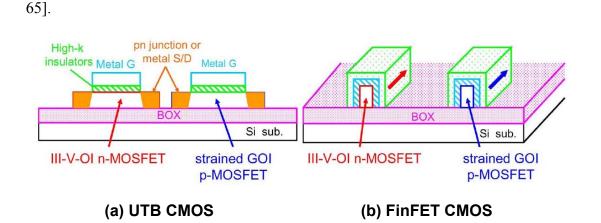

| Fig. 1.16 | Ultimate CMOS structure composed of III-V NMOSFET and Ge<br>PMOSFET [46]. (a) UTB platform (b) Multiple-gate architecture<br>CMOS                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

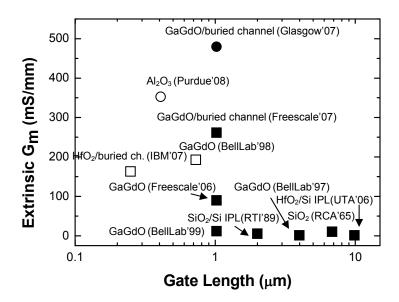

| Fig. 1.17 |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

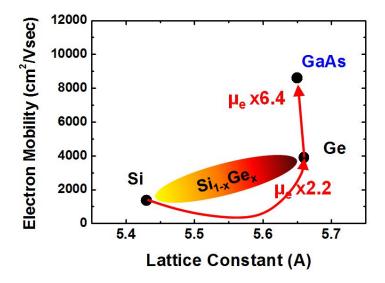

| Fig. 2.1  | Illustration of GaAs heteroepitaxial growth via compositionally graded $Si_{1-x}Ge_x$ buffer layer to overcome the lattice mismatch between GaAs and Si. The guide line is drawn schematically referring to experimental data of electron Hall mobility for unstrained $Si_{1-x}Ge_x$ at 300K [12]47                                                                                                                                                |

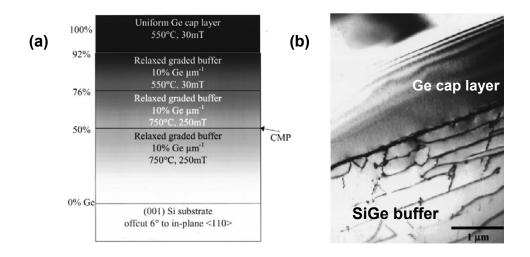

| Fig. 2.2  | <ul><li>(a) Schematic of the structure for optimized Ge heteroepitaxy on Si via graded SiGe buffer layers. Ge concentrations are indicated on the left.</li><li>(b) Cross-sectional TEM image of the upper graded region [10]</li></ul>                                                                                                                                                                                                             |

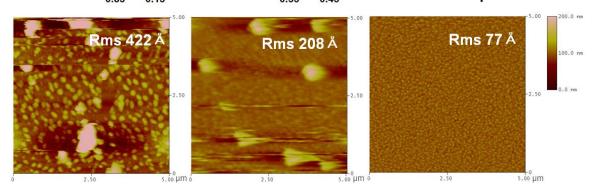

| Fig. 2.3  | AFM images of GaAs grown on strained $Si_{1-x}Ge_x/Si$ substrate for $x=0.15, 0.45, and 1$                                                                                                                                                                                                                                                                                                                                                          |

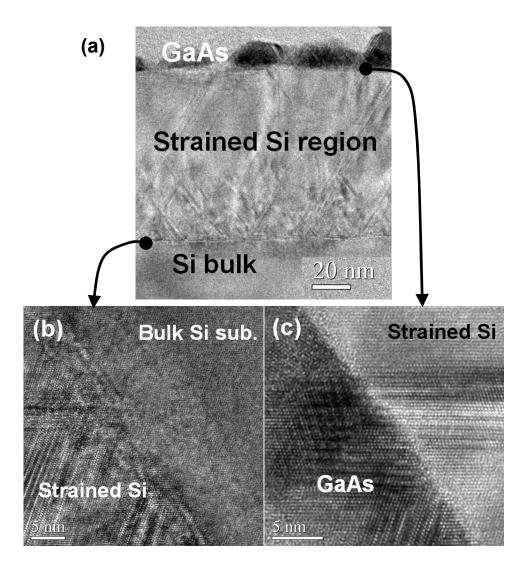

| Fig. 2.4  | TEM images of GaAs grown on strained Ge epi/Si substrate. GaAs<br>MBE growth on the Si substrate results in island structures and a<br>discrete Si layer with dislocation defects. (a) TEM image in a low<br>magnification. (b) TEM image of the lower interface. (c) A high<br>magnification TEM image of the interface between GaAs and Si                                                                                                        |

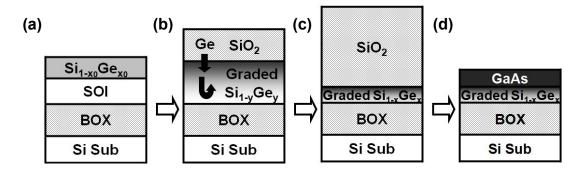

| Fig. 2.5  | Process flow of the fabrication of GaAs heteroepitaxial layer on a graded SGOI prepared by a Ge condensation method. (a) SiGe epilayer growth on SOI with low Ge concentration, $x_0$ . (b) Ge condensation during oxidation. (c) Oxidation stops when graded SGOI is accomplished with high Ge concentration on the top of the SGOI layer. (d) After removing the top SiO <sub>2</sub> layer, MBE GaAs epitaxial layer is grown on the graded SGOI |

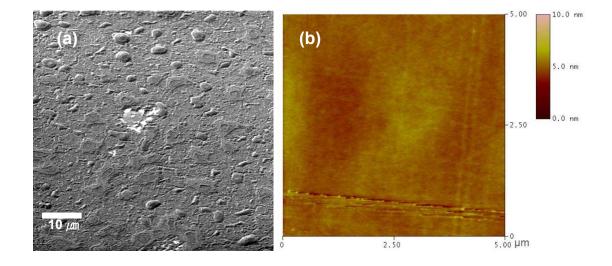

| Fig. 2.6  | Major issues in conventional Ge condensation: Scanning electron<br>microscope (SEM) image of agglomeration (a) and AFM image of<br>crosshatch patterned surface (b) after the conventional Ge<br>condensation                                                                                                                                                                                                                                       |

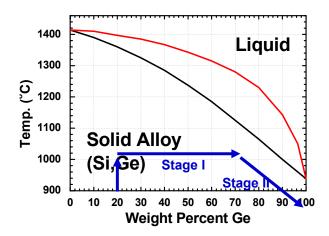

| Fig. 2.7  | Schematic illustration of a temperature profile for the two-step Ge condensation with a phase diagram of Si-Ge alloy                                                                                                                                                                                                                                                                                                                                |

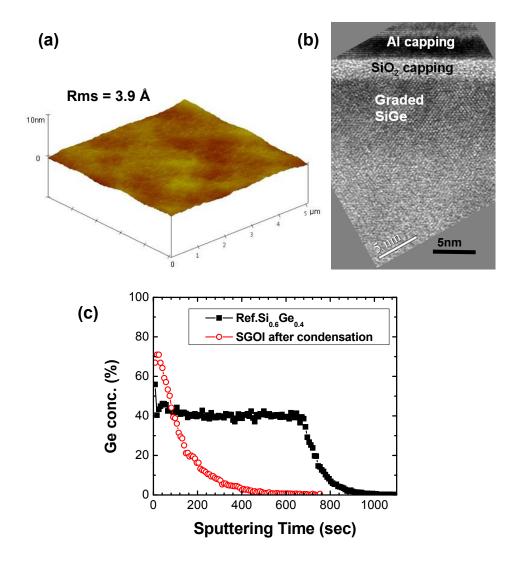

| Fig. 2.8  | Modified two-step Ge condensation result; (a) AFM image of graded SGOI after removal of SiO <sub>2</sub> grown during the oxidation. (b) TEM result of the graded SGOI of 42nm thickness. (c) SIMS depth profile of the graded SGOI. Ge concentration at the surface is around 71%                                                                                                                                                                  |

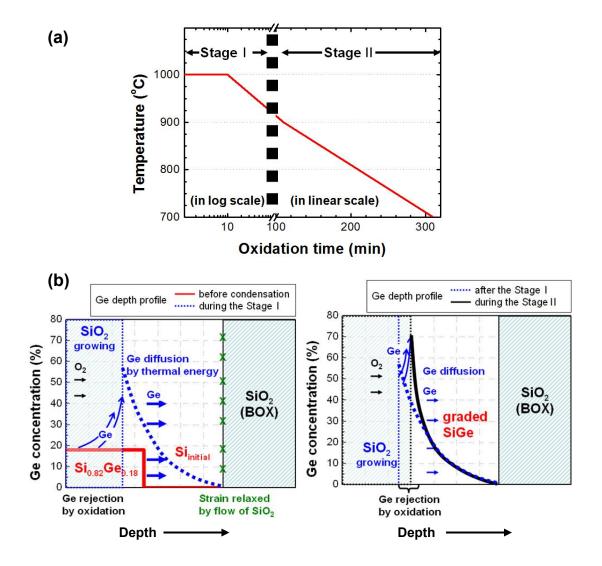

| Fig. 2.9  | (a) Schematic illustration of the modified two-step Ge condensation<br>oxidation recipe. (b) Schematic drawing of the film structure with Ge<br>profile at each stage                                                                                                                                                                                                                                                                               |

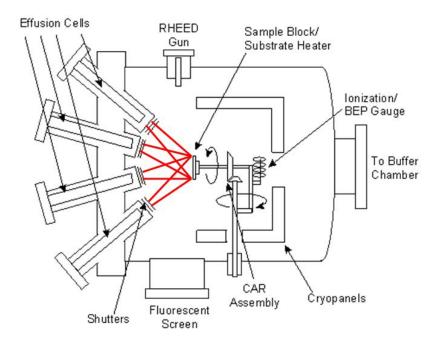

| Fig. 2.10 | Schematic of an MBE growth chamber showing the beam nature of particle flow from the effusion cell to the substrate                                                                                                                                                                                                                                                                                                                                 |

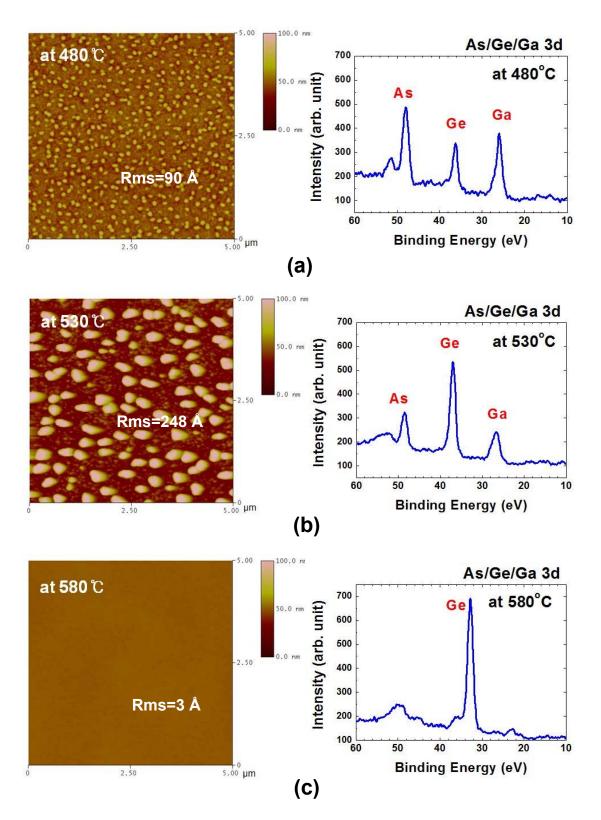

| Fig. 2.11 | Results of GaAs MBE growths on graded SGOI substrate without<br>MEE nucleation at different MBE temperatures; (a) 480 °C, (b) 530 °C,<br>and (c) 580 °C. GaAs is barely deposited and the measured surface<br>roughness of 3 Å indicates just the surface of SGOI                                                                                                                                                                                   |

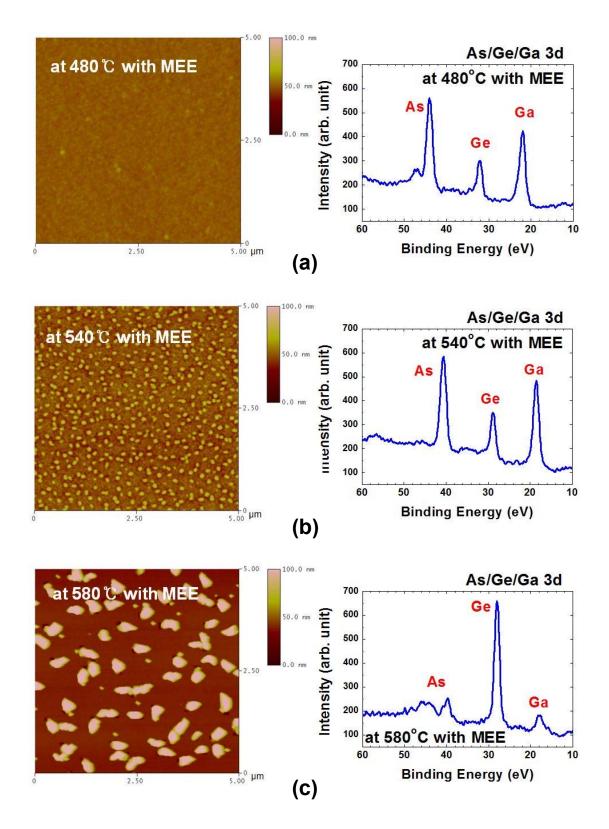

| Fig. 2.12 | Results of GaAs MBE growths on graded SGOI substrate with MEE nucleation at different MBE temperatures; (a) 480 °C. The XPS 3d <sub>2/5</sub>                                                                                                                                                                                                                                                                                                       |

|           | peaks show a good coverage of GaAs layer on SGOI substrate. (b) 540 °C. GaAs coverage is still good but the surface roughness in rms                                                                                                                                                      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | becomes as high as 74 Å. (c) 580 °C. The GaAs islands are formed on the substrate                                                                                                                                                                                                         |

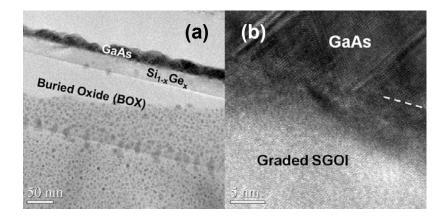

| Fig. 2.13 | TEM result of GaAs on graded SGOI grown by MBE at 480 °C without MEE nucleation. TEM images of (a) GaAs/graded SGOI/BOX stack and (b) the GaAs on SGOI at the interface                                                                                                                   |

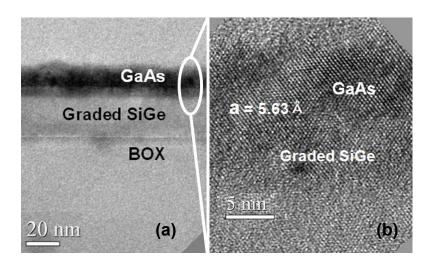

| Fig. 2.14 | TEM result of GaAs on graded SGOI grown by MBE at 480 °C with MEE nucleation at 400 °C (a) TEM image of GaAs/graded SGOI/BOX stack (b) High resolution TEM image of the GaAs on SGOI                                                                                                      |

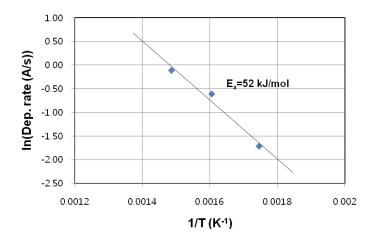

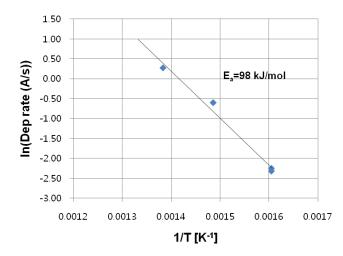

| Fig. 3.1  | Arrhenius plot of the logarithm of the HfO <sub>2</sub> deposition rate vs inverse temperature                                                                                                                                                                                            |

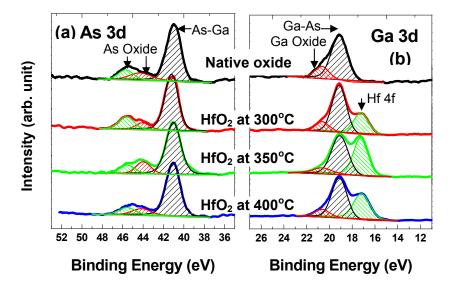

| Fig. 3.2  | (a) As 3d and (b) Ga 3d XPS spectra showing composition difference<br>of surface oxide film for a native oxide and subsequent $\sim 2 \text{ nm HfO}_2$                                                                                                                                   |

| Fig. 3.3  | depositions at different temperatures on a GaAs surface                                                                                                                                                                                                                                   |

| Fig. 3.4  | Arrhenius plot of the logarithm of the HfAlO deposition rate vs inverse temperature                                                                                                                                                                                                       |

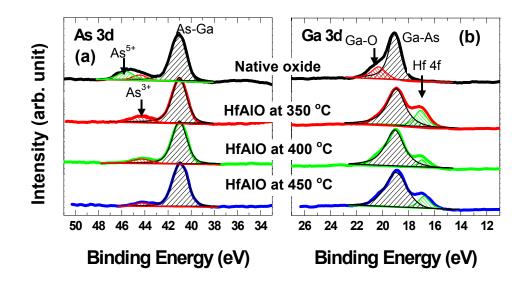

| Fig. 3.5  | (a) As 3d and (b) Ga 3d spectra showing the composition of surface oxide film for a native oxide of GaAs and subsequent ~2 nm HfAlO                                                                                                                                                       |

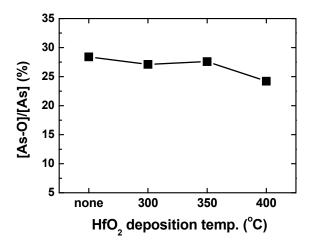

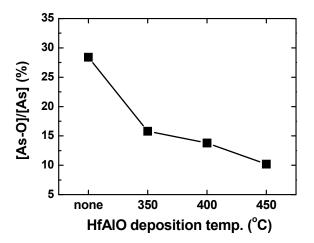

| Fig. 3.6  | depositions on the non-cleaned GaAs surface at different temperatures. 85<br>The area ratio between the peaks from As oxide and total As 3d for the<br>different GaAs samples where 2 nm thick HfAlO films were deposited<br>on non-cleaned GaAs (indicated as native oxide) at different |

| Fig. 3.7  | temperatures                                                                                                                                                                                                                                                                              |

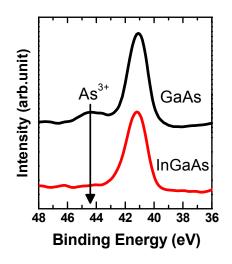

| Fig. 3.8  | XPS spectra of the As 3d peaks for GaAs and In <sub>0.53</sub> Ga <sub>0.47</sub> As after HCl cleaning                                                                                                                                                                                   |

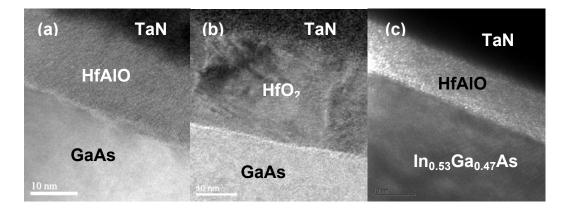

| Fig. 3.9  | TEM images showing the interfacial structures for the annealed samples at 400 °C of (a) HfAlO and (b) HfO <sub>2</sub> films on p-GaAs and (c) HfAlO on p-In <sub>0.53</sub> Ga <sub>0.47</sub> As substrate                                                                              |

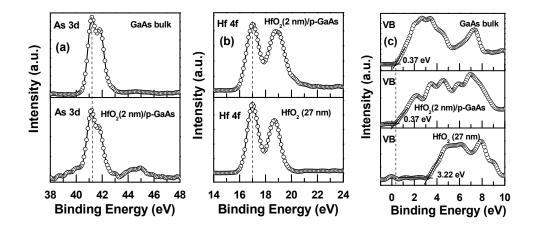

| Fig. 3.10 | (a) As 3d core level, (b) Hf 4f core level, and (c) valence band spectra<br>of p-GaAs substrate and HfO <sub>2</sub> films deposited on p-GaAs and annealed<br>at 400 $^{\circ}$ C in N <sub>2</sub> for 1 min. [37]                                                                      |

| Fig. 3.11 | (a) As 3d core level, (b) Hf 4f core level, and (c) valence band spectra of p-GaAs substrate and HfAlO films deposited on p-GaAs and annealed at 400 $^{\circ}$ C in N <sub>2</sub> for 1 min. [37]                                                                                       |

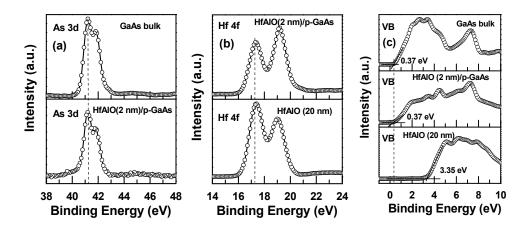

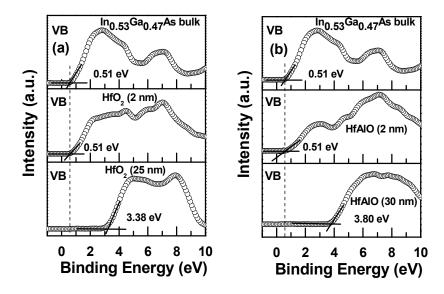

| Fig. 3.12 | Valence band spectra of (a) HfO <sub>2</sub> films and (b) HfAlO films deposited<br>on p-In <sub>0.53</sub> Ga <sub>0.47</sub> As and annealed at 400 °C for 1 min                                                                                                                        |

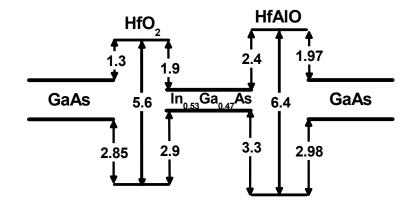

| Fig. 3.13 | Band alignment diagram for MOCVD HfO <sub>2</sub> and HfAlO on p-<br>In <sub>0.53</sub> Ga <sub>0.47</sub> As and p-GaAs estimated by XPS measurement. [42]95                                                                                                                             |

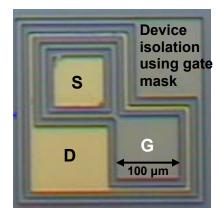

| Fig. 3.14                         | A microscope image of a ring-shaped MOSFET where G, S and D                                                                                                                                            |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $E_{i\alpha} = 2.15$              | present gate, source and drain regions, respectively                                                                                                                                                   |

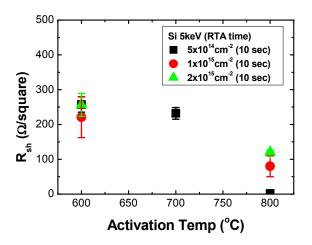

| Fig. 3.15                         | $R_{sh}$ of the p-GaAs samples activated at various RTA temperatures for 10 s after Si implantation at different dose conditions                                                                       |

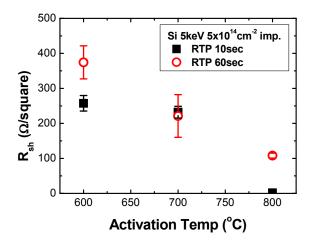

| Fig. 3.16                         | $R_{sh}$ of p-GaAs implanted Si with the dose of $5 \times 10^{14}$ cm <sup>-2</sup> as a function                                                                                                     |

| e                                 | of activation RTA temperature. The effect of annealing time is shown.100                                                                                                                               |

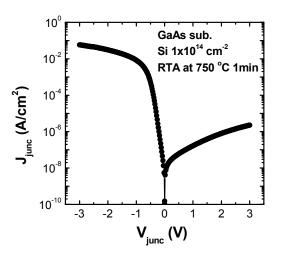

| Fig. 3.17                         | Junction current density, $J_{junc}$ vs the voltage applied between the Si                                                                                                                             |

| -                                 | implanted n <sup>+</sup> S/D and the p-GaAs substrate in GaAs NMOSFET 101                                                                                                                              |

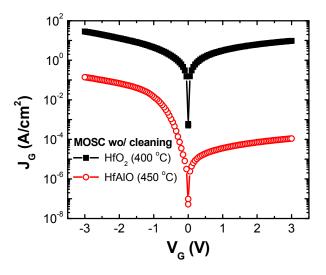

| Fig. 3.18                         | $J_G$ vs $V_G$ plot of p-GaAs MOS capacitors with 8 nm MOCVD high- $k$                                                                                                                                 |

|                                   | film deposited at the optimized deposition temperature for each high- $k$                                                                                                                              |

| <b>D</b> <sup>1</sup> <b>0</b> 10 | without pre-deposition cleaning. 102                                                                                                                                                                   |

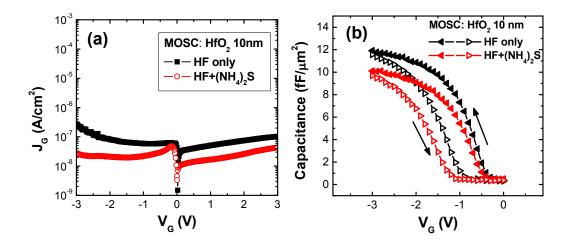

| Fig. 3.19                         | (a) $J_G$ vs $V_G$ plots and (b) bidirectional <i>C</i> - <i>V</i> curves measured at 1 kHz                                                                                                            |

|                                   | for GaAs MOS capacitors with different pre-deposition cleanings                                                                                                                                        |

| E. 2 20                           | before $HfO_2$ deposition. 103                                                                                                                                                                         |

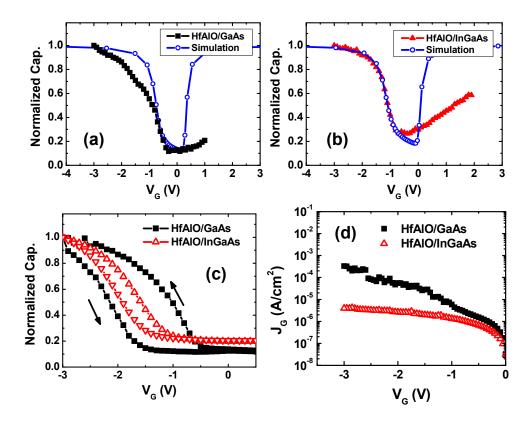

| Fig. 3.20                         | (a) <i>C-V</i> characteristics of p-GaAs/HfAlO and (b) p-                                                                                                                                              |

|                                   | In <sub>0.53</sub> Ga <sub>0.47</sub> As/HfAlO MOS capacitors measured at 200 Hz with                                                                                                                  |

|                                   | simulated $C-V$ comparisons. (c) The bidirectional $C-V$ characteristics                                                                                                                               |

|                                   | of the capacitors measured at 10 kHz. The hysteresis of p-<br>$L_{p} = C_{p} = A_{p}/(1fA_{p}) c_{p}$                                                                                                  |

|                                   | In <sub>0.53</sub> Ga <sub>0.47</sub> As/HfAlO capacitor at $V_{\rm FB}$ is 34% of it from GaAs/HfAlO capacitor (d) $L_{\rm FB}$ characteristics of the MOS capacitors [42]                            |

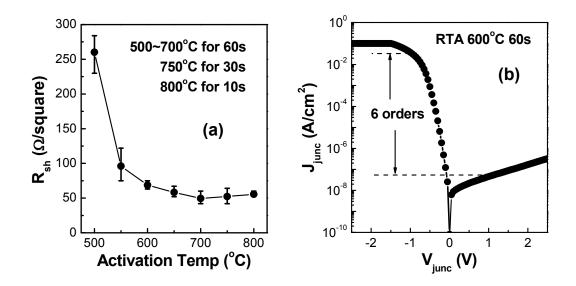

| Fig. 3.21                         | capacitor. (d) $J_{\rm G}$ - $V_{\rm G}$ characteristics of the MOS capacitors. [42] 104<br>(a) Sheet resistance of Si implanted n <sup>+</sup> S/D with a dose of 1×10 <sup>14</sup> cm <sup>-2</sup> |

| Fig. 5.21                         | at 50 keV on $In_{0.53}Ga_{0.47}As/InP$ substrate by activation RTA                                                                                                                                    |

|                                   | temperature (b) Junction current density versus the voltage applied                                                                                                                                    |

|                                   | between the Si implanted $n^+$ S/D contact and the p-substrate back                                                                                                                                    |

|                                   | contact in the InGaAs MOSFET. [47]                                                                                                                                                                     |

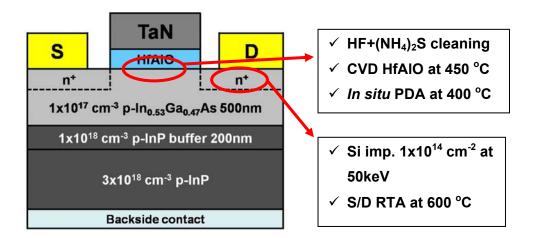

| Fig. 3.22                         | Schematic cross section of the self-aligned $In_{0.53}Ga_{0.47}As$ NMOSFET                                                                                                                             |

| 1 18. 5.22                        | integrated with a CVD HfAlO gate dielectric and a TaN metal gate.                                                                                                                                      |

|                                   | Key process conditions developed for the E-mode NMOSFET                                                                                                                                                |

|                                   | fabrication are listed in sequence. 106                                                                                                                                                                |

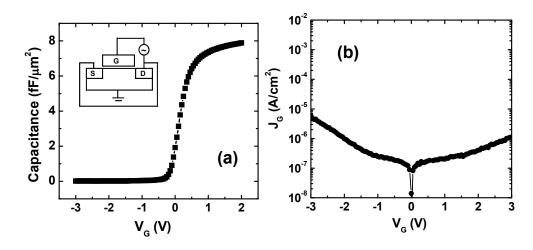

| Fig. 3.23                         | (a) Inversion <i>C</i> - <i>V</i> measured at 100 kHz. Measurement configuration is                                                                                                                    |

| C                                 | inset into the <i>C</i> - <i>V</i> plot. (b) $J_G$ - $V_G$ with backside grounded                                                                                                                      |

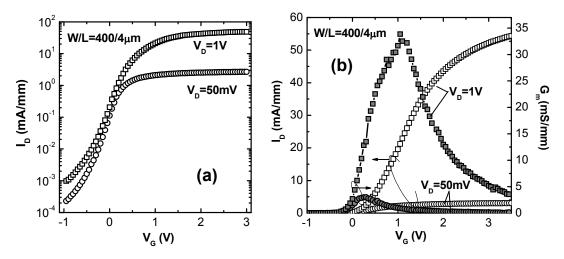

| Fig. 3.24                         | (a) Log scale $I_D$ - $V_G$ at $V_D$ = 50 mV and 1V showing subthreshold                                                                                                                               |

|                                   | behavior of an $In_{0.53}Ga_{0.47}As$ NMOSFET with a gate length of 4 $\mu$ m.                                                                                                                         |

|                                   | (b) The linear scale $I_D$ - $V_G$ and transconductances as a function of the                                                                                                                          |

|                                   | gate bias at $V_D = 50 \text{ mV}$ and 1V                                                                                                                                                              |

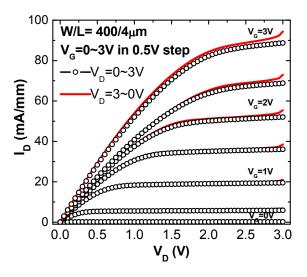

| Fig. 3.25                         | $I_D - V_D$ of an In <sub>0.53</sub> Ga <sub>0.47</sub> As NMOSFET of 4 µm gate length in a                                                                                                            |

|                                   | bidirectional $V_D$ sweeping for the hysteresis study                                                                                                                                                  |

| Fig. 3.26                         |                                                                                                                                                                                                        |

|                                   | correction for an $In_{0.53}Ga_{0.47}As$ NMOSFET of 4 µm gate length 109                                                                                                                               |

| Fig. 4.1                          | Schematic MOS structure integrated with high-k/metal gate on InGaAs                                                                                                                                    |

| e                                 | substrate passivated with PH <sub>3</sub> -based passivation technique                                                                                                                                 |

| Fig. 4.2                          | Schematic drawing of the multi-chamber CVD used                                                                                                                                                        |

| Fig. 4.3                          | Process flow of self-aligned InGaAs channel MOSFET with PH <sub>3</sub> -                                                                                                                              |

|                                   | based passivation process                                                                                                                                                                              |

| Fig. 4.4                          | AFM images of $In_{0.53}Ga_{0.47}As$ surfaces passivated with 1% PH <sub>3</sub> /N <sub>2</sub> at                                                                                                    |

|                                   | different conditions as listed in Table 4.1                                                                                                                                                            |

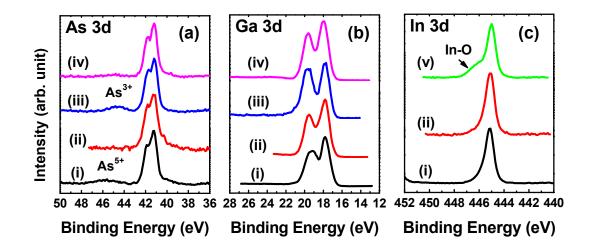

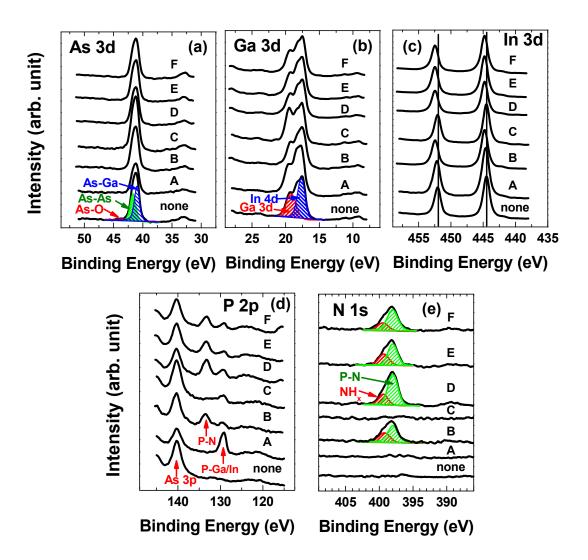

| Fig. 4.5                          | XPS spectra for the In <sub>0.53</sub> Ga <sub>0.47</sub> As surfaces with and without the PH <sub>3</sub> -                                                                                           |

|                                   | based passivation treatment as listed in Table 4.1; (a) As 3d, (b) Ga 3d,                                                                                                                              |

|           | (c) In 3d, (d) P 2p, and (e) N 1s core level spectra for the different samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

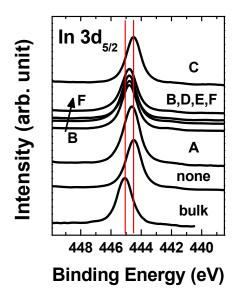

| Fig. 4.6  | In $3d_{5/2}$ core level spectra for the In <sub>0.53</sub> Ga <sub>0.47</sub> As surfaces with and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fig. 4.7  | without passivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

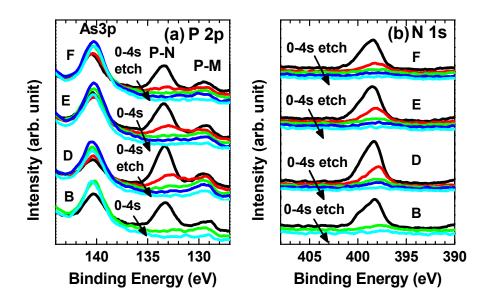

| Fig. 4.8  | XPS depth profiles for the different $P_xN_y$ passivation samples B, D, E,<br>and F of (a) P 2p and (b) N 1s core level spectra measured at TOA =<br>$30^{\circ}$ . <i>In situ</i> sputtering has been employed with a film etching rate of ~1<br>Å/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

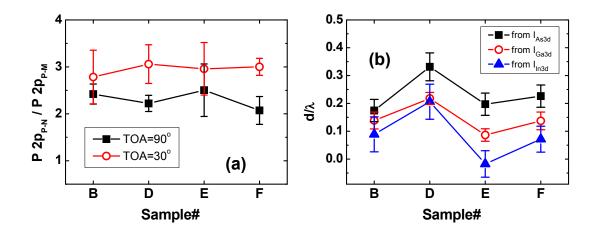

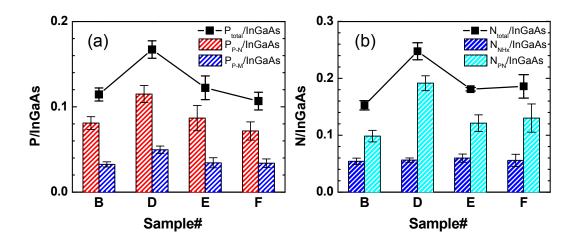

| Fig. 4. 9 | (a) The amount of phosphorus incorporation into the substrate from the relative XPS peak intensity of P/InGaAs for the $P_xN_y$ passivated samples (B, D, E, and F) determined from the phosphorus chemical components of P-N and P-metal bond which are indicated as $P_{P-N}$ and $P_{P-M}$ , respectively. $P_{total}/InGaAs$ indicates the total amount of phosphorus incorporation. (b) The amount of nitrogen incorporation with relative intensity of N 1s line against the InGaAs substrate peaks for samples B, D, E, and F. The fractions of different chemical components of NH <sub>x</sub> (where $x=1$ or 2) and P-N are indicated as $N_{NHx}/InGaAs$ and $N_{PN}/InGaAs$ , respectively, with total amount of nitrogen incorporation, $N_{total}/InGaAs$ |

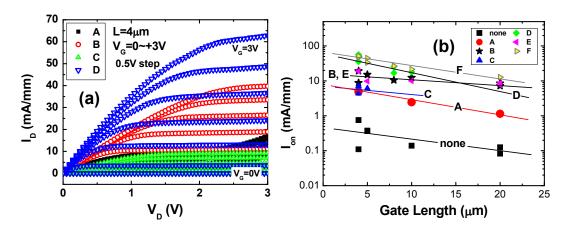

| Fig. 4.10 | (a) $I_D$ - $V_D$ characteristics for the In <sub>0.53</sub> Ga <sub>0.47</sub> As/HfO <sub>2</sub> /TaN MOSFET<br>with different passivation conditions. (b) On-current, $I_{on}$ which is $I_D$ at<br>$V_G = 3$ V and $V_D = 1$ V for the different passivation conditions as a<br>function of gate length of the MOSFET devices                                                                                                                                                                                                                                                                                                                                                                                                                                       |

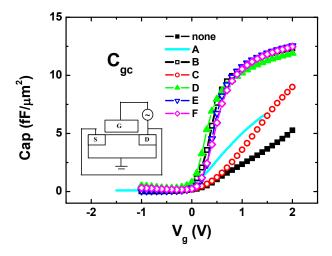

| Fig. 4.11 | Gate-to-channel capacitance ( $C_{gc}$ ) versus gate voltage of the passivated<br>and non-passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs measured at 1 MHz using<br>split <i>C-V</i> method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

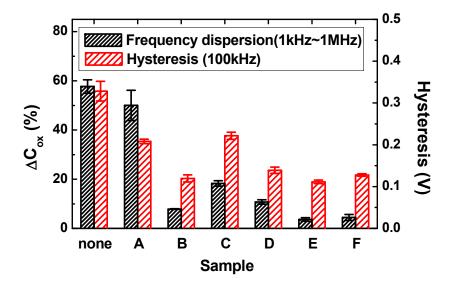

| Fig. 4.12 | Frequency dispersion obtained from the difference of inversion<br>capacitance, $C_{gc}$ at $V_G = 2V$ between 1 kHz and 1 MHz and hysteresis<br>measured from a $V_{FB}$ shift in bidirectional <i>C</i> - <i>V</i> measurement at 100<br>kHz for different passivation conditions on In <sub>0.53</sub> Ga <sub>0.47</sub> As/HfO <sub>2</sub><br>MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                |

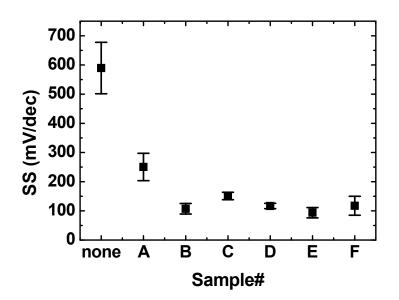

| Fig. 4.13 | SS for the MOSFETs with different passivation conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

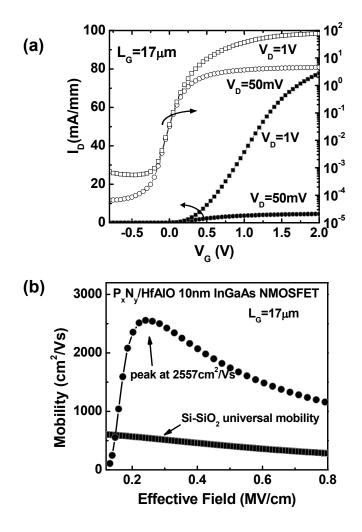

| Fig. 4.14 | (a) $I_D$ - $V_G$ characteristics of MOCVD HfAlO/TaN NMOSFET on $P_xN_y$ -<br>passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As ( $L_G = 17 \mu m$ ). (b) Mobility vs effective<br>electric field of the InGaAs device in comparison with the Si universal<br>mobility curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

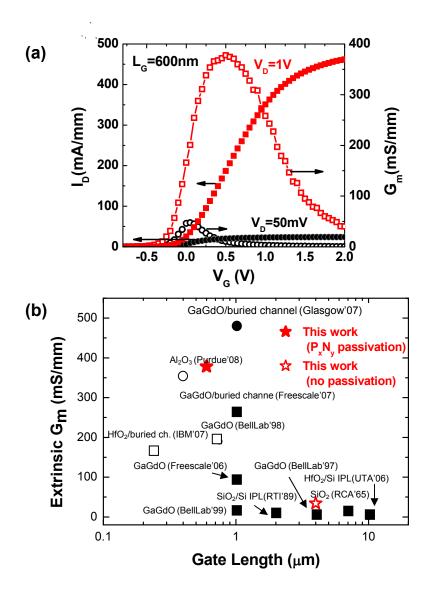

| Fig. 4.15 | (a) $I_D$ - $V_G$ characteristics of the $P_xN_y$ -passivated InGaAs/HfAlO/TaN<br>MOSFET with $L_G = 600$ nm, showing $G_m$ of 378 mS/mm. (b)<br>Comparison of $G_m$ of the InGaAs NMOSFETs with and without the<br>$P_xN_y$ -passivation in this work with the published $G_m$ of E-mode<br>NMOSFETs from 1965 to 2008 (Fig. 1.17). Open symbols are high<br>indium concentration channels of InGaAs (In $\geq 0.53$ ), whereas closed                                                                                                                                                                                                                                                                                                                                  |

|           | symbols are GaAs or InGaAs with low indium concentration channels<br>in the previously reported data [52]       |

|-----------|-----------------------------------------------------------------------------------------------------------------|

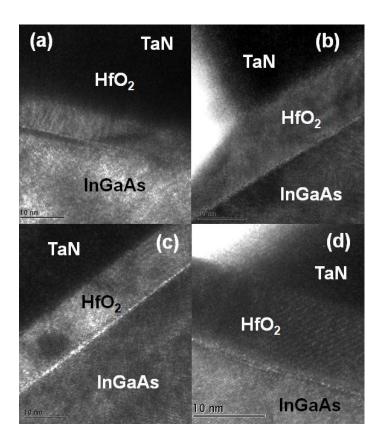

| Fig. 4.16 | Cross-sectional TEM images of InGaAs/HfO <sub>2</sub> /TaN gate stack without                                   |

| C         | $P_x N_y$ passivation layer after anneal at 700 °C for 10 sec (a) and with the                                  |

|           | $P_x N_y$ passivation layer after at 600 °C for 1 min (b), at 700 °C for 10 s                                   |

|           | (c), and 750 $^{\circ}$ C for 5 s (d). For substrate, In <sub>0.53</sub> Ga <sub>0.47</sub> As is used for (a), |

|           | (b), and (d) and In <sub>0.7</sub> Ga <sub>0.3</sub> As for (c)                                                 |

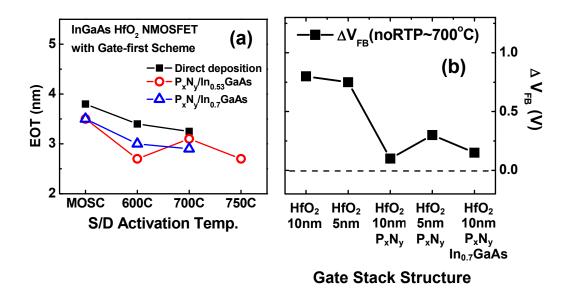

| Fig. 4.17 | (a) EOT vs. S/D activation temperature for 10 nm thick HfO <sub>2</sub> gate                                    |

|           | stacks on the InGaAs with and without $P_xN_y$ passivation and (b)                                              |

|           | changes in $V_{FB}$ by RTA at 700 °C for the MOS devices with different                                         |

|           | gate stacks on InGaAs                                                                                           |

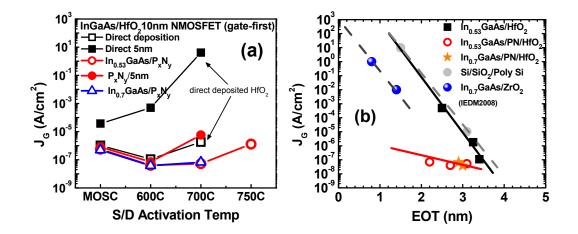

| Fig. 4.18 | (a) Gate leakage current density, $J_G$ at $ V_{FB}+1V $ for InGaAs/HfO <sub>2</sub>                            |

|           | MOS capacitors with and without $P_x N_y$ passivation as a function of                                          |

|           | S/D activation temperature and (b) $J_G$ of this work in comparison with                                        |

|           | the reported results                                                                                            |

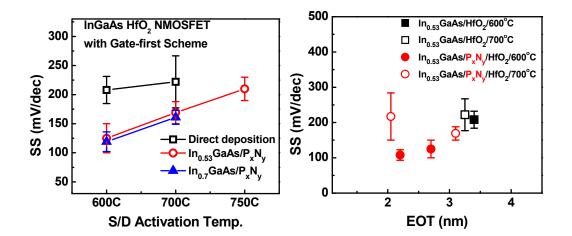

| Fig. 4.19 | $P_xN_y$ passivation effect on SS of the InGaAs/HfO <sub>2</sub> MOSFETs: (a) SS                                |

|           | vs S/D activation temperature where the HfO <sub>2</sub> is 2 nm thick and (b) SS                               |

|           | scalability with EOT                                                                                            |

|           |                                                                                                                 |

## LIST OF SYMBOLS AND ACRONYMS

### Symbol/Acronym Description

| Symbol/Actonym    | Description                                                     |

|-------------------|-----------------------------------------------------------------|

| 2D                | two-dimensional                                                 |

| a                 | lattice constant                                                |

| α                 | elastic strain                                                  |

| AFM               | atomic force microscopy                                         |

| ALD               | atomic layer deposition                                         |

| BE                | binding energy                                                  |

| BEP               | beam equivalent pressure                                        |

| BOX               | buried oxide                                                    |

| BTBT              | band-to-band tunneling                                          |

| СВО               | conduction band offset                                          |

| $C_{gc}$          | gate-to-channel capacitance                                     |

| CMOSFET           | Complementary metal-oxide-semiconductor field-effect transistor |

| СМР               | chemical mechanical polishing                                   |

| $C_{ox}$          | gate oxide capacitance                                          |

| $\delta$          | plastic strain                                                  |

| DHF               | dilute HF                                                       |

| DIBL              | drain-induced barrier lowering                                  |

| $D_{it}$          | density of interface states                                     |

| $\mathcal{E}_{o}$ | permittivity of vacuum                                          |

| EDS               | energy dispersive X-ray spectroscopy                            |

| $E_g$             | bandgap                                                         |

| E-mode            | enhancement mode                                                |

| EOT               | electrical equivalent oxide thickness                           |

| f                 | lattice mismatch                                                |

| FDSOI             | fully depleted silicon-on-insulator                             |

| FGA               | forming gas anneal                                              |

| FWHM              | full width at half-maximum                                      |

| GaAs-OI           | GaAs-on-insulator                                               |

| GIDL              | gate-induced drain leakage                                      |

|                   |                                                                 |

| $G_m$             | transconductance                                                                 |

|-------------------|----------------------------------------------------------------------------------|

| GOI               | Ge-on-insulator                                                                  |

| HA-2              | HfAl(OiPr) <sub>5</sub> (MMP) <sub>2</sub>                                       |

| $h_c$             | critical thickness                                                               |

| HTB               | hafnium tetra tert-butoxide, Hf(OC(CH <sub>3</sub> ) <sub>3</sub> ) <sub>4</sub> |

| IC                | integrated circuit                                                               |

| $I_D$             | drain current of MOSFET                                                          |

| I <sub>Dsat</sub> | MOSFET saturation current                                                        |

| III-V-OI          | III-V-on-insulator                                                               |

| I <sub>leak</sub> | leakage current                                                                  |

| $I_{off}$         | off-state current                                                                |

| Ion               | on-state current                                                                 |

| ITRS              | International Technology Roadmap for Semiconductors                              |

| $J_G$             | gate leakage current density                                                     |

| k                 | relative permittivity (dielectric constant) of dielectric                        |

| $k_B$             | Boltzmann's constant                                                             |

| L                 | channel length of MOSFET                                                         |

| $L_G$             | gate length of MOSFET                                                            |

| $m^*$             | effective mass                                                                   |

| μ                 | carrier mobility                                                                 |

| MBE               | molecular beam epitaxy                                                           |

| MEE               | migration-enhanced epitaxy                                                       |

| MIGS              | metal-induced gap states                                                         |

| ML                | monolayer                                                                        |

| MOCVD             | metal-organic chemical vapor deposition                                          |

| MOSFET            | metal-oxide-semiconductor field-effect transistor                                |

| NMOSFET           | n-channel MOSFET                                                                 |

| PDA               | post-deposition anneal                                                           |

| PDSOI             | partially depleted SOI                                                           |

| PMOSFET           | p-channel MOSFET                                                                 |

| PVD               | physical vapor deposition                                                        |

| q                 | electron charge                                                                  |

| rf                | radio-frequency                                                                  |

| RHEED           | reflection high-energy electron diffraction       |

|-----------------|---------------------------------------------------|

| rms             | root-mean-square                                  |

| $R_{sh}$        | sheet resistance                                  |

| RTA             | rapid thermal anneal                              |

| S/D             | source/drain                                      |

| SCE             | short-channel effects                             |

| SEM             | scanning electron microscopy                      |

| SGOI            | SiGe-on-insulator                                 |

| SIMS            | secondary ion mass spectroscopy                   |

| SOI             | Si-on-insulator                                   |

| SS              | subthreshold slope                                |

| STS             | scanning tunneling spectroscopy                   |

| Т               | temperature                                       |

| τ               | intrinsic delay                                   |

| TEM             | transmission electron microscopy                  |

| TOA             | take-off angle                                    |

| $T_{ox}$        | equivalent oxide thickness of the gate dielectric |

| UHV CVD         | ultrahigh-vacuum chemical vapor deposition        |

| UTB             | ultrathin body                                    |

| VBM             | valence band maximum                              |

| VBO             | valence band offset                               |

| $V_D$           | drain voltage                                     |

| $V_{dd}$        | power supply voltage                              |

| $V_{FB}$        | flatband voltage                                  |

| $V_G$           | gate voltage                                      |

| V <sub>th</sub> | threshold voltage                                 |

| W               | channel width of MOSFET                           |

| XPS             | X-ray photoelectron microscopy                    |

# CHAPTER 1 INTRODUCTION

The remarkable development in integrated circuit (IC) capability, which has been made over the past five decades, is due to the success on miniaturization of the IC component devices, such as transistors, capacitors, and resistors, mostly made by using semiconductors. The smaller the semiconductor devices can be made, the higher the IC performance is achievable per unit chip area. In addition, as multi-functional ICs are needed, the response time of the semiconductor devices should be one of the critical requirements for high-performance ICs. Therefore, most researches in microelectronics industry have thus focused on how to make smaller and faster semiconductor devices.

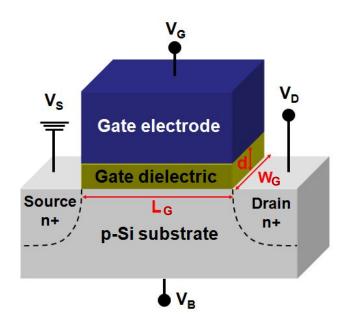

Among the semiconductor devices, metal-oxide-semiconductor field-effect transistor (MOSFET) is the most important building block today. Although the concept of the MOSFET was developed well in the early 1930s, the first MOSFETs suitable for commercial use appeared in the 1960s. It was mainly due to the discovery of a thermally oxidized Si structure MOSFET which was first demonstrated by Kahng and Atalla in 1960 [1]. Since then, the thermally oxidized Si structure MOSFETs have been widely used in ICs because of their simpler fabrication, higher density and lower power compared to the other types of devices. A schematic n-channel MOSFET (NMOSFET) is illustrated in Fig. 1.1 with its operation principle as a digital switch.

Fig. 1.1 Schematic of a Si NMOSFET structure. Gate dimension is defined by the gate length,  $L_G$ , the gate width,  $W_G$ , and the thickness of gate dielectric, d. If a large positive voltage is applied to  $V_G$ , the p-type Si surface under the gate ( $W_G \times L_G$ ) is inverted and a conductive n-type channel is induced connecting the source and the drain.

The miniaturization, called scaling, of MOSFET has been achieved by simple reduction of its dimension to increase the transistor density without degradation of the device performance. Over a span of 30 years, the minimum feature size ( $\sim L_G$ ) available in MOS technologies has been reduced by a factor of 200 (from  $\sim$ 20 to  $\sim$ 0.1 µm) and the area density of devices has increased by more than 40,000 times [2]. On the other hand, the gate stack system has been maintained as Si channel, SiO<sub>2</sub> gate dielectric, and highly doped poly-Si gate electrode. That is largely due to the system's superior properties such as low interface state density between SiO<sub>2</sub> and Si substrate, excellent thermal stability of SiO<sub>2</sub> on Si, and high dielectric breakdown field of SiO<sub>2</sub> [3]. However, the rapid scaling has brought this Si-based technology to the point where fundamental physical phenomena such as tunneling current of a thin SiO<sub>2</sub> dielectric film and tunneling current through the drain-to-body junction are beginning to impede the further progress. In order to overcome this difficulty, many new and innovative changes to the basic Si-based complementary MOSFET (CMOSFET) technology are

being explored, including new gate geometries, the use of strain to enhance the mobility, and the use of new gate stack materials. Thus this work of development of high mobility channel layer formation technology has been carried out for the innovative change.

The subsequent sections in this chapter provide the background and objectives of this work to find ways to extend the scaling and to resolve the fundamental issues in the traditional Si-based CMOS technology. Some of the most promising approaches to maintain the MOSFET scaling speed are reviewed with brief theoretical considerations. Finally, a scope of this work will be given, followed by the organization of this thesis.

### **1.1 MOS SCALING BEYOND THE 10 nm NODE**

In this section, a brief overview of MOS scaling trend with present state-of-theart CMOSFET technologies, industry targets for future progress, and challenges to accomplish the goal of MOS scaling beyond the 10 nm gate length will be presented as a background of this thesis.

#### **1.1.1 OVERVIEW OF MOSFET SCALING**

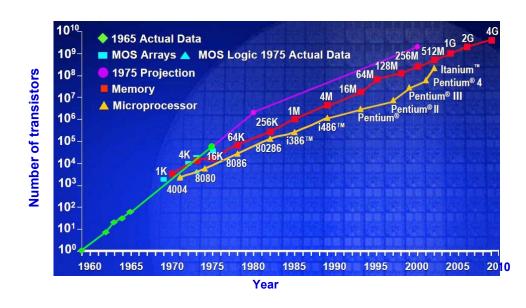

The continued scaling of MOSFET to reduce the cost per function with increased transistor density has been a driving force in IC industry. In 1965, G. E. Moore, the founder of Intel Corporation, predicted that the number of transistors placed on an IC would double every two years [4] and the statement, since then, has been known as Moore's law guiding the direction of progress as shown in Fig. 1.2.

Fig. 1.2 Illustration of Moore's Law: The number of microprocessor transistors by year. [5]

The physical dimension scaling principle behind the Moore's law can simply be expressed by the long-channel MOSFET equation, in which the saturation drive current,  $I_{Dsat}$  of MOSFET can be depicted as follows:

$$I_{Dsat} = \frac{W}{2L} \mu C_{ox} \left( V_G - V_{th} \right)^2 = \frac{W}{2L} \mu \frac{\varepsilon_o k_{ox}}{d} \left( V_G - V_{th} \right)^2$$

(1.1)

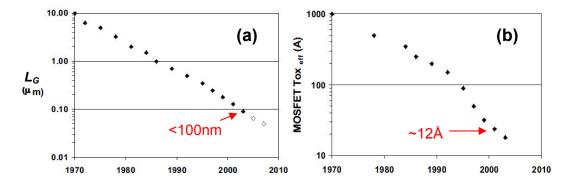

where W and L are the channel width and length respectively,  $\mu$  is the carrier mobility in the channel,  $C_{ox}$  is the gate oxide capacitance density,  $V_G$  is the gate bias,  $V_{th}$  is the threshold voltage of the transistor,  $\varepsilon_o$  is the permittivity of vacuum,  $k_{ox}$  is the relative permittivity of the oxide, called dielectric constant, and d is the physical thickness of the oxide. The channel dimension ( $W \times L$ ) is regarded as same as the gate dimension ( $L_G \times W_G$ ) in an ideal self-aligned MOSFET structure. When the gate dielectric is SiO<sub>2</sub>,  $k_{ox}$  is 3.9 and d is SiO<sub>2</sub> thickness,  $T_{ox}$ . The most important output parameter of MOSFET is the intrinsic delay,  $\tau = CV/I$ , where C is the total gate capacitance per transistor width, V is the power supply voltage,  $V_{dd}$ , and I is the saturation drive current per transistor width,  $I_{Dsat}$ . Hence, the MOSFET performance is directly proportional to  $I_{Dsat}$ . The gate length,  $L_G$  and  $T_{ox}$ , i.e. d in the case of SiO<sub>2</sub> dielectric, have been reduced exponentially according to the equation (1.1) to increase  $I_{Dsat}$  and to decrease  $\tau$ . Those  $L_G$  and  $T_{ox}$  scaling trends are illustrated in Fig. 1.3a and b, respectively [5].

Fig. 1.3 (a) Gate length,  $L_G$  and (b) gate oxide thickness,  $T_{ox}$  changes in production MOSFET by year [5].