# **TOP-DOWN ENGINEERED SILICON AND**

## GERMANIUM NANOWIRE MOSFET

**PENG JIANWEI**

## NATIONAL UNIVERSITY OF SINGAPORE

2010

# TOP-DOWN ENGINEERED SILICON AND GERMANIUM NANOWIRE MOSFET

## **PENG JIANWEI** B.Eng. (National University of Singapore) 2006

## A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE 2010

# Acknowledgements

I would like to thank everyone that contributed in various ways to this thesis. First and foremost, I would like to take this opportunity to express my sincere gratitude to my advisors, Prof. Lee Sungjoo and Dr. Lo Guoqiang, Patrick for their invaluable guidance and encouragement throughout my 4 years' Ph.D. study at National University of Singapore. Without their help, I would not be able to overcome all those difficulties and walk all the way to here to write this thesis. I am greatly thankful to Prof. Lee for his kindness and patience in helping me on my research. Prof. Lee is an experienced advisor who could always point out the fundamental issues directly and gave practical suggestions on my research work. Moreover, he is also a kind elder who is patient and careful on helping me on my mistakes. I also truly appreciate the helpful guidance and support from Dr. Lo. I would like to thank Dr. Lo for providing me the opportunity to join the Institute of Microelectronics (IME), Singapore for my Ph.D research work, where I continuously get support from him on various matters. My appreciation also goes to Dr. Navab Singh from the Institute of Microelectronics, Singapore, for his valuable advice and technical discussions. Without his expertise and advice in semiconductor technology, I would not be able to undertake all my projects smoothly.

I would also like to express my deepest appreciation to Dr. Lap Chan and Dr. Ng Chee Mang for their supports and knowledge sharing. I like the Wednesday session and absorbed a lot of nutriment, technique and non-technique knowledge, from the interaction with them and the rest of the Special Group students. I would also like to thank Dr. Yu Ming-Bin, Dr. Wei Yip Lo, Dr. Zhu Si Yang, for their assistance and discussion to conduct my process in the clean room. I benefited greatly through interactions with them. I would like to thank all the technical staff in Semiconductor Process Technology department, especially Mr. Deng Wei, for their kindness and help on my research works.

Special thanks also go to my seniors in Silicon Nano Device Lab (SNDL), National University of Singapore, especially Dr. Zang Hui, Dr. Jiang Yu, Dr. Fu Jia, Dr. Zhao Hui, Dr. Yang Weifeng, Dr. He Wei, Dr. Yang Jianjun, Dr. Gao Fei, Dr. Ren Chi, Dr. Tan Kian Ming, Dr. Shen Chen et al. for their assistance on many of my technical problems encountered during my graduate study. To my research buddies, Chin Yoke King, Wang Jian, Xie Ruilong, Lim Shiya, Phyllis, Li Yida, Sun Yuan, Lu Weijie et al., I would like to say that my research life would be much tougher without their help and discussion.

Last but not least, my thanks go to my parents for their supports and encouragements during my doctorial studying.

# Abstract

A large part of the success of integrated circuits could be attributed to the continuous scaling of metal-oxide-semiconductor-field effect-transistors (MOSFETs), which lead to faster and cheaper transistors simultaneously. However, as the transistor dimensions shrink down to the sub-100 nm regime, it has become challenging to continuously improve transistors' performance by conventional scaling techniques. It is found that on-state current, power consumption and short channel effects have a tradeoff relationship with each others. As a result, any technique to improve transistor performance needs to overcome/mitigate the stringent constrains of this tradeoff.

The nanowire transistor architecture and germanium (Ge) channel are considered to be promising performance boosters to improve transistor performance which can effectively overcome/mitigate the tradeoff between on-state current, power consumption and short channel effects. In this thesis, nanowire gate-all-around (GAA) Schottky Barrier (SB)-MOSFETs and Ge nanowire transistors are studied as potential candidates for future high performance transistor applications.

Nanowire GAA MOSFETs integrated with 1-D NiSi Schottky source/drain (S/D) were explored and demonstrated on silicon (Si) nanowires with diameter down to 4 nm. Although NiSi has a high hole SB height of 0.46 eV, the Si nanowire SB-MOSFET still demonstrated a high on-state current and a subthreshold swing (SS) close to the ideal value 60 mV/dec. The performance improvement was attributed to the improved carrier injection as a result of the superior gate electrostatic control over the channel in the GAA nanowire device architecture.

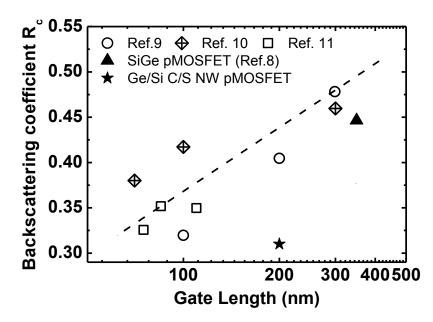

As a potential performance booster, Ge nanowire transistors were explored. Ge nanowires (NWs) were fabricated on an epitaxial grown Ge layer by a novel technique of two-step etching with polymerization in between. Ge-nanowires (GeNWs) with diameter down to 14 nm were integrated with the TaN/High-k gate stack to form Ge nanowire pMOSFETs. The on/off ratio as high as 6 orders at -1.2 V  $V_{DS}$  was achieved on the 14 nm diameter Ge nanowire transistor. However, hole field effect mobility was low due to the surface roughness scattering and the Coulomb scattering caused by the heavy interface state trap density. To improve the GeNW surface topology, Epitaxial-Si over GeNW was employed. The Ge/Si core/shell nanowires were integrated with the TaN/HfO<sub>2</sub> gate stack to form GAA GeNW pMOSFETs. With the introduction of the Si epitaxial shell, the Ge nanowire transistor performance was significantly improved. A 200 nm gate length Ge/Si core/shell nanowire GAA pMOSFET demonstrated high on-state current of 150  $\mu$ A/ $\mu$ m, a peak field effect mobility of 254 cm<sup>2</sup>/V-s, and a backscattering coefficient of 0.31.

# **Table of Contents**

| Ack  | nowledg       | gements                                 | I           |

|------|---------------|-----------------------------------------|-------------|

| Abst | t <b>ract</b> | • • • • • • • • • • • • • • • • • • • • | .III        |

| List | of Table      | es                                      | .IX         |

| List | of Figur      | res                                     | X           |

| List | of Symb       | bols XV                                 | <b>VIII</b> |

| List | of Abbr       | reviations                              | XIX         |

| Chaj | pter 1        | Introduction                            | 1           |

| 1.1  | Approac       | whes to improve MOSFET performance      | 1           |

| 1.2  | MOSFE         | T scaling                               | 5           |

|      | 1.2.1         | Overview of MOSFET scaling              | 5           |

|      | 1.2.2         | Challenges of further scaling MOSFET    | 7           |

| 1.3  | High-k/n      | metal-gate for gate dielectric scaling  | 9           |

| 1.4  | Objectiv      | ves and scopes                          | 12          |

| 1.5  | Thesis of     | rganization                             | 13          |

| Chaj | pter 2        | Literature Review                       | 15          |

| 2.1  | Nanowir       | re gate-all-around architecture         | 15          |

| 2.2  | Nanowir       | res fabricated by bottom-up approach    | 19          |

| 2.3 | Nanowires fabricated by top-down approach           | 20 |

|-----|-----------------------------------------------------|----|

| 2.4 | Germanium channel for future transistors            | 22 |

| 2.5 | Challenges of the Ge channel transistor             | 24 |

|     | 2.5.1 Gate dielectric                               | 24 |

|     | 2.5.2 Junction leakage                              | 26 |

|     | 2.5.3 Process integration                           | 26 |

| 2.6 | Summary                                             | 27 |

| Cha | apter 3 Si Nanowire GAA MOSFETs Integrated with 1-1 | D  |

| Sch | ottky Barrier Source/Drain                          | 28 |

| 3.1 | Schottky diode                                      | 28 |

| 3.2 | Schottky barrier MOSFETs                            | 31 |

|     | 3.2.1 Advantages of SB-MOSFETs                      | 31 |

|     | 3.2.2 Operating principles of SB-MOSFETs            | 32 |

|     | 3.2.3 Challenges of SB-MOSFETs                      | 35 |

| 3.3 | Advantages of Si nanowire GAA SB-MOSFETs            | 36 |

| 3.4 | Si nanowire SB-MOSFETs fabrication                  | 38 |

| 3.5 | Device physical characterization                    | 46 |

| 3.6 | Device IV characteristics                           | 48 |

| 3.7 | Effective SBH in Si nanowire SB-MOSFETs             | 55 |

| 3.8 | Simulation study of the Schottky barrier junction   | 57 |

| 3.9  | Summa    | ry and Discussion                                       | 59    |

|------|----------|---------------------------------------------------------|-------|

| Cha  | pter 4   | Ge Nanowire PMOSFETs on Epitaxial Grown                 | Ge    |

| Sub  | strate   |                                                         | 60    |

| 4.1  | Introduc | ction                                                   | 60    |

| 4.2  | Ge nano  | owires on epitaxial Ge substrate                        | 66    |

|      | 4.2.1    | High-quality Ge epitaxial growth on Si substrate        | 66    |

|      | 4.2.2    | Ge nanowires fabrication on epitaxial Ge substrate      | 67    |

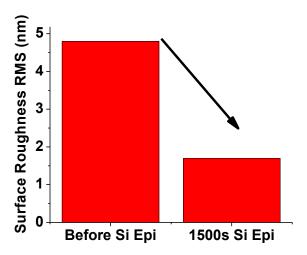

|      | 4.2.3    | Ge surface roughness after Ge nanowire formation proces | ses73 |

| 4.3  | Ge nano  | owire pMOSFETs fabrication                              | 75    |

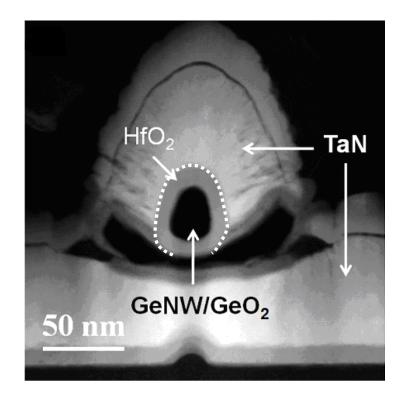

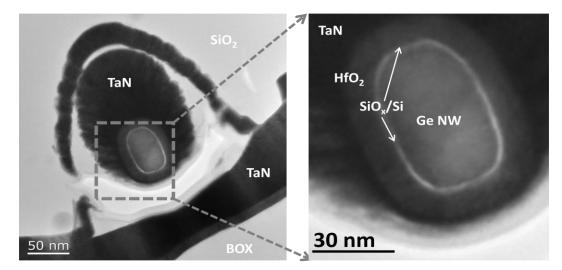

| 4.4  | Device   | channel TEM characterization                            | 77    |

| 4.5  | Ge nano  | owire pMOSFETs I-V characteristics                      | 78    |

|      | 4.5.1    | The Ge nanowire transistor performance                  | 78    |

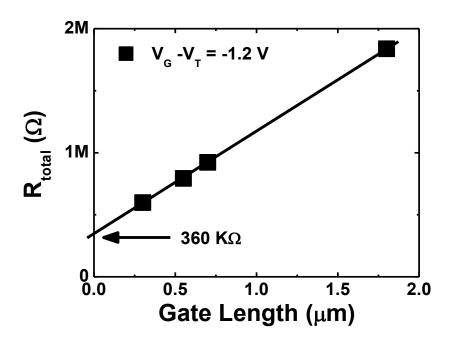

|      | 4.5.2    | S/D resistance                                          | 80    |

|      | 4.5.3    | Hole mobility characterization                          | 80    |

|      | 4.5.4    | Interface state density                                 | 83    |

| 4.6  | Discuss  | ion                                                     | 83    |

| 4.7  | Summa    | ry                                                      | 84    |

| Cha  | pter 5   | Ge/Si Core/Shell Nanowire PMOSFETs                      | 85    |

| 5.1  | Introdu  | ction                                                   | 85    |

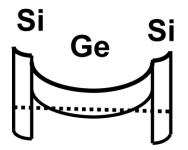

| 5.2. | The epi  | taxial-Si shell on a Ge nanowire                        | 86    |

|         | 5.2.1     | Process qualification of the epitaxial-Si shell on a G | e nanowire86 |

|---------|-----------|--------------------------------------------------------|--------------|

|         | 5.2.2     | Epitaxial-Si growth process for Ge surface morphole    | ogy          |

| impr    | ovement   |                                                        |              |

| 5.3.    | Ge/Si co  | re/shell nanowire pMOSFETs fabrication                 |              |

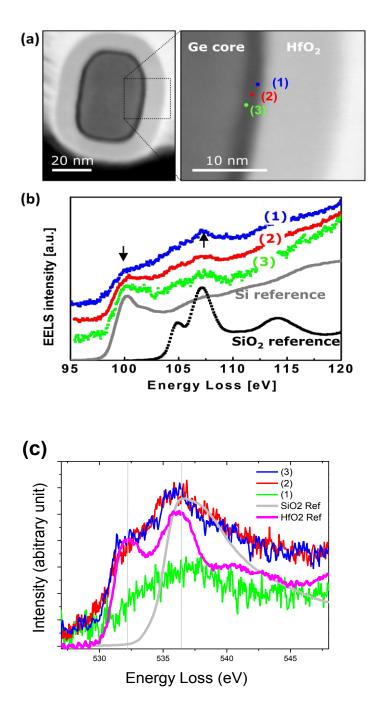

| 5.4     | Device c  | hannel physical characterization                       |              |

| 5.5     | Device I  | -V characterization                                    |              |

| 5.6     | Hole mo   | bility in the Ge/Si core/shell nanowire channel        | 97           |

| 5.7     | Hole inje | ection in the Ge/Si core/shell nanowire channel        |              |

| 5.8. \$ | Summary . |                                                        |              |

| Cha     | pter 6    | Conclusions and Recommendations                        | 106          |

| 6.1     | Conclusi  | ons                                                    | 106          |

| 6.2     | Recomm    | endations                                              | 109          |

| Ref     | erences   |                                                        | 113          |

| List    | of Publi  | cations                                                | 124          |

# **List of Tables**

| Table 1.1: Transistor parameters in constant-voltage scaling and constant-field scaling, assuming long channel device and power = $I_D * V_D$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1: Summary of the key device parameters of some of the reported nanowire NMOS                                                         |

| Table 2.2: Intrinsic material properties of Si, Ge and a few popular III-V compounds                                                          |

| Table 3.1: Commonly reported silicide Schottky barrier height on n-type      Si                                                               |

| Table 3.2: Etching parameters in precision 5000 for highly selective etch of poly      Si over oxide                                          |

| Table 4.1: Summary of some reported Ge MOSFETs    61                                                                                          |

| Table 4.2: Process condition of the passivation and isotropic etch in the Ge nanowire formation process                                       |

| Table 4.3: Splits condition and results of Ge surface roughness investigation                                                                 |

# **List of Figures**

| Figure 1.1: (a) Schematic of a conventional planar NMOS cross-sectional image             |

|-------------------------------------------------------------------------------------------|

| and (b) a typical inverter circuit consisting of one NMOS and one                         |

| PMOS2                                                                                     |

| Figure 1.2: 2009 ITRS product technology trends: MPU product functions/chip               |

| and industry average "Moore's Law" and chip size trends[11]5                              |

| Figure 1.3: The limit of the gate leakage current $(J_{g,limit})$ required by ITRS versus |

| the simulated gate leakage current $(J_{g,simulated})$ for high performance               |

| applications[11]10                                                                        |

| Figure 2.1: Schematics of transistor architecture evolution: (a) FD-SOI MOSFET;           |

| (b) double gate transistor; (c) Tri-gate transistor; (d) $\pi$ -gate transistor;          |

| (e) $\Omega$ -gate transistor; (f) GAA transistor                                         |

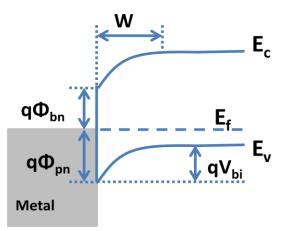

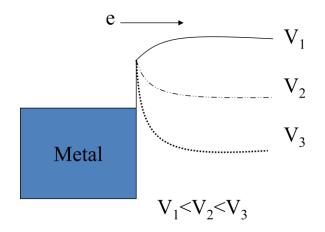

| Figure 3.1: Schematic energy band diagram of a Schottky diode on p-type silicon.          |

|                                                                                           |

| Figure 3.2: Schematic of hole transport mechanism in a Schottky diode. The                |

| energy of hole 1 is higher than the Schottky barrier, traveling from                      |

| the semiconductor to the metal by thermal emission. Hole 2 travel                         |

| from the semiconductor to the metal by quantum mechanical                                 |

| tunneling                                                                                 |

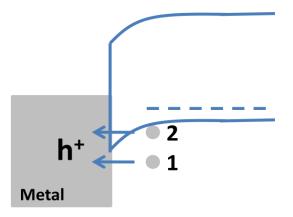

| Figure 3.3: Schematic cross sectional view of (a) a conventional heavily doped            |

| S/D nMOSFET and (b) a Schottky barrier nMOSFET32                                          |

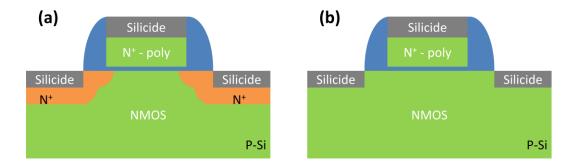

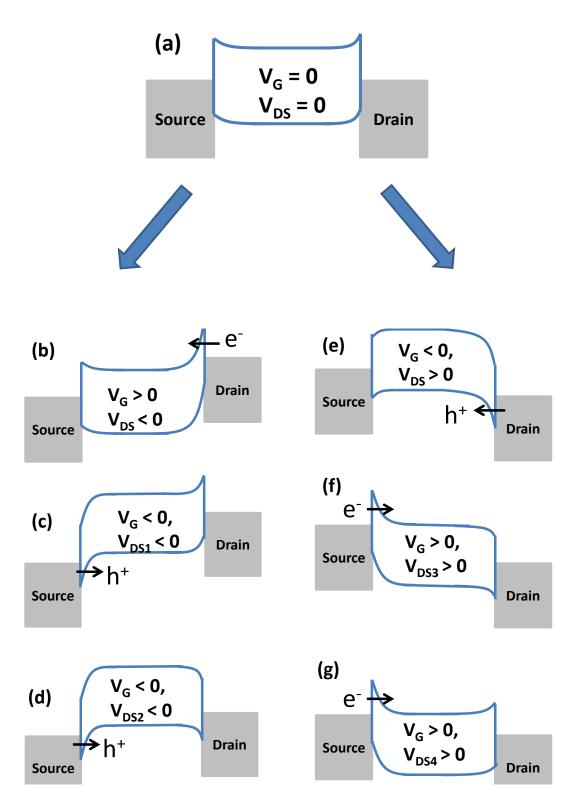

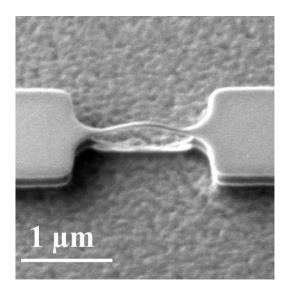

- Figure 3.5: Schematic of gate modulation of Schottky barrier width......37

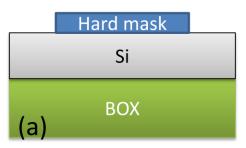

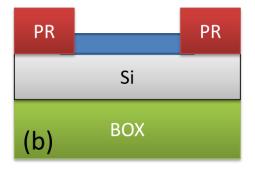

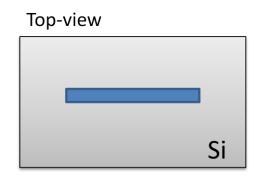

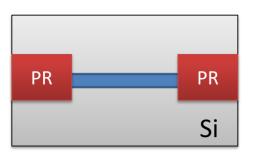

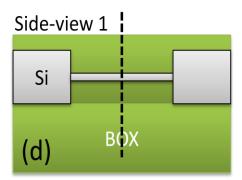

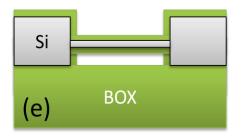

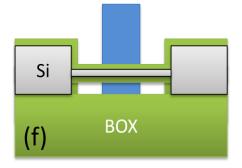

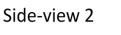

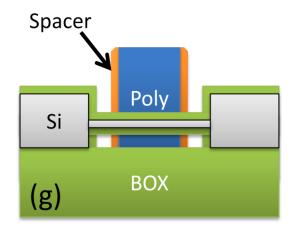

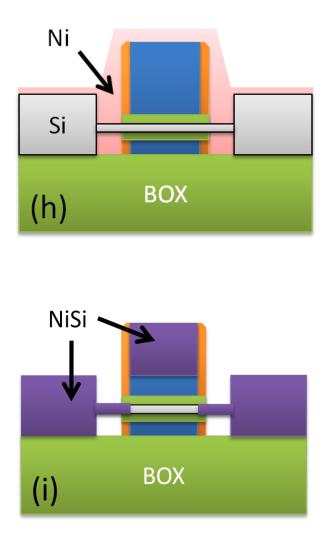

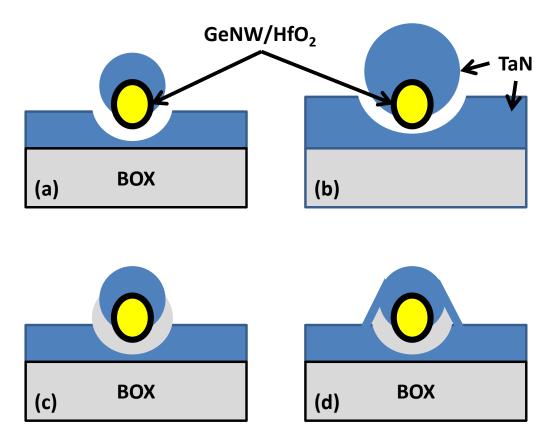

- Figure 3.6: Schematics of the Si nanowire NiSi S/D MOSFET fabrication process.

Schematics after (a) fin hard mask pattern and etch; (b) S/D photoresist pattern; (c) Si-fin etch; (d) self-retarded Si-fin oxidation;

(e) gate oxide growth; (f) LPCVD amorphous Si deposition; (g) poly-gate etch and spacer formation; (h) oxide wet etch and Ni deposition; (i) Ni silicidation and Ni wet removal. From (a) to (c), the left side is the cross-sectional view and the right side is the top view. From (d)-(f), the left side is the side view and the right side is the cross-sectional view.

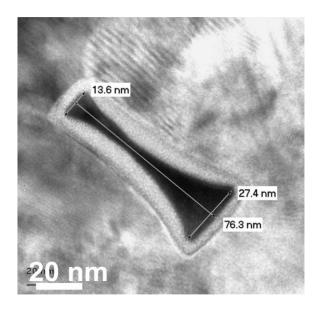

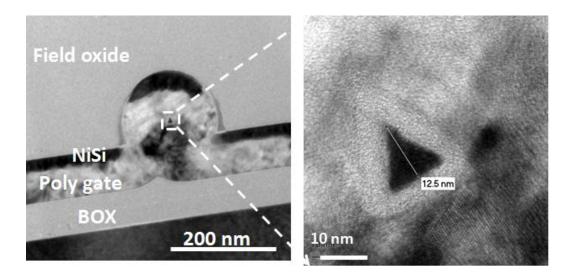

- Figure 3.9: TEM image of 80-nm-wide Si fins after  $875^{\circ}$ C dry oxidation......47

- Figure 3.10: TEM images of a single 12.5-nm height triangular shape Si nanowire formed by dry oxidation at 875°C......47

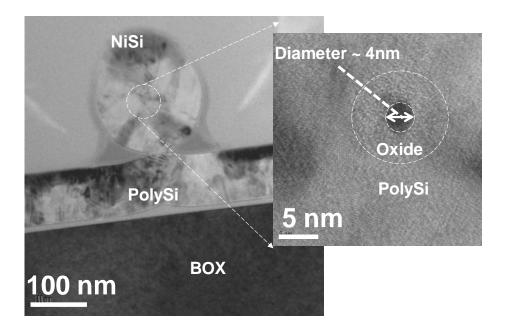

| Figure 3.11: Cross sectional TEM images of a single 4 nm diameter Si nanowire          |

|----------------------------------------------------------------------------------------|

| formed by dry oxidation at 875°C. A circular Si nanowire surrounded                    |

| by 5 nm gate oxide is observed48                                                       |

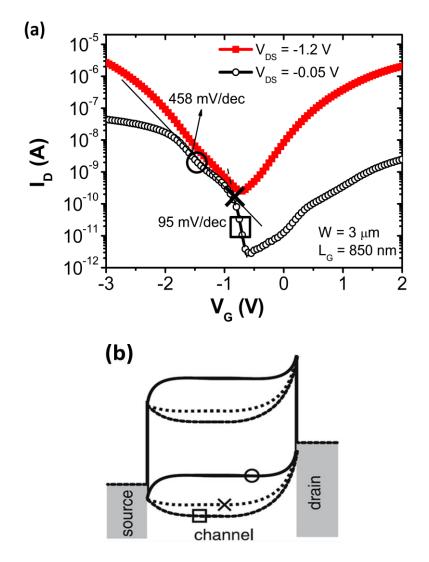

| Figure 3.12: (a) $I_DV_G$ characteristics of a planar Si Schottky barrier pMOSFET. (b) |

| Energy band diagram of a Si Schottky barrier pMOSFET. The $\Box$ , $\times$            |

| and $\bigcirc$ stand for the regime under different gate bias in the $I_DV_G$ and      |

| in the energy band diagram49                                                           |

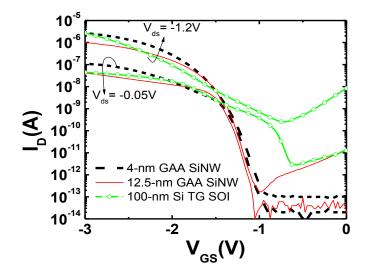

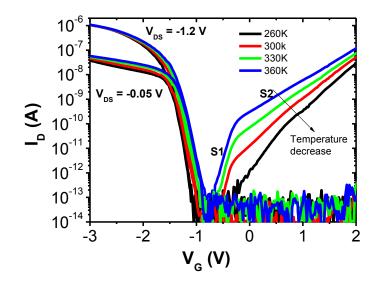

| Figure 3.13: The $I_DV_G$ characteristics of a 4-nm, 12.5-nm diameter GAA Si           |

| nanowire and a 100-nm Si thickness top-gate SOI NiSi S/D SB-                           |

| MOSFETs52                                                                              |

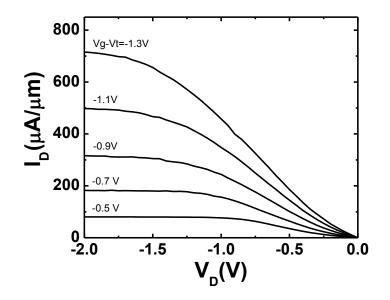

| Figure 3.14: Output characteristics of a 4-nm diameter, 150 nm gate length NiSi        |

| Schottky barrier S/D Si nanowire GAA FET. The non-linearity of the                     |

| linear region suggests the impact of Schottky barrier                                  |

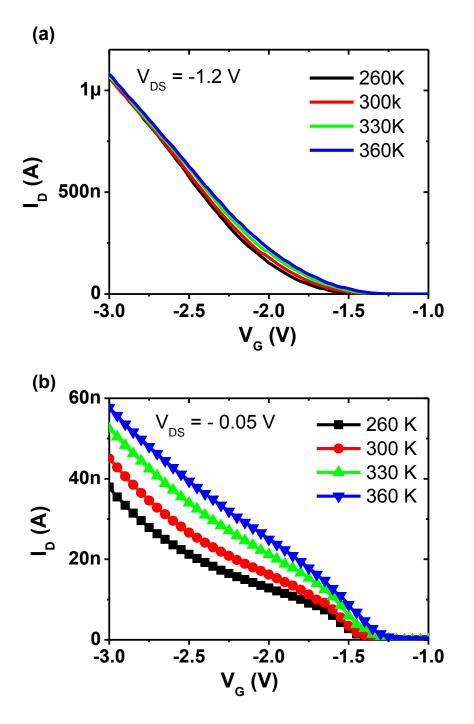

| Figure 3.15: The transfer characteristics of a 12.5 nm width 850-nm gate length Si     |

| nanowire Schottky barrier MOSFET at temperature from 260 K to                          |

| 360 K53                                                                                |

| Figure 3.16: The linear plot of the transfer characteristic of a 12.5 nm width 850-    |

| nm gate length Si nanowire Schottky barrier MOSFET at                                  |

| temperature from 260 K to 360 K at (a) $VDS = -1.2$ V and (b) $VDS =$                  |

| -0.05 V                                                                                |

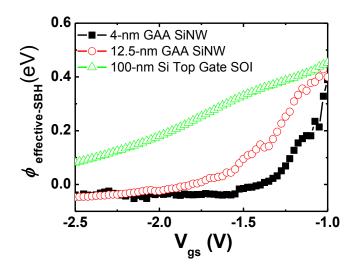

| Figure 3.17: the effective Schottky barrier height of a 4-nm-diameter and a 12.5-      |

| nm-diameter Si nanowire GAA SB-MOSFET as a function of gate                            |

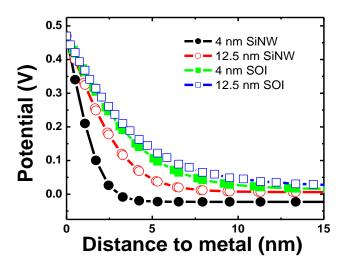

| Figure 3.18: Calculated potential profile of the Schottky barrier at on-state. The    |

|---------------------------------------------------------------------------------------|

| circle ones represent the Si nanowire GAA SB-MOSFET and the                           |

| square ones represent top-gate SOI SB-MOSFET57                                        |

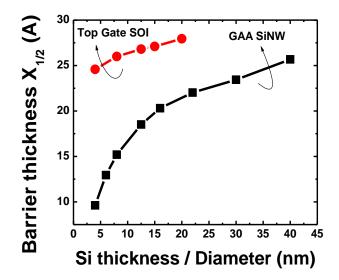

| Figure 3.19: Calculated Full-Barrier-Width at Half Maximum (X1/2) as a function       |

| of the Si body thickness of top-gate SOI planar devices and Si                        |

| nanowire diameters                                                                    |

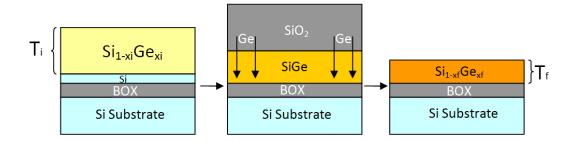

| Figure 4.1: Schematic illustration of Ge condensation technique. $T_i$ is the initial |

| SiGe thickness and T <sub>f</sub> is the final SiGe/Ge thickness64                    |

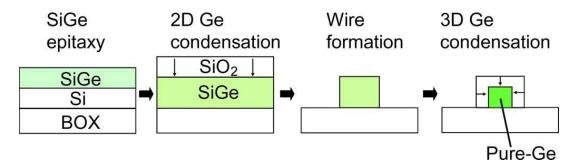

| Figure 4.2: Schematic illustration of proposed fabrication procedures for Ge          |

| nanowire. Two/three dimensional Ge condensations are properly                         |

| utilized [10]64                                                                       |

| Figure 4.3: 45° tilted SEM image of SiGe nanowire after three-dimensional Ge          |

| condensation and oxide strip. The nanowire bends due to large                         |

| compressive stress induced by the replacement of Si atoms with Ge                     |

| atoms65                                                                               |

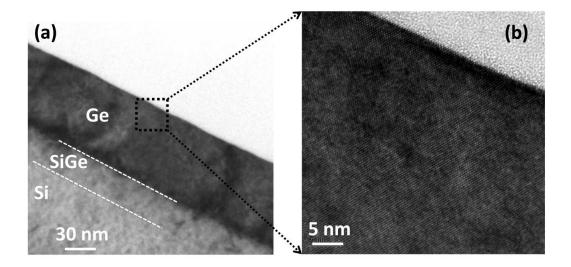

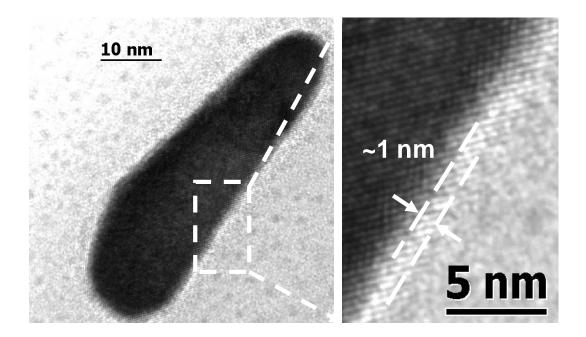

| Figure 4.4: HR-TEM image of cross sectional view of Ge epitaxial grown on Si          |

| with ~ 30 nm SiGe buffer layer. The left side is the zoomed in view                   |

| of the surface Ge lattice67                                                           |

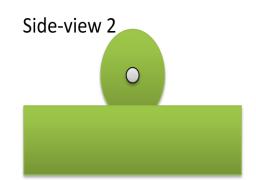

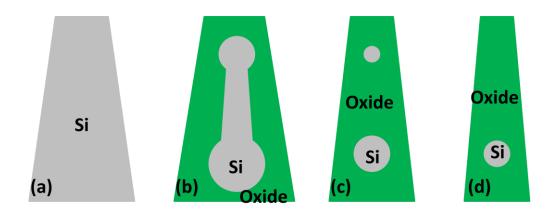

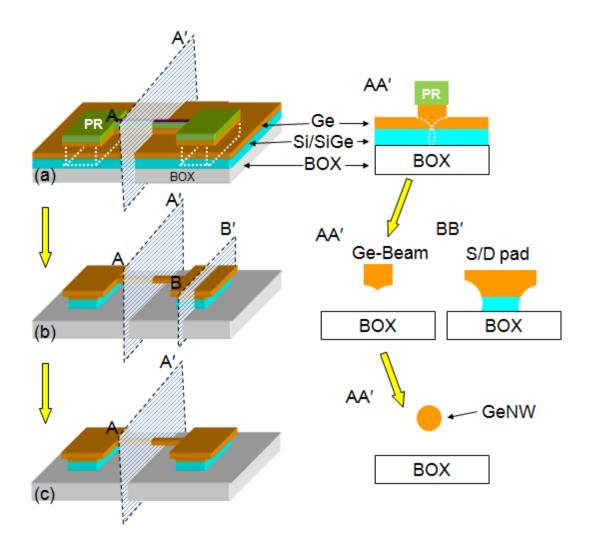

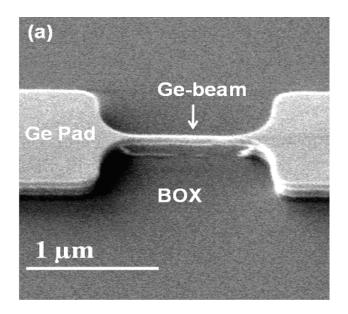

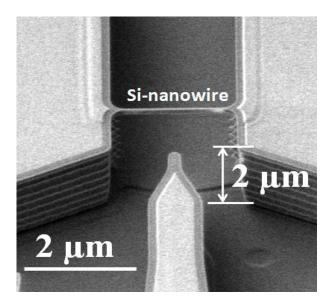

| Figure 4.5: Schematics of the Ge nanowire formation process flow. (a) After fin       |

| patterning, photoresist trimming and anisotropic Ge etching. The                      |

| dotted line indicates the consequential isotropic etching profile. The                |

| starting material is Ge (~100 nm) / SiGe (~30 nm) / Si (~25 nm) on                    |

BOX. (b) After isotropic etching and photoresist striping. The bottom Ge and SiGe/Si buffer layer are totally removed. (c) After

| cyclic thermal oxidation and wet etching of Ge oxide. The suspended |

|---------------------------------------------------------------------|

| Ge-beam is trimmed down to Ge nanowire. The left hand side is the   |

| 3-D schematics and the right hand side is the corresponding cross-  |

| sectional view70                                                    |

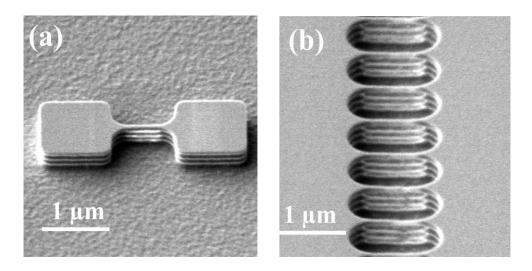

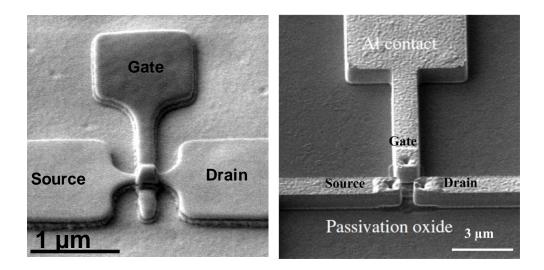

- Figure 4.8: 45° tilted SEM image of multi-stacked nanowires formed by repeating the two-step etching processes on testing Si wafer......73

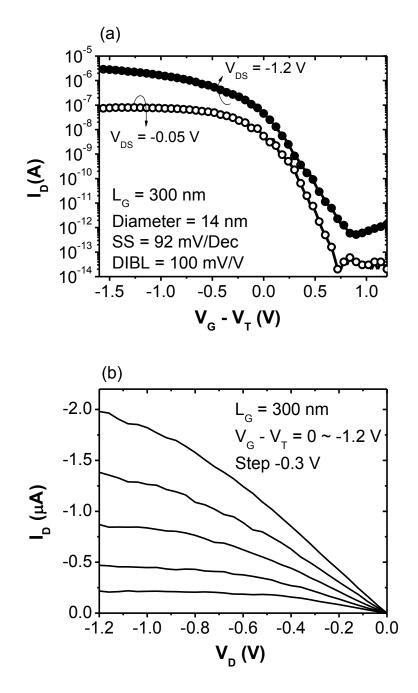

- Figure 4.12: (a)  $I_D$ - $V_G$  and (b)  $I_D$ - $V_D$  characteristics of an  $\Omega$ -gate GeO<sub>2</sub> shell GeNW transistor. The diameter of the GeNW is 14 nm and the gate

| length is | 300 | nm. | GeNW | is | covered | with | 6.8 | nm | $GeO_2$ | shell | and | 11 |

|-----------|-----|-----|------|----|---------|------|-----|----|---------|-------|-----|----|

|           |     |     |      |    |         |      |     |    |         |       |     |    |

nm HfO<sub>2</sub> dielectric.....79

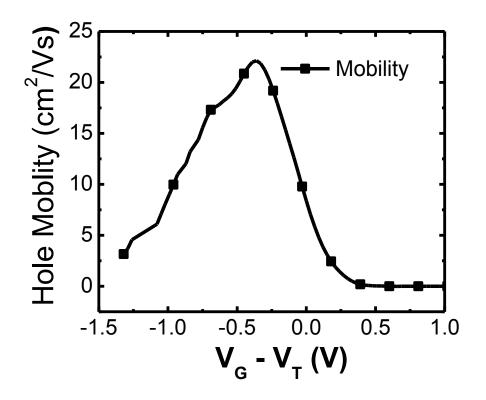

- Figure 4.14: Hole mobility in a Ge nanowire as a function of the gate over drive. The peak mobility is ~  $22 \text{ cm}^2/\text{V*s}$  after S/D resistance correction. 82

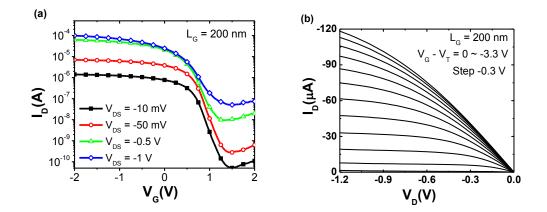

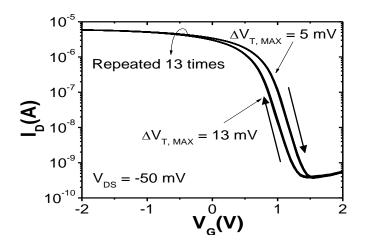

- Figure 5.5: (a)  $I_D$ - $V_G$  and (b)  $I_D$ - $V_D$  characteristics of Ge/Si core/shell nanowire GAA PMOS. The Ge/Si core/shell nanowire diameter is 35 nm and

| gate length is 200 nm. The epitaxial-Si shell is with 2 nm and $HfO_2$ is                        |

|--------------------------------------------------------------------------------------------------|

| 11 nm. Subthreshold slope is 162 mV/dec at $V_{DS} = -50 \text{ mV}92$                           |

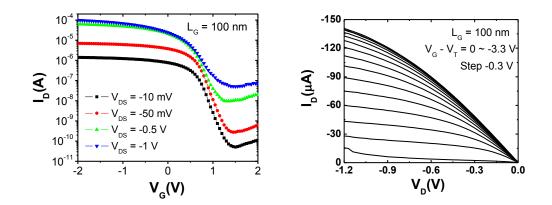

| Figure 5.6: (a) $I_D$ - $V_G$ and (b) $I_D$ - $V_D$ characteristics of Ge/Si core/shell nanowire |

| GAA pMOSFET. The Ge/Si core/shell nanowire diameter is 35 nm                                     |

| and gate length is 100 nm. Subthreshold slope is 202 mV/dec at $V_{\text{DS}}$                   |

| =- 50 mV93                                                                                       |

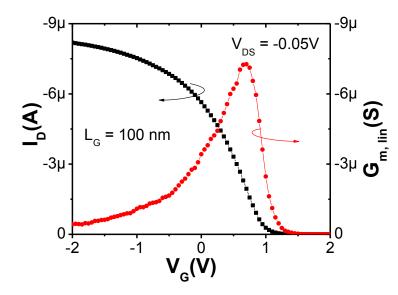

| Figure 5.7: Linear $I_D$ - $V_G$ and $G_m$ - $V_G$ obtained from a Ge/Si core/shell nanowire     |

| GAA PMOS with 100 nm gate length. The peak transconductance is                                   |

| 7.27 μS93                                                                                        |

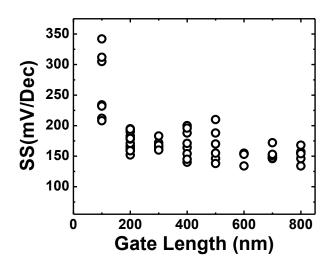

| Figure 5.8: SS of Ge/Si core/shell nanowire GAA pMOSFET vs. gate length94                        |

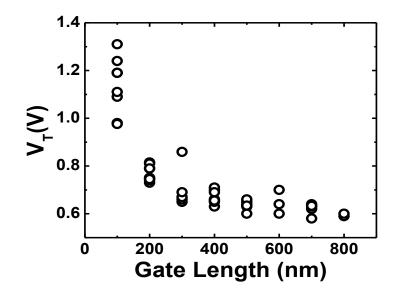

| Figure 5.9: Threshold voltage of Ge/Si core/shell nanowire GAA pMOSFETs vs.                      |

| gate length. $V_T$ is ~ 0.7 V for long channel devices                                           |

| Figure 5.10: Energy band diagram of the Ge/Si core/shell structure. The dotted                   |

| line is the Fermi level95                                                                        |

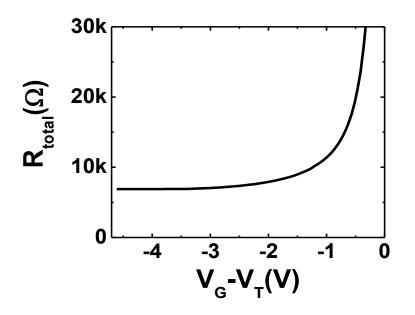

| Figure 5.11: Total series resistance of a 200 nm gate length Ge/Si core/shell                    |

| nanowire pMOSFET as a function of gate overdrive. The smallest                                   |

| total resistance is $\sim$ 7 k $\Omega$ at -4.5 V gate overdrive96                               |

| Figure 5.12: Total series resistance of Ge/Si core/shell nanowire pMOSFETs at                    |

| various gate overdrives as a function of gate length. The parasitic                              |

| series resistance is extracted by extrapolating the total series                                 |

| resistances of various gate length devices to an intersect point, which                          |

| is ~ 3.5 k $\Omega$ for this batch of Ge/Si core/shell nanowire devices97                        |

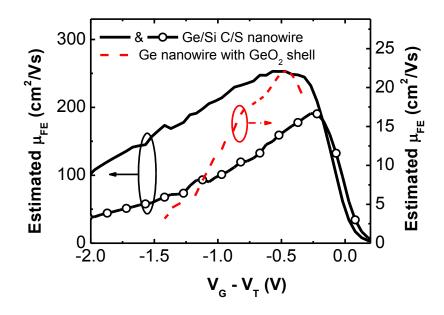

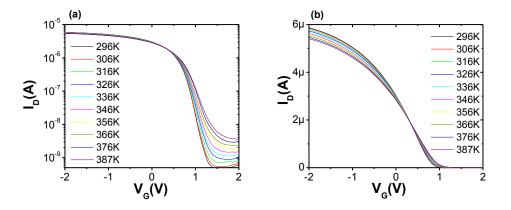

Figure 5.13: Estimated hole field-effect mobility ( $\mu_{FE}$ ) in the Ge/Si C/S nanowire and Ge nanowire with GeO<sub>2</sub> shell as a function of gate overdrives.

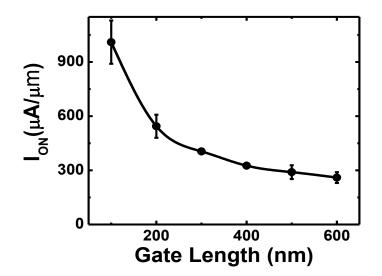

- Figure 5.14: On-state current of Ge/Si core/shell nanowire pMOSFETs at  $V_G V_T$ = -0.7 V and  $V_{DD}$  = 1 V, as a function of gate length......100

- Figure 5.17: The (a) log scale plot and (b) linear scale plot of drain current of a 200 nm gate length Ge/Si core/shell nanowire pMOSFET  $V_{DS}$  = -

0.05 V as a function of gate bias at different temperature. ......103

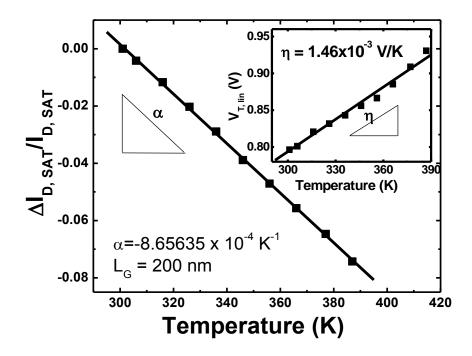

- Figure 5.18:  $I_{D, SAT}$  and  $V_{T, Lin}$  (inset) variation of GAA Ge/Si core/shell pMOSFET as a function of temperature, from which the ballistic efficiency is extracted to be 0.524.  $I_{D,SAT}$  is obtained at  $V_G = -1.5$  V.

- Figure 5.19:  $I_{D, SAT}$  and  $V_{T, Lin}$  (inset) variation of GAA Ge/Si core/shell pMOSFET as a function of temperature, from which the ballistic efficiency is extracted to be 0.524.  $I_{D,SAT}$  is obtained at  $V_G = -1.5$  V.

# **List of Symbols**

| Symbol                                                                                                             | Description                                                                                                                                                                                                                                                               | Unit                                                                                                |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| С                                                                                                                  | Capacitance                                                                                                                                                                                                                                                               | fF/µm <sup>2</sup>                                                                                  |

| C                                                                                                                  | Capacitance of gate oxide                                                                                                                                                                                                                                                 | fF/µm <sup>2</sup>                                                                                  |

| $\xi^{\text{ox}}$<br>P<br>$X_j$<br>$N_{\text{sub}}$<br>$I_G$                                                       | Scaling factor<br>Power consumption<br>S/D junction depth<br>Substrate doping<br>Gate leakage current<br>Gate dielectric constant                                                                                                                                         | W<br>nm<br>/cm <sup>3</sup><br>A                                                                    |

| E <sub>G</sub><br>E <sub>C</sub><br>E <sub>F</sub>                                                                 | Semiconductor bandgap<br>Si conduction band-edge<br>Fermi-level energy                                                                                                                                                                                                    | eV<br>eV<br>eV                                                                                      |

| E <sub>v</sub>                                                                                                     | Si valence band-edge                                                                                                                                                                                                                                                      | eV                                                                                                  |

| $G_m$ $I_{Dsat}$ $I_{off}$ $I_{on}$ $I$ $D$                                                                        | Transconductance<br>Drain saturation current (per unit width)<br>Off state current (per unit width)<br>On state current (per unit width)<br>Transistor drive current                                                                                                      | S<br>A/μm<br>A/μm<br>A/μm<br>A                                                                      |

| $ \begin{array}{l} \mu_{\rm eff} \\ \mu_{\rm FE} \\ N_A \\ \tau \\ V_{DS} \\ V_{GS} \\ V_{DD} \\ V_T \end{array} $ | Effective mobility<br>Field effective mobility<br>Substrate doping concentration atoms<br>Intrinsic gate delay<br>Drain voltage<br>Gate voltage<br>Supply Voltage<br>Threshold voltage                                                                                    | cm <sup>2</sup> /V-s<br>cm <sup>2</sup> /V-s<br>/cm <sup>3</sup><br>s<br>V<br>V<br>V<br>V<br>V<br>V |

| $V_{T,lin}$<br>$L_{G}$<br>q<br>$T_{ox}$<br>W<br>$\varepsilon_{Si}$<br>$\varepsilon_{SiO2}$<br>$\Phi$<br>bn         | Linear threshold voltage<br>(Extracted in linear regime at low $V_{DS}$ )<br>Gate length<br>Electronic charge<br>Equivalent oxide thickness<br>Transistor gate width<br>Permittivity of silicon<br>Permittivity of silicon oxide<br>Schottky barrier height for electrons | V<br>nm<br>C<br>nm<br>$\mu$ m<br>F/cm <sup>2</sup><br>F/cm <sup>2</sup><br>eV                       |

| $\Phi_{_{bp}}$                                                                                                     | Schottky barrier height for holes                                                                                                                                                                                                                                         | eV                                                                                                  |

| $V_{bi}$<br>$V_F$<br>T<br>$R_c$                                                                                    | Built-in potential in Schottky diode<br>Forward bias voltage<br>Temperature<br>Backscattering coefficient                                                                                                                                                                 | eV<br>V<br>K                                                                                        |

# **List of Abbreviations**

| AFM       | Atomic force microscopy                               |  |  |

|-----------|-------------------------------------------------------|--|--|

| ALD       | Atomic layer deposition                               |  |  |

| BOX       | Buried oxide                                          |  |  |

| CMOS      | Complimentary-Metal-Oxide-Semiconductor               |  |  |

| CVD       | Chemical vapor deposition                             |  |  |

| CET       | Capacitance equivalent thickness                      |  |  |

| C-V       | Capacitance-Voltage                                   |  |  |

| CD        | Critical dimensions                                   |  |  |

| DG        | Double-Gate                                           |  |  |

| DHF       | Diluted Hydrofluoric (acid)                           |  |  |

| DIBL      | Drain induced barrier-Lowering                        |  |  |

| EDX       | Energy dispersive X-ray                               |  |  |

| EELS      | Electron energy loss spectroscopy                     |  |  |

| EOT       | Equivalent oxide thickness                            |  |  |

| GAA       | Gate-All-Around                                       |  |  |

| Ge        | Germanium                                             |  |  |

| GIDL      | Gate induced drain leakage                            |  |  |

| GOI       | Germanium-On-Insulator                                |  |  |

| HK        | high- $\kappa$ (dielectric)                           |  |  |

| HM        | Hard mask                                             |  |  |

| HRTEM     | High resolution transmission electron microscopy      |  |  |

| ITRS      | international technology roadmap for semiconductors   |  |  |

| ICs       | Integrated Circuits                                   |  |  |

| I-V       | Current-Voltage                                       |  |  |

| LPCVD     | Low pressure chemical vapor deposition                |  |  |

| MG        | Metal-Gate                                            |  |  |

| MOSFET    | Metal-Oxide-Semiconductor-Field-Effect-Transistor     |  |  |

| NW        | Nanowire                                              |  |  |

| PDA       | Post deposition annealing                             |  |  |

| PMD       | Post metal dielectric                                 |  |  |

| PR        | Photoresist                                           |  |  |

| PVD       | Physical vapor deposition                             |  |  |

| PECVD     | Plasma enhanced chemical vapor deposition             |  |  |

| RF        | Radio frequency                                       |  |  |

| RMS       | Root mean square                                      |  |  |

| RTA       | Rapid thermal annealing                               |  |  |

| RIE       | Reactive ion etching                                  |  |  |

| SBH       | Schottky barrier height                               |  |  |

| SB-MOSFET | Schottky barrier MOSFET                               |  |  |

| SC-1      | Standard cleaning-1 ( $NH4OH + H2O2 + H2O$ ) solution |  |  |

| Si        | Silicon                                               |  |  |

| SS        | Subthreshold swing                                    |  |  |

| SCE       | Short channel effects                                 |  |  |

| S/D       | Source/drain                                          |  |  |

|           |                                                       |  |  |

| SEM     | Scanning electron microscopy                     |  |  |

|---------|--------------------------------------------------|--|--|

| STEM    | Scanning transmission electron microscopy        |  |  |

| SOI     | Silicon-On-Insulator                             |  |  |

| SG-NW   | SiGe nanowire                                    |  |  |

| TEM     | Transmission electron microscopy                 |  |  |

| UHV     | Ultra high vacuum                                |  |  |

| UTB     | Ultra thin body                                  |  |  |

| UTB-SOI | Ultra thin body Silicon-On-Insulator             |  |  |

| VLS     | Vapor liquid solid                               |  |  |

| XTEM    | Cross-sectional transmission electron microscope |  |  |

# Chapter 1 Introduction

Nowadays, integrated chips (ICs) have been widely used and become a critical component in almost every aspects of our daily life. ICs mainly consist of planar silicon (Si) Metal-Oxide-Semiconductor-Field-Effect-Transistors (MOSFETs) and the performance of the individual MOSFET is a key factor of the whole circuits' performance. Thus, intensive studies have been carried out to improve MOSFET performance ever since its invention in the early 1960s. This chapter will discuss various approaches to improve MOSFET performance and their challenges. At the end, it is the thesis organization.

## **1.1** Approaches to improve MOSFET performance

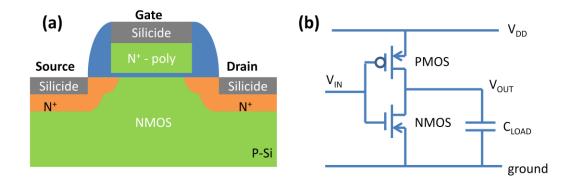

The schematic of an nMOSFET is shown in Fig. 1.1 (a). A MOSFET is an electrical switch and the current flowing between the two terminals of source & drain (S/D) is controlled by the electric field from the third terminal of gate (G). There are two operating modes of a transistor. One is the off-state at which its gate bias is the same as its source bias. At off-state mode, there is no current flow between the S/D. The other mode is on-state at which its gate bias is the same as its drain bias. At on-state mode, a thin layer of inversion charge below the gate electrode is formed by the electrical field from the gate electrode. This layer of charges connects the S/D and let the current flows between them. Fig. 1.1 (b)

shows a typical inverter circuit. If the input voltage ( $V_{IN}$ ) is initially zero at ground voltage, nMOSFET is at off-state and pMOSFET is at on-state. In this case, the loading capacitor ( $C_{LOAD}$ ) is charged and the output voltage ( $V_{OUT}$ ) is at supply voltage ( $V_{DD}$ ). When  $V_{IN}$  is switched from zero to supply voltage  $V_{DD}$ , nMOSFET turns to on-state and pMOSFET turns to off-state. In this case,  $C_{LOAD}$  is discharged through the nMOSFET. In this discharging process,  $V_{OUT}$  switches from  $V_{DD}$  to zero in response to the switching of  $V_{IN}$  from zero to  $V_{DD}$ . The responding speed of this circuit is determined by the on-state current of nMOSFET and the amount of charge stored in the loading capacitor  $C_{LOAD}$ . Similarly, the capacitor is charged through the pMOSFET when  $V_{IN}$  switches from  $V_{DD}$  to zero, and the responding speed of this circuit is determined by the on-state current of state current of pMOSFET and the amount of charge stored in the loading capacitor  $C_{LOAD}$ .

Figure 1.1: (a) Schematic of a conventional planar NMOS cross-sectional image and (b) a typical inverter circuit consisting of one NMOS and one PMOS.

As discussed above, the switching speed of the inverter circuit is determined by the on-state current of the transistors and the loading capacitor  $C_{LOAD}$ . In real applications,  $C_{LOAD}$  consists of both the interconnect capacitance and transistors' capacitance, which is complicated and circuit dependent. For simplicity, the speed of an individual transistor is evaluated by its intrinsic gate delay  $\tau$  [1]:

$$\tau = \frac{C_{GATE} * V_{DD}}{I_{ON}} \tag{1.1}$$

where  $C_{GATE}$  is the transistor gate capacitance,  $V_{DD}$  is the supply voltage and  $I_{ON}$  is the on-state current. The on-state current of a long channel transistor can be described as:

$$I_{ON} = \frac{C_{ox} * \mu * W * (V_G - V_T)^2}{2L_G}$$

(1.2)

where  $C_{OX}$  is the gate capacitance per unit area,  $\mu$  is the effective carrier mobility, W is the transistor width,  $V_G$  is the gate voltage,  $L_G$  is the channel length, and  $V_T$ is the threshold voltage which can be expressed as a portion of the supply voltage  $V_{DD}$ . Thus,  $V_T = \alpha^* V_{DD}$ , where  $\alpha$  is a constant between 0 and 1. At the on-state in which  $V_G = V_{DD}$ , after replacing  $I_{ON}$  with the equation 1.2, the intrinsic gate delay can be described as:

$$\tau = \frac{C_{GATE} * V_{DD}}{I_{ON}} = \frac{C_{OX} * W * L_G * V_{DD}}{I_{ON}} = \frac{2 * \alpha^2 * L_G^2}{\mu * V_{DD}}$$

(1.3)

According to the equation 1.3, there are four approaches to improve the transistor speed:

- 1. Increasing the supply voltage  $V_{DD}$ ;

- 2. Decreasing the constant  $\alpha$  to have a smaller V<sub>T</sub>;

- 3. Decreasing the transistor gate length  $L_G$ ;

- 4. Increasing the carrier mobility  $\mu$ .

Approach (1) and (2) are not preferred as the gain of speed by these approaches has a cost of higher power consumption. The power consumption of one transistor can be roughly described by [2]:

$$P \approx Af C_{LOAD} V_{DD}^{2} + I_{o} * 10^{-\frac{V_{T}}{SS}} * V_{DD} + I_{LEAK} * V_{DD}$$

(1.4)

where A is a constant value, f is the operating frequency,  $I_o$  is the drain current at  $V_G = V_T$ ,  $I_{LEAK}$  is the total leakage current including gate and junction leakages, SS is the subthreshold slope. The equation 1.4 clearly shows larger  $V_{DD}$  and smaller  $V_T$  would increase the power consumption significantly.

Approach (3) has been adopted by the semiconductor industry and kept improving the MOSFET performance for around four to five decades. This approach is generally referred as scaling down. The magic of scaling down is that it could improve the transistor performance and lower the fabrication cost simultaneously. However, it has become challenge to scale down further due to stringent constrains in the tradeoff between on-state current, power consumption and short channel effects in sub-100 nm technology node. This approach, including its advantages and challenges, will be discussed in details in section 1.2.

Approach (4) is an alternative and increasingly important approach of improving the MOSFET performance for advanced transistors. Since approach (3) of scaling down Si-MOSFET is much cheaper and easier, this approach has not being attractive for a long time. However, as the scaling of Si MOSFETs approaches its physical limit, this approach has attracted increasingly more attention recently. Some technologies under this category, such as strain engineering, have been employed to improve the carrier mobility in sub-90-nm technology nodes already [3]. Furthermore, semiconductor with higher carrier mobility such as germanium (Ge) [4-8] and III-V compounds [1, 9, 10], have been intensively investigated as alternative channel materials for future transistors.

### **1.2 MOSFET scaling**

#### 1.2.1 Overview of MOSFET scaling

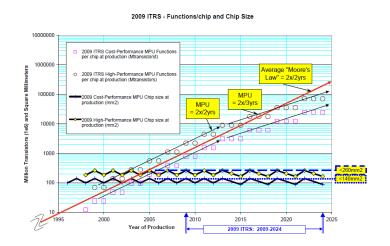

Perhaps, a large part of the success of the planar Si MOSFET is due to the fact that it can be scaled down to increasingly smaller dimensions, which gains two benefits simultaneously: (1) faster transistor, which means higher performance ICs; (2) lower cost per transistor as each transistor takes less area on the chips. This remarkable trend was first pointed out by Gordon Moore and well known as Moore's law, which predicts that the number of transistors per integrated circuit would double approximately every  $\sim 2$  years within approximately the same size chip (Fig. 1.2)[1].

Figure 1.2: 2009 ITRS product technology trends: MPU product functions/chip and industry average "Moore's Law" and chip size trends[11].

| Scaling factor: ξ | Before Scaling  | Constant-Voltage  | Constant-Field   |

|-------------------|-----------------|-------------------|------------------|

| Gate Length       | L <sub>G</sub>  | ξL <sub>G</sub>   | ξL <sub>G</sub>  |

| Gate Width        | W               | ξW                | ξW               |

| Oxide Thickness   | T <sub>ox</sub> | T <sub>ox</sub>   | ξT <sub>ox</sub> |

| Supply Voltage    | V <sub>DD</sub> | V <sub>DD</sub>   | $\xi V_{DD}$     |

| Drain Current     | I <sub>D</sub>  | I <sub>D</sub>    | ξI <sub>D</sub>  |

| Power / Area      | Р               | P/ ξ <sup>2</sup> | Р                |

| Delay             | τ               | $\xi^2 t$         | τ                |

Table 1.1: Transistor parameters in constant-voltage scaling and constant-field scaling, assuming long channel device and power =  $I_D * V_D$ .

There are two types of scaling, constant-voltage scaling and constant-field scaling. Table 1.1 shows the transistor parameters in the two scaling approaches. In constant-voltage scaling, only the lateral dimensions – the gate length  $L_G$  and gate width W of the transistor – are scaled down by the scaling factor  $\xi$ ; while in constant-field scaling, the lateral and perpendicular dimensions as well as the supply voltage, are scaled down proportionally to maintain an approximately constant electrical field in the channel and the gate oxide.

In constant-voltage scaling, both the perpendicular dimensions and the supply voltage remains the same. Thus, as the gate length scales down, the electrical field between drain and source would keep increasing. At certain point, the electrical field is so strong that the Source/drain (S/D) depletion region would meet with each other and lead to mal-function transistors. Hence, the perpendicular dimension and the supply voltage need to be scaled down as well in

practical application, which is similar to constant-field scaling. In real application, it is generally required that the next generation of scaled-down circuit works faster than the last generation. This requirement is generally accomplished by not scaling down the supply voltage as aggressively as other parameters for a tradeoff with higher power density consumption.

#### **1.2.2** Challenges of further scaling MOSFET

For a long time, a faster and cheaper transistor can be obtained by adopting the constant field scaling approach without causing any serious issues. However, it has been recognized that, in sub-100 nm regime, this conventional device scaling has confronted the difficulty that the three main performance indexes associated with MOSFET performance – on current, power consumption and short channel effects – have a tradeoff with each other, owing to several physical and essential limitations directly related to the device scaling down [10].

Short channel effects arise when the MOSFET channel length is scaled down to the same order of magnitude as the depletion-layer width of the S/D junction. As the gate length is reduced, drain and source become so close that the channel potential is influenced not only by the gate bias, but also by the drain bias. Thus, the potential barrier at channel is no longer effective to block the carrier transportation between source/drain. To suppress short channel effects, it is required to have thinner gate oxide, higher substrate doping ( $N_{sub}$ ), smaller S/D junction depth ( $X_j$ ), lower extension concentration and lower supply voltage ( $V_{DD}$ ). However, it is obvious that those requirements conflict with those of higher I<sub>ON</sub> and lower power consumption. Thinner gate oxide will increase gate leakage (I<sub>G</sub>) exponentially, which increase the power consumption significantly. It is reported that the direct tunneling current of  $I_G$  increases approximately one order with every 2 Å reduction of gate oxide thickness for a normal gate oxide thickness of 15 Å [12]. Smaller  $X_j$  and lower extension concentration increase S/D series resistance, which consequentially decrease on current significantly. The increase of  $N_{sub}$  is necessary in suppressing short channel effects in bulk MOSFETs; however, it increases  $I_{leak}$  due to junction tunneling current and gate induced drain leakage current. In addition, it causes the reduction of  $I_{ON}$  as it lowers the carrier mobility.

From equation 1.4, it is required to have smaller  $V_{DD}$ , larger  $V_T$  and thicker gate oxide to have lower power consumption. Apparently, smaller  $V_{DD}$  and larger  $V_T$  decrease  $I_{ON}$  while thicker gate oxide leads to worse short channel effect performance. On the other hand, achieving larger on-state current requires higher  $V_{DD}$ , smaller  $V_T$ , thinner gate oxide, higher extension concentration, higher junction depth and lower substrate doping, which apparently conflict with those of lower power consumption and better short channel effects immunity.

As a result, for any approach of further improving the MOSFET performance, it needs to overcome these difficulties or to mitigate these stringent constraints in this tradeoff, that is to satisfy the high performance and low power consumption against these physical limitations simultaneously. High-k/metal-gate, which can mitigate the tradeoff between gate leakage and equivalent-oxidethickness (EOT) requirements, have already been implemented for advanced MOSFETs. Employing the nanowire gate-all-around (GAA) transistor architecture is another approach to reduce the stringent requirement on EOT. High mobility semiconductor such as Ge has also attracted heavy attentions as alternative channel materials to improve on-state current without sacrificing the power consumption and short channel effects performance.

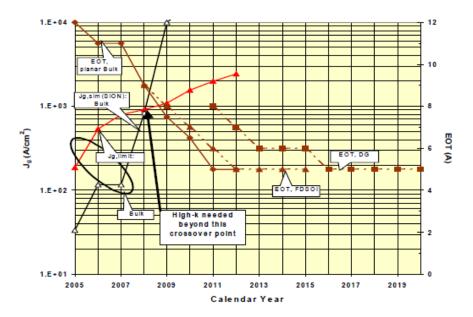

#### **1.3** High-k/metal-gate for gate dielectric scaling

High-k gate dielectric is necessary to scales down the EOT further for advanced transistors. One of the main challenges to scale down advanced MOSFETs is the gate oxide scaling. As listed in table 1.1, the oxide thickness is required to be reduced by the scaling factor  $\xi$  for the next generation transistors. For the last four decades, the SiO<sub>2</sub> gate dielectric thickness has been scaled down and reached its physical limit. According to International Technology Roadmap for Semiconductors (ITRS), a MOSFET with gate length below 90 nm will need oxide thickness of less than 12 Å as shown in Fig. 1.3. That corresponds to only a few layers of SiO<sub>2</sub> atoms, and it is so thin that the gate leakage has already become a major portion of the transistor power consumption. Further scaling down the oxide thickness will increase the leakage current exponentially, as the gate leakage current increases approximately one order with every 2 Å reduction of SiO<sub>2</sub> thickness when the SiO<sub>2</sub> thickness is less than 15 Å [12]. An alternative gate dielectric with dielectric constant (k) greater than  $SiO_2$  (k=3.9) has been proposed to reduce the gate tunneling leakage. With the benefit of higher dielectric constant, the gate dielectric physical thickness can be larger to suppress leakage current while maintain the same capacitive coupling to the channel. Among all the reported high-k materials, hafnium based oxide compound has already been employed by the semiconductor industry for its sufficiently large bandgap ( $E_g \sim 5.6 \text{ eV}$ ) and fairly high k value ~ 20 - 25. Additionally, thermal stable HfO<sub>2</sub> with EOT ~ 10 Å has been demonstrated on both Si [13] and Ge [6]. However, many challenges remains on further scaling down the EOT of hafnium oxide based material, such as the undesired interfacial layer formed by oxygen atoms and the substrate. The dielectric constant (k value) of this interfacial layer, such as SiO<sub>2</sub> for high-k on Si substrate, is much lower compared than that of high-k materials, and it limits further scaling down of the gate stack EOT. Thus, more scientific and technological innovations are needed to continue the scaling.

Figure 1.3: The limit of the gate leakage current  $(J_{g,limit})$  required by ITRS versus the simulated gate leakage current  $(J_{g,simulated})$  for high performance applications[11].

Another performance booster is the metal gate. The conventional gate electrode of heavily doped poly-Si has many advantages, such as adjustable work function, excellent compatibility to  $SiO_2$  and superior thermal stability. As MOSFETs scales down, it is found that poly-Si electrode has several problems and it is no longer a suitable gate electrode for advanced MOSFETs. The first problem is poly-depletion effect, which refers to the phenomenon that a thin layer of heavily doped poly close to the gate oxide is depleted and leads to  $\sim 3 - 5$  Å thicker EOT. This phenomenon is ignored for a long time as the EOT of the conventional long channel transistors is large. However, since the EOT of advanced transistors has been scaled down to less than 15 Å already, the additional 3 - 5 Å EOT due to the poly depletion effect becomes a significant portion and makes further gate oxide scaling problematic. Another problem of poly gate is that, the gate oxide of advanced transistors is so thin that boron could easily diffuse through the gate oxide into the substrate channel, which leads to a shifted threshold voltage and larger the gate dielectric leakage. Moreover, for high-k dielectric applications, the thermal dynamical stability of poly on high-k gate stacks and work function's Fermi-level pinning effects are all well reported problems. As a replacement of poly-Si gate, metal gate electrodes do not have all of these problems.

High-k/metal-gate has become necessary for advanced transistors, as it is able to reduce the gate leakage current or suppress short channel effects without sacrificing other key transistor performance parameters. Dual work function metal gates are normally required for deeply scaled planar devices. However, midbandgap metal gate is adequate for a GAA device due to better electrostatic coupling of GAA architecture. Among all the metal gate candidates, TaN is one of the well reported metal electrodes and it is chosen as the metal gate in this work for its good thermal stability on high-k materials and their mid-bandgap work function.

### **1.4 Objectives and scopes**

This project is to explore the top-down engineered nanowire GAA MOSFET for future transistor applications and to address its possible performance bottlenecks. The nanowire GAA architecture is well reported for its superior gate electrostatic coupling to the channel which is able to overcome/mitigate the stringent constraints in the tradeoff discussed in section 1.2; thus, it makes further scaling possible. In this project, two main issues are addressed:

- 1. The high parasitic series resistance of a nanowire GAA transistor limits its on-state current. The possible solution is studied in this project by replacing the heavily doped source/drain with highly conductive metal. The fabrication and understanding of the Si nanowire gate-all-around MOSFET with 1-D NiSi Schottky barrier source/drain is included in this thesis. The effective Schottky barrier height and Schottky barrier shape of Si nanowire and planar Schottky barrier MOSFETs are studied by both experimental data and MEDICI simulation in this project.

- 2. Ge is explored as a high carrier mobility channel and it is integrated with the nanowire GAA transistor architecture. A novel technique of fabricating Ge nanowires on an epitaxial Ge layer is presented in this thesis. The passivation layer of GeO<sub>2</sub> and Si shell are explored and characterized in this project. Ge nanowire transistors integrated with HfO<sub>2</sub>/TaN gate stack are characterized and studied in this project.

#### **1.5** Thesis organization

This thesis is organized in the following chapters:

Chapter 2 gives a background and literature review on nanowire and Ge transistors. The evolution of transistor architectures is presented and the motivation of developing nanowire GAA transistors is highlighted. The two main streams of nanowire fabrication technique - bottom-up and top-down techniques - are discussed. The background knowledge on Ge transistors is also discussed in chapter 2, including the motivation and major challenges of replacing Si channel with Ge channel. The development history of gate oxide of Ge MOSFETs is presented in chapter 2. Other challenges such as junction leakage and process integration are also discussed in chapter 2.

Chapter 3 presents the work of the Si nanowire gate-all-around MOSFET integrated with 1-D NiSi Schottky barrier source/drain. The background knowledge of Schottky barrier MOSFET is discussed first. The detailed fabrication processes of Si nanowire GAA MOSFETs integrated with 1-D NiSi Schottky source/drain are presented in this chapter. Device characterization is conducted on both Si nanowire and planar Schottky barrier MOSFETs. Carrier injection is found to be improved in nanowire GAA transistors in this chapter.

Chapter 4 presents the Ge nanowire pMOSFET on epitaxial Ge substrate. The detailed processes of Ge epitaxial growth on Si substrate and Ge nanowire formation on the epitaxial Ge substrate are presented and characterized. Ge nanowires integrated with HfO<sub>2</sub>/TaN gate stack and GeO<sub>2</sub> passivation shell are demonstrated and characterized in this chapter. Chapter 5 presents Ge/Si core/shell nanowire pMOSFETs. Epitaxial grown Si shell on Ge is explored as a technique to smooth the Ge surface. Additional implantation and Ni germanidation process through contact holes are employed to reduce the high series resistance of Ge nanowire transistors presented in chapter 4. Ge/Si core/shell nanowire pMOSFETs are characterized and studied in this chapter. The integration of the Si shell is found to be able to improve hole mobility in the Ge nanowire channel significantly.

Chapter 6 summarizes the major results and findings. It also provides some suggestions on future research.

# Chapter 2 Literature Review

## 2.1 Nanowire gate-all-around architecture

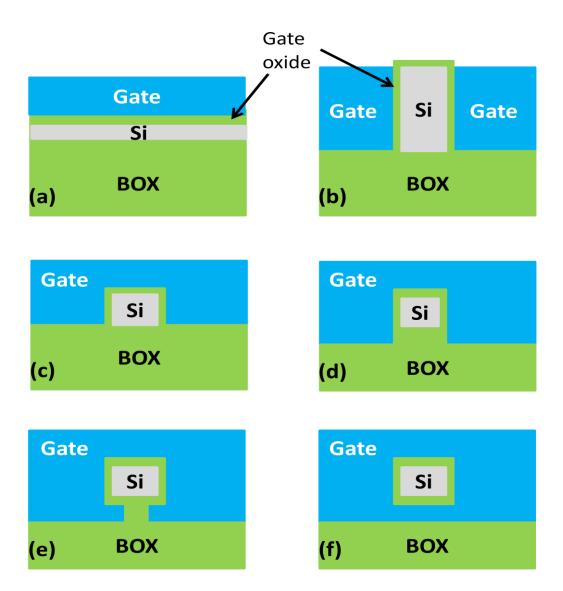

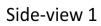

As discussed in chapter 1, MOSFET scaling requires scaling down the gate oxide thickness to suppress short channel effects for conventional bulk transistors, which, however, trades off with power consumption. While employing high-K/metal-gate is an approach to overcome/mitigate this tradeoff, employing innovative transistor architectures is another effective approach. Those innovative transistor architectures are able to enhance the gate electrostatic coupling to the channel. As a result, short channel effects can be effectively suppressed without scaling down the gate oxide thickness when switching from the conventional transistor architecture to those innovative ones. Fig. 2.1 shows those transistor architectures that have been extensively explored in the last decades. They are the fully depleted silicon-on-insulator (FD-SOI) transistor [14-16], the double-gate transistor [17, 18], the tri-gate transistor [19-21], the  $\pi$ -gate transistor[22-24], the  $\Omega$ -gate transistor[24-27] and the gate-all-around (GAA) nanowire transistor[28-30], with the gate electrostatic coupling capability becomes better and better.

Among all those innovative architectures, GAA nanowire MOSFETs have attracted intensive attentions from the research community for reasons discussed in the following paragraphs.

Figure 2.1: Schematics of transistor architecture evolution: (a) FD-SOI MOSFET; (b) double gate transistor; (c) Tri-gate transistor; (d)  $\pi$ -gate transistor; (e)  $\Omega$ -gate transistor; (f) GAA transistor.

The first advantage of the nanowire GAA architecture is its best electrostatic control over the channel and thus it has the best scalability [27, 31, 32]. By solving the Poisson's equation for potential in a double-gate SOI and a nanowire GAA transistor architecture, it has been clearly shown that the GAA nanowire architecture has better immunity to short channel effects [17, 32, 33]. At 1997, Auth et al. showed that, compared with double-gate MOSFETs, the minimum gate length of GAA transistors could be reduced up to 40 % while maintaining the same short channel performances with the same gate oxide and channel thickness[32]. Bescond et al. reported a simulation work on various device architectures with the gate length in sub-10-nm regime, and predicted that the GAA nanowire transistor has the best control over short channel effects[31]. His simulation work shows that a reasonable small subthreshold swing (SS) and drain induced barrier lowering (DIBL) are achievable at the sub-10-nm gate length regime with the GAA nanowire architecture.

|                  | Ref. [29] | Ref.[34]        | Ref. [35]       | Ref. [27]       | Ref. [36]        |

|------------------|-----------|-----------------|-----------------|-----------------|------------------|

| NW diameter (nm) | 5         | 8               | 1.5             | 5               | ~5               |

| Gate structure   | GAA       | GAA             | GAA             | Ω-gate          | GAA              |

| Gate type        | Poly-Si   | TiN             | Poly-Si         | Poly-Si         | Poly-Si          |

| Dielectric       | SiO2      | SiO2            | SiO2            | SiO2            | SiO2             |

| Lg(nm)           | 8         | 15              | 350             | 10              | 130              |

| EOT (nm)         | 4         | 3.5             | 4               | 1.9             | 5                |

| Vdd (V)          | 1.2       | 1               | 1.2             | 1               | 1.5              |

| Ion (µA/µm)      | 3740      | 1440            | 2400            | 522             | 1039             |

| Normalization    | Diameter  | Diameter        | Diameter        |                 | Diameter         |

| SS (mV/Dec)      | 75        | 72              | 60              | 75              | 72-74            |

| DIBL (mV/V)      | 22        | 50              | 6               | 80              | 4~12             |

| Ion/Ioff         | >107      | 10 <sup>6</sup> | 10 <sup>6</sup> | 10 <sup>5</sup> | >10 <sup>8</sup> |

Table 2.1: Summary of key device parameters of some of reported nanowire nMOSFETs.

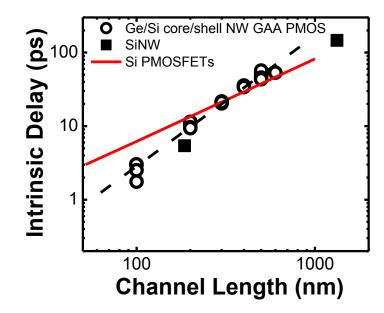

Experimental works confirmed the excellent scalability of the nanowire transistor. At 2004, Yang et al. reported the first sub-10 nm gate length nanowire transistors [27] with fairly good short channel performance in terms of  $I_{on}/I_{off}$  ratio, SS and DIBL. The reported 10 nm gate length inversion mode nanowire nMOSFET achieved intrinsic gate delay of 0.22 ps, on/off ratio of 52200, SS of 75 mV/dec and DIBL of 80 mV/V. The reported 5 nm gate length  $\Omega$ -gated accumulation mode nanowire pMOSFET achieved intrinsic gate delay of 0.48 ps, on/off ratio of 5 orders, SS of 63 mV/dec and DIBL of 14 mV/V. Those values are much better than those of reported double-gate FinFET [37], planar SOI [38, 39] and conventional bulk transistors [40] with similar gate length. Table 2.1 lists some of the reported nanowire transistor performance.

The second advantage of the nanowire GAA architecture is the higher carrier mobility. Firstly, the acoustic phonon scattering should be suppressed because of the reduced phase space for backscattering in 1-D system[41]. Secondly, the channel is intrinsic; thus, coulomb scattering is minimized. For a conventional bulk transistor, the channel doping level kept increasing to suppress short channel effects as device scales down. However, higher dopant concentration degrades the carrier mobility significantly. Lastly, the surface scattering is suppressed due to volume inversion effect[42], and reduced transverse electric fields due to the increased capacitive coupling of the geometry.

Another advantage of the nanowire architecture is the ultra low power consumption. This advantage enables the nanowire transistor of great potential in mobile electronics as well as bio-applications which require ultra-low power consumption. The leakage of the nanowire transistor is ultra-low, which is possibly due to: (1) the channel leakage is suppressed by the superior gate coupling to the channel; (2) the S/D-channel junction leakage is minimized as a result of the minimized junction area; (3) the gate leakage is reduced due to the mitigation of gate oxide scaling. The ultra-low leakage in the nanowire transistor also partially contributed to its high on/off ratio.

Currently, there are two approaches to fabricate nanowires: bottom-up approach and top-down approach. These two approaches have their advantages and disadvantages and both of them will be discussed in the following two sections.

## 2.2 Nanowires fabricated by bottom-up approach

In bottom-up approach, nanowires are synthesized. There are a number of methods reported that can synthesize nanowires, such as template-directed growth [43-46], laser ablation growth [47-50], catalyst-assisted growth [51-56] and other methods [57]. Among those methods, vapor-liquid-solid (VLS) growth, one of the catalyst-assisted growth mechanisms, is the most well studied and reported methods for semiconductor nanowires synthesis [51-54, 58]. In VLS growth, the nano-scale particles of the catalyst are dispersed on a substrate. Then, the temperature is raised high enough to transform the catalyst nano-particles into liquid clusters. Those liquid catalytic clusters act as the energetically favored sites for localized decomposition of the vapor phase reactants, absorption of vapor phase reactants and crystallization continues, the nanowires are grown from the catalytic clusters. The advantages of this approach are: (1) the size of the synthesized nanowire is determined by the size of the liquid catalytic cluster. The nanowire diameter as

small as 10 nm has been demonstrated with this technique; (2) uniform in-situ doping can be obtained by including the doping gas sources during the wire synthesis, and it can be well controlled to switching from n-type to p-type by simply switching the dopant gas sources. It is reported that Si[60], Ge [55, 57], SiGe and some III-V compounds nanowires[46] can be synthesized by this approach and the nanowire diameter and doping can be well controlled [61].

The bottom up approach has the advantage of low cost, as it does not require the expensive lithography process. However, the biggest challenge of this approach is to integrate those synthesized nanowires into functional ICs in a cost effective and reliable way. Typically, the synthesized nanowires are randomly spread over the wafer and they need complicated techniques to be integrated into device architecture for achieving specific functionalities. Some of the techniques reported for this purpose are 'pick-and-place' with AFM tip [62], liquid suspension[63], electric- or magnetic-field schemes[64-66], and fluid flow[59, 60]. Such processes lack control in repeatability and scalability. Moreover, the throughput is very low, which is a main economical factor for any new technique to be accepted in manufacture industry. These integration issues limit the nanowire fabricated by bottom-up approach from commercial applications.

# 2.3 Nanowires fabricated by top-down approach

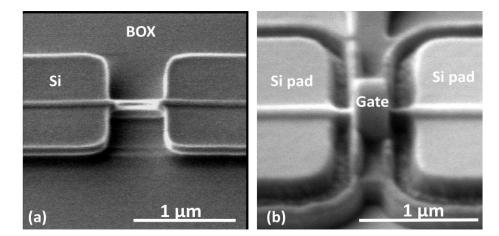

In top-down approach, the pattern is first defined by lithography process and then transferred into the substrate to form fin-like structures, which are then converted into nanowires by trimming down the fins. Si nanowires have been successfully demonstrated with this technique, in which the converting process normally is thermal oxidation followed by wet etch of oxide. The controllability and process window of the Si nanowire oxidation process is reported to be good due to a self-limiting effect, which refers to the phenomenon that the oxidation rate becomes slower and self-limiting as the Si-fin is trimmed down to nanowire size [35, 67-73].

The self-limiting oxidation of Si nanowires is first reported by Liu et al. at 1993[68]. It was reported that, unlike oxidation of planar Si surface where the oxide thickness increases along a parabolic curve, the oxide thickness over a Si column structure is self-limited and the final nanowire diameter was controlled by the oxidation temperature. It was reported that, the nanowire diameters were limited to be 11 and 6 nm after the dry oxidation of 30 nm diameter Si column at 800 and 850 °C separately for a long time [68]. In the following works, Liu et al. reported that the self-limiting phenomenon could be observed only when the oxidation temperature is below 950 °C and the main mechanism of the selflimiting effect was suggested to be attributed to the increase in the activation energy of oxide diffusivity as a result of the large stress in the formed oxide during the oxidation process [69]. In that work, 2-nm-wide Si nanowires with aspect ratio of more than 100 to 1 was achieved[69]. At 2000, Heidemeyer et al. reported the pattern dependent oxidation and the self-limiting effect in the oxidation of Si dots [70]. It was proposed that the oxidation rate decreases with increasing stress perpendicular to the Si surface and self-limiting occurs when the stress is over a critical value[70]. At 2008, Cui et al. suggested that the origin of the self-liming oxidation comes from the change of distribution of diffusion activation energy in the high density region which rises monotonically along with

the oxidation[71]. CMOS compatible process for nanowire fabrication utilizing the self-limiting oxidation has also been reported. Theng et al. explored the selflimiting technique for dual nanowire channels on SOI platform[73]. Although thin Si bridge is observed because the oxidation time is not long enough in Theng's work, the later work reported by Singh et al. successfully demonstrated circular single crystalline Si nanowire with diameter down to 3 nm formed by self-limiting oxidation on SOI wafers [35].

Unlike the bottom-up approach, the top-down approach does not have the integration issue as all the nanowires are printed by the lithography process. Moreover, the top-down fabrication process has the advantages of excellent repeatability, scalability, high throughput and compatible with the conventional CMOS process technology.

### **2.4** Germanium channel for future transistors

As discussed in chapter 1, replacing Si with other semiconductor having higher carrier mobility is another effective way to improve the MOSFET performance. The domination of Si MOSFETs in the ICs market could partially be attributed to the fact that Si has much better native oxide than its counterparts. The Si-SiO<sub>2</sub> system is perfect for MOSFET gate oxide, for its low interface state density, good thermal stability and low leakage current. However, this advantage of Si has gone as SiO<sub>2</sub> has been replaced by high-k gate dielectric, for suppressing gate leakage current while satisfying the EOT requirement. Thus, nowadays, other semiconductor with higher intrinsic carrier mobility, such as Ge, become very attractive to be integrated with high-k gate dielectric for the future advanced transistors.

Table 2.2 lists the intrinsic materials properties of Si, Ge and a few popular III-V compounds. As shown in the table, Ge offers the highest intrinsic hole mobility, ~ 4 times higher than that of Si, and 2.5 times higher electron mobility than that of Si. Several times higher carrier mobility than the Si universal hole mobility has been demonstrated based on high-k/Ge system [6, 7]. Furthermore, a compressively strained Ge pMOSFET is demonstrated to have ten times or higher hole mobility against a Si pMOSFET [74-77]. As the scaling of the Si MOSFET approaches its physical limits, high-k/Ge system has received more and more attentions as an alternative way of improving the MOSFET performance [78]. Therefore, the Ge channel MOSFET is generally regarded as one of the most promising channel materials for high speed applications.

Table 2.2: Intrinsic material properties of Si, Ge and a few popular III-V compounds.

|                                     | Si   | Ge   | GaAs | InP  | InAs  | InSb  |

|-------------------------------------|------|------|------|------|-------|-------|

| Electron mob. (cm <sup>2</sup> /Vs) | 1600 | 3900 | 9200 | 5400 | 40000 | 77000 |

|                                     |      |      |      |      |       |       |

| Hole mob. (cm <sup>2</sup> /Vs)     | 430  | 1900 | 400  | 200  | 500   | 850   |

| Band gap (eV)                       | 1.12 | 0.66 | 1.42 | 1.34 | 0.36  | 0.17  |

| Permittivity                        | 11.9 | 16   | 12   | 12.6 | 14.8  | 17    |

| Melt Point (°C)                     | 1415 | 937  | 1238 | 1059 | 941   | 525   |

## **2.5** Challenges of the Ge channel transistor

Although Ge has great potential of higher performance, there are several challenges associated with the fabrication of Ge MOSFETs.

#### 2.5.1 Gate dielectric

The first and biggest challenge of fabricating Ge MOSFETs is the lacking of high quality gate stacks. Unlike Si, native Ge oxides (GeO and GeO<sub>2</sub>) are water soluble and thermodynamically unstable[79]. This has been a bottleneck in introducing Ge channels into CMOS technology. Thermally grown native oxide of Ge is found to be primarily  $\text{GeO}_2$  with small amounts of  $\text{GeO}_x$  (x < 2)[79]. GeO2 is water soluble, which not only leads to reliability concern but also makes the fabrication process challenge most of the cleaning processes have water. Furthermore, this  $Ge/GeO_x$  system is reported to have high interface state density  $(D_{it})$  [80] which leads to lower mobility. GeO<sub>x</sub>N<sub>y</sub> has better thermal and chemical stability than native Ge oxides and it was once explored as a gate dielectric candidate. Shang *et. al.* reported ~ 40% enhancement in hole field effect mobility over the silicon universal curve [81] with this  $GeO_xN_y$  gate dielectric. Chui *et al.* studied the scalability of GeO<sub>x</sub>N<sub>y</sub> on Ge and reported CET down to 1.9 nm [82]. However, none of those works demonstrated GeO<sub>x</sub>N<sub>y</sub> as a suitable candidate for the future ultra-scaled MOSFET due to the high leakage based on experimental results. Probably the contribution of these studies is to use GeO<sub>x</sub>N<sub>y</sub> as a surface passivation layer in high-k/Ge system. Introducing nitrogen at the interface by annealing Ge in NH<sub>3</sub> ambient at 500-600 °C was first reported by Bai et al. [83] as an effective way to suppress gate leakage. The film grown by this technique is found containing oxygen as well and its chemical composition is  $GeO_xN_y$ . However, the interface trap density of  $GeO_xN_y/Ge$  system is not sufficient low for high performance transistor application. Those traps reduce the mobility gains of replacing Si with Ge and lead to a large hysteresis in the MOS device.

To obtain high quality high-k/Ge interface, several other pre-gate surface passivation techniques have been investigated, such as  $PH_3$  gas treatment[84],  $AIN_x$  passivation[84], sulfur passivation[85, 86], Si passivation [87, 88] and GeO<sub>2</sub> passivation[6, 89-91]. These surface passivation techniques can either reduce the interface state density or suppress the Ge out-diffusion into high-k dielectrics.

Recently, GeO<sub>2</sub> as an interfacial passivation layer has attracted a renewed attention. Takahashi et al. reported that GeO<sub>2</sub> decomposition is the root of high interface state density at the GeO<sub>2</sub>/Ge interface and low interface trap density of thermally grown Ge oxide could be obtained once the decomposition of GeO<sub>2</sub> are suppressed [91]. Later, Xie et al. reported that high quality gate stack with D<sub>it</sub> as low as  $2 \times 10^{11}$  cm<sup>-2</sup>\*eV<sup>-1</sup> could be achieved by incorporating fluorine passivation in GeO<sub>2</sub>/Ge system, and reported hole mobility as high as three times of the Si universal hole mobility based on this system [6, 89, 90]. However, further reliability studies are needed for this approach.

The most popular and intensive studied approach is Si passivation [87, 92-95]. Wu et al., report that annealing Ge in SiH<sub>4</sub> right before HfO<sub>2</sub> deposition could suppress gate leakage and achieve ~ 140 % higher hole mobility [94]. Later, Bai et al. reported Si passivation achieved low  $D_{it}$  of 7 × 10<sup>10</sup> cm<sup>-2</sup>\*eV<sup>-1</sup> and low gate leakage simultaneously [95]. The Si passivation layer works in such a way that it is consumed to form an interfacial layer before the underneath Ge reacts with  $HfO_2$ . There are two advantages of this approach: (1) the formation of unstable  $GeO_2$  could be minimized; (2) the dangling bonds between Si and Ge could be minimized, as the lattice mismatch between them is small enough to be handled by the ultra-thin Si layer. Hence, it could be expected to have the improved MOSFET performance. De Jaeger et al. reported that that the Si thickness must be controlled within a few monolayers to obtain a high quality, defect free Ge-HfO<sub>2</sub> interfacial layer on the planar substrate [93].

#### 2.5.2 Junction leakage

The smaller bandgap of Ge compared with Si has been a concern because of its influence on band-to-band tunneling which leads to junction leakage. The reported junction leakage of  $n^+/p$  and  $p^+/n$  Ge diodes formed by boron and phosphorus implantation can be reduced to  $10^{-4}$  A/cm<sup>2</sup> with annealing, which is considered acceptable for device operation[5]. However, it is still necessary to optimize the implantation and activation process to achieve this optimum result.

#### **2.5.3 Process integration**

Although Ge process is CMOS technology compatible, process integration issues should be taken care. For instance, the widely used chemical cleaning solution for Si such as piranha and SC1 cannot be used for Ge cleaning process. Process temperature is another issue. As shown in table 2.2, the melting temperature of Ge is 937 °C. The melting temperature of nano-scale structure is reported to be lower than that of bulk material[96]. Thus, process temperature of Ge device needs to be taken care, especially for Ge nanowires investigated in this project. Normally, the process temperature is kept to be below 600 °C for safety.

# 2.6 Summary