# INVESTIGATIONS INTO DESIGN AND CONTROL OF POWER ELECTRONIC SYSTEMS FOR FUTURE MICROPROCESSOR POWER SUPPLIES

**Ravinder Pal Singh**

NATIONAL UNIVERSITY OF SINGAPORE 2010

# INVESTIGATIONS INTO DESIGN AND CONTROL OF POWER ELECTRONIC SYSTEMS FOR FUTURE MICROPROCESSOR POWER SUPPLIES

Ravinder Pal Singh

(B.Tech(Hons), IIT Kharagpur, India)

A THESIS SUBMITTED

#### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

$\boldsymbol{2010}$

### Acknowledgements

This thesis arose in part out of years of research that has been done since I came to the Power Electronics group at National University of Singapore (NUS). By that time, I have worked with a great number of people who deserve special mention. They have contributed in assorted ways to the research and helped making of this thesis possible. It is a pleasure to convey my gratitude to all of them in my humble acknowledgment.

First and foremost, I offer my sincerest gratitude to my supervisor, Assoc. Prof. Ashwin M. Khambadkone, who has supported me throughout my thesis with his patience and knowledge, whilst allowing me the room to work in my own way. His truly scientist intuition has made him a constant oasis of ideas, which exceptionally inspired and enriched my growth as a student and as a researcher. One simply could not wish for a better or friendlier supervisor. I am indebted to him more than he knows.

I would also like to thank my co-supervisors Assoc. Prof. Ganesh S. Samudra and Assoc. Prof. Yung C. Liang. They have been extremely enthusiastic and supportive regarding this research. Without their encouragement and support this study would have not been possible.

In my daily work I have been blessed with a friendly and cheerful group of fellow students: (in alphabetical order) Amit K. Gupta, Anshuman Tripathi, Chen Yu, K. Viswanathan, Kong Xin, Krishna Mainali, Sanjib Kr. Sahoo, Xu Xinyu and Zhou Haihua. It was really wonderful working with them in the laboratory and helping each other. I have learnt a lot through our miscellaneous chats. Thank you all for being my friends.

Our lab officers Mr Woo, Mr Chandra, Mr Teo and Mr Seow have been a great help. I appreciate their helpful nature and dedication in making laboratory such a nice place to work.

There are some people outside the power electronics laboratory whose presence has made my stay at NUS really easy. I am also grateful to the members of (my) Tennis Club. Our regular tennis sessions have helped me pull out from stressed conditions. I have to also thank my apartment mates: Khattu, Debu, Sree and Saurabh for their continued support and friendship.

My study at National University of Singapore was made possible through the academic research grant for this project (R-263-000-305-112) and the graduate research scholarship. I am extremely thankful to National University of Singapore for the financial support.

And finally, no words suffice to express my heartfelt gratitude to those who are closest to me. I would have never reached so far without the constant love and support of my parents and my sister. I would also like to thank my wife Navdeep whose presence helped make the completion of my work possible. Thankyou Navdeep for supporting me to work on the thesis during the weekends. Although it took me little longer than expected, but now I have made it. Mom and Dad, this dissertation is for you!

# Contents

|               | Ack   | knowledgements                               | i    |

|---------------|-------|----------------------------------------------|------|

|               | Sun   | nmary v                                      | viii |

| $\mathbf{Li}$ | st of | Tables                                       | xi   |

| $\mathbf{Li}$ | st of | Figures                                      | xii  |

| 1             | Intr  | roduction                                    | 1    |

| <b>2</b>      | Bac   | ekground and Problem Definition              | 8    |

|               | 2.1   | Digital Control of Voltage Regulator Modules | 8    |

|               |       | 2.1.1 Digital Control of DC-DC Converters    | 10   |

|               |       | 2.1.2 Digital Control of high current VRMs   | 12   |

|               | 2.2   | Time Resolution of DPWM                      | 15   |

|               | 2.3   | Current Sensing Techniques                   | 21   |

|     | 2.3.1   | Series resistance                          | 22 |

|-----|---------|--------------------------------------------|----|

|     | 2.3.2   | Inductor Voltage Sensing                   | 24 |

|     | 2.3.3   | MOSFET $R_{ds,ON}$ Sensing                 | 25 |

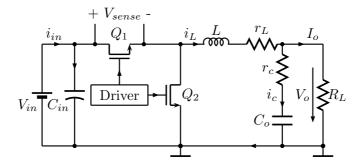

|     | 2.3.4   | SenseFET                                   | 26 |

|     | 2.3.5   | Current Transformers (CT)                  | 27 |

|     | 2.3.6   | Rogowski Coil                              | 28 |

|     | 2.3.7   | Hall Effect Sensor                         | 28 |

| 2.4 | Currei  | nt Sharing in Paralleled Converters        | 29 |

| 2.5 | Impro   | ving the Transient Response of a Converter | 35 |

| 2.6 | Summ    | ary                                        | 40 |

| Dig | ital Co | ontrol of VRMs                             | 42 |

| 3.1 | Introd  | uction                                     | 42 |

|     | 3.1.1   | Controller Design Methods                  | 43 |

|     | 3.1.2   | Frequency Domain Design                    | 44 |

|     | 3.1.3   | Control Structure                          | 47 |

|     | 3.1.4   | Transformation to discrete-time controller | 48 |

|     | 3.1.5   | Current and Voltage Sensing                | 51 |

|     | 3.1.6   | Controller Implementation                  | 53 |

3

|   |     | 3.1.7 Stability Analysis                                          | 57 |

|---|-----|-------------------------------------------------------------------|----|

|   |     | 3.1.8 Digital Dither                                              | 59 |

|   | 3.2 | Experimental Results                                              | 61 |

|   | 3.3 | Summary                                                           | 64 |

| 4 | Tim | e Resolution of the DPWM                                          | 66 |

|   | 4.1 | Introduction                                                      | 66 |

|   | 4.2 | Proposed Scheme                                                   | 67 |

|   |     | 4.2.1 Extending the scheme for finer resolution                   | 70 |

|   |     | 4.2.2 Effect due to variation in component values                 | 71 |

|   | 4.3 | Simulation Results                                                | 73 |

|   | 4.4 | Experimental Results                                              | 75 |

|   | 4.5 | Summary                                                           | 79 |

| 5 |     | nt Magneto Resistive (GMR) effect based Current Sensing<br>hnique | 80 |

|   | 5.1 | Introduction                                                      | 80 |

|   | 5.2 | Proposed Method                                                   | 81 |

|   |     | 5.2.1 Description                                                 | 81 |

|   |     | 5.2.2 Work on Magnetoresistive effect                             | 84 |

|   |     | 5.2.3 Magnetic Field distribution due to current carrying track 86                                                                                |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 5.2.4 Performance Evaluation                                                                                                                      |

|   | 5.3 | Experimental Results                                                                                                                              |

|   | 5.4 | Summary                                                                                                                                           |

| 6 | Cur | ent Sharing in Multiphase Converters 102                                                                                                          |

|   | 6.1 | Introduction $\ldots$                                            |

|   | 6.2 | Proposed Scheme                                                                                                                                   |

|   |     | $5.2.1  \text{Current Sensing} \dots \dots$ |

|   |     | 5.2.2 Power Loss Analysis                                                                                                                         |

|   |     | 5.2.3 Current Sharing                                                                                                                             |

|   |     | 5.2.4 Stability Analysis                                                                                                                          |

|   |     | 5.2.5 Accuracy in current sharing                                                                                                                 |

|   | 6.3 | Experimental Results                                                                                                                              |

|   | 6.4 | Summary                                                                                                                                           |

| 7 | Imp | oving the Step-Down Transient Response 122                                                                                                        |

|   | 7.1 | Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $122$                                               |

|   | 7.2 | Proposed Scheme: Working Principle                                                                                                                |

|   |     | 7.2.1 Switching Algorithm                                                                                                                         |

|   |     | 7.2.2 Output Capacitor Design              |

|---|-----|--------------------------------------------|

|   |     | 7.2.3 Slew rate determines the fall time   |

|   |     | 7.2.4 Power Loss Analysis                  |

|   |     | 7.2.5 Implementation of Proposed Scheme    |

|   | 7.3 | Experimental Results                       |

|   | 7.4 | Summary                                    |

| 8 | Imp | proving the Step-Up Transient Response 150 |

|   | 8.1 | Introduction                               |

|   | 0.1 |                                            |

|   | 8.2 | Proposed Scheme                            |

|   |     | 8.2.1 Working Principle                    |

|   |     | 8.2.2 Switched Capacitor Circuit Design    |

|   |     | 8.2.3 Slew rate determines the rise time   |

|   |     | 8.2.4 Power Loss Analysis                  |

|   |     | 8.2.5 Implementation of Proposed Scheme    |

|   | 8.3 | Experimental Results                       |

|   | 8.4 | Summary                                    |

| 9 | Cor | nclusions 180                              |

| Appendix A           | 186 |

|----------------------|-----|

| Bibliography         | 189 |

| List of Publications | 203 |

viii

### Summary

Voltage Regulator Modules (VRMs) are used to provide power to the microprocessors. These modules are expected to deliver high currents upto 200A at low output voltages of around 1.2V. In order to reduce losses, microprocessors use dynamic voltage scaling, whereby the supply voltage to the microprocessor is adjusted with the computation load. To this end, the processor sends a 7-bit Voltage Identification (VID) code to the VRM, that dictates its output voltage.

Since the digital interface to the microprocessor is available to the VRM, the digital control is well suited for this purpose. However, the digital controllers have the drawbacks of reduction in phase margin due to presence of Zero Order Hold (ZOH) in Digital Pulse-Width Modulators (DPWM) and the limited resolution of the DPWM output. The digital controllers designed in this work take into account the reduction in phase margin due to presence of DPWM based ZOH. The effect of quantization of filter coefficients is also analyzed and a minimum word length filter structure is proposed for such controllers. In addition, a DPWM architecture is proposed to improve the time resolution of the DPWM. The proposed scheme is fabricated in the form of an Application Specific Integrated Circuit (ASIC) and is verified using experimental results.

The VRM control requires the inductor currents to be sensed. Thus, a current sensing method is described which is based on Giant Magneto Resistive (GMR)

effect. It is based on sensing the magnetic field generated by the flow of current. Using fundamental equations of the field distribution, it is shown how the sensor can be used for sensing the inductor current. Simulation and test results are provided to assist the analysis.

Due to high currents, it becomes essential to have multiphase topology, where the synchronous buck converters are connected in parallel such that each phase leg carries only a fraction of the total output current. However, the current control of such a topology will require N-current sensors. Thus, a sensing and sharing algorithm is proposed which uses only one current sensor.

The control of a VRM ensures the voltage regulation during steady state operation. However, the transient response of a DC-DC converter still gets governed by the fundamental equation of rate of change of inductor current. It is proportional to the voltage across the inductor and inversely proportional to the inductance. Two new circuit topologies are proposed which increases the slew rate of inductor current during transient and thus improve the transient response of the system. The performance of these topologies are verified with simulation and experimental results. These schemes give another design freedom to optimally design the converters, resulting in lower inductor current ripple and requiring smaller output capacitor as compared to the conventional schemes.

In all, this dissertation focuses on the design development and control of Voltage Regulator Modules for low voltage and high current applications. Theoretical developments have been appropriately supported with analytical and experimental results.

# List of Tables

| 3.1 | Parameters of the interleaved buck converter prototype                          | 65  |

|-----|---------------------------------------------------------------------------------|-----|

| 8.1 | Slew rate comparison for different levels of input voltages in a buck converter | 154 |

# List of Figures

| 1.1 | Intel CPU transistors double every 18 months (source:[2])                                                                                                                                                                                                       | 1  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Historical power trend for Intel CPUs (source:[3])                                                                                                                                                                                                              | 2  |

| 2.1 | Block schematic of (a) Analog PWM controller and (b) Digital PWM controller.                                                                                                                                                                                    | 10 |

| 2.2 | Experimental results for observing the resolution of output voltage.<br>Case (i): Single Edge, 100MHz clock; Case (ii) Dual Edge, 100MHz clock; Case (iii) Dual Edge, 200MHz clock.                                                                             | 20 |

| 2.3 | Compensation network to remove the effect of parasitic inductance.                                                                                                                                                                                              | 23 |

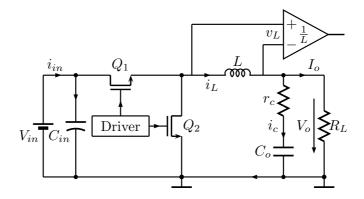

| 2.4 | Inductor voltage sensing for obtaining the inductor current                                                                                                                                                                                                     | 25 |

| 2.5 | Current sensing based on MOSFET $R_{ds,ON}$                                                                                                                                                                                                                     | 26 |

| 2.6 | Current Sensing using SenseFET method.                                                                                                                                                                                                                          | 27 |

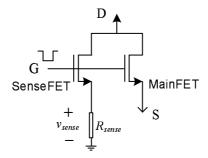

| 2.7 | Various current sharing schemes: (a) Current Mode control (b) Sin-<br>gle wire current sharing scheme (c) Paralleled converters connected<br>with Oring-connection (d) Current Sharing controller used in O-ring<br>architecture (e) An automatic master scheme | 32 |

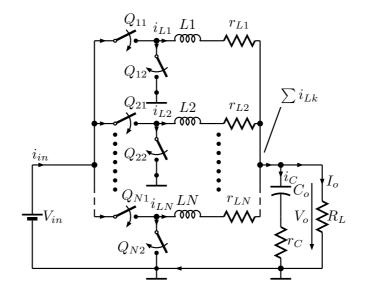

| 3.1 | N-phase interleaved buck converter                                                                                                                                                                                                                              | 44 |

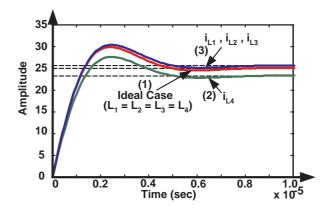

| 3.2 | Step response of the inductor current transfer functions with param-<br>eter mismatch                                                                                                                                                                           | 46 |

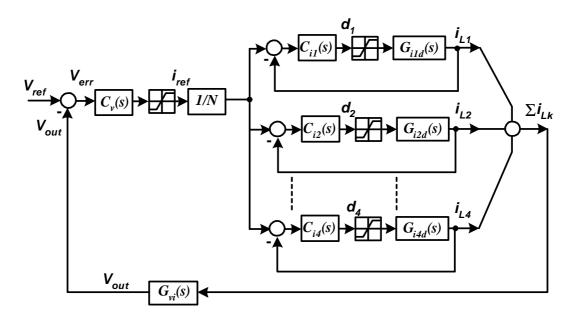

| 3.3 | Cascaded control loop for 4-phase interleaved VRM                                                                                                                                                                                                               | 48 |

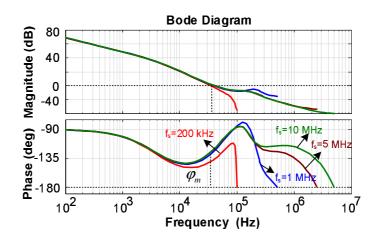

| 3.4 | Bode plot of the system at various sampling rates                                                                                                                                                                                                               | 49 |

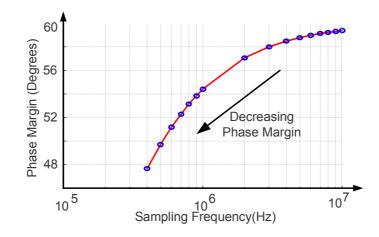

| 3.5  | Effect of sampling frequency on phase margin of the compensated systems                                                                                                                                                                                               | 50 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

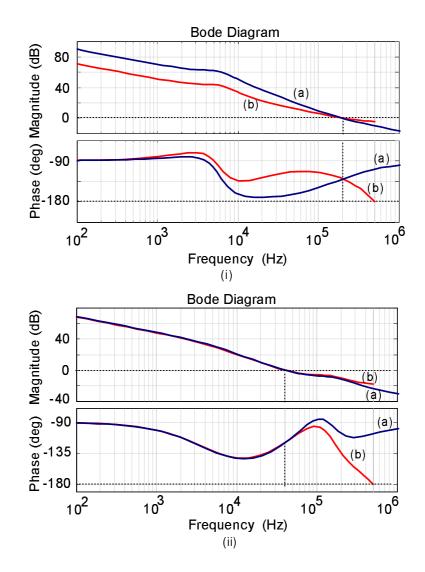

| 3.6  | Bode plots of the system obtained by different methods. (i) Inner Current Loop (ii) Voltage Loop with inner current loop closed. Curves: (a) Continuous time system, (b) Digital control system                                                                       | 51 |

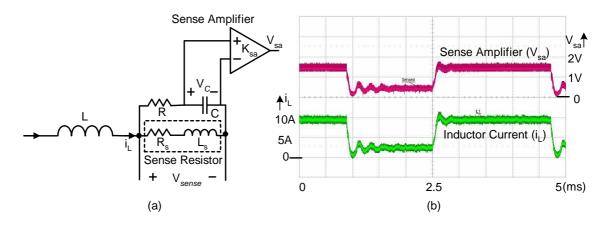

| 3.7  | (a) Filtering the voltage across the sense resistor to eliminate the effects of parasitic inductance and (b) Output of the sense amplifier and the inductor current as measured using current probe                                                                   | 52 |

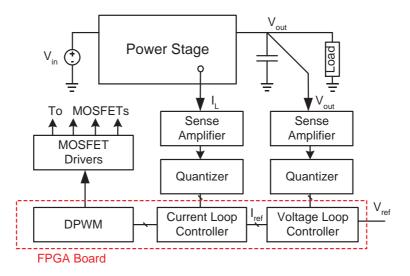

| 3.8  | Schematic of digital controller design using FPGA                                                                                                                                                                                                                     | 53 |

| 3.9  | Effect of truncation on the filter coefficients in current controller                                                                                                                                                                                                 | 55 |

| 3.10 | Direct Form : Filter realization                                                                                                                                                                                                                                      | 56 |

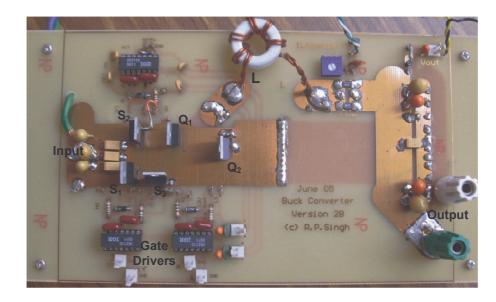

| 3.11 | Photograph of the prototype of a 4-phase interleaved converter de-<br>veloped in the lab                                                                                                                                                                              | 59 |

| 3.12 | (a) Switching waveform patterns to realize 1-bit dither; (b) Switching waveform patterns to realize 2-bit dither                                                                                                                                                      | 60 |

| 3.13 | Switching waveform patterns to realize 3-bit dither                                                                                                                                                                                                                   | 61 |

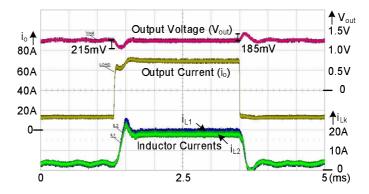

| 3.14 | Result showing the dynamic response of digitally controlled 4-phase interleaved converter for a step load variation from 15A to 70A                                                                                                                                   | 62 |

| 3.15 | Result showing the dynamic performance of the controller with a<br>daptive voltage positioning for a step load change from 15A to<br>$80\mathrm{A}_{}$ .                                                                                                              | 64 |

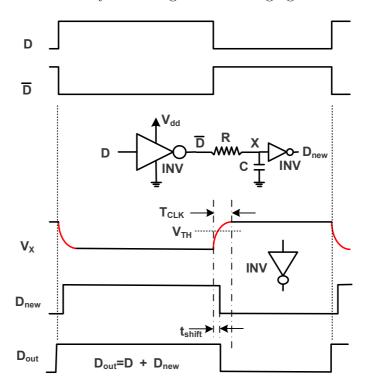

| 4.1  | Schematic of the scheme for delaying the edges of the gate pulses .                                                                                                                                                                                                   | 68 |

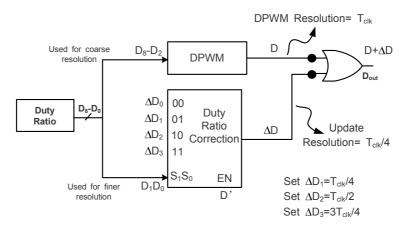

| 4.2  | Block schematic of the proposed scheme. The duty ratio is updated based on the least significant bits                                                                                                                                                                 | 69 |

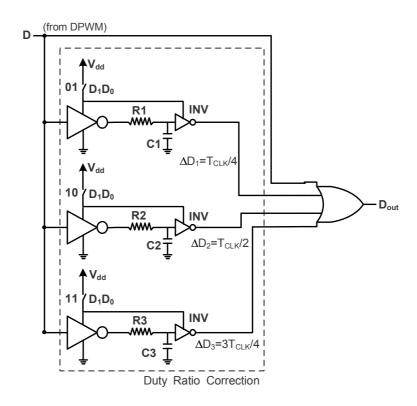

| 4.3  | Detailed schematic of the proposed scheme. The duty ratio is up-<br>dated based on the least significant bits                                                                                                                                                         | 72 |

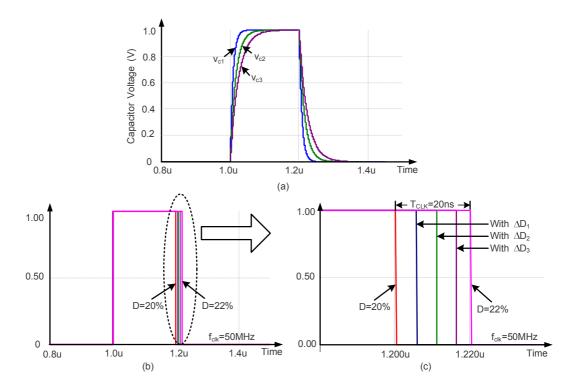

| 4.4  | Simulation results showing the performance of the proposed scheme.<br>(a) Resulting voltage waveforms at capacitors C1, C2 and C3; (b)<br>The PWM pulses obtained using the proposed scheme and (c) The<br>4 possible duty ratios generated using the proposed scheme | 73 |

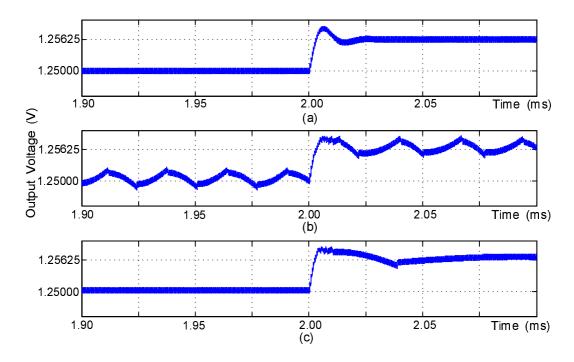

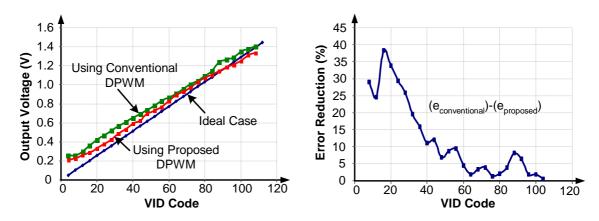

| 4.5  | Simulation results showing the performance of three different control methods: (a) Analog control; (b)Conventional Digital Control and (c) Proposed Controller with duty ratio correction                                                                                                               | 74 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

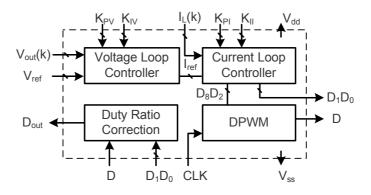

| 4.6  | Block schematic of the chip architecture                                                                                                                                                                                                                                                                | 75 |

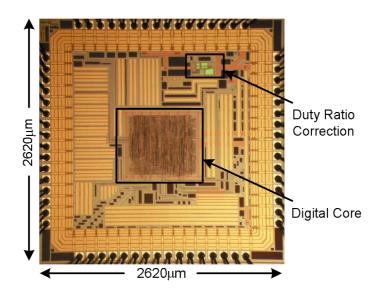

| 4.7  | Micrograph of the fabricated ASIC, named DigResv1 $\ .\ .\ .$ .                                                                                                                                                                                                                                         | 75 |

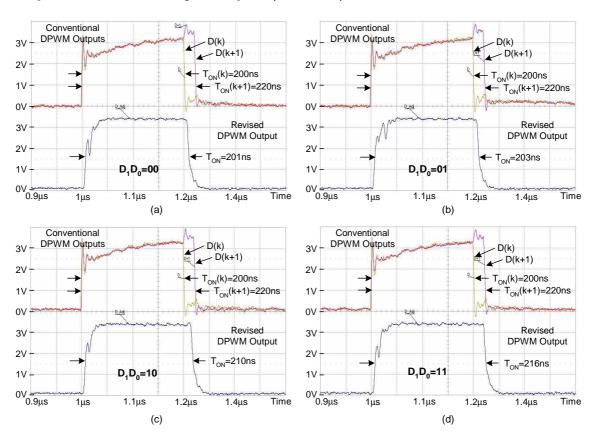

| 4.8  | Experimental results showing the variation of duty ratio in accor-<br>dance with duty-ratio correction command $(D_1D_2)$                                                                                                                                                                               | 76 |

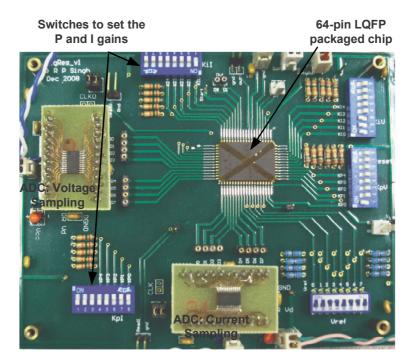

| 4.9  | Experimental prototype of the controller realized using the fabri-<br>cated ASIC and the off-chip ADCs                                                                                                                                                                                                  | 77 |

| 4.10 | Experimental results the output voltage regulation for proposed case and conventional case.                                                                                                                                                                                                             | 78 |

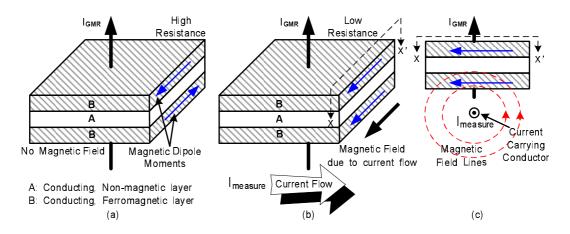

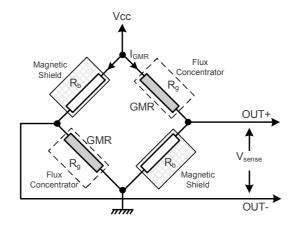

| 5.1  | Working principle of Giant Magneto Resistive Effect. (a) Higher re-<br>sistance due to anti-parallel magnetic moments, (b) Paralleled mag-<br>netic moments reduces the electrical resistance and (c) Cross sec-<br>tion along XX' plane showing alignment of magnetic moments due<br>to magnetic field | 83 |

| 5.2  | Wheatstone Bridge configuration available for sensing application                                                                                                                                                                                                                                       | 84 |

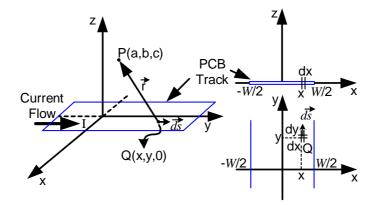

| 5.3  | Magnetic field at point P due to a long current carrying PCB track.                                                                                                                                                                                                                                     | 87 |

| 5.4  | (a) Magnetic Field Distribution as obtained from MATLAB (b)<br>Magnetic Field Distribution as obtained from QuickField                                                                                                                                                                                  | 90 |

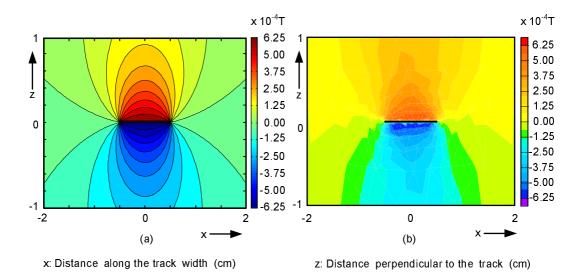

| 5.5  | (a) Current detection using GMR magnetic field sensor whose axis of sensitivity is in the horizontal direction; (b) Input Output Characteristics of sensor at a supply voltage of 20 V and (c) Linearity of output voltage with varying supply voltage.                                                 | 92 |

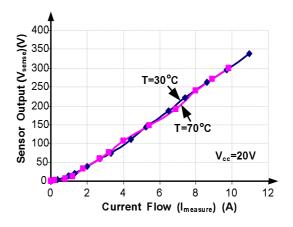

| 5.6  | Input-Output characteristics at two different temperatures $(T = 30^{\circ}C \text{ and } T = 70^{\circ}C) \dots \dots$                                                                           | 92 |

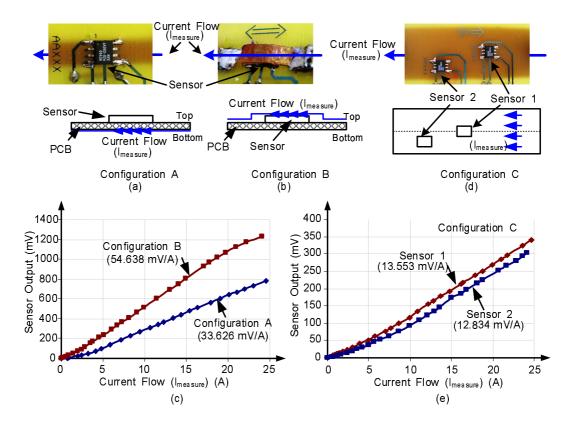

| 5.7  | (a) Current flow through the bottom layer; (b) Current flow through<br>a conductor placed on top on sensor; (c) Output voltage as obtained<br>from configurations A and B; (d) Placement of sensors on a wider<br>track; and (e) Input Output characteristics as obtained from config-<br>uration C     | 93 |

|      | uration C                                                                                                                                                                                                                                                                                               | 30 |

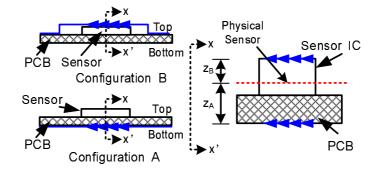

| 5.8  | Determining the location of physical sensor in the Sensor chip                                                                                                                                                                                                                                                                                                                                                                        | 94  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

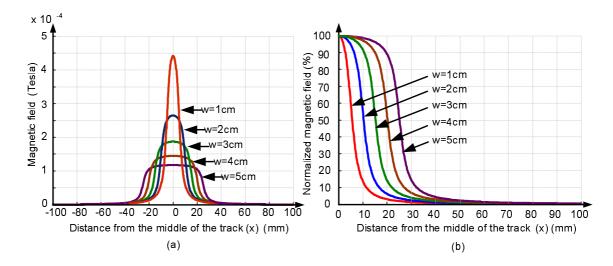

| 5.9  | Curves showing magnetic field distribution for varying track widths carrying a current of 10 A.                                                                                                                                                                                                                                                                                                                                       | 96  |

| 5.10 | Curves showing the location of points where magnetic field reduces<br>to 90% in configuration A. Region (1) has magnetic field > 90% of<br>$B_{max}$ and region (2) has magnetic field < 10% of $B_{max}$                                                                                                                                                                                                                             | 98  |

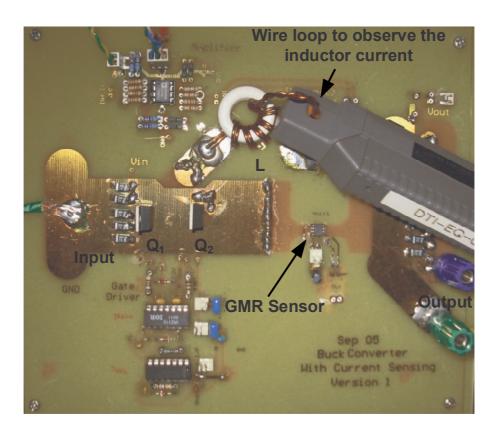

| 5.11 | Experimental prototype of a buck converter which uses a GMR sensor for current sensing. A current probe is also used to observe the inductor current.                                                                                                                                                                                                                                                                                 | 99  |

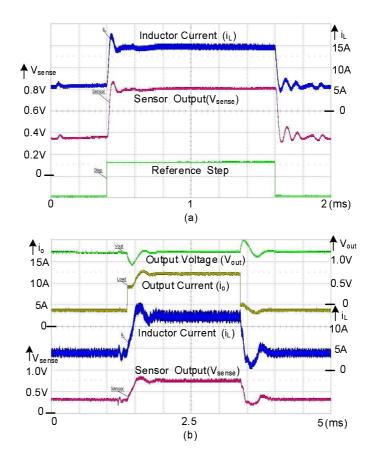

| 5.12 | (a) Result showing the dynamic response of digitally controlled buck converter for a step change in current reference; (b) Output voltage with a step change in load current from 3A to 12A.                                                                                                                                                                                                                                          | 100 |

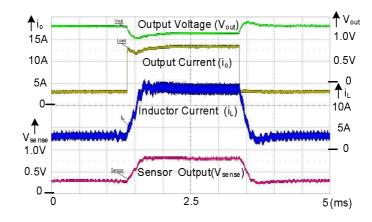

| 5.13 | Result showing the dynamic performance of the controller with adap-<br>tive voltage positioning for a step load change                                                                                                                                                                                                                                                                                                                | 101 |

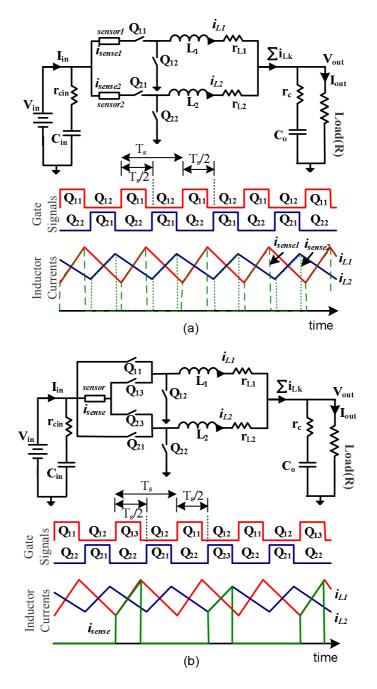

| 6.1  | Current Sensing in a 2-phase interleaved buck converter                                                                                                                                                                                                                                                                                                                                                                               | 105 |

| 6.2  | Current sensing in a 2-phase system using single sensor $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                    | 107 |

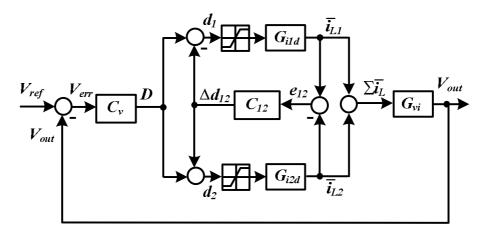

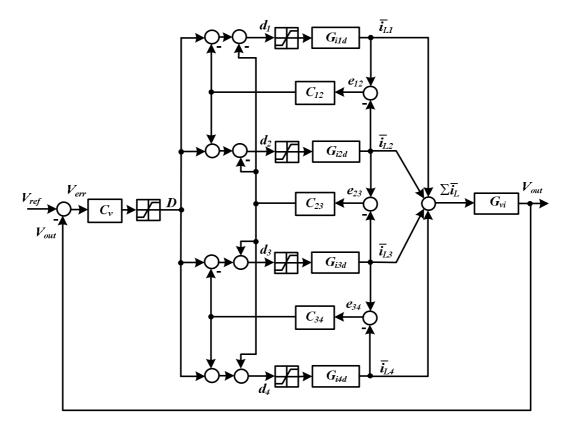

| 6.3  | Two phase control architecture with duty ratio compensation for current sharing                                                                                                                                                                                                                                                                                                                                                       | 109 |

| 6.4  | The proposed control architecture as applied to a 4-phase interleaved converter                                                                                                                                                                                                                                                                                                                                                       | 110 |

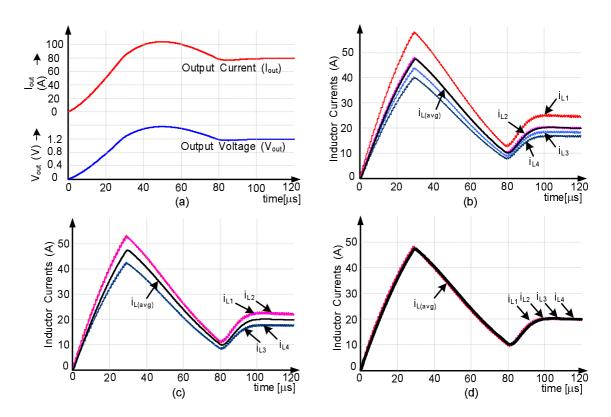

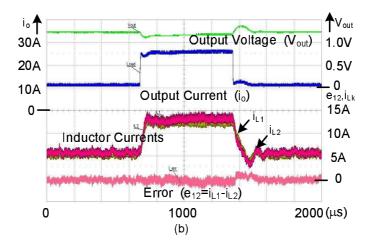

| 6.5  | Simulation results showing the performance of the scheme during startup transient (a) Output voltage and output current, (b) Distribution of load current among individual phases, (c) Mismatch between $i_{L1}$ , $i_{L2}$ and $i_{L3}$ , $i_{L4}$ and (d) Balanced inductor currents using proposed scheme $\ldots \ldots \ldots$ | 111 |

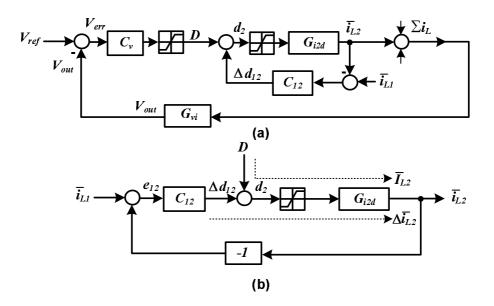

| 6.6  | (a) Simplified control architecture based on duty ratio compensa-<br>tion for achieving current sharing (b) Constant duty ratio D being<br>updated based on current mismatch                                                                                                                                                                                                                                                          | 113 |

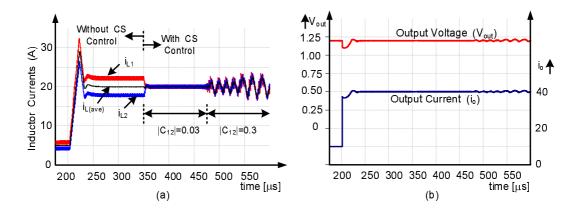

| 6.7  | Simulation results showing the effect of increasing the gain of the current sharing controller                                                                                                                                                                                                                                                                                                                                        | 115 |

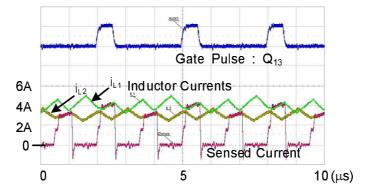

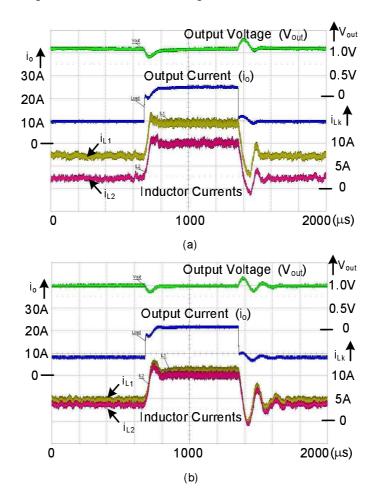

| 6.8  | Experimental results showing the output voltage and distribution of inductor currents during load transients (a) Current controller is disabled (b) Result showing the dynamic performance of the controller when current controller is enabled | 117 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

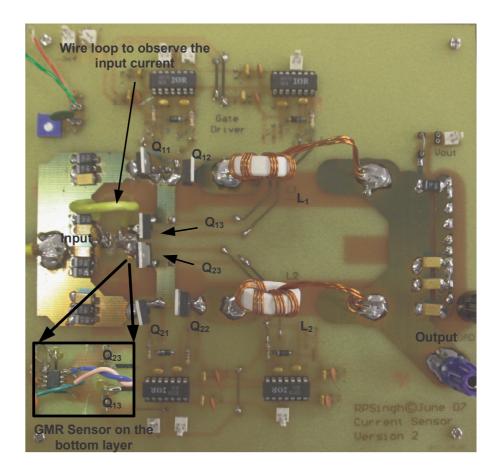

| 6.9  | Experimental prototype of the two phase converter used to demon-<br>strate the proposed current sensing scheme.                                                                                                                                 | 118 |

| 6.10 | Experimental results showing the dynamic performance of the controller with adaptive voltage positioning for a step load change                                                                                                                 | 120 |

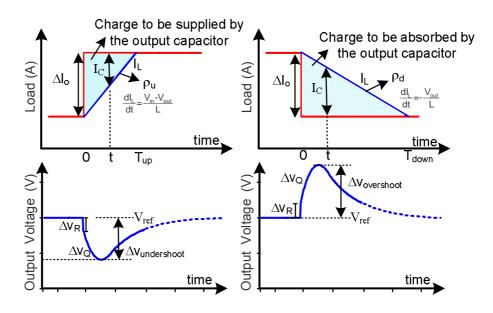

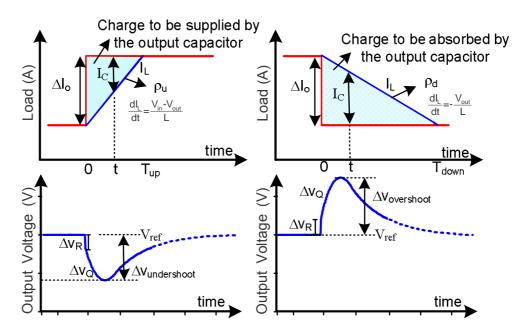

| 7.1  | Charging and discharging of the output capacitor during sudden change in load current                                                                                                                                                           | 123 |

| 7.2  | Region showing the comparison of voltage overshoot and undershoot<br>for load transients of different magnitudes                                                                                                                                | 126 |

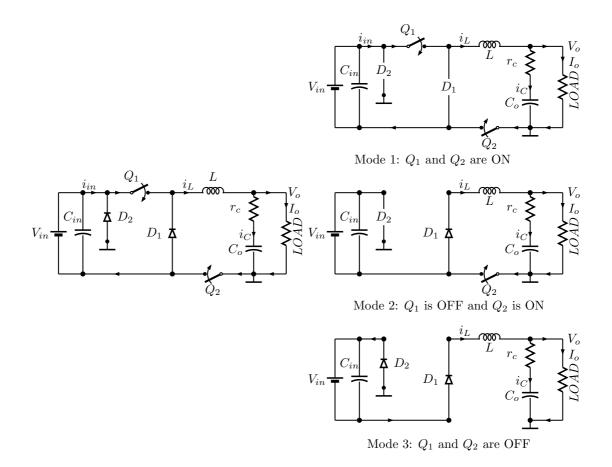

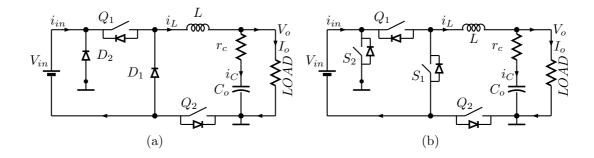

| 7.3  | (a) The proposed converter for improving the step-down load transients. (b) Equivalent circuit during its three modes of operation.                                                                                                             | 130 |

| 7.4  | Difference in the slew rates - required and available                                                                                                                                                                                           | 132 |

| 7.5  | Simulation result showing the performance of the proposed scheme<br>during a step change in current reference. (a) Conventional Scheme<br>(b) Proposed scheme using the same converter parameters as the<br>conventional scheme                 | 134 |

| 7.6  | Typical waveforms during step change in the load. The input voltage is switched after time $t_1$                                                                                                                                                | 136 |

| 7.7  | Simulation result showing the performance of the proposed scheme<br>during a step change in load current. (a) Conventional Scheme (b)<br>Proposed scheme using the same converter parameters as the con-<br>ventional scheme                    | 139 |

| 7.8  | Reducing the fall time by increasing the slew rate of the inductor current                                                                                                                                                                      | 141 |

| 7.9  | (a) The proposed scheme using diodes. (b) The diodes are replaced by synchronous rectifiers                                                                                                                                                     | 142 |

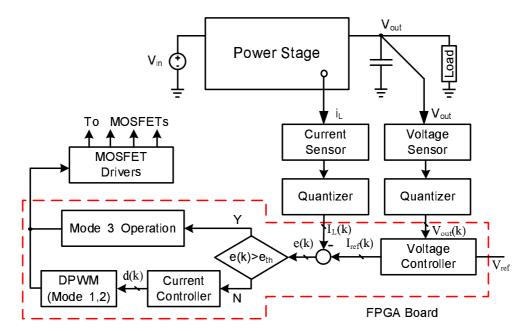

| 7.10 | Schematic of digital controller design using FPGA                                                                                                                                                                                               | 143 |

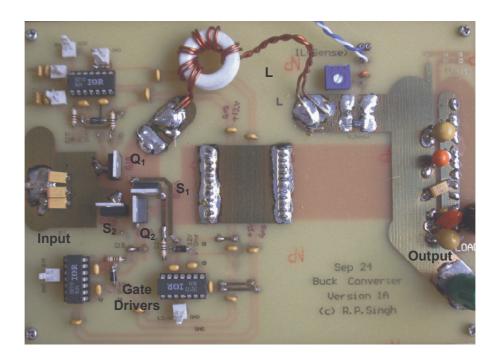

| 7.11 | Experimental prototype of the buck converter used to demonstrate the proposed scheme                                                                                                                                                                                  | 145 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

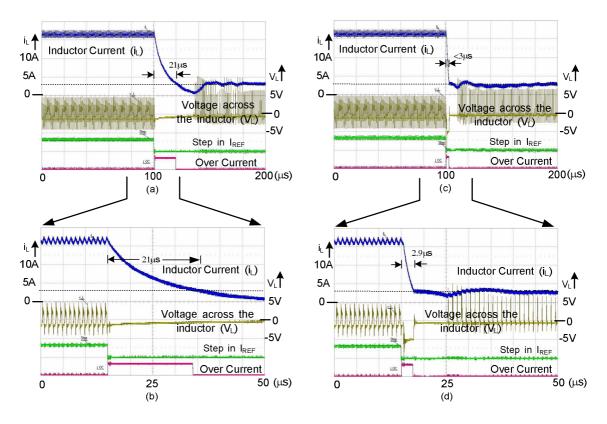

| 7.12 | Experimental result showing the performance of the system with<br>a step change in reference current. (a),(b) Conventional converter<br>(c),(d) Proposed buck converter                                                                                               | 146 |

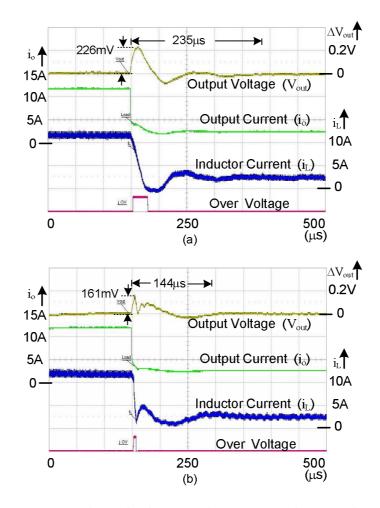

| 7.13 | Experimental result showing the output voltage and inductor current<br>during load transients in a buck converter with cascaded control<br>loops (a) Response of the Conventional buck converter (b) Response<br>of the proposed buck converter                       | 148 |

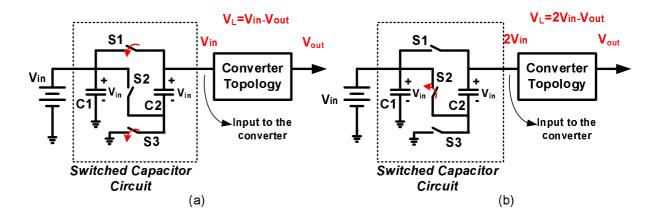

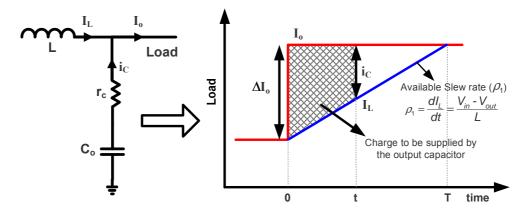

| 8.1  | Working principle of the proposed scheme. The voltage across the inductor is changed by altering the input voltage                                                                                                                                                    | 152 |

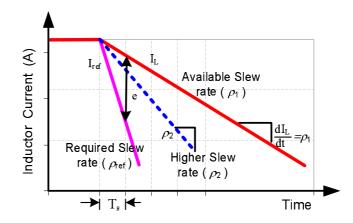

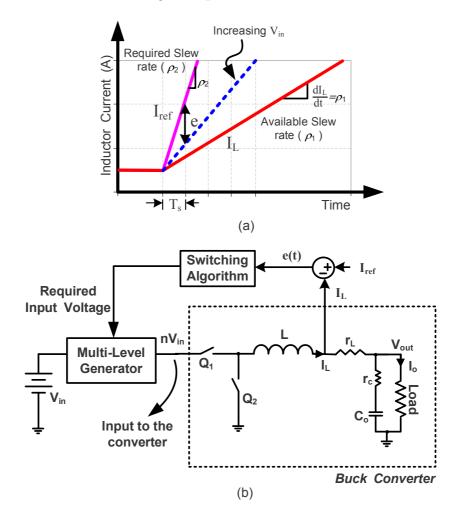

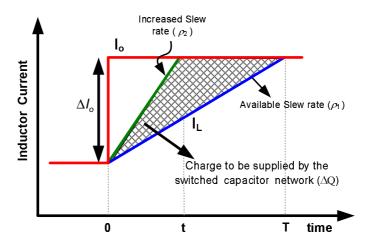

| 8.2  | Difference in the slew rates - required and available. The slew rate is increased by increasing the input voltage.                                                                                                                                                    | 157 |

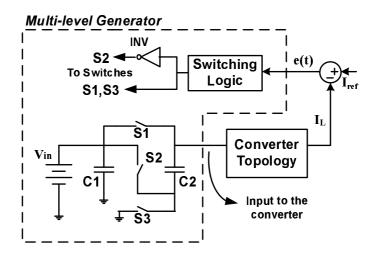

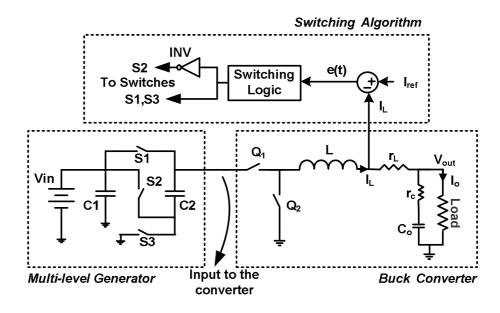

| 8.3  | Multi-level generator applied to a power converter                                                                                                                                                                                                                    | 159 |

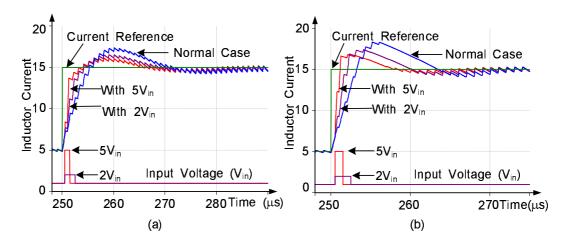

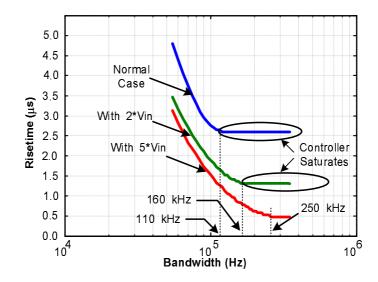

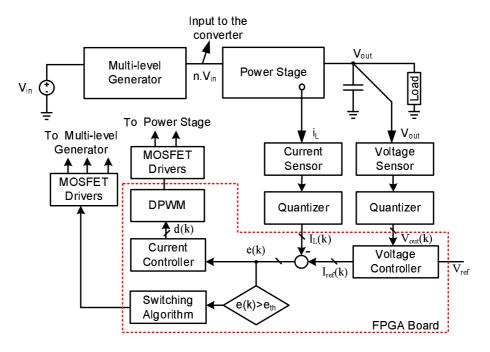

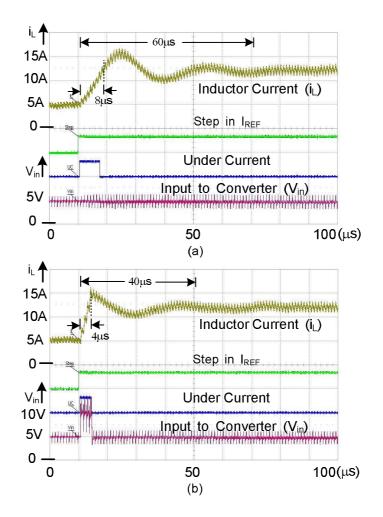

| 8.4  | Simulation result showing the performance of the proposed scheme during a step change in current reference. (a) Closed loop bandwidth of 50kHz (b) Closed loop bandwidth of 100kHz                                                                                    | 160 |

| 8.5  | Discharging of output capacitor during sudden load change                                                                                                                                                                                                             | 161 |

| 8.6  | Typical waveforms during step change in the load. The input voltage is switched after time $t_1$                                                                                                                                                                      | 162 |

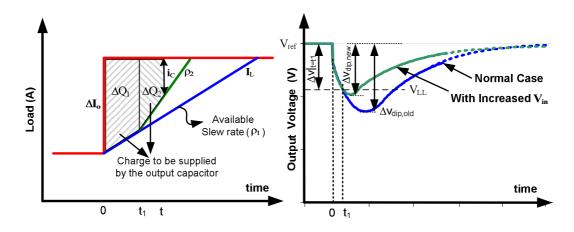

| 8.7  | Simulation result showing the performance of the proposed scheme during a step change in the load current. (i) Normal case where input voltage is kept constant, (ii) Converter having 2 levels of input voltage and (iii) Converter having 5 levels of input voltage | 166 |

| 8.8  | Charge supplied by the switched capacitor network to increase the slew rate of inductor current.                                                                                                                                                                      | 167 |

| 8.9  | Reducing the rise time by increasing the slew rate of the inductor current                                                                                                                                                                                            | 170 |

| 8.10 | Block schematic of the proposed scheme showing a buck converter<br>and a switched capacitor network at its input                                                                                                                                                      | 171 |

| 8.11 | Block schematic of the proposed scheme                                                                                                                                                                                                                                | 174 |

xvii

| 8.12 | Experimental prototype of the buck converter used to demonstrate the proposed scheme.                                                                                                                                                                    | 175 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

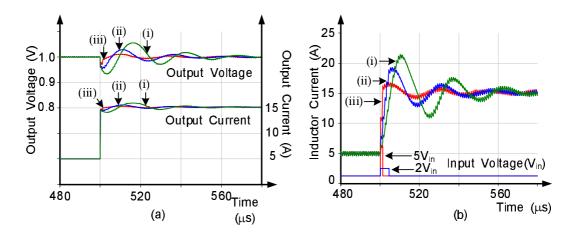

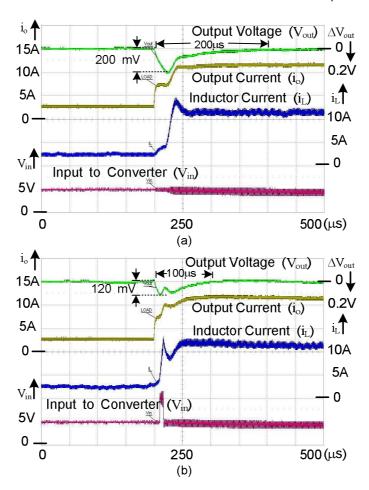

| 8.13 | Experimental result showing the performance of the system with a step change in reference current. (a) Conventional converter with input voltage constant (b) Converter with switched input voltage .                                                    | 176 |

| 8.14 | Experimental result showing the output voltage and inductor current<br>during load transients in a buck converter with cascaded V+I control<br>loops (a) Conventional converter with input voltage constant (b)<br>Converter with switched input voltage | 177 |

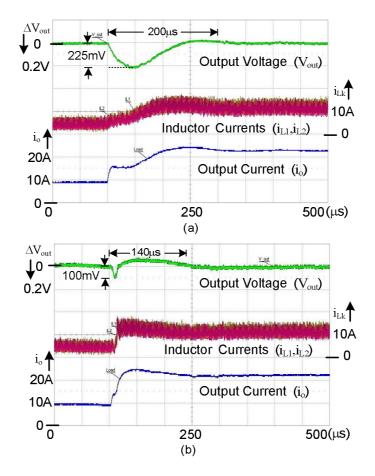

| 8.15 | Experimental result showing the output voltage and inductor current<br>during load transients in a buck converter with cascaded V+I control<br>loops (a) Conventional converter with input voltage constant (b)<br>Converter with switched input voltage | 178 |

| A.1  | Charging and discharging of the output capacitor during sudden change in load current                                                                                                                                                                    | 186 |

### List of Symbols

- $V_{in}$  Input voltage (V)

- $V_{out}$  Output voltage (V)

- $V_{ref}$  Reference voltage (V)

- $I_o$  Output current (A)

- $\Delta I_o$  Change in output current (A)

- $I_L$  Inductor current (A)

- $\Delta I_L$  Inductor current ripple (A)

- $v_{ref}$  Reference voltage for AVP (V)

- $i_o$  Instantaneous output current (A)

- $R_{droop}$  Droop resistance for AVP ( $\Omega$ )

- L Circuit inductance (H)

- $L_k$  Inductance of phase  $k(\mathbf{H})$

- $r_L$  dc resistance of inductor  $(\Omega)$

- $C_o$  Output capacitance (F)

- $r_c$  Equivalent resistance of output capacitor ( $\Omega$ )

- $C_{in}$  Input Capacitance (F)

- $r_{cin}$  Equivalent resistance of input capacitor ( $\Omega$ )

- $f_s$  Switching frequency (Hz)

- $T_s$  Switching period (s)

- $f_{CLK}$  Clock Frequency (Hz)

- $T_{CLK}$  Time period of the clock (Hz)

- $N_{ADC}$  ADC Resolution (bits)

- $N_{DPWM}$  DPWM Resolution (bits)

- $\rho_u$  Slew rate of inductor current during step-up transient (A/s)

- $\rho_d$  Slew rate of inductor current during step-down transient (A/s)

- $\rho_1$  Available slew rate of inductor current (A/s)

- $\rho_2$  Revised slew rate of inductor current (A/s)

### Chapter 1

### Introduction

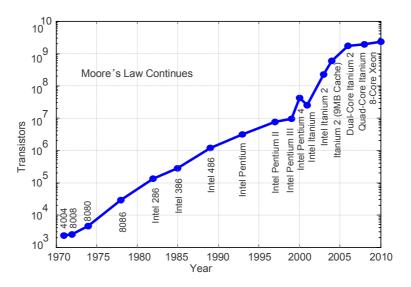

Microprocessor scaling has consistently adhered to Moores law [1], thereby doubling the transistors every 18 months, as seen in Fig. 1.1 [2]. Increasing transistor density combined with the performance demanded from next-generation microprocessors result in increased processor power. Scaling of transistors also necessitates a reduction in the operating voltages both for reliability of the finer-dimension devices and for reducing the power consumed by the microprocessor.

Figure 1.1: Intel CPU transistors double every 18 months (source:[2])

The power loss is  $P_L \propto N \cdot C \cdot (V_{dd})^2 \cdot f_{clk}$  where, N is the number of cells,  $V_{dd}$  is the supply voltage,  $f_{clk}$  is the clock frequency and C is the capacitive loading of a single CMOS cell. Since the number of CMOS cells per die area is growing as predicted by the Moore's law, the net result is increased power consumption of the future microprocessors. Historical data on the increase in power for Intel microprocessors is included in Fig. 1.2 [3][4]. It is seen that the power doubles approximately every 36 months. This is attributed to simple analytical relation based on increasing clock frequency, transistor count and less aggressive voltage reduction. However, since the power consumption of the chip is large, any reduction in voltage will increase the supply current drawn by the microprocessors.

Figure 1.2: Historical power trend for Intel CPUs (source:[3])

According to Intel's prediction, one can expect the power consumption of around 200W. The supply voltage will drop to below 1V and the supply current will be around 200A [4]. The output voltage tolerance is required to be less than 1% even in the presence of high slew rates of current drawn by the microprocessors. These tight required regulations, place an enormous burden on the circuits that provides power to the chip. These circuits are collectively referred to as Voltage Regulator Modules (VRMs). Normally the VRMs supplying power to the microprocessors derive power from a 12V regulated bus [5][6]. For low voltage low current VRMs, a synchronous buck converter has been found to be suitable for such conversion. However if a single stage buck converter is used in 12V to 1V, 200A VRM, then due to the stringent voltage regulation requirements and due to the large slew rates of the current, large output filter will be required. Due to limited space on motherboards, such size of VRMs would not be feasible [7].

To meet the requirements of limited space on motherboard and the tight regulations, the power conversion must be done at higher switching frequencies. This will reduce the size of the required components and it will provide a fast transient response. The amount of required output filter size can also be reduced using an interleaving multiphase topology. With multiphase topology, the synchronous buck converters are connected in parallel, such that each phase leg carries only a fraction of the total output current. By operating the various converters in a phase-shifted manner, such a topology can offer decreased magnitude of output voltage ripple. It also helps in increasing the frequency of the voltage ripple. Thus, the size of filter components can be reduced to a greater extent.

In an interleaved buck converter topology, it is important to share the currents equally among various phases. However, due to variation in the inductor values, differences of components, connections and layout results in unequal current distribution among phases. This causes uneven distribution of losses and reduces the overall efficiency. Thus, appropriate current sharing mechanism is required to distribute the current evenly among the phases.

In order to maintain good current sharing among the phases a current sensor needs to be added in a DC-DC converter. For a paralleled converter system, sensor needs to be added for each converter. The performance of any such design will depend on the performance of the current sensing technique. The output of current sensor should be linear in the operating range of VRMs and should have high bandwidth so as to sense the currents during load transients with high slew rate. Apart from the high output currents, the VRMs are expected to maintain tight voltage regulation even in the presence of such large load current transients.

This thesis focuses on the design development and control of Voltage Regulator Modules for low voltage and high current applications. All the above issues related to the VRM design have been considered. Followings are the major contributions of this work.

- The first important contribution is the development of digital controllers for interleaved buck converters. Problem of variations in inductor values among different phases has been brought out and a method to overcome them has been discussed. Such digital controllers can be implemented with simple Field Programmable Gate Array (FPGA) development kits for quick prototyping.

- Such implementation uses a Digital Pulse Width Modulator (DPWM) to control the duty ratio of the gate pulses. However, the time resolution of these pulses gets limited by the operating clock frequency of the FPGA board.

Thus, a scheme is presented which improves the time resolution as compared to the conventional architecture. The proposed scheme is fabricated in  $0.35 \mu m$  Austria Micro-Systems (AMS) process and is verified with experimental results.

- The third contribution is an isolated current sensor which works on the magnetic field developed by the current to be measured. Comprehensive analysis to evaluate the feasibility of such a current sensor has been carried out. Experimental results are presented to verify the working principle of such a sensor, when applied to high current applications.

- In an interleaved buck converter, a current sensor is normally employed for each phase so as to achieve current sharing among individual phases. Detailed analytical study has been done to establish the feasibility of a scheme which can reduce the number of sensors in such a system. Thus, a scheme is presented which uses a single current sensor to sense various currents and is independent of number of phases. The performance of such a scheme is verified with experimental results.

- In a buck converter, the slew rate of inductor current gets limited by the circuit parameters. The slew rate can be increased either by increasing the voltage across the inductor or by reducing the inductance. However, reduction of inductance will result in higher losses and on the other hand, the voltage across the inductor is limited by the input and output voltage. Another significant contribution is the development of circuit topology which increases

the slew rate of inductor current during dynamics. The performance of such a topology is verified with simulation and experimental results.

• Analytical verifications are presented to show that the step down load transient is more critical in a buck converter with low conversion ratio. Hence, a new topology is developed which improves the step-down load transients in such low voltage buck converters.

Altogether, this dissertation attempts to solve the above mentioned issues. There are 9 chapters in this dissertation, each with a specific focus. The organization of the thesis is as follows.

- The next chapter will give a literature survey of various solutions aimed to address the above mentioned issues. The performance of these methods has been critically analyzed. This will help to bring out the focus of the present work and also recognize the problems.

- Starting from the basic concepts, the need for a fast digital controller is discussed in chapter three. It gives the design development of such a controller which can be easily implemented on an FPGA platform.

- The fourth chapter discusses the limited time resolution of the gate pulses. It presents a hybrid digital PWM architecture which helps to improve the time resolution of such pulses.

- The fifth chapter evaluates various sensors which are used for current sensing. Identifying the need for a current sensor which is suitable for given low voltage

and high current applications, a current sensing method is proposed.

- In an N-paralleled converter N current sensors are required. The sixth chapter discusses the current sharing scheme which uses single sensor to sense the inductor current in a multiphase converter.

- Two new circuit topologies which improves the step-up and step-down load transients have been covered in chapter seven and chapter eight respectively.

- Finally, chapter nine concludes this thesis highlighting the major contributions of this research.

#### Chapter 2

# Background and Problem Definition

#### 2.1 Digital Control of Voltage Regulator Modules

Advances in processor technology have posed stringent requirements on the voltage regulator module (VRM) design. Due to stringent regulation requirements, the design of next generation VRMs need a thorough understanding of the performance and design trade-offs. The supply voltage of the microprocessor will drop to below 1 V and the supply current will be around 200 A [4]. For microprocessor loads, high slew rates of VRM output current are expected. In addition, the VRM output voltage regulation is required to be less than  $\pm 1\%$ .

In order to reduce losses, microprocessors use dynamic voltage scaling, whereby the supply voltage of the microprocessor is adjusted with the computational load [8]. To this end, the processor sends a 7-bit Voltage Identification (VID) code to the VRM, that dictates its output voltage. Depending on the VID code, the output voltage level changes by 6.25mV step every  $5\mu s$  [6].

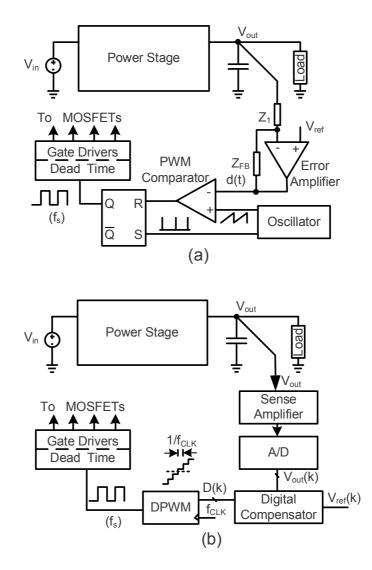

Usually the analog control methods have been proposed for VRMs [7], [9], [10], [11]. Fig. 2.1(a) shows a typical analog voltage-mode control method. In this implementation, the digital VID code has to be converted to its equivalent analog signal  $V_{ref}$ . An error amplifier processes the output voltage error  $(V_{ref} - V_{out})$  and realizes a compensator for the desired control action. It requires proper selection of passive components for realizing the desired compensators. However, component variations and aging effect are also commonly seen in analog control design which affects the system performance. Moreover, the presence of noise in the system makes it difficult to achieve a resolution of 6.25mV.

Since the reference voltage is available to the VRM as a digital code, it can be easily incorporated into the digital controllers. Recently, the digital controllers have gained attention due to their low quiescent power, immunity to analog component variations, ease of implementing advanced controller architecture and other advantages. Moreover, developments in Field Programmable Gate Arrays (FPGA) makes it a useful platform to design and validate the digital controllers. The controllers may then be fabricated to result in a digital controller integrated circuit (IC). However, the disadvantages of digital control include finite word length effects and sampling time delay due to presence of Zero order Hold (ZOH).

Although digital control is suited for VRM due to the digital interface to the

Figure 2.1: Block schematic of (a) Analog PWM controller and (b) Digital PWM controller.

microprocessor and the other generic advantages of digital control, it is a challenge to deliver the performance required of the next generation VRMs [4].

#### 2.1.1 Digital Control of DC-DC Converters

A comparison of various digital control design approaches for DC-DC converters have been presented in [12] and [13]. A digital proportional + integral + derivative (PID) controller for DC-DC applications presented in [14], uses a lookup table. The lookup table maps the controller behavior to various values of the digitized error signal. Since the size of the lookup table depends on the range of the error signal and the desired regulation of the output voltage, this is scheme only suitable for small range of operating conditions.

For hand-held devices, DC-DC converter power supplies have to operate very efficiently to prolong battery life. To this end, [15] uses a load dependent operation that alternates between two discrete switching frequencies for the same output voltage. It achieves high efficiency by operating the converters in discontinuous conduction mode at light loads.

As opposed to analog control methods, digital control adds quantization noise. High resolution is required to minimize quantization noise. To this end, a high resolution Analog to Digital Converter (ADC) is required. Moreover, a high speed of conversion is necessary to achieve high control bandwidth. Such ADCs need large floor space in digital ICs. To overcome the problem of large floor space, [16] proposes a delay line ADC. However, due to process and temperature variations, the delay cannot be defined precisely. Hence, it requires calibration of ADC.

Increasing the resolution of ADC creates another problem. It has been shown [17] that, if the resolution of ADC is greater than the resolution of the Digital Pulse-Width-Modulator (DPWM) counter and there is no integral control action, a limit cycle oscillation occurs. Therefore, it has been recommended that the resolution of DPWM be at least 1 bit higher than that of ADC. However, for a given clock frequency, increasing the DPWM resolution results in a lower switching frequency. To meet, the high switching frequency demand along with high resolution of DPWM, few methods have been proposed. For example, a digital PWM using a ring-oscillator-multiplexer scheme is implemented in [18]. On the other hand, a dither signal is used to increase the effective DPWM resolution while using a low resolution of the PWM counter [17].

#### 2.1.2 Digital Control of high current VRMs

Most digital control schemes for VRMs, proposed so far, are voltage-mode control. However, there are few examples of current mode control such as [19] and [20]. Current control facilitates current sharing in interleaved converters, which is a popular topology for VRMs.

A low complexity digital peak current control is presented in [20]. However, it results in variable switching frequency operation. The scheme uses low resolution digital-to-analog converters (DACs) to generate a droop compensated current and voltage reference signal. These are compared with the actual signals with help of an analog comparators. Though the scheme achieves a high current operation with a fast current control, its resolution is dictated by the DACs.

On the other hand an average current mode or voltage mode control, uses

the average value of the sampled state variable, respectively.

In order to achieve high bandwidth, over-sampling is used. In over-sampling, sufficient number of samples of the state variable are taken within a switching period. The average value of the state variable is then computed over the switching period. This average value is used to compute the duty ratio for the next switching period [21]. This introduces a ZOH behvaior in the system.

On the other hand, multi-sampling can be used to reduce the effect of ZOH in DPWM. In multi-sampling, multiple samples are taken within the switching period. Hence, the value of the state variable that is compared with the DPWM ramp is not equal to the sampled and held value at the start of the switching period. However, this method can introduce high frequency ripple due to the aliasing error in the sampled variable. To overcome this error, a repetitive filter is proposed [22] that eliminates the aliasing effect and thus achieves a control bandwidth that is similar to that of analog control.

A predictive current control [19] is proposed for VRMs. The scheme requires the converter parameter like inductor value (L) to formulate the control law. However, such scheme will require a disturbance observer to compensate for the unmodeled dynamics. An appropriate gain has to be calculated for the disturbance observer. Insufficient gain reduces the response time of the system while high gain causes limit cycle. Moreover, for current sharing, precise value of each phase inductor is required. Previously reported models of interleaved converters assume all the inductors to be the same, in which case, the problem is reduced to having N synchronous buck converters in parallel. In practice, it is very difficult to have same value for all inductors. There can be  $\pm 5 - 10\%$  variation in the inductor values, resulting in asymmetry in the phases. This results in uneven distribution of inductor current among individual phases. Thus, appropriate current sharing mechanism is required to distribute the current evenly among the phases. A current mode control is used to solve this problem which takes into account the variations among inductance values.

Thus, a digital control scheme with individual phase current loops is used to achieve current sharing during dynamics and steady state operation. In a typical digital control system, the duty ratio command is the fed to the Digital Pulse-Width-Modulator (DPWM) to produce the gate signals for the converter. Due to the nature of DPWM, such digital control systems are characterized by the presence of the Zero-Order-Hold (ZOH). Therefore the performance of these systems is a function of DPWM switching period. Thus, appropriate digital controllers need to be designed taking into account the performance degradation due to presence of DPWM based ZOH. Moreover, the performance also depends on quantization error, round-off and truncation errors. The effect of quantization of filter coefficients need to be analyzed and a minimum word length filter structure should be obtained.

## 2.2 Time Resolution of DPWM

Most digital control schemes use DPWM to obtain the gate pulses. However, the performance of such systems get limited due to the finite resolution of the DPWM pulses.

A typical block schematic for implementing a digital control is shown in Fig. 2.1(b). The control algorithm takes the digitized error signal  $(V_{ref}(k) - V_{out}(k))$  and computes the discrete set of duty-cycle command D(k). The duty ratio word is processed by DPWM which generates the gate pulses at the desired switching frequency  $(f_s)$ .

To implement this, a counter based DPWM is commonly used which provides high linearity and is simple to design. However, the minimum time resolution of such a DPWM is equal to the time period of its clock. This puts stringent requirement on clock frequency if fine resolution of duty ratio is required, for example, in a VRM type application.

It has been shown in [10] and [23] that it is advantageous to obtain the VRM output from a 5V bus. Thus, for our analysis the input voltage has been chosen as  $V_{in} = 5V$ . For obtaining  $\Delta V_{out} = 6.25mV$  with  $V_{in} = 5V$ , we need a resolution of

$$\Delta D = \frac{\Delta V_{out}}{V_{in}} = 0.00125 \tag{2.1}$$

If the switching frequency is  $f_s = 1MHz$ , this corresponds to a time resolution of  $\Delta t = 1.25ns$ . For obtaining such time resolution, the counter based DPWM has

to be operated at 800MHz!

In general, for achieving N-bit resolution of the DPWM block, it needs to be clocked at  $2^{N}.f_{s}$ , where  $f_{s}$  is the switching frequency of the converter. For example, an 8-bit DPWM generating switching frequency of  $f_{s} = 1MHz$  will require a clock frequency of  $f_{CLK} = 256MHz$  and so on. To meet, the high switching frequency demand along with high resolution of DPWM, various methods have been proposed in the past. Some of these methods are described below.

It has been established that if the resolution of the DPWM counter is smaller than the resolution of ADC and there is no integral control action, a limit cycle oscillation occurs [17]. Therefore, it has been recommended that the resolution of DPWM be at least 1-bit higher than that of ADC. Thus, a dither signal is used to increase the effective DPWM resolution while using a lower-resolution DPWM counter. Introducing dither increases the overall resolution of the DPWM but it results in sub-harmonic oscillations. For M-bit increase in effective DPWM resolution, it will result in sub-harmonic oscillation at  $f_s/2^M$ , where  $f_s$  is the switching frequency of the converter. Moreover, a limit on the maximum possible increase in effective resolution is established in [17].

In order to increase the resolution of DPWM, a ring-oscillator-multiplexer based DPWM scheme is proposed [18]. The time-resolution of the output depends on the delay introduced by the cells in the ring-oscillator. However, for N-bit resolution this will require  $2^N$  stage oscillator and a  $2^N$ -to-1 multiplexer to select the appropriate signal from the ring oscillator. Such an implementation of the DPWM module requires large silicon area, which increases exponentially with the number of resolution bits (N). Moreover, high-frequency operation of such an oscillator results in power loss. In order to reduce power, tapped delay line structure has been proposed [24], [25]. The tapped delay line operates at the switching frequency, thus reducing the power significantly. However, this scheme also requires  $2^N$  stage delay line and a  $2^N$ -to-1 multiplexer to select the appropriate signal from the delay line, which results in large silicon area.

In order to reduce the silicon area, segmented delay line has been proposed [25]. In such a scheme, the delay line is segmented into groups of smaller delay lines. The desired signal can be selected by using smaller multiplexer. In order to increase the resolution, such segments need to be cascaded and an appropriate multiplexer is used. Another variation of segmented delay line scheme is segmented binary weighted delay line based DPWM [26]. In such a scheme, the delay cells are designed to provide binary weighted delays. Although the number of delay cells is reduced, but the size of individual delay cells will vary as to provide the desired delay. The larger delay is generated by simply replicating the basic delay cells, resulting in the same overall number of delay cells.

Silicon area resulting from delay cells can be reduced by using a hybrid approach [16], [27]. It resolves the high-resolution duty ratio word into two groups: coarse duty-ratio command comprising of the most-significant bits and fine dutyratio command comprising of the lower-significant bits. While the coarse duty ratio is obtained using counter based DPWM, the fine duty ratio is obtained using standard delay-line structure. This can reduce the number of delay cells required, however, the area and power are still dictated by the effective increase in the DPWM resolution.

Similarly, [28] resolves the duty-ratio word into decimal part and integral part and two pulses are obtained using these parts. The decimal pulse slowly precharges the input capacitor of the driver IC through a series resistance. Based on the initial voltage at the capacitor, the delay-time of the gate pulse can be changed and hence the resolution of the duty-ratio. Since the scheme is based on the pre-charging the input capacitor, it requires the decimal pulse to be ahead of the integer part pulse. Furthermore, the decimal pulse should not be such that it results in a voltage greater than the threshold voltage. Thus, the operation of this scheme gets limited to a narrow range.

The above methods use a constant switching frequency and on-time is varied to adjust the duty-ratio. Alternately, a constant on-time modulation has been proposed in [29]. It uses counter based DPWM structure, which increases the switching period by  $T_{CLK}$  so as to reduce the duty ratio. The drawback of such a scheme is that for different values of duty cycle, the switching frequency is different. If the clock frequency is not large enough, this may result in significant variation in switching frequency.

With the advent of FPGA technology, it is also possible to increase the clock

frequency. Delay-locked loops (DLL) are commonly present on FPGA for obtaining the phase shifted clocks. Using these DLLs, it is possible to multiply or divide the clock frequency. The multiple of clock frequency is used to obtain the finer duty ratio pulses [30]. However, an increase in clock frequency by 4 will only result in a 2-bit increase in effective resolution of DPWM. Since the modern FPGAs can provide a maximum of  $4f_{CLK}$ , the scheme results in a limited improvement.

In order to overcome the limitations of the DLL method, Digital Clock Manager (DCM) circuit has been employed [31]. DCM is present on modern high-end FPGA boards and is essentially a delay locked loop along with the digital frequency synthesizer and a phase shifter [32], [33]. It can provide phase shifted versions of the input clock - 0 deg, 90 deg, 180 deg and 270 deg along with the multiples of input frequency  $2f_{CLK}$  and  $4f_{CLK}$ . Using one DCM, a 2-bit increase in effective resolution of DPWM can be achieved. Such DCM circuits need to be cascaded for increasing the resolution further. In cascaded DCM structure, the subsequent DCM stage is operated at twice the clock frequency of its preceding DCM stage. In comparison, both the DLL scheme [30] and DCM architechture [31] benefit from the FPGA on board resources to implement the delay line. The latter relies on the phase of the input clock while the former relies on the multiple of the system clock.

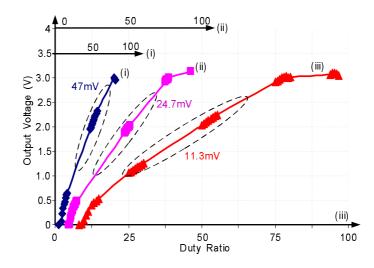

In addition to increasing the system clock frequency, both the edges of the clock can also be exploited. In order to implement this, a counter based DPWM is used and the converter is operated in open-loop. Clock frequency of 100MHz and 200MHz is used and both the edges are used to increment the counter. As seen

Figure 2.2: Experimental results for observing the resolution of output voltage. Case (i): Single Edge, 100MHz clock; Case (ii) Dual Edge, 100MHz clock; Case (iii) Dual Edge, 200MHz clock.

from Fig. 2.2, increasing the clock frequency can improve the duty ratio resolution and hence the output voltage variation. Using (2.1) we have

$$\Delta V_{out} = \Delta D \cdot V_{in} \tag{2.2}$$

For 100MHz clock, we have  $\Delta D = 0.01$  or  $\Delta D = 0.005$  for single edge and dual edge scheme respectively. Thus, for an input voltage of  $V_{in} = 5V$ , this results in  $\Delta V_{out} = 50 \, mV$  and  $\Delta V_{out} = 25 \, mV$ . Similarly, using both the edges of 200MHz clock,  $\Delta V_{out} = 12.5mV$  can be achieved. Thus, by using both positive and negative edges of the clock the time-resolution can be improved by two times. However, any further improvement in time-resolution requires the clock frequency to be increased which is not a viable solution.

The methods described above either increase the clock frequency or use a customized DPWM architecture. The schemes based on customized DPWM architecture results in increased silicon area and power consumption, which is undesirable. On the other-hand, the schemes based on DLL and counter-based DPWM are not scalable in nature and provides resolution improvement only for a limited range.

Thus, a DPWM architecture is required which can improve the time resolution without having to increase the clock frequency or resulting in additional power loss.

Nonetheless, DPWM block needs to operate with a digital control scheme, which implements voltage mode control or current mode control. Such control schemes require the inductor current to be sensed. Current sensing is also required for load sharing among paralleled converters. The performance of such a system will depend upon the current sensor employed for this purpose.

## 2.3 Current Sensing Techniques

Numerous methods have been proposed and implemented for sensing the current. All these current sensing techniques can be broadly classified as non-isolated and isolated sensing techniques. The non-isolated sensing technique involves sensing the voltage drop across some resistive element in the circuit or by filtering the voltage across the inductor. On the other hand, the isolated measurement of an electric current is usually done by sensing the magnetic field created by the current to be measured. Some of these methods are listed here:

#### 2.3.1 Series resistance

This method is based on putting a known sense resistor in series with the inductor and sensing the voltage across it. This method gains its popularity because of its simplicity, accuracy and relatively large bandwidth. However, such a current sensing scheme results in power loss. For example, in a 4-phase 100 A VRM, where each leg carries 25 A of current and output voltage is less than 1V, the additional drop across the sensing resistor can be significant, and will result in reduced efficiency. Thus a low resistance is required. A  $1 m\Omega$  resistance will give an output of 25 mV and results in a loss of 0.625 W, whereas  $5 m\Omega$  sense resistor will give an output of 125 mV but results in a loss of 3.125 W. By decreasing the sense resistance, the power loss can be reduced but the sensed voltage becomes small. Signals of such small magnitude are hard to sense in noisy environment. Thus, there exists a trade-off between efficiency and noise. Secondly, such a resistance will have positive thermal coefficient, which will cause the resistance to change with increase in temperature, resulting in inaccuracy in current measurement.

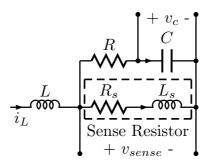

Another drawback of such a sensing method is the presence of parasitic inductance in the series resistor. Due to fast changing currents, the sensor output will not just be proportional to the magnitude but also to rate of change of current. Although non-inductive resistors are available, their inductance is of the order of nH. Therefore a compensation network is required to filter out the effect of the parasitic inductance.

Figure 2.3: Compensation network to remove the effect of parasitic inductance.

A simple low-pass RC network is used to filter the voltage across the senseresistor. One such arrangement is shown in Fig. 2.3. For  $R_s + sL_s \ll R + 1/(sC)$ , the voltage across the series-sense resistor is  $v_{sense} = (R_s + sL_s)i_L$ , where  $R_s$  is the resistance and  $L_s$  is the parasitic inductance associated with it. The voltage across the capacitor is

$$v_c = \frac{v_{sense}}{1 + sRC} = \frac{R_s + sL_s}{1 + sRC} i_L \tag{2.3}$$

$$v_c = R_s \frac{1 + sL_s/R_s}{1 + sRC} i_L \tag{2.4}$$

Hence, by ensuring  $RC = L_s/R_s$ , the sensed voltage will be proportional to the inductor current  $(v_c = R_s \cdot i_L)$ .

PCB trace can also be used for sensing the current. However, if a small length of PCB track is used, the resistance will be small and the signal strength will be poor. A longer track is required in order to improve the signal strength. However, doing so will increase the inductance associated with it.

The effective series resistance (ESR) of the inductor can also be used for sensing the current. The voltage across the inductor can be used to sense the current flowing through it. It is given as

$$v_L = L \frac{di_L}{dt} + r_L i_L \tag{2.5}$$

where  $r_L$  is the ESR of the inductor and  $i_L$  is the current flowing through the inductor. Thus the average current flowing through the inductor can be obtained by using a low pass filter [34]. It is fundamentally same as the resistive sensing method. But this method will require exact knowledge of the inductance and ESR. Thus this method is certainly not advisable if the components have large tolerances.

### 2.3.2 Inductor Voltage Sensing

This method uses the inductor voltage to measure the inductor current [35]. If the series resistance of the inductor is negligible, then the voltage across the inductor is given as

$$v_L = L \frac{di_L}{dt} \tag{2.6}$$

where L is the inductance and  $i_L$  is the inductor current. Thus the inductor current can be obtained by integrating  $v_L$  over time (Fig. 2.4).

$$i_L = \int \frac{1}{L} v_L dt \tag{2.7}$$

Such a scheme, however, requires exact value of the inductor. In practice, any inductor used in the converter will have an associated ESR.

$$v_L = L \frac{di_L}{dt} + r_L i_L \tag{2.8}$$

Integrating this over time will saturate the integrator due to the presence of DC term  $r_L i_L$ . Thus, this method will require compensation for the ESR of the induc-

tor.

Figure 2.4: Inductor voltage sensing for obtaining the inductor current.

### 2.3.3 MOSFET R<sub>ds,ON</sub> Sensing

The on-state resistance of the MOSFET can also be used for sensing the current. The resistance of a MOSFET in its linear operating region is given as

$$R_{ds,ON} = \frac{L}{W \cdot \mu C_{ox} \cdot (V_{gs} - V_{th})}$$

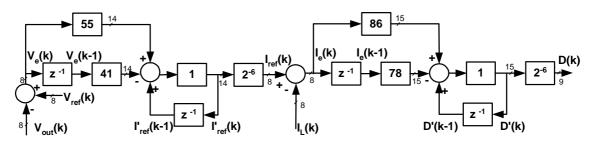

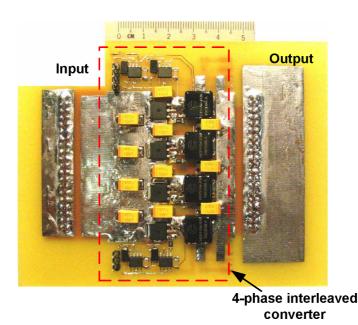

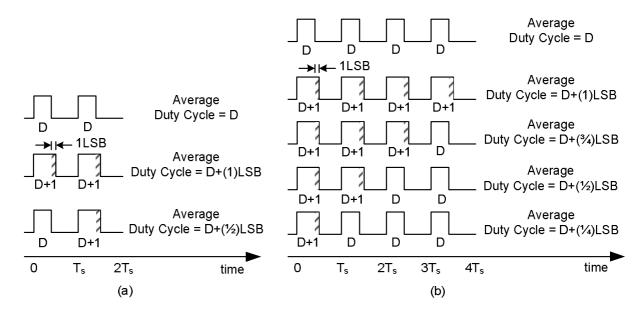

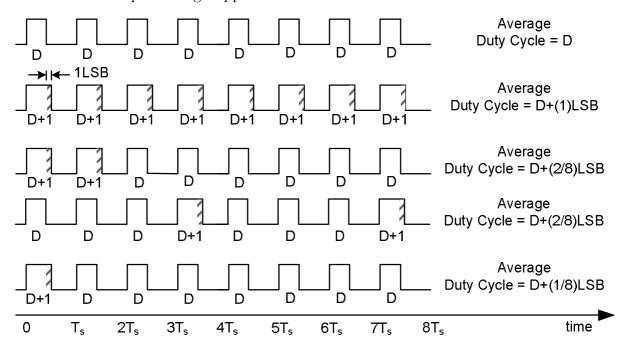

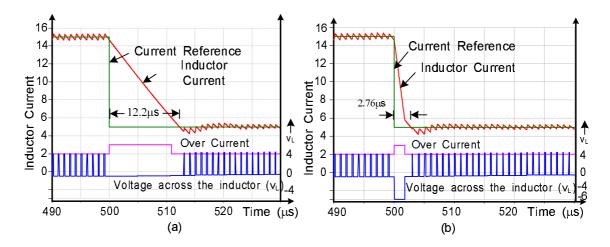

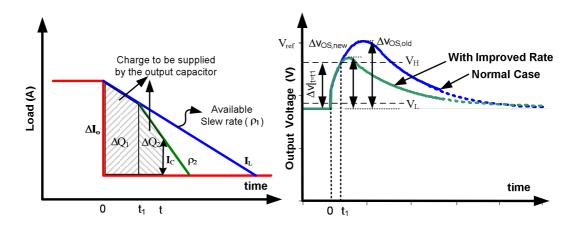

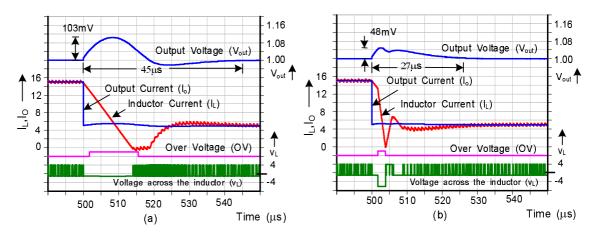

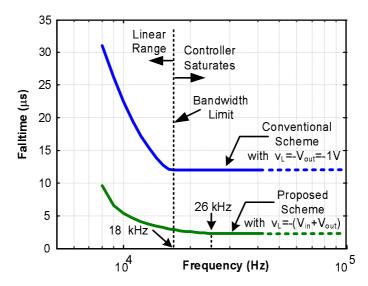

(2.9)