# B\*-TREE REPRESENTATION BASED THERMAL AND VARIABILITY AWARE FLOORPLANNING FRAMEWORK

# SHEFALI SRIVASTAVA

(B.Tech. (Hons), CSJM University, India)

# A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

# Acknowledgements

First of all, I would like to express my deepest gratitude and appreciation to my supervisor **Dr. Ha Yajun**, without whom, this thesis would not have materialized. I sincerely thank him for his valuable guidance, suggestions and constant support throughout my M.Eng thesis research work. I am grateful that he provided me with the opportunity to work on the cutting-edge technology and the most important research areas in the VLSI domain, which has further enhanced my career prospects in future. His emphasis on reasoning out everything, on clarity in presentation of ideas and on looking at the holistic picture of a problem has always guided me in the right direction. His persistence in conquering difficulties in research and the enthusiasm for work have served as excellent examples for me to follow throughout my career.

Finally, I would also like to thank all those who have directly or indirectly provided advice and assistance during the course of my research work in the National University of Singapore.

# **Table of Contents**

| Acknowledgements                                | 1    |

|-------------------------------------------------|------|

| Table of Contents.                              | ii   |

| Summary                                         | vi   |

| List of Tables                                  | viii |

| List of Figures.                                | ix   |

| Chapter 1 Introduction                          | 1    |

| 1.1 Overview                                    | 1    |

| 1.1.1 Floorplanning                             | 1    |

| 1.1.2 Thermal and Power Dissipation effects     | 2    |

| 1.1.3 Design Prototyping                        | 3    |

| 1.2 Problem Definition                          | 4    |

| 1.3 Our Contributions.                          | 7    |

| 1.4 Organization of the Thesis                  | 8    |

| Chapter 2 Background and Related Work           | 10   |

| 2.1 Floorplanning                               | 10   |

| 2.1.1 Topological Representation.               | 10   |

| 2.1.1.1 Normalized Polish Expression.           | 13   |

| 2.1.1.2 Sequence Pair.                          | 15   |

| 2.1.1.3 Corner Block List.                      | 18   |

| 2.1.1.4 B*-Tree                                 | 21   |

| 2.1.1.5 Comparison of different Representations | 27   |

| 2.1.2 Block and Net Model.                                       | 28 |

|------------------------------------------------------------------|----|

| 2.1.2.1 Block Model and Pin Assignment                           | 28 |

| 2.1.2.2 Half Perimeter Wirelength Estimation (HPWL) method       | 30 |

| 2.1.3 Cost Function.                                             | 32 |

| 2.1.4 Floorplanning Algorithms.                                  | 33 |

| 2.1.4.1 Cluster Growth                                           | 34 |

| 2.1.4.2 Genetic Algorithms.                                      | 37 |

| 2.1.4.3 Simulated Annealing                                      | 38 |

| 2.1.5 Floorplanning Methodology                                  | 40 |

| 2.2 Thermal and Power Dissipation effects                        | 41 |

| 2.2.1 Sources of Power Dissipation.                              | 41 |

| 2.2.1.1 Dynamic Power Dissipation                                | 42 |

| 2.2.1.1.1 Interconnect Power Dissipation                         | 43 |

| 2.2.2 Temperature Estimation.                                    | 44 |

| 2.2.2.1 Hotspot Tool.                                            | 46 |

| 2.3 Variation Models                                             | 47 |

| 2.3.1 Interval Arithmetic (IA)                                   | 49 |

| 2.3.2 Affine Arithmetic (AA)                                     | 51 |

| 2.3.3 Monte Carlo Simulation                                     | 54 |

| Chapter 3 Interconnect Power and Thermal aware Floorplanning     | 55 |

| 3.1 Motivation                                                   | 55 |

| 3.2 Problem Formulation                                          | 57 |

| 3 3 Interconnect Power and Thermal aware Floorplanning Algorithm | 58 |

| 3.3.1 Methodology and Algorithm                | 58  |

|------------------------------------------------|-----|

| 3.3.2 Interconnect Power Distribution.         | 61  |

| 3.3.3 Temperature Approximation                | 66  |

| 3.4 Experimental Results                       | 67  |

| 3.4.1 Experimental Setup.                      | 67  |

| 3.4.2 Results and Analyses                     | 69  |

| 3.4.3 Discussion.                              | 79  |

| 3.5 Conclusion.                                | 80  |

| Chapter 4 Variability Aware Floorplanning      | 81  |

| 4.1 Motivation                                 | 81  |

| 4.2 Problem Formulation.                       | 83  |

| 4.3 Algorithm                                  | 87  |

| 4.3.1 Monte Carlo Simulation Approach          | 91  |

| 4.3.2 Our Approach                             | 92  |

| 4.3.2.1 Determination of x Co-ordinates        | 93  |

| 4.3.2.2 Determination of <i>y</i> Co-ordinates | 94  |

| 4.3.2.3 Determination of Area Range.           | 96  |

| 4.3.2.4 Determination of Wirelength Range      | 96  |

| 4.4 Experimental Results.                      | 99  |

| 4.4.1 Experimental Setup.                      | 99  |

| 4.4.2 Results and Analyses.                    | 100 |

| 4.4.3 Discussion.                              | 102 |

| 4.5 Conclusion                                 | 103 |

| Chapter 5 Conclusions and Future Directions | 104 |

|---------------------------------------------|-----|

| 5.1 Conclusions                             | 104 |

| 5.2 Future Directions.                      | 105 |

| Bibliography                                | 107 |

# **Summary**

The evolution of deep submicron technologies has placed a high importance on power dissipation and temperature of the chip. In addition, the increasing design complexity is causing higher levels of uncertainty in design prototyping in the early chip planning stages, thus leading to parameter variations which are posing an ever-increasing challenge to performance analysis of high-speed designs. The purpose of this thesis is to develop an interconnect power and thermal aware, and a variability-aware floorplanner based on B\*-Tree representation, to combat the effects of scaling technologies on temperature and variations due to design uncertainty, separately. The thesis consists of two parts which explain our work done in the areas of interconnect power and thermal aware floorplanning, and variability-aware floorplanning as described below.

Interconnect power dissipation is becoming a performance bottleneck in sub micron technologies leading to dramatic rise in chip temperatures which have negative impact on chip performance and reliability. However, most prior work fail to consider the switching activity of interconnects in deriving interconnect power dissipation and in exploring a thermal-aware floorplan. This can result in peak temperatures being underestimated by as much as 15°C according to our experiments. In this work, we present an interconnect power and thermal aware floorplanner that aims at reducing hotspots and distributing temperature evenly across a chip, while optimizing the traditional design metrics, chip area and wirelength. Results demonstrate that our floorplanner is effective in lowering peak temperatures by as much as 20% while providing floorplans that are as compact as the traditional area oriented techniques with just a slight overhead of total wirelength by 2% when testing on five MCNC benchmarks.

The ever increasing growth of design complexity with the scaling of technologies towards the nanometer regime brings with it a challenging increase in the amount of variability due to uncertainty in initial estimates in early phases of the chip planning. With the introduction of variations due to uncertainty in block characteristics such as width, height and aspect ratio, a traditional deterministic floorplanner is unable to take block's variations into account and a variability-aware floorplanner is needed. In this work, we use an affine arithmetic (AA) model to develop a fast and optimized variability-aware floorplanner. The AA model enables a fast and accurate estimation of the variable range of floorplan metrics such as area and wirelength in the presence of variations of each block's dimensions. Compared with the Monte Carlo simulation results, the average errors of mean and range values computed by the proposed method are -0.78% & -12.96% respectively for area, -2.43% & -13.23% respectively for wirelength and up to 100X speed up by testing on five MCNC benchmarks. Our solution to this problem is also interesting to related problems such as warehouse floorplanning.

# **List of Tables**

| Table 2.1. Comparisons among the solution spaces and time complexity of various floorplan representations | 28  |

|-----------------------------------------------------------------------------------------------------------|-----|

| Table 2.2. Pin locations of a five terminal net.                                                          | 32  |

| Table 3.1. MCNC benchmarks information.                                                                   | 68  |

| Table 3.2. Results considering traditional area and wirelength minimizations                              | 69  |

| Table 3.3. Results using our thermal aware floorplanner                                                   | 70  |

| Table 3.4. Comparison of runtime results for Hung's floorplanner and our floorplanner                     | 72  |

| Table 4.1. Ranges of width and height for each block.                                                     | 86  |

| Table 4.2. Values of width, height and location of each block                                             | 86  |

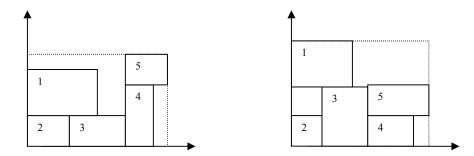

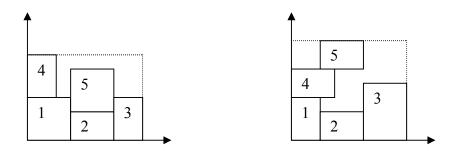

| Table 4.3. Width, height and area of the floorplan layout of Figures 4.3 (a) and (b)                      | 87  |

| Table 4.4. Width, height and location of each block for B*-Tree 2                                         | 88  |

| Table 4.5. Width, height and area of the floorplan layout of Figures 4.5 (a) and (b)                      | 89  |

| Table 4.6. MCNC benchmarks information.                                                                   | 100 |

| Table 4.7. Results for area and wirelength using MC approach                                              | 100 |

| Table 4.8. Results for area and wirelength using our approach                                             | 101 |

| Table 4.9. Area and wirelength comparison results of our algorithm and Monte-Carlo simulation (MC) method | 101 |

# **List of Figures**

| Figure 2.1: Slicing floorplan and its corresponding binary tree.                                                                                                                                                                                                                                     | 11 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2: Mosaic floorplan (wheel structure)                                                                                                                                                                                                                                                       | 12 |

| Figure 2.3: General floorplan.                                                                                                                                                                                                                                                                       | 12 |

| Figure 2.4: Relationship among the solution spaces of slicing, mosaic and general floorplans.                                                                                                                                                                                                        | 13 |

| Figure 2.5: Slicing floorplan, its NPE and the corresponding slicing tree                                                                                                                                                                                                                            | 14 |

| Figure 2.6: (a) Oblique grid for sequence pair ( $<4\ 3\ 1\ 6\ 2\ 5>$ , $<6\ 3\ 5\ 4\ 1\ 2>$ ) (b) Four of block 1 (c) Corresponding packing. Dimensions for the six blocks are: 1 ( $4\times 6$ ), 2 ( $3\times 7$ ), 3 ( $3\times 3$ ), 4 ( $2\times 3$ ), 5 ( $4\times 3$ ) and 6 ( $6\times 4$ ) |    |

| Figure 2.7: The horizontal and vertical constraint graphs of a sequence pair <431625 <635412>) (a) Horizontal constraint graph (b) Vertical constraint graph                                                                                                                                         | -  |

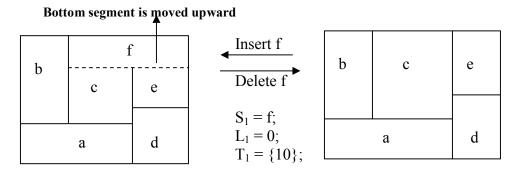

| Figure 2.8: Two different kinds of T-junction and orientation of the corner block (CB) "f"                                                                                                                                                                                                           | 18 |

| Figure 2.9: Deletion/Insertion of vertically oriented corner block "f"                                                                                                                                                                                                                               | 19 |

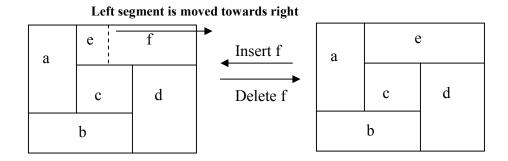

| Figure 2.10: Deletion/Insertion of horizontally oriented corner block "f"                                                                                                                                                                                                                            | 19 |

| Figure 2.11: A CBL list and the resultant floorplan                                                                                                                                                                                                                                                  | 21 |

| Figure 2.12: (a) A placement (b) The corresponding B*-Tree                                                                                                                                                                                                                                           | 22 |

| Figure 2.13: Pseudo code of algorithm for finding the placement from a corresponding B*-Tree                                                                                                                                                                                                         |    |

| Figure 2.14: Adding a new module on top, we search the contour from left to right and update it with the top boundary of the new module                                                                                                                                                              | 24 |

| Figure 2.15: Example showing the perturbations process on placement and its corresponding B*-Tree.                                                                                                                                                                                                   | 26 |

| Figure 2.16: Block and terminal locations in a chip                                                                                                                                                                                                                                                  | 28 |

| Figure 2.17: Pin locations on a block.                                                                                                                                                                                                                                                               | 29 |

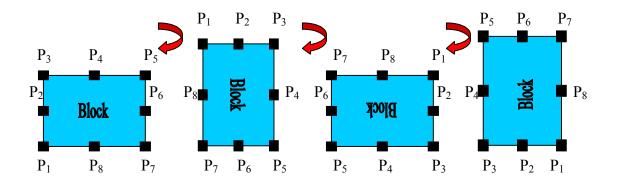

| Figure 2.18: Different block orientations and corresponding pin locations                                                                                                                                                                                                                            | 30 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Figure 2.20: HPWL of a net.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                                                                                 |

| Figure 2.21: Example of determination of HPWL of a five termin                                                                                                                                                                                                                                                                                                                                                                                                                             | nal net31                                                                                          |

| Figure 2.22: Cluster growth floorplanning                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34                                                                                                 |

| Figure 2.23: Linear ordering algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                 |

| Figure 2.24: Classification of nets during linear ordering                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                                                 |

| Figure 2.25: Cluster growth algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                                                 |

| Figure 2.26: Genetic algorithm flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38                                                                                                 |

| Figure 2.27: Pseudo code of simulated annealing algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                                                                                                 |

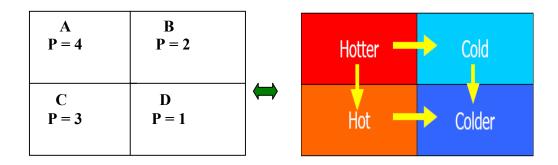

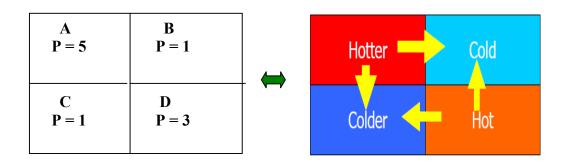

| Figure 2.28: Case 1: a) Power distribution profile b) Correspond flow.                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                                                  |

| Figure 2.29: Case 2: a) Power distribution profile b) Correspond flow.                                                                                                                                                                                                                                                                                                                                                                                                                     | =                                                                                                  |

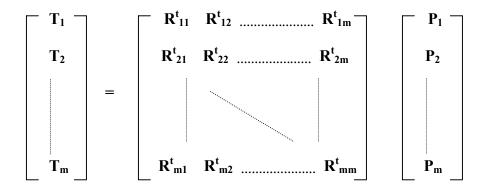

| Figure 2.30: Transfer thermal resistance matrix R <sup>t</sup>                                                                                                                                                                                                                                                                                                                                                                                                                             | 16                                                                                                 |

| 1 15010 2.50. Transfer inclinal resistance matrix it                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                                 |

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                 | ware floorplanning                                                                                 |

| Figure 3.1: Pseudo code of the interconnect power and thermal a                                                                                                                                                                                                                                                                                                                                                                                                                            | ware floorplanning60 and switching activity                                                        |

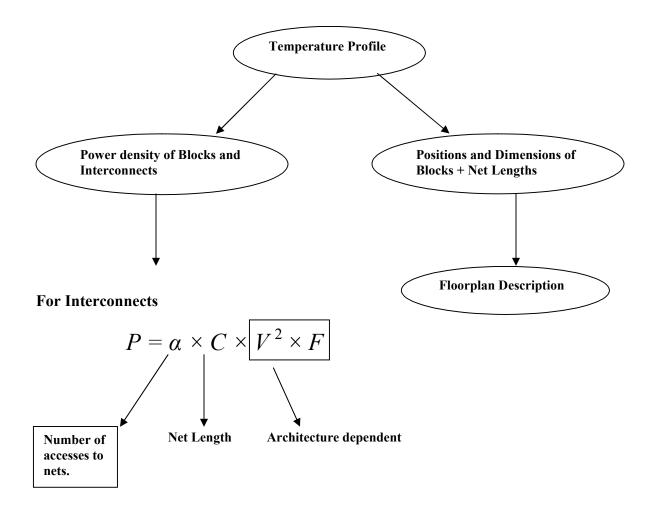

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm.  Figure 3.2: Diagram showing relationship between temperature a                                                                                                                                                                                                                                                                                                                                                 | ware floorplanning60 and switching activity61                                                      |

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm.  Figure 3.2: Diagram showing relationship between temperature a of interconnect.                                                                                                                                                                                                                                                                                                                                | ware floorplanning                                                                                 |

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm                                                                                                                                                                                                                                                                                                                                                                                                                  | ware floorplanning                                                                                 |

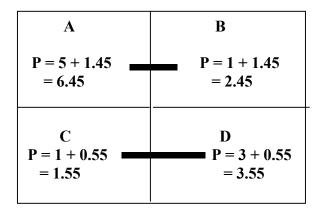

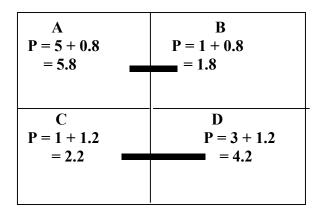

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm.  Figure 3.2: Diagram showing relationship between temperature a of interconnect.  Figure 3.3: Pseudo code of the Calculate_Power algorithm  Figure 3.4: Power distribution profile for case 1                                                                                                                                                                                                                   | ware floorplanning                                                                                 |

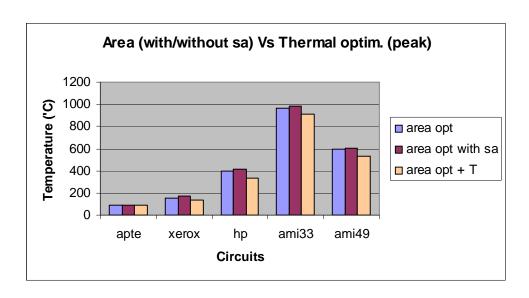

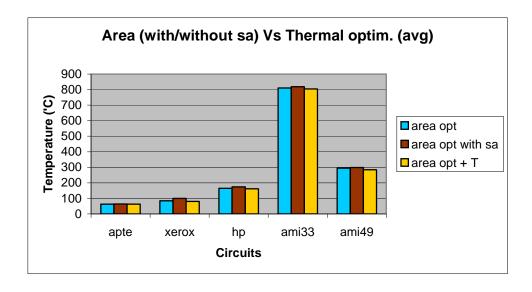

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm.  Figure 3.2: Diagram showing relationship between temperature a of interconnect.  Figure 3.3: Pseudo code of the Calculate_Power algorithm.  Figure 3.4: Power distribution profile for case 1.  Figure 3.5: Power distribution profile for case 2.  Figure 3.6: Comparison of peak temperatures for area optimization.                                                                                         | ware floorplanning                                                                                 |

| Figure 3.1: Pseudo code of the interconnect power and thermal a algorithm.  Figure 3.2: Diagram showing relationship between temperature a of interconnect.  Figure 3.3: Pseudo code of the Calculate_Power algorithm.  Figure 3.4: Power distribution profile for case 1.  Figure 3.5: Power distribution profile for case 2.  Figure 3.6: Comparison of peak temperatures for area optimizations consideration of switching activity and thermal aware optimizations area optimizations. | ware floorplanning60 and switching activity61636465 on with/without on71 zation with otimization71 |

| Figure 3.9: Floorplan of <i>xerox</i> with area and thermal optimization                            | 74 |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 3.10: Floorplan of <i>hp</i> with area optimization only                                     | 75 |

| Figure 3.11: Floorplan of <i>hp</i> with area and thermal optimization                              | 75 |

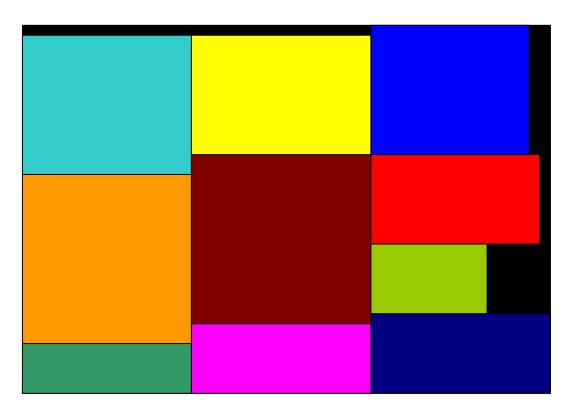

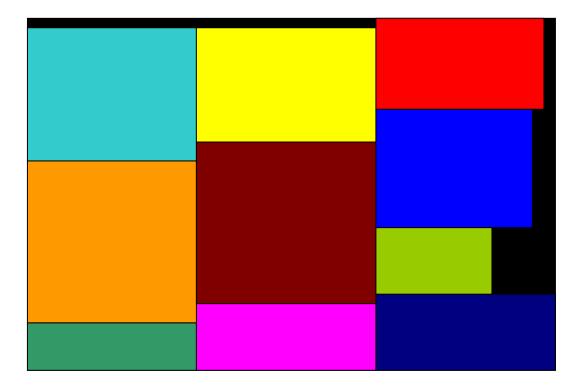

| Figure 3.12: Floorplan of <i>ami33</i> with area optimization only                                  | 76 |

| Figure 3.13: Floorplan of <i>ami33</i> with area and thermal optimization                           | 76 |

| Figure 3.14: Floorplan of <i>ami49</i> with area optimization only                                  | 77 |

| Figure 3.15: Floorplan of <i>ami49</i> with area and thermal optimization                           | 77 |

| Figure 3.16: Floorplan of <i>apte</i> with area optimization, and area and thermal optimization.    | 78 |

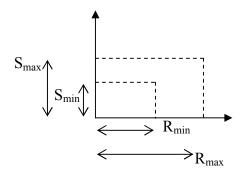

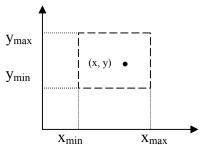

| Figure 4.1: Width and height ranges of a module                                                     | 84 |

| Figure 4.2: Left bottom co-ordinate ranges (x, y) of a module                                       | 84 |

| Figure 4.3: (a) and (b): Impact of variability on chip area and location of modules                 | 86 |

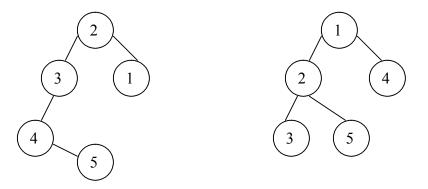

| Figure 4.4: (a) B*-Tree 1 (b) B*-Tree 2                                                             | 88 |

| Figure 4.5: (a) and (b): Impact of variability on chip area and location of modules for B*-Tree 2   |    |

| Figure 4.6: Pseudo code of our floorplanning algorithm                                              | 91 |

| Figure 4.7: Pseudo code of placement using MC approach.                                             | 92 |

| Figure 4.8: Pseudo code for determination of <i>x</i> and <i>y</i> co-ordinates using our approach. | 95 |

| Figure 4.9: Pseudo code of placement using our approach                                             | 98 |

# Chapter 1

# Introduction

# 1.1 Overview

Aggressive scaling of process technologies towards the nanometer regime has enabled feature sizes to shrink continuously. This allows designers to pack more functionality onto a single die. However, the increased level of integration within a single die imposes rigid constraints on the power consumption budget and hence the temperature profile of the chip. Also, it brings with it a challenging increase in the amount of variability due to uncertainty in initial estimates in the early phases of VLSI design i.e. design prototyping.

# 1.1.1 Floorplanning

Floorplanning is an important step in the VLSI design process to plan the positions and orientations of a set of circuit modules on a chip in such a way that no blocks overlap and the circuit performance is optimized. It can have drastic impacts on the quality and flexibility of a design such as layout area, wirelength congestion, power density and temperature of the chip. As technology moves into the deep-submicron era, circuit sizes and complexities are growing rapidly and floorplanning has become more important than ever before. With the introduction of uncertainty in the block dimensions at the time of floorplanning, a variability-aware floorplanner can predict the ranges of area and wirelength of a design that impact acceptability assessment of the chip architecture in the early design decision stage.

There are two aspects in general when dealing with the floorplanning problem. The first one is to find an appropriate topological representation (CBL, B\*-Tree, O-Tree, TBS, BSG, Sequence Pair, TCG etc.) in the form of a data structure to represent the geometrical relationship among the blocks. The second aspect considers the application of a stochastic search method on the representation to find an optimized floorplan. Most floorplanning algorithms use simulated annealing to search for an optimal solution. Floorplanning has been proven to be a NP-hard problem, hence, it is important to chose a good representation and a searching methodology to perturb the infinite solution space to search for a near optimal floorplan solution in less time. Most of the research is focused on these two aspects of the floorplanning problem.

#### 1.1.2 Thermal and Power Dissipation effects

Interconnects have become the center of attraction in terms of power consumption and performance as the process technology scales into the deep sub micron region. However, interconnects, unlike transistors, have not scaled down exponentially as we move to nano meter era. This has led to an increase in the total capacitance of interconnects and hence dynamic power dissipation despite the introduction of low dielectric materials. Secondly, long interconnects, compared to the scaled transistors, are becoming exceptionally long. In order to keep the delays of these long wires tractable, repeaters and flip-flops are inserted to prevent performance degradation. However, these additional components have detrimental impacts on interconnect power dissipation.

Power density directly translates into heat which may lead to a significant increase in chip temperature. As a result, the temperature in modern high performance VLSI circuits increases dramatically due to smaller feature size, higher packing density and

rising power consumption. The hotspot in a modern chip might have a temperature of more than 100°C while the intrachip temperature differentials can be larger than 10~20°C [41]. Temperature can have a dramatic impact on circuit performance, power, and reliability: MOS current drive capability decreases approximately 4% for every 10°C temperature increase while the leakage current increases exponentially with the temperature increase resulting in thermal runaways. The interconnect resistance also becomes larger with increasing temperature. For example, the resistivity of copper increases by 39% from 20°C to 120°C. Higher resistivity causes longer interconnect RC delay and hence performance degradation. The interconnect (Elmore) delay increases approximately 5% for every 10°C increase in temperature [1]. Higher temperatures accelerate electro migration failures and reduce the lifetime of the device. Finally, high temperature of the chip makes cooling solutions significantly more expensive. Therefore, it is very important to eliminate hotspots and have a thermal balanced design. Power-aware design alone is not able to address the temperature challenge because the thermal distribution profile depends on not only the power density but also the physical size and location of each functional block. Therefore, even though it is related to the power-aware design area, thermal-aware design itself is a distinct and important research area.

## 1.1.3 Design Prototyping

Design prototyping has gathered much attention recently due to increasing complexity of VLSI designs and the need for area and performance measures early in the chip planning stage. Based on the assessment of the above measures, the chip architecture is revisited and it is partially or completely redesigned accordingly to meet the design

specifications. This saves a lot of time and cost incurred otherwise due to changes made after the actual implementation. Since design prototyping occurs very early in the design phase, uncertainty exists in the circuit physical dimensions and the technology library cells. This poses a challenging task to the designer to have initial estimates about area and performance parameters of the chip. Therefore, we need to correctly model these uncertainty variations not only to determine the correct expected circuit area and performance of a design but also to correctly optimize the design such that the percentage of parts that meet a specified performance target is maximized.

#### 1.2 Problem Definition

The work in the thesis is inspired from the concerns at rising trends in accurate thermal-conscious mechanisms and the impact of variations due to design uncertainty in early planning stage of a chip fabricated with sub-micron technologies. Designers are looking at developing new methods to tackle these problems at an early design stage so that unnecessary work may be avoided at later stages. Floorplanning has been a major focus of attention and research since it can impact many important design decisions at an early stage.

Many thermal-aware floorplanners exist that estimate the temperature of the chip and help to reduce hotspots by clever floorplanning techniques. However, with the onset of high switching activity circuits i.e. circuits which have high usage of specific interconnects and increasing interconnect power dissipation, previous floorplanners fail to provide accurate temperature estimates. Therefore, we need to consider the switching activity of different interconnects in deriving the total power dissipation in a circuit. Since the temperature of the chip depends largely on the power distribution profile in a chip,

neglecting any of the factors responsible for power dissipation will give a pessimistic analysis of temperature estimates.

As designs are getting more complex, it is difficult to have the entire design (the netlist and the database library) completely specified and available at the time of floorplanning. This introduces uncertainty in block dimensions which then need to be specified by a range of values for further evaluation. Floorplanning with uncertainty is the process of obtaining an accurate floorplan with missing data. With the introduction of variations in block characteristics such as width, height and aspect ratio, due to design uncertainty, a traditional deterministic floorplanner is unable to take block variations into account and a variability-aware floorplanner is needed. The traditional floorplanners optimize design metrics to find one best *fixed* floorplan for blocks with only *fixed* block characteristics. For example, an area driven traditional floorplanner might perform optimizations to find one fixed floorplan that yields the minimum total area. It assumes that each block has fixed block area or aspect ratio when estimating the total chip area. However, the variability-aware floorplanner optimizes design metrics to find one best relative floorplan for all blocks with variable block characteristics. For example, an area driven variability-aware floorplanner might perform optimizations to find one relative floorplan that yields the minimum average total area for all possible variations in the range. It assumes that each block has variable block area or aspect ratio when estimating the total chip area. As a result, with the introduction of variability in the dimensions for each module, the conventional approach fails to estimate the ranges of area, wirelength and other floorplan metrics.

To estimate the range caused by variations, two types of brute-force approaches

can be tried. The first approach assumes the worst-case magnitude for each variation but the resulting floorplan will be very pessimistic. The second approach performs Monte Carlo simulations to consider enough points in a very large variation space, although the results are relatively accurate but the simulation time is extremely long. Both approaches are not ideal to have a fast and accurate estimation of ranges.

To provide a fast yet accurate estimation of ranges caused by variations, the related area in statistical static timing analysis (STA) uses analytical approaches to find closed-form expressions for the distributions of circuit delays. These methods use normal distributions, interval valued analysis, probabilistic intervals or mathematical statistical models. We believe a similar approach is needed to quickly and accurately estimate the floorplan metric ranges.

Thus, our problem definition consists of developing a floorplanning algorithm with the objective of minimizing chip area and wirelength together with achieving two major goals as outlined below:

- Accurate chip thermal modeling with the consideration of switching activity of interconnects and netlength in determining interconnect power dissipation together with the block power dissipation in a chip. The goal of floorplanning algorithm is to evenly spread out the temperature on a chip and thus reduce hotspots.

- Determining the range of total area and wirelength under the presence of variations in dimensions of modules. The goal is to determine the best relative floorplan with the smallest range and average for all possible variations in total area and wirelength.

#### 1.3 Our Contributions

We develop a floorplanner based on B\*-Tree representation and use the simulated annealing algorithm to get the best floorplan layout meeting the criteria as outlined in the problem definition given earlier. The major contributions of the thesis are two fold.

First, our work incorporates the feature of switching activity of interconnects while calculating the power densities across the entire chip and shows that it can lead to different power density profiles depending on values of switching activity, keeping other parameters like positions and dimensions of functional blocks and interconnect lengths constant. This results in significant change in chip temperature leading to localized hot spots. We then develop an interconnect power and thermal aware floorplanner that aims at reducing hotspots and distributing temperature evenly across a chip while optimizing the traditional design metrics, chip area and wirelength. A thermal modeling tool called HotSpot is used to determine the chip temperature profile. Our work is novel with regard to the different floorplanning algorithms developed till recently for chip temperature estimates as none of the previous works take switching activity of the interconnects into account for determining the temperature of the chip. Results in our work indicate that excluding switching activity in interconnect power determination can result in peak temperatures to be under estimated by as much as 15°C. Our floorplanner is effective in lowering peak temperatures by as much as 20% while providing floorplans that are as compact as the traditional area oriented techniques with a slight overhead of total wirelength by 2% when testing on five MCNC benchmarks

Second, we present a mathematical model using affine arithmetic to estimate the range of floorplan metrics such as chip area and wirelength under the given variations in dimensions for each module. Our work is a breakthrough with reference to earlier related work that considers variations of width and height of each block to be limited to certain discrete values in a range. Also, we use more advanced analytical technique i.e. affine arithmetic to perform range calculations on a set of MCNC benchmark circuits. Moreover, we also determine range of wirelength in addition to the range of area. We determine the most feasible B\*-Tree as the solution which can give the lowest range of values lying as close as possible to the minimum average values of area and wirelength for a given set of variations. We then run Monte Carlo simulations to verify the accuracy of our affine arithmetic model. Experimental results show that, compared with the Monte Carlo simulation results, the average errors of mean and range values computed by the proposed method are -0.78% & -12.96% respectively for area, -2.43% & -13.23% respectively for wirelength and up to 100X speed up by testing on five MCNC benchmarks. Our solution to this problem is also interesting to other related problems such as warehouse floorplanning.

# 1.4 Organization of the Thesis

The remainder of this thesis is organized as follows. Chapter 2 gives the

background information on floorplanning, thermal and power dissipation effects, and variations due to design uncertainty, which provide the base and framework for the work done in this thesis. The chapter gives an overview of floorplanning concepts including the description of B\*-Tree and simulated annealing algorithm which have been used in our work. Further, it describes the sources of power dissipation in a chip together with the role of interconnects in determining power dissipation, and hence the temperature estimation of the chip using a thermal modeling tool called Hotspot. Finally, the chapter gives a brief overview of Monte Carlo simulation method, numerical computation methods i.e. interval arithmetic and affine arithmetic which have been used for modeling variations. Chapter 3 reviews the previous work which has served as a source of motivation for this research work and formally describes the problem definition, solution approach and experimental results for our contribution towards making thermal-aware floorplanning more accurate with the incorporation of switching activity of interconnects in deriving the power dissipation in a chip. Chapter 4 presents the formal problem formulation for our contribution towards developing a variability-aware floorplanner based on affine arithmetic to enable a fast and accurate estimation of the variable range of floorplan metrics such as area and wirelength in the presence of variations of block dimensions due to design uncertainty. The chapter reviews the previous related work, explains our variability-aware floorplanning algorithm in detail and presents the experimental results based on both the Monte Carlo simulation approach and our approach. Chapter 5 draws the conclusions and provides future research directions.

# Chapter 2

# **Background and Related Work**

In this chapter, we discuss some preliminary topics which will provide the necessary ground framework for the work done in this thesis. The chapter is organized as follows. Section 2.1 briefly discusses floorplanning concepts and the typical approach followed to solve a floorplanning problem. It gives an overview of various topological representations, block and net model including pin assignment and wirelength estimation method, and various floorplanning algorithms. Section 2.2 discusses various causes of power dissipation including interconnect power dissipation. It also explains the method to estimate temperature together with a brief description of thermal modeling tool called Hotspot. Section 2.3 explains Monte Carlo simulation method, and mathematical models like interval arithmetic and affine arithmetic, which are used for modeling variations.

# 2.1 Floorplanning

Floorplanning is an important step in physical design of VLSI circuits to plan the positions and orientations of a set of circuit modules on a chip in order to optimize the circuit performance. The quality of the floorplan solution depends largely on the choice of topological representation and the floorplanning algorithm selected to search over an infinite solution space.

# 2.1.1 Topological Representation

In order to floorplan a circuit design, an abstract representation is needed to represent the geometrical relation or topologies among blocks so that some algorithms can

be applied on to solve the problem. This abstract representation is called topological representation and is commonly specified by a rectangular dissection of the floorplan region. Floorplans can be divided into two categories, the *slicing floorplans* [4], [5] and the *non-slicing floorplans* [6], [7], [8] and [9].

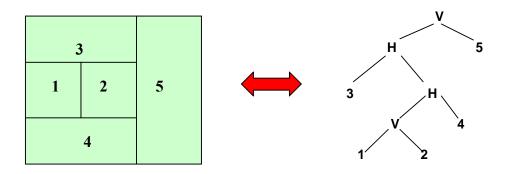

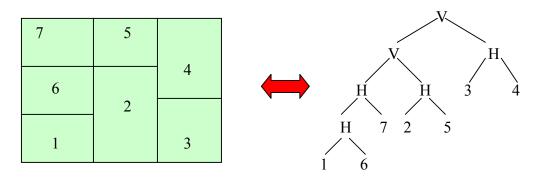

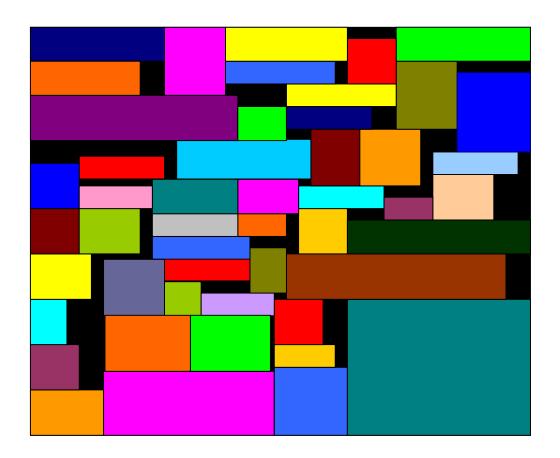

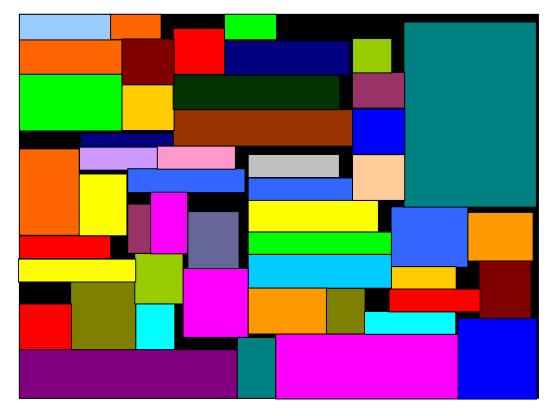

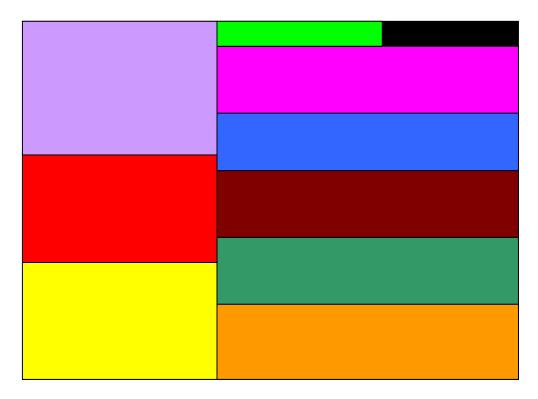

Slicing floorplan is a rectangular dissection that can be obtained by recursively cutting a rectangle horizontally or vertically into two smaller rectangles. Slicing floorplans are represented by slicing structures which can be modeled by a binary tree with *n* leaves and *n-i* nodes where each node represents a vertical cut line or a horizontal cut line and each leaf a basic rectangle. Figure 2.1 shows the slicing floorplan and its corresponding binary tree.

Figure 2.1: Slicing floorplan and its corresponding binary tree.

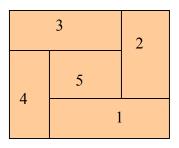

Non-slicing floorplans are further categorized into mosaic floorplans and general floorplans. Mosaic floorplan is one which is dissected into exactly n rooms so that each room is occupied by one and only one block. E.g. a wheel structure as shown in Figure 2.2. In addition, there is no crossing cut in the mosaic floorplan.

Figure 2.2: Mosaic floorplan (wheel structure).

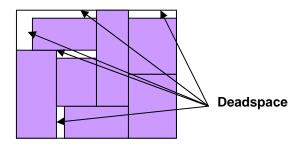

General floorplan is similar to mosaic floorplan in that non-slicing structures are allowed. However, the floorplan region can be dissected into more than n rooms such that some rooms are empty, i.e. not occupied by any block as in Figure 2.3.

Figure 2.3: General floorplan.

Deadspace of a floorplan is the space that is wasted as shown in Figure 2.3.

Minimizing area is the same as minimizing deadspace. Deadspace percentage is computed as

$$\frac{(A - \sum A_i)}{\sum A_i} \times 100\% \tag{2.1}$$

where  $A_i$  is the area of each block i and A is the total area of the floorplan.

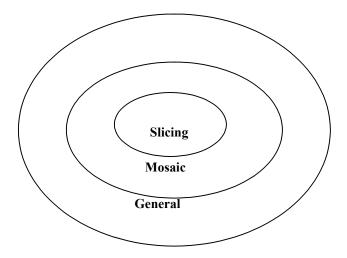

Slicing floorplan is a special case of mosaic floorplan and mosaic floorplan is a special case of general floorplan. The relationship among the solution spaces of slicing, mosaic and general floorplans is illustrated in Figure 2.4 on next page.

Figure 2.4: Relationship among the solution spaces of slicing, mosaic and general floorplans.

Various topological representations like Normalized Polish Expression, B\*-Tree [10], O-Tree [6], Sequence Pair [11], Corner Block List (CBL) [12], Bounded Sliceline Grid (BSG) [8], Transitive Closure Graph (TCG) [13] etc. have been proposed to represent slicing and non-slicing floorplans. We briefly describe some of the most popular representations below.

## 2.1.1.1 Normalized Polish Expression (NPE)

Normalized polish expression [5] proposed by Wong and Liu is used for representing slicing floorplans. NPE removes the redundancy in the binary tree representation, which is due to the existence of more than one binary tree corresponding to the same slicing floorplan. An ideal data representation is one which is able to represent all possible combinations of floorplan without having two or more data representations that correspond to the same floorplan.

An expression,  $E = e_1, e_2, ..., e_{2n-1}$ , where  $e_i \in \{1, 2, ..., n, H, V\}$ ,  $1 \le i \le 2n-1$ , is a polish expression of length 2n-1 iff

- Every operand j,  $1 \le j \le n$ , appears exactly once in the expression, and

- The expression E has the balloting property, i.e. for every sub-expression  $E_i = e_1, e_2, ..., e_i, 1 \le i \le 2n-1$ , the number of operands is greater than the number of operators.

A polish expression is said to be a normalized polish expression iff E has no consecutive H's and V's (e.g. 16H7H25HV34HV).

We can view a normalized polish expression as a bottom UP description of a slicing structure. In fact, we can interpret the symbols H and V as two binary operators between slicing structures. If A and B are slicing structures, we can interpret AHB and AVB as the resulting slicing structures obtained by placing B on top of A, and B to the right of A, respectively. A postorder traversal of the slicing tree results in a NPE with V and H as the operators, and the basic rectangles as operands (See Figure 2.5). This expression specifies how to build the final slicing structure from smaller ones. Figure 2.5 shows the slicing floorplan, its NPE and the corresponding slicing tree.

NPE = 16H7H25HV34HV

Figure 2.5: Slicing floorplan, its NPE and the corresponding slicing tree.

### 2.1.1.2 Sequence Pair

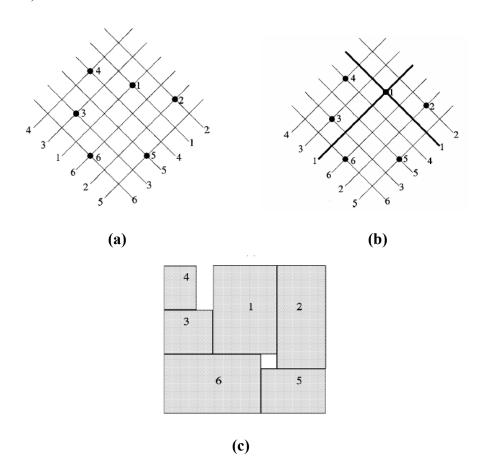

Murata et al. [11] proposed the sequence-pair representation for rectangular module placement. The main idea is to use a sequence pair to represent the geometric relation of modules, place the modules on a grid structure and construct corresponding constraint graphs to evaluate cost. This representation requires 2n[log n] space to encode a sequence pair and there are  $(n!)^2$  combinations in total where n is the number of modules. Further, the transformation between a sequence pair and a placement takes O(nlog n) time.

A sequence pair ( $\Gamma$ +,  $\Gamma$ -) is a pair of sequences of elements representing a list of blocks. The two sequences  $\Gamma$ + and  $\Gamma$ - are permutations of a given block set. The sequence pair structure is actually a meta grid. Given a sequence pair, one can construct a 45 degree oblique grid as shown in Figure 2.6 (a). For every block, the plane is divided by the two crossing slope lines into four cones as shown in Figure 2.6 (b). Block 2 is in the right cone of block 1, then it is to the right of block 1 [see Figure 2.6 (c)]. In general, the relative positions between any two blocks  $\alpha$  and  $\alpha$  can be derived from a sequence pair ( $\Gamma$ +,  $\Gamma$ -) by the following rules.

• Horizontal constraint:

If  $(\Gamma +, \Gamma -) = (< ...a, ..., b...>, < ...a, ..., b...>)$ , block b is at the right side of block a.

• Vertical constraint:

If  $(\vec{1} +, \vec{1} -) = (< ...a, ..., b...>, < ...b, ..., a...>)$ , block b is below block a.

For example,  $(\Gamma^+, \Gamma^-) = (<431625>, <635412>)$  is a sequence pair of block set  $\{1, 2, 3, 4, 5, 6\}$ . Figure 2.6 shows the oblique grid and packing of the sequence pair (<431625>, <635412>).

Figure 2.6: (a) Oblique grid for sequence pair (<4 3 1 6 2 5>, <6 3 5 4 1 2>) (b) Four cones of block 1 (c) Corresponding packing. Dimensions for the six blocks are: 1 (4 × 6), 2 (3 × 7), 3 (3 × 3), 4 (2 × 3), 5 (4 × 3) and 6 (6 × 4).

#### **Evaluation of a Sequence Pair**

In order to evaluate the corresponding floorplan of a sequence pair and determine the position of each block, Murata et al. [11] used two weighted directed constraint graphs  $G_h$  and  $G_v$  that are constructed according to horizontal and vertical constraints of a sequence pair. Then, the longest path algorithm is invoked to determine the longest paths of the two graphs. The longest paths of  $G_h$  and  $G_v$  are the width and

height of the corresponding placement of the sequence pair respectively. Figures 2.7 (a) and (b) are examples of the weighted directed constraint graphs  $G_h$  and  $G_v$  of the sequence pair  $(\vec{\Gamma}+,\vec{\Gamma}-)=(<431625>,<635412>)$ .

Figure 2.7: The horizontal and vertical constraint graphs of a sequence pair (<431625>, <635412>) (a) Horizontal constraint graph (b) Vertical constraint graph.

The time complexity of the longest path algorithm is  $O(n^2)$  where n is the number of blocks. It had been proved that the longest path of  $G_h$  is equivalent to the longest common subsequence of  $\Gamma$  and  $\Gamma$ , and the longest path of  $G_v$  is equivalent to the longest common subsequence of  $\Gamma$  and  $\Gamma$  where  $\Gamma$  is the reverse sequence of  $\Gamma$ . Based on the theorm, Tang et al. [7] used an effective data structure to determine the longest common subsequence of a sequence pair in O(nloglogn) time. They use a complete binary tree and a doubly-linked list to determine the longest common subsequence of a sequence pair. The doubly linked list is used to keep the longest common subsequence during the evaluating process and a complete binary tree is used to find the position of a new element which will be inserted into the doubly-linked list.

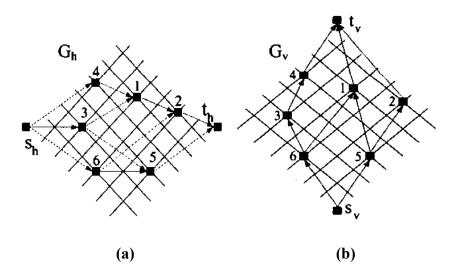

### 2.1.1.3 Corner Block List (CBL)

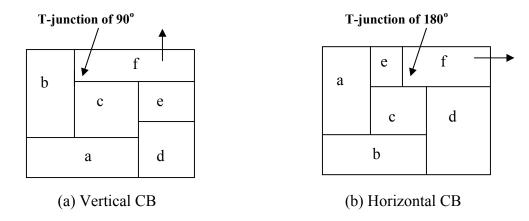

Corner Block List is proposed by Hong et al. [12] to represent mosaic floorplan. The corner block (CB) is the block at upper-right corner of the floorplan. The left and bottom bounding segments of CB form a T-junction.

Figure 2.8: Two different kinds of T-junction and orientation of the corner block (CB) "f".

The orientation of CB is defined by the orientation of its T-junction. The T-junction has only two types of orientations: T rotated by 90 degrees (Figure 2.8 (a)) and by 180 degrees (Figure 2.8 (b)) counterclockwise respectively. If T is rotated 90 degrees counterclockwise, the CB is vertically oriented, and its corresponding entry in list L is set by a "0". Otherwise, the CB is horizontally oriented, and the entry in list L is set by a "1". For example, in Figure 2.8 (a), the orientation of corner block "f" is vertical and is denoted by "0" whereas in Figure 2.8 (b), the orientation of "f" is horizontal and is denoted by "1".

Figure 2.9: Deletion/Insertion of vertically oriented corner block "f".

Figure 2.10: Deletion/Insertion of horizontally oriented corner block "f".

# **Corner Block Deletion**

The core idea of CBL representation is embodied in the corner block deletion operation. The way to delete a CB depends on its orientation. To delete a CB which is vertically oriented, its bottom segment is shifted to the top boundary of the floorplan and the attached T-junctions (if any) are pulled along with the segment. Figure 2.9 illustrates this operation. The corner block "f" is vertically oriented, thus, in order to delete this CB, the bottom segment of its room is shifted to the top boundary and the attached T-junction (in this case there is only one attached T-junction) is pulled along with the bottom segment. If the CB is horizontally oriented, the left segment of its room is shifted to the right boundary of the floorplan and the attached T-junctions (if any) are pulled along with the segment. Figure 2.10 illustrates the deletion of horizontally oriented CB "f".

#### **Corner Block Insertion**

Corner block deletion is the inverse of deletion. If the inserted CB is vertically oriented, the horizontal segment from the top of the floorplan covering a designated numbers of T-junctions is pushed down in order to create a room for the inserting CB. Figures 2.9 and 2.10 illustrate the insertion operation of corner block "f" starting from the floorplan shown in the right and obtaining the floorplan as shown in the left after insertion of CB "f". If the corner block is horizontally oriented, the operation is similar to those of vertical oriented but instead of pushing the top segment, the vertical segment at the right of the floorplan is pushed towards left.

It can be observed that the floorplan still remains mosaic after the deletion or insertion operation.

### Transformation from floorplan to CBL

CBL list is constructed by recursive deletion of CBs in the floorplan until there is no CB left in the floorplan. For each deletion of a CB, its name is recorded in list S, its orientation recorded in list L and the number of its attached T-junctions is recorded by the same number of successive "1"s ended by a "0" in a binary list  $T_i$  (Figure 2.11). At the end of deletions of all CBs, three lists are obtained: the block name list  $S = \{M_n, M_{n-1}, ..., M_1\}$ , the orientation list  $L = \{L_n, L_{n-1}, ..., L_2\}$  and the T-junction list  $T = \{T_n, T_{n-1}, ..., T_2\}$ . Then each list is reversed and all the items of the T-junction list are combined into a single binary vector T. The triple (S, L, T) is called a corner block list.

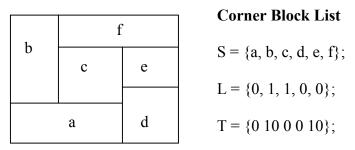

Figure 2.11: A CBL list and the resultant floorplan.

#### Transformation from CBL to floorplan

Construction of the floorplan from a CBL is the inverse process. Blocks are inserted in turn either from the right for vertical orientation or from the top for horizontal orientation, covering required number of T-junctions given by the corresponding entry in list *T*. Figure 2.11 illustrates the resultant floorplan of a corner block list.

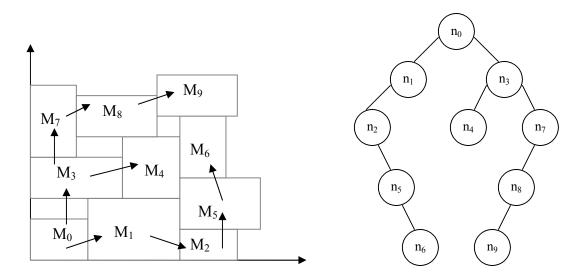

#### 2.1.1.4 B\*-Tree

We shall review the B\*-Tree representation in this section. Chang et al. [10] presented a binary tree based representation for a left and bottom compacted placement called B\*-Tree and showed its superior properties for operations. Given a placement P, we can construct a unique B\*-Tree in linear time by using a recursive procedure similar to the depth first search (DFS) algorithm. Each node  $n_i$  in a B\*-Tree denotes a module. The root of a B\*-Tree corresponds to the module on the bottom-left corner. The left child  $n_j$  of a node  $n_i$  denotes the module  $m_j$  that is the lowest adjacent module on the right-hand side of  $m_i$  i.e.

$$x_i = x_i + w_i \tag{2.2}$$

The right child  $n_k$  of a node  $n_i$  denotes the module  $m_k$  that is the lowest visible module above  $m_i$  and with the same x co-ordinate as  $m_i$  i.e.

$$x_k = x_i \tag{2.3}$$

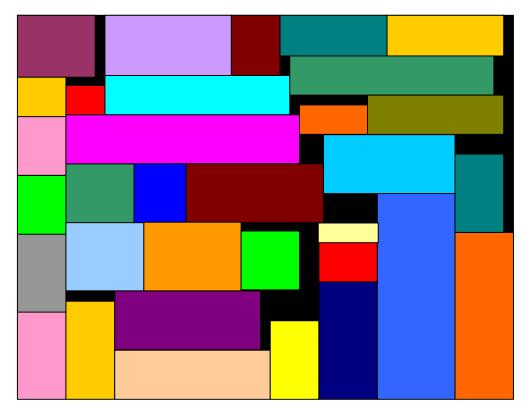

Figures 2.12 (a) and (b) show a placement and its corresponding B\*-Tree respectively. The root  $n_0$  of the B\*-Tree in Figure 2.12 (b) denotes that  $m_0$  is the module on the bottom-left corner of the placement. For node  $n_3$  in the B\*tree,  $n_3$  has a left child  $n_4$  which means that module  $m_4$  is the lowest adjacent module in the right-hand side of module  $m_3$  (i.e.  $x_4 = x_3 + w_3$ ).  $n_7$  is the right child of  $n_3$  since module  $m_7$  is the visible module over module  $m_3$  and the two modules have the same x co-ordinate ( $x_7 = x_3$ ).

Figure 2.12: (a) A placement (b) The corresponding B\*-Tree.

We shall show the procedure to get the placement from a B\*-Tree. We first define a permutation  $\pi$  which is the label sequence when we traverse the tree in depth-first search order. The first element in permutation  $\pi$  is the root of tree. We now introduce a contour structure which is used by Guo et al. in [6]. The contour structure is a doubly linked list of modules, which describes the contour line in the current compaction direction. Without the contour structure, the runtime for placing a new module is linear to the number of modules. By maintaining the contour structure, the y co-ordinate for a newly inserted

module can be computed in O(1) time. For each module  $m_i$ , let  $\psi(i)$  be the set of modules  $m_k$  with its order lower than  $m_i$  in permutation  $\pi$  and interval  $(x_k, x_k + w_k)$  overlaps interval  $(x_i, x_i + w_i)$  by a non-zero length. If  $\psi(i)$  is non-empty, we have

$$y_i = \max_{k \in \psi(i)} y_k + h_k \tag{2.4}$$

Otherwise

$$y_i = 0$$

(2.5)

The algorithm for finding the placement from a corresponding B\*-Tree is outlined in Figure 2.13 below. It uses a contour structure to reduce the run time for finding the y co-ordinate of a module while solving the equations (2.4) and (2.5).

```

Input: B*-Tree(\pi [0:n])

Output: Placement with position (x_i, y_i) for each module m_i

Begin

Set perm = 1

Set contour = NULL

Set current contour = 0

For code = 0 to n-1

if code = 0 then

Set current module = \pi [perm]

If current contour = 0 then

Set x[current module] = x[current contour] + w[current contour]

Else set x[curent module] = 0

End if

Set y[current module] = find max y (contour, current module)

Update contour (contour, current module)

Set current contour = current module

Set perm = perm + 1

Else set current contour = prev [current contour]

End if

End for

End.

```

Figure 2.13: Pseudo code of algorithm for finding the placement from a corresponding B\*-Tree.

We use a variable current contour to record the module where we want to insert

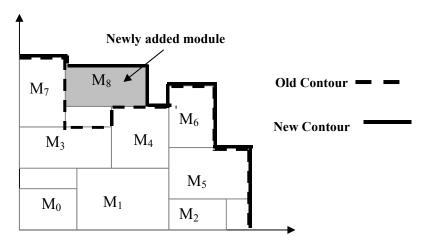

the next module in the contour. Figure 2.14 shows how  $find\_max\_y$  determines the y co-ordinate of current module and how  $update\_contour$  updates the contour structure when we add a new module  $m_8$  to the placement. The old contour is composed of modules  $m_7$ ,  $m_3$ ,  $m_4$ ,  $m_6$  and  $m_5$ . After  $m_8$  is placed, the new contour becomes  $m_7$ ,  $m_8$ ,  $m_4$ ,  $m_6$  and  $m_5$ . Note that we only need to search modules  $m_3$  and  $m_4$  to get  $m_8$ 's y co-ordinate  $y_8$  with the contour structure.

Figure 2.14: Adding a new module on top, we search the contour from left to right and update it with the top boundary of the new module.

We perturb a B\*-Tree (a feasible solution) to another B\*-Tree by using the following four operations.

- 1 **Op1**: Rotate a module.

- 2 **Op2**: Move a module to another place.

- 3 **Op3**: Swap two modules.

To cope with rotated modules while performing Op1, when inserting a deleted node into a B\*-Tree, we can perform the operation twice at each position to find a better solution, one for the original orientation, and the other for the rotated one. Op2 deletes and inserts a module. For the deleted node associated with a rectangular module, we simply delete the

node from the B\*-Tree. Op2 and Op3 need to apply the Insert and Delete operations for inserting and deleting a node to and from a B\*-Tree. We explain the two operations as below.

#### **Deletion**

There are three cases for the deletion operation.

- 1 Case 1: A leaf node.

- 2 Case 2: A node with one child.

- 3 Case 3: A node with two children.

In Case 1, we simply delete the target leaf node. In Case 2, we remove the target node and then place its only child at the position of the removed node. The tree update can be performed in O(1) time. In Case 3, we replace the target node  $n_t$  by either its right child or left child  $n_c$ . Then, we move a child of  $n_c$  to the original position of  $n_c$ . The process proceeds until the corresponding leaf node is handled. It is obvious that such a deletion operation requires O(h) time where h is the height of the B\*-Tree. Note that in Cases 2 and 3, the relative positions of the modules might be changed after the operation, and thus, we might need to reconstruct a corresponding placement for further processing.

#### Insertion

When adding a module, we may place it around some module. We define two types of positions as follows.

- 1 *Internal position:* A position between two nodes in a B\*-Tree.

- 2 External position: A position pointed by a NULL pointer.

Both these positions can be used for inserting a new node.

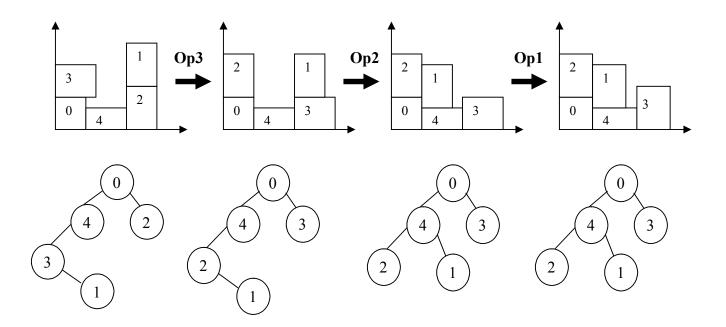

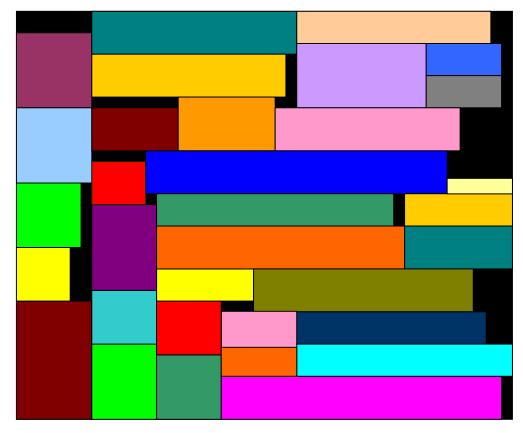

We explain the perturbation process with the help of an example in Figure 2.15

that illustrates all the three moves namely Op1, Op2 and Op3. We start with an initial placement and then perform the three operations in the order, i.e. swapping two modules, moving a module from one place to another and rotating a module successively. The corresponding B\*-Tree for each placement obtained after the perturbation process is given below it as shown in the Figure 2.15. Note that the rotation operation does not change the configuration of the B\*-Tree, only the block orientation changes in the same position in the placement.

Figure 2.15: Example showing the perturbations process on placement and its corresponding B\*-Tree.

We summarize the advantages of B\*-Tree as follows:

1. Based on ordered binary trees, B\*-Trees are very easy for implementation and can perform the respective primitive tree operations: *search*, *insertion* and *deletion* in only O(1), O(1) and O(n) times while existing representations for non-slicing floorplans need at least O(n) time for each of these operations where n is the number of modules.

- B\*-Tree is very flexible for handling the floorplanning problems with various types of modules (e.g. hard, pre-placed, soft, and rectilinear modules) directly and efficiently.

They can handle non-slicing structures.

- 3. The correspondence between an admissible placement (i.e. which is compacted and can neither move down nor move left) and its induced B\*-Tree is 1-to-1 (i.e. no redundancy). Further, the transformation between them takes only linear time.

- 4. B\*-Trees do not need to construct constraint graphs for area cost evaluation. The area cost after exchanging two modules can be recomputed incrementally on a B\*-Tree. Specifically, the modules ahead of the exchanged modules in the depth-first search (DFS) of a B\*-Tree remain unchanged. Therefore, we need to consider only the modules behind the exchanged ones for cost update.

- 5. The solution space is smaller, i.e.  $O(n!2^{2n-2}/n^{1.5})$ .

# 2.1.1.4 Comparison of different topological representations

The strength of each topological representation can be roughly evaluated by looking at the upper bound of their solution space. Usually, lower the bound, better a representation. Another way of evaluating the performance of the floorplan representation is by looking at its time complexity to transform a floorplan to a placement configuration. A good topological representation should be easily transformed into an actual placement. We summarize the strengths and weaknesses of various topological representations used more popularly in Table 2.1.

Table 2.1. Comparisons among the solution spaces and time complexity of various floorplan representations.

| Data Structure                 | Solution Space          | Time complexity |

|--------------------------------|-------------------------|-----------------|

| NPE                            | $O(n!2^{3n}/n^{1.5})$   | O(n)            |

| B*-Tree                        | $O(n!2^{2n-2}/n^{1.5})$ | O(n)            |

| O-Tree                         | $O(n!2^{2n-2}/n^{1.5})$ | O(n)            |

| Sequence Pair                  | $(n!)^2$                | $O(n^2)$        |

| Corner Block List (CBL)        | $O(n!2^{3m})$           | O(n)            |

| Transitive Closure Graph (TCG) | $(n!)^2$                | $O(n^2)$        |

| Bounded Sliceline Grid (BSG)   | $n!C(n^2,n)$            | $O(n^2)$        |

# 2.1.2 Block and Net Model

Floorplan layout shows the locations of blocks and terminals. Characteristics and arrangement of blocks as well as terminals need to be determined accurately. Net list is described by a net model which also explains how to estimate wirelength.

## 2.1.2.1 Block Model and Pin Assignment

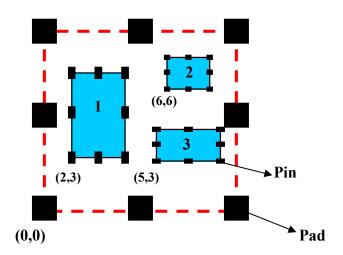

Origin for chip is at (0, 0). Blocks are specified by their lower left (x, y) co-ordinates (positive numbers), and height and width as shown in Figure 2.16.

Figure 2.16: Block and terminal locations in a chip.

- There are two types of terminals: terminals attached to the frame and terminals attached to the blocks. The first type is denoted as *pad* and the second as *pin* as shown in Figure 2.16.

- Each block has a set of pins at locations specified by (x, y) co-ordinates as depicted in Figure 2.17. The process of identifying a pin location is called pin assignment. Note that the pin locations are determined relative to the chip's origin and are termed as absolute co-ordinates  $(x_{abs}, y_{abs})$ . Pin locations specified relative to block's lower left co-ordinates (x, y) are termed as relative co-ordinates  $(x_{rel}, y_{rel})$ . Relationship between absolute and relative pin co-ordinates is given by the following equations.

$$x_{abs} = x + x_{rel} \tag{2.6}$$

and

$$y_{abs} = y + y_{rel}$$

(2.7)

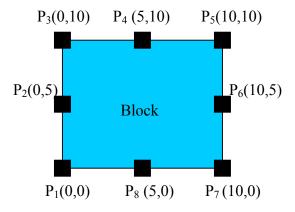

Figure 2.17: Pin locations on a block.

A block can be placed on a chip in any one of the four orientations as depicted in Figure 2.18. Note that the pins rotate too with the block rotation and their locations get modified accordingly.

Figure 2.18: Different block orientations and corresponding pin locations.

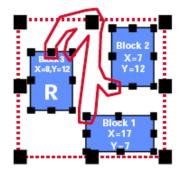

A net is just a set of two or more pins. Figure 2.19 shows an example of a five terminal net where two pins are from block 3, other two from blocks 1 and 2 respectively, and the fourth terminal is a pad. Exact wirelength of each net is not known until routing is done.

Figure 2.19: Example of a five terminal net.

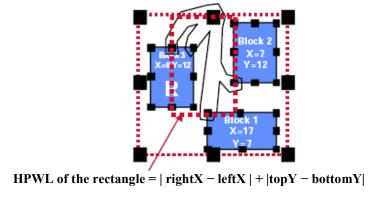

## 2.1.2.2 Half Perimeter Wirelength Estimation (HPWL) method

There are many methods available to estimate wirelength in a floorplan. However, HPWL is the most popular method for wirelength estimation.

We compute the *HPWL* of a net containing j terminals, each having location  $(x_j, y_j)$  as follows:

$$HPWL_x = max(x_i) - min(x_i)$$

(2.8)

$$HPWL_{y} = max(y_{j}) - min(y_{j})$$

(2.9)

$$HPWL = HPWL_x + HPWL_y \tag{2.10}$$

As shown in Figure 2.20, HPWL perimeter length metric for a two terminal net is determined by enclosing the net in a rectangle and computing the semi perimeter of the rectangle as below:

$$|rightX - leftX| + |topY - bottomY|$$

(2.11)

Figure 2.20: HPWL of a net.

We illustrate the determination of HPWL by an example of a five terminal net shown in Figure 2.19. The net consists of one chip pin i.e. pad and four other block pins. HPWL is determined by enclosing the net in a rectangle as shown dotted in Figure 2.21 below. The semi perimeter of the rectangle gives the HPWL of the net.

Figure 2.21: Example of determination of HPWL of a five terminal net.

Table 2.2 lists the (x, y) co-ordinates for all the pins in the net. We calculate the value of

$HPWL_x$  and  $HPWL_y$  from equations (2.8) and (2.9) respectively. Finally, we sum up  $HPWL_x$  and  $HPWL_y$  to yield the HPWL of the net.

Table 2.2. Pin locations of a five terminal net.

| Pin    | Pin                       |  |

|--------|---------------------------|--|

| number | co-ordinates              |  |

|        | $(\mathbf{x},\mathbf{y})$ |  |

| 1      | (2, 7)                    |  |

| 2      | (4, 7)                    |  |

| 3      | (5, 3)                    |  |

| 4      | (6, 5)                    |  |

| 5      | (5, 10)                   |  |

$$HPWL_x = max(x_i) - min(x_i) = 6 - 2 = 4$$

$$HPWL_v = max(y_i) - min(y_i) = 10 - 3 = 7$$

$$HPWL = HPWL_x + HPWL_y = 4 + 7 = 11$$

Total wirelength is given by the summation of lengths for all nets.

## 2.1.3 Cost Function

As the number of feasible solutions for a given instance of a floorplanning problem is very large, floorplanning algorithms use cost function as a measure that allows selecting superior floorplans with specific criteria. The possible criteria may be minimizing area, wirelength, delays, optimizing routing structure, power density and temperature of the chip or a combination of two or more of the above criteria. The specific criterion ensures greater reliability and performance of the circuits. A commonly used objective function is a weighted sum of area and wirelength:

$$Cost = \alpha \times A + \beta \times L \tag{2.12}$$

where A is the total area of the packing, L is the total wirelength, and  $\alpha$  and  $\beta$  are constants.

# 2.1.4 Floorplanning Algorithms

Several floorplanning algorithms exist that search over a solution space to determine the optimal floorplan solution. Floorplanning algorithms are classified into three classes:

- 1. **Constructive:** These algorithms attempt to build up a feasible solution by starting from a seed module; then, other modules are selected one at a time and added to the partial floorplan. Algorithms that fall under this category are as below.

- Cluster Growth

- Partitioning and Slicing

- Mathematical Programming

- Rectangular Dualization

- 2. **Knowledge-Based approach:** A knowledge expert system is implemented consisting of 3 basic elements.

- Knowledge base containing data describing the floorplan problem and its current state.

- Rules stating how to manipulate the data in the knowledge base in order to progress toward a solution.

- Inference engine controlling the application of the rules to the knowledge base.

- 3. **Iterative**: These algorithms employ techniques that start from an initial floorplan which then undergoes a series of perturbations until a feasible floorplan is obtained or no more improvements can be achieved. Algorithms that fall under this category are enumerated as below.

- Simulated Annealing

- Force Directed Interchange

- Genetic Algorithm

Some of the most popular algorithms used in research are discussed in the section below.

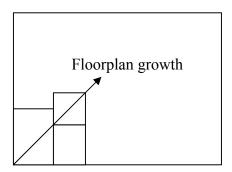

#### 2.1.4.1 Cluster Growth

Figure 2.22: Cluster growth floorplanning.

In this approach, the floorplan is constructed in a greedy fashion; one module at a time until each module is assigned to a location of the floorplan. A seed module is selected and placed into a corner of the floorplan (lower left corner). Then, the remaining modules are selected one at a time and added to the partial floorplan while trying to grow evenly on upper, diagonal, and right sides simultaneously (Figure 2.22), maintaining any stated aspect ratio constraint on the modules as well as the chip itself and optimizing other criteria. Criteria might include: minimization of wiring length, minimization of dead space or both.

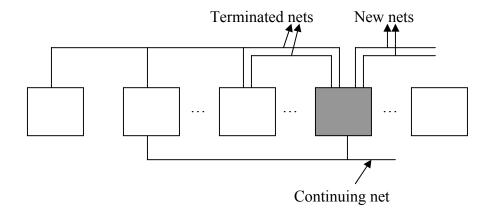

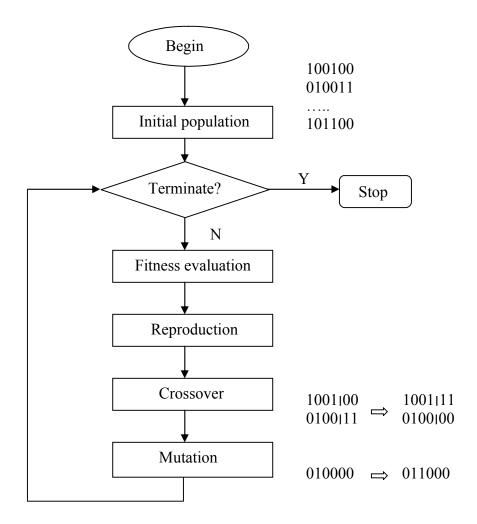

To determine the order in which the modules should be selected, the modules are initially organized into a linear order. Linear ordering algorithms order the given module netlist into a linear list so as to minimize the number of nets that will be cut by any vertical line drawn between any consecutive modules in the linear order. Linear ordering is one of