# A FRAMEWORK TO EXPLORE LOW-POWER ARCHITECTURE AND VARIABILITY-AWARE TIMING ESTIMATION OF FPGAS

LEE CHEE SING

(B.Eng.(Hons.), NUS)

#### A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2007

## Acknowledgements

My sincere thanks go to my advisor, Assistant Professor Ha Yajun. Without his help, this work would never have been possible. I have enjoyed a wonderful research experience under his supervision as he has gone beyond the duties of a supervisor to act as a mentor as well as a supporter.

I would also like to give special thanks to Professor Ben Chen (M. Eng./Ph.D. Program Coordinator), who provided impetus for the project, laid down the initial specifications and gave advices. Also, I would like to give a special acknowledgment to Professor Jonathan Rose and Vaughn Betz (creators of VPR tool) from the University of Toronto as well as Professor Jorge Stolfi (creator of affine arithmetic model) for their help in formulating the technical aspects of this work. Their contribution of ideas and software had greatly aided in the development of my research.

In addition, during this Master's program, I have gained wonderful experience working with different groups of people. Special thanks to Dr Heng Chun Huat for his valuable contribution to the project on the designing of the reconfigurable buffer for a low-power FPGA architecture. Thanks to Pu Yu and Kumaran, with who have allow me to gain more insight to VLSI circuit designing in this project too. Next, thanks to my hardware timing analysis project team (Zhang Wenjuan, Chen Xiaolei and Loke Wei Ting), who have worked closely with me on the research on timing estimation in FPGAs. Also, thanks to my fellow colleagues, Shakith, Teo Jenn Yue, Li Yanhui, Shefali, Zhang Wenjuan, Chen Xiaolei, Loke Wei Ting and Yu Heng for the various knowledge enriching sharing mini-seminars that are organized by our supervisor.

Last but not least, I would like to give special thanks to my family, friends and anyone who is not mentioned here but had helped in one way or another.

## Contents

| ${f Acknowledgements}$                       | ii   |

|----------------------------------------------|------|

| Table of Contents                            | vii  |

| Abstract                                     | viii |

| List of Figures                              | xi   |

| List of Tables                               | xiv  |

| List of Abbreviations                        | xv   |

| 1 Introduction                               | 1    |

| 1.1 FPGA Architecture                        | 2    |

| 1.2 Process variation                        | 3    |

| 1.2.1 Traditional corner-based timing method | 5    |

| 1.3 Problem definition                       | 5    |

| 1.3.1 Limitation of CAD tools                | 7    |

|   |     | 1.3.2  | Limitation of power reduction in interconnects | 7  |

|---|-----|--------|------------------------------------------------|----|

|   |     | 1.3.3  | Limitation of SSTA techniques                  | 9  |

|   | 1.4 | Propo  | sed research approach                          | 9  |

|   |     | 1.4.1  | Proposed CAD framework                         | 10 |

|   |     | 1.4.2  | Proposed low power FPGA architecture           | 11 |

|   |     | 1.4.3  | Proposed variability-aware timing estimation   | 11 |

|   | 1.5 | Contri | ibutions                                       | 12 |

|   | 1.6 | Thesis | organization                                   | 12 |

| 2 | Bac | kgroui | nd and Related Works                           | 14 |

|   | 2.1 | FPGA   | routing architecture                           | 14 |

|   | 2.2 | CAD    | flow for FPGA design                           | 18 |

|   | 2.3 | Existi | ng power estimation techniques                 | 23 |

|   | 2.4 | Existi | ng SSTA techniques                             | 23 |

| 3 | Mo  | deling | of the CAD Framework                           | 26 |

|   | 3.1 | Frame  | work design approach                           | 26 |

|   | 3.2 | Frame  | work implementation approach                   | 28 |

|   |     | 3.2.1  | Initializing the architecture template         | 28 |

|   |     | 3.2.2  | Editing the architecture template              | 33 |

|   |     | 3.2.3  | CAD tool interface                             | 34 |

|   | 3.3 | Routin | ng resource graph                              | 38 |

|   | 3.4                  | Placement and routing processes                     | 38 |

|---|----------------------|-----------------------------------------------------|----|

|   |                      | 3.4.1 Placement process                             | 40 |

|   |                      | 3.4.2 Routing process                               | 44 |

| 4 | Fra                  | mework Experimental Results and Analysis            | 50 |

|   | 4.1                  | Display of generic FPGA architecture                | 51 |

|   | 4.2                  | Display of edited FPGA architecture                 | 52 |

|   | 4.3                  | Display of architecture after placement and routing | 54 |

|   | 4.4                  | Placement and routing results                       | 55 |

| 5 | $\operatorname{Cas}$ | e Study 1: A Low-power FPGA Architecture            | 59 |

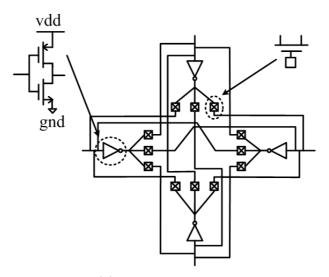

|   | 5.1                  | Conventional switch block                           | 59 |

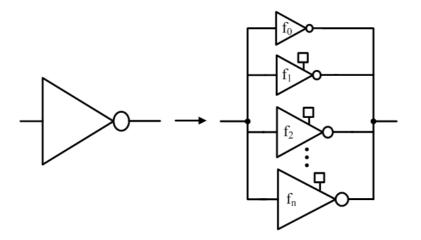

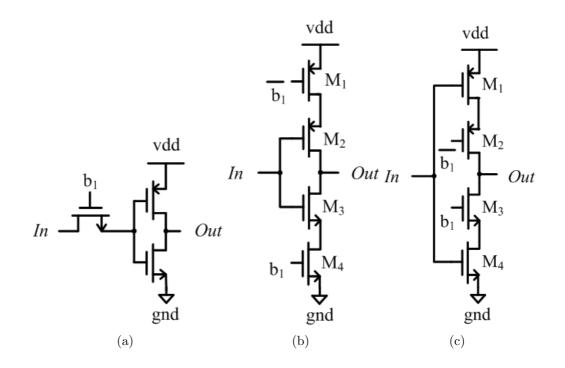

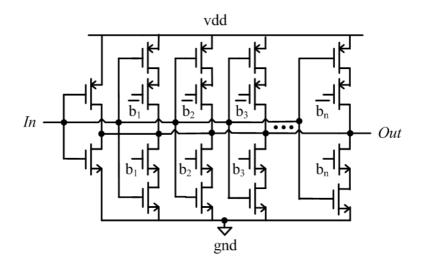

|   | 5.2                  | Reconfigurable switch block                         | 62 |

|   | 5.3                  | Proposed switch block and FPGA architecture         | 66 |

|   | 5.4                  | EDA support                                         | 66 |

|   | 5.5                  | Power analysis                                      | 69 |

| 6 | $\operatorname{Cas}$ | e Study 2: A Interval-based FPGA Timing Estimator   | 72 |

|   | 6.1                  | Deterministic timing estimation                     | 72 |

|   | 6.2                  | Modeling of process variation                       | 73 |

|   | 6.3                  | Introduction to interval arithmetic                 | 74 |

|   | 6.4                  | Introduction to affine arithmetic                   | 75 |

|   | 6.5                  | Interval-based timing estimation                    | 77 |

|   |                      |                                                     |    |

|        | 6.5.1   | Modeling of Variation                | •••   | 78 |

|--------|---------|--------------------------------------|-------|----|

|        | 6.5.2   | Comparison with Statistical modeling | · • • | 80 |

|        | 6.5.3   | Complexity                           | •••   | 81 |

| 6.6    | Desig   | gn methodology                       | •••   | 82 |

| 6.7    | Timin   | ng delay analysis                    | •••   | 84 |

| 7 Coi  | nclusio | ons and Future Work                  |       | 91 |

| 7.1    | Concl   | lusion                               | · · · | 91 |

| 7.2    | Futur   | re work                              | · • • | 93 |

| Biblio | graphy  | У                                    |       | 95 |

### Abstract

This thesis is written in 3 main sections. First, a new CAD framework is designed. As semiconductor technology gets scaled down, more transistors will be allowed to be fabricated onto a single chip. There is a need for a new tool to handle the building of larger FPGAs. Heterogeneity is brought into the development phase to improve FPGAs' qualities. We propose a framework to allow researchers to design arbitrary architectures with the help of a graphical user interface. It enables the initialization of essential circuit parameters to obtain a basic architectural layout. Editing of the initial design can be performed to allow the creation of an arbitrary architectural design. It is built in with placement and routing capabilities to test the feasibility of the newly designed architecture. Different arbitrary architectures are being tested using a set of MCNC benchmarks. Furthermore, porting of the designed architecture's resource graph to the current state-of-art VPR for more complete testing is made available.

Second, we use the developed framework to investigate an alternative approach to minimize the short-circuit power of FPGA global interconnects without the luxury of dual supply. A reconfigurable buffer, with programmable driving strength, is designed and integrated into the FPGA switch block. EDA support is built into our framework to test this new architecture. With our methodology, interconnect buffers can choose the right driving strength based on the exact wire load after detailed routing. Our simulation results show that, by applying larger driving strength along the critical paths and relaxing the driving strength along the non-critical paths, the proposed FPGA architecture can reduce the overall dynamic power by 6.10% - 10.05%, compared with the conventional FPGA architecture. Our approach is complementary to the existing dual supply voltage solution. Both techniques can be combined to further reduce the overall dynamic power consumption.

Third, we use a developed framework VPR to explore a fast and accurate intervalbased timing estimator for variability-aware FPGA physical synthesis tools. As process variations of deep sub-micron technologies have created significant timing uncertainty, this generates the need for a new generation of variability-aware physical synthesis tools for FPGAs. Ideally, variability-aware tools should be able to perform both timing variability estimation during the synthesis and timing variability analysis after the synthesis. SSTA methods are being developed to perform the timing variability analysis after the synthesis, but they are computationally expensive and not fast enough to provide the timing variability estimation during the synthesis. Hence, we propose a fast and accurate interval-based method for the timing variability estimation. This method uses correlation-aware affine intervals instead of probability density distributions to model timing uncertainties. Compared to Monte Carlo simulations, we estimate the mean of timing variation within the accuracy of 1%, the average looseness range of about 22.6% and 4.5% for the Uniform and Gaussian distribution respectively and a 1000X simulation speed-up. This work can be easily extended to ASIC flows. Furthermore, using our developed framework, this case study can be extended to non-regular architectures.

## List of Figures

| 1.1 | Corner-based timing analysis: 2n corners for n parameters | 6  |

|-----|-----------------------------------------------------------|----|

| 2.1 | Types of FPGA architecture                                | 17 |

| 2.2 | An island-style FPGA                                      | 18 |

| 2.3 | Typical FPGA CAD flow                                     | 22 |

| 2.4 | Complexity problem in path-based approach                 | 25 |

| 3.1 | Interface for initialization                              | 29 |

| 3.2 | Logic block pins location                                 | 30 |

| 3.3 | Types of connection block connectivity                    | 31 |

| 3.4 | Types of switch block connectivity                        | 32 |

| 3.5 | FPGA routing architecture template                        | 33 |

| 3.6 | Edit CLB's pin orientation                                | 35 |

| 3.7 | Edit track information                                    | 35 |

| 3.8 | Edit connection box                                       | 36 |

| 3.9 | Edit switch box connectivity                              | 36 |

|                                                                               | 37                                                                                    |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| a directed graph                                                              | 39                                                                                    |

| ed-annealing algorithm used in the place-                                     |                                                                                       |

|                                                                               | 41                                                                                    |

| nodel $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 42                                                                                    |

| blocks                                                                        | 43                                                                                    |

|                                                                               | 44                                                                                    |

|                                                                               | 45                                                                                    |

| der negotiated congestion algorithm used                                      |                                                                                       |

|                                                                               | 47                                                                                    |

|                                                                               | 49                                                                                    |

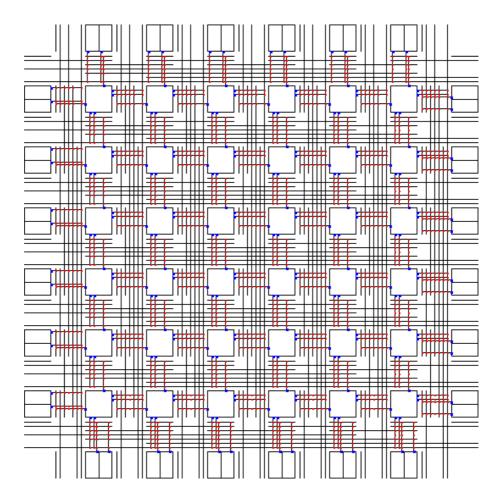

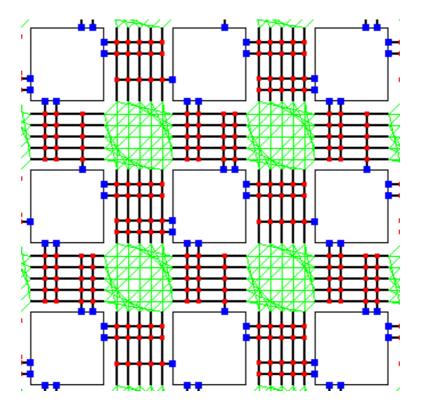

| of FPGA routing architecture                                                  | 51                                                                                    |

| ple of FPGA routing architecture                                              | 52                                                                                    |

|                                                                               |                                                                                       |

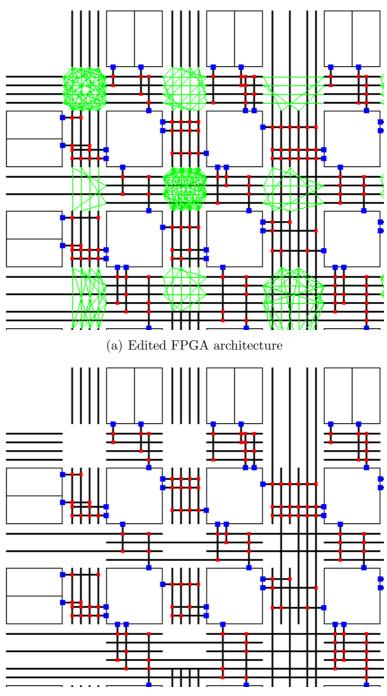

| re with heterogeneity                                                         | 53                                                                                    |

| re with heterogeneity                                                         | 53<br>54                                                                              |

|                                                                               |                                                                                       |

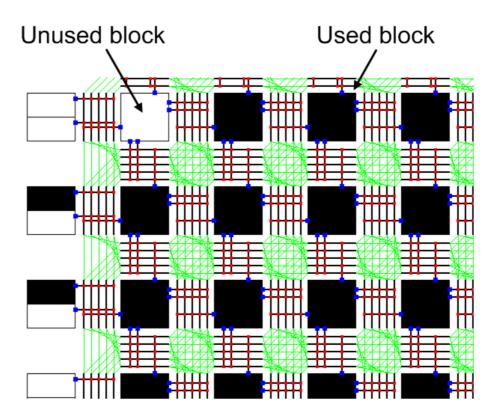

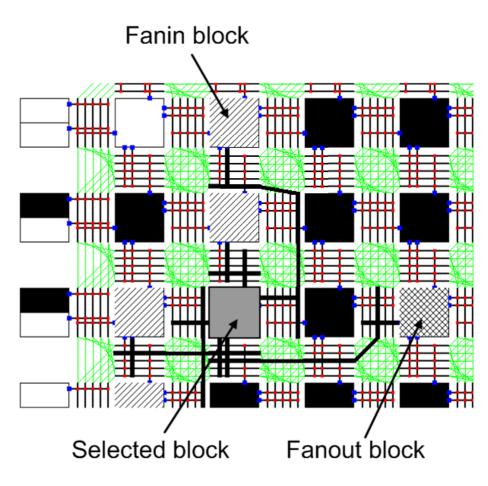

| nent and routing                                                              | 54                                                                                    |

| nent and routing                                                              | 54<br>55                                                                              |

| ment and routing                                                              | 54<br>55<br>57                                                                        |

| nent and routing                                                              | 54<br>55<br>57<br>61                                                                  |

|                                                                               | ed-annealing algorithm used in the place-         nodel         blocks         blocks |

| 5.5  | Equivalent circuits of configurable buffer                                                 | 65 |

|------|--------------------------------------------------------------------------------------------|----|

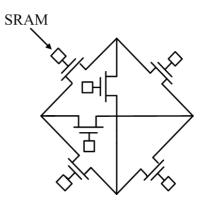

| 5.6  | Switch point integrated with reconfigurable buffer $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 67 |

| 5.7  | EDA flow for propose FPGA routing architecture                                             | 68 |

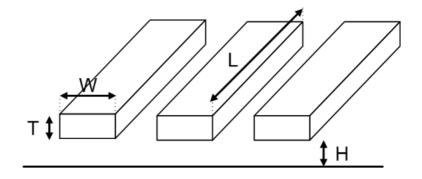

| 6.1  | Geometry of wiring                                                                         | 74 |

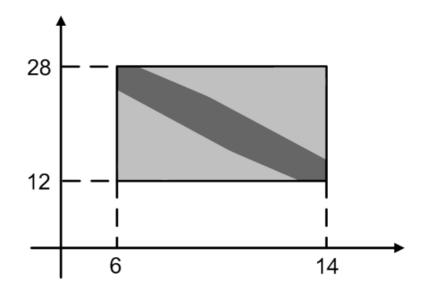

| 6.2  | Joint range of two partially dependent quantities in Affine Arithmetic                     | 78 |

| 6.3  | The grid-based model to model correlations                                                 | 80 |

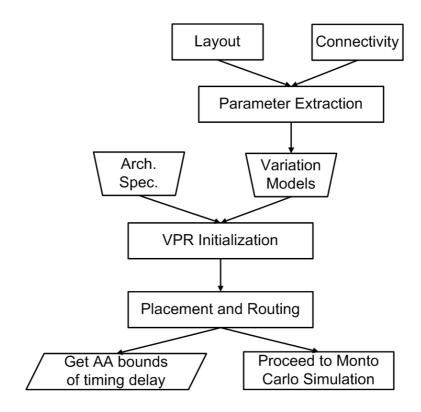

| 6.4  | Design flow chart                                                                          | 83 |

| 6.5  | Variation initialization interface                                                         | 84 |

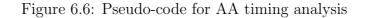

| 6.6  | Pseudo-code for AA timing analysis                                                         | 85 |

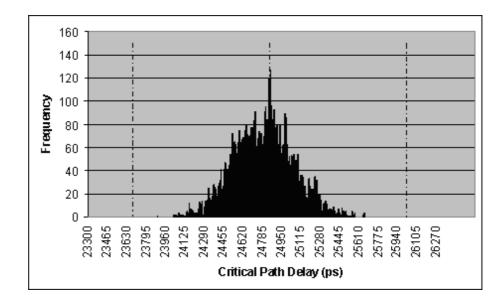

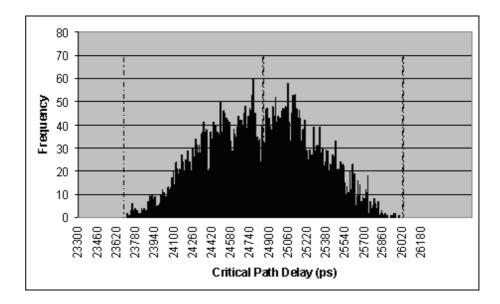

| 6.7  | MC initialization interface                                                                | 85 |

| 6.8  | Frequency distribution of des using Gaussian distribution and single                       |    |

|      | stream for 10000 iterations (MC) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 87 |

| 6.9  | Frequency distribution of des using Uniform distribution and single                        |    |

|      | stream for 10000 iterations (MC) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 87 |

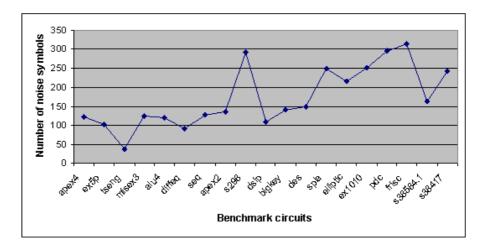

| 6.10 | Max no. of noise symbols on an AA variable to illustrate that com-                         |    |

|      | plexity does not grow with circuit's size                                                  | 88 |

## List of Tables

| 1.1 | CMOS technology roadmap                                                     | 4  |

|-----|-----------------------------------------------------------------------------|----|

| 3.1 | Menu bar Options and descriptions                                           | 37 |

| 3.2 | Temperature update schedule                                                 | 41 |

| 4.1 | Minimum channel widths required to place and route 20 large bench-          |    |

|     | mark circuits                                                               | 56 |

| 4.2 | Minimum channel widths required to place and route 20 large bench-          |    |

|     | mark circuits using modified architecture                                   | 58 |

| 5.1 | New FPGA architecture energy consumption for 20 large benchmark             |    |

|     | circuits                                                                    | 70 |

| 6.1 | Parameter and its variation                                                 | 86 |

| 6.2 | Comparison of bounds of critical path (ns) - Uniform $\ldots \ldots \ldots$ | 89 |

| 6.3 | Comparison of bounds of critical path (ns) - Gaussian                       | 89 |

## List of Abbreviations

| AA   | Affine Arithmetic                       |

|------|-----------------------------------------|

| ASIC | Application-Specific Integrated Circuit |

| CAD  | Computer-Aided Design                   |

| CLB  | Configurable Logic Block                |

| CMOS | Complementary MetalOxideSemiconductor   |

| DLL  | Delay-Lock Loop                         |

| EDA  | Electronic Design Automation            |

| FPGA | Field-Programmable Gate Array           |

| GUI  | Graphical User Interface                |

| HDL  | Hardware Description Language           |

| I/O  | Input/Output                            |

| IA   | Interval Arithmetic                     |

| IOB  | Input/Output Block                      |

|      |                                         |

LE Logic Element

- **LUT** Look-Up Tables

- MPGA Mask-Programmable Gate Array

- MCNC Microelectronics Corporation of North Carolina

- PLD Programmable Logic Device

- **RRG** Routing Resource Graph

- **RTL** Register Transfer Level

- **STA** Static Timing Analysis

- SSTA Statistical Static Timing Analysis

- SOC System-On-a-Chip

- **VPR** Versatile Placement and Routing tool for FPGAs

- **VLSI** Very Large Scale Integration

- **TTL** Transistor-Transistor Logic

### Chapter 1

## Introduction

For the past few decades, microelectronics has been the technology in demand for the development of both the hardware and software systems. With the continuous increase in the level of integration of electronic devices, this form of technology improves tremendously. The trend towards higher integration brings about the evolution of more sophisticated and faster systems to meet the increasing market demand. As a result, the final products become better and cheaper.

Field programmable gate arrays (FPGAs) are first introduced during the mid-1980s. At that time, FPGAs are only made up of transistor-transistor logic (TTL) equivalent logic gates. With enhancements in the very-large-scale integration (VLSI) processing technology, FPGAs have evolved to system-on-a-chips (SOC) with millions of logic gates being packed together. Ever since, FPGA becomes a widely adopted design at the heart of most electronic systems for its wide abundance of resources and efficiency.

Moreover, with the discovering of new processing techniques over the recent years, the semiconductor technology has been seen scaling down as predicted by the Moore's Law. This results in more transistors to be able to get fabricated onto a single chip; and opens up more opportunities for researches to build larger and sophisticated FP-GAs than ever. Furthermore, new features are continuously being discovered and added into these FPGAs to cater for different design needs. For example, power efficient FPGAs are being developed for portable electronic devices for which low power consumption is a key requirement. As of today, we have seen numerous researches with innovative ideas evolving and this has led to the development of FPGA architectures of higher qualities and efficiencies.

#### 1.1 FPGA Architecture

An FPGA architecture is made up of several millions of logic gates fused together. In order to develop an optimized and efficient architecture is not an easy task. However, a good approach to start off is to first implement an architecture instance in all the selected classes of FPGAs and evaluates their performances. The architecture displaying the best combination of placement and routing results in terms of timing, area or power is deemed to be the best. Previous researches [1–5] have shown that a proper design of the routing architecture does play a major role in determining its quality. The description of the architecture plays an important role in determining the overall efficiency of the FPGA too.

Different approaches in describing an FPGA architecture have been adopted in many of the existing frameworks. One brute force method to describe the routing architecture is by manually specifying all the interconnections between the logic blocks through the use of a routing resource graph (RRG). This enables researches to have the flexibility in describing different forms of architectures. However, this method is not practical as a typical FPGA RRG's size can go up to megabytes or even larger. Eventually, due to its inefficiency and impracticability, such a low level and detailed specification is not applied.

A more practical approach is to first design a basic tile with its interconnections manually and uses a program to automatically replicate that basic structure into an array to form a complete architecture. This technique is applied by George in [5] to design low energy FPGA architectures. Not only it is time consuming, this method also shows limitation in terms of flexibility as the whole architecture is a replica of the basic tile.

#### 1.2 Process variation

With the continuous scaling of technology into the deep sub-micron regions, the amount of variability increases significantly in the process parameters that have to be accounted for. For example, more than 35% variations on the gate length are cited for 90nm processes and they are even larger for 65 nm processes [6]. Also, as shown

in Table 1.1 [7], the magnitude of the parameter variations does not scale down as fast as the nominal values. As such, the parameter variation, as a percentage of the nominal value, gets larger with decreasing technology.

| Parameters     | Nominal Values |      |      |      | $3\sigma$ Values |      |      |      |      |      |

|----------------|----------------|------|------|------|------------------|------|------|------|------|------|

| Years          | 1997           | 1999 | 2002 | 2005 | 2006             | 1997 | 1999 | 2002 | 2005 | 2006 |

| Leff [nm]      | 250            | 180  | 130  | 100  | 70               | 80   | 60   | 50   | 40   | 33   |

| Tox [nm]       | 5              | 4.5  | 4    | 3.5  | 3                | 0.4  | 0.36 | 0.39 | 0.42 | 0.48 |

| Vdd [V]        | 2.5            | 1.8  | 1.5  | 1.2  | 0.9              | 0.25 | 0.18 | 0.15 | 0.12 | 0.09 |

| Vth [mV]       | 500            | 450  | 400  | 350  | 300              | 50   | 45   | 40   | 40   | 40   |

| $W$ [ $\mu$ u] | 0.8            | 0.55 | 0.5  | 0.4  | 0.3              | 0.2  | 0.17 | 0.14 | 0.12 | 0.1  |

| $H \ [\mu m]$  | 1.2            | 1    | 0.9  | 0.8  | 0.7              | 0.3  | 0.3  | 0.27 | 0.27 | 0.25 |

| $p [m\Omega]$  | 45             | 50   | 55   | 60   | 75               | 10   | 12   | 15   | 19   | 25   |

Table 1.1: CMOS technology roadmap

Process variations [8,9] can be classified as inter-die variations, which affect the entire chip, and intra-die variations, which are the results of layout-specific variations. These variations are normally accompanied with a complex spatial or temporal correlation structure. They create significant timing uncertainty and yield degradation. This growing problem brings about the need to build the next generation variabilityaware electronic design automation (EDA) tools.

The above observation is especially important for FPGA vendors because they are almost always the first to use the most advanced technologies. For example, Xilinx is the first in the whole semiconductor industry to fabricate their Virtex-2 FPGAs in 130nm, Virtex-4 in 90 nm, and Virtex-5 in 65nm processes. As the process shrinks, variations in effective channel length, threshold voltage and gate oxide thickness become more prominent. This will greatly influence the timing performance of FPGAs. Hence, the FPGA physical synthesis tools need to consider the impact of process variations on timing in order to help guide timing-driven optimizations.

#### **1.2.1** Traditional corner-based timing method

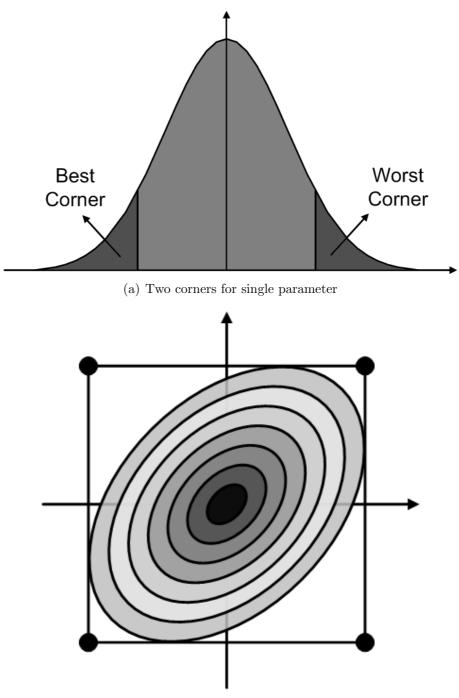

Process variations and their correlations have been studied over the years. Their importance accelerates as the technology continues to scale down. Traditionally, parameter variations and correlations are handled using the corner-based deterministic static timing analysis as shown in Figure 1.1 [7]. From Figure 1.1(a), two corners known as the worst case and best case are individually timed for a single parameter variation. However, if the two parameter variations are of significance, four corners are to be timed individually as shown in Figure 1.1(b). Hence, as the parameter variations increases, an exponential number of corners need to examine individually. This makes the approach to be cumbersome and inefficient. In addition, the corner-based approach only provides information on whether the circuit is able to function at the extreme corners and not on the quantitative yield information which is more critical.

#### **1.3** Problem definition

Although there had been existing works which are efficient in describing FPGA architectures, reducing power usage and handling of process variations in FPGAs, there are still many problems that need to be solved to improve them.

(b) Four corners for two parameters

Figure 1.1: Corner-based timing analysis: 2n corners for n parameters

#### 1.3.1 Limitation of CAD tools

Currently, there have been several promising computer-aided design (CAD) tools [1– 5] capable of describing routing architecture with enhanced design complexity, better cost-saving or even improved efficiency. For example, Emerald [1] makes use of the *WireC* schematics to describe its routing architecture. This method requires inputs like routing architecture description, logic block architecture description and architecture specific metrics in order to provide the basic features needed in placement and routing tools. In another example, the Versatile Placement and Routing tool (VPR) [2,3] makes use of an FPGA architecture description language to describe its routing architecture. An "architecture generator" is used to convert this specification into a detailed and complete architecture for future work on optimization and visualization. However, both the Emerald and VPR CAD tools share a common limitation. Their architecture description techniques limit the range of architectures only to a selected class of templates. This limitation prevents the design of heterogeneous architectures.

#### **1.3.2** Limitation of power reduction in interconnects

Among the routing resources in an FPGA architecture, switch buffers are the most important components that determine its performance. The buffer not only behaves as an intermediate repeater to regenerate the signal, it also breaks a long RC network to minimize the interconnect delay. Therefore, the buffer chosen must be large enough to drive its downstream circuits. While buffers can be fully customized for various applications in application specific integrated circuits (ASIC) design, FPGAs do not have such freedom because they are pre-fabricated. Targeting at driving the worst case of load normally results in having unnecessarily large buffers within a FPGA chip. These oversized buffers can cause undesirable problems.

First, due to the non-zero rising and falling time of the input signal, a larger buffer will result in larger peak and average short-circuit currents during the transition period, hence resulting in an increase in the short circuit power. From the simulations, it can be shown that the short-circuit power accounts for roughly 10% of the total dynamic power, depending on the actual synthesized circuits. As a result, the dynamic power, which consists of both the switching power and the short-circuit power, is increased.

Second, a larger buffer creates more ground-bounce noise. In custom ASIC design, large transient current is avoided by using the minimum required buffers. This will minimize the ground bounce noise introduced by Ldi/dt, where L is the inductance associated with the package pins, bonding wires and on-chip metal lines for power routing. Ground bounce noise reduces the available noise margin for the digital circuits [10]. In addition, it also deteriorates the performance of the sensitive analog circuit on the chip, such as delay-lock loop (DLL), which is crucial for the functioning of large digital circuits. If an oversized buffer is used within the FPGAs, large transient current and thus large ground bounce noise are inevitable.

#### **1.3.3** Limitation of SSTA techniques

In relation to process variation, there has been several works [11–21] considering the impact of variations on circuit performances using statistical static timing analysis (SSTA). These approaches are classified into various categories such as block-based, path-based, incremental, etc. In [12, 14], the authors propose techniques to get the bounds of the delay distributions instead of calculating the exact distributions using path-based or block-based analysis techniques. In [16], the proposed approach does an estimation based on a generic path analysis rather than evaluating every path statistically. However, many of these researchers have advocated complicated SSTA techniques, primarily due to handling correlation and path reconvergence during the MAX operation fundamental to static timing analysis (STA). This leads to undesirable high computation complexity and large CPU overhead. Furthermore, most of these statistical analysis techniques typically assume the circuit parameters as independent random variables with a Gaussian distribution. This is not true in most cases.

#### 1.4 Proposed research approach

From the problem definitions above, we propose three approaches to solve each of them individually. First, a CAD framework capable of designing heterogeneous architecture is developed. Second, a FPGA architecture with reconfigurable buffer is designed to allow different operating buffer modes to save power. Third, a novel idea is proposed to handle process variations while considering spatial correlation and path reconvergence.

#### 1.4.1 Proposed CAD framework

In order to facilitate the designing of heterogeneous FPGA routing architecture, a graphical user interface (GUI) framework is proposed. In this framework, an interface is built to allow users to input essential parameters to generate a generic routing architecture. This removes the hassle to come out with a descriptive language to implement the architecture. After which, using the drawn architecture, users can click on any components and do editing to them. With this flexibility, users can design any kind of routing architectures that they desired. This eliminates any forms of restriction or constrain that are encountered in the existing CAD tools.

After the design is finalized, a RRG is generated. This RRG is a detailed internal representation of the routing architecture which specifies how each component in the architecture is connected with each other. Placement and routing algorithms are implemented to test the feasibility of the design architecture. The placer does the placing of the logic blocks in the physical position of the FPGA while the router finds the best path for all the nets.

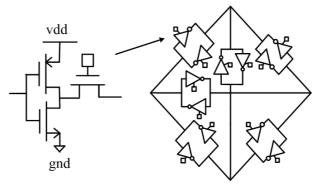

#### 1.4.2 Proposed low power FPGA architecture

In order to provide a way to minimize the transient current by using only the minimum required driving strength, the use of a reconfigurable buffer is proposed. The concept behind our methodology is that, a large buffer can be physically considered as a combination of smaller buffer cells. The different modes of driving strength can be obtained through the binary combinations of the small buffer cells. We integrate this reconfigurable buffer into the FPGA switch blocks. In this way, we are capable of choosing the right driving strength for each wire based on their exact load after detailed routing. By using larger driving strength along the critical paths and relaxing the driving strength along the non-critical paths, the overall dynamic power consumption and transient current can be reduced.

#### 1.4.3 Proposed variability-aware timing estimation

In order to perform a fast and accurate timing estimation for the variabilityaware FPGA physical synthesis tools, an interval-based method is proposed. Two models are initially suggested: interval arithmetic (IA) and affine arithmetic (AA). IA [22] is a surprisingly long-lived branch of range analysis. It makes use of intervals to represent uncertainties in variables. However, it does not consider correlation and dependency between the variables. On the other hand, AA [23], which is a novel refinement of interval analysis, can be applied to the problem of circuit timing analysis [24,25] and can preserve correlations among variables. With the motivation in mind, we employ AA to propose a new interval-based timing estimation technique for FPGAs with correlation and dependencies among process parameters being accounted for. Furthermore, AA is chosen for its low complexity and distribution independent property, in contrast to the existing SSTA methods.

#### 1.5 Contributions

The work done for this thesis makes the following contributions:

- 1. Designed a CAD framework capable of producing an arbitrary FPGA routing architecture.

- 2. Incorporated placement and routing algorithms to test the framework.

- 3. Designed a power efficient FPGA architecture.

- 4. Designed a fast interval-based timing estimator for FPGAs.

#### 1.6 Thesis organization

The remainder of this thesis is organized as follows. The next chapter presents some general background on the research topic and related works. Chapter 3 describes the modeling of the proposed framework. Chapter 4 shows a design of an arbitrary architecture and some generated results. Chapter 5 discusses a case study to investigate a low-power FPGA switch block with reconfigurable buffers using our framework. Chapter 6 presents another case study to investigate the use of the affine model to handle process variations using VPR. Finally, Chapter 7 presents the conclusions and suggestions for future work.

### Chapter 2

## **Background and Related Works**

This chapter begins with a general overview of the different types of the FPGA routing architectures used in the academic research as well as in the industry. Next, a description of a typical CAD flow for a FPGA design is illustrated. Finally, literature reviews on the existing power estimation and SSTA techniques are presented.

#### 2.1 FPGA routing architecture

There is a wide variety of FPGA architectures developed by various vendors. These vendors include Actel, Altera, QuickLogic, Xilinx, and so on. Although the exact structure of these FPGAs varies from vendor to vendor, all FPGAs consist of three fundamental components needed to define a typical architecture:

1. Logic blocks capable of implementing multiple logic functions.

- 2. Logic blocks which support wide range of I/O signaling standard.

- 3. Routing resources used to realize all interconnections among the blocks.

The complexity of the logic block is classified into two types: coarse-grained and fine-grained. A coarse-grained logic block contains substantial logic structures, lookup tables (LUTs), flip-flops or programmable logic device (PLD) modules. As the complexity of the logic block increases, more functions can be implemented. The 4-input LUT is most widely employed in coarse-grained architectures [26]. In finegrained architecture, it is made up of a large number of relatively simple logic blocks, which consists of a few basic gates, multiplexes or transistors with programmable interconnect resources. In terms of logic block and routing resource layout, FPGAs can be further classified into four main architecture groups [26].

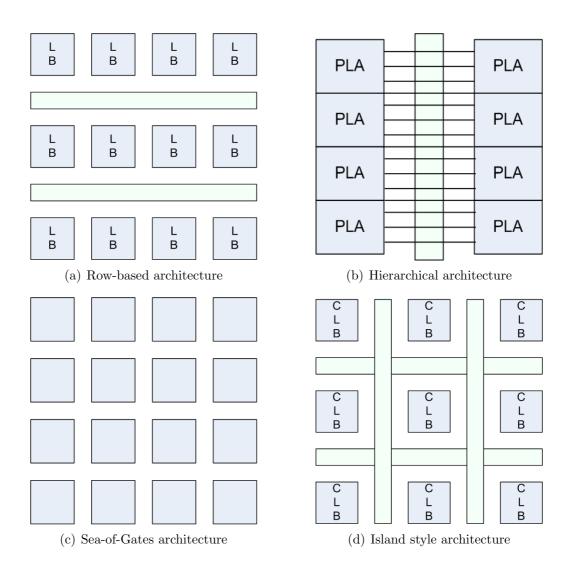

- **Row-based** In row-based architecture, logic blocks are arranged in rows with its routing resources separated by routing switches. The routing resources consist of mainly horizontal wire segments of various lengths and a few vertical wire segments which are used for routing between rows. (See Figure 2.1(a))

- **Hierarchical** In hierarchical architecture, logic blocks and routing resources are displayed in a hierarchical mode. A two-dimensional array of programmable logic blocks is used to implement the multi-level logic functions. Intra-level and inter-level interconnections are used in this architecture. (See Figure 2.1(b)).

Sea-of-Gates In sea-of-gates architecture, fine-grained logic blocks are organized

in a symmetrical array manner. Routing resources are overlaid on top of these blocks. This structure resembles the architecture used in the mask programmable gate arrays (MPGAs). (See Figure 2.1(c))

Island-Style In island-style architecture, logic blocks, also known as configurable logic blocks (CLBs), are arranged in a symmetrical array with the Input/Output Blocks (IOBs) on the periphery of the chip. Routing tracks have Manhattan geometry, that is, they are either horizontal or vertical of various lengths. The CLBs are typically coarse-grained and are separated by programmable routing switches. (See Figure 2.1(d)).

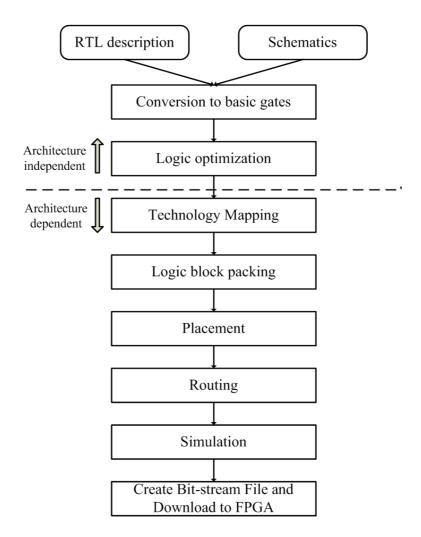

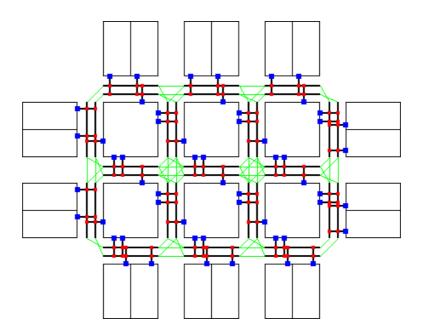

Figure 2.2 shows the details of a typical island-style FPGA architecture which consists of three main routing resources: wire segments, connection block and switch box. The wire segments or routing tracks [27] are the paths taken by a signal transmitted from one source to its destinations (sinks). The length of a track may vary across the architecture and is determined by the number of CLBs it spans. A connection block connects a pin of a logic block to a specific track in the channel. The switch box [28] is a switch matrix that connects the tracks in a channel to other tracks in the adjacent channels. The connection blocks' and switch boxes' patterns may vary across the architecture.

Figure 2.1: Types of FPGA architecture

Figure 2.2: An island-style FPGA

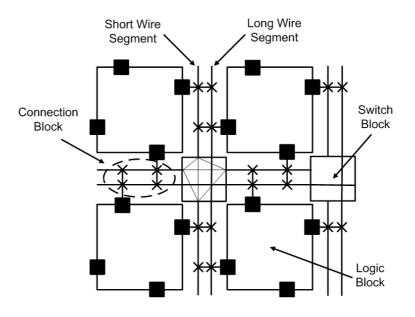

#### 2.2 CAD flow for FPGA design

To implement an FPGA architectural design, a series of steps is needed with each step assisted by a CAD tool. A typical design procedure employed by most commercial FPGA tools is shown in Figure 2.3.

**Design Entry** The description of a logic circuit can be specified using a register transfer level (RTL) description. A hardware description language (HDL) such as VHDL or Verilog can also be used. Alternatively, the circuit can be described using schematic drawing with the help of a state machine language or a schematic tool.

- Synthesis & Optimization Logic synthesis does the generation of a detailed representation of the circuit with all the features required for fabrication. Optimization does the enhancement of the overall quality of the circuit in terms of performance, area and ease of testing. During synthesis, the target design, which is in terms of behavioral or logical description at the design entry level, is converted into a netlist of gates. If a schematic design is available, the logic design is already created. Using the logic design, an optimizer removes the redundant logic gates and simplifies the logic operations to minimize the set of gates used, while maintaining its functionality. This stage of the design phase is known to be technology independent as the type of elements used in the final circuit is not considered here.

- **Technology Mapping** Once the design is generated, a technology-dependent mapping [29] tool is used to restructure the basic logic gates into k-LUT-sized groups, where k is based on the specific FPGA architecture on which the design is to be implemented. Conventional methods of technology mapping involve the use of standard cell library with pre-defined circuits. However, these methods require a large number of library cells. Hence, new algorithms for mapping are developed with the following criterion:

- 1. LUT number minimization

- 2. Routability

- 3. Delay Minimization

Logic Block Packing In clustered FPGA architectures, a logic block is normally made up of one or more logic elements (LE) [3]. A LE usually includes a k-LUT and a flip-flop. State-of-art architecture usually uses a 4-input LUT. The main objectives of the packing process are to combine the LUTs and latches into LEs and group the LEs into CLBs. This packing aims to maximize the number of LEs per CLB so as to minimize the number of signal connections between the CLBs [3].

VPack proposed by Betz and Rose [30], is one of the best known packing tools for clustered-based FPGAs. VPack first packs a flip flop and a LUT together into a LE using a matching based method. These LEs are then packed in a greedy manner into logic clusters by filling each cluster to its optimal capacity. In this way, the number of used inputs to each cluster is minimized.

Placement When the circuit has been reduced to a netlist which describes the connectivity between the logic blocks, a placement tool [31] is used to determine the physical location of these blocks within the target FPGA according to its physical view. During placement, parameters like overall layout size, total wire length and delay are optimized. Several placement techniques are available in the existing market. Wire-driven placement is placement which aims to optimize the routing cost. Timing-driven placement [32] is applied to reduce the length of critical path to meet timing constraints. Routability-driven placement [33] balances the wire density across the architecture. Most commercially available placement tools uses timing-driven placement as it is more efficient in improving the speed of FPGA-based circuit as compared to wire-driven placement.

- Routing Routing [34] is the process of assigning specific routing resources to each net based on the RRG to realize the connectivity between logic blocks. Routing a net corresponds to finding a path from a start node (source) to the end nodes (sinks) with the help of the RRG. The design is acceptable and workable if and only if the circuit is routable within the given resources available in the targeted architecture. Routing algorithms aim to fulfill two objectives. First, they aim to avoid congestion channels so that routing one net will not use up the routing resource that another net needs. Second, they aim to optimize propagation delay by routing critical nets with the shortest and fastest paths.

- Simulation Simulation entails the analyzing of the circuit response to a set of input stimuli over a time interval. After placement and routing have been done, the implemented design is simulated to ensure its functionality. Any design errors found is corrected at this stage.

- **Create Bitstream File & Download to FPGA** With all the previous steps being successfully completed, the bitstream files can be generated for downloading to the target FPGA architecture to implement the logic and interconnection configurations. Once the FPGA is successfully programmed, it is ready for use.

Figure 2.3: Typical FPGA CAD flow

#### 2.3 Existing power estimation techniques

Over the years, different techniques had been explored for power efficient FP-GAs to prolong battery life. Dual supply voltage schemes had been proposed to achieve lower dynamic power consumption. [35] presented a hierarchical interconnect architecture with low voltage swing signaling circuit. [36, 37] built the framework for FPGA power evaluation and analysis. [38] achieved power reduction by pre-defined dual-Vdd/dual-Vt fabrics. [39, 40] employed the configurable dual-Vdd supply to obtain a performance and power tradeoff. [41] proposed the voltage scaling scheme for commercial FPGAs. The benefit brought by dual supply voltages is obvious as the switching power is directly proportional to the square of the supply voltage. However, dual supply technique complicates the chip and system design. Either on-chip or off-chip regulators need to be provided for dual supply techniques and extra power routing is required. A huge number of configurable level converters are also needed to avoid a Vdd-Low interconnect switch from driving a Vdd-High interconnect switch. Hence, to explore new FPGA architectures like the above, a highly flexible design framework is required.

#### 2.4 Existing SSTA techniques

As mentioned in section 1.2.1, the traditional corner-based timing analysis is unable to accurately perform timing predictions, thus SSTA is proposed to replace this method. SSTA has the ability to capture circuit variability by modeling delays as statistical random variables and capture any possible correlation that exist between the circuit components [17]. In general, SSTA does offer fast and accurate timing predictions as compared to traditional corner-based timing analysis.

Existing SSTA approaches either assume Gaussian or non-Gaussian distributions. Others may add in consideration for correlation effects. Most of these proposed approaches are classified into two approaches: path-based SSTA [11–16] and blockbased SSTA [17–21]. In path-based SSTA, it aims to provide an estimation of the circuit performance based on selected critical paths. This method is inefficient for large circuit as the worst case complexity of selecting the critical paths statistically grows exponentially with circuit size. Hence, path-based SSTA is not easily scalable to manage large circuits.

The block-based SSTA works by progressive computation. In this method, every component in the architecture is first treated as a timing block. Timing analysis is done from block to block using the timing graph in a forward manner, without ever tracking its history. Signals propagating through the timing blocks will sum up the delays into the arrival time. Delays and arrival times are called the timing variables of the circuit. Hence, the computation complexity for block-based SSTA is observed to grow linearly with circuit size.

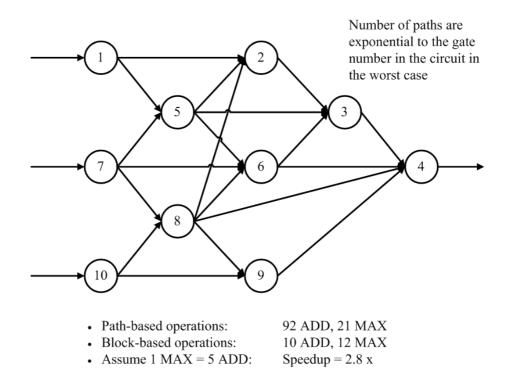

The complexity comparison between the path-based and block-based approaches for a simple circuit is shown in Figure 2.4 [7]. From the figure, we notice that the block-based approach shows 2.8x speedup even in such a simple case.

Figure 2.4: Complexity problem in path-based approach

However, to handle correlations among parameters, most approaches assume Gaussian distributions, which is not entirely the case in digital circuits. Other distributions require extensive computation, either for regression [42] or numerical integration [43]. On the whole, SSTA methods are computationally expensive and not fast enough to provide the variability-aware timing estimation during the synthesis optimizations.

## Chapter 3

## Modeling of the CAD Framework

As mentioned in chapter 1, existing CAD tools do not provide enough flexibility for users to design arbitrary FPGA routing architectures. We therefore need a tool to fulfill this capability.

#### 3.1 Framework design approach

The proposed architecture that can be designed is the island-style architecture as seen in Figure 2.2. To specify this architecture, the number of CLBs and IOBs need to be defined. An approach is to ask users to key in the specific number of blocks required. However, this method does not allow users to specify the shape of the architecture. Instead, we adopt another method, that is, to allow users to specify the dimension of the architecture to achieve arbitrary shapes of the architecture to be created. Furthermore, the layout of the island-style architecture will cause the number of IOBs to restrict the number of CLBs to be implemented or vice versa. This will result in excess blocks being declared when trying to accommodate the required number of CLBs or IOBs. Therefore, we allow users to have the flexibility to decide how many IO pads are needed at each physical location of an IOB. With the flexibility to define the dimension and number of IO pads, wastage of excess blocks declared is reduced and the dimension of the FPGA architecture is made more compacted.

In addition, the flexibility of each logic block can be further enhanced by allowing users to decide the number and the orientation of pins on the logic blocks. With this freedom to define arbitrary positions of the pins on the logic blocks, the routability and performance of the architecture can be improved.

Routing tracks play a critical role in routing performance, hence giving more freedom to define arbitrary wire segments should be allowed. However, this approach is too computational intensive. Instead, we constrain users to declare only single, double, hex and long tracks in the architecture. To enhance routability, the double and hex tracks are staggered [44]. In addition, we allow users to define the connectivity pattern of the connection block and switch box. For the connection box, users can decide how many tracks a pin can connect to in the channel. For the switch box, users can specify which tracks in the adjacent channel that a particular track can connect to.

After the basic parameters are defined, an initial architecture layout is generated.

In order for a more arbitrary architecture to be designed, we implement several popup interfaces for users to alter some parameters when they double-click on a specific resource of the architecture. These interfaces include the ability for users to change the number or orientation of pins on any logic blocks, change the pins' connectivity to routing tracks, change the switch pattern in the switch box or change the types of tracks in any channels.

## 3.2 Framework implementation approach

The proposed framework is developed in two phases. First, an interface that is used for initializing the basic parameters to create a basic routing architecture is created. Second, several additional interfaces are created which will pop-up by double-clicking on the components of the drawn architecture. These interfaces allow the editing of the corresponding clicked components. Once the design is finalized, placement and routing can commence.

#### 3.2.1 Initializing the architecture template

To begin the design of the architecture, certain basic parameters need to be specified. An initializing interface is thus set up to allow users to key in the necessary parameters. Figure 3.1 shows the interface developed. Using this interface, it simplifies the task to describe a generic FPGA architecture. An explanation of each parameter settings is as follows.

| Initialization |       |                      |

|----------------|-------|----------------------|

| Width          |       | Timing Budget (ns)   |

| Height         |       | Single Track         |

| Pads per IOB   |       | Double Track         |

| Input Pin No.  |       | Hex Track            |

| Clock No.      |       | Long Track           |

|                |       | Buffers Normal 💌     |

|                | BLOCK | Fc Style All tracks  |

|                |       | Fs Style 1 · 1 Map 💌 |

|                | ОК    | Cancel               |

Figure 3.1: Interface for initialization

In the top left hand corner, we have five different parameters that need to be set. The first and second parameters state the width and height of the required architecture respectively. The third parameter states the required number of IO pads to be declared at a physical location of an IOB. The forth and fifth parameters indicate the number of input pins and clock pins to be declared, respectively.

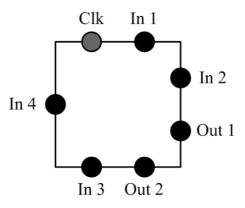

Next, on the lower left corner, users can define the orientation of the pins desired by specifying the required number on each side of the logic block using the boxes provided. Using these parameters, our framework is programmed to distribute the input and output pins evenly around the entire perimeter of each logic block so as to enhance routability. This technique is known as the full-perimeter pin positioning [45]. An example of a logic block with one clock, four input and two output pins is illustrated in Figure 3.2.

Figure 3.2: Logic block pins location

On the upper right corner, there are five parameters. First, the timing budget states the required timing constraint to be achieved for its critical path. This is explained further when we introduce the idea on reconfigurable buffers in chapter 5. The next four parameters allow different kinds of routing track to be specified by stating the preferred number corresponding to the desired tracks. Single track means that the track spans one logic block length, whereas the double and hex track spans two and six logic block lengths, respectively. The long track spans the entire width and height of the architecture.

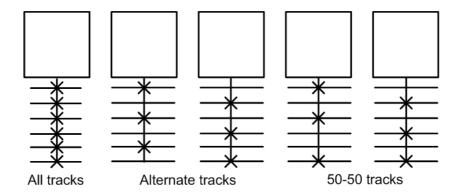

On the lower right corner, three drop-down interfaces are shown. First, users can define the types of buffers required in the architecture, that is, normal buffers or programmable (reconfigurable) buffers. Second, we have the options to define the different types of block connectivity,  $F_c$ , needed for all the pins of the blocks. Three options on the style of the connection blocks are given. (See Figure 3.3)

- 1. Users can choose to have the pins connected to all available tracks.

- 2. Users can choose to have the pins connected to alternate tracks.

- 3. Users can choose to have the pins connected to 50% of the available tracks randomly.

Figure 3.3: Types of connection block connectivity

For options 2 and 3, we ensure that the connection block pattern is pathologically good by fulfilling the following conditions:

- Ensure each pin is connected to different wire types (if any).

- Ensure multiple pins on each side connect to alternate tracks.

- Ensure pins sharing the same channel share at least one common track.

- Ensure pins sharing the same channel connect to different tracks.

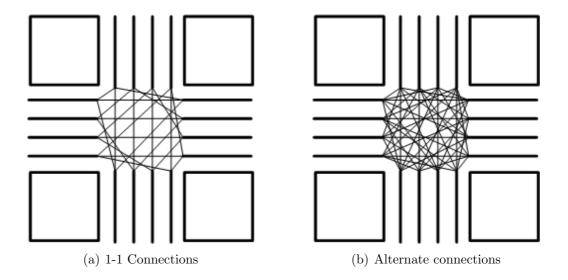

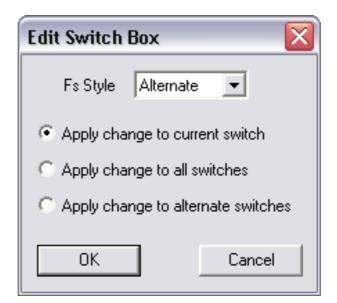

Third is the menu to define the switch connectivity,  $F_s$ , of the switch boxes. In this framework, all switch boxes defined consist of only buffers and no pass transistors. Users are given three options in this selection menu:

- 1. Tracks are connected to all tracks in the adjacent channels.

- 2. Tracks are connected to one track of each of the adjacent channels. (Figure 3.4(a))

- 3. Tracks are connected to alternate tracks of each of the adjacent channels. (Figure 3.4(b))

Figure 3.4: Types of switch block connectivity

After the initial settings are done, the resulting FPGA routing architecture is drawn. Figure 3.5 shows the design of a FPGA routing architecture of dimension 3 x 2.

Figure 3.5: FPGA routing architecture template

#### 3.2.2 Editing the architecture template

After the architecture is drawn, users can click any of the template components: logic blocks, routing channels, switch boxes or pins, to edit the original settings and create a customized routing architecture. Four different interfaces are illustrated next.

First, an interface to edit the logic blocks is described. Upon clicking on any of the CLBs, an interface is shown (See Figure 3.6). In this interface, users can re-initialize the number or orientation of pins of the selected block by keying a new set of data in the boxes provided. Three options are provided to allow users to specify whether to apply the changes made to the current CLB, all CLBs or to alternate CLBs.

Second, an interface to edit the routing channels is shown. Users can select any of the vertical or horizontal channel by clicking on it. Using the pop-up interface seen in Figure 3.7, users can re-specify the kind of tracks desired for the selected channel. This can be done by adding in new values in the corresponding spaces provided. Also, users can specify whether to apply these changes to all vertical and/or horizontal channels by checking the required boxes.

Third, an interface to edit the pin's connectivity is illustrated. By clicking on a pin of any logic blocks, an interface is produced as shown in Figure 3.8. In this interface, it allows users to change the connectivity pattern of the selected pin to the routing tracks it is facing. Four options are provided for users to indicate how the changes can be applied to. The four options are: all pins of current block, all pins of all similar blocks, alternate pins of current block or alternate pins of all similar blocks.

Forth, an interface to edit the switch box connectivity is presented. Users can click on any of the switch box to reconfigure its switch pattern. Figure 3.9 shows the interface when a switch box is selected. Three options are given for users to choose whether to apply the change made to the current switch box, all switch boxes or alternate switch boxes. Having finalized the architecture, users can proceed to do placement and routing to test the feasibility of their new design.

#### 3.2.3 CAD tool interface

In this section, we introduce the features that our framework is able to perform. Figure 3.10 shows the initial interface when the program is run. A description of the various menu bar options is listed in Table 3.1.

| Edit Pin Orientation 🛛 🛛 🔀                |           |  |  |  |  |

|-------------------------------------------|-----------|--|--|--|--|

|                                           |           |  |  |  |  |

|                                           |           |  |  |  |  |

| <ul> <li>Apply change to curre</li> </ul> | ent block |  |  |  |  |

| Apply change to similar blocks            |           |  |  |  |  |

| C Apply change to alternate blocks        |           |  |  |  |  |

| ОК                                        | Cancel    |  |  |  |  |

Figure 3.6: Edit CLB's pin orientation

| Edit Track Information |                 |  |  |  |

|------------------------|-----------------|--|--|--|

| Single Track           |                 |  |  |  |

| Double Track           |                 |  |  |  |

| Hex Track              |                 |  |  |  |

| Long Track             |                 |  |  |  |

| Apply change to all ve | ertical tracks  |  |  |  |

| Apply change to all ho | rizontal tracks |  |  |  |

| ОК                     | Cancel          |  |  |  |

Figure 3.7: Edit track information

| Edit Connection Box                               |                                          |  |  |  |  |  |

|---------------------------------------------------|------------------------------------------|--|--|--|--|--|

| Fc Style 🛛 All tracks 💌                           |                                          |  |  |  |  |  |

| Apply change to all pins of current               | nt block                                 |  |  |  |  |  |

| C Apply change to all pins of all blo             | O Apply change to all pins of all blocks |  |  |  |  |  |

| C Apply change to alternate pins of current block |                                          |  |  |  |  |  |

| O Apply change to alternate pins of all blocks    |                                          |  |  |  |  |  |

| ОК                                                | Cancel                                   |  |  |  |  |  |

Figure 3.8: Edit connection box

Figure 3.9: Edit switch box connectivity

Figure 3.10: Program interface

| Menu bar | Options         | Descriptions                                    |  |  |

|----------|-----------------|-------------------------------------------------|--|--|

| File     | New             | Initialize new architecture                     |  |  |

|          | Exit            | Quit the application; prompts to save documents |  |  |

| View     | No display      | Enable/Disable graphics drawing                 |  |  |

|          | Toggle switch   | Toggle the switch box visible/invisible         |  |  |

|          | Status bar      | Show or hide the status bar                     |  |  |

| Build    | Read Place File | le Read existing placement file                 |  |  |

|          | Read Net File   | Read netlist file                               |  |  |

|          | Create RRG      | Create Routing Resource Graph for VPR           |  |  |

|          | Placement       | Commence Placement                              |  |  |

|          | Routing         | Commence Global/Detailed Routing                |  |  |

| Help     | About Editor    | Display program information                     |  |  |

Table 3.1: Menu bar Options and descriptions

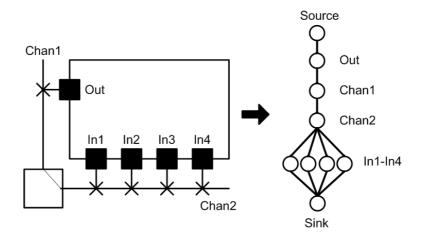

#### 3.3 Routing resource graph

After the FPGA routing architecture is finalized, an RRG is generated to specify the resources in it. The RRG is essential as it contains all connectivity information such as wires to which a given wire segment can connect and is used by the router to make routing decisions.

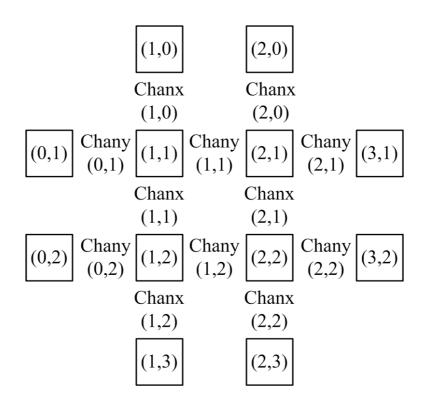

The RRG [46] is described by a directed graph, G=(V,E), where the set of nodes V corresponds to the functional block pins or wires in the routing architecture and the set of edges E corresponds to the switches that connect these nodes. In addition, the type of source and sink nodes are added to model the logically equivalent output and input pins, respectively. This RRG can be either manually generated once the routing architecture is being created or it will be automatically generated before routing commences. The generated RRG can be ported to VPR too. Figure 3.11 shows the RRG corresponding to a portion of the architecture whose functional block has 4 input pins and 1 output pin with 1 wire segment in both the vertical and horizontal channels.

#### **3.4** Placement and routing processes

Placement and routing are two mutually dependent processes. Placement is the process of assigning functional blocks to their physical locations in the architecture. In the island style FPGA architecture, the CLBs are arranged in a two-dimensional

Figure 3.11: Modeling FPGA routing as a directed graph

array with the IOBs on the periphery of the chip. Hence, placement is done using a coordinate system to track both x and y directions. Routing is the process of finding a connected path from a source to its sinks using the available routing resources. The RRG is used to enable fast retrieval of the inter-connections of the various components. In typical CAD tools, placement and routing are carried out as two independent phases. However, there are still cases where both are carried out simultaneously.

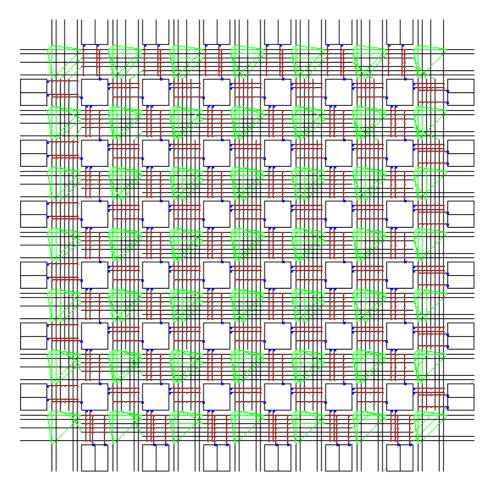

In our framework, placement is carried out followed by routing. Global and detailed routings are done in the routing phase. The RRG is used by the router to locate physical paths available for each net. In global routing, all nets are routed without any constraints. Detailed routing is done to establish physical connections between the logic blocks by assigning distinct paths to individual nets, while considering constraints like congestion, signal performance, and resource utilization.

#### 3.4.1 Placement process

In FPGA devices, there have been different placement techniques being adopted to bind logic elements to a physical unit on the device. Different algorithms have also been developed to suit the different types of architectures. All of these algorithms have the ability to handle constraints and cost minimization. Typical placement constraint includes user's constraints to fix certain logic blocks at a particular location. On the other hand, cost minimization includes the minimization of matrices like total wire lengths, usage of routing resources, etc and also to reduce congestion to enhance routability. Despite these constraints, all placement algorithms aim to present a good placement for the router to complete its routing efficiently.

#### Placement algorithm

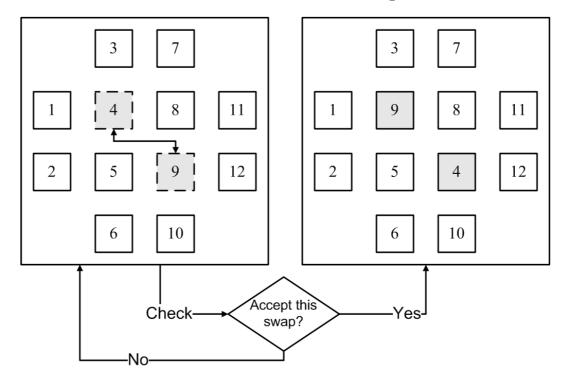

In our framework, the simulated annealing placement algorithm [3, 47] is implemented. Its pseudo-code is shown in Figure 3.12. Initially, each block is randomly assigned to an available vacancy in the target FPGA architecture to generate an initial placement solution. An initial temperature, T, is computed in a similar manner to [48]. A range limiter  $R_{limit}$  is introduced to allow blocks with that range to be considered for swapping. Initially,  $R_{limit}$  is set to the entire chip.

Next, pair-wise swapping is done and evaluated against a temperature schedule [30]. A temperature schedule is computed as  $T_{new} = \alpha T_{old}$ , where  $\alpha$  depends on the fraction of attempted moves that were accepted  $(R_{accept})$  at  $T_{old}$  as shown in Table 3.2. At each temperature, there is a total of  $10^* (N_{blocks})^{1.33}$  swaps. The placement cost which determines the acceptance of a swap is determined by a cost function:

$$cost = \sum_{n}^{N_{nets}} q(n) * [bb_x(n) + bb_y(n)]$$

(3.1)

Figure 3.12: Pseudo-code for the simulated-annealing algorithm used in the placement step

| Fraction of moves accepted $(R_{accept})$ | α    |

|-------------------------------------------|------|

| $R_{accept} > 0.96$                       | 0.5  |

| $0.80 < R_{accept} \le 0.96$              | 0.9  |

| $0.15 < R_{accept} \le 0.80$              | 0.95 |

| $R_{accept} \le 0.15$                     | 0.8  |

Table 3.2:

Temperature update schedule

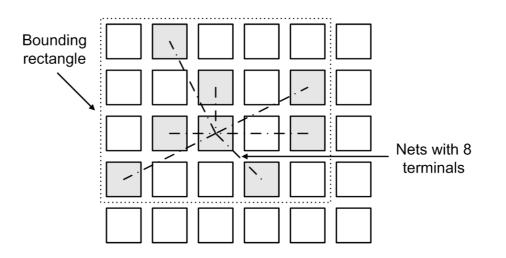

For each net,  $bb_x$  and  $bb_y$  are defined as the horizontal and vertical spans of its bounding box. This is commonly known as the half-perimeter model (Figure 3.13) which is widely used to estimate the wire-length of a net [49]. Given a block b with coordinates  $(x_b, y_b)$ , the half-perimeter of a net n is calculated as follows:

$$half - perimeter = [MAX_{ben}(x_b) - MIN_{ben}(x_b) + 1] + [MAX_{ben}(y_b) - MIN_{ben}(y_b) + 1]$$

$$(3.2)$$

Figure 3.13: Half-perimeter wavelength model

A q(n) factor [50] is introduced to compensate for any underestimation of the wire-length by this model. This value depends on the number of sinks a net has to connect. For nets with less than 3 terminals, q(n) is set to 1 and slowly increases to 2.79 for nets with 50 terminals. For large fan-out nets having more than 50 sinks, the value of q(n) increases linearly as follows [30]:

$$q(n) = 2.7933 + 0.02626 * (TerminalNumber - 50)$$

(3.3)

An illustration showing the swapping of two CLBs during placement is shown in Figure 3.14. Finally, the program will terminate when  $T < 0.005 * Cost / N_{nets}$ . A placement file is then generated which shows the physical locations of all the logic

blocks. The format of this file is discussed in the following section.

Figure 3.14: Swapping between two logic blocks

#### Placement file format

After placement has been completed, a placement file is generated as shown in Figure 3.15. The first line of the placement file lists the netlist used during the placement. The second line of the file gives the size of the logic block array as per designed. All the following lines have the following format:

block name x y sub-block physical location

The block name is the name of this block, as given in the input netlist file. x and y are the row and column coordinates in which the block is placed, respectively. The sub-block is applicable to IOBs. As we can have different number of pads on the

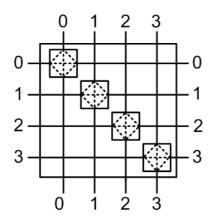

IOB, this sub-block number specify the pad position given the x and y coordinates. For CLBs, the sub-block number is always zero. The physical location indicates the physical placement of the block name on the architecture. Figure 3.16 shows the coordinate system used via a 2 x 2 FPGA architecture.

| Netlist file: sample.net<br>Array size: 2 x 2 logic blocks |   |   |        |              |  |  |

|------------------------------------------------------------|---|---|--------|--------------|--|--|

| #block name                                                | x | у | subblk | block number |  |  |

| #                                                          |   |   |        |              |  |  |

| i_31_                                                      | 0 | 1 | 0      | #1           |  |  |

| i_56_                                                      | 0 | 1 | 1      | #2           |  |  |

| i_47_                                                      | 2 | 3 | 0      | #3           |  |  |

| i_34_                                                      | 0 | 2 | 0      | #4           |  |  |

| out: $o_9$                                                 | 0 | 2 | 1      | #5           |  |  |

| o_1_                                                       | 2 | 1 | 0      | #6           |  |  |

| o_9_                                                       | 1 | 2 | 0      | #7           |  |  |

| o_2_                                                       | 1 | 1 | 0      | #8           |  |  |

| [93]                                                       | 2 | 2 | 0      | #9           |  |  |

Figure 3.15: Sample placement file

#### 3.4.2 Routing process

In most FPGA devices, routing is carried out in two steps: global routing and detailed routing. In global routing, the router assigns paths that a net can transverse from its source to its destination(s). Its objective is to find the shortest possible connection path with the least usage of routing elements and avoid congestion. Once global routing is done, the regions or routing areas where congestion are likely to occur are identified. Detailed routing then commences by assigning specific tracks to the nets within the given routing regions and avoiding the identified congestion

Figure 3.16: Coordinate system used

regions where possible.

At present, there are several routing algorithms. These algorithms aim to satisfy two criterions. First, they aim to minimize congestion cost such that each net will not use up the routing resource that another net needs. These algorithms are known to be routability-driven. An example is the Pathfinder negotiated congestion algorithm [45] used in VPR. This algorithm aims to minimize the propagation delay by routing critical nets first with the shortest path while minimizing the use of routing resources. Second, they aim to minimize the critical path delay. Such algorithms are called timing-driven. One example is the maze-routing algorithm based on Dijkstra's shortest path algorithm [51].

#### Routing algorithm

In our framework, the pathfinder negotiated congestion algorithm is implemented as the routing algorithm. Its pseudo-code is shown in Figure 3.17 [45, 46]. Global routing is first carried out followed by detailed routing. First, the router takes in the starting point and computes the shortest path to the destination using breath-first search. An evaluation cost function is formulated to measure the cost of a route from its source to its targeted sink(s) [45, 46]:

$$cost = (1 + h_n \cdot h_{fac}) * (1 + p_n \cdot p_{fac}) + b_{n,n-1}$$

(3.4)

The  $p_n$  term measures the current congestion at a node. It is updated every time any net is being ripped up and rerouted.  $h_n$  refers to the past congestion at the current node. It is updated after each iteration. Initially,  $h_n$  is 0 and is increased after each routing iteration. The  $b_{n,n-1}$  terms penalizes bends. Two controlling factors,  $h_{fac}$  and  $p_{fac}$ , are used to force nets with alternative routes to avoid using congested paths.

Some modifications are done to the breadth-first search algorithm to improve its efficiency [30]. The default algorithm is time-consuming as it requires k-1 iteration to find the paths of k terminals of the net as after each path is found, its wavefront is emptied and a new wave-front is formed for the subsequent sink. To remedy this, all the terminals of each nets are arranged in terms of Manhattan distance from their source, starting from the nearest to the furthest, prior to routing. After each successful routing, the wave-front is not emptied but stored in a sorted order. When a new iteration begins, the router will search through this set of data to find the

| 1  | While shared resources exist (global router)              |

|----|-----------------------------------------------------------|

| 2  | Loop over all signals $i$ (signal router)                 |

| 3  | Rip up routing tree $\mathrm{RT}_i$                       |

| 4  | $\mathrm{RT}_i \leftarrow \mathrm{s}_i$                   |

| 5  | Loop until all sinks $t_{ij}$ have been found             |

| 6  | Initialize priority queue PQ to $RT_i$ at cost 0          |

| 7  | Loop until new $t_{ij}$ is found                          |

| 8  | Delete lowest cost node $m$ from PQ                       |

| 9  | Loop over famouts $n$ of node $m$                         |

| 10 | Add n to PQ at cost $c_n + P_{im}$                        |

| 11 | End                                                       |

| 12 | End                                                       |

| 13 | Loop over nodes $n$ in path $t_{ij}$ to $s_i$ (backtrace) |

| 14 | Update $c_n$                                              |

| 15 | Add $n$ to $\mathrm{RT}_i$                                |

| 16 | End                                                       |

| 17 | End                                                       |

| 18 | End                                                       |

| 19 | End                                                       |

|    |                                                           |

Figure 3.17: Pseudo-code for the Pathfinder negotiated congestion algorithm used in the routing step

nearest starting point and expand out to its designated sink. In this way, the router takes a shorter amount of time to reach to its next sinks then having to expand its wave-front from scratch.

Moreover, instead of allowing the algorithm to go through all the adjacent vertexes of the map and to avoid overly circuitous routes, we reduce the search by the router to at most 3 channels outside the boundary of the source pin and the sink pin. Once routing is successfully completed, a routing file is generated.

#### Routing file format

The first line of the routing file [3] gives the FPGA architecture size. The remainder of the routing file lists the detailed routing for each net. Each routing net begins with the word *net* and its count, followed by the name of the net given in the netlist file in brackets. The following lines define the routing of the net. Each line begins with a keyword that identifies a type of routing segment.

The keywords used are *SOURCE* (output pin from which the net starts), *SINK* (input pin where the net terminates), *OPIN* (output pin), *IPIN* (input pin), *CHANX* (horizontal channel) and *CHANY* (vertical channel). Each routing net begins with a *SOURCE* and ends in a *SINK*. In brackets after the keyword is the coordinates of this routing resource based on Figure 3.16.

Next, the pad number (if the *SOURCE*, *SINK*, *IPIN* or *OPIN* is on an IOB), pin number (if the *IPIN* or *OPIN* was on a CLB), class number (if the *SOURCE* or *SINK* was on a CLB) or track number (for *CHANX* or *CHANY*) is listed. The pad or pin number indicates the pin reference number given to each pin of each logic block. Class number '0' indicates the CLB is a *SINK* and '1' indicates the CLB is a *SOURCE*. As for the track number, track 1 is the topmost track of *CHANX*, while in *CHANY* track 1 is the leftmost track.

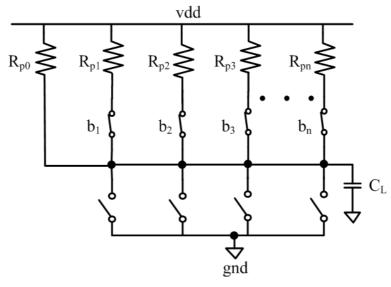

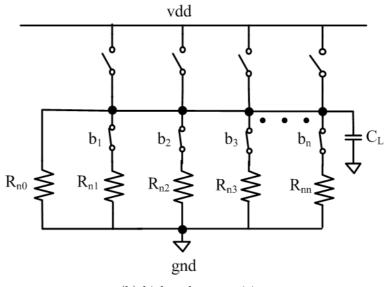

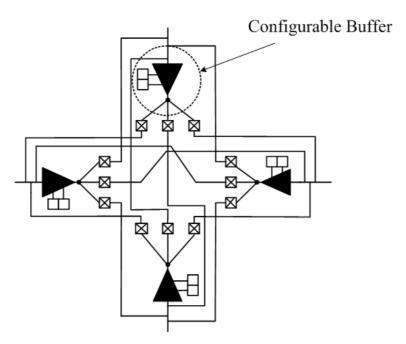

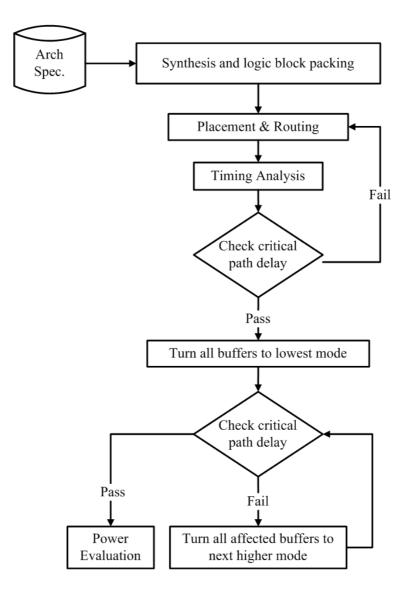

For an N-pin net, we need N-1 distinct wiring paths to connect all the pins. The first wiring path goes from a *SOURCE* to a *SINK*. The routing segment listed immediately after the *SINK* is the part of the existing routing to which the new path