# INVESTIGATION OF HIGH-K GATE DIELECTRICS FOR ADVANCED CMOS APPLICATION

## YU XIONG FEI

NATIONAL UNIVERSITY OF SINGAPORE

2006

# INVESTIGATION OF HIGH-K GATE DIELECTRICS FOR ADVANCED CMOS APPLICATION

## YU XIONG FEI

(B. Eng., ZheJiang University)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

# Acknowledgements

Many thanks are due to numerous colleagues and individuals who have directly or indirectly assisted in the preparation of this manuscript.

My advisor, Prof. Zhu Chun Xiang has been instrumental in directing the progress of my doctoral research over the last four years. I would like to gratefully thank him for providing me with invaluable guidance, and the awesome opportunity to address some of the most daunting challenges faced by the semiconductor industry today. Prof. Zhu gave me ample freedom to pursue several different projects during the course of my research while always providing valuable insight and making sure that I did not lose sight of my primary research objective.

I would also like to thank Dr. Yu Ming Bin, my advisor in the Institute of Microelectronics, I have had the pleasure of knowing him even since I joined NUS and he has always been supportive of my research endeavors and provided valuable guidance all along.

I would like to greatly acknowledge the intellectual support of Prof. Li Ming Fu during my graduate research. He has been closely associated with a significant part of my research, and his knowledge and mastery of the field have been truly inspirational. I would like to take this chance to express my sincere thanks to Prof. Dim-Lee Kwong and Prof. Albert Chin for their instruction, guidance, wisdom and kindness in teaching and encouraging me. My thanks go to Prof. Yoo Woo Jong and Prof. Lee Sung Joo for serving on my qualifying examination committee. Many thanks also go to Prof. Cho Byung Jin and Prof. Yeo Yee-Chia for many valuable technical discussions.

I have had the pleasure of collaborating with numerous exceptionally talented graduate students and colleagues over the last few years. I would like to thank my colleagues in Prof. Zhu's group, such as Hu Hang, Ding Shi Jin, Wu Nan, Zhang Qing Chun, Huang Ji Dong and Fu Jia for their discussions and supports. I would also like to thank Yu Hong Yu, Chen Jing Hao, Kim Sung Jung, Wang Xin Peng, Ren Chi, Shen

Chen, Gao Fei, Chen Jing De and Wang Ying Qian for their support and close friendship which I will always cherish. I would like to extend my appreciation to all other SNDL graduate students and technical staffs for their support and friendship.

Finally, I would like to express my deep gratitude to my parents Yu Hai Zheng and Zhang Yu Hua, who have always encouraged my academic endeavors inspite of the enormous physical distance between us. My deepest love and gratitude go to my wife, Wang Xin, for her love, patience, and enduring support.

# **Table of Contents**

| Acknowledgement                                                                         |

|-----------------------------------------------------------------------------------------|

| Table of Contentsii                                                                     |

| Summaryvii                                                                              |

| List of Tables                                                                          |

| List of Figuresx                                                                        |

| Chapter 1 Introduction                                                                  |

| 1.1 Introduction of Device Scaling                                                      |

| 1.1.1 Evolution of ULSI Technology                                                      |

| 1.1.2 Device Scaling Approaches                                                         |

| 1.1.3 Scaling and Improved Performance                                                  |

| 1.2 Scaling Limits for Conventional Gate Dielectrics                                    |

| 1.2.1 Limitations of SiO <sub>2</sub> as the Gate Dielectric for Advanced CMOS Devices? |

| 1.2.2 SiON and Si <sub>x</sub> N <sub>y</sub> /SiO <sub>2</sub> Gate Dielectrics        |

| 1.3 Alternative High- <i>k</i> Gate Dielectrics                                         |

| 1.3.1 Selection Guidelines for High- <i>k</i> Gate Dielectrics                          |

| 1.3.1.1 Permittivity and Barrier Height                                                 |

| 1.3.1.2 Thermodynamic Stability on Si and Film Morphology                               |

| 1.3.1.3 Interface Quality                                                                                                                                                                                                                                               |                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.3.1.4 Process Compatibility                                                                                                                                                                                                                                           | 15                         |

| 1.3.1.5 Reliability                                                                                                                                                                                                                                                     | 15                         |

| 1.3.2 Evolution of High-k Gate Dielectric                                                                                                                                                                                                                               | 17                         |

| 1.3.3 Major Challenges of Hf-based Gate Dielectrics Implementation                                                                                                                                                                                                      | 20                         |

| 1.3.3.1 Thermal Stability                                                                                                                                                                                                                                               | 20                         |

| 1.3.3.2 Mobility Degradation                                                                                                                                                                                                                                            | 21                         |

| 1.3.3.3 Charge Trapping induced $V_{th}$ Instability                                                                                                                                                                                                                    | 23                         |

| 1.3.3.4 Fermi Level Pinning Effect Induced High $V_{th}$                                                                                                                                                                                                                | 23                         |

| 1.4 Major Achievements and Organization of This Thesis                                                                                                                                                                                                                  | 24                         |

| References                                                                                                                                                                                                                                                              | 28                         |

|                                                                                                                                                                                                                                                                         |                            |

| Chapter 2 A Novel HfTaO with Excellent Properties for AcGate Dielectric Application                                                                                                                                                                                     | dvanced                    |

| •                                                                                                                                                                                                                                                                       |                            |

| Gate Dielectric Application                                                                                                                                                                                                                                             | 32                         |

| Gate Dielectric Application  2.1 Introduction                                                                                                                                                                                                                           | 32                         |

| Gate Dielectric Application  2.1 Introduction                                                                                                                                                                                                                           | 323435                     |

| Gate Dielectric Application  2.1 Introduction                                                                                                                                                                                                                           | 323435                     |

| Gate Dielectric Application  2.1 Introduction  2.2 Experiments  2.3 Results and Discussion  2.3.1 Physical Characteristics of HfTaO                                                                                                                                     | 32<br>34<br>35<br>35       |

| Gate Dielectric Application  2.1 Introduction  2.2 Experiments  2.3 Results and Discussion  2.3.1 Physical Characteristics of HfTaO  2.3.2 C-V, J-V, Thermal Stability and Interface Properties of HfTaO                                                                | 32<br>35<br>35<br>41       |

| Gate Dielectric Application  2.1 Introduction  2.2 Experiments  2.3 Results and Discussion  2.3.1 Physical Characteristics of HfTaO  2.3.2 C-V, J-V, Thermal Stability and Interface Properties of HfTaO  2.3.3 Charge Trapping Induced Electrical Instability in HfTaO | 32<br>34<br>35<br>41<br>48 |

| 2.3.5 Suppression of Boron Penetration in HfTaO Gate Dielectric5                                                 | 9 |

|------------------------------------------------------------------------------------------------------------------|---|

| 2.4 Conclusions6                                                                                                 | 3 |

| References6                                                                                                      | 5 |

| Chapter 3 Advanced HfTaON/SiO <sub>2</sub> Gate Stack for Low Standby<br>Power Application                       | y |

| 3.1 Introduction6                                                                                                | 9 |

| 3.2 Experiments                                                                                                  | 1 |

| 3.3 Results and Discussion                                                                                       | 2 |

| 3.3.1 Physical Characteristics of HfTaON/SiO <sub>2</sub> Gate Stack                                             | 2 |

| 3.3.2 Thermal Stability of HfTaON/SiO <sub>2</sub> Gate Stack7                                                   | 8 |

| 3.3.3 <i>C-V</i> and <i>J-V</i> of HfTaON/SiO <sub>2</sub> Gate Stack and Interface Properties7                  | 9 |

| 3.3.4 Transistor Characteristics of HfTaON/SiO <sub>2</sub> Gate Stack                                           | 5 |

| 3.3.5 V <sub>th</sub> Instability in HfTaON/SiO <sub>2</sub> Gate Stack8                                         | 9 |

| 3.4 Conclusions                                                                                                  | 2 |

| References9                                                                                                      | 4 |

| Chapter 4 Effect of Gate Dopant Penetration on Leakage Current in n <sup>+</sup> Poly-Si/HfO <sub>2</sub> Device | n |

| 4.1 Introduction9                                                                                                | 8 |

| 4.2 Review of Literature9                                                                                        | 9 |

| 4.3 Experiments                                                                                                  | 2 |

| 4.4 Results and Discussion 10                                                                                    | 3 |

| 4.4.1 C-V and J-V Characteristics                                                         | 103           |

|-------------------------------------------------------------------------------------------|---------------|

| 4.4.2 Physical Characteristics                                                            | 105           |

| 4.4.3 Discussion.                                                                         | 109           |

| 4.5 Conclusions                                                                           | 109           |

| References                                                                                | 111           |

| Chapter 5 Effective Suppression of Fermi Level Pinn Si/High-k by Inserting Poly-SiGe Gate | ning in Poly- |

| 5.1 Introduction                                                                          | 115           |

| 5.2 Fermi Level Pinning at Poly-Si/high- <i>k</i> Interface                               | 116           |

| 5.2.1 Theoretical Background                                                              | 116           |

| 5.2.2 Fermi Level Pinning at Poly-Si/High- <i>k</i> interface                             | 118           |

| 5.2.3 Possible Mechanism of Fermi Level Pinning Effect                                    | 120           |

| 5.2.3.1 Interfacial Bonding (Si-Hf or Si-O-Al Bond)                                       | 120           |

| 5.2.3.2 HfB <sub>2</sub> Formation                                                        | 122           |

| 5.2.3.3 Oxygen Vacancy Formation                                                          | 123           |

| 5.3 Poly-SiGe for Gate Electrode Application                                              | 126           |

| 5.3.1 Background of Poly-SiGe Gate                                                        | 126           |

| 5.3.2 Review of Literature                                                                | 127           |

| 5.4 Suppression of Fermi Level Pinning in Poly-SiGe/high-k                                | 132           |

| 5.4.1 Background                                                                          | 132           |

| 5.4.2 Experiments                                                                         | 133           |

| 5.4.3 Suppressed Fermi Level Pinning by Poly-SiGe Gate                                    | 134           |

| 5.5 Conclusion                                                                                  | 141       |

|-------------------------------------------------------------------------------------------------|-----------|

| References                                                                                      | 142       |

| Chapter 6 Impact of Nitrogen in High- $k$ Gate Dielectric Trapping Induced $V_{th}$ Instability | on Charge |

| 6.1 Introduction                                                                                | 147       |

| 6.2 Effects of N in HfON on Electrical Characteristics                                          | 149       |

| 6.2.1 Experiments                                                                               | 149       |

| 6.2.2 Results and Discussion                                                                    | 150       |

| 6.2.3 Conclusion.                                                                               | 155       |

| 6.3 Impact of Nitrogen on Charge Trapping Induced $V_{th}$ Instability                          | 156       |

| 6.3.1 Experiments                                                                               | 156       |

| 6.3.2 Results and Discussion.                                                                   | 157       |

| 6.3.3 Conclusion.                                                                               | 168       |

| 6.4 Summary and Major Contributions                                                             | 168       |

| References                                                                                      | 170       |

| Chapter 7 Conclusions and Future Work                                                           |           |

| 7.1 Summary of Results                                                                          | 174       |

| 7.2 Major Contributions and Suggestions of Future Work                                          | 178       |

| Appendix                                                                                        |           |

| List of Publications                                                                            | 182       |

# **Summary**

In order to maintain historical trends of improved device performance, the continued aggressive scaling of CMOS devices for leading-edge technology is driving the conventional  $SiO_2/SiON$  gate dielectrics to their physical limits due to excessive gate leakage current and reliability concerns. High dielectric constant (k) gate dielectrics, as the replacement of the  $SiO_2/SiON$ , have been extensively investigated in the past few years, because of their potential for reducing gate leakage current while keeping the equivalent oxide thickness (EOT) thin. Timely implementation of the high-k gate dielectrics will involve dealing with four major challenging issues, including (1) thermal stability, (2) mobility degradation, (3) charge trapping induced threshold voltage ( $V_{th}$ ) instability, and (4) Fermi level pinning induced high  $V_{th}$ .

The main purpose of this thesis was to overcome the four major challenges, and also attempt to integrate the high-*k* gate dielectrics to conventional self-aligned poly-Si gate and advanced metal gate process.

In **Chapter 2**, we proposed a novel HfTaO gate dielectric with high dielectric constant, sufficient high crystallization temperature, good thermal stability, strong boron penetration immunity, low interface state density ( $D_{it}$ ), high mobility, and excellent  $V_{th}$  instability. These suggest that the HfTaO is a very promising candidate as an alternative gate dielectric for future CMOS application.

A novel HfTaON/SiO<sub>2</sub> gate stack, which consists of a HfTaON film with k value of 23 and a 10-Å SiO<sub>2</sub> interfacial layer, was proposed for low standby power application in **Chapter 3**. This gate stack provided much lower gate leakage current against SiO<sub>2</sub>, good interface properties and thermal stability, excellent transistor characteristics, superior carrier mobility and negligible  $V_{th}$  instability. These excellent properties observed in the HfTaON/SiO<sub>2</sub> may be mainly attributed to the good physical and electrical characteristics in HfTaO, and the insertion of SiO<sub>2</sub> interfacial layer.

In **Chapter 4**, the experimental results demonstrated that the gate dopant penetration may remarkably affect the gate leakage current in n<sup>+</sup> poly-Si/HfO<sub>2</sub> devices. Based on the experimental results and physical analyses, a hypothesis of generation of dopant-related defects at grain boundaries in crystallized HfO<sub>2</sub> film was proposed. These imply that the phosphorus or arsenic penetration is also significant concern for poly-Si/HfO<sub>2</sub> devices.

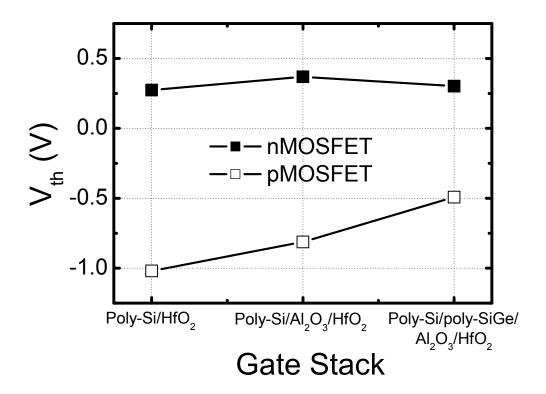

In **Chapter 5**, we have demonstrated that the unacceptably high  $V_{th}$  induced by the Fermi Level pinning at poly-Si/high-k interface was effectively suppressed by inserting a poly-SiGe gate electrode. The acceptable  $V_{th}$  of 0.3 V for nMOS and -0.49 V for pMOS was successfully achieved in the poly-Si/poly-SiGe/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> device. This finding could make a great breakthrough for integration of high-k gate dielectric into conventional poly-Si gate process.

Finally, the impacts of nitrogen on charge trapping induced  $V_{th}$  instability in high-k gate dielectric with metal and poly-Si gates have been extensively studied. A novel phenomenon, which the incorporated nitrogen in high-k film played opposite role in charge trapping induced  $V_{th}$  instability between the devices with metal and poly-Si gate, was demonstrated in **Chapter 6**.

Overall, the results of all studies presented in this thesis may contribute to a good understanding of material properties, electrical characteristics and reliability in high-k gate dielectrics for advanced CMOS application. Several approaches presented in this thesis can be used to effectively solve the major challenges for implementation of the high-k gate dielectrics.

# **List of Tables**

| Table 1.1 | The technology scaling rules for constant-field, constant-voltage and generalized scaling                                                                                                                            | p.4   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 1.2 | CMOS ULSI technology generations                                                                                                                                                                                     | p.5   |

| Table 1.3 | ITRS 2005 for the scaling of dielectric thickness with year                                                                                                                                                          | p.10  |

| Table 1.4 | Comparison of relevant properties for various gate dielectric materials                                                                                                                                              | p.13  |

| Table 3.1 | Comparison of device performances between the $HfTaON/SiO_2$ gate stack and $Hf$ -silicates devices. The $HfTaON/SiO_2$ shows lower leakage current and higher carrier mobility compared to those published results. | p.92  |

| Table 4.1 | Summary of the formation of gate stacks for the poly-Si gate, TaN metal gate devices, and also the doping concentration of the poly-Si gates.                                                                        | p.103 |

| Table 5.1 | Variations of work function (WF) for $n^+$ and $p^+$ poly-SiGe gates with increasing Ge content.                                                                                                                     | p.131 |

| Table 5.2 | The process flow of poly-Si/HfO $_2$ (SH), poly-Si/Al $_2$ O $_3$ /HfO $_2$ (SAH) and poly-Si/poly-SiGe/Al $_2$ O $_3$ /HfO $_2$ (GAH) gate stacks formation. The Ge content is ~30% in SiGe gate.                   | p.133 |

# **List of Figures**

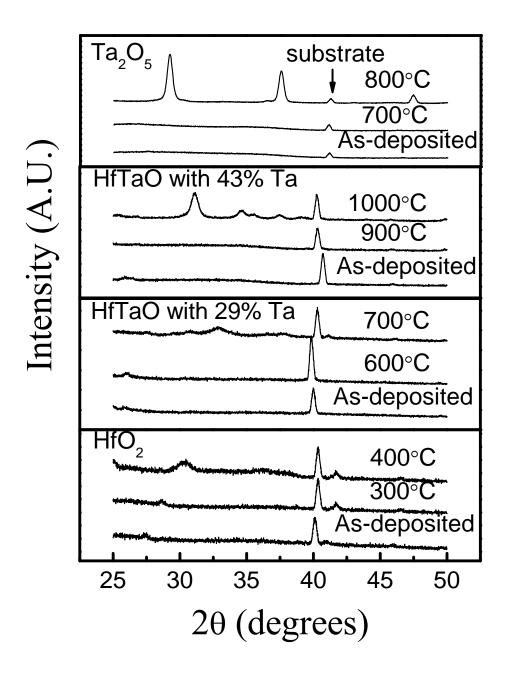

- **Fig. 2.1** XRD spectra of HfO<sub>2</sub>, HfTaO and Ta<sub>2</sub>O<sub>5</sub> films for as-deposited p.36 and different temperature annealing in  $N_2$  ambient. The crystallization temperature of HfO<sub>2</sub> film is increased up to  $1000^{\circ}$  C by incorporating 43% Ta.

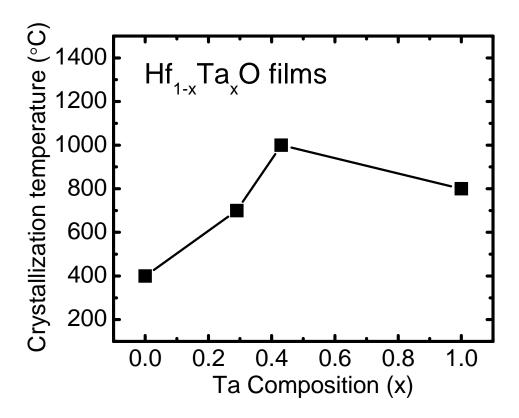

- **Fig. 2.2** Crystallization temperatures of HfTaO films as a function of Ta p.37 composition. It is note that the crystallization temperature of HfTaO with 43% Ta is higher than that of pure HfO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>.

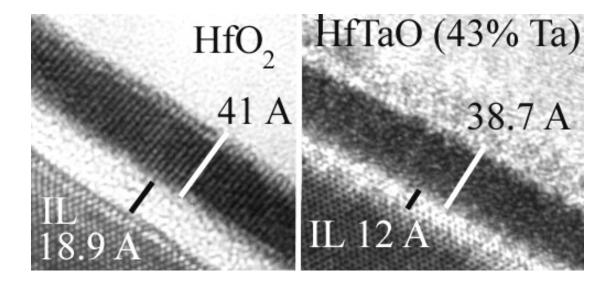

- **Fig. 2.3** TEM micrographs of HfO<sub>2</sub> and HfTaO with 43% Ta films after p.38 activation annealing at 950°C for 30sec. The HfO<sub>2</sub> film shows fully crystallized and HfTaO with 43% Ta film remains amorphous structure.

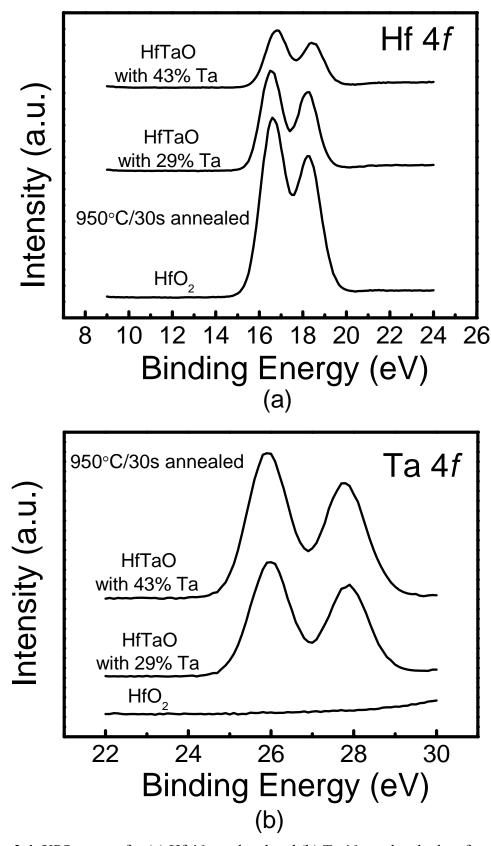

- Fig. 2.4 XPS spectra for (a) Hf 4f core level and (b) Ta 4f core level p.39 taken from HfO<sub>2</sub>, HfTaO with 29% and 43% Ta films after PDA at 700° C for 40sec and activation annealing at 950° C for 30sec. Any evidence of Hf-Si or Ta-Si bonds formation can not be observed in the films.

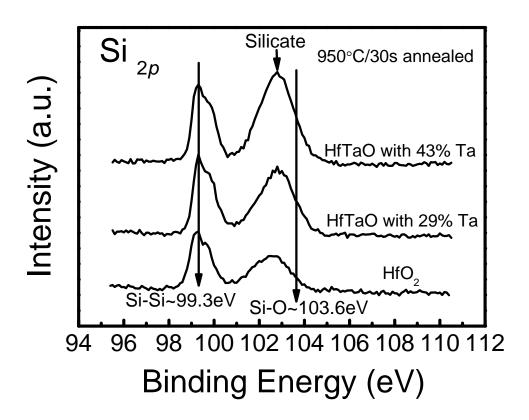

- Fig. 2.5 XPS spectra for Si 2p peaks of HfO<sub>2</sub>, HfTaO with 29% and 43% p.40 Ta films after PDA at 700° C for 40sec and activation annealing at 950° C for 30sec. The silicate-like IL peak (102.8eV) slightly shifts to high binding energy with Ta composition, as well as with increased intensity.

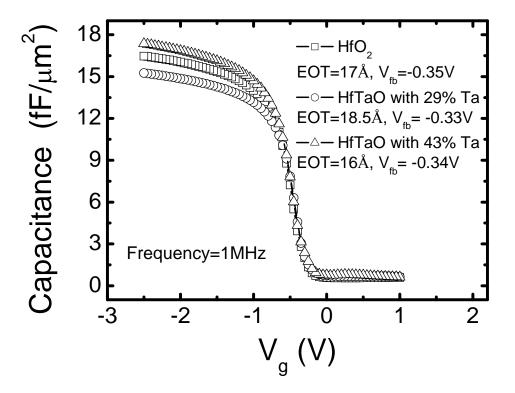

- Fig. 2.6 Typical *C-V* curves of MOS capacitors with HfO<sub>2</sub>, HfTaO with p.41 29% and 43% Ta gate dielectrics after activation annealing at 950° C for 30sec. The HfO<sub>2</sub> and HfTaO capacitors show similar flat band voltage, indicating that negligible fixed charges were

introduced by incorporating Ta into HfO<sub>2</sub>.

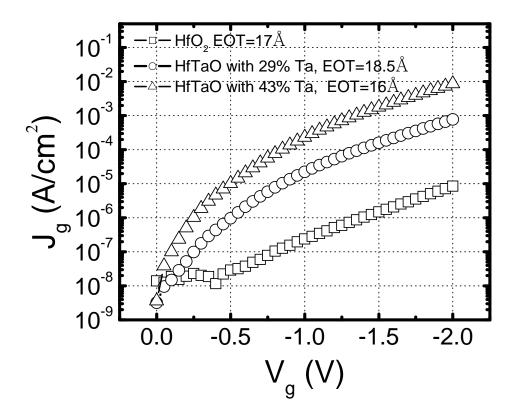

- **Fig. 2.7** Typical *J-V* curves of MOS capacitors with HfO<sub>2</sub>, HfTaO with p.42 29% and 43% Ta gate dielectrics after activation annealing at 950° C for 30sec. HfTaO dielectrics show higher leakage current compared to HfO<sub>2</sub>.

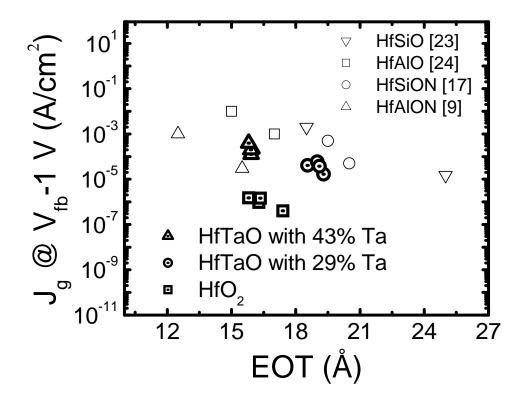

- **Fig. 2.8** Comparison of leakage currents vs. *EOT* for HfO<sub>2</sub>, HfTaO and p.43 published results. Even the leakage currents of HfTaO films are higher than HfO<sub>2</sub>, still comparable to HfSiO, HfSiON, HfAlO, and HfAlON.

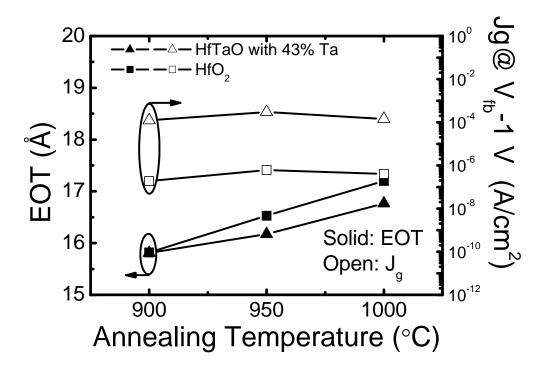

- **Fig. 2.9** EOT and gate leakage currents as functions of the activation p.44 annealing temperature. The increased EOT in  $HfO_2$  is slight higher than that in HfTaO.

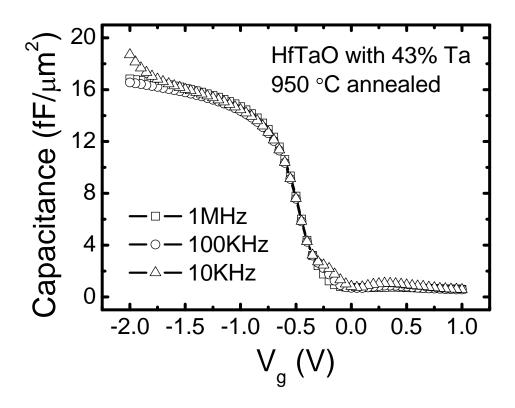

- **Fig. 2.10** Negligible frequency dispersion of the HfTaO with 43% Ta p.45 capacitance between 10KHz, 100KHz and 1MHz. This indicates that the interface traps in the HfTaO gate dielectric can not respond at high frequency.

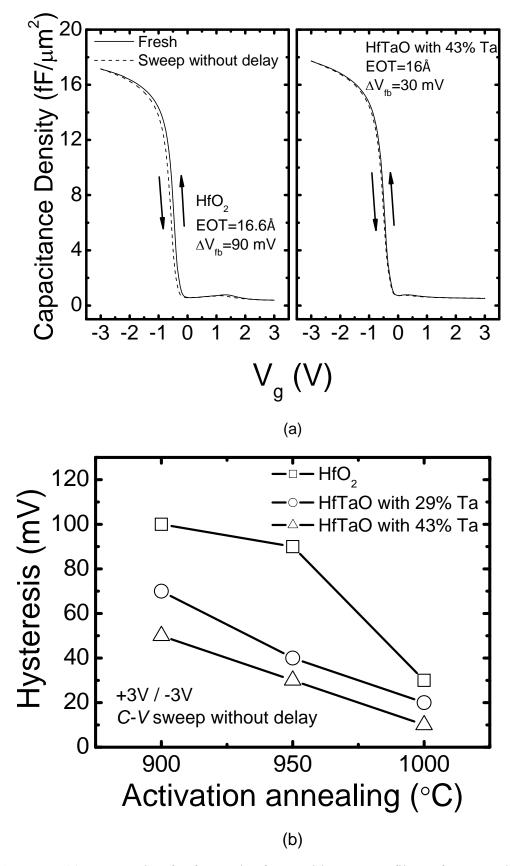

- **Fig. 2.11** (a) Hysteresis of HfO<sub>2</sub> and HfTaO with 43% Ta films after p.46 annealing at 950°C for 30sec. (b) Hysteresis of HfO<sub>2</sub> and HfTaO films as a function of activation annealing temperature. The hysteresis was quantified by the difference in  $V_{fb}$  during the voltage sweeps between  $\pm 3V$ .

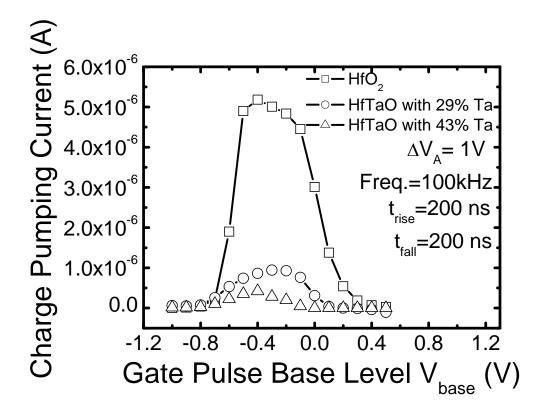

- Fig. 2.12 Charge pumping current measured on nMOSFETs with HfO<sub>2</sub> p.47 and HfTaO gate dielectrics after activation annealing at 950°C for 30sec. By incorporating Ta into HfO<sub>2</sub> film, the charge pumping current is reduced by one order of magnitude.

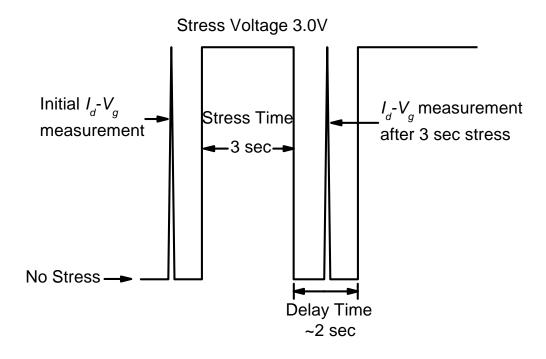

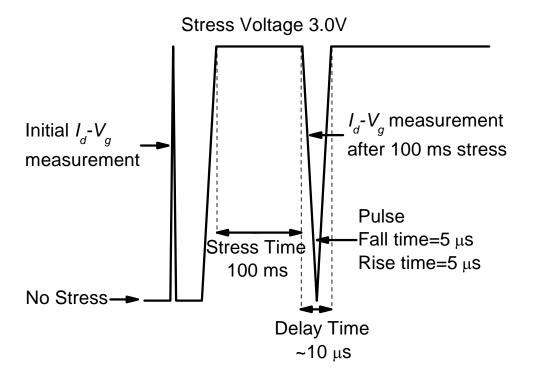

- **Fig. 2.13** Schematic diagram of the static (DC) measurement technique. p.48

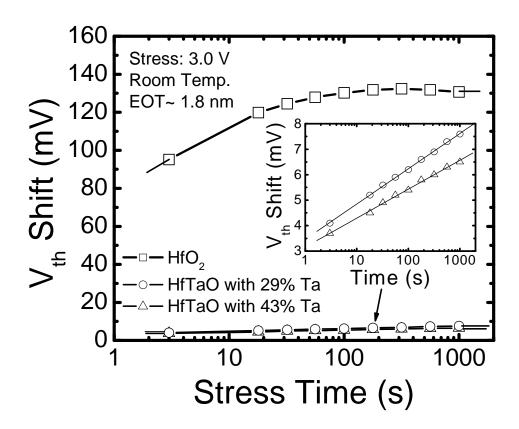

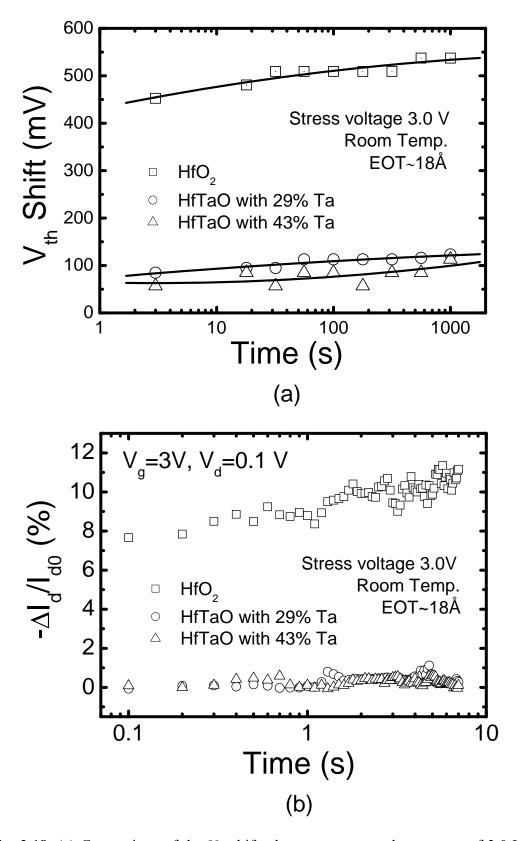

- Fig. 2.14 Comparison of the  $V_{th}$  shifts due to constant voltage stress of p.49 3.0V in HfO<sub>2</sub> and HfTaO films measured by static (DC)

technology. HfTaO has about 20 times lower  $V_{th}$  shift than HfO<sub>2</sub>, indicating that HfTaO films have ultra lower traps compared to HfO<sub>2</sub>.

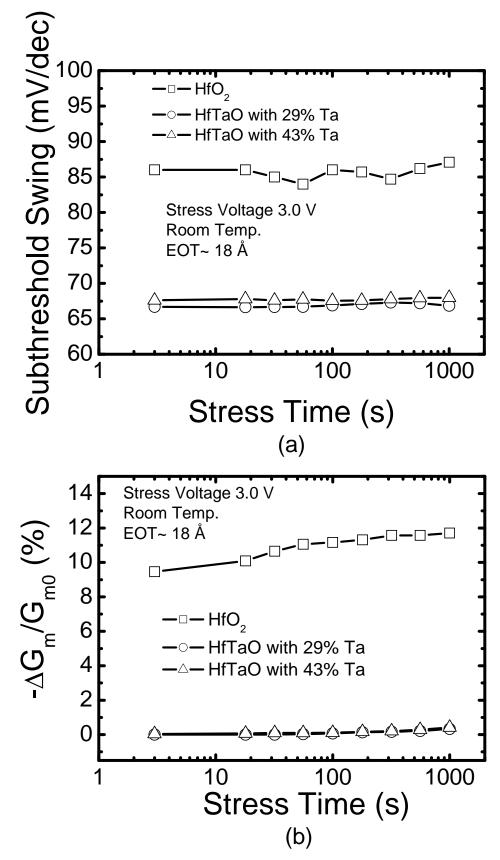

- **Fig. 2.15** (a) Subthreshold swing and (b) transconductance ( $G_m$ ) variations p.51 as a function of constant voltage stress time. Negligible variations of subthreshold swing and  $G_m$  can be observed in HfTaO films.

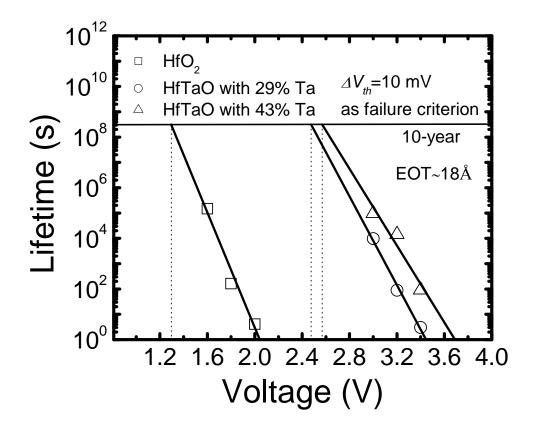

- **Fig. 2.16** Lifetime projection of charge trapping induced  $V_{th}$  shifts for p.52 HfO<sub>2</sub> and HfTaO gate dielectrics. The device lifetime of HfO<sub>2</sub> gate dielectric is greatly prolonged by incorporating Ta.

- **Fig. 2.17** Schematic diagram of the transient (pulsed  $I_d$ - $V_g$ ) measurement p.53 technique.

- **Fig. 2.18** (a) Comparison of the  $V_{th}$  shifts due to constant voltage stress of p.55 3.0V in HfO<sub>2</sub> and HfTaO films measured by pulsed  $I_d$ - $V_g$  technology. (b) Charge trapping induced drain current degradation as a function of constant voltage stress time.

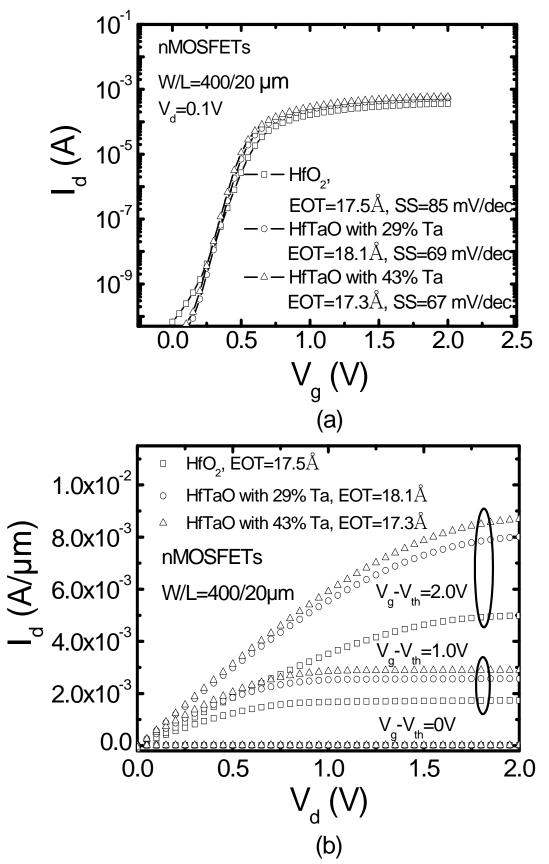

- **Fig. 2.19** (a)  $I_d$ - $V_g$  and (b)  $I_d$ - $V_d$  curves of nMOSFETs with HfO<sub>2</sub> and p.57 HfTaO gate dielectrics. HfTaO nMOSFETs show higher drain current and lower subthreshold swing compared to HfO<sub>2</sub>.

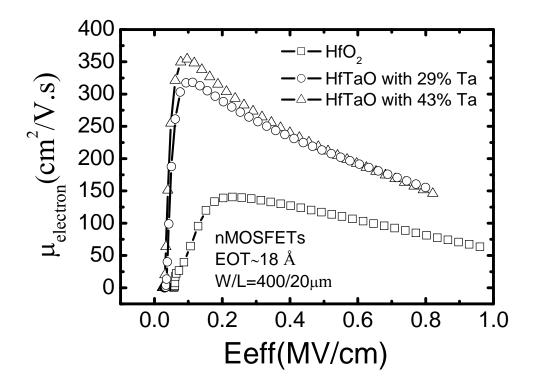

- Fig. 2.20 Effective electron mobility of nMOSFETs with HfO<sub>2</sub> and p.58 HfTaO gate dielectrics extracted by split *C-V* method. HfTaO nMOSFETs show much higher electron mobility than that of HfO<sub>2</sub>.

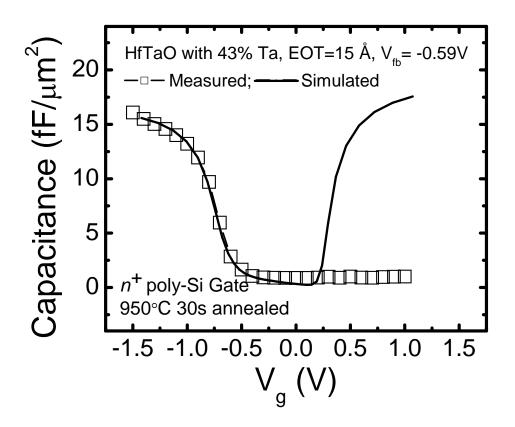

- **Fig. 2.21** *C-V* characteristic of 43% Ta HfTaO nMOS capacitor with p.60 poly-Si gate after activation annealing at 950° C for 30sec. The measurement was done at frequency of 1MHz and room temperature.

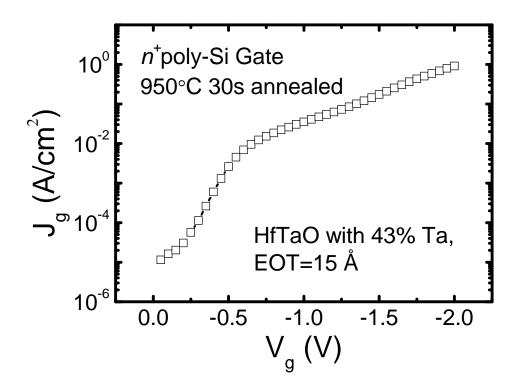

- **Fig. 2.22** *J-V* characteristic of HfTaO nMOS capacitor with poly-Si gate p.61 after activation annealing at 950° C for 30sec.

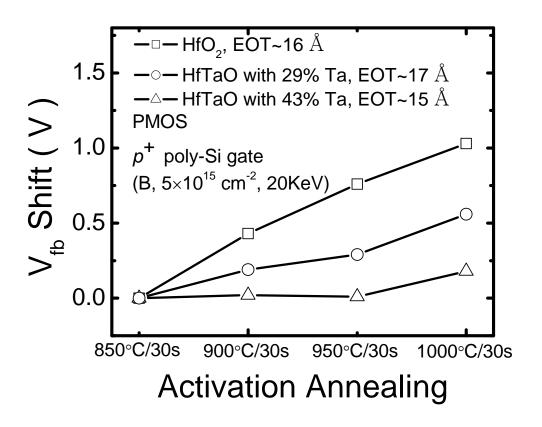

- **Fig. 2.23** Comparison of the  $V_{fb}$  shift in HfO<sub>2</sub> and HfTaO pMOS p.62 capacitors after various temperature annealing. HfTaO films show stronger immunity to boron penetration than HfO<sub>2</sub>, due to its high crystallization temperature.

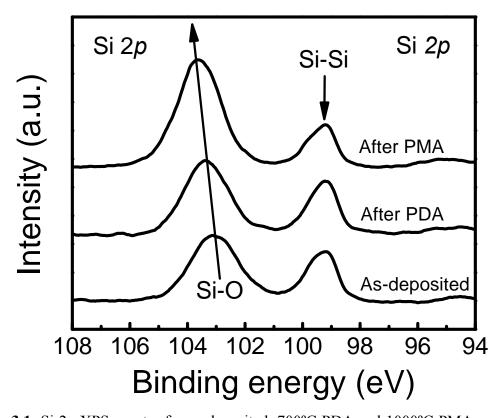

- **Fig. 3.1** Si 2*p* XPS spectra for as-deposited, 700°C PDA and 1000°C p.72 PMA annealed HfTaON/SiO<sub>2</sub> films. The Si-O peak slightly shifts to higher position and the intensity is increased with annealing temperature.

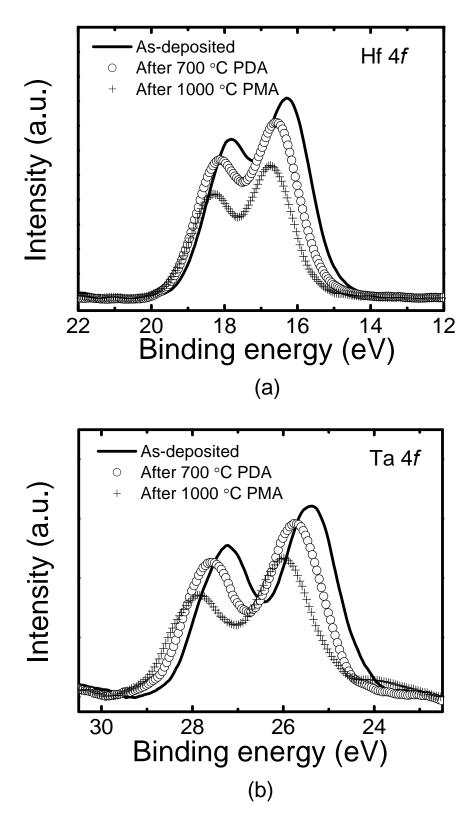

- Fig. 3.2 XPS peaks of (a) Hf 4f and (b) Ta 4f for as-deposited, 700°C p.73 PDA and 1000°C PMA annealed HfTaON/SiO<sub>2</sub> gate stack. It is notable that both Hf and Ta peaks move towards higher binding energy, and the intensity of the peaks are decreased with annealing temperature. No evidence of Hf-Si and Ta-Si bonds formation are observed in high temperature annealed films.

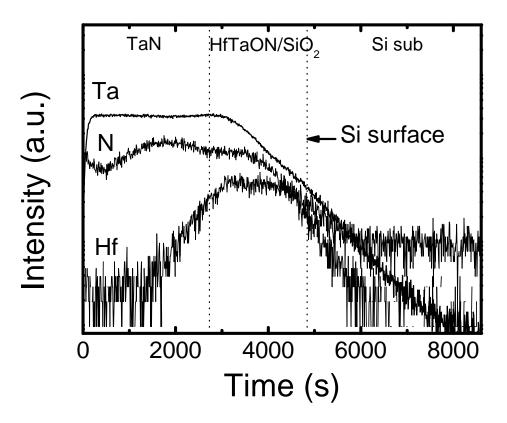

- **Fig. 3.3** SIMS profiles of Hf, Ta and N in HfTaON/SiO<sub>2</sub> film after p.74 annealing at 1000°C. The Hf, Ta, and N atoms mainly distribute away from Si surface.

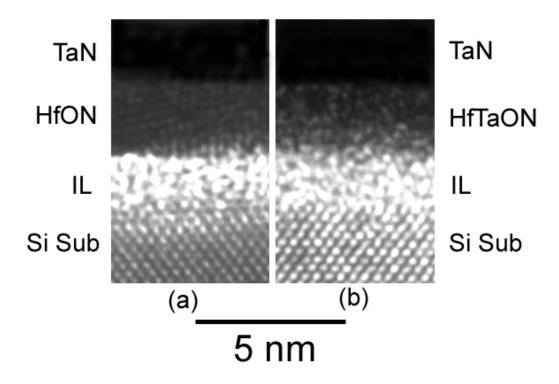

- **Fig. 3.4** TEM micrographs of (a) HfON/SiO<sub>2</sub> and (b) HfTaON/SiO<sub>2</sub> gate p.75 stack after PMA at 1000°C for 10sec. The HfON film is partially crystallized and the HfTaON remains amorphous structure.

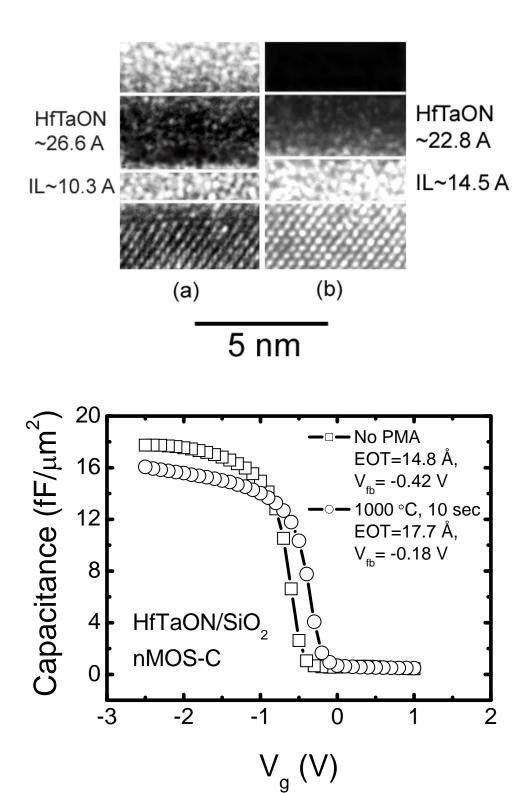

- **Fig. 3.5** TEM pictures of HfTaON/SiO<sub>2</sub> gate stack (a) without and (b) p.77 with PMA at 1000°C for 10sec. (c) corresponding *C-V* curves of HfTaON/SiO<sub>2</sub> nMOS capacitors without and with PMA at 1000°C for 10sec.

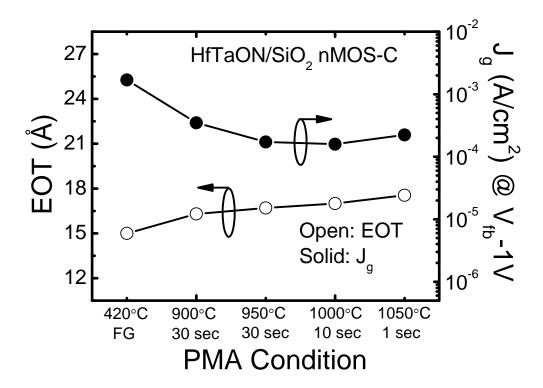

- **Fig. 3.6** EOT and gate leakage current as a function of the PMA p.78 condition. The increase in EOT with PMA temperature from 420°C to 1050°C is less than 3 Å for HfTaON/SiO<sub>2</sub>. The gate

leakage current decreases slightly with the PMA temperature, which is mainly due to the increase in *EOT*.

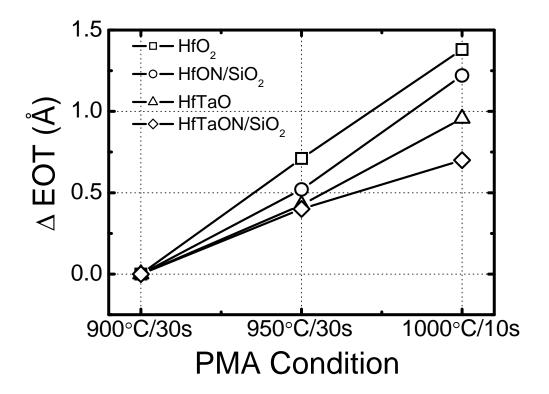

- **Fig. 3.7** The increase in *EOT* as a function of PMA conditions for HfO<sub>2</sub>, p.79 HfON/SiO<sub>2</sub>, HfTaO and HfTaON/SiO<sub>2</sub> gate stacks. The HfTaON/SiO<sub>2</sub> exhibits the lowest increase in EOT compare to other gate stacks, which indicates that the HfTaON/SiO<sub>2</sub> shows the best thermal stability among those gate stacks.

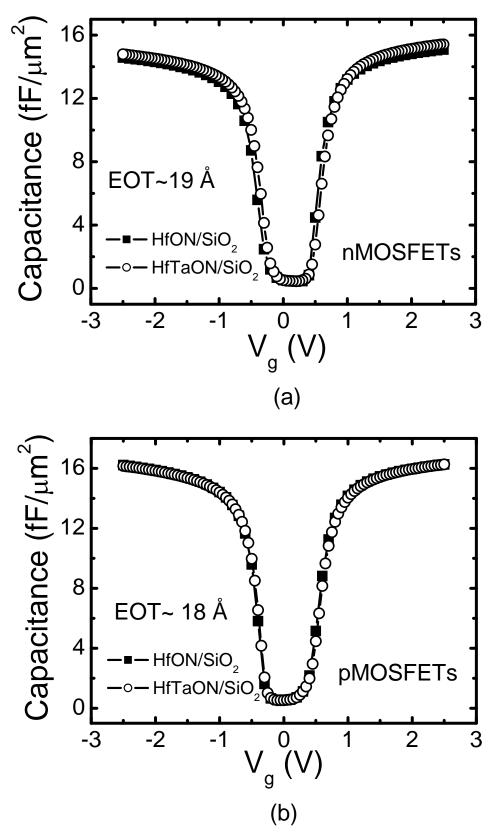

- Fig. 3.8 Typical *C-V* characteristics of (a) nMOSFETs and (b) p.80 pMOSFETs with HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks. The HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks show similar flat band voltage.

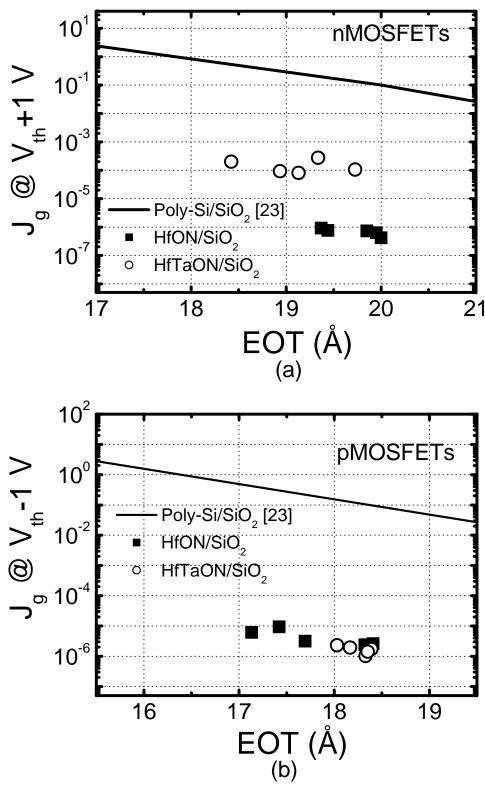

- **Fig. 3.9** EOT dependences of gate leakage currents at  $V_g = V_{th} \pm 1$ V for (a) p.82 nMOSFETs and (b) pMOSFETs with HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks, respectively. The gate leakage currents of HfTaON/SiO<sub>2</sub> are higher than HfON/SiO<sub>2</sub> in nMOSFETs, whereas similar with HfON/SiO<sub>2</sub> in pMOSFETs.

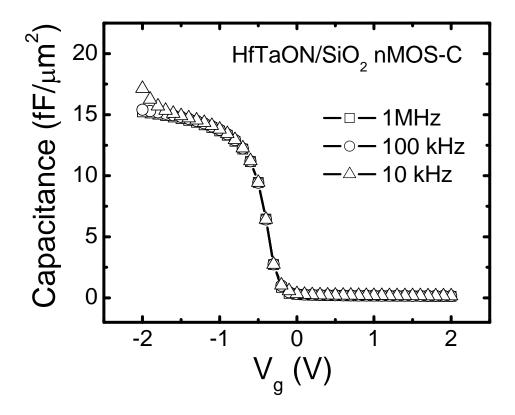

- **Fig. 3.10** HfTaON/SiO<sub>2</sub> nMOS capacitor shows negligible frequency p.83 dispersion at frequency range from 10kHz to 1MHz.

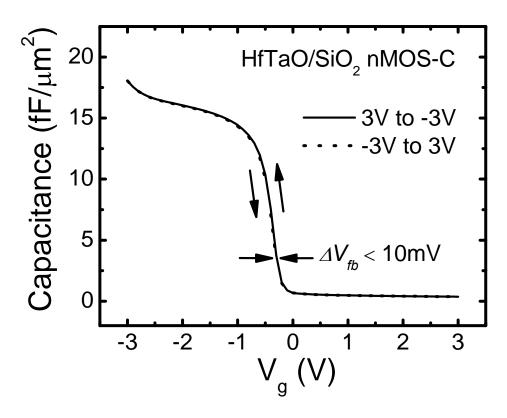

- **Fig. 3.11** Almost no *C-V* hysterisis for nMOS capacitor with HfTaON/ p.84 SiO<sub>2</sub> gate stack after sweeping between 3V and -3V.

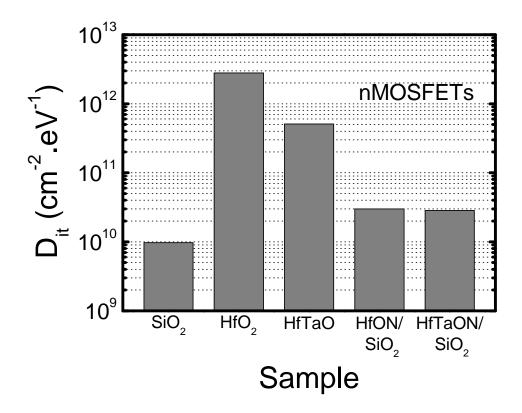

- **Fig. 3.12** Comparison of  $D_{it}$  at the midgap for nMOSFETs with SiO<sub>2</sub>, p.85 HfO<sub>2</sub>, HfTaO, HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks. The HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks show similar  $D_{it}$ , however, they are still slightly higher than that in SiO<sub>2</sub>.

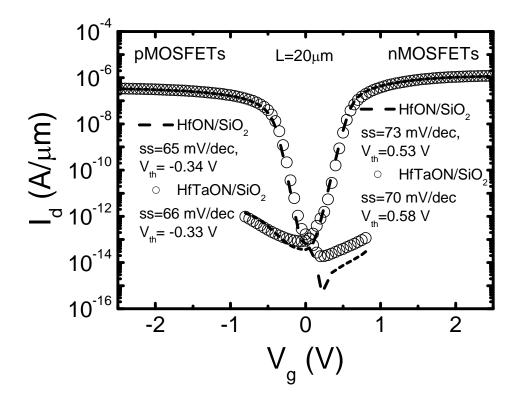

- **Fig. 3.13**  $I_d$ - $V_g$  curves for MOSFETs with HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> p.86 gate stacks. The HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks show similar threshold voltages and sub-threshold swings for both nMOS and pMOSFETs.

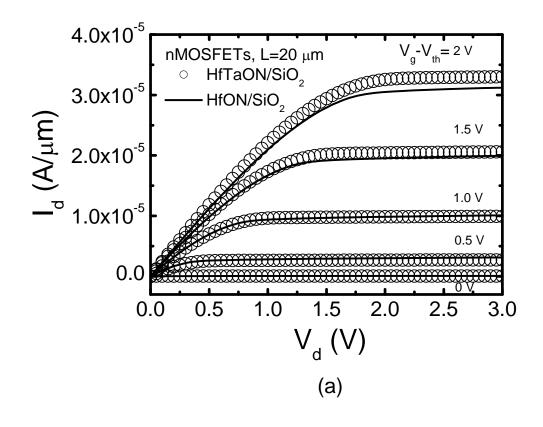

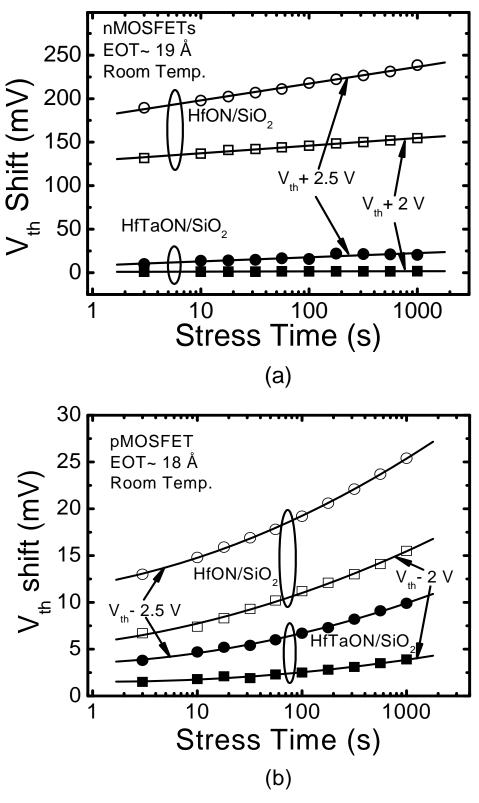

- **Fig. 3.14**  $I_d$ - $V_d$  characteristics for (a) nMOSFETs and (b) pMOSFETs with p.87 HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks.

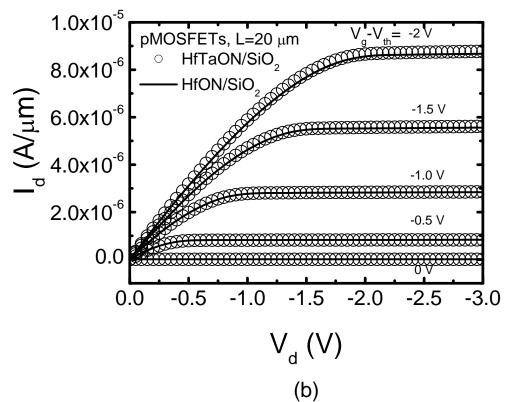

- **Fig. 3.15** Comparison of (a) electron and (b) hole mobility in HfON/SiO<sub>2</sub> p.88 and HfTaON/SiO<sub>2</sub> MOSFETs. Both electron and hole mobility in HfON/SiO<sub>2</sub> are slightly lower than those in HfTaON/SiO<sub>2</sub> at low effective filed region, but almost no difference at middle or high effective filed region.

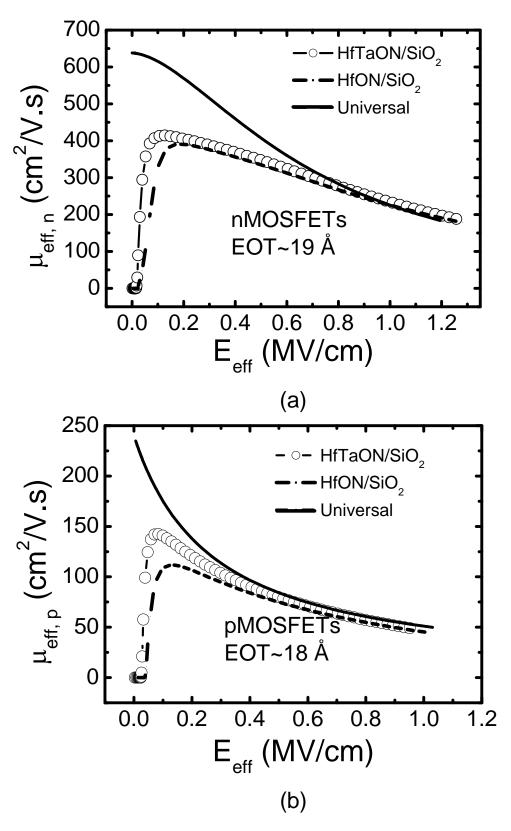

- **Fig. 3.16**  $V_{th}$  instability for (a) nMOSFETs and (b) pMOSFETs with p.91 HfON/SiO<sub>2</sub> and HfTaON/SiO<sub>2</sub> gate stacks under constant voltage stresses. The  $V_{th}$  shift in HfON/SiO<sub>2</sub> is remarkably suppressed by incorporating Ta.

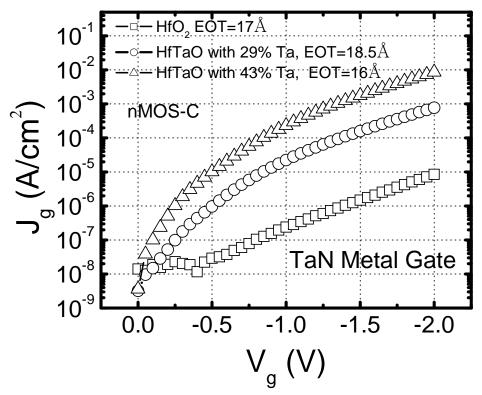

- **Fig. 4.1** Typical *J-V* curves of TaN metal gate MOS capacitors with p.100 HfO<sub>2</sub>, HfTaO with 29% and 43% Ta dielectrics after activation annealing at 950° C for 30sec. HfTaO dielectrics show higher leakage current compared to HfO<sub>2</sub>.

- **Fig. 4.2** Typical *J-V* curves of n<sup>+</sup> poly-Si gate MOS capacitors with p.100 HfO<sub>2</sub>, HfTaO with 29% and 43% Ta dielectrics after activation annealing at 950° C for 30sec. HfTaO dielectrics show lower leakage current compared to HfO<sub>2</sub>.

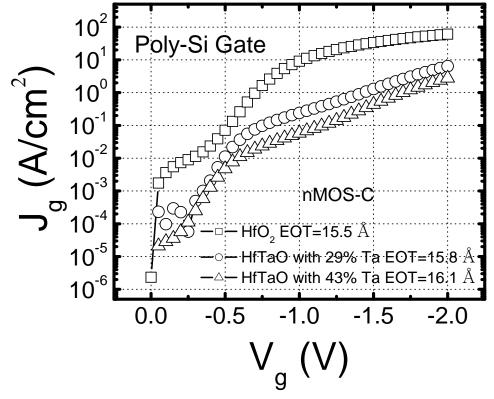

- **Fig. 4.3** (a) Comparison of gate leakage currents for the n<sup>+</sup> poly-Si gate p.104 and metal gate devices as a function of the gate bias. (b) *C-V* characteristics for S-1, S-2 and M-1 nMOS capacitors. The *C-V* curves of S-3 and S-4 cannot be measured due to the excessive gate leakage currents.

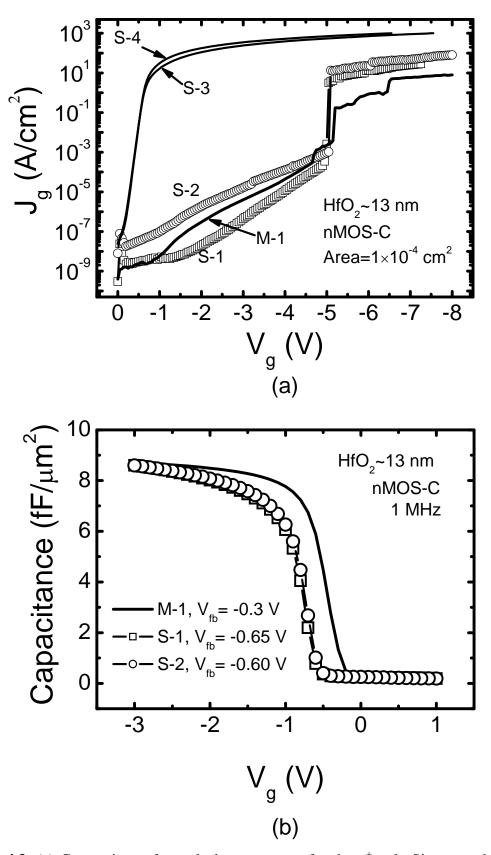

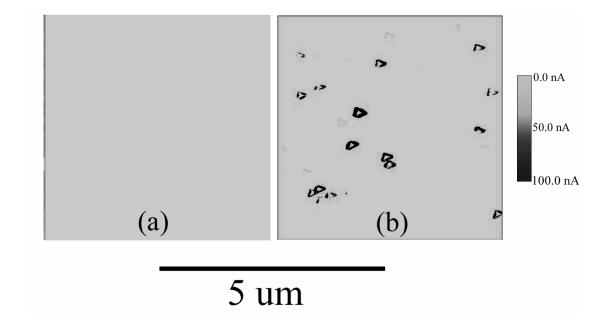

- Fig. 4.4 C-AFM current images of samples (a) S-1 and S-2, (b) S-3 and p.105 S-4 after removal of the poly-Si gates. The evident leakage paths are found in the HfO<sub>2</sub> films with heavy doping poly-Si gate (S-3 and S-4), whereas no leakage path are observed in the HfO<sub>2</sub> films with low doping poly-Si gates (S-1 and S-2) at the tip bias of 40 mV.

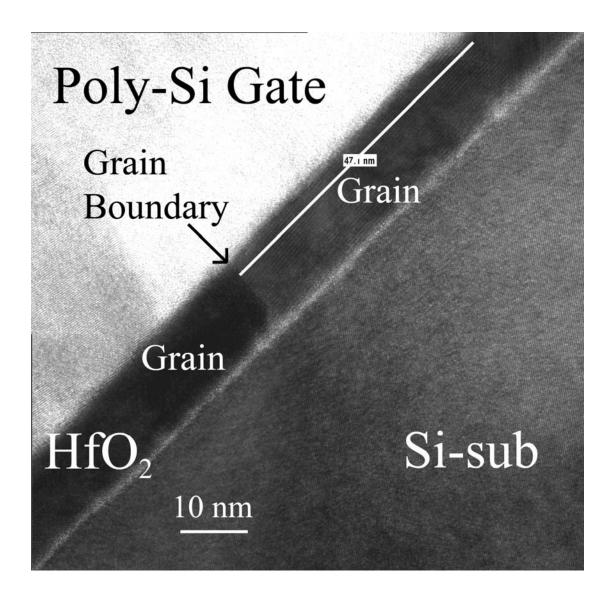

|          | HfO <sub>2</sub> film shows crystallized structure with obvious grain boundary.                                                                                                                                                                                                                                                              |       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

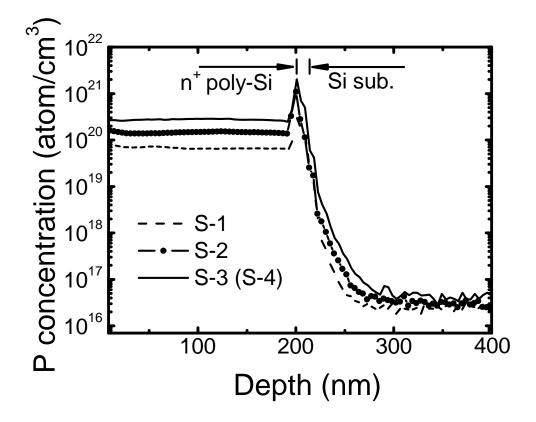

| Fig. 4.6 | SIMS profiles of phosphorus in the n <sup>+</sup> poly-Si/HfO <sub>2</sub> stacks after activation annealing at 1000°C for 10sec. The diffusion of phosphorus into HfO <sub>2</sub> gate dielectric becomes more serious with increasing the doping concentration of poly-Si gate. (S-3 and S-4 show similar phosphorus-diffusion profiles.) | p.108 |

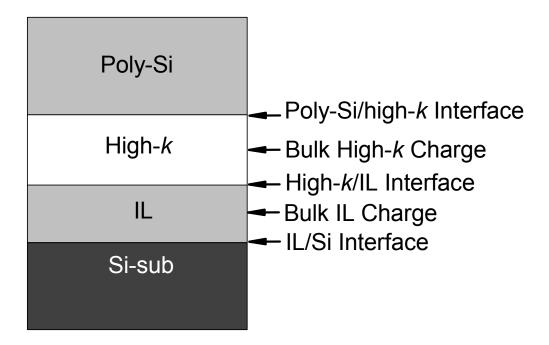

| Fig. 5.1 | Possible location of charges, which cause the $V_{th}$ shift.                                                                                                                                                                                                                                                                                | p.117 |

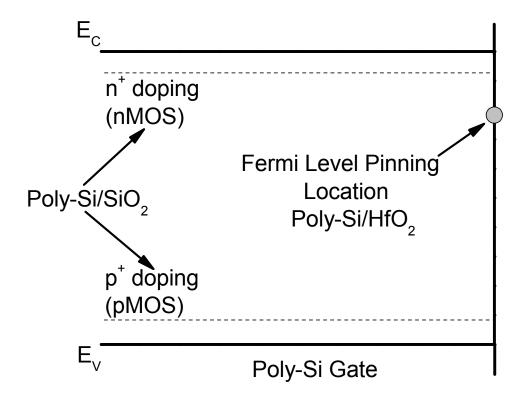

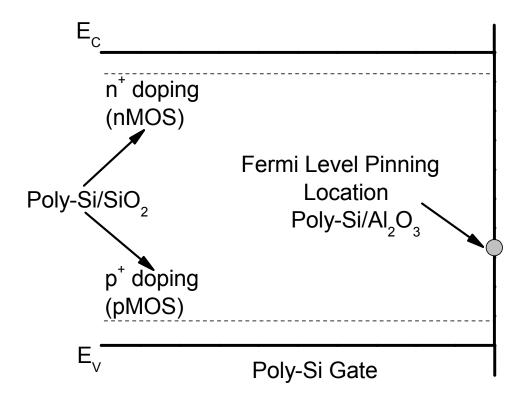

| Fig. 5.2 | Fermi Level Pinning Location in poly-Si/HfO <sub>2</sub> .                                                                                                                                                                                                                                                                                   | p.119 |

| Fig. 5.3 | Fermi Level Pinning Location in poly-Si/Al <sub>2</sub> O <sub>3</sub> .                                                                                                                                                                                                                                                                     | p.120 |

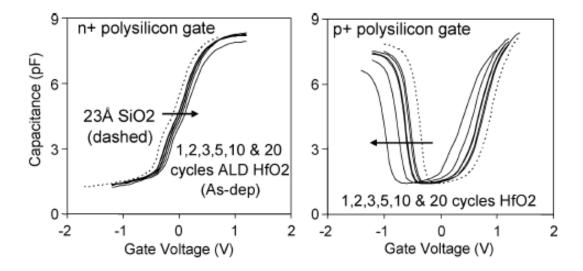

| Fig. 5.4 | $C\text{-}V$ curves for as-deposited sub-monolayer ALD HfO <sub>2</sub> pMOS devices with $n^+$ gate (left) and $p^+$ gate (right). Note that for each subsequent ALD cycle, the $C\text{-}V$ curve for the $n^+$ gate shifts to the right whereas the $C\text{-}V$ curve for $p^+$ gate shifts to the left.                                 | p.121 |

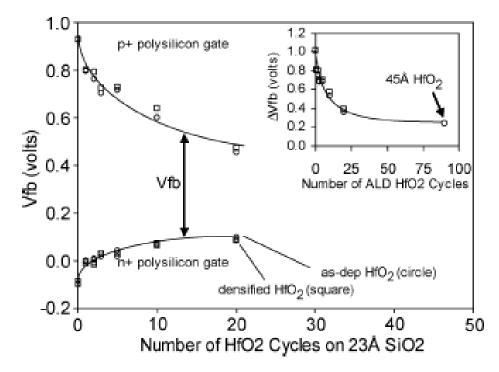

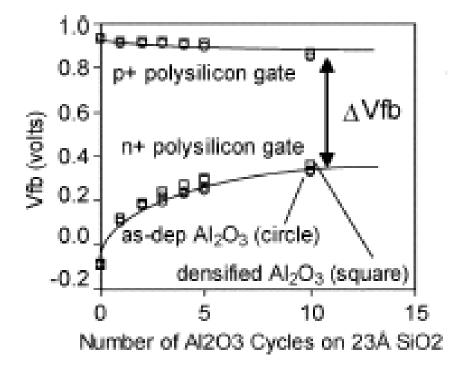

| Fig. 5.5 | $V_{fb}$ versus number of HfO <sub>2</sub> ALD cycles. (Inset: $\Delta V_{fb}$ versus number of HfO <sub>2</sub> ALD cycles.)                                                                                                                                                                                                                | p.122 |

| Fig. 5.6 | $V_{fb}$ versus number of HfO <sub>2</sub> ALD cycles.                                                                                                                                                                                                                                                                                       | p.122 |

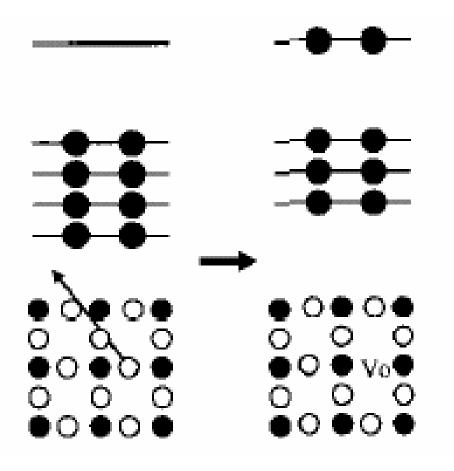

| Fig. 5.7 | Schematic illustration of generation of two surplus electrons by <i>Vo</i> formation in HfO <sub>2</sub> .                                                                                                                                                                                                                                   | p.124 |

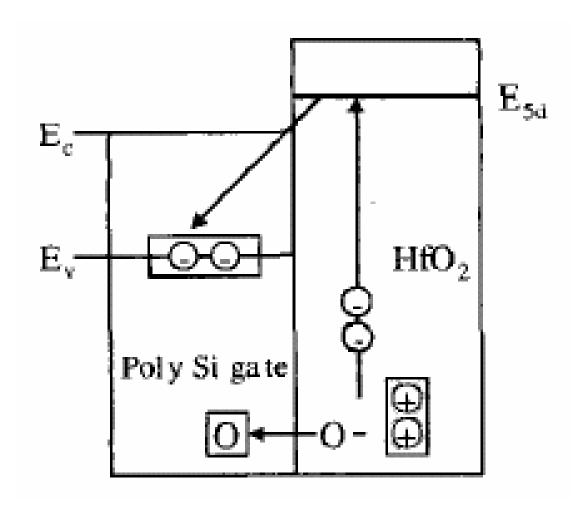

| Fig. 5.8 | Schematic illustration of <i>Vo</i> formation and subsequent electron transfer across the interface in poly-Si/HfO <sub>2</sub> structure.                                                                                                                                                                                                   | p.125 |

TEM image of the high leaky HfO<sub>2</sub> films (S-3 and S-4) with p.107

poly-Si gate after activation annealing at 1000°C for 10sec. The

Fig. 4.5

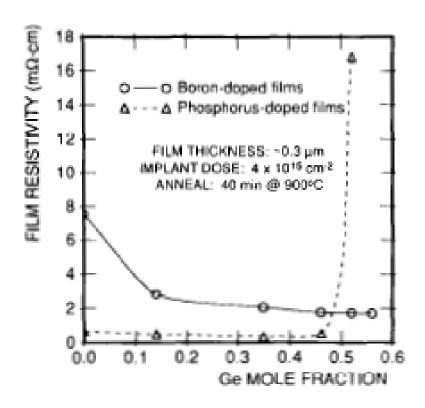

| Fig. 5.9  | Resistivity of heavily doped poly-SiGe films.                                                                                                                                                                                                                                                                            | p.127 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

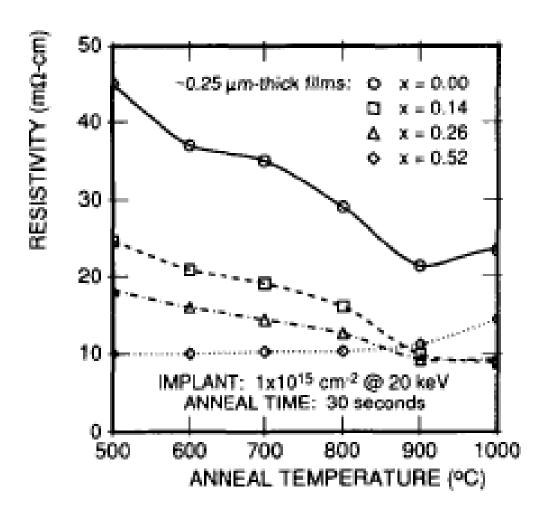

| Fig. 5.10 | Resistivity of poly-SiGe films implanted with boron and then annealed for 30sec each at successively higher temperatures.                                                                                                                                                                                                | p.128 |

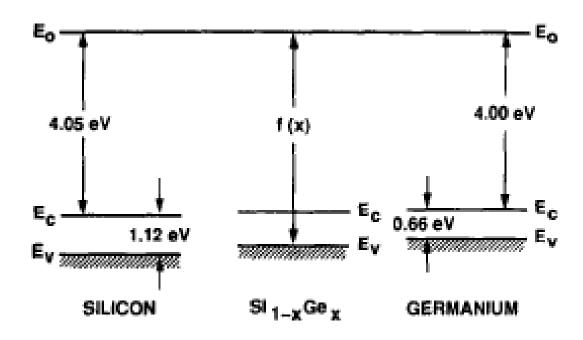

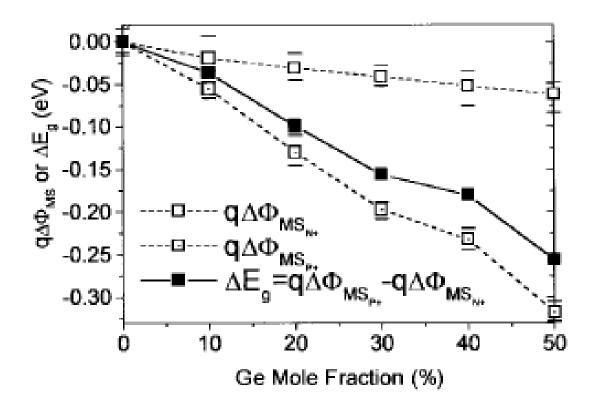

| Fig. 5.11 | Comparison of energy band levels in Si, SiGe, and Ge.                                                                                                                                                                                                                                                                    | p.130 |

| Fig. 5.12 | Reduction in poly-SiGe energy bandgap as a function of Ge mole fraction. The error bars represent the deviation of $\Phi_{MS}$ for each poly-SiGe film.                                                                                                                                                                  | p.131 |

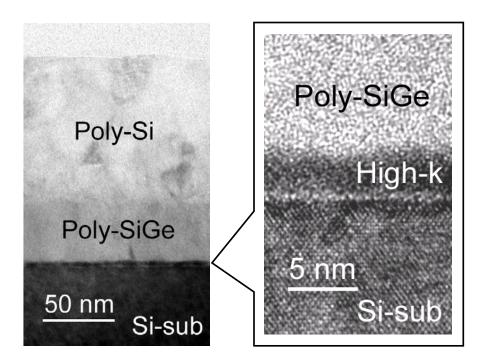

| Fig. 5.13 | TEM image of poly-Si/poly-SiGe/Al $_2$ O $_3$ /HfO $_2$ (GAH) gate stack (left) and high resolution TEM image of the high- $k$ gate dielectric of Al $_2$ O $_3$ /HfO $_2$ (right).                                                                                                                                      | p.134 |

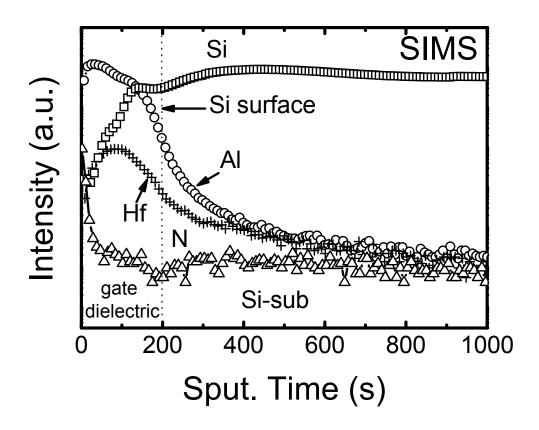

| Fig. 5.14 | SIMS profiles of Al, Hf, Si, and N in Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> /SiO <sub>2</sub> gate stack after activation annealing at 900°C. The concentration of N incorporated by PDA is around 5% (XPS result).                                                                                           | p.135 |

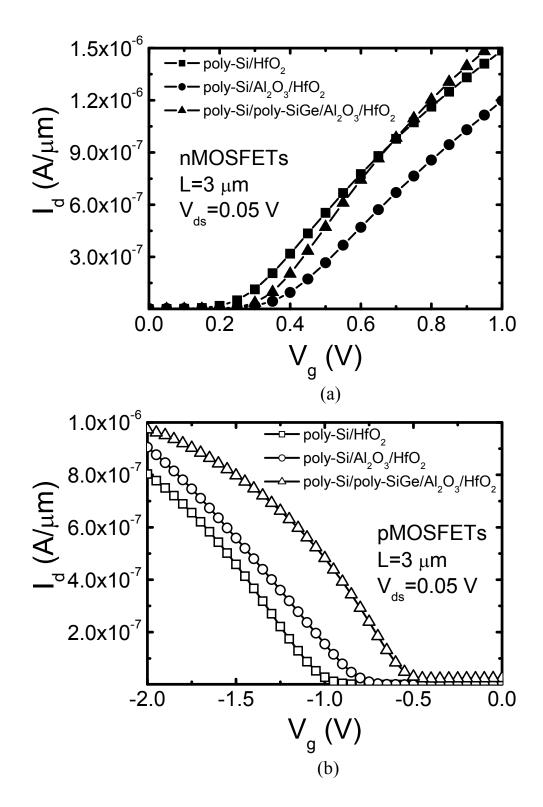

| Fig. 5.15 | (a) $I_D$ - $V_G$ curves for nMOSFETs with SH, SAH and GAH gate stacks. The $V_{th}$ for SH, SAH, and GAH nMOSFETs are 0.27, 0.37 and 0.30V, respectively. (b) $I_D$ - $V_G$ curves for pMOSFETs with SH, SAH and GAH gate stacks. The $V_{th}$ for SH, SAH, and GAH pMOSFETs are -1.02, -0.81 and -0.49V, respectively. | p.136 |

| Fig. 5.16 | Comparison of $V_{th}$ for both nMOS and pMOSFETs with SH, SAH, GAH gate stacks. The $V_{th}$ is tunable by using the poly-SiGe gate and $Al_2O_3$ capping layers.                                                                                                                                                       | p.137 |

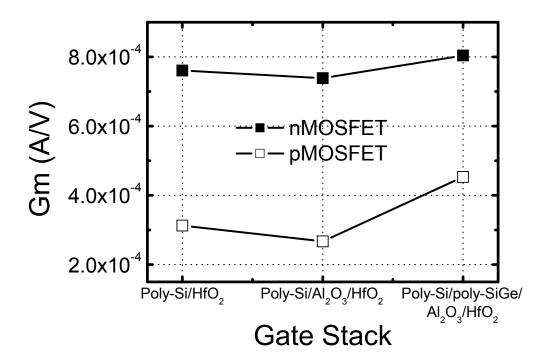

| Fig. 5.17 | Comparison of $G_m$ for both nMOS and pMOSFETs with SH, SAH, and GAH gate stacks. The $G_m$ in GAH gate stack is higher                                                                                                                                                                                                  | p.139 |

than in SH and SAH, in particular for pMOSFETs.

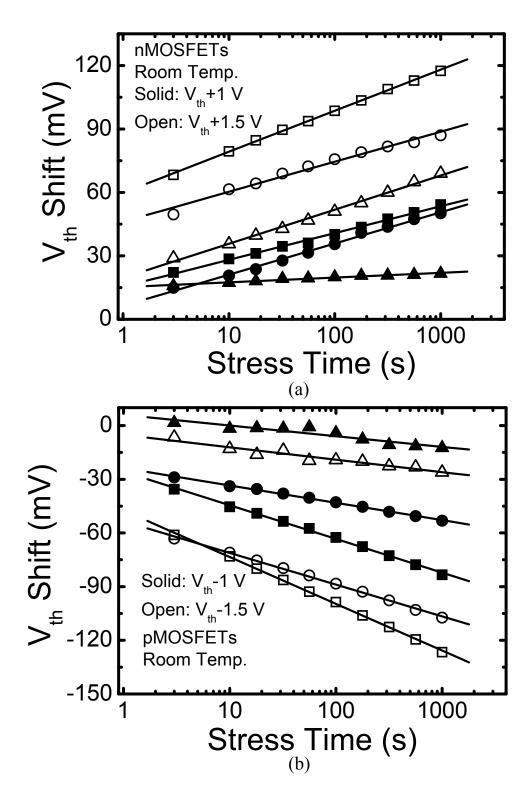

**Fig. 5.18** Comparison of the  $V_{th}$  instability for (a) nMOS and (b) p.140 pMOSFETs with SH, SAH and GAH gate stacks. The GAH gate

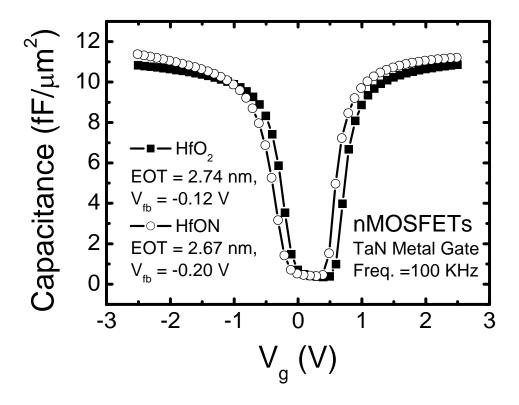

- **Fig. 6.1** *C-V* curves of TaN metal gate nMOSFETs with HfO<sub>2</sub> and HfON p.150 gate dielectrics. The HfON gate dielectric shows higher gate capacitance and negative shift in  $V_{fb}$  compared to HfO<sub>2</sub>.

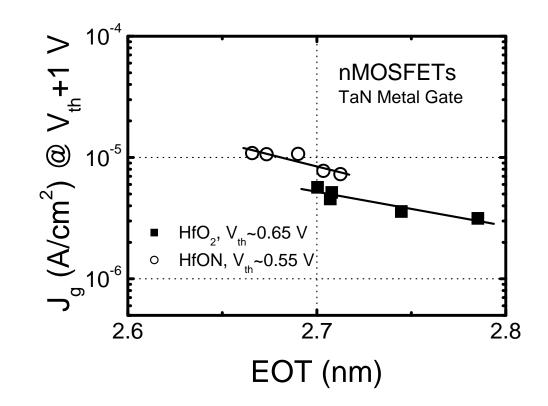

- **Fig. 6.2** EOT dependence of gate leakage currents at  $V_g=V_{th}+1$ V for TaN p.151 metal gate nMOSFETs with HfO<sub>2</sub> and HfON gate dielectrics. The leakage currents of HfON gate dielectric are slightly higher than that of HfO<sub>2</sub>.

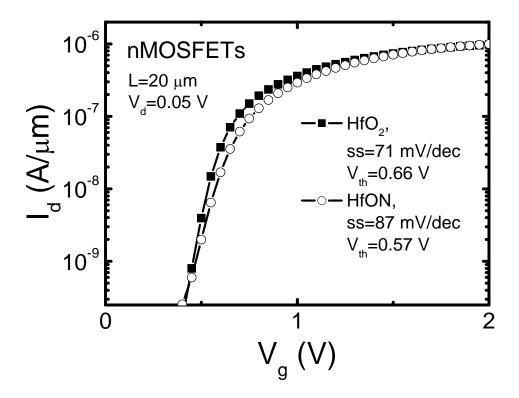

- **Fig. 6.3** Subthreshold characteristics for TaN metal gate nMOSFETs p.152 with HfO<sub>2</sub> and HfON gate dielectrics. The HfON exhibits higher subthreshold slope compared to HfO<sub>2</sub>.

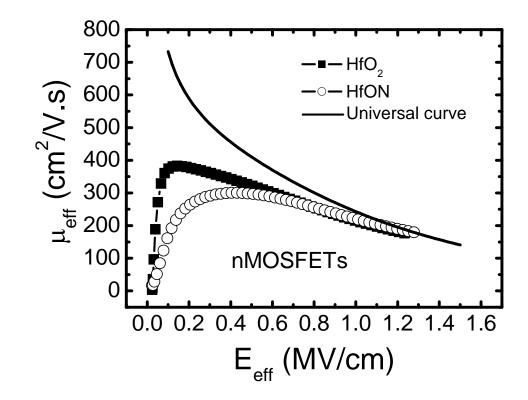

- Fig. 6.4 Effective electron mobility of TaN metal gate nMOSFETs with p.153 HfO<sub>2</sub> and HfON gate dielectrics. The electron mobility of HfON is lower than that of HfO<sub>2</sub> at low effective field region (<0.5 MV/cm), whereas no difference is found at medium and high effective field region.

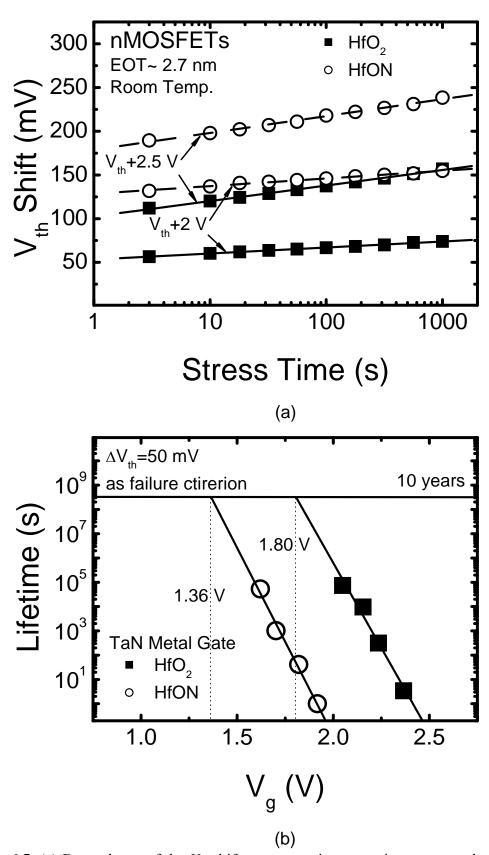

- Fig. 6.5 (a) Dependence of the V<sub>th</sub> shift on stress time at various stress p.154 voltages for TaN metal gate nMOSFETs with HfO<sub>2</sub> and HfON gate dielectrics.

(b) Lifetime projection of V<sub>th</sub> shift for TaN metal gate nMOSFETs with HfO<sub>2</sub> and HfON gate dielectrics.

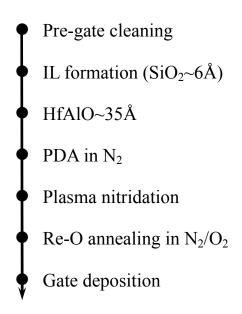

- **Fig. 6.6** Process flow of gate stacks formation (HfAlO with 26% Al). p.156

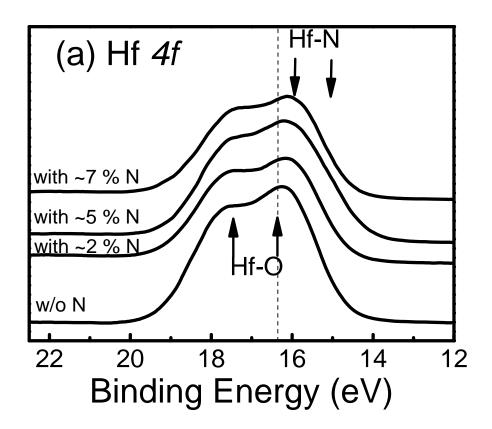

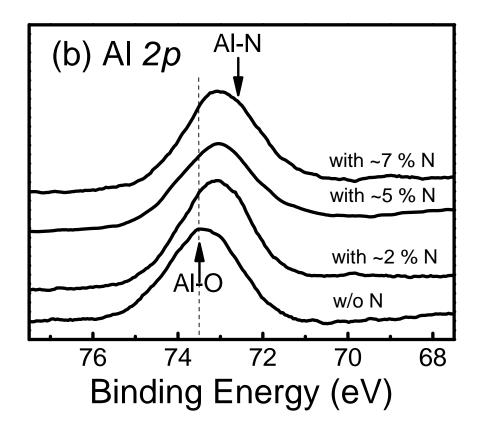

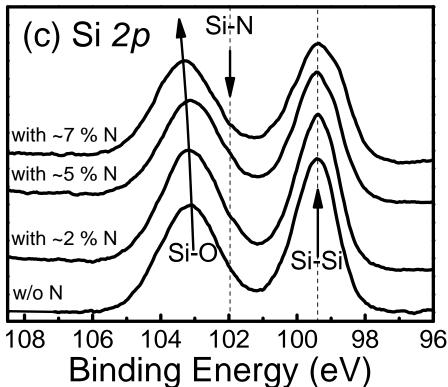

- Fig. 6.7 XPS spectra of (a) Hf 4f, (b) Al 2p, and (c) Si 2p for HfAlO with p.157 and without nitridation. It is noted that the Hf-O and Al-O -158 bonds move to lower binding energy position (Hf-N and Al-N) and the Si-O bond shifts to high binding energy.

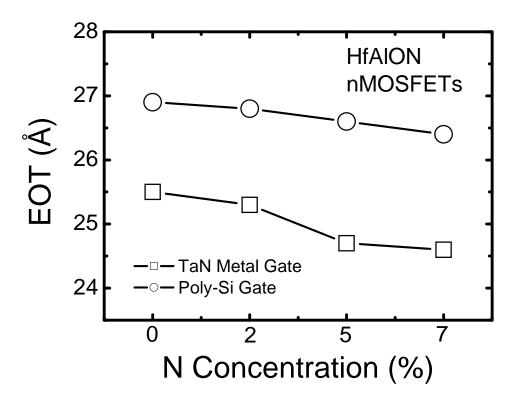

- Fig. 6.8 EOT as a function of N concentration in HfAlON gate p.159

dielectrics for both TaN and poly-Si gate nMOSFETs.

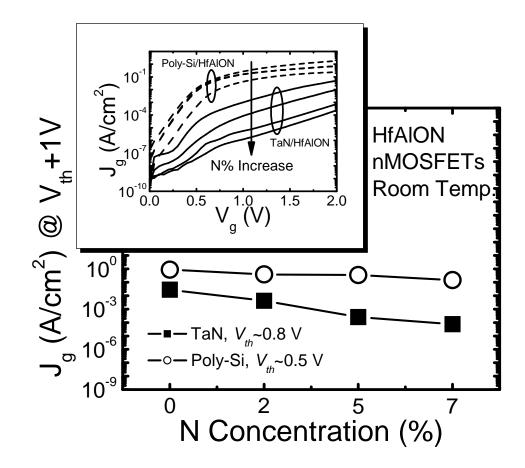

- **Fig. 6.9** Gate leakage currents (at  $V_g=V_{th}+1V$ ) as a function of the N p.160 concentration in HfAlON gate dielectrics for TaN and poly-Si nMOSFETs, and also the corresponding  $J_g-V_g$  curves are shown in the inset.

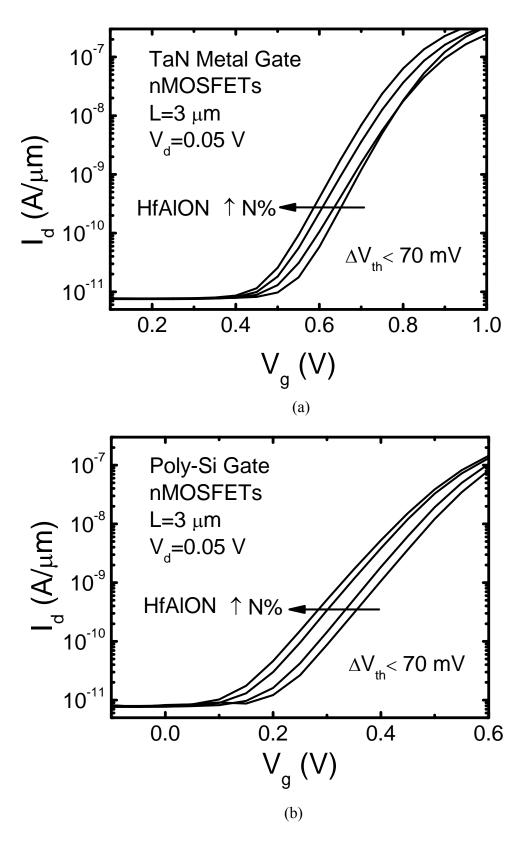

- **Fig. 6.10** Comparison of  $I_d$ - $V_g$  characteristics for (a) TaN metal and (b) p.161 poly-Si gate nMOSFETs with HfAlON with 0%, 2%, 5% and 7% nitrogen.

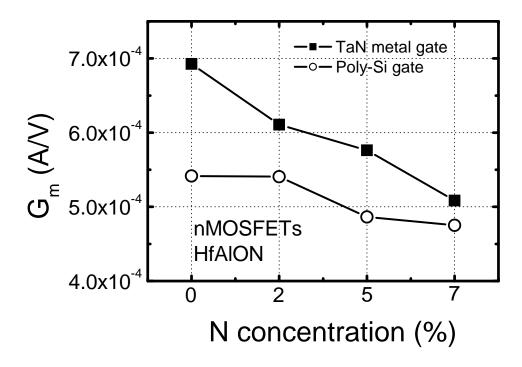

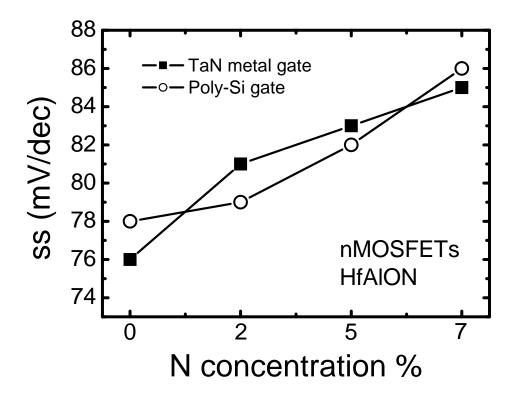

- **Fig. 6.11** Variation of  $G_m$  as a function of nitrogen concentration in p.162 HfAlON films for TaN metal and poly-Si gate nMOSFETs.

- **Fig. 6.12** Variation of *ss* as a function of nitrogen concentration in p.163 HfAlON films for TaN metal and poly-Si gate nMOSFETs.

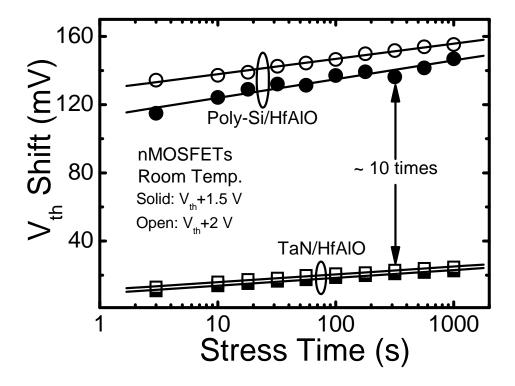

- **Fig. 6.13** Comparison of charge trapping induced  $V_{th}$  shift in HfAlO films p.164 between TaN metal and poly-Si gate nMOSFETs.

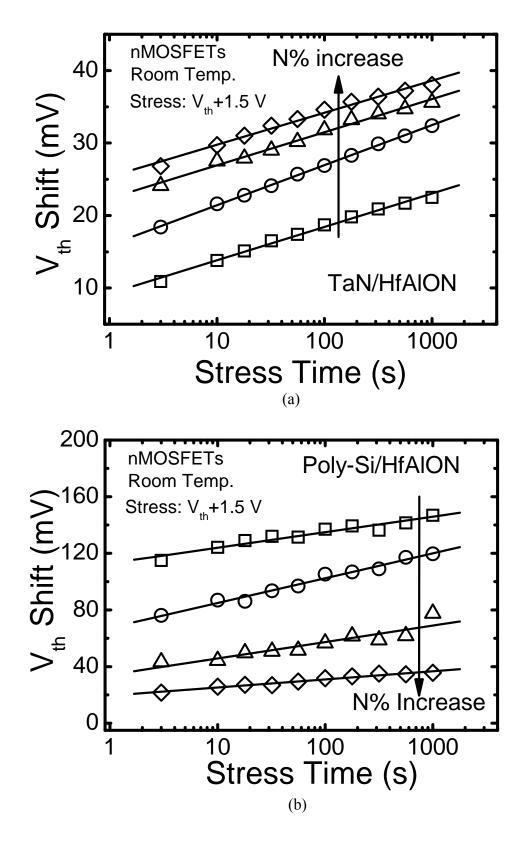

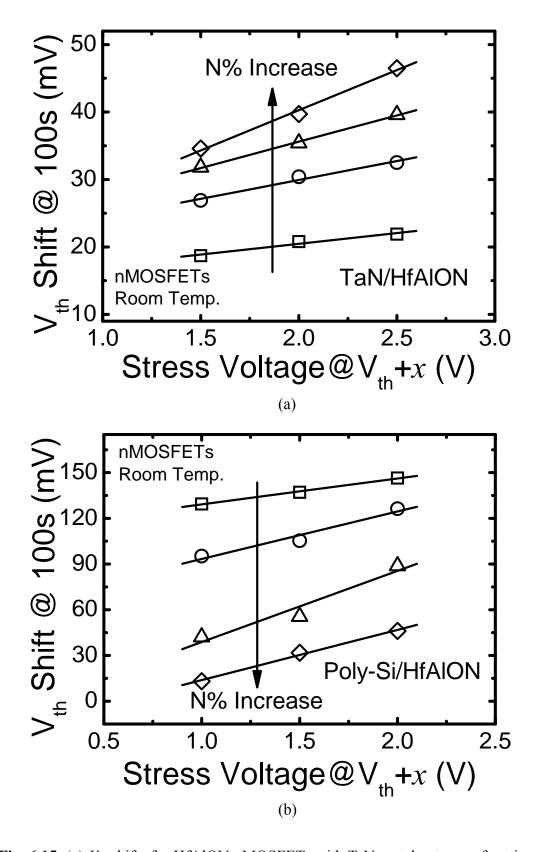

- **Fig. 6.14** (a)  $V_{th}$  shift in HfAlON nMOSFETs with TaN metal gate. The p.165  $V_{th}$  shift increases with increasing nitrogen concentration. (b)  $V_{th}$  shift in HfAlON nMOSFETs with poly-Si gate. The  $V_{th}$  shift decreases with increasing nitrogen concentration.

- **Fig. 6.15** (a)  $V_{th}$  shifts for HfAlON nMOSFETs with TaN metal gate as a p.167 function of applied stress voltages.

- (b)  $V_{th}$  shifts for HfAlON nMOSFETs with poly-Si gate as a function of applied stress voltages.

# **Chapter 1**

#### Introduction

#### 1.1 Introduction of Device Scaling

#### 1.1.1 Evolution of ULSI Technology

It has been sixty years since the invention of the bipolar transistor (1947), around fifty years since the invention of the integrated circuit (IC) technology (1958), and more than forty-five years since the invention of the metal oxide semiconductor field effect transistor (MOSFET, 1960). During the period, there has been an unprecedented growth of the semiconductor industry, which has made an enormous impact on the way people work and live. At the beginning of the semiconductor industry, the semiconductor market was broadly based on bipolar transistors. In the last three decades, the most prominent growth area of the semiconductor industry has been in silicon IC technology, which has evolved from small-scale integration (SSI), to medium-scale integration (MSI), to large-scale integration (ULSI), to very-large-scale integration (VLSI), and finally to ultra-large-scale integration (ULSI). By far, the ULSI technology has infiltrated practically every aspect of our daily life.

The most important ULSI device is, of course, the MOSFET because of its advantages in device miniaturization, low power dissipation, and high yield compared to all other semiconductor devices. The MOSFET also serves as a basic component for many key device building blocks, including the complementary metal oxide semiconductor (CMOS), the dynamic random access memory (DRAM), and the static

random access memory (SRAM). Therefore, the ULSI device is almost synonymous with the silicon MOSFET.

The sustained growth in ULSI technology is driven by the continuous scaling of MOSFET to ever smaller dimensions. The benefits of miniaturization, such as higher packing densities, higher circuit speeds, and lower power consumption, have been the key factors in the evolutionary progress leading to today's computers and communication systems that offer superior performance, dramatically reduced cost per function, and much reduced physical size, in comparison with their predecessors.

The primary motivation for continuous scaling of MOSFET is to increase transistors per chip, which may reduce cost effectively. During the most of time in semiconductor industry's history, the behavior of scaling of MOSFET has followed the well-known Moore's law, which predicts that the number of transistors per chip would be double every 18 months [1]. At this rate, the transistors per chip have been increased from 10<sup>3</sup> in the year of 1972 to more than 10<sup>9</sup> of today's leading-edge technology. In the meantime, cost per function has decreased at an average rate of ~ 25-30% per year per function [2]. In the past fifty years, cost per function has gone down by 100 million times. By 2000, the price per bit is less than 0.1 milli-cents for a 64-megabit memory chip. Similar price reductions are expected for logic ICs. Additional benefits from device miniaturization include improvement of device speed and reduction of power consumption. Higher speed leads to expanded IC functional throughput rates, so that future ICs can perform data processing, numerical computation, and signal conditioning at 100 and higher gigabit-per-second rates [3]. Reduced power consumption results in lowering of the energy required for each switching operation. The required energy, called the power-delay product, has decreased by six orders of magnitude since 1960 [4].

#### 1.1.2 Device Scaling Approaches

ULSI technology evolution in the past few decades has followed the path of device scaling for achieving "smaller, cheaper and faster" circuit. MOSFET scaling

has been propelled by the rapid advancement of lithographic techniques for delineating channel length of 1  $\mu$ m and below. However, the MOSFET with channel length below 1  $\mu$ m normally results in short-channel effect. For a short-channel MOSFET, the depletion charge controlled by the gate is reduced because part of the depletion charge under the gate is controlled by the source-drain junctions [5]. The most undesirable short-channel effect is a reduction in the gate threshold voltage ( $V_{th}$ ) at which the device turns on, especially at high drain voltages. Full realization of benefits of new high-resolution lithographic techniques therefore requires the suitable device scaling rules that can keep short-channel effects under control at very small dimensions.

There are various sets of device scaling rules aimed at reducing the device size while keeping device function, such as constant-field scaling, constant-voltage scaling, and the generalized scaling rules [6-8].

In constant-field scaling, it was proposed that one can keep short-channel effects under control by scaling down the vertical dimensions (gate insulator thickness, junction depth, etc.) along with the horizontal dimensions, while also proportionally decreasing the applied voltages and increasing the substrate doping concentration (decreasing the depletion width). The principle of constant-field scaling is to scale the device voltages and the device dimensions (both horizontal and vertical) by a same factor, so that the electric field remains unchanged. However, the requirement to reduce the applied voltages by the same factor as the reduction of physical dimension in constant-field scaling is difficult to implement since the threshold voltage and sub-threshold slope are not easily controlled for scaling [9]. If the scaling of threshold voltage is lower than other factors, the drive current would be reduced. Thus, a constant-voltage scaling rule was proposed to address this issue, where the voltages remain unchanged while device dimensions are scaled. However, constant-voltage scaling will result in an extremely high electric field, which causes unacceptable leakage current, power consumption, and dielectric breakdown as well as hot-carrier effects [9]. To avoid the extreme cases of constant-field and constant-voltage scaling, a generalized scaling approach has been developed, where the electric field is scaled

by a factor of  $\kappa$  while the device dimensions are scaled by a factor of  $\alpha$  [7]. In **Table 1.1**, the technology scaling rules for constant-field, constant-voltage and generalized scaling schemes are compared.

**Table 1.1**: The technology scaling rules for constant-field, constant-voltage and generalized scaling [6-8]

| MOSFET Device and Circuit                   | Multiplicative Factor for MOSFET's |              |                     |  |

|---------------------------------------------|------------------------------------|--------------|---------------------|--|

| parameters                                  | Constant E                         | Constant V   | Generalized         |  |

| Device Dimensions $(T_{ox}, L_g, W, X_j)$   | $1/\alpha$                         | $1/\alpha$   | $1/\alpha$          |  |

| Voltage (V)                                 | $1/\alpha$                         | 1            | κ/α                 |  |

| Electric Field (E)                          | 1                                  | α            | К                   |  |

| Capacitance ( $C = \varepsilon A/t$ )       | $1/\alpha$                         | $1/\alpha$   | $1/\alpha$          |  |

| Inversion Layer Charge Density $(Q_i)$      | 1                                  | α            | К                   |  |

| Circuit Delay Time ( $\tau \sim CV/I$ )     | $1/\alpha$                         | $1/\alpha^2$ | 1/κα                |  |

| Power per Circuit ( <i>P~VI</i> )           | $1/\alpha^2$                       | α            | $\kappa^3/\alpha^2$ |  |

| Power-Delay Product per Circuit ( $P\tau$ ) | $1/\alpha^3$                       | $1/\alpha$   | $\kappa^2/\alpha^3$ |  |

| Circuit Density ( $\propto 1/A$ )           | $\alpha^2$                         | $\alpha^2$   | $\alpha^2$          |  |

| Power Density (P/A)                         | 1                                  | $\alpha^3$   | K <sup>3</sup>      |  |

(α: Dimensional Scaling Factor; κ: Voltage Scaling Factor)

In reality, the CMOS technology evolution has followed mixed steps of constant-field, constant-voltage and generalized scaling, as shown in **Table 1.2**.

**Table 1.2**: CMOS ULSI technology generations [9]

| Feature Size (μm) | Power-Supply | Gate Oxide    | Oxide Field |

|-------------------|--------------|---------------|-------------|

|                   | Voltage (V)  | Thickness (Å) | (MV/cm)     |

| 2                 | 5            | 350           | 1.4         |

| 1.2               | 5            | 250           | 2.0         |

| 0.8               | 5            | 180           | 2.8         |

| 0.5               | 3.3          | 120           | 2.8         |

| 0.35              | 3.3          | 100           | 3.3         |

| 0.25              | 2.5          | 70            | 3.6         |

#### 1.1.3 Scaling and Improved Performance

The industry's demand for greater integrated circuit functionality and performance at lower cost requires an increased circuit density, which has translated into a higher density of transistors on a chip. This rapid shrinking of the transistor feature size has forced the channel length and gate dielectric thickness to also decrease rapidly.

From a ULSI circuit performance point of view, an improved performance requires to reduce the dynamic response (i.e., charging and discharging) of the MOSFET, associated with a decrease of switching time  $\tau$ . The switching time is limited by the fall time required to discharge the load capacitance or the rise time required to charge the load capacitance by the drive current. In the case where parasitic capacitances are ignored, an increase in the device drive current  $I_D$  results in a decrease in the switching time or improvement on the performance. The drive current can be written as:

$$I_{D} = \frac{W}{L} \mu C_{inv} (V_{G} - V_{th}) V_{D}, (V_{D} << V_{G})$$

(1-1)

Where W is the width of the transistor channel, L is the channel length,  $\mu$  is the channel carrier mobility (assumed constant here),  $C_{inv}$  is the capacitance density

associated with the gate dielectric when the underlying channel is in the inverted state,  $V_G$  and  $V_D$  are the voltages applied to the transistor gate and drain, respectively, and the threshold voltage is given by  $V_{th}$ . Initially,  $I_D$  increases linearly with  $V_D$  and then eventually saturates to a maximum when  $V_{D, sat} = V_G - V_{th}$  to yield, then

$$I_{D,sat} = \frac{W}{L} \mu C_{inv} \frac{(V_G - V_{th})^2}{2}$$

(1-2)

The term  $(V_G-V_{th})$  is limited in range due to reliability and room temperature operation constraints, since too large a  $V_G$  would create an undesirable, high electric field across the oxide. Furthermore,  $V_{th}$  cannot easily be reduced below about 200 mV. This is due to the non-scalability of the sub-threshold slope, and also reducing  $V_{th}$  below 200 mV would lead to high off-state leakage current  $I_{off}$ . Typical specification temperature ( $\leq 100$  °C) could therefore cause statistical fluctuations in thermal energy, which would adversely affect the desired the  $V_{th}$  value. Thus, even in this simplified approximation, a reduction in the cannel length or an increase in the gate capacitance will result in an increased  $I_{D, sat}$ .

If one ignores quantum mechanical and depletion effects from a Si substrate and gate, the gate capacitance is given by

$$C = \frac{k\varepsilon_0 A}{t_{eq}} \tag{1-3}$$

Where k is the dielectric constant (also referred to as the relative permittivity) of the gate dielectric,  $\varepsilon_0$  is the permittivity of free space (=8.85×10<sup>-3</sup> fF/ $\mu$ m), A is the area of the gate, and  $t_{eq}$  is the equivalent oxide thickness (EOT) of the gate dielectric. It is easily seen then that a decrease in the  $t_{eq}$  of dielectric results in an increase in the gate capacitance.

The term EOT represents the theoretical thickness of SiO<sub>2</sub> that would be required to achieve the same capacitance density as the dielectric. For example, if the capacitor dielectric is SiO<sub>2</sub>, the EOT is the thickness of the SiO<sub>2</sub>. If the capacitor dielectric is an alternative dielectric, such as high-k gate dielectric, the physical thickness of the high-k ( $t_{high-k}$ ) employed to the EOT can be obtained form the expression:

$$\frac{EOT}{k_{SiO_2}} = \frac{t_{high-k}}{k_{high-k}} \tag{1-4}$$

or simply,

$$t_{high-k} = \frac{k_{high-k}}{k_{SiO_2}} EOT = \frac{k_{high-k}}{3.9} EOT$$

(1-5)

Thus, a dielectric with a relative permittivity of 19.5 affords a physical thickness of 50 Å to obtain *EOT* of 10 Å.

Consequently, the improved performance associated with the increase in the device drive current  $I_D$  of MOSFET requires rapid shrinking of MOSFET channel length, which has forced the gate dielectric thickness (EOT) to also decrease rapidly. The channel length of MOSFET has been scaled from 25  $\mu$ m of the first MOSFET to the ~0.035  $\mu$ m (65 nm node) of today's leading-edge technology, while the gate dielectric thickness has been decreased from 1000 Å to around 12 Å, respectively. Scaling theory in conjunction with observation of past industry trends (e.g., Moore's law) has led to the creation of so-called roadmaps for semiconductor technology. The most public and widely agreed roadmap is the International Technology Roadmap for Semiconductors (ITRS) [2]. The ITRS is a statement of the historical trend as well as a projection of the future device needs and performances as perceived at the time of formulation of the roadmap. Based on the prediction of ITRS, the MOSFET with channel length of 10 nm and equivalent oxide thickness of 5 Å would be required for mass production by the year of 2015.

#### 1.2 Scaling Limits for Conventional Gate Dielectrics

#### 1.2.1 Limitations of SiO<sub>2</sub> as the Gate Dielectric for Advanced CMOS Devices

For the past several decades, the robust SiO<sub>2</sub> has always been used as the gate dielectric in CMOS technology. The use of amorphous, thermally grown SiO<sub>2</sub> as the gate dielectric offers several key advantages in CMOS processing, including a stable (thermodynamically and electrically), high-quality interface as well as superior

electrical isolation properties. In modern CMOS processing, the defect charge densities are of the order of 10<sup>10</sup>/cm<sup>2</sup>, and midgap interface state densities are ~ 10<sup>10</sup>/cm<sup>2</sup>-eV in SiO<sub>2</sub>/Si system. Moreover, hard breakdown fields (electric fields that result in a catastrophic increase in the resultant tunneling current through the dielectric) of 15 MV/cm are routinely obtained in SiO<sub>2</sub> regardless of the transistor dimensions. In addition, minimal low-frequency *C-V* hysterisis and frequency dispersion (< 10 mV), minimal dielectric charging and interface degradation, and the sufficiently high carrier mobility (both electrons and holes) can be usually obtained for the MOSFET with SiO<sub>2</sub>/Si system [2]. The apparent robust natures of SiO<sub>2</sub>, coupled with industry's acquired knowledge of oxide process control, have been the key elements enabling the continuous scaling of SiO<sub>2</sub> gate dielectric for the past several decades in CMOS technology.

Despite this remarkable contribution of SiO<sub>2</sub>, the continuous scaling of SiO<sub>2</sub> gate dielectric thickness is problematic in advanced CMOS technology. The major concerns are the unacceptably high leakage current under the required operating voltages, boron penetration from poly-Si gate, and reliability issue.

Since the dominant transport mechanism through gate dielectric less than  $\sim$ 30 Å thick is by direct tunneling of electrons or holes, the leakage current increases exponentially with decreasing thickness due to the fundamental quantum mechanical rules [10]. For example, a typical leakage current density for 15-Å-thick SiO<sub>2</sub> at 1 V is  $\sim$ 1 A/cm<sup>2</sup>. As the SiO<sub>2</sub> thickness approaches 10 Å, the leakage current density increases to 100 A/cm<sup>2</sup> at the same operating voltage. Based on experimental evidence of the excellent electrical properties of such ultra-thin SiO<sub>2</sub> film, it has been demonstrated that MOSFET with SiO<sub>2</sub> thickness as thin as 13-15 Å continue to operate satisfactorily, however, the high leakage currents of 1-10 A/cm<sup>2</sup> (at  $V_{DD}$ ) were measured for such devices [11]. The rapid increase in leakage current with the decrease of the SiO<sub>2</sub> thickness would lead to heat dissipation and power consumption problems regarding to the operation of CMOS devices, especially with respect to standby power dissipation. As first reported by Timp et al. [12], scaling of CMOS structures with SiO<sub>2</sub> gate dielectric thinner than about 10-12 Å results in no further

gains in transistor drive current, which is due to the high gate leakage induced inversion charge loss.

In addition to leakage current increasing with scaled SiO<sub>2</sub> thickness, the issue of boron penetration through the SiO<sub>2</sub> gate dielectric is a significant concern. The large gradient between the heavily doped poly-Si gate electrode, the undoped SiO<sub>2</sub> and lightly doped Si channel causes boron to diffuse rapidly through a ultrathin SiO<sub>2</sub> upon thermal annealing, which results in a higher concentration of boron in the channel region. A change in channel doping then causes a shift in  $V_{th}$ , which clearly alters the intended device properties in an unacceptable way [13].

An equally important issue regarding ultrathin  $SiO_2$  gate dielectric is oxide reliability [14-16]. The carriers traveling through the  $SiO_2$  gate dielectric may generate defects including carrier traps and interface states, and upon accumulation to the critical density, the dielectrics properties will be degraded. The accumulated charge to breakdown values  $(Q_{bd})$  for the dielectrics decreases with the thickness [14]. Recently, it was predicted that oxide films thinner than  $\sim 14$  Å may not achieve the reliability required by the industry roadmap [15].

#### 1.2.2 SiON and Si<sub>x</sub>N<sub>y</sub>/SiO<sub>2</sub> Gate Dielectrics

The concerns regarding high leakage currents, boron penetration and reliability of ultra-thin SiO<sub>2</sub> have led to materials structures such as SiON and Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> stacks for near-term gate dielectric alternatives. These structures provide a slightly higher k value than SiO<sub>2</sub> (pure Si<sub>3</sub>N<sub>4</sub> has  $k \sim 7$ ) for reduced leakage due to the physically thicker film (as discussed in **Eq. 1-5**), reduced boron penetration and better reliability characteristics [17-19]. Furthermore, small amounts of N ( $\sim$ 0.1%) at or near the Si channel interface have been shown to control channel hot-electron degradation effects [20]. However, large amounts of N near this interface degrade device performance, which is attributed to several factors, including excess charge induced by N atoms, a high defect density arising from bonding constraints imposed at the interface [21] (which causes increased channel carrier scattering), and from the defect

levels in the Si-nitride layer which reside near the valence band of Si. In contrast, improved electrical properties have been obtained by using  $Si_xN_y/SiO_2$  gate stack, which can achieve EOT < 17 Å with a leakage current of  $\sim 10^{-3}$  A/cm<sup>2</sup> at 1.0 V bias [22].

**Table 1.3**: ITRS 2005 for the scaling of dielectric thickness with year [2]

| Year                                                 | 2005  | 2006  | 2007  | 2008  | 2009  |

|------------------------------------------------------|-------|-------|-------|-------|-------|

| Physical gate length for high performance (nm)       | 32    | 28    | 25    | 22    | 20    |

| Physical gate length for low operating power (nm)    | 45    | 37    | 32    | 28    | 25    |

| Physical gate length for low standby power (nm)      | 65    | 53    | 45    | 37    | 32    |

| EOT for high performance (Å)                         | 12    | 11    | 11    | 9     | 7.5   |

| EOT for low operating power (Å)                      | 14    | 13    | 12    | 11    | 10    |

| EOT for low standby power (Å)                        | 21    | 20    | 19    | 16    | 15    |

| Maximum gate leakage for high performance (A/cm²)    | 188   | 536   | 800   | 909   | 1100  |

| Maximum gate leakage for low operating power (A/cm²) | 33    | 41    | 78    | 89    | 100   |

| Maximum gate leakage for low standby power (A/cm²)   | 0.015 | 0.019 | 0.022 | 0.027 | 0.031 |

(The dark color indicates no solution until now)

This leakage current is  $\sim 100$  times lower than that for a pure SiO<sub>2</sub> layer of the same *EOT*, and the leakage reduction arises from both a physically thicker film and from a small amount of N at the channel interface.

Despite these encouraging results from a variety deposition and growth techniques, scaling with the SiON and  $Si_xN_y/SiO_2$  appears to be limited to  $EOT\sim13$  Å [23]. Below this, the effects of gate leakage, reliability or electron channel mobility degradation will most likely prevent further improvements in devices performance. On the other hand, it has been suggested that 7 Å is the physical thickness limit for  $SiO_2$  or SiON, because the  $SiO_x$  sub-oxide region at any oxide/Si interface is  $\sim3.5$  Å thick and there are two oxide/Si interfaces at the channel and the gate electrode. According to the most recent ITRS, the current gate dielectrics ( $SiO_2$  or SiON) may only represent current two years near-term solutions for scaling the CMOS transistors [2], as shown in **Table 1.3**.

Consequently, the aggressive shrinking of gate dielectric thickness is driving the conventional SiO<sub>2</sub> or SiON gate dielectrics to its physical limit and the research groups in semiconductor industry have difficulty in searching any alternative gate dielectric candidates for future CMOS application.

# 1.3 Alternative High-k Gate Dielectrics

As discussed in the previous sections, the continued aggressive scaling of the MOSFETs for leading-edge technology in order to maintain historical trends of improved device performance is driving the conventional SiO<sub>2</sub> or SiON gate dielectric to its physical limits. The major concerns are unacceptably high leakage current under the required operating voltages, boron penetration from poly-Si gate, and reliability issue. As an alternative to SiO<sub>2</sub> or SiON gate dielectric, many works have been done on high-*k* materials as a means to provide a substantially thicker (physical thickness) dielectric for reduced leakage current and improved gate capacitance. According to ITRS 2005, the high-*k* gate dielectric will be required beginning in ~2008 [2]. Therefore, the timely implementation of high-*k* gate dielectric is an imperative task

for maintaining the historical trend of device scaling in semiconductor industry.

#### 1.3.1 Selection Guidelines for High-k Gate Dielectrics

All of the alternative high-k materials must meet a set of criteria to perform as successful gate dielectric. In this section, a systematic consideration of the required properties of the appropriate high-k materials will be discussed for the gate dielectric application.

#### 1.3.1.1 Permittivity and Barrier Height

Selection of a gate dielectric with a higher permittivity than that of SiO<sub>2</sub> is clearly essential. As mentioned in **Eq. 1-5**, a dielectric with a higher permittivity may provide a physically thicker film to achieve the same EOT, and also reduce the leakage current. However, it has been reported that the materials with ultra-high permittivity may cause fringing field induced barrier lowering effect when it was used as the gate dielectric [24]. The fringing field induced barrier lowering effect predicts that the device off-state leakage current increases as k value increases (become significant especially when k > 25), which is due to that a significant fringing field at the edge of a high-k dielectric could lower the barrier for carriers transport into the drain, and hence seriously degrade the on/off characteristics of the device. It is therefore appropriate to find a dielectric with moderate k value for advanced CMOS gate dielectric application. A single dielectric layer with  $k \sim 12-25$  could allow a physical dielectric thickness of 35–50 Å to obtain the EOT values required for 65 nm CMOS and beyond.

In order to obtain low leakage currents, it is desirable to find a gate dielectric that has large band offset for both electrons and holes ( $\Delta E_C$  and  $\Delta E_V$ ). Since the  $\Delta E_C$  and  $\Delta E_V$  of many potential gate dielectrics have not been reported, the closest, most readily attainable indicator of band offset is the band gap ( $E_G$ ) of the dielectric. A large  $E_G$  generally corresponds to a large  $\Delta E_C$ , but the band structure for some materials has a large valence band offset  $\Delta E_V$  which constitutes most of the band gap

of the dielectric (such as Ta<sub>2</sub>O<sub>5</sub>).

The  $E_G$  of the dielectric should be balanced against its dielectric constant. The dielectric constant generally increases with increasing atomic number for a given cation in a metal oxide. However, the band gap energy of the metal oxides tends to decrease with increasing atomic number [25]. **Table 1.4** shows the comparison of relevant properties for various gate dielectric materials. As can be seen, the band gap energy tends to decrease with increasing the dielectric constant.

**Table 1.4** Comparison of relevant properties for various gate dielectric materials. [26-28]

| Dielectric                     | Dielectric constant (K) | Gap energy (eV) | Electron barrier to Si (eV) |

|--------------------------------|-------------------------|-----------------|-----------------------------|

| SiO <sub>2</sub>               | 3.9                     | 8.8             | 3.15                        |

| $Si_3N_4$                      | 7.8                     | 5.1             | 2.1                         |

| $Al_2O_3$                      | 8 – 11.5                | ~6.5 - 8.7      | ~2.4 - 2.8                  |

| $ZrO_2$                        | 22 - 28                 | ~5.5 - 5.8      | ~1.4 - 2                    |

| ZrSiO <sub>4</sub>             | 10 – 12                 | ~6              | 1.5                         |

| $HfO_2$                        | 25 – 30                 | ~5.25 - 5.7     | ~1.5 - 1.9                  |

| HfSiO <sub>4</sub>             | ~10                     | ~6              | 1.5                         |

| $TiO_2$                        | ~80                     | 3.5             | ~1.2                        |

| Ta <sub>2</sub> O <sub>5</sub> | ~25                     | ~5              | ~0.3 - 0.5                  |

#### 1.3.1.2 Thermodynamic Stability on Si and Film Morphology

For all thin gate dielectrics, the interface with Si plays a key role, and in most cases is the dominant factor in determining the overall electrical properties. Most of the high-k metal oxide systems investigated so far have unstable interfaces with Si:

the reaction between high-*k* materials and Si during high thermal budget process to form an undesirable interfacial layer. Moreover, the thickness of the undesirable interfacial layer normally increases with the temperature of process, which results in an increased *EOT* (thermodynamic instability). The thermal stability of gate oxides on silicon in the subsequent high-temperature process also has a critical impact on the Si/dielectric interface quality. One high-temperature process from a typical CMOS process flow is the source/drain (S/D) activation annealing (up to 1000°C), for which the gate dielectric must undergo such high-temperature annealing. Also, the increase in the interfacial layer due to the high-temperature annealing is desirable to be suppressed.

On the other hand, most of alternative gate dielectrics are polycrystalline films after the subsequent high-temperature process, but it is desirable to select a material which remains in an amorphous structure after such process. The polycrystalline gate dielectrics may be problematic because grain boundaries serve as high-diffusion paths of oxygen and dopants, causing undesirable interfacial layer growth, electrical instability, and defect generation [29]. In addition, grain size and orientation changes throughout the polycrystalline film could cause significant variations in dielectric constant, leading to irreproducible properties.

#### 1.3.1.3 Interface Quality

A clear goal of any potential high-k gate dielectric is to obtain a sufficiently high-quality interface with the Si channel, as close as possible to that of SiO<sub>2</sub>. The typical production SiO<sub>2</sub> gate dielectrics have a midgap interface state density ( $D_{it}$ ) of  $\sim 2\times 10^{10}$  states/cm<sup>2</sup>, whereas most of the high-k materials show  $D_{it} \sim 10^{11}$ - $10^{12}$  states/cm<sup>2</sup>. Obviously, it is difficult to deposit any high-k material creating a better interface than that of SiO<sub>2</sub>. Due to the high  $D_{it}$  observed in high-k gate dielectrics, degradation in leakage current and carrier mobility are therefore expected. The ideal gate dielectric stack could have an interfacial layer comprised of several monolayers of Si-O containing material to improve interface properties, and also a high-k film on

top of the interfacial layer to provide physically thicker gate dielectric.

# 1.3.1.4 Process Compatibility

A crucial factor in determining the final film quality and properties is the method by which the dielectrics are deposited in a fabrication process. The deposition process for the dielectric must be compatible with current or expected CMOS processing, cost, and throughput. Physical vapor deposition (PVD) methods have provided a convenient means to evaluate materials systems for alternate dielectric applications. However, the damage inherent in a sputtering PVD process results in surface damage and thereby creates unwanted interfacial states. For this reason, chemical vapor deposition (CVD) methods, such as metal organic chemical vapor deposition (MOCVD) and atomic layer chemical vapor deposition (ALCVD), have proven to be quite successful in providing uniform coverage over complicated device topologies.

On the other hand, a significant issue for integrating any advanced gate dielectric into standard CMOS is that the dielectric should be compatible with poly-Si gate process. Poly-Si gates are desirable because dopant implant conditions can be tuned to create the desired  $V_{th}$  for both nMOS and pMOS, and also the process integration schemes are well established in industry. Moreover, metal gate are very desirable for eliminating dopant depletion effects and sheet resistance constraints, thus the metal gate has been widely investigated for future CMOS gate application.

# 1.3.1.5 Reliability

The electrical reliability of a new gate dielectric must also be considered critically for application in CMOS technology. The determination of whether or not a high-k dielectric satisfies the strict reliability criteria requires a well-characterized materials system. Moreover, recent lessons from the scaling changes associated with ultrathin SiO<sub>2</sub> may come into play with the high-k dielectric. Several major reliability issues observed in high-k gate dielectric are described as follows:

### (1) Charge Trapping in High-k Gate Dielectrics