## HIGH PERFORMANCE CONTROL OF A THREE-

## PHASE PWM RECTIFIER

**YIN BO**

NATIONAL UNIVERSITY OF SINGAPORE

2008

## HIGH PERFORMANCE CONTROL OF A THREE-PHASE PWM RECTIFIER

### **YIN BO**

(M.Eng., Wuhan University, China)

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### DEPARMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2008

## Acknowledgements

I would like to express my gratitude to all those who gave me their support to complete this thesis. First and foremost, I am deeply indebted to my supervisor Prof. Ramesh Oruganti whose constant guidance, sustaining encouragement and stimulating suggestions helped me all the time during my doctoral research and writing up this thesis. Without him, I could not have finished my research work smoothly. As a mentor, he was always there to discuss my ideas, to help me to think through my problems and to teach me to write academic papers. I would like to express my sincere thanks to him for his patience during my learning process. As an experienced advisor, he was always there to help me to reduce stress due to my challenging research, to advise research schedules and to provide opportunities for me to attend conferences and future career. I would like to thank for his considerateness and kindness to me and all his students. I learnt a lot from him not only to be a precise researcher but also to be a nice person.

I would like to give my thanks to Prof. Panda, my co-supervisor, for his invaluable advice and help throughout my study. I will never forget his always timely help and his unreserved supervision in the advanced control field. Without his effort, it would have taken longer for me to finish my research.

I would also like to thank Prof. Bhat for his encouragement, guidance and support. From him, I learnt how to be a precise scholar.

I would like to thank Prof. Loh Ai Poh, Prof. Dipti Srinivasan, Prof. Xu Jian-Xin and Prof. Wang Qin-Guo for their valuable comments and suggestions.

i

I am grateful to National University of Singapore for supporting this research project through the research grant R-263-000-190-112.

I thank lab officers Mr. Woo Ying Chee, Mr. Chandra, Mr. Teo Thiam Teck and Mr. Seow Hung Cheng for their kind help whenever I have troubles. Special thanks go to Mr. Abdul Jalil Bin Din for his prompt PCB fabrication services and Mr. Johari Bin Khamis for his timely components provision.

As a research scholar, my stay in the Centre for Power Electronics of NUS was made pleasant by many of my friends. Foremost among them is Dr. Viswanathan Kanakasabai, who not only shares with me his knowledge, but also his happiness. Among the other friends, I would like to thank Chen Yu, Cao Xiao, Heng Deng, Hu Ni, Krishna Mainali, Kong Xin, Li Yanlin, Liu Min, Qin Meng, Marecar Hadja, Niu Pengying, Ravinder Pal Singh, Sahoo S. K., Wang Wei, Wu Xinhui, Wei Guannan, Xu Xinyu,Ye Zhen, Yang Yuming and Zhou Haihua.

Deep in my heart are special thanks to my husband, Deng Heng. His love has accompanied me through bad and good moments. Finally, I want to thank my parents who made all this possible. I dedicate this thesis to them and to Prof. Ramesh Oruganti.

## **Table of Contents**

| Сн   | APTER 1                 | INTRODUCTION                                                                                        | 1   |

|------|-------------------------|-----------------------------------------------------------------------------------------------------|-----|

| 1.0  | Backgro                 | und                                                                                                 | 1   |

| 1.1  | PWM ree                 | ctifier system operating under balanced supply voltage conditions.                                  | 4   |

| 1.2  | PWM ree                 | ctifier system operating under unbalanced supply voltage condition                                  | 1s5 |

| 1.3  | Research                | objectives                                                                                          | 6   |

| 1.4  | Thesis co               | ontributions                                                                                        | 7   |

| 1.5  | Thesis or               | ganization                                                                                          | 11  |

| Сн   | APTER 2                 | LITERATURE SURVEY ON CONTROL SCHEMES FOR THR                                                        | EE- |

|      | Рна                     | SE PWM RECTIFIERS                                                                                   | 14  |

| 2.0  | Introduct               | ion                                                                                                 | 14  |

| 2.1  | Models of               | of a PWM rectifier operating under balanced supply voltages                                         | 15  |

|      | 2.1.1                   |                                                                                                     |     |

|      | 2.1.2<br>2.1.3          | Model in stationary frame (SF)<br>Models in synchronously rotating frame (SRF)                      |     |

| 2.2  |                         | ctifier systems operating under balanced supply voltage conditions                                  |     |

|      |                         | Linear controllers                                                                                  |     |

|      | 2.2.2<br>2.2.3<br>2.2.4 |                                                                                                     | 32  |

| 2.3  |                         | ctifiers operating under unbalanced supply voltage conditions– a survey                             | 38  |

|      | 2.3.1                   | Voltage-oriented control methods                                                                    |     |

|      | 2.3.2<br>2.3.3          | Ripple-oriented control method<br>Power-oriented control method                                     |     |

|      | 2.3.4                   |                                                                                                     |     |

| 2.4  | Conclusio               | ns                                                                                                  | 49  |

| Сн   |                         | THREE-PHASE BOOST-TYPE PWM RECTIFIER UNDER<br>ANCED SUPPLY VOLTAGE CONDITIONS                       |     |

| 3.0  |                         | ion                                                                                                 |     |

| 3.1  |                         | und                                                                                                 |     |

| 3.2  | •                       | ISO model of a three-phase PWM rectifier                                                            |     |

| _ /_ | 3.2.1<br>3.2.2          | Equivalent circuit for a three-phase PWM rectifier<br>Non-linear feed-forward decoupling controller | 55  |

|     | 3.2.4                                                       | A simple SISO model<br>Small signal model using the state space averaging approach<br>Limitation on achievable performance of the voltage loop                                                                                                                                                                             | 64                              |

|-----|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.3 | Experime                                                    | ental verification of the proposed dual SISO model                                                                                                                                                                                                                                                                         | 71                              |

| 3.4 | •                                                           | mode control and current mode control - design examples and ental results                                                                                                                                                                                                                                                  | 80                              |

|     |                                                             | Voltage Mode Control Design<br>Current mode control design<br>The <i>q</i> -axis controller design                                                                                                                                                                                                                         | 83                              |

| 3.5 | Closed lo                                                   | oop experimental verification of the proposed controllers                                                                                                                                                                                                                                                                  | 85                              |

|     | 3.5.1<br>3.5.2<br>3.5.3<br>3.5.4                            | Measurement of closed-loop loop transfer function Bode plots<br>Steady-state operation - experimental results<br>Transient operation - experimental results<br>Experimental results under unbalanced supply voltage operation                                                                                              | 89<br>90                        |

| 3.6 | Conclusi                                                    | ons                                                                                                                                                                                                                                                                                                                        | 100                             |

| Сн  | Рная                                                        | Output Power Control Strategy for a Three-<br>se PWM Rectifier under Unbalanced Supply<br>tage Conditions                                                                                                                                                                                                                  |                                 |

| 4.0 |                                                             | ion                                                                                                                                                                                                                                                                                                                        |                                 |

|     | Positive-                                                   | and negative- sequence equivalent circuits for an unbalanced P system                                                                                                                                                                                                                                                      | WM                              |

| 4.2 | Proposed                                                    | output power control strategy                                                                                                                                                                                                                                                                                              | 108                             |

|     | 4.2.2<br>4.2.3                                              | Background<br>Proposed control strategy<br>Control Scheme<br>Fheoretical vector power factor with the output power control method                                                                                                                                                                                          | 110                             |

| 4.3 | Experime                                                    | ental results                                                                                                                                                                                                                                                                                                              | 121                             |

| 4.4 | Conclusi                                                    | ons                                                                                                                                                                                                                                                                                                                        | 126                             |

| Сн  |                                                             | IMPLEMENTATION ISSUES IN PARTIAL OUTPUT POWE<br>TROL STRATEGY                                                                                                                                                                                                                                                              |                                 |

| 5.0 | Introduct                                                   | ion                                                                                                                                                                                                                                                                                                                        | 128                             |

| 5.1 | Analysis                                                    | of different implementation methods of the OPC method                                                                                                                                                                                                                                                                      | 131                             |

|     | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7 | Background.         Estimation of the rectifier bridge input voltages.         Implementation of OPC method using Estimation Method 1.         Implementation of OPC method using Estimation Method 2.         Discussion on parameter k.         Simulation verification.         Comments on OPC implementation methods. | 132<br>134<br>140<br>143<br>145 |

| 5.2 |                                                             | tion of the reason for the poor performance of the POPC metho                                                                                                                                                                                                                                                              |                                 |

|     |                                                             |                                                                                                                                                                                                                                                                                                                            | 14/                             |

|     |                                                    | Introduction to the POPC method                                                                                                                                                                                                                                                                 |

|-----|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3 | Improved                                           | l realization of the POPC Method151                                                                                                                                                                                                                                                             |

| 5.4 | Simulatio                                          | on and experimental verification152                                                                                                                                                                                                                                                             |

| 5.5 | Discussio                                          | on157                                                                                                                                                                                                                                                                                           |

| 5.6 | Conclusio                                          | ons157                                                                                                                                                                                                                                                                                          |

| Сн  |                                                    | PERFORMANCE ASSESSMENT OF POWER REGULATION<br>EMES FOR UNBALANCED SUPPLY CONDITIONS159                                                                                                                                                                                                          |

| 6.0 | Introduct                                          | ion159                                                                                                                                                                                                                                                                                          |

| 6.1 | Discussio                                          | on on power factor definitions161                                                                                                                                                                                                                                                               |

| 6.2 | Power reg                                          | gulation methods for unbalanced supply operation166                                                                                                                                                                                                                                             |

|     |                                                    | Voltage-oriented control (VOC) method                                                                                                                                                                                                                                                           |

| 6.3 | Investiga                                          | tion of achievable power factor176                                                                                                                                                                                                                                                              |

|     | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6 | Average active and reactive power.176Nullifying power ripple.176Nullifying power ripple at the supply input terminals.177Nullifying power ripple at the rectifier bridge input terminals.179Power factor with the voltage-oriented control method.182Evaluation of achievable power factors.183 |

| 6.4 | Experime                                           | ental results with the different control methods                                                                                                                                                                                                                                                |

| 6.5 | Conclusio                                          | ons195                                                                                                                                                                                                                                                                                          |

|     | Boos                                               | CURRENT TRACKING SCHEMES FOR THE THREE-PHASE<br>ST-Type PWM Rectifier197                                                                                                                                                                                                                        |

|     |                                                    | ion197                                                                                                                                                                                                                                                                                          |

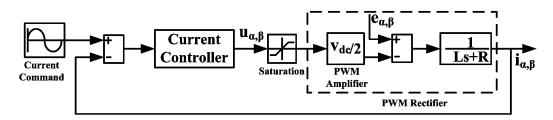

| 7.1 | System n                                           | nodel of a PWM rectifier200                                                                                                                                                                                                                                                                     |

|     | 7.1.1<br>7.1.2<br>7.1.3                            | Transfer function of current loop                                                                                                                                                                                                                                                               |

| 7.2 | P + Resort                                         | nant control (P+RC) current tracking scheme                                                                                                                                                                                                                                                     |

|     | 7.2.1<br>7.2.2                                     | Introduction to P + Resonant controller [74, 75]203<br>Practical implementation                                                                                                                                                                                                                 |

| 7.3 | Integral v                                         | variable structure control (IVSC) current tracking scheme208                                                                                                                                                                                                                                    |

|     | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5          | Controller design.209The quasi-sliding mode.210The quasi-sliding mode band.210Chattering reduction.212Choice of parameters.213                                                                                                                                                                  |

| 7.4 Hybrid Iterative learning controller (Hybrid ILC) current tracking scheme214                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4.1Iterative learning control – an introduction2147.4.2Hybrid ILC current control scheme2167.4.3Practical implementation issues219                     |

| 7.5 The design of current controllers                                                                                                                    |

| 7.5.1 Design of P + Resonant controller.2227.5.2 Design of integral variable structure control.2247.5.3 Design of the Hybrid ILC current controller .225 |

| 7.6 Experimental comparison of current controllers                                                                                                       |

| <ul><li>7.6.1 Current control with voltage loop open</li></ul>                                                                                           |

| 7.7 Detailed experimental results with Hybrid ILC current controller236                                                                                  |

| 7.7.1Steady-state operation                                                                                                                              |

| 7.8 Conclusions                                                                                                                                          |

| CHAPTER 8 CONCLUSIONS AND FUTURE WORK244                                                                                                                 |

| 8.0 Introduction                                                                                                                                         |

| 8.1 PWM rectifier system under balanced supply245                                                                                                        |

| <ul><li>8.1.1 Development and verification of a dual SISO model</li></ul>                                                                                |

| 8.2 PWM rectifier system under unbalanced supply247                                                                                                      |

| <ul> <li>8.2.1 Proposal of an output power control (OPC) scheme</li></ul>                                                                                |

| conditions                                                                                                                                               |

| 8.3 Current Tracking Schemes                                                                                                                             |

| 8.4 Future work                                                                                                                                          |

| <ul> <li>8.4.1 Solutions to dynamic response problem due to RHP zero</li></ul>                                                                           |

| <b>R</b> EFERENCES                                                                                                                                       |

| APPENDIX A NON-MINIMUM PHASE FEATURE IN A PWM                                                                                                            |

| <b>RECTIFIER</b>                                                                                                                                         |

| A.0 Introduction                                                                                                                                         |

A.1 State-space-averaged model of a PWM rectifier system in SRF......264

| A.2 Presence of non-minimum phase feature in the system model                                                                                                                                       | 265  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul><li>A.2.1 Voltage control scheme</li><li>A.2.2 Current control scheme</li></ul>                                                                                                                 |      |

| APPENDIX B MODEL OF A THREE-PHASE PWM RECTIFIER IN AN<br>UNBALANCED SYSTEM AND SEPARATION OF SEQUENTIAL<br>COMPONENTS                                                                               | 270  |

| B.0 Introduction                                                                                                                                                                                    |      |

| B.1 Symmetrical components analysis of an unbalanced three-phase power sys                                                                                                                          |      |

| B.2 Space vector representations in stationary frame                                                                                                                                                | 272  |

| B.3 Space vector representations in positive- and negative- sequence synchron rotating frame                                                                                                        | •    |

| B.4 System modeling in positive- and negative- sequence synchronously rotati frames                                                                                                                 | 0    |

| B.5 Separation of sequential components                                                                                                                                                             | 276  |

| <ul><li>B.5.1 Notch filter</li><li>B.5.2 Delaying method</li></ul>                                                                                                                                  |      |

| APPENDIX C SMALL SIGNAL MODEL FOR THE <i>D</i> -AXIS DYNAMICS                                                                                                                                       | 280  |

| C.0 Open loop transfer functions                                                                                                                                                                    | 280  |

| C.1 Closed loop transfer functions                                                                                                                                                                  | 285  |

| APPENDIX D MEASUREMENT OF BODE PLOTS IN A DSPACE<br>Controlled PWM Rectifier System                                                                                                                 | 290  |

| D.0 Introduction                                                                                                                                                                                    | 290  |

| D.1 Measurement of open-loop bode plots                                                                                                                                                             | 290  |

| D.2 Measurement of loop transfer function Bode plots                                                                                                                                                | 292  |

| APPENDIX E POWER DEFINITION IN A THREE-PHASE SINUSOIDAL                                                                                                                                             |      |

| UNBALANCED SYSTEM                                                                                                                                                                                   | .294 |

| E.1 Power definitions in <i>a-b-c</i> frame [5-7]                                                                                                                                                   | .294 |

| E.2 Power definition in stationary frame                                                                                                                                                            | .295 |

| <ul><li>E.2.1 Power definitions</li><li>E.2.2 Space vector expression of three-phase variables in stationary frame</li><li>E.2.3 Power definition expressions in space vector formulation</li></ul> | .296 |

| E.3 Power definition expressions in synchronously rotating frame                                                                                                                                    | .298 |

| E.4 Discussion on Different Reactive Power Definitions in SRF                                                                                                                                       | .299 |

| APPENDIX F UNCERTAINTY AND STABILITY ROBUSTNESS                                                                                                                                                     | .301 |

| Api | PENDIX H ARCHITECTURE OF DSPACE DS1104                              | .309 |

|-----|---------------------------------------------------------------------|------|

| Api | PENDIX G TIME DELAY IN A DSPACE SYSTEM                              | .306 |

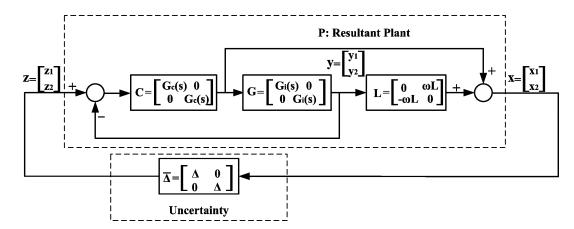

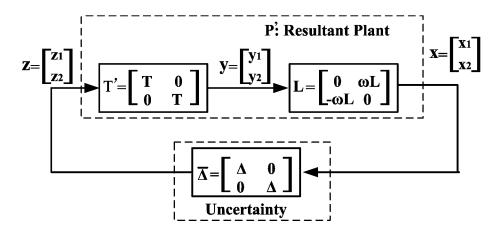

| F.5 | M-Files for singular value calculation for system shown in Fig. 5.6 | 305  |

| F.4 | M-Files for singular value calculation for system shown in Fig. 5.3 | 304  |

| F.3 | Robust stability for the SISO case                                  | 304  |

| F.2 | Description of the plant uncertainty                                | 302  |

| F.1 | Representation of uncertainty                                       | 301  |

|     |                                                                     |      |

## **SUMMARY**

The three-phase boost type PWM rectifier has been widely used as an improved utility interface in recent years since it has the potential to operate with sinusoidal line currents at a desired power factor and with nearly constant *dc* output voltage with a small output capacitor. However, due to its inherent multi-input and multi-output (MIMO) non-linear structure and non-minimum phase feature, designing a proper controller for such a converter is generally a challenging task even under balanced supply voltage operating conditions. In addition, supply voltage imbalance, which is a common occurrence in a power system, complicates the control task further.

The aims of the work reported in this thesis can be brought under three categories:

- To develop an accurate but simple control-oriented model for a PWM rectifier under balanced operating conditions

- To evaluate reported power regulation schemes for a PWM rectifier under unbalanced operating conditions and to propose and investigate new schemes if needed.

- To investigate high performance current tracking schemes for the control of unbalanced line currents in a PWM rectifier and to propose and investigate new schemes if needed.

Firstly, to facilitate controller design and to give meaningful insight into the

behavior of PWM rectifiers, a simple dual single-input single-output (SISO) model was developed by separating the *d*-axis and the *q*-axis dynamics through appropriate feed-forward decoupling and near unity power factor assumption. The effectiveness of the proposed model was verified experimentally in both the frequency and time domains. It was found that the proposed *d*-axis equivalent SISO model was similar to a traditional *dc*-*dc* boost converter. This finding opens up possible new avenues for controlling three-phase PWM rectifier systems with the well-developed analysis and design techniques of *dc*-*dc* converters. As examples, the voltage-mode and current-mode controllers commonly used with *dc*-*dc* controllers were successfully implemented on the PWM rectifier, and this also further justifies the effectiveness of the proposed dual SISO model.

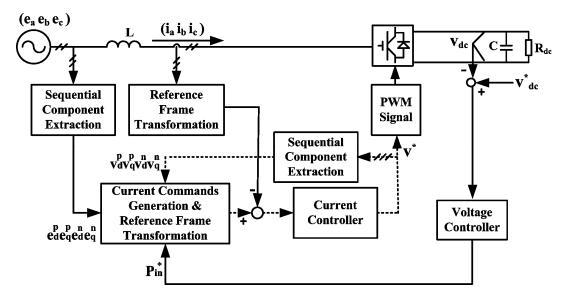

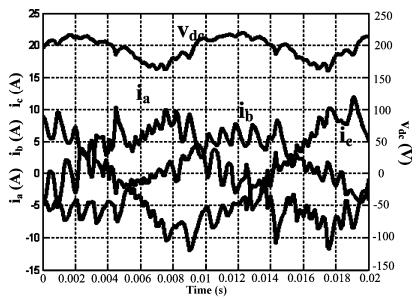

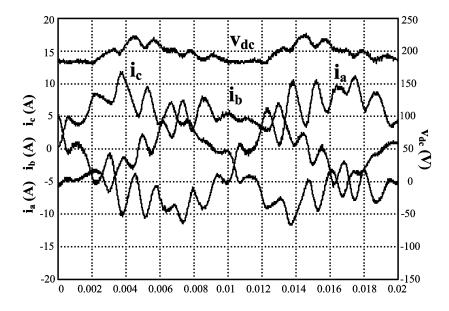

Next, in order to maintain constant *dc* output voltage and sinusoidal line currents when operating under unbalanced supply voltage conditions, an output power control (OPC) method is proposed. Also, an improved realization of the existing partial output power control (POPC) method, which results in overcoming the performance limitations encountered with the POPC method reported in literature, is suggested. A third new method, called voltage oriented control (VOC) method capable of excellent input side performance was also proposed. Experimental comparisons among the four control schemes, namely, the existing input power control (IPC) method and the proposed schemes, OPC, POPC with the proposed improved realization, and the VOC methods were carried out using a 1 kW laboratory prototype. Experimental results show that both the proposed OPC method and the POPC method with the improved realization can provide high input side and output side performances. Investigations have also been presented to show that the effective power factor (EPF) definition evaluates the power flow condition more fairly than the more common vector power factor (VPF) definition in an unbalanced system.

Thirdly, in order to achieve excellent input side performance, current tracking schemes based on both integral variable structure control (IVSC) and iterative learning control (ILC) were proposed and implemented in the stationary frame. Experimental comparisons with the widely used dual current controller (DPIC) and a newly developed P + Resonant controller (P+RC) were also carried out. Results show that the proposed ILC based hybrid current controller (Hybrid ILC) achieves excellent steady-state performance with good transient response suggesting this to be a promising technique for controlling periodic currents commonly existing in power converters applications.

In conclusion, this thesis studies fully the issues related a PWM rectifier system operating under both balanced and unbalanced conditions and also suggests future work related to this field.

#### List of Publication Associated to the Research Work

#### Journal papers:

- 1. B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "An output-power-control strategy for a three-phase PWM rectifier under unbalanced supply conditions," *IEEE Trans. on Industrial Electronics*, vol. 55, No. 5, May 2008, pp:2140-2151.

- 2. B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "A simple single-input-singleoutput (SISO) model for a three-phase PWM rectifier," *IEEE Trans. on Power Electronics*, vol. 24, no.3, March, 2009, pp:620-631.

#### Conference papers:

- 1. B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "A novel instantaneous power control strategy for a PWM rectifier under unbalanced input voltage conditions," in *Proc.* the 30th *IEEE* Conf. *Industrial Electronics Society*, Busan, Korea 2004, pp251-256.

- 2. B. Yin, S. K. Panda, R. Oruganti and A. K. S. Bhat, "A Novel Current Regulation Scheme for Boost Type PWM Rectifier Based on Iterative Learning Control," in *Proc.* the *IEEE Conf. Power System Technology*, Singapore. 2004, pp: 1786-1791.

- 3. B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "High-Performance Control of a Boost Type PWM Rectifier under Unbalanced Operating Conditions with Integral Variable Structure Control," *Proceedings of the 36th IEEE Power Electronics Specialists Conference (PESC 2005)*, June 2005, pp:1992-1997.

- 4. B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "Control of a three-phase PWM rectifier Based on a dual single-input single-output linear model," *The 6th International Conf. on Power Electronics and Drive Systems*, 2005, pp: 456-461.

- 5. B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "Experimental verification of a dual single-input single-output model of a three-phase boost-type PWM Rectifier" *in Proc. the 31th IEEE Conf. Industrial Electronics Society*, North Carolina, USA, 2005.

- B. Yin, R. Oruganti, S. K. Panda, and A. K. S. Bhat, "Performance comparison of voltage mode control and current mode control of a three-phase PWM Rectifier based on a dual SISO model," *in Proc. the 32th IEEE Conf. Industrial Electronics Society*, Paris, France 2006, pp: 1908-1914.

## List of Tables

| Table 2.1 Models of a PWM rectifier system.    20                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2 Classification of control schemes for operation under balanced supply conditions                                    |

| Table 2.3 Classification of control schemes for PWM rectifier systems under unbalanced supply voltage conditions              |

| Table 3.1 Comparison between a <i>dc-dc</i> boost converter and a three-phase <i>ac-dc</i> rectifier                          |

| Table 3.2 The location of RHP zero corresponding to the choice of the inductor value                                          |

| Table 3.3 Experimental rectifier specifications                                                                               |

| Table 3.4 Closed loop small signal transfer functions                                                                         |

| Table 3.5 Summaries of comparison results                                                                                     |

| Table 3.6 Total harmonic distortion of experimental results                                                                   |

| Table 6.1 Unbalanced power flow conditions with supply voltage imbalance164                                                   |

| Table 6.2 Active and reactive power values for the systems in Table 6.1                                                       |

| Table 6.3 Determination of power factor values using data in Table 6.1 and Table 6.2                                          |

| Table 6.4 Calculated VPF and EPF values                                                                                       |

| Table 6.5 Simulation based comparison of power factors with different control methods using original power factor definitions |

| Table 6.6 Simulation based comparison of power factors with different controlmethods using equations given in Table 6.4187    |

| Table 6.7 Experimental performance with different control schemes    193                                                      |

| Table 6.8 Comparison of different power regulation schemes                                                                    |

| Table 7.1 Experimental system parameters.    228                                                                              |

| Table 7.2 Experimental total harmonic distortion results – with only current controller                                       |

| Table 7.3 Experimental total harmonic distortion results – closed loop voltage control operation                              |

## **List of Figures**

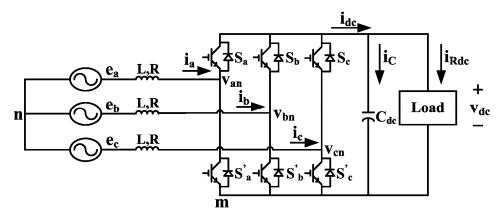

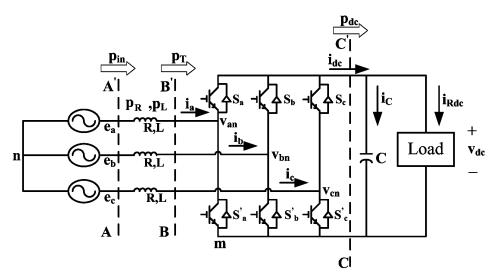

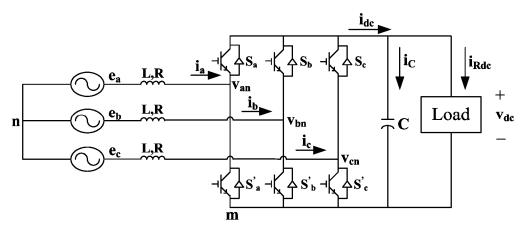

| Fig.1.1 Configuration of a three-phase boost-type PWM rectifier1                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.2.1 Structure of a three phase <i>ac</i> to dc PWM rectifier19                                                                                                                                                                        |

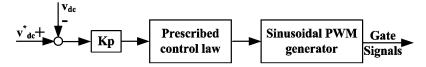

| Fig.2.2 Schematic diagram for indirect current control or phase and amplitude control                                                                                                                                                     |

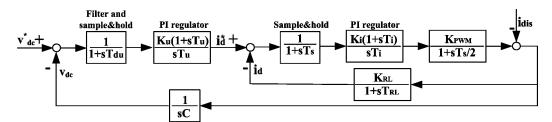

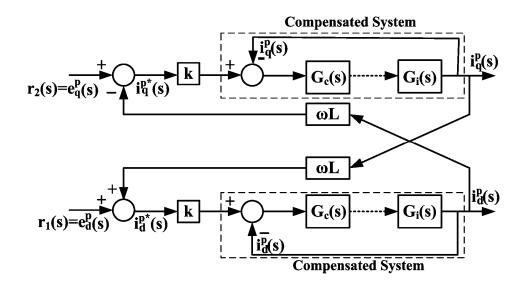

| Fig.2.3 Schematic diagram for a PWM rectifier system with a cascaded structure using PI controllers                                                                                                                                       |

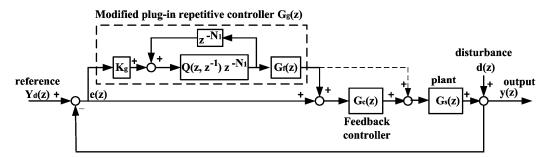

| Fig.2.4 "Plug-in" repetitive control system                                                                                                                                                                                               |

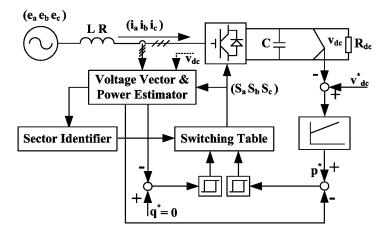

| Fig.2.5 Configuration of direct power control of PWM rectifiers                                                                                                                                                                           |

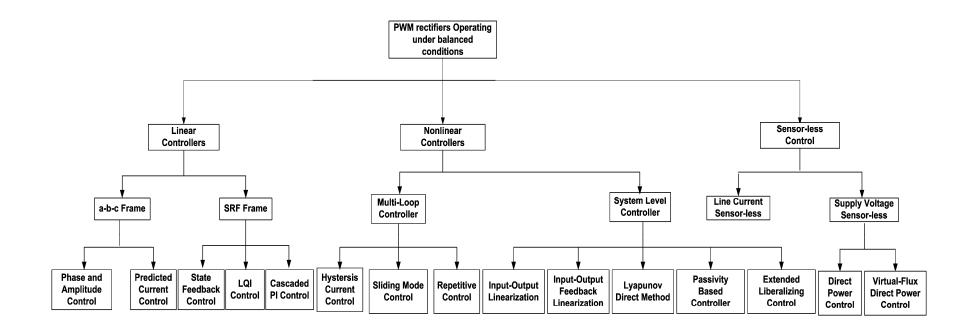

| Fig.2.6 Classification of control schemes for a PWM rectifier operating under balanced supply voltage conditions                                                                                                                          |

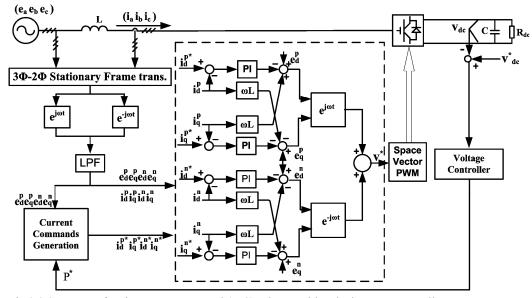

| Fig.2.7 Implementation of an unbalanced compensation scheme42                                                                                                                                                                             |

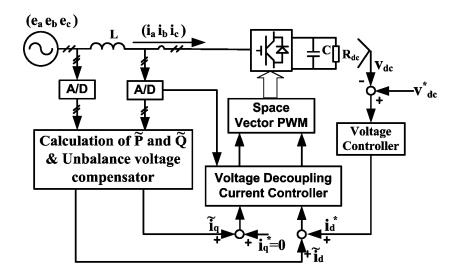

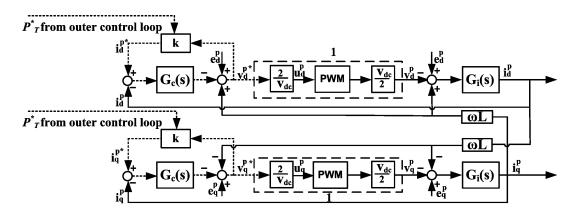

| Fig.2.8 Structure of an input power control (IPC) scheme with a dual current controller                                                                                                                                                   |

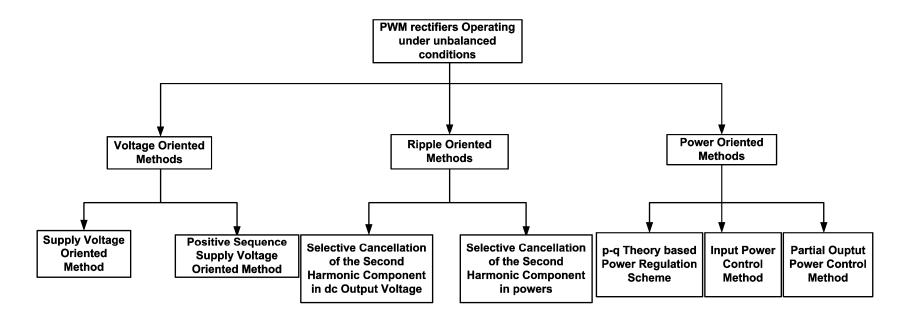

| Fig.2.9 Classification of control schemes for a PWM rectifier operating under unbalanced supply voltage conditions                                                                                                                        |

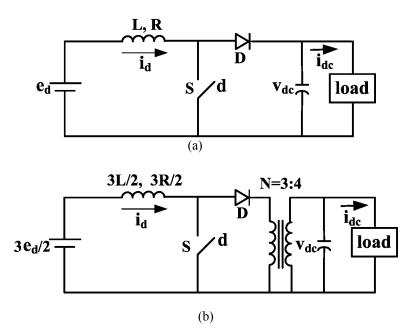

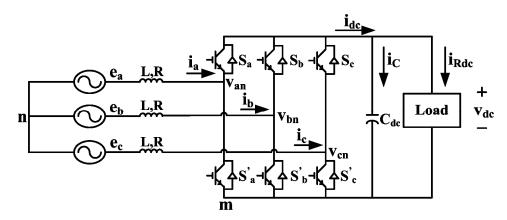

| Fig.3.1 Structure of a three-phase <i>ac</i> to <i>dc</i> PWM rectifier                                                                                                                                                                   |

| Fig.3.2 Equivalent circuit in SRF                                                                                                                                                                                                         |

| Fig.3.3 Equivalent circuit in SRF after decoupling and neglecting of <i>q</i> -axis disturbance on <i>d</i> -axis dynamics                                                                                                                |

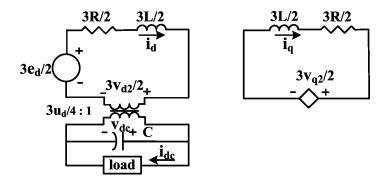

| Fig.3.4 (a) A <i>dc</i> to <i>dc</i> boost converter (b) Proposed <i>d</i> -axis equivalent circuit for the three-phase PWM rectifier                                                                                                     |

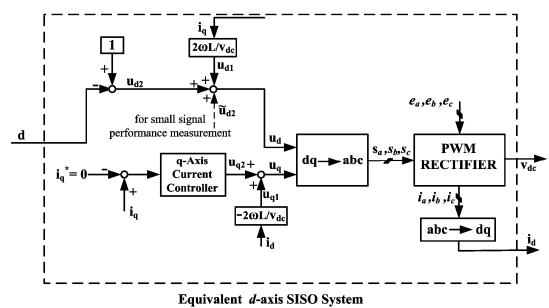

| Fig.3.5 Block diagram for realizing the equivalent <i>d</i> -axis SISO system of the PWM rectifier                                                                                                                                        |

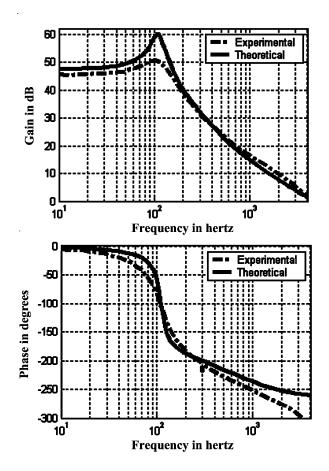

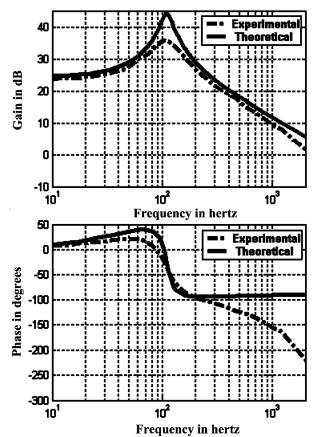

| Fig.3.6 Control-to- $dc$ output voltage Bode plots under a supply voltage of 60VRMS, 50 $Hz$ and a load resistor of 45 $\Omega$ - Quasi open-loop operation                                                                               |

| Fig.3.7 Control-to- <i>d</i> -axis current Bode plots under a supply voltage of 60VRMS, $50Hz$ and a load resistor of $45\Omega$ - Quasi open-loop operation                                                                              |

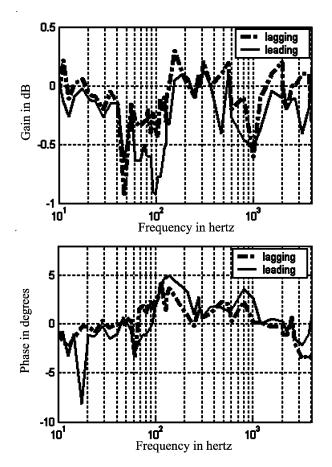

| Fig.3.8 Magnitude and phase difference curves between unity power factor operation<br>and leading power factor operation (solid line) and between unity power<br>factor operation and lagging power factor operation (dashed line) with a |

| supply voltage of 60VRMS, $50Hz$ and a load resistor of $45\Omega$ - Quasi open-<br>loop operation                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

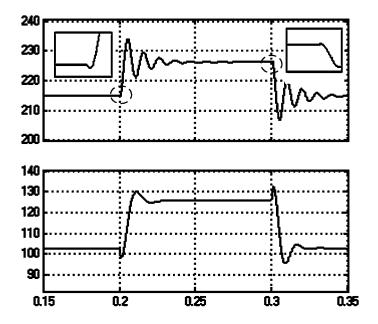

| Fig.3.9 Output voltage, <i>d</i> -axis current and a-phase current waveforms for a step change in d-axis duty ratio d from 0.21 to 0.25 and back to 0.21 under a supply voltage of 60VRMS, $50Hz$ and a load resistor of $45\Omega$ - Quasi open-loop operation                                                                                                 |

| Fig.3.10 Output voltage, <i>d</i> -axis current and <i>a</i> -phase current waveforms for a step change in <i>d</i> -axis switching function <i>d</i> from 0.45 to 0.55 and back to 0.45 under a supply voltage of 20VRMS, $50Hz$ and a load resistor of $20\Omega$ - Quasi open-loop operation                                                                 |

| Fig.3.11 Simulated step responses (a) a step change in d-axis switching function d from 0.21 to 0.25 and back to 0.21 under a supply voltage of 60VRMS, $50Hz$ and a load resistor of $45\Omega$ (b) a step change in d-axis switching function d from 0.45 to 0.55 and back to 0.45 under a supply voltage of 20VRMS, $50Hz$ and a load resistor of $20\Omega$ |

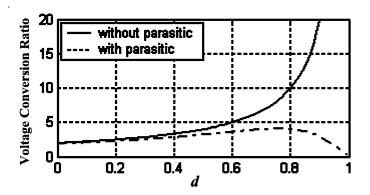

| Fig.3.12 Effect of parasitic loss on voltage conversion ratio (without inductor parasitic resistance / with inductor parasitic resistance of value 1 <i>Ω</i> )79                                                                                                                                                                                               |

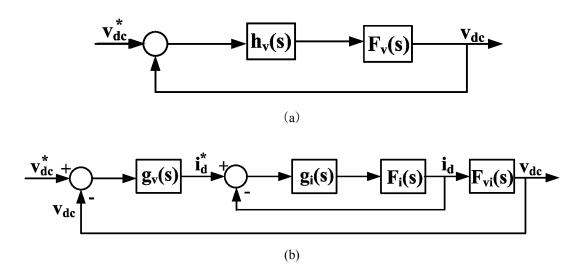

| Fig.3.13 Structure of voltage mode control and current mode control                                                                                                                                                                                                                                                                                             |

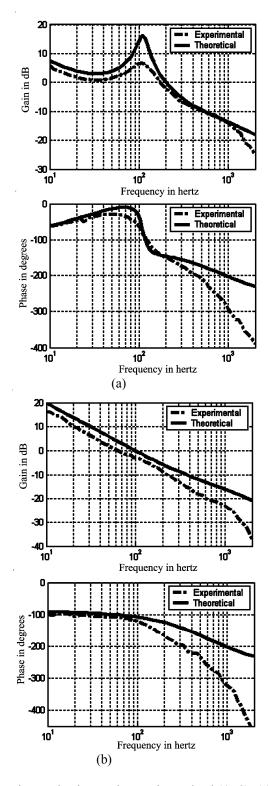

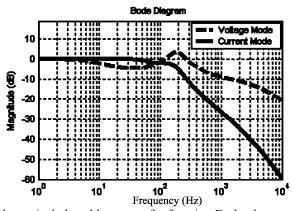

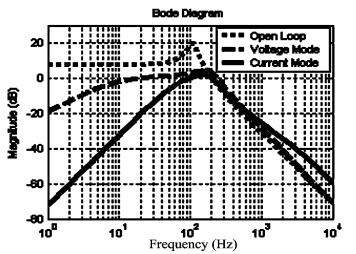

| Fig.3.14 Loop transfer function Bode plots under maximum load (45Ω): (a) with voltage mode controller, and (b) with current mode controller                                                                                                                                                                                                                     |

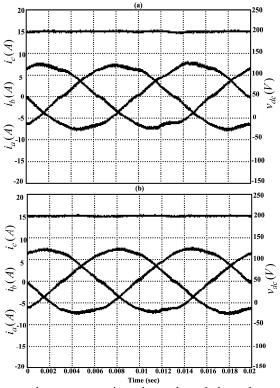

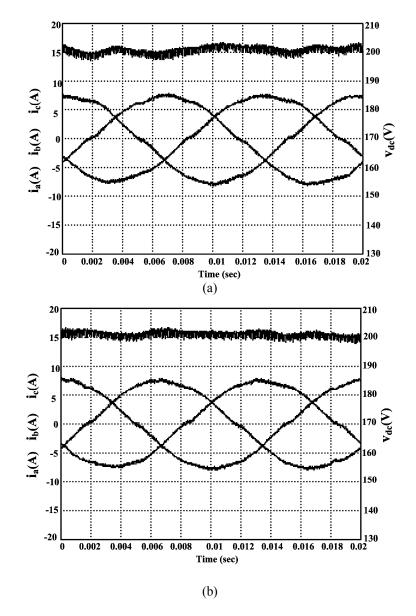

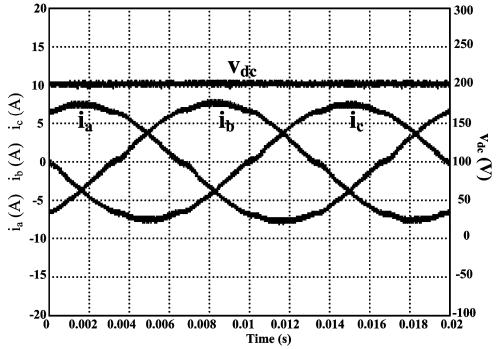

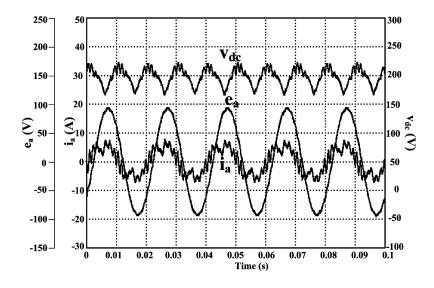

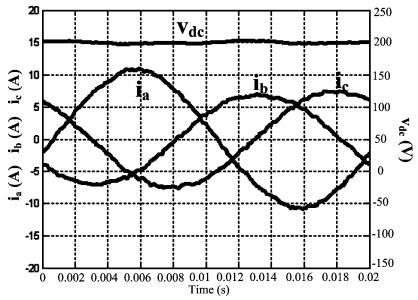

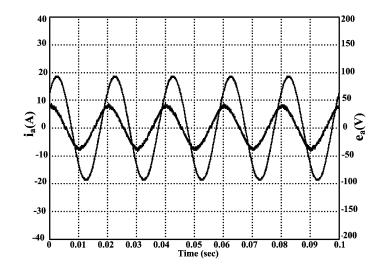

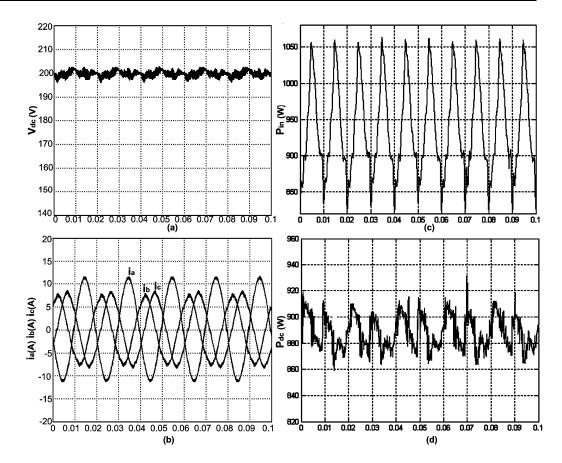

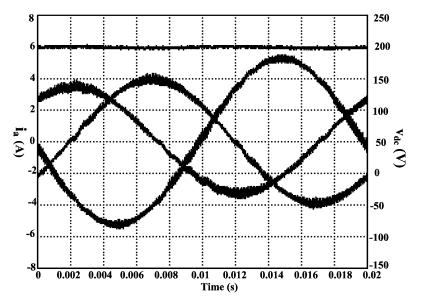

| Fig.3.15 Waveforms under steady-state operation: three-phase balanced current and output voltage: (a) Voltage mode control. (b) Current mode control                                                                                                                                                                                                            |

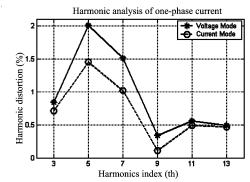

| Fig.3.16 Frequency spectra of a-phase current90                                                                                                                                                                                                                                                                                                                 |

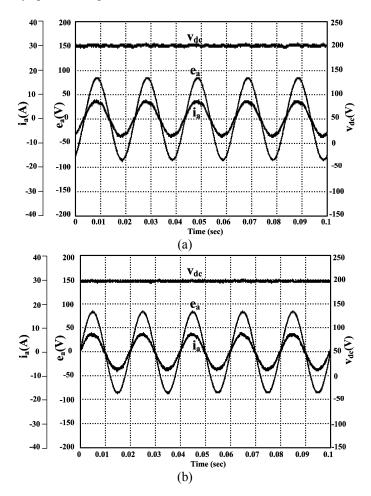

| Fig.3.17 Steady-state waveforms - a-phase current, a-phase supply voltage and <i>dc</i> output voltage: (a) Voltage mode control. (b) Current mode control90                                                                                                                                                                                                    |

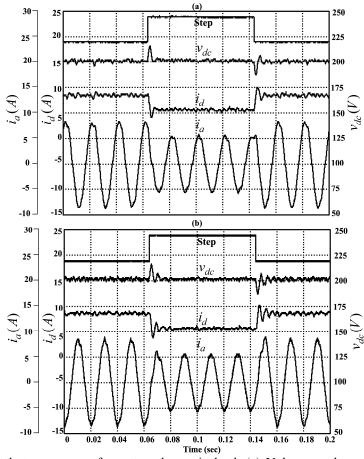

| Fig.3.18 Experimental step response for a step change in voltage reference: (a)<br>Voltage mode control. (b) Current mode control92                                                                                                                                                                                                                             |

| Fig.3.19 Comparison of theoretical closed loop transfer function Bode plots93                                                                                                                                                                                                                                                                                   |

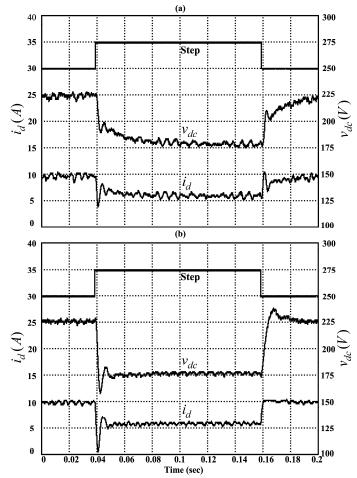

| Fig.3.20 Experimental step response for a step change in load: (a) Voltage mode control. (b) Current mode control                                                                                                                                                                                                                                               |

| Fig.3.21 Comparison of theoretical output impedance curves94                                                                                                                                                                                                                                                                                                    |

| Fig.3.22 Experimental step response for a step change in supply voltage: (a) Voltage mode control. (b) Current mode control                                                                                                                                                                                                                                     |

| Fig.3.23 Comparison of theoretical audio susceptibility performance                                                                                                                                                                                                                                                                                             |

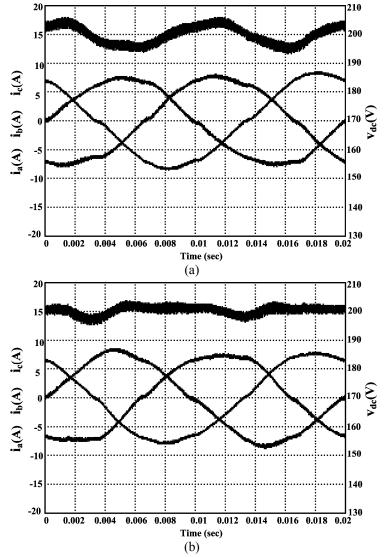

| Fig.3.24 Waveforms for steady-state operation: three-phase balanced current and output voltage: (a) Voltage mode control. (b) Current mode controlunder 1.67% magnitude unbalance in a-phase                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Fig.3.25 Waveforms for steady-state operation: three-phase balanced current and output voltage: (a) Voltage mode control. (b) Current mode control under 10% magnitude unbalance in a-phase</li></ul> |

| Fig.4.1 Structure of a three phase ac to dc PWM rectifier103                                                                                                                                                  |

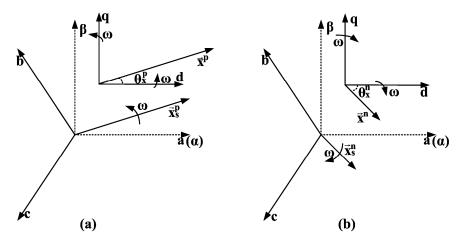

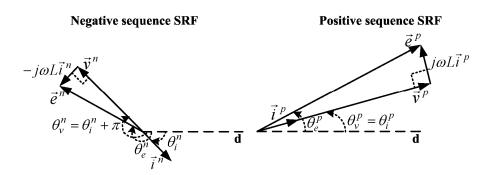

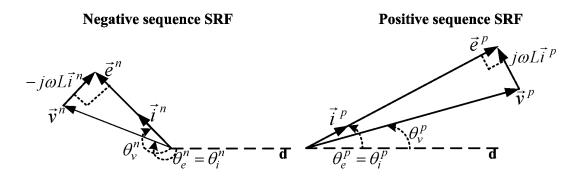

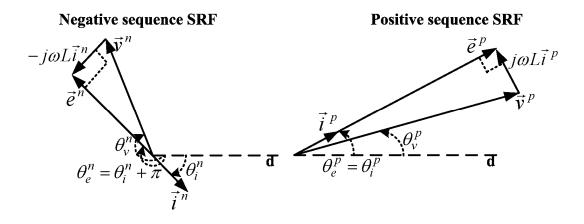

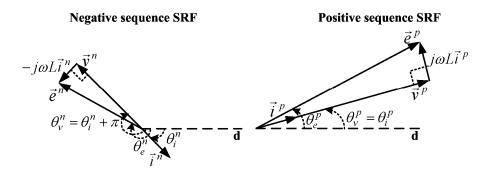

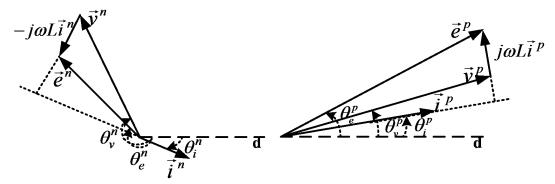

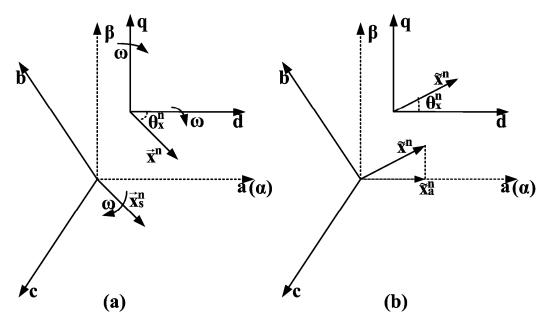

| Fig.4.2 Vector diagrams of a positive sequence component and a negative sequence component in different frames at t=0. a) a positive sequence vector diagram b) a negative sequence vector diagram            |

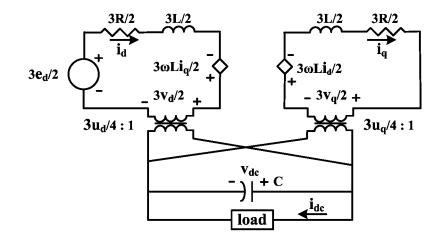

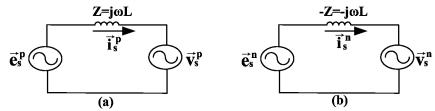

| Fig.4.3 Input side equivalent circuits: a) for the positive sequence system b) for the negative sequence system                                                                                               |

| Fig.4.4 Phasor diagram of the output power control method113                                                                                                                                                  |

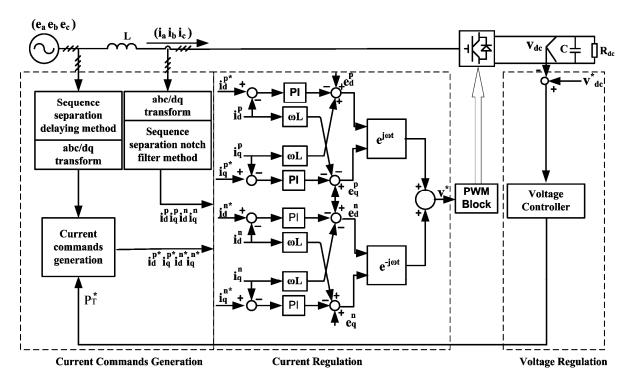

| Fig.4.5 Overall detailed control block diagram of the proposed scheme117                                                                                                                                      |

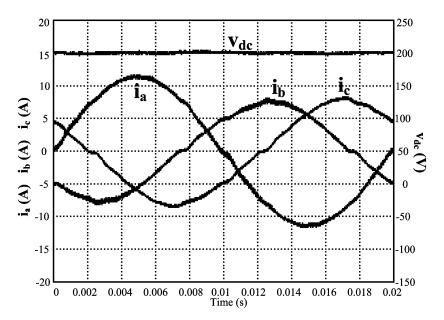

| Fig.4.6 Experimental waveforms of three-phase currents and dc output voltage under balanced supply - Proposed output power control method                                                                     |

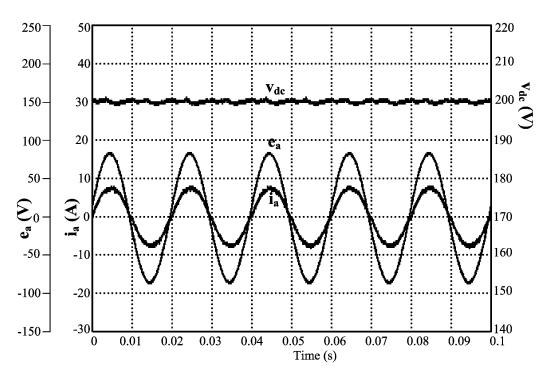

| Fig.4.7 Experimental waveforms of a-phase current, a-phase supply voltage and zoomed <i>dc</i> output voltage under balanced supply - Proposed output power control method                                    |

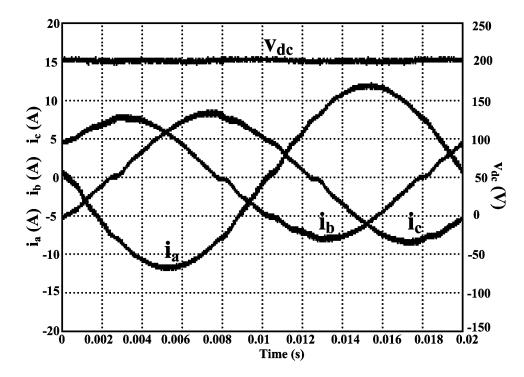

| Fig.4.8 Experimental waveforms of three-phase currents and <i>dc</i> output voltage under unbalanced supply - Proposed output power control method123                                                         |

| Fig.4.9 Experimental waveforms of three-phase currents and $dc$ output voltage under unbalanced operating conditions for a step change in load from $90\Omega$ to $60\Omega$ and back to $90\Omega$           |

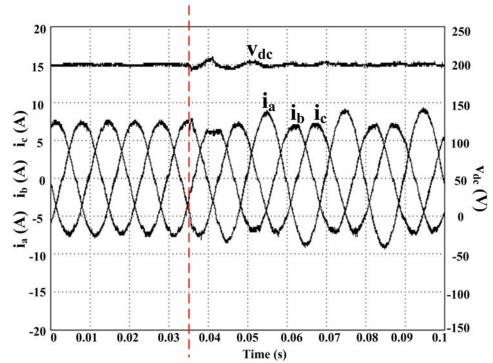

| Fig.4.10 Experimental waveforms of three-phase currents and <i>dc</i> output voltage under a step change of supply voltage from normal balanced operating conditions to unbalanced operating conditions       |

| Fig.5.1 Detailed closed-loop subsystem for a PWM rectifier in the positive sequence SRF – OPC scheme using Estimation Method 1                                                                                |

| Fig.5.2 Simplified closed-loop subsystem for a PWM rectifier in the positive sequence SRF – OPC scheme using Estimation Method 1                                                                              |

| Fig.5.3 Standard system used to formulate stability condition – OPC scheme using<br>Estimation Method 1                                                                                                       |

| Fig.5.4 Detailed closed-loop subsystem for a PWM rectifier in the positive sequence SRF – OPC scheme using Estimation Method 2141                                                                             |

| Fig.5.5 Simplified control subsystem for a PWM rectifier in the positive sequence SRF – OPC scheme using Estimation Method 2142                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.5.6 The feedback loop of Fig. 5.5 redrawn to formulate stability condition – OPC scheme using Estimation Method 2                                                                                                                              |

| Fig.5.7 Simulation waveforms with unbalanced supply voltage - OPC scheme using<br>Estimation Method 1                                                                                                                                              |

| Fig.5.8 Simulation waveforms with unbalanced supply voltage - OPC scheme using Estimation Method 2                                                                                                                                                 |

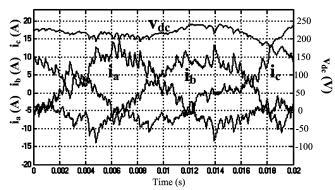

| Fig.5.9 Experimental steady-state waveforms under unbalanced supply voltage: a-<br>phase current, a-phase supply voltage and dc output voltage under<br>unbalanced condition – POPC method with implementation as in [52]<br>(Estimation Method 1) |

| Fig.5.10 Control system block diagram for the partial output power control method [52] (Estimation method 1)                                                                                                                                       |

| Fig.5.11 Simulated waveforms for unbalanced supply voltage - POPC scheme using<br>Estimation Method 1                                                                                                                                              |

| Fig.5.12 Experimental waveforms for unbalanced supply voltage - POPC scheme using Estimation Method 1                                                                                                                                              |

| Fig.5.13 Simulated waveforms for unbalanced supply voltage – POPC scheme using<br>Estimation Method 2                                                                                                                                              |

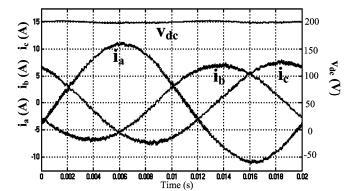

| Fig.5.14 Experimental waveforms for unbalanced supply voltage - POPC scheme using Estimation Method 2                                                                                                                                              |

| Fig.5.15 Experiment results for a-phase current and a-phase voltage under unbalanced condition                                                                                                                                                     |

| Fig.5.16 Experiment results for b-phase current and b-phase voltage under unbalanced condition                                                                                                                                                     |

| Fig.5.17 Experiment results for c-phase current and c-phase voltage under unbalanced condition                                                                                                                                                     |

| Fig.6.1 Phasor diagram for the voltage-oriented control method167                                                                                                                                                                                  |

| Fig.6.2 Phasor diagram of the input power control method                                                                                                                                                                                           |

| Fig.6.3 Phasor diagram of the output power control method173                                                                                                                                                                                       |

| Fig.6.4 Phasor diagram of the partial output power control method175                                                                                                                                                                               |

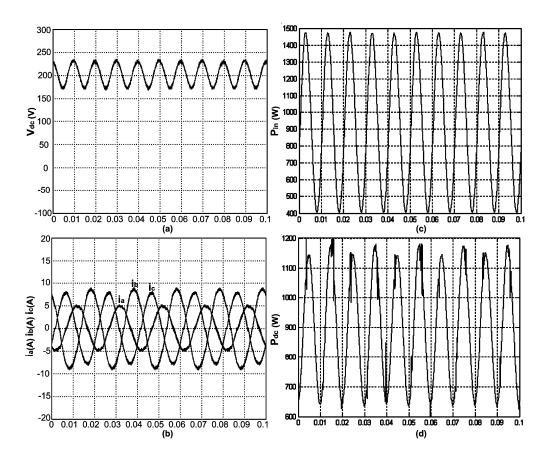

| Fig.6.5 Experimental waveforms with unbalanced supply: (a) output voltage (b) three-phase currents (c) input power (d) output power – the VOC method                                                                                               |

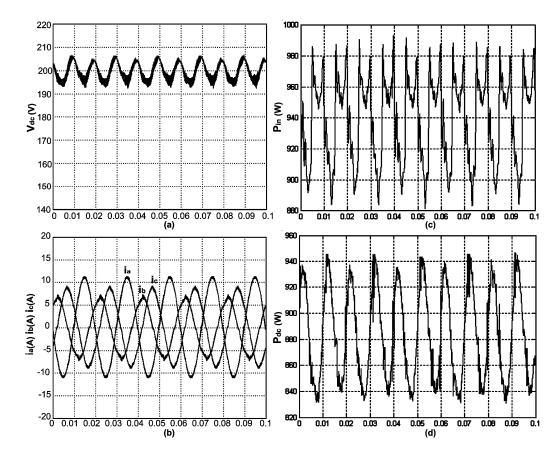

| Fig.6.6 Experimental waveforms with unbalanced supply: (a) output voltage (b) three-phase currents (c) input power (d) output power –the IPC method                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.6.7 Experimental waveforms with unbalanced supply: (a) output voltage (b) three-phase currents (c) input power (d) output power – the POPC method (with Estimation Method 2)                         |

| Fig.6.8 Experimental waveforms with unbalanced supply: (a) output voltage (b) three-phase currents (c) input power (d) output power – the OPC method                                                     |

| Fig.7.1 Structure of a three-phase boost-type PWM rectifier                                                                                                                                              |

| Fig.7.2 Structure of the current loop of the PWM rectifier system203                                                                                                                                     |

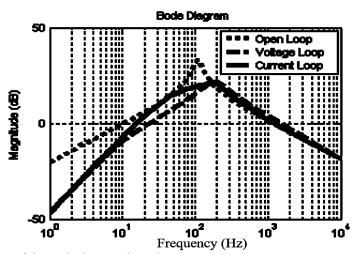

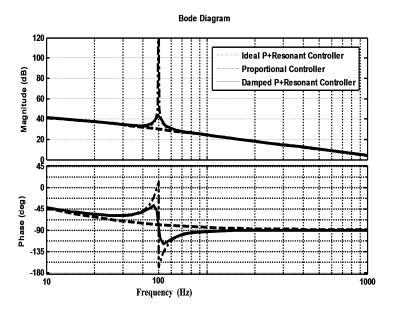

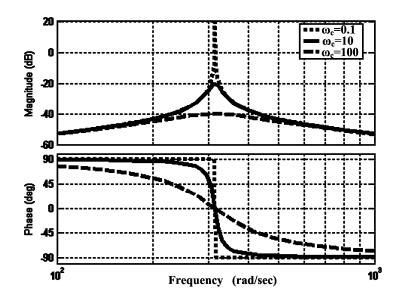

| Fig.7.3 Frequency responses of loop transfer function with only a proportional controller, with an ideal P + Resonant Controller and with a damped P + Resonant controller with a resonant gain Ki=15206 |

| Fig.7.4 Frequency response of the resonant term for variation in $\omega c$ and K <sub>I</sub> =1207                                                                                                     |

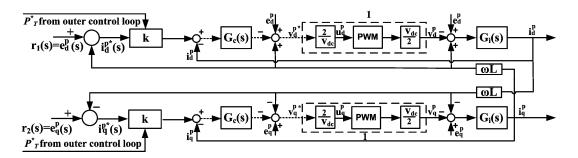

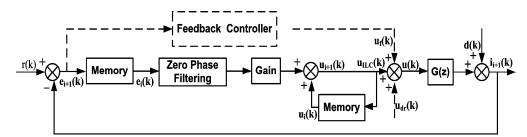

| Fig.7.5 Block diagram of the Hybrid ILC controller for a PWM rectifier system                                                                                                                            |

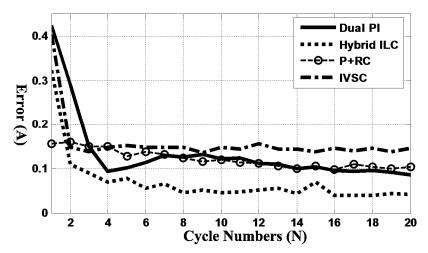

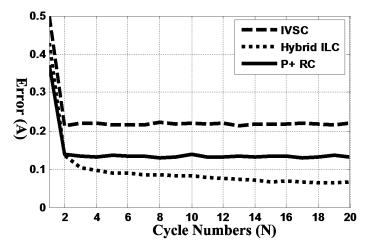

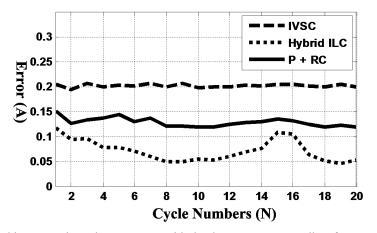

| Fig.7.6 Tracking error in a-phase RMS current with different current controllers for a step change in current commands from 4.2 A to 2.4 A                                                               |

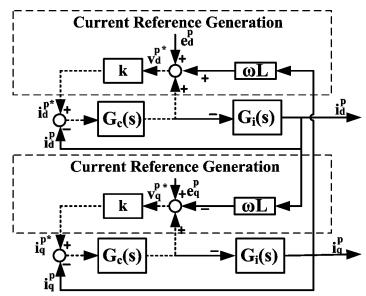

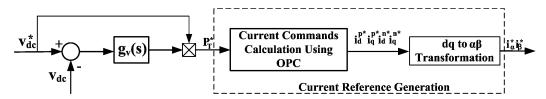

| Fig.7.7 Schematic diagram for current reference generation with both voltage and current control loops closed                                                                                            |

| Fig.7.8 Tracking errors in a-phase current (RMS value) with the three current controllers for a step change in dc output voltage reference from 175 V to 225 V                                           |

| Fig.7.9 Tracking errors in a-phase currents with the three current controllers for a step change in load from 90 $\Omega$ to $60\Omega$                                                                  |

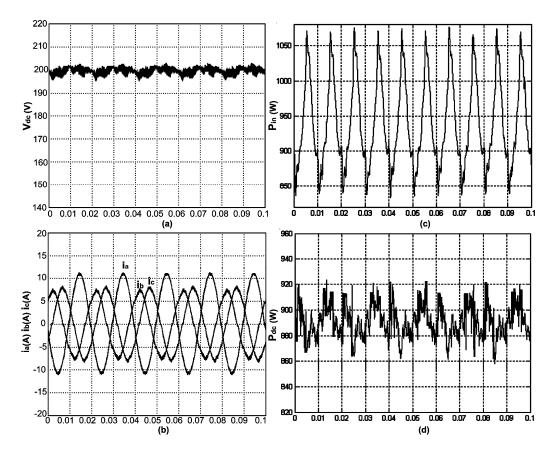

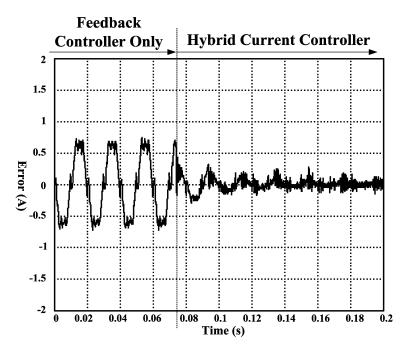

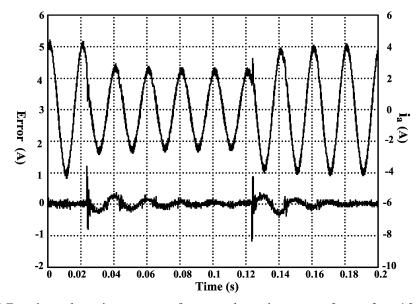

| Fig.7.10 Reduction in current tracking error on application of ILC – Hybrid ILC current controller                                                                                                       |

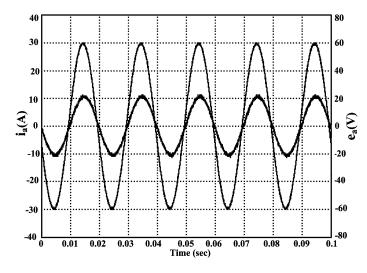

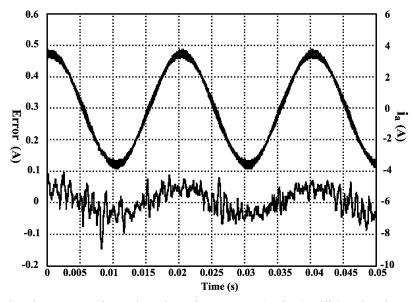

| Fig.7.11 Steady-state experimental result: a-phase current (scale: 2 A/div) and a-<br>phase error (scale (0.1 A/div) – Hybrid ILC current controller238                                                  |

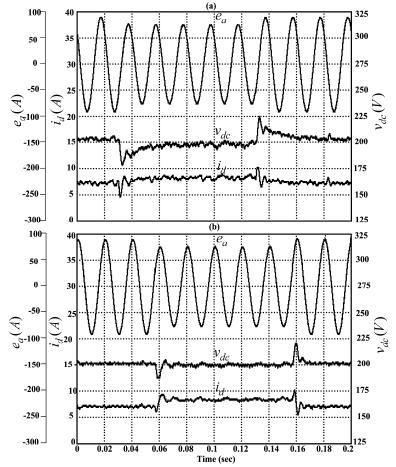

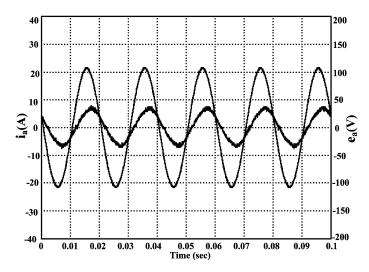

| Fig.7.12 Experimental waveforms for unbalanced supply voltages condition –<br>Hybrid ILC current controller                                                                                              |

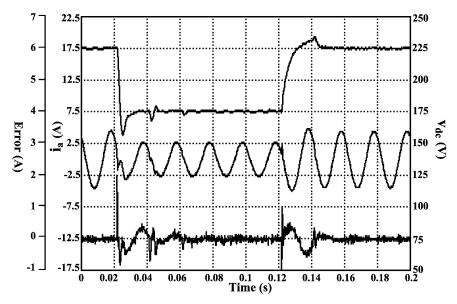

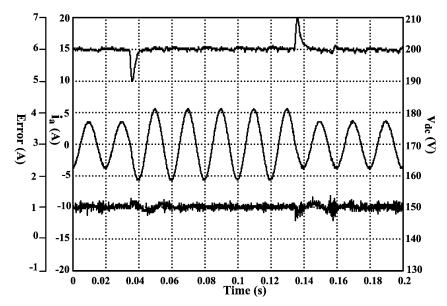

| Fig.7.13 Experimental transient responses for a step change in current reference from 4.2 A to 2.4 A and back to 4.2 A – Hybrid ILC current controller with only the current loop closed                 |

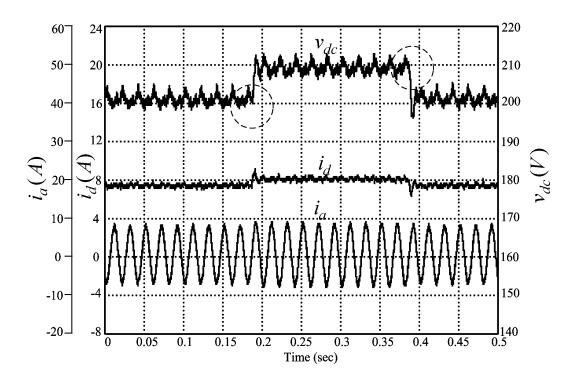

| Fig.7.14 Experimental transient response for a step change in dc output voltage reference from 225 V to 175 V and back to 225 V – Hybrid ILC current controller with both the voltage and current loops closed         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

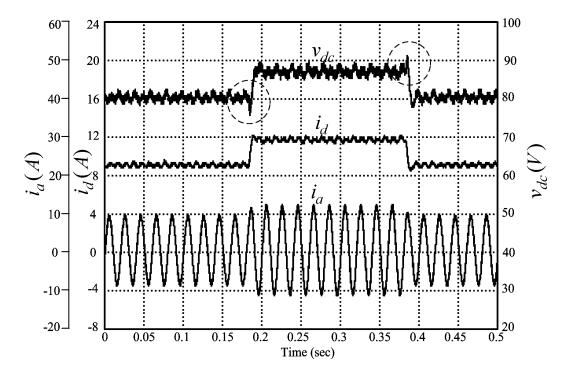

| Fig.7.15 Experimental transient response for a step change in load from 90 $\Omega$ to 60 $\Omega$ and back to 90 $\Omega$ – Hybrid ILC current controller with both the voltage and current loops closed              |

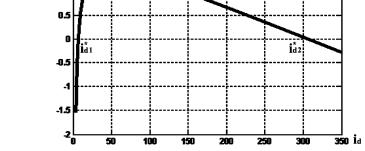

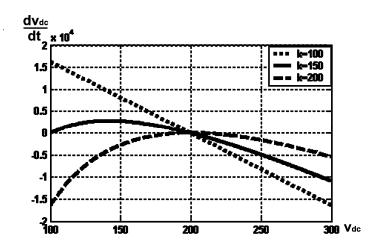

| Fig.A.1 Phase trajectory of the zero dynamics of the voltage control scheme266                                                                                                                                         |

| Fig.A.2 Phase trajectory of the zero dynamics of the current control scheme 268                                                                                                                                        |

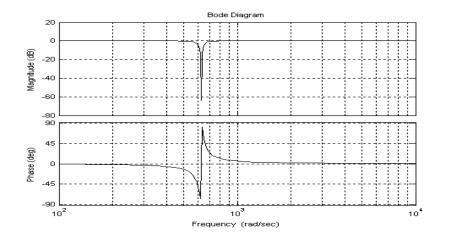

| Fig.B.1 Bode diagram for notch filter with notch frequency 100-Hz277                                                                                                                                                   |

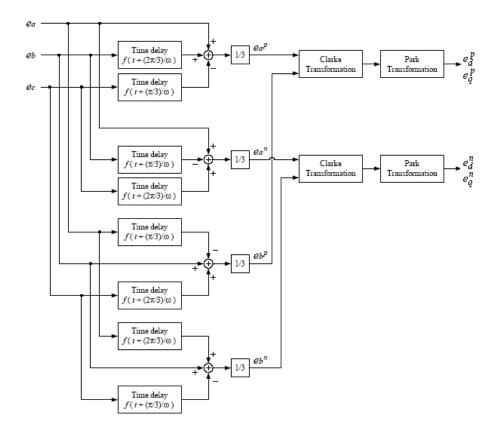

| Fig.B.2 Block diagram showing the implementation of the delaying method of calculating                                                                                                                                 |

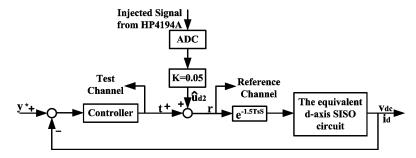

| Fig.D.1 Diagram for measurement of open loop Bode plots of the equivalent SISO system                                                                                                                                  |

| Fig.D.2 Diagram for the measurement of closed loop Bode plots of the equivalent SISO system                                                                                                                            |

| Fig.E.1 a)Vector diagram of a negative sequence component at t=0 in the instantaneous reactive power definition b)Vector diagram of a negative sequence component at t=0 in the conventional reactive power definition |

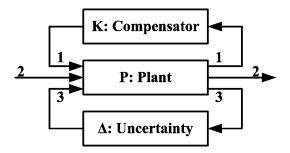

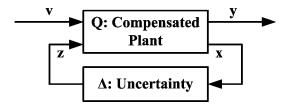

| Fig.F.1 Standard representation of uncertainty                                                                                                                                                                         |

| Fig.F.2 Standard representation for robust stability condition formulation                                                                                                                                             |

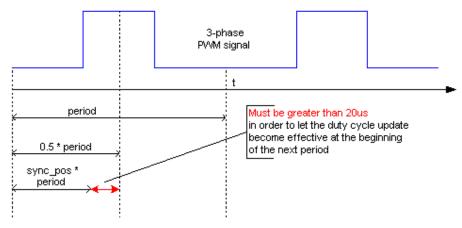

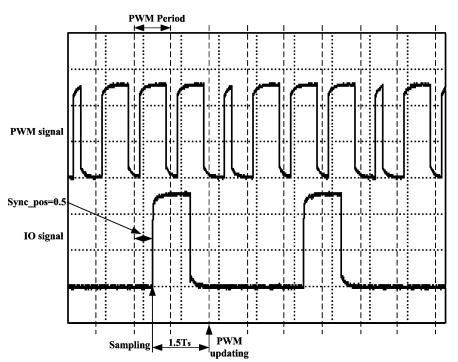

| Fig.G.1 Diagram for the synchronization interrupt signal                                                                                                                                                               |

| Fig.G.2 Experimental waveforms for a-phase PWM signal and IO signal                                                                                                                                                    |

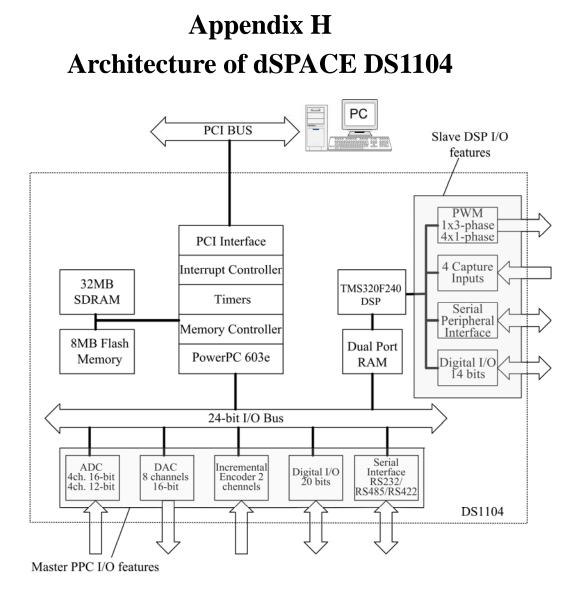

| Fig.H.1 Architecture of the DSP DS1104 controller board                                                                                                                                                                |

## **CHAPTER 1**

## INTRODUCTION

#### 1.0 Background

In many power electronic applications, an *ac*-to-*dc* converter, widely known as a 'rectifier' [1, 2], is used as a front-end converter for interfacing the power electronic equipment with the utility system. Traditionally, such *ac*-to-*dc* power conversion has been accomplished by means of diodes which are essentially uncontrolled power semiconductor switches, or by thyristors which may be viewed as semi-controlled switches. In several power electronic systems, such as in switch-mode *dc* power supplies, *ac* motor drives or *dc* servo drives, the *ac* to *dc* uncontrolled diode rectifier or the line-commutated thyristor rectifier, has been used at the front end to provide an uncontrolled or controlled *dc* output voltage.

However, such implementations can cause severe harmonic pollution problems

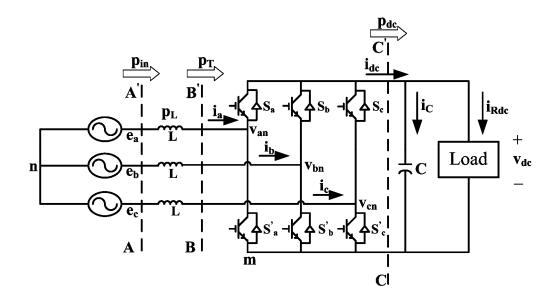

Fig. 1.1 Configuration of a three-phase boost-type PWM rectifier

in the utility grid. As the current drawn from the utility is highly distorted with a poor power factor, problems such as voltage distortion, additional losses due to high RMS current value, possible over-voltages due to system resonance conditions, and errors in metering and malfunction of utility relays are known to occur [3, 4]. Due to these problems, limits have been placed in recent times on the harmonic content of the line current of utility interfaced equipment by many standards and guidelines [5-7], such as IEC 1000-3-2, IEC 1000-3-4 and IEEE Std 519. In all such cases, where the amount of distorted current injected into the utility is limited by harmonic standards and guidelines, ac to dc rectifiers using diodes or thyristors cannot normally be used.

In addition, rectifiers using diodes or thyistors can only provide low quality *dc* output voltage. A large capacitor is normally required for smoothing the *dc* output voltage which increases the converter size, make the dynamic response slow and can decrease its reliability [1]. In the case of thyristor controlled rectifiers, the use of a large output capacitor also increases the system time constant and this when coupled with the low switching frequency degrades the dynamic performance of the system.

Due to the above, the demand for improved utility interface in various applications has increased substantially. By using semiconductor switches such as IGBTs (Insulated-Gate Bipolar Transistor), high frequency switching and better input and output performances become possible.

Among the available high performance three-phase rectifiers, the boost-type

2

Pulse-Width-Modulated (PWM) rectifier incorporating IGBTs (Fig. 1.1) has become the leading candidate in most three-phase ac-to-dc applications because of its salient attributes. By properly controlling a boost-type PWM rectifier, line currents drawn from the utility can be made to be sinusoidal and in phase with their corresponding supply voltages. Besides input current shaping and power factor correction, the dcoutput voltage provided by the rectifier can be maintained constant without the need for any large output-side energy storage elements. This is a consequence of the fact that the instantaneous power flow in any balanced three-phase ac system is constant. In addition, such a rectifier has bidirectional power delivery capability which is required in many ac and dc motor drive systems. These desirable attributes have made such PWM rectifiers very popular in three-phase ac-to-dc applications, for example, as the front-end converter for uninterruptible power supply systems (UPS) and inverter-fed variable-voltage and variable-frequency (VVVF) ac motor drives in industrial processes [8].

However, controlling the PWM rectifier system is not an easy task even under balanced operating conditions due to the complex nature of the system. The desirable attributes of PWM rectifiers mentioned in the previous paragraph can be fully realized under ideal balanced supply voltage conditions only with a properly implemented control scheme. Additionally, the presence of supply voltage imbalance in a PWM rectifier system will typically lead to forgoing the advantages by giving rise to a *dc* output voltage ripple at twice the line frequency as well as low order harmonics in the utility side line currents. In order to take full advantage of the strengths of the PWM rectifier under both balanced and unbalanced supply voltage conditions, it is important to investigate the issues associated with a three-phase boost-type PWM rectifier operating under both these conditions. The following two sections will present briefly the issues associated with the operation of a three-phase PWM rectifier.

# 1.1 PWM rectifier system operating under balanced supply voltage conditions

Normally, the control objectives of a PWM rectifier system are to regulate the *dc* output voltage and to shape the line currents so as to achieve unity power factor operation on the *ac* side. However, designing a proper controller for such a PWM rectifier system is generally a challenging task even in a balanced system. The available state-space-averaged model [26, 28] for the three phase rectifier under balanced supply conditions does not give much insight into the design of the controllers due to the rectifier's complex non-linear multi-input multi-output (MIMO) structure and the presence of a non-minimum phase feature in the system operation. Besides complicating the controller design, the presence of the non-minimum phase feature in this non-linear MIMO system also prevents us from fully understanding the behavior of the PWM rectifier system.

Extensive research has been carried out by other researchers on the modeling and control of PWM rectifier systems. Some simple MIMO linear models have been developed in [18, 19]. However, in these models, the non-minimum phase property

4

inherent in the PWM rectifiers has been neglected. Although this simplifies the system model and hence the controller design, the resulting closed-loop system will only operate stably within certain ranges of system parameters. This is because the information on the location of the non-minimum phase property determines the realizable closed loop bandwidth of the PWM rectifier system. Thus, it is important for a designer be able to include in the PWM rectifier model the non-minimum phase property in order to predict system performance and stability more accurately.

Therefore, issues associated with the PWM rectifier system operating under balanced supply voltage conditions mainly involve the need for the development of a simple, accurate and informative model with which the behavior of a PWM rectifier can be explained and explored easily and control schemes can be designed and implemented without much difficulty.

## **1.2 PWM rectifier system operating under unbalanced** supply voltage conditions

Although the PWM rectifier has the flexibility to control the power flow between the utility and the dc load, its performance can be sensitive to supply voltage imbalance [8]. To maintain a good operating environment for power customers, levels of imbalance of utility supply voltages should be typically maintained at less than 1% as prescribed by IEEE Std 1159-1995 [6]. However, due to poor enforcement of these standards, the imbalance in input supply is a common phenomenon in power utility, particularly in a weak ac system and may emerge because of the following reasons [5-11].

- Uneven distribution of single phase loads. Voltage imbalances due to imbalances in phase loads can be particularly severe if large single phase loads, such as arc furnaces are used [6-7].

- Asymmetrical winding of transformers which will cause different voltage drops in each phase.

- Unbalanced transmission impedance per phase which can also give rise to voltage imbalances.

- Influences due to fault or damage occurring in the transmission network.

Regardless of the causes, appearance of supply voltage imbalance will severely affect the behavior of a PWM rectifier. It would prevent the advantages of the rectifier system, such as low distortion input current and low ripple output dc voltage, from being fully realized.

Thus, the issues associated with a PWM rectifier system operating under unbalanced supply voltage conditions are mainly centered around two aspects, namely, developing a power regulation scheme with which the potential of a PWM rectifier can be partially or fully realized and current tracking schemes with which the required unbalanced line currents can be effectively tracked.

#### **1.3 Research objectives**

The overall purpose of the research work reported in this thesis is to investigate and solve some of the main control problems associated with a three-phase boost-type PWM rectifier operating under both balanced and unbalanced supply voltage conditions.

The main objectives of the research work are as follows:

To develop a simple, yet physically insightful model that is useful in the analysis and control of the PWM rectifier under balanced supply conditions.

To investigate and propose power regulation scheme(s) which can provide both high input performance and high output performance for a PWM rectifier system operating under unbalanced supply conditions.