### HBM: A HYBRID BUFFER MANAGEMENT SCHEME FOR SOLID STATE DISKS

**GONG BOZHAO**

### A THESIS SUBMITTED

### FOR THE DEGREE OF MASTER OF SCIENCE

### **DEPARTMENT OF COMPUTER SCIENCE**

### NATIONAL UNIVERSITY OF SINGAPORE

**June 2010**

## Acknowledgement

Fist of all, I want to thank my parents for their love and encouragement when I felt depressed during this period.

I would like to express my deep-felt gratitude to my supervisor, Prof. Tay Yong Chiang, for his guidance and patience. He always gave me valuable suggestions when I did not know how I should do research. He also cared about my life and offered his help for job opportunities. I also wish to thank Dr. Wei Qingsong for his help on this thesis. It was his research work that inspired me. The comments from Assoc. Prof. Weng Fai WONG and Assoc. Prof. Tulika Mitra for my Graduate Research Paper are greatly appreciated.

I like to thank a lot of my friends around me, Wang Tao, Suraj Pathak, Shen Zhong, Sun Yang, Lin Yong, Wang Pidong, Lun Wei, Gao Yue, Chen Chaohai, Wang Guoping, Wang Zhengkui, Zhao Feng, Shi Lei, Lu Xuesong, Hu Junfeng, Zhou Jingbo, Li Lu, Kang Wei, Zhang Xiaolong, Zheng Le, Lin Yuting, Zhang Wei, Deng Fanbo, Ding Huping, Hao Jia, Chen Qi, Ma He, Zhang Meihui, Lu Meiyu, Liu Linlin, Cui Xiang, Tan Rui, Chen Kejie, for sharing wonderful time with me.

Special thanks to friends currently in China, Europe and US. They were never ceasing in caring about me.

#### Gong Bozhao

# Contents

| A  | cknow   | vledgement                              | i   |

|----|---------|-----------------------------------------|-----|

| St | ımma    | ry                                      | v   |

| Li | st of [ | Tables                                  | vi  |

| Li | st of l | Figures                                 | vii |

| 1  | Intr    | oduction                                | 1   |

|    | 1.1     | Motivation                              | 2   |

|    | 1.2     | Contribution                            | 3   |

|    | 1.3     | Organization                            | 4   |

| 2  | Bac     | kground and Related Work                | 5   |

|    | 2.1     | Flash Memory Technology                 | 5   |

|    | 2.2     | Solid State Drive                       | 7   |

|    | 2.3     | Issues of Random Write for SSD          | 9   |

|    | 2.4     | Buffer Management Algorithms for SSD    | 10  |

|    |         | 2.4.1 Flash Aware Buffer Policy         | 11  |

|    |         | 2.4.2 Block Padding Least Recently Used | 12  |

|   |                         | 2.4.3                                                                     | Large Block CLOCK                                                                                                                                                         | 14                                                                                                                     |

|---|-------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                         | 2.4.4                                                                     | Block-Page Adaptive Cache                                                                                                                                                 | 16                                                                                                                     |

| 3 | Hyb                     | rid Buf                                                                   | fer Management                                                                                                                                                            | 18                                                                                                                     |

|   | 3.1                     | Hybric                                                                    | l Management                                                                                                                                                              | 19                                                                                                                     |

|   | 3.2                     | A Buff                                                                    | Fer for Both Read and Write Operations                                                                                                                                    | 21                                                                                                                     |

|   | 3.3                     | Locali                                                                    | ty-Aware Replacement Policy                                                                                                                                               | 22                                                                                                                     |

|   | 3.4                     | Thresh                                                                    | old-based Migration                                                                                                                                                       | 28                                                                                                                     |

|   | 3.5                     | Impler                                                                    | nentation Details                                                                                                                                                         | 30                                                                                                                     |

|   |                         | 3.5.1                                                                     | Using B+ Tree Data Structure                                                                                                                                              | 30                                                                                                                     |

|   |                         | 3.5.2                                                                     | Implementation for Page Region and Block Region                                                                                                                           | 32                                                                                                                     |

|   |                         | 3.5.3                                                                     | Space Overhead Analysis                                                                                                                                                   | 34                                                                                                                     |

|   |                         |                                                                           |                                                                                                                                                                           |                                                                                                                        |

|   | 3.6                     | Dynan                                                                     | nic Threshold                                                                                                                                                             | 36                                                                                                                     |

| 4 |                         |                                                                           | nic Threshold                                                                                                                                                             | 36<br><b>40</b>                                                                                                        |

| 4 |                         | eriment                                                                   |                                                                                                                                                                           |                                                                                                                        |

| 4 | Expe                    | eriment<br>Workle                                                         | and Evaluation                                                                                                                                                            | <b>40</b><br>40                                                                                                        |

| 4 | <b>Expo</b><br>4.1      | eriment<br>Workle                                                         | and Evaluation                                                                                                                                                            | <b>40</b><br>40<br>41                                                                                                  |

| 4 | <b>Expo</b><br>4.1      | eriment<br>Workle<br>Experi                                               | and Evaluation                                                                                                                                                            | <b>40</b><br>40<br>41<br>41                                                                                            |

| 4 | <b>Expo</b><br>4.1      | eriment<br>Workle<br>Experi<br>4.2.1                                      | and Evaluation   bad Traces   ment Setup   Trace-Driven Simulator                                                                                                         | <b>40</b><br>40<br>41<br>41<br>42                                                                                      |

| 4 | <b>Expo</b><br>4.1      | eriment<br>Workle<br>Experi<br>4.2.1<br>4.2.2<br>4.2.3                    | and Evaluation   bad Traces   ment Setup   Trace-Driven Simulator   Environment                                                                                           | <b>40</b><br>40<br>41<br>41<br>42<br>42                                                                                |

| 4 | <b>Exp</b> (4.1)<br>4.2 | eriment<br>Workle<br>Experi<br>4.2.1<br>4.2.2<br>4.2.3                    | and Evaluation   bad Traces   ment Setup   Trace-Driven Simulator   Environment   Evaluation Metrics                                                                      | <ul> <li>40</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> </ul>                         |

| 4 | <b>Exp</b> (4.1)<br>4.2 | eriment<br>Workle<br>Experi<br>4.2.1<br>4.2.2<br>4.2.3<br>Analys          | and Evaluation   bad Traces   ment Setup   Trace-Driven Simulator   Environment   Evaluation Metrics   Sis of Experiment Results                                          | <ul> <li>40</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> </ul>             |

| 4 | <b>Exp</b> (4.1)<br>4.2 | eriment<br>Workle<br>Experi<br>4.2.1<br>4.2.2<br>4.2.3<br>Analys<br>4.3.1 | and Evaluation   oad Traces   ment Setup   Trace-Driven Simulator   Environment   Evaluation Metrics   sis of Experiment Results   Analysis on Different Random Workloads | <ul> <li>40</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> <li>50</li> </ul> |

| 4.3.5      | Energy Consumption of Flash Chips | 56 |

|------------|-----------------------------------|----|

| Conclusion |                                   | 59 |

5

### Summary

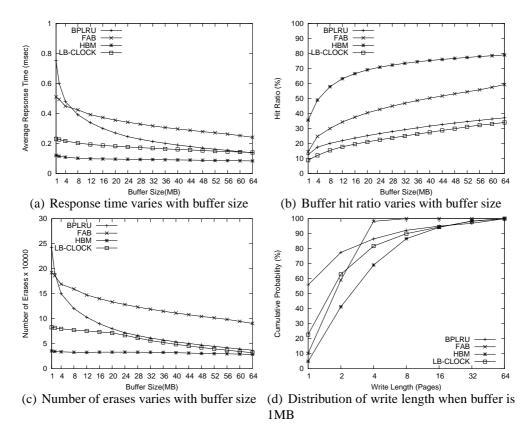

Random writes significantly limit the application of flash memory in enterprise environment due to its poor latency and high garbage collection overhead. Several buffer management schemes for flash memory have been proposed to overcome this issue, which operate either at page or block granularity. Traditional page-based buffer management schemes leverage temporal locality to pursue buffer hit ratio improvement without considering sequentiality of flushed data. Current block-based buffer management schemes exploit spatial locality to improve sequentiality of write accesses passed to flash memory at a cost of low buffer utilization. None of them achieves both high buffer hit ratio and good sequentiality at the same time, which are two critical factors determining the efficiency of buffer management for flash memory. In this thesis, we propose a novel hybrid buffer management scheme referred to as HBM, which divides buffer space into page region and block region to make full use of both temporal and spatial localities among accesses in hybrid form. HBM dynamically balances our two objectives of high buffer hit ratio and good sequentiality for different workloads. HBM can make more sequential accesses passed to flash memory and efficiently improve the performance.

We have extensively evaluated HBM under various enterprise workloads. Our benchmark results conclusively demonstrate that HBM can achieve up to 84% performance improvement and 85% garbage collection overhead reduction compared to existing buffer management schemes. Meanwhile, the energy consumption of flash chips for HBM is limited.

# **List of Tables**

| 1.1 | Comparison of page-level LRU, block-level LRU and hybrid LRU | 3  |

|-----|--------------------------------------------------------------|----|

| 3.1 | The rules of setting the values of $\alpha$ and $\beta$      | 38 |

| 4.1 | Specification of workloads                                   | 40 |

| 4.2 | Timing parameters for simulation                             | 42 |

| 4.3 | Synthetic workload specification in Disksim_Synthgen         | 51 |

| 4.4 | Energy consumption of operations inside SSD                  | 57 |

# **List of Figures**

| 2.1 | Flash memory chip organization                                        | 6  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | The main data structure of FAB                                        | 11 |

| 2.3 | Page padding technique in BPLRU algorithm                             | 13 |

| 2.4 | Working of the LB-CLOCK algorithm                                     | 15 |

| 3.1 | Syntem overview                                                       | 19 |

| 3.2 | Distribution of request sizes for ten traces from SNIA                | 20 |

| 3.3 | Hybrid buffer management                                              | 21 |

| 3.4 | Working of LAR algorithm                                              | 27 |

| 3.5 | Threshold-based migration                                             | 29 |

| 3.6 | B+ tree to manage data for HBM $\ldots$                               | 31 |

| 3.7 | Data management in page region and block region                       | 32 |

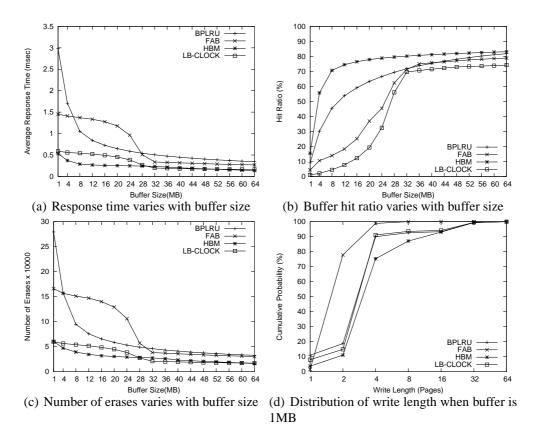

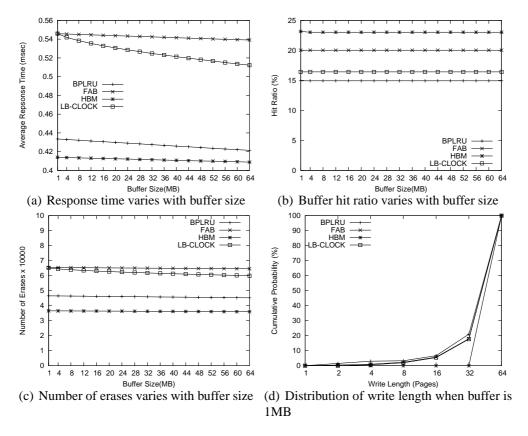

| 4.1 | Result of Financial Trace                                             | 44 |

| 4.2 | Result of MSNFS Trace                                                 | 46 |

| 4.3 | Result of Exchange Trace                                              | 47 |

| 4.4 | Result of CAMWEBDEV Trace                                             | 48 |

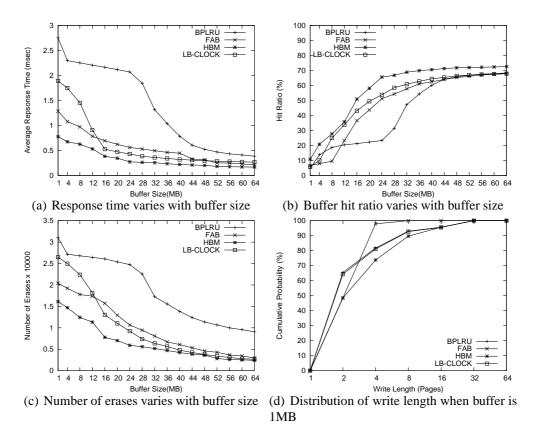

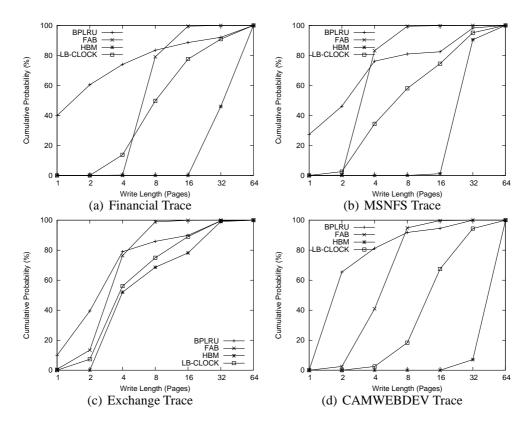

| 4.5 | Distribution of write length when buffer size is $16MB \ldots \ldots$ | 50 |

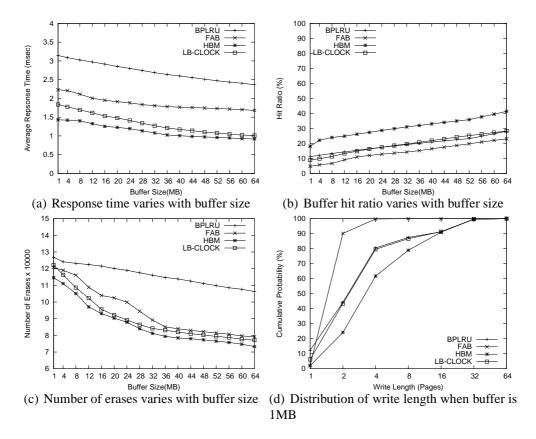

| 4.6 | Result of Synthetic Trace                                             | 52 |

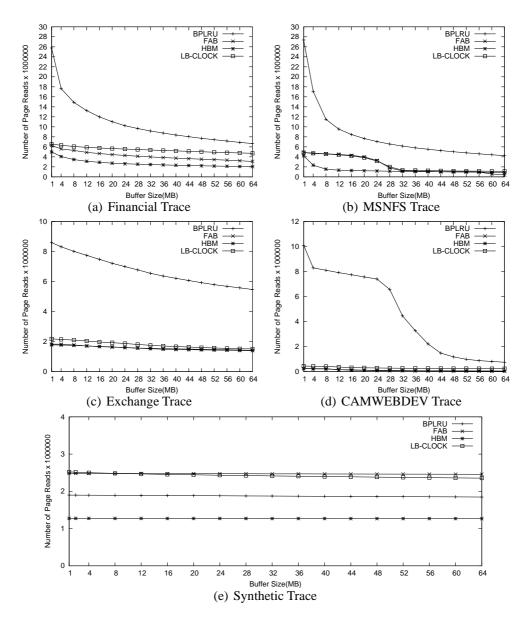

| 4.7 | Total page reads under five traces                                    | 53 |

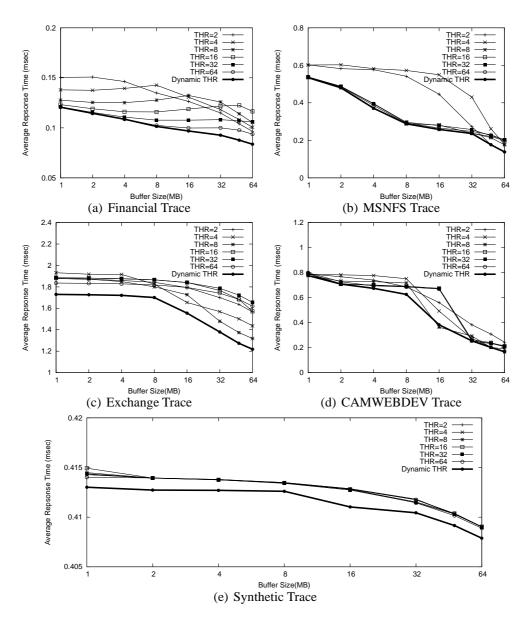

| 4.8 | Effect of thresholds on HBM                                           | 55 |

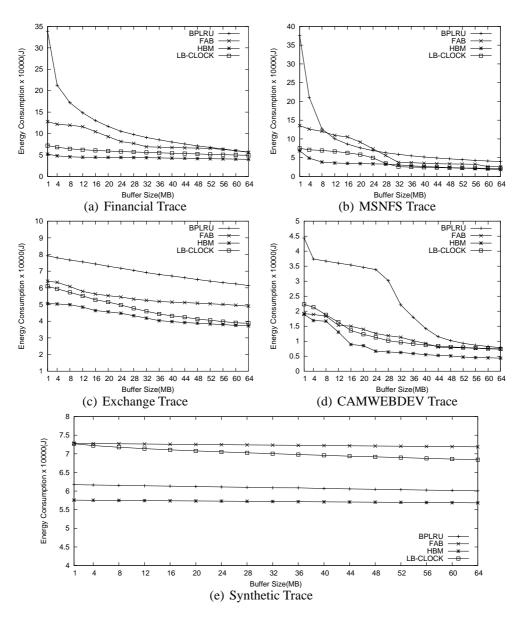

| 4.9 | Energy consumption of flash chips under five traces                   | 58 |

# Chapter 1

# Introduction

Flash memory has shown its obvious merits especially in the storage space compared to the traditional hard disk drive (HDD), such as small size, quick access, saving energy [14]. It is originally used as primary storage in the portable devices, for example, MP3, digital camera. As its capacity is increasing and its price is dropping, replacing HDD over the personal computer storage and even server storage with flash memory in the form of Solid State Drive (SSD) has been paid more attention. Actually, Samsung<sup>1</sup> and Toshiba<sup>2</sup> have launched the laptops with only SSDs. Google<sup>3</sup> considers replacing parts of its storage with Intel<sup>4</sup> SSD storage in order to save energy [10], and MySpace<sup>5</sup> has made use of the Fusion-IO<sup>6</sup> ioDrives Duo as its primary storage servers instead of hard disk drives, and this switch brought it large energy consumption [29].

<sup>&</sup>lt;sup>1</sup>www.samsung.com

<sup>&</sup>lt;sup>2</sup>www.toshiba.com

<sup>&</sup>lt;sup>3</sup>www.google.com

<sup>&</sup>lt;sup>4</sup>www.intel.com

<sup>&</sup>lt;sup>5</sup>www.myspace.com

<sup>&</sup>lt;sup>6</sup>www.fusionio.com

### 1.1 Motivation

Although SSD shows its attractive worthiness especially on improving the random read performance due to no mechanical characteristic, however, it could suffer from random write<sup>7</sup> issue especially when it is applied in the enterprise environment [33].

Just like HDD, SSD can make use of RAM inside as the buffer to improve performance [22]. The buffer can delay the requests which directly operate on flash memories, such that the response time of operations could be reduced. Additionally, it also can reorder the write request stream to make the sequential write flushed first when the synchronized write is necessary. Different from HDD, buffer inside SSD can be managed not only at page granularity but also at block granularity<sup>8</sup>. In other words, the basic unit in the buffer could be a logical block equal to the physical block size in flash memories. Block is larger than page in flash memory, which usually consists of 64 or 128 pages. The internal structure of flash memory will be introduced in section 2.1. Existing buffer management algorithms try to exploit the temporal locality or spatial locality in the access patterns in order to get high buffer hit ratio or good sequentiality of flushed data, which are two critical factors determining the efficiency of buffer management inside SSD.

However, these two targets could not be achieved simultaneously under the existing buffer management algorithms. Therefore, we are motivated to design a novel hybrid buffer management algorithm which manages data both at page granularity and block granularity, in order to fully utilize both temporal and sequential localities to achieve high buffer hit ratio and good sequentiality for

SSD.

<sup>&</sup>lt;sup>7</sup>In this thesis, random request means small-to-moderate sized random request if not specified.

<sup>&</sup>lt;sup>8</sup>Another expression of page granularity or block granularity is page-level or block-level, page-based or block-based

To illustrate the limitation of current buffer management schemes and our motivation to design a hybrid buffer management, a reference pattern including sequential and random accesses is shown in the Table 1.1.

**Table 1.1:** Comparison of page-level LRU, block-level LRU and hybrid LRU. Buffer size is 8 pages and an erase block contains 4 pages. Hybrid LRU maintains buffer at page and block granularity, and only full blocks will be managed at block granularity and will be selected as victim. In this example, we use [] to denote block boundary.

| Access    | Page-Level LRU     |       |      | Block-Level LRU            |           |      | Hybrid LRU          |           |      |

|-----------|--------------------|-------|------|----------------------------|-----------|------|---------------------|-----------|------|

| Access    | Buffer(8)          | Flush | Hit? | Buffer(8)                  | Flush     | Hit? | Buffer(8)           | Flush     | Hit? |

| 0,1,2,3   | 3,2,1,0            |       | Miss | [0,1,2,3]                  |           | Miss | [0,1,2,3]           |           | Miss |

| 5,9,11,14 | 14,11,9,5,3,2,1,0  |       | Miss | [14],[9,11],[5],[0,1,2,3]  |           | Miss | 14,11,9,5,[0,1,2,3] |           | Miss |

| 7         | 7,14,11,9,5,3,2,1  | 0     | Miss | [5,7],[14],[9,11]          | [0,1,2,3] | Miss | 7,14,11,9,5         | [0,1,2,3] | Miss |

| 3         | 3,7,14,11,9,5,2,1  |       | Hit  | [3],[5,7],[14],[9,11]      |           | Miss | 3,7,14,11,9,5       |           | Miss |

| 11        | 11,3,7,14,9,5,2,1  |       | Hit  | [9,11],[3],[5,7],[14]      |           | Hit  | 11,3,7,14,9,5       |           | Hit  |

| 2         | 2,11,3,7,14,9,5,1  |       | Hit  | [2,3],[9,11],[5,7],[14]    |           | Miss | 2,11,3,7,14,9,5     |           | Miss |

| 14        | 14,2,11,3,7,9,5,1  |       | Hit  | [14],[2,3],[9,11],[5,7]    |           | Hit  | 14,2,11,3,7,9,5     |           | Hit  |

| 1         | 1,14,2,11,3,7,9,5  |       | Hit  | [1,2,3],[14],[9,11],[5,7]  |           | Miss | 1,14,2,11,3,7,9,5   |           | Miss |

| 10        | 10,1,14,2,11,3,7,9 | 5     | Miss | [9,10,11],[1,2,3],[14]     | [5,7]     | Miss | 10,1,14,2,11,3,7,9  | 5         | Miss |

| 7         | 7,10,1,14,2,11,3,9 |       | Hit  | [7],[9,10,11],[1,2,3],[14] |           | Miss | 7,10,1,14,2,11,3,9  |           | Hit  |

|           | Sequential flush   | 0     |      |                            | 1         |      |                     | 1         |      |

|           | Buffer hit         |       | 6    |                            |           | 2    |                     |           | 3    |

In this example, page-level LRU achieves 6 hits higher than block-level LRU, and block-level LRU has 1 sequential flush better than page-level LRU. Hybrid LRU achieves 3 buffer hits and 1 sequential flush, which combines the advantages of both page-level LRU and block-level LRU.

#### **1.2** Contribution

In order to research on the device-level buffer management<sup>9</sup> for SSD using FlashSim [25] SSD simulator designed by the Pennsylvania State University, some implementation work has been done first. Firstly, we add BAST [24] FTL scheme into FlashSim, because some existing buffer management algorithms are based on this basic log-block FTL [24] scheme. Then we integrate a buffer module above FTL level and implement four buffer management algorithms for SSD, which are BPLRU [22], FAB [18], LB-CLOCK [12], and HBM.

We propose a hybrid buffer management scheme referred to as HBM, which

<sup>&</sup>lt;sup>9</sup>It means the buffer is inside SSD.

gives consideration to buffer hit ratio and sequentiality by exploiting both temporal and spatial localities among access patterns. Based on this hybrid scheme, the whole buffer space is divided into two regions: page region and block region. These two regions are managed in different ways. Specifically, in the page region, data is managed and adjusted in logical page granularity to improve buffer space utilization, while logical block is the basic unit in the block region. Page region prefers the random small sized access pages, while sequential access pages in the block region are replaced first when new incoming data cannot be hold any more. Data can not only be moved inside page region or block region, but also dynamically migrated from page region to block region when the number of pages in the same logical block reaches a threshold that is adaptive to different workloads. According to hybrid management and dynamic migration, HBM improves the performance of SSD by significantly reducing the internal fragmentation and garbage collection overhead associated with random write, meanwhile, the energy consumption of flash chips for HBM is limited.

#### **1.3 Organization**

The remainder of this thesis is organized as follows: Chapter 2 gives an overview of background knowledge of flash memory and SSD, and surveys some existing well known buffer management algorithms inside SSD. Chapter 3 presents details of hybrid buffer management scheme. Evaluation and experiment results are presented in Chapter 4. In Chapter 5, we conclude this thesis and possible future work is summarized.

## Chapter 2

# **Background and Related Work**

In this chapter, basic background knowledge of flash memory and SSD is introduced first. The issue of random writes for SSD is subsequently explained. Then we mainly present three existing buffer management algorithms for SSD. After each buffer management, the work will be summarized in brief. Specially, in the end of this chapter, we introduce a similar research framework with ours: BPAC, however, from which our research work have different internal techniques.

#### 2.1 Flash Memory Technology

Two types of flash memories<sup>1</sup>, NOR and NAND [36], are existing. In this thesis, flash memory refers to NAND specifically, which is much like block devices accessed in units of sectors, because it is the common data storage material regarding to flash memory based SSDs on the market.

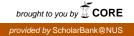

Figure 2.1 shows the internal structure of a flash memory chip, which consists dies sharing a serial I/O bus. Different operations can be executed in different dies. Each die contains one or more planes, which contains blocks (typically 2048 blocks) and page-sized registers for buffering I/O. Each block includes

<sup>&</sup>lt;sup>1</sup>We also use term "flash chips" or "flash memory chips" as alternative expression of flash memory.

Figure 2.1: Flash memory chip organization. Figure adapted from [35]

pages, which has data and mete data area. The typical size of data area is 2KB or 4KB, and meta data area (typically 128 bytes) is used to store identification or correction information and page state: *valid, invalid* or *free*. Initially, all the pages are in free state. When a write operation happens on a page, the state of this page is changed to valid. For updating this page, mark this page invalid first, then write data into a new free page. This is called *out-of-place update* [16]. In order to change the invalid state of a page into free again, the whole block that contains the page should be erased first.

Three operations are allowed for NAND: *Read*, *Write* and *Erase*. As for reading a page, the related page is transferred into the page register then I/O bus. The cache register is especially useful for reading sequential pages within a block, specifically, pipelining the reading stream by page register and cache register can improve the read performance. Read operation costs least in the flash memory. To write a page, the data is transferred from I/O bus into page register first, similar to the read operation, for sequentially writing, the cache register can be used. A write operation can only change bit values from 1 to 0 in the flash chips. Erasing is the only way to change bit values back to 1. Unlike read and write both of which can be performed at the page level, the block accessed unit is for erasing. After erasing a block, all bit values for all pages within a block are set to 1. So erase operation cost most in the flash memory. In addition, for each block, erase count that can be endured before it is worn out is finite, typically

around 100000.

#### 2.2 Solid State Drive

SSD is constructed from flash memories. It provides the same physical host interface as HDD to allow operating systems to access SSD in the same way as conventional HDD. In order to do that, an important firmware called Flash Translation Layer (FTL) [4] is implemented in the SSD controller. Three important functions provided by FTL are *address mapping*, *garbage collection* and *wear leveling*.

Address Mapping - FTL maintains the mapping information between logical page and physical page [4]. When it processes the write operation, it writes the new page to a suitable empty page if the requested place has already been accessed before. Meanwhile, it marks the valid data in the requested place invalid. Depending on the granularity of address mapping, FTL can be classified into three groups: page-level, block-level and hybrid-level FTL [9]. In the page-level FTL, each logical page number (LPN) is mapped to each physical page number (PPN) in flash memory. However this efficient FTL requires much RAM inside SSD in order to store the mapping table. Block-level FTL associates logical blocks with physical blocks, in which the mapping table is less. However, the mechanism that requires the same page offsets between the logical block and the corresponding physical block makes it not efficient because updating one page could lead to update the whole block. Hybrid-level FTL<sup>2</sup> combines page mapping with block mapping. It reserves a small amount of blocks called log blocks in which page-level mapping is used to buffer the small size write requests. Other than log blocks, the rest blocks called data blocks in which block-level mapping is used to hold ordinary data. The data block holds old data after write requests, the new data will be written in the corresponding

<sup>&</sup>lt;sup>2</sup>It is also called Log-scheme FTL

log block. Hybrid-level FTL shows less garbage collection overhead and the required size of mapping table is less than page-level FTL. However, it incurs expensive full merges for random write dominant workloads.

*Garbage Collection* - when free blocks are used up or a pre-defined threshold, garbage collection module is triggered to produce more free blocks by recycling invalidated pages. Regarding page-level mapping, it should first copy the valid pages out of the victim block and then write them into some new block. For block-level and hybrid-level mappings, it should merge the valid pages together with the updated pages whose logical page number is the same as them. During merge operation, due to copying valid pages of the data block and log block (under hybrid-level mapping), extra read and write operations must be invoked besides the necessary erase operations. Therefore, merge operations cost most during garbage collection [21].

There are three kinds of merge operations: *switch merge*, *partial merge* and *full merge* [16]. Considering the hybrid-level mapping, switch merge usually happens when the page sequence of log block is the same as that of data block. Log block will become the new data block because of all the new pages within it, while data block which contains all the old pages will be just erased without extra read or write operations. So switch merge cost less among merge operations. Partial merge happens when log blocks still can become new data block. In other words, all the valid pages in the data block can be copied to the log block first, then the data block is erased. Compared to partial merge, full merge happens in the condition that some valid page in the data block can not be copied to the log block and only a new allocated data block can hold it. During full merge, not only valid pages in the log block, after that, the old data block and log block, but also the ones in the log block, after that, the old data block and log block are erased. So full merge cost most among merge operations.

On the basis of the cost of merge operations, an efficient garbage collection

should make good use of switch merge operations and avoid full merge operations. Sequential writes which update sequentially can create opportunities of switch merge operations, and small sized random writes often go with expensive full merges. This is the reason why SSD suffers from random writes.

*Wear leveling* - some blocks are often written because of the locality in most workloads. So there exists wear out problem for some blocks due to frequently erasure compared to other blocks. FTL takes the responsibility for ensuring that even use is made of all the blocks by some wear leveling algorithm [7].

There are many kinds of FTLs proposed in academia, such as BAST, FAST [27], LAST [26], Superblock-based FTL [20], DFTL [16] and NFTL [28] and so on. Of these schemes, BAST and FAST are two representative ones. The biggest difference between BAST and FAST is that BAST has one to one correspondence between log block and data block, while FAST has many to many correspondence. However, in this thesis, BAST is used as the default FTL because almost every existing buffer management algorithm in SSD is based on BAST FTL [21].

#### 2.3 Issues of Random Write for SSD

Firstly, according to out-of-place update for flash memory (see section 2.1), *internal fragmentation* [8] could be seen sooner or later if small size and random writes are distributed in much range of logical address space. It could result in some invalid page existing in almost all physical blocks. In that case, the prefetching mechanism inside SSD could not be effective because pages which are logically contiguous are probably physically distributed. This causes the bandwidth of sequential read to drop closely to the bandwidth of random read.

Secondly, the performance of sequential writes could be optimized over striping or interleaving mechanism [5][31]inside SSD, which is not effective for random writes. If a write is sequential, the data can be striped and written across different parallel units. Moreover, multi-page read or write can be efficiently interleaved over pipeline mechanism [13], while multiple single-page reads or writes can not be conducted in this way.

Thirdly, more random writes can incur higher overhead of garbage collection, which is usually triggered to produce more free blocks when the number of free blocks gets lower than a pre-defined threshold. During garbage collection, sequential writes can incur lower-cost switch merge operations, and random writes can incur much higher-cost full merge operations which are usually accompanied by extra reads or writes. In addition, these internal operations running in the background may compete for resources with incoming foreground requests [8] and therefore increase latency.

Finally, increased erase operations due to random writes could incur more erase operations and shorten the lifetime of the SSD. Experiments in [23] show that random write intensive workload could make flash memory wear out over hundred times faster than sequential write intensive workload.

### 2.4 Buffer Management Algorithms for SSD

Many existing disk based buffer management algorithms are based on page level, such as LRU, CLOCK [11], 2Q [19] and ARC [30]. These algorithms try to increase buffer hit ratio as much as possible. Specifically, they only focus on utilizing temporal locality to predict the next pages to be accessed and minimize page fault rate [17]. However, directly applying these algorithms is not enough for SSD because spatial locality is not catered for, and the sequential requests may be broken up into small segments so that the overhead of flash memories may increase when replacement happens.

In order to exploit spatial locality and provide more sequential writes for flash

memories in SSD, buffer algorithms based on block level are proposed, such as FAB, BPLRU and LB-CLOCK. According to these algorithms, accessing a logical page results in adjusting all the pages in the same logical block based on the assumption that all pages in this block have the same recency. In the end of this section, a similar algorithm with our work called BPAC [37] will be introduced in brief. However, we have several different internal designs and implementations. Because BPAC is introduced by a short research paper which shows not much information about its details, moreover, BPAC and our work has been done independently at the same time, so here we just briefly describe some similarities and differences.

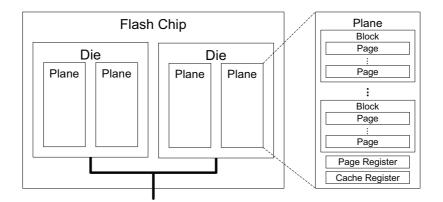

#### 2.4.1 Flash Aware Buffer Policy

The flash aware buffer (FAB) [18] is a block-level buffer management algorithm for flash storage. Similar to LRU, it also maintains a LRU list in its data structure. However, the node in the list is not a page unit, but a block unit, meaning that pages belonging to the same logical block of flash memory are in the same node. When a page is accessed, the whole logical block which belongs to is moved to the head of the list which is the most recent accessed end. If a new page is added to the buffer, it is also inserted into the most recent used end of the list. Moreover, due to block-level algorithm, FAB flushes the whole victim block, not a single victim page. The logical view of FAB is shown in figure 2.2.

Figure 2.2: The main data structure of FAB

In the block node, the page counter means the number of pages which belong to the block. In FAB, a block whose has the largest page counter is always to be selected to be flushed. If there is not only one candidate victim block, it will choose the least recently used one.

In some cases, FAB decreases the number of extra operations in the flash memory, because it flushes valid pages in the buffer as often as possible, and it may decrease copy valid page operations when erasing a block in the flash memory. Especially, when the victim block is full, the switch merge can be executed. Therefore, FAB shows better performance than LRU when most of I/O requests are sequential due to the small latency of erase operation when it is triggered. However, when the I/O requests are random, it may lower its performance. For example, if the page counter of every block node is one and the buffer is full. FAB becomes the normal LRU in this extreme case. FAB has Another problem that the recently used pages will be evicted if they belong to the block that has the largest page counter. This problem results from the fact that selecting a victim page is mostly based on the value of page counter, not the page recency. In addition, based on the rule of FAB, only dirty pages are actually written into the flash memory, and all the clean pages are discarded. This policy may results in internal fragmentation, which significantly impacts the efficiency of garbage collection and performance.

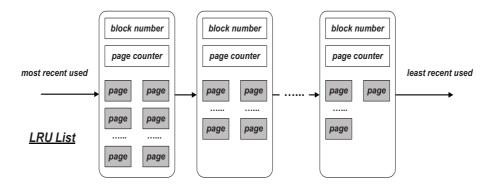

#### 2.4.2 Block Padding Least Recently Used

Similar to FAB, Block Padding Least Recently Used (BPLRU) [22] also a blocklevel buffer algorithm, moreover, it manages the blocks by LRU. Besides blocklevel LRU, BPLRU adopts a kind of Page Padding technique which improves the performance of random writes. With this technique, when a block needs to be evicted and it is not full, first reads those vacant pages not in the evicted block now but in the flash memory, then writes all pages in victim block sequentially. So this technique can bring BPLRU sequentiality of flushed block at the cost of more extra read operations, because read operation is the least costly in flash memory. Figure 2.3 shows working of page padding.

Figure 2.3: Page padding technique in BPLRU algorithm

In this example, the current victim block has page 0 and page 3, and page 1 and page 2 are in the data block of flash memory, so BPLRU first reads page 1 and page 2 from the flash memory in order to make the victim block full, then writes the full victim block into the log block sequentially, and only a switch merge may happens.

In addition to page padding, BPLRU uses another simple technique called LRU Compensation. It assumes that a block that is written sequentially shows the least possibility that some page is written in this block again in the near future. So if the most recently accessed block is written sequentially, it is moved to the end of LRU list that is least recent used.

It is also worthy to note that BPLRU is just a writing buffer management algorithm. For read operation, BPLRU first checks buffer, if buffer hit happens, it will read data from buffer, but it does not re-arrange the LRU list by read operations. If buffer miss happens, it will directly read data from the physical flash memory storage, and does not allocate buffer space for read data. Normal buffer including FAB allocates buffer for data which is read, but BPLRU does not.

On the one hand, although page padding may increase the read overhead, an efficient switch merge operation is introduced as many as possible instead of the expensive full merge operation, so BPLRU improves the performance of random writes in flash memory. On the other hand, when most of blocks only include few pages, the increased read overhead could be so large that it in turn lowers the performance. In addition, if the vacant pages are not in the flash memory either, the efficiency of page padding could be impacted. Despite the fact that BPLRU concerns the page recency by selecting the victim block in the end of the LRU list, it just considers some page of high recency. In other words, if one of pages in a block has a high recency, other not recently used pages belonging to the same block also stay in the buffer. These pages will waste the space of buffer and increase the buffer miss ratio. Additionally, when page replacement has to happen, all the pages in the whole victim block are flushed simultaneously, including the pages that may be accessed later. Therefore, while spatial locality is aware in block-level scheme, temporal locality is ignored to some extent. So it will result in low buffer space utilization or low buffer hit ratio, and further decrease the performance of SSD. This is also the common issue of block-level buffer management algorithm.

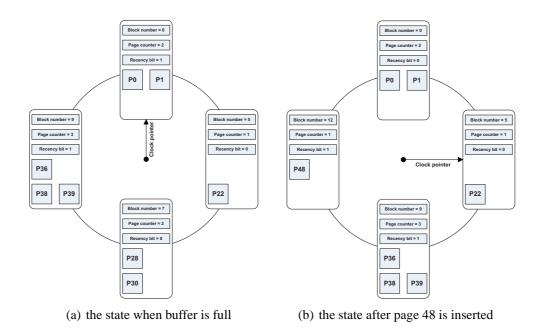

#### 2.4.3 Large Block CLOCK

Large Block CLOCK (LB-CLOCK) [12] also manages buffer with logical blocks. Other than the algorithms above, it is not designed based on LRU, but the CLOCK [11]. A reference bit is tagged in every block in the buffer. When any page of one block is accessed, the reference bit is set to 1. Logical blocks in the buffer are managed in the form of a circular list, and a pointer traverses clockwise. When it has to select a victim block, LB-CLOCK first finds the

Figure 2.4: Working of the LB-CLOCK algorithm

block that the clock pointer is pointing to, then checks its reference bit. It sets the reference bit to 0 if the value 1 is shown, and moves the clock pointer to the next block. The clock pointer stops moving until the value 1 of reference bit is encountered. Different from CLOCK algorithm, LB-CLOCK further chooses the victim block from the candidate victim blocks set which includes the blocks whose reference bits are 0 prior to current victim selection until the block which has the largest number of pages is selected. Figure 2.4 shows a running example of LB-CLOCK.

In this example, suppose a block can include 4 pages at most, when page 48 is going to be inserted, LB-CLOCK has to replace a victim block with new block 12 (48/4) due to full buffer now. Now the clock pointer is pointing to block 0 when starting to choose a victim block. Because the reference bit of block 0 is 1, the clock pointer moves next after the reference bit is set to 0. Now it is pointing to block 5 whose reference bit is 0, so the victim selection process is over. As shown in figure 2.4(a), the candidate victim blocks are block 5 and block 7, because their reference bits are 0. Block 0 is not considered because its reference bit is just changed into 0 in this current selection round. Finally,

block 7 has the highest number of pages and it is chosen as the final victim block. After replacement, block 12 with page 48 is inserted into the position which is just before block 0 as the clock pointer initially points to block 0, and its reference bit is set to 1, as shown in figure 2.4(b).

In addition, LB-CLOCK makes use of the following heuristic: it assumes that there is low probability that a block will be accessed again in the near future if the last page (i.e. page which has the biggest page number) of the block is written. So if the last page is written and the current block is full, this block is one victim candidate. If the current block is not full after the last page written but it has more pages than the previously evicted block, it is also one victim candidate. Besides, just like BPLRU, the block written sequentially shows low possibility that it will be accessed later such that it can be a victim candidate block.

Similar to BPLRU, LB-CLOCK is also a writing buffer management algorithm, meaning that it will not allocate buffer space for read data. So it reduces the opportunity that a full block is formed in the buffer. When a victim block has to be chosen, LB-CLOCK is different from FAB which takes preference for block space utilization (page counter described in section 2.2), and then recency. On the contrary, it takes preference for recency and then block space utilization. Although it tries to make a balance between the priority given to recency and block space utilization, the assumptions in the heuristic are not strongly supported.

#### 2.4.4 Block-Page Adaptive Cache

Block-Page Adaptive Cache (BPAC) is a write buffer algorithm which aims to fully make use of temporal locality and spatial locality to improve the performance of flash memory. It is a similar research work with our HBM, but has different strategies and details. Here we just briefly shows some similarities and differences before our HBM is introduced. Just like HBM, BPAC [37] has the framework in which page list and block list are separately maintained to better explore temporal locality and spatial locality. In addition, there exist dynamically page migrations between page list and block list.

In the similar framework, BPAC and HBM has many obvious and significant differences. BPAC is just a write buffer compared to HBM that not only focuses on write operations but also read operations. In addition, BPAC makes use of thresholds based on experiments to control page migrations between page list and block list. Not like BPAC, only dynamically page migration from page list to block list is designed in HBM, because the migration from block list to page list may result in a great number of page insert operations, especially when the number of pages in a block get bigger as capacity of flash memory increases, massively inserting pages into page list lowers the performance of algorithm. Besides two differences above, a new algorithm called LAR is designed in HBM to quickly index the nodes. The details of HBM will be shown in the next section.

## Chapter 3

# **Hybrid Buffer Management**

We design HBM as a universal buffer scheme, meaning that it is not only for write operations but also read operations. We have assumed that the buffer memory is RAM. A RAM usually exists in current SSDs in order to store mapping information of FTL [22]. When SSD is powered on, mapping information is read from flash chips into RAM. Once SSD is powered off, mapping information is written back to flash chips. We choose to use all of available RAM as buffer for HBM.

Figure 3.1 shows the system overview considered in this thesis. Host system may include a buffer where LRU could be applied. However in this thesis, we do not assume any special buffer algorithm in host side. SSD includes RAM for buffering read and write accesses, FTL and flash chips.

In this chapter, we will describe the design of HBM in detail. Hybrid management and universal feature servicing both read and write accesses are proposed first. Then a locality-aware replacement policy called LAR<sup>1</sup> is designed to manage the block region of HBM. In order to implement page migration from page region to block, we advance threshold-based migration method and meanwhile adopt B+ tree to manage HBM efficiently. Space overhead due to B+ tree is

<sup>&</sup>lt;sup>1</sup>We designed LAR in the paper "FlashCoop: A Locality-Aware Cooperative Buffer Management for SSD-based Storage Cluster", which is published in ICPP 2010.

| Host System |                                              |        |          |  |  |  |

|-------------|----------------------------------------------|--------|----------|--|--|--|

| writes      |                                              |        | reads    |  |  |  |

|             |                                              |        |          |  |  |  |

| (Univers    | RAM Buffer<br>(Universal Buffer Scheme, HBM) |        |          |  |  |  |

| writes      | writes                                       |        |          |  |  |  |

| Flash       | Flash Translation Layer                      |        |          |  |  |  |

| Flash Chips | S                                            | Fla    | sh Chips |  |  |  |

|             |                                              |        |          |  |  |  |

| Flash Chips | 5                                            | Fla    | sh Chips |  |  |  |

| Sol         | id State                                     | e Driv | е        |  |  |  |

**Figure 3.1:** System overview. The proposed buffer management algorithm HBM is applied to RAM buffer inside SSD.

also analyzed in theory. How to dynamically adjust threshold will be discussed in the final section of this chapter.

#### 3.1 Hybrid Management

Some previous researches [34][15] claimed that the more popular the file is, the smaller size it has, and large files are not accessed frequently. So file size and its popularity have inverse relation. As [26] reports, 80% of file requests are to files whose size is less than 10KB and the locality type of each request is deeply related to its size.

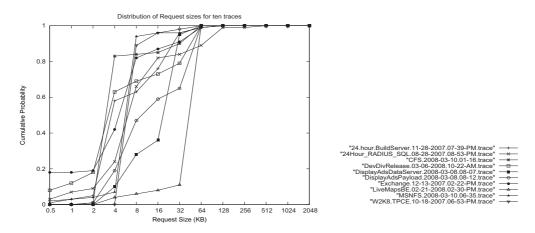

Figure 3.2 shows the distribution of request sizes over ten traces which we randomly downloaded from Storage Network Information Association (SNIA) [2]. CDF curves are used to show percentage of requests whose sizes are less than a certain value. As shown in figure 3.2, most of request sizes are between 4K and 64K, and few request sizes are bigger than 128K. Although only ten traces are analyzed, we can see that small size request is much more popular than big size request.

Random accesses are small and popular, which have high temporal locality. As shown in Table 1.1, page-level buffer management exhibits better buffer space

Figure 3.2: Distribution of request sizes for ten traces from SNIA [2]

utilization and it is good at exploiting temporal locality to achieve high buffer hit ratio. Sequential accesses are large and unpopular, which have high spatial locality. The block-level buffer management scheme can effectively make use of spatial locality to form a logical erasable block in the buffer, and meanwhile good block sequentiality can be maintained in this way.

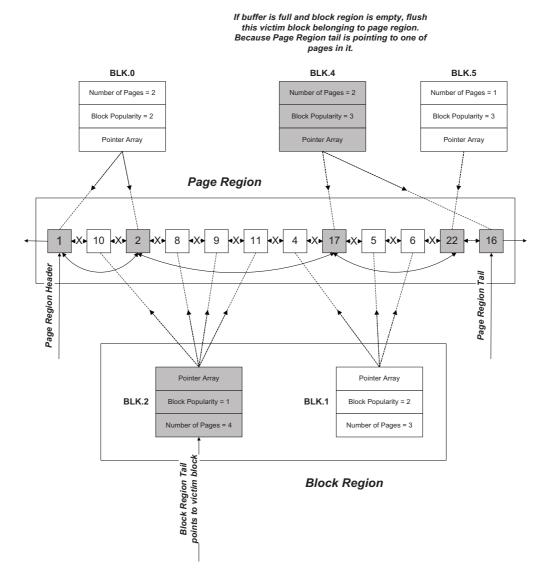

Enterprise workloads are a mixture of random and sequential accesses. Only page-level or only block-level buffer management is not enough to fully utilize both temporal and spatial localities among enterprise workloads. So it is reasonable for us to make use of hybrid management, which divides the buffer into page region and block region, as shown in the figure 3.3. These two regions are managed separately. Specifically, in the page region, buffer data is managed at single page granularity to improve buffer space utilization. Block region operates at the logical block granularity that has the same size as the erasable block size in the NAND flash memory. One unit in the block region usually includes two pages at least. However, this minimum value can be adjusted statically or dynamically, which will be explained in the section 3.6.

Page data is either in page region or in block region. Both regions serve incoming requests. It is worthy to note that many existing buffer management algorithms can be used to manage pages in page region such as LRU, LFU. LRU is the most common buffer management algorithm in operating systems.

Block Region

**Figure 3.3:** Hybrid Buffer Management. Buffer space is divided into two regions, page region and block region. In the page region, buffer data is managed and sorted in page granularity, while block region manages data in block granularity. Page can be placed in either of two regions. Block in block region is selected as victim for replacement.

Due to its efficiency and simplicity, pages in page region are organized as pagelevel LRU list. When a page buffered in the page region is accessed (read or write), only this page is placed at the most recent used end of the page LRU list. As for block region, we design a specific buffer management algorithm called LAR which will be described in the section 3.3.

Therefore, the temporal locality among the random accesses and spatial locality among sequential accesses can be fully exploited by page-level buffer management and block-level buffer management respectively.

#### **3.2** A Buffer for Both Read and Write Operations

As for flash memory, the temporal locality and spatial locality can be understood as *block-level temporal locality*: the pages in the same logical block are likely to be accessed (read/write) again in the near future. In the real application, read and write accesses are mixed and exhibit the block-level temporal locality. In this case, separately servicing the read and write accesses in different buffer space may destroy the original locality present among access sequences. Some existing buffer managements for flash storage such as BPLRU and LB-CLOCK only allocate memory for write requests. Although it creates more space for write requests than the buffer which serves both read and write operations, however, it may suffer from more extra overhead due to the read miss. As [12] claims, servicing foreground read operations is helpful for the shared channel which sometime has overload caused by both read and write operations. Moreover, the saved channel's bandwidth can be used to conduct background garbage collection task, which helps to reduce the influences of each other. In addition, read operations are very common in some read intensive applications such as digital picture reader, so it is reasonable for buffer to serve not only write requests but also read operations.

Taking BPLRU as an example, as described in section 2.4.2, it is designed only for writing buffer. In other words, BPLRU exploits the block-level temporal locality only among write accesses, and especially full blocks are constructed only through writes accesses. So in this case, there is not much possibility for BPLRU to form full blocks when read misses happen. BPLRU uses page padding technique to improve block sequentiality of flushed data at a cost of additional reads, which in turn impacts the overall performance. For random dominant workload, BPLRU needs to read a large number of additional pages, which can be seen in our experiment later. Unlike BPLRU, we leverage the block-level temporal locality not only among write accesses but also read accesses to naturally form sequential block and avoid large numbers of extra read operations. HBM treats read and write as a whole to make full use of locality of accesses, meanwhile, HBM groups both dirty and clean pages belonging to the same erasable block into a logical block in the block region. How to read or write data will be presented in detail in section 3.3.

### 3.3 Locality-Aware Replacement Policy

This thesis views negative impacts of random writes on performance as penalty. The cost of sequential write is much lower than that of random write. Popular data will be frequently updated. When replacement happens, unpopular data should be replaced instead of popular data. Keeping popular data in buffer as long as possible can minimize the penalty. For this purpose, we give preference to random access pages for staying in the page region, while sequential access pages in block region are replaced first. What's more, the sequentiality of flushed block is beneficial to garbage collection of flash memory.

*Block popularity* - small sized file is accessed frequently and big sized file is not accessed frequently. In order to make good use of the access frequency in block region, block popularity is introduced, which is defined as block access frequency including reading and writing of any pages of the block. Specifically, when a logical page of a block is accessed (including read miss), we increase the block popularity by one. Sequentially accessing multiple pages of a block is treated as one block access instead of multiple accesses. Thus, block with sequential accesses will have low popularity value. One advantage of using block popularity is that full blocks formed due to accessing big size file usually have low popularity. Full blocks will be probably flushed into flash memory when replacement is necessary, which is beneficial to reduce garbage collection overhead of flash memory.

A locality aware replacement policy called LAR is designed for block region. The functions of LAR in form of pseudo code are shown in Algorithm 3.1, 3.2 and 3.3, which consider the case that the request size is only one page data. For requests which include more than two pages, several small sized requests, each of which only includes the pages belonging to a single block, will be processed after breaking up the original big request. For one request, sequentially accessing multiple pages of a block is treated as one block access, thus, the block popularity will be only increased by one.

*How to read and write* - when requested data is in the page region, re-arrange the LRU list of page region. Because LAR is designed for block region, here all

the operations below happen in the block region.

| Algorithm 3.1: Read Operation For LAR |                                                           |  |  |  |  |  |

|---------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| D                                     | Data: LBN(logical block number), LPN(logical page number) |  |  |  |  |  |

| 1 <b>if</b>                           | 1 if found then                                           |  |  |  |  |  |

| 2                                     | Read page data in the buffer;                             |  |  |  |  |  |

| 3 e                                   | nd                                                        |  |  |  |  |  |

| 4 e                                   | lse                                                       |  |  |  |  |  |

| 5                                     | Read page data from flash memory;                         |  |  |  |  |  |

| 6                                     | if not enough free space then                             |  |  |  |  |  |

| 7                                     | Replace();/* refer to Algorithm 3.3 */                    |  |  |  |  |  |

| 8                                     | end                                                       |  |  |  |  |  |

| 9                                     | if LBN is not found then                                  |  |  |  |  |  |

| 10                                    | Allocate a new block;                                     |  |  |  |  |  |

| 11                                    | Write page data in the buffer;                            |  |  |  |  |  |

| 12                                    | Block popularity $= 1;$                                   |  |  |  |  |  |

| 13                                    | Page state for $LPN = clean$ ;                            |  |  |  |  |  |

| 14                                    | Number of pages $= 1;$                                    |  |  |  |  |  |

| 15                                    | end                                                       |  |  |  |  |  |

| 16                                    | if LBN is found but LPN is not found then                 |  |  |  |  |  |

| 17                                    | Write page data in the buffer;                            |  |  |  |  |  |

| 18                                    | Block popularity ++;                                      |  |  |  |  |  |

| 19                                    | Page state for $LPN = clean$ ;                            |  |  |  |  |  |

| 20                                    | Number of pages ++;                                       |  |  |  |  |  |

| 21                                    | end                                                       |  |  |  |  |  |

| 22                                    | Re-arrange the LAR list;                                  |  |  |  |  |  |

| 23 e                                  | 23 end                                                    |  |  |  |  |  |

For read requests, if the read request is hit, read data directly (Alog 3.1, lines 1-3), and re-arrange the block region based on LAR (Alog 3.1, line 22). Here, we simply suppose that block region is managed in LAR list, the specific data structure managing block region will be presented in section 3.6. Otherwise, HBM would then fetch data from flash memory and a copy of the data will be placed in the buffer as reference for future requests (Alog 3.1, line 5). At this time, if buffer is full, replacement operation is triggered to produce more space (Alog 3.1, lines 6-8). When there is enough space to hold new data, put it in the buffer. Then two cases should be considered. If the logical block which new page belongs to has been already in the buffer, we update the corresponding information of this logical block (Alog 3.1, lines 16-21); otherwise, we should

allocate a new logical block first (Alog 3.1, lines 9-15). Finally, re-arrange the

LAR list (Alog 3.1, line 22).

| Algorithm 3.2: Write Operation For LAR                              |  |  |  |  |  |

|---------------------------------------------------------------------|--|--|--|--|--|

| Data: LBN(logical block number), LPN(logical page number), PageData |  |  |  |  |  |

| 1 if found then                                                     |  |  |  |  |  |

| 2 Update the corresponding page in the buffer;                      |  |  |  |  |  |

| 3 Block popularity++;                                               |  |  |  |  |  |

| 4 Page state for LPN = dirty;                                       |  |  |  |  |  |

| 5 end                                                               |  |  |  |  |  |

| 6 else                                                              |  |  |  |  |  |

| 7 <b>if</b> not enough free space <b>then</b>                       |  |  |  |  |  |

| 8   Replace();   /* refer to Algorithm 3.3 */                       |  |  |  |  |  |

| 9 end                                                               |  |  |  |  |  |

| 10 <b>if</b> LBN is not found <b>then</b>                           |  |  |  |  |  |

| 11 Allocate a new block;                                            |  |  |  |  |  |

| 12 Write page data in the buffer;                                   |  |  |  |  |  |

| 13 Block popularity = 1;                                            |  |  |  |  |  |

| 14 Page state for LPN = dirty;                                      |  |  |  |  |  |

| Number of pages $= 1;$                                              |  |  |  |  |  |

| 16 end                                                              |  |  |  |  |  |

| 17 <b>if</b> LBN is found but LPN is not found <b>then</b>          |  |  |  |  |  |

| 18 Write page data in the buffer;                                   |  |  |  |  |  |

| 19 Block popularity ++;                                             |  |  |  |  |  |

| 20 Page state for LPN = dirty;                                      |  |  |  |  |  |

| 21 Number of pages ++;                                              |  |  |  |  |  |

| 22 end                                                              |  |  |  |  |  |

| 23 Re-arrange the LAR list;                                         |  |  |  |  |  |

| 24 end                                                              |  |  |  |  |  |

For write requests, if the write request is hit, modify the old data, update the corresponding information of the logical block which requested page belongs to and re-arrange the LAR list; otherwise, the operations are similar to the ones for read requests, except that page state should be set dirty (Alog 3.2, line 4, 14 and 20).

*Victim block selection* - every page in the buffer keeps a state value for itself: *clean* and *dirty*. Modified page will be dirty, and page read from flash memory due to read miss will be clean. When there is not enough space in the buffer, the least popular block indicated by block popularity in the block region is selected as victim (Alog 3.3, line 1). If more than one block has the same least popularity,

#### Algorithm 3.3: Replacement For LAR

| 1 Find the victim block which has the smallest block popularity;        |

|-------------------------------------------------------------------------|

| 2 if not only one victim block then                                     |

| 3 Block of them, which has the largest number of pages, will be chosen; |

| 4 <b>if</b> Still not only one victim block <b>then</b>                 |

| 5 randomly pick one from them;                                          |

| 6 end                                                                   |

| 7 end                                                                   |

| s if there are dirty pages in victim block then                         |

| 9 Both dirty pages and clean pages in victim block are sequentially     |

| flushed;                                                                |

| 10 end                                                                  |

| 11 else                                                                 |

| 12 All the pages in victim block will be discarded;                     |

| 13 end                                                                  |

| 14 Re-arrange the LAR list;                                             |

a block having the largest number of buffered pages is further selected as a victim (Alog 3.3, line 3). After this selection, if there is still more than one block, the final victim block will be further chosen randomly from them (Alog 3.3, lines 4-6).

*Selection compensation* - only if block region is empty, we select the least recently used page as victim from page region. The pages belonging to the same block as this victim page will be also flushed sequentially. This policy tries to avoid flushing single page, which has high negative impact on garbage collection and internal fragmentation.

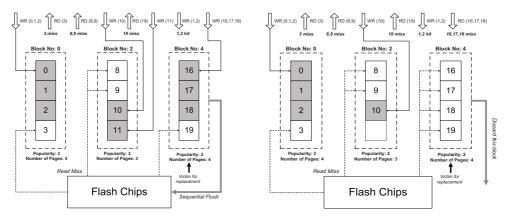

*How to flush the victim block -* once a block is selected as victim, there are two cases to deal with: (1) If there are dirty pages in this block, both dirty pages and clean pages of this block are sequentially flushed into flash memory (Alog 3.3, lines 8-10). This policy guarantees that logically continuous pages can be physically placed onto continuous pages, so as to avoid internal fragmentation and keep the sequentiality of flushed pages. By contrast, FAB flushes only dirty pages in the victim block and discards all the clean pages without considering the sequentiality of flushed data. (2) If there are no dirty pages in the block, all

(a) The victim block which has the smallest (b) The victim block is further chosen by block popularity is sequentially flushed number of pages, and discarded due to no dirty pages

Figure 3.4: Working of LAR algorithm

the clean pages of this block will be discarded (Alog 3.3, lines 11-13).

Figure 3.4 illustrates working of our LAR. In figure 3.4(a), upon write request WR(0,1,2) is coming, because they belong to block 0 and block 0 is not in the buffer, a new block 0 should be allocated first, and pages of 0, 1 and 2 are written in the buffer. Therefore, the popularity of block 0 is 1 and number of pages is 3. As read request RD(3) is coming, one missed page is read from flash chips and stored in the block 0, whose popularity is then increased by 1 and number of pages is updated as 4. Similarly, pages of 8 and 9 form block 2 with popularity 1. As write request WR(10) is coming, both popularity and number of pages in block 2 are increased by 1. Read request RD(19) initially forms block 4, whose popularity is 1 and number of pages is 1.Write request WR(11) increases the popularity and number of pages of block 2 by 1, respectively. Two page hits happen when write request WR(1,2) is coming, which updates the popularity of block 0 as 3. Finally, write request WR(16, 17, 18) updates the popularity and number of pages of block 4 as 2 and 4, respectively. Of three blocks in the buffer, block 4 is regarded as victim block due to its least popularity, and it will be sequentially flushed into flash chips.

Due to the different request sequence from figure 3.4(a), the final state of buffer in figure 3.4(b) is different. Specifically, the popularity, number of pages of block and page states are different. When replacement happens, block 4 is still victim block although its popularity is equal to the one of block 2, because its number of pages is bigger than block 2. Then block 4 will be discarded since all the pages in block 4 are clean.

After LAR is used, more sequential requests are passed to the flash chips, while most random requests are filtered. Requests which show spatial stronger locality can be processed efficiently.

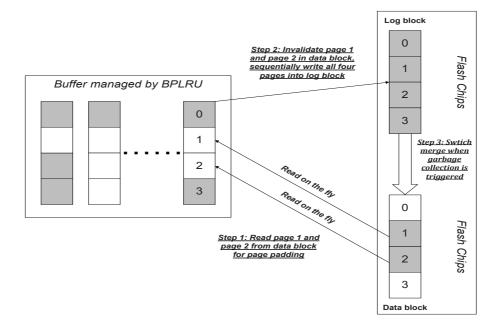

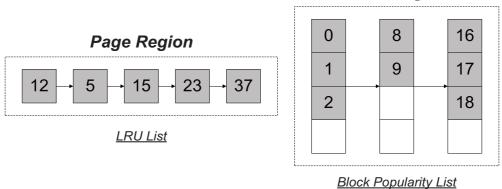

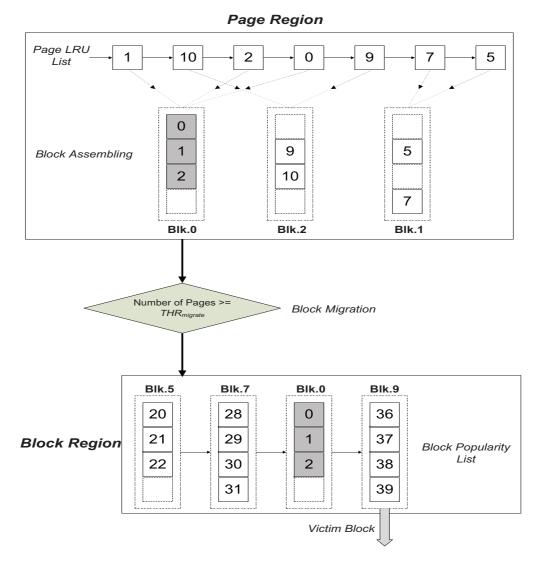

#### **3.4 Threshold-based Migration**

A threshold which is the minimum number of pages included in each block in block region can be set statically or dynamically. Whichever policy is applied, buffer data in page region will be migrated to block region if the number of pages in a block reaches the threshold, as shown in figure 3.5. How to determine the threshold value will be discussed in section 3.6. For instance, in figure 3.5, suppose that the threshold is 3, page 0, page 1 and page 2 which belong to block 0 are all in the page region at the same time. According to threshold-based migration, these three pages should be constructed to block 0 and migrated into the block region. Block region is updated then.

The blocks in the block regions are formed in the two ways: one the one hand, when a large sized request involving many continuous pages is issued, the block may be constructed directly. On the other hand, it could be constructed due to many small sized requests involving pages belonging to the same block as block 0 in figure 3.5. Therefore, with filter effect of the threshold, random pages due to small size requests will stay in the page region, while the selected blocks as block 0 in figure 3.5 reside in the block region. Temporal locality among random pages and spatial locality among sequential blocks can be fully utilized in the hybrid buffer management.

**Figure 3.5:** Threshold-based Migration.  $THR_{migration}$  is a threshold which denotes the minimum number of pages for a block in block region. Buffer data in page region will be migrated to block region only if the number of pages in a block reaches  $THR_{migration}$ . Grey boxe (Blk.0) denotes that a block is found and migrated to block region. An erase block consists of 4 pages.

## **3.5 Implementation Details**

Suppose page region and block region are managed by LRU and LAR list respectively, finding an associated page in buffer is not efficient, and we must traverse two lists every time searching pages are necessary. So CPU power should be cared when we design HBM to search one particular page quickly. In addition, how to implement threshold-based data migration should be also efficiently designed. Meanwhile, limited memory space should be achieved due to the precious memory size inside SSD.

#### **3.5.1 Using B+ Tree Data Structure**

B+ tree [1] is primarily used in data storage and it is used for quickly data search requirement. For example, in file systems, some of which use B+ tree for metadata indexing. Unlike binary search tree, a high fan out value helps B+ tree to shorten the path length to search an element in the tree. In some relational database management systems such as IBM DB2 [1], B+ tree is supported for table indices.

We adopt B+ tree indexing to manage data for two reasons: one is its efficient retrieval for a particular page; the other is that the memory size for B+ tree is limited, which will be analyzed in section 3.5.3.

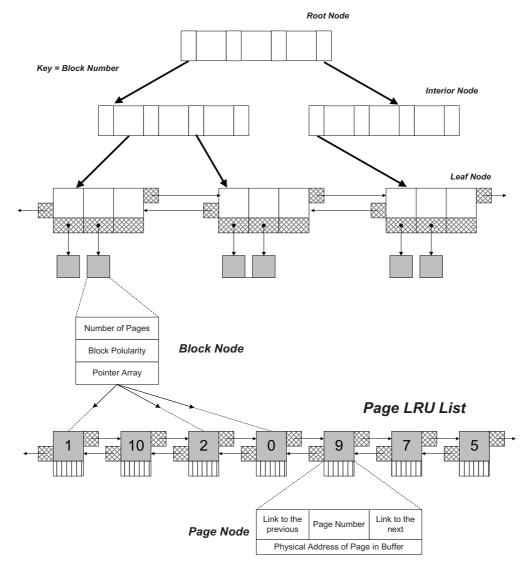

Figure 3.6 shows B+ tree indexing to manage data for HBM. Two basic data structures should be present first: *block node* and *page node*. Block node describes a block in terms of block popularity, number of pages in the block including clean and dirty pages, and pointer array which points to the page nodes; Page node describes a page in terms of page number, two link pointers for LRU, and physical address of page data. B+ tree index is built over the block nodes. It uses block number as key to assemble the pages that belong to the same block. The leaf node of B+ tree has pointers to corresponding block nodes.

Figure 3.6: B+ tree to manage data for HBM

### 3.5.2 Implementation for Page Region and Block Region

Figure 3.7 shows the implementation for page region and block region of HBM.

Figure 3.7: Data management in page region and block region

*Forming block region -* initially, all the page nodes in the buffer are included in page region, meaning that they are all linked by pointers for LRU. A page region header indicates the most recent used end of LRU list, pointing to the first page node in page region. Meanwhile, a page region tail indicates the least recent used end of LRU list, pointing the last page node in page region. Upon arrival of an access in the page region, we deal with it in following way. After dividing the page number by the number of pages per block, we first get the block number.

Then we search the B+ tree using the block number to find the corresponding block node. If the block node exists, we update the block node including block popularity, number of pages and pointer (if page does not exist, add a new page node into LRU list, and a pointer corresponding to new page node is added into block node). If the block node does not exist, we add a new page node and a corresponding block node, and then update the LRU list. If the number of pages in the block is below the threshold, update the LRU list; otherwise, all the pages in the block will be migrated to block region. Specifically, we extract these pages from LRU list in the page region by modifying the related links for LRU of page nodes, and then the two links for LRU of extracted page nodes are set NULL, for example, marker "X" in figure denotes that there are not any links between two page nodes. In other words, how to determine whether a page node belongs to page region or block region depends on the links for LRU of it. If the link is NULL, the page node is in block region; otherwise, it is in page region. The reason why we manage page region and block region in this way is that we do not have to really manage a LAR list (the replacement policy in block region is LAR) in block region. All we need is quickly finding the victim block when replacement has to happen.

*Selecting the victim block* - the victim block should has the smallest block popularity, such as BLK.2 in figure 3.7. If there is more than one block like this, the one that has the least number of pages will be chosen. So there is a pointer called block region tail which points to the current victim block.

When one block node is just migrated into block region, we compare this block node with the victim to see whether this block can replace the current victim block, and update the block region tail pointer if necessary. When the victim block is updated, we need to traverse all the block nodes by leaf nodes of B+ tree to determine whether we need to change the victim block. Because updating the victim block seldom happens, the cost of traversing all the block nodes is limited. *What to do when block region is empty* - that the pointer of block region tail is NULL means that the block region is empty. In this condition, if we have to replace pages from page region for free space, the page which the page region tail points to will be chosen, and besides this page, other pages that belongs to the same block as this page will also be chosen. In other words, we first find the victim page by page region tail, then search the block node that belongs to, e.g., BLK.4 in figure 3.7, and sequentially flush all the current pages indicated in the block node from low page number to high page number.

#### 3.5.3 Space Overhead Analysis

By using B+ tree indexing, the pages belonging to the same block can be quickly searched and located. Meanwhile, the space overhead of B+ tree and the block node is limited. As shown in figure 3.6, B+ tree generally includes two parts: leaf nodes and interior nodes (including root node). In order to analyze the space overhead, we first make following assumptions:

- 1. Integer or pointer type consumes 4 bytes;

- 2. B+ tree uses a "fill factor" to control the growth and shrinkage. A 50% fill factor [32] would be the minimum for any B+ tree. In other words, at least half of child pointers are valid. The typical fill factor is 67% in practice [32], however we set it to be 50% for convenience of analysis. In addition, as fill factor increases, the number of interior nodes will decrease. In order to analyze the worse case, the minimum fill factor 50% should be set. In this case, the leaf node will also remain at least half-full;

- Suppose the ratio of number of interior nodes to number of leaf nodes is r, 0<r<1. In practice, the number of interior nodes is much smaller than leaf nodes. B+ tree is height balanced and the fan out of B+ tree is 133 on average [32]. In this condition, because the fill factor is at least 50%</li>