### LANTHANOID BASED MATERIALS IN ADVANCED

### **CMOS TECHNOLOGY**

**CHEN JINGDE**

NATIONAL UNIVERSITY OF SINGAPORE

2009

# LANTHANOID BASED MATERIALS IN ADVANCED CMOS TECHNOLOGY

**CHEN JINGDE**

**B.** Eng., National University of Singapore, 2003

A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### DEPARTMENT OF ELECTRICAL AND COMPUTER

#### ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2009

#### ACKNOWLEDGMENTS

First and foremost, I would like express my utmost gratitude to my research advisor, Dr. Yeo Yee-Chia, who has guided me through the most difficult period in my research life, provided me with invaluable support, guidance, encouragement, knowledge, and the awesome research opportunities during my studies. It is difficult to imagine how little I could have done if Dr. Yeo had not encourage me to attempt on those ideas seemingly beyond reach. He demonstrated to me how a researcher should be confident in his study; how the confidence comes from the pursue of every detail and continual cross-checking; and how one should be open-minded and actively seek criticism. He has my tremendous appreciation and respect.

I am extremely grateful to my supervisor during the first three years, Prof. Li Ming-Fu for bringing me to the research area of silicon processing technology. He has always been there to give insights into my research work and I have greatly benefited from his guidance. I would also like to take this chance to express my sincere appreciation to Dr. Yu Ming-Bin, for his kindly help and invaluable advices. There have been lots of collaboration work and fruitful discussions that contribute to my thesis development.

I would like to thank Dr. Yu Hong-Yu who was my mentor at the beginning of my research work. Many of research plans in the initial year were under his steering. We also had fruitful collaborations after he joined IMEC. In addition, I am grateful to Dr. Zhu Shi-Yang for his guidance in the Schottky source/drain transistor project. My special thanks go to my colleague, Yang Jianjun, who worked together with me in several projects. We both benefited from those brain storms or even arguments. It is such a pleasure working with you.

The experimental work was carried out in the silicon nano device lab at the National University of Singapore. I received a lot of technical and logistic support from the managers and technicians there. I would like to thank Prof. Byung-Jin Cho and Prof. Ganesh Samudra for their tremendous contribution in establishing and maintaining SNDL in both its facilities and traditions. Mr. Yong Yu-Fu, Mr. Patrick Tang, Mr. O Yan Wai Linn and Mr. Sun Zhi-Qiang are gratefully acknowledged for their support.

I have had the pleasure of collaborating with numerous exceptionally talented graduate students over the last few years. There have been general technical discussions on a large variety of topics every day in SNDL. This culture of open discussion has been very memorable experience. I believe it is to a certain extent a unique character of SNDL. It is impossible to enumerate all, but I cannot fail to mention Shen Chen, Qing Chun, Wu Nan, Xiong Fei, Ren Chi, Gao Fei, Ying Qian, Li Rui, Pu Jing, Rui Long, Li Tao, Zhou Qian, Yang Yue and Gen Quan for the numerous discussions over lunch, or while idling in the clean room. I have benefited the collaboration work with them, and their friendship makes my stay in NUS more enjoyable. I also would like to extend my appreciation to all other SNDL teaching staff, fellow graduate students, and technical staff.

My deepest gratitude goes out to my mum and my brother, who have always been supportive of my academic endeavours. I can never forget their inspiration and encouragement during my education years in spite of the enormous physical distance between us, their constant love and support made the long hours and frustrations bearable.

Chen Jingde

Singapore, Sept. 2009

## **TABLE OF CONTENTS**

| Acknowledgements  | i    |

|-------------------|------|

| Table of Contents | iv   |

| Abstract          | viii |

| List of Tables    | x    |

| List of Figures   | xi   |

| List of Symbols   | xxii |

Page No.

#### **Chapter 1** Introduction

| 1.1 | Lanthanoid Elements and Their Compounds |                                       | 2  |

|-----|-----------------------------------------|---------------------------------------|----|

|     | 1.1.1                                   | The Lanthanoid Series                 | 2  |

|     | 1.1.2                                   | Lanthanoid Silicides                  | 3  |

|     | 1.1.3                                   | Lanthanoid Oxides                     | 5  |

| 1.2 | 1.2 Integrated Circuit Scaling          |                                       |    |

|     | 1.2.1                                   | Transistor Scaling                    | 7  |

|     | 1.2.2                                   | Scaling of Integrated Passive Devices | 13 |

| 1.3 | Objec                                   | ctive of Research                     | 16 |

| 1.4 | Thesi                                   | s Organization                        | 16 |

| Ref | erence                                  | s                                     | 18 |

### Chapter 2 Schottky Barrier Source/Drain Field-Effect Transistor

| 2.1 | 2.1 Background and Theories |                                                            |    |  |

|-----|-----------------------------|------------------------------------------------------------|----|--|

|     | 2.1.1                       | Motivation for Schottky Barrier Source/Drain Transistors . | 26 |  |

|     | 2.1.2  | Schottky Barrier and Metal Work Function28   |

|-----|--------|----------------------------------------------|

|     | 2.1.3  | Schottky Barrier Extraction                  |

|     | 2.1.4  | SSDT Structure and Principles of Operation31 |

| 2.2 | Proce  | ess Development                              |

|     | 2.2.1  | Overview                                     |

|     | 2.2.2  | Integration Issues                           |

|     | 2.2.3  | SSDT device Fabrication                      |

| 2.3 | Devie  | ce Characterization and Analysis43           |

|     | 2.3.1  | Schottky Diode Characterization43            |

|     | 2.3.2  | Transistor Characterization                  |

| 2.4 | Conc   | lusion54                                     |

| Ref | erence | s56                                          |

### Chapter 3 Yb Doped Ni FUSI for the N-MOSFETs Gate Electrode Application

| 3.1 | Intro                                    | duction                                                | 60 |

|-----|------------------------------------------|--------------------------------------------------------|----|

| 3.2 | Proce                                    | Process Development                                    |    |

|     | 3.2.1                                    | Process Flow for MOS Capacitors                        | 62 |

|     | 3.2.2                                    | Thickness Ratio Control and Sputter Sequence for Yb/Ni | 63 |

|     | 3.2.3                                    | Silicidation Process Optimization                      | 65 |

| 3.3 | 3.3 Device Characterization and Analysis |                                                        |    |

|     | 3.3.1                                    | Material Characterization                              | 69 |

|     | 3.3.2                                    | Work Function Tunability                               | 74 |

|     | 3.3.3                                    | Reliability Assessments                                | 79 |

| 3.4 | CMC                                      | S Integration Scheme                                   | 82 |

| 3.5 | Inve                                     | stigation of Work Function Tuning Mechanism            | 84 |

| 3.6 | Con                                      | clusion                                                |    |

| References           | ;                                                                                                     | 89  |

|----------------------|-------------------------------------------------------------------------------------------------------|-----|

| Chapter 4            | NMOS Compatible Work Function of TaN Meta<br>with Erbium Oxide Doped Hafnium Oxide Gate<br>Dielectric |     |

| 4.1 Introd           | luction                                                                                               | 93  |

| 4.2 Exper            | iment                                                                                                 | 94  |

| 4.3 Resul            | ts and Discussion                                                                                     | 95  |

| 4.3.1                | Physical Characterization                                                                             | 95  |

| 4.3.2                | Electrical Characterization                                                                           |     |

| 4.3.3                | Dipole Models for Metal Gate Work Function Tunability                                                 | 105 |

| 4.4 HfO <sub>2</sub> | Incorporated with Other Lanthanoid Elements                                                           | 108 |

| 4.5 Conc             | usion                                                                                                 | 110 |

| Reference            | 5                                                                                                     | 111 |

## Chapter 5 Lanthanoid Oxides for Precision RF/analog MIM Capacitors

| 5.1 Introduction                                                                 | 114 |

|----------------------------------------------------------------------------------|-----|

| 5.2 Device Fabrication and Material Screening                                    | 115 |

| 5.2.1 Device Fabrication                                                         | 115 |

| 5.2.2 Material Screening                                                         | 117 |

| 5.3 MIM Capacitors with a single layer $Sm_2O_3$ dielectric                      | 119 |

| 5.3.1 Physical Characterization                                                  | 119 |

| 5.3.2 Electrical Characterization                                                | 123 |

| 5.4 MIM Capacitors with a single layer Er <sub>2</sub> O <sub>3</sub> dielectric | 126 |

| 5.4.1 Physical Characterization                                                  | 126 |

| 5.4.2 Electrical Characterization                                                | 129 |

| 5.5 Further Reduction of quadratic VCC by stacking with SiO <sub>2</sub>         | 135 |

| 5.5.1 Device Structure and Cancelling Effect                                     | 135 |

|     | 5.5.2   | MIM Capacitors with $Sm_2O_3/SiO_2$ dielectric stack1                                  | 38 |

|-----|---------|----------------------------------------------------------------------------------------|----|

|     | 5.5.3   | MIM Capacitors with Er <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> dielectric stack1 | 43 |

| 5.6 | Summ    | ary1                                                                                   | 52 |

| Ref | erences | 1                                                                                      | 54 |

## Chapter 6 Conclusion and Future Works

| 6.1 | Cor    | nclusion158                                                 |

|-----|--------|-------------------------------------------------------------|

|     | 6.1.1  | Schottky Barrier Source/Drain Field-Effect Transistor158    |

|     | 6.1.2  | Yb Doped Ni FUSI for the N-MOSFETs Gate Electrode           |

|     |        | Application159                                              |

|     | 6.1.3  | NMOS Compatible Work Function of TaN Metal Gate with        |

|     |        | Erbium Oxide Doped Hafnium Oxide Gate Dielectric159         |

|     | 6.1.4  | Lanthanoid Oxides for Precision RF/analog MIM Capacitors160 |

| 6.2 | Sugg   | estions for Future Work160                                  |

| Ref | erence | s163                                                        |

### APPENDIX

| A. | LIST OF PUBLICATIONS |  |

|----|----------------------|--|

| •  |                      |  |

### ABSTRACT

Aggressive complementary metal-oxide-semiconductor (CMOS) scaling requires the development of new materials and device architectures. This dissertation focuses on introducing lanthanoid based materials into CMOS technology to address some of the new challenges in CMOS scaling.

The low work function lanthanoid silicides are potential candidates for N-type Schottky source/drain field-effect transistor (N-SSDT). Several lanthanoid elements, including Dy, Er, Tb and Yb, were investigated to form the self-aligned silicide (salicide) S/D for N-SSDT. The YbSi<sub>2-x</sub> has been found to be a very promising candidate for N-SSDT as it provides a high drive current with a very low leakage current. By addressing the compatibility issues of lanthanoid materials with conventional CMOS process, a low temperature, implantation free MOSFET process featuring a "hole spacer", Schottky barrier source/drain, high- $\kappa$  dielectric and metal gate electrode was successfully developed.

The elimination of polysilicon gate depletion effect and reduction in gate leakage current are major advantages of metal gate/high- $\kappa$  dielectric gate stack over conventional polysilicon/SiO(N) gate stack. However, achieving the desired effective metal gate work function  $\Phi_m$  to meet threshold voltage requirements in future CMOS devices is one of the main hurdles for its implementation. We demonstrate two methods for tuning the metal gate work function towards the silicon conduction band edge. The first one is to incorporate ytterbium (Yb) into Ni fully-silicided (Ni-FUSI) gate. Yb has a low work function of 2.59 eV. During the silicidation process, Yb atoms accumulate at the NiSi/SiO<sub>2</sub> interface and achieved a FUSI gate  $\Phi_m$  lowering of about 0.3 to 0.5 eV. However, this method is less effective on high- $\kappa$  dielectrics. The second method is to incorporate lanthanoid oxides into hafnium oxide gate dielectric. Conduction band-edge TaN gate  $\Phi_m$  values of 4.1 to 4.24 eV were obtained by doping HfO<sub>2</sub> gate dielectric with Er<sub>2</sub>O<sub>3</sub> and several other lanthanoid oxides. Interface dipole models were discussed to explain the effective gate  $\Phi_m$  tunability.

After addressing the challenges active device, we explore the scaling down of metal-insulator-metal (MIM) capacitors by investigating a series of lanthanoid oxides as candidates for the insulator layer. MIM capacitors using  $Sm_2O_3$  or  $Er_2O_3$  dielectric material were found to have better voltage linearity as compared with other high- $\kappa$  materials at the same capacitance density. Satisfactory leakage current and frequency dispersion properties indicate that both oxides are promising. It was found that both oxygen vacancy in the dielectric film and the interfacial layer at the high- $\kappa$ /bottom electrode interface played an important role in the voltage linearity of the MIM stack. An innovative dielectric structure is developed by intentionally inserting a thin SiO<sub>2</sub> layer between the lanthanoid oxide and bottom electrode. We achieved high capacitance density (up to 8.5 fF/ $\mu$ m<sup>2</sup>) with quadratic VCC lower than 100 ppm/V<sup>2</sup> by engineering the thickness ratio of high- $\kappa$  to SiO<sub>2</sub> layers. This performance can meet the International Technology Roadmap for Semiconductors (ITRS) requirements in 2013 and indicates that MIM capacitors with high- $\kappa$ /SiO<sub>2</sub> dielectric stack can be a long-term solution to RF and analog/mixed-signal capacitor technology.

## LIST OF TABLES

| Table 1.1 | List of lanthanoid elements, photoelectric work functions, and ionic radii of the trivalent lanthanoid ions.                                                                                                                                                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2 | Summary of dielectric constant $\kappa$ values of lanthanoid oxides.                                                                                                                                                                                                                        |

| Table 1.3 | Specifications for the scaling of transistors, derived from <i>ITRS</i> 2008.                                                                                                                                                                                                               |

| Table 1.4 | Specifications for the scaling of MIM capacitors, derived from <i>ITRS</i> 2008.                                                                                                                                                                                                            |

| Table 2.1 | Summary of the features, advantages and benefits of the Schottky source/drain transistor technology 2                                                                                                                                                                                       |

| Table 2.2 | Electrical characteristics of various lanthanoid silicide/p-Si<br>(100) contacts formed by solid-state reaction and their<br>corresponding N-SSDT properties                                                                                                                                |

| Table 3.1 | Experimental splits and deposition time for Yb-incorporated<br>Ni FUSI capacitors. There are two options for the deposition<br>sequence of Ni and Yb: (1) Yb first, Ni second; (2) cosputter<br>Yb and Ni followed by Ni only.                                                              |

| Table 4.1 | Summary of all lanthanoid elements incorporated into $HfO_2$<br>for metal gate work function tuning. All elements exhibit low<br>electronegativities. The concentration of each element is<br>derived from XPS measurements. The $\Phi_{m,eff}$ values are<br>extracted from Fig. 4.14 (b). |

| Table 5.1 | Split table for MIM capacitors with $Sm_2O_3$ -on-SiO <sub>2</sub> laminate dielectric, showing the thicknesses of $Sm_2O_3$ and $SiO_2$ used in each split and the capacitance density measured                                                                                            |

| Table 5.2 | Comparison of DC performance of reported binary high-κ<br>MIM capacitors. 15                                                                                                                                                                                                                |

## LIST OF FIGURES

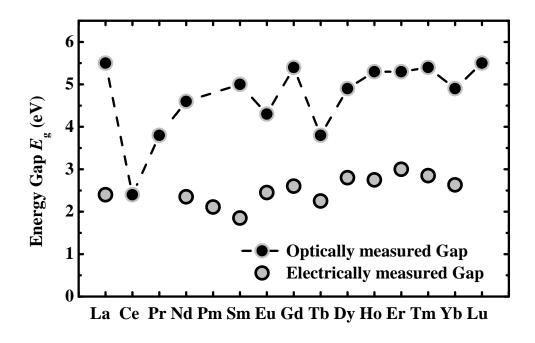

| Fig. 1.1  | Energy gap of Ln <sub>2</sub> O <sub>3</sub> oxides                                                                                                                                                                                              | 7  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

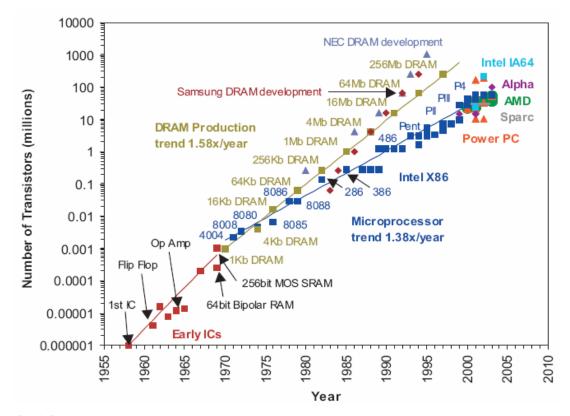

| Fig. 1.2: | The number of transistors on integrated circuits such as microprocessors and DRAM increases exponentially over the years                                                                                                                         | 8  |

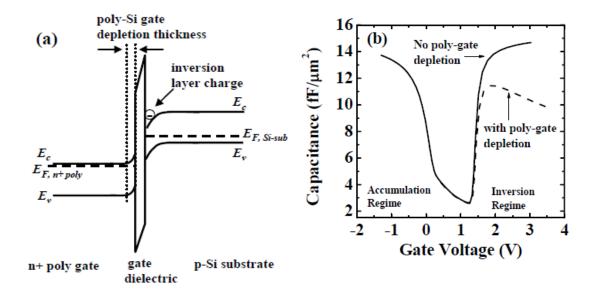

| Fig. 1.3  | (a) The energy band diagram of an NMOSFET showing the poly-Si gate depletion layer during inversion bias. (b) The capacitance-voltage plot depicts how the poly-Si gate depletion effect decreases the gate capacitance in the inversion regime. | 12 |

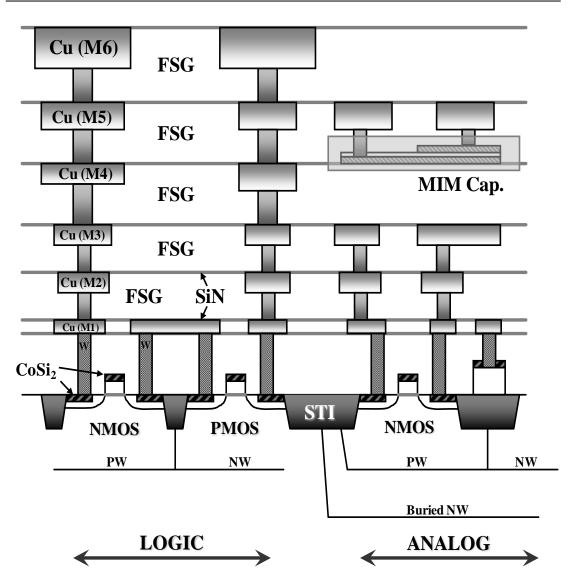

| Fig. 1.4  | Cross sectional view of digital-analog mixed-signal circuit,<br>where MIM capacitor is integrated in the Cu<br>back-end-of-the-line.                                                                                                             | 14 |

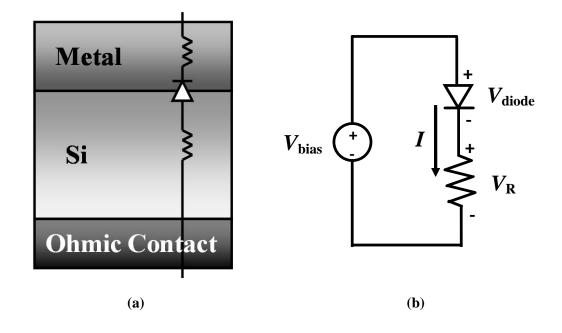

| Fig. 2.1  | (a) Schottky diode structure. (b) Equivalent circuit of Schottky diode. The resistances from the top electrode and bottom Si substrate are considered as one resistor.                                                                           | 30 |

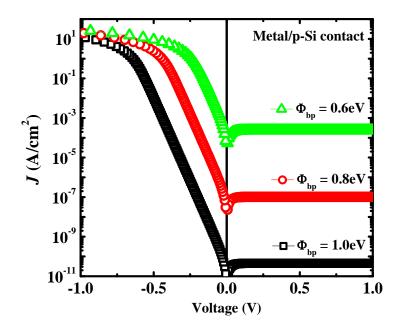

| Fig. 2.2  | Simulated <i>J-V</i> curves of metal/p-Si Schottky contact with an electron barrier of 0.6 eV, 0.8 eV and 1.0 eV. The series resistance is assumed to be 80 $\Omega$ .                                                                           | 30 |

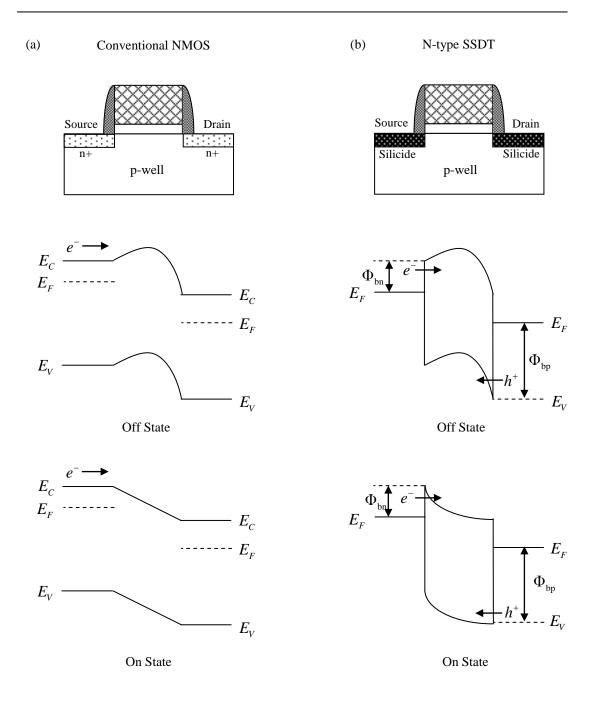

| Fig. 2.3  | Device architecture and band diagrams in off and on states for (a) conventional impurity-doped S/D NMOS device, and (b) SSDT device.                                                                                                             | 32 |

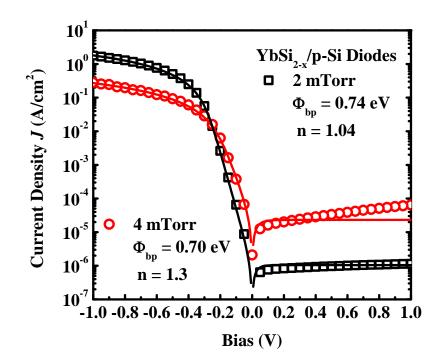

| Fig. 2.4  | <i>I-V</i> curves of YbSi <sub>2-x</sub> /p-Si diodes, with Yb deposited at 2 mTorr and 4 mTorr.                                                                                                                                                 | 37 |

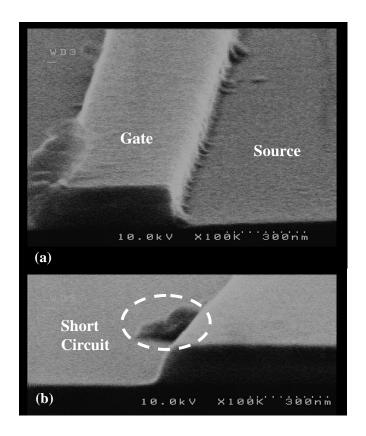

| Fig. 2.5  | (a) Scanning Electron Microscope (SEM) of a transistor with poly-Si/SiO <sub>2</sub> gate, SiO <sub>2</sub> spacer and YbSi <sub>2-x</sub> S/D. (b) SEM image zoomed in to one of the bridges between S/D and gate on the side wall.             | 38 |

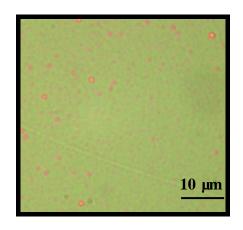

| Fig 2.6   | Optical microscopic image of $SiO_2$ surface after selective etch.<br>Yb was first deposited on the $SiO_2$ , annealed at 350°C for 1 minute, and then removed by selective wet etch by 5% HNO <sub>3</sub>                                      | 39 |

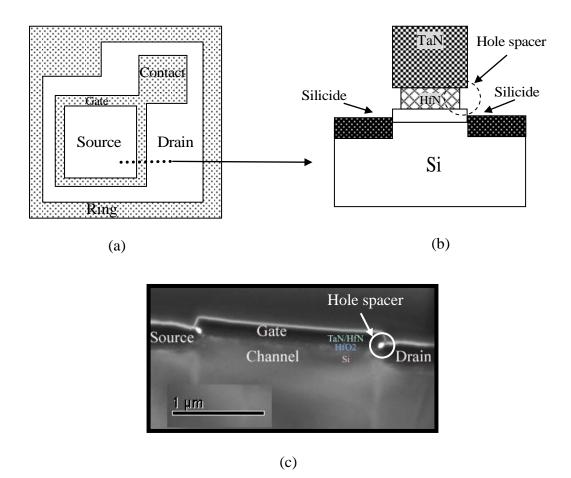

| Fig. 2.7  | <ul> <li>(a) Top view schematic of a one-mask transistor. (b)</li> <li>Cross-section schematic of a one-mask transistor. (c)</li> <li>Cross-section TEM of a SSDT device of 2-μm gate length</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

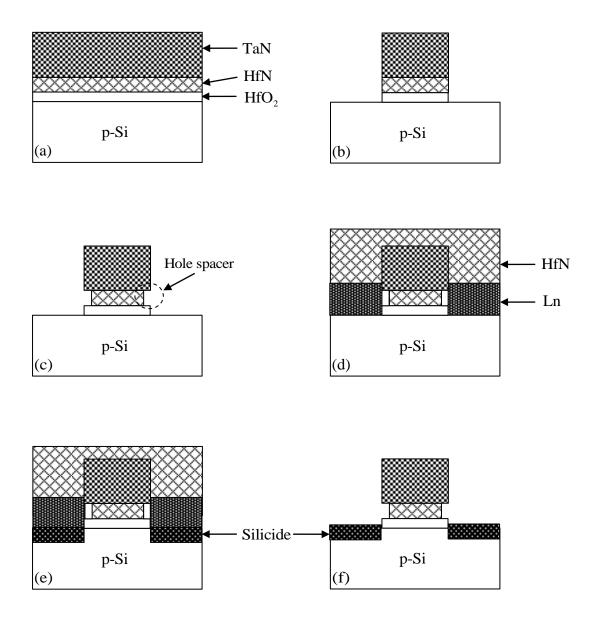

| Fig. 2.8  | Process flow of Schottky source/drain transistors. (a) Deposition<br>of gate stack. (b) Patterning of gate stack. (c) DHF dip to remove<br>the native oxide on source/drain region. A hole is formed on the<br>side wall of HfN. (d) Deposition of lanthanoid metals (Dy, Er,<br>Tb, or Yb), capped by HfN to prevent oxidation during<br>silicidation. (e) Silicidation in RTP. (f) Selective etch of top HfN<br>(by DHF) and un-reacted lanthanoid metal (by diluted HNO <sub>3</sub> );<br>lanthanoid silicide source/drain are intact |

| Fig. 2.9  | Room temperature <i>I-V</i> curves of various LnSi <sub>2-x</sub> /p-Si(100) diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

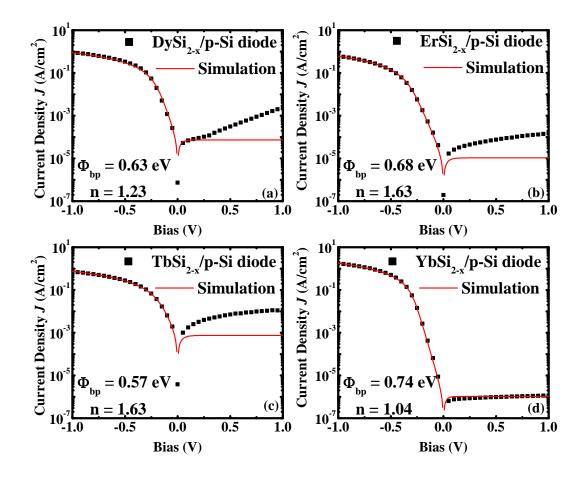

| Fig. 2.10 | Thermal emission model fitting of the <i>I-V</i> curves of Schottky diodes. (a) $DySi_{2-x}/p-Si$ ; (b) Er $Si_{2-x}/p-Si$ ; (c) Tb $Si_{2-x}/p-Si$ ; (d) $YbSi_{2-x}/p-Si$                                                                                                                                                                                                                                                                                                                                                               |

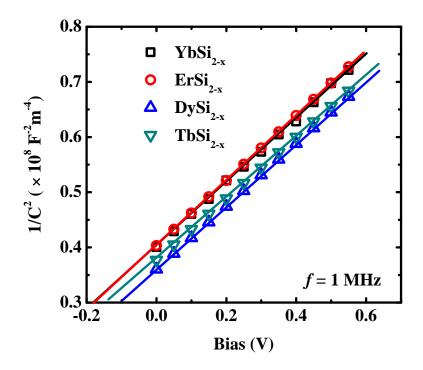

| Fig. 2.11 | Reverse bias $C$ - $V$ curves for LnSi <sub>2-x</sub> /p-Si diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

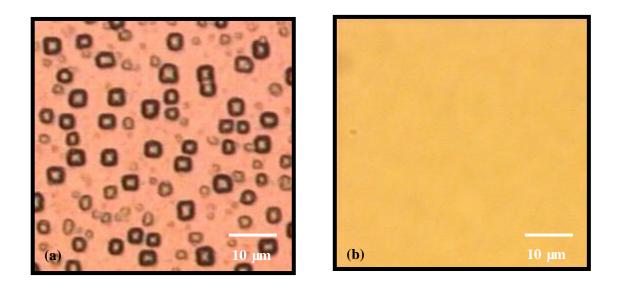

| Fig. 2.12 | Top view of (a) DySi <sub>2-x</sub> and (b) YbSi <sub>2-x</sub> as observed using an optical microscope                                                                                                                                                                                                                                                                                                                                                                                                                                   |

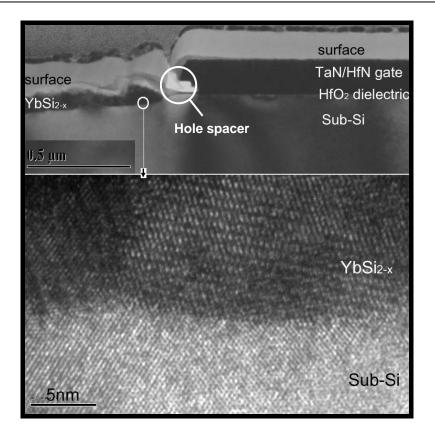

| Fig. 2.13 | <ul> <li>(Top) Cross sectional TEM image of the N-SSDT with YbSi<sub>2-x</sub> source/drain fabricated by our simplified one-mask process.</li> <li>(Bottom) High resolution XTEM image of polycrystalline YbSi<sub>2-x</sub>/Si(100) contact.</li> </ul>                                                                                                                                                                                                                                                                                 |

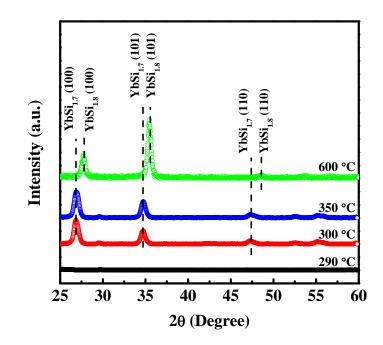

| Fig. 2.14 | X-ray diffraction (XRD) spectra of Yb silicide formed at different annealing conditions. 4                                                                                                                                                                                                                                                                                                                                                                                                                                                |

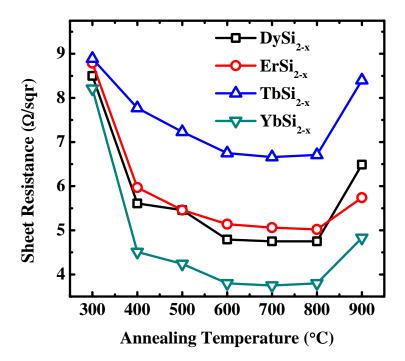

| Fig. 2.15 | Sheet resistance of lanthanoid silicides formed at different annealing conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

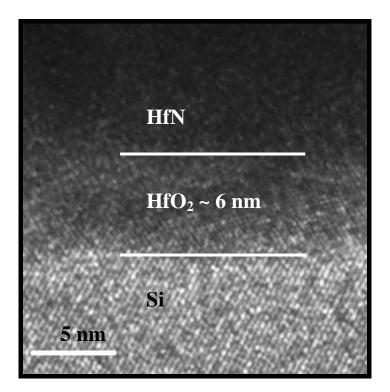

| Fig. 2.16 | High resolution TEM image of the HfN/HfO <sub>2</sub> /p-Si gate stack, with 700 °C post-deposition anneal (PDA) and 420 °C forming gas anneal (FGA).                                                                                                                                                                                                                                                                                                                                                                                     |

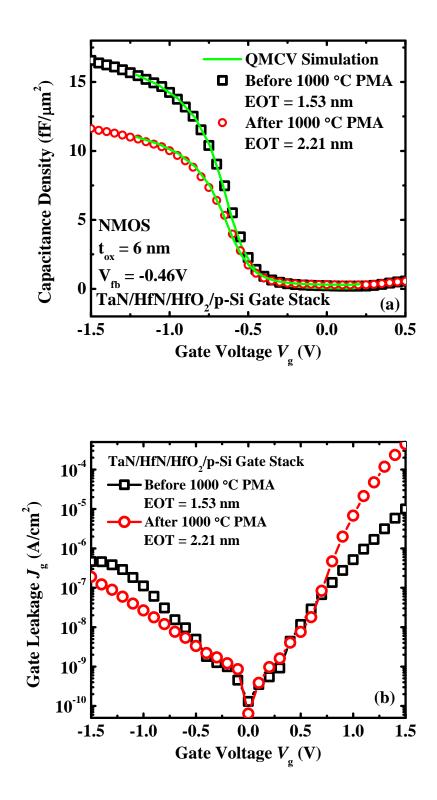

| Fig. 2.17 | (a) <i>C-V</i> and (b) <i>I-V</i> curves of the TaN/HfN/HfO <sub>2</sub> /p-Si gate structure.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

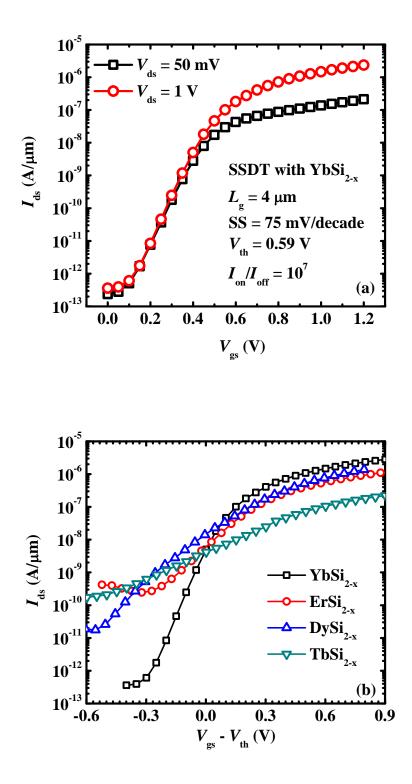

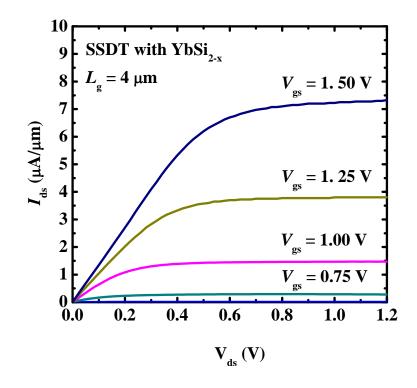

| Fig. 2.18 | (a) $I_{ds} \sim V_{gs}$ characteristics of TaN/HfN/HfO <sub>2</sub> gated n-SSDT with YbSi <sub>2-x</sub> . (b) $I_{ds}$ - $V_{gs}$ characteristics of TaN/HfN/HfO <sub>2</sub> gated n-SSDT with DySi <sub>2-x</sub> , ErSi <sub>2-x</sub> , TbSi <sub>2-x</sub> , YbSi <sub>2-x</sub>              | 2 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Fig. 2.19 | $I_{\rm ds} \sim V_{\rm ds}$ characteristics of TaN/HfN/HfO <sub>2</sub> gated n-SSDT with YbSi <sub>2-x</sub> source/drain. 52                                                                                                                                                                       | 3 |

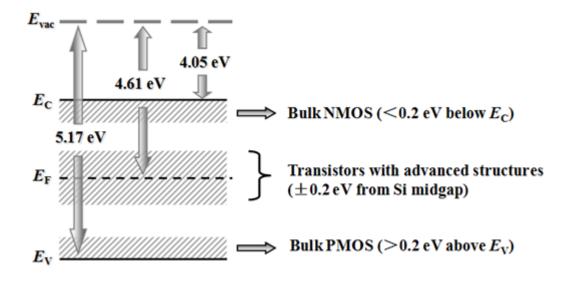

| Fig. 3.1  | Metal gate effective work function $(\Phi_m)$ requirements for both<br>planar bulk transistors and ultra-thin body transistors                                                                                                                                                                        | 2 |

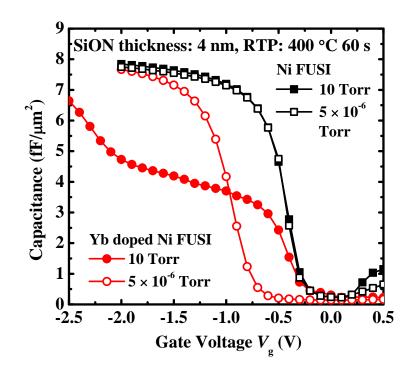

| Fig. 3.2  | The effect of different pressure during the silicidation process.The C-V curve of Yb doped NiSi is distorted for the 10 Torr RTPpressue.60                                                                                                                                                            | 6 |

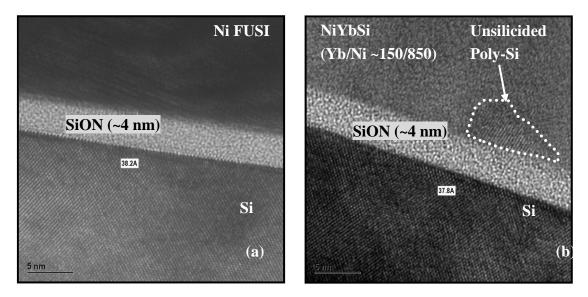

| Fig. 3.3  | High-resolution TEM results of (a) Ni FUSI and (b) NiYb FUSIcapacitors, annealed at a pressure of 10 Torr.60                                                                                                                                                                                          | 6 |

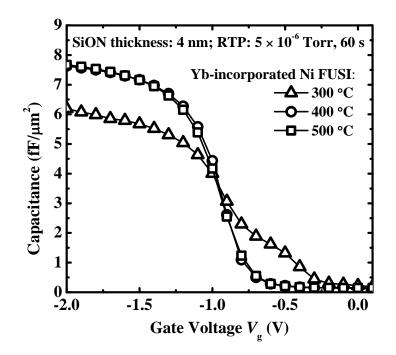

| Fig. 3.4  | The effect of different annealing or silicidation temperature onC-V curves.60                                                                                                                                                                                                                         | 8 |

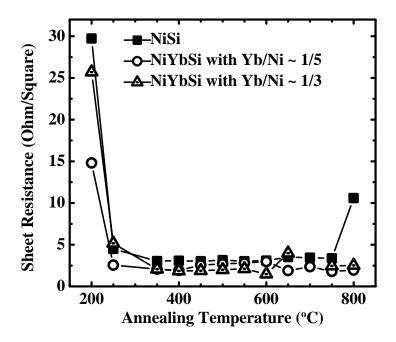

| Fig. 3.5  | Phase transformation curve for NiSi and NiYbSi (with Yb/Ni<br>deposition ratio ~ 1/5 and 1/3 respectively).64                                                                                                                                                                                         | 8 |

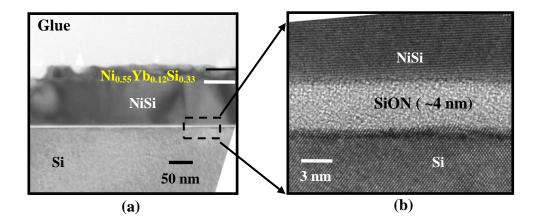

| Fig. 3.6  | XTEM shows that the bulk layer of Yb doped NiSi (Yb/Ni $\sim 1/3$ ) is fully silicided, and the resulting silicide thickness is $\sim 120$ nm.<br>Two different layers in the Yb doped NiSi (corresponding to Figs. 3.2 & 3.3) are observed. A smooth NiYbSi/SiON interface is also revealed by XTEM. | 9 |

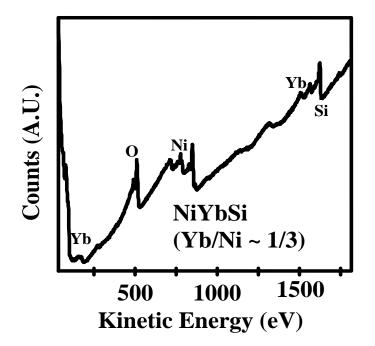

| Fig. 3.7  | Based on AES, composition of the top layer of Yb doped NiSi $(Yb/Ni \sim 1/3)$ is: $Ni_{0.55}Yb_{0.12}Si_{0.33}$                                                                                                                                                                                      | 0 |

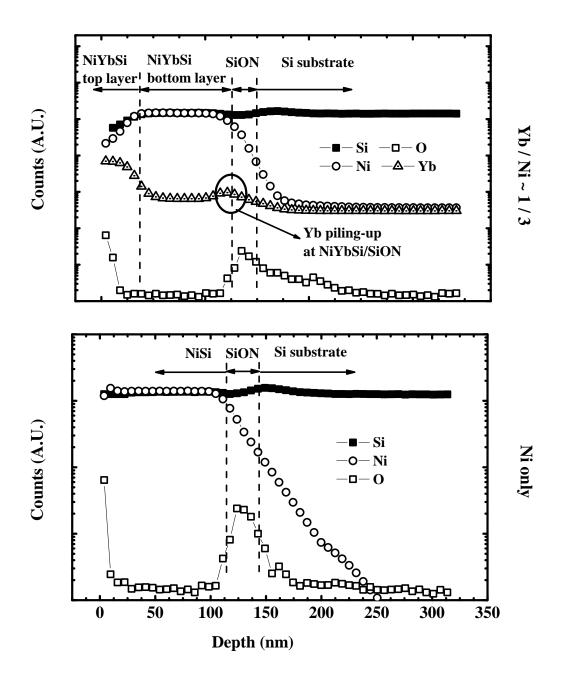

| Fig. 3.8  | SIMS spectra for NiSi and Yb doped NiSi (Yb/Ni $\sim$ 1/3) shows<br>that Yb is mainly distributed at top layer of silicide. Pile-up of<br>Yb at the NiYbSi/SiON interface is also observed                                                                                                            | 1 |

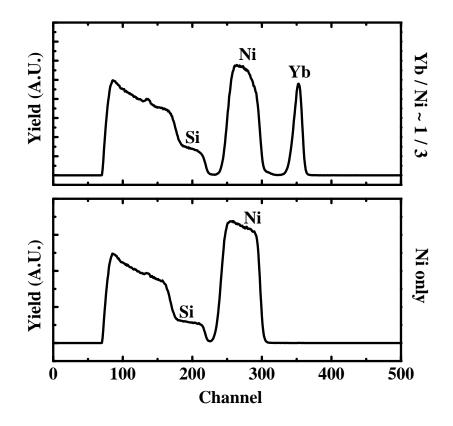

| Fig. 3.9  | RBS spectrum comparison between Yb-incorporated NiSi (Yb/Ni ~1/3) and NiSi. For Yb doped NiSi, Yb is mainly distributed at top layer of silicide. Yb signal is not detected at the bottom layer probably due to its concentration is below the RBS detection limit (<1 at.%).                         | 2 |

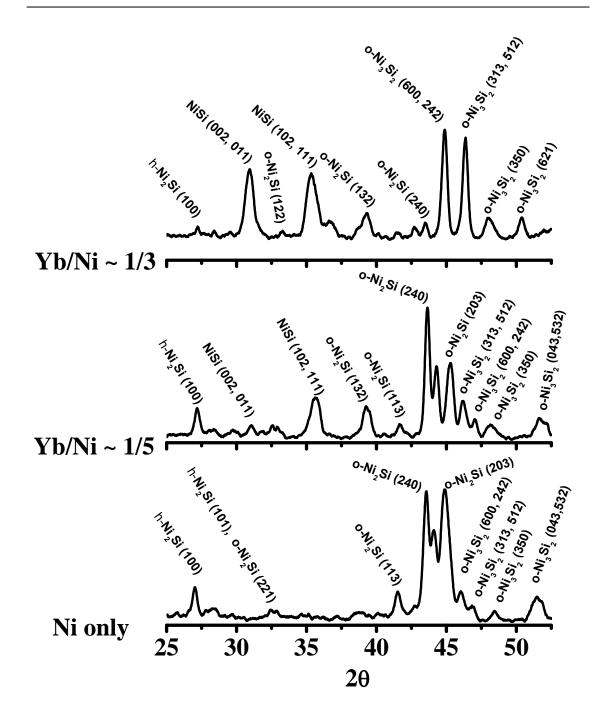

| Fig. 3.10 | XRD study reveal that from the NiSi to NiYbSi (Yb/Ni $\sim$ 1/5 and $\sim$ 1/3 respectively), the phase transits from Ni rich Ni <sub>2</sub> Si to Ni <sub>3</sub> Si <sub>2</sub> and NiSi                                                                                                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

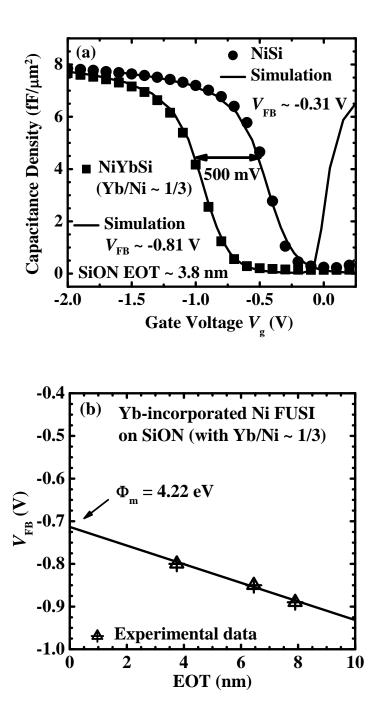

| Fig. 3.11 | (a) Measured and simulated C-V data for capacitors with NiYbSi (Yb/Ni ~1/3) and NiSi gate electrodes. Deposited SiON thickness is ~ 4nm. No change in EOT is observed with addition of Yb. (b) The plot of EOT vs. $V_{\rm FB}$ for the devices with NiYbSi (with Yb/Ni ~ 1/3) gate electrode. The work function extracted is 4.22 eV on SiON, fixed charge $Q_{\rm ox} / q = 4.59 \times 10^{11} {\rm cm}^{-2}$ |

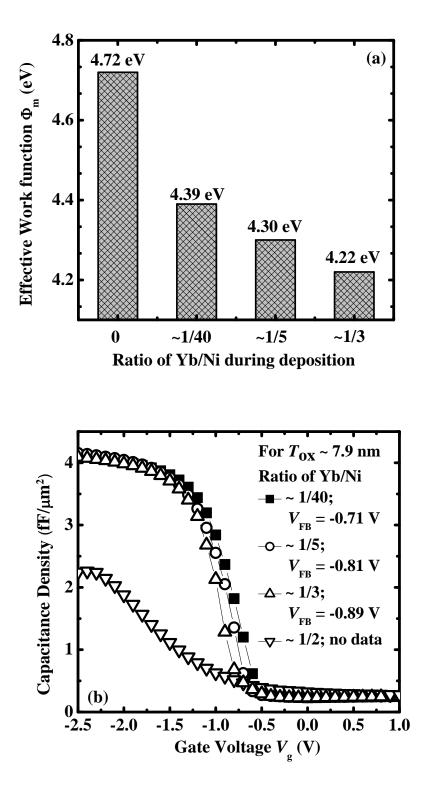

| Fig. 3.12 | (a) Work function of Yb-incorporated Ni FUSI is tunable by modifying Yb incorporation during deposition. (b) <i>C-V</i> plots of Yb incorporated Ni FUSI with different YB/Ni ratios. It is noted that excessive Yb might degrade the device dielectric (e.g. Yb/Ni $\sim 1/2$ )                                                                                                                                 |

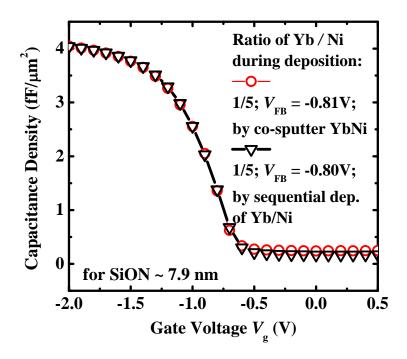

| Fig. 3.13 | <i>C-V</i> characteristics are comparable for Yb incorporated Ni FUSI devices fabricated by two different methods, co-sputter YbNi and sequential sputter Yb and Ni (Yb first)                                                                                                                                                                                                                                   |

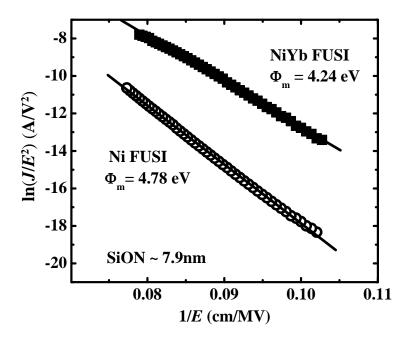

| Fig. 3.14 | FN plots for the devices with Ni FUSI and NiYb FUSI gate 78                                                                                                                                                                                                                                                                                                                                                      |

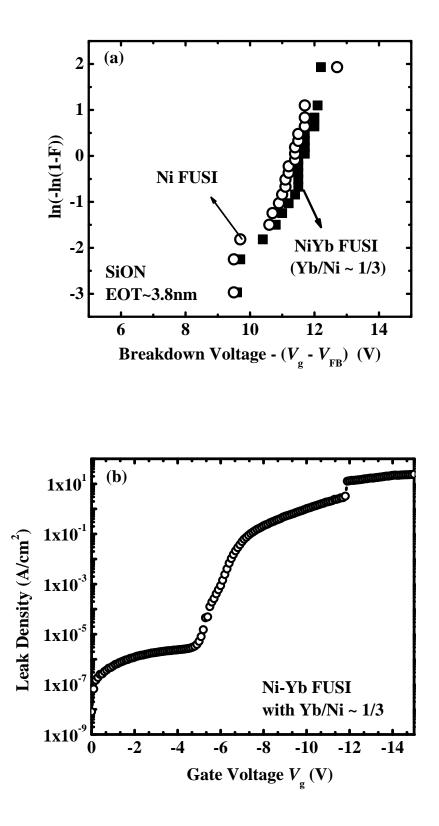

| Fig. 3.15 | <ul> <li>(a) TZBD comparison between the devices with Ni FUSI and NiYb FUSI electrodes (on SiON dielectric).</li> <li>(b) A typical <i>J-V</i> sweep for the device with NiYbSi gate.</li> </ul>                                                                                                                                                                                                                 |

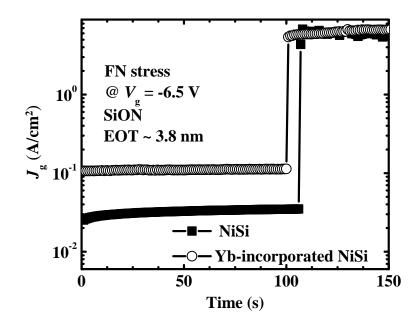

| Fig. 3.16 | 'Current density'-time characteristics for Ni FUSI and<br>Yb-incorporated Ni FUSI devices under constant voltage FN<br>stress (gate injection). 8                                                                                                                                                                                                                                                                |

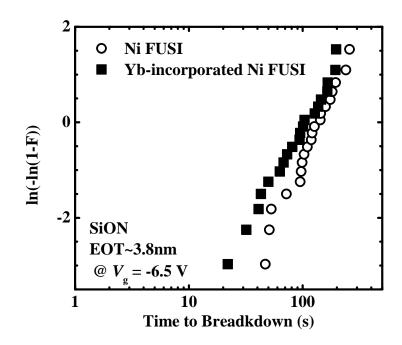

| Fig. 3.17 | TDDB (under gate injection and FN-CVS) comparison betweenthe devices with NiYbSi and NiSi gate electrode (on SiONdielectric).8                                                                                                                                                                                                                                                                                   |

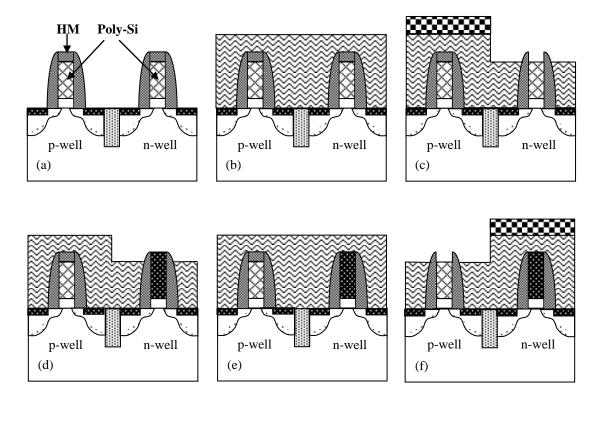

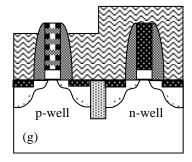

| Fig. 3.18 | Proposed CMOS integration scheme using Yb-incorporated Ni<br>FUSI for n-FETs, and Pt FUSI for p-FETs. (a) CMOS fabrication<br>conventionally using undoped poly-Si gate, after source/drain<br>silicidation; (b) oxide reflow and chemical mechanical<br>planarization (CMP); (c) lithography to mask n-FET region and<br>etch the hard mask to expose the poly of p-FET and hard mask<br>stripping; (d) photo resist strip and FUSI the poly-Si of p-FET<br>(e.g. PtSi <sub>x</sub> ); (e) oxide reflow and CMP; (f) lithography to mask<br>n-FET region and etch the hard mask to expose the poly of<br>n-FET; (g) photo resist strip and FUSI the poly-Si of n-FET (e.g.<br>Yb-incorporated Ni FUSI). | 83 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

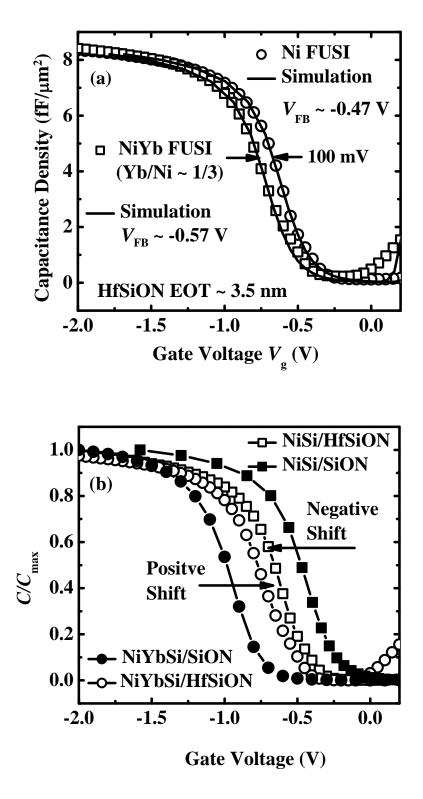

| Fig. 3.19 | (a) Measured and simulated <i>C-V</i> data for capacitors with Yb-incorporated Ni FUSI (Yb/Ni ~1/3) and undoped Ni FUSI gate electrodes. The EOT of HfSiON is ~ 3.5nm. The $V_{\text{FB}}$ shift is 0.1 V. (b) From SiON to HfSiON dielectric, $V_{\text{FB}}$ is positive for NiSi gate electrode, and negative for NiYbSi gate electrode                                                                                                                                                                                                                                                                                                                                                               | 86 |

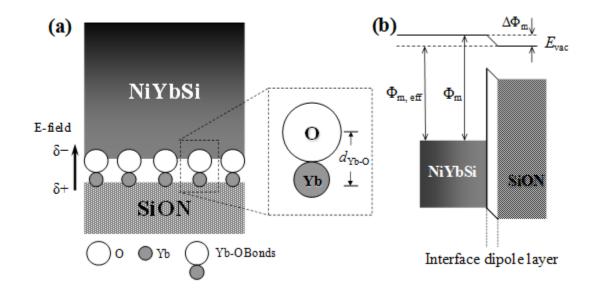

| Fig. 3.20 | (a) A schematic showing highly polarized Yb-O dipoles at the NiYbSi/SiON interface. (b)The $\Phi_m$ of NiYbSi is reduced due to the presence of dipole at the NiYbSi and SiON interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88 |

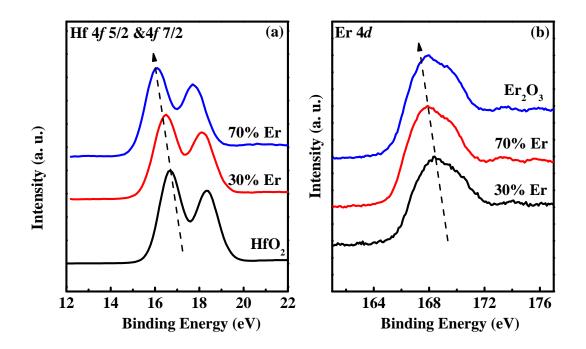

| Fig. 4.1  | XPS spectra for (a) Hf $4f$ core levels; (b) Er $4d$ core levels. The core level peak positions of Hf $4f$ and Er $4d$ shift continuously towards lower binding energy with increasing Er concentration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96 |

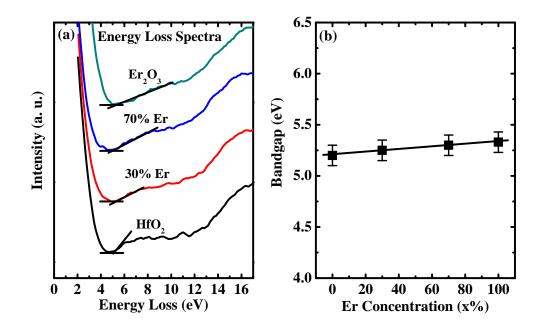

| Fig. 4.2  | (a) O 1 <i>s</i> energy loss spectra for HfO <sub>2</sub> , HfErO with 30% Er and 70% Er, and Er <sub>2</sub> O <sub>3</sub> samples. The cross points (obtained by linearly extrapolating the segment of maximum negative slope to the base line) denote the energy gap $E_g$ values. (b) Dependence of $E_g$ on Er concentration. The solid line is obtained by linear-least-square fit of the data points.                                                                                                                                                                                                                                                                                            | 96 |

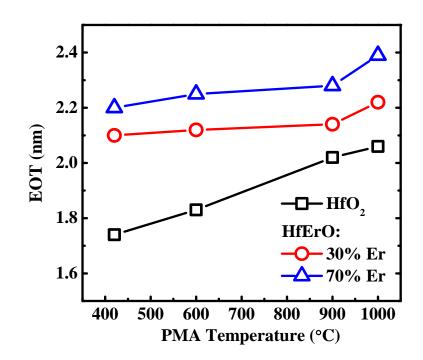

| Fig. 4.3  | EOT variation for TaN gated MOS capacitors with $HfO_2$ and $HfErO$ dielectrics as a function of PMA temperatures, which indicates $HfErO$ films have better thermal stability than $HfO_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98 |

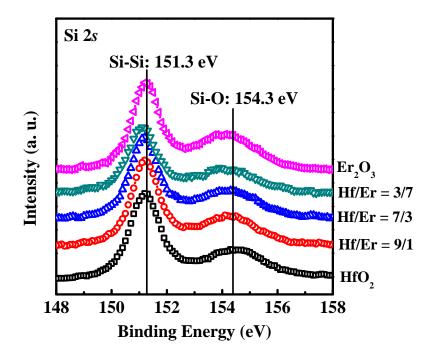

| Fig. 4.4  | XPS spectra for Si 2 <i>s</i> core level taken from HfO <sub>2</sub> , HfErO and $Er_2O_3$ after 600 °C PDA. The Si-O bond is found on all samples, indicating the existence of a low- $\kappa$ interfacial layer between the deposited dielectric and silicon substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                | 98 |

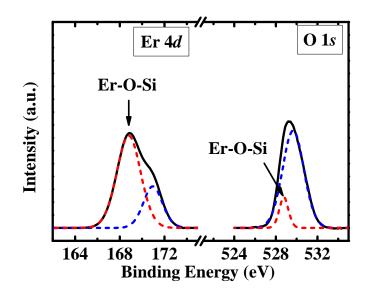

| Fig. 4.5  | Er core level and O 1s spectra for 4 nm HfErO (30% Er) deposited on silicon substrate. The PDA temperature was 600 °C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 99 |

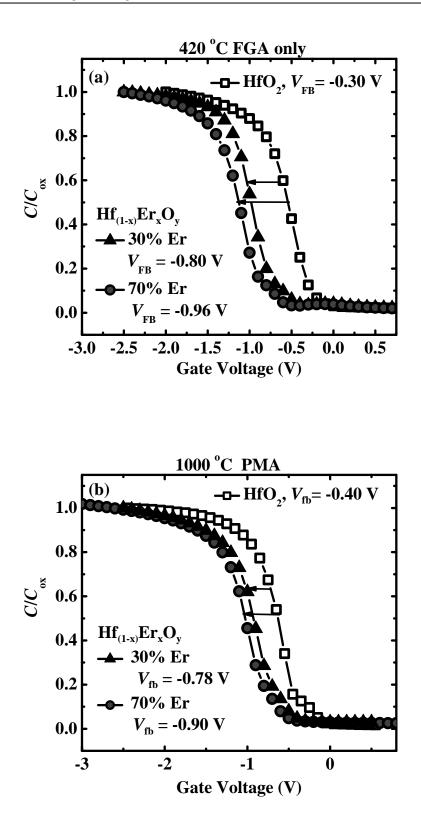

| Fig. 4.6  | (a) Typical <i>C-V</i> curves of capacitors with $HfO_2$ and $HfErO$ (with 30% and 70% Er) gate dielectrics and TaN metal gate after 420 °C forming gas annealing. (b) Typical <i>C-V</i> curves of capacitors with $HfO_2$ and $HfErO$ (with 30% and 70% Er) gate dielectrics and TaN metal gate after 1000°C, 5 second annealing                                                        | 100 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

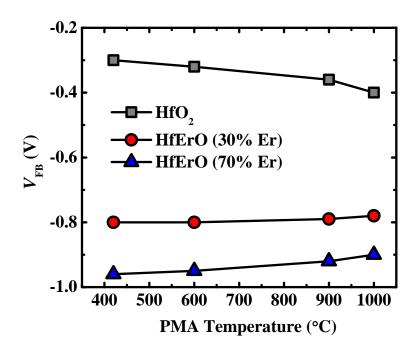

| Fig. 4.7  | Flatband voltage variation for TaN gated MOS capacitors with HfO <sub>2</sub> and HfErO dielectrics as a function of PMA temperature 1                                                                                                                                                                                                                                                    | 101 |

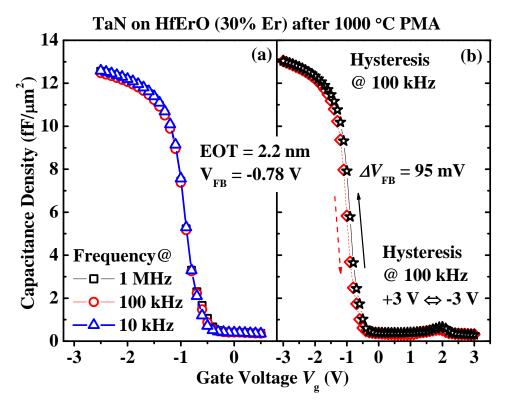

| Fig. 4.8  | <ul> <li>(a) <i>C-V</i> curves of the HfErO with 30% Er measured at 10 kHz, 100 kHz and 1 MHz.</li> <li>(b) Hysteresis of MOS capacitors with HfErO (30% Er) dielectric after annealing at 1000°C for 5 seconds.</li> </ul>                                                                                                                                                               | 102 |

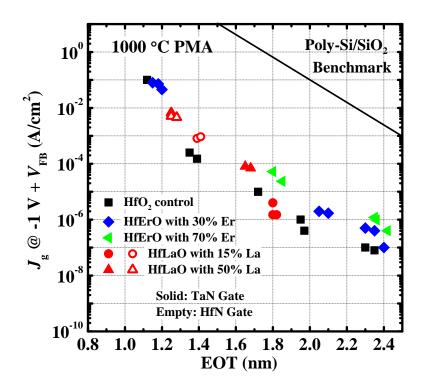

| Fig. 4.9  | The relationship between gate leakage current density and EOT for MOS capacitors with HfO2, HfLaO and HfErO gate dielectrics and TaN or HfN metal gate. Compared with poly-Si/SiO <sub>2</sub> benchmark at the same EOT, HfErO provides ~4 orders reduction in gate leakage current. HfLaO data is from Ref. [5]                                                                         | 103 |

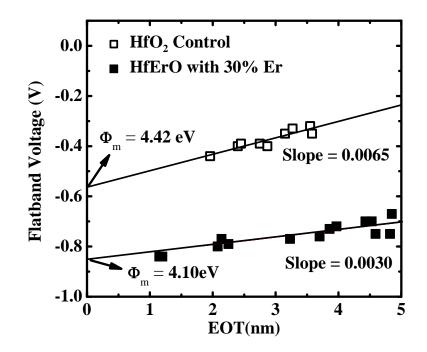

| Fig. 4.10 | $V_{\rm FB}$ vs. EOT plot was used to extract the modulated TaN $\Phi_{\rm m}$ in TaN/HfO <sub>2</sub> or TaN/HfErO gate stack by eliminating the effect of fixed oxide charge. The PMA temperature was 1000°C. The p-Si substrate doping was $6 \times 10^{15}$ cm <sup>-3</sup> .                                                                                                       | 104 |

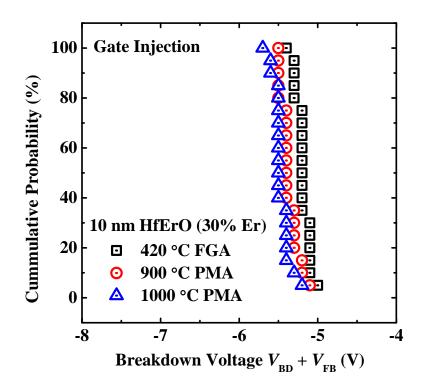

| Fig. 4.11 | Dependence of cumulative probability on breakdown voltage of<br>TaN gated MOS capacitors with HfErO (30% Er)                                                                                                                                                                                                                                                                              | 105 |

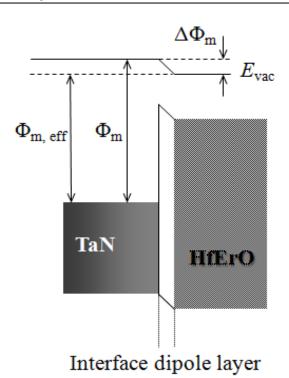

| Fig. 4.12 | The effect of an interface dipole layer on TaN $\Phi_m$ is illustrated in the energy band diagram. The $\Phi_m$ of TaN is reduced by $\Delta \Phi_m$ due to the presence of the interface dipole.                                                                                                                                                                                         | 107 |

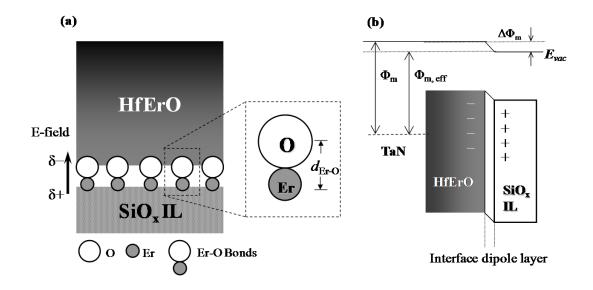

| Fig. 4.13 | (a) A schematic showing highly polarized Er-O dipoles at the HfErO/SiO <sub>x</sub> interface. (b)The $\Phi_m$ of TaN is reduced due to the presence of dipole at the HfErO and SiO <sub>x</sub> interface, which is different from Fig. 4.12.                                                                                                                                            | 107 |

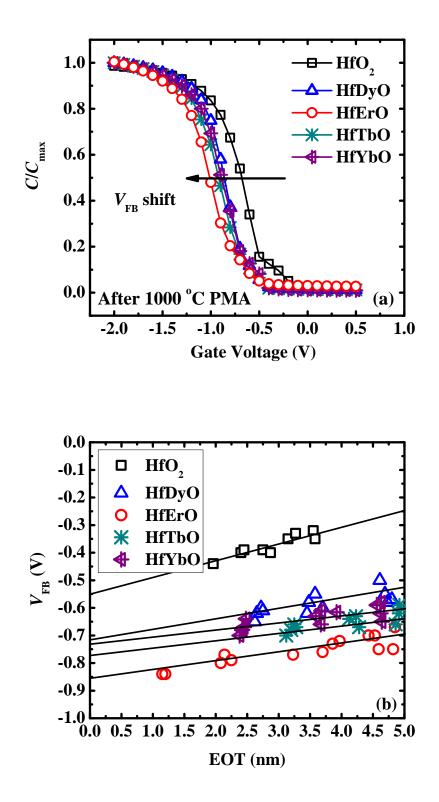

| Fig. 4.14 | (a) <i>C-V</i> curves of HfO <sub>2</sub> doped by $Er_2O_3$ , $Tb_2O_3$ , $Yb_2O_3$ and $Dy_2O_3$ after 1000 °C anneal. All curves show significant flatband voltage shift towards silicon conduction band. (b) <i>V</i> <sub>FB</sub> versus EOT plot was used to extract the TaN $\Phi_m$ modulated by doping HfO <sub>2</sub> with by $Er_2O_3$ , $Tb_2O_3$ , $Yb_2O_3$ and $Dy_2O_3$ | 109 |

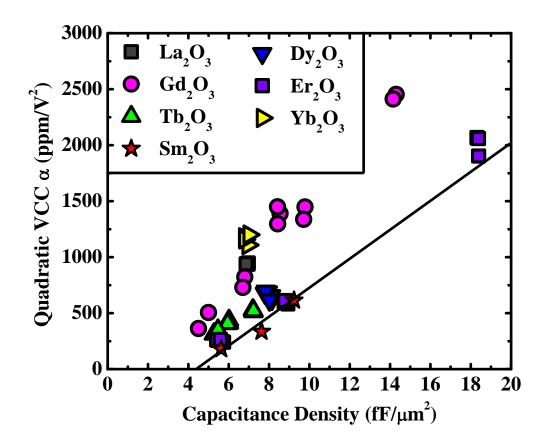

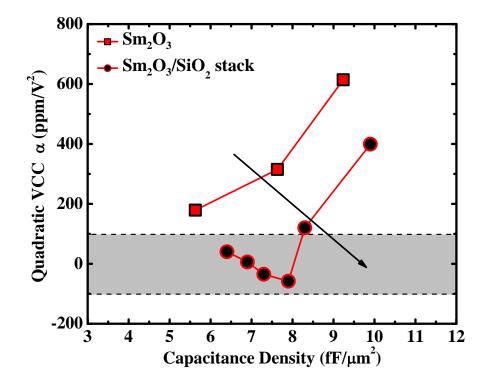

| Fig. 5.1 | Summary of quadratic VCC of MIM capacitors with various lanthanoid oxides, plotted versus capacitance density for all lanthanoid oxide MIM capacitors.                                                                                                                                                                                                                                                                                                                                                                                                         | 117 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

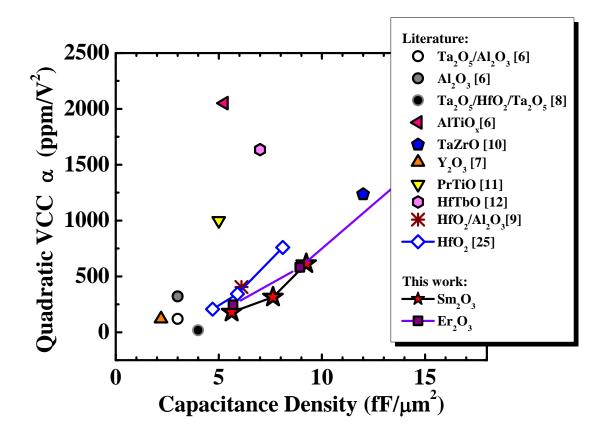

| Fig. 5.2 | The values of $\alpha$ extracted from MIM capacitors with a single $Sm_2O_3$ or $Er_2O_3$ dielectric layer in this work are compared with data published in the literature.                                                                                                                                                                                                                                                                                                                                                                                    | 118 |

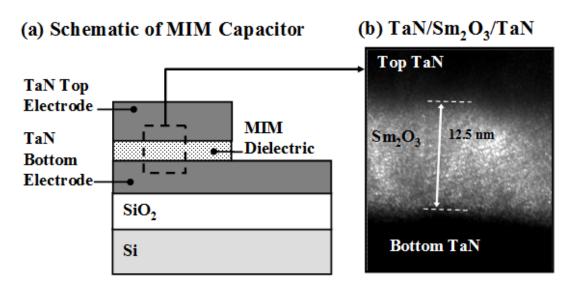

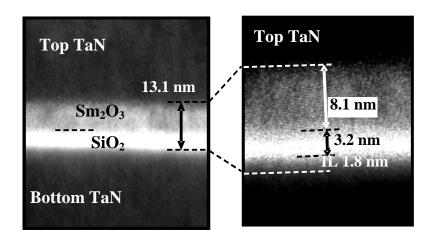

| Fig. 5.3 | (a) Schematic of Metal-Insulator-Metal (MIM) capacitor having top and bottom tantalum nitride (TaN) electrodes. (b) In one split, the MIM dielectric is a single $Sm_2O_3$ layer, as shown in the cross-sectional TEM image.                                                                                                                                                                                                                                                                                                                                   | 119 |

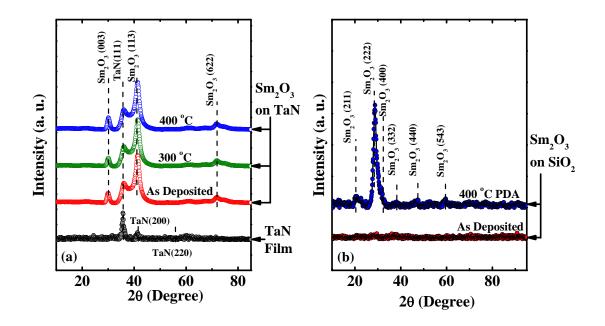

| Fig. 5.4 | (a) X-ray diffraction (XRD) spectra of as-deposited $Sm_2O_3$ on TaN, as well as $Sm_2O_3/TaN$ stack after being annealed at 300 °C and 400 °C. XRD spectrum of an exposed TaN surface is also obtained. As-deposited $Sm_2O_3$ on TaN is poly-crystalline. (b) XRD spectra of as-deposited $Sm_2O_3$ on SiO <sub>2</sub> , as well as $Sm_2O_3/SiO_2$ stack after being annealed at 400 °C. As-deposited $Sm_2O_3$ on SiO <sub>2</sub> is amorphous.                                                                                                          | 120 |

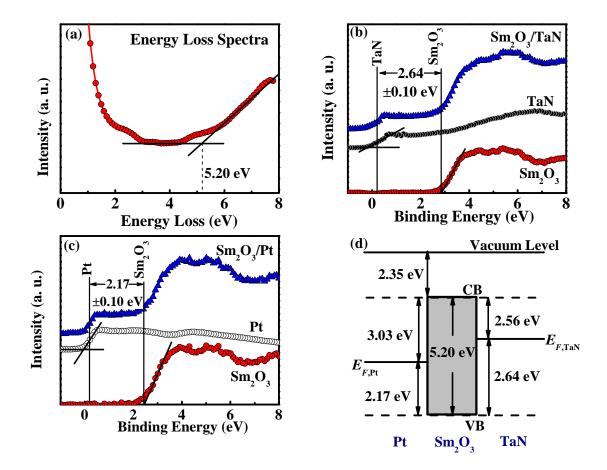

| Fig. 5.5 | (a) Oxygen (O) 1 <i>s</i> energy-loss spectra obtained from bulk $Sm_2O_3$ which went through a 400 °C post-deposition anneal (PDA). The energy band gap of $Sm_2O_3$ is 5.20 eV. (b) Valence-band spectrum for $Sm_2O_3/TaN$ and the deconvoluted spectra for thick $Sm_2O_3$ and TaN. (c) Valence-band spectrum for $Sm_2O_3/Pt$ and the deconvoluted spectra for thick $Sm_2O_3$ and Pt. (d) Energy-band diagram showing the band alignment for Pt, $Sm_2O_3$ , and TaN                                                                                     | 122 |

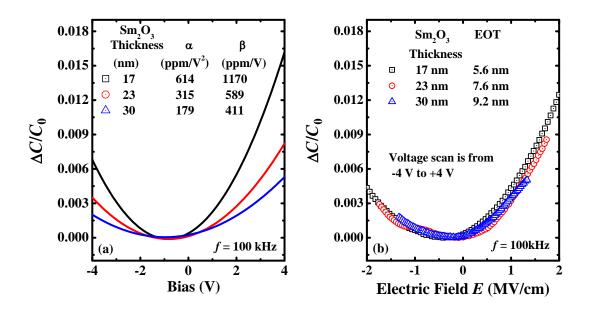

| Fig. 5.6 | (a) Voltage-dependant normalized capacitance $(\Delta C/C_0)$ measured<br>at 100 kHz for MIM capacitors with a single Sm <sub>2</sub> O <sub>3</sub> dielectric<br>layer having a thickness of 17 nm, 23 nm, or 30 nm. By fitting<br>a second-order polynomial equation (solid lines) to the<br>experimental data (plotted in symbols), the quadratic voltage<br>coefficient of capacitance and the linear voltage coefficient of<br>capacitance are obtained. (b) Plot of $\Delta C/C_0$ versus electric<br>field <i>E</i> for the same MIM capacitors in (a) | 123 |

xvii

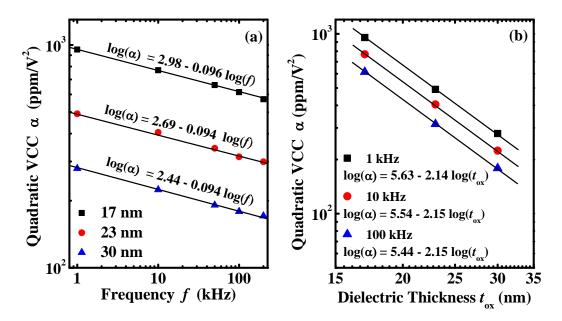

| Fig. 5.7  | (a) Frequency dependence of $\alpha$ for MIM capacitors with a single Sm <sub>2</sub> O <sub>3</sub> dielectric layer having a thickness of 17 nm, 23 nm, and 30 nm. The straight lines are a linear fit to the data points on a log-log scale. (b) Thickness dependence of $\alpha$ at 1 kHz, 10 kHz, and 100 kHz with a linear fit (solid line) in log-log scale to experimental data (symbols).                                                                                                                                                                                             | 124 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

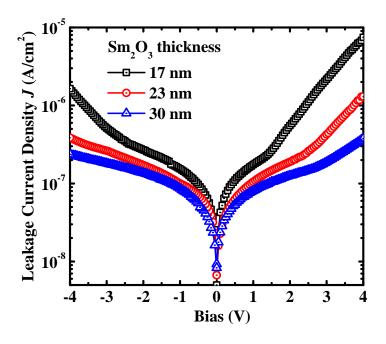

| Fig. 5.8  | Room temperature $J$ - $V$ characteristics of MIM capacitors with a single Sm <sub>2</sub> O <sub>3</sub> dielectric layer having a thickness of 17 nm, 23 nm, and 30 nm.                                                                                                                                                                                                                                                                                                                                                                                                                      | 125 |

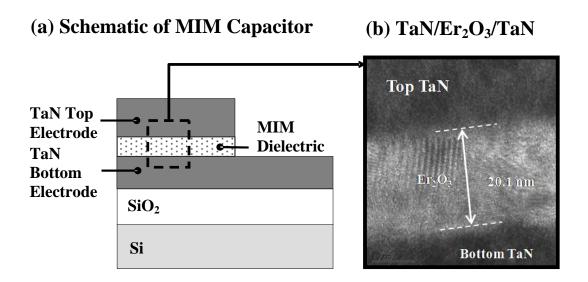

| Fig. 5.9  | (a) Schematic of Metal-Insulator-Metal (MIM) capacitor having top and bottom tantalum nitride (TaN) electrodes. (b) In one split, the MIM dielectric is a single $Er_2O_3$ layer, as shown in the cross-sectional transmission electron microscopy (TEM) image.                                                                                                                                                                                                                                                                                                                                | 126 |

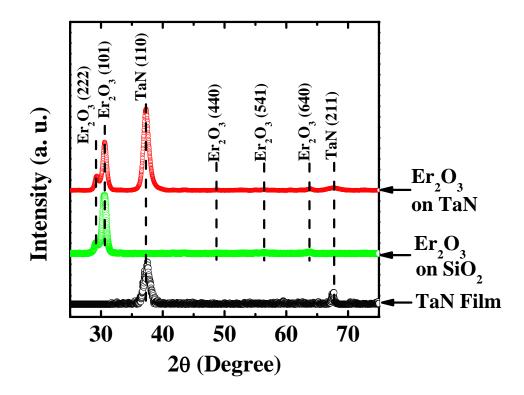

| Fig. 5.10 | XRD spectra of $Er_2O_3$ on $SiO_2$ and TaN, after being annealed at 400 °C. XRD spectrum of an exposed TaN surface is also obtained. The $Er_2O_3$ films are polycrystalline.                                                                                                                                                                                                                                                                                                                                                                                                                 | 127 |

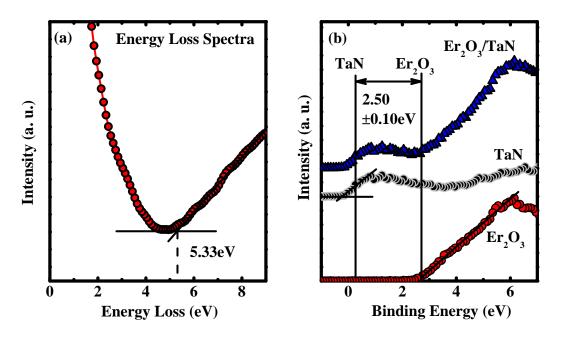

| Fig. 5.11 | (a) Oxygen (O) 1s energy-loss spectra obtained from bulk $Er_2O_3$ which went through a 400 °C post-deposition anneal (PDA). The energy band gap of $Er_2O_3$ is 5.33 eV. (b) Valence-band spectrum for $Er_2O_3/TaN$ and the deconvoluted spectra for $Er_2O_3$ and TaN.                                                                                                                                                                                                                                                                                                                      | 127 |

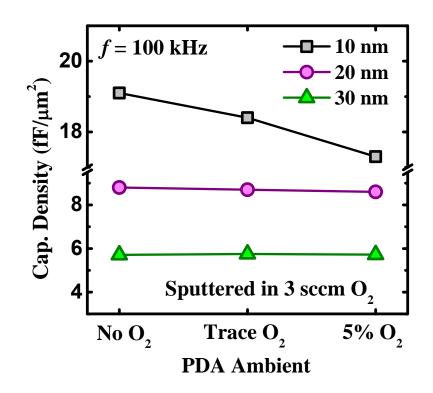

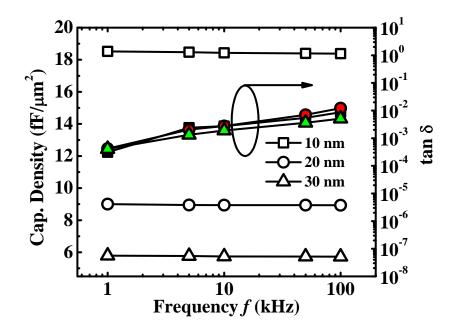

| Fig. 5.12 | The change of capacitance densities as a function of oxygen concentration in PDA ambient. The increased oxygen concentration has a larger impact on 10 nm $Er_2O_3$ than that on 20 nm and 30 nm $Er_2O_3$ .                                                                                                                                                                                                                                                                                                                                                                                   | 129 |

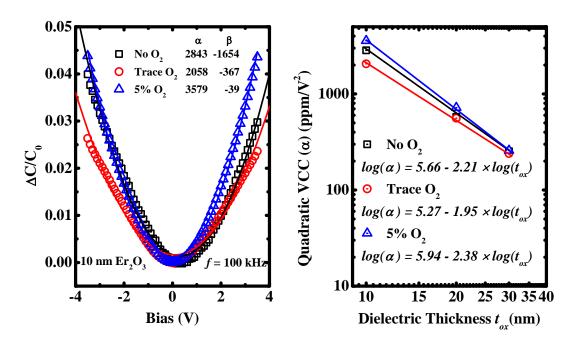

| Fig. 5.13 | (a) Voltage-dependant normalized capacitance $(\Delta C/C_0)$ measured<br>at 100 kHz for MIM capacitors with a single 10 nm Er <sub>2</sub> O <sub>3</sub><br>dielectric layer annealed in different oxygen concentrations. By<br>fitting a second-order polynomial equation (solid lines) to the<br>experimental data (plotted in symbols), the quadratic voltage<br>coefficient of capacitance and the linear voltage coefficient of<br>capacitance are obtained. (b) Thickness dependence of $\alpha$<br>with a linear fit (solid line) in log-log scale to experimental data<br>(symbols). | 130 |

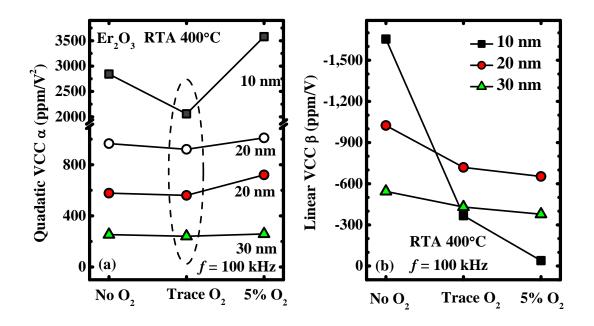

| Fig. 5.14 | (a) Quadratic VCC $\alpha$ as a function of oxygen concentration in PDA ambient. The solid symbols represent MIM capacitors with Er <sub>2</sub> O <sub>3</sub> deposited in 27-sccm Ar/3-sccm O <sub>2</sub> during the PVD; the open symbols represent MIM capacitors with Er <sub>2</sub> O <sub>3</sub> deposited in 28-sccm Ar/2-sccm O <sub>2</sub> during the PVD. (b) Linear VCC as a function of oxygen concentration in PDA ambient.                                                                                                                                                                                        | 131 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

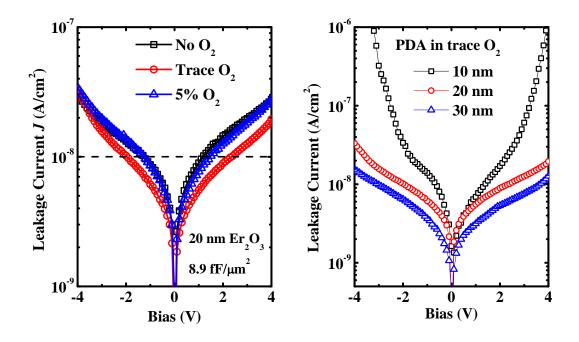

| Fig. 5.15 | (a) Effect of oxygen concentration during PDA on $J-V$ characteristics of MIM capacitors with 20-nm single $Er_2O_3$ dielectric layer; (b) Comparison of $J-V$ characteristics of MIM capacitors with a single $Er_2O_3$ dielectric layer having a thickness of 10, 20 and 30 nm with a PDA in trace oxygen.                                                                                                                                                                                                                                                                                                                          | 132 |

| Fig. 5.16 | Frequency dependence of capacitance density and frequency dispersion of loss tangent ( $1/Q$ factor) for MIM capacitors with a single Er <sub>2</sub> O <sub>3</sub> dielectric layer having a thickness of 10 nm, 20 nm, and 30 nm. The open symbols represent capacitance density; while the solid symbols represent the loss tangent.                                                                                                                                                                                                                                                                                              | 134 |

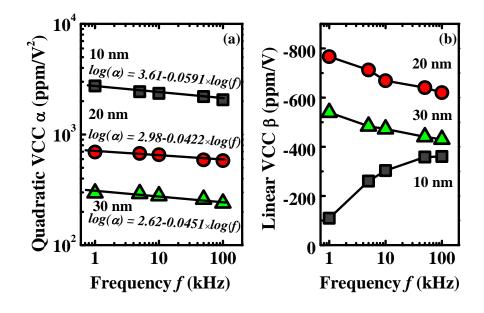

| Fig. 5.17 | (a) Frequency dependence of $\alpha$ for MIM capacitors with a single $Er_2O_3$ dielectric layer having a thickness of 10 nm, 20 nm, and 30 nm, annealed in trace $O_2$ . The straight lines are a linear fit to the data points on a log-log scale. (b) Frequency dependence of $\beta$ for MIM capacitors with a single $Er_2O_3$ dielectric layer having a thickness of 10 nm, 20 nm, and 30 nm, annealed in trace $O_2$                                                                                                                                                                                                           | 134 |

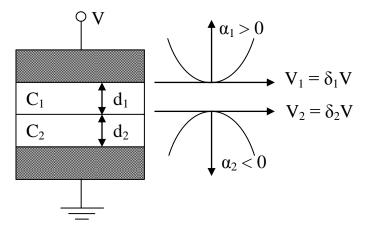

| Fig. 5.18 | Cross sectional schematics of an MIM capacitor with stacked<br>dielectrics. When two different capacitors are connected in<br>series, voltages divided in the stack decide the voltage linearity<br>of the capacitance of the stack.                                                                                                                                                                                                                                                                                                                                                                                                  | 137 |

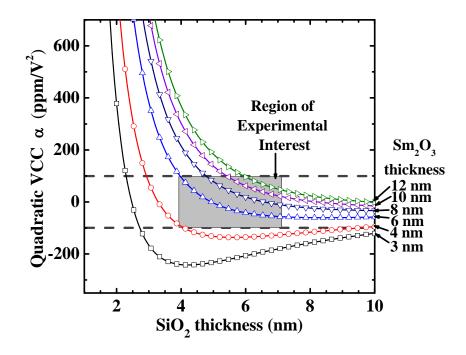

| Fig. 5.19 | Simulated $\alpha$ versus SiO <sub>2</sub> thickness plot for different Sm <sub>2</sub> O <sub>3</sub> thicknesses from 3 to 12 nm. The value of $\alpha$ should preferably be within ±100 ppm/V <sup>2</sup> , as indicated by the horizontal dashed lines. The choice of SiO <sub>2</sub> and Sm <sub>2</sub> O <sub>3</sub> thicknesses should preferably be in the target region where $\alpha$ is small and relatively insensitive to a variation in the thickness of SiO <sub>2</sub> . The gray region shows the range of thicknesses of SiO <sub>2</sub> and Sm <sub>2</sub> O <sub>3</sub> to be selected in our experiment. | 137 |

| Fig. 5.20 | The left figure shows a $Sm_2O_3$ layer formed on a $SiO_2$ layer as<br>the dielectric in a MIM capacitor with TaN electrodes. A high<br>resolution TEM image is given on the right, clearly showing the<br>presence of an interfacial layer (IL) between $SiO_2$ and the TaN<br>bottom electrode. 139                                                                                                                                                                                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

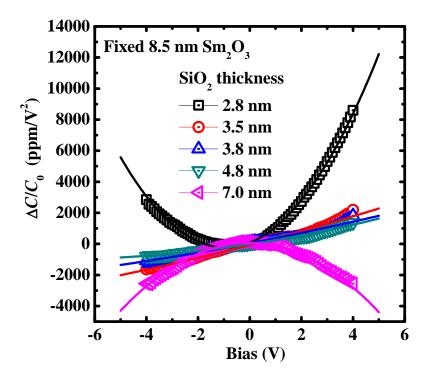

| Fig. 5.21 | Normalized $C$ - $V$ curves of Sm <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> MIM capacitors with Sm <sub>2</sub> O <sub>3</sub> fixed at 8.5 nm while varying SiO <sub>2</sub> thickness from 2.8 nm to 7 nm. Curvature of $C$ - $V$ curves changes from positive to negative as the SiO <sub>2</sub> thickness is increased                                                                                                                                                                                                                                                                     |

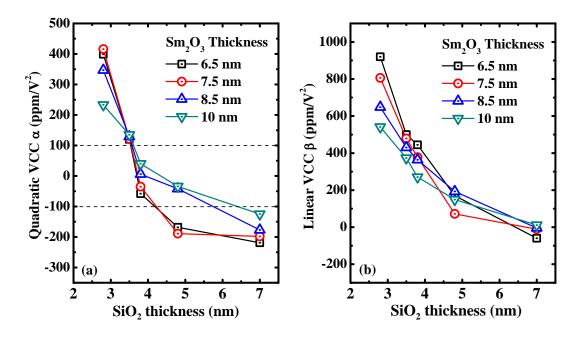

| Fig. 5.22 | (a) Quadratic VCC ( $\alpha$ value) versus the thickness of SiO <sub>2</sub> with varying the thickness of SiO <sub>2</sub> and Sm <sub>2</sub> O <sub>3</sub> . (b) Linear VCC ( $\beta$ value) versus the thickness of SiO <sub>2</sub> with varying the thickness of SiO <sub>2</sub> and Sm <sub>2</sub> O <sub>3</sub> . Both $\alpha$ value and $\beta$ value can be modulated by increasing the thickness of SiO <sub>2</sub> layer. Near zero $\alpha$ value can be obtained by optimizing the EOT ratio of SiO <sub>2</sub> to Sm <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> stack. 140 |

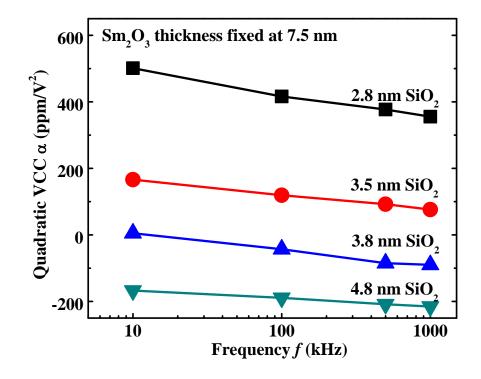

| Fig. 5.23 | Frequency dependence of $\alpha$ for the Sm <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> MIM capacitors<br>with Sm <sub>2</sub> O <sub>3</sub> fixed at 7.5 nm while varying SiO <sub>2</sub> thickness from<br>2.8 nm to 4.8 nm. 141                                                                                                                                                                                                                                                                                                                                                              |

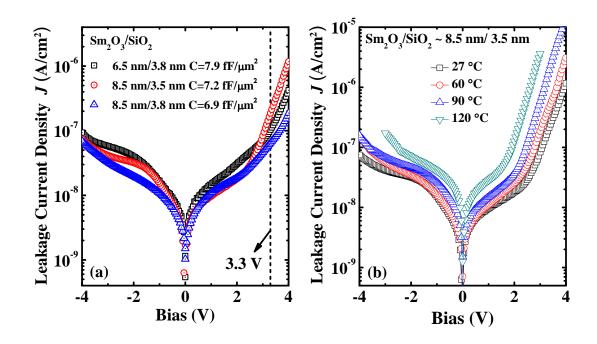

| Fig. 5.24 | (a) <i>J-V</i> characteristics of $Sm_2O_3/SiO_2$ MIM capacitors with 3 different thickness combinations at room temperature; (b) <i>J-V</i> characteristics of $Sm_2O_3/SiO_2$ MIM capacitors with 8.5 nm $Sm_2O_3$ and 3.5 nm $SiO_2$ measured at different temperatures (27-120 °C). 142                                                                                                                                                                                                                                                                                                         |

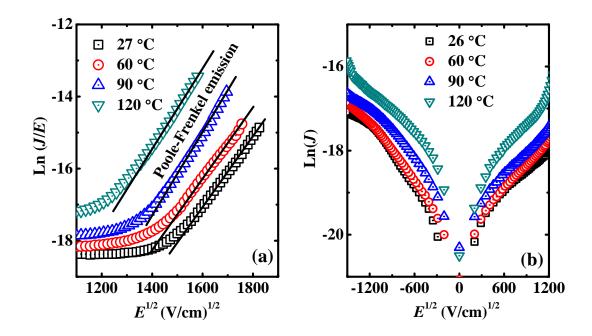

| Fig. 5.25 | (a) Plot of $\ln(J/E)$ versus $E^{1/2}$ as a function of temperature together with the linear fitting for the leakage current at high positive bias; (b) Plot of $\ln(J)$ versus $E^{1/2}$ as a function of temperature at low bias                                                                                                                                                                                                                                                                                                                                                                 |

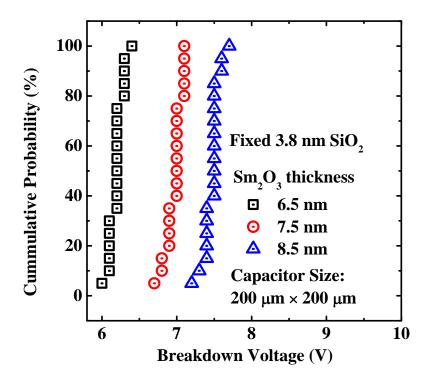

| Fig. 5.26 | Cumulative percentage for breakdown voltage of the MIM capacitors with various different Sm <sub>2</sub> O <sub>3</sub> thicknesses formed on a 3.8 nm SiO <sub>2</sub> layer.                                                                                                                                                                                                                                                                                                                                                                                                                      |

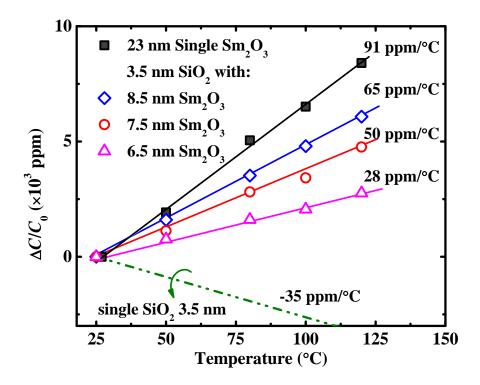

| Fig. 5.27 | Adding SiO <sub>2</sub> layer improves the TCC of Sm <sub>2</sub> O <sub>3</sub> MIM capacitors<br>by the canceling effect due to the negative TCC of SiO <sub>2</sub> MIM<br>capacitors. 145                                                                                                                                                                                                                                                                                                                                                                                                       |

| Fig. 5.28 | A comparison of MIM capacitors with a single layer $Sm_2O_3$ dielectric and a $Sm_2O_3/SiO_2$ dielectric stack. The lowest values for $\alpha$ can be achieved at various capacitance densities by exploiting the canceling effect in the $Sm_2O_3/SiO_2$ dielectric stack.          | 146 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

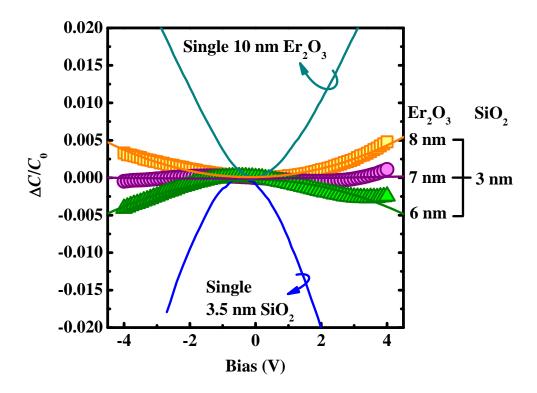

| Fig. 5.29 | Normalized <i>C</i> - <i>V</i> curves of $Er_2O_3/SiO_2$ stack MIM capacitors.<br>Curvature of <i>C</i> - <i>V</i> curves changes from negative to positive as the $Er_2O_3$ thickness is increased.                                                                                 | 148 |

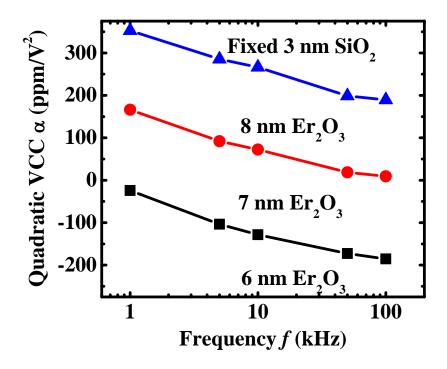

| Fig. 5.30 | Frequency dependence of $\alpha$ for MIM capacitors with different $Er_2O_3/SiO_2$ stacks.                                                                                                                                                                                           | 148 |

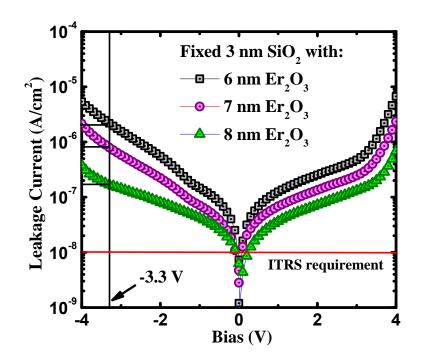

| Fig. 5.31 | <i>J-V</i> characteristic of $Er_2O_3/SiO_2$ MIM capacitors with 6, 7 and 8 nm $Er_2O_3$ , stacked with 3 nm $SiO_2$ .                                                                                                                                                               | 149 |

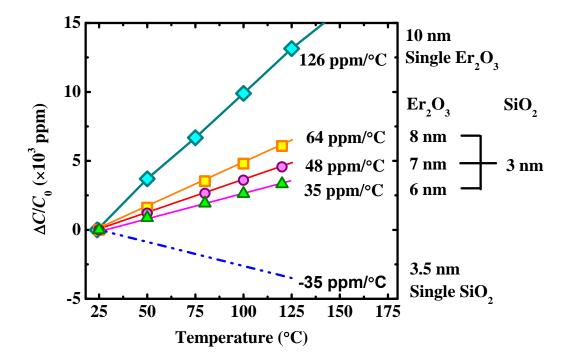

| Fig. 5.32 | Adding $SiO_2$ layer improves the TCC of $Er_2O_3$ MIM capacitors<br>by the canceling effect due to the negative TCC of $SiO_2$ MIM<br>capacitors.                                                                                                                                   | 149 |

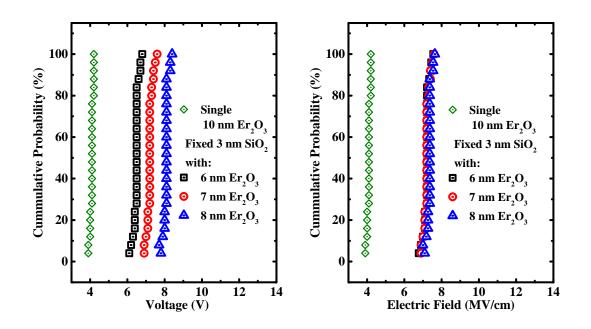

| Fig. 5.33 | Cumulative probability dependent on breakdown voltage and breakdown field of the MIM capacitors with single $Er_2O_3$ layer and $Er_2O_3/SiO_2$ stacks.                                                                                                                              | 150 |

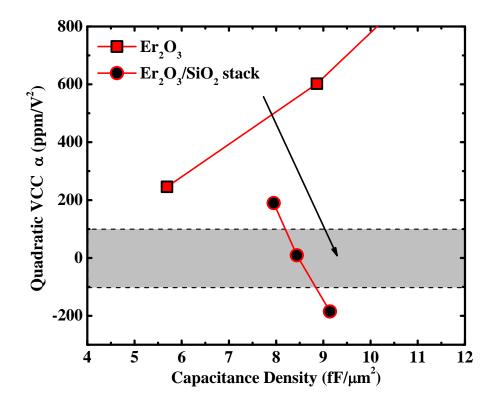

| Fig. 5.34 | A comparison of MIM capacitors with a single layer $Er_2O_3$<br>dielectric and a $Er_2O_3/SiO_2$ dielectric stack. The lowest values<br>for $\alpha$ can be achieved at various capacitance densities by<br>exploiting the canceling effect in the $Er_2O_3/SiO_2$ dielectric stack. | 151 |

| Fig. 5.35 | A comparison of $Sm_2O_3/SiO_2$ and $Er_2O_3/SiO_2$ stacks with $HfO_2/SiO_2$ stack. $Sm_2O_3/SiO_2$ and $Er_2O_3/SiO_2$ stacks are better to meet the capacitance density requirements.                                                                                             | 153 |

## LIST OF SYMBOLS

| Symbol                 | Description                                  | Unit               |

|------------------------|----------------------------------------------|--------------------|

| С                      | Capacitance                                  | fF/µm <sup>2</sup> |

| $C_{ox}$               | Capacitance of gate oxide                    | $fF/\mu m^2$       |

| $E_c$                  | Si conduction band-edge                      | eV                 |

| $E_F$                  | Fermi-level energy                           | eV                 |

| $E_{v}$                | Si valence band-edge                         | eV                 |

| $E_{vac}$              | Vacuum level                                 | eV                 |

| f                      | Frequency                                    | Hz                 |

| $I_D$                  | Transistor drive current                     | А                  |

| $J_G$                  | Gate current density                         | A/cm <sup>2</sup>  |

| <i>m</i> *             | Effective mass                               | kg                 |

| $N_d$                  | Doping concentration                         | cm <sup>-2</sup>   |

| $Q_{ox}$               | Oxide fixed charge density                   | cm <sup>-2</sup>   |

| q                      | Electronic charge                            | С                  |

| <i>t</i> <sub>ox</sub> | Dielectric physical thickness                | nm                 |

| $T_{\rm ox}$           | Equivalent oxide thickness                   | nm                 |

| $V_{\rm ds}$           | Transistor drain voltage                     | V                  |

| $V_{\rm gs}$           | Gate voltage                                 | V                  |

| $V_{\rm FB}$           | Flatband voltage                             | V                  |

| $V_{\rm th}$           | Threshold voltage                            | V                  |

| α                      | Quadratic voltage coefficient of capacitance | ppm/V <sup>2</sup> |

| β                      | Linear voltage coefficient of capacitance    | ppm/V              |

| З                      | Permittivity                                 | F/cm <sup>2</sup>  |

| $\Phi_{ m bn}$         | Electron barrier height                      | eV                 |

| $\Phi_{ m bp}$         | Hole barrier height                          | eV                 |

| $\Phi_{\rm Si}$        | Work function of Si substrate                | eV                 |

| $\Phi_{\rm m}$ | Work function of metal gate  | eV    |

|----------------|------------------------------|-------|

| ρ              | Resistivity                  | μΩ·cm |

| к              | Relative dielectric constant | none  |

## **Chapter 1**

## Introduction

As the author is typing this thesis, the ITRS (International Technology Roadmap for Semiconductors) Summer Public Conference is being held during SEMICON West. New materials and devices are being investigated to extend CMOS. In CMOS technology development, new materials, such as high- $\kappa$  and low- $\kappa$ dielectric, metal gate, stressors and new silicide materials have played and will continue to play an important role.

Lanthanoid elements and their compounds, which have widely been used in lasers, catalysts, magnets, glass and ceramics, are strategic materials for several major industry areas, including the military weapons. They have become more important in microelectronics as the demand for performance cannot be fulfilled by existing materials. This chapter would discuss the characteristics of lanthanoid elements and their potential to address the challenges in the silicon CMOS technology.

#### **1.1 Lanthanoid Elements and Their Compounds**

#### 1.1.1 The Lanthanoid Series

Lanthanoid elements are the 15 elements of the Periodic Table (La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, and Lu) with the atomic numbers from 57 through 71 (Table 1.1). The lanthanoid series (Ln) is named after lanthanum. Lanthanoids are sometimes referred to as the "rare earths", which is used to describe all the lanthanoids together with scandium (Sc) and yttrium (Y). The use of this name is deprecated by International Union of Pure and Applied Chemistry (IUPAC), as they are neither rare in abundance nor "earths" (an obsolete term for water-insoluble oxides of electropositive metals incapable of being smelted into metal using late 18th century technology). These elements are in fact fairly abundant in nature, although rare as compared to the "common" earths such as lime or magnesia. IUPAC currently recommends the name *lanthanoid* rather than *lanthanide*, as the suffix "-ide" generally indicates negative ions whereas the suffix "-oid" indicates similarity to one of the members of the containing family of elements. In the older literature, the name *lanthanon* was often used.

Lanthanoids are chemically similar to each other and closely resemble the first element in the series - La. The lanthanoids occur as trivalent cations in nature except for cerium (Ce) and europium (Eu). An important feature is that they all have low work function, ranging from 2.59 eV (Yb) to 3.3 eV (La). The photoelectric work functions of all lanthanoid elements are listed in Table 1.1.

| Atomic No.                  | 57    | 58    | 59    | 60    | 61    | 62    | 63    | 64    |

|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Symbol                      | La    | Ce    | Pr    | Nd    | Pm    | Sm    | Eu    | Gd    |

| Work function               | 3.3   | 2.7   | 2.7   | 3.3   | -     | 3.2   | 2.54  | 3.07  |

| Ln <sup>3+</sup> radii (nm) | 0.123 | 0.115 | 0.114 | 0.112 | -     | 0.106 | 0.106 | 0.104 |

| Atomic No.                  | 65    | 66    | 67    | 68    | 69    | 70    | 71    |       |

| Name                        | Tb    | Dy    | Но    | Er    | Tm    | Yb    | Lu    |       |

| Work function               | 3.09  | 3.09  | 3.09  | 3.12  | 3.12  | 2.59  | 3.15  |       |

| Ln <sup>3+</sup> radii (nm) | 0.100 | 0.099 | 0.098 | 0.096 | 0.094 | 0.093 | 0.092 |       |

**Table 1.1.** List of lanthanoid elements, photoelectric work functions [2], and ionic radii of the trivalent lanthanoid ions [1].

In the outer electronic configuration of the lanthanoid series, the  $6s^2$  shell is always occupied, the  $5d^1$  configuration appears in La, Ce, Gd and Lu, and then the 4fshell is progressively filled as the atomic number increases. The number of electrons in the 4f shell is therefore the distinctive characteristic of the lanthanoid elements. The 4f sub-shell lies inside the ion, shielded by the  $5s^2$  and  $5p^6$  closed sub-shells. The ionic radii of the lanthanoids decrease through the period - the so-called lanthanide contraction – from 0.123 nm in La to 0.092 nm in Lu [1].

#### 1.1.2 Lanthanoid Silicides

Metal silicide thin films are commonly used in ohmic contacts, MOS gate electrodes, and silicidation of diffusion regions. Silicides of platinum (Pt), tungsten

(W), titanium (Ti), cobalt (Co), nickel (Ni), tantalum (Ta) and other metals have been heavily investigated, and some of them are now commonly used in manufacturing. The lanthanoid silicides are relatively new to CMOS processing technology, but their low work function and low Schottky barrier to the n-type silicon [3] have made them attractive in the development of new infrared detectors, work function tuning in FUSI metal gate [4] and Schottky source/drain transistors [5, 6].

The lanthanoid disilicides (LnSi<sub>2</sub>) are a large group among the lanthanoid silicides. However, the perfect stoichiometry of 1:2 is not commonly seen in thin silicide films. The silicon atoms behave like interstitials and the silicon sublattice in the silicide usually contain vacancies. The actual compositions vary between 1:1.66 and 1:1.85, especially for heavy lanthanoid silicides from Gd to Lu [7-9]. Lanthanoid disilicides with silicon vacancies are usually denoted as LnSi<sub>2-x</sub>.

The most common method for forming lanthanoid silicide thin films is by depositing a thin layer of the metal onto clean silicon surface by Physical Vapor Deposition (PVD), which includes e-beam evaporation and sputtering; the silicide is then formed by annealing either in furnace or in RTP. The reactions of lanthanoid silicides show remarkably different growth kinetics from those observed in the formation of other transition metal silicides. By annealing lanthanoid metal on Si substrates, it has been shown that Si atoms are the dominant diffusing species during the silicide formation [10, 11]. It is generally accepted that the mechanism of lanthanoid silicide thin film formation is dominated by nucleation phenomena. The solid state interactions between lanthanoid and silicon exhibit a critical temperature. Below the critical temperature, reactions are very sluggish; while above this temperature, reaction is fast. For La, it was found that although the reaction starts from as low as 200  $\mathbb{C}$ , the disilicide phase LaSi<sub>2</sub> does not form until 600  $\mathbb{C}$  [12, 13].

This suggests an intermediate stage of formation of  $LaSi_{2-x}$  [13]. As lanthanoid metals are chemically reactive, the oxidation of the lanthanoid elements must be prevented during the formation of silicides.

#### 1.1.3 Lanthanoid Oxides

Lanthanoid metals react with oxygen vigorously and form oxides [14]. These oxides are thermally stable. In the solid state, the +3 oxidation state ( $Ln_2O_3$ ) is generally the stable one for the lanthanoid elements in the solid state. This is advantageous because, when one element has more than one stable oxidation state, more than one stoichiometry is possible which, in turn, could lead to a complicated band structure [15]. Some lanthanoid elements are also stable in the oxidation state +2 (Sm, Eu, Tb, and Yb), and others in the oxidation state +4 (Ce, Pr, Tb) [16, 17]. Two issues of major concern in microelectronics are the dielectric constant ( $\kappa$ ) and the energy gap ( $E_g$ ).