## INVESTIGATION OF HIGH-K DIELECTRIC FILMS INCORPORATED WITH LANTHANUM AND THEIR APPLICATION IN FLASH MEMORY DEVICES

HE WEI

### NATIONAL UNIVERSITY OF SINGAPORE

### INVESTIGATION OF HIGH-K DIELECTRIC FILMS INCORPORATED WITH LANTHANUM AND THEIR APPLICATION IN FLASH MEMORY DEVICES

He Wei

(B. Eng., Harbin Institute of Technology)

### A THESIS SUBMITTED FOR THE DEGREE OF

### **DOCTOR OF PHILOSOPHY**

### DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

### Abstract

The SONOS-type of flash memory is one of the promising candidates to replace the conventional floating-gate type flash memory to enable continued memory device down-sizing. For a typical SONOS-type flash memory, there is a tradeoff between data retention and operation speeds. In order to break this tradeoff,  $Al_2O_3$  as a blocking oxide has been proposed and exhibits promising results. However, the permittivity of  $Al_2O_3$  is not high (only around 9) and even higher permittivity dielectrics, such as LaAlO<sub>x</sub> and HfLaO<sub>x</sub>, were investigated here to further improve the memory performance.

The lanthanum-incorporated dielectrics (LaAlO<sub>x</sub> and HfLaO<sub>x</sub>) were deposited using the atomic layer deposition (ALD) method at 300°C. The enhancement of deposition rate of La<sub>2</sub>O<sub>3</sub> was observed when co-introducing the Hf or Al precursor into the process chamber to form HfLaO<sub>x</sub> or LaAlO<sub>x</sub>, respectively. Overall, the ALD processes of both HfLaO<sub>x</sub> and LaAlO<sub>x</sub> showed good self-limiting behavior, good film uniformity, low carbon impurity and a strictly linear relationship between the film thickness and deposition cycles, indicating good ALD characteristics.

Both ALD LaAlO<sub>x</sub> and HfLaO<sub>x</sub> layers exhibited wide energy band gap and relatively large conduction band offset. LaAlO<sub>x</sub> films with a higher La percentage showed higher permittivity. The permittivity of amorphous LaAlO<sub>x</sub> films with 46% La was around 18 and these films could stand annealing temperature up to 850°C. In

contrast, at low temperatures (~ 500°C), HfLaO<sub>x</sub> with 8 at.% La would crystallize to a cubic-like phase and this phase has a much greater permittivity (~ 38) than that of amorphous or monoclinic phases (~ 20). This increase in permittivity resulted in a significant improvement in the overall leakage current. Moreover, the permittivities and leakage currents are dependent on annealing temperatures.

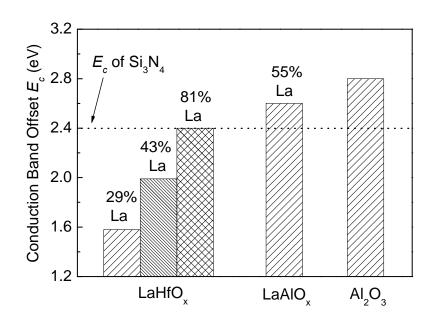

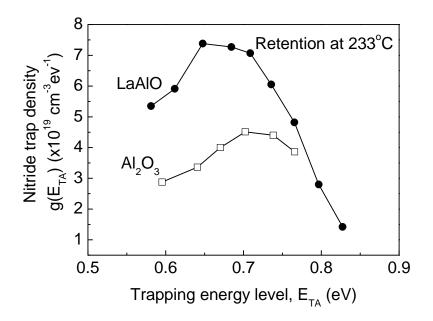

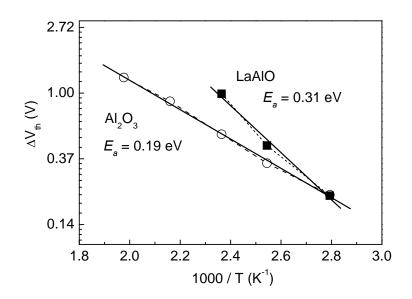

Both LaAlO<sub>x</sub> and HfLaO<sub>x</sub> were used as blocking oxides in nitride-based SONOS-type flash memories. In comparison with memory cells using Al<sub>2</sub>O<sub>3</sub> blocking oxide, those with LaAlO<sub>x</sub> or HfLaO<sub>x</sub> blocking oxide exhibited improved memory characteristics, such as faster operation speeds, wider saturation window, and better time-to-breakdown ( $t_{BD}$ ) reliability. Furthermore, memory cells with LaAlO<sub>x</sub> blocking oxide showed improved retention performance below 120°C, which is similar to normal memory working temperature. On the other hand, memory cells using HfLaO<sub>x</sub> blocking oxide showed degraded retention performance due to their relatively low conduction band offset. By compiling above data retention results, it is found that the conduction band offset of blocking oxide over Si is required to be greater than 2.4 eV. However, few dielectrics can satisfy such requirement. In addition, by using the modified Yang's model, the trapping energy depth in nitride films was calculated to be ~ 0.7 eV below the nitride conduction band edge.

Overall,  $LaAlO_x$  is a promising candidate as a blocking oxide to further boost the memory performances. And  $HfLaO_x$ , due to its improved permittivity under cubic phase, may be useful in other applications, e.g. in DRAMs.

### Acknowledgements

# Many colleagues and individuals who have directly or indirectly assisted in the preparation of this manuscript are much appreciated.

First of all, I would like to express my sincere gratitude to my thesis advisors, namely, Prof. Daniel Chan and Prof. Byung-jin Cho for their invaluable guidance, wisdom, and kindness in instructing and encouraging me during my postgraduate study at NUS. I will definitely benefit from the experience and knowledge I have gained from them throughout my life. I am especially grateful to Prof. Cho who provided me an opportunity to join Silicon Nano Device Lab and start the postgraduate study; secondly for his patience and painstaking efforts devoted to my research as well as his kindness and understanding which accompanied me over the last four years. Besides, I am also grateful to Prof. Chan's, who guided me through the Ph.D study, offered me a position to continue the study and spent a lot of time in correcting the thesis. Hence, my best wishes will go to Prof. Cho and Prof. Chan as I am deeply appreciated for their generous help.

Besides, I have had a great pleasure of collaborating with numerous talented graduate students and colleagues over the past four years. Firstly, I would like to give my thanks to my colleagues in Prof. Cho's group, including Dr. Kim Sun-Jung, Dr. Hwang Wansik, Dr. Shen Chen, Ms. Zhang Lu, and Ms. Pu Ji for their useful discussions and kind assistances. Secondly, many thanks also go to Mr. Zhang Gang, Mr. Sun Zhiqiang, Mr. Ma Fajun and other technical staffs (Mr. Yong YuFoo, Mr. Lau BoonTeck, Mr. Tang Patrick, and O Yan Wai Linn) for their knowledge and experiences which had benefited me, as well as the long lasting friendship. I would also like to extend my appreciation to all NUS members including professors (such as Prof. Samudra Ganesh, Dr. Zhu Chunxiang, Dr. Yeo Yee-Chia, Dr. Yuan Zeliang, etc.), non-academic staffs and graduate students for the terrific academic environment, as well as the technical staffs in IMRE who have assisted me in material analysis, such as Dr. Zhang Zheng, Lim Poh Chong, Doreen Lai Mei-Ying, etc.

Last but not least, my deepest love and gratitude will go to my family, especially to my wife and my parents for their self-giving love, patience and support throughout my life.

He Wei Nov 2009

### **Table of Contents**

| Abstract                                                                                           | I             |

|----------------------------------------------------------------------------------------------------|---------------|

| Acknowledgements                                                                                   | III           |

| Table of Contents                                                                                  | V             |

| List of Tables                                                                                     | .VIII         |

| List of Figures                                                                                    | IX            |

| List of Symbols and Abbreviations                                                                  | .XVI          |

| Chapter 1 Introduction of Flash Memory and High-K Dielectrics                                      | 1             |

| 1.1 Overview                                                                                       | 1             |

| 1.2 Nitride-based SONOS-type Flash Memory                                                          | 4             |

| 1.2.1 Overview of Non-volatile Memory Candidates                                                   | 4             |

| 1.2.2 A Brief Review of SONOS-type Flash Memory                                                    | 8             |

| 1.2.3 Using High-к Dielectric to Improve Memory Performance                                        | 11            |

| 1.3 Lanthanum-incorporated High-к Dielectrics                                                      | 13            |

| 1.3.1 Dielectric Parameters for the Selection of High-κ Thin Film                                  | 13            |

| 1.3.2 Lanthanum-incorporated High- $\kappa$ Dielectrics: LaAlO <sub>x</sub> and HfLaO <sub>x</sub> | 17            |

| 1.3.3 Current Developments of LaAlOx and HfLaOx Dielectrics                                        | 19            |

| 1.3.4 Using ALD LaAlO <sub>x</sub> and HfLaO <sub>x</sub> Dielectrics in Memory Application        | 23            |

| 1.4 Outline of the Thesis                                                                          | 25            |

| References                                                                                         | 26            |

| Chapter 2 High-K Dielectrics Engineering by Atomic Layer Deposition (ALI                           | <b>D)</b> .35 |

| 2.1 Introduction                                                                                   | 35            |

| 2.1.2 Introduction of ALD Principles                                                               | 36            |

| 2.3 Experiment Conditions                                                                                                                                                                                                                                                                                                                          | 41                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 2.4 ALD Process of Lanthanum-incorporated Dielectrics                                                                                                                                                                                                                                                                                              | 41                                          |

| 2.5 Characterization of Deposited Film                                                                                                                                                                                                                                                                                                             | 53                                          |

| 2.6 Summary                                                                                                                                                                                                                                                                                                                                        | 57                                          |

| References                                                                                                                                                                                                                                                                                                                                         | 57                                          |

| Chapter 3 Characteristics of Lanthanum-incorporated Dielectrics                                                                                                                                                                                                                                                                                    | 61                                          |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                   | 61                                          |

| 3.2 Experiments                                                                                                                                                                                                                                                                                                                                    | 62                                          |

| 3.3 Physical Characteristics of HfLaO <sub>x</sub> and LaAlO <sub>x</sub> Films                                                                                                                                                                                                                                                                    | 66                                          |

| 3.4 Electrical Characteristics of HfLaO <sub>x</sub> Films                                                                                                                                                                                                                                                                                         | 75                                          |

| 3.5 Electrical Characteristics of LaAlO <sub>x</sub> Films                                                                                                                                                                                                                                                                                         | 86                                          |

| 3.6 Summary                                                                                                                                                                                                                                                                                                                                        | 90                                          |

| References                                                                                                                                                                                                                                                                                                                                         | 91                                          |

| Chapter 4 Evaluation of SONOS-type Memory Cells with                                                                                                                                                                                                                                                                                               | 05                                          |

| <b>Aanthanum-incorporated Dielectrics as Blocking Oxide</b> 4.1 Introduction                                                                                                                                                                                                                                                                       |                                             |

| 4.1.1 Architecture of Flash Memory                                                                                                                                                                                                                                                                                                                 |                                             |

|                                                                                                                                                                                                                                                                                                                                                    |                                             |

| •                                                                                                                                                                                                                                                                                                                                                  | 96                                          |

| 4.1.2 Basic Operation of Memory Cell                                                                                                                                                                                                                                                                                                               | 96<br>98                                    |

| <ul><li>4.1.2 Basic Operation of Memory Cell</li><li>4.1.3 Endurance and Data Retention</li></ul>                                                                                                                                                                                                                                                  | 96<br>98<br>100                             |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li></ul>                                                                                                                                                                                                      | 96<br>                                      |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li></ul>                                                                                                                                                                                                      | 96<br>                                      |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li></ul>                                                                                                                                                                                                      | 96<br>                                      |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li></ul>                                                                                                                                                                                                      | 96<br>98<br>100<br>102<br>105<br>107<br>107 |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li> <li>4.3 Experiments</li> <li>4.4 Results and Discussion</li> <li>4.4.1 LaAlO Memory Cells</li> <li>4.4.2 HfLaO Memory Cells</li> </ul>                                                                    | 96<br>                                      |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li> <li>4.3 Experiments .</li> <li>4.4 Results and Discussion .</li> <li>4.4.1 LaAlO Memory Cells .</li> <li>4.4.2 HfLaO Memory Cells .</li> <li>4.5 Charge Trapping Energy and Activation Energy.</li> </ul> |                                             |

| <ul> <li>4.1.2 Basic Operation of Memory Cell.</li> <li>4.1.3 Endurance and Data Retention.</li> <li>4.2 Theoretical Considerations</li> <li>4.3 Experiments .</li> <li>4.4 Results and Discussion .</li> <li>4.4.1 LaAlO Memory Cells .</li> <li>4.4.2 HfLaO Memory Cells .</li> </ul>                                                            | 96<br>                                      |

| Chapter 5 Conclusion and Suggestions                   | 130 |

|--------------------------------------------------------|-----|

| 5.1 Conclusion                                         |     |

| 5.2 Suggestions for Future Work                        |     |

| References                                             | 134 |

| Appendix - List of Publications Related to This Thesis | 135 |

### List of Tables

| Table 1.1 A comparison of the characteristics of the non-volatile memories. The |                 |    |     |            |       |        |         |     |  |

|---------------------------------------------------------------------------------|-----------------|----|-----|------------|-------|--------|---------|-----|--|

|                                                                                 | characteristics | of | the | SONOS-type | flash | memory | combine | the |  |

| parameters for both NOR-type and NAND-type memory cells.                        |                 |    |     |            |       | 5      |         |     |  |

**Table 2.1** Recipes configuration of HfO2, La2O3 and HfLaOx. The unit of the<br/>number in the table is "second".46

## **List of Figures**

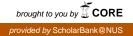

| Fig. | 1.1 | The trend of ever-increasing number of transistors per die in microprocessor and memory products during the past 40 years. This graph shows the device scaling basically follows Moore's Law.                                                                                                                                    | 2  |

|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

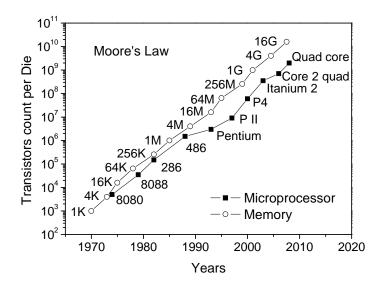

| Fig. | 1.2 | A structure illustration of the floating-gate flash memory. The charges are<br>stored inside the floating gate which is sandwiched between the<br>inter-poly dielectric and bottom oxide.                                                                                                                                        | 3  |

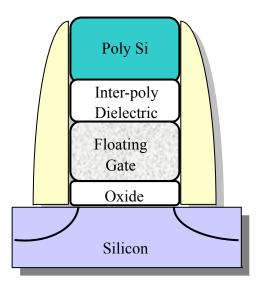

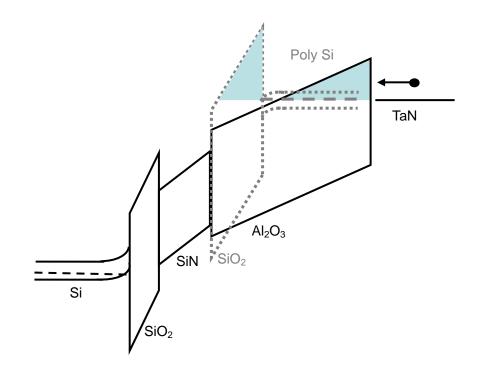

| Fig. | 1.3 | A structure illustration of the nitride-based SONOS-type flash memory.<br>The charges are locally trapped inside the nitride film and immobile.                                                                                                                                                                                  | 6  |

| Fig. | 1.4 | A comparison of the energy band diagram between conventional SONOS<br>memory cell (dashed line) and TANOS memory cell (solid line) under<br>the erase operation. The TANOS memory cell exhibits longer electron<br>tunneling distance, leading to higher programming / erasing speed due to<br>the lower back-tunneling current. | 11 |

| Fig. | 1.5 | An overview of dielectric constant ( $\kappa$ value) versus energy band gap. It implies a general rule of tradeoff between the $\kappa$ value and the energy band gap.                                                                                                                                                           | 15 |

| Fig. | 1.6 | A schematic of conduction band offset ( $\Delta E_c$ ) and valence band offset ( $\Delta E_v$ ) of a dielectric oxide over silicon. Higher $\Delta E_c$ and higher $\Delta E_v$ are desired to achieve the smaller leakage current.                                                                                              | 16 |

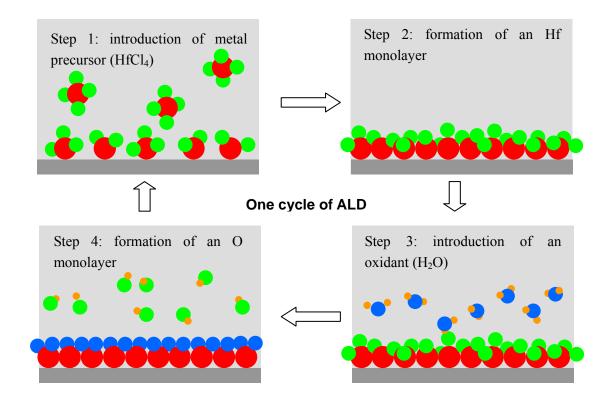

| Fig. | 2.1 | A schematic illustration of an-ALD process cycle. By repeating the ALD cycle, the stoichiometric $HfO_2$ can be deposited.                                                                                                                                                                                                       | 36 |

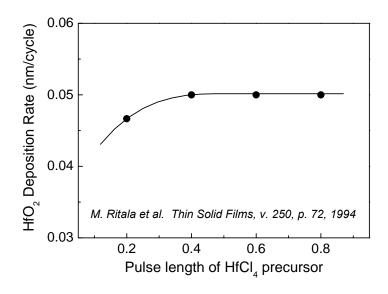

| Fig. | 2.2 | A schematic illustration of self-limiting characteristic using ALD $HfO_2$ as<br>an example. When the pulse length is greater than 0.4 s, the deposition<br>rate is independent of the pulse length, which implies a wide process<br>window to achieve the constant deposition rate.                                             | 38 |

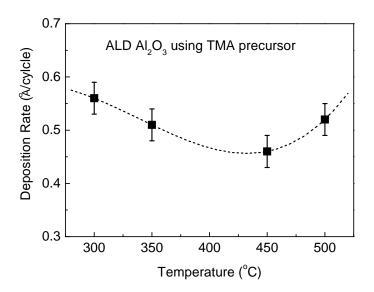

| Fig. | 2.3 | The deposition rate of $Al_2O_3$ as a function of deposition temperatures.<br>The deposition temperature for ALD $Al_2O_3$ is suggested to be below 450°C.                                                                                                                                                                       | 42 |

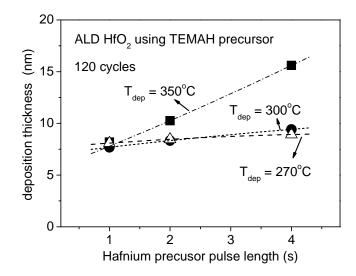

| Fig. | 2.4 | The self-limiting characteristic of $HfO_2$ deposited using $Hf(NEtMe)_4$ precursor under various deposition temperatures. The deposition                                                                                                                                                                                        |    |

temperature is suggested to be below 350°C.

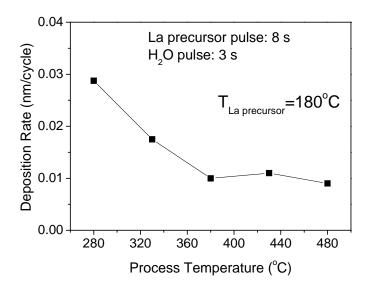

- Fig. 2.5 The deposition rate of La<sub>2</sub>O<sub>3</sub> as a function of deposition temperature. A 100 cycles of deposition was performed during evaluation. It shows that the deposition temperature for La<sub>2</sub>O<sub>3</sub> can be raised up to 480°C.

44

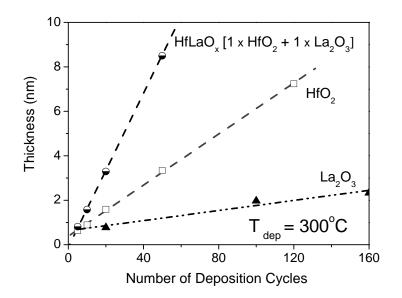

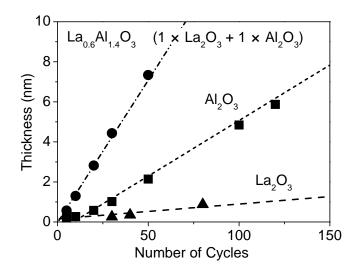

- Fig. 2.6 Thicknesses of La<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and HfLaO<sub>x</sub> as a function of deposition cycles. The pulse length of La precursor, H<sub>2</sub>O, Hf precursor and H<sub>2</sub>O was set to 8 s, 3 s, 1 s and 0.5 s, respectively. The deposition rate of HfLaO<sub>x</sub> is much greater than the sum of the individual deposition rate of HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>, implying a reaction improvement.

45

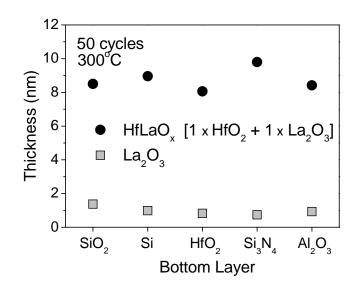

- Fig. 2.7 Comparison of the deposition rate between HfLaO<sub>x</sub> and La<sub>2</sub>O<sub>3</sub> on different seed layers. It shows that the deposition rate enhancement of HfLaO<sub>x</sub> is not related to the contacting substrate materials.

47

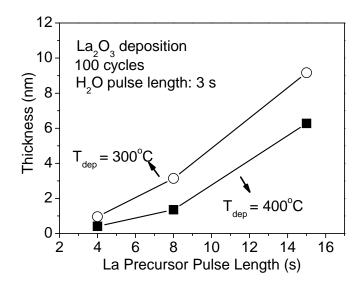

- Fig. 2.8 The deposition rate of La<sub>2</sub>O<sub>3</sub> as a function of La precursor pulse length at 300°C and 400°C, respectively. No self-limiting behavior was observed.

48

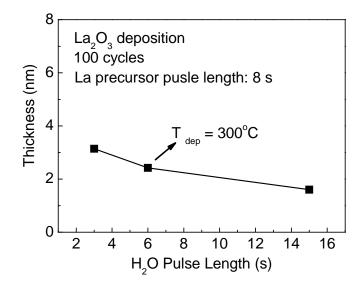

- Fig. 2.9 The deposition rate of La<sub>2</sub>O<sub>3</sub> as a function of H<sub>2</sub>O pulse length, the deposition temperature was set to 300°C. It is abnormal that deposition rate decreased with the increase of H<sub>2</sub>O pulse length.

49

- Fig. 2.10 Thicknesses of La<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub> and LaAlO<sub>x</sub> as a function of deposition cycles. The pulse length of La precursor, H<sub>2</sub>O, Al precursor and H<sub>2</sub>O was set to 8 s, 3 s, 0.2 s and 0.5 s, respectively. The deposition rate enhancement of LaAlO<sub>x</sub> was also observed.

50

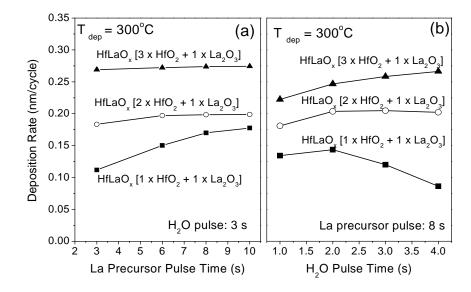

- Fig. 2.11 Self-limiting characteristics of the HfLaO<sub>x</sub> films as a function of (a) La precursor pulse length and (b) H<sub>2</sub>O pulse length. It was found that higher Hf:La pulsing ratio led to better self-limiting behavior.

52

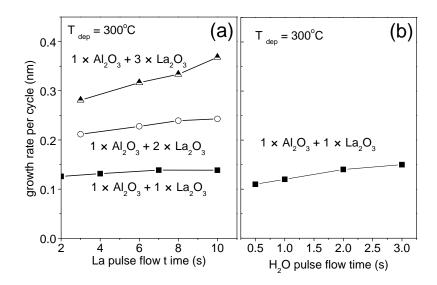

- Fig. 2.12 Self-limiting characteristics of LaAlO<sub>x</sub> as a function of (a) La precursor pulse length and (b) H<sub>2</sub>O pulse length. Higher number of Al:La pulsing ratio led to better self-limiting behavior.

52

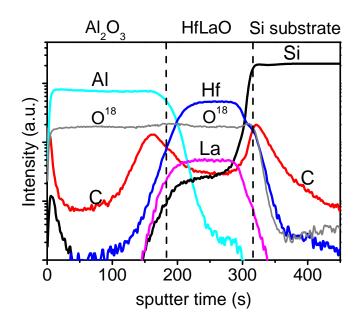

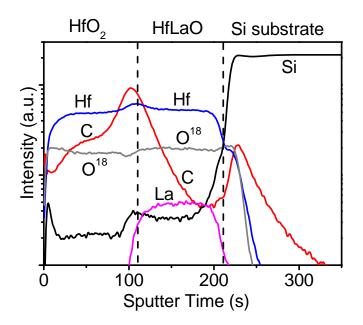

- Fig. 2.13 The depth profile measured by the TOF-SIMS analysis for ALD Al<sub>2</sub>O<sub>3</sub> / HfLaO<sub>x</sub> gate stack. All the curves have been normalized by the intensity of Gallium where Gallium was used as the primary ion source. The parallel lines between Hf and La elements indicated a uniform distribution in vertical direction. The carbon impurity and silicon impurity in HfLaO<sub>x</sub> were detected.

54

- Fig. 2.14 The depth profile measured by the TOF-SIMS method for ALD  $HfO_2$  /

HfLaO<sub>x</sub> gate stack. All the curves have been normalized with the intensity of Gallium. The carbon impurity and silicon impurity in HfLaO<sub>x</sub> films is lower and higher than that of in HfO<sub>2</sub>, respectively. 55

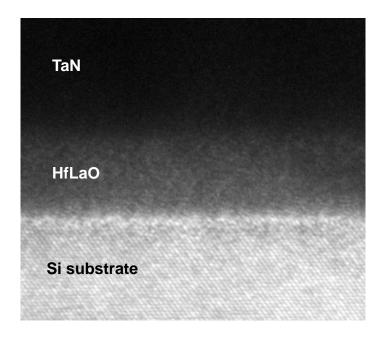

- Fig. 2.15 TEM image of ALD HfLaO<sub>x</sub> film growth at 300°C. An amorphous film with smooth surface was observed. 56

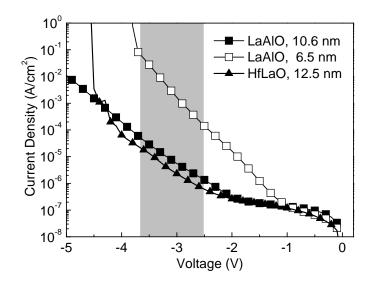

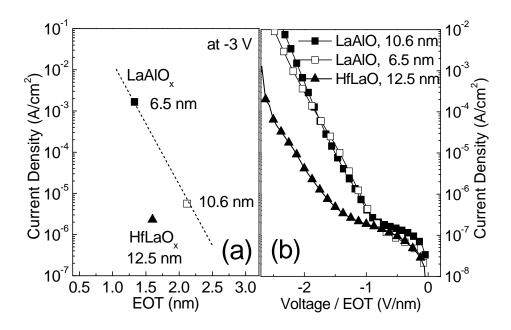

- Fig. 3.1 The leakage current density as a function of voltage (I-V) for LaAlO<sub>x</sub> and 65 HfLaO<sub>x</sub> films.

- Fig. 3.2 A comparison of leakage current between  $LaAlO_x$  and  $HfLaO_x$  using (a) the  $J_{g}$ -EOT method and (b) the EOT normalization method. The EOT normalization method has the advantages of less split requirement for LaAlO<sub>x</sub> and more visual comparison among the dielectrics with large EOT variation. But the x-axis of the EOT normalization method does not have any physical meaning. 65

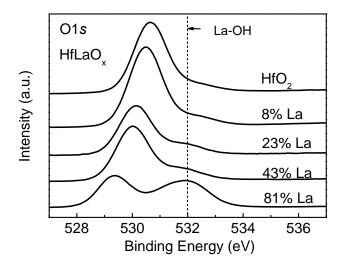

- **Fig. 3.3** The XPS spectra of O 1s core level of  $HfLaO_x$  films with various La percentages. The La-OH bond is more obvious for the films with higher La percentage. 66

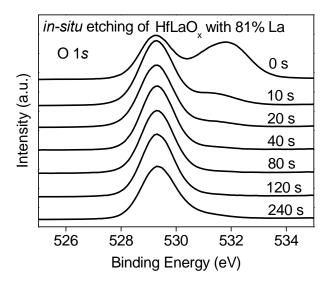

- Fig. 3.4 The XPS spectra of O 1s core level for 81% La-HfLaO<sub>x</sub> with Ar *in-situ* etching. After 20 s in-situ etching, the La-OH bond cannot be detected. 67

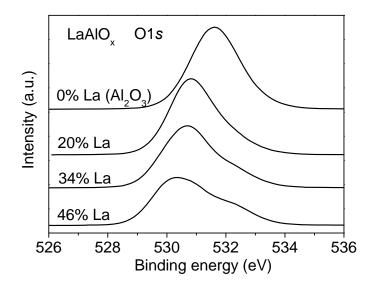

- Fig. 3.5 The XPS spectra of O 1s core level of LaAlO<sub>x</sub> films. The La-OH bond located at 531.6 eV is more obvious for the films with higher La **68** percentage.

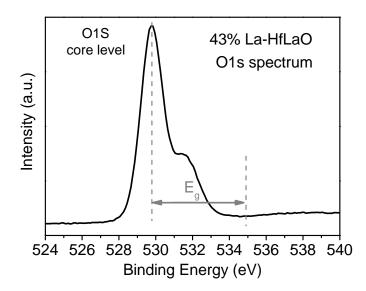

- Fig. 3.6 An illustration of energy band gap abstraction in O 1s spectrum. The energy band gap  $(E_g)$  refers to the difference between the O 1s core level and the onset of spectra loss. 69

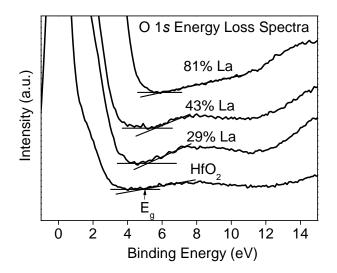

- Fig. 3.7 O 1s energy-loss spectra for 15-nm HfLaO<sub>x</sub> films with different La percentages. The intercept points indicate the values of energy band gap  $(E_g)$ . HfLaO<sub>x</sub> films with higher La percentage exhibit wider energy band 70 gap.

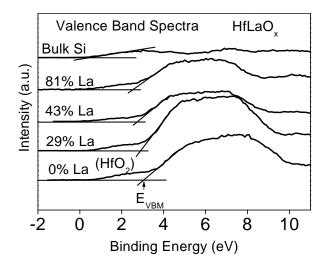

- **Fig. 3.8** The valence band spectra of bulk Si substrate and HfLaO<sub>x</sub> films (3-nm). HfLaO<sub>x</sub> films with higher La percentage shows smaller valence band offset over Si.

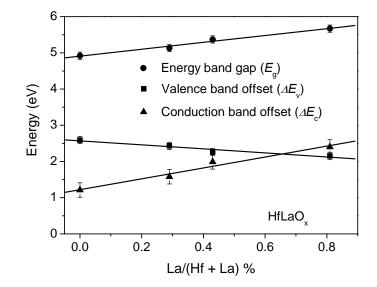

- **Fig. 3.9** A summary of energy band gap  $(E_g)$ , valence band offset  $(\Delta E_v)$  and conduction band offset ( $\Delta E_c$ ) of HfLaO<sub>x</sub> films as functions of La percentage. With incorporation of La into HfO<sub>2</sub>, the  $E_g$  and  $\Delta E_c$  are

improved.

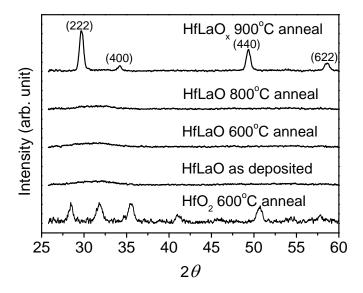

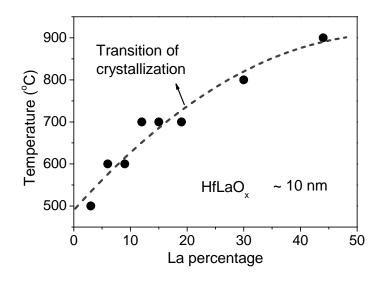

- Fig. 3.10 The XRD spectra of 18-nm HfLaO<sub>x</sub> and HfO<sub>2</sub> films annealed at various temperatures. The atomic ratio of La/(La + Hf) was around 44%. The cubic phase spectra of HfLaO<sub>x</sub> (top curve) are observed that clearly distinguished from the monoclinic phase of HfO<sub>2</sub> (bottom curve). 73

- Fig. 3.11 The onset of the crystallization temperature as a function of La percentage for HfLaO<sub>x</sub> films. The HfLaO<sub>x</sub> films with higher La percentage exhibits higher crystallization temperature.

74

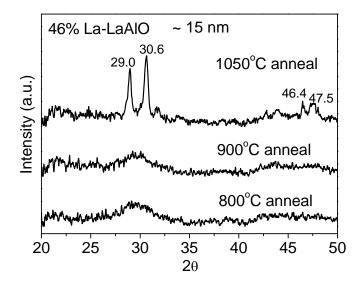

- Fig. 3.12 The XRD spectra of LaAlO<sub>x</sub> films annealed at various temperatures. The spectra peaks of crystallized LaAlO<sub>x</sub> film cannot fit to cubic-LaAlO<sub>3</sub> peaks but to monoclinic- La<sub>2</sub>O<sub>3</sub> peaks, indicating a phase separation.

75

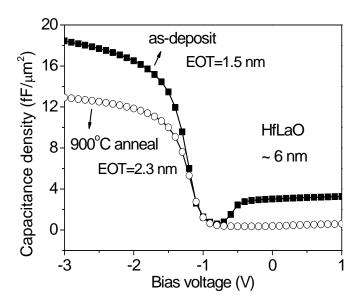

- Fig. 3.13 The C-V characteristics of HfLaO<sub>x</sub> on p-type silicon substrate. A sharp transition at the depletion region is observed, implying a high quality interface.

76

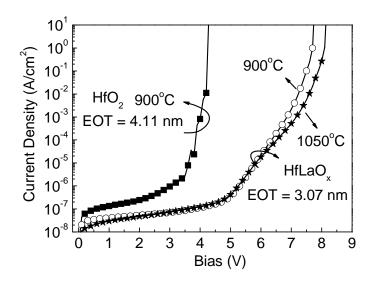

- Fig. 3.14 Leakage current comparison between 29% La-HfLaO<sub>x</sub> films and HfO<sub>2</sub> film in MIM structures. The devices were annealed in a N<sub>2</sub> ambient at 900°C for 30 sec or 1050°C for 10 sec. The leakage currents of HfLaO<sub>x</sub> films did not exhibit any degradation after annealing at high temperatures.

77

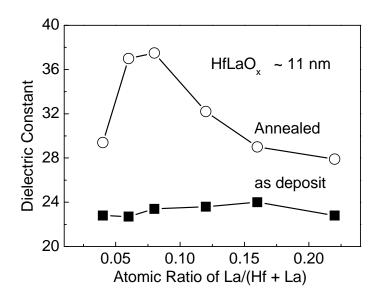

- Fig. 3.15 Comparison of dielectric constant before and after anneals for  $HfLaO_x$  films with different La percentages. The  $\kappa$  values of  $HfLaO_x$  films increased dramatically after crystallization. The highest  $\kappa$  values can be as high as 38 when La percentage is in the range of 6% to 8% in  $HfLaO_x$  films.

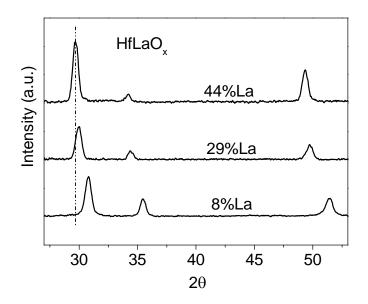

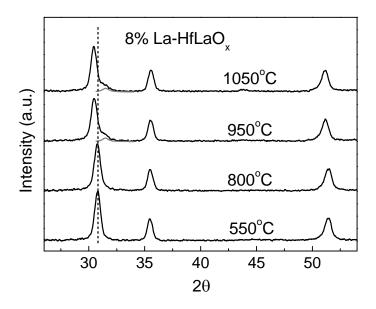

- Fig. 3.16 The XRD spectra for crystallized HfLaO<sub>x</sub> films with various La percentages. With the increase of La percentage, the peaks of cubic phase shift toward lower incident angle, implying an increase of cubic crystal volume.

80

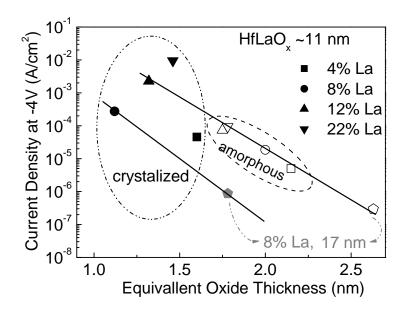

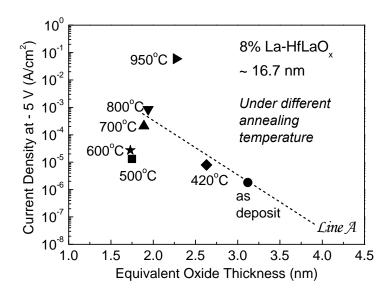

- Fig. 3.17 The leakage current comparison of  $HfLaO_x$  films with different La percentages. All the data points of leakage current were extracted at 4 volts. Another leakage current of 17-nm-thick 8% La-HfLaO<sub>x</sub> film was also shown here to draw the reference line. Among all the films, crystallized 8% La-HfLaO<sub>x</sub> films exhibit the lowest leakage currents.

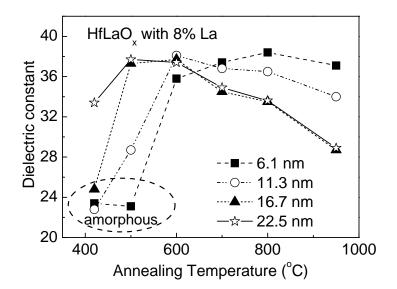

- Fig. 3.18 The dielectric constant of 8% La-HfLaO<sub>x</sub> films with various thicknesses

72

78

as a function of annealing temperatures. When the annealing temperature was far above the onset of the crystallization temperature, the  $\kappa$  values decreased.

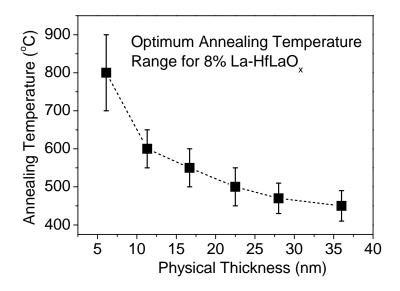

- Fig. 3.19 A summary of annealing temperature needed to obtain the optimum film property for 8% La-HfLaO<sub>x</sub> films as a function of physical thicknesses. HfLaO<sub>x</sub> with thinner physical thickness require higher annealing temperatures. 83

- Fig. 3.20 The XRD spectra for 8% La-HfLaO<sub>x</sub> films with annealing at different temperatures. The main peak of cubic phase shifts to lower incident and a new small peak of monoclinic phase appear besides this main peak. 84

- Fig. 3.21 Comparison of leakage currents of 8% La-HfLaO<sub>x</sub> films under different annealing temperatures. All the data points of leakage current are extracted -5 volts. The dashed line (Line A) is a reference line for the amorphous  $HfLaO_x$  films (under as-deposited condition). When annealing temperature is 500°C or 600°C, the 8% La-HfLaOx films exhibits the lowest leakage current. 85

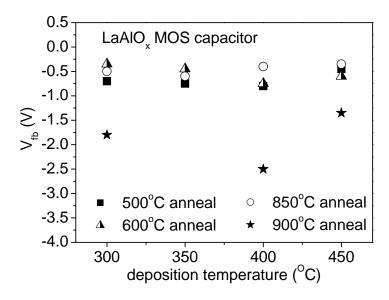

- **Fig. 3.22** The flat band voltage  $(V_{fb})$  distribution for LaAlO<sub>x</sub> films deposited at various temperatures as a function of annealing temperatures. LaAlO<sub>x</sub> films with 900°C anneal exhibit abnormal flat band voltage shift. 87

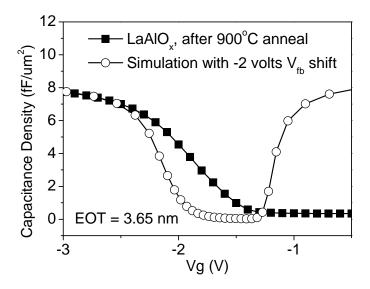

- Fig. 3.23 A comparison of the C-V curves between 40% La-LaAlO<sub>x</sub> film and a simulated curve. The gentle slope of C-V curve at the depletion region indicates a large amount of traps at the silicon interface. 87

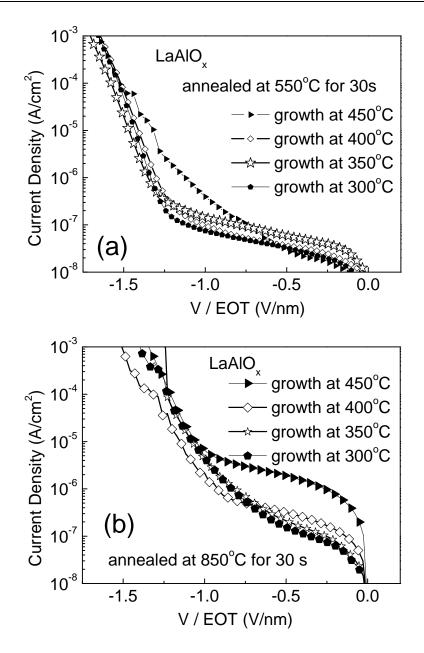

- Fig. 3.24 Leakage current comparison for  $LaAlO_x$  films deposited at various temperatures. All films were annealed at (a) 550°C for 30s and (b) 850°C for 30s under one atmospheric pressure in N<sub>2</sub> ambient. The LaAlO<sub>x</sub> films deposited at 450°C exhibits a degraded leakage current, indicating the deposition temperature should be below 450°C. 89

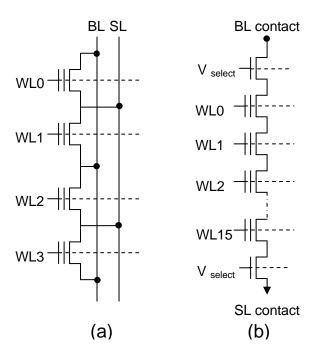

- Fig. 4.1 A schematic illustration of typical circuit diagram of (a) NOR-type flash memory and (b) NAND-type flash memory. Here, BL, SL and WL refers to bit line, source line and word line, respectively. Because of the series connection, NAND flash memory offers the highest integration density thus lowest cost-per-bit.

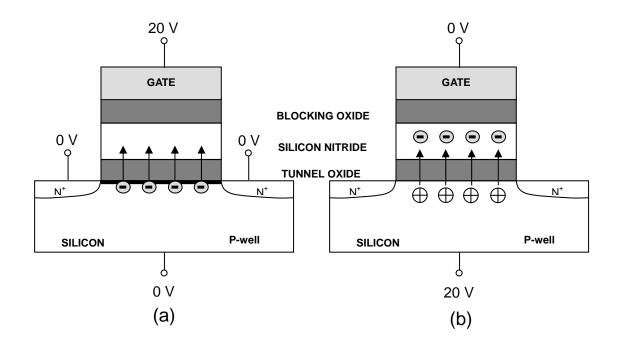

- Fig. 4.2 A schematic illustration of NAND-type SONOS cell under (a) program and (b) erasure by Fowler-Nordheim tunneling. **98**

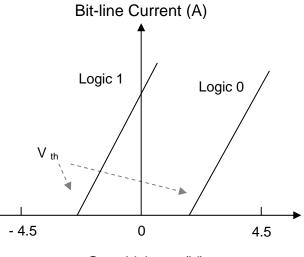

Fig. 4.3 An illustration of reading operation for NAND memory cell. Here, the bit

82

line of the memory string is connected to a sense amplifier. By sensing the bit-line current, the status of memory cells can be detected. **100**

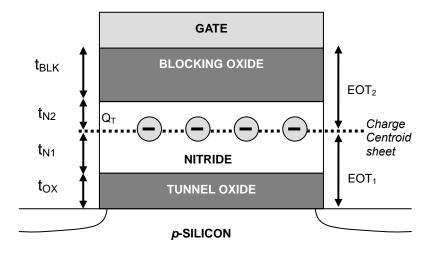

- Fig. 4.4 A cross-section of SONOS structure with assumption of a sheet charge centroid in nitride;  $t_{OX}$ ,  $t_{NI}$ ,  $t_{N2}$  and  $t_{BLK}$  are the physical thickness of tunnel oxide, distance from charge centroid to tunnel oxide, distance from charge centroid to blocking oxide and physical thickness of locking oxide, respectively. The assumption of charge centroid sheet greatly simplifies the analysis of electric field. 102

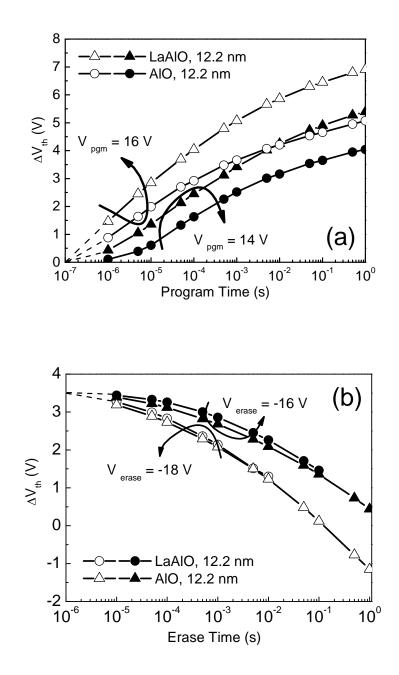

- Fig. 4.5 A comparison of (a) Programming and (b) erasing characteristics between LaAlO and AlO memory cells. During the erasure, the initial  $V_{th}$  was set to 3.5 V. Compared with AlO memory cells, LaAlO memory cells showed faster programming speed and better performance of breakdown.

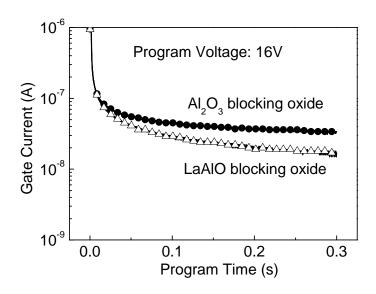

- Fig. 4.6 A comparison of gate leakage current of memory cells during program. The lower current of LaAlO memory cell implies faster programming speed. 109

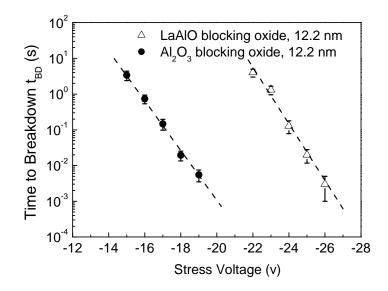

- Fig. 4.7 A comparison of time-to-breakdown (hard breakdown) between LaAlO and AlO memory cells under a constant voltage stress. Memory cells with LaAlO<sub>x</sub> as blocking oxide exhibited much improved time-to-breakdown performance.

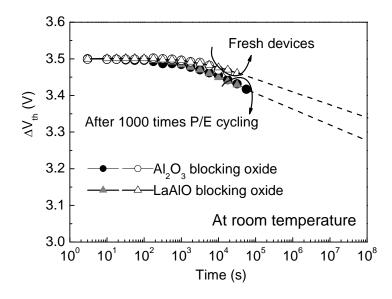

- Fig. 4.8 Comparisons of data retention between LaAlO and AlO memory cells for both fresh and cycled devices. LaAlO and AlO memory cells showed almost the same retention performance at room temperature.

110

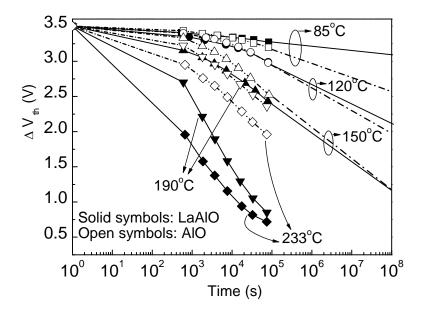

- Fig. 4.9 Comparisons of data retention between LaAlO and AlO memory cells at various elevated temperatures. LaAlO memory cells showed improved data retention when baking temperature was below 150°C but degraded retention performance at even higher baking temperatures.

111

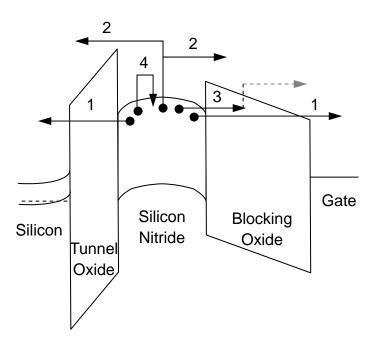

- Fig. 4.10 An illustration of band diagram of a SONOS memory cell in excess electrons state under the retention mode. The electron loss mechanism is illustrated as: 1) trap-to-band tunneling, 2) thermal emission, 3) trap-to-trap tunneling, 4) Poole-Frenkel emission (including trap redistribution). Among them, thermal emission and trap-to-band tunneling are believed to be the dominant mechanisms of charge loss. 112

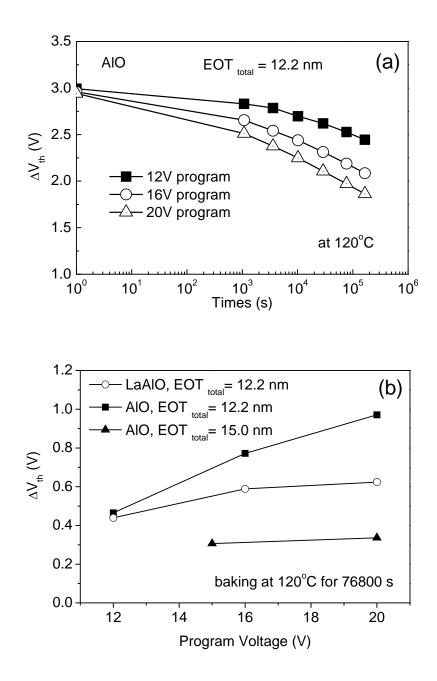

- Fig. 4.11 (a) Dependence of AlO data retention on program voltage, (b) comparisons of  $V_{th}$  shift for AlO and LaAlO memory cells under various

XIV

program voltages. The baking temperature was set to 120°C during retention measurement. It shows that the higher program voltage would result in the worse data retention. 114

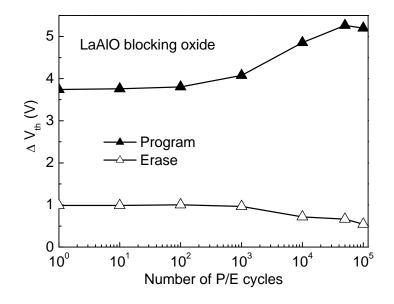

- Fig. 4.12 Endurance of LaAlO memory cell with P/E cycles up to 100,000 times. The wider memory window was observed as the number of P/E cycles increased.116

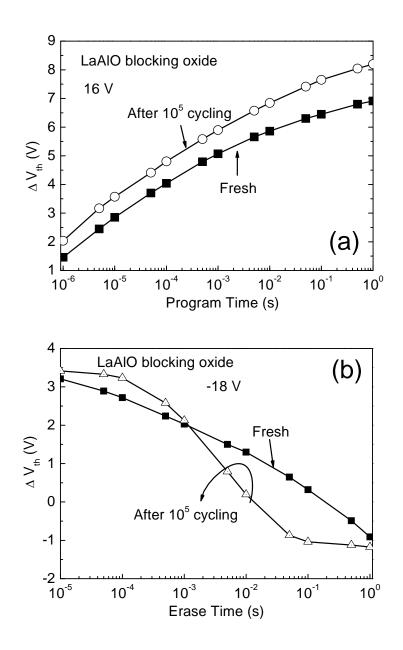

- Fig. 4.13 A comparison of (a) programming and (b) erasing characteristics between the fresh and 100,000 times P/E cycled LaAlO memory cells. 117

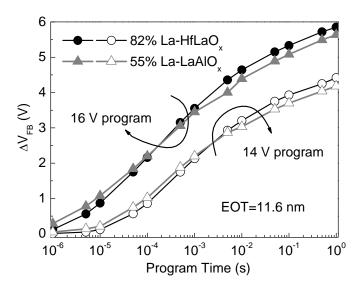

- Fig. 4.14 A comparison of programming characteristics between HfLaO and LaAlO memory cells. The similar programming characteristics were observed.

118

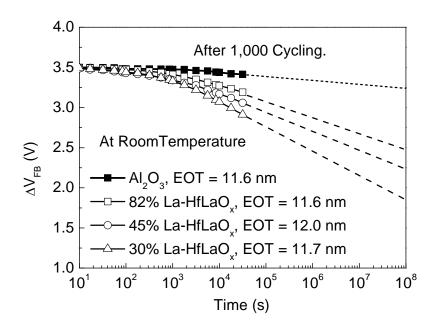

- Fig. 4.15 Comparisons of data retention of HfLaO and AlO memory cells at room temperature. HfLaO<sub>x</sub> with higher La percentage exhibited worse data retention.

- Fig. 4.16 Comparisons of conduction band edge of Al2O3, HfLaOx and LaAlOxfilms.120

- Fig. 4.17 Extracted value of nitride trapping density as a function of the trapping energy based on the data retentions of LaAlO and AlO memory cells at high temperatures. It shows that the trapping depth in nitride film is 0.6 to 0.75 eV below the nitride conduction band edge.

124

- Fig. 4.18 Arrhenius plot of data retention as a function of temperatures for LaAlO and AlO memory cells. LaAlO memory cells exhibited greater activation energy.

126

# List of Symbols and Abbreviations

| $E_c$             | Conduction band edge                              |

|-------------------|---------------------------------------------------|

| $E_g$             | Energy band gap                                   |

| $E_{TA}$          | Trapping Energy                                   |

| $E_{v}$           | Valence band edge                                 |

| $J_g$             | Current density                                   |

| k                 | Dielectric constant                               |

| t <sub>eq</sub>   | Equivalent oxide thickness                        |

| $T_{ox}$          | Tunnel oxide                                      |

| $V_{fb}$          | Flat-band voltage                                 |

| $V_g$             | Gate voltage                                      |

| V <sub>th</sub>   | Threshold voltage                                 |

| $\mathcal{E}_{0}$ | Permittivity in vacuum                            |

| ALD               | Atomic layer deposition                           |

| CVD               | Chemical vapor deposition                         |

| C-V               | Capacitance-voltage                               |

| EOT               | Equivalent oxide thickness                        |

| FGA               | Forming gas anneal                                |

| FN tunneling      | Fowler-Nordheim tunneling                         |

| HRTEM             | High-resolution transmission electron microscopic |

| I-V               | Current-voltage                                   |

| MBE               | Molecular beam epitaxy                            |

| MIM               | Metal insulator metal                             |

| MOCVD             | Metal-organic chemical vapor deposition           |

| MOS               | Metal oxide semiconductor                         |

| ONO               | Oxide-nitride-oxide                               |

| PLD   | Pulse laser deposition                          |

|-------|-------------------------------------------------|

| PVD   | Physical vapor deposition                       |

| RTP   | Rapid thermal anneal                            |

| SONOS | Poly silicon-oxide-nitride-oxide-silicon memory |

| TMA   | Trimethylaluminum                               |

| XPS   | X-ray photoelectron spectroscopic               |

| XRD   | X-ray diffraction                               |

# Chapter 1 Introduction of Flash Memory and High-K Dielectrics

### **1.1 Overview**

During the last decade, memory products have become a main growth engine for the semiconductor businesses owing to the huge demands from computers, mobile phones, digital cameras, and MP3 music players, etc [1]. The price of a bit of memory is ever-decreasing and the performance is ever-increasing. All of these successful achievements rely on the "scaling technology" which is primarily based on the shrinking of physical dimension of the MOSFET (metal-oxide-semiconductor field effect transistor). One of the great advantages of this "scaling technology" is that the device structures and memory structures undergo few changes during the scaling. The little changes in structures facilitate the integration of more transistors or memory cells in one chip, thus effectively enabling lower power consumption and lower manufacturing cost per die. This "scaling technology" follows the famous Moore's Law, which predicted a constant growth rate of chip complexity (double the density every 3 years) in 1965 [2]. Moore's prediction has been realized over the past 40 years in both memory and microprocessor products, as shown in Fig 1.1. The memory density has increased at an amazing speed and the number of memory cells per die doubled nearly every year, which is even greater than the prediction of Moore's Law.

**Fig. 1.1** The trend of ever-increasing number of transistors per die in microprocessor and memory products during the past 40 years [1]. This graph shows the device scaling basically follows Moore's Law.

Generally, memory products are divided into two branches, volatile memory and non-volatile memory. The volatile memory, such as SRAM (static random access memory) or DRAM (dynamic random access memory), loses the data contents when the power supply is turned off [3]. On the contrary, the non-volatile memory, such as EPROM (electrically programmable ROM), EEPROM (electrically erasable programmable ROM), or flash can keep the data content for a long duration even without the power supply [3]. Among the non-volatile memories, flash memory, a special EEPROM where the entire chip or an array is erased simultaneously, occupies the majority of market share due to its attractive compromise between cost and performance. In other words, the flash memory has the capability of electrical program and electrical erasure while using the smallest cell size [4].

At present, flash memory utilizes electron charges stored in a floating gate to

accomplish non-volatile data storage [4]. The floating gate is usually made of polysilicon (polycrystalline silicon) and is sandwiched by dielectric layers. The bottom layer adjacent to the silicon substrate is called tunnel oxide. The upper layer adjacent to the ploysilicon control gate is called inter-poly dielectric (IPD) [4]. A cross-sectional view of floating-gate type flash memory is illustrated in Fig 1.2. The charges stored inside the floating gate determine the threshold voltage, and thus impacts the source-to-drain current. By sensing the source-to-drain current, the memory status of the device can be detected [4].

**Fig. 1.2** A structure illustration of the floating-gate flash memory. The charges are stored inside the floating gate which is sandwiched between the inter-poly dielectric and bottom oxide.

Floating-gate type flash memory has been successfully developed during the last two decades [1]. However, it is facing severe challenges as the semiconductor industry enters the 45-nm technology node. Besides the common challenges faced by CMOS transistors (such as nano-dimension patterning, strong short channel effect, and wide spread-out of process variation, etc.), floating-gate type flash memory also faces other special challenges. First, both tunnel oxide  $(T_{ox})$  and inter-poly dielectric (IPD), using conventional SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> films, have reached their thickness scaling limit of 8 nm and 12 nm, respectively [4, 5]. This requires the introduction of high  $\kappa$ dielectrics to continue the scaling with decreased leakage current and maintain a reasonable coupling ratio ( $\sim 0.7$ ) of control-gate (CG) to floating-gate (FG) [5]. However, the introduction of high  $\kappa$  dielectrics may cause reliability issues [5]. The second problem is the strong cell-to-cell interference due to the scaling-down of the distance between floating gates, which also causes a concern of reliability [6]. Lastly, the most fundamental issue in floating-gate type flash memory is the significant reduction in the electron numbers during further scaling. For 30-nm gate length devices, the electron number is expected to be less than 100 for a threshold shift of 6 V. In order to achieve the 10-years data retention, a maximum of 10 electrons are allowed being loss within 10 years. Such low electron loss tolerance has set a big challenge for better achievement of data retention and endurance [1, 6-8]. In summary, all these challenges imply that it is difficult to continue the scaling of floating-gate type flash memory without performance degradation, thus a new type of non-volatile memory is needed.

#### **1.2 Nitride-based SONOS-type Flash Memory**

#### 1.2.1 Overview of Non-volatile Memory Candidates

To replace the floating-gate type flash memory, several types of non-volatile

memories have been proposed, such as nitride-based poly silicon-oxide-nitrideoxide-silicon (SONOS-type) flash memory, phase-change random access memory (PCRAM), ferroelectric random access memory (FeRAM), magnetic random access memory (MRAM), etc [5]. The characteristics of non-volatile memory candidates are summarized in Table 1.1.

|                                    | SONOS flash                                      | FeRAM                    | MRAM                                                | PCRAM                                |

|------------------------------------|--------------------------------------------------|--------------------------|-----------------------------------------------------|--------------------------------------|

|                                    | memory                                           | memory                   | memory                                              | memory                               |

| Operational mechanism              | Electronic charge                                | Polarization             | Magneto-<br>resistance                              | Phase resistance                     |

| Cell size per bit / F <sup>2</sup> | 1~3.3*                                           | 15                       | 20                                                  | 4                                    |

| Program endurance                  | 10 <sup>5</sup>                                  | 10 <sup>14</sup>         | 10 <sup>16</sup>                                    | 10 <sup>10</sup>                     |

| Read                               | Non-destructive                                  | Destructive              | Non-destructive                                     | Non-destructive                      |

| Read voltage                       | 2 V                                              | 1.2 V                    | 3.3 V                                               | 0.4 V                                |

| Program voltage                    | 6~15 V                                           | 1.2 V                    | 3.3 V                                               | 1 V                                  |

| Program speed                      | 1 – 1000 µs                                      | 80 ns                    | 25 ns                                               | <500 ns                              |

| Erase speed                        | 1 – 100 ms                                       | 80 ns                    | 25 ns                                               | <500 ns                              |

| Read speed                         | 60 ns                                            | 80 ns                    | 30 ns                                               | 50 ns                                |

| Block erase                        | Yes                                              | No                       | No                                                  | No                                   |

| New materials                      | No                                               | Yes                      | Yes                                                 | Yes                                  |

| Multi-bit storage                  | Yes                                              | No                       | No                                                  | Yes                                  |

| cost per bit                       | Low / high                                       | High                     | High                                                | Medium                               |

| Retention (years)                  | 10 - 20                                          | 10                       | > 10                                                | > 10                                 |

| Technology issues                  | Endurance;<br>high voltage;<br>gate length scale | Cell size<br>scalability | Write current;<br>disturbance;<br>cell size scaling | Thermal;<br>cross talk;<br>multi-bit |

**Table 1.1** A comparison of the characteristics of the non-volatile memories [3, 5, 9, 10]. The characteristics of the SONOS-type flash memory combine the parameters for both NOR-type and NAND-type memory cells.

Based on the information in Table 1.1, it is obvious that none of the four non-volatile memory candidates succeeds in all characteristics, but all of them have key advancements in at least some of the important areas. MRAM offers the fastest operation speed, the longest "life span" and the highest programming endurance [9]. While PCRAM offers the best scaling capability and the lowest programming/reading voltages [9]. FeRAM has a relatively fast operation speed, low energy consumption and high program-erase endurance [3]. Besides, FeRAM is not a perfect non-volatile memory because it is a destructive read-out technology, so every read is accompanied by a write to restore the data [3]. Compared to others, SONOS-type flash memory possesses several advantages.

**Fig. 1.3** A structure illustration of the nitride-based SONOS-type flash memory. The charges are locally trapped inside the nitride film and immobile.

Firstly, SONOS-type flash memory can achieve the highest chip density because it consists of only one transistor, as shown in Fig. 1.3, thus lower cost per bit [5]. The SONOS memory cell is a simple MOSFET cell, except that a silicon nitride trapping layer is inserted between the dielectrics. In comparison, other types of non-volatile memories consist of more than one transistor. A FeRAM, MRAM or PCRAM cell generally has one transistor and one capacitor, one transistor and one magnetic tunnel junction, or one bipolar junction transistor and one resistor, respectively [10]. Therefore, their processes are more complicated than SONOS-type flash memory. Secondly, SONOS-type flash memory can implement multi-bit-percell storage scheme easily [4]. By controlling the amount of charges stored in nitride trapping layer, four or eight distinct states of threshold voltages can be achieved within a single cell, which corresponds to two-bit-per-cell or three-bit-per-cell memory [7]. The multi-bit storage scheme enhances the memory capacity significantly without increasing process steps, thus reducing the memory cost per bit dramatically. Besides, it is worth to note that PCRAM is also capable of two-bit-per-cell storing scheme but encounters huge challenges in implementing three-bit-per-cell storing scheme [5]. Thirdly, SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> used in SONOS-type flash memory are commonly used in conventional CMOS processes [4]. This enables the fabrication process of SONOS memory compatible with current CMOS processes, and especially suitable for embedded memory applications. In contrast, new materials other non-volatile memories (like  $PbZr_{0.52}Ti_{0.48}O_3$ used in in FeRAM. CoFe/AlO<sub>x</sub>/NiFe in MRAM, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> in PCRAM) are not fully compatible with conventional CMOS processes [3, 9]. Lastly, the capability of block erasure in SONOS-type flash memory makes the entire array to be erased quickly and simultaneously like a flash (so called "flash" memory) [4]. This simultaneous erasure compensates the disadvantage of slow erasing speed of SONOS-type flash memory

and makes it an edge in large-scale data storage application [4].

In addition, compared with conventional floating-gate type flash memory, nitride-based SONOS-type flash memory has an advancement of storing more electrons, making further scaling possible [1]. Furthermore, due to the localized-charge-storing mechanism, the nitride-based SONOS-type flash memory is free from cell-to-cell interference and more tolerant of dielectric defects [6].

In short, all of these advantages make the nitride-based SONOS-type flash memory a strong candidate to replace the conventional floating-gate type flash memory. Of course, SONOS-type flash memory also faces several challenges in data retention and endurance which will be discussed later in this chapter.

#### 1.2.2 A Brief Review of SONOS-type Flash Memory

The poly silicon-oxide-nitride-oxide-silicon (SONOS) memory is a multi-dielectric device consisting of three layers. The middle layer - silicon nitride - acts as trapping layer holding charges. Unlike traditional floating-gate type flash memory, the charges stored in nitride layer are immobile and distributed discretely. These discrete charges are responsible for the threshold voltage shift. In order to retain these charges for long duration and be free from external disturbance, the nitride layer is sandwiched by two oxide layers, as shown in Fig. 1.3. Similarly to floating-gate type flash memory, the bottom oxide layer adjacent to the silicon substrate, called tunnel oxide, permits the transfer of charges from the silicon

substrate to nitride trapping layer by tunneling mechanism [11]. The top oxide layer isolating the gate electrode from nitride layer, called blocking oxide, was introduced in 1980s to allow the further thickness scaling of the nitride layer from 25 nm to 5 nm and allow lower programming voltages [11].

For the traditional nitride-based SONOS memory cells, the tunnel oxide was normally set to 1 to 2 nm to achieve a fast erase speed [12]. However, such thin layer significantly changes leakage due to the direct tunneling mechanism, thereby, resulting in poor data retention over time [1, 13]. On the other hand, if the tunnel oxide is increased to 4 nm to achieve good data retention, the SONOS memory cell will encounter some problems, such as slow erasure and even early erasing saturation leading to smaller operation window [14]. In order to solve this quandary, different methods have been investigated, such as band engineering SONOS (BE-SONOS) [15-17], using high-κ dielectric in blocking oxide layer or trapping layer [14, 17-21], atomic ratio tuning between Si and N in trapping layer [22, 23], etc.

Band engineering SONOS (BE-SONOS), first proposed by H.L. Lue *et al.*, uses triple layers of ultra-thin oxide-nitride-oxide (ONO) to replace single layer tunnel oxide (SiO<sub>2</sub>) [15]. Because of the conduction band offset between oxide and nitride, the ONO tunnel oxide structure allows different tunneling distance under different situation. For example, under the situation of data retention, the charge will tunnel through all three layers before escaping away because of the low electric field on gate stack; on the other hand, under the situation of memory programming or erasing, high electric field results in strong band bending thus short tunneling distance (probably only the single layer). Therefore, both good retention and high operation speed can be easily achieved [15, 24]. Another method named as TANOS (TaN-Al<sub>2</sub>O<sub>3</sub>-nitride-oxide-silicon), proposed by C. H. Lee *et al.*, used a high  $\kappa$  layer of Al<sub>2</sub>O<sub>3</sub> as blocking oxide and high work function TaN as metal gate [21]. The TANOS structure cells have a higher electric field in tunnel oxide, but a lower electric field in blocking oxide compared to conventional SONOS cells, therefore, enabling higher programming speed and lower programming voltages [20, 21]. Similarly, due to the scaling limit of physical thickness of 4 nm for nitride layer [25], some groups used high  $\kappa$  dielectrics (such as HfSiO<sub>x</sub>, HfAlO<sub>x</sub> Al<sub>2</sub>O<sub>3</sub>, HfON or HfO<sub>2</sub>) as trapping layer to achieve higher electric field in tunnel oxide, resulting in higher programming / erasing speed [18, 19, 26-28]. But the trapping mechanism in these new dielectrics is believed to be much different from silicon nitride, thus requiring further investigations Simultaneously, some other groups were still focusing on nitride trapping [18, 26]. layer and have achieved improved data retention by simply varying nitrogen or hydrogen concentrations [29-31]. It was found that the reduced hydrogen concentration (lower density of Si-H bond) in nitride film could improve the data Besides, D.S. Golubović et al. reported that lower nitrogen retention [29]. concentration in nitride film could result in wider memory window, better cycling endurance, improved erase-state retention but degraded program-state retention [30]. The author further mentioned that modifying the nitride film from nitrogen-rich to silicon-rich would increase hole trap energy level but reduce electron trap energy level [30]. Similar deduction was also reported by T.H. Kim *et al.* that the silicon-rich nitride film has larger trap density in shallow energy level than stoichiometric silicon nitride film [31].

#### 1.2.3 Using High-ĸ Dielectric to Improve Memory Performance

Among the above methods, using high- $\kappa$  Al<sub>2</sub>O<sub>3</sub> as blocking oxide (TANOS) is believed to be the most successful method and has been widely used in other methods, like the BE-SONOS method [17], the nitride layer engineering method [22], the evolved 3-D structure method (FinFET) [32], etc.

**Fig. 1.4** A comparison of the energy band diagram between conventional SONOS memory cell (dashed line) and TANOS memory cell (solid line) under the erase operation. The TANOS memory cell exhibits longer electron tunneling distance, leading to higher programming / erasing speed due to the lower back-tunneling current.

The energy band structure of TANOS under the erase operation is illustrated in Fig. 1.3. The band structure of the conventional SONOS cell is also plotted as dashed lines as a comparison. For an easy illustration, both Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> are set to the same equivalent oxide thickness (EOT). Because of the higher dielectric constant, Al<sub>2</sub>O<sub>3</sub> blocking oxide layer has a thicker physical thickness, thus a smaller electric field compared with SiO<sub>2</sub> blocking oxide layer under the same voltage stress. Although having a relative smaller energy band-gap, Al<sub>2</sub>O<sub>3</sub> still has a lower tunneling probability (longer electron tunneling distance) than SiO<sub>2</sub>, which is shown as the shadow area in Fig. 1.4. This lower tunneling current through Al<sub>2</sub>O<sub>3</sub> blocking oxide layer in TANOS cells provides faster programming / erasing speed and lower programming voltage compared with conventional SONOS cells [20]. Furthermore, TaN has a relatively higher work function than  $n^+$  polysilicon. Thus the electron barrier offset between TaN gate and blocking oxide becomes larger. The larger barrier offset will further reduce the back-tunneling electron current during erasure, therefore, increases the erase speed and suppresses the erase saturation [21, 24].

A significantly improved performance is achieved when using Al<sub>2</sub>O<sub>3</sub> instead of SiO<sub>2</sub> as a blocking oxide [21]. But the  $\kappa$  value of Al<sub>2</sub>O<sub>3</sub> is only about 9, which is relatively low compared to other high- $\kappa$  dielectric candidates [33]. Thus, it is possible to further improve the nitride-based SONOS-type memory performance if even higher  $\kappa$  dielectric is used as blocking oxide. However, few papers have explored this possibility. With a  $\kappa$  value of 12, hafnium silicate was investigated by Erlbacher *et al.* as a blocking oxide [34]. The author showed improved erasing speed and a much better time-to-breakdown reliability. However, the memory cells exhibited initial decay of flat-band voltage and data retention degradation [34]. In order to improve the data retention, the author further suggested reducing the physical thickness of hafnium silicate [34], which is contrary to original goal. Another high- $\kappa$  dielectric HfAlO ( $\kappa$ ~15) was also investigated by Wang *et al.* as both blocking oxide and tunnel oxide while with HfSiO as a trapping layer [27]. The author showed high erasing speed and good data retention [27]. But it was hard to evaluate the effect of each single layer because too many new materials were used at the same time.

In this study, we explored the possibility of using high- $\kappa$  dielectrics as blocking oxide to further improve the programming/erasing speed as well as the memory data retention.

### 1.3 Lanthanum-incorporated High-к Dielectrics

Over the past decade, many high- $\kappa$  dielectrics have been investigated, such as Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, SrTiO<sub>3</sub> and Ba<sub>x</sub>Sr<sub>1-x</sub>TiO<sub>3</sub>, etc. In order to find suitable high- $\kappa$  dielectrics for memory application, it is necessary to know the key characteristics of high- $\kappa$  dielectrics and the requirements from memory cells first.

#### 1.3.1 Dielectric Parameters for the Selection of High-ĸ Thin Film

As for the thin film dielectric evaluation, the key parameters have been suggested by Wilk *et al*, such as dielectric constant, band gap, band alignment,

thermodynamic stability, film morphology (crystal and amorphous phases), defects, reliability, etc. [35]

Dielectric constant of a material, also named as its relative permittivity, is defined as

$$\kappa = \mathcal{E}_r \big/ \mathcal{E}_0 \tag{1-1}$$

where  $\varepsilon_r$  is the static permittivity of the material, and  $\varepsilon_0$  is the permittivity of free space where  $\varepsilon_0 = 8.854 \times 10^{-12}$  F/m. Using the dielectric constant, the capacitance of a parallel-gate-electrode capacitor is expressed as

$$C = \frac{\kappa \varepsilon_0 A}{t_{ox}} \tag{1-2}$$

where *C* is the capacitance of the capacitor, *A* is the area of overlap of gate electrodes, and  $t_{ox}$  is the physical thickness between the two electrodes. The equation (1-2) shows that the capacitance can remain unchanged with a thicker physical thickness by using a higher  $\kappa$  dielectric. Thus, hopefully, the physically thicker film will result in a lower leakage current and thereby improve the device reliability.

When replacing the oxide with a new high- $\kappa$  dielectric, it is convenient to use the term of "equivalent oxide thickness" (EOT) to monitor the "electrical thickness" of the new high- $\kappa$  dielectric. The equivalent oxide thickness ( $t_{eq}$ ) is defined as the thickness of SiO<sub>2</sub> needed to maintain the same capacitance density as the high- $\kappa$ material has in a capacitor. It is given by

$$t_{eq} = \frac{\kappa_{OX}}{\kappa_{high-\kappa}} t_{high-\kappa}$$

(1-3)

where  $\kappa_{OX}$  and  $\kappa_{high-\kappa}$  is the dielectric constant of the SiO<sub>2</sub> (~3.9) and the replaced

high- $\kappa$  dielectric, respectively, and  $t_{high-\kappa}$  is the physical thickness of the replaced high- $\kappa$  dielectric.

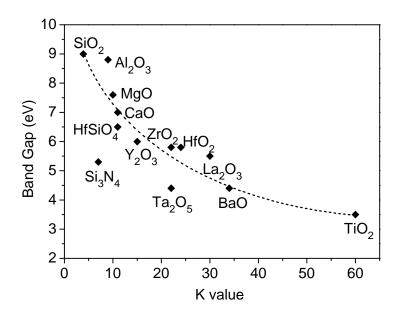

Ideally, a high- $\kappa$  dielectric with higher  $\kappa$  value and wider band gap ( $E_g$ ) is desired. However, this is impossible in reality since there is a tradeoff between the  $\kappa$ value and the energy band gap, as shown in Fig. 1.5 [36]. Generally, the energy band gap decreases as the  $\kappa$  value increases. This relationship implies that there is no ideal dielectric with both a wide band gap and a high  $\kappa$  value.

**Fig. 1.5** An overview of dielectric constant ( $\kappa$  value) versus energy band gap. It implies a general rule of tradeoff between the  $\kappa$  value and the energy band gap [36].

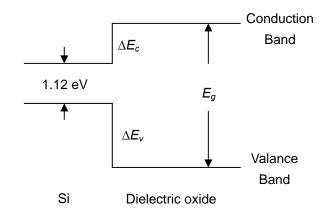

Besides the band gap  $(E_g)$ , the band alignment between the dielectric and semiconductor substrate or metal gate is another key parameter in dielectric evaluation. As an example, Figure 1.6 schematically shows the conduction band offset  $(\Delta E_c)$  and valence band offset  $(\Delta E_v)$  against silicon when aligning oxide and silicon together. The conduction band offset ( $\Delta E_c$ ) and valence band offset ( $\Delta E_v$ ) against silicon are key parameters in determining the electron and the hole current, respectively. Normally, the electron current has an exponential relationship with the barrier offset, as expressed in the formulas of Schottky emission, Frenkel-poole emission and tunneling emission [37].

Fig. 1.6 A schematic of conduction band offset ( $\Delta E_c$ ) and valence band offset ( $\Delta E_v$ ) of a dielectric oxide over silicon. Higher  $\Delta E_c$  and higher  $\Delta E_v$  are desired to achieve the smaller leakage current.

The gate-first process scheme requires the gate dielectric to withstand the high temperature anneal. This annealing temperature is typically greater than 900°C. The purpose of this anneal is to activate the source-drain dopants. Under such high temperatures, most high- $\kappa$  dielectrics would change their phases from amorphous to poly crystalline. It is generally believed that the formation of crystalline phase in a thick high- $\kappa$  dielectric would degrade the leakage current due to possible leakage route through the grain boundaries [35].

In addition, unlike in SiO<sub>2</sub>, the bonds in high- $\kappa$  dielectric oxides cannot relax

easily, which results in a high concentration of intrinsic defects [38]. The research of these intrinsic defects is still ongoing and there remain a lot of debates. Generally, it is believed that most of these defects in high- $\kappa$  dielectrics origin from imprecise stoichiometry, disorder of atoms, impurities, dislocation at grain boundaries, dipoles or unwanted bonds at the interface [35, 38]. These defects would act as the charge center and lead to an increase of leakage current, a shift of threshold voltage, a decrease of lifespan or even an earlier electrical breakdown [38]. The quantity of these defects can be partially reflected by the hysteresis of the capacitance-voltage (*C-V*) curves. Furthermore, these defects and reliability in high- $\kappa$  dielectric films are also highly dependent on the deposition method and post deposition annealing treatments. The reliability is normally characterized by the methods of stress-induced leakage current (SILC), bias temperature instability (BTI), time-dependent dielectric breakdown (TDDB), and mean time to failure (MTF), etc.

#### 1.3.2 Lanthanum-incorporated High-к Dielectrics: LaAlO<sub>x</sub> and HfLaO<sub>x</sub>

In nitride-based SONOS-type flash memory, a suitable blocking oxide candidate should have high enough electron and hole barriers to retain charges inside the nitride film for a long time. The electron or hole barrier over silicon is required to be larger than 1 eV [35]. Because there is a trade-off relationship between  $\kappa$  value and energy band-gap, as shown in Fig. 1.5, high- $\kappa$  dielectrics with a  $\kappa$  value in the range of 15 to 30 is mostly preferred. In addition, the gate-first process scheme requires dielectrics that can withstand high source-drain temperature anneal.

Taking process requirements (such as water nonreactive) and conduction band offset requirement (1 eV over Si conduction band edge) into consideration, possible candidates from periodic table are narrowed down to Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub> and other lanthanides oxide (such as Pr<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub>, Lu<sub>2</sub>O<sub>3</sub>, etc.). However, all these oxides have their own predominant disadvantages, such as a relatively low  $\kappa$  value (9 to 15) for Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> and Lu<sub>2</sub>O<sub>3</sub>, low crystallization temperatures for ZrO<sub>2</sub> and HfO<sub>2</sub>, and strong hygroscopic property for lanthanides oxides. In order to minimize these undesirable properties, ternary dielectrics were proposed, such as HfSiO<sub>x</sub>, ZrSiO<sub>x</sub>, HfAlO<sub>x</sub>, LaAlO<sub>x</sub>, HfLaO<sub>x</sub>, etc. In this way, the ternary dielectric can, normally, inherit the desirable properties from two dielectric oxides, while simultaneously minimize their undesirable properties. For example, it is reported that HfSiO<sub>x</sub> has the properties of a large energy band gap, a high  $\kappa$  value (~10 to 15), improved crystallization temperature up to 900°C, and improved reliability, etc.

Among these ternary dielectrics, lanthanum-incorporated high- $\kappa$  dielectrics (LaAlO<sub>x</sub> and HfLaO<sub>x</sub>) provide high  $\kappa$  values ranging from 13 to 33 [39-45]. And their conduction band offsets over silicon are reported to be greater than 1.5 eV [46-48]. Moreover, the stoichiometric LaAlO<sub>3</sub> and HfLaO<sub>3</sub> can remain amorphous phase up to 850 °C [41-43, 49, 50]. These properties meet the requirement for memory application to a great extent. It was also reported that, with the incorporation of lanthanum, the reliability of dielectrics can be greatly improved [51, 52]. Furthermore, according to the simulation results, lanthanum-incorporated dielectric films offer the lowest leakage current compared to other high- $\kappa$  dielectrics [53]. Therefore, lanthanum-

incorporated high- $\kappa$  dielectrics (LaAlO<sub>x</sub> and HfLaO<sub>x</sub>) were chosen to be targeted as blocking oxide in SONOS-type flash memory in this study.

## 1.3.3 Current Developments of LaAlO<sub>x</sub> and HfLaO<sub>x</sub> Dielectrics

$LaAlO_x$  and  $HfLaO_x$  have been widely studied as possible candidates to replace SiO<sub>2</sub> as the gate dielectric.

#### A. Literature Review of LaAlO<sub>x</sub>

The dielectric constant ( $\kappa$ ) of LaAlO<sub>x</sub> films varied from 13 to 33 in different papers. In the study by R. Devine, a  $\kappa$  value of 14 was reported for both amorphous and poly-crystalline LaAlO<sub>x</sub> using sputter method [40]. Similar  $\kappa$  value of 14 and 13 were also reported for films deposited using MBE or ALD method by Vellianitis *et al.* and Lim *et al.*, respectively [39, 54]. In contrast, , Park *et al.* reported a  $\kappa$  value of 24 when using the same MBE deposition method [55]. An even higher  $\kappa$  value of 33 was reported by Shi *et al.* for amorphous LaAlO<sub>x</sub>N<sub>y</sub> (y = 0.4) using the pulse laser deposition (PLD) method [42]. However, such high  $\kappa$  value has not been repeated by any other groups so far.

The optical energy band gap of LaAlO<sub>3</sub> was reported by Cicerrella *et al.* to be 5.84 eV and 6.33 eV for thinner and thicker films, respectively, using spectroscopic ellipsometry [56]. Using the XPS method, a higher value of the energy band gap (6.5 eV) of LaAlO<sub>3</sub> was reported by Suzuki *et al.* In addition, the conduction band offset

and valence band offset against Si were measured to be 2.4 eV and 3.0 eV, respectively [46]. For single crystalline LaAlO<sub>3</sub>, similar band offsets were reported by Mi *et al.* [47]. Moreover, the large values of band offset against silicon of LaAlO<sub>3</sub> have a great impact on leakage current. The leakage current flowing through LaAlO<sub>3</sub> film, reported by Goldenblum *et al.*, was found to fit the space charge limited (SCL) current behavior very well [57]. That is, the square root of the leakage current had a linear relationship with the applied voltage. The space charges caused by impurities inside LaAlO<sub>3</sub> were suggested to be located near the Si band edge [57].

The reported temperature for the onset of LaAlO<sub>3</sub> crystallization ranged from 850°C to 1000°C. It was found that LaAlO<sub>3</sub> films deposited by the CVD method had a slightly lower crystallization temperature than the ones deposited by the PVD method. Shao *et al.* and Gaskell *et al.* both reported that LaAlO<sub>3</sub> films deposited by using MOCVD and ALD would remain amorphous after annealing at 850°C [43, 49]. However, LaAlO films deposited by using the PVD method like sputter or MBE can remain amorphous after annealing at even higher temperature, such as 935°C or 1000°C [50, 58].

Different annealing conditions were investigated in order to improve the film quality,. Miotti *et al.* and Edon *et al.* both reported that thermal annealing at 600°C under  $O_2$  ambient on LaAlO<sub>3</sub> films would result in better electrical characteristics as compared to films annealed in an  $N_2$  ambient [59, 60]. However, the side effect of high temperature anneal under  $O_2$  ambient will form a much thick interfacial layer which is undesired. Besmehn *et al.* revealed that the constitution of interfacial layer changed from SiO<sub>x</sub> to La-Al-Si-O at 500°C anneal [61]. In contrast, Clémer *et al.* reported that the SiO<sub>x</sub> interfacial layer only existed at 800°C anneal, and the transition of SiO<sub>x</sub> interfacial layer to La-Al-Si-O interfacial layer occurred at 930°C [62]. In addition, a high temperature anneal would not only result in the interfacial layer transformation, but also atomic migration. When film was annealed at 800°C for 60 s, reported by Miotti *et al.*, Si atom migrated from substrate into sputtered LaAlO<sub>3</sub> film and this migration could be greatly suppressed by thermal nitridation of LaAlO<sub>3</sub> using NH<sub>3</sub>[59]. The suppression of atomic migration were also reported by Sivasubramani *et al.* using plasma nitridation method [50].

The lattice mismatch is only 1.3% between crystalline LaAlO<sub>3</sub> and Si substrate. Theoretically, it is possible to epitaxially grow single crystalline LaAlO<sub>3</sub> on Si substrate. However, simulations revealed that a stable interface between stoichiometric LaAlO<sub>3</sub> and Si could not be obtained [63]. This conclusion was consistent with the experiment reports by Gaillard *et al.* [64]. In order to achieve epitaxial growth, a seed layer of SrTiO<sub>3</sub> or  $\gamma$ -Al<sub>2</sub>O<sub>3</sub> was applied as a template between the LaAlO<sub>3</sub> and the Si substrate. By this way, the single-crystalline LaAlO<sub>3</sub> films were successfully deposited using molecular beam epitaxy (MBE) method [47, 65].

In comparison with  $La_2O_3$ ,  $LaAlO_x$  exhibited better hydroscopic property, lower leakage current and smaller *C-V* hysteresis [66, 67].

#### **B.** Literature Review of HfLaO<sub>x</sub>

Compared to LaAlO<sub>x</sub>, there are fewer reports on the HfLaO<sub>x</sub> dielectric. The reported dielectric constant of HfLaO<sub>x</sub> ranges from 18 to 23 for amorphous films and monoclinic crystal films [44, 45, 68]. However, when La percentage was 4%, a higher  $\kappa$  value of 28 for HfLaO<sub>x</sub> was reported by Yamamoto *et al.* [41]. Author attributed this increment of  $\kappa$  value to cubic crystal formation [41]. In addition, the energy band gap, valence band offset and conduction band offset of amorphous Hf<sub>2</sub>La<sub>2</sub>O<sub>7</sub> over Si was measured to be 5.6 eV, 2.4 eV and 2.1 eV, respectively, using XPS [48].

The crystallization temperature of amorphous Hf<sub>2</sub>La<sub>2</sub>O<sub>7</sub> was reported to be 900°C [68, 69]. Furthermore, when La percentage decreased from 50% to 15%, the crystallization temperature dropped to 600°C accordingly[69]. The relationship between crystallization temperature and La percentage was further summarized by Yamamoto *et al.* [41].