## SIGMA-DELTA CLASS D AUDIO POWER AMPLIFIER

## IN CMOS TECHNOLOGY

# **PAN JUNLE**

(B.Eng.(Hons.).NUS)

### A THESIS SUBMITTED

## FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2009

#### ACKNOWLEDGEMENT

I would like to express my sincere appreciation and utmost gratitude to my project supervisors, Assistant Professor Yao Libin and Associate Professor Lian Yong, for their invaluable advice, guidance, patience, encouragement and support throughout the duration of this project. I am extremely grateful for all the time they spent helping me with my problems and pointing me to the right direction.

## **CONTENTS**

| ACKNOWLEDGEMENTS                  | i     |

|-----------------------------------|-------|

| TABLE OF CONTENTS                 | .11   |

| SUMMARY                           | . vii |

| LIST OF TABLES                    | viii  |

| LIST OF FIGURES                   | ix    |

| LIST OF SYMBOLS AND ABBREVIATIONS | xiv   |

| CHAPTER 1 | INTRODUCTION |  |

|-----------|--------------|--|

|           |              |  |

| 1.1 Background                          | 1  |

|-----------------------------------------|----|

| 1.2 Objective                           | 2  |

| 1.3 Project Flow                        | 3  |

| 1.4 Thesis organization and Publication | .4 |

| CHAPTER 2 BACKGROUND OF CLASS D POWER AMPLIFIER 5   |   |

|-----------------------------------------------------|---|

| 2.1 Background of Audio Power Amplifier5            |   |

| 2.1.1 Linear Amplifier6                             |   |

| 2.1.2 Switching Amplifier                           |   |

| 2.2 Performance Metrics for Audio Power Amplifier 1 | 2 |

| 2.2.1    | Power Efficiency(η)                 | 12 |

|----------|-------------------------------------|----|

| 2.2.2    | Dynamic Range (DR)                  | 12 |

| 2.2.3    | Total Harmonic Distortion (THD)     | 13 |

| 2.2.4    | Signal to Noise Ratio (SNR)         | 14 |

| 2.2.5    | Power Supply Rejection Ratio (PSRR) | 14 |

| 2.3 Cond | clusion                             | 15 |

| CHAPTER 3 ARCHITECTURAL DESIGN                  |

|-------------------------------------------------|

| 3.1 General Achitecture of Class D Amplifier 16 |

| 3.2 Signal modulation scheme 19                 |

| 3.2.1 Pulse Width Modulation                    |

| 3.2.2 Sigma Delta Modulation 22                 |

| 3.3 Architectural of output stage               |

| 3.3.1 Half bridge output                        |

| 3.3.2 Full H bridge output                      |

| 3.3.3 Dead time and distortion                  |

| 3.4 Three-level switching scheme for SDM        |

| 3.5 PSRR and Feedback Topology                  |

| 3.6 Overall architectural design                |

| CHAPTER 4: SIGMA-DELTA MODULATOR DESIGN              |

|------------------------------------------------------|

| 4.1 Basis of Sigma-Delta Modulator                   |

| 4.2 System level design                              |

| 4.2.1 System Level Design Parameters 50              |

| 4.2.1.1 Modulator Architecture                       |

| 4.2.1.2 Oversampling Ratio                           |

| 4.2.1.3 Loop Coefficient 53                          |

| 4.2.1.4 Order of Loop Filter                         |

| 4.2.1.5 Number of bit for quantizer                  |

| 4.2.2 Stability analysis of single loop SD modulator |

| 4.2.3 Fully feed-forward topology                    |

| 4.2.4 System parameters optimization                 |

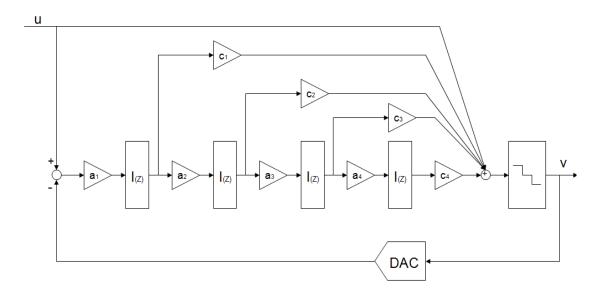

| 4.2.4.1 Architecture of SD Modulator                 |

| 4.2.4.2 Order of Loop Filter and OSR                 |

| 4.2.4.3 Loop Coefficient Optimization                |

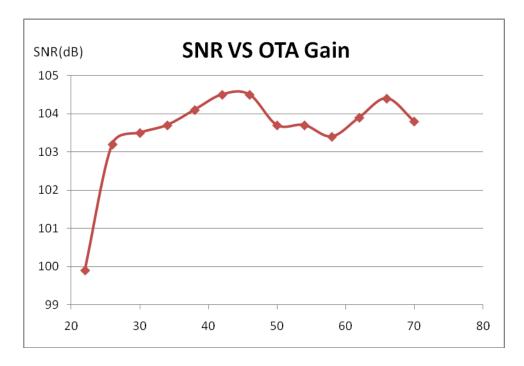

| 4.2.4.4 OTA Gain                              |

|-----------------------------------------------|

| 4.2.4.5 Effect of OTA Offset                  |

| 4.2.4.6 Overall System Level SD Design 82     |

| 4.3 Circuit Implementation                    |

| 4.3.1 OTA Design 85                           |

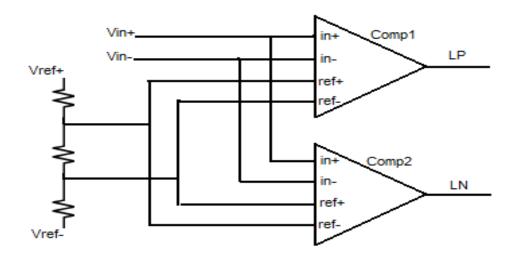

| 4.3.2 Comparator and 1.5-bit quantizer design |

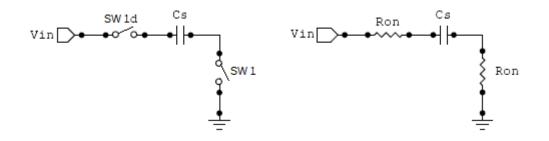

| 4.3.3 Sampler Design                          |

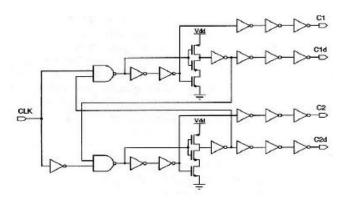

| 4.3.4 Non-overlap Clock generator design      |

| 4.3.5 Feed Forward Summing Design             |

| 4.3.6 Feedback and Vref generation100         |

| CHAPTER 5: OUTPUT STAGE  | DESIGN |

|--------------------------|--------|

| 5.1 Full H-bridge Outpu  | t102   |

| 5.2 Gate Driving Circuit |        |

| 5.3 Output LPF           |        |

| CHAPTER 6: MEASUREMENT RESULTS                       | 113 |

|------------------------------------------------------|-----|

| 6.1 H-bridge output waveform comparison (simulation) | 117 |

| 6.2 Output waveform                                  | 119 |

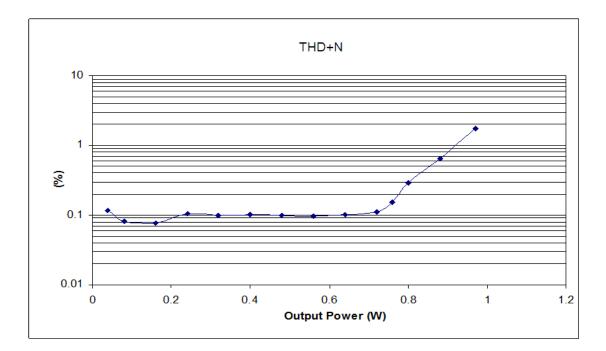

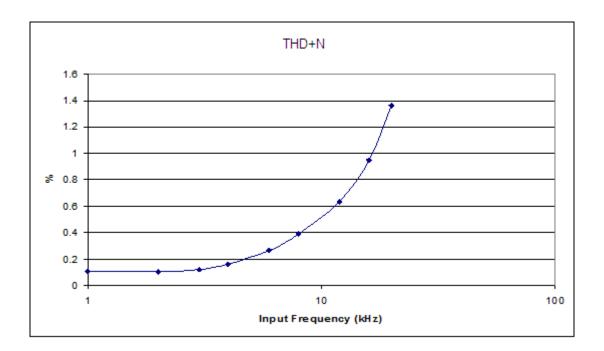

| 6.3 THD+N performance                                | 123 |

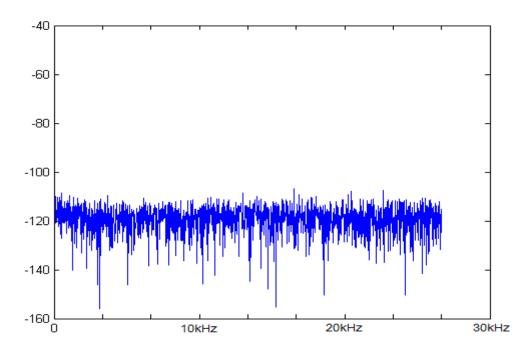

| 6.4 Output Dynamic Range                             | 126 |

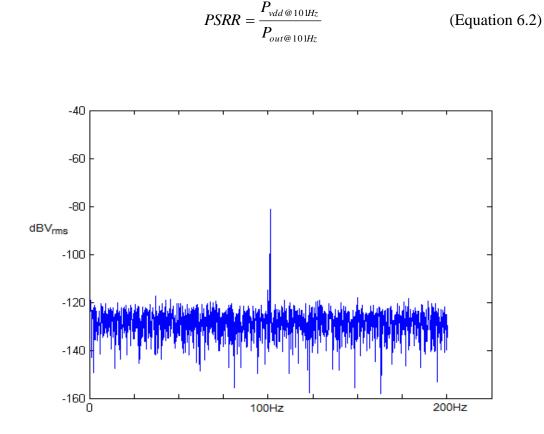

| 6.5 PSRR                                             | 127 |

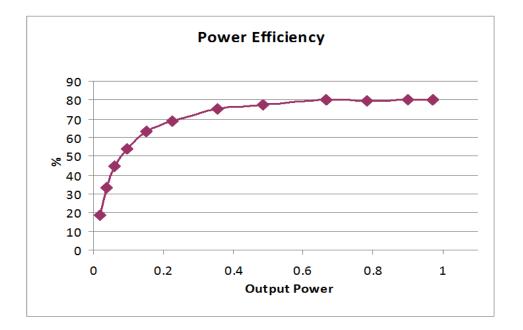

| 6.6 Overall power efficiency                         | 129 |

| 6.7 Conclusion                                       | 131 |

| CHAPTER 7: | CONCLUSION | ſ | <br>135 |

|------------|------------|---|---------|

|            |            |   |         |

| REFERENCE |     |

|-----------|-----|

| APPENDIX  | 141 |

### **Summary**

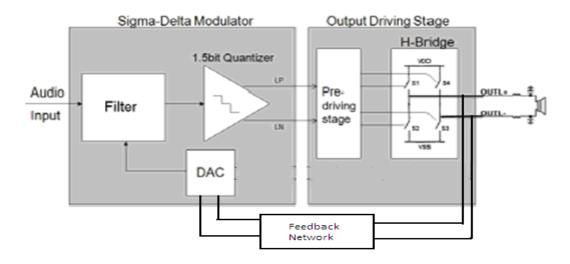

A one-channel high power efficiency Class D audio power amplifier utilizing full-feedforward Sigma-Delta topology is introduced. Compared to conventional structure, the power efficiency of this design is improved by using a novel three-level switching scheme which greatly reduces the switching activity of the modulator output and the power transistors, especially when the input power is small.

The main building blocks of this Class D power amplifier are high-linear single loop full-feedforward Sigma-Delta modulator, power transistors driving circuit and full H-bridge output stage. The output signal of the full H-bridge is directly feedback to the Sigma-Delta modulator which improved the PSRR of the power amplifier.

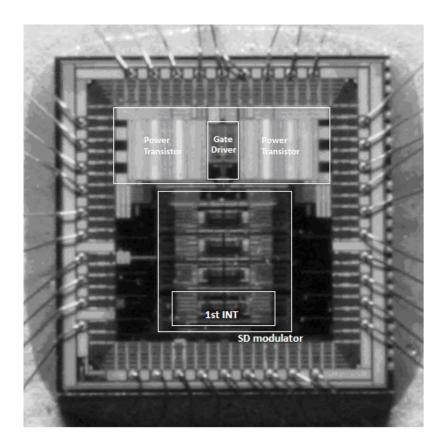

This design is realized in  $0.35 \,\mu\text{m}$  CMOS technology. The power transistors and the Sigma-Delta modulator are integrated in a single chip which has  $3.97 \, mm^2$  active area. The testing results show that the power efficiency for low input power is truly improved by using new switching scheme. The operational power supply for this design is ranged from 2.5 V to 4.5 V. With 3.3 V power supply, the THD reaches 0.0817% at 0.1 W output power and the PSRR is 64.8 dB. With 4 Ohm load, the maximum power efficiency is 80%.

# LIST OF TABLES

| Table 1.1: Design Specifications                                                |

|---------------------------------------------------------------------------------|

| Table 4.1: Calculated SRN of 1-bit quantization ideal SD modulator [Pel97] 69   |

| Table 4.2: SNR performance of stable 2nd to 4th order conventional SD modulator |

| with optimized loop coefficient [Pel97]70                                       |

| Table 4.3: SNR performance of 2nd to 4th order fully feed forward SD modulator  |

| with optimized loop coefficient [Yao05]71                                       |

| <b>Table 4.4:</b> Output states of the 1.5-bit quantizer    95                  |

| Table 5.1: Components value for the LPF    112                                  |

| Table 6.1: Summary of measurement results    131                                |

| Table 6.2 Performance Comparison                                                |

## **LIST OF FIGURES**

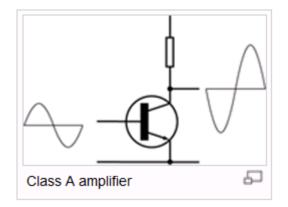

| Fig 2.1.1a: Class A amplifier7                                            |

|---------------------------------------------------------------------------|

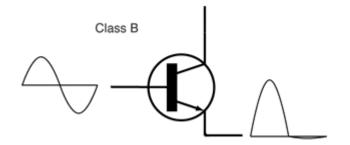

| Fig 2.1.1b: A single Class B element7                                     |

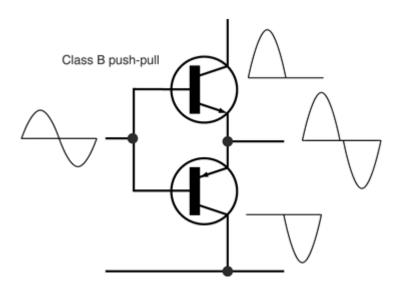

| Fig 2.1.1c: Class B push-pull amplifier8                                  |

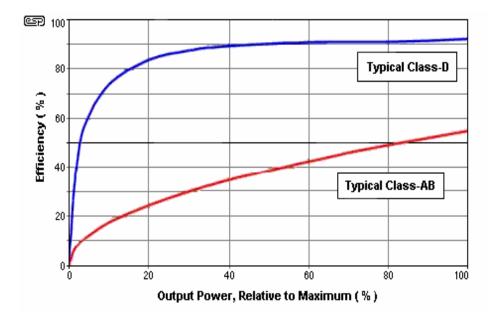

| Fig 2.1.2: Power efficiency of Class D VS. Class AB11                     |

| Fig 3.1: Block diagram of a Class D amplifier16                           |

| Fig 3.2: Typical PWM input and output signal20                            |

| Fig 3.3: Typical output waveform of two-level quantization SD modulator22 |

| Fig 3.4 Half bridge output circuit25                                      |

| Fig 3.5: Supply voltage pumping effect27                                  |

| Fig 3.6: Differential output stage and its LC LPF27                       |

| Fig 3.7: Local current loop to prevent pumping effect29                   |

| Fig 3.8: Dead time of output control signal30                             |

| Fig 3.9: Current flow in full H bridge                                       |

|------------------------------------------------------------------------------|

| Fig 3.10: H-bridge output voltage and load current of 1-bit SD modulator 36  |

| Fig 3.11: H-bridge output voltage and load current of 1.5-bit SD modulator37 |

| Fig 3.12 Normalized switching activity of 1 bit and 1.5 bit SD modulator at  |

| different output power                                                       |

| Fig 3.13: Linear model for open loop class D amplifier 39                    |

| Fig 3.14: Linear model for class D amplifier with feedback40                 |

| Fig 3.15(a): Model of SDM class D amplifier with feedback from quantizer 41  |

| Fig 3.15(b): Model of SDM class D amplifier with feedback from H bridge42    |

| Fig 3.16: Block diagram of proposed class D amplifier                        |

| Fig 4.1: Structure of simplest single loop 1st order SD modulator45          |

| Fig 4.2: Noise Injection model for 1st order conventional SD modulator46     |

| Fig 4.3: Frequency response of SD modulator due to Noise shaping 47          |

| Fig 4.4: Conventional 2nd order single loop SD modulator                     |

| Fig 4.5: Quantization noise in Nyquist rate sampling and oversampling 49     |

| Fig 4.6: A 4th order cascaded 2-1-1 SD modulator [Yao05] 52                  |

| Fig 4.7: Variable gain linear model for SD modulator57                       |

| Fig 4.8: Root locus of the poles for 3rd order conventional SD modulator58   |

| Fig 4.9: 1st order single loop fully feed forward SD modulator               |

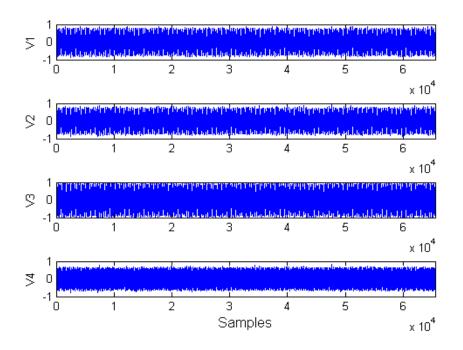

| Fig 4.10a: Integrators output of 4th order conventional SD modulator65       |

|------------------------------------------------------------------------------|

| Fig 4.10b: Integrators output of 4th order fully feed forward SD modulator65 |

| Fig 4.11: A 3rd order fully feed forward SD modulator66                      |

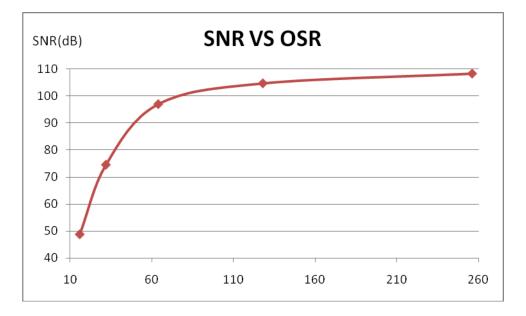

| Fig 4.12: SNR vs OSR for the proposed 4th order modulator72                  |

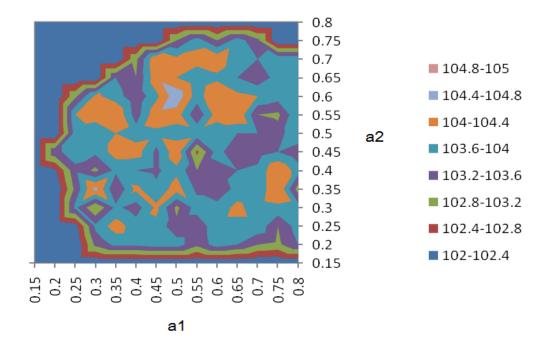

| Fig 4.13: Contour plot of SNR with a1 and a2 as sweeping variable73          |

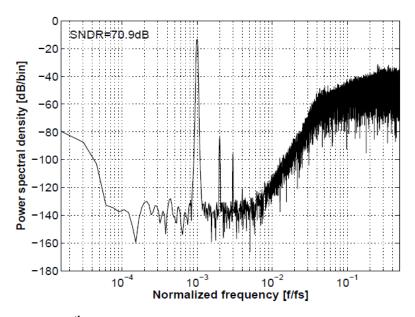

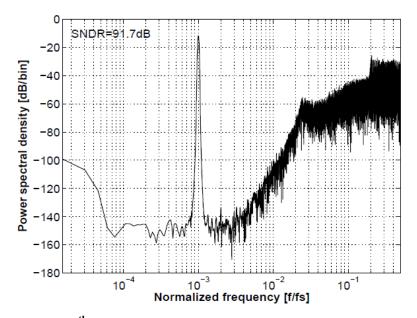

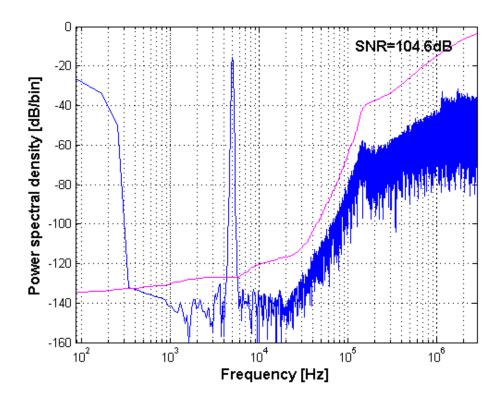

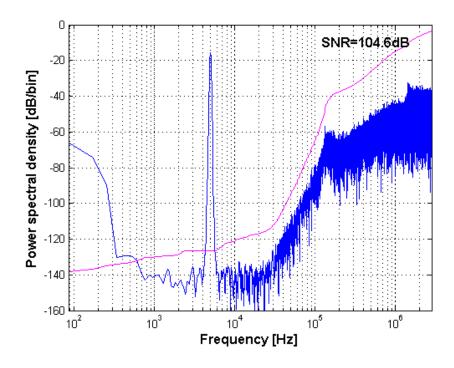

| Fig 4.14a: PSD of 4th order conventional SD modulator with non-linear OTA,   |

| Ao=40dB                                                                      |

| Fig 4.14b: PSD of 4th order fully feed forward SD modulator with non-linear  |

| OTA, Ao=40dB76                                                               |

| Fig 4.15: SNR performance base on OTA gain for proposed SD modulator78       |

| Fig 4.16a: Effect of 1st stage OTA offset alone                              |

| Fig 4.16b: Effect of 2nd stage OTA offset alone80                            |

| Fig 4.17: Overall architectural of proposed 4th order fully feed forward SD  |

| modulator with a 1.5-bit quantizer                                           |

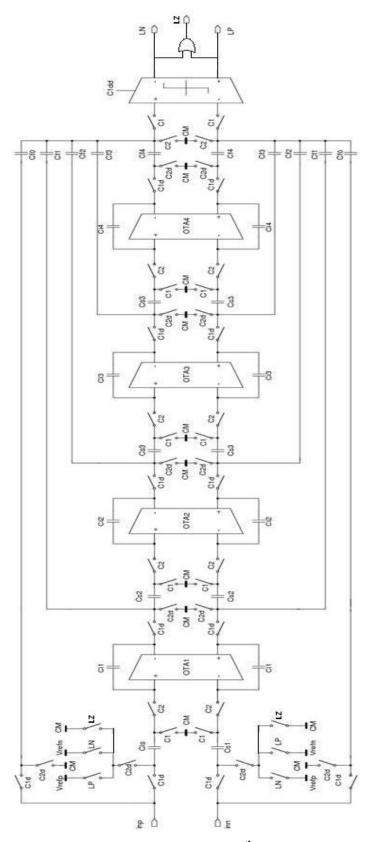

| Fig 4.18: Circuit implementation of proposed 4th order fully feed forward SD |

| modulator                                                                    |

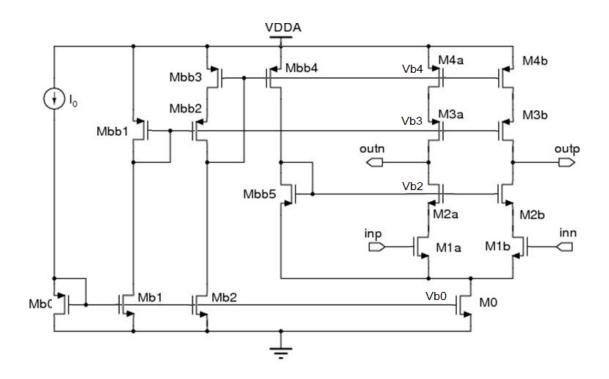

| Fig 4.19: Schematic design of the single stage telescopic OTA 87             |

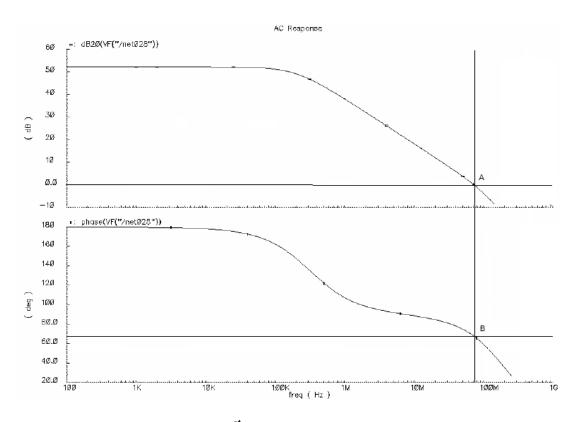

| Fig 4.20: AC response of 1st stage OTA with 16pF loading capacitance90       |

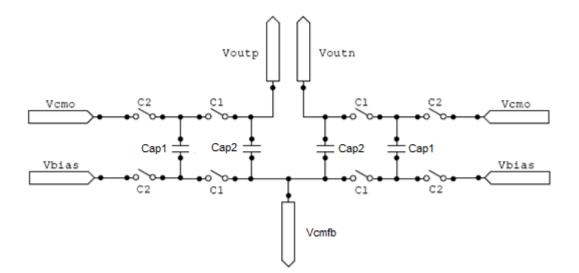

| Fig 4.21: Switch-capacitor CMFB91                                            |

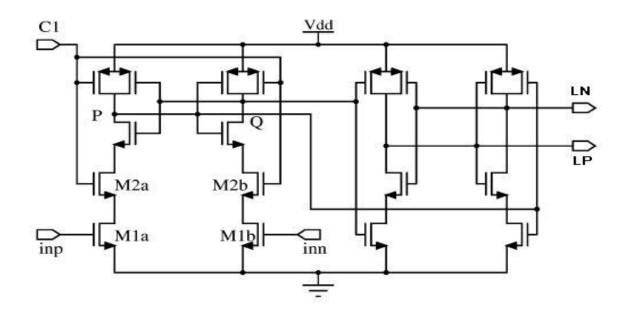

| Fig 4.22: Schematic of regenerative latch comparator               |

|--------------------------------------------------------------------|

| Fig 4.23: 1.5-bit quantizer                                        |

| Fig 4.23a: Schematic of sampler95                                  |

| Fig 4.23b: equivalent circuit at sampling phase                    |

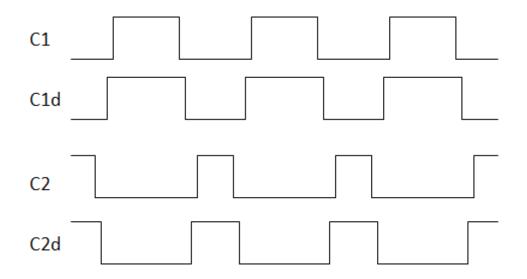

| Fig 4.24: Clock generator                                          |

| Fig 4.25: Output of clock generator                                |

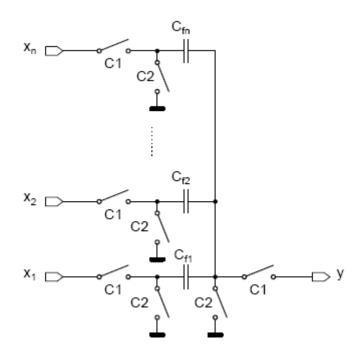

| Fig 4.26: Summing point of the feed forward path                   |

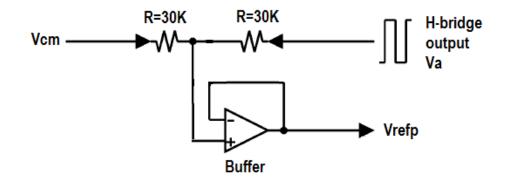

| Fig 4.27: Reference voltage generation circuit                     |

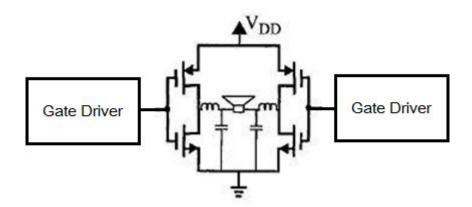

| Fig 5.1: Output stage of class D amplifier: Gate Driver, H-Bridge  |

| and LPF 102                                                        |

| Fig 5.2: Test bench for extraction of on-resistance 106            |

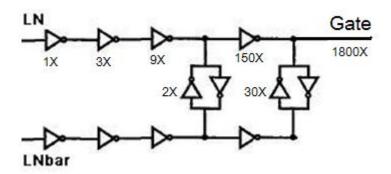

| Fig 5.3: structure of gate driver                                  |

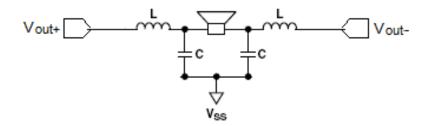

| Fig 5.4: Differential version of LC LPF for Class D amplifier 110  |

| Fig 6.1: Die Photo 113                                             |

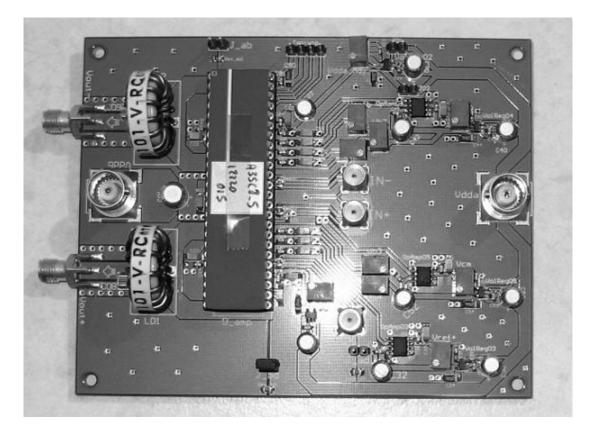

| Fig 6.2: Photo of Testing PCB 114                                  |

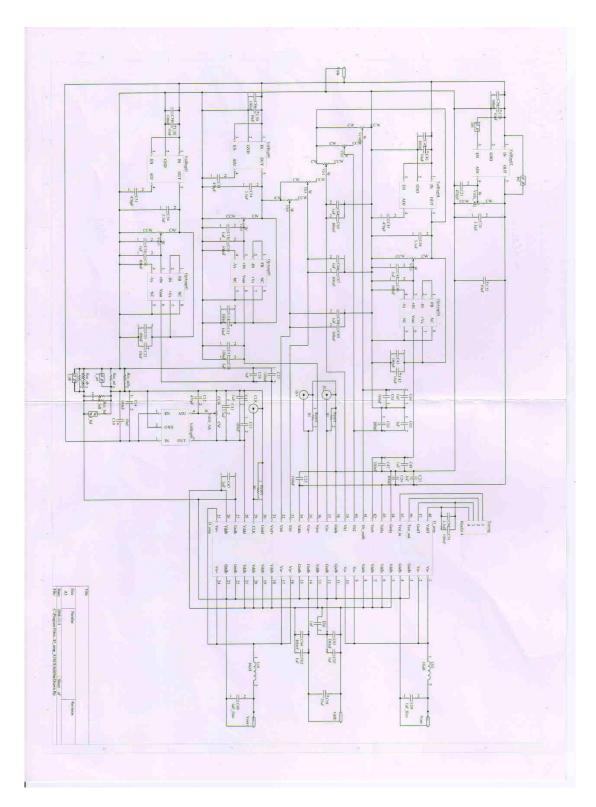

| Fig 6.3: Schematic of testing PCB 116                              |

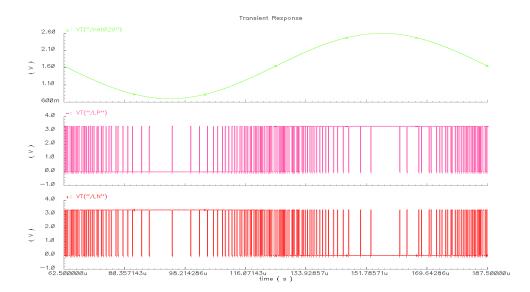

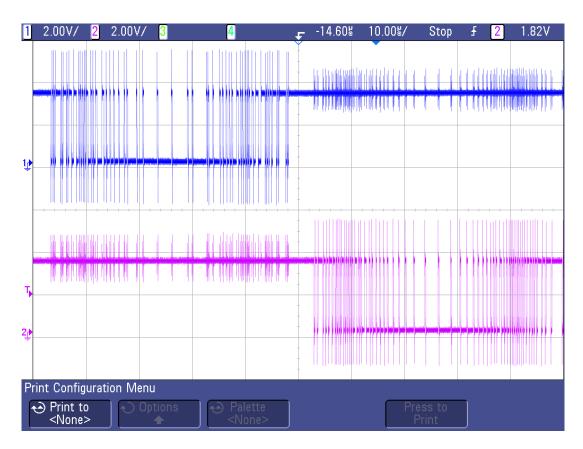

| Fig 6.4: Output pulse train with 1-bit SD modulator at high output |

| 17 |

|----|

| L  |

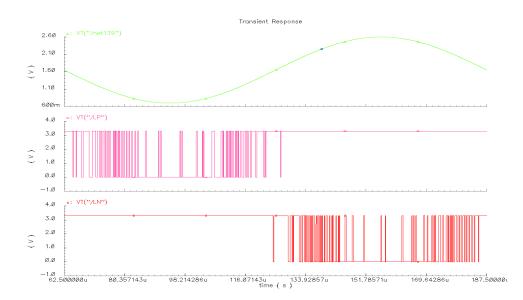

| Fig 6.5: Output pulse train with 1.5-bit SD modulator at high output |

|----------------------------------------------------------------------|

| power                                                                |

| Fig 6.6: Output pulse train with 1-bit SD modulator at low output    |

| power                                                                |

| Fig 6.7: Output pulse train with 1.5-bit SD modulator at low output  |

| power 118                                                            |

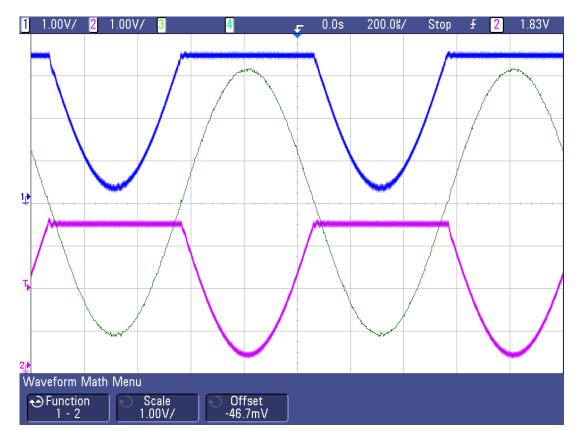

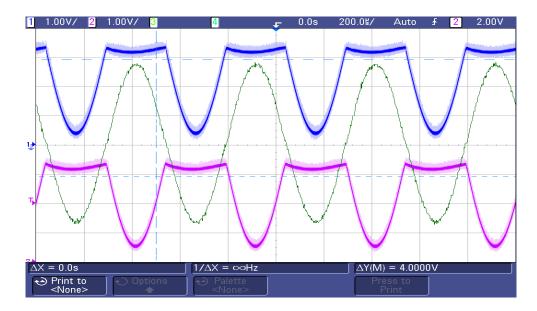

| Fig 6.8: Output waveform of H-bridge without load 119                |

| Fig 6.9: Output waveform of LC LPF without load120                   |

| Fig 6.10: Output waveform of H-bridge with 4 Ohm load 121            |

| Fig 6.11: Output waveform of LC LPF with 4 Ohm load 121              |

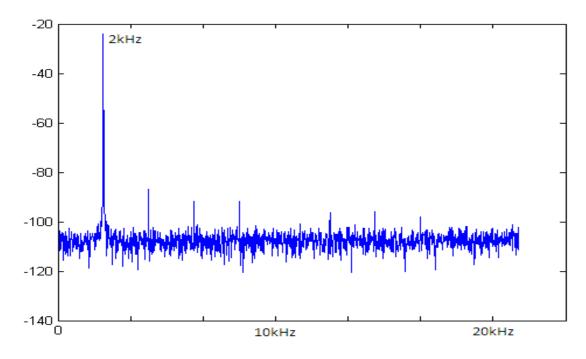

| Fig 6.12: Output spectrum of LPF with 4 Ohm load at 0.16FS output    |

| power 124                                                            |

| Fig 6.13: THD+N VS Output power of designed class D amplifier 124    |

| Fig 6.14: THD+N VS input frequency of designed class D amplifier 125 |

| Fig 6.15: Noise floor of LPF output within audio band 126            |

| Fig 6.16: Output power spectrum with 101Hz supply noise       128    |

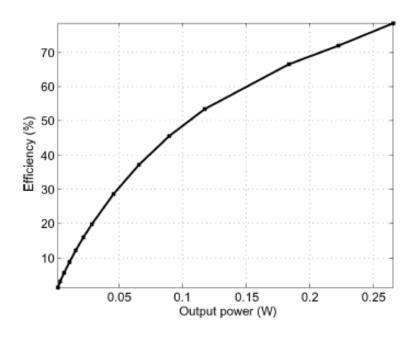

| Fig 6.16: Power efficiency with 4 Ohm load @ 3.3V supply 129         |

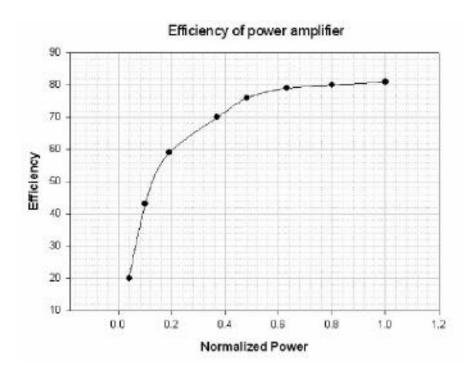

| Fig 6.17: Power efficiency VS output power in Reference [Axh07]132   |

| Fig 6.18: Power efficiency VS output power in Reference [Cho06]133   |

# LIST OF SYMBOLS AND ABBREVIATIONS

| K    | Boltzmann's Constant, 1.38 x $10^{-23}$ m <sup>2</sup> kg s <sup>-2</sup> K <sup>-1</sup> |  |

|------|-------------------------------------------------------------------------------------------|--|

| Τ    | Absolute Temperature, 273K                                                                |  |

| CMOS | Complementary Metal Oxide Semiconductor                                                   |  |

| DAC  | Digital-to-Analog Converter                                                               |  |

| DC   | Direct Current                                                                            |  |

| FFT  | Fast Fourier Transform                                                                    |  |

| NMOS | N-channel MOS                                                                             |  |

| NTF  | Noise Transfer Function                                                                   |  |

| OSR  | Oversampling Ratio                                                                        |  |

| ΟΤΑ  | Operational Transconductance Amplifier                                                    |  |

| PMOS | P-channel MOS                                                                             |  |

| PSD  | Power Spectral Density                                                                    |  |

| PSRR | Power supply rejection ratio                                                              |  |

| PWM  | Pulse Width Modulation                                                                    |  |

| RF   | Radio Frequency                                                                           |  |

| SNR  | Signal-to-Noise Ratio                                                                     |  |

| VLSI | Very Large Scale Integrated Circuit                                                       |  |

| SD   | Sigma-Delta                                                                               |  |

# Chapter 1: Introduction

### 1.1 Background

Portable audio electronic devices such as mobile phone, MP3 player, have grown in popularity. They employ a power amplifier to drive a small loud speaker. Since these portable devices are powered by batteries and the power consumption of the audio system is significant to the total power consumption of devices, a highly efficient power amplifier with low power dissipation and low distortion is required [Kyo08]. The class D power audio amplifier provides a good solution in term of power efficiency. Compared to traditional class AB audio power amplifier, whose maximum power efficiency is around 60%, the class D power amplifier nowadays achieves much higher power efficiency. The theoretical maximum efficiency of a class D amplifier is 100%, but practically achievable is 90% at high output power [Axh07]. High power efficiency of class D power amplifier effectively reduces the supply current requirement so that the operation time of batteries is longer. Besides that, high power efficiency implies that less power is dissipated on the power amplifier itself. This greatly relaxes the thermal problem commonly found in power

amplifier. The bulky heat sink for power amplifier can even be eliminated to further reduce the size of the portable devices [Dap00]. These two advantages of class D audio power amplifier make it widely used for portable audio application.

The major drawback of class D power amplifier is its higher distortion level compared to other type of power amplifier. Apart from distortion, electromagnetic interface (EMI) caused by high frequency switching operation is another problem [Ber03]. Therefore, to design a class D audio power amplifier which produces good quality sound with high efficiency is a big challenge.

### 1.2 Objective

The main objective of this project is to design a 1-channel class D audio power amplifier using full-feedfoward Sigma Delta modulator using 0.35  $\mu$ m CMOS technology with 3.3 V power supply. The design aims to maximize the power efficiency with low distortion and high PSRR. The load for this design is a 4 $\Omega$  or 8 $\Omega$ resistive load. Table 1.1 shows the design specifications for this project:

| Power Supply             | 3.3V                   |

|--------------------------|------------------------|

| Quiescent Current        | <10mA                  |

| Load                     | $4\Omega$ or $8\Omega$ |

| Dynamic Range            | >90dB                  |

| Maximum Output Power     | 1W                     |

| PSRR                     | >60dB                  |

| THD+N                    | <0.1%                  |

| Maximum Power Efficiency | >80%                   |

|                          |                        |

| Active area              | As small as possible   |

#### **Table 1.1: Design Specifications**

The design is done in Cadence EDA environment. This design is fabricated for the evaluation of the chip performance. Apart from the design of IC chip, testing PCB and the output filter for the class D power amplifier are also designed for the testing purpose in this project.

### **1.3 Project Flow**

This research project can be separated into four stages. The first stage is paper research. The most recently published papers on class D power amplifier are studied in order to get a clear view on the research work done in this area. The second stage is the system level design. In this stage, the architecture of the power amplifier and the specifications of building blocks are determined. A single-stage 4th-order fully feedforward Sigma-Delta modulator is adopted to modulate the input signal. The third stage is transistor level schematic and layout design with simulation verification. Corner simulation and Monte Carlo simulation are carried out in this stage to ensure that the design is able to work properly with process variations in fabrication. The last stage is the design of testing PCB and evaluation of the fabricated IC chip. In this stage, the performance of the designed class D power amplifier is extracted and compared with other designs.

### **1.4** Thesis organization and publication

This thesis is presented in seven chapters. Chapter 1 shows the motivation of this project and defines design specifications. Chapter 2 introduces the background knowledge of audio power amplifiers and the performance metrics. Chapter 3, 4 and 5 are the main body of this thesis. They include the details of system level design, block level design and transistor level design. Chapter 6 presents the details of sample chips measurement and the performances comparison between this design and other designs in recent publications. Chapter 7 gives brief conclusion of this project and suggests the direction of further improvement of the design.

This design had been published in International SoC conference 2008, Busan, South Korea. The publication list is shown in Appendix.

# Chapter 2: Background of Class D Power Amplifier

In this chapter, a short introduction of different types of power amplifier architectures and their trade-offs is discussed. Several general performance parameters are introduced and followed by the basic background knowledge about the class D power amplifier.

### 2.1 Background of Audio Power Amplifier

Audio power amplifier is an electronic device that produces high-power replication of low-power audio signal to deliver driving power for loudspeakers. Generally power amplifier can be classified into two categories: linear amplifier and switching amplifier.

### 2.1.1 Linear Amplifier

Class A, Class B and Class AB power amplifiers are the commonly used linear power amplifiers. The output devices of a linear amplifier are operating at linear region for bipolar junction transistors or saturation region for CMOS transistors. They act as active resistors to regulate the power delivery to loads.

In Class A amplifier, the output devices are continuously conducting for the entire cycle. This avoids turning the output on and off and hence Class A amplifier has very high linearity. However, since the output devices are always conducting current even if there is no input at all, power is wasted and this results in very low power efficiency. The power efficiency of Class A amplifier is typically from 5% to 25%. Inefficiency of Class A amplifier introduces serious problems that limit its usage as audio amplifier although it delivers best sound quality. First of all, its low power efficiency results in very high heat dissipation on the amplifier itself when large output power if required. Huge and expensive heat sink is needed. Secondly a powerful power supply is also required in order to drive a Class A amplifier.

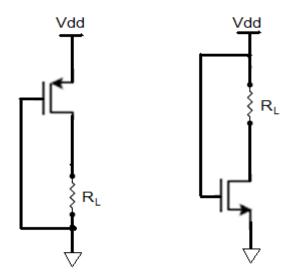

Fig 2.1.1a: Class A amplifier

In Class B amplifier, one output element only conducts half of the input wave cycle. Therefore, its power efficiency is greatly improved compared with Class A amplifier. Theoretically, Class B amplifier has maximum power efficiency up to 78.5%. However, there is trade-off between linearity and power efficiency. Since one output element only conducts in one half cycle and completely off in another half cycle, it creates large amount of distortion. Class B amplifier with single amplifying element is hardly found in application.

Fig 2.1.1b: A single Class B element

Fig 2.1.1c: Class B push-pull amplifier

In practical, the push-pull arrangement is commonly used in constructing Class B amplifier. Two Class B elements work together to form a complementary pair. Each amplifies one half of the input wave cycle and then combines them in the output to generate a full cycle output waveform. Although this architecture performs much better than the single Class B element, it suffers from crossover distortion. This refers to the small mismatch at the crossover point between the two halves of the output signal. This distortion reduces the linearity of the Class B push-pull amplifier. Many attempts have been made to reduce the crossover distortion. One is to bias the output elements to avoid completely turn-off when they're not in use, which is known as Class AB operation. Strictly speaking, Class AB amplifier is not a separate class. It is the combination of Class A and Class B. Each output element in Class AB conducts current more than 50% and less than 100% of input wave cycle, which depending on the biasing of the output devices. Class AB is a good compromise between power efficiency and linearity and it is widely used for audio amplifier.

In general, linear amplifiers have high linearity and low distortion in term of performance. Apart from that, gain of linear amplifiers is constant and it is not a function of supply voltage. Hence, their power supply rejection ratio (PSRR) is also high. However, the power efficiency of linear amplifiers is usually low, which is about 50% typically. Low power efficiency makes it unsuitable to be used in batteries-driven portable electronic devices.

### 2.1.2 Switching Amplifier

Most of time, the switching amplifier refers to Class D amplifier. Its operation is very different from linear amplifiers: The output devices of Class D amplifier operate as switches which are turned completely "on" or completely "off", making their resistance either zero or infinity in ideal case. The output devices are almost not losing any power by operating in this way: when the devices are complete "on", the voltage difference across them is zero; when the devices are complete "off", the current flows through them is zero. Since the power dissipated in the output device is the product of the voltage difference and current flow, ideally, the power dissipated in devices is zero no matter in "on" state or in "off" state. Therefore, the power efficiency of Class D amplifier is 100% theoretically.

However, in reality the power efficiency of Class D amplifier can never reach 100%. This is because there is no ideal switch in practice. The small on-resistance at "on" state and non-infinite resistance at "off" state of the switch dissipates power on the switch itself. Besides the imperfection of the output devices, high frequency switching of the output devices also causes power loss. In real switching process, the output devices cannot be turned "on" or "off" immediately. There is transition time between "on" and "off". During the transition period, neither the current flow nor the voltage difference of the output devices is zero, and hence power is dissipated on the devices. Furthermore, in order to reduce the on-resistance of the output devices, the size of the output devices is usually large. This introduces large parasitic capacitance to the output devices. In the switching process, high frequency charging and discharging of the parasitic capacitance waste power. These power losses related to switching process is named switching loss. It cannot be neglected if the switching frequency is high. Last but not least, the power consumed by signal processing unit and gate driving unit of Class D amplifier further reduce its power efficiency.

In practice, the power efficiency of CMOS Class D audio power amplifier is typically 75% to 90%. High power efficiency implies less heat dissipation on the amplifier and less current requirement. Therefore, the power supply and heat sink requirements are relaxed for Class D amplifier. This helps to reduce the cost and device size. Furthermore, high power efficiency also helps to extend batteries life. Hence, compared to linear power amplifier, Class D amplifier is far more suitable to be used in portable electronic devices such as PDA, MP3 player and notebook.

Fig2.1.2: Power efficiency of Class D VS. Class AB [int]

## 2.2 Performance Metrics for Audio Power Amplifier

The performance of audio power amplifier can be identified by some parameters, for example THD, PSRR, power efficiency and etc. The system parameters below are some of the most important ones.

### **2.2.1** Power Efficiency $(\eta)$

Power efficiency is the ratio of the power delivered to load and the total power delivered by the power supply. To maximise the power efficiency is always one of the design targets regardless of type of the power amplifier.

$$\eta = \frac{P_{out}}{P_{total}} \times 100\% = \frac{\frac{V_{out\_rms}^2}{R_L}}{I_{total\_avg} \times V_{dd}} \times 100\%$$

(Equation 2.1)

### 2.2.2 Dynamic Range (DR)

The dynamic range is specified as the ratio of the rms value of largest possible undistorted sinusoidal signal to the rms value of noise amplitude. The higher the dynamic range, the better the amplifier performances. One can calculate the dynamic range of an amplifier by the following equation:

$$DR = 20 \times \log_{10} \frac{V_{O \max\_rms}}{V_{noise\_rms}}$$

(Equation 2.2)

### 2.2.3 Total Harmonic Distortion (THD)

THD is a measurement of linearity of a system. A non-linear system adds harmonic of original frequencies to introduce distortion to the signal. For audio amplifier, THD should be kept as low as possible so that it can reproduce good sound quality. The following equation shows the calculation of THD commonly for audio specification (percentage THD) :

$$THD = \sqrt{\frac{V_{h2}^2 + V_{h3}^2 + V_{h4}^2 + \dots + V_{hn}^2}{V_{signal}^2}} \times 100\%$$

(Equation 2.3)

### 2.2.4 Signal to Noise Ratio (SNR)

SNR is the measurement that compares the signal level to the background noise level. It is defined as the ratio of the output signal power to the noise power within the bandwidth of interest. SNR can be calculated by the following equation:

$$SNR = 20 \times \log_{10} \frac{V_{signal\_rms}}{V_{noise\_rms}}$$

(Equation 2.4)

### 2.2.5 Power Supply Rejection Ratio (PSRR)

PSRR describes the ability of a device to reject noise from power supply. The definition of PSRR is the ratio of the change in supply voltage to the corresponding change in output voltage of the device. PSRR varies in different frequency and generally it tends to worsen with increasing frequency. Ideal amplifier has infinite PSRR.

$$PSRR = 20 \times \log_{10} \frac{\Delta V_{dd_{-}rms}}{\Delta V_{out_{-}rms}}$$

Equation (2.5)

## 2.3 Conclusion

In this chapter, the basis of Class D power amplifier is presented. It operates very differently from a linear amplifier. Using switching mode of the output device, Class D amplifier can achieve very high power efficiency, which is the main advantage for this type of amplifiers. Besides the Class D amplifier, other types of amplifier such as Class A, Class B amplifiers are briefly introduced in order to visualize the basic differences between switching amplifiers and linear amplifiers.

# Chapter 3: Architectural Design

Due to the switching nature of class D power amplifier, its structure is very different from conventional linear amplifier. The input signal must be modulated into switch control signal before it processes to output stage. In this chapter, the general architectural design of class D amplifier is discussed. An appropriate architecture of each building block is chosen and presented in the second half of this chapter.

### 3.1 General Architecture of Class D Amplifier

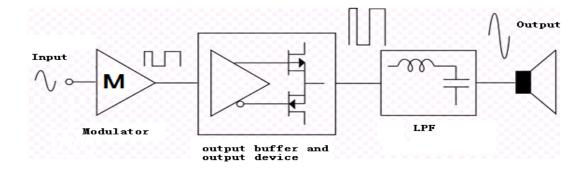

Fig3.1: Block diagram of a Class D amplifier

The above figure shows the general block diagram of a Class D amplifier. There are four main building blocks: signal modulator, output buffer, output devices (switches) and low pass filter (LPF).

The signal modulator is in charge of converting analog input signal into sequence of pulse. This pulse at modulator output is the digital representation of the analog input signal: its average value is directly proportional to the amplitude of the input signal at that time. In order to get an accurate estimation of the input signal, the frequency of pulse must be much higher than the bandwidth of the input signal. The pulse train from signal modulator is fed into the output buffer to generate the output switch control signal to regulate the power deliver to the loads.

The output buffer between the signal modulator and output devices is used for driving the output devices and introducing dead time. The output devices of solidstate Class D amplifier are usually power transistors which are very large in size. The purpose is to reduce the on-resistance to improve the power efficiency. Hence, the input capacitance of the output device is quite large due to its large size. In order to charge and discharge the input capacitance of the output device very fast to reduce the transition time, the output buffer between signal modulator and output power transistors is required. Besides to provide driving power to the gates, output buffer play a role in controlling the dead time to prevent shoot through current at output stage. As mention above, the output device of a Class D power amplifier is usually halfbridge or full H-bridge. They consist of CMOS power transistors and work as switches to supply large current to drive Low Pass Filter (LPF) and speaker. The output signal from the H-bridge is high power pulse train. Unwanted spectral components of this pulse train, for example, the pulse frequency and its harmonics, must be removed by a passive low pass filter to reconstruct the input analog signal. This filter is usually made with (theoretically) lossless components like inductors and capacitors in order to maintain efficiency.

### 3.2 Signal modulation scheme

As shown in the previous section, the input audio signal needs to be converted into switch control signal to regulate the output power transistors to deliver current. This job is done with signal modulator. Although there are many ways to implement signal modulator for class D amplifier, the fundamental principle is the same: to encode information of audio input signal into a pulse stream. The spectrum of modulator output contains both high frequency pulse information and input audio signal content. Generally speaking, those modulation techniques produce bit stream that its pulse width or the pulse frequency is directly proportional to the instantaneous input amplitude. The most common modulation schemes used in class D amplifier are Pulse Width Modulation (PWM) and Sigma Delta Modulation (SDM). SDM technique is adopted in this project.

#### 3.2.1 Pulse Width Modulation

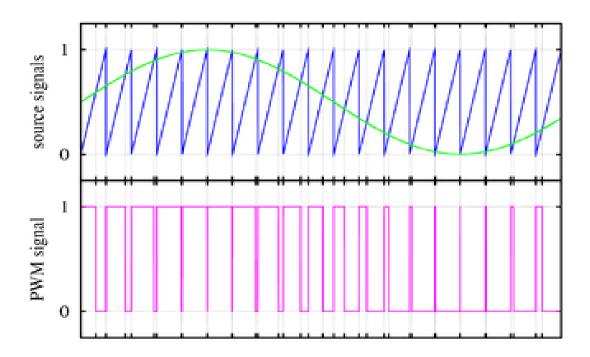

As its name states, the pulse width of PWM modulator output is varying with the amplitude of the input signal. This can be achieved by comparing the input signal to a sawtooth waveform which is running at much higher frequency than the signal band [Kyo08]. Usually the sawtooth waveform has fixed carrier frequency. The pulse train produced by PWM modulator also runs in this carrier frequency. The figure below illustrates the idea of PWM clearly.

Fig3.2: Typical PWM input and output signal

If the audio input signal (green wave) level is higher than the sawtooth signal (blue wave) level, the output of PWM modulator is at high state, and visa versa. We

can see that the frequency of PWM signal is constant, but its duty cycle is changing with the input signal amplitude.

Some attractive features of PWM make it popular in class D amplifier design. Firstly, it can achieve above 100 dB signal-to-noise ratio (SNR) at audio band with as low as hundreds of kHz carrier frequency [Gaa05]. The low carrier frequency implies less power loss due to switching activity. Secondly, PWM modulator is stable at very high percentage of modulation [Gaa05]. This allows PWM to have high output power.

Unfortunately, there are some undesirable features of PWM modulator. First of all, as we can see from figure 3.2, the PWM signal has constant carrier frequency. This introduces concentrated high power peak at carrier frequency in spectrum. Its harmonics produce EMI with the AM radio band. Secondly, PWM process inherently adds distortion in many modulation schemes [Nie97]. One more problem is that when the input signal level is very low, the duty cycle of the PWM signal is very small for high percentage of modulation [Nie97]. It is clearly shown in figure 3.2. This very short pulse width creates problems in gate driving circuit design: if they do not have enough driving capability, they cannot switch fully on output power transistor to reproduce the short pulse. Therefore, full modulation is usually not achievable for PWM base class D amplifier which limits maximum output power of amplifier.

### 3.2.2 Sigma Delta Modulation

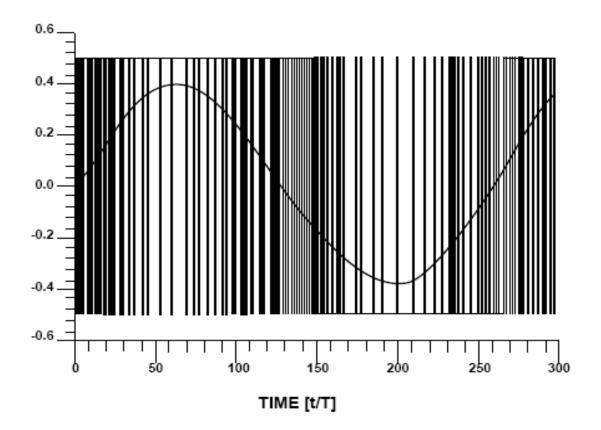

Compare to PWM, SDM encode input audio signal into steam of pulse in different way: instead of changing the duty cycle of pulse train in carrier frequency, SDM varies pulse density according to the input. The number of pulses in a time window is directly proportional to the average value of the input audio signal level at that instant. Therefore, SDM is a kind of Pulse Density Modulation. The typical output waveform of conventional two-level quantization SD modulator is below:

Fig3.3: Typical output waveform of two-level quantization SD modulator

Figure 3.3 clearly shows that the pulse density of the modulator output is directly proportional to the amplitude of the input signal. SM modulator makes a rough evaluation of input signal. The mean output value is equal to the mean input value.

From the above output waveform of SD modulator we can notice some of its interesting characteristics. First of all, its individual pulse width is fixed. This avoids short pulse width problem that imposed by PWM and relaxes the design requirement of gate driving circuit. Secondly, we can see that in time domain the SD modulator output is no longer running at a fixed frequency. It is varying with the input signal. Translate this into frequency domain imply that the high frequency energy in SDM is distributed over a wide range of frequency. This is an advantageous feature over PWM as there is no more concentrated tones at carrier frequency and its harmonics, which is able to reduce the EMI problem.

Apart from the characteristics stated above, there are two important features that make SDM attractive. They are Oversampling and Noise Shaping: Oversampling helps to reduce the quantization noise level while Noise Shaping helps to push in band noise out of band of interest so that the in band noise reduce further. These two features allow SDM to achieve high SNR within band of interest. Since SD modulator is used in this class D amplifier design, more detail on SDM and the structure of SD modulator will be covered in next chapter.

# 3.3 Architectural of output stage

There are two commonly used output architecture for class D power amplifier: Half bridge circuit and full bridge circuit. Half bridge is the single ended output version while full H bridge is a differential implementation of the output power transistors. Each implementation has its pros and cons. In brief, half bridge is potentially simpler to implement while full H bridge has better audio performance. Apart from the output stage topology, the impact of dead time introduced by gate control circuit is also discussed in this section.

### 3.3.1 Half bridge output

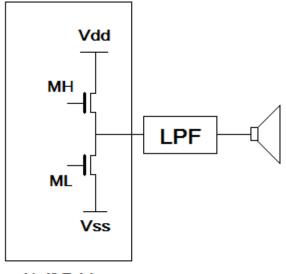

The figure below shows a general half bridge circuit:

Half-Bridge

Fig3.4 Half bridge output circuit

MH and ML are the power transistors to deliver power. When MH turns on, charge is injected into LPF and speaker; when ML turns on, LPF is discharged and the voltage level at the LPF output is reduced. MH and ML are never turn on simultaneously to prevent creating low impedance path between Vdd and Vss.

Half bridge architecture is simpler than full bridge architecture. And it has the same functionality as the full bridge output. However, two disadvantages of half bridge structure limit its usage in class D amplifier:

- Half bridge structure can be powered by bipolar power supplies or single power supplies. However, with single power supplies, a harmful dc bias voltage which is half of Vdd is imposed across the speaker. It creates power loss so that degrades the efficiency of the amplifier. Therefore, this undesirable dc biasing voltage should be removed by inserting a large dc blocking capacitor in between the half bridge circuit and speaker. By doing this, the output filter becomes more bulky and costly.

- Half bridge also suffers from supply voltage pumping effect. Due to the single ended structure, the energy flowing in the output stage is bidirectional. The energy stored in the inductor of output LPF is kicked back into power supply bus. This introduces power supply noise which degrades the performance of class D amplifier. The voltage level of these spikes can be reduced by adding large decoupling capacitor in between Vdd and Vss. This also increases the cost of amplifier. The figure below shows how this pumping effect occurs:

Fig3.5: Supply voltage pumping effect

As the single ended output version, half bridge circuit is simpler to build. However, due to its inferior performance compare to full H bridge, it is not widely used in class D amplifier design.

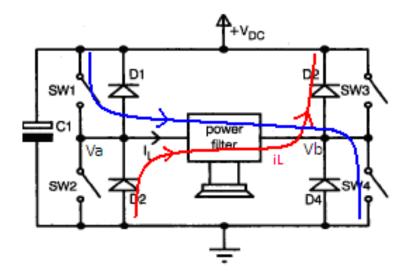

### 3.3.2 Full H bridge output

Full H bridge structure is the differential ended version of the output stage.

The following figure show a full H bridge circuit.

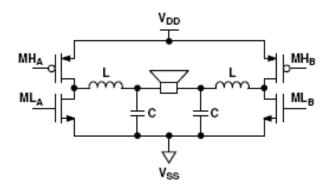

Fig3.6: Differential output stage and its LC LPF

In one time period, MHa and MLb turn on at the same time while the other two are in off state, current flows from Vdd to Vss and delivers power to the speaker. In another time period, MHb and MLa turn on to deliver power.

The full H bridge consists of two half bridge. Hence more components are needed to construct this circuit and its LPF. Although the cost to build full H bridge is higher, it is still much more popular than half bridge due to its superior audio performance:

• First of all, unlike single ended version, full bridge does not suffer from supply voltage pumping effect. This is because the inductor current flowing into one of the half bridge flows out from the other one due to the complementary switching operation of these two half bridge. Therefore, no energy is pumped back into the power supply. Since the gain of class D amplifier is directly proportional to the supply bus voltage, reducing fluctuation in supply voltage implies less distortion introduced in the output signal. The following diagram shows how full H bridge is immune to supply voltage pumping effect:

Fig3.7: Local current loop to prevent pumping effect

- Due to the differential operation, full H bridge topology inherently eliminates even orders harmonic distortion as well as harmful dc biasing offset [Axh07].

Hence, full H bridge usually runs with single power supply without the dc blocking capacitor.

- With the same power supply voltage, the output signal swing of full H bridge topology is two times compares to the single ended implementation. Since power=V^2, the full bridge structure is able to deliver four times output power of half bridge, which is especially valuable in low voltage design [Axh07].

- Another important feature of full H bridge is that 3 level switching operation can be implemented. This switching scheme effectively reduces the differential EMI and the switching activity of the output power transistors.

Since three levels switching operation is one of the most important of this class D amplifier design, full H bridge output stage topology is adopted in this design project.

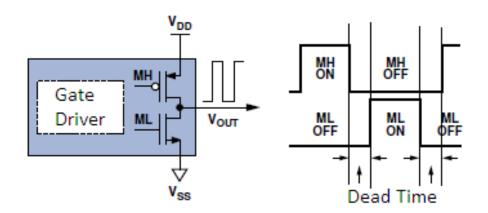

### 3.3.3 Dead time and distortion

The purpose of introducing dead time for output stage control signal is to prevent both PMOS and NMOS of the output power transistors turn on during the transition period. Due to power efficiency requirement, the power transistors have low resistance in order to reduce conduction loss. Simultaneously turning on high side and low side power transistors create a low impedance path that shorts Vdd and Vss directly. This introduces a very large short circuit current which adds on to power loss, and more importantly, the reliability issue on output stage.

Fig3.8: Dead time of output control signal

The above figure shows how dead time, or non-overlapping time, works on the output stage. During the dead time period, both MH and ML are turned off. This operation ensures that one switch starts to turn on only after the other one has been completely turned off. Therefore, there is no low impedance path between Vdd and Vss at any time so that no shoot through current is formed. The voltage across the load depends on the direction and magnitude of the load current during the dead time period [Mos99].

Although the dead time of switching control helps to improve the power efficiency of the amplifier and addresses reliability issue, it also introduces switching timing error in gate control signal at the same time. Since this timing error is the main cause of the nonlinearity, dead time has significant contribution to the distortion of class D amplifier [Mos99]. Next figure shows the mechanism of timing error induced by the dead time. The diodes in this figure are body diodes of the output power transistors. The blue line shows the load current path during conduction period while the red line shows the load current path during the dead time period.

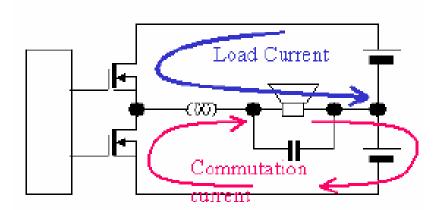

Fig3.9: Current flow in full H bridge

The operation of full H bridge can be categorized into two regions: the single directional output current operation region and bidirectional output current operation region. When the output current is larger than the LPF inductor ripple current, the output current flows in single direction within one whole period and it is in single directional output current operation region. When the output current is smaller than the inductor ripple current, the output current flows in operation region. When the output current is smaller than the inductor ripple current, the output current flows in positive direction in on-time period and it flows in negative direction in off-time period. The full bridge is in bidirectional output current operation region.

During the conduction period of positive single directional output current operation region, SW1 and SW4 turn on. The left side full bridge output Va is at high voltage level. Load current flows from Vdd to ground through SW1 and SW4. Since the output current is larger than the inductor ripple current, it is still flowing in the same direction during the dead time period due to the inductor of LPF. The output current flows from ground to Vdd through the body diodes of SW2 and SW3 as all switches are turned off in this particular period. D2 and D3 conduct and so that node Va is connected to ground. Hence, Va is low during dead time. In another word, the voltage level of left half bridge output node goes low at the instant when SW1 is turned off. In summary, for positive single directional output current operation region, the output voltage only follows the SW1 switching signal from the gate driving stage. Since on-time from modulator is equal to on-time + dead time from gate driver, the on-time of H bridge is shortened by one dead time compare to the correct on-time from modulator. This timing error lowers the gain of class D amplifier. The situation is the same for negative direction output current operation region.

In the bidirectional output current operation region, since the load current is lower than the inductor ripple current, the output current of H bridge returns to zero during the dead time. All the switches and body diodes are in off mode and so that the output node of H bridge is floating and Va is undetermined in this particular period. For simplicity, we can consider that the Va in dead time has the same voltage level before the dead time. In this case, at the instant when SW1 is turned off, node Va is floating and it is in high voltage level since Va is high before SW1 turned off. Therefore, the on-time of the H bridge is on-time of SW1 from gate signal plus the dead time, which is the same as the correct on-time from the modulator. In summary, dead time does not add timing error in bidirectional output current operation region and hence, no variation in the gain of class D amplifier.

Since the output current magnitude is dependent on the audio input signal, operation region of the full bridge output is changing from time to time. As the gain is different for each operation region, the output waveform will be distorted. The gain error is directly proportional to the timing error introduced by the gate driving stage, reducing the dead time decreases the timing error so that the distortion decreases at the same time. Therefore, the dead time should be minimized in order to get good sound quality.

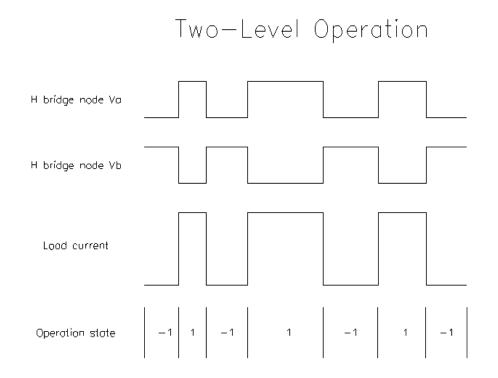

## **3.4** Three level switching scheme for SDM

1 bit quantizer is widely used in SD modulator design due to the simplicity and linearity. It uses 1 bit digital to analog converter (DAC) to implement the feedback. Since the nonlinearity of DAC directly add to the input, and this nonlinearity is not able to be suppressed by the loop filter, the nonlinearity of DAC introduces distortion to the output signal without attenuation. Therefore, the linearity of feedback DAC is very important in SD modulator design. Single bit quantization SD modulator is inherently linear as it only has two output levels and two points define a straight line, and hence it is widely used in design.

However, from figure 3.3, we can notice an interesting phenomenon for 1-bit sigma-delta modulator is that the output switching activity is very high when the input amplitude is small. This is due to the high quantization noise of single bit SD modulator, which makes the output switching frequently between state 1 and state -1 so that its average value is small. This degrades the power efficiency of the class D amplifier for low output power due to high switching loss. Furthermore, because of fully differential switching operation of each half bridge, there is always a conduction current flowing in the output stage. Figure 3.10 in the next page shows the voltage at the output nodes, Va and Vb, of each half bridge and the conduction current flowing

into the load. Va and Vb are always in complementary and only two differential operating states exist, which means current is always flowing between this two nodes. Output current is positive at state 1, while it is negative at state -1. This continuous conduction current induced conduction loss of full bridge output and therefore further degrades the power efficiency.

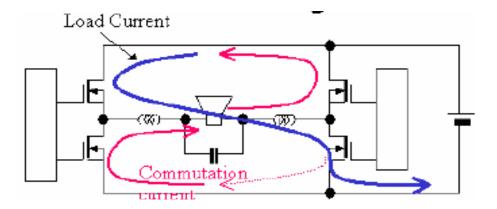

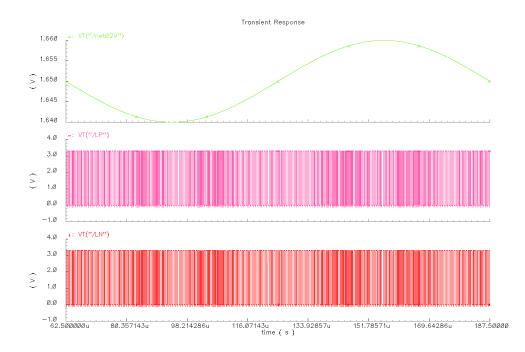

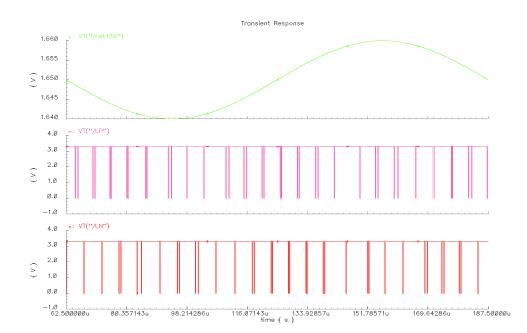

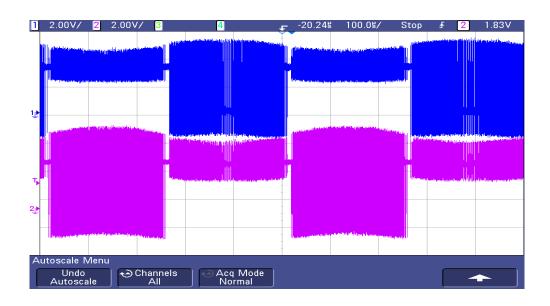

Fig3.10: H-bridge output voltage and load current of 1-bit SD modulator

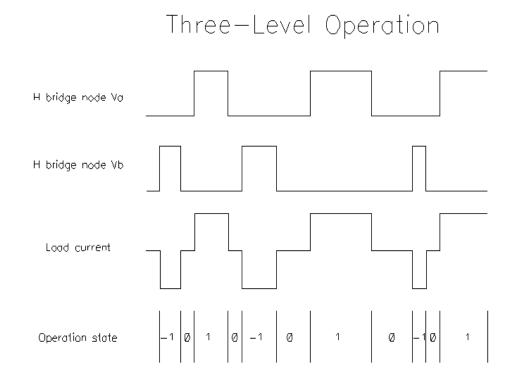

In this design, 1.5 bit quantization SD modulator is adopted and three-level switching scheme is used. Compare to conventional binary switching operation which only processes state 1 and state -1, three-level switching scheme brings in one more state: the state 0. At state 1 and -1, two half bridge outputs Va and Vb are opposite,

while at state 0, two half bridge outputs have the same polarity, either both are at Vdd or both are at ground. This common mode state is used in conjunction with two differential states to produce three-state modulation. The differential input to the LPF of the output stage is positive, zero and negative in three different states. The output voltage of each half bridge and the output current are shown in figure 3.11. At state 0, the output stage current is zero since both Va and Vb are at voltage low. Instead of keep providing current to the load in binary switching scheme, the full H bridge only provides current to the load when it is needed. This greatly reduces the conduction loss due to the imperfect switches.

Fig3.11: H-bridge output voltage and load current of 1.5-bit SD modulator

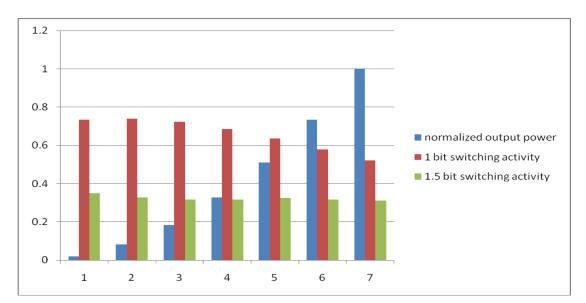

One more advantage of 1.5 bit quantization is that instead of switching frequently between state 1 and state -1 to deliver low output power, the 1.5 bit quantization modulator outputs higher density of state 0 to represent low output power. This prevents high switching activity for low input amplitude and further improves the power efficiency of the amplifier. Figure 3.12 shows the normalized switching activity of the 1 bit SD modulator and 1.5 bit SD modulator with different output power simulated in MatLab:

Fig3.12 Normalized switching activity of 1 bit and 1.5 bit SD modulator at different output power

It is obvious that the switching activity of the full H bridge driven by 1.5 bit SD modulator is lower than the one driven by 1 bit SD modulator, especially when the output power is small. Decrease in differential switching also helps to reduce differential EMI.

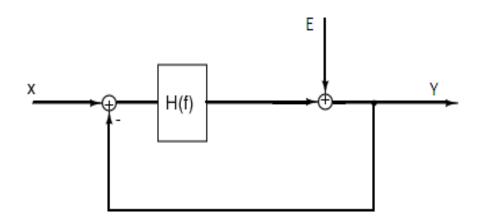

# 3.5 PSRR and Feedback Topology

One of the major drawbacks of class D power amplifier is the poor Power Supply Rejection Ratio (PSRR) [Put03]. Since the output stage is a full H bridge or a half bridge for class D amplifier, the output transistors connecting the power supplies to the LPF which is a very low impedance path. The fluctuation in power supplies bus is directly coupled to the load with very little attenuation. Hence, there is almost no rejection for the power supply noise for the open loop class D amplifier and the PSRR is very low [Put03]. This means a very stable and clean power supply is required to drive the open loop class D amplifier. Furthermore, since the gain of class D amplifier is directly proportional to the bus voltage, variation in bus voltage change the gain of the amplifier which results in distortion at the output. This further degrades the performance of class D amplifier. Figure 3.13 depicts the simplest linear model for an open loop class D amplifier:

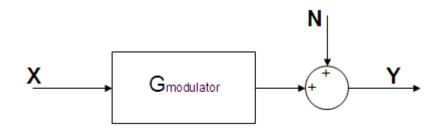

Fig3.13: Linear model for open loop class D amplifier

Where X is the input, Y is the output and N is only considering the power supply noise. The power supply noise transfer function is unity which implies 0 dB PSRR. Although the LPF is able to reject the supply noise outside the signal band, all the noise within audio frequency is passed through and affects the sound quality.

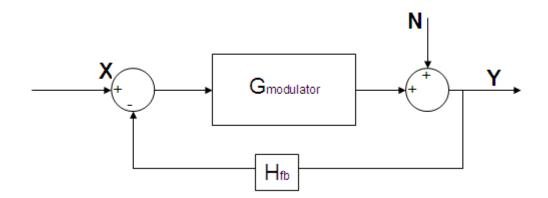

One way to address this issue is to use feedback with high loop gain. This helps to improve PSRR of the amplifier greatly. Besides that, it also attenuates the distortion caused by the bus voltage variation. With this negative feedback, the voltage fluctuation in power supplies is suppressed by the loop filter. Figure 3.14 shows the linear model with feedback.

Fig3.14: Linear model for class D amplifier with feedback

Consider N as the power supplies noise, the noise transfer function is:

$$H_N = \frac{1}{G_{\text{modulator}} \cdot H_{fb} + 1}$$

(Equation 3.1)

We can see that the supplies noise is suppressed by the loop gain of the filter. If the loop gain is very large within the audio band, which is the case in SD modulator class D amplifier, the noise will be attenuated greatly. Hence, the PSRR of the amplifier is improved.

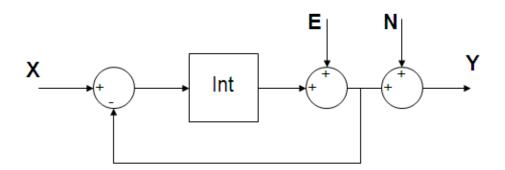

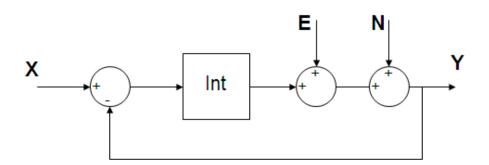

SD modulator is used in this design. It is a feedback system which suppresses the quantization noise. If we adjust the feedback loop so that to include the power supplies noise, the PSRR of the whole system will be improved a lot. This concept is illustrated in figure 3.15(a) and 3.15(b).

Fig3.15(a): Model of SDM class D amplifier with feedback from quantizer

Fig3.15(b): Model of SDM class D amplifier with feedback from H bridge

E is the quantization noise and N is the power supplies noise. By shifting the feedback point from quantizer of SD modulator to the H bridge output of class D amplifier can include both the quantization noise and power supplies noise. This feedback topology guarantees the design to be able to achieve high PSRR.

### **3.6** Overall architectural design

Fig3.16: Block diagram of proposed class D amplifier

Figure 3.16 depicts the proposed overall architectural design for this class D amplifier. Those blocks in gray areas are the on-chip components. A 1.5 bit SD modulator is used in this design to reduce the switching loss and conduction loss. A full H-bridge output stage helps to deliver more power and to eliminate the 2nd order harmonic distortion. The output of full H-bridge is fed back directly to the input of the modulator to improve PSRR of the class D amplifier. A zero-dead-time gate driving circuit is used in this design to minimize the distortion introduced by timing error. The gate driving circuit is designed in a way that the transition time for the gate control signal is very short to minimize the short circuit conduction loss. Due to low cut-off frequency, the lossless LC LPF is not able to be integrated onto the chip and it is built on the testing PCB.

# Chapter 4: Sigma-Delta Modulator Design

Signal modulator is the most important building block for a class D power amplifier. Pulse width modulation scheme and sigma-delta modulation scheme are commonly used for the signal modulator design. In this design, a three-levelquantization SD modulation scheme is chosen. The oversampling and noise shaping features of SD modulator helps to improve performance of class D amplifier.

The design details of the SD modulator for this project are discussed in this chapter. It consists of three major parts. In the first part, the basic principle of SD modulation is introduced and its main features are discussed. In the second part, the system level design of the SD modulator is cover. The system parameters and the architecture of the SD modulator are determined in this part. The system level design is mainly done by doing behavioural simulation in MatLab. The circuit implementation of the SD modulator and the transistor-level design of its building blocks are covered in the last part.

# 4.1 Basis of Sigma-Delta Modulator

Before going into the detail discussion of SD modulator design, a brief introduction on conventional SD modulation is given for better understanding.

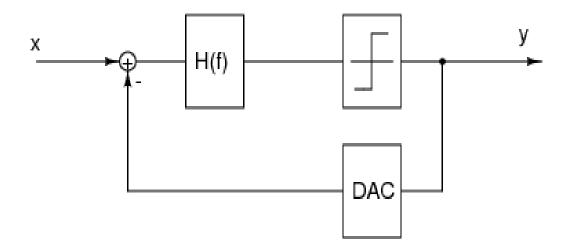

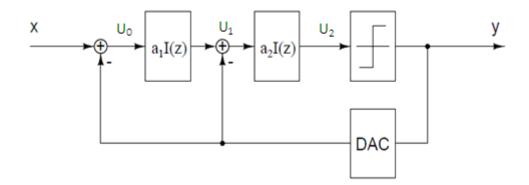

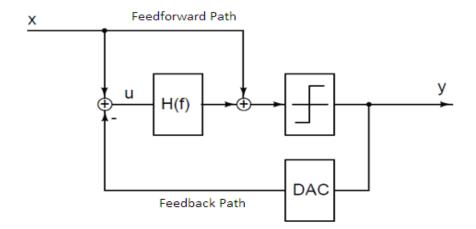

Fig 4.1: Structure of simplest single loop 1st order SD modulatorf

Figure 4.1 shows the simplest conventional sigma-delta modulator. It is configured as a closed loop using negative feedback, and has the noise-shaping property that removes the nonlinear components within the signal band [Kyo08]. The analog input, X, is fed to an integrator, and the output of the integrator is fed to a quantizer (A/D converter). The output of the modulator, Y, is converted back to analog signal by DAC and subtracted from the analog input. This feedback forces the

output of modulator, Y, tracks closely to the analog input signal, X, and so that the average value of the quantized signal is equal to the average value of input signal.

In order to study how the SD modulator process signal and noise, the linear model for conventional 1st order SD modulator needs to be built. The tricky part on building up this linear model is the existence of quantizer, which is a non-linear element. Since the output bitstream of the modulator contains the average input value, this bitstream can be seen as the combination of input and large magnitude noise. Therefore, the quantizer can be modelled as a signal source which adds noise to the input. Here is the linear model for the conventional 1st order SD modulator.

Fig 4.2: Noise Injection model for 1st order conventional SD modulator

The signal transfer function and noise transfer function for this conventional sigma-delta modulator are shown below:

Signal transfer function:

$$S_{(f)} = \frac{H_{(f)}}{1 + H_{(f)}}$$

(Equation 4.1)

Noise transfer function:

$$N_{(f)} = \frac{1}{1 + H_{(f)}}$$

(Equation 4.2)

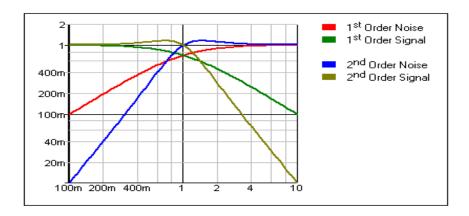

If H(f) is chosen to have high magnitude within the signal band, it is clear that S(f) becomes close to unity while N(f) become very small within band of interest. The SD modulator can be seen as a band pass filter for signal X and band stop filter for noise E. However, the noise outside the signal band is not reduced by the feedback system as the loop gain outside the signal band is small. For class D amplifier application, the out-of-band noise can be filter out by the LPF at the output stage.

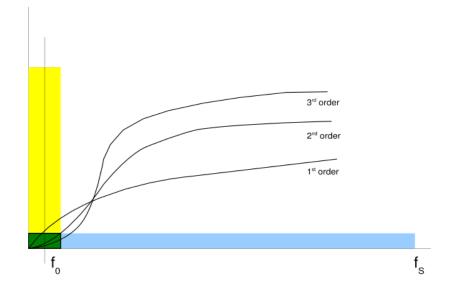

This is the noise shaping feature of sigma-delta modulation. It can reduce the in band noise and hence, improve the SNR in the signal band. The following figure illustrates this concept.

Fig 4.3: Frequency response of SD modulator due to Noise shaping

Fig 4.4: Conventional 2nd order single loop SD modulator

The 2nd order SD modulator contains two integrators inside the loop. The noise shaping is more aggressive if the orders of the loop filter increase. As we can see from figure 4.3, the 2nd order loop has steeper slop at the low frequency. This implies that the 2nd order loop have better noise rejection ability and so that its output has higher SNR than the one produced by 1st order loop filter.

Another important feature of sigma-delta modulator is oversampling. In order to prevent anti-aliasing, signal is usually sampled in its Nyquist rate. If the sampling rate is higher than the signal's Nyquist rate, it is called oversampling. If the maximum signal bandwidth is  $f_o$  and the sampling rate is  $f_s$ , the oversampling ratio can be calculated by:

$$OSR = \frac{f_s}{2f_o}$$

(Equation 4.3)

The advantage of oversampling is that it uniformly distributes the quantization noise across fs rather than fo. This reduces the quantization noise level according to the OSR. The plot below explains this concept:

Fig 4.5: Quantization noise in Nyquist rate sampling and oversampling

The total quantization noise is the same for both in a Nyquist converter (in yellow) and in an oversampling converter (in blue), but it is distributed over a larger spectrum. The quantization noise level for the oversampling converter is 1/OSR of the quantization noise level for the Nyquist converter. Therefore, the higher the oversampling ratio, the better the SNR performance. The curves in figure 4.5 shows the noise shaping ability of 1st, 2nd and 3rd order SD modulator respectively.

# 4.2 Sigma-Delta Modulator System Level Design

System level design is important science optimization in block level help to relax the constrains in circuit level design. In this section, system level issues are covered, includes SD modulator topology selection, stability issue and system level parameters optimization. Besides that, a novel SD modulator topology is introduced and its advantages over conventional topology are discussed in this section.

### 4.2.1 System level Design parameters

In this section, the major design parameters in system level are briefly introduced and the design strategy is also discussed.

### 4.2.1.1 Modulator architecture

Generally speaking there are two types of SD modulator architectures: single loop SD modulators and cascaded SD modulators.

As the name stated, the single loop architecture consists of only one single SD loop in the modulator. It is the simpler and easier-to-build architecture since the building blocks requirement is relaxed comparing to cascaded architecture, especially the gain of the OTAs. The major drawbacks of single loop architecture are its weaker noise shaping ability and its instability. A high order single loop SD modulator tends to suffer from oscillation when the input signal level is large.

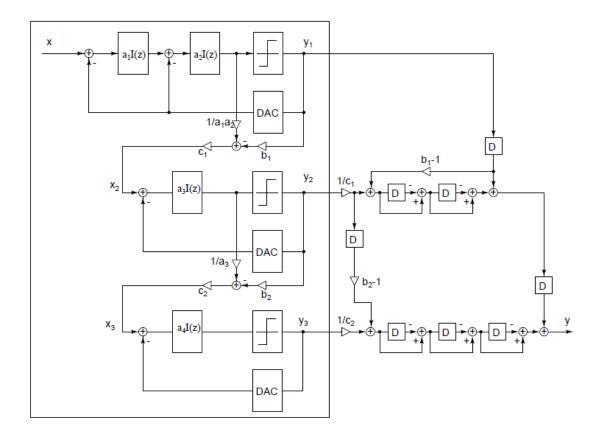

The cascaded architecture consists of cascading several single loop SD modulators. Fig 4.6 shows an example of a 4<sup>th</sup> order cascaded SD topology. Theoretically, orders of single loop SD modulator used for cascading is not restricted. However, low order of SD modulator is used in each cascade stage in practice for stability purpose. The main advantages of cascaded architecture are the high linearity and good stability. With proper design, a cascaded SD modulator can have high order loop filter yet remains stable. Therefore, it can achieve higher SNR than single loop architecture. However, due to noise leakage problem of cascaded architecture, requirement of the building blocks is very high. Since finite OTA dc gain, settling error of integrator and mismatch of loop coefficient are the main causes of noise leakage, very high OTA dc gain is require.

Since the cascaded architecture is highly sensitive to the nonlinearity of building blocks, its implementation is very difficult. And hence, the single loop architecture is adopted in this design project.

Fig 4.6: A 4<sup>th</sup> order cascaded 2-1-1 SD modulator [Yao05]

### 4.2.1.2 Oversampling ratio

Section4.1 shows that higher oversampling ratio (OSR) results in lower quantization noise level. SNR of a SD modulator can be increased by using higher OSR. For a Nth order SD modulator, doubling of OSR results in (0.5+N) bit increase in SNR. Unfortunately, speed limitation of circuit implementation does not allow OSR going too high. In practice, lower OSR is preferred to achieve the same modulator performance. This is because reducing OSR helps to relax the speed requirement of the circuit and helps to decrease the switching activity of class D amplifier output stage.

### 4.2.1.3 Loop coefficient

The stability issue of single loop SD modulator which is greater then 2nd order is addressed by the loop coefficient of the loop filter. Increase in loop coefficient results in more aggressive noise shaping and hence, better SNR in signal band. However, large loop coefficient make the loop filter become more prone to instability. Therefore, there is a trade-off between the linearity performance and stability when choosing the loop coefficient. A balance between SNR and stability is needed for the optimization of loop coefficient.

### 4.2.1.4 Order of loop filter

Order of loop filter can be increased by inserting integrator into the forward path of the loop. As shown in Fig 4.5, noise shaping ability increases when the order of loop filter is getting higher. Hence, higher order loop filter helps SD modulator to get better SNR performance. However, the stability becomes the major concern for high order single loop SD modulator. The loop coefficient should be reduced to maintain the stability of the modulator when the order of loop filter increases. Since SNR performance decreases when the loop coefficient reduced, further increase in the order will not gain much increase in SNR if the order of the loop filter is already high. In summary, the SNR performance of a single loop SD modulator is limited by the stability requirement. In practice, the loop filter of SD modulator is usually 3<sup>rd</sup> order to 5<sup>th</sup> order.

#### 4.2.1.5 Number of bit for quantizer

Single bit quantizer is very popular in the SD modulator design because of the intrinsic linearity of single bit DAC in the feedback path. Nevertheless, the amplitude of quantization noise is large due to single bit quantization. This results in some problems like low SNR, high internal signal swing and more prone to instability comparing to the one using multi-bit quantizer.

By employing multi-bit quantizer, the SD modulator can have better loop stability due to its lower amplitude of quantization noise. Therefore, the order of loop filter can be increased and larger loop coefficient can be used. As a result, the SNR performance of multi-bit quantization SD modulator is superior than single-bit quantization SD modulator provided the linearity of multi-bit DAC in the feedback path is very high. However, designing a highly linear multi-bit DAC is not an easy task. Although there are many linearization techniques for DAC design, they have some drawbacks and greatly increase the complexity of design. More importantly, since the multi-bit DAC is at the feedback path, its nonlinearity can not be suppressed by the loop filter but just added to the output directly.

In this project, a 1.5-bit quantizer is adopted for the SD modulator design as the three-level-switching scheme is used for the full H-bridge output stage.

### 4.2.2 Stability analysis of single loop SD modulator

Since SD modulator is a feedback system, stability issue is one of the potential problems that need to be addressed in system level design. In previous analysis, we know that increasing the order of the loop filter can enhance the noise shaping ability and so that the modulator can achieve higher in band SNR. However, the single loop SD modulator structure is prone to instability if the order of the loop filter is greater than two [Can85]. And the modulator tends to be more unstable if the order of the loop filter increase.

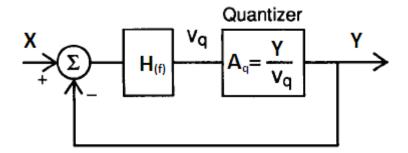

In order to analyse the stability of the SD modulator, an appropriate linear model needs to be built. It is not an easy task as SD modulator is a highly nonlinear system due to the existence of quantizer. The noise injection linear model used in section 4.1 models the quantizer by a linearized gain stage with an additive noise source to represent the distortion component introduce by the quantizer. Although this linear model can predict the noise shaping of the modulator, it provides insufficient information to analyze the stability of SD modulator. Therefore, a more versatile model needs to be used for the stability analysis. In this chapter, the variable gain linear model is employed for stability analysis. In this model, the nonlinear quantizer is modelled as a linear gain stage with arbitrary gain value which is depending on the input and output value of the quantizer [Bai94].

Fig 4.7: Variable gain linear model for SD modulator

Fig 4.7 shows the variable gain linear model. Vq and Y are the input and output of quantizer respectively. Aq is the variable quantizer gain which solely depends on the instantaneous value of Y and Vq. Since the quantizer output Y only has two voltage levels: voltage high or voltage low, Aq is small if the amplitude of Vq is large, and vice versa. Modelling the quantizer in this way allows root locus techniques to be applies in investigating system stability. The root moves along the locus as the linearized quantizer gain change. If the gain falls into the locus segment that is outside the unit cycle, the system becomes unstable. As a result, signal input level tends to be large due to feedback. The transfer function of variable gain model is:

$$\frac{Y_{(s)}}{X_{(s)}} = \frac{A_q \bullet H_{(s)}}{1 + A_q \bullet H_{(s)}}$$

(Equation 4.4)

Fig 4.8: Root locus of the poles for 3<sup>rd</sup> order conventional SD modulator

Α

Fig 4.8 shows the root locus for 3<sup>rd</sup> order modulator with loop coefficient [0.25 0.5 1] [Bai94]. The poles of the system move due to the quantizer gain Aq. There are two locus need to be analysis separately. For the one along Real axis, the pole of system goes outside the unit cycle when Aq goes to infinity. That means the system becomes unstable and the signal level in the modulator will increase. As the quantizer input level increases, Aq will decrease. This will drift this pole back within the unit cycle and the system stability is restored. Therefore, the system is stable if the quantizer gain is very large.

For the 2<sup>nd</sup> locus, this pair of complex poles are within the unit cycle when the quantizer gain is very large. However, as Aq decrease to a critical point, Aq\_crit, the poles move outside the unit cycle. The system becomes unstable and the quantizer input level is getting larger and larger. The increase in quantizer input further reduces the quantizer gain, and the roots move along the locus outside the unit cycle instead of moving back inside. Hence, if the quantizer gain is smaller than Aq\_crit, the system becomes unstable. In another word, the modulator becomes unstable when the quantizer input level is very large.

This stability analysis gives insight that how to make SD modulator stable. Generally speaking, the system becomes unstable if the internal signal level becomes too large. Another thing to mention here is that if the loop coefficient decrease or the integrator delay reduces, the value of Aq\_crit also reduces. This implies the loop filter can accommodate larger internal signal and thus the modulator becomes more stable.

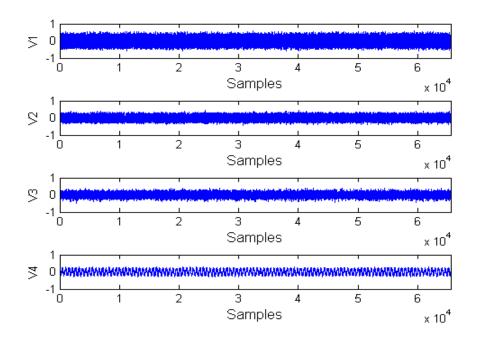

## 4.2.3 Fully feed-forward topology

Feed forward is another type of control system comparing to feedback. Feed forward control is an open loop system which applies the compensation control signal directly to the controller before error appears. Hence, it controls the system before the output making error. However, the compensation control signal of a feedback loop is based on error signal, which means feedback loop controls the system after making error. Therefore, feed forward control is much faster than the feedback control. Nevertheless, due to the "open loop" nature of feed forward control, it is not able to tell if the output produces error. This is the major drawback of feed forward control. To overcome this problem, feedforward-feedback combination control system is developed. The feed forward path helps system to react fast while the feedback loop can correct the residual error which is not compensated by the feed forward control.

Fig 4.9: 1<sup>st</sup> order single loop fully feed forward SD modulator

Figure 4.6 shows a 1st order single loop fully feed forward SD modulator. It is a feedforward-feedback combination control system. The feed forward topology has the main advantages of conventional SD modulator: oversampling and noise shaping. It has some unique characteristics. Equation 4.5 and 4.6 are the signal transfer function and noise transfer function for this single loop feed forward SD modulator:

Signal transfer function:

$$S_{(f)} = 1$$

(Equation 4.5)

Noise transfer function:

$$N_{(f)} = \frac{1}{1 + H_{(f)}}$$

(Equation 4.6)

The noise transfer function of fully feed forward topology is identical to that of conventional SD modulator, which implies that it has the same noise shaping ability as the conventional structure. More interestingly, the signal transfer function for the feed forward SD modulator is unity. It does not contain any terms related with H(f). This unity signal transfer function means that the non-linearity of the building blocks will not contaminate the input signal [Kyo08]. Therefore, the harmonic distortion introduced by the non-linearity of the loop filter is significantly reduced comparing to conventional SD modulator. This unity signal transfer function feature is attractive in design. Since the effect of nonlinearity of the building blocks in feed forward is not as significant as in conventional topology, the design requirements for each building block is relaxed [Sil01][Gha06]. This means lower OTA gain can be used in design which makes design much easer.

Another major different between fully feed forward topology and conventional topology SD modulator is the input signal of the loop filter, U. Although the input signal of the loop filter is different between the modulator input and modulator output feedback signal for both feed forward topology and conventional topology, the signal contain of U is different for these two topologies due to the delay of the integrators in the loop filter. For the conventional SD modulator, the modulator input signal, X, needs to go through the integrators in the loop filter to reach the quantizer. Due to the integrators delay, the modulator output, Y, is the delayed version of the modulator input, X. For example, the Fig. 4.4 shows a conventional 2nd order SD modulator. The signal U2 at the quantizer input has two integrators delay comparing to X. According to the signal and noise transfer function of conventional SD modulator in Equation 4.1 and Equation 4.2, the quantizer input can be written as:

$$U_{(f)} = X_{(f)} - Y_{(f)} \text{ and } Y_{(f)} = S_{(f)} \bullet X_{(f)} + E_{(f)} \bullet N_{(f)}$$

$$U_{(f)} = (1 - S_{(f)}) \bullet X_{(f)} - N_{(f)} \bullet E_{(f)}$$

$$U_{(f)} = \frac{1}{1 + H_{(f)}} \bullet X_{(f)} - N_{(f)} \bullet E_{(f)}$$

(Equation 4.7)

Equation 4.7 clearly shows that the input signal of loop filter contains both the quantization error and the high pass version of the modulation input signal, X. This high pass version of X is restored to its full amplitude by the integrators in the loop [Sil01], which makes the internal signal swings in the loop filter to be high. This high internal signal swing reduces the overload level of the modulator and makes the modulator more susceptible to instability.

For the fully feed forward topology, due to the existence of feed forward path, the modulator input signal, X, is brought to quantizer input directly instead of passing through the integrators. Therefore, the output signal, Y, has no delay [Sil01]. Hence, the input and output of the modulator can cancel out at the input of loop filter. There is no high pass version of X in the error signal U.

The following paragraph derives the input signal of the loop filter, U, for fully feed forward SD modulator.

$$\begin{aligned} Y_{(f)} &= S_{(f)} \bullet X_{(f)} + E_{(f)} \bullet N_{(f)} \quad \text{and} \quad S_{(f)} = 1 \\ \\ Y_{(f)} &= X_{(f)} + E_{(f)} \bullet N_{(f)} \\ \\ U_{(f)} &= X_{(f)} - Y_{(f)} = -E_{(f)} \bullet N_{(f)} \end{aligned}$$

(Equation 4.8)