## DEVELOPMENT AND CHARACTERIZATION OF HIGH-K DIELECTRIC/GERMANIUM GATE STACK

**XIE RUILONG**

(B.Eng. (Hons.), NUS)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE DECEMBER 2009 To Guo Qian

## ACKNOWLEDGMENTS

First and foremost, I would like to express my deepest gratitude to my principle advisor, Professor Zhu Chun Xiang for his knowledge, constant guidance and encouragement throughout the course of my research. He was always there to listen and to give advice. He showed me different ways to approach a research problem and the need to be persistent to accomplish any goal.

I would like to gratefully thank my co-supervisors Dr. Yu Ming Bin for his kindly support and all the opportunities provided in collaboration with Institute of Microelectronics, and Professor Li Ming Fu for his valuable suggestions and the fruitful discussions. I am also very grateful to Chartered Semiconductor Manufacturing, Ltd. for the financial support and to Dr. Chan Lap and Dr. Ng Chee Mang not only for their teaching and training but also for their valuable advice on my future career.

I would like to express my warmest thanks to Dr. Wu Nan and Dr. Zhang Qing Chun for many stimulating and joyful discussions. Special thanks to Sun Zhi Qiang, He Wei, and Shen Chen for their important helps in experiments and device characterizations. I would like to thank my colleagues in Prof. Zhu's group, such as Yu Xiong Fei, Huang Ji Dong, Zhang Chunfu, Song Yan, Fu Jia, Yang Jian Jun and Phung Thanh Hoa, for their discussions and supports. Many thanks to my peers in SNDL: Ren Chi, Wang Xin Peng, Gao Fei, Chen JingDe, Rinus Lee, Zang Hui, Jiang Yu, Pu Jing, Zhang Lu, Yang Wei Feng, Wang Jian, Peng Jian Wei, Chin Hock Chun and Liu Bin. I have benefited the collaboration work with them, and their friendship makes my stay in NUS more enjoyable. I also would like to extend my appreciation to all other SNDL teaching staff, fellow graduate students, and technical staff.

I also would like to express my appreciation to Ma Yu Wei and Du Guo An from Chartered SP group for their valuable discussions.

Last but not least, my deepest thanks to my wife, Guo Qian, whose tremendous understanding and support throughout those four years have made this work possible. Special recognition also belongs to my parents, who through my childhood and study career had always encouraged me to follow my heart and inquisitive mind in any direction.

## **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS      | III          |

|-----------------------|--------------|

| TABLE OF CONTENTS     | $\mathbf{V}$ |

| ABSTRACT              | IX           |

| LIST OF FIGURES       | XI           |

| LIST OF TABLES        | XVIII        |

| LIST OF SYMBOLS       | XIX          |

| LIST OF ABBREVIATIONS | XXII         |

## 1. Introduction

| 1.1.  | Challenges of MOSFETs scaling and possible solutions            | .1 |

|-------|-----------------------------------------------------------------|----|

| 1.2.  | High-k gate dielectrics                                         | .3 |

|       | 1.2.1. Limits of SiO <sub>2</sub> scaling                       | 3  |

|       | 1.2.2. Alternative gate dielectrics                             | 5  |

| 1.3.  | Ge MOSFETs                                                      | .8 |

| 1.4.  | Current status of Ge channel MOS devices with high-k dielectric | 11 |

| 1.5   | Thesis outline and original contributions                       | 23 |

| Refer | ences                                                           | 25 |

## 2. Effects of Sulfur Passivation on High-k/Ge Gate Stack

| 2.1.   | Experiments             | .32 |

|--------|-------------------------|-----|

| 2.2.   | Results and discussions | 32  |

| 2.3.   | Conclusions             | .44 |

| Refere | nces                    | 45  |

### 3. Effects of Silicon Nitride Passivation on High-k/Ge Gate Stack

| 3.1.   | Experiments                                       | 48 |

|--------|---------------------------------------------------|----|

| 3.2.   | Physical effects of silicon nitride passivation   | 48 |

| 3.3.   | Electrical effects of silicon nitride passivation | 54 |

| 3.4.   | Conclusions                                       | 59 |

| Refere | nces                                              | 51 |

## 4. High-k Gate Stack on Germanium Substrate with Fluorine Incorporation

| 4.1. | Principle and criteria of post gate treatment                     |

|------|-------------------------------------------------------------------|

| 4.2. | Effects of F incorporation without pre-gate surface passivation67 |

|      | 4.2.1. Experiments                                                |

|      | 4.2.2. Results and discussions                                    |

|      | 4.2.3. Summary                                                    |

| 4.3.   | Effects of fluorine incorporation with Si pre-gate surface passivation | .74 |

|--------|------------------------------------------------------------------------|-----|

|        | 4.3.1. Experiments                                                     | .74 |

|        | 4.3.2. Results and discussions                                         | .75 |

| 4.4.   | Conclusions                                                            | .80 |

| Refere | nces                                                                   | .82 |

# 5. Interface Engineered High Mobility High-k/Ge pMOSFETs with 1 nm Equivalent Oxide Thickness

| 5.1.   | Effects of F incorporation and FGA on TaN/HfO <sub>2</sub> /GeO <sub>2</sub> /Ge MOS capacitors86 |

|--------|---------------------------------------------------------------------------------------------------|

|        | 5.1.1. Experiments                                                                                |

|        | 5.1.2. Results and discussions                                                                    |

|        | 5.1.3. Summary                                                                                    |

| 5.2.   | Ge pMOSFEs with 1 nm EOT94                                                                        |

|        | 5.2.1. Device performance of Ge pMOSFETs94                                                        |

|        | 5.2.2. Interface characterization100                                                              |

|        | 5.2.3. Discussions                                                                                |

| 5.3.   | Conclusions109                                                                                    |

| Refere | nces                                                                                              |

| 6.2.   | Results and discussions | 116 |

|--------|-------------------------|-----|

| 6.3.   | Conclusions             | 121 |

| Refere | ences                   | 122 |

#### 7. Conclusions and Recommendations

| 7.1.  | Conclusions124                     |

|-------|------------------------------------|

| 7.2.  | Recommendations for future work128 |

| Refer | ences                              |

Appendix – Computer Programs

**List of Publications**

132

## ABSTRACT

Scaling of the gate stack has been a key to enhancing the performance of complementary metal-oxide-semiconductor (CMOS) field-effect transistors (FETs) of the past 40 years. However, as the metal-oxide-semiconductor field-effect transistors (MOSFET) continues to scale down to tens of nanometers, Si/SiO<sub>2</sub> based device is approaching its fundamental limits, the motivation for alternative gate stacks has increased considerably. High-k/Ge gate stack is very promising for future nanoscale devices because it improves the device performance in terms of both drive current and power consumption. The most important technical issue for high-k/Ge MOSFET technology is the passivation of the Ge surface.

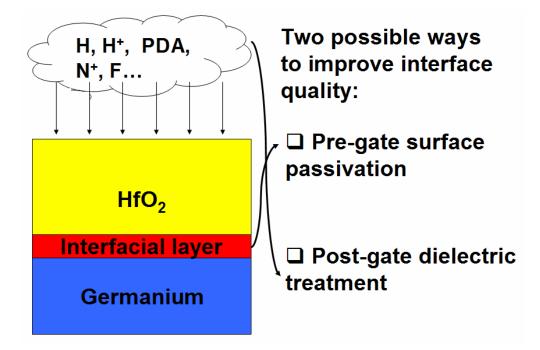

In this study, two approaches to improve the high-k/Ge interface qualities were investigated. The first approach was using pre-gate surface passivation for high-k/Ge gate stack. Two pre-gate surface passivation techniques were investigated. The first one was the sulfur passivation. We found that the Ge diffusion was suppressed by introducing sulfur atoms at high-k/Ge interface, due to less  $\text{GeO}_x$  (x < 2) formation, and consequently, the interface trap density ( $D_{it}$ ) was significantly reduced. However, device with sulfur passivation presented a large amount of hysteresis. The second one was silicon nitride passivation by SiH<sub>4</sub>-NH<sub>3</sub> treatment. This was an improved version of Si passivation. We found that ultrathin silicon nitride layer was more effective to suppress the Ge diffusion than ultrathin Si layer. Moreover, the unexpected positive threshold voltage shift was also eliminated by using silicon nitride passivation, which was attributed to the suppressing of interfacial dipole formation.

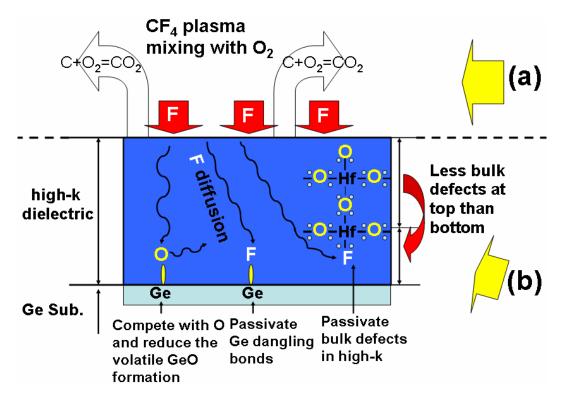

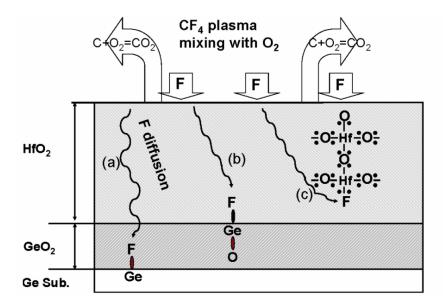

The second approach to improve the high-k/Ge interface quality is to adopt proper post-gate treatment processes. For the first time, we proposed and demonstrated a postgate CF<sub>4</sub> plasma treatment process to incorporate fluorine (F) into high-k/Ge gate stacks. We found that F tends to segregate at high-k/Ge interface upon thermal annealing and both the interface quality and high-k bulk quality were significantly improved by F incorporation. This was attributed to the Ge-F and Hf-F bonds formation at interface and in the bulk high-k, respectively. The post-gate treatment was found to be compatible with pre-gate surface passivation. By applying both techniques on high-k/Ge gate stack, the optimum interface quality was able to be achieved.

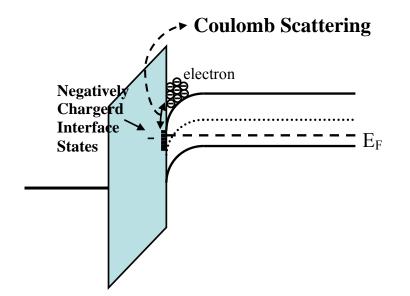

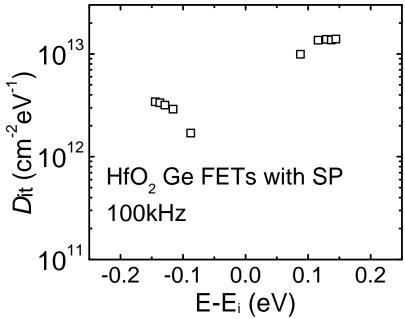

Variable rise/fall time charge pumping method was also used to characterize the interface properties of Ge MOSFETs. We found that F passivation was capable to reduce interface traps that located in the both bottom half and upper half of the Ge bandgap. It was also observed that  $D_{it}$  distribution in Si passivated Ge MOSFETs was asymmetric with much higher density in the upper half of the Ge bandgap. Those traps can act as Coulomb scattering centers when the MOSFETs operate under inversion, which can be possible cause of severe electron mobility degradation for Ge nMOSFETs.

## List of Figures

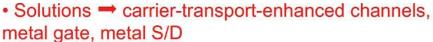

- Fig. 1.1. Tradeoff factors among short-channel effects, on current ( $I_{on}$ ) and power 2 consumption under simple device scaling and possible solutions to mitigate the relationship. Critical device or physical parameters to provide the tradeoff, such as power-supply voltage  $V_{dd}$  and threshold voltage  $V_{th}$ , are shown between the two indexes, and also, the physical mechanisms causing the tradeoffs are shown inside the boxes

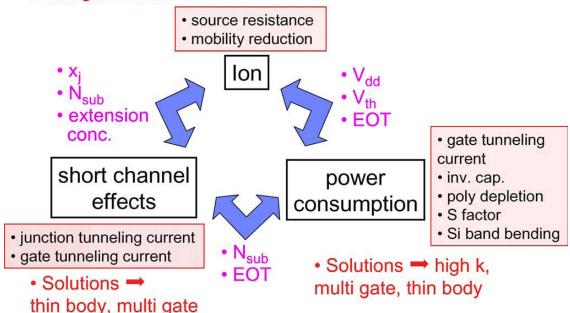

- Fig. 1.2. (Left) Schematic energy band diagram of an n-Si/SiO<sub>2</sub>/metal gate structure, 4 illustrating direct tunneling of electrons from the Si substrate to the gate.  $\phi$  is the energy barrier height at the Si/SiO<sub>2</sub> interface, V<sub>ox</sub>, the potential drop in the SiO<sub>2</sub> layer and V<sub>G</sub>, the applied gate voltage. (Right) Simulated tunneling current through a MOS as a function of the potential drop in the gate oxide, V<sub>ox</sub>, for different SiO<sub>2</sub> gate layer thickness. Shaded areas represent the maximum leakage current specified by the ITRS for high performance and low operating power application, respectively.

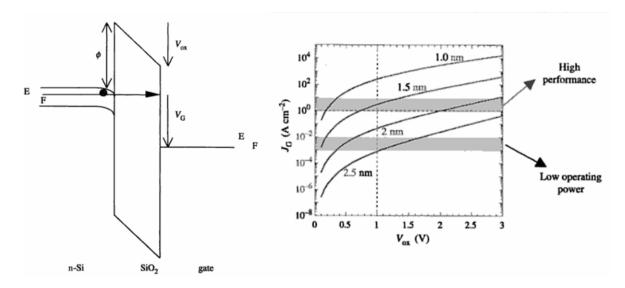

- Fig. 2.1. XPS data in S 2p region from Ge(100) substrates after only HF clean or after 33  $HF + (NH_4)_2S$  treatment.

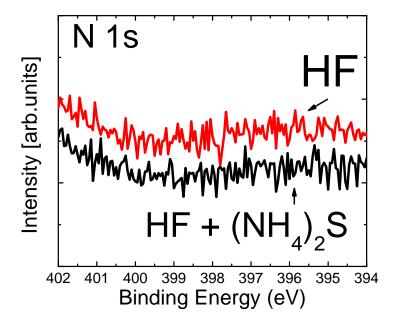

- Fig. 2.2. XPS data in N 1s region from Ge(100) substrates after only HF clean or 33 after HF +  $(NH_4)_2S$  treatment.

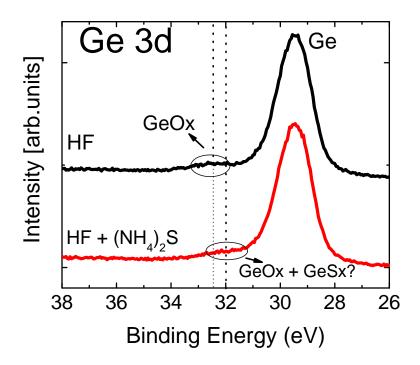

- Fig. 2.3. XPS data in Ge 3d region from Ge(100) substrates after only HF clean or 34 after HF + (NH<sub>4</sub>)<sub>2</sub>S treatment.

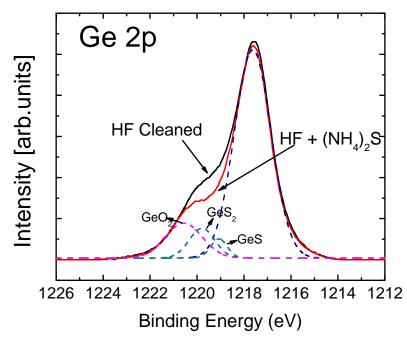

- Fig. 2.4. Fig. 2.4. XPS data in Ge 2p region from Ge(100) substrates after only HF 34 clean or after HF +  $(NH_4)_2S$  treatment. The dot lines are deconvoluted peaks for sample with  $(NH_4)_2S$  treatment.

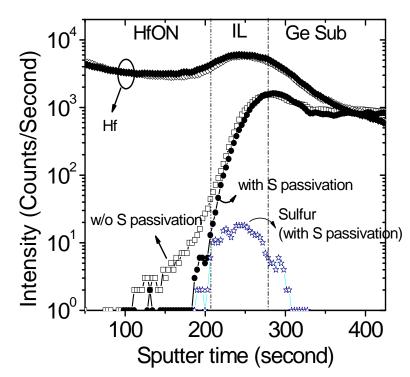

- Fig. 2.5. SIMS profiles for HfON/Ge gate stack after 500°C PDA in  $N_2$  ambient for 36 30s.

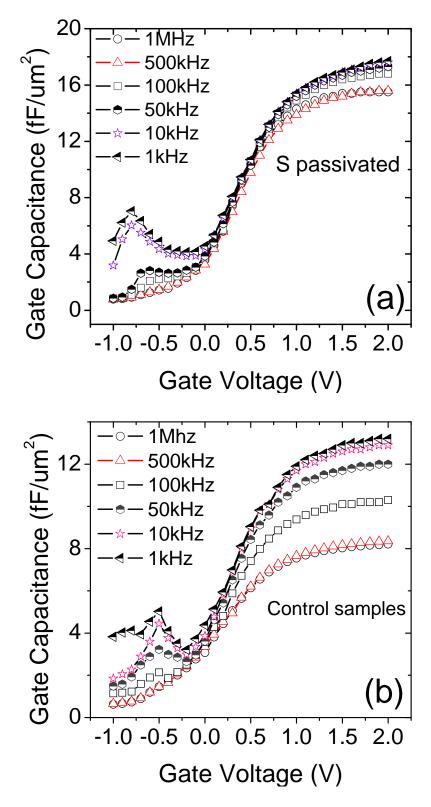

- Fig. 2.6. Capacitance-Voltage characteristics of TaN/HfON/Ge capacitors (a) with 37 (NH<sub>4</sub>)<sub>2</sub>S treatment, (b) without (NH<sub>4</sub>)<sub>2</sub>S treatment, after a 550°C PMA, in N<sub>2</sub> ambient for 30s.

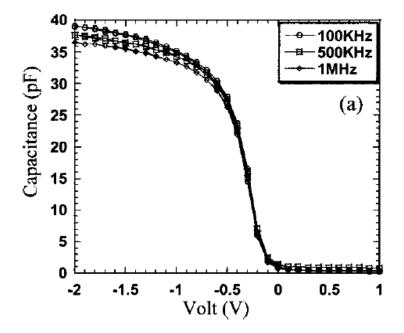

- Fig. 2.7. Capacitance–voltage curves measured at 100 kHz, 500 kHz, and 1 MHz for 39 (a) zirconia grown by ozone oxidation.

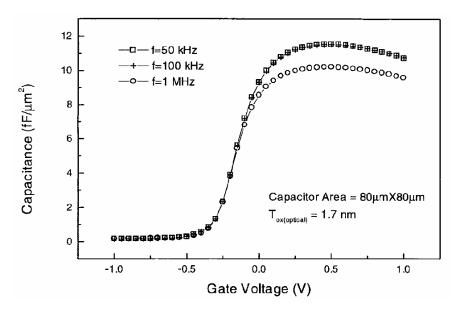

- Fig. 2.8. High-frequency *C-V* measurement of MOS capacitor at 50 kHz (square), 39 100 kHz (cross), and 1 MHz (circle). *C-V* characteristics depend on frequency in the parallel circuit model As-deposited Sm<sub>2</sub>O<sub>3</sub> on TaN is shown to be likely poly-crystalline.

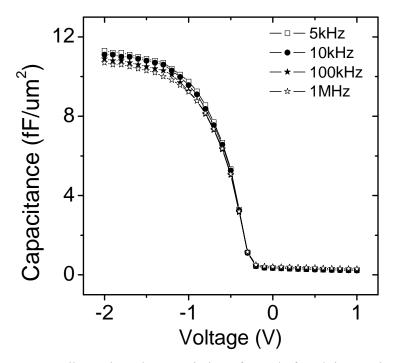

- Fig. 2.9. Frequency dispersion characteristics of TaN/HfON/Si capacitors. The 40 dispersion at accumulation region is attributed to the parasitic resistance.

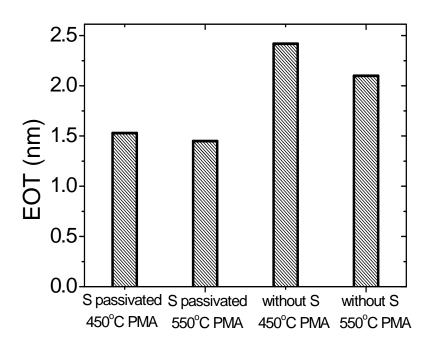

- Fig. 2.10. EOT values with different surface treatment and post metal annealing 41 temperatures. Sulfur passivated samples show about 0.7nm thinner EOT.

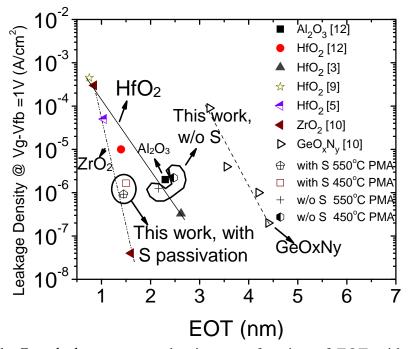

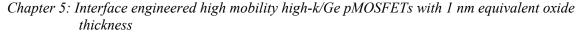

- Fig. 2.11. Gate leakage current density as a function of EOT with different surface 42 treatment and PMA temperatures together with published data.

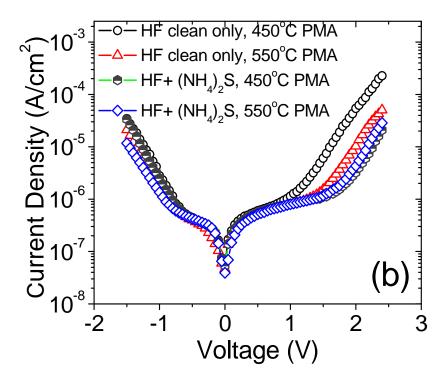

- Fig. 2.12. Typical Ig-Vg curves of Ge MOS Capacitors with different surface treatment 43 and PMA temperatures.

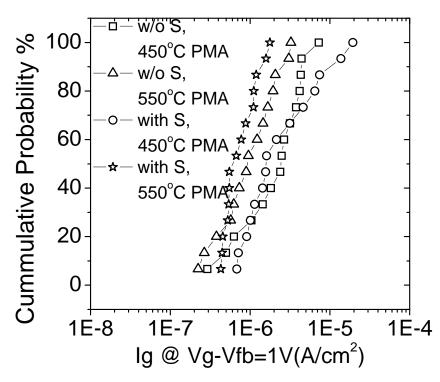

- Fig. 2.13. Cumulative probability of leakage current densities of Ge MOS capacitors 43 with different surface treatments and PMA temperatures.

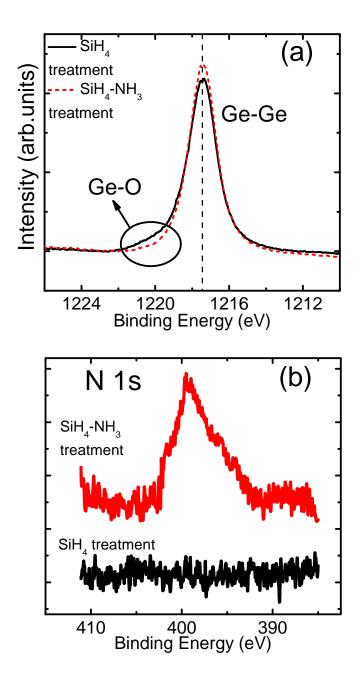

- Fig. 3.1. (a) High resolution XPS data in (a) Ge 2p and (b) N 1s for Ge wafers after 49 SiH<sub>4</sub> or SiH<sub>4</sub>-NH<sub>3</sub> treatment. Ultrathin (~6Å) Si passivation layer by SiH<sub>4</sub> treatment can not adequately prevent GeO<sub>x</sub> formation at Ge surface when sample is exposed to oxidized ambient (e.g. air).

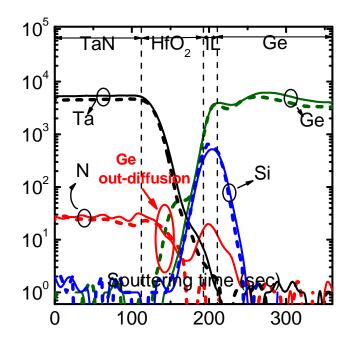

- Fig. 3.2. SIMS profiles for HfO<sub>2</sub> gated Ge MOS capacitors with Si passivation (dash) 50 and silicon nitride (SN) passivation (solid). Red: N. Blue: Si. Green: Ge. Ta: Black.

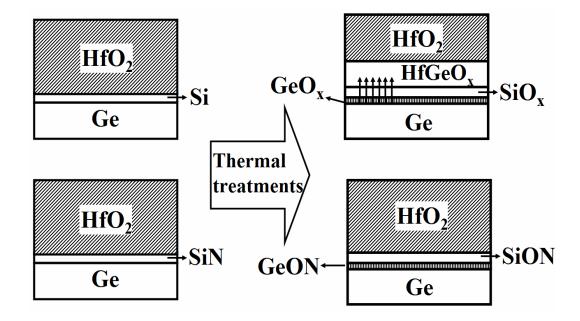

- Fig. 3.3. Schematic illustration of better passivation effects by silicon nitride layer. 50 After thermal treatments, ultrathin Si layer can be oxidized, especially when HfO<sub>2</sub> thickness is large and subsequently, volatile GeO could be formed and results serious Ge out-diffusion. Introduction of N can suppress volatile GeO formation at high-k/Ge interface.

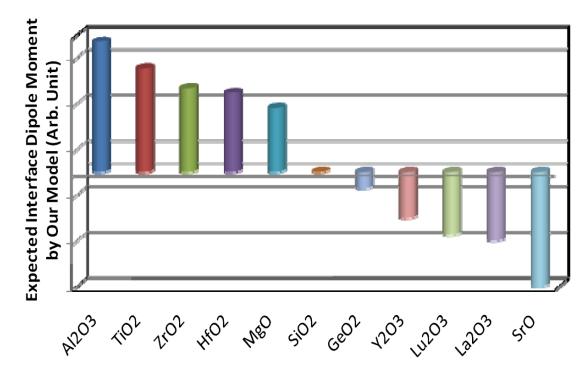

- Fig. 3.4. Summary of the dipole moment formed at high-k/SiO<sub>2</sub> interface predicted 53 by our model, for various high-k candidates including GeO<sub>2</sub>. The dipole direction to increase *VFB* is represented as a positive direction.

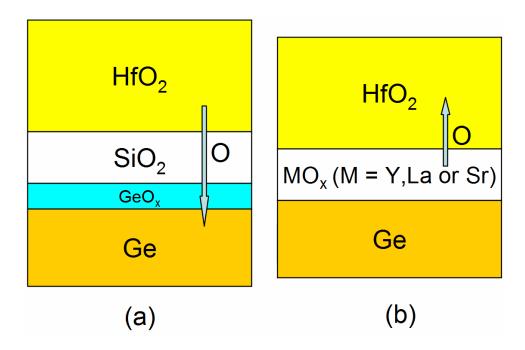

- Fig. 3.5. Oxygen transfer direction for (a)HfO<sub>2</sub>/SiO<sub>2</sub>/GeO<sub>x</sub>/Ge gate stack and 53

(b) $HfO_2/MO_x/Ge$  gate stack (M = Y, La or Sr).

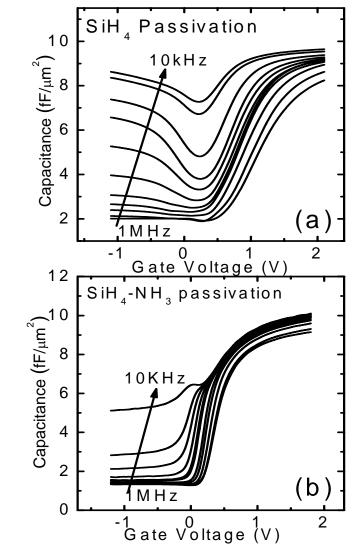

- Fig. 3.6. C-V characteristics of HfO<sub>2</sub> gated Ge MIS capacitors with (a) Si passivation 54 and (b) SN passivation measured at 1MHz, 800kHz, 500kHz, 300kHz, 200kHz, 100kHz, 80kHz, 50kHz, 30kHz, 20kHz and 10kHz.

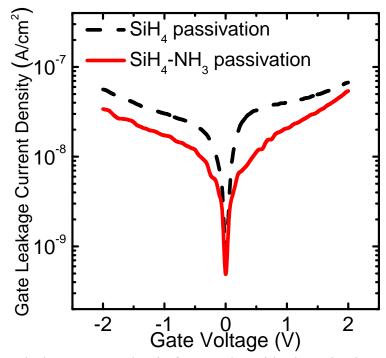

- Fig. 3.7. Gate leakage current densiy for samples with Si passivation and SN 55 passivation. Smaller  $J_g$  is observed for devices with SN passivation.

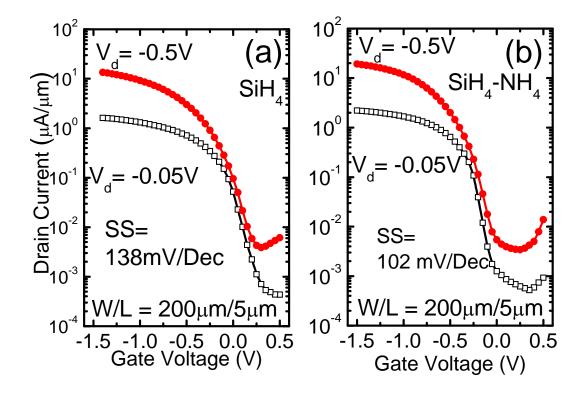

- Fig. 3.8. Well-behaved  $I_d$ - $V_g$  characteristics for Ge pMOSFETs (L = 5 µm) with (a) Si 55 passvation and (b) SN passivation.

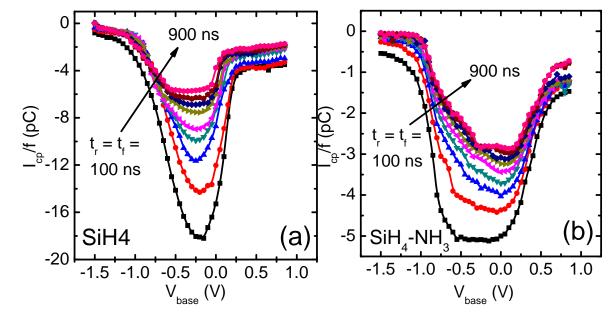

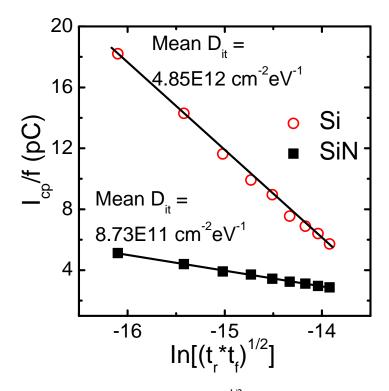

- Fig. 3.9. Rise and fall time dependence of charge pumping (CP) currents ( $t_r = t_f = 57$  100, 200, 300, 400, 500, 600, 700, 800, and 900 ns) for samples with (a) Si passivation and (b) SN passivation. The area is 14400µm<sup>2</sup>, amplitude is 1V and frequency is 200 kHz.

- Fig. 3.10.  $Q_{cp}(=I_{cp}/f)$  as a function of  $\ln(t_r \times t_f)^{1/2}$  that provides the mean  $D_{it}$  for samples 57 with Si or SN passivation.

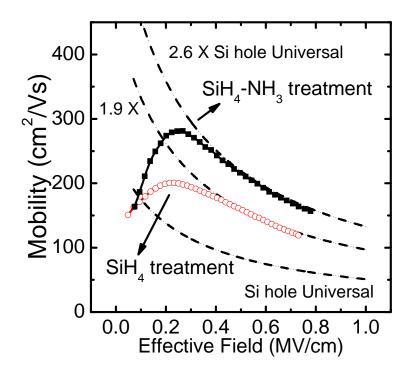

- Fig. 3.11. Hole mobility as a function of vertical effective vertical field for Ge 58 pMOSFETs ( $L = 5\mu m$ ) with Si or SN passivation.

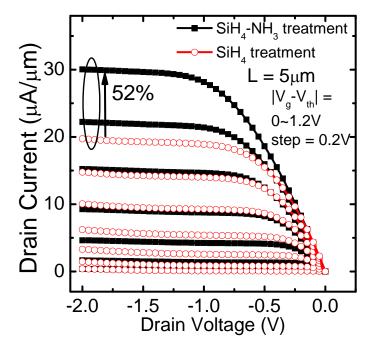

- Fig. 3.12.  $I_d$ - $V_d$  for Ge pMOSFETs (L = 5 µm). About 52% enhanced drive current is 58 obtained for SN passivated device at  $V_g$ - $V_t$  = -1.2V and  $V_d$ = -2V.

- Fig. 4.1. Concept of interface engineering processes: Pre-gate passivation and 65 Post-gate dielectric treatment.

- Fig. 4.2. (a) F incorporation to high-k dielectric during CF<sub>4</sub>-plasma treatment. (b) 67

Various mechanisms that can take place during the subsequent PDA or S/D activation annealing process for devices with CF<sub>4</sub>-plasma treatment.

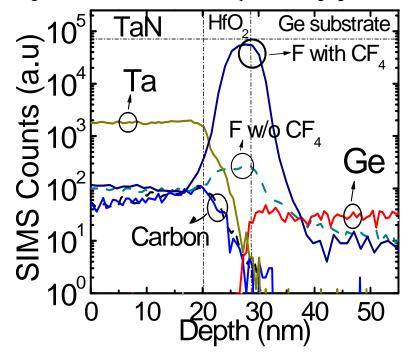

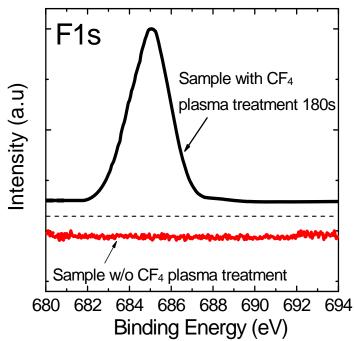

- Fig. 4.3. SIMS depth profile for samples with and without  $CF_4$ -plasma treatment. F 69 was incorporated in the bulk high-k dielectric and high-k/Ge interface.

- Fig. 4.4. F 1s XPS spectrum for samples with and without  $CF_4$ -plasma treatment on 69  $HfO_2/Ge$  gate stack.

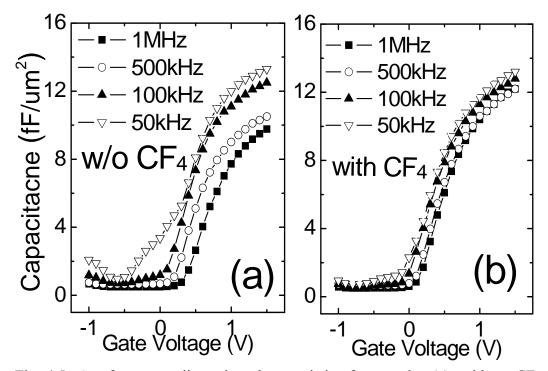

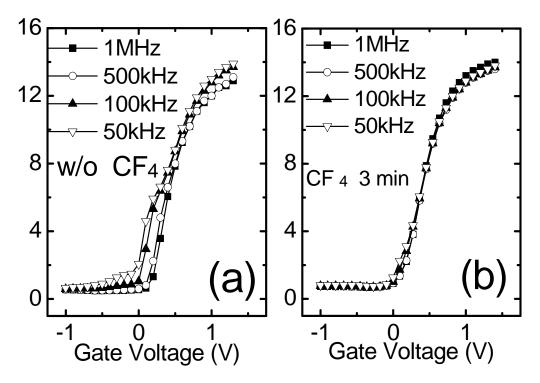

- Fig. 4.5. Fig. 4.5. *C-V* frequency dispersion characteristics for samples (a): with 70  $CF_4$ -plasma treatment and (b): without  $CF_4$ -plasma treatment.

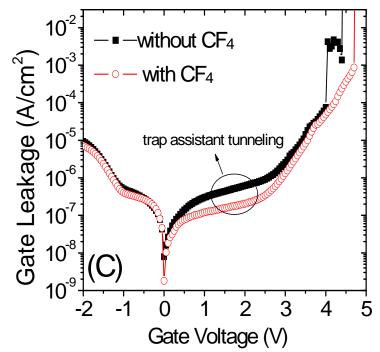

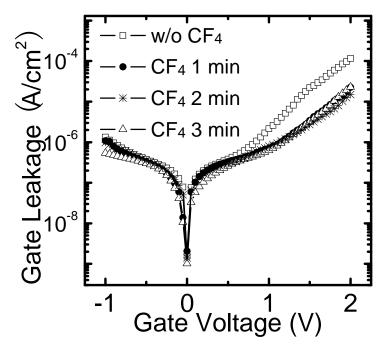

- Fig. 4.6.  $I_{g}$ - $V_{g}$  characteristics for samples with and without CF<sub>4</sub>-plasma treatment. 72

- Fig. 4.7. Cumulative probability of breakdown voltages for samples with and without 72  $CF_4$ -plasma treatment.

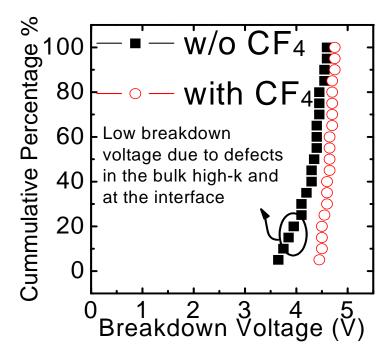

- Fig. 4.8. Samples with both Si passivation and  $CF_4$ -plasma treatment show excellent 75 high frequency *C*-*V* characteristics.

- Fig. 4.9. *C-V* frequency dispersion characteristics for SP samples (a) without 76  $CF_4$ -plasma treatment and (b) with  $CF_4$ -plasma treatment for 3 min. Both frequency-dependent  $\Delta V_{fb}$  and stretch-out disappear for  $CF_4$  treated samples.

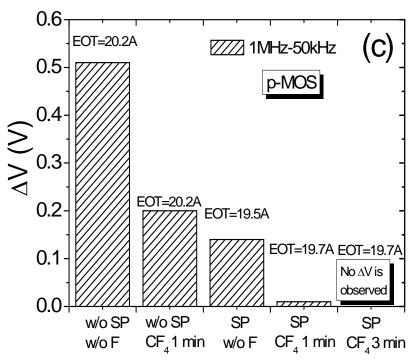

- Fig. 4.10. Comparison of frequency dependent flat band voltage shift for samples with 76 different pre-gate or post-gate treatment conditions.

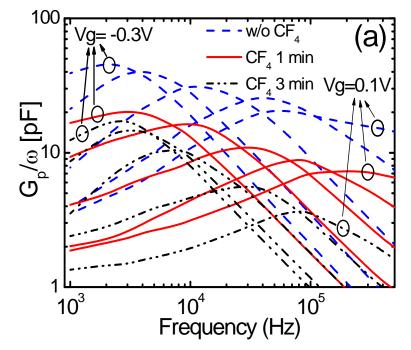

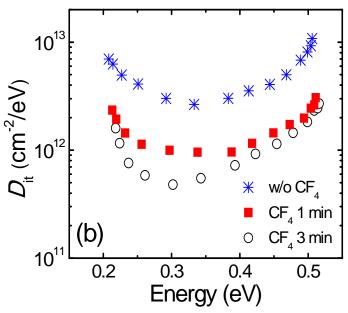

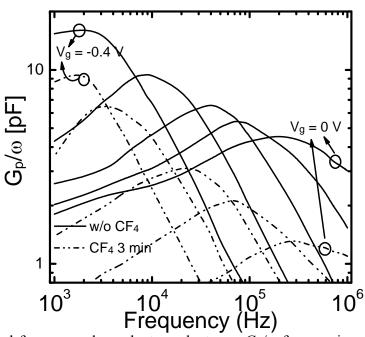

- Fig. 4.11. Frequency dependent conductance  $G_p/\omega$  for a series of gate voltages for SP 78 samples w/o F treatment, with F treatment for 1 min, and with F treatment for min, respectively.

- Fig. 4.12. Plot of  $D_{it}$  vs energy relative to the valence band edge for samples w/o CF<sub>4</sub> 78 treatment, with CF<sub>4</sub> treatment for 1- and 3- min, respectively. Interface quality is greatly improved after CF<sub>4</sub>-plasma treatment.

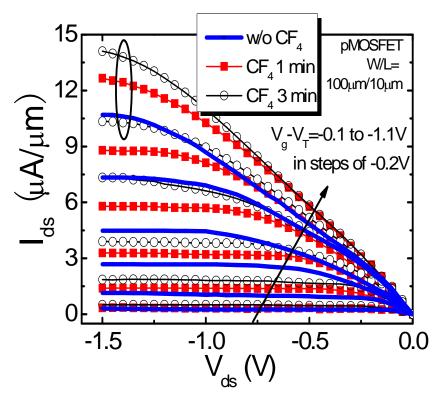

- Fig. 4.13. Output characteristics for Ge pMOSFETs with Si passivation and 79 CF<sub>4</sub>-plasma treatment for different duration. Enhanced drive currents were achieved after CF<sub>4</sub> plasma-treatment.

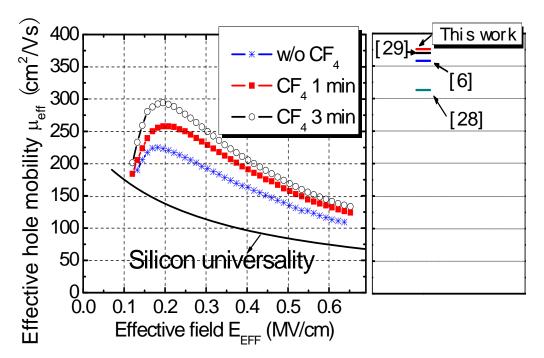

- Fig. 4.14. *Left*: effective hole mobility in Ge pMOSFETs versus effective field for 80 silicon passivated devices with different  $CF_4$  treatment conditions without correction. *Right*: peak  $\mu_{eff}$  after correction together with other reported data.

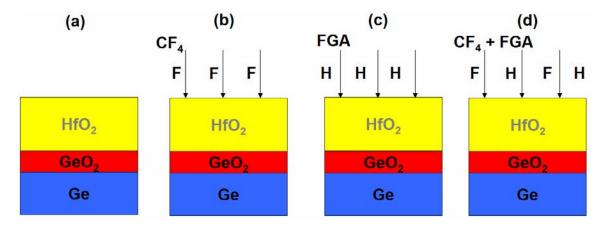

- Fig. 5.1. Splits for post gate treatments scheme for TaN/HfO<sub>2</sub>/GeO<sub>2</sub>/Ge MOS 87 capacitors.

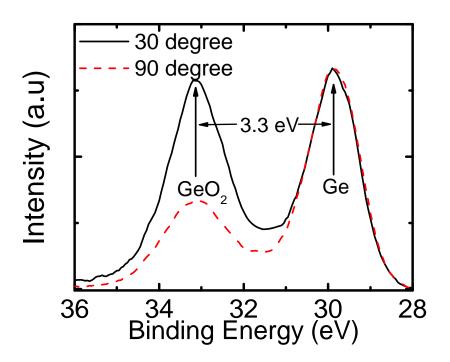

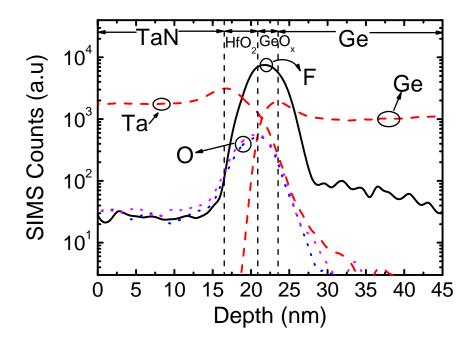

- Fig. 5.2. Angle resolved XPS Ge 3d spectra for germanium samples after the thermal 88 oxidation at 400°C. The thickness of GeO<sub>2</sub> is about 2 nm.

- Fig. 5.3. SIMS profiles for TaN/HfO<sub>2</sub>/GeO<sub>x</sub>/Ge gate stack after PDA and FGA. The 88 oxygen profiles are taken for both samples with and without  $CF_4$  plasma

treatment process. Other curves are taken from CF<sub>4</sub> treated samples.

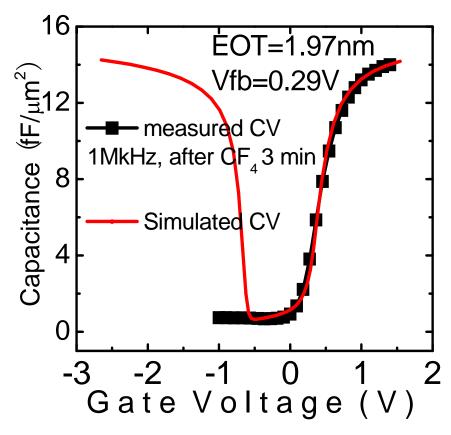

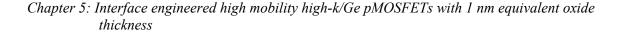

- Fig. 5.4. Capacitance-voltage characteristics of TaN/HfO<sub>2</sub>/GeO<sub>x</sub>/Ge gate stacks (~ 2 89 nm GeO<sub>2</sub> and 4.5 nm HfO<sub>2</sub>) measured at 1Mhz, 900kHz, 800kHz,..., 200kHz, 100kHz, 90kHz, 80kHz,..., 20kHz and 10kHz (a) with neither CF<sub>4</sub> plasma treatment nor FGA; (b) with CF<sub>4</sub> plasma treatment for 3 min but without FGA; (c) without CF<sub>4</sub> plasma treatment but with FGA; (d) with both CF<sub>4</sub> plasma treatment and FGA.

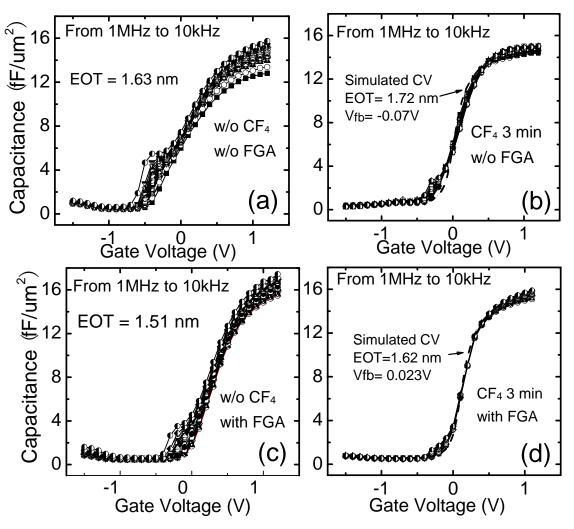

- Fig. 5.5. Frequency dependent flat band voltage shifts ( $\Delta V$ ) and Equivalent oxide 90 thickness (EOT) for samples both with and without FGA of different CF<sub>4</sub> treatment conditions.

- Fig. 5.6.  $I_g$ - $V_g$  characteristics for forming gas annealed samples with different CF<sub>4</sub> 92 plasma treatment conditions.

- Fig. 5.7. Typical frequency dependent conductance  $G_p/\omega$  for a series of gate voltage 92 for forming gas annealed samples without CF<sub>4</sub> plasma treatment and samples with CF<sub>4</sub> plasma treatment for 3 min.

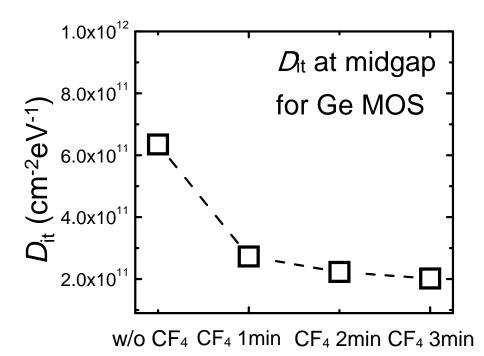

- Fig. 5.8. Extracted midgap  $D_{it}$  for FGA annealed samples with different F treatment 93 conditions.

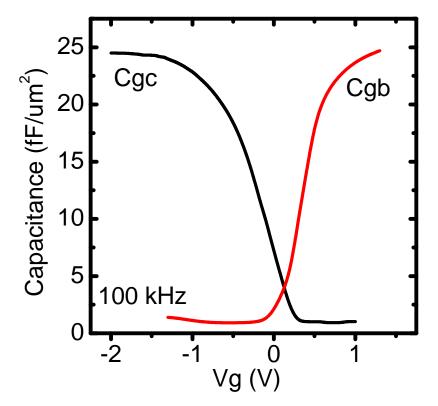

- Fig. 5.9. Split *C-V* obtained for a  $200\mu m \times 10\mu m$  pMOSFET. 95

- Fig. 5.10. Gate-leakage-current density as a function of EOT together with published 96 data.

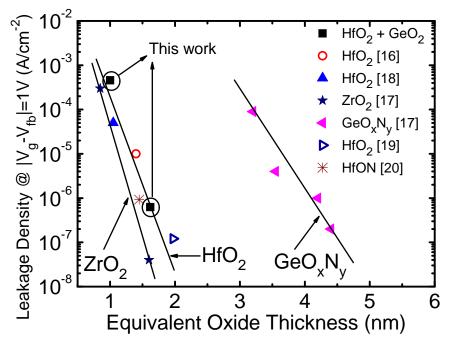

- Fig. 5.11. Linear  $I_d$ - $V_g$  and  $G_m$ - $V_g$  obtained for 200µm × 10µm pMOSFETs. Device 97 with F incorporation shows higher  $I_d$  and  $G_m$ .

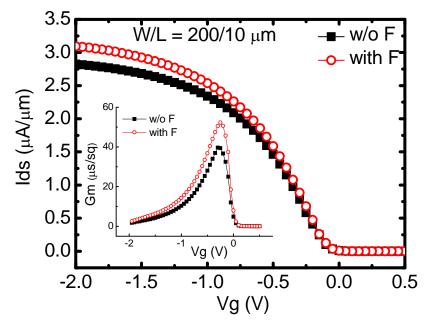

- Fig. 5.12. Hole mobility as a function of vertical effective field for 200μm × 10μm 97 pMOSFETs, with and without F incorporation. The mobility enhancement is maintained for large field. Right figure shows the comparison of peak hole mobility with previous reported record values.

- Fig. 5.13. Well behaved  $I_d$ - $V_g$  characteristics for the 200µm × 10µm pMOSFETs with 98 and without F incorporation. Devices with GeO<sub>2</sub> passivation and Forming gas annealing (FGA) show SS about 98mV/dec, while devices with GeO<sub>2</sub> passivation and both post-gate treatments including CF<sub>4</sub> plasma treatment and FGA exhibit smaller SS about 85mV/dec, indicating better interface

quality.

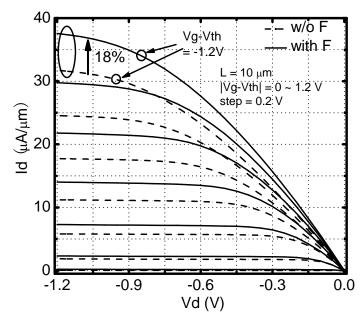

- Fig. 5.14.  $I_d$ - $V_d$  for 200µm × 10µm pMOSFETs. About 18% Enhanced drive current is 99 obtained after F incorporation. Drive current is 37.8 µA/µm at  $V_g V_t = V_d = -1.2V$ . This is the highest record drive current published for unstrained Ge devices to date.

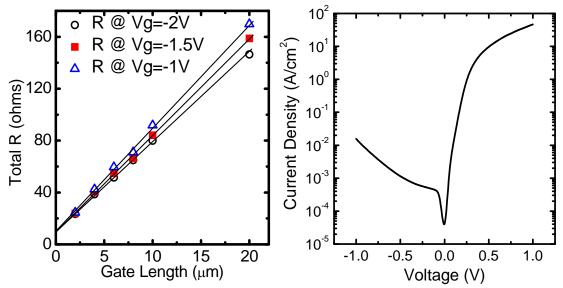

- Fig. 5.15. Fig. 5.15. Left: Series resistance  $R_s$  for the Al contacted Source/Drain 100 extracted from the total resistance vs. gate length at  $V_g = -2V$ , -1.5V and -1V for 200µm width devices. Right: Junction leakage characteristics.

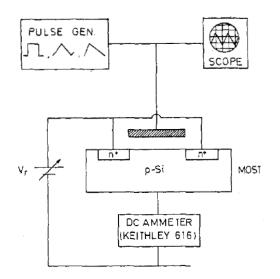

- Fig. 5.16. Basic experimental set-up for charge pumping measurement on HfO<sub>2</sub>/Ge 101 gate stack.

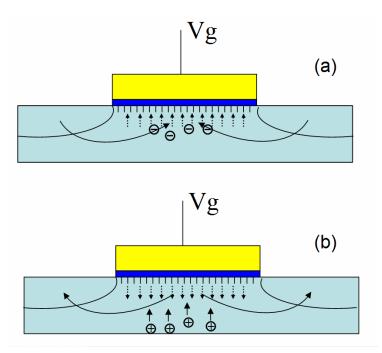

- Fig. 5.17. Illustration of charge pumping effects by varying the  $V_{\rm g}$  on a MOSFET. 101

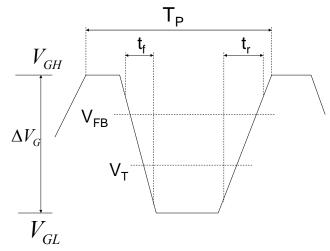

- Fig. 5.18. Waveform applied at the gate when performing charge pumping. 102

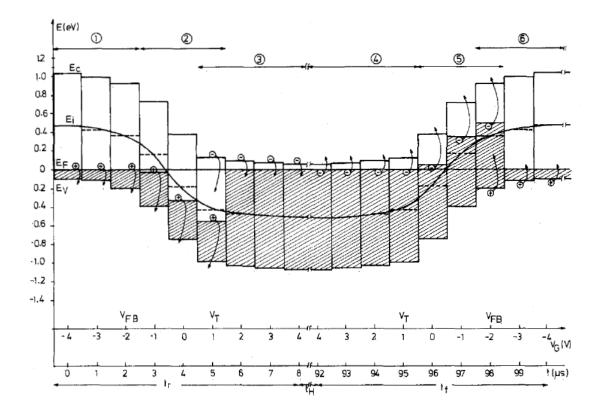

Fig. 5.19. Different processes occurring during one cycle of the gate pulse ( $T_p = 100$  103 us), using the energy-band diagrams (the Fermi level is used as the zero reference level): 1) steady-state emission of holes to valence band (towards the substrate)

2) nonsteady-state emission of holes to valence band (towards the substrate)

3) trapping of electrons (from source and drain);

4) steady-state emission of electrons to conduction band (towards source and drain)

5) nonsteady-state emission of electrons to conduction band (towards source and drain)

6) trapping of holes (from substrate).

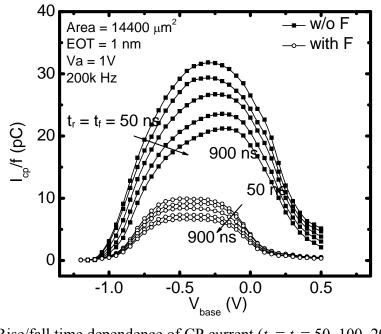

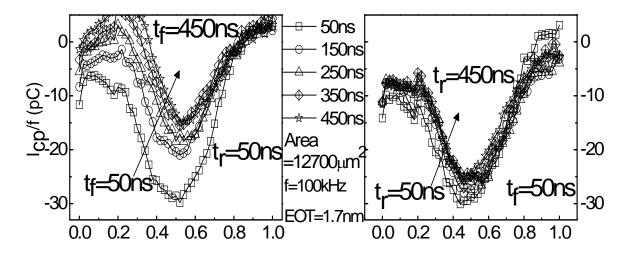

- Fig. 5.20. Rise/fall time dependence of CP current ( $t_r = t_f = 50, 100, 200, 500, 900$  ns) 104 for Ge pMOSFETs with or without F incorporation.

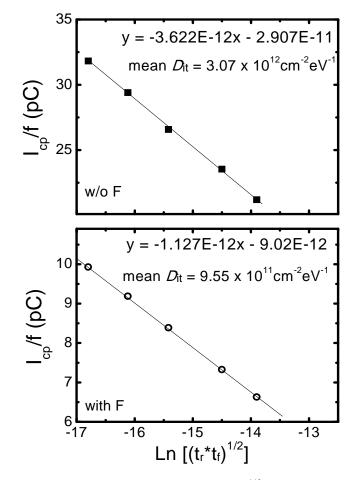

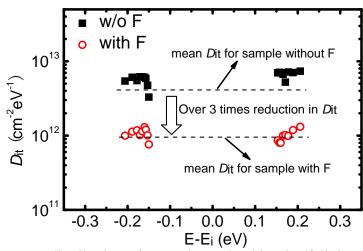

- Fig. 5.21.  $Q_{cp} (= I_{cp}/f)$  as a function of  $\ln(t_r \cdot t_f)^{1/2}$  provides the mean  $D_{it}$  for samples without F incorporation is about  $3.07 \times 10^{12} \text{ cm}^{-2} \text{eV}^{-1}$  and for samples with F incorporation is about  $9.55 \times 10^{11} \text{ cm}^{-2} \text{eV}^{-1}$ , respectively.

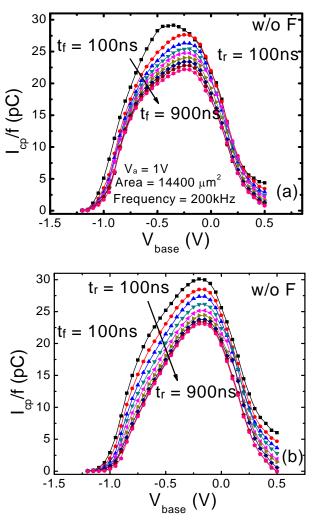

- Fig. 5.22. (a) Fall time dependence of CP current curves for fixed rise time of 100 ns 106 to measure the  $D_{it}$  distribution in the upper half of the Ge bandgap. (b) Rise

time dependence of CP current curves for fixed fall time of 100 ns to measure the  $D_{it}$  distribution in the lower half of the Ge bandgap for samples without F incorporation.

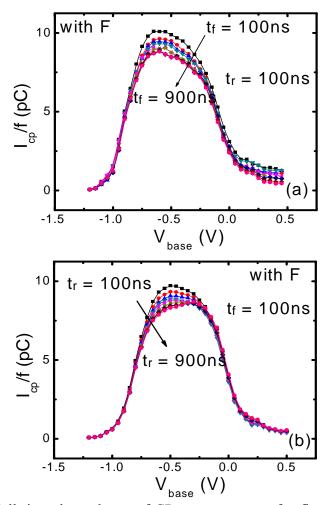

- Fig. 5.23. (a) Fall time dependence of CP current curves for fixed rise time of 100 ns 107 to measure the  $D_{it}$  distribution in the upper half of the Ge bandgap. (b) Rise time dependence of CP current curves for fixed fall time of 100 ns to measure the  $D_{it}$  distribution in the lower half of the Ge bandgap for samples with F incorporation.

- Fig. 5.24. Energy distribution of  $D_{it}$  as determined by rise/fall time dependence of  $I_{cp}$ . 107

- Fig. 5.25. F incorporation into high-k/Ge gate stack and various possible passivation 108 mechanism during subsequent annealing steps: (a) passivation of interface traps at GeO<sub>2</sub>/Ge interface by forming Ge-F; (b) passivation of interface traps at HfO<sub>2</sub>/GeO<sub>2</sub> interface; (c) passivation of HfO<sub>2</sub> bulk traps by forming Hf-F.

- Fig. 6.1. Schematic illustration of n-channel electron mobility degradation by 114 Coulomb Scattering.

- Fig. 6.2. (a) Strong fall-time dependence of charge pumping currents from 50 ns to 116 450 ns for fixed rise time of 50 ns; (b) Relatively week rise-time dependence of charge pumping currents from 50 ns to 450 ns for fixed fall-time of 50 ns.

- Fig. 6.3. Energy distribution of interface traps in HfO<sub>2</sub> gated Ge MOSFETs as 117 determined by rise/fall time dependence of charge pumping currents under room temperature.

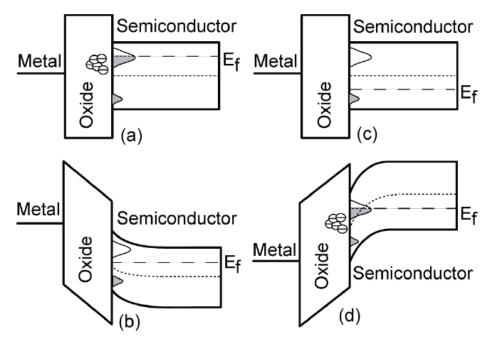

- Fig. 6.4. Energy band diagrams of MOS system with asymmetrical distribution of 117 interface trap density along the bandgap. (a) p-MOS under flat-band; (b) p-MOS near weak inversion; (c) n-MOS under flat-band; (d) n-MOS near strong inversion.

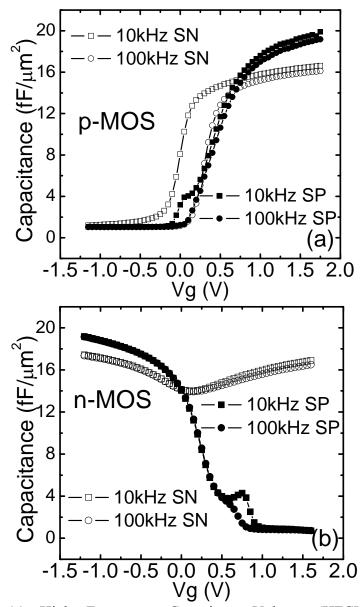

- Fig. 6.5. (a) High Frequency Capacitance-Voltage (HFCV) characteristics of 119 TaN/HfO<sub>2</sub>/Ge p-MOS capacitors with surface nitridation (SN) or silicon passivation (SP); (b) HFCV characteristics of TaN/HfO<sub>2</sub>/Ge n-MOS capacitors with SN or SP.

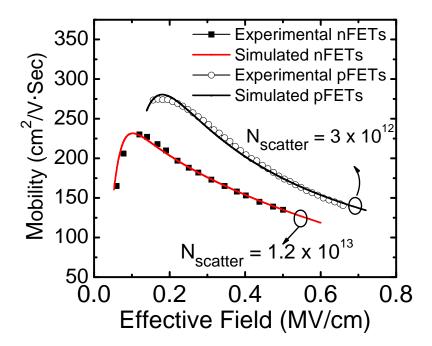

- Fig. 6.6. Effective carrier mobility of  $HfO_2$  Ge MOSFETs with SP together with 120 simulation results.

## List of Tables

| Table 1.1. | Key characteristics of a wide variety of gate dielectrics on Si.                                                                               | 8   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1.2. | Material properties of alternative channel materials.                                                                                          | 9   |

| Table 4.1. | Comparison of $D_{it}$ , EOT, hysteresis and gate leakage current for Ge capacitors with different pre-gate or post-gate treatment conditions. | 79  |

| Table 5.1. | Equations used for analyzing CP data with trapezoidal pulse waveform.                                                                          | 104 |

## List of Symbols

| χ                 | Electron affinity of a semiconductor                      |

|-------------------|-----------------------------------------------------------|

| $\mathcal{E}_0$   | Permittivity of free space                                |

| $\phi$            | Electron barrier height                                   |

| $\mu_{ m e}$      | Mobility of electron                                      |

| $\mu_{ m eff}$    | Effective mobility                                        |

| $\mu_{ m h}$      | Mobility of hole                                          |

| $\sigma_{\rm n}$  | Capture cross section area of electron                    |

| $\sigma_{ m p}$   | Capture cross section area of hole                        |

| ω                 | Angular frequency                                         |

| $\Delta V$        | Frequency dependent flat-band voltage shift               |

| A                 | Area                                                      |

| a                 | Lattice constant                                          |

| С                 | Capacitance                                               |

| $C_{gb}$          | Gate to substrate capacitance per unit area               |

| $C_{gc}$          | Gate to channel capacitance per unit area                 |

| $C_{ m inv}$      | Gate to channel capacitance under inversion per unit area |

| $C_{\min}$        | Minimum capacitance of a MOS capacitor                    |

| $D_{\rm it}$      | Density of interface states                               |

| Ec                | Conduction band edge                                      |

| $E_{\rm eff}$     | Vertical effective electric field in a MOSFET channel     |

| E <sub>em.e</sub> | Electron emission energy level                            |

| $E_{\rm em.h}$    | Hole emission energy level                                |

| $E_{ m F}$        | Fermi level of a semiconductor                            |

| $E_{g}$           | Energy bandgap of a semiconductor                         |

| $E_{ m i}$        | Intrinsic Fermi level of a semiconductor                  |

| $E_{ m v}$                 | Valence band edge                                                           |

|----------------------------|-----------------------------------------------------------------------------|

| f                          | Frequency                                                                   |

| $G_{\mathrm{m}}$           | Transconductance of a MOSFET                                                |

| $G_{\rm p}$                | Equivalent parallel conductance of an MOS capacitor                         |

| $I_{\rm cp}$               | Charge pumping current                                                      |

| Id                         | Current through the drain                                                   |

| Ig                         | Leakage current through the gate electrode                                  |

| $I_{\text{off}}$           | Drain leakage when the MOSFET is off                                        |

| Ion                        | Channel saturation current when the MOSFET is on                            |

| J                          | Current density                                                             |

| $J_{ m g}$                 | Gate leakage current density                                                |

| k                          | Dielectric constant (relative permittivity)                                 |

| k <sub>Ge</sub>            | Dielectric constant of Ge (relative permittivity)                           |

| k <sub>high-k</sub>        | Dielectric constant of high permittivity dielectric (relative permittivity) |

| $k_{SiO_2}$                | Dielectric constant of SiO <sub>2</sub> (relative permittivity)             |

| L                          | Gate length of a MOSFET                                                     |

| $N_{\rm c}$                | Effective density of states in the conduction band                          |

| n <sub>i</sub>             | Intrinsic carrier concentration in a semiconductor                          |

| N <sub>scatter</sub>       | Interface scattering density                                                |

| $N_{sub}$                  | Substrate doping concentration                                              |

| $N_{ m v}$                 | Effective density of states in the valence band                             |

| q                          | Electronic charge                                                           |

| $\mathcal{Q}_{\mathrm{b}}$ | Depletion charge in the bulk per unit area                                  |

| $Q_{ m cp}$                | Recombined charge per cycle in the charge pumping measurement               |

| $Q_{\rm i}$                | Inversion charge in the channel per unit area                               |

| R                          | Resistance                                                                  |

| $R_{\rm s}$                | Series resistance                                                           |

|                            |                                                                             |

| t <sub>high-k</sub>    | Physical thickness of high permittivity dielectric                     |

|------------------------|------------------------------------------------------------------------|

| $t_{\rm inv}$          | Capacitance equivalent oxide thickness in inversion                    |

| $T_{\rm m}$            | Melting point                                                          |

| $T_p$                  | Period of the gate pulse                                               |

| $t_f$                  | Fall time of the gate pulse signal                                     |

| $t_{\rm ox}$           | Equivalent oxide thickness                                             |

| $t_{ m poly}$          | Equivalent oxide thickness due to poly depletion effect                |

| <i>t</i> <sub>qm</sub> | Equivalent oxide thickness due to quantum mechanical effect of channel |

| $t_r$                  | Rise time of the gate pulse signal                                     |

| Va                     | Amplitude of gate pulse                                                |

| V <sub>d</sub>         | Drain voltage                                                          |

| V <sub>dd</sub>        | Positive supply voltage                                                |

| V <sub>ds</sub>        | Drain-source bias                                                      |

| $V_{ m fb}$            | Flat band voltage                                                      |

| $V_{g}$                | Gate voltage                                                           |

| V <sub>ox</sub>        | Voltage dropped on oxide                                               |

| $V_{\mathrm{th}}$      | Threshold voltage                                                      |

| W                      | Gate width of a MOSFET                                                 |

| X                      | Reactance                                                              |

| x <sub>j</sub>         | Junction depth                                                         |

| Ζ                      | Impedance                                                              |

## List of Abbreviations

| ALD                       | Atomic layer deposition                                     |

|---------------------------|-------------------------------------------------------------|

| C-V                       | Capacitance — voltage characteristic                        |

| CET                       | Capacitance equivalent oxide thickness                      |

| CMOS                      | Complementary metal-oxide-semiconductor device              |

| СР                        | Charge pumping                                              |

| CVD                       | Chemical vapor deposition                                   |

| DI                        | Deionized                                                   |

| EOT                       | Equivalent oxide thickness                                  |

| FGA                       | Forming gas annealing                                       |

| FUSI                      | Full silicidation                                           |

| $G_{ m m}$ - $V_{ m g}$   | Transconductance-gate voltage characteristic                |

| GOI                       | Germanium on insulator                                      |

| HFCV                      | High frequency capacitance-voltage characteristic           |

| $I_{\rm d}$ - $V_{\rm d}$ | Drain current — drain voltage characteristic                |

| $I_{ m d}$ - $V_{ m g}$   | Drain current — gate voltage characteristic                 |

| IC                        | Integrated circuit                                          |

| ICP                       | Inductively coupled plasma                                  |

| IL                        | Interfacial layer                                           |

| ITRS                      | International Technology Roadmap for Semiconductors         |

| J-V                       | Leakage current-voltage characteristic                      |

| $J_{ m g}$ - $V_{ m g}$   | Gate leakage current-gate voltage characteristic            |

| LCR                       | Inductance (L), Capacitance (C), and Resistance (R)         |

| MOCVD                     | Metalorganic chemical vapor deposition                      |

| MOS                       | Metal-oxide-semiconductor device, usually the MOS capacitor |

| MOSFET                    | Metal-oxide-semiconductor field-effect transistor           |

| nMOS    | n-type MOS device                      |

|---------|----------------------------------------|

| nMOSFET | n-type channel MOSFET                  |

| PDA     | Post deposition annealing              |

| PMA     | Post metal annealing                   |

| pMOS    | p-type MOS device                      |

| pMOSFET | p-type channel MOSFET                  |

| PVD     | Physical vapor deposition              |

| QMCV    | Quantum mechanical capacitance voltage |

| RF      | Radio frequency                        |

| RTP     | Rapid thermal processing               |

| S/D     | Source drain                           |

| SIMS    | Secondary ion mass spectroscope        |

| SS      | Substreshold swing                     |

| UHV     | Ultra high vacuum                      |

| UTB     | Ultrathin body                         |

| UV      | Ultraviolet                            |

| XPS     | X-ray photoelectron spectroscopy       |

|         |                                        |

XTEM Cross-section transmission electron microscopy

## **Chapter 1**

### Introduction

#### 1.1. Challenges of MOSFETs scaling and possible solutions

The success of the semiconductor industry relies on the continuous improvement of integrated circuit (IC) performance by reducing the dimensions of the key component of these circuits: the metal-oxide-semiconductor field effect transistor (MOSFET). Indeed, the reduction of device dimensions, or scaling, allows the integration of a higher density of transistors on a chip, enabling higher switching speed and reduced costs. The scaling of MOSFET device was originally predicted by Intel co-founder Gordon E. Moore, in 1965 [1]. Moore's law describes a long term trend in the history of computing hardware, in which the number of transistors that can be placed inexpensively on an integrated circuit has doubled approximately every two years<sup>\*</sup>. The key concept of the MOSFET scaling proposed by Dennard *et al.* in 1974 [2] is that various structure and electrical parameters of MOSFET (such as gate length, gate width, gate thickness and power supply voltage) should be scaled in concert, which guarantees the reduction in device dimensions without compromising the current-voltage characteristics. However, as the MOSFET continues to scale down to tens of nanometers, this conventional device scaling

<sup>&</sup>lt;sup>\*</sup>Although originally calculated as a doubling every year [1], Moore later refined the period to two years. It is often incorrectly quoted as a doubling of transistors every 18 months, as David House, an Intel Executive, gave that period to chip performance increase. The actual period was about 20 months.

scheme has confronted the difficulty that the three main indexes associated with MOSFET performance: short-channel effects, on current ( $I_{on}$ ) and power consumption have the tradeoff relationships between each other, owing to several physical and essential limitations directly related to the device miniaturization (e.g. to maintain the  $I_{on}$  scaling, SiO<sub>x</sub>N<sub>y</sub> with equivalent oxide thickness (EOT) ~ 1 nm has to be used for 45 nm node technology, but this will cause greater power consumption in terms of high gate leakage current). The schematic diagram of this tradeoff relationship is shown in Fig. 1.1 [3].

Fig. 1.1. Tradeoff factors among short-channel effects, on current ( $I_{on}$ ) and power consumption under simple device scaling and possible solutions to mitigate the relationship. Critical device or physical parameters to provide the tradeoff, such as power-supply voltage  $V_{dd}$  and threshold voltage  $V_{th}$ , are shown between the two indexes, and also, the physical mechanisms causing the tradeoffs are shown inside the boxes [3].

Consequently, to continue the MOSFET scaling in the future, novel device technologies or new materials that simultaneously satisfy the high performance and low power consumption under healthy device characteristics against these physical limitations are strongly desired to overcome these challenges or to mitigate these stringent constraints in the tradeoff relations. A group of these novel device technologies or new materials have been proposed to solve the ultimate scaling issues for future MOSFET, including high-k/metal-gate, high carrier mobility or high carrier velocity channels, ultrathin-body (UTB) structures, multigate structures, and metal source/drain, which are called the technology boosters in the International Technology Roadmap for Semiconductors (ITRS) [4]. The basic principle of these technology boosters is to boost or improve a specific device parameter like the gate leakage current, mobility, shortchannel effects, and so on.

In this thesis, we focus on the gate stack engineering, because gate stack technology is the key driver for MOSFET scaling. The advanced gate stacks must fulfill both requirements of low power consumption and high performance. Therefore, the introduction of high-k materials for gate dielectrics and high carrier mobility material for channels is of paramount importance.

#### 1.2. High-k gate dielectrics

#### 1.2.1 Limits of SiO<sub>2</sub> scaling

The excellent material and electrical properties of thermal  $SiO_2$  allowed the successful scaling of Si-based MOSFETs in the twentieth century. Properly working MOSFETs with  $SiO_2$  gate layer as thin as 1.5 nm has been reported [5, 6]. However, further scaling of  $SiO_2$  gate layer thickness is problematic. The first problem is the

concern of high leakage current flowing through the metal-oxide-semiconductor (MOS) structure. For the ultrathin SiO<sub>2</sub> gate layer (< 3 nm), charge carriers can flow through the gate dielectric by the direct tunneling mechanism [7] as illustrated in Fig. 1.2 [8]. It has been shown that the tunneling probability increases exponentially as the thickness of the SiO<sub>2</sub> layer decreases [7, 9]. As shown in the Fig. 1.2, the leakage current density exceeds 100 A/cm<sup>2</sup> at  $V_{ox} = 1$ V in a 1 nm thick SiO<sub>2</sub> layer ( $V_{ox}$  is the potential drop across the dielectric layer). It also can be seen from this figure that the SiO<sub>2</sub> layer thickness scaling is limited by the leakage current specifications from ITRS. SiO<sub>2</sub> gate dielectric is not suitable for 80 nm technology and below because the EOT requirement of 80 nm node and below is less than 1.4 nm for high performance logic and 1.7 nm for low operating power and the leakage current densities of the SiO<sub>2</sub> layers with those thickness will exceed the maximum leakage current specifications.

Fig. 1.2. (Left) Schematic energy band diagram of an n-Si/SiO<sub>2</sub>/metal gate structure, illustrating direct tunneling of electrons from the Si substrate to the gate.  $\phi$  is the energy barrier height at the Si/SiO<sub>2</sub> interface, V<sub>ox</sub>, the potential drop in the SiO<sub>2</sub> layer and V<sub>G</sub>, the applied gate voltage. (Right) Simulated tunneling current through a MOS as a function of the potential drop in the gate oxide, V<sub>ox</sub>, for different SiO<sub>2</sub> gate layer thickness. Shaded areas represent the maximum leakage current specified by the ITRS for high performance and low operating power application, respectively.

Another issue arising from SiO<sub>2</sub> scaling is boron penetration through the gate dielectric. Upon thermal annealing, the boron from heavily doped poly-silicon gate can easily diffuse through the thin SiO<sub>2</sub> layer into substrate. This will cause unexpected threshold voltage shift and reliability issues [10]. Actually, to tackle the gate leakage and boron penetration issues, in most aggressive high performance technologies, SiO<sub>x</sub>N<sub>y</sub> is used as gate dielectric. SiO<sub>x</sub>N<sub>y</sub> has a dielectric constant ~7, which is higher than SiO<sub>2</sub>, thus a larger physical thickness is allowed to achieve the same EOT. In addition, introduction of nitrogen into SiO<sub>2</sub> greatly reduces the boron diffusion benefited from the Si-O-N networking bonds formed in SiO<sub>x</sub>N<sub>y</sub> [11]. In this case, SiO<sub>x</sub>N<sub>y</sub> dielectric layer with EOT as thin as 1.1 nm still exhibits acceptable leakage current and amount of boron penetration, extending the scaling limit to 45 nm technology node. However, for sub-45 nm technologies, SiO<sub>x</sub>N<sub>y</sub> will not be used as gate dielectric since sub-1 nm EOT is necessarily required and SiO<sub>x</sub>N<sub>y</sub> can no longer fulfill the gate leakage requirement.

#### 1.2.2 Alternative gate dielectrics

The MOS structure actually behaves like parallel plate capacitors. The capacitance density at strong inversion  $C_{inv}$  is given by

$$C_{inv} = \frac{k_{SiO_2}\varepsilon_0}{t_{inv}}$$

(1.1)

where  $k_{SiO_2}$  is the relative dielectric constant of SiO<sub>2</sub> ( $k_{SiO_2} = 3.9$ ),  $\varepsilon_0$  is the permittivity of free space (8.85 × 10<sup>-12</sup> Fm<sup>-1</sup>) and  $t_{inv}$  is the capacitance equivalent oxide thickness (CET) of the gate oxide. Higher  $C_{inv}$  value enables the MOS structure to have more inversion carriers in the channel at the given gate voltage, and thus increases the drive current of MOSFETs. According to equation (1.1), to increase  $C_{inv}$ , we should decrease the  $t_{inv}$ . The  $t_{inv}$  consists of three components and can be expressed as

$$t_{inv} = t_{poly} + t_{ox} + t_{qm} \tag{1.2}$$

$t_{poly}$  is the thickness contributing by poly-Si depletion effect,  $t_{ax}$  is the equivalent oxide thickness (EOT) of the gate dielectric<sup>\*</sup>, and  $t_{qm}$  is the thickness attributed to quantum mechanical effect of carriers in the channel.  $t_{poly}$  could be reduced by replacing the poly-Si gate with metal gate, which is not the focus of this study.  $t_{qm}$  is an intrinsic mechanism and cannot be eliminated. The most effective way to reduce the  $t_{inv}$  is to decease  $t_{ax}$  (EOT). For the past several decades, the gate oxide thickness has been scaled down from hundred nm to now about ~ 1 nm. As pointed out in section 1.2.1, SiO<sub>2</sub> or SiO<sub>x</sub>N<sub>y</sub> has reached to its scaling limits. To further decrease the EOT while maintaining the gate leakage current of MOS structure, an insulator with a higher dielectric constant than SiO<sub>2</sub> (high-k material) with larger physical thickness should be used. The increased physical thickness can also solve the boron penetration problem and improve the gate dielectric reliability. As an example, using ZrO<sub>2</sub> as gate dielectric ( $k_{high-k} \sim 20$ ) would allow us to use a 5.1 nm thick layer in order to achieve an EOT of 1 nm<sup>\*</sup>.

A lot of research efforts have been made on high-k gate dielectrics for the potential replacement of  $SiO_2$  in advance CMOS technologies. The material that could be

<sup>\*</sup>The EOT ( $t_{ox}$ ) of a material is defined as the thickness of the SiO<sub>2</sub> layer that would be required to achieve the same capacitance density as the high-k material in consideration. EOT is given by  $t_{ox} = t_{high-k} \times k_{SiO_2} / k_{high-k}$ , where  $t_{high-k}$  and  $k_{high-k}$  are the physical thickness and relative dielectric constant of high-k dielectric, respectively.

the good candidate needs to satisfy a long list of requirements [12], e.g.:

- The relative dielectric constant of the material should be somewhere between 10 and 30. Dielectrics with higher k value will give rise to fringe fields from the gate to the drain or source and these fields can degrade short channel performances.

- The dielectric material must be an insulator with a band gap greater than 5 eV and the band offsets with silicon must be sufficient. Generally, increasing dielectric constant leads to lower conduction and valence band offset for materials in contact with silicon, and there is an inverse relationship between dielectric constant and the band gap. To prevent conduction by Schottky emission of electrons or holes into their respective bands, i.e. reduce leakage currents, the barrier at each band must be greater than 1 eV.

- Low density of intrinsic defects at the Si/dielectric interface and in the bulk of the material, providing high mobility of charge carriers in the channel and sufficient gate dielectric life time.

- Good thermal stability in contact with Si, preventing the formation of a thick SiO<sub>x</sub> interfacial layer or silicide layers.

Table 1.1 lists the key characteristics of a wide variety of potential high-k gate dielectrics together with SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> for comparison. It can be seen that HfO<sub>2</sub> and LaAlO<sub>3</sub> meet most of the criteria listed above, such as k value, band offsets and good thermal stability. Indeed, the materials that received by far the most attention as alternative gate dielectrics are Hf-based, either HfO<sub>2</sub> or (nitrided) HfSiO<sub>x</sub> over a broad compositional range. The Intel's 45 nm technology microprocessor has already adopted Hf-based high-k dielectrics as gate insulator. Since Hf-based gate dielectrics have already

#### Chapter 1: Introduction

been demonstrated to be a very important high-k material for Si-based MOS devices. In this thesis, we will still focus on Hf-based high-k gate dielectrics for advanced gate stack application with alternative channel material.

| Dielectric                     | k value | Bandgap       | Conduction  | Valence     | Thermal stability  |  |

|--------------------------------|---------|---------------|-------------|-------------|--------------------|--|

|                                |         | ( <b>eV</b> ) | band offset | band offset | on silicon         |  |

|                                |         |               | (eV)        | (eV)        |                    |  |

| SiO <sub>2</sub>               | 3.9     | 9.0           | 3.2         | 4.7         | > 1050°C           |  |

| Si <sub>3</sub> N <sub>4</sub> | 7       | 5.3           | 2.4         | 1.8         | > 1050°C           |  |

| Al <sub>2</sub> O <sub>3</sub> | 9       | 8.8           | 2.8         | 4.9         | ~ 1000°C           |  |

| HfO <sub>2</sub>               | 25      | 5.8           | 1.4         | 3.3         | ~ 950°C            |  |

| HfSiO <sub>4</sub>             | 11      | 6.5           | 1.8         | 3.6         | > 900°C            |  |

| La <sub>2</sub> O <sub>3</sub> | 30      | 6.0           | 2.3         | 2.6         | -                  |  |

| a-LaAlO <sub>3</sub>           | 30      | 5.6           | 1.8         | 2.7         | ~ 1000°C           |  |

| Ta <sub>2</sub> O <sub>5</sub> | 22      | 4.4           | 0.35        | 2.95        | Not stable         |  |

| TiO <sub>2</sub>               | 80      | 3.5           | 0           | 2.4         | -                  |  |

| Y <sub>2</sub> O <sub>3</sub>  | 15      | 6.0           | 2.3         | 2.3         | Silicate formation |  |

| ZrO <sub>2</sub>               | 25      | 5.8           | 1.5         | 3.2         | Forms silicides    |  |

Table 1.1. Key characteristics of a wide variety of gate dielectrics on Si [13-16].

#### **1.3. Ge MOSFETs**

Replacing the  $SiO_xN_y$  with high-k material mainly solve the high power consumption issue in MOSFET scaling, however, as mentioned earlier, the new technology node also needs increased  $I_{on}$  for higher performance. Stress-induced improvement of device performance has been widely reported. However, the mobility enhancement by strain is subject to limitation [17]. Furthermore, as the transistor size becomes small enough (gate length < 20 nm), ballistic transport will become the dominant carrier transport mechanism. The transistor speed is no longer determined by the saturation velocity but the injection velocity at the source region, which is proportional to the mobility. Therefore, a MOSFET with high-k gate dielectrics and high mobility channel materials is a good option for future nanoelectronic devices.

|                                                                           | Ge                    | Si                    | GaAs                 | InSb                 | InP                  |

|---------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|----------------------|----------------------|

| Bandgap, $E_{g}$ (eV)                                                     | 0.66                  | 1.12                  | 1.42                 | 0.17                 | 1.35                 |

| Breakdown field (MV/cm)                                                   | 0.1                   | 0.3                   | 0.06                 | 0.001                | 0.5                  |

| Electron affinity, $\chi$ (eV)                                            | 4.05                  | 4.0                   | 4.07                 | 4.59                 | 4.38                 |

| Hole mobility, $\mu_h$ (cm <sup>2</sup> /V·s)                             | 1900                  | 450                   | 400                  | 1250                 | 150                  |

| Electron mobility, $\mu_e$ (cm <sup>2</sup> /V·s)                         | 3900                  | 1500                  | 8500                 | 80000                | 4600                 |

| Effective density of states in valence band, $N_v$ (cm <sup>-3</sup> )    | 6.0×10 <sup>18</sup>  | 1.04×10 <sup>19</sup> | 7.0×10 <sup>18</sup> | 7.3×10 <sup>18</sup> | 1.1×10 <sup>19</sup> |

| Effective density of states in conduction band, $N_c$ (cm <sup>-3</sup> ) | 1.04×10 <sup>19</sup> | 2.8×10 <sup>19</sup>  | $4.7 \times 10^{17}$ | $4.2 \times 10^{16}$ | 5.7×10 <sup>17</sup> |

| Lattice constant, a (nm)                                                  | 0.565                 | 0.543                 | 0.565                | 0.648                | 0.587                |

| Dielectric constant, k                                                    | 16                    | 11.9                  | 13.1                 | 17.7                 | 12.4                 |

| Thermal conductivity (W/cm·k)                                             | 0.58                  | 1.3                   | 0.55                 | 0.18                 | 0.68                 |

| Melting point, $T_{\rm m}$ (°C)                                           | 937                   | 1412                  | 1240                 | 527                  | 1060                 |

Table 1.2. Material properties of alternative channel materials [18, 19].

Table 1.2 lists the key material characteristics of Si, Ge and main III-V semiconductors. Among these materials, Ge offers the greatest potential for future CMOS application. Because it is the only material that provides higher mobility for both hole and electron with appropriate bandgap, breakdown field, thermal conductivity and melting point. In particular, the bulk hole mobility of Ge is the highest of all Group IV and III-V semiconductor materials. As shown later, it has actually been demonstrated that

#### Chapter 1: Introduction

unstrained Ge pMOSFETs can provide 3 times hole mobility against the Si universal hole mobility. Furthermore, Ge based MOS devices have shown to be compatible with strain technology for both nMOSFET [20] and pMOSFET [3]. It is found that the hole mobility enhancement of as high as ten is obtained by combing both Ge channel (GOI with 93% Ge content) and compressive strain [3]. Thus, Ge-channel MOSFETs have been regarded as one of the most promising channel materials for high speed application.

However, the current performance of Ge nMOSFETs is too poor to reach the level for the 22 nm node in the ITRS. Therefore, it maybe useful to investigate the feasibility of III-V MOSFETs because the enhancement factor of the bulk electron mobility against Si can amount to 3-50 for III-V semiconductors. However, it is easier to fabricate MOSFETs in Ge than in III-V materials since the surface passivation of III-V semiconductor is more challenging. Ge also has a larger density of states in the conduction band than III-V materials, which is another advantage for achieving a large drive current. It is suspected that the low mobility of Ge nMOSFETs is mainly attributed to the high density of interface traps of the gate stacks [21]. So Ge is also a potential nMOSFETs candidate if significant improvement of the interface quality can be achieved.

To realize the Ge-based CMOS technologies, there are a few issues to be solved, which are listed below [3]:

(1) High-k gate insulator formation with high quality interface and small EOT.

(2) High-quality Ge or GOI channel layer formation.

(3) Formation of low resistivity source/drain junctions.

- (4) Improvement of poor performance of Ge nMOSFETs

- (5) Reduction in large off state leakage current ( $I_{off}$ ) due to smaller bandgap

- (6) Appropriate CMOS structures and integration technologies.

In this thesis, we will focus on the issue (1). This is because in order to realize the desired high mobility Ge CMOS for sub-22 nm nodes, a viable high-k gate stack on Ge must at least have a low density of interface traps and small EOT.

#### 1.4. Current status of Ge channel MOS devices with high-k dielectrics

Due to the water soluble nature of amorphous GeO<sub>2</sub>, the early works mainly used germanium oxynitride as gate dielectrics. Rosenberg and Martin reported this kind of Ge pMOSFETs in 1988 [22]. Some subsequent result was reported from the same research group with improved hole mobility of 1050 cm<sup>2</sup>/V·s [23]. Further progress was made by Ransom *et al.* with both n-channel and p-channel MOSFETs together in 1991 [24]. A gate-self-aligned process flow was used in this paper, which is very close to contemporary device fabrication flow already. Both n- and p-channel mobilities obtained from long channel device characteristics were greater than 1000 cm<sup>2</sup>/V·s, which are much higher than the mobility obtained from Si devices. In 2002, effective hole mobility measured by split *C-V* method was reported by Shang *et al.* with GeON dielectrics that was less than 10 nm thick [25]. Over 40% hole mobility enhancement is obtained over the Si control and a subthreshold slope less than 100 mV/dec was demonstrated. Although these results are encouraging, the equivalent oxide thicknesses are all too large to meet the ITRS requirement. Chui *et al.* studied the scalability of field.

dielectrics for MOS applications [26]. They found that GeON was not suitable for highly scaled MOSFET application (EOT < 2 nm) due to the high leakage current density.

In order to meet the gate leakage requirement, high-k dielectrics must be implemented on Ge substrate. In 2002, Chui *et al.* demonstrated Ge MOS capacitors with ZrO<sub>2</sub> gate dielectrics for the first time [27]. The gate dielectric was formed by UHV sputtering of ~ 20-30 Å Zr films on the Ge surface followed by *in-situ* UV ozone oxidation at room temperature. EOT as low as 5~8 Å and *C-V* hysteresis as small as 16 mV were achieved. The group further reported the Ge pMOSFETs with such high-k dielectrics with peak hole mobility as high as 313 cm<sup>2</sup>/V·s [28]. However, the gate leakage currents for their samples were quite high and prevented the extraction of other device characteristics like interface states density. Kim *et al.* further investigated the ZrO<sub>2</sub>/Ge gate stack, which was formed by atomic layer deposition (ALD) [29]. Large frequency dispersion and hysteresis were presented in the *C-V* characteristics, which was ascribed to poor interface quality.

Although introduction of high-k gate dielectrics enabled the scaling of EOT, the interface quality is poor when high-k dielectrics directly deposited on the Ge substrate. For ZrO<sub>2</sub>/Ge gate stack, the poor interface quality was believed to originated from either the large areal density of interfacial dislocations due to the relatively large lattice mismatch or because of a very high density of interface states due to intrinsic differences in bonding coordination across the chemically-abrupt ZrO<sub>2</sub>/Ge interface [29]. For the HfO<sub>2</sub>/Ge gate stack, it was reported that a significant amount of germanium was found

inside HfO<sub>2</sub> film deposited by metalorganic chemical vapor deposition (MOCVD) [30]. Similar Ge incorporation was also observed in physical vapor deposition (PVD) HfO<sub>2</sub> on Ge substrate after high-temperature annealing [31]. There are several possible mechanisms causing the Ge diffusion into HfO<sub>2</sub>. Zhang *et al.* believed that the fast germanium diffusion in dielectrics is probably due to its higher self-diffusivity coefficient compared to Si [31]. Kita *et al.* suggested that the diffusion might be attributed to the desorption of Ge-riched volatile Hf-Ge-O [32]. Whereas some other studies speculated that the formation of volatile GeO at HfO<sub>2</sub>/Ge interface caused the diffusion [33]. The Ge diffusion into high-k dielectrics can cause significant degradation of interface quality and device performance. The high-k/Ge MOS characteristics tend to deteriorate when high-k/Ge is treated with thermal processes above 500 °C [34]. Such deterioration can be attributed to the fact that Ge-O bonds inevitably exist at the interface between Ge and high-k dielectrics.

The poor interface quality of high-k/Ge gate stack becomes the most challenging issue for the Ge MOSFETs. Many efforts have been made to improve the interface quality between high-k and Ge. In 2003, Bai *et al.* used an RTP NH<sub>3</sub> annealing before HfO<sub>2</sub> gate dielectric deposition for Ge MOS capacitors [35]. XTEM picture revealed that an ultra-thin interfacial layer (~8Å) was formed between the HfO<sub>2</sub> and Ge, which was believed to be the Ge oxynitride. By using the NH<sub>3</sub> passivation, electrical characteristics such as EOT, gate leakage current, hysteresis and  $D_{it}$  were significantly improved. The Ge pMOSFETs with such NH<sub>3</sub> treatment and HfO<sub>2</sub> gate dielectrics were further made by Ritenour *et al.* [36]. These devices exhibited sub-90 mV/decade substreshold swing and low gate leakage current. An 1.8 X enhancement of hole mobility was achieved compared to Si control wafers. Van Elshocht *et al.* [30] and Lu *et al.* [33] investigated the Ge diffusion for MOS capacitors with NH<sub>3</sub> treatment. It was found that there was much less Ge diffusion for samples with NH<sub>3</sub> treatment compared to samples without NH<sub>3</sub> treatment.

The physical characteristics of NH<sub>3</sub> annealing was investigated by Wu *et al.* [37]. High resolution XPS study showed that GeO<sub>x</sub>N<sub>y</sub> is formed during NH<sub>3</sub> annealing. The concentrations of oxygen and nitrogen were quantified to be about 0.83:0.17. Although high purity NH<sub>3</sub> gas (99.999%) was used in the experiment, the concentration of oxygen in Ge oxynitride was very high. They author suspected that the oxygen was introduced by the NH<sub>3</sub> gas source since the main impurity was O<sub>2</sub>, H<sub>2</sub>O and H<sub>2</sub>. The results also implied that Ge was much easier to be oxidized than nitrified. Gusev *et al.* further studied the microstructure of HfO<sub>2</sub> gate dielectric deposited on Ge [38]. It was found that the lack of an interlayer enables quisiepitaxial growth of HfO<sub>2</sub> on the Ge surface after wet chemical treatment whereas a nitrided interface (grown by thermal oxynitridation in NH<sub>3</sub>) resulted in an amorphous HfO<sub>2</sub>. Nitrided interfaces produced much better quality stacks.

Besides thermal NH<sub>3</sub> annealing, other techniques have also been reported to form the Ge oxynitride interlayer. Chen *et al.* reported an alternative surface nitridation technique by exposing the Ge substrate to an atomic N beam from a remote RF source at  $350^{\circ}$ C to  $600^{\circ}$ C [39]. Nuclear reaction analysis of nitride Ge substrate showed a nitrogen surface density of  $2.3 \times 10^{15}$  cm<sup>-2</sup>, translating to a substrate coverage of 3 to 4 monolayers. The surface nitridation was found to be effective to reduce EOT and *C-V* hysteresis for HfO<sub>2</sub> gated MOS capacitors. On the other hand, the nitridation also introduced a negative flatband voltage shift ~ 0.7 V, indicating of positive charge introduction or the incorporation of a charge dipole. Although improved electrical characteristics were obtained by surface nitridation, the  $D_{it}$  was still found to be high (~  $6 \times 10^{12}$  eV<sup>-1</sup>cm<sup>-2</sup>) near the mid-gap using high-frequency/low-frequency method. The author also reported Al<sub>2</sub>O<sub>3</sub> gated Ge MOS capacitor with surface nitridation. Interestingly, much lower  $D_{it}$  was found compared to HfO<sub>2</sub> gated samples, at the expense of increase in EOT and gate leakage current. To further minimize the GeO<sub>x</sub> (x<2) component and increase N incorporation in the Ge oxynitride interlayer, a wet-NO oxidation was proposed by Xu *et al.* [40]. The mechanisms involved probably lie in the hydrolysable property of GeO<sub>x</sub> in water-containing atmosphere.

Some groups of researchers also tried to fabricate Ge MOS structures with pure germanium nitride (Ge<sub>3</sub>N<sub>4</sub>). Because it is believed that the unstable GeO<sub>x</sub> component can degrade the interface quality and high oxygen concentration may also lead to partially crystallization of Ge oxynitride films [37]. However, most of the films obtained through thermal nitridation were Ge oxynitride. Oxygen incorporation in these films was unavoidable, attributed to native oxide or residual oxygen in the reactor or oxygen impurities in the gas sources. Maeda *et al.* presented a demonstration of pure nitridation of clean Ge substrate using a plasma process at low temperatures [41]. The surface cleaning of Ge substrate and subsequent nitridation were performed in the same chamber.

#### Chapter 1: Introduction

In situ physical characteristics showed that oxygen was not present in these germanium nitride films. They also managed to fabricated the Ge MOS capacitors with EOT as low as 1.23 nm. These devices exhibited good high-frequency C-V characteristics but the gate leakage current is substantially high due to the fact that  $Ge_3N_4$  was not a high-k material. The same group of researchers further optimized the process conditions and they found the smoothest interface and surface can be achieved in the Ge<sub>3</sub>N<sub>4</sub> films grown at 100°C [42]. It was also pointed out that the top surface of Ge<sub>3</sub>N<sub>4</sub> films was oxidized easily once the Ge<sub>3</sub>N<sub>4</sub> films were exposed to air. The similar phenomenon was also reported by Kutsuki et al. [43]. They found that humidity in the air accelerated the degradation of  $Ge_3N_4$  layers and that under 80% humidity condition, most of the Ge-N bonds converted to Ge-O bonds. Therefore it is essential to take the best care of moisture in the fabrication of Ge MOS devices with Ge<sub>3</sub>N<sub>4</sub> insulator or passivation layer. Maeda et al. further demonstrated HfO<sub>2</sub> gated Ge MOS capacitors with pure Ge<sub>3</sub>N<sub>4</sub> interfacial layers [44]. The gate stack exhibited excellent interface quality with minimum  $D_{it} \sim 1.8 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ . It was noteworthy that  $D_{it}$  increased exponentially as the energy approached to the midgap. The thermal stability of the high-k gate stack was also improved with Ge<sub>3</sub>N<sub>4</sub> interfacial layer. However, there is no report on transistor performance in that paper.

As mentioned earlier, pure  $Ge_3N_4$  is hard to form on Ge surface due to two reasons. The first is that it is difficult to avoid residual oxygen content inside the process chamber or at Ge surface. The second is that Ge is much easier to be oxidized than nitrided [37]. Thus, some other groups of researchers tried to use metal nitride or metal oxynitride passivation layer to minimize the GeO<sub>x</sub> (x<2) content at high-k/Ge surface.

Gao et al. demonstrated a surface passivation using AlN<sub>x</sub> film for HfO<sub>2</sub> gated Ge MOS capacitors [45]. The AlN<sub>x</sub> layer was deposited by reactive sputtering of Al target in N<sub>2</sub>/Ar ambient. For comparison, they also fabricated Ge MOS capacitors with thermal NH<sub>3</sub> treatment. Interestingly, the author found that the intensity of GeO<sub>2</sub> peak increased significantly after HfO<sub>2</sub> deposition for sample with surface nitridation, indicating that most of the  $GeO_x$  component was formed at interface during the  $HfO_2$  deposition process. Whereas for devices with  $AlN_x$  passivation, the  $GeO_x$  component was reduced because AlN<sub>x</sub> acted as a better oxygen diffusion barrier. The electrical characteristics and thermal stability was also improved for device with AlN<sub>x</sub> passivation. Kim et al. further made both n and p channel Ge MOSFETs with AlN<sub>x</sub> or Hf<sub>3</sub>N<sub>4</sub> passivation layer deposited by ALD [46]. Good C-V characteristics were achieved with EOT as low as 0.8 nm. However, the devices exhibited quite high interface states. The mobility for pMOSFETs was only slightly higher than Si hole universal and mobility for nMOSFETs was much lower than Si electron universal. It can be seen that although metal nitride passivation layer acts as a better oxygen barrier, but the high  $D_{it}$  seems to an intrinsic problem that limits its implementation for MOSFETs fabrication. Some recent works presented another  $TaO_xN_y$ passivation layer, formed either by plasma enhanced ALD [47] or reactive sputtering (with PDA) [48]. TaO<sub>x</sub>N<sub>y</sub> interlayer was demonstrated to be a good diffusion barrier between high-k and Ge. Electrical characteristics like EOT, hysteresis and D<sub>it</sub> were improved. Dit value was lower than MOS capacitors with AlNx or Hf3N4 interlayer reported earlier. A peak hole mobility of 225 cm<sup>2</sup>/V·s was demonstrated for Ge pMOSFETs with TaO<sub>x</sub>N<sub>y</sub> interlayer, which was about ~1.7 X enhancement over Si hole universal.

By now, we have reviewed a few nitride based Ge surface passivation techniques. By forming Ge oxynitride, Ge<sub>3</sub>N<sub>4</sub>, metal nitride or metal oxynitride interlayer, high-k gated Ge MOS devices showed improved electrical characteristics such as EOT, gate leakage current, *C-V* characteristics and  $D_{it}$ . The improvements are attributed to less Ge diffusion into high-k dielectrics by reducing the amounts of GeO<sub>x</sub> (x<2) formation at interface. High-k gated Ge pMOSFETs with enhanced hole mobility (as high as a 1.8X Si universal) have been demonstrated whereas electron mobility of Ge nMOSFETs is very poor.

Besides the nitride based surface passivation techniques, another alternative passivation process-Si passivation was proposed and demonstrated on HfO<sub>2</sub> gated Ge MOS capacitors by Wu *et al.* in 2004 [49]. Two important criteria were pointed out for an effective Si passivation: (1) Si must completely cover the Ge surface and Ge surface should be free of germanium oxide; (2) The Si passivation layer should be thin enough and consumed during the subsequent high-k deposition so that the MOSFET channel is still kept in Ge. XPS studies showed that Ge-O bonds were greatly reduced by Si passivation and Si cap layers were totally oxidized after HfO<sub>2</sub> deposition. Very good *C-V* characteristics were achieved with EOT as low as 13.5Å and gate leakage current as low as  $1.16 \times 10^{-5}$  A/cm<sup>2</sup>@ 1V. Wu *et al.* further demonstrated TaN/HfO<sub>2</sub>/Ge pMOSFETs with Si passivation [50]. TEM picture showed that a thin amorphous interfacial layer was obtained after Si passivation. Ge pMOSFETs with NH<sub>3</sub> treatment were also fabricated for comparison. The author found that devices with Si passivation exhibited lower gate leakage current and better thermal stability. The improvements were believed to be

resulted from the significant suppression of unstable germanium oxide formed at interface, as well as the uniform amorphous interfacial layer after the silicon passivation process. The peak hole mobility for NH<sub>3</sub> treated and Si passivated MOSFETs were 79.9 cm<sup>2</sup>/V·s and 194.1 cm<sup>2</sup>/V·s, respectively. The author further optimized the Si passivation process by tuning the Si interlayer and HfO<sub>2</sub> thickness [51]. It was found that by increasing the Si cap thickness and decreasing the HfO<sub>2</sub> thickness, better *C-V* characteristics and interface quality were achieved. This is because increasing the amount of Si would reduce the amount of GeO<sub>x</sub> (x<2) at the interface and hence, lead to fewer interface traps. At the same time, increasing HfO<sub>2</sub> thickness tends to consume more Si, and more GeO<sub>x</sub> might form, resulting in worse interface quality. A much higher hole mobility with peak ~ 240 cm<sup>2</sup>/V·s was achieved by optimizing the ratio between HfO<sub>2</sub> and Si. Ge nMOSFETs were also reported with peak electron mobility ~ 215 cm<sup>2</sup>/V·s, which was still much lower than Si electron universal.

In 2006, Zimmerman *et al.* demonstrated HfO<sub>2</sub> gated Ge pMOSFETs with Si passivation fabricated with a Si-compatible process flow using 200 mm (100) Ge-on-Si wafers [52]. Approximately a 3X mobility enhancement was observed compared to Si hole universal with EOT ~ 1.2 nm. Short channel devices were also fabricated using the same process flow. Correcting for  $R_s$ , the peak field effective mobilities extacted for even the shortest devices ( $L_g \sim 0.125 \mu m$ ) remained above 300 cm<sup>2</sup>/V·s. Joshi *et al.* also reported high mobility (~ 3X Si) Ge pMOSFETs using direct SiO<sub>x</sub> passivation [53]. Highly scaled sub-100 nm Ge pMOSFETs with Si passivation were also demonstrated [54, 55]. Similar to Wu's finding [51], it was also found that the interface quality was

improved with increasing Si cap thickness. Mitard *et al.* further observed that Ge could diffuse into Si and this Ge incorporation in Si could give strong impact on electrical performance. A low temperature Si layer deposition at 350°C was proposed to solve this issue [54].

The principles of both nitride based passivation and Si passivation actually are quite similar. Both passivation techniques improve the gate stack quality by reducing the volatile  $\text{GeO}_x$  (x<2) formation at high-k/Ge interface and suppress the Ge diffusion into high-k dielectrics.

As in the case of SiO<sub>2</sub> with Si, GeO<sub>2</sub> is still believed to be the ideal passivating layer for Ge. Unlike the Ge sub-oxide (GeO<sub>x</sub>), GeO<sub>2</sub> is not a volatile material and thus has the potential to act as a dielectric material. In 2007, Takahashi *et al.* investigated the possibility of using GeO<sub>2</sub> as a gate dielectric for Ge MOS devices [56]. They firstly studied the GeO<sub>2</sub>/Ge interface kinetics by annealing the stack at different temperatures. It was observed that GeO<sub>2</sub> reacted with Ge forming volatile GeO which desorbs above 500-600°C. It can be easily expected that GeO desorption should degrade the dielectric film and interface characteristics. Therefore, a Ni-FUSI cap layer, which acted as part of gate electrode, was implemented on GeO<sub>2</sub>/Ge stack to suppress the GeO desorption. Surprisingly, very good *C-V* characteristics were achieved. Both Ge p- and n- channel MOSFETs were fabricated using Ni-FUSI/GeO<sub>2</sub>/Ge gate stack. Recorded hole mobility ~ 370 cm<sup>2</sup>/V·s with S/D resistance correction was obtained for pMOSFETs whereas ~ 270 cm<sup>2</sup>/V·s without S/D resistance correction was obtained for nMOSFETs. Matsubara *et al.*  further investigated the interface quality of GeO<sub>2</sub>/Ge using low temperature conductance method [57]. It was found that very promising interface quality could be obtained for GeO<sub>2</sub>/Ge interface with  $D_{it}$  as low as  $9.3 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>, which was approaching to SiO<sub>2</sub>/Si standard. The same group further presented very high hole mobility (> 400 cm<sup>2</sup>/V·s) Ge pMOSFETs with this GeO<sub>2</sub> dielectric layer capped with SiO or Al<sub>2</sub>O<sub>3</sub> [58]. However, the physical thickness of their gate stack was quite large (> 40 nm).