# TOP-DOWN SI NANOWIRE TECHNOLOGY IN DISCRETE CHARGE STORAGE NONVOLATILE MEMORY APPLICATION

## FU JIA

(B. Eng., Xi'an Jiaotong University)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2009

## Acknowledgements

I have been very fortunate to be a member of an active and open research lab in the National University of Singapore (NUS) and the Institute of Microelectronics (IME), a reputable A\*STAR research institute. Prof. Zhu Chun Xiang, my main supervisor in the Silicon Nano Device Laboratory, NUS, is the most important person to my research work. I would like to thank him for bringing me into this colorful research world and also giving me many opportunities and freedom to pursue my interests. I would also like to thank Dr. Yu Ming Bin, my co-supervisor in IME, for his guidance and assistance that allowed me to adapt to a new working environment quickly. My sincere gratitude goes to Dr. Navab Singh and Dr. Lo Guo Qiang, who played a significant role in my research work in IME and gave me inspirations for many ideas. All of them are great mentors who have provided me with their patient guidance.

PhD life has been an enjoyable journey. I will always remember the interesting and precious memories I had of lectures by inspiring lecturers Prof. Cho Byung Jin, Prof. Ganesh Samudra, Prof. Yoo Wong Jong, Prof. Lee Sung Joo and my own professor in my initial two years in NUS. I also had a joyful time collaborating with my lab fellows. I would like to thank my seniors and colleagues in Prof. Zhu's group, such as Dr. Yu Xiongfei, Dr. Wu Nan, Dr. Zhang Qingchun, Dr. Huang Jidong, Dr. Song Yan, Chunfu, Jianjun and Ruilong for their guidance and encouragement. I would also like to express my gratitude to all my SNDL friends, such as Dr Ren Chi, Dr. Wang Yingqian, Dr. Gao Fei, Dr. Wang Xinpeng, Dr. Tan Kian Ming, Dr. Shen Chen, Chen Jingde, Pu Jing, Jiang Yu, Zhang Lu, Zhao Hui, Zang Hui, He Wei, Yang

Weifeng, Peng Jianwei, Wang Jian and Lee Wayne Yong, for their guidance and close friendship which I will always treasure. I would like to take this opportunity to thank the technical staffs in SNDL and IME for their great support and assistance in my PhD study.

My deepest gratitude goes to my dear parents. Your strong confidence towards me could drive any scares away from me over these years. My special thanks here go to you, Mr. Loh Guo Pei. Your knowing love makes me feel that I could never be lonely in any difficult circumstance.

# **Table of Contents**

| Acknowledgements      | I    |

|-----------------------|------|

| Table of Contents     | III  |

| Summary               | VI   |

| List of Tables        | VIII |

| List of Figures       | IX   |

| List of Symbols       | XV   |

| List of Abbreviations | XVII |

# **Chapter 1 Introduction**

| 1.1 Introduction of Semiconductor Memory Technology     | 1  |

|---------------------------------------------------------|----|

| 1.1.1 Semiconductor Memory Categories                   | 1  |

| 1.1.2 Structure and Operation Mechanism of Flash Memory | 5  |

| 1.1.3 Challenges of Semiconductor Flash Memory Scaling  | 9  |

| 1.2 Scope of Project                                    | 15 |

| 1.3 Organization of Thesis                              | 16 |

| Reference                                               | 18 |

# Chapter 2 Literature Review

| 2.1 Introduction           | . 21 |

|----------------------------|------|

| 2.2 Gate Stack Engineering | . 21 |

| 2.2.1 Nanocrystal Memory   | . 21 |

| 2.2.2 Bandgap Engineering Memory               |  |

|------------------------------------------------|--|

| 2.2.3 High-к-based MONOS Memory                |  |

| 2.3 Novel Structure Nonvolatile Memory Devices |  |

| 2.4 Si Nanowire Technology                     |  |

| 2.4.1 Bottom-up Approach                       |  |

| 2.4.2 Top-down Approach                        |  |

| Reference                                      |  |

## Chapter 3 Gate-All-Around Si Nanowire SONOS Memory

| 3.1 Introduction                                    |    |

|-----------------------------------------------------|----|

| 3.2 Nanowire and Nanowire Memory Device Fabrication |    |

| 3.3 Results and Discussion                          |    |

| 3.4 Conclusion                                      | 58 |

| Reference                                           | 59 |

# Chapter 4 GAA Nanowire for TFT SONOS Multi-Level-Cell Memory Application

| 4.1 Introduction                                   |  |

|----------------------------------------------------|--|

| 4.2 Poly-Si Nanowire TFT Memory Device Fabrication |  |

| 4.3 Results and Discussion                         |  |

| 4.4 Conclusion                                     |  |

| Reference                                          |  |

# Chapter 5 GAA Nanowire MONOS for High Speed Memory Application

| 5.1 Introduction                             | 2 |

|----------------------------------------------|---|

| 5.2 TAHOS Nanowire Memory Device Fabrication | 4 |

| 5.3 Results and Discussion |  |

|----------------------------|--|

| 5.4 Conclusion             |  |

| Chapter 6 Conclusions      |  |

| 00 |

|----|

| L  |

## **Summary**

The commercial flash memory, which currently uses a polysilicon floating gate as the charge storage material, has faced issues of non-scalability of the tunnel oxide and interpoly dielectric in the course of scaling, due to the significantly reduced coupling ratio and serious gate interference. Due to scaling limitations of the conventional floating-gate nonvolatile flash memory cells, another type of nonvolatile memory based on discrete charge trapping is currently being considered as a promising alternative. The discrete charge storage nonvolatile memories are immune to local defect related leakage due to isolated charge storage nodes, providing larger scaling capability than floating gate devices.

This thesis proposes methodologies to resolve issues of gate stack scaling and voltage scaling in the SONOS type discrete charge storage nonvolatile memory in order to increase the possibility of it being employed in future semiconductor nonvolatile memory application. This thesis discusses solutions to scale the discrete trapped charge-storage nonvolatile memory based on a state-of-the-art non-traditional structure – a gate-all-around nanowire channel structure – whose fabrication method completely follows the CMOS-compatible rule in order to increase industrial adaptability of this novel technology.

A high-speed SONOS nonvolatile memory cell with a gate-all-around (GAA) Si-nanowire architecture is discussed in detail. The method of fabricating vertically stacked top-down nanowires with 5-nm diameter is highlighted. The nanowire SONOS device exhibits evident improvements in low voltage programming and fast programming and erasing speeds with regards to the planar control device. The performance enhancement mechanism shall be explained by device modeling which investigates electron energy distribution, potential energy profile and electric field along each layer surrounding the nanowire channel. The gate-all-around nanowire channel structure is introduced into the poly-Si memory as a promising methodology to resolve issues of poor device subthreshold performance, low memory speed and inferior device uniformity in low temperature polycrystalline Si TFT memory devices, which can be integrated in future system-on-panel and system-on-chip applications. A strategy of optimizing SONOS-type memory characteristics is illustrated and discussed by integrating high- $\kappa$  dielectric materials and metal gate electrode. The application of high- $\kappa$  materials and TaN metal gate electrode, used to replace the conventional material used in nitride-based SONOS devices, exhibits improvement of memory erasing characteristics and causes of the performance enhancement will be investigated.

This thesis discusses several strategies to overcome challenges that SONOStype discrete charge storage nonvolatile memory currently faces. In conclusion, novel device structures, in addition to new materials such as high- $\kappa$  dielectrics and high work function metal gates, are promising candidates that can potentially be integrated into memory devices. Devices with the nanowire channel structure show promise for future nonvolatile applications due to their improved performance.

# List of Tables

**Table 4.1**Comparison of memory characteristics with reported TFT p.76SONOS-type memory devices. The GAA nanowire TFT<br/>memory in this work displays the advantages in both<br/>electrostatic and transient characteristics.

# **List of Figures**

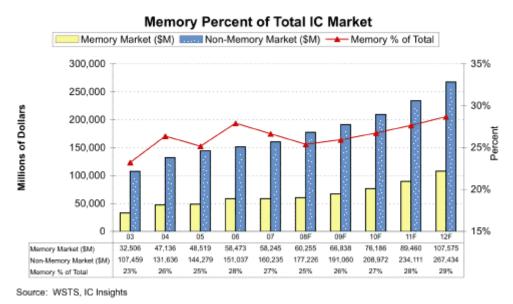

| Fig. 1.1 | Revenues of semiconductor memory market versus year.                                                                                                                                                                                                                                                                                                                                                                            | p.1  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

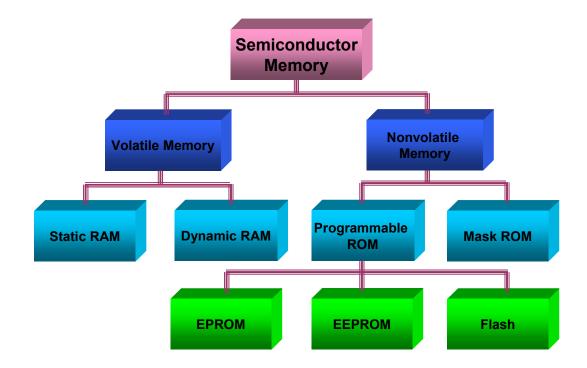

| Fig. 1.2 | Semiconductor memory family tree                                                                                                                                                                                                                                                                                                                                                                                                | p.2  |

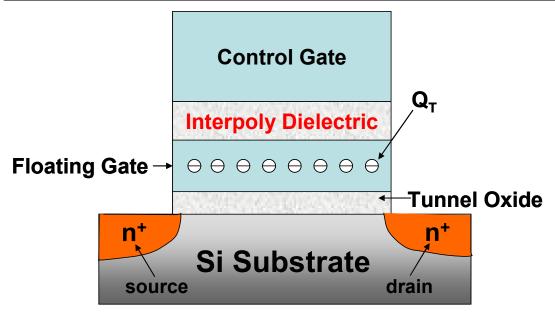

| Fig. 1.3 | A schematic cross-section of a single floating-gate transistor. FG is surrounded by dielectric layers and isolated from channel and IPD. Taking the n-type memory cell as an example, electrons are injected from substrate by applying a positive voltage stress at the gate. Electrons will be trapped in the FG even after the power is removed from the gate.                                                               | p.6  |

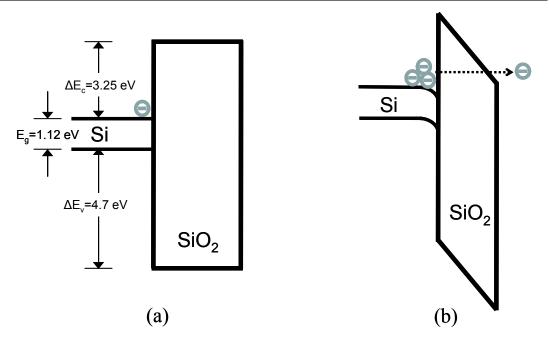

| Fig. 1.4 | Si and SiO <sub>2</sub> energy band diagram system (a) without applying<br>any voltage and (b) with applying a positive voltage at SiO <sub>2</sub><br>side. Electrons are able to tunnel through the thick SiO <sub>2</sub> layer by<br>F-N tunneling due to a strong electric field reduces the barrier<br>width. Conduction and valence band offset ( $\Delta E_c$ and $\Delta E_v$ ) keeps<br>unchanged during the process. | p.8  |

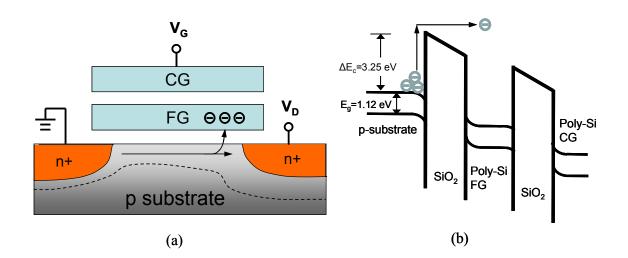

| Fig. 1.5 | (a) At CHE stress condition, electrons gain enough energy while<br>drifting across the channel and are injected through the tunnel<br>oxide, causing a gate current. (b) Energy band diagram of a<br>floating-gate memory cell during programming by hot-carrier<br>injection.                                                                                                                                                  | p.9  |

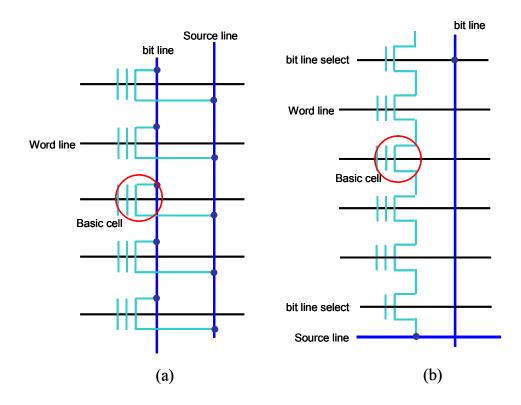

| Fig. 1.6 | Comparison of NOR and NAND flash architectures (a) NOR-<br>type with shared bit line and source line. (b) NAND-type with a<br>common bit line and a common source line, showing concise<br>structure advantage.                                                                                                                                                                                                                 | p.10 |

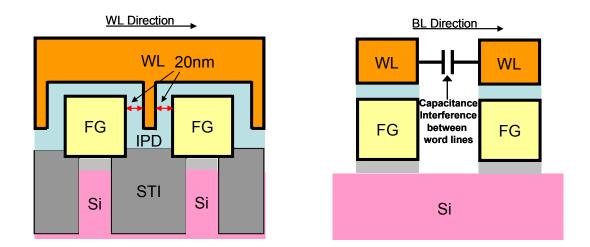

| Fig. 1.7 | Schematic cross section of a floating-gate cell in a (a) word line                                                                                                                                                                                                                                                                                                                                                              | p.12 |

Fig. 1.7 Schematic cross section of a floating-gate cell in a (a) word line p.12 direction and (b) bit line direction. (a) Space between neighboring FG becomes too narrow to be filled with two IPD layers and control gate poly-Si. (b) V<sub>th</sub> of an unselected cell can be programmed mistakenly due to the capacitance interference

of the adjacent charge.

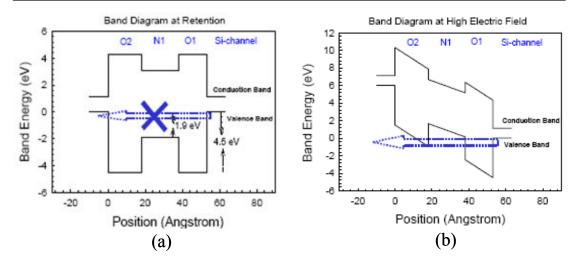

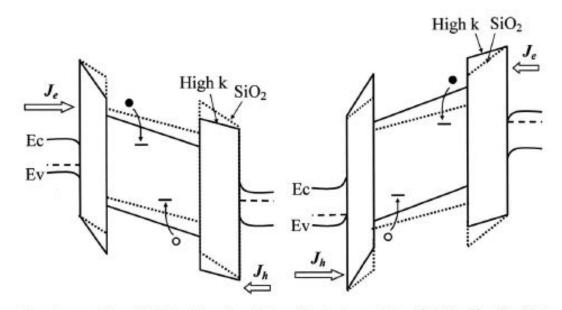

- **Fig. 2.1** The band diagram of BE-SONOS under different electric fields, p.24 showing only the tunnel oxide part. (a) At retention mode, direct tunneling is prohibited since the barrier width carriers experience is the whole physical thickness of ONO layer. (b) At program/erase mode or under high electric field, carriers could only see the thickness of a thin layer of oxide; hence the speed can be significantly enhanced due to reduced barrier width.

- **Fig. 2.2** Schematic band diagram for the memory device using nitride p.25 (dashed line) and high-k (solid line) as charge trapping layer under electric field at the perform mode (a) and erase mode (b). The electric field across the blocking oxide is released and transferred to tunnel oxide, hence the carriers tunneling efficiency is improved compared with ONO device.

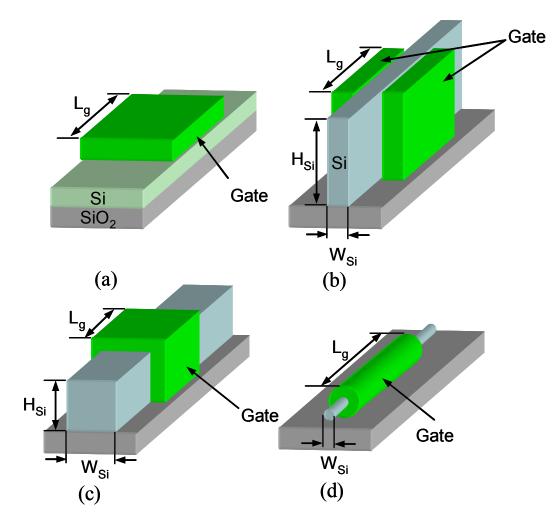

- Fig. 2.3 Progression of device structure from a single-gated planer on p.28 SOI to a fully GAA nanowire channel, with the number of gates increasing. (a) Single-gate structure. (b) Double gate structure, with a tall fin and two symmetrical gates electrically interconnected. (c) Tri-gate or FinFET structure, where gate electrode controls the channel on three surfaces. (d) Gate-all-around structure with a nanowire channel.

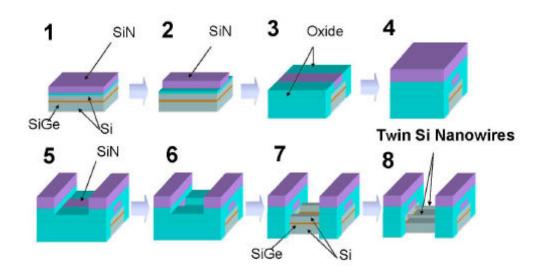

- Fig. 2.4 Progress flow of the damascene-gate nanowire device p.31 fabrication used by Samsung's group (1) SiGe / Si growth and shallow trench isolation (STI) (2) hard mask SiN trimming (3) oxide fill in STI and CMP (4) damascene gate stack deposition (5-6) 1st and 2nd damascene gate etch (7) field oxide recess (8) SiGe removal and H<sub>2</sub> anneal and (9) gate oxide and gate material deposition.

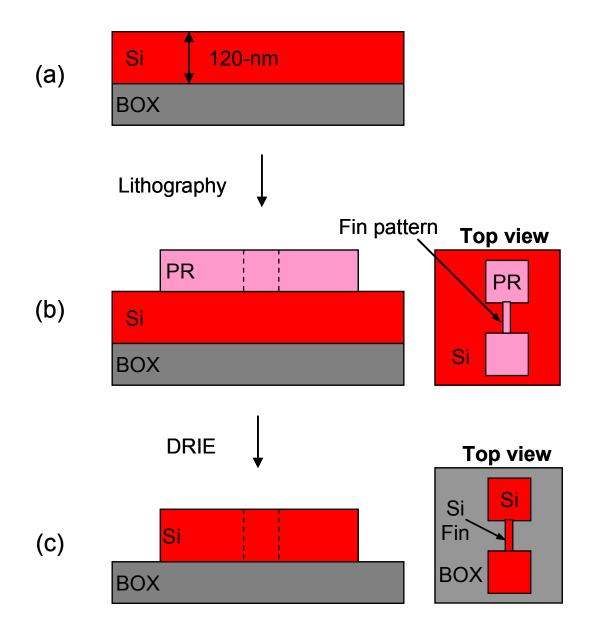

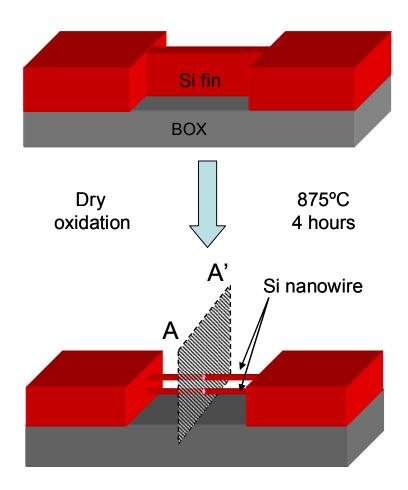

- **Fig. 3.1** Schematic of the Si fin fabrication process. Starting wafer p.43 consisting of 120-nm Si layer (a) has undergone lithography (b) and the DRIE process (c) to achieve the Si fin. The smallest defined fin width is 40-nm after the resist trimming process, and the DRIE with the well-anisotropic property enables the good quality fin etch.

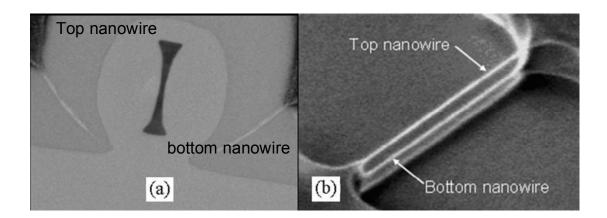

- Fig. 3.2 (a) Sample prepared before the oxidation process is finished, p.45 TEM image shows the phenomenon where two nanowires are formed if the Si fin has a high aspect ratio. (b) Tilted SEM image shows the two vertically staked Si nanowire channels connecting S/D pads.

- **Fig. 3.3** Schematics of the Si nanowire fabrication process. The Si p.45 nanowire is fabricated using self-limiting oxidation at a temperature below 950°C. A high aspect ratio of the fin ensures there will be two vertically stacked nanowires. The vertically stacked nanowires have the advantage of space saving as compared to laterally stacked nanowires.

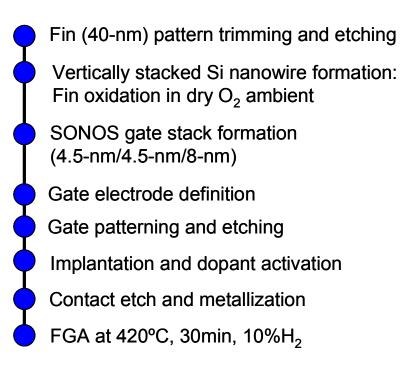

- **Fig. 3.4** Process flow depicting the formation of vertically stacked twin p.46 Si nanowire and GAA Si nanowire nonvolatile memory device.

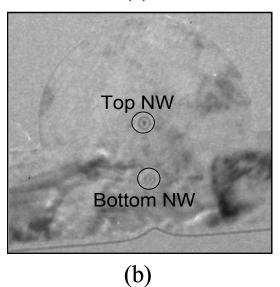

- Fig. 3.5 (a) The titled SEM image of actual device taken before the p.47 passivation  $SiO_2$  was deposited. (b)Vertically stacked two Si nanowire (VST-SiNW as indicated) channels were surrounded by ONO and poly-Si gate electrode.

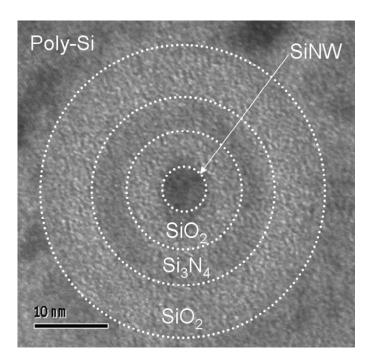

- Fig. 3.6 The high resolution TEM picture shows the cross section part of p.48 one of the two nanowire channels of a fully processed nanowire SONOS device. The Si nanowire with surrounding ONO layers followed by poly-Si gate could be seen clearly. Diameter of wire is about 5-nm and the thickness of each layer of ONO gate stack is 4.5-nm/4.5-nm/8-nm.

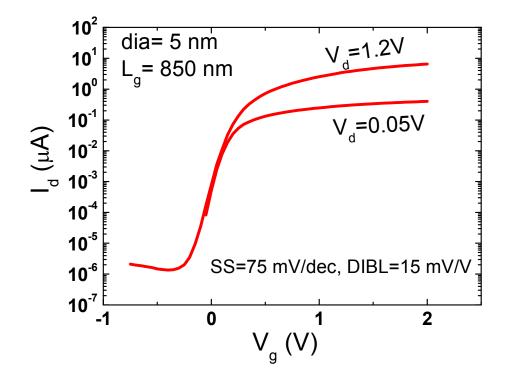

- **Fig. 3.7** The transfer characteristics of GAA nanowire memory devices p.49 with nanowire diameter of 5-nm and gate length of 850-nm shows good electrostatic behavior.

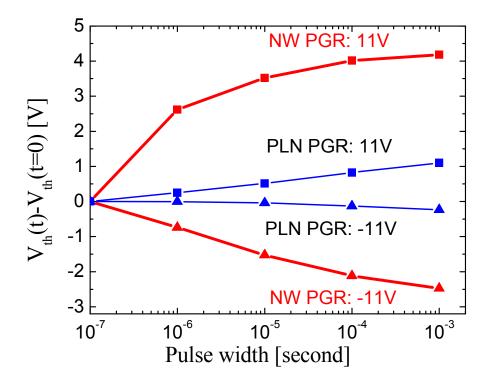

- Fig. 3.8 Transient memory characteristics of nanowire SONOS (NW) p.50 device and planar (PLN) control device at  $\pm$  11 V pulse stresses. Devices with a gate length of L<sub>G</sub> 850-nm are used for characterization. Channel widths are 5-nm for NW device (diameter) and 5-µm for PLN device respectively.

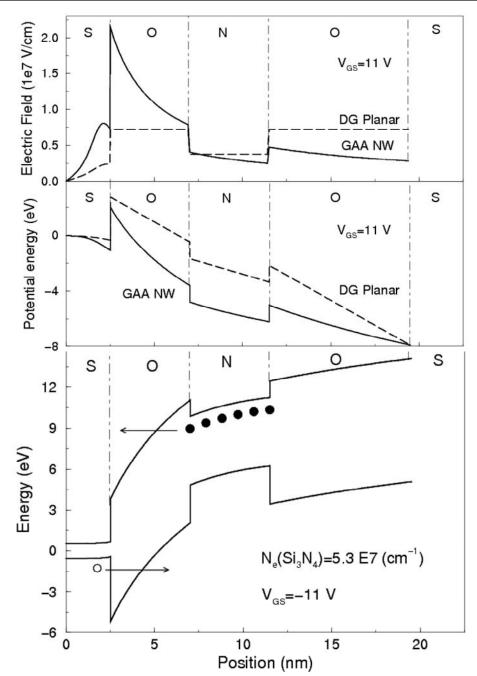

- **Fig. 3.9** Simulated (a) electric field distribution and (b) potential energy p.52 profile of GAA nanowire and planar structures at gate stress 11 V. For the GAA device (solid line), the electric field at the Si-SiO<sub>2</sub> interface is almost three times larger as compared to the planar device (dashed line). The effective barrier width of the GAA nanowire device is also less than half the oxide physical thickness. (c) Potential energy profile at  $V_{GS} = -11$  V prior to the start of the erasing process for the GAA nanowire device. An electron concentration of  $5.3 \times 10^7$  cm<sup>-1</sup>, corresponding to a shift of 2.6V in V<sub>th</sub>, is assumed in the nitride layer. The barrier width for holes tunneling from the channel to the oxide is reduced due to the cylindrical architecture, thus increasing the erase speed.

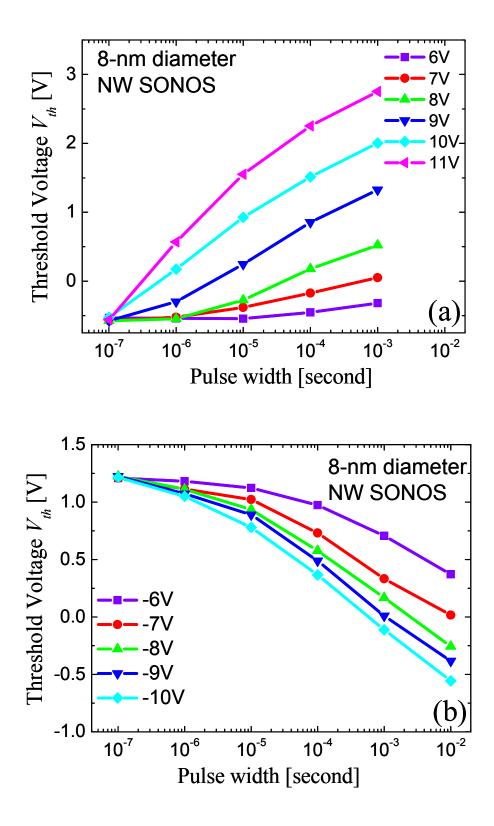

- Fig. 3.10 (a) Programming and (b) erasing characteristics of Si nanowire p.54 SONOS cell (NW diameter  $\sim 8$ -nm) of gate length of 850-nm. Based on the programming characteristics, this device exhibits a  $V_{th}$  shift of 1.13 V in 1  $\mu$ s using a pulse of +11 V on the gate.

- Fig. 3.11 (a) Programming and (b) erasing characteristics of Si nanowire p.55 SONOS cell (NW diameter ~ 5-nm) of gate length of 850-nm. Based on the programming characteristics, this device exhibits a  $V_{th}$  shift of 2.61 V in 1 µs using a pulse of +11 V on the gate.

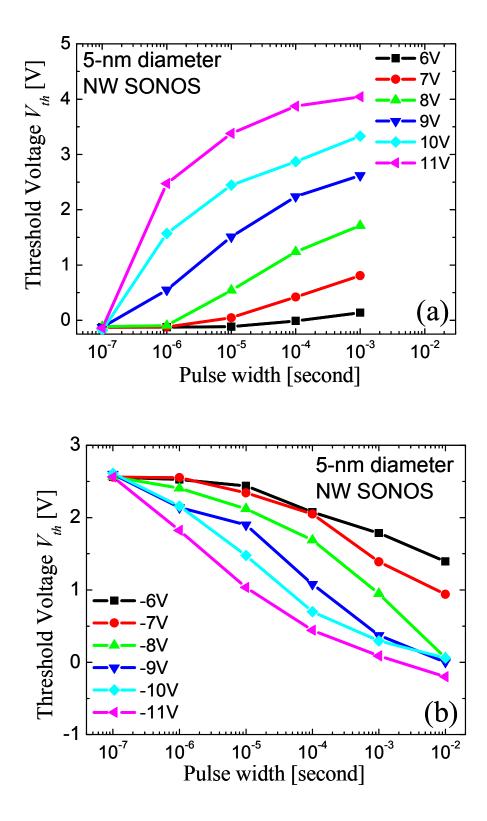

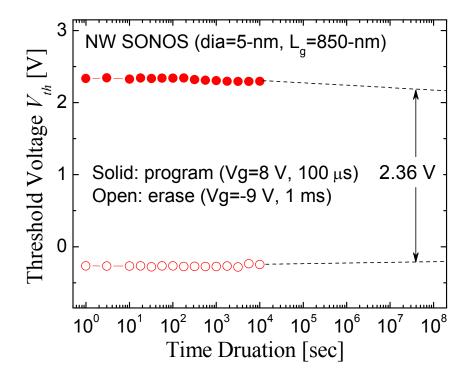

- Fig. 3.12 Room-temperature data retention properties for nanowire p.57 devices. The stored charge could be kept well for the measured  $10^4$  seconds.

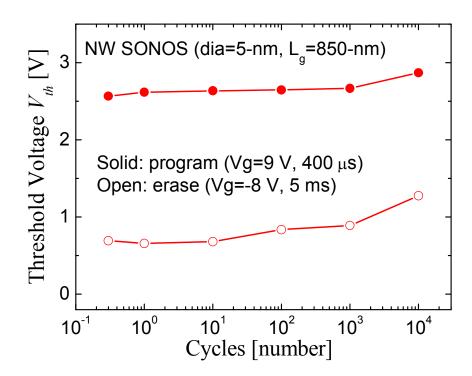

- Fig. 3.13 Endurance characteristics of the Si nanowire SONOS device. p.57

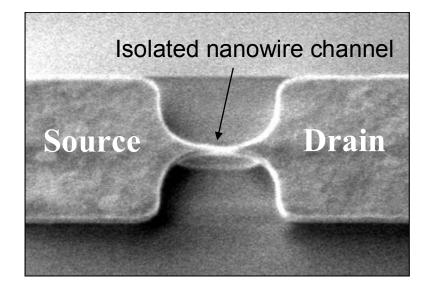

- **Fig. 4.1** A tilted SEM image of isolated nanowire channel with source p.66 and drain pads located on SiO<sub>2</sub> after the nanowire was released in DHF. It can be seen that the amorphous Si has converted to poly-Si after the steam oxidation step.

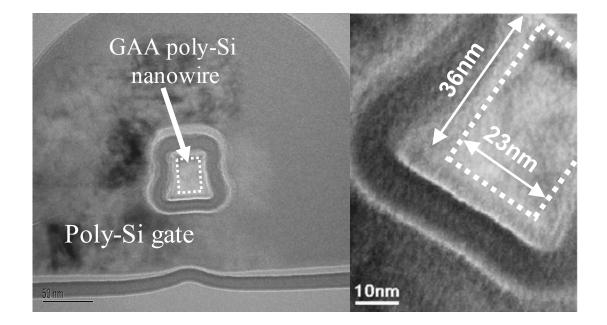

- **Fig. 4.2** TEM cross-section through the poly-Si nanowire of a fabricated p.66 device. The cross-section was cut across the nanowire channel. The nanowire channel width and height are 23-nm and 36-nm respectively as shown by the arrows.

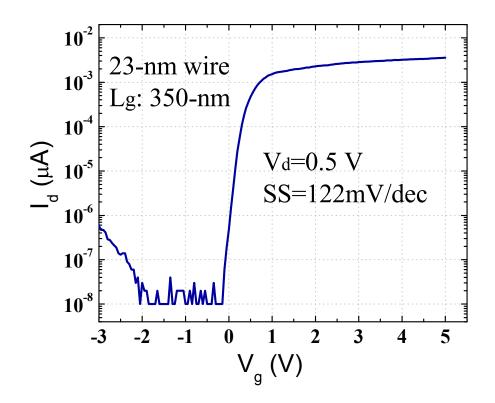

- **Fig. 4.3** Transfer characteristics of nanowire TFT SONOS device with p.67 23-nm width and 350-nm gate length. Improved SS is exhibited as compared to other reported TFT SONOS memory devices.

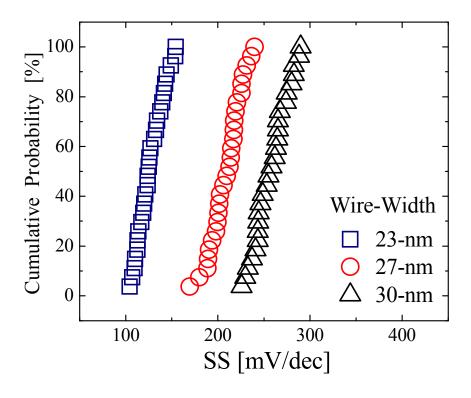

- **Fig. 4.4** The dependence of SS on poly-Si nanowire width. It can be seen p.68 that the device with smaller wire width achieves better SS, which is due to reduced gate controllability and increased volume of grain boundaries in the wider nanowire channel.

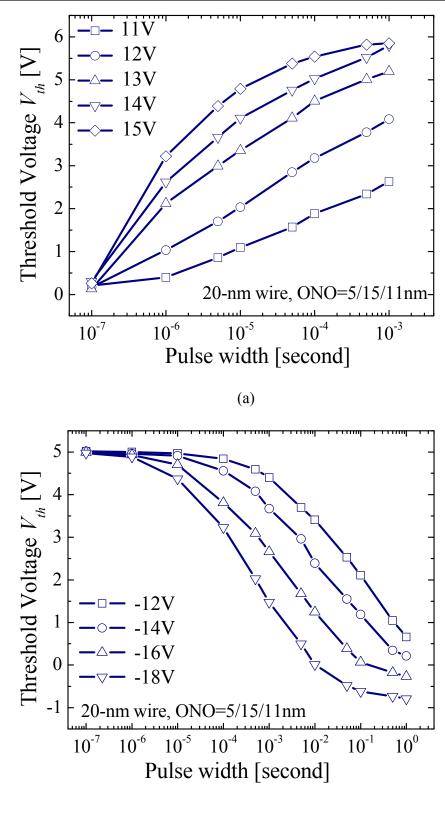

- Fig. 4.5 The P/E characteristics of nanowire TFT SONOS with wire p.71 width 23-nm. The gate pulse stress ranged from 11 V to 15 V and -12 V to -18 V.  $\Delta V_{th}$  of 2.96 V could be achieved in 1  $\mu$ s at 15 V gate pulse during program.

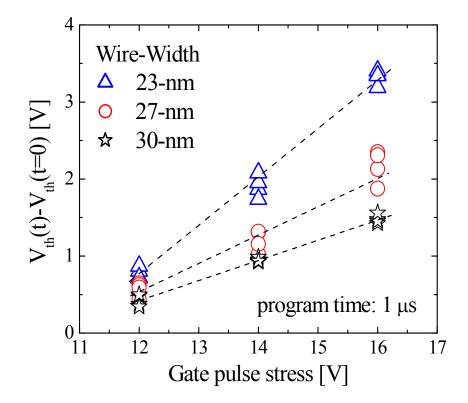

- **Fig. 4.6** Comparison of memory window among devices with three p.72 different nanowire widths under different stress voltage for a program time of 1 μs. The device with the narrowest wire width

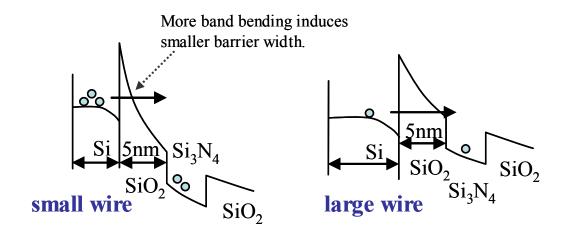

shows the fastest speed.

- **Fig. 4.7** The band diagram during program in devices with smaller wire p.73 width (left) and larger wire width (right). Stressed at the same voltage, the electric field across the tunnel oxide of the device with smaller wire width is enhanced as compared to that of the counterpart, due to the particular GAA structure.

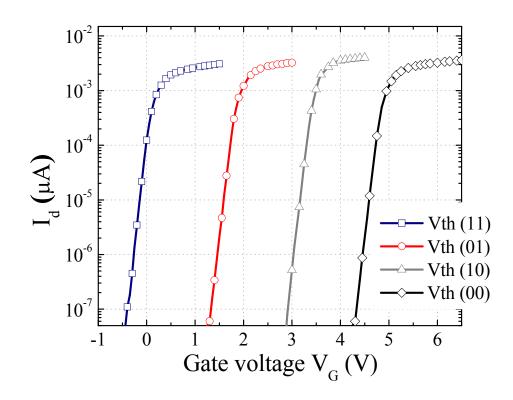

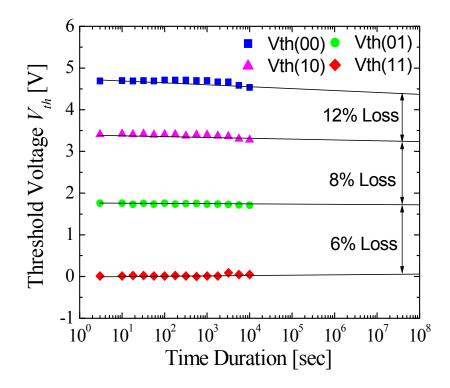

- Fig. 4.8 The  $I_d$ -V<sub>g</sub> at four states shows the feasibility of the MLC p.74 application for TFT SONOS. Around 1.5-V memory window is set between the different states.

- **Fig. 4.9** The room temperature retention properties measured at different p.75 data states. The most severe degradation is 12% charge loss after 10 years.

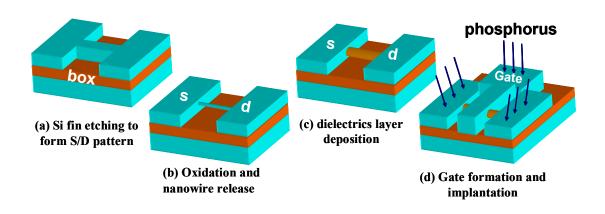

- **Fig. 5.1** The schematics of the main process steps along with the process p.85 fabrication flow for fabricating the GAA nanowire TAHOS memory cell.

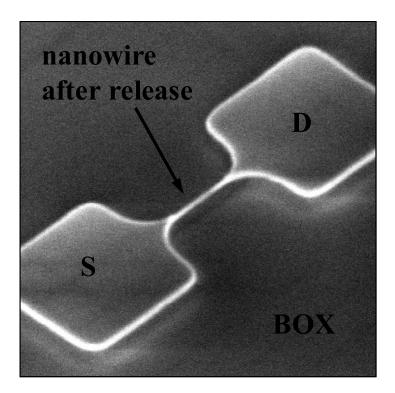

- **Fig. 5.2** A tilted SEM image of the nanowire with source and drain pads p.85 located on BOX after the nanowire was released in DHF.

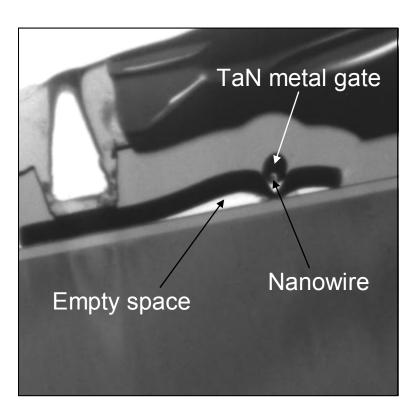

- **Fig. 5.3** TEM image showing the cross-section of fabricated GAA p.87 nanowire TAHOS device. The nanowire can be observed to be surrounded by TaN metal gate and high-κ oxide. Empty spaces are attributed to high stress formed at the interface TaN layer.

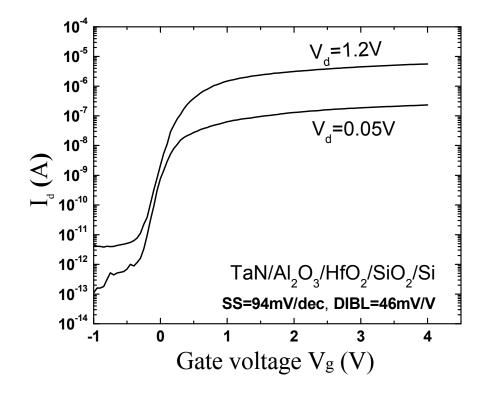

- Fig. 5.4 The  $I_d$ -V<sub>g</sub> curve measured from the nanowire TAHOS device p.88 shows good subthreshold and electrostatic property, despite a thick EOT used in memory.

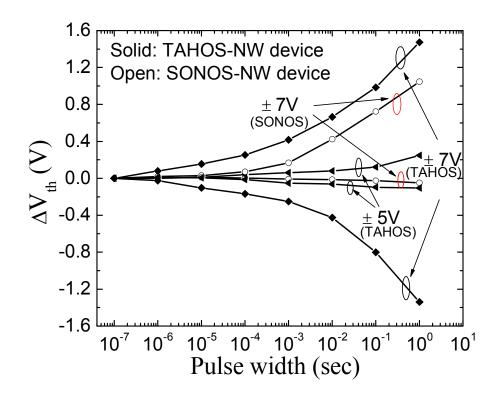

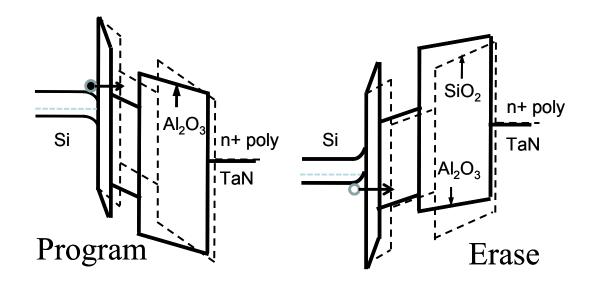

- Fig. 5.5 Transient memory characteristics of the nanowire TAHOS (NW- p.89 TAHOS) device as well as the nanowire SONOS (NW-SONOS) control device at the onset of the P/E. The TAHOS device shows equivalent program and erase speed while the SONOS device does not.

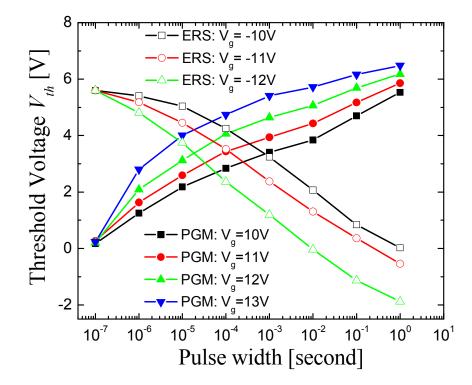

- **Fig. 5.6** Program and erase characteristics of nanowire TAHOS memory p.91 (TAHOS-NW in the figure). Large memory window and especially enhanced erase speed can be seen.

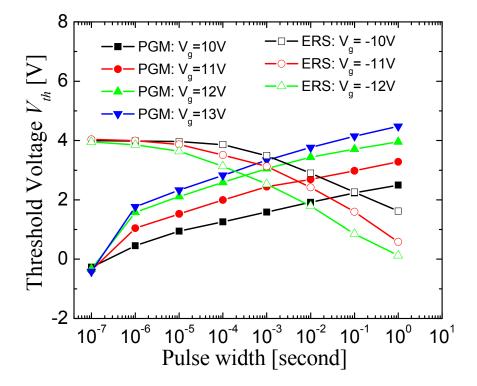

- **Fig. 5.7** Program and erase characteristics of nanowire SONOS memory p.91 device (SONOS-NW in the figure). The erasing speed is much less than the programming speed which greatly retards the cycling of SONOS.

- **Fig. 5.8** Band diagram of nanowire TAHOS (solid line) and nanowire p.93 SONOS (dash line).

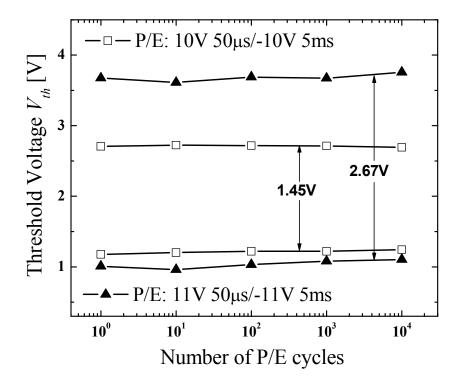

- Fig. 5.9 P/E endurance of nanowire TAHOS device at two cycling p.94 conditions. The larger memory window with 2.67 V magnitude was achieved when the device was under  $\pm 11V$  stress voltage cycling conditions with a slight upward shift.

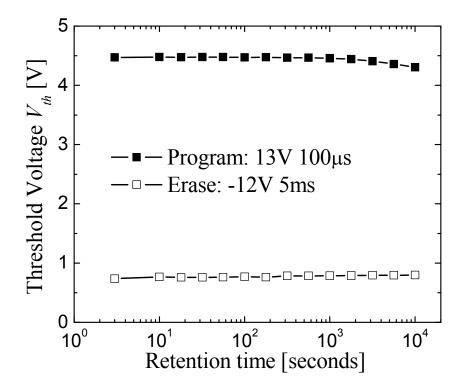

- Fig. 5.10 Room temperature data retention of the nanowire TAHOS p.95 device. The same magnitude of memory window can be achieved by a smaller P/E voltage as compared to its counterpart, despite slightly larger charge loss at the same measurement time period.

# List of Symbols

| С          | capacitance (F)                                                            |

|------------|----------------------------------------------------------------------------|

| d          | thickness                                                                  |

| $d_{nw}$   | diameter of nanowire                                                       |

| Ε          | electrical field (V/cm)                                                    |

| $E_g$      | band gap (eV)                                                              |

| $E_{inj}$  | electric field at the injecting surface                                    |

| h          | Planck's constant $(6.626 \times 10^{-34} \text{ Js})$                     |

| Ι          | current (A)                                                                |

| $I_d$      | drain current (A)                                                          |

| $I_g$      | gate leakage current (A)                                                   |

| J          | current density (A/cm2)                                                    |

| L          | channel length (µm)                                                        |

| <i>m</i> * | effective mass (kg)                                                        |

| Q          | charge (C)                                                                 |

| $Q_T$      | charges stored in the gate insulator at a distance $d_1$ from the gate (C) |

| Т          | temperature (°C)                                                           |

| t          | time (sec)                                                                 |

| $t_{ox}$   | thickness of oxide                                                         |

| V          | voltage (V)                                                                |

| $V_{cg}$   | control gate potential (V)                                                 |

| $V_d$      | drain voltage (V)                                                          |

| $V_g$      | gate voltage (V)                                                           |

| $V_{fb}$   | flatband voltage (V)                                                       |

|            |                                                                            |

- $V_{th}$  threshold voltage (V)

- $\Phi_b$  barrier height (eV)

- $\kappa_{Si3N4}$  dielectric constant of Si<sub>3</sub>N<sub>4</sub> (relative permittivity)

- $\kappa_{SiO2}$  dielectric constant of SiO<sub>2</sub> (relative permittivity)

- $\Delta E_c$  conduction band offset (eV)

- $\Delta E_v$  valence band offset (eV)

- $\Delta V_{th}$  threshold voltage shift (V)

## List of Abbreviations

BBHH Band-To-Band Tunneling Hot Hole Injection BOX **Buried** Oxide CG **Control Gate** CHE **Channel Hot Electron** CVD **Chemical Vapor Deposition** DIBL Drain-Induced-Barrier-Lowing DG Double Gate DRAM Dynamic Random Access Memory DRIE Deep Reactive Ion Etching DT **Direct Tunneling EEPROM** Electrically Erasable and Programmable Read Only Memory EOT Equivalent Oxide Thickness EPROM Electrically Programmable Read Only Memory FG Floating Gate Fowler-Nordheim F-N GAA Gate-All-Around HRTEM High Resolution Transmission Electron Microscopy IPD Interpoly Dielectric

Atomic layer Deposition

ALD

- ITRS International Technology Roadmap for Semiconductors

- LPCVD Low Pressure Chemical Vapor Deposition

- MONOS Metal/Oxide / Nitride / Oxide / Silicon

- NC Nanocrystal

- NVM Nonvolatile Memory

- PDA Post Deposition Anneal

- PECVD Plasma-Enhanced Chemical Vapor Deposition

- Poly-Si Polycrystalline Silicon

- PVD Physical Vapor Deposition

- RAM Random Access Memory

- ROM Read Only Memories

- S/D Source and Drain

- SCE Short Channel Effect

- SEM Scanning Electron Microscopy

- SIMS Secondary Ion Mass Spectroscopy

- SOI Silicon-On-Insulator

- $SONOS \qquad Si \,/\, SiO_2 \,/\, Si_3N_4 \,/\, SiO_2 \,/\, Si$

- STI Shallow Trench Isolation

- SRAM Static Random Access Memory

- SS Subthreshold Swing

- TAHOS TaN / Al<sub>2</sub>O<sub>3</sub> / HfO<sub>2</sub> / SiO<sub>2</sub> / Si

- TEOS Tetraethyl Orthosilicate

- TEM Transmission Electron Microscopy

- UTB Ultra-Thin Body

- VLS Vapor-Liquid-Solid

- VLSI Very Large-Scale Integration

# **Chapter 1**

# Introduction

## 1.1 Introduction of Semiconductor Memory Technology

### 1.1.1 Semiconductor Memory Categories

Despite some unpredictable fluctuations, the semiconductor market has been increasing steadily over the years, and the growing trend is expected to continue in the future. Memory components have been an important part of the semiconductor market and are projected to account for more than 20% of the IC market, making them the second largest category of IC's overall behind logic components [1.1], as shown in Fig. 1.1.

Fig. 1.1: Revenues of semiconductor memory market versus year.

Semiconductor memories are based on a metal-oxide-semiconductor (MOS) technology. As shown in Fig. 1.2, there are various types of semiconductor memories, which are fundamental to the architecture of computers. There are two basic categories of semiconductor memories: volatile memory, which requires power to maintain the data content; and nonvolatile memory, which is able to maintain the data content without any power supply. Most forms of random access memory (RAM) are of the volatile type. Random access means that locations in the memory can be written to or read from in any order. All data on the computer is stored on the hard drive, but in order for the Central Processing Unit (CPU) to work, the data is written into the RAM chips. There are two different types of RAM: dynamic random access memory (DRAM) and static random access memory (SRAM), which are different in the technology they use to store data.

Fig. 1.2: Semiconductor memory family tree

Being the more common type, DRAM has a simple structure: only one transistor and a capacitor are required for each bit. This enables DRAM to be packed with a high density. Since capacitors leak charge, data stored in DRAM has an extremely short storage time, typically about 100 ms. Information is stored for DRAM by refreshing the capacitor charge periodically. DRAM offers access times of about 60 ns [1.2].

A typical SRAM contains six transistors (6T) to store a memory bit. Each bit is stored on four transistors, while two additional transistors control the access during read and write operations. Unlike DRAM, SRAM does not need to be refreshed periodically. Therefore, SRAM is faster as it can give as low as 10 ns access time. Despite being faster, SRAM is not as commonly used as DRAM due to the much higher cost-per-bit. Hence, SRAM is used as a memory cache in powerful microprocessors which requires fast speed to access data frequently, while slower DRAM is used for main memory for its attractive low cost per byte.

On the other hand, nonvolatile memories are typically used as secondary storage in commercial electronic products. In the last decade, memory chips with low power consumption and low cost have attracted more and more attention due to the increasing popularity of portable electronic devices. Nonvolatile memories have become a very important category of semiconductor memory ever since the first Erasable Programmable Read Only Memory (EPROM) was invented [1.3]. Almost all electronic systems require the storage of some information in a permanent way. Thanks to the nonvolatile aspect, nonvolatile memories have enhanced the development of multimedia applications and personal consumer appliances such as digital cameras and USB Flash drives. The market share of nonvolatile memories has increased exponentially over the past few years, and is projected to grow further.

Nonvolatile memories include mask-programmed ROM and reprogrammable memories such as EPROM, Electrically Erasable and Programmable Read Only Memory (EEPROM) and flash. The mask-programmed ROM chips physically encode the data when they are manufactured at the factory with a special mask; however, they are not allowed to change the content. EPROM has a one-transistor memory cell and can provide high density and cost effectiveness, but it provides the opportunity to reprogram the device after the data are erased by exposure under strong ultraviolet light for a long time. The erasure ability of EPROM enables it to be reused and makes it an important invention in the development of semiconductor memory. EEPROM is based on a structure similar to EPROM, but it differentiates itself from EPROM by its electrical programming and erasing ability. EEPROM can write and erase each bit separately, and the data stored can be maintained for as long as required. Thus, EEPROM has the features of both RAM and ROM in that the EEPROM can be accessed per single bit like RAM, and at the same time, it can keep the contents when it loses electrical power like ROM. However, EEPROM's are manufactured for specific applications, due to the larger area and higher cost per cell.

Flexibility and cost are usually the two aspects to be compared between different nonvolatile memories [1.4]: flexibility shows the robustness of the device, while cost represents process complexity for a specific cell size. The flash memories presented by Toshiba in the 1984 [1.5] turned out to be the best compromise of the two parameters. Although flash is a specific EEPROM, flash is erased by blocks of different size while a regular EEPROM is erased bit by bit. Flash memory also costs much less than EERPOM and therefore became a dominant nonvolatile memory technology. Two main applications have opened up and driven the development of the current flash market [1.6]. The first application of flash memory is using NOR type

flash, which provides fast memory read speed and random access to any location, to store program code in cellular phones. Another application is the usage of NAND type flash as data storage medium in devices such as USB memory cards, MP3 music players and PDAs, which plays a significant role in lowering the costs of such devices. As a result, the flash market, especially the NAND type flash, had grown exponentially in the past decade. It is projected that the flash market will generate tens of billions of dollars in revenue and reach the size of DRAM market by 2010 [1.7].

#### 1.1.2 Structure and Operation Mechanism of Flash Memory

A common flash memory cell consists of one floating-gate transistor. The transistor in flash memory is similar to a standard MOSFET, except there are two gates instead of one in MOSFET. The schematic cross section of a floating gate device is shown in Fig. 1.3. The first gate is referred to as a control gate, which acts as the external gate. The second gate is a floating gate (FG) completely surrounded by dielectric layers, tunnel oxide and interpoly dielectric (IPD). Being electrically isolated, the FG is able to charge and hold carriers for the memory cell.

The basic operation principle of flash memory devices is the storage of charges in the floating gate, as illustrated in Fig. 1.3. If the charges are injected into the gate insulator layer, the threshold voltage of the device can be changed between two distinct values. From the theory of the MOS transistor, the shift of threshold voltage can be expressed by equation (1) [1.8]:

$$\Delta V_T = V_T - V_{T0} = -\frac{Q_T}{\varepsilon_I} d_I \tag{1}$$

where

$Q_T$  = the charges stored in the FG at a distance  $d_I$  from the control gate  $\varepsilon_I$  = the dielectric constant of the insulator

**Fig. 1.3**: A schematic cross-section of a single floating-gate transistor. FG is surrounded by dielectric layers and isolated from channel and IPD. Taking the n-type memory cell as an example, electrons are injected from substrate by applying a positive voltage stress at the gate. Electrons will remain trapped in the FG even after the power is removed from the gate.

The information on the device is detected by reading the drain current using a gate voltage with a value between two possible threshold voltages. Conventionally, the state with high read current and lower threshold voltage is recognized as logic "1", as the transistor is conducting a current; while the other state with low read current and higher threshold voltage corresponds to logic "0" state, since the transistor is cut off at this state.

Depending on the material of the storage medium in the transistor, the flashtype nonvolatile memory can be divided into two classes. The first class of devices contains a conducting or semiconducting layer to store the charges, which are trapped and electrically isolated by the surrounding dielectric layers; this type of devices is usually referred as a floating gate structure as shown in Fig. 1.3. In the second class of devices, the charges are stored in discrete trapping centers of a dielectric layer, such as  $Si_3N_4$  [1.9] or HfAlO [1.10]. This type of devices is usually referred to as

#### Chapter 1 Introduction

charge-trapping memories. SONOS (Silicon/Oxide/Nitride/Oxide/Silicon) memory is the most typical charge-trapping memory and it has been considered as a promising candidate to replace floating-gate memory, due to the scaling advantage of the SONOS structure compared to the floating-gate device structure.

In both classes of nonvolatile memories, the charges are stored in the trapping materials and the programming of the memory devices is realized by modifying the threshold voltage. In order to inject the charges into the trapping material through the tunnel oxide layer, there are two mechanisms commonly used nowadays: Fowler-Nordheim (F-N) tunneling mechanism, which is usually used in devices with relatively thin tunnel oxides; and channel hot electron (CHE) injection, which is employed for device with relatively thick tunnel oxides. The details of the two mechanisms are introduced below.

### 1.1.2.1 F-N Tunneling

F-N tunneling mechanism is based on the quantum mechanical tunneling mechanism induced by a high electric field; therefore it is also a field-assisted electron tunneling mechanism. When a voltage is dropped across the Si-SiO<sub>2</sub> structure, as shown in Fig. 1.4, the band structure will be influenced. The barrier height for electron tunneling is kept unchanged since it is determined by the conduction band offset between the two different materials. However, electrons in the silicon conduction band are able to tunnel through the triangular energy barrier as the barrier width has been greatly reduced. The probability of the tunneling through the oxide layer is dependent on the magnitude of the applied electric field.

Fig. 1.4: Si and SiO<sub>2</sub> energy band diagram system (a) without applying any voltage and (b) with applying a positive voltage at SiO<sub>2</sub> side. Electrons are able to tunnel through the thick SiO<sub>2</sub> layer by F-N tunneling due to a strong electric field reduces the barrier width. Conduction and valence band offset ( $\Delta E_c$ and  $\Delta E_v$ ) keeps unchanged during the process.

In Fig. 1.4,  $\Delta E_c$  indicates the Si-SiO<sub>2</sub> energy barrier height (3.25 eV for electrons and 4.7 eV for the holes). The applied voltage at the control gate induces the electric field at the injecting surface (E<sub>cg</sub>), resulting in a potential barrier with a width dependent on the applied voltage. The electrons collected at the floating gate leads to a tunneling current density which is given by equation (2) [1.11]:

$$J = \alpha E_{cg}^2 \exp\left(-\frac{\beta}{E_{cg}}\right)$$

(2)

with

$$\alpha = \frac{q^3}{8\pi h\Delta E_c} \frac{m}{m^*}, \ \beta = 4\sqrt{2m^*} \frac{\Delta E_c^{\frac{3}{2}}}{3hq}$$

### 1.1.2.2 CHE Tunneling

Nonvolatile memory can also be programmed by hot-carrier injection

mechanism [1.12]. The hot electron injection is for n-type NVM on a p-substrate. Hot carriers generally refer to the particles which attain the kinetic energy from a high electric field. The hot-electrons get their energy from the drain voltage, and are further accelerated by the lateral electric field along the channel. Once they obtain sufficient energy, these hot electrons will surmount the SiO<sub>2</sub>/Si barrier and tunnel into the floating gate to program the cell. Potential at the control gate V<sub>cg</sub> affects the charges tunneling into the floating gate while the potential at the drain V<sub>d</sub> plays a role in determining the speed of programming. Fig. 1.5 (a) shows a cross section of a NVM with hot electron injection programming. The change of band structure during the hot electron programming process is shown in Fig. 1.5 (b).

Fig. 1.5: (a) At CHE stress condition, electrons gain enough energy while drifting across the channel and are injected through the tunnel oxide, causing a gate current. (b) Energy band diagram of a floating-gate memory cell during programming by hot-carrier injection.

### 1.1.3 Challenges of Semiconductor Flash Memory Scaling

The tunneling mechanisms are commonly known to be closely related to the architectures of flash memory circuits. NOR flash and NAND flash are the two main

#### Chapter 1 Introduction

categories which dominate the nonvolatile memory market today. In the internal circuit configuration of NOR as shown in Fig. 1.6, the individual floating-gate n-type transistors share a bit line, while the sources are connected together by sharing a source line on the other side. Programming of NOR flash is usually done by CHE tunneling in 10 µs, and erasing is conducted by F-N tunneling with a relatively longer time (~0.5 s) [1.6]. The array of NAND flash allows a much smaller configuration size, as a string of 16 or 32 cells are connected between a common bit line and source line. Its simpler design translates to a small cell size and low cost-per-bit. Moreover, the cell is programmed and erased by F-N tunneling as a block, enabling fast memory erase speed. Despite its complicated design, NOR flash architecture allows for fast random read access, which is required for code execution. In contrast, NAND is more suitable for high capacity data storage applications.

**Fig. 1.6**: Comparison of NOR and NAND flash architectures (a) NOR-type with shared bit line and source line. (b) NAND-type with a common bit line and a common source line, showing concise structure advantage.

Nonvolatile memory technology is going through a fast evolution amongst the semiconductor technologies in the last decade. The development of NAND-type flash memory technology has led to higher density memory designs and Giga-bits commercial products are also available now [1.13]. In the current NAND technology trend, 60-nm node has been completed in the R& D process [1.14]. However, the vast majority of flash memory devices will face significant challenges when the technology further scales down NAND-type flash memory to the 40-nm node [1.15].

It is important to scale the electrical oxide thickness (EOT) of the gate stack to achieve a small memory cell density and to reduce utilization power. A common issue when scaling the gate stack is the non-scalability of the tunnel oxide thickness. Tunnel oxide needs to be scaled to enable channel length scaling. There is always a tradeoff between the memory transient performance and the charge retention characteristics. A thin tunnel oxide is desirable to achieve increased memory speed. However, if the tunnel oxide is reduced to too much, it will degrade the memory nonvolatile properties to a large extent, since electrons stored in the floating gate are prone to tunnel out through the Frenkel-Poole mechanism when there is a defect in the tunnel oxide [1.16]. Moreover, due to the conductive poly-Si floating gate, a single leakage path resulting from endurance cycles would lead to loss of all stored charges. In order to maintain data retention for 10 years at an elevated temperature after 10<sup>5</sup>-10<sup>6</sup> endurance cycling without program/read disturbance, the lower limit of tunnel oxide thickness must be greater than 7~8-nm for floating-gate devices due to stress induced low field tunneling.

One key issue is maintaining adequate coupling of the control gate to the floating gate. The control gate controls the channel indirectly. The control degree is indicated by the gate coupling ratio which is achieved by  $C_{(control gate to floating gate})$

#### Chapter 1 Introduction

$_{capacitance}/C_{(total floating gate capacitance)}$ . The gate coupling ratio should be larger than 0.6. In the flash memory circuit, the control gate wraps around the FG to increase the CG to FG capacitance, and the thickness of IPD layer is approximately 20-nm. The reduced coupling ratio results in the increased programming and erasing voltage to maintain memory speed, which degrades the memory reliability. As the scale down proceeds, the space between neighboring FG becomes too narrow to be filled with two IPD layers and control gate poly-Si, as shown in Fig. 1.7. Therefore, at below 40-nm node, it is difficult to maintain the gate coupling ratio at a value of larger than 0.6.

During the rapid reduction of the memory array density, the poly-Si word lines would be patterned very closely to each other. Thus, the poly-Si word line would suffer serious capacitance interference from the adjacent word lines as illustrated in Fig. 1.7 (b), especially when the word line is very long. The cross coupling effect resulting from the capacitance interference can sometimes cause erroneous programming [1.17].

**Fig. 1.7**: Schematic cross section of a floating-gate cell in a (a) word line direction and (b) bit line direction. (a) Space between neighboring FG becomes too narrow to be filled with two IPD layers and control gate poly-Si. (b) V<sub>th</sub> of an unselected cell can be programmed mistakenly due to the capacitance interference of the adjacent charge.

Based on the previous discussion, it is understandable why the nonvolatile memory research community is seeking innovative technologies to replace the current floating-gate flash memory. One of the main challenges is that planar floating gate memory device scaling is approaching the physical limits. A large amount of research work is being conducted on replacing the floating-gate flash with alternatives, such as FeRAM (Ferro-electric RAM), MRAM (Magnetic RAM) and phase change memory. It turns out that the discrete charge trapping type flash memory is the more suitable choice for nonvolatile memory applications compared to other candidates. Discrete charge trapping type flash memories have a similar device structure as the floatinggate flash, while the other candidates consume a larger area. A FeRAM cell consists of one transistor and one capacitor [1.18], while a MRAM is composed of a magnetic tunnel junction [1.19]. The continued scaling of stack capacitor is quite challenging for a FeRAM, and both FeRAM and MRAM have the drawback of sensitivity to IC processing temperatures and conditions [1.2]. Although phase change memory is considered a promising technology, the biggest challenge is the cost disadvantage and the contact between the hot phase-change region and the adjacent dielectric. [1.20].

On the other hand, the discrete charge trapping type flash memory cell such as SONOS, MONOS (Metal/AlO/SiN/Oxide/Si) [1.21] and nanocrystal memory [1.22] can achieve the highest chip density. It has been widely investigated recently to use charge trapping materials such as silicon nitride, high permittivity (high- $\kappa$ ) dielectric and nanocrystals to replace the conductive poly-Si floating gate. The discrete charge trapping nonvolatile memory has inherent advantages over traditional floating-gate devices, such as natural immunity to capacitance interference, simple process, lower applied voltage and robust tolerance to dielectric defects. In a floating-gate device, all

stored charges would be able to leak through a single defect chain in the thin tunnel oxide. The requirements for advanced technology nodes in NAND flash memory in the near term are summarized in Table 1.1, according to International Technology Roadmap of Semiconductors (ITRS) 2007 Edition [1.2]. As illustrated in the table, SONOS-type flash memory has an advantage in device density scaling.

| Year of Production                    | 2009  | 2010  | 2011  | 2012    |

|---------------------------------------|-------|-------|-------|---------|

| A. Floating gate NAND Flash           |       |       |       |         |

| Tunnel oxide thickness (nm)           | 6-7   | 6-7   | 6-7   | 6-7     |

| Interpoly dielectric material         | ONO   | ONO   | ONO   | High- κ |

| Interpoly dielectric thickness        | 10-13 | 10-13 | 10-13 | 9-10    |

| Highest P/E voltage (V)               | 15-17 | 15-17 | 15-17 | 15-17   |

| B. Charge trapping NAND Flash (MANOS) |       |       |       |         |

| Tunnel oxide thickness (nm)           | 3-4   | 3-4   | 3-4   | 3-4     |

| Blocking oxide thickness (nm)         | 6-8   | 6-8   | 6-8   | 6-8     |

| Trapping layer thickness(nm)          | 5-7   | 5-7   | 5-7   | 5-7     |

| Highest P/E voltage (V)               | 15-17 | 15-17 | 15-17 | 15-17   |

Table 1.1: Flash Nonvolatile memory technology requirements

However, the planar oxide-nitride-oxide (ONO) gate stack thickness is not easily scalable in the long term due to the data retention concerns. With a typical equivalent oxide thickness (EOT) of more than 10nm used in the device, it is easier to suffer the problems induced by severe short channel effects (SCE) in memory devices as compared to CMOS logic devices. The low on-off ratio and unwanted large subthreshold swing (SS) could also potentially trigger the reading error of a memory cell [1.23].

#### **1.2 Scope of Project**

From the view point of device structure, multi-gate device structures, that is, double-gate, trigate,  $\Pi$ -gate,  $\Omega$ -gate and gate-all-around, have been explored extensively as planar device scaling approaches the end of the technology roadmap. The ultra thin body SOI field effect transistor structure and the multi-gate fully depleted FinFET structure have been proposed to suppress SCE for sub-100-nm CMOS technologies. The thin layer of silicon channel on SOI wafer can eliminate subsurface punch-through observed in bulk-Si devices, while the multi-gate structure features a narrow channel body which controls the channel potential better than the single gate structure. It reflects better SCE suppression effect by lower SS, DIBL and reduced V<sub>th</sub> roll-off in device performance. Among the many types of multi-gate structure, devices with a nanowire channel are being widely investigated for their potential to advance the CMOS and nonvolatile memory technologies to extreme scaling limits.

In this dissertation, new methodologies which enable further scaling of nonvolatile memory devices will be evaluated. Due to the scaling advantage of discrete charge trapping type memory devices based on the aforementioned discussion, this study will focus on one type of discrete charge trapping memory devices, SONOS-type memory device, which is built on non-traditional device architecture. Considering the industrial compatibility, the top-down nanowire channel structure is fabricated and investigated by using CMOS technology. The novel nanowire device can potentially be a strategy to be exploited for the next technology node.

### **1.3 Organization of Thesis**

This thesis addresses the issues of gate stack scaling and voltage scaling for future semiconductor nonvolatile memory device and discusses solutions to scale the discrete trapped charge-storage nonvolatile memory by using the advanced nanowire structure. The whole thesis consists of six chapters which have been arranged as follows.

Chapter 1 provides an introductory overview of the semiconductor nonvolatile memory technology and discusses the advantages of SONOS-type based discrete charge trapping nonvolatile memory. It also presents the current critical challenges existing in the memory device scaling progress.

Chapter 2 gives a detailed literature study on key findings in the earlier research work on SONOS-type memory, including the advantages and disadvantages considering its employment in next generation commercial memory products. Memory devices with different types of state-of-the-art non-traditional structures are also reviewed.

In chapter 3, we focus on the fabrication process of gate-all-around (GAA) Sinanowire which is being integrated for the nonvolatile SONOS memory application. The introduced GAA structure, controlling the conducting channel from all directions, may provide the device much better gate controllability and hence influence the memory characteristics. The performance of high-speed SONOS device and the reason for enhancement will be examined in detail.

In Chapter 4, we introduce the nanowire structure into the poly-Si TFT memory as a promising candidate to be integrated in system-on-panel or system-on-chip applications. The GAA structure has an advantage of small channel cross section,

which may reduce the negative effect brought about by poly-Si grains and the boundaries between them. The performances will be presented and the causes for the performance improvement will also be discussed.

In Chapter 5, by integrating high- $\kappa$  dielectric materials and metal gate electrode, a strategy of optimizing nanowire SONOS-type memory characteristics is illustrated. The application of high- $\kappa$  materials and high work function metal gate electrode is used to replace the conventional materials, and have the potential to solve the limits existing in nitride-based SONOS devices. The performance enhancement in the new device will be investigated.

Last but not least, an overall conclusion is given in Chapter 6 to summarize the major results. Possible future work is also proposed in this chapter too.

## Reference

- [1.1] P. Cappelletti, in *IEDM Tech. Dig.*, 2004 Short Course: Memory devices.

- [1.2] International Technology Roadmap of Semiconductors (ITRS), Semiconductor Industry Association, Banjoes, CA, 2007.

- [1.4] R. Bez, E. Camerlenghi, A. Modelli, and A. Visconti, in *Proceedings of the IEEE*, vol. 91, no. 4, April, 2003.

- [1.5] F. Masuoka, M. Asano, H. Ivahashi, T. Komuro, S. Tanaka, "A new flash E<sup>2</sup>PROM cell using triple polysilicon technology", in *IEDM Tech. Dig.*, pp. 464-467, 1984.

- [1.6] Jan Van. Houdt, "Flash memory: a challenged memory technology", in *IEEE International Conference on Integrated Circ. Design and Tech.*, pp. 1-4, 2006.

- [1.7] Alan Niebel, "Business outlook for the non-volatile memory Market", in *IEEE Non-Volatile Semiconductor Memory Workshop*, pp. 6-7, 2006.

- [1.8] William D. Brown, Joe E. Brewer, "Nonvolatile semiconductor memory technology: A comprehensive guide to understanding and using NVSM devices" *Wiley-IEEE Press*, pp. 5, October 1997.

- [1.9] M. H. White, Y. L. Yang, A. Purwar, and M. L. French, "A low voltage SONOS nonvolatile semiconductor memory technology", in *IEEE Trans. on Components, Packing, and Manufacturing Tech.*, vol. 20, no. 2, pp. 190-195, 1997.

- [1.10] Yan Ny Tan, Wai Kin Chim, Wee Kiong Choi, Moon Sig Joo, Tsu Hau Ng, and Byung Jin Cho, "High-k HfAlO charge trapping layer in SONOS-type nonvolatile memory device for high speed operation", in *IEDM Tech. Dig.*, pp. 889-892, 2004.

- [1.11] M. Lenzlinger, and E. H. Snow, "Fowler-Nordheim tunneling in thermally grown SiO<sub>2</sub>", in *J. Appl. Phys.*, vol. 40, pp. 278-283, 1969.

- [1.12] Daniel C. Guterman, Isam H. Rimawi, Te-Long. Chiu, Richard D. Halvorson, and David J. McElroy, "An electrically alterable nonvolatile memory cell using a floating gate structure," *IEEE Tran. Electron Devices*, vol. 26, no. 4, p. 576-586, 1979.

- [1.13] K. Kim, J. H. Choi, J. Choi, H.-S. Jeong, "The future prospect of nonvolatile memory", in *IEEE VLSI-TSA-TECH*, *Proceedings of Technical Papers*, pp. 88-94, 2005.

- [1.14] J. H. Park, S. H. Hur, J. H. Lee, J. T. Park, J. S. Sel, J. W. Kim, S. B. Song, J. Y. Lee, J. H. Lee, S. J. Son, Y. S. Kim, M. C. Park, S. J. Chai, J. D. Choi, U. I. Chung, J. T. Moon, K. T. Kim, K. Kim, and B. I. Rye, "8Gb MLC (Multi-Level Cell) NAND flash memory using 63nm process technology", in *IEDM Tech. Dig.*, pp. 873-876, 2004.

- [1.15] C. Y. Lu, K. Y. Hsieh, R. Liu, "Future challenges of flash memory technologies", in *Microelectronics Eng.*, pp. 283-286, 2009.

- [1.16] C. S. Pan, K. Wu, D. Chin, G. Sery, J. Kiely, "High-temperature charge loss mechanism in a floating-gate EPROM with an oxide-nitride-oxide (ONO) interpoly stacked dielectric", in *IEEE Electron Device Lett.*, vol. 12, no. 9, pp. 506-509, 1991.

- [1.17] She Min, "Semiconductor flash memroy scaling", PhD dissertation, 2003.

- [1.18] R. E. Jones, Jr., P. D. Maniar, R. Moazzami, P. Zurcher, J. Z. Witowski, Y. T. Lii, P. Chu, and S. J. Gillespie, "Ferroelectric non-volatile memories for low-voltage, low-power applications", in *Thin Solid Films*, vol. 270, no. 1-2, pp. 584-588, 1995.

- [1.19] S. Tehrani, J. M. Slaughter, E. Chen, M. Durlam, J. Shi, M. Deherren, "Progress and outlook for MRAM technology", in *IEEE Trans. on Magnetics*, vol. 35, no. 5, pp. 2814-2819, 1999.

- [1.20] Http://en.wikipedia.org/wiki/Phase-change\_memory.

- [1.21] C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park, and K. Kim, "A novel SONOS structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for multi-giga bit flash memories", in *IEDM Tech. Dig.*, pp. 613-616, 2003.

- S. K. Samanta, P. K. Singh, Won Jong Yoo, Ganesh Samudra, Yee-Chia Yeo, L.

K. Bera, and N. Balasubramanian, "Enhancement of memory window in short channel nonvolatile meomry devices using double layer tungsten nanocrystals", in *IEDM Tech. Dig.*, pp. 170-173, 2005.

- [1.23] M. H. White, D. A. Adams, and J. Bu, "On the go with SONOS", IEEE Circuits and Devices, Vol.16, pp. 22-31, 2000.

# **Chapter 2**

## **Literature Review**

#### **2.1 Introduction**

Applications for nonvolatile memory have experienced exponential growth in recent years due to the need for low power solid-state storage and rapidly declining prices of nonvolatile memories. Conventional floating-gate flash faces significant challenges below 45-nm node. Charge trapping devices are proposed to continue the scaling of nonvolatile memories, and innovative gate stack engineering or threedimensional structure integrated on charge trapping device may provide the ultimate solution.

#### 2.2 Gate Stack Engineering

#### **2.2.1 Nanocrystal Memory**

Nanocrystal based charge trapping memory has shown scaling advantages over nitride based charge trapping memory, despite the fact that nanocrystal memory is relatively new and that nitride memory has been studied for quite a long time [2.1]. The ordering of the trap sites can be controlled in nanocrystal memory, while the ordering of trap sites is randomly distributed in nitride memory. Nanocrystal memory is also capable of multi-bit storage application by using Coulomb blockade. A significant amount of research work has been done on nanocrystal based flash memory structures using semiconductor nanocrystals like Si and Ge. Several Si nanocrystal fabrication processes have been proposed, the most common of which are the ion implantation method and the direct growth method. Nanocrystal features, such as size, size distribution, lateral isolation and uniformity, generally require good process control in the fabrication process [2.2]. The ion implantation method uses an implantation step to implant excess silicon through the poly-silicon gate of the memory transistor and into the gate oxide layer; it will then be followed by a thermal anneal step to precipitate the Si atoms to form distinct Si nanocrystal dots [2.3]. In the direct growth method, low pressure chemical vapor deposition (LPCVD) is used to deposit small amounts of poly-Si on top of the tunnel oxide surface [2.4]. The deposition process is stopped before a continuous layer is formed, resulting in hemispherical Si islands on the tunnel oxide. A further thermal oxidation step can be added to enhance the lateral isolation between the nanocrystals [2.5]. The direct growth method is a more promising technique in terms of process compatibility. Compared with Si, Ge has a narrower bandgap and a similar electron affinity [2.6]. It has been reported that the Ge nanocrystal was integrated into flash memory devices by thermal oxidation techniques such as  $Si_{1-x}Ge_x$  [2.7], co-sputtering and annealing [2.8]. Metal nanocrystals have also been proposed [2.9], aiming to engineer the potential well depth of the storage nodes and achieve longer data retention.

Nanocrystal memories have demonstrated robust memory behaviors. Threshold voltage ( $V_{th}$ ) windows were increased from only several hundreds of millivolts in the pioneering works [2.10], to a 6V memory window as demonstrated by Singh *et al.* in Au nanocrystal devices [2.11]. Excellent memory endurance behavior on nanocrystal memories was also observed, displaying only limited  $V_{th}$  window closure after more than 10<sup>5</sup> write/erase cycles [2.12]. Retention data that have been measured also suggest better retention behavior in nanocrystal memory than floatinggate memory devices [2.12] [2.13]. However, as statistical information has yet to demonstrate that nanocrystal memory meets the requirements for nonvolatile memory, the claims that nanocrystal memory is nonvolatile remains unverified.

#### 2.2.2 Bandgap Engineering Memory

An ideal nonvolatile memory device should possess long data retention as well as fast operation speed. However, there is a tradeoff between these two characteristics: the adoption of a thin tunnel oxide to achieve high memory speed would sacrifice the data retention time, while growing a thick tunnel oxide to ensure long data retention time will significantly reduce the memory speed. The reduction is specially obvious for the erase speed, as the hole experiences a higher barrier height at Si/SiO<sub>2</sub> interface than the electron does. BE-SONOS (Bandgap Engineered SONOS) with bandgap engineering of the tunnel oxide shows the potential to maximally suppress the tradeoff and improve both characteristics [2.14]. In the bandgap engineering, the traditional SiO<sub>2</sub> tunnel oxide is replaced by a triple layer of SiO<sub>2</sub>/SiN/SiO<sub>2</sub> (ONO), since ONO demonstrates non-trapping ability with an ultra-thin thickness. As shown in Fig. 2.1, due to the lower hole-tunneling barrier in SiN (~1.9 eV) as compared to SiO<sub>2</sub> (~4.5 eV), a large electron or hole tunneling current could tunnel through the ultra-thin ONO tunneling layer under a high electric field. On the other hand, in the case of data retention, hole direct tunneling is blocked by the total thickness of the ONO barrier under a low electric field. Another bandgap engineering example, as demonstrated by Y. Q. Wang *et al.* in 2006, shows that a simple Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> double tunneling layer for MONOS type memory [2.15] based on the concept of layered tunnel barrier [2.16] is beneficial for enhancing hole tunneling efficiency.

**Fig. 2.1**: The band diagram of BE-SONOS under different electric fields, showing only the tunnel oxide part. (a) At retention mode, direct tunneling is prohibited since the barrier width carriers experience is the whole physical thickness of ONO layer. (b) At program/erase mode or under high electric field, carriers could only see the thickness of a thin layer of oxide; hence the speed can be significantly enhanced due to reduced barrier width.

#### 2.2.3 High-к-based MONOS Memory

SONOS devices have received increasing interest due to their better endurance, smaller chip size and lower power consumption than floating-gate devices. However, charge retention and erase speed remain major challenges for SONOS to overcome in order to enter into the commercial mass storage flash memory market. Since the erase speed for SONOS type memory is determined by the competition between the direct tunneling current of holes through the tunnel oxide and the unwanted F-N tunneling current of electrons through the blocking oxide, the tunnel oxide thickness must be very thin in order to establish a stable erase operation. The charge loss through a very thin tunnel oxide is also a significant challenge to overcome in order to secure data storage. Therefore, aggressive scaling of CMOS logic and mass storage devices has triggered the investigation on high permittivity dielectric materials (high- $\kappa$ ) as an alternative to SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>.

Si sub tunnel Ox. SiN Blocking Ox. Gate Si sub tunnel Ox. SiN Blocking Ox. Gate

(a)

(b)

**Fig. 2.2**: Schematic band diagram for the memory device using nitride (dashed line) and high- $\kappa$  (solid line) as blocking layer under electric field at the progam mode (a) and erase mode (b). The electric field across the blocking oxide is decreased and transferred to tunnel oxide, hence the carriers tunneling efficiency is improved compared with ONO device.

In a conventional SONOS device, the electric field in blocking oxide (SiO<sub>2</sub>) is generally about two times larger than in Si<sub>3</sub>N<sub>4</sub> for devices with comparable thickness of nitride and top oxide, due to the lower permittivity of SiO<sub>2</sub> ( $\kappa_{SiO^2} \sim 3.9$ ) as compared to Si<sub>3</sub>N<sub>4</sub> ( $\kappa_{Si3N_4} \sim 7.5$ ). A substantial part of applied voltage would drop across the top oxide and cause the unwanted electron back tunneling. By replacing SiO<sub>2</sub> with high- $\kappa$  dielectric as the blocking oxide, the electric field across the blocking oxide would be reduced, while the electric field across the tunnel oxide would be proportionally increased, as shown in Fig. 2.2 [2.17]. A thicker tunnel oxide can thus reduce the program and erase voltage for SONOS devices without losing any operation speed. The simulation results given by Gritsenko *et al.* shows that by using Al<sub>2</sub>O<sub>3</sub> or ZrO<sub>2</sub> as the top dielectric, the programming voltage amplitude decreases or the programming time reduces from 1 ms to 10  $\mu$ s [2.18]. C. H. Lee *et al.* developed a TANOS device with the structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub>/TaN and the memory cell demonstrated efficient erase with a thick tunnel oxide [2.19]. It also demonstrated that the TaN metal gate blocks the gate electron current more effectively than the poly-Si gate, resulting in a significant decrease of the saturation level of V<sub>th</sub> at the erasing state. The data retention of the TANOS device was investigated by J. S. Lee *et al.* and was found to be excellent [2.20]. With an original memory window of 6 V, such a device is expected to take more than 40 years to have less than 0.5 V charge loss at 85°C. A 4Gb TAHOS NAND flash memory has been successfully developed with the 63-nm design rule [2.21]. There are also remarkable research works on SOHOS structure devices with high- $\kappa$  material as the charge storage layer. SOHOS structure memory device, due to the difference in band offset and the degree of crystallization of the high- $\kappa$  material [2.22].

#### **2.3 Novel Structure Nonvolatile Memory Devices**

The scaling of planar bulk devices is facing significant challenges due to limited electrostatic control of the channel potential and leading to SCEs: 1) V<sub>th</sub> rolloff, large DIBL and poor subthreshold slope; 2) increased gate and junction leakage; and 3) increased source/drain resistance. N. Collaert *et al.* predicted that planar devices will not make any further scaling after the 32-nm node [2.23]. The research community is pursuing new routes for further scaling. One route is by employing new materials discussed previously – 45-nm CMOS with high- $\kappa$  and metal gate electrode has been put into production by Intel in 2007 [2.24]. The other route is by adopting a new device structure, with the objective of improving electrostatics of a single MOSFET or memory cell, and accommodating the integration needs of new materials. Fully depleted ultra-thin body (UTB) silicon-on-insulator (SOI) MOS device structure consisting of a very thin ( $t_{si} \le 10$ -nm) has drawn much interest a decade ago. K. Ishii *et al.* presented suppressed SCE on a 40-nm gate length thin channel (11-nm) MOSFET [2.25]. M. K. Kim *et al.* demonstrated good memory behavior as well as excellent SCE immunity on a minimum 30-nm gate length SONOS charge trapping memory [2.26]. The ratio of the channel length to the channel thickness typically requires  $\ge 3$  to maintain full substrate depletion under gate control [2.27], which means a Si channel as thin as 4-nm is required to scale device to the 22-nm node. However, at a gate length of 25-nm, the thickness-induced V<sub>th</sub> variation will start to happen when the body thickness reduced to 7-nm [2.28]. Too much thin channel body also raises issues of mobility degradation and high source and drain resistance in logic devices.

A variety of multiple-gate nontraditional structures have been proposed in recent years. The increased number of gates provides improved electrostatic control to the channel, which alleviates the stringent requirement of body thickness scaling in UTB SOI structure, and the multi-gate device structure can be used in conjunction with UTB SOI to further improve the gate control of the channel. Fig. 2.3 shows the evolution of the multi-gate structure schematically. Double gate (DG) SOI devices have two symmetrical gates electrically interconnected, and can be achieved with many techniques such as the fin process [2.29], tunnel epitaxy [2.30], etc. Numerical simulation results suggest that the DG SONOS device can be scaled down to 50-nm, and in addition to the improved scalability of the memory cell, the two conducting channels provide a 2-bit per cell storage [2.31]. Tri-gate structures [2.32], such as the II-gate [2.33] and omega-gate structures [2.34], feature similar processing technique like the bulk-Si. The multiple gates control the fin on three geometric sides,

suggesting that excellent short-channel device performance can be achieved. Xuan *et al.* demonstrated the first SONOS device with three conducting channel surfaces, and the SONOS can be scaled down to 40-nm gate length with good subthreshold properties [2.35]. A window of 2 V is achieved with a 5 ms/10V program pulse and a 10 ms/-11V erase pulse in such a device. M. Specht *et al.* demonstrated a tri-gate SONOS memory cell which features a 20-nm gate length and a sub 10-nm fin width [2.36]. Such a device could be operated at high speed and in multi-level mode despite the thick tunnel oxide it contains.

Fig. 2.3: Progression of device structure from a single-gated planer on SOI to a fully GAA nanowire channel, with the number of gates increasing. (a) Single-gate structure. (b) Double gate structure, with a tall fin and two symmetrical gates electrically interconnected. (c) Tri-gate or FinFET structure, where gate electrode controls the channel on three surfaces. (d) Gate-all-around structure with a nanowire channel.

The gate-all-around (GAA) structure is the most promising among all emerging device structures for the ultimate device scaling. As the name suggests, the GAA structure possesses a gate which is fully surrounds the channel body and thus provides the best electrostatic control [2.37]. The reduction in channel width and thickness further increases the effectiveness of the gate control. As the simulation indicates, the gate length can be scaled to 5-nm with the scaling of the channel to nanowire [2.38]. Therefore, the GAA structure, combined with the ultra-narrow body or nanowire body, shows the most promise as a candidate for extreme device scaling.

#### 2.4 Si Nanowire Technology

#### 2.4.1 Bottom-up Approach

One dimensional semiconductor materials, such as nanotubes and nanowires, offer the possibility of ballistic transport since scattering is much suppressed [2.39]. There is an increasing interest in the synthesis and assembly of nanomaterials which may serve as the building blocks for the next generation of electronic and optical devices. Most of the reported works use the bottom-up approach to grow nanowires, and gold is the most popular catalyst for synthesizing Si nanowires via the vapor-liquid-solid (VLS) mechanism, which was first reported and studied in detail by Wagner *et al.* [2.40]. In the VLS mechanism, Si nanowire can be synthesized by coating a Si substrate with a thin gold film and annealing the substrate to obtain Au-Si catalyst particles. When a vapor phase Si precursor is introduced at a substrate temperature, which is the Au-Si mixture melting temperature, the catalyst particles become supersaturated with Si. Crystalline Si nanowires will then nucleate and grow. Since the Au-Si catalyst particle located at the tip of the nanowire is in a liquid state during growth, the method was named the VLS method. The liquid particle serves as

a preferential site for absorption of Si from the vapor phase precursor.

However, the catalyst metal gold could trap electrons and holes in Si, which pose a serious contamination problem for CMOS technology. Although there are some reports on the use of other metal catalysts for Si nanowire growth, such as Pt, Fe, and Ga, either the growth temperatures are too high, or the metals are not compatible in modern semiconductor manufacturing processes. The control of diameter and length thus is critical in the nanowire growth process as the electrical and optical properties of Si nanowires are strongly dependent on their size. The "bottom up" synthesized nanowires typically show poor control of size and dimension, and the positions of the nanowires are hard to predict as the nanowires are usually distributed on the wafer surface arbitrarily [2.41]. More complicated processes are hence required for further device fabrication on such nanowires. Other bottom-up techniques reported for nanowire preparation include laser ablation [2.42], liquid suspension, fluid flow, etc. All these techniques have an issue with the control of repeatability and scalability. In addition, these techniques have very low throughput that do not result in significant economic advantages.

#### 2.4.2 Top-down Approach

The bottom-up approach creates integration issues that have hindered the widespread application of Si nanowires. On the other hand, the top-down approach could provide better control by using precise lithography and etching processes. The top-down approach is CMOS compatible; hence nanowires fabricated using the top-down process could be more easily embedded into circuits and other micro-systems. A top-down Si nanowire field effect transistor with channel width down to 20-nm has been fabricated using electron-beam lithography on SOI wafer [2.43]. The results show that the carrier mobility of the nanowire device is 1.3 to 2.2 times higher than

that of the reference device with larger dimension, which could be attributed to the possible suppression of inter-valley phonon scattering. S. D. Suk *et al.* has demonstrated a twin Si nanowire transistor on bulk wafer using a complicated self-aligned damascene-gate process [2.44], with the damascene-gate process schematics shown in Fig. 2.4. No roll-off of V<sub>th</sub>, small SS and Drain Induced Barrier Lowering (DIBL) can be observed down to 30-nm gate length for both n- and p-type MOSFETs with a 10-nm diameter. GAA Si nanowire SONOS nonvolatile memory has been developed by the same research group using the same process technique [2.45]. By using the CHE and hot hole injection mechanisms for program and erase, program speed of 1 µs at V<sub>d</sub>=2 V, V<sub>g</sub>=6 V and erase speed of 1 ms at V<sub>d</sub>=4.5 V, V<sub>g</sub>=-6 V could be achieved with a 2~3-nm nanowire and a 30-nm gate.

Fig. 2.4: Progress flow of the damascene-gate nanowire device fabrication used by Samsung's group (1) SiGe / Si growth and shallow trench isolation (STI) (2) hard mask SiN trimming (3) oxide fill in STI and CMP (4) damascene gate stack deposition (5-6) 1st and 2nd damascene gate etch (7) field oxide recess (8) SiGe removal and H<sub>2</sub> anneal and (9) gate oxide and gate material deposition.

Nanowire MOSFET and nonvolatile memory devices with GAA device structure are able to achieve excellent performance in a scaled size and be fabricated for a mass production purpose due to the modern process technology used. However, the complicated damascene-gate technique that Samsung used to fabricate nanowires is difficult to adopt in the industrial environment. Hence, it is necessary to find a new technique to realize the potential of nanowires.

Previously, some research work reported that thermal oxidation of small silicon wires shows a self-limiting effect due to high stresses [4.46]. Sub-10-nm diameter vertical Si nanowire column was reported using a combination of electron beam lithography, reactive ion etching and self-limiting thermal oxidation. Below a critical temperature of 950°C, thermal oxidation proceeds for a while, but then a selflimiting effect starts, in which after a few hours of oxidation the Si reduction and the oxide growth become extremely slow compared to the planar oxide growth rate. Moreover, they appear to saturate to different asymptotic values depending on the starting Si volume. The time to achieve the saturation decreases with increasing temperature. The limiting core (nanowire) diameter depends on the outside oxide shell thickness, and the temperature dependence of limiting core diameters becomes weaker at higher temperature [4.47]. Liu et al. postulated that this self-limiting phenomenon is due to the increasing activation energy of oxidant diffusivity in a highly stressed oxide, as newly formed SiO<sub>2</sub> has to expand more to accommodate a given increase in volume for Si-O reactions. The smaller the core, the greater the oxide layer has to expand, which causes a greater stress and retards the process of further oxidation.

## Reference

- [2.1] M. H. White, D. A. Adams, and J. Bu, "On the go with SONOS", in *IEEE Circuits and Devices*, Vol.16, pp. 22-31, 2000.

- [2.2] Jan De Blauwe, "Nanocrystal nonvolatile memory devices", in *IEEE Trans. on Nanotechnology*, vol. 1, pp. 72-77, 2002.

- [2.3] P. Dimitrakis, E. Kapetanakis, D. Tsoukalas, D. Slarlatos, C. Bonafos, G. B. Asssayag, and P. Normand, "Silicon nanocrystal memory devices obtained by ultra-low-energy ion-beam synthesis", in *Solid-State Electronics*, vol. 48, pp. 1511-1517, 2004.

- [2.4] V. Ioannou-Sougleridis, and A. G. Nassiopoulou, "Investigation of charging phenomena in silicon nanocrystal metal-oxide-semiconductor capacitors using ramp current-voltage measurements", in *J. Appl. Phys.*, vol. 94, pp. 4084-4087, 2003.

- [2.5] D. N. Kouvatsos, V. Ioannou-Sougleridis, and A. G. Nassiopoulou, "Charging effects in silicon nanocrystals within SiO<sub>2</sub> layers, fabricated by chemical vapor deposition, oxidation, and annealing", in *Appl. Phys. Lett.*, vol. 82, pp. 397, 2003.

- [2.6] S. M. Sze, *Physics of Semiconductor Devices*, 2<sup>nd</sup> ed., New York: Wiley, pp. 849-850, 1981.

- [2.7] Y.-C. King, T.-J King, and C. Hu, "MOS memory using germanium nanocrystals formed by thermal oxidation of Si<sub>1-x</sub>Ge<sub>x</sub>", in *IEDM Tech. Dig.*, pp. 115-118, 1998.

- [2.8] J. H. Chen, Y. Q. Wang, W. J. Yoo, Y.-C. Yeo, G. Samudra, D. S. H. Chan, A. Y. Du, and D.-L. Kwong, "Nonvolatile flash memory device using Ge

nanocrystals embedded in HfAlO high-k tunneling and control oxides: Device fabrication and electrical perofrmance" in *IEEE Tran. Electron Devices*, vol. 51, no. 11, pp. 1840-1848, 2004.