# ADDRESSING PERFORMANCE BOTTLENECKS FOR TOP-DOWN ENGINEERED NANOWIRE TRANSISTORS

#### **JIANG YU**

NATIONAL UNIVERSITY OF SINGAPORE

2009

# ADDRESSING PERFORMANCE BOTTLENECKS FOR TOP-DOWN ENGINEERED NANOWIRE TRANSISTORS

#### **JIANG YU**

B. Sci. (Peking University, P. R. China) 2005

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2009

#### Acknowledgements

First and foremost, I would like to take this opportunity to express my sincere gratitude to my advisors, Prof. Chan Siu hung Daniel and Prof. Kwong Dim-Lee for their invaluable guidance, encouragement throughout my Ph.D. study at NUS. I am greatly thankful to Prof. Chan for his kindness and patience in helping me in my research. He is an experienced advisor, who gave me continuous encouragement for my graduate study. In addition, he was also willing to listen to every aspect of my life in Singapore, and made it feel as though I was sharing my personal matters with an elder. He guided me not just academically, but also in my personal development. I also truly appreciate Prof. Kwong's wise guidance and foresight for my Ph.D research work. He asked me to cultivate a habit of reading a paper everyday, which keeps me learning all the time and abreast of the latest scientific development. Without his expertise and advice in semiconductor technology, I would not be able to undertake all my projects smoothly. I would like to thank Prof. Kwong for providing me the opportunity to join the Institute of Microelectronics (IME), Singapore for my Ph.D research work, where I was able to work with and learn from many experts in diverse areas.

I would also like to express my deepest appreciation for Dr. Patrick Lo and Dr. Navab, Singh from the Institute of Microelectronics, Singapore, for their valuable advice and technical discussions for my research work. I benefited greatly through interactions with them. They gave me inspiration throughout all my projects during my graduate study. I would also like to thank Dr. Yu Ming-Bin, Dr. Wei Yip Lo, Dr. Subhash Chander Rustagi, Dr. Zhang Gang, Kavitha Devi Buddharaju for their support which had helped me greatly. I would like to thank Cindy Soh Mei Cheng for facilitating the arrangements which make everything go smoothly in IME. I would like to thank all the technical staff

in NanoEP department for their kindness, help and suggestions for my research work. I would not have been able to do my doctoral research smoothly otherwise.

Special thanks to my seniors in Silicon Nano Device Lab (SNDL) at NUS, especially Dr. Ren Chi, Dr. Chui King Jien, Dr. Ang Kah Wee, Dr. Tan Kian Ming, Dr. Shen Chen, Dr. Wang Xin Peng, Rinus Lee, Gao Fei, Song Yan for their assistance on many of my technical problems encountered during my graduate study. Many thanks to my research buddies, Zhao Hui, Xie Ruilong, Tan Eu-Jin, Chin Yoke King, Peng Jian Wei and all the SNDL students for their indispensable help for my research work and for the great academic atmosphere created.

My deepest love and gratitude goes out to my parents who have given me their support and encouragement during my doctorial studies. Most importantly, a special "Thank you!" goes out to my dearest Jason who has always been there unconditionally with his love and support throughout these years.

## **Table of Contents**

| Acknov    | wledgements                                 | ii   |

|-----------|---------------------------------------------|------|

| Table o   | of Contents                                 | iv   |

| Summa     | ary                                         | viii |

| List of   | Tables                                      | X    |

| List of 1 | Figures                                     | xi   |

| List of   | Symbols                                     | 1    |

| List of A | Abbreviations                               | 3    |

| СНАРТ     | ΓER 1                                       | 5    |

| 1. IN     | TRODUCTION                                  | 5    |

| 1.1       | Overview for CMOS Scaling                   | 5    |

| 1.2       | Why Nanowire Transistors?                   | 6    |

| 1.2       | 2.1 Innovation on Architecture and Material | 7    |

| 1.2       | 2.2 GAA Nanowire FETs                       | 9    |

| 1.3       | Objectives and Scope                        | 10   |

| 1.4       | Thesis Organization                         | 12   |

| CHAP      | ΓER 2                                       | 14   |

| 2. LI     | TERATURE REVIEW                             | 14   |

| 2.1       | Introduction                                | 14   |

| 2.2       | Nanowire Synthesis                          | 15   |

|    | 2.2.1 | Bottom-up Method                               | 15         |

|----|-------|------------------------------------------------|------------|

|    | 2.2.2 | Top-down Method                                | 17         |

|    | 2.3   | Nanowire FETs.                                 | 21         |

|    | 2.3.1 | Bottom-up Nanowire FETs                        | 21         |

|    | 2.3.1 | Top-down Nanowire FETs                         | 23         |

|    | 2.4   | Challenges of Nanowire Transistors.            | 27         |

| C  | HAPTI | ER 3                                           | 30         |

| 3. |       | ANNEL ENGINEERING EXPLORATION (1) - Ge Rich    | 30         |

|    | 3.1   | Introduction                                   | 30         |

|    | 3.2   | SiGe Growth and Ge Condensation.               | 32         |

|    | 3.2.1 | Review on the Ge Condensation Technique        | 32         |

|    | 3.2.2 | Experiments on SiGe Growth and Ge Condensation | 34         |

|    | 3.3   | SiGe Nanowire Formation                        | 37         |

|    | 3.4   | Ge Rich Nanowire FETs                          | 40         |

|    | 3.4.1 | Ge Rich Nanowire FETs Farication               | 40         |

|    | 3.4.2 | Electrical Characteristics of SGNW FETs        | 42         |

|    | 3.4.3 | Energy Band Diagram Investigation of SGNW      | 46         |

|    | 3.5   | Conclusion                                     | 57         |

|    |       | ANNEL ENCINEEDING EVALORATION (2) SiColSi      | 58         |

| 4. |       | ANNEL ENGINEERING EXPLORATION (2) -SiGe/Si     | <b>5</b> 0 |

|    | Core  | e/Shell Nanowire FETs                          | 58         |

|    | 4.1   | Introduction                                   | 58         |

|    | 4.2   | Device Fabrication                             | 59         |

| 4  | 1.3   | Results and Discussions                                  | 64  |

|----|-------|----------------------------------------------------------|-----|

|    | 4.3.1 | SEM Analysis of Core/Shell NW Structures                 | 64  |

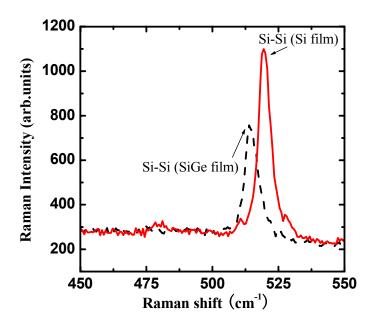

|    | 4.3.2 | SiGe Epitaxy Film Study and Core/Shell Structure         | 65  |

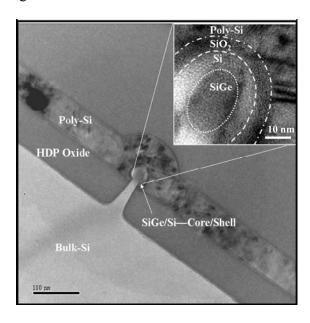

|    | 4.3.3 | TEM Analysis of the Core/Shell Structure                 | 67  |

|    | 4.3.4 | Electrical Characteristics of the Core/Shell Structure   | 68  |

|    | 4.3.4 | Challenges of the Core/Shell Structure Process           | 73  |

| ۷  | 1.4   | Conclusions                                              | 74  |

| СН | IAPTI | ER 5                                                     | 75  |

|    |       |                                                          |     |

| 5. | SOU   | RCE AND DRAIN ENGINEERING IN GAA NANOWIRE                |     |

|    | FET   | s FOR HIGH PERFORMANCE APPLICATION                       | 75  |

| 5  | 5.1   | Introduction                                             | 75  |

| 5  | 5.2   | Material Investigation                                   | 78  |

| 5  | 5.3   | Device Fabrication                                       | 84  |

| 5  | 5.4   | Dopant Profile Optimizations                             | 87  |

| 5  | 5.5   | Device Electrical Characteristics                        | 90  |

|    | 5.5.1 | $I_D$ - $V_G$ Curve and Series Resistance Investigations | 90  |

|    | 5.5.2 | Ion-Ioff Characteristics Enhancement                     | 93  |

|    | 5.5.3 | Backscattering Study for High S/D dopant Split           | 97  |

| 5  | 5.6   | Conclusions                                              | 99  |

| CH | IAPTI | ER 6                                                     | 100 |

| 6. | TH    | RESHOLD VOLTAGE ENGINEERING OF GAA                       |     |

| 0. |       |                                                          | 100 |

|    | NAN   | NOWIRE FETS FOR CMOS CIRCUIT INTEGRATION                 | 100 |

| 6  | 5.1   | Introduction                                             | 100 |

| 6  | 5.2   | Device Fabrications with FUSI Gate                       | 101 |

| 6.3    | Device Electrical Characteristics                                | 105 |

|--------|------------------------------------------------------------------|-----|

| 6.3    | GAA Single Metal FUSI Gates with Dual Tune-able $\Phi_m$         | 105 |

| 6.3    | Impact on Absolute $V_T$ , $I_{Off}$ and $I_{on}$ , and on $V_T$ | 111 |

| 6.3    | Tuned_FUSI NW FETs Low Power CMOS Circuit Application            | 116 |

| 6.3    | .4 FUSI Gate-Induced Stress Effects on Nanowire Channel          | 124 |

| 6.4    | Conclusions                                                      | 128 |

| СНАР'  | ΓER 7                                                            | 129 |

| 7. CO  | ONCLUSION AND OUTLOOK                                            | 129 |

| 7.1    | SiGe Nanowire Transistors with High-k/Metal Gate Integrations    | 129 |

| 7.2    | SiGe/Si Core/Shell transistors fabricated on Bulk Si substrate   | 130 |

| 7.3    | Metallic NW S/D Contacts Technique for Ultra-Scaled GAA Si NW    |     |

|        | Transistors                                                      | 131 |

| 7.4    | GAA FUSI Structure with Dual Work Functions Si NW Transistors    | 131 |

| 7.5    | Recommendations for Future Research                              | 132 |

| Refere | nces                                                             | 134 |

| Annen  | dix A: Publication List                                          | 153 |

#### **Summary**

The continuous advancement has allowed CMOS technology to meet the demands of higher device density, faster clock rate and lower power consumption. However, as the scaling dimensions shrink down to the sub-100 nm regime, immense physical challenges make the use of conventional scaling techniques alone insufficient. Novel one-dimensional (1D) structures such as semiconductor nanowires (NWs) are considered to be promising structures for nanoscale devices and circuits. In this thesis, several approaches have been investigated in order to address the performance bottlenecks and to further enhance the performance of semiconductor nanowire devices.

In this work, Ge rich nanowire transistors are demonstrated with metal gate/high-k gate stack. Using the pattern size dependent Ge condensation technique, lateral heterostructure Ge nanowire transistors are found to have higher drive current compared to the conventional homo-structure planar devices. Lower backscattering ratio is obtained in this Ge rich nanowire structure.

In a cost-effective approach for SiGe nanowire integration, the SiGe core/shell nanowire devices are fabricated on bulk Si substrate. Due to the lattice mismatch between SiGe core and Si shell, the SiGe core channel is under compressive stress, which improves the hole mobility due to hole effective mass reduction. With the surface passivation effect of the Si shell, the interface between the channel and dielectric is greatly improved.

The parasitic source and drain (S/D) resistances in extremely scaled Gate-All-Around (GAA) nanowire devices can pathologically limit the device drive current performance. Superior drive current was achieved in short gate length GAA nanowire

devices by utilizing metallic nanowire contacts. The parasitic S/D extension resistance was reduced significantly by using the ultra-thin Ni silicidation technique.

It is necessary to set the transistor threshold voltages correctly for both n and pFETs for nanowire circuit integrations. Dopant segregated FUSI GAA structure was demonstrated with successful dual work function implementation, achieving symmetrical threshold voltages ( $\pm 0.3$ V). Good inverter transfer characteristics and relatively low ring oscillator delay are observed.

# **List of Tables**

| Table 5.1: Split table for this work                                                            | 90  |

|-------------------------------------------------------------------------------------------------|-----|

| Table 5.2 summarizes and compares the key device parameters of this work with other prior work. | 97  |

| Table 6.1 : Splits of Gate Types and Doping                                                     | 106 |

| Table 6.2 Parameters $V_T$ , SS, DIBL for each split of NFETs                                   | 107 |

| Table 6.3 Parameters $V_T$ , SS, DIBL for each split of PFETs                                   | 110 |

# List of Figures

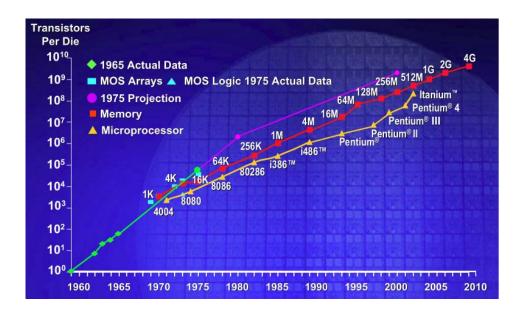

| Fig. 1.1: Moore's law for memory chips and microprocessors plotted on a semi-<br>logarithmic scale, the uppermost curve is the Moore projection based on<br>data up to 1975 at Intel Corporation                                                                                                                                                                                                                                         | 5  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

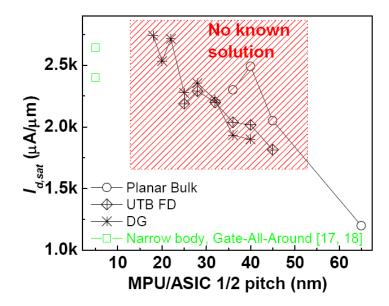

| Fig. 1.2: 2006 The ITRS 2006 N-MOSFET $I_{d,sat}$ requirements for various MOSFET structures.                                                                                                                                                                                                                                                                                                                                            | 9  |

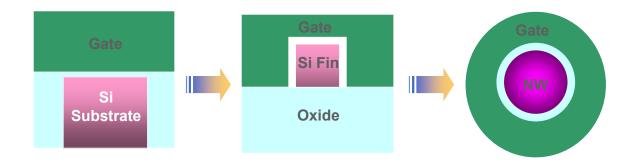

| Fig. 1.3: Schematics of devices structure evolution from conventional planar transistors to the tri-gate structure and then the GAA nanowire structure                                                                                                                                                                                                                                                                                   | 9  |

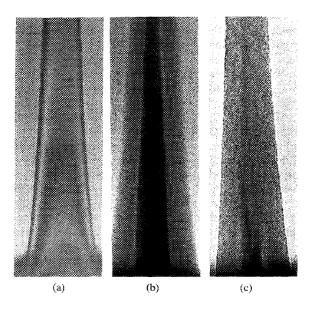

| Fig. 2.1: TEM Micrographs of the bottom nonuniform portions of Si nano-columns going through (a) 0h, (b) 8h, and (c) 16h of dry oxidation at 850 ° C. Enhanced oxidation rate near the bottom region where the diameter are larger is clearly evident [108].                                                                                                                                                                             | 18 |

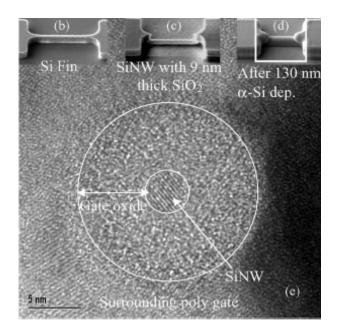

| Fig. 2.2: (b) Tilt view SEM image of 1000-nm-long Si fins after top silicon etch processes. (c) SiNW after SiO <sub>2</sub> deposition. (d) SiNW after gate oxide and 130-nm α-Si deposition. (e) TEM image cross section of nanowire with a circular 4-nm-thick wire 9-nm oxide with full coverage by α-Si from all the sides. [124]                                                                                                    | 20 |

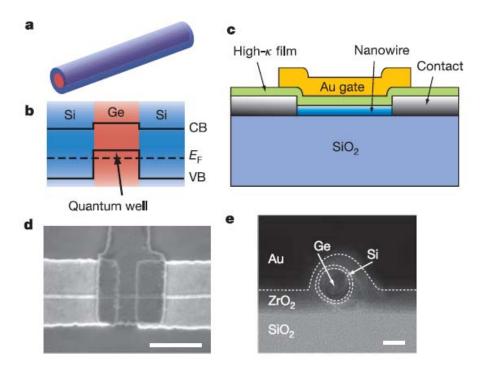

| Fig. 2.3: (a) Schematic of a Ge/Si core/shell nanowire. (b) Cross-sectional diagram. (c) Schematic of the NWFET device with high-k dielectric layer and Au top gate. (d) Top-view SEM image of a typical device. The Au top gate overlaps with the Ni source/drain electrodes to ensure full coverage of the channel. (e) Cross-sectional TEM image of a device prepared using 7 nm ZrO <sub>2</sub> dielectric. Scale bar, 10 nm [116]. | 22 |

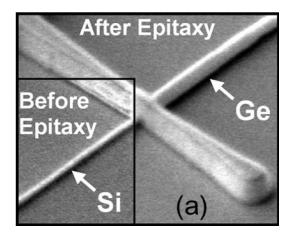

| Fig. 2.4: (L) SEM images depicting a nanowire FET before and after Ge epitaxy to form the raised Ge S/D regions. (R) Cross-sectional TEM of MeltED Ge nanowire S/D regions. [131].                                                                                                                                                                                                                                                       | 25 |

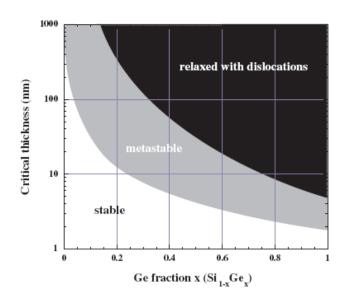

| Fig. 3.1: Matthews and Blakeslee critical thickness plotted against germanium fraction for pseudomorphic $\mathrm{Si}_{1-x}\mathrm{Ge}_x$ layers grown on bulk (100) silicon. Also included a metastable curve for MBE growth at 550 °C [182]                                                                                                                                                                                            | 33 |

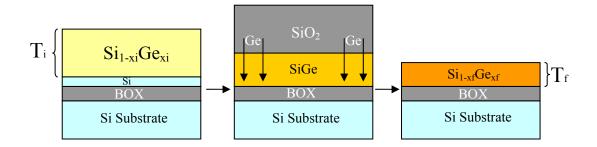

| Fig. 3.2: Schematics illustrating the Ge condensation technique                                                                                                                                                                                                                                                                                                                                                                          | 34 |

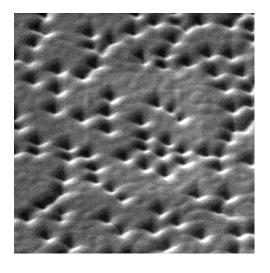

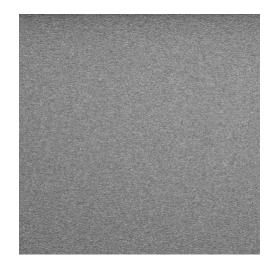

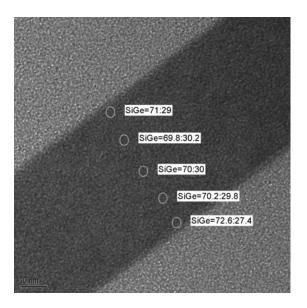

| Fig. 3.3: 50nm SiGe 25%@ 580°C Fig. 3.4: 20nm SiGe 25%@ 580°C                                                                                                                                                                                                                                                                                                                                                                            | 35 |

| Fig. 3.5: TEM micrograph of SiGe layer after Ge condensation, a uniform SiGe layer was achieved by the cyclic oxidation and annealing steps                                                                                                                                                                                                                                                                                              | 36 |

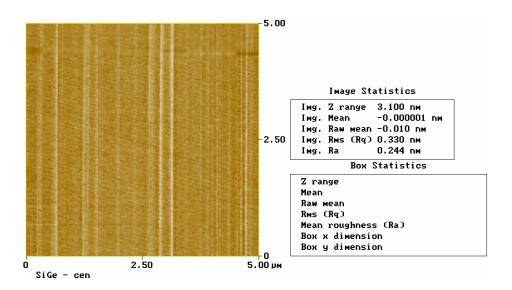

| Fig. 3.6: AFM surface analysis of SiGe film after Ge condensation technique.  Good surface morphology is obtained with RMS value~ 0.33 nm                                                                                                                                                                                                                                                                                                | 37 |

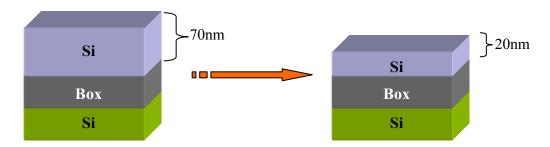

| Fig. 3.7: Schematics illustrating of SOI thinning down process by dry oxidation process                                                                                                                                                                                                                                                                                                                                                  | 37 |

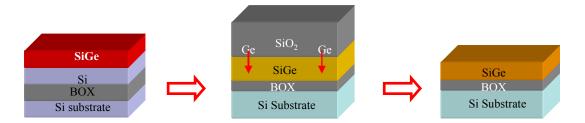

| Fig. 3.8: Schematics illustrating Ge condensation process by the cyclic oxidation and annealing processes                                                                                                                                                                                                                                                                                                                                | 38 |

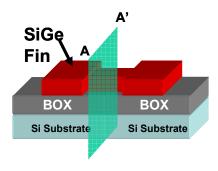

| Fig. 3.9: Schematics after SiGe fin definitions. The AA' plane denotes the cutting plane of the SiGe fin cross-sections.                                                                                                                                                                                                                                                                                                                  | 38 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

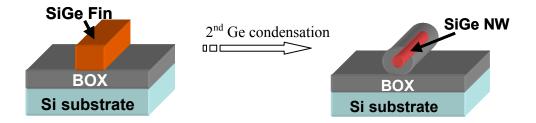

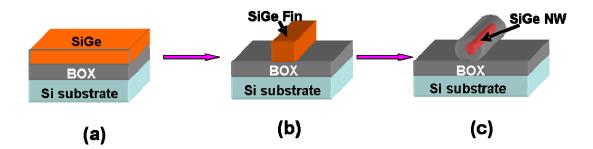

| Fig. 3.10: Schematics illustrating the 2 <sup>nd</sup> Ge condensation technique, after the 2 <sup>nd</sup> Ge condensation technique, Ge rich nanowire formed.                                                                                                                                                                                                                                                                           | 39 |

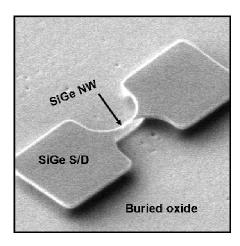

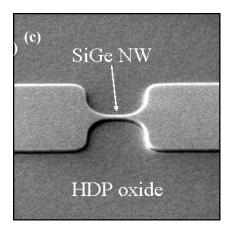

| Fig. 3.11: SEM image after SiGe NW release processes.                                                                                                                                                                                                                                                                                                                                                                                     | 39 |

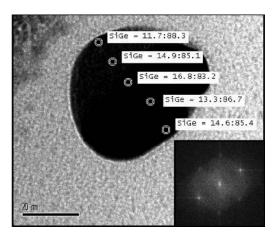

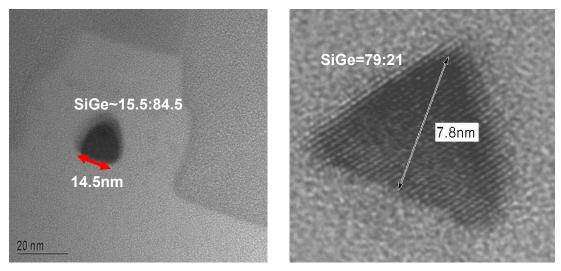

| Fig. 3.12: TEM images after SiGe nanowire oxidation and formation. SiGe nanowires with diameter of 14.5nm, Ge%~84.5% and with diameter of 7.8 nm, Ge%~21% are formed respectively.                                                                                                                                                                                                                                                        | 40 |

| Fig. 3.13: Schematics illustration SiGe NW formation processes                                                                                                                                                                                                                                                                                                                                                                            | 40 |

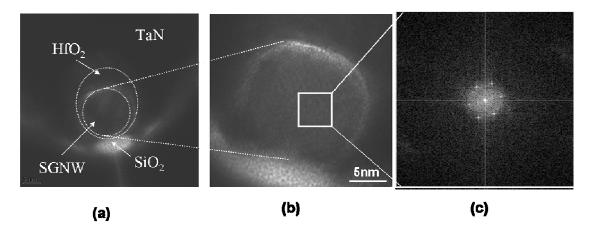

| Fig. 3.14 (a) TEM image of channel cross-section, showing the SiGe (70%) nanowire with diameter of 12 nm and HfO <sub>2</sub> /TaN gate stack. (b) HRTEM image of the SiGe nanowire, good crystalline structure can be seen clearly. (c) Reciprocal space diffractogram (FFT) analysis. Clear and sharp spots in the diffractogram implies defect free and crystalline SGNW formed by this two step process                               | 41 |

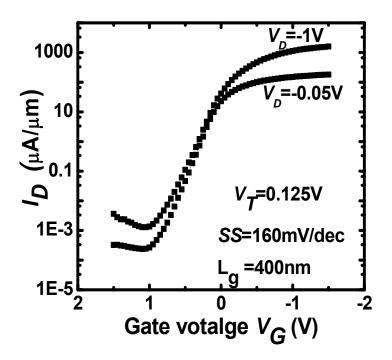

| Fig. 3.15 $I_D$ - $V_G$ characteristics of SiGe NW device with NW diameter of 12nm, $Lg$ - 400 nm, DIBL ~ 40mV/dec, $I_{on}$ - $I_{off}$ ~ $10^5$                                                                                                                                                                                                                                                                                         | 42 |

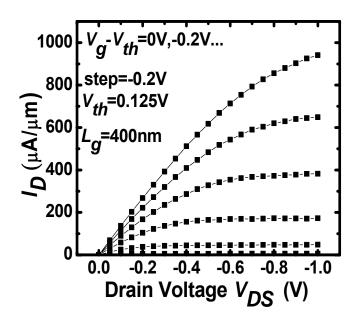

| Fig. 3.16 $I_D$ - $V_D$ characteristics of the same device. Drive current is ~1000 $\mu$ A/ $\mu$ m @ $V_G$ - $V_T$ =-1.0V                                                                                                                                                                                                                                                                                                                | 43 |

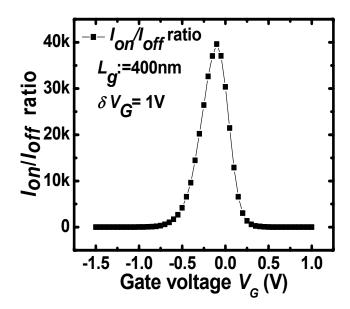

| Fig. 3.17 $I_{on}$ - $I_{off}$ ratio for 400nm SiGe NW. ( $I_{on}$ - $I_{off}$ ratio = $I_D$ value@ $V_G$ +1V divided by that @ $V_G$ . $V_G$ from -1.5V to 1V)                                                                                                                                                                                                                                                                           | 44 |

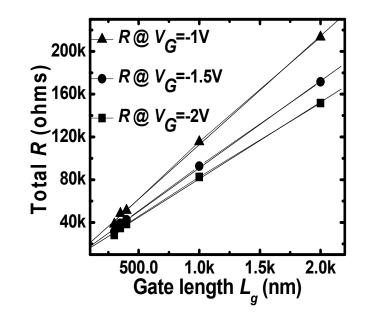

| Fig. 3.18 Plot of resistance as a function of $L_G$ @ $V_G$ =-1V,-1.5V,-2V. The extracted series resistance is ~10k $\Omega$ .                                                                                                                                                                                                                                                                                                            | 44 |

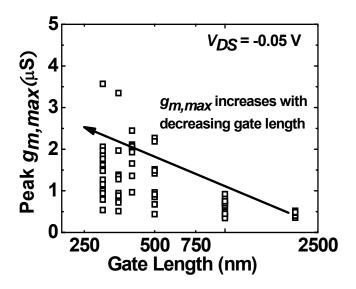

| Fig. 3.19 Plot of $g_m$ peak as a function of $L_G$ . As $L_G$ decreases, $g_m$ peak increases                                                                                                                                                                                                                                                                                                                                            | 45 |

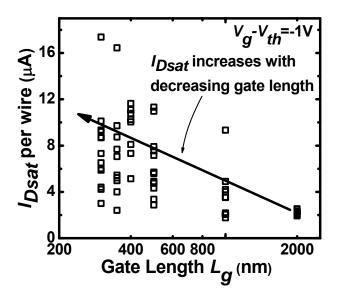

| Fig. 3.20 Plot of $I_{Dsat}$ per wire versus $L_G$ . $I_{Dsat}$ improves when $L_G$ decreases.                                                                                                                                                                                                                                                                                                                                            | 46 |

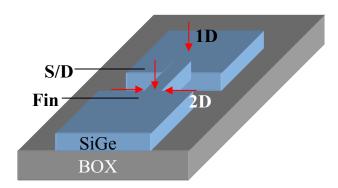

| Fig. 3.21 Schematic illustrating pattern size dependent Ge condensation technique                                                                                                                                                                                                                                                                                                                                                         | 47 |

| Fig. 3.22 Schematic illustrating Ge% difference between SiGe NW channel and source/drain area, thus forming the lateral heterostructure.                                                                                                                                                                                                                                                                                                  | 47 |

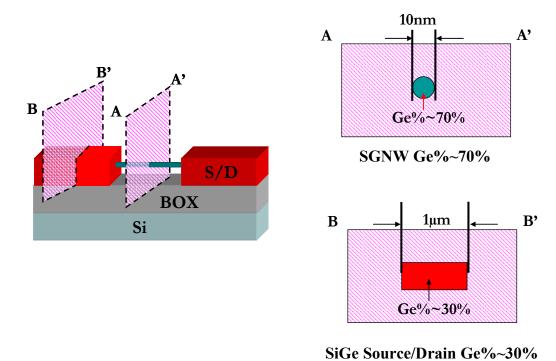

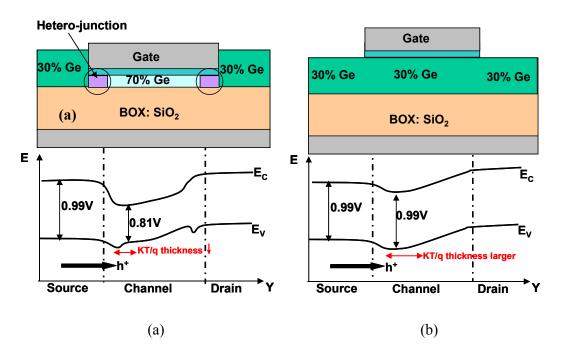

| Fig. 3.23 (a) SEM image of a completed SGNW FETs with AA' and BB' representing two TEM cutting planes. (b) TEM image of S/D region for AA' cut. Ge concentration is around 30%. (c) TEM micrograph of cross-section (BB' cut) for SiGe NW channel, followed by the HfO <sub>2</sub> and TaN metal gate stack. The diameter of SiGe NW is 12nm. EDX showing Ge% in SiGe NW is 70%, and the HRTEM image of SiGe NW is showing on the right. | 48 |

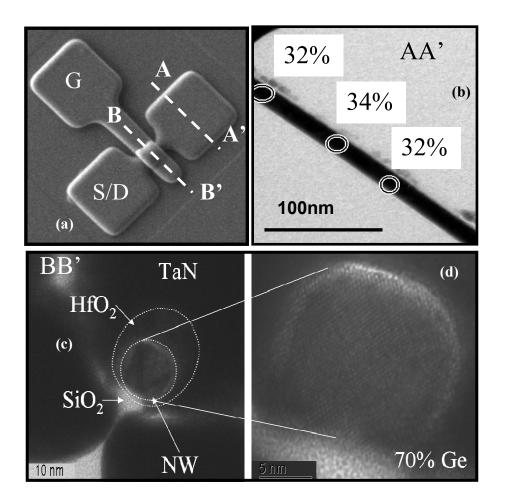

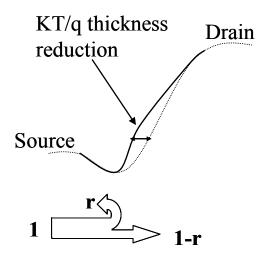

| Fig. 3.24 Schematic view of SiGe NW devices with hetero-structure along channel direction. Ge concentration is modulating in S-C-D, where 30% Ge is in S/D while 70% in the channel area. The band diagram along the channel                                                                                                                                                                                                              |    |

| direction is shown below. As Ge% varies, the band gap changes from 0.99V (S/D) to 0.81V (Channel). This results valence band offset between source and channel, which reduces the KT/q layer thickness from source towards channel. Fig. 3.24 (b) Shows schematic view of homo-structure for comparison, the KT/q layer thickness is larger compared to heterostructure devices.                                                                         | 49 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

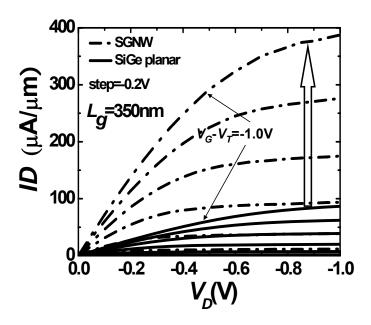

| Fig. 3.25 $I_D$ – $V_D$ characteristics comparing the performance of hetero SGNW pFET (current normalized to perimeter) with planar homo SiGe channel (W = 1 $\mu$ m) device. Drive current of SGNW device is 4.5× than that of planar devices.                                                                                                                                                                                                          | 50 |

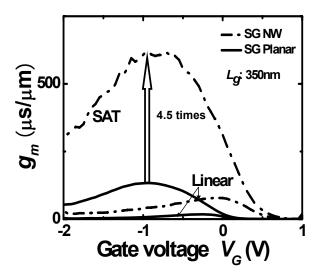

| Fig. 3.26 $G_m$ – $V_G$ characteristics of hetero nanowire and homoplanar devices. Both saturation and linear $G_m$ show 4.5 × enhancements for hetero nanowire device (normalized to perimeter) in comparison to homoplanar (normalized to W). Saturation $G_m$ does not decrease too rapidly after the peak, which indicates that ON-state channel resistances dominate compared to the parasitic series resistances at lower gate overdrive voltages. | 51 |

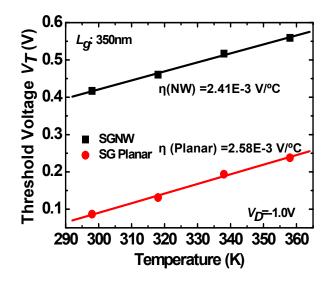

| Fig. 3.27 Threshold voltage dependency with temperature for both SGNW and SG planar devices. Comparable η observed for two kinds of devices                                                                                                                                                                                                                                                                                                              | 52 |

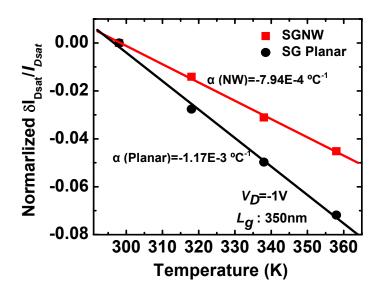

| Fig. 3.28 Drive current changes with temperature for SGNW and planar devices at $V_D$ =-1V. Temperature coefficient $\alpha$ of SGNW is 32% smaller than planar devices.                                                                                                                                                                                                                                                                                 | 53 |

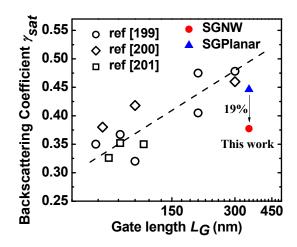

| Fig. 3.29 Comparison of backscattering coefficient for this work and other work (ref [199-201]). $\gamma_{sat}$ of SGNW was found far below the fitting line at the same gate length. And 19% reduction has been achieved for SGNW devices over planar devices.                                                                                                                                                                                          | 53 |

| Fig. 3.30 Band diagram illustrates KT/q layer thickness reducing in 70% Ge channel of SGNW devices.                                                                                                                                                                                                                                                                                                                                                      | 54 |

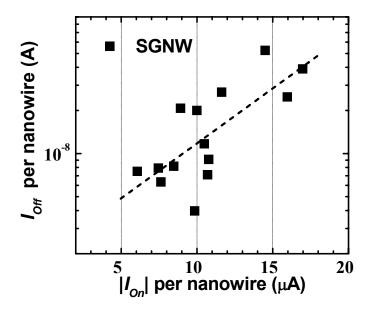

| Fig. 3.31 $I_{Off}$ – $I_{On}$ plot for hetero SGNW devices ( $I_{Off} = I_{DS}@V_{GS} = +0.7 \text{ V}$ , $I_{On} = I_{DS}@V_{GS} = -0.7 \text{ V}$ ). A dashed line is linearly fitted to the data points. Improving process uniformity is likely to reduce the spread of data points                                                                                                                                                                  | 56 |

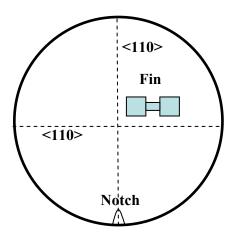

| Fig. 4.1: Schematics illustrating the notch orientation and channel orientation fabricated in this work.                                                                                                                                                                                                                                                                                                                                                 | 59 |

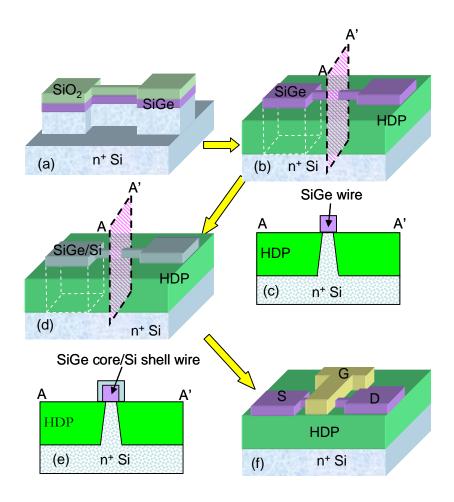

| Fig. 4.2: Schematics of process flow illustrating the core/shell nanowire transistors fabrication.                                                                                                                                                                                                                                                                                                                                                       | 60 |

| Fig. 4.3: Line/space patterns with printed line $CD \sim 80$ nm using alternating phase shift mask showing excellent line edge and line width uniformity. Bottom is a high zoom image taken at a rotation.                                                                                                                                                                                                                                               | 61 |

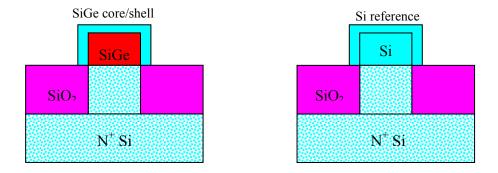

| Fig. 4.4: Schematics illustrating the channel cross section. For the SiGe wafer, after Si epitaxy, a core/shell structure formed on top of the n <sup>+</sup> Si pillar while the reference wafer remains Si on top of n <sup>+</sup> Si pillar. The channel widths are comparable for two kinds of devices.                                                                                                                                             | 62 |

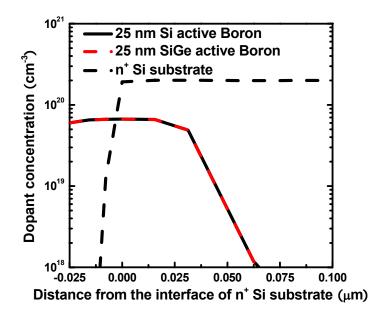

| Fig. 4.5: TCAD simulations of the S/D implantation profile for SiGe and Si wafers separately. Comparable dopant concentration profile is observed                                                                                                                                                 | 63 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

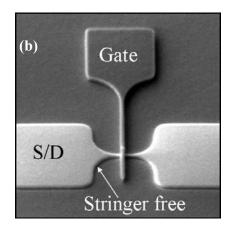

| Fig. 4.6: (a) SEM image after CMP process & SiGe NW release (b) SEM image after gate pattern transfer. Gate lengths $L_G$ down to ~40nm were formed. Parasitic gate stringers were removed. (c) SEM image of NW device after spacer formation. (d) SEM images after metal contact etching process | 64 |

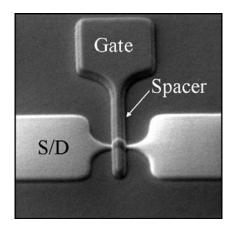

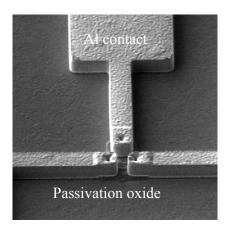

| Fig. 4.6: (c) SEM image of NW device after spacer formation. (d) SEM images after metal contact etching process.                                                                                                                                                                                  | 65 |

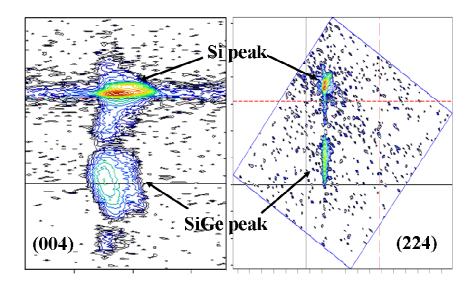

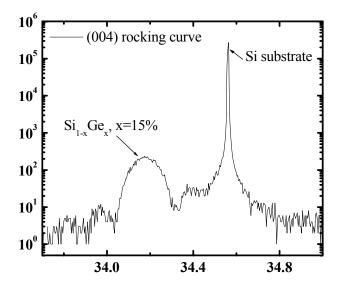

| Fig. 4.7: (004) and (224) reciprocal space maps show excellent alignment between the SiGe and Si peaks, indicating pseudomorphic epitaxial growth. The SiGe film and the Si substrate have similar in-plane lattice constants.                                                                    | 66 |

| Fig. 4.8: High resolution XRD rocking curve shows excellent crystalline quality of 15% SiGe film grown pseudo-morphically on the bulk Si substrate                                                                                                                                                | 66 |

| Fig. 4.9: High resolution XRD rocking curve shows excellent crystalline quality of 15% SiGe film grown pseudo-morphically on the bulk Si substrate                                                                                                                                                | 67 |

| Fig. 4.10: TEM micrograph of channel cross-section with SiGe/Si Core/Shell                                                                                                                                                                                                                        | 68 |

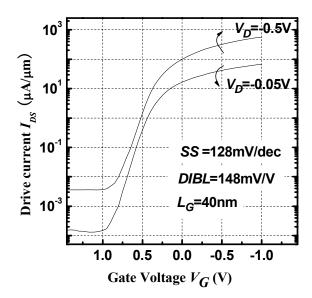

| Fig. 4.11: $I_D$ - $V_G$ transfer characteristic of typical NW devices for gate length of 40 nm. Good short channel control was maintained despite the thick gate oxide.                                                                                                                          | 69 |

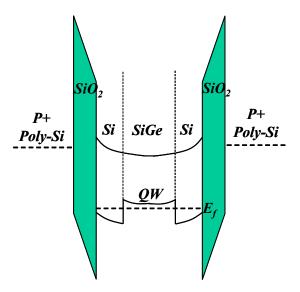

| Fig. 4.12: Band diagram schematic (not to scale) of channel cross section of SiGe/Si Core/Shell structure. The hole quantum well (QW) in the strained SiGe region is illustrated.                                                                                                                 | 69 |

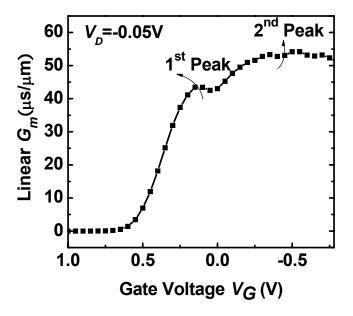

| Fig. 4.13: Linear $G_m$ characteristic shows two $G_m$ peaks, which corresponds to SiGe (core) and Si (shell) channel conduction.                                                                                                                                                                 | 70 |

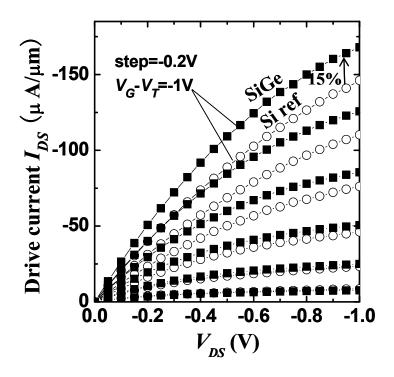

| Fig. 4.14: $I_D$ - $V_D$ family of curves of the same device. The normalized drive current of Si/SiGe nanowire device is $167\mu\text{A}/\mu\text{m}$ at $V_G$ - $V_T$ =-1V. A 15% enhancement is observed for the core/shell devices compared to the Si reference devices.                       | 71 |

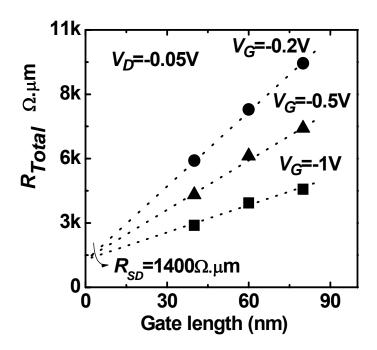

| Fig. 4.15: Total resistance as a function of gate gate length for three gate bias voltages. S/D series resistance $R_{SD}$ is estimated to be about 1400 $\Omega\mu m$                                                                                                                            | 72 |

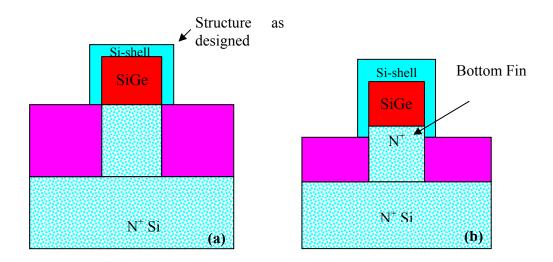

| Fig. 4.16: (a) cross section of the core/shell structure as designed. (b) Cross section of the structure due to over etching process happened and bottom fin exposed.                                                                                                                             | 73 |

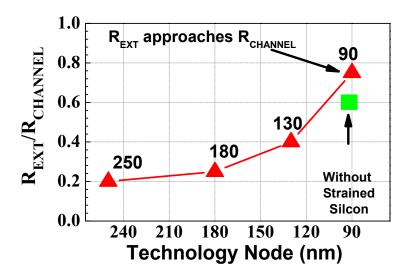

| Fig. 5.1: Ratio of external resistance over channel resistance at different technology node. The historical ratio is 20%.                                                                                                                                                                         | 77 |

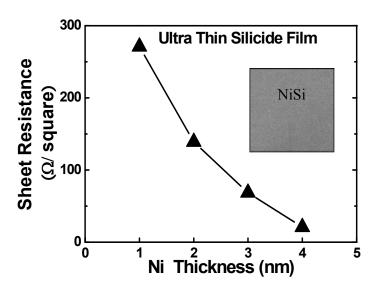

| Fig. 5.2: Sheet resistance values as a function of deposited Ni thickness for ultra thin silicide film. The sheet resistance value chosen is the average value of 48 points across the wafer. Inset is the SEM images of the 4 nm Ni deposited NiSi film.                                         | 79 |

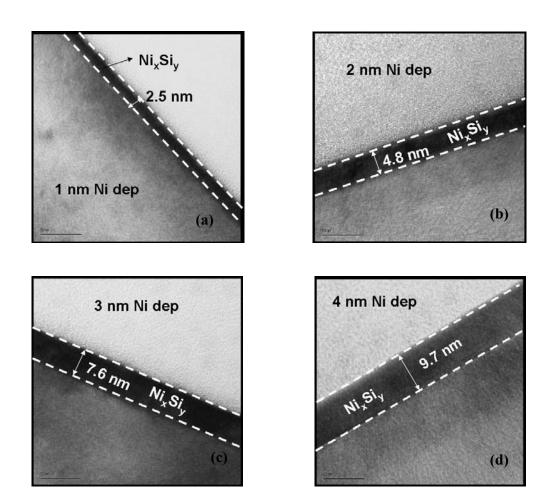

| Fig. 5.3: HRTEM micrographs for the thin Ni <sub>x</sub> Si <sub>y</sub> film with Ni deposition thicknesses from 1 nm to 4 nm. The formed Ni <sub>x</sub> Si <sub>y</sub> thicknesses are indicated in the figures.                                                                                                      | 30 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

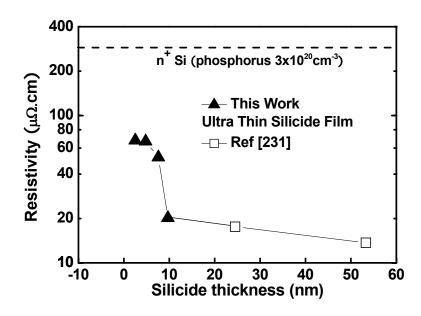

| Fig. 5.4: Resistivity values as a function of silicide thickness which further expands of ref. [231] work (open symbols) to thinner silicide thickness region with highly doped Si as dashed line. The resistivity increases significantly when the silicide thickness is below 9.7nm.                                    | 31 |

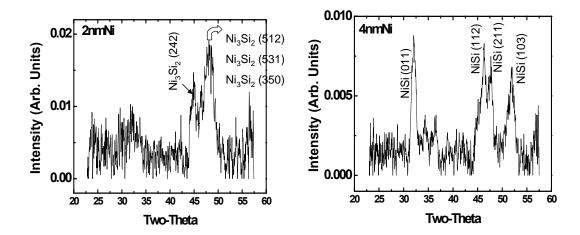

| Fig. 5.5: XRD phase analysis for the ultra thin Ni <sub>x</sub> Si <sub>y</sub> film with Ni deposition thickness of 2 nm and 4 nm, respectively. The 2 nm Ni deposition thickness fits well with the Ni <sub>3</sub> Si <sub>2</sub> phase (a) while the 4 nm Ni deposition thickness fits well with the NiSi phase (b). | 32 |

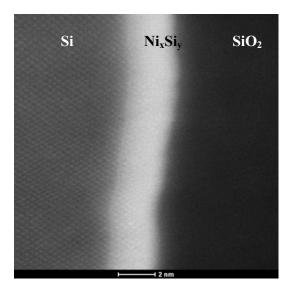

| Fig. 5.6: STEM image of the ultra thin Ni <sub>x</sub> Si <sub>y</sub> formed from 1 nm Ni deposition thickness. The Si lattice structure keeps continuing towards the Ni <sub>x</sub> Si <sub>y</sub> film.                                                                                                              | 33 |

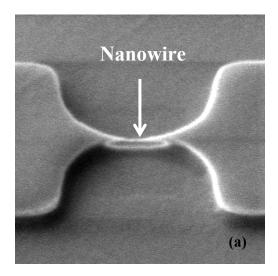

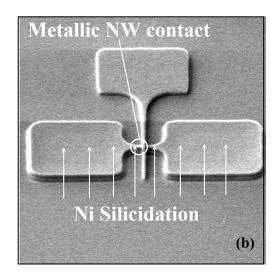

| Fig. 5.7: (a) SEM image after Si NW release (b) SEM image after gate etch.  Arrows indicate nanowire and pad Silicidation. The circle shows the nanowire contact regions.                                                                                                                                                 | 34 |

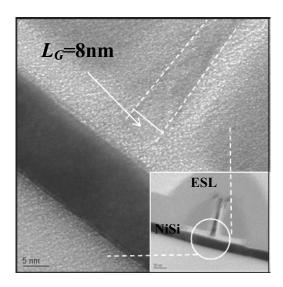

| Fig. 5.8: HRTEM image of gate structure cross-section, gate length is ~8nm. Inset shows zoom out view of gate structure, with ESL as etching stop layer                                                                                                                                                                   | 35 |

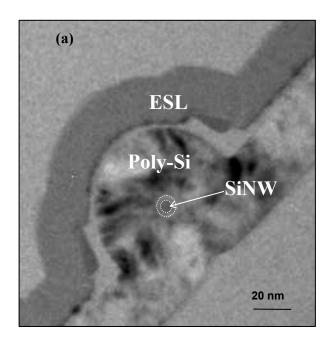

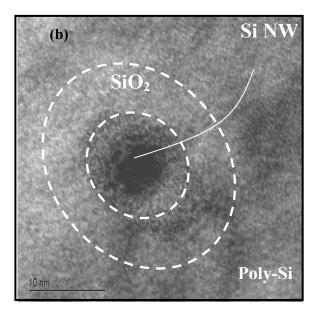

| Fig. 5.9: (a) TEM micrograph of the channel cross-section. The GAA structure was successfully formed with 4 nm oxide and followed by the poly Si. ESL is covered on top of the poly Si gate stack. (b) HRTEM image of channel cross-section showing 10 nm SiNW surrounded by 4 nm oxide and followed by poly silicon.     | 86 |

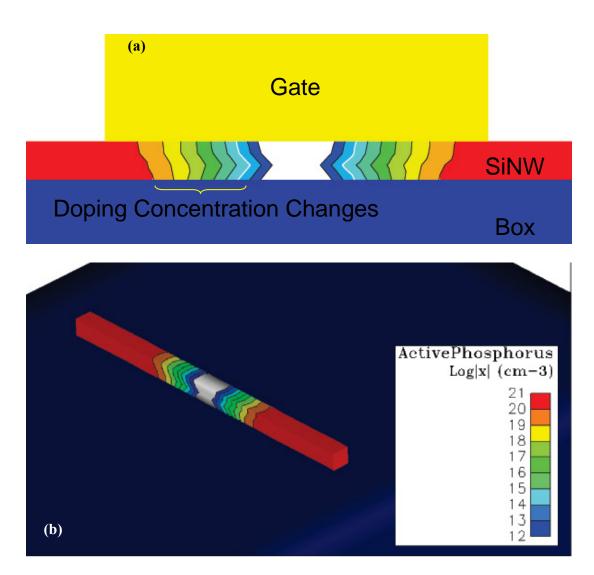

| Fig. 5.10: (a) TCAD simulation for the gate profile with the structure of 10 nm size nanowire source/drain extensions with the same gate pattern size. (a) Doping concentration profile along the nanowire region with different color standing for different channel doping.                                             | 88 |

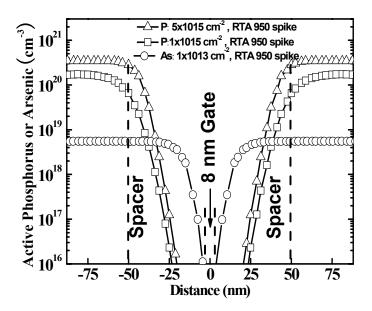

| Fig. 5.11: Active dopant profile with different implant conditions. As LDD profile was also showing. $5 \times 10^{15} \text{cm}^{-3}$ shows higher active dopant concentration and sharper profile.                                                                                                                      | 39 |

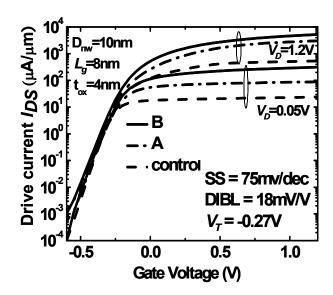

| Fig. 5.12: showing DC characteristics comparison between the three splits. Large enhancement has been obtained on sample B. Highly doped S/D doping with metallic nanowire contacts.                                                                                                                                      | )1 |

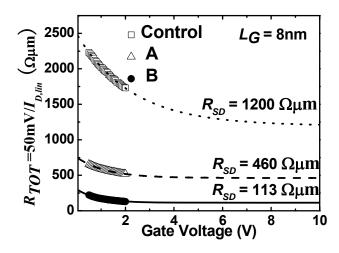

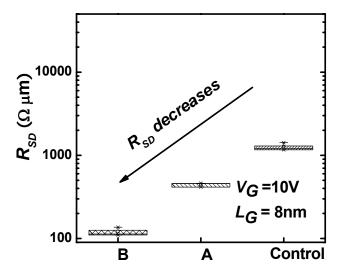

| Fig. 5.13: $R_{SD}$ resistance for control, split A, split B are 1200Ωμm, 460Ωμm & 113Ωμm, respectively. Metallic NW reduces $R_{SD}$ significantly9                                                                                                                                                                      | )1 |

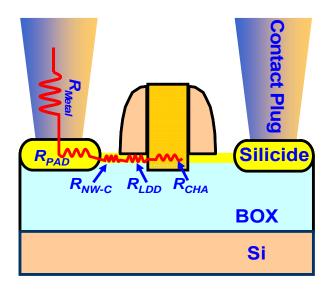

| Fig. 5.14: Gate cross section illustrating the total resistance components for a typical nanowire transistor.                                                                                                                                                                                                             | 12 |

| Fig. 5.15: Statistical $R_{SD}$ extraction for three splits by exponential fitting @ $V_G$ =10V. Splits B obtained the smallest series resistance among the three splits.                                                                                                                                                 | )3 |

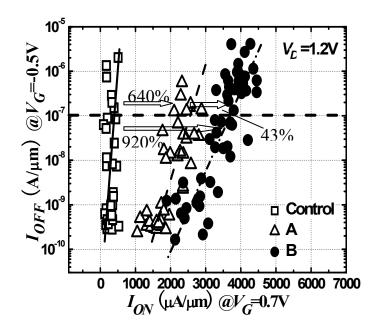

| Fig. 5.16: Comparison of $I_{off}$ versus $I_{on}$ .Sample B shows large enhancement over control and sample A.                                                                                                                                                                                                 | . 94 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

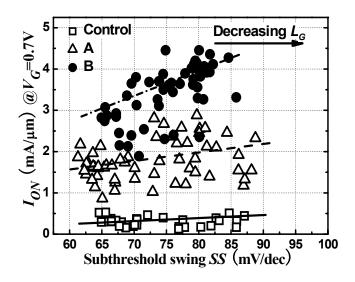

| Fig. 5.17: Comparison of $I_{on}$ versus SS. Sample B shows large improvement over control and sample A.                                                                                                                                                                                                        | .95  |

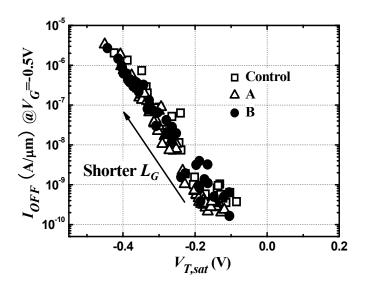

| Fig. 5.18: Comparison of $I_{Off}$ versus $V_{T,sat}$ . No short channel degradation has been found on sample A and B compared to control.                                                                                                                                                                      | .96  |

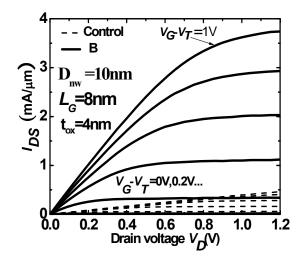

| Fig. 5.19: $I_D$ - $V_D$ curve for control and split B. Large enhancement has been obtained on sample B. Drive current is $3740\mu\text{A}/\mu\text{m}@V_G$ - $V_T$ =1V                                                                                                                                         | .96  |

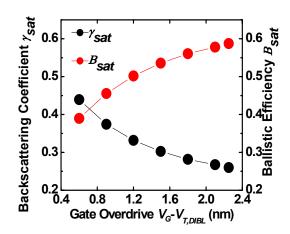

| Fig. 5.20: Backscattering ratio $r_{sat}$ and ballistic efficiency $B_{sat}$ extracted at various gate overdrives. A minimum rsat of ~0.26 was obtained @ $V_{G^-}$ $V_{T,\text{DIBL}}$ =2.25V.                                                                                                                 | . 98 |

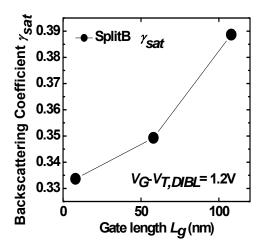

| Fig. 5.21: Backscattering ratio $r_{sat}$ extracted for various gate lengths at $V_G$ - $V_T$ , $_{DIBL}$ =1.2V. $r_{sat}$ decreases (improves) as gate lengths are scaled down                                                                                                                                 | .98  |

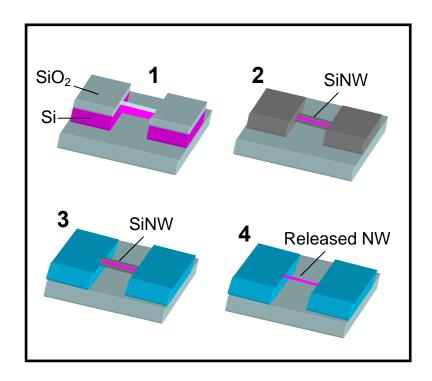

| Fig. 6.1: Schematics illustrating the process flow for the nanowire local release by utilizing the reverse gate mask.                                                                                                                                                                                           | 102  |

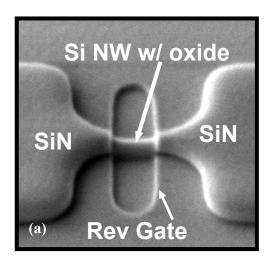

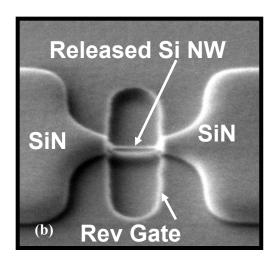

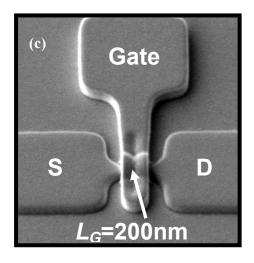

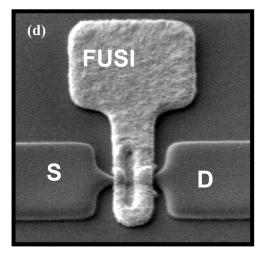

| Fig. 6.2: (a) SEM image after reverse gate etching process. S/D regions are covered by the SiN layer. (b) SEM image after Si NW local release. Only the reverse gate region, the nanowire is fully released. S/D regions are protected by the SiN layer during local release.                                   | 103  |

| Fig. 6.2: (c) After gate pattern transfer. The gate length depends on the reverse mask, the $L_G$ is 200nm. (c) FUSI device after gate FUSI process (RTA Soak anneal at 420°C). GAA FUSI gate formed with S/D region protected by SiN/oxide layer to prevent over-silicidation of the S/D regions.              | 103  |

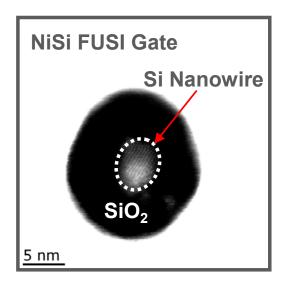

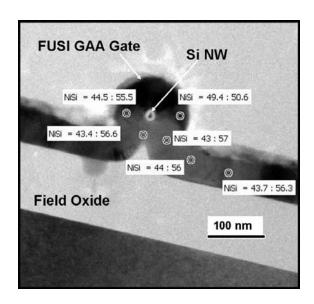

| Fig. 6.3: HAADF STEM image of channel cross section. The homogeneously high intensity of the surrounding gate further confirms the full silicidation                                                                                                                                                            | 104  |

| Fig. 6.4: TEM image of NW channel cross-section, showing the GAA FUSI NiSi gate. EDX analysis indicates that the Ni:Si ratio is close to 1:1. The wraparound regions are also fully silicided.                                                                                                                  | 105  |

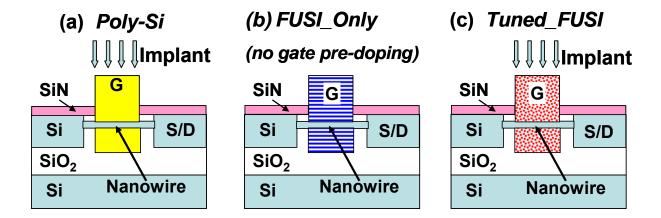

| Fig. 6.5: Schematics showing the nanowire device splits. The control Split (a) is with conventional implantation-doped poly-Si gate stack. Split (b) has FUSI gate stack without any prior gate implantation step. Split (c) has FUSI gate with gate pre-doping via implantation for gate work-function tuning. | 106  |

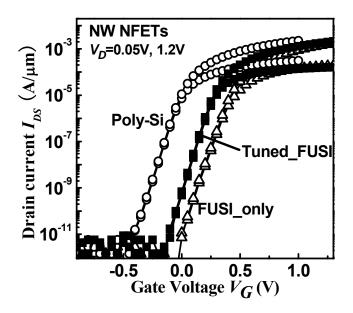

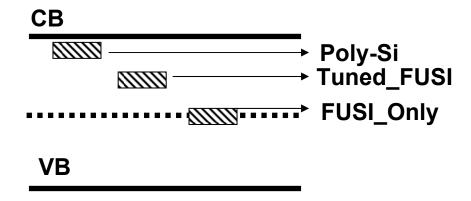

| Fig. 6.6: $I_D$ - $V_G$ of NFETs. $V_T$ successfully tuned by Phosphorus pre-doping before FUSI. There is no degradation in SS and DIBL observed.                                                                                                                                                               | 107  |

| Fig. 6.7: Band diagram schematics illustrating the Fermi-Level difference among different gate stack material. (Not to scale).                                                                                                                                                                                  | 108  |

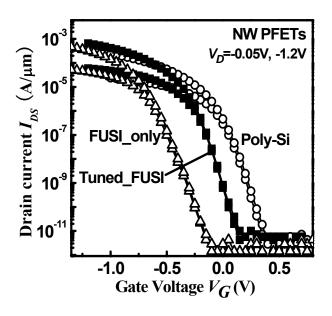

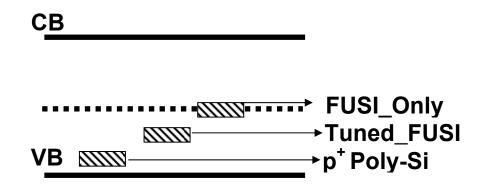

| Fig. 6.8: $I_D$ - $V_G$ of PFETs. $V_T$ successfully tuned by Phosphorus pre-doping before FUSL. There is no degradation in SS and DIBL observed.                                                                                                                                                               | 109  |

| Fig. | 6.9: Band diagram schematics illustrating the Fermi-Level difference among different gate stack material. (Not to scale).                                                                                                                | .110  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

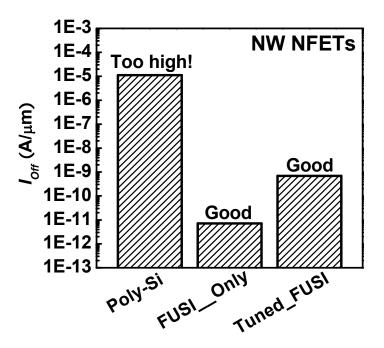

| Fig. | 6.10: $I_{Off}$ of NFETs. Poly-Si gate NW NFET has $I_{Off}$ that is too high. FUSI gate NW NFETs show excellent $I_{Off}$ values. By tuning the $V_T$ , the $I_{Off}$ can be set at the designed value.                                 | . 111 |

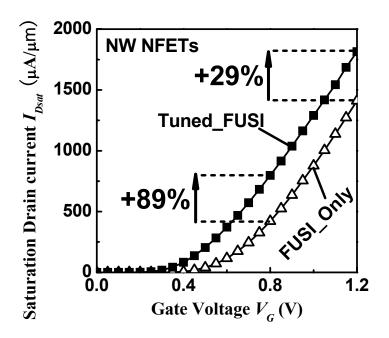

| Fig. | 6.11: $I_{on}$ of Tuned_FUSI NFET is enhanced by 29% over FUSI_Only NFET at $V_G = V_{DD} = 1.2$ V. $I_{on}$ enhancement is 89% at $V_G = 0.8$ V. This shows the importance of $V_T$ tuning when $V_{DD}$ is scaled down                 | . 112 |

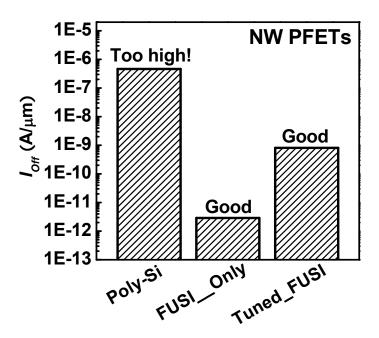

| Fig. | 6.12: $I_{Off}$ of PFETs. Poly-Si gate NW PFET has $I_{Off}$ that is too high. FUSI gate NW PFETs show excellent $I_{Off}$ values. By tuning the $V_T$ , the $I_{Off}$ can be set at the designed value.                                 | . 113 |

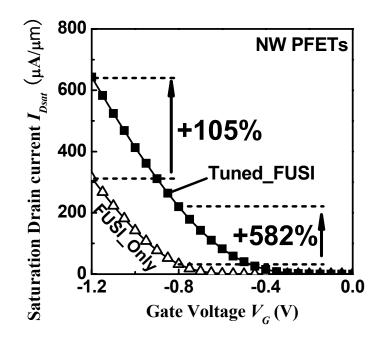

| Fig. | 6.13: $I_{on}$ of Tuned_FUSI PFET is enhanced by 105% over FUSI_Only PFET at $V_G = V_{DD} = -1.2$ V. $I_{on}$ enhancement is 582% at $V_G = 0.8$ V. This shows the importance of $V_T$ tuning when $V_{DD}$ is scaled down.             | . 113 |

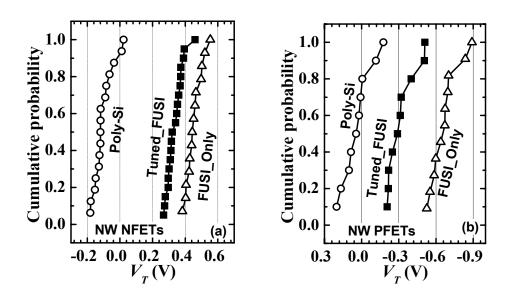

| Fig. | 6.14: Statistical plot of $V_T$ for NW NFETs (a) and PFETs (b) clearly shows the $V_T$ differences between splits. $V_T$ extracted from linear $I_D$ using max. $G_m$ and tangent method.                                                | . 114 |

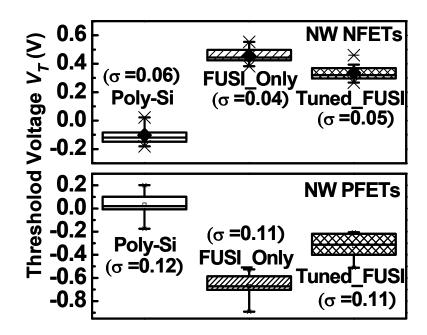

| Fig. | 6.15: Statistical plot of $V_T$ for for all three splits. $V_T$ was extracted from linear regime using max. $G_m$ and tangent method. No degradation of $V_T$ variation was observed.                                                    | .115  |

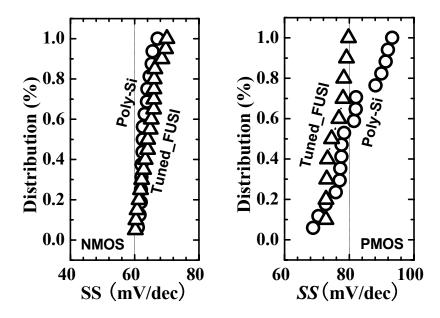

| Fig. | 6.16: Cumulative distribution of SS for Poly-Si and Tuned_FUSI splits. Both splits indicated comparable SS values.                                                                                                                       | .116  |

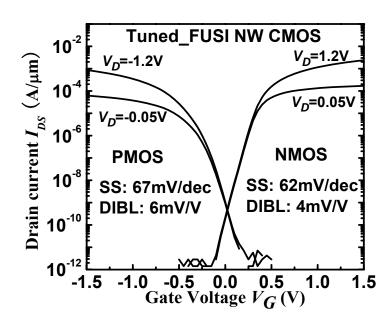

| Fig. | 6.17: $I_D$ - $V_G$ characteristics of Tuned_FUSI NW CMOS. Nearly symmetrical $V_T$ achieved with comparable short channel control. The drain current is normalized by nanowire diameter ~7 nm.                                          | .117  |

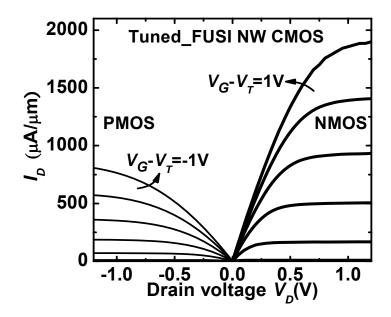

| Fig. | 6.18: $I_D$ - $V_D$ characteristics of Tuned_FUSI NW CMOS. The difference in drive current is attributed to electron and hole mobility differences and the higher series resistances in PFETs.                                           | .117  |

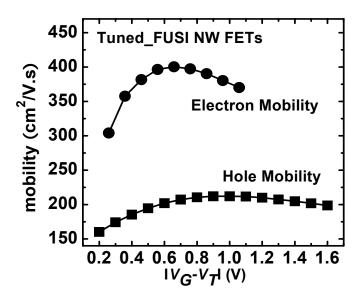

| Fig. | 6.19: Electron and hole mobility for Tuned_FUSI NW devices. $C_{inv}$ was obtained from a test structure with 1000 nanowires. The peak electron mobility is 400 cm <sup>2</sup> /V.s and hole peak mobility is 212 cm <sup>2</sup> /V.s. | . 118 |

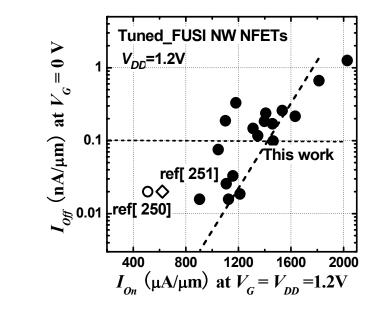

| Fig. | 6.20: $I_{on}$ - $I_{Off}$ plot of Tuned_FUSI NW NFETs. Significant enhancement obtained compared to LSTP benchmark work [250, 251]. At 20 pA/ $\mu$ m, the $I_{on}$ is 1180 $\mu$ A/ $\mu$ m.                                           | . 119 |

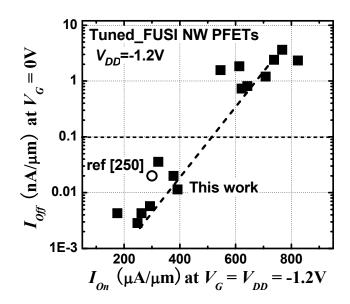

| Fig. | 6.21: $I_{on}$ - $I_{Off}$ plot of Tuned_FUSI NW PFETs. Significant enhancement obtained compared to LSTP benchmark work [250]. At 20 pA/ $\mu$ m, the $I_{on}$ is 405 $\mu$ A/ $\mu$ m.                                                 | . 120 |

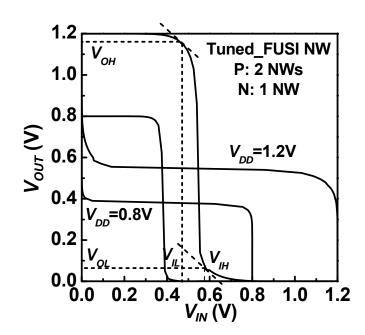

| Fig. | 6.22: Inverter transfer characteristics of Tuned_FUSI NWs. A sharp transfer obtained with excellent noise margin of NMH= 0.585V, NML= 0.407V at $V_{DD}$ =1.2V                                                                           | 121   |

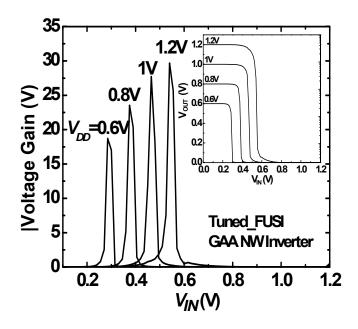

| Fig.   | 6.23: Voltage gain characteristics of Tuned_FUSI NW Inverter at different $V_{DD}$ . High inverter gain was obtained down to $V_{DD}$ =0.6V, indicating the suitability of GAA NW inverters for low $V_{DD}$ operation                                                                                                                         | 121 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

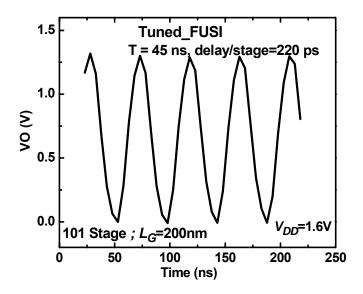

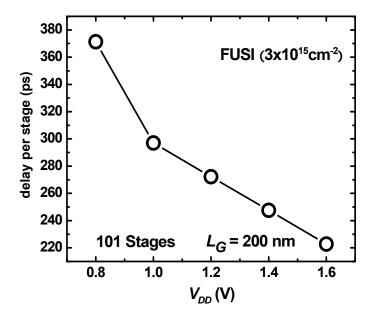

| Fig.   | 6.24: Tuned_FUSI GAA NW ring oscillators output characteristics of 101 stages at power supply voltage of $V_{DD}$ =1.6V. The per stage delay obtained is 220ps.                                                                                                                                                                                | 122 |

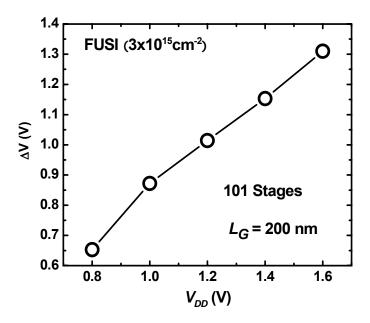

| Fig.   | 6.25: Ring oscillator behavior at different power supply voltages. As $V_{DD}$ decreases, the $\Delta V$ (magnitude of output voltage) drops.                                                                                                                                                                                                  | 123 |

| Fig.   | 6.26: Ring oscillator behavior at different power supply voltages. As $V_{DD}$ decreases, the delay per stage increases.                                                                                                                                                                                                                       | 123 |

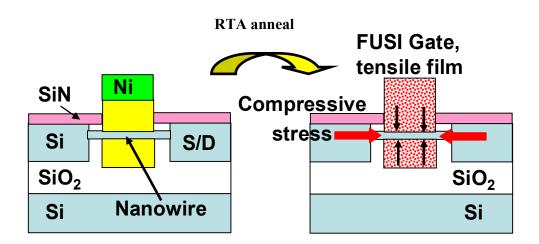

| Fig.   | 6.27: Schematics of silicidation process. The tensile FUSI gate film induces compressive channel stress. All FUSI silicidation processes were performed at 420°C. After FUSI, an additional split (FUSI_HT) went through a further stress-enhancing RTA anneal at 550°C to increase the silicide stress, and its corresponding channel stress. | 124 |

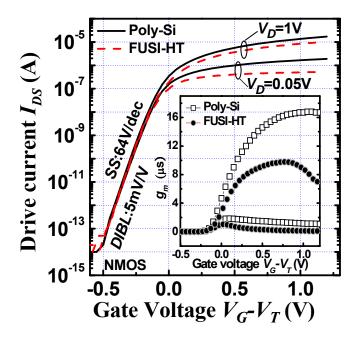

| Fig.   | 6.28: <i>I-V</i> transfer characteristics of high stress FUSI split cover poly-Si split with the transconductance characteristics shown as inset. Due to the channel is under compressive strain, the performance of the FUSI_HT NFETs degrades.                                                                                               | 125 |

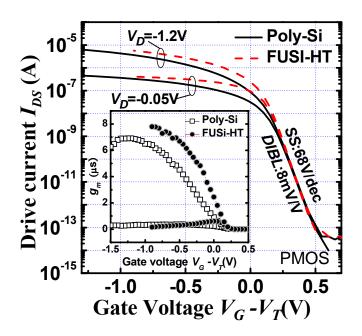

| Fig.   | 6.29: <i>I-V</i> transfer characteristics of high stress FUSI split cover poly-Si split with the transconductance characteristics shown as inset. Due to the channel is under compressive strain, the performance of the FUSI_HT PFETs enhanced.                                                                                               | 126 |

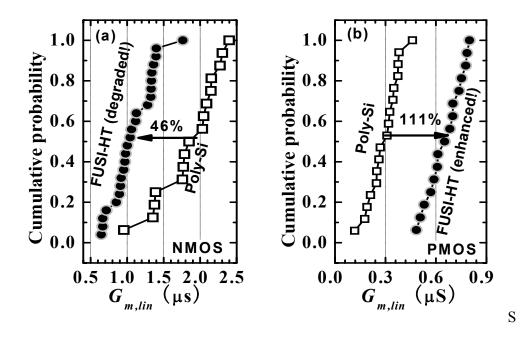

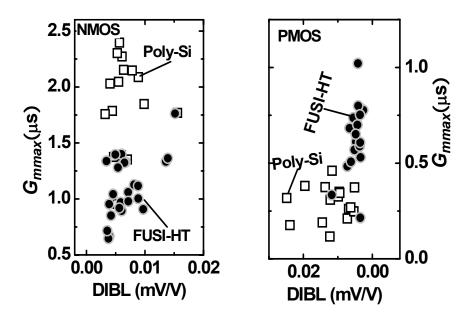

| Fig.   | 6.30: Cumulative distribution of peak $g_m$ at linear region for both N and P FETs. Due to the gate-induced compressive channel stress, $G_m$ of FUSI_HT is degraded for NFETs while enhanced for NW PFETs. For Tuned_FUSI no significant reduction was obtained for NW NFETs, while large enhancement was obtained for PFETs.                 | 127 |

| Fig. ( | 6.31: Plot of $G_{mmax}$ with DIBL for FUSI_HT and Poly Si. A clear enhancement is observed for PFETs while degradation for NFETs. Comparable DIBL indicated there is no short channel degradation occurred for the FUSI gate process.                                                                                                         | 128 |

# **List of Symbols**

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                             | Unit                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Capacitance                                                                                                                                                                             | fF/μm <sup>2</sup>                                 |

| Cox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Capacitance of gate oxide                                                                                                                                                               | fF/μm <sup>2</sup>                                 |

| E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Si conduction band-edge                                                                                                                                                                 | eV                                                 |

| $\overset{	ext{c}}{	ext{E}}_{	ext{F}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fermi-level energy                                                                                                                                                                      | eV                                                 |

| E<br>F, n+ poly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Fermi-level energy of n+ poly-Si gate                                                                                                                                                   | eV                                                 |

| E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fermi-level energy of Si substrate                                                                                                                                                      | eV                                                 |

| F, Si-sub                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Intrinsic Si Fermi-level energy                                                                                                                                                         | eV                                                 |

| Fi<br>E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Si valence band-edge                                                                                                                                                                    | eV                                                 |

| E E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Vacuum level                                                                                                                                                                            | eV                                                 |