С

i t

V

÷

е

w

m

t

е

а

d

а

t

а

а

t i

0

n

Q

თ 🗓 Cւძ

**ZHONG HANMEI**

NATIONAL UNIVERSITY OF SINGAPORE 2005

# SIMULATION OF SUPERJUNCTION MOSFET DEVICES

## **ZHONG HANMEI**

(B.Eng., Xi'an Jiaotong University, P.R.C.)

## A THESIS SUBMITTED

## FOR THE DEGREE OF MASTER OF ENGINEERING

## DEPARTMENT OF ELECTRICAL AND COMPUTER

### ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2005

#### ABSTRACT

Interdiffussion problem is unavoidable in superjunction device fabrication process. The practical superjunction device performance under interdiffusion influence is studied by extensive simulation and described in the thesis.

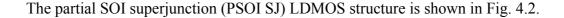

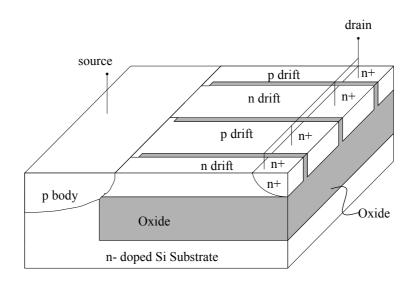

Partial SOI superjunction LDMOS structure is proposed in recent years in undergraduate projects. 3-D simulation by DAVINCI is done to study its performance. Simulation considers all the possible structure variations of the device such as p, n column width variation and gate structure variation. The performances under different structures are compared to select the best structure. Simulation results show that the performance of partial SOI device has broken the silicon limit. Finally, the detail process flow is proposed for the future fabrication.

Keywords: Superjunction devices, power devices, ideal silicon limit, interdiffusion, partial SOI superjunction LDMOS

## ACKNOWLEDGEMENT

I would like to express my sincere gratitude to my supervisor, Professor Yung C. Liang, for his precious guidance, patience and great assistance in my graduate research.

I would like to express my sincere gratitude to Professor Ganesh S. Samudra for his guidance in my simulation work.

I would like to appreciate my parents and brother for their love and encouragement in my research process.

I am grateful for all the friends in the power electronics lab for their help in many aspects.

## **DECLARATION OF ORIGINAL CONTRIBUTIONS**

The author would like to declare the original contributions based on the research as follows:

- 1. The practical superjunction performance under interdiffusion influence is investigated and described in chapter 3.

- 2. Simulation of partial oxide superjunction LDMOS structure is described in chapter 4.

## CONTENTS

| ACKNOWLEDGEMENT                       |                   | Ι                                                    |     |

|---------------------------------------|-------------------|------------------------------------------------------|-----|

| DECLARETION OF ORIGINAL CONTRIBUTIONS |                   | Ii                                                   |     |

| TABLE OF                              | TABLE OF CONTENTS |                                                      | Iii |

| SUMMARY                               | <b>,</b>          |                                                      | Vi  |

| LIST OF FI                            | GURES             | 5                                                    | Vii |

| LIST OF TA                            | BLES              |                                                      | Xi  |

| LIST OF SY                            | MBOL              | S                                                    | Xii |

| LIST OF AI                            | BBREV             | IATIONS                                              | Xv  |

|                                       |                   |                                                      |     |

| Chapter 1                             | Intro             | duction                                              | 1   |

| 1.1                                   | Histor            | y of superjunction device                            | 1   |

| 1.2                                   | Objec             | tives                                                | 5   |

| 1.3                                   | Thesis            | soutline                                             | 5   |

|                                       |                   |                                                      |     |

| Chapter 2                             | Supe              | rjunction (SJ) Device Physics and analyses           | 7   |

| 2.1                                   | Power             | MOSFETs basic                                        | 7   |

|                                       | 2.1.1             | Off-state analysis                                   | 8   |

|                                       | 2.1.2             | On-state analysis                                    | 11  |

| 2.2                                   | Super             | junction devices                                     | 13  |

|                                       | 2.2.1             | SJ characteristics at Off-state                      | 14  |

|                                       |                   | (a) Comparison of breakdown with conventional device | 14  |

|                                       |                   | (b) Derivation of breakdown equation for SJ device   | 15  |

|                                       | 2.2.2             | Specific on-resistance of SJ device                  | 19  |

| 2.3                                   | Curren            | nt state of superjunction device and technology      | 20  |

|           | 2.3.1 Vertical SJ devices                               | 21 |

|-----------|---------------------------------------------------------|----|

|           | 2.3.2 Lateral SJ devices                                | 22 |

| 2.4       | Summary                                                 | 25 |

|           |                                                         |    |

| Chapter 3 | Practical SJ performance under interdiffusion influence | 26 |

| 3.1       | Interdiffusion problem in current technology            | 26 |

| 3.2       | Practical SJ performance under given thermal cycles     | 28 |

|           | 3.2.1 Simulation methodology                            | 28 |

|           | 3.2.2 The realistic optimum SJ performance curves       | 34 |

|           | 3.2.3 The interdiffusion influence on breakdown voltage | 34 |

|           | 3.2.4 Practical concentration equation                  | 42 |

|           | 3.2.5 Practical SJ performance equation                 | 45 |

| 3.3       | Summary                                                 | 48 |

|           |                                                         |    |

| Chapter 4 | Partial SOI superjunction LDMOS                         | 49 |

| 4.1       | Review of partial SOI technology                        | 49 |

| 4.2       | Partial SOI superjunction LDMOS                         | 51 |

|           | 4.2.1 Structure                                         | 51 |

|           | 4.2.2 Off-state and On-state Operation                  | 52 |

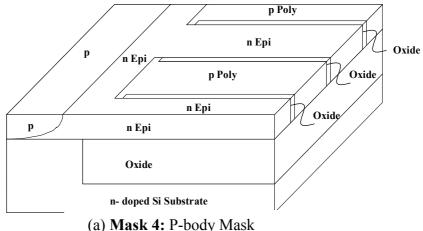

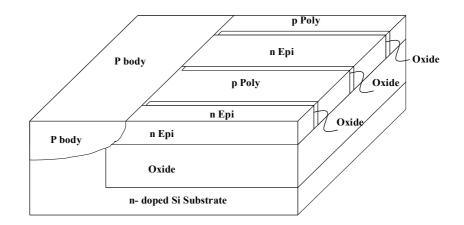

|           | 4.2.3 Process steps                                     | 53 |

| 4.3       | Gate variations of PSOI SJ LDMOS                        | 59 |

| 4.4       | Simulation of PSOI SJ LDMOS                             | 64 |

|           | 4.4.1 Process simulation                                | 65 |

|           | (a) P, n column width                                   | 67 |

|           | (b) P, n column concentration                           | 68 |

|           |                                                         |    |

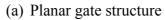

|                                                      | 4.4.2                                | Planar gate device simulation            | 74  |

|------------------------------------------------------|--------------------------------------|------------------------------------------|-----|

|                                                      |                                      | (a) Off-state simulation                 | 74  |

|                                                      |                                      | (b) On-state simulation                  | 77  |

|                                                      | 4.4.3                                | The 3-D simulation structures in DAVINCI | 79  |

|                                                      | 4.4.4                                | Summary of simulation results            | 81  |

| 4.5                                                  | Summa                                | ıry                                      | 87  |

|                                                      |                                      |                                          |     |

| Chapter 5                                            | Develo                               | opment of detailed process flow          | 88  |

| 5.1                                                  | Practica                             | al process requirement                   | 88  |

| 5.2                                                  | Detailed                             | d process flow for all gate structure    | 89  |

| 5.3                                                  | Summa                                | ıry                                      | 112 |

|                                                      |                                      |                                          |     |

| Chapter 6                                            | Conclu                               | usion                                    | 114 |

|                                                      |                                      |                                          |     |

| REFERENC                                             | ES                                   |                                          | 117 |

| APPENDIX A: DRIFT LENGTH CALCULATION OF CONVENTIONAL |                                      | 122                                      |     |

|                                                      | DEV                                  | ICE                                      |     |

| APPENDIX                                             | APPENDIX B: P, N COLUMN CACULATION 1 |                                          | 124 |

| APPENDIX                                             | C: LIST                              | OF PUBLICATIONS                          | 126 |

| APPENDIX                                             | APPENDIX D: LIST OF SIMULATION FILES |                                          | 127 |

### SUMMARY

The research work described in thesis is conducted around superjunction MOSFET devices. Two aspects of superjunction MOSFET devices are investigated through simulations. Firstly, the influence of interdiffusion on practical superjunction device performance is investigated. Based on extensive simulation results, the practical superjunction performance curves are arrived. In addition, some empirical equations such as concentration equation, specific on resistance equation are derived. The performance curves are compared with the theoretical superjunction curves to show the interdiffusion influence. The equations can give guidance in superjunction device design in practical conditions.

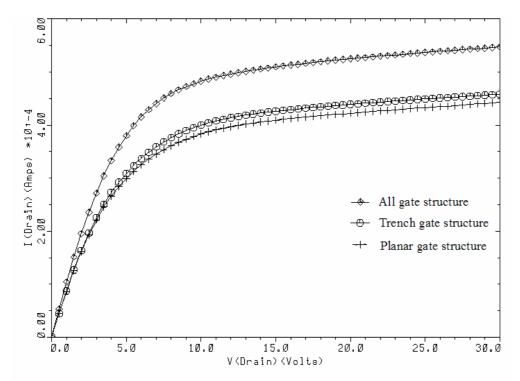

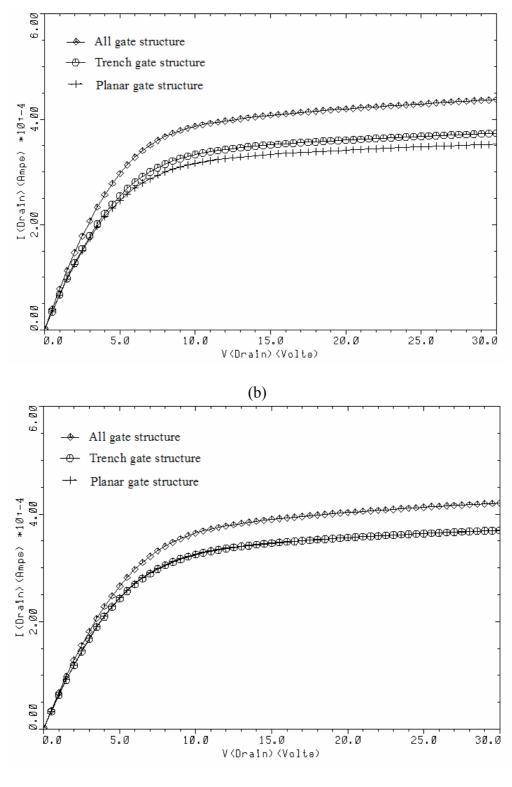

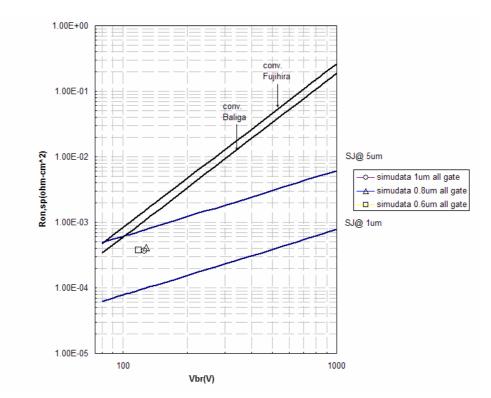

The second part of thesis presents results of detailed 3-D simulations of partial SOI superjunction LDMOS using DAVINCI, a 3-D simulator. The simulation work investigates the influence of the structure variations on the device performance. The structure variations include p, n column width variation and gate structure variation. The simulation results show that "all gate" structure with the smallest simulated n column width has the best performance compared with "trench gate" and "planar gate" structure. And the device performance has broken the silicon limit. To prepare for future fabrication, detailed process flow is proposed in the final part of thesis.

## **LIST OF FIGURES**

| Fig. 1.1: | Superjunction device structure extracted from [3]                                                                                                                                                                                           | 2  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.2: | Superjunction RMOS device extracted from ref.6 (a)RMOS structure (b) drift region with superjunction structure of RMOS structure                                                                                                            | 4  |

| Fig. 2.1: | Conventional power MOSFET structure (a) VDMOS structure(b)<br>LDMOS structure                                                                                                                                                               | 8  |

| Fig. 2.2: | Simplified Off-state structure and electrical field distribution                                                                                                                                                                            | 9  |

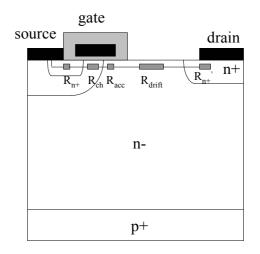

| Fig. 2.3: | Components of resistance within LDMOS structure on the current flow path                                                                                                                                                                    | 11 |

| Fig. 2.4: | Conventional diode structure compared with superjunction diode structure                                                                                                                                                                    | 13 |

| Fig. 2.5: | Electrical field profiles in (a) conventional diode and (b) superjunction diode For the SJ diode, the field is plotted along the outer edge of n column                                                                                     | 15 |

| Fig. 2.6: | Field profiles of $E_1$ along middle of n column AA' (solid line) and along middle of p column (dash line)                                                                                                                                  | 16 |

| Fig. 2.7: | Schematic electrical Field profile along middle of n column AA'                                                                                                                                                                             | 17 |

| Fig. 2.8: | Ideal $R_{on, sp}$ - $V_{BR}$ performance comparison between conventional (CV) structure and superjunction(SJ) devices                                                                                                                      | 20 |

| Fig. 2.9: | The schematic view of lateral 3-D RESURF MOSFET                                                                                                                                                                                             | 23 |

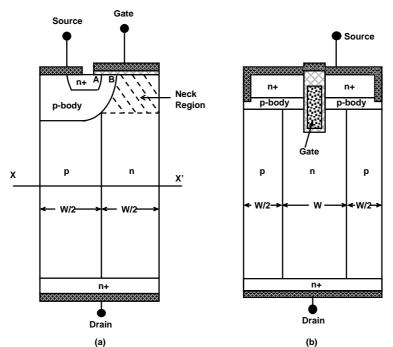

| Fig. 3.1: | The two vertical Superjunction power MOSFET structures (a) SJ DMOS structure (b) SJ UMOS structure                                                                                                                                          | 28 |

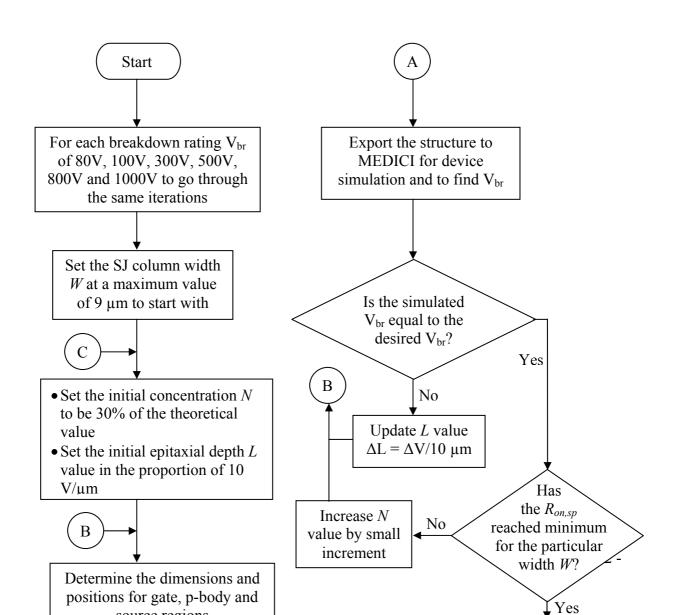

| Fig. 3.2: | Flow chart of simulation methodology                                                                                                                                                                                                        | 31 |

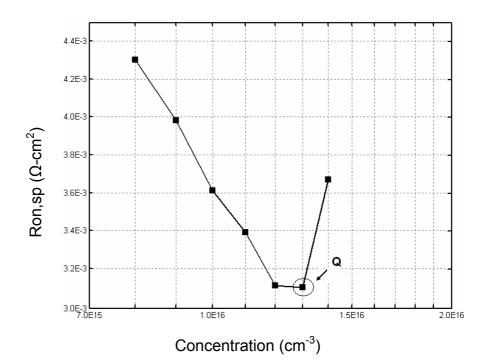

| Fig. 3.3: | The relationship between $R_{on,sp}$ and column doping concentration<br>at the given breakdown voltage (300V) and column width<br>(1.7µm). The optimum concentration for column width of 1.7 µm<br>is $1.3 \times 10^{16}$ cm <sup>-3</sup> | 32 |

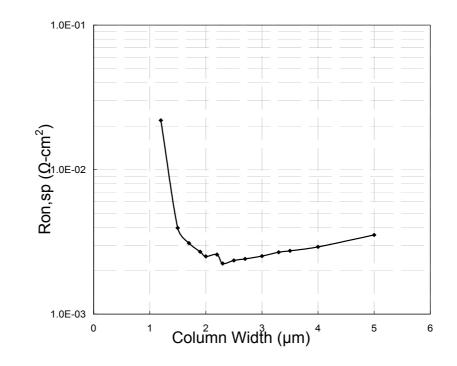

| Fig. 3.4: | The relationship between $R_{on,sp}$ and the column width at given<br>breakdown voltage (300V). The optimal $R_{on,sp}$ at 300V is<br>$2.24 \times 10^{-3} \ \Omega$ -cm <sup>2</sup> at column width W = 2.3 µm                            | 33 |

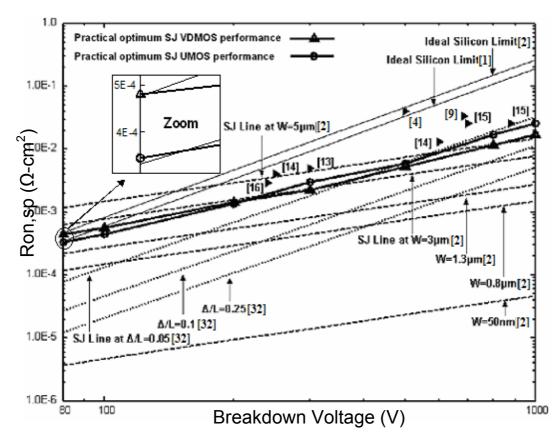

- Fig. 3.5: The simulated practical optimum SJ performance curves (SJ 35 DMOS and SJ UMOS) with dopant inter-diffusion included compared with the ideal SJ performance lines and the ideal silicon limit curves. A "zoom in" figure is added to show clearly the curves near 80V

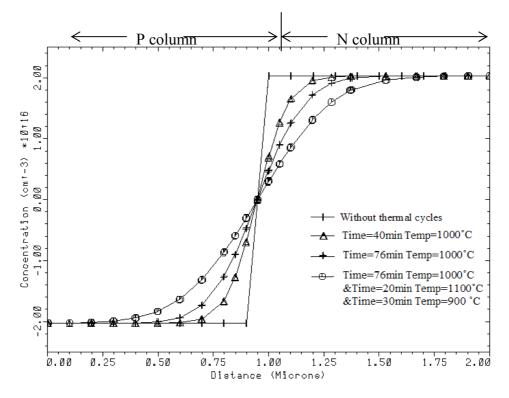

- Fig. 3.6: The doping profiles changing from ideal case without thermal 36 budget to the real case with full thermal budget. The thermal budgets for each doping profile are labelled in the figure. The simulated device is SJ VDMOS with column width of  $2\mu m$  and ideal concentration of  $2.03 \times 10^{16}$  /cm<sup>3</sup>. The doping profiles are cut along line X-X' in Fig. 3.1(a)

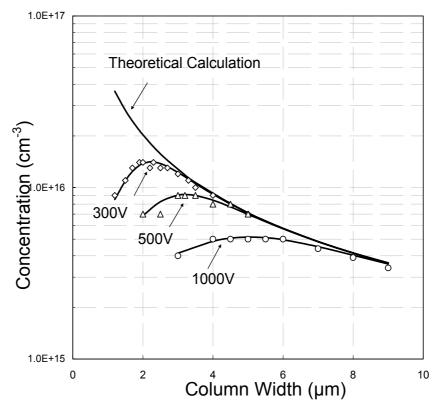

- Fig. 3.7: The relationships between the simulated optimal concentration 37 and column width at 300 V, 500 V and 1000 V along with and the ideal concentration curve which is calculated using equation  $N = 1.2 \times 10^{12} \times W^{-8/7}$  are shown. For each breakdown voltage, the void markers represent the simulated data and the solid lines are the fitting curves calculated using the empirical equation (3.1)

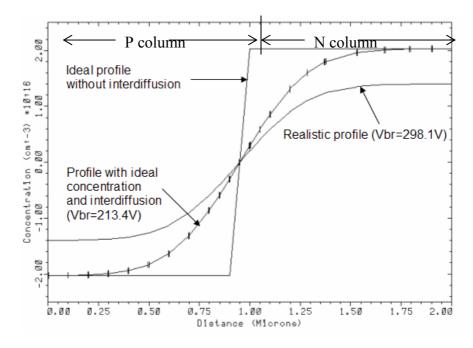

- Fig. 3.8: The ideal profile without interdiffusion and the profile with ideal 38 concentration and interdiffusion are compared to the realistic profile. The three profiles are cut along line X-X' in Fig. 3.1(a). The data used are the ideal concentration  $(2.03 \times 10^{16} / \text{cm}^3)$  and practical concentration  $(1.4 \times 10^{16} / \text{cm}^3)$  for 300V device with the column width of 2µm, which can be found from Fig. 3.7. The breakdown voltages for the two cases with interdiffusion are also labeled.

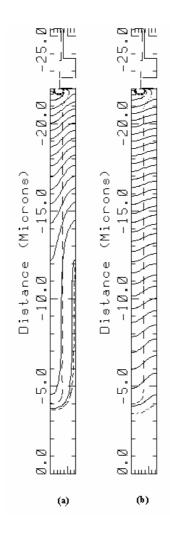

- Fig. 3.9: For both structures, the solid lines are the potential contours and 39 the dash lines are the depletion boundaries. Both structures have the same column width of 1.5  $\mu$ m and epitaxial depth 22 $\mu$ m, only the column concentrations are different, namely (a) the theoretical concentration of 2.82 ×10<sup>16</sup>/cm<sup>3</sup> with a breakdown voltage of 149.53V, and (b) the optimal concentration of 1.1 ×10<sup>16</sup>/cm<sup>3</sup> with a breakdown voltage of 301.06V.

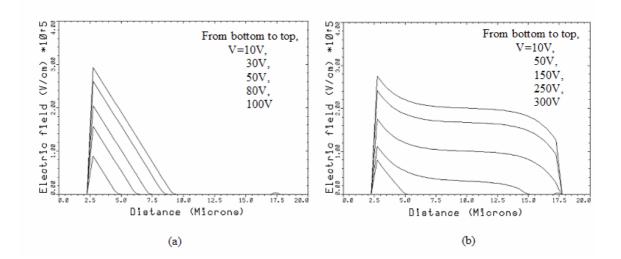

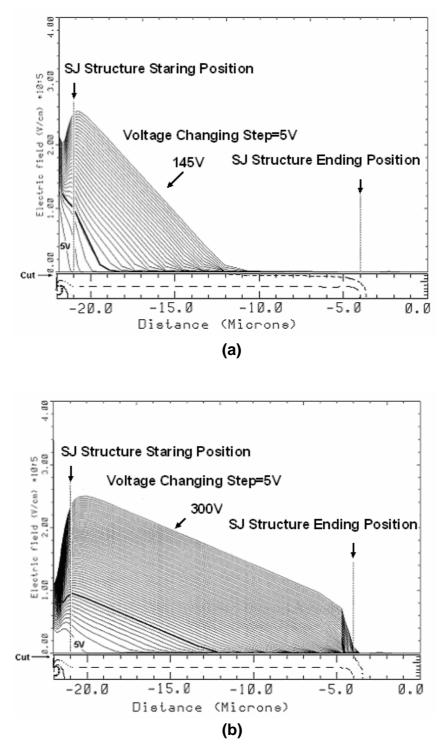

- Fig. 3.10: The electric field profiles within n-column in (a) and (b) are 40 corresponding to the structures in Fig. 3.7 (a) and (b). The cuts are at the centre of n-column with the applied blocking voltage changing in a step of 5V to the respective breakdown voltages. The E-field profile at which the p-column has just been fully depleted is marked by a darker line.

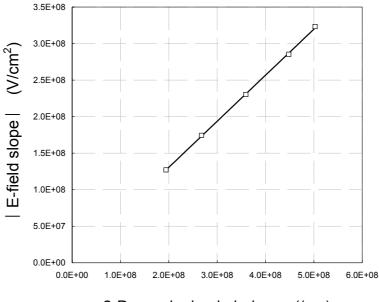

- Fig. 3.11: The relationship between 2-D p-n doping integral imbalance and 41 the E-field slopes

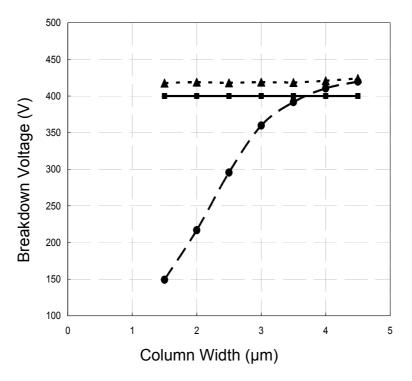

- Fig. 3.12: The relationships between breakdown voltage and column widths 46 for two groups of devices. The two groups have the same drift region length of 27μm and the same set of column widths. One

group use the theoretical concentration, whose breakdown voltages are shown by dash lines and circles. The other group use the practical concentration, whose breakdown voltages are shown in dotted line and triangles. The expected breakdown voltages are shown in solid line and rectangles.

- Fig. 3.13: Practical SJ performance curves under the thermal cycles given 47 by table 3.1 at fixed column widths 1µm, 3µm and 5µm

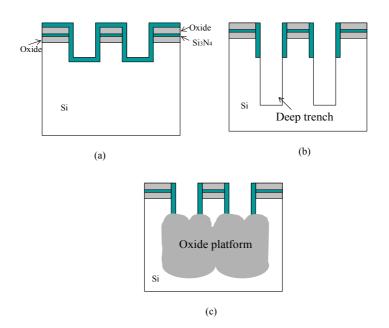

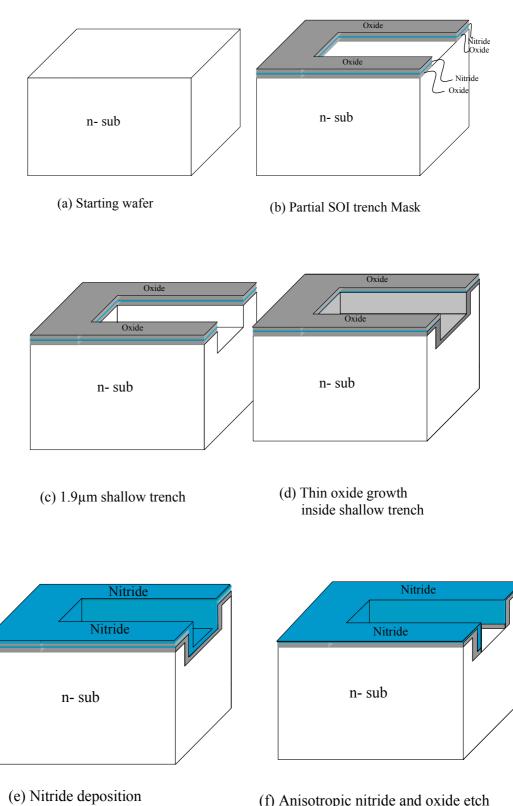

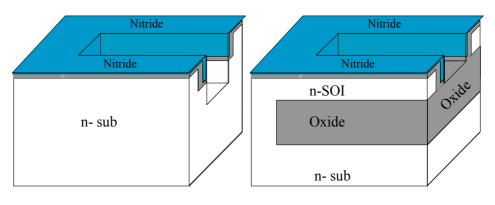

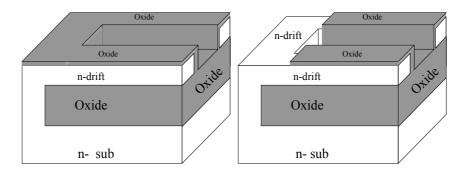

- Fig. 4.1: Key process steps of the partial oxide platform formation (a) 50 Shallow trench etch and oxidation mask formation (b) Deep trench formation (c) Oxide platform formation

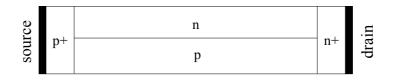

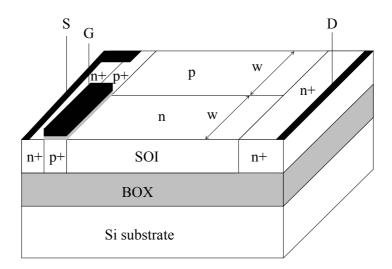

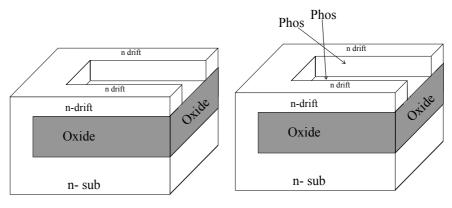

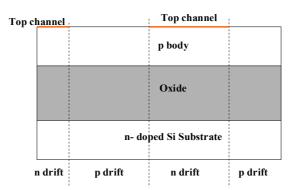

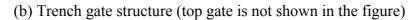

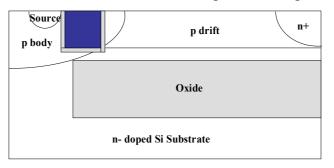

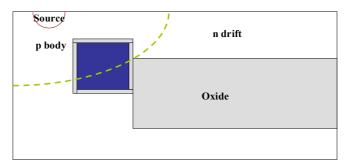

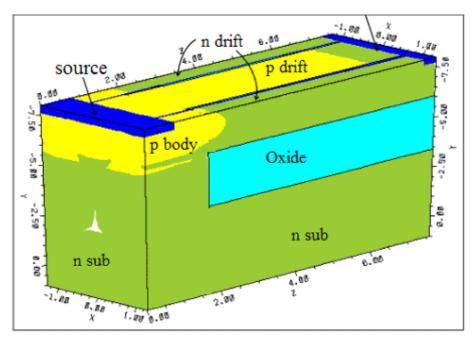

| Fig. 4.2: | Schematic structures of PSOI SJ LDMOS | 51 |

|-----------|---------------------------------------|----|

|           |                                       |    |

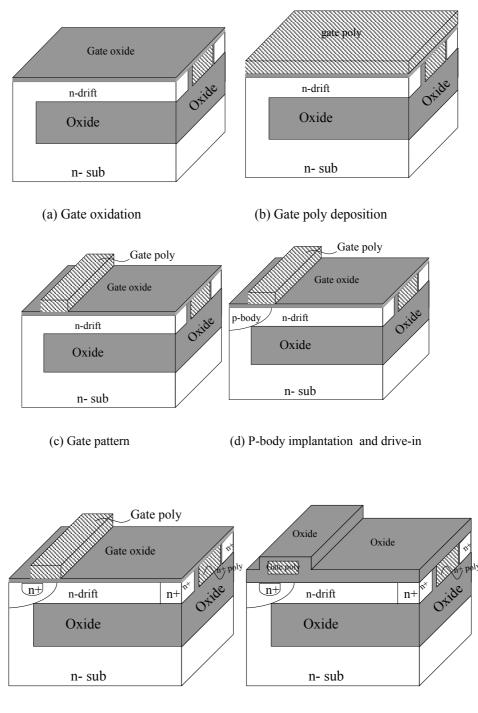

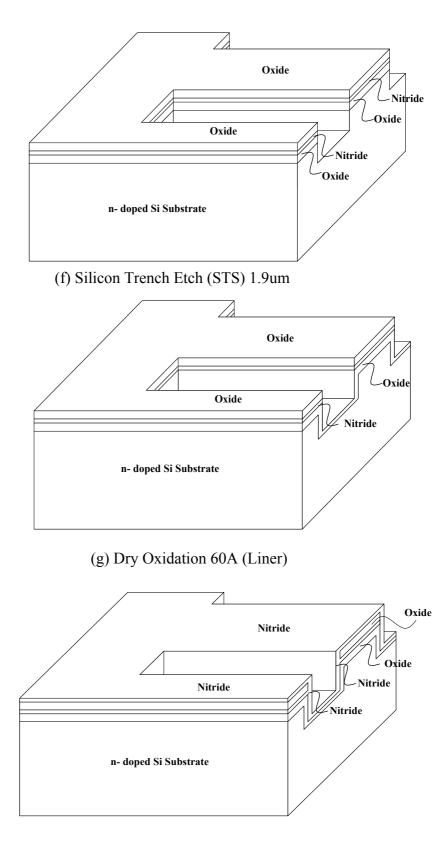

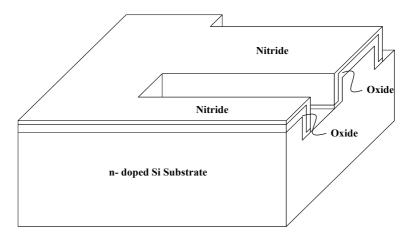

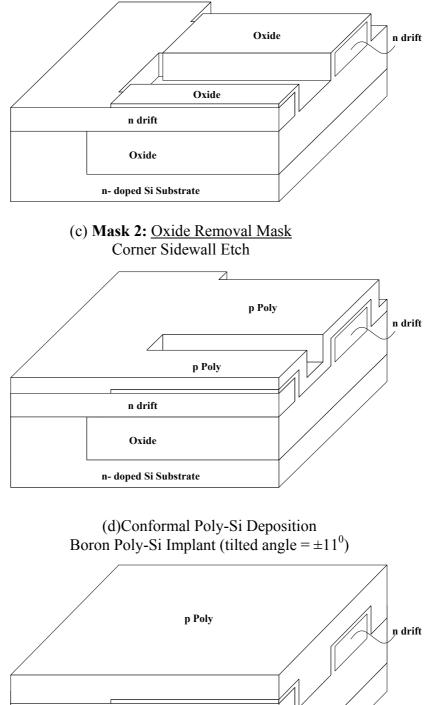

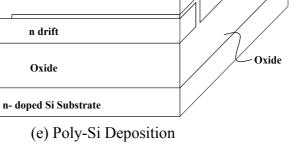

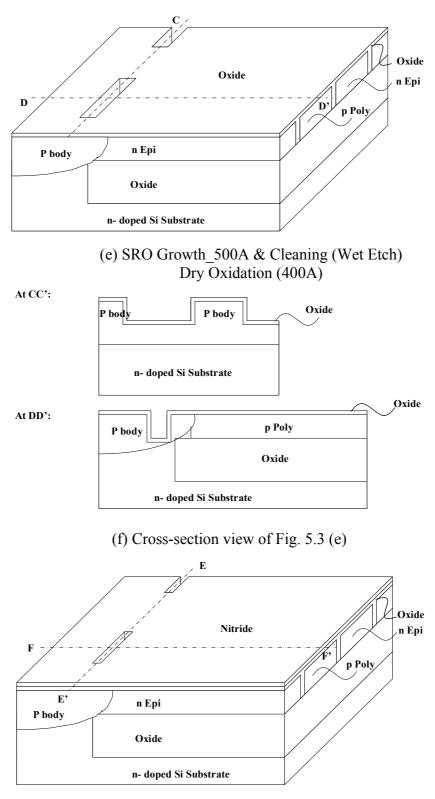

- Fig. 4.3:Partial oxide formation process55

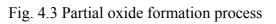

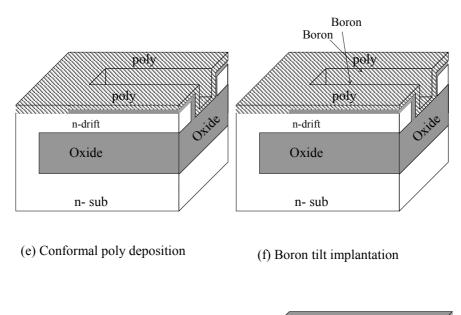

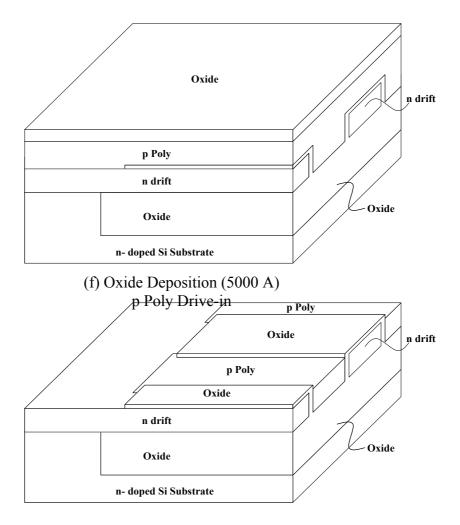

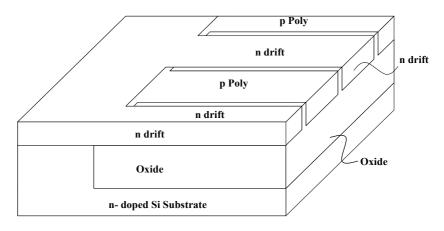

- Fig. 4.4:P, n column formation process56

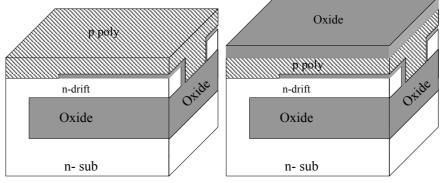

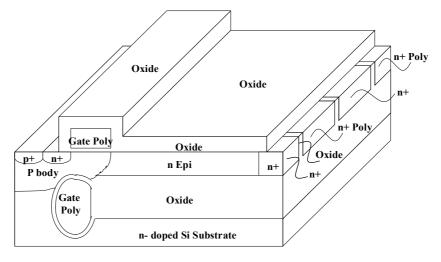

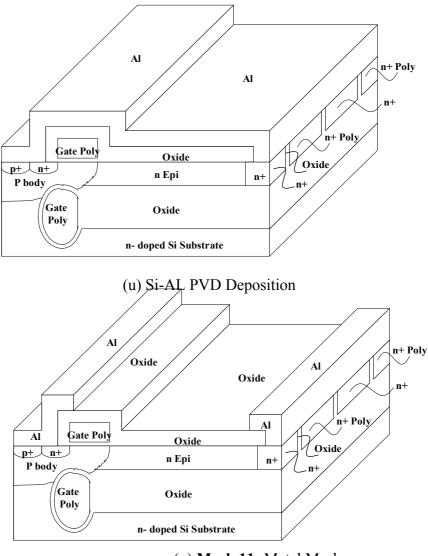

- Fig. 4.5:MOSFET structure formation process58

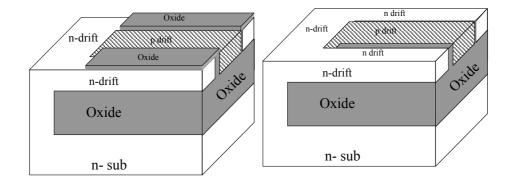

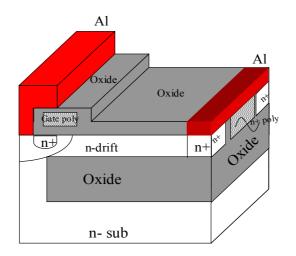

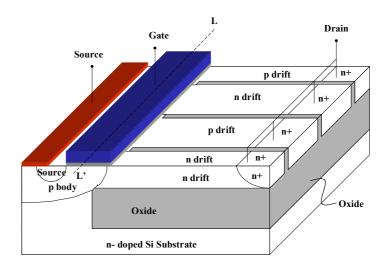

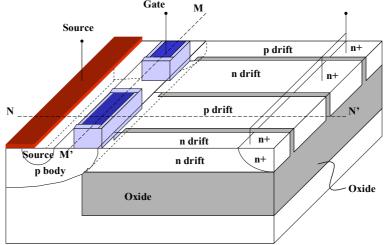

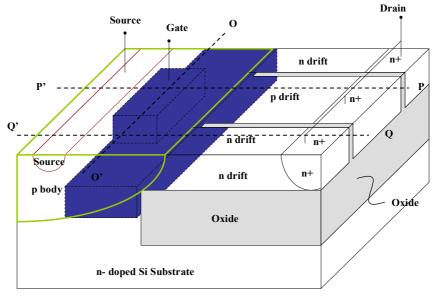

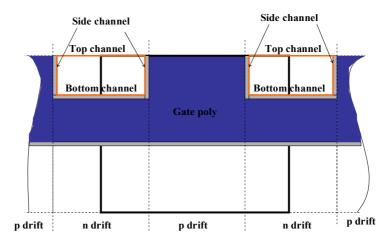

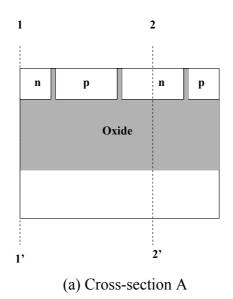

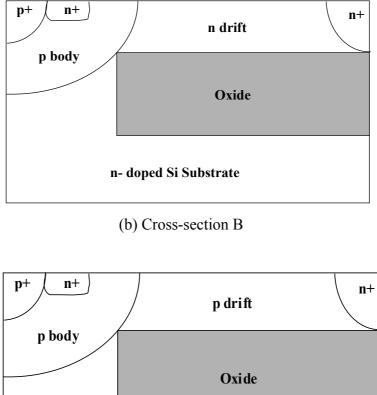

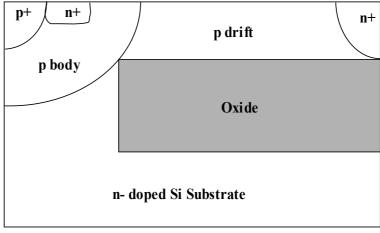

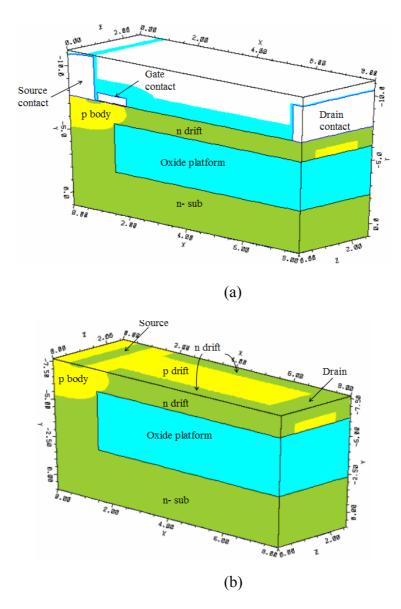

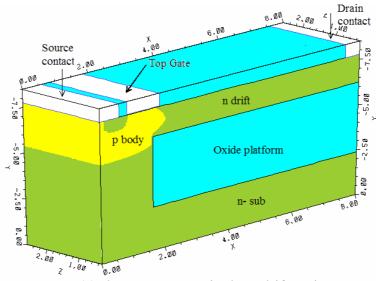

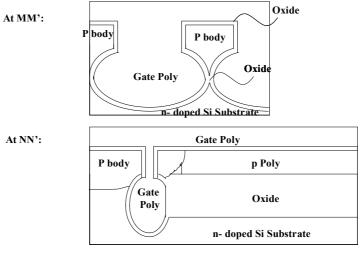

- Fig. 4.6: The three kinds of gate structure and cross-section views (a) 62

Planar gate structure (a1) the cross-section view of planar gate structure cut along L-L' (b) Trench gate structure (top gate is not shown in the figure) (b1) the cross-section view of trench gate cut along M-M' (b2) the cross-section view of trench gate cut along N-N' (c) All gate structure (top gate and gate oxide are not shown in the structure) (c1) the cross-section view of all gate cut along P-P'(c3) the cross-section view of all gate cut along P-P'

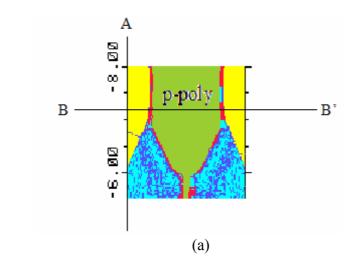

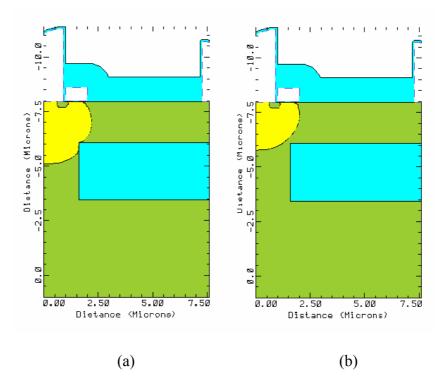

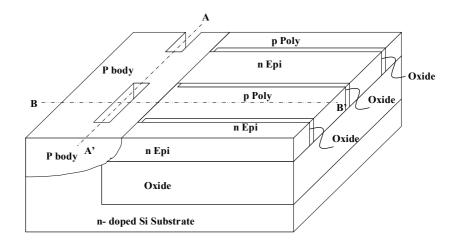

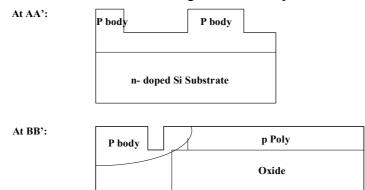

- Fig. 4.7: Cross-sections cut along (a) line A-A' (b) line B-B' and (c) line 66 C-C'

- Fig. 4.8: Simulation result of cross-section A 67

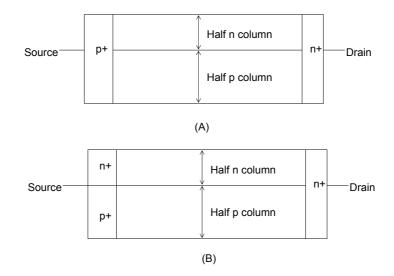

- Fig. 4.9: 2-D simulation structure (A) Off-state simulation structure (B) 69 On- state simulation structure

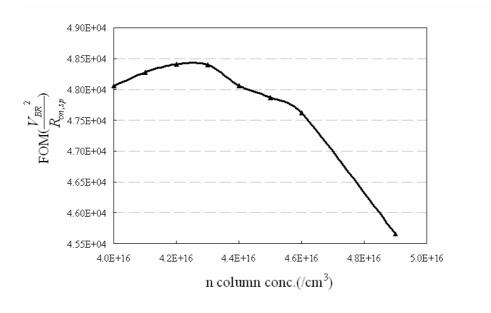

- Fig. 4.10: The relationship between figure of merit and n column 70 concentration with the drift length fixed

- Fig. 4.11: (a) p,n column structure extracted from Fig. 4.7. (b) n column 71 doping profile along the line A-A' in (a). (c) p, n column doping profile along the line B-B' in (a). The targeted n column concentration is 4.2E16 cm<sup>-3</sup>, and the targeted p column concentration is 1.87E16 cm<sup>-3</sup>

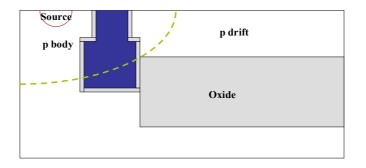

- Fig. 4.12: (a) theoretically required p-body (b) practically achievable p- 73 body

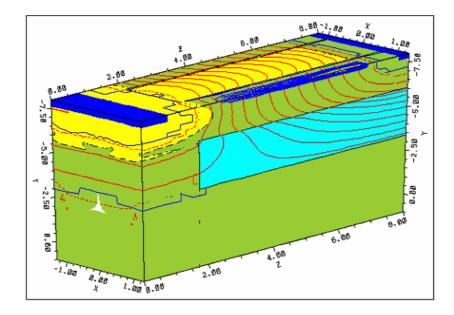

- Fig. 4.13: (a) Schematic view of Off-state structure and (b) Off-state 75 structure in Davinci

- Fig. 4.14: The Off-state structure at breakdown. The breakdown voltage is 76 126V. The potential lines are red solid lines at 10V interval. The impact ionization contours are blue solid lines. The depletion boundary lines are red dashed lines.

- Fig. 4.15: The On-state structure formed by importing cross-section B to 78 DAVINCI (a) the whole structure (b) structure cut along certain Y plane to show p, n columns.

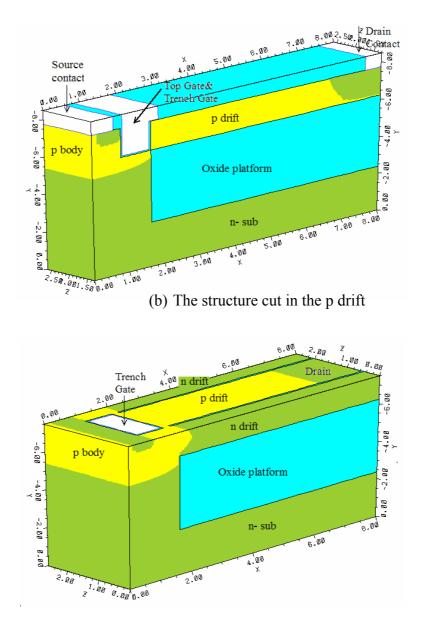

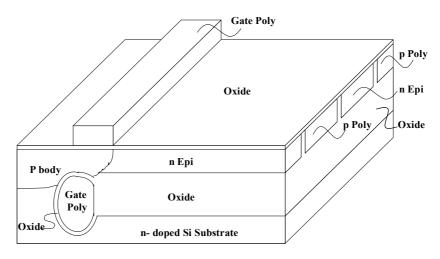

- Fig. 4.16: The On-state simulation structure of the trench gate device (a) the 80 structure cut in the n drift region (b) the structure cut in the p drift region (c) the structure cut at the top

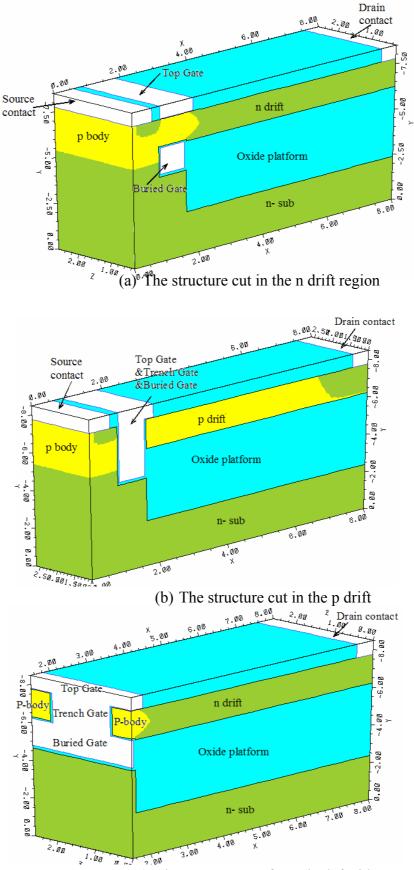

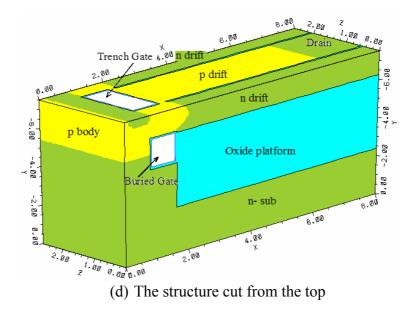

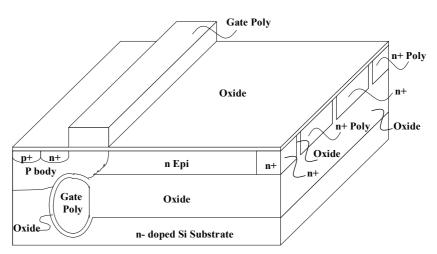

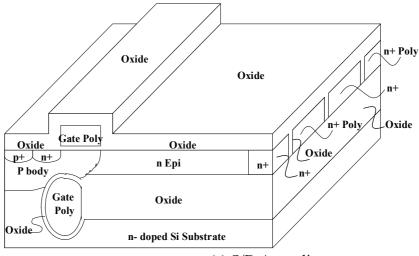

- Fig. 4.17: The On-state simulation structure of the all gate device (a) the 81 structure cut in the n drift region (b) the structure cut in the p drift region (c) the structure cut from the left side (d) the structure cut from the top

- Fig. 4.18: The drain curves at gate voltage of 20V for three kinds of gate 83 structures (a) for n column width of  $1\mu m$  (b) for n column width of  $0.8\mu m$  (c) for n column width of  $0.6\mu m$ .

- Fig. 4.19: The performance data of the all gate devices with different n 86 column width  $0.6\mu m$ ,  $0.8\mu m$  and  $1\mu m$  compared with the conventional silicon limit lines and ideal SJ device lines at  $5\mu m$  and  $1\mu m$ . The two SJ lines are calculated by equation (2.21).

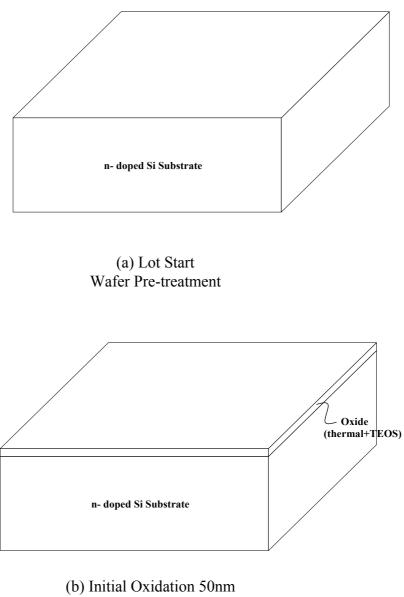

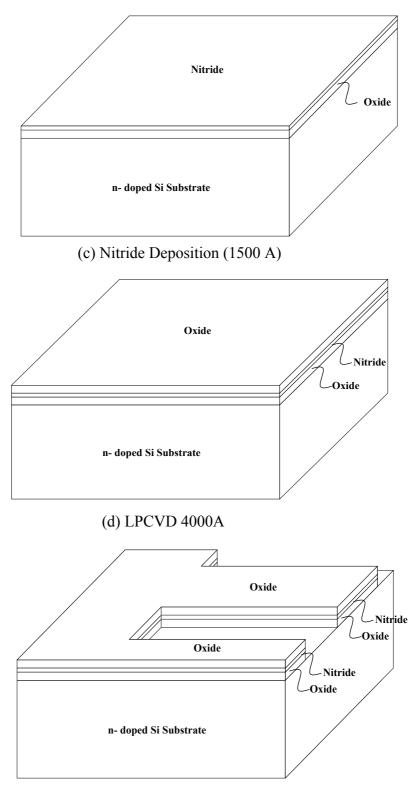

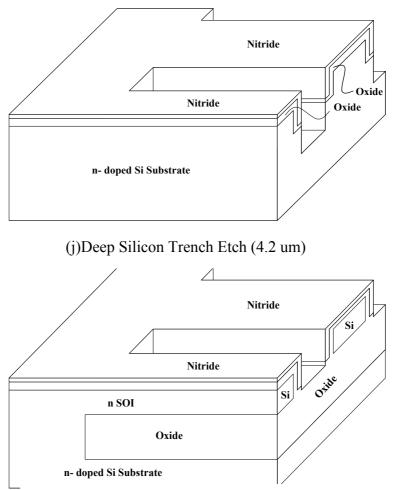

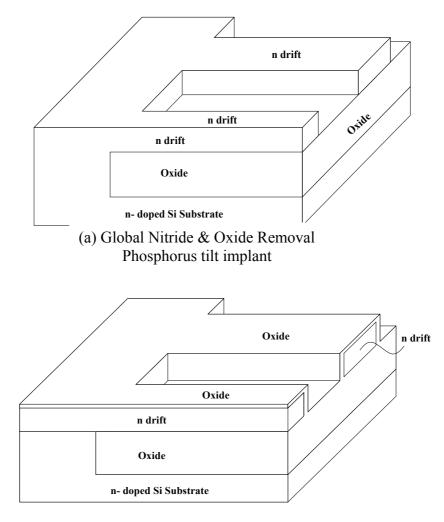

| Fig. 5.1: | Partial SOI formation process                                 | 92  |

|-----------|---------------------------------------------------------------|-----|

| Fig. 5.2: | P, n column formation process                                 | 98  |

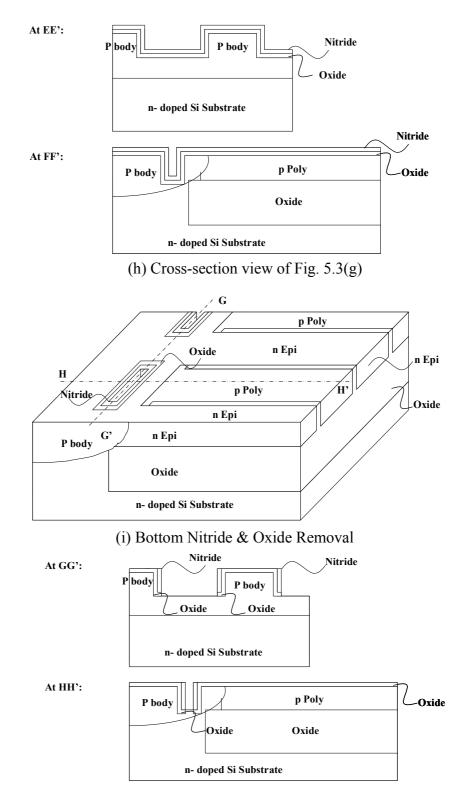

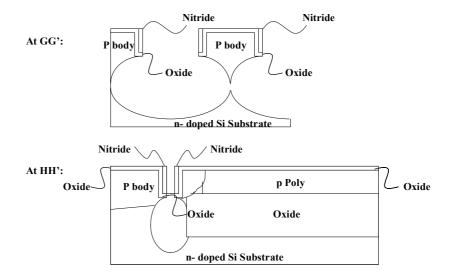

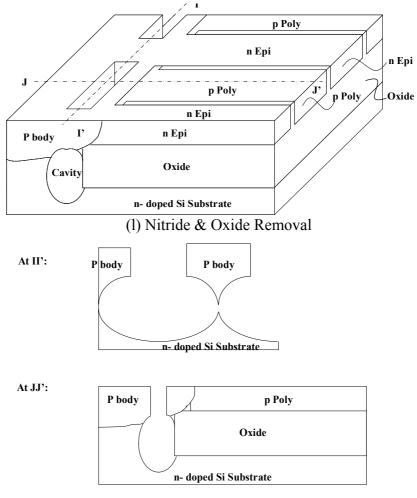

| Fig. 5.3: | Multi-gate formation process                                  | 112 |

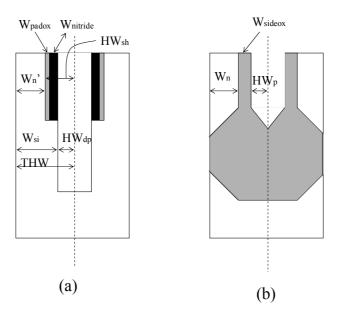

| Fig. B.1  | Schematic structures for calculation of p, n column width (a) | 124 |

Fig. B.1 Schematic structures for calculation of p, n column width (a) 12 before oxidation (b) after oxidation

## LIST OF TABLES

| Table 3.1: | Thermal cycles in MOSFET device fabrication and in process simulation                                               | 30  |

|------------|---------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2: | The calculated practical concentration and the theoretical concentration for device breakdown rating of 400V        | 45  |

| Table 4.1: | The parameters and breakdown voltage of the device shown in Fig. 4.13                                               | 76  |

| Table 4.2: | The on-state performance data of the device with n column width of $1 \mu m$                                        | 79  |

| Table 4.3: | The comparison of on-state performance data of devices with different gate variations and different n column widths | 85  |

| Table B.1  | Index Table for variables used                                                                                      | 124 |

## LIST OF SYMBOLS

| α                         | Ionization coefficient                            |

|---------------------------|---------------------------------------------------|

| L                         | Depletion length(µm)                              |

| $N_{D}$                   | Drift region concentration( $cm^{-3}$ )           |

| $V_{BR}$ or $V_{br}$      | Breakdown voltage(V)                              |

| $\mathcal{E}_{S}$         | Permittivity of Silicon                           |

| q                         | Elementary charge(C)                              |

| Ε                         | Electric field $(V/cm)$                           |

| Ron                       | On resistance( $\Omega$ )                         |

| $R_{n+}$                  | Source resistance( $\Omega$ )                     |

| R <sub>ch</sub>           | Channel resistance( $\Omega$ )                    |

| $R_{acc}$                 | Accumulation layer resistance( $\Omega$ )         |

| <i>R</i> <sub>drifi</sub> | Drift region resistance( $\Omega$ )               |

| $R_{n+}$                  | Drain resistance ( $\Omega$ )                     |

| R <sub>on,sp</sub>        | Specific on-resistance ( $\Omega \cdot cm^{-2}$ ) |

| $l_{drift}$               | Length of drift region (µm)                       |

| μ                         | Electron mobility( $cm^2/V \cdot s$ )             |

| А                         | Cross-sectional area of current flow $(cm^2)$     |

| $N_A$                     | Acceptor doping concentration( $cm^{-3}$ )        |

| $N_D$                     | Donor doping concentration( $cm^{-3}$ )           |

| $E_y$                     | The y component of the electrical field $(V/cm)$  |

| $E_0$                     | Constant component of $E_y(V/cm)$                 |

| $E_{I}$                   | $E_y$ - $E_0(V/cm)$                               |

|                           |                                                   |

| $V_B$                         | The applied reverse voltage(V)                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------|

| $E_{1n}$                      | The maximum value of $E_1$ along the middle of n column( $V/cm$ )                             |

| $E_{1p}$                      | The maximum value of $E_1$ along the middle of p column( $V/cm$ )                             |

| V <sub>lateral</sub><br>merge | Lateral merge voltage of p, n column width(V)                                                 |

| $N_{p^+}$                     | Concentration in p+ region( $cm^{-3}$ )                                                       |

| $X_n$                         | The depletion depth in n column at $V_{lateral}(\mu m)_{merge}$                               |

| $E_C$                         | The critical electrical field $(V/cm)$                                                        |

| $E_{max}$                     | Maximum electric field(V/cm)                                                                  |

| W                             | P, n column width(µm)                                                                         |

| $E_A$                         | Electrical field at $p+/n$ junction ( $V/cm$ )                                                |

| $W_m$                         | The column width at Merge point of practical concentration and ideal concentration( $\mu m$ ) |

| $W_{d}$                       | Depletion width(µm)                                                                           |

| W <sub>padox</sub>            | Pad oxide thickness(µm)                                                                       |

| W <sub>nitride</sub>          | Nitride thickness(µm)                                                                         |

| Wsideox                       | Side wall oxide thickness(µm)                                                                 |

| W <sub>si</sub>               | Deep trench silicon thickness(µm)                                                             |

| THW                           | Half width of total structure(µm)                                                             |

| HW <sub>n</sub>               | Half width of n column before oxidation(µm)                                                   |

| $HW_n$                        | Half width of n column after oxidation(µm)                                                    |

| $HW_p$                        | Half width p column(µm)                                                                       |

| $HW_{dp}$                     | Half width of deep trench(µm)                                                                 |

| $HW_{sh}$                     | Half width of shallow trench(µm)                                                              |

|                               |                                                                                               |

## LIST OF ABBREVIATIONS

- MOS Metal-Oxide-Semiconductor

- MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

- DMOS Double-diffusion MOS

- LDMOS Lateral DMOS

- VDMOS Vertical DMOS

- UMOS U-shaped trench Gate MOS

- SOI Silicon on Insulator

- SJ Superjunction

- PSOI Partial SOI

- BOX Buried oxide

## **Chapter 1**

### Introduction

Power devices are mainly used as power switches in various systems such as high voltage DC transmission, motor drive, transportation, induction heating and communications [1].

Power MOSFETs, which are based on the original field effect transistors introduced in 70s, are the most popular power device in today's era. The power MOSFET is a unipolar, majority carrier and voltage controlled transistor. It has the benefit of fast switching and simple gate drive circuitry. Therefore, it is suitable for high frequency integrated circuits.

Unfortunately, power MOSFETs have one major drawback — high on-state conduction loss. The device doping is limited by the requirement to support high breakdown voltage. The trade-off relationship between specific on-state resistance  $(R_{on,sp})$  and breakdown voltage  $(V_{br})$  has been defined as "silicon limit"[1][2], which shows a more than square relationship  $(R_{on,sp} \sim V_{br}^{2.5})$ . The relationship indicates that the on-resistance of power MOSFETs increases rapidly with the increase of breakdown voltage, which makes them only suitable for low voltage (<200V) applications.

A lot of effort has been put into the improvement of the performance of MOSFETs. Earlier effort can only make the performance of power MOSFETs as close as possible to the "silicon limit". Recently, some novel ideas have been proposed to overcome the "silicon limit" [3-11]. These ideas are based on modification of the one-type doped drift region to add an opposite doped region to it. This kind of structure is defined as superjunction structure [2]. Devices based on superjunction structure have been fabricated and made commercially available [9].

#### **1.1 History of superjunction device**

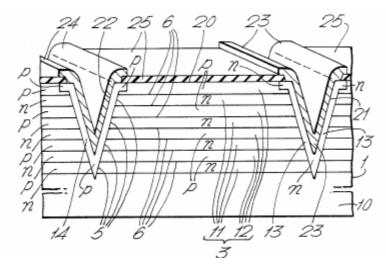

The earliest superjunction concept appears at D.J.Coe's patent [3]. The superjunction device structure is shown in fig. 1.1[3]. The superjunction structure appears at the drift region, region 3. Region 3 comprises of first regions 11 of a first conductivity type (n-type) and second regions 12 of the opposite, second conductive type (p-type). Regions 11 are interleaved with regions 12. The existence of p-type region helps the depletion of the whole drift region. Thus, higher breakdown voltage can be achieved by this kind of structure.

Fig. 1.1 Superjunction device structure extracted from [3]

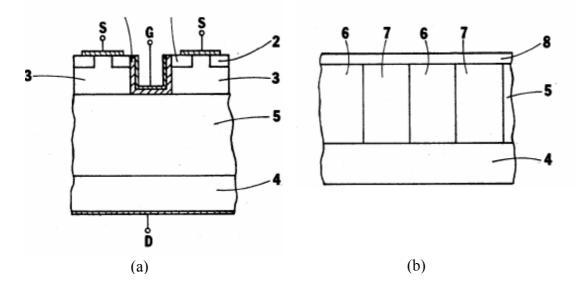

Later on, the development of the concept is divided into two groups. One group is similar to the original concept to use the buried opposite doped region or floating opposite doped regions [4, 5]. The other group uses the alternatively stacked p, n region or multi-RESURF superjunction region as the drift region [6-11]. This kind of structure is shown in Fig. 1.2. Fig. 1.2(a) shows a vertical RMOS structure. The popular name for RMOS is UMOS. The drift region is region 5. Fig. 1.2(b) shows the drift region of the RMOS structure, which comprises of oppositely doped region 6(n-type) and region 7(p-type). Region 6 and region 7 are alternatively stacked; each n-type region is surrounded by the neighbor p-type regions and vice visa. Thus, when the drift region is fully depleted, the n-regions and the p-regions contribute charges with opposite signs, and the fields introduced by them cancel each other out for most part. This is called the charge compensation principle. Actually, the second group concept is widely recognized as the superjunction concept because the charge compensation principle is used in the device design, which is firstly proposed by X.-B. Chen's patent [6].

Although the devices discussed in these patents and papers are actually superjunction devices, the name of "superjunction" is firstly prominently proposed by T. Fujihira [2]. In this paper, a summary of various superjunction device structures are given and the general equation for superjunction device is derived for the first time. Later, other papers give some different superjunction equations. All these equations show a linear or slightly more than linear relationship between  $R_{on,sp}$  and  $V_{br}$  [4][11]. Compared with the more than square relationship in "silicon limit", the performance of superjunction device has overcome the "silicon limit".

Fig. 1.2 Superjunction RMOS device extracted from ref.6 (a)RMOS structure (b) drift region with superjunction structure of RMOS structure

In history, the development of the two kinds of superjunction devices – vertical devices and lateral devices is not parallel. Till now, most of the developed superjunction devices are vertical devices. Vertical superjunction devices are realized by various fabrication technologies such as COOLMOS<sup>TM</sup> technology, STM, VTR-DMOS and PFVDMOS etc.[9][12-16]. Due to the thermal process involved in fabrication, the dopant - interdiffusion problem is unavoidable in most of the fabrication technology. The interdiffusion between the p, n column of superjunction structure will affect the device performance. One part of the research work is to investigate the interdiffusion influence on practical superjunction device performance.

Recently, the superjunction concept is also used on lateral devices [11][17-22]. Some new concepts such as unbalanced superjunction structure, double gate, and SOI structure are proposed to improve the lateral superjunction device performance. The voltages of these lateral devices are in medium range - 120V or 150V. The research of the lateral superjunction devices is still on simulation stage [11][17-22]. The few fabricated devices are on bulk wafer [22].

In this project, the performance of a partial SOI superjunction LDMOS at breakdown rating 120V is investigated through extensive simulation. Compared with previous lateral device, the device uses partial SOI technology and multi-gate structure to improve its performance. The fabrication probability of the device is also explored.

### **1.2 Objectives**

This research is,

- (a) To gain a thorough understanding of superjunction Theory;

- (b) To investigate the practical superjunction performance under the interdiffusion influence;

- (c) To simulate the performance of partial SOI superjunction LDMOS device at breakdown rating of 120V and develop a process flow based on current technology.

#### **1.3 Thesis Outline**

The thesis covers all the research work during the candidature, which include superjunction theory exploration, practical superjunction performance simulation, partial SOI superjunction LDMOS performance simulation and fabrication exploration.

The thesis is divided into six chapters:

**Chapter 1** – The pros and cons of power MOSFETs are presented followed by the history of superjunction devices. The scope of the research work is presented afterwards.

**Chapter 2** – The superjunction theory is reviewed and the superjunction device performance equation is derived based on the theory. The present state of the superjunction device development is provided. This chapter provides the theoretical basis of the whole research work.

Chapter 3 – Since the interdiffusion problem is unavoidable in the fabrication technology, the practical superjunction performance under interdiffusion influence is investigated based on extensive simulation work. The research work summarized in this chapter can give guidance for superjunction device design in practical condition.

**Chapter 4** – The extensive simulation work of partial SOI superjunction LDMOS is summarized in this chapter. The device structure and operation is discussed in detail. Based on the proposed process steps, the simulation work is done to test its performance. The further improvement of device performance by changing gate structures are also discussed and tested by simulation.

**Chapter 5** – The detailed process flow for all gate partial SOI superjunction LDMOS is proposed in this chapter. The process flow is illustrated by 3-D figures with detailed explanation.

**Chapter 6** – This chapter gives the summary of the whole thesis.

### Chapter 2

## Superjunction (SJ) device theory and analyses

It has been mentioned in last chapter that the performance of conventional power MOSFETs is constrained by "silicon limit" [1] [2]. Many efforts have been put into improving the conventional device structure. Finally, the invention of superjunction structure greatly improved the device performance [3-11]. In this chapter, the analysis of conventional device is firstly provided with the emphasis on "silicon limit". Then, performance of superjunction device, which aims to break "silicon limit", is discussed in detail. Finally, the realization of superjunction structure in various devices is reviewed, and problems encountered are summarized.

#### 2.1 **Power MOSFETs Basics**

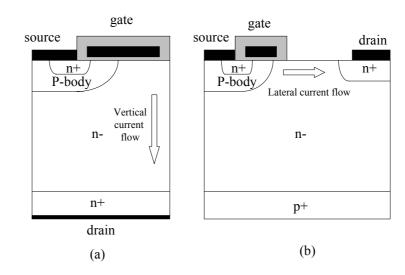

The most popular structure of power MOSFETs is the DMOSFET structure shown in Fig. 2.1[1]. The device name is derived from the channel formation process, *double-diffusion* process. The difference between the vertical DMOSFET (VDMOS) and the lateral DMOSFET (LDMOS) is the current flow direction, which is also shown in Fig. 2.1.

As power switch in most of power applications, power MOSFET operates on two states - Off-state and On-state. By applying different control voltage on gate terminal, power MOSFET easily shifts between the two states. Using n-channel MOSFET as example, when the applied gate voltage is below threshold voltage, the device is in Off-state. As a switch, it is "open". Thus, in the Off-state, there will be a small leakage current through the device. If the applied voltage between drain and source is too high, the device will breakdown and a large leakage current will pass through it. So, the blocking voltage of the device must be high enough for specific application. In the other case, when applied gate voltage is above the threshold voltage, an inverse channel will form below the gate for the device to conduct current. This is the Onstate of power MOSFET and corresponding to the "close" state of a switch. In this state, forward current will pass through the power MOSFET and the voltage falling on it should be very small. The conduction loss of power MOSFET is decided by the resistance along the current path.

Fig. 2.1 Conventional power MOSFET structure (a) VDMOS structure (b) LDMOS structure

#### 2.1.1 Off-state analysis

The most important parameter for Off-state is the breakdown voltage. During the Off-state operation, the applied reverse voltage is mainly supported by the junction between p-body an n-drift region for both VDMOS and LDMOS. Therefore, the DMOSFET structure can be simplified as a parallel-plane, abrupt p, n junction. The simplified structure, together with electrical field distribution is shown in Fig. 2.2.

Fig. 2.2 Simplified Off-state structure and electrical field distribution

The applied reverse voltage is primarily distributed over the depletion region from x=0 to x=L. When the free carriers travel through the depletion region, they gain energy from the accelerating electrical field. They also collided with atoms in the lattice. When the applied voltage is increased, the electrical field in the depletion region increases and the free carriers will gain higher energy. If the free carriers gain enough high energy, they will ionize the lattice atoms during collide process. This is called impact ionization. The electron-hole pairs produced by impact ionization are also accelerated by the same electrical field to ionize other lattice atoms. So, the impact ionization is a multiplicative phenomenon that produces a cascade of mobile carriers. The device is considered to undergo avalanche breakdown when the rate of impact ionization approaches infinity. The avalanche breakdown can be identified by the condition that the ionization integral equals to one [1]. This condition can be expressed by:

$$\int_0^L \alpha \cdot dx = 1$$

(2.1)

where  $\alpha$  is the ionization coefficient.

The ionization coefficient can be approximately expressed by electrical field E:

$$\alpha = 1.8 \times 10^{-35} \cdot E^{7}$$

(2.2)

To find out the relationship between breakdown voltage and various parameters of the device, Poisson's equation is solved. The equation in n- region is given by:

$$\frac{d^2 V}{dx^2} = -\frac{dE}{dx} = -\frac{Q(x)}{\varepsilon_s} = -\frac{qN_D}{\varepsilon_s}$$

(2.3)

Combining the equation (2.3) with the boundary condition that the electrical field goes to zero at the depletion edge L provides the solution for electrical field:

$$E(x) = \frac{qN_D}{\varepsilon_S}(x-L)$$

(2.4)

Integrating the electrical field through the depletion region with boundary condition that potential is zero in the p+ region provides the potential distribution:

$$V(x) = \frac{qN_D}{\varepsilon_S} (Lx - \frac{x^2}{2})$$

(2.5)

Substituting electrical field distribution (2.4) to the ionization integral (2.1) and (2.2) gives:

$$\int_{0}^{L} 1.8 \times 10^{-35} \left[ \frac{qN_{D}}{\varepsilon_{s}} (L-x) \right]^{7} dx = 1$$

(2.6)

Solving above equation for the depletion length L gives:

$$L = 2.67 \times 10^{10} N_D^{-7/8}$$

(2.7)

Substituting equation (2.7) to (2.5), the breakdown voltage  $V_{BR}$  is expressed by drift region concentration  $N_{D}$ :

$$V_{BR} = 5.34 \times 10^{13} N_D^{-3/2}$$

(2.8)

Eliminating  $N_D$  from equations (2.7) and (2.8), the depletion length L can be expressed by breakdown voltage  $V_{BR}$ :

$$L = 2.58 \times 10^{-6} V_{BR}^{7/6}$$

(2.9)

#### 2.1.2 On-state analysis

During on-state operation, the total resistance along the current flow path determines the voltage drop in the device. The various components of on-resistance are shown in Fig. 2.3.

Fig. 2.3 Components of resistance within LDMOS structure on the current flow path

According to Fig. 2.3, on-state resistance of LDMOS can be given by:

$$R_{on} = R_{n+} + R_{ch} + R_{acc} + R_{drift} + R_{n+}$$

(2.10)

where  $R_{n+}$  represents source resistance;  $R_{ch}$  represents channel resistance;  $R_{acc}$  represents accumulation layer resistance below gate;  $R_{drift}$  represents drift region resistance;  $R_{n+}$  represents drain resistance. Normally, the source and drain resistance can be neglected due to the high doping concentration of these regions. Accumulation resistance is also not so important because the overlap region between gate and drift region is very small. The channel resistance and drift region resistance compose of the major part of the total on-resistance. The relevant importance of these two components varies with breakdown voltage ratings. As the breakdown voltage increases, the drift region resistance becomes more and more important [1].

The specific on-resistance of drift region is calculated by:

$$R_{on,sp} = R_{on} \cdot A = \frac{l_{drift}}{q\mu N}$$

(2.11)

where A is the cross-sectional area of current flow.

By substituting equations (2.7) and (2.8) to above equation, the relationship between  $R_{on,sp}$  and breakdown voltage is given by:

$$R_{on,sp} = 5.4 \times 10^{-9} \times V_{BR}^{2.5}$$

(2.12)

where  $q = 1.6021 \times 10^{-19} C$  and  $\mu = 1500 \text{ cm}^2/\text{V-s}$  are used in the calculation.

Equation (2.12) is called "silicon limit". This limit shows a more than square relationship between specific on resistance and breakdown voltage for conventional structure. In the following section, the performance of superjunction device will be analyzed.

#### **2.2 Superjunction Devices**

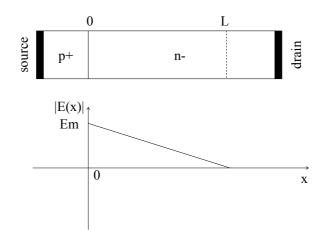

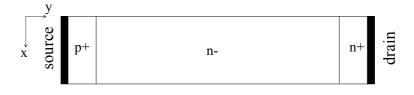

Superjunction devices are designed to break the "silicon limit". The difference between conventional device structure and superjunction device structure is the drift region design. The two kinds of structures used in diode device are shown in Fig. 2.4.

(a) Conventional diode structure with n- drift region

(b) Superjunction diode structure with alternatively stacked p, n column as drift region

Fig. 2.4 Conventional diode structure compared with superjunction diode structure

It's easily noted from Fig. 2.4 that conventional drift region composes of one type epilayer, either n or p, while the superjunction drift region is made up of two types oppositely doped, alternatively stacked epi-layer. Fig. 2.4 (b) shows an interdigitated p-n column structure, which is most commonly used. Other structures are also possible [23].

#### 2.2.1 SJ characteristics at Off-state

#### (a) Comparison of breakdown with conventional device

To compare the Off-state performance of SJ device and conventional device, the two structures shown in Fig. 2.4 are used in Medici simulation to test the respective breakdown voltage. The n+, p+ contact region are heavily doped ( $N_D=N_A=3\times10^{19}$  cm<sup>-3</sup>), the n and p strips in superjunction structure, and n- layer of conventional structure are lightly doped ( $N_D=N_A=3\times10^{15}$  cm<sup>-3</sup>). The drift length is 15µm, and n+, p+ region are 2.5µm long. The drift region width is 5 µm. The simulation results show that the breakdown voltage for conventional drift region is 116V, and for superjunction drift region is 338V. It's obvious that by using superjunction structure in drift region, the device can sustain higher reverse voltage.

The improvement of breakdown voltage by using superjunction structure can be better understood through electrical field profiles. The electrical field distributions for the two structures are plotted in Fig. 2.5. As the structure in Fig. 2.4(a) is an effectively one-dimensional structure, there is no variation in the x direction. While, in Fig. 2.4(b), the structure is two dimensional, the electrical field has both x component and y component. For easy analysis, the electrical field is drawn along the outer edge of n column. In this position, the electrical field only has y component due to the symmetric structure.

Fig. 2.5(a) shows that in conventional drift structure, the field profile is triangle shape, with constant slope and advancing towards drain contact as the voltage increases. In this structure, the depletion boundary moves gradually towards drain as voltage increases. For the superjunction structure, situation is totally different. The p+ region helps the depletion of n column; the n+ helps the depletion of p column; and most importantly p, n column helps the depletion of each other. So, the drift region is totally depleted at a relatively low voltage. After the fully depletion of the drift region, the field profile becomes rectangle shape and eventually moves up as voltage increases. Because the breakdown voltage is simply the area under the field profile when the maximum electrical field reaches critical value, the SJ structure certainly has higher breakdown voltage than conventional structure

Fig. 2.5 Electrical field profiles in (a) conventional diode and (b) superjunction diode For the SJ diode, the field is plotted along the outer edge of n column

#### (b) Derivation of breakdown equation for SJ device

Since superjunction structure is two-dimensional (2-D) structure, 2-D Poisson equation should be solved to get the potential and electrical field equation. This has been done by several authors [24-27]. The solution of the y component of the electrical field  $E_y$  shows that it composes of two parts, one is a constant value  $E_0$  the other is the  $E_1$ .  $E_0$  is thought to be produced by the voltage applied and equal to that of a p<sup>+</sup>-i-n<sup>+</sup> diode under the same reverse voltage. The equation of  $E_0$  is given by:

$$E_0 = \frac{V_B}{L}$$

(2.13)

where  $V_B$  is the applied reverse voltage, L is the drift length.

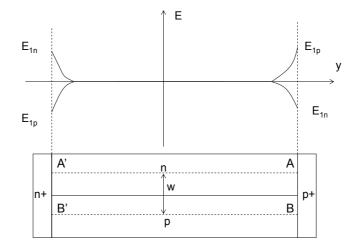

The profile of  $E_1$  is shown in Fig. 2.6. The maximum value of  $E_1$  along the middle of n column is labeled as  $E_{1n}$ , along middle p column labeled as  $E_{1p}$ .  $E_1$  is thought to be produced by the charge in the drift region. According to the charge compensation principle, most of the charge in p, n column is compensated by each other except some near charge the p+ and n+ contact. Therefore,  $E_1$  is zero in most part of the drift region; only near p+, n+ contact there is peak value of  $E_1$ . Adding a constant value  $E_0$  to the profile of  $E_1$ , the resulting profile  $E_y$  is very similar to the profile shown in Fig. 2.5(b).

Fig. 2.6 Field profiles of E<sub>1</sub> along middle of n column (dash line) and along middle of p column (dash line)

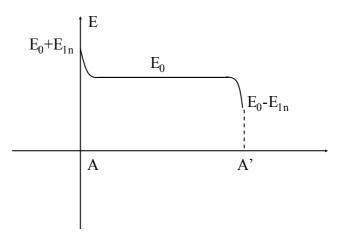

It has been proved that the maximum electrical field appears at point A and B in Fig. 2.6, with the value of  $E_0 + E_{1n}$  and  $E_0 + E_{1p}$ . The minimum electrical field appears at points A' and B' with the value of  $E_0 - E_{1n}$  and  $E_0 - E_{1p}$ . Suppose the p, n column widths are equal, then  $E_{1n} = E_{1p}$ . The electrical field along the middle of n column is reproduced in Fig. 2.7 for the analysis of breakdown voltage. From Fig. 2.7, the optimum situation is that when breakdown occurs, the maximum electrical field  $E_0 + E_{1n}$  reaches the critical electrical field, while the minimum electrical field  $E_0 - E_{1n}$  is just zero. In other words, this condition means that when breakdown occurs, p, n column just fully depleted. At the optimum condition,  $E_0$  and  $E_{1n}$  have the relationship:  $E_0 = E_{1n} = E_C/2$ , and breakdown voltage can be calculated by  $E_0 \times L$  i.e.  $\frac{E_C}{2} \times L$ . The concentration satisfying this condition is the optimum concentration.

Fig. 2.7 Schematic electrical Field profile along middle of n column AA'

In the following, the maximum electrical field equation will be derived first to get the optimum concentration and breakdown voltage. For simplicity, the case that p, n column has same column width and same column concentration ( $N_D = N_A = N$ ) is used in the derivation. Suppose before the fully depletion of p, n column, the electrical field only increases at the p+/n and n+/p junction. The lateral merge voltage  $V_{lateral}$  of p, n column is given by,

$$V_{lateral}_{merge} = \frac{qNw^2}{4\varepsilon_s}$$

(2.14)

At this voltage, the depletion depth in n column  $X_n$  is given by:

$$x_{n} = \left[\frac{2\varepsilon_{s}V_{lateral}N_{p^{+}}}{q(N+N_{p^{+}})N}\right]^{1/2} \approx \frac{1}{\sqrt{2}}w$$

(2.15)

Then, the electrical field at p+/n junction before p, n column fully depletion  $E_A$  is arrived as:

$$E_A = x_n \left(\frac{qN}{\varepsilon_s}\right) = \frac{qN}{\sqrt{2}\varepsilon_s} w \tag{2.16}$$

For the first order approximation, this field peak should be less than or equal to the critical electrical field, that is:

$$E_{\max} = E_A = E_C$$

(2.17)

where  $E_C$  is the critical electrical field, expressed as  $Ed(N) = 4010 N^{1/8}$ .

Based on the expressions of  $E_A$  and  $E_C$ , the optimum column concentration is derived as:

$$N = 1.2 \times 10^{12} \, w^{-\frac{8}{7}} \tag{2.18}$$

Equation (2.17) is obtained by substituting q=1.60218×10<sup>-19</sup> C,  $\epsilon_s$ =11.9×8.85×10<sup>-14</sup> F/cm.

When the optimum concentration used in the SJ structure, the breakdown voltage can be expressed as following:

$$V_{BR} = E_0 \times L = \frac{E_C}{2} \times L = \frac{E_A}{2} \times L$$

(2.19)

where L is the drift length.

Substituting equation (2.16) to (2.19), the breakdown voltage is expressed by device parameter:

$$V_{BR} = \frac{qN}{2\sqrt{2\varepsilon_s}} wL \tag{2.20}$$

This equation is only applicable when the column concentration used is the optimum concentration. All the derived equations are first-order equations.

#### 2.2.2 Specific on-resistance of SJ device

The relationship between  $R_{on,sp}$  and  $V_{BR}$  for superjunction device is obtained by substituting equation (2.18) and (2.20) to the specific on-resistance definition equation (2.11):

$$R_{on,sp} = \frac{2 \times l_{drift}}{q\mu N} = \frac{2 \times \left(\frac{2\sqrt{2} \times \varepsilon_s \times V_{BR}}{qNw}\right)}{q\mu N} = \frac{4\sqrt{2} \times \varepsilon_s \times V_{BR}}{q^2 \mu N^2 w} = 0.107 w^{9/7} V_{BR}$$

(2.21)

where  $R_{on,sp}$  is in unit of  $\Omega$ -cm<sup>2</sup>; w is in unit of cm; and  $V_{BR}$  is in unit of V.

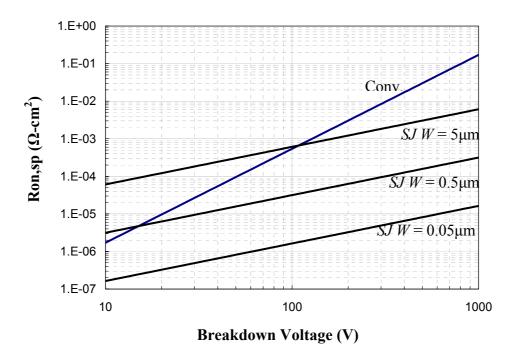

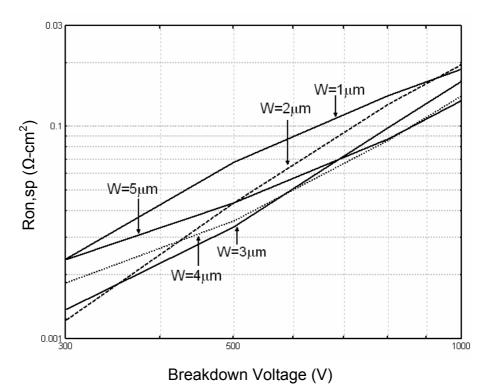

Equation (2.21) is the ideal  $R_{on,sp}$  vs  $V_{BR}$  relationship for superjunction devices. This is a linear relationship compared the more than square relationship for conventional device. To see clearly the superior performance of SJ device, the superjunction performance lines given by equation (2.21), together with the "ideal silicon limit" line expressed by equation (2.12), are shown in Fig 2.8. Fig. 2.8 shows that for breakdown voltage larger than 100V, superjunction devices have a lower specific resistance than the ideal silicon limit. This means that the silicon limit has been broken by the superjunction structure. The figure also shows that the higher breakdown voltage, the more prominent of the superjunction benefit.

Fig. 2.8 Ideal R<sub>on, sp</sub> - V<sub>BR</sub> performance comparison between conventional (CV) structure and superjunction(SJ) devices

# 2.3 Current state of superjunction device and technology

Superjunction concept is initially used in vertical devices. The reason is that the superiority of superjunction device is more prominent at high breakdown voltage and the whole wafer depth can be used to fabricate a vertical device to realize high breakdown voltage. While, for lateral device which is mainly used in medium or low breakdown voltage, it is not easy to achieve high breakdown voltage. Using superjunction structure in lateral device is still a new concept and the usage is limited at medium or low voltage range. Therefore, the fabrication technology of vertical SJ device is more mature than lateral SJ device. Till now, vertical SJ device has been made commercially available, while, lateral SJ device fabrication is still in research stage.

#### 2.3.1 Vertical SJ devices

Most of fabricated SJ devices are vertical devices [9] [12-16]. There are many kinds of fabrication technology available which all have their pros and cons.

COOLMOS<sup>TM</sup> is the first commercially available superjunction device. The fabrication technology used is multiple deposition of epitaxial layers and subsequent implantation steps. This technology can achieve device performance of 3.5  $\Omega$ -mm<sup>2</sup>@600V. The problem of the technology is that the resulted p, n column doping profile is not very satisfying. Along the drift region, p, n column shows radial profile due to limited number of epitaxial steps than can be employed. The interdiffusion between p, n column during driven-in process causes blur boundary between p, n column. Also the number of implantation masks needed to form p, n column profiles is a little large.

Compared with COOLMOS<sup>TM</sup> technology, Super Trench Power MOSFET (STM) uses trench etching and p, n tilt implantation to form p, n column doping profile. This technology only needs one additional mask over the conventional DMOS process [13, 14]. The device simulation results show it can achieve 5 m $\Omega$ -cm<sup>2</sup>@ 300V. STM technology far surpasses conventional multi-epitaxy used in COOLMOS<sup>TM</sup> because it can realize very tight cell pitch, thus can achieve lower R<sub>on,sp</sub> [14].

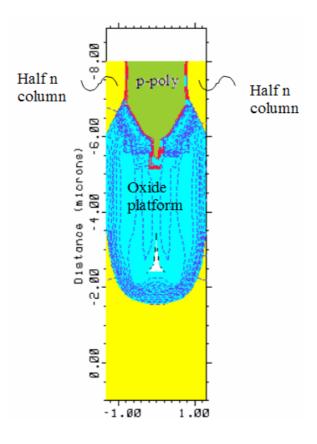

Another similar fabrication technology is Vertical Deep Trench RESURF DMOS (VTR-DMOS) [15]. In this technology, a deep trench is etched to create vertical a sidewall, then highly doped p-poly is deposited along the sidewall to introduce solid boron source, finally boron diffuse into the sidewall to form p column. From

simulation results, VTR-DMOS shows a 5.5X improvement in  $R_{on,sp}$  for breakdown voltage over 700V compared with conventional VDMOS.

A recent simple fabrication technology is Polysi Flanked VDMOS (PFVDMOS) [16]. This technology overcomes the interdiffusion problem between p, n column by introduce a thin layer oxide between them. The fabrication process is first growing n epi-layer, then etching it to leave space for p column. Next, dry oxidation is performed to form thin oxide layer. After removing the oxide on top and bottom part, a thin layer poly is deposited in the trench. To get uniform profile in p column, boron tilt implantation into the thin poly layer, poly refill and drive-in process are performed. This technology can produce rather uniform profile. In the p, n column formation process, only simple process steps such as etching, deposition, implantation and poly-fill are used.

#### 2.3.2 Lateral SJ devices

Recently, SJ concept has been used in lateral MOSFET structure to improve it performance. Various structures have been proposed to achieve good performance [11] [17-22] [24, 28].

When lateral SJ structure was first proposed in 1998, it is called lateral 3-D RESURF device [11]. According to the author, the structure is based on the extension of RESURF concept to the third dimension. The lateral 3-D RESURF power MOSFET structure is shown in Fig. 2.9. After replacing conventional drift region to SJ structure, the breakdown voltage ability of the device has been greatly improved for the same

doping concentration due to the rectangular field distribution achieved by the SJ structure.

Fig. 2.9 The schematic view of lateral 3-D RESURF MOSFET

To further improve the specific on resistance, the same author proposed double gate structure [11]. Adding the second gate and p+ contact in the drain side, the p column can also be used to conduct current. Another variation of the structure is to use unbalanced SJ structure in drift region [17]. In the unbalanced structure, n column width eventually increases towards the drain end, while, p column width eventually decreases. This is to ensure that after p, n column fully depletion, the charge in n column will be greater than that in p column. Therefore, there is net charge increasing from source end to drain end. The net charge is similar to that produced by a linearly doping profile. This net charge is to counterbalance a layer of mobile charge on the surface of BOX, which is produced by field effect action across the SOI-BOX-substrate structure when a large reverse bias applied in the off-state. This mobile charge will affect the uniform distribution of the electrical field. After using the unbalanced SJ structure, the field distribution is very uniform and high breakdown

voltage can be achieved. To solve the same problem, another group proposed to use a different kind of substrate-sapphire [21]. The BOX and si-substrate in Fig. 2.9 are replaced by sapphire in the new structure. Without the SOI-BOX-substrate structure, the field effect action doesn't exist, so electrical field distribution is very uniform. Another benefit is that the sapphire has much better heat conduction ability than BOX-substrate structure.

The above devices are emphasis on the Off-state performance for high breakdown voltage. For medium level power applications, 120V interdigitated LDMOS (IDLDMOS) was proposed to have better performance than conventional LDMOS [18]. Device structure is similar to that in Fig. 2.9, with the only difference in channel formation process. The performance of the proposed structure can achieve 1.15 m $\Omega$ -cm<sup>2</sup> @124V, which is better than the performance of conventional LDMOS. A similar superjunction LDMOS structure was proposed to have breakdown voltage of 150V and specific on resistance 1.65 m $\Omega$ -cm<sup>2</sup>[19]. The author emphasized on the fabrication aspect of the device. The fabrication steps, device layout design have been proposed and proved by the simulation.

The superjunction structure helps to increase the doping concentration of the n-drift layer, and lateral trench gate allows to increases channel area. If the two structures used in the same device, both the drift region resistance and channel resistance can be reduced. The structure is called lateral trench gate superjunction SOI-LDMOSFETs [20]. The device is aimed at breakdown voltage 120V and the specific resistance can be reduced to 60% of conventional SOI-LDMOSFETs.

Although superjunction LDMOS has been proved theoretically to have better performance than conventional LDMOS, the fabrication technology still needs to be developed. Till now, only few structures are fabricated [22][28]. One fabricated device is on bulk silicon wafer [22]. First, n-drift region is formed by implanting high dose phosphorus to the lightly doped p-type substrate. Then, p-strip mask was patterned and the boron ions were implanted to form the p-strip region. The dosage used to form p-strip are several times higher than n-drift. The fabricated SJ-RESURF LDMOSFET has a performance of 3.53  $\Omega$ -mm<sup>2</sup> @ 335V.The on-resistance is 25% better than that of conventional structure. The other fabricated SJ LDMOS is on sapphire substrate using the 0.5µm CMOS/SOS technology [28]. The process includes three pairs of complementary LDD-CMOS transistors. Lateral isolation between devices is implemented using recessed LOCOS that extends down to sapphire substrate. The superjunction drift region is implemented by stacking alternating n and p-pillars made of layers corresponding to the channel regions of, respectively, PMOS and NMOS devices. The experimental breakdown voltage is 170V with the lateral electrical field of  $17V/\mu m$ , which implies charge compensation. 3-D simulations predict silicon limit of conventional LDMOS can be broken when the aspect ratio of pillar height to width exceeds  $1.2 \,\mu m / 0.3 \mu m$ .

## 2.4 Summary

In this chapter, the performance of conventional power MOSFET device is firstly analyzed with the emphasis on "silicon limit". Then, the superjunction device is investigated in detail. The off-state performance of superjunction device is compared with that the conventional device to show its superiority. The off-state and on-state equations are derived based on electrical field analysis. Finally, the current status of superjunction device is reviewed, and problems encountered are summarized.

# **Chapter 3**

# Practical SJ performance under interdiffusion influence

Chapter 2 has summarized the current state of superjunction device and technology. Although superjunction device and technology have developed for many years, there are still some constrains existing in device structure or fabrication technology. Interdiffusion problem is one of the technology constrains. In this chapter, the interdiffusion problem is discussed and the study of practical superjunction device performance under given thermal cycles with the major consideration of interdiffusion is described.

# 3.1 Interdiffusion problem in current technology

Till now, most of the fabricated SJ devices are vertical devices. Few lateral SJ devices are fabricated. The available fabrication technologies for vertical SJ devices are

COOLMOS<sup>™</sup> technology, STM, VTR-DMOS and PFVDMOS [9][12-16]. These technologies have been introduced in section 2.3.1 of chapter 2. Each technology has its own pros and cons.

To achieve the best performance in superjunction structure, precisely charge-balanced p and n voltage-sustaining columns must be formed to have exactly the same doping concentration and the same column width. However, to achieve ideal matching condition in practice is rather difficult, if not impossible. In addition, even if the doping of both p-n columns could be made equal, the quality of sidewall junction formed by the neighbouring p-n columns plays another important role to influence the breakdown voltage. This constraint becomes more dominant when p- and n-column widths get smaller for devices rated in lower voltage region, e.g. below 200 V. For a column width less than 3 µm, the approach of using multiple-layer epitaxial growth and implantation process [9] to form vertical p-n columns becomes unsuitable due to the constraints of multiple misalignments of masks, auto-doping in the epitaxial process and thermally-induced dopant inter-diffusion in annealing processes. Instead, the silicon trench and selective epitaxial growth processes can be used at a lower temperature to overcome the above-mentioned constraints [29-31].

However, other follow-on fabrication processes involving thermal cycles for MOSFET gate and source formation are always needed. These high temperature thermal cycles promote dopant inter-diffusion between non-ideal p-n columns and give rise to the formation of a wider dopant transition region between p-n columns, resulting in more non-uniform dopant distribution. The sidewall junction quality is thus worsened, and in turn, this lowers the achievable breakdown voltage of superjunction devices having narrow column width.

- 28 -

The dopant interdiffusion phenomenon is unavoidable in most of the fabrication technology such as COOLMOS<sup>™</sup> technology, STM, VTR-DMOS. The PFVDMOS technology forms a thin oxide layer between p, n column to prevent the interdiffusion. The technology achieves the expected result. However, the interdiffusion influence on the SJ device performance is still needed to discover.

As part of the research work, the practical SJ performance under given process thermal cycles is investigated. When the process thermal cycles are fixed, the amount of interdiffusion caused by thermal cycles is fixed. The aim of the study is to find the influence of interdiffusion on the SJ device performance.

### **3.2** Practical SJ performance under given thermal cycles

#### 3.2.1 Simulation methodology

To get the realistic SJ performance under given process thermal cycles, two vertical SJ MOSFET structure, DMOS and UMOS, are the used in the simulation. The schematic view of DMOS and UMOS structures are shown in Fig. 3.1 (a) and (b).

Fig. 3.1 The two vertical Superjunction power MOSFET structures (a) SJ DMOS structure (b) SJ UMOS structure

The conducting n-column is set initially to have equal doping and width as the nonconducting p-column at the selective epitaxy growth stage then followed by all device thermal processes in order to find the optimum SJ device performance in practice. In process simulation, a silicon wafer of n-epitaxial layer grown on  $n^+$  substrate is used. A trench is etched and p-column is grown by low-temperature (<550° C) selective epitaxy. The epitaxial layer now containing interdigitated p- and n-columns is further processed to form p-body, gate and source regions so as to complete the MOSFET structure. P-body and source regions are self-aligned to the gate edge to ensure fixed channel length for structural consistency for all cases in the investigation. The channel length is fixed at 0.3  $\mu$ m. The right edge of source region, i.e. point A, is always aligned with the junction of p-n columns. The distance between p-body right edge, i.e. point B, and the p-n column junction is maintained at a reasonable distance, so that the neck region in DMOS structure will not be too small. The device geometries are summarised as following. The minimum source length is 0.5 µm, of which the overlap with gate oxide region is  $0.1 \,\mu\text{m}$ . The column width varies from minimum of 1.3 µm to 9 µm at 0.1 µm step. No obvious degradation on breakdown voltage by the inter-column dopant diffusion in SJ structure was observed when the width is more than 9  $\mu$ m in the simulated breakdown voltage range from 80V to 1000V. The neck length for DMOS is equal to half of the column width minus the channel length, i.e. it varies from  $0.35 \,\mu\text{m}$  to  $4.2 \,\mu\text{m}$ .

The epitaxial thickness is adjusted to the minimum for each specific breakdown voltage so that smallest achievable  $R_{on,sp}$  is achieved. All essential thermal cycles such as gate oxide growth, n<sup>+</sup> source-drain anneals and p-body drive-in are included in TSUPREM [39] process simulation. The main thermal processes in MOSFET device

fabrication are listed in Table 3.1. The thermal budget shown in Table 3.1 is taken from previously optimized fabrication conditions in the run sheet, which is intended for a high voltage device. Compared with the thermal process in Table 3.1, the interdiffusion caused by p column epitaxy process can be neglected because the growth temperature is below  $550^{\circ}$  C.

To find the realistic and optimum SJ performance curve, the approach is to find the minimum  $R_{on,sp}$  at various column width, doping concentration and drift length at each breakdown voltage. The simulation process was carried out in three nested loops, i.e. to determine these three optimal parameters at a particular breakdown voltage. A flow chart is given in Fig. 3.2 to illustrate the simulation methodology.

For each breakdown voltage, the column width (*W*) is set at the maximum value and the initial concentration (*N*) is set at 30% of the theoretical value of  $N = 1.2 \times 10^{12} \times W^{-8/7}$  to start with the iterations. The drift region depth is set initially at a value by assuming uniform field of 10 V/µm over the drift length. The structure formed by the process simulation (TSUPREM) is imported into device simulation (MEDICI) [40] to simulate device performance. The iterations are to find the locally-optimal doping concentration first at each column width, and for all different column widths to

| Thermal process     | Time (min) | Temperature (degree Celsius) | determine |

|---------------------|------------|------------------------------|-----------|

| Gate oxide growth   | 76         | 1000                         |           |

| P-body driven-in    | 20         | 1100                         | the       |

| Source/drain anneal | 30         | 900                          |           |

|                     |            |                              | globally- |

optimal column width and doping concentration to yield the minimum  $R_{on,sp}$  for a

given breakdown voltage. For example, consider the case of column width W = 1.7 µm for device breakdown rating of 300 V. The calculated optimal concentration based on the ideal SJ theory for W = 1.7 µm is  $2.44 \times 10^{16}$  cm<sup>-3</sup>. In practice, the optimal concentration is likely to be lower; hence, we start from the concentration of  $8 \times 10^{15}$  cm<sup>-3</sup> (30% of ideal value). The concentration is gradually increased while the width *W* is fixed.

#### Fig. 3.2 Flow chart of simulation methodology

For each concentration, the drift length to sustain the expected breakdown voltage, i.e. 300 V, is adjusted accordingly. Then, the  $R_{on,sp}$  is found with that concentration and epitaxial thickness. *W* is decided firstly because the initial value of *N* can be calculated based on it. *L* is decided finally because *W* and *N* have small influence on it. As can be seen in Fig. 3.3, under realistic process conditions, the increase in the doping concentration enables a lower  $R_{on,sp}$  and the performance point moves towards the point Q where the optimal value is reached. This occurs at the concentration of  $1.3 \times 10^{16}$  cm<sup>-3</sup>, a value below the theoretically calculated one mainly due to influence of dopant inter-diffusion. During thermal process, the substrate dopant may also outdiffuse into the epitaxial drift region. The out-diffusion phenomenon has been considered and included in the drift length adjustment, so that the drift length after thermal process is at the correct quantity to sustain the target voltage, i.e. 300 V in the current example.

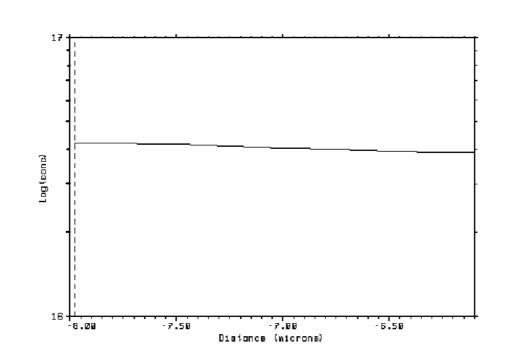

Fig. 3.3 The relationship between  $R_{on,sp}$  and column doping concentration at the given breakdown voltage (300V) and column width (1.7µm). The optimum concentration for column width of 1.7 µm is  $1.3 \times 10^{16}$  cm<sup>-3</sup>

For each column width, the optimal concentration and  $R_{on,sp}$  to achieve a specific breakdown voltage can be found using the methodology described above. By observing  $R_{on,sp}$  varying with changing W, the globally-optimal  $R_{on,sp}$  can be found for a given breakdown voltage. For the breakdown voltage of 300 V, the  $R_{on,sp}$  versus Wcurve is shown in Fig. 3.4. The optimal  $R_{on,sp}$  at 300 V rating is  $2.24 \times 10^{-3} \Omega$ -cm<sup>2</sup> at the column width of 2.3 µm. Hence, by following the same approach, it is now possible to find the globally-optimal  $R_{on,sp}$  for each breakdown voltage. This has been done for breakdown voltages of 80 V, 100 V, 200 V, 300 V, 500 V, 800 V and 1000 V respectively.

Fig. 3.4 The relationship between  $R_{on,sp}$  and the column width at given breakdown voltage (300V). The optimal  $R_{on,sp}$  at 300V is  $2.24 \times 10^{-3} \ \Omega$ -cm<sup>2</sup> at column width W = 2.3  $\mu$ m

#### 3.2.2 The realistic optimum SJ performance curves

The realistic optimal SJ performance curves under inter-column diffusion influence for both DMOS and UMOS of minimum  $R_{on,sp}$  versus  $V_{br}$  are shown in Fig. 3.5, together with the ideal silicon limit lines of conventional structure [1, 2] and ideal SJ performance lines for different column width W [2] and different  $\Delta/L$  [32] where  $\Delta$  is the hexagonal column width and L is the drift region depth as defined in [32]. Experimental data extracted from published work [4, 9, 13-15] are also labelled in Fig. 3.5. It is clearly shown that all the experimental data have a higher specific resistance above the realistic optimal SJ performance curves. With dopant inter-diffusion included in practical process, the realistic optimal SJ performance curves are not linear in the log-log plane as ideal SJ performance lines. Compared with the ideal silicon limit line, when the breakdown voltage is below 80 V, the realistic  $R_{on,sp}$  of SJ structure is worse than that of the ideal unipolar silicon limit.

#### 3.2.3 The interdiffusion influence on breakdown voltage

To understand why the practical SJ curves become like this, the interdiffusion influence on breakdown voltage is studied.

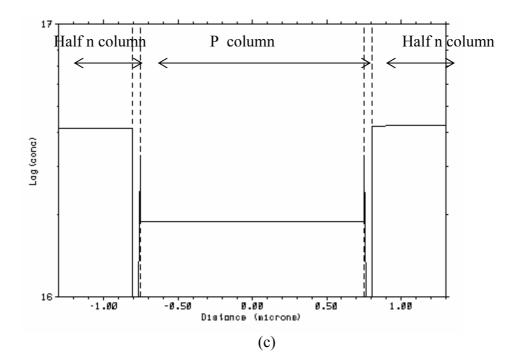

To show the transition between ideal and realistic situation, the doping profiles changing from ideal case without thermal budget to the realistic case with full thermal budget are shown in Fig. 3.6. The simulated device is SJ VDMOS with column width of  $2\mu m$  and ideal concentration of  $2.03 \times 10^{16}$  /cm<sup>3</sup>. The doping profiles are cut along line X-X' as in Fig. 3.1(a). The dopant inter-diffusion creates a wider dopant transition region at p-n junction and it also alters the junction position away from its origin metallurgical position of equal p and n column widths.

Fig. 3.5 The simulated practical optimum SJ performance curves (SJ DMOS and SJ UMOS) with dopant inter-diffusion included compared with the ideal SJ performance lines and the ideal silicon limit curves. A "zoom in" figure is added to show clearly the curves near 80V

By cutting the line along X-X', as shown in Fig. 3.1(a), perpendicular to the current flow, and integrating the doping concentration in p-column and n-column respectively, the difference between p-column doping integral  $Q_p$  and n-column doping integral  $Q_n$ can be found and is defined as one-dimensional (1-D) p-n doping integral imbalance. The two-dimensional (2-D) p-n doping imbalance is obtained by numerically integrating the 1-D p-n imbalance along the entire length of SJ column in the drift region. The results show that, for higher column concentration the imbalance of doping integral is more severe for a given thermal cycle. In turn, the sustainable voltage becomes lower. Hence, the column concentration is reduced in order to maintain the sustainable breakdown voltage.

Fig. 3.6 The doping profiles changing from ideal case without thermal budget to the real case with full thermal budget. The thermal budgets for each doping profile are labelled in the figure. The simulated device is SJ VDMOS with column width of  $2\mu m$  and ideal concentration of  $2.03 \times 10^{16}$  /cm<sup>3</sup>. The doping profiles are cut along line X-X' in Fig. 3.1(a) - 37 -