# A VERY HIGH SPEED BANDPASS CONTINUOUS TIME SIGMA DELTA MODULATOR FOR RF RECEIVER FRONT END A/D CONVERSION

## K. PRAVEEN JAYAKAR THOMAS

(B. Tech., Madras Institute of Technology, Anna University)

A THESIS SUBMITTED

### FOR THE DEGREE OF MASTER OF ENGINEERING

### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2004

### Abstract

Directly sampling the Radio Frequency (RF) signal in the receiver front end moves the forthcoming Intermediate Frequency (IF) conversion, filtering, channel selection and In phase, Quadrature phase demodulation into the digital domain. Pushing more functions of the receiver into digital domain will tend to a system which is less complex, low distortion and more robust to temperature and process variation with reduced cost, size, weight and power dissipation. The above demands a very high speed Analog to Digital Converter (ADC) which would sample the signals directly at GHz with high linearity and dynamic range.

Though previously continuous-time bandpass Sigma Delta modulators were used for RF digitization, all of the reported work used RF bipolar transistors of SiGe HBT, AlGaAs/GaAs HBT or InP HBT in realizing the modulator. This limits the monolithic integration of the ADC and the digital signal processing modules (which are prevailingly designed in CMOS) on the same chip in a RF receiver. Hence this research thesis focuses on designing a very high frequency Sigma Delta modulator in CMOS technology. This is the first time that such a high frequency modulator is ever tried in CMOS.

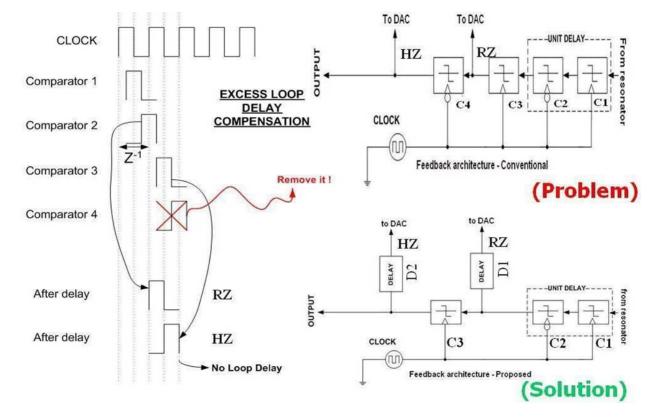

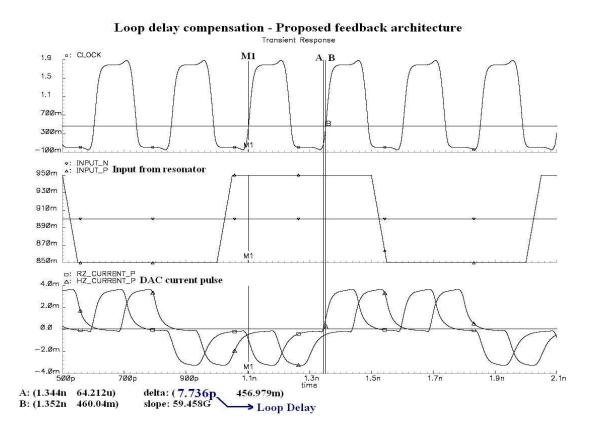

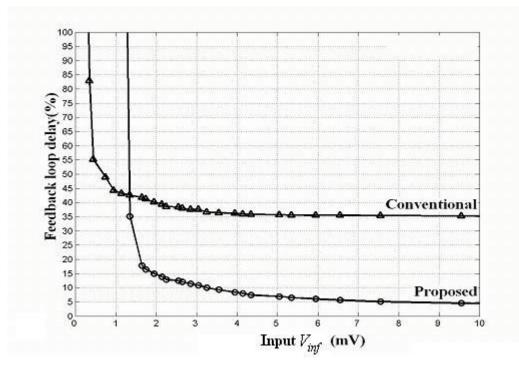

A design and circuit implementation of a CMOS fourth-order continuous-time bandpass  $f_s/4$  Sigma-Delta modulator is presented. The modulator uses fully differential multi feedback architecture. A novel way of realizing the feedback architecture in circuit in order to overcome the problem of loop delay in the modulator is proposed. Simulation results comparing the conventional architecture and the proposed one are also reported. To realize the bandpass filters, integrated LC resonators with active Q enhancement is used. A very high frequency transconductor is used to driving the bandpass LC resonators. Dynamic comparators are used to quantize the signal and the output is shaped to a return to zero, half return to zero waveform. The feedback occurs in current domain with the current from the switched current source DACs and that from the transconductor.

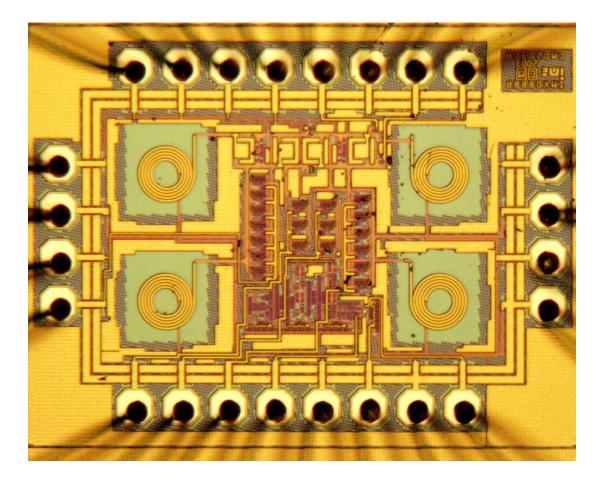

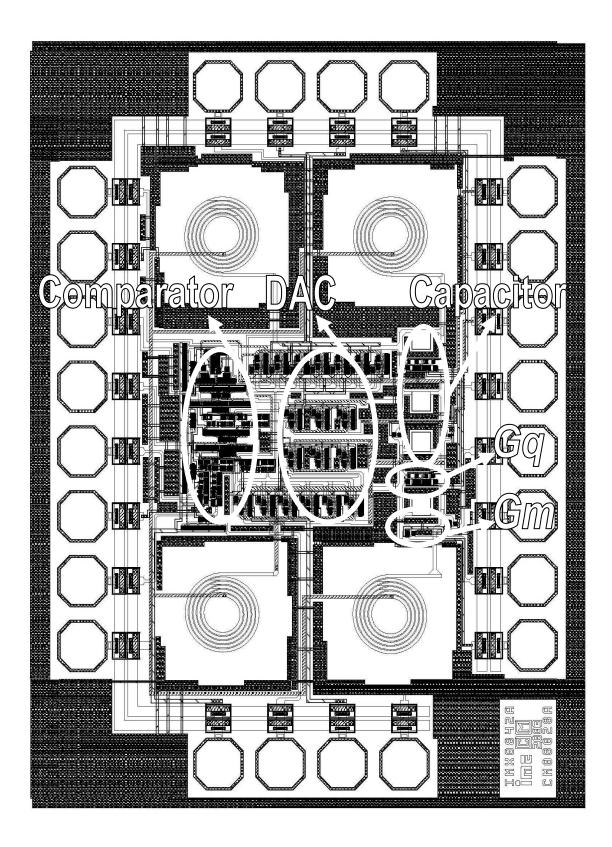

The modulator, designed for 0.18µm/1.8V 1P6M CMOS process occupies a total area of 1.8mm<sup>2</sup> dissipating 290mW from a 1.8V power supply. At a sampling rate of 4GHz and a signal of 1GHz with 500 kHz bandwidth, the circuit achieves a peak Signal-to-Noise and Distortion Ratio (SNDR) of 40dB. With the proposed architecture the loop delay is keep below 3% of the clock period. The proposed architecture is also put under test for higher sampling frequencies to prove its stability.

### Acknowledgements

I sincerely thank my supervisors Dr. Ram Singh Rana, Institute of Microelectronics, and Assoc. Prof. Lian Yong, National University of Singapore, for giving me the valuable opportunity of doing research under their supervision. I also thank them for their guidance and help through out the course.

I would like to thank Ms. Tan Mei Fang Serene, Institute of Microelectronics, and Mr. Oh Boon Hwee, Institute of Microelectronics, for helping me in layout and fabrication of PCB.

Special thanks to Institute of Microelectronics, Singapore, for providing me a JML scholarship to support my research.

Finally I thank all my friends in Signal Processing and VLSI design laboratory, National University of Singapore, for making the two years of research an enjoyable one.

# Table of contents

| Abstracti                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgementsiii                                                                                                                                                                                                                                                                                                                                          |

| Table of contents iv                                                                                                                                                                                                                                                                                                                                         |

| List of Figures vii                                                                                                                                                                                                                                                                                                                                          |

| List of Tablesix                                                                                                                                                                                                                                                                                                                                             |

| List of Abbreviations x                                                                                                                                                                                                                                                                                                                                      |

| Chapter 1 Introduction 1                                                                                                                                                                                                                                                                                                                                     |

| 1.1 Role of ADC in Radio Receivers – Moving towards "Less Analog More Digital" 1         1.1.1 Superheterodyne Receiver with baseband ADC                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                              |

| 2.1 Quantization noise72.2 Sigma Delta Modulator – Pulse Density Modulation102.2.1 Noise Shaping122.2.2 Oversampling152.3 The choice of an ADC for RF front end162.3.1 Band pass Sigma Delta modulator172.3.2 DT $\Sigma \Delta Ms$ Vs CT $\Sigma \Delta Ms$ 192.3.3 Review of existing research in very high frequency CT $\Sigma \Delta M$ 202.4 Summary21 |

| 2.2 Sigma Delta Modulator – Pulse Density Modulation102.2.1 Noise Shaping122.2.2 Oversampling152.3 The choice of an ADC for RF front end162.3.1 Band pass Sigma Delta modulator172.3.2 DT ΣΔMs Vs CT ΣΔMs192.3.3 Review of existing research in very high frequency CT ΣΔM20                                                                                 |

| Chapter 4 | Non-Idealities of Continuous-Time Sigma Delta Modulator and De | sign |

|-----------|----------------------------------------------------------------|------|

|           | Issues at High Frequencies                                     | 33   |

| 4.1 Loop delay and modulator stability at very high frequencies |    |

|-----------------------------------------------------------------|----|

| 4.2 Clock jitter effects on SNR                                 |    |

| 4.3 Variation of DAC pulse shape due to quantizer metastability | 40 |

| 4.4 Inter-symbol interference with unequal DAC rise/fall time   | 44 |

| 4.5 MOSFET Vs Bipolar in very high frequencies                  |    |

| 4.5.1 MOSFET cut-off frequency $(f_T)$                          |    |

| 4.5.2 Delay-line effects in a MOSFET                            |    |

| 4.6 Summary                                                     |    |

# Chapter 5 The Implementation of 4<sup>th</sup> Order LC Bandpass Modulator in Circuit.. 50

| 5.1 Modulator circuit topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2 Design of bandpass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52 |

| 5.3 Comparator circuit architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 5.5 Loop delay compensation in feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Chapter 6 Test Plan and Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 6.1 Output buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 6.1.1 Test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 6.1.2 Test results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79 |

| 6.2 Feedback comparator structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80 |

| 6.2.1 Test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81 |

| 6.2.2 Test results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82 |

| 6.3 Analyzing the testing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |

| 5.2 Design of bandpass filter         5.3 Comparator circuit architecture         5.4 High speed current switched DAC         5.5 Loop delay compensation in feedback.         5.6 Modulator layout and post layout simulation         5.6.1 Analyzing for lower SNR         5.6.2 Testing the modulator for higher sampling frequency of 6GHz.         5.7 Summary         Chapter 6 Test Plan and Measurements.         6.1 Output buffer.         6.1.1 Test setup.         6.1.2 Test results         6.2 Feedback comparator structure         6.2.1 Test setup.         6.2 Test results         6.3 Analyzing the testing results.         6.4 The BP CT ΣΔM.         Chapter 7 Conclusion and Future Work.         7.1 Conclusion | 83 |

| Chapter 7 Conclusion and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85 |

| 7.1 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85 |

| 7.2 Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86 |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87 |

| Appendix A: MATLAB Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Appendix B: Simulink models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Appendix C: Layout of test structure          |     |

|-----------------------------------------------|-----|

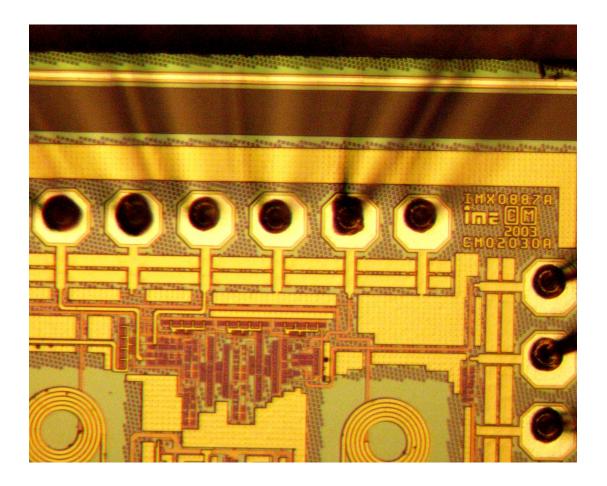

| Appendix D: Chip photograph of test structure |     |

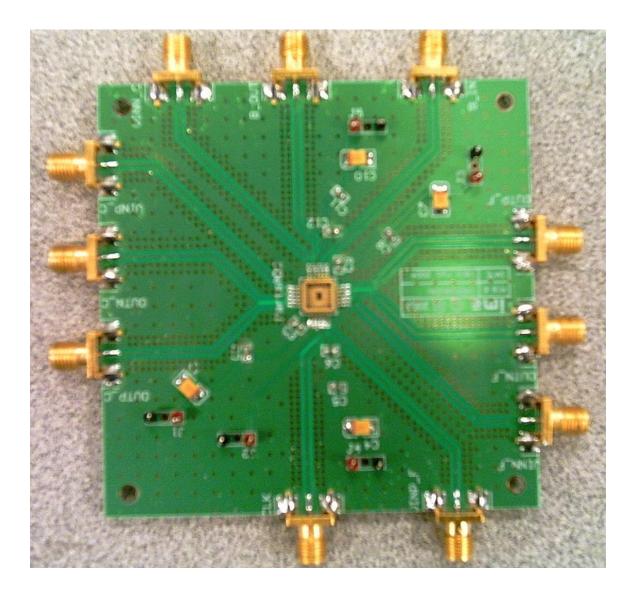

| Appendix E: Test PCB                          | 100 |

| Appendix F: Chip photograph of CT BP ΣΔM      | 101 |

# List of Figures

| Figure 1.1: Radio receiver architectures                                                       | 3    |

|------------------------------------------------------------------------------------------------|------|

| Figure 2.1: Quantization                                                                       | 8    |

| Figure 2.2: Quantization noise spectral density                                                |      |

| Figure 2.3: The basic components of Sigma Delta modulator                                      | . 10 |

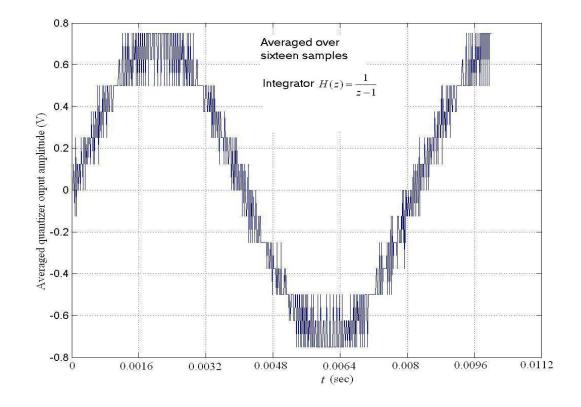

| Figure 2.4: The averaged quantizer output signal tracking the modulator sine input             | . 11 |

| Figure 2.5: Linearizing the quantizer in $\Sigma\Delta M$                                      | . 12 |

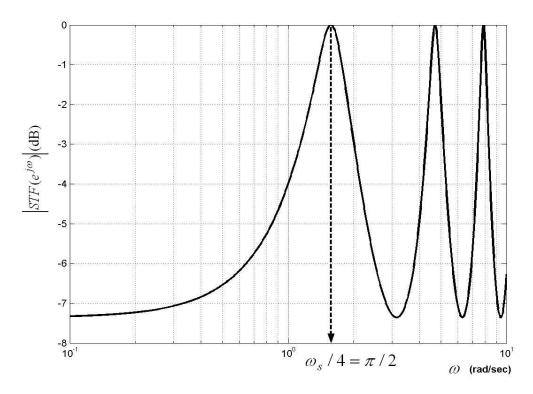

| Figure 2.6(a): Magnitude of Signal Transfer Function STF(z)                                    | . 14 |

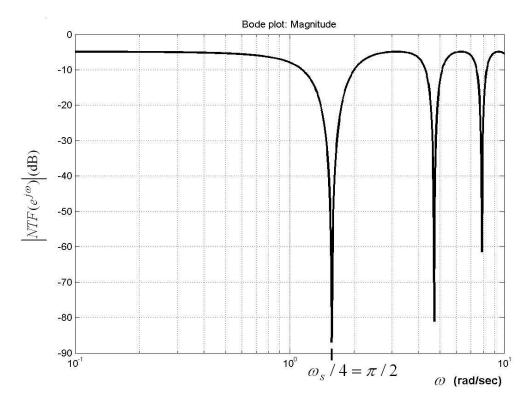

| Figure 2.6(b): Magnitude of Noise Transfer Function NTF(z)                                     | . 14 |

| Figure 2.7: The anti-aliasing filter magnitude response                                        | . 17 |

| Figure 2.8: An application of BP $\Sigma\Delta M$                                              | . 18 |

| Figure 3.1: Block diagram of a continuous time Sigma Delta modulator                           | . 22 |

| Figure 3.2: Open loop continuous time Sigma Delta modulator                                    | . 23 |

| Figure 3.3: The fourth order bandpass CT $\Sigma \Delta M$ which is not fully controllable     | . 25 |

| Figure 3.4: A multi feedback CT bandpass $\Sigma\Delta M$ architecture.                        | . 26 |

| Figure 3.5: State space representation of $\Sigma\Delta M$                                     |      |

| Figure 3.6: Ideal Simulink model of the multi feedback CT $\Sigma\Delta M$                     |      |

| Figure 3.7: Power spectral density of output from Simulink model                               |      |

| Figure 3.8: Dynamic range plot for the Simulink model of CT $\Sigma \Delta M$ .                |      |

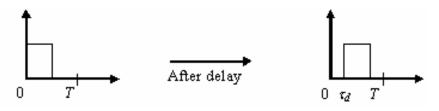

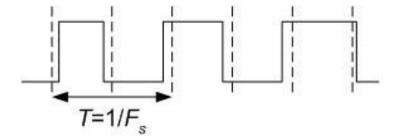

| Figure 4.1: Delay in RZ DAC pulse.                                                             |      |

| Figure 4.2: Open loop CT $\Sigma \Delta M$ with excess loop delay.                             |      |

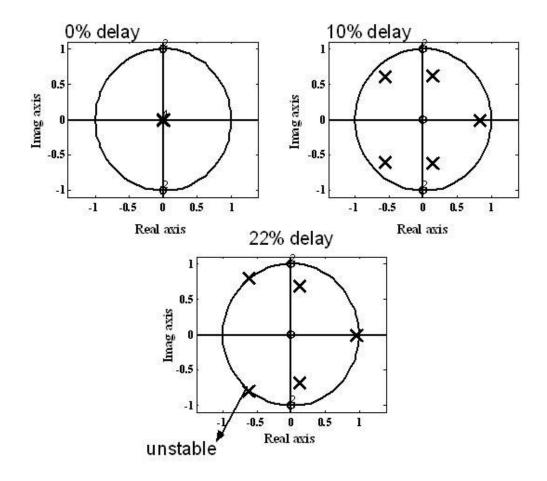

| Figure 4.3: Root locus of the noise transfer function $NTF(z,m)$                               |      |

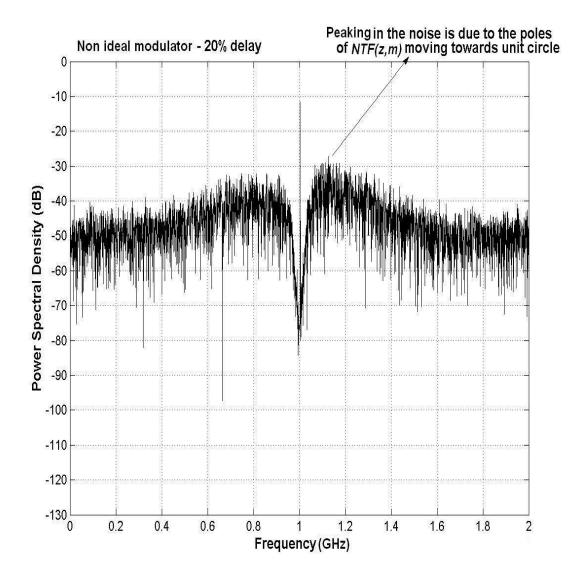

| Figure 4.4: Power spectral density of the output from a loop delayed CT $\Sigma\Delta M$       |      |

| Figure 4.5: A jitter in the sampling clock.                                                    |      |

| Figure 4.6: DAC pulse due to a jittered sampling clock                                         |      |

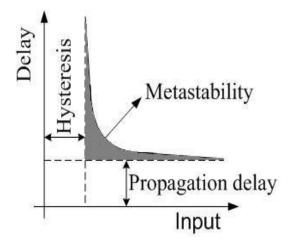

| Figure 4.7: Non ideal quantizer characteristics                                                |      |

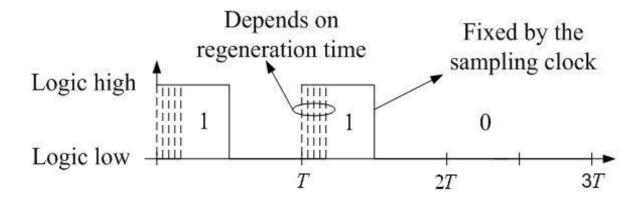

| Figure 4.8: DAC pulse width variation due to quantizer metastability                           |      |

| Figure 4.9: Simulation of quantizer metastability                                              |      |

| Figure 4.10: NZ DAC waveform asymmetry.                                                        |      |

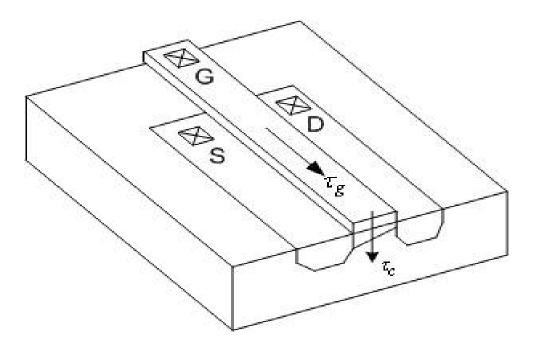

| Figure 4.11: The delay in a MOS transistor to respond to a signal applied to its gate          |      |

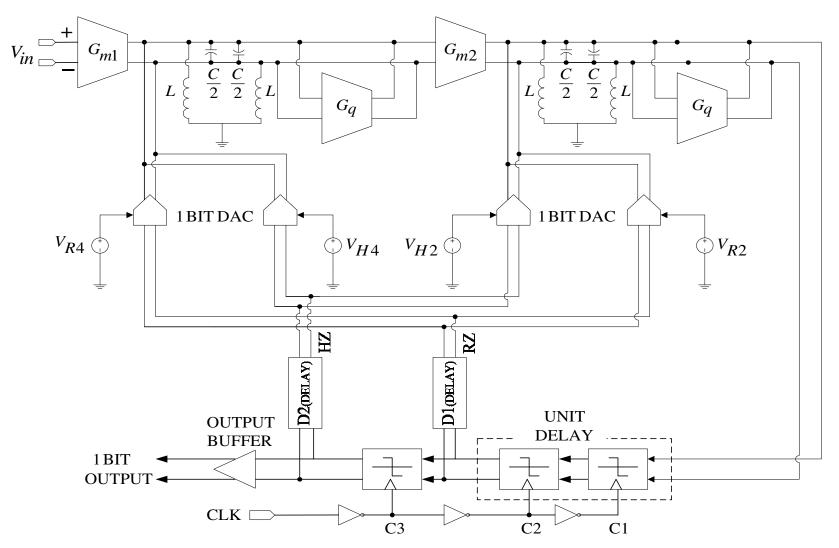

| Figure 5.1: Circuit topology of 4 <sup>th</sup> bandpass continuous time Sigma Delta modulator |      |

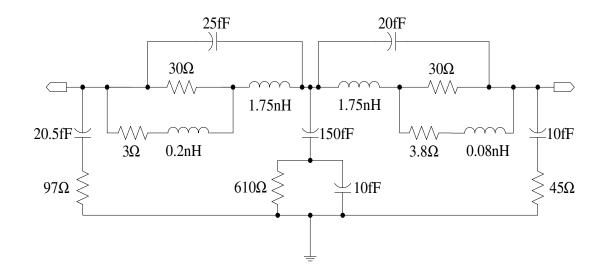

| Figure 5.2: Equivalent circuit of an integrated inductor                                       |      |

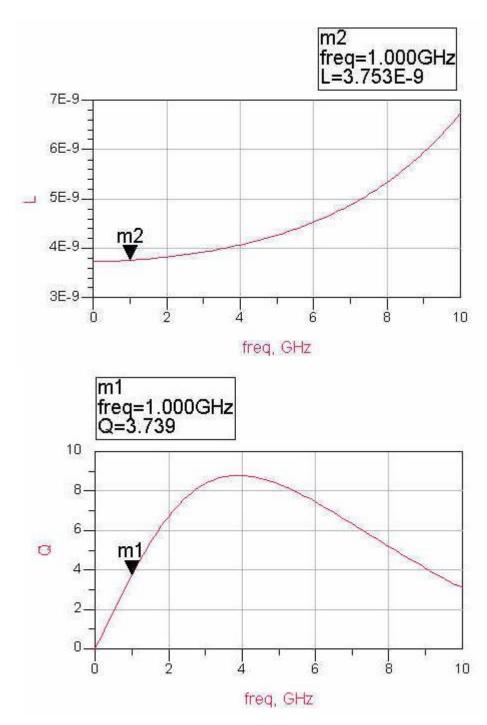

| Figure 5.3: The simulated value of L and $Q_L$ of the integrated inductor                      | . 53 |

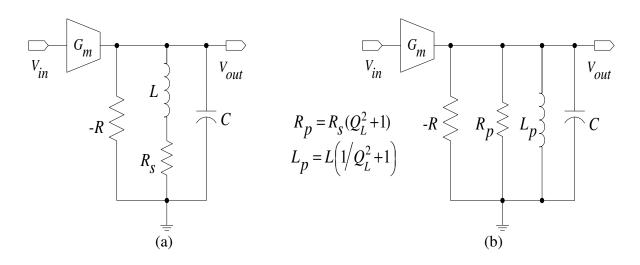

| Figure 5.4: Bandpass LC resonator                                                              | . 54 |

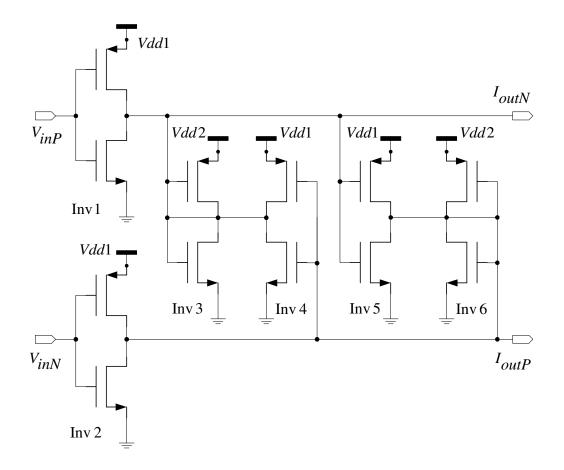

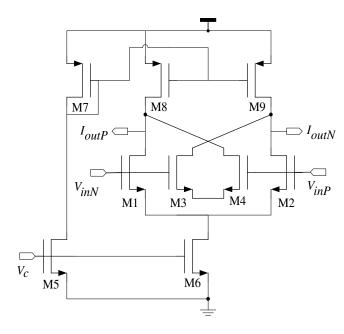

| Figure 5.5: A VHF transconductor with negative resistance                                      | . 55 |

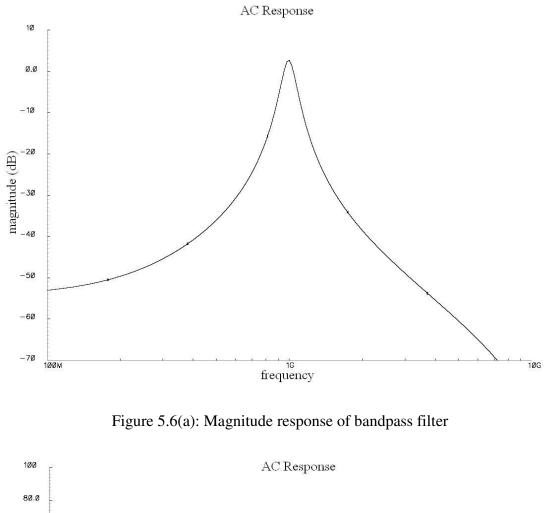

| Figure 5.6(a): Magnitude response of bandpass filter                                           | . 56 |

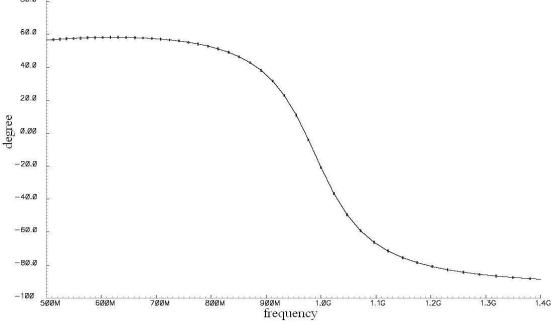

| Figure 5.6(b): Phase response of bandpass filter                                               | . 56 |

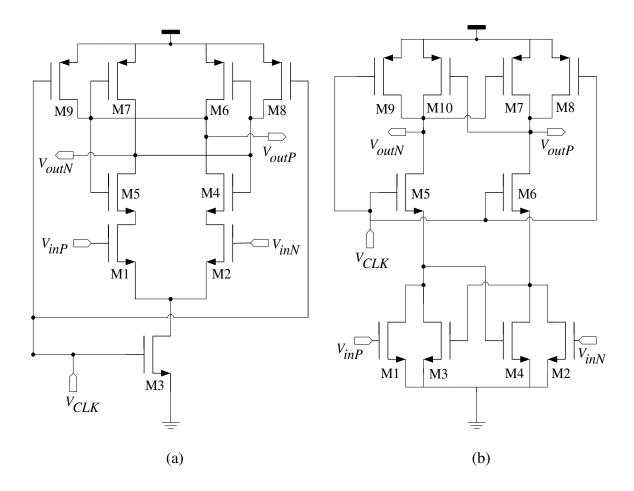

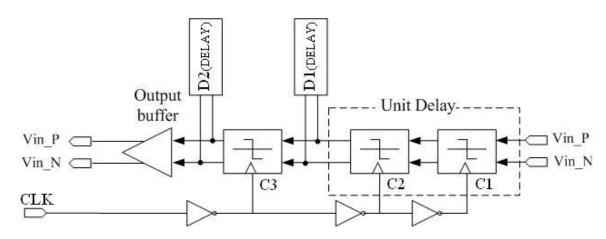

| Figure 5.7: The RZ latches used as quantizers in feedback loop                                 | . 57 |

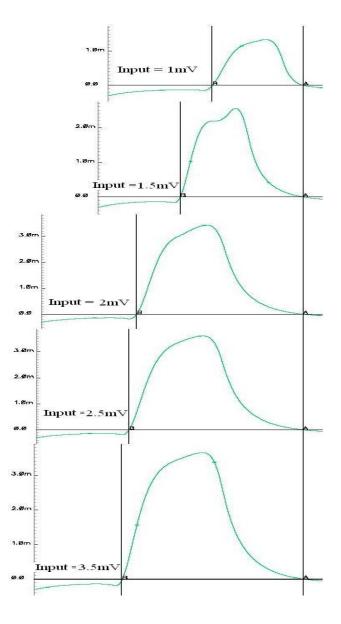

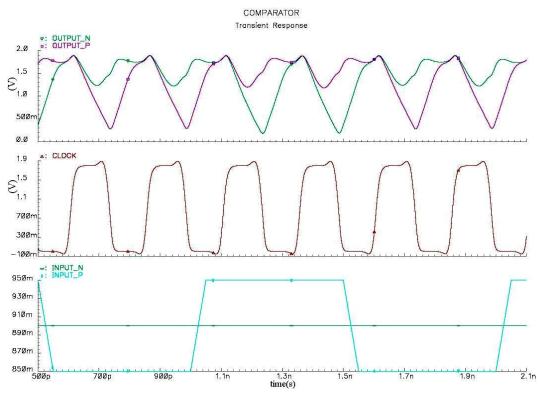

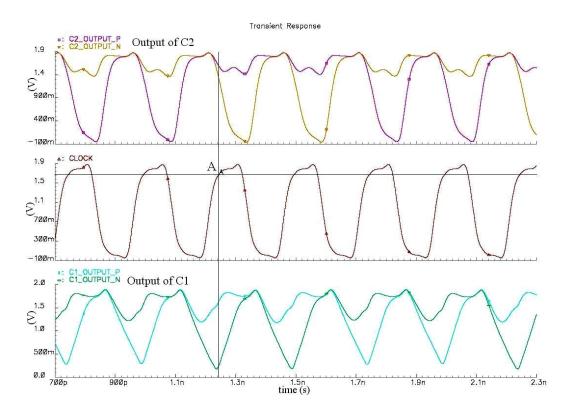

| Figure 5.8: Simulation of the comparator.                                                      | . 59 |

| Figure 5.9: Reducing metastability by digital implementation of unit delay                     | . 59 |

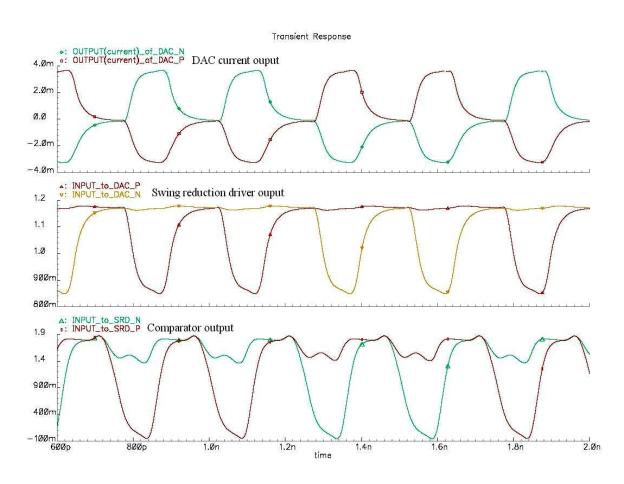

| Figure 5.10: High speed current switched DAC                                                   |      |

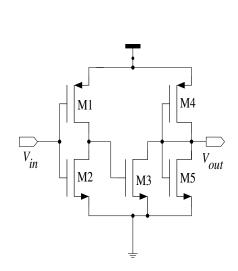

| Figure 5.11: Swing reduction driver.                                                           |      |

| Figure 5.12: Output of swing reduction driver and DAC current pulse                            | . 61 |

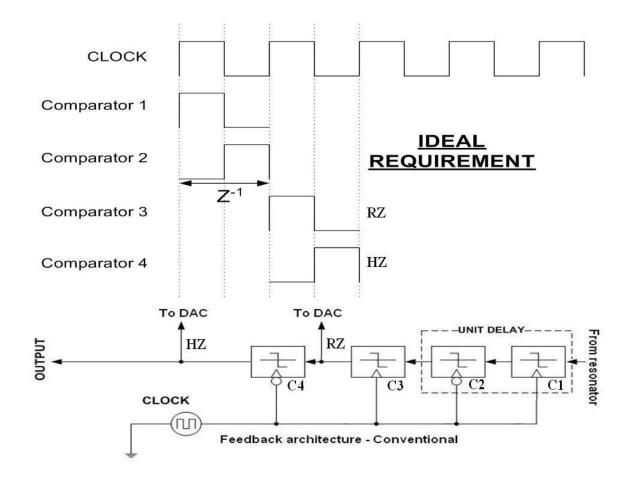

| Figure 5.13: Conventional feedback architecture in ideal situation.                                      | . 62 |

|----------------------------------------------------------------------------------------------------------|------|

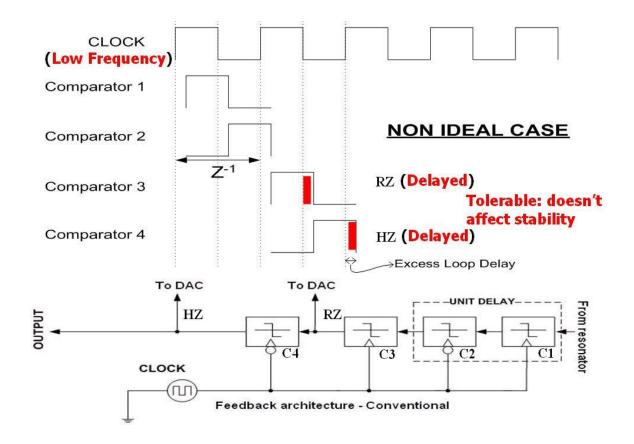

| Figure 5.14: Conventional feedback architecture under non ideal situation and when                       |      |

| clock frequency is low.                                                                                  | . 63 |

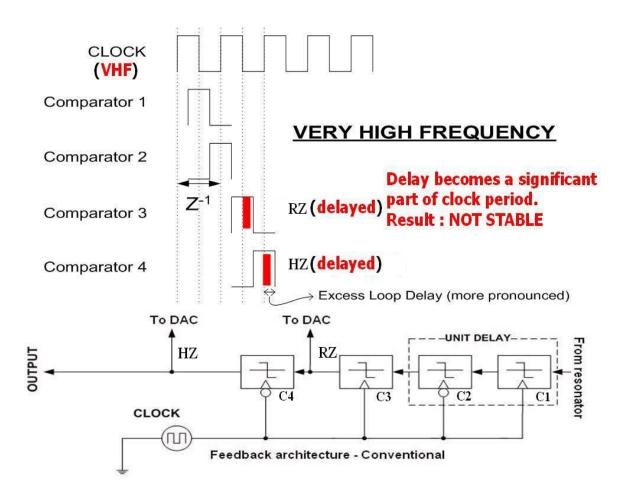

| Figure 5.15: The non ideal conventional feedback architecture with very high frequence                   | ;y   |

| (VHF) sample clock.                                                                                      | . 64 |

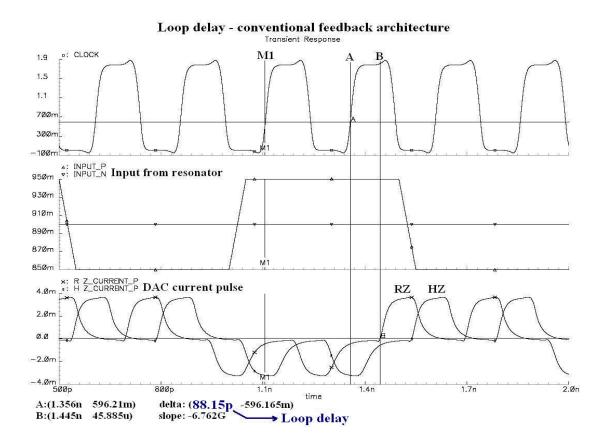

| Figure 5.16: Loop delay of a conventional feedback architecture                                          |      |

| Figure 5.17: The proposed feedback architecture                                                          | 65   |

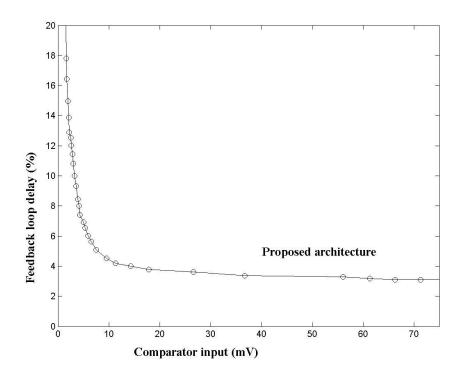

| Figure 5.18: Simulation of the proposed feedback architecture.                                           | . 68 |

| Figure 5.19: Comparison of the loop delays from proposed and conventional feedback                       |      |

| structures.                                                                                              | . 68 |

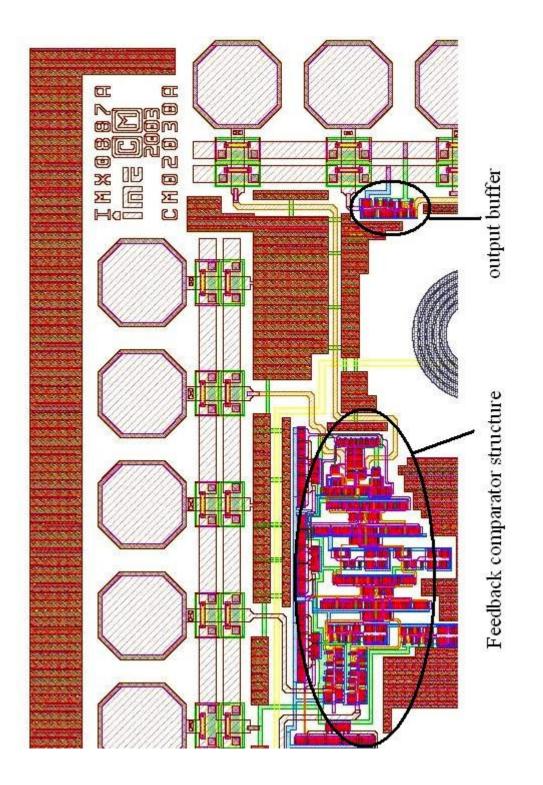

| Figure 5.20: The Layout of 4 <sup>th</sup> order continuous time bandpass $\Sigma\Delta M$               | . 71 |

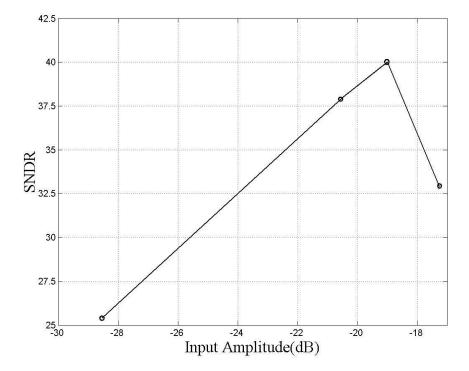

| Figure 5.21: Dynamic range plot                                                                          |      |

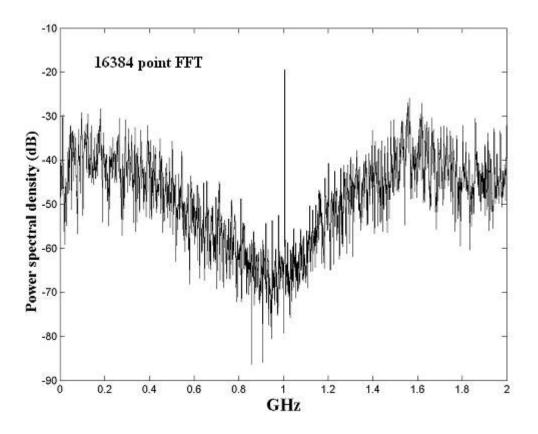

| Figure 5.22: Spectrum of the output bit stream from a 4 <sup>th</sup> order CT bandpass $\Sigma\Delta M$ | . 73 |

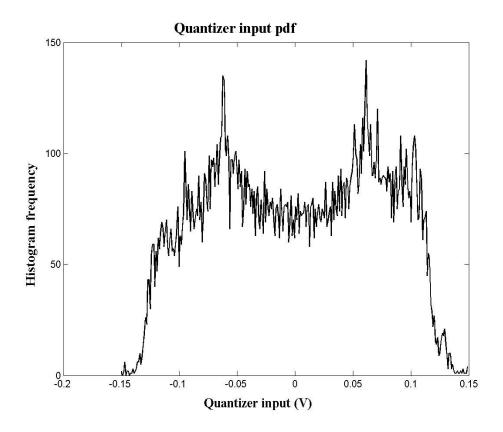

| Figure 5.23: Quantizer input pdf                                                                         | . 74 |

| Figure 5.24: Loop delay of the proposed feedback architecture for larger inputs                          | . 75 |

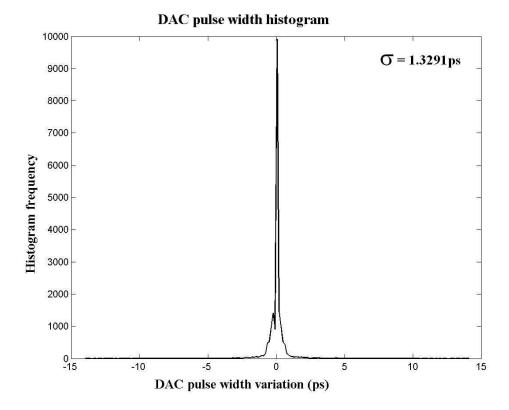

| Figure 5.25: DAC pulse width variance pdf.                                                               | . 75 |

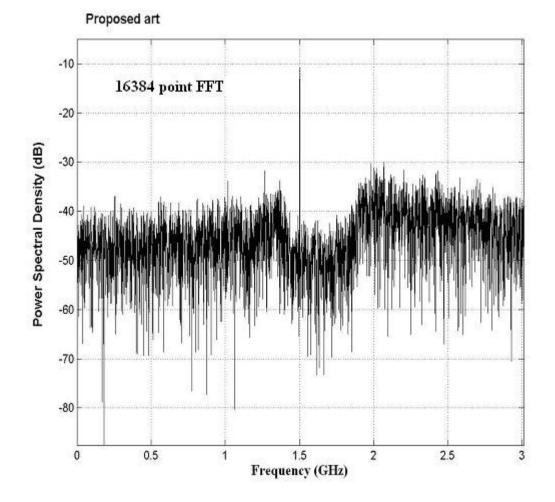

| Figure 5.26: Power Spectral Density of output bit stream                                                 | . 76 |

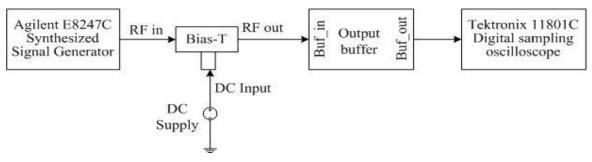

| Figure 6.1: Test setup of output buffer.                                                                 |      |

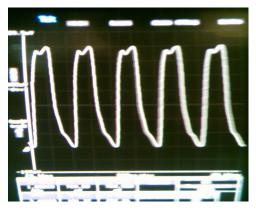

| Figure 6.2: Buffer output at1GHz                                                                         |      |

| Figure 6.3: Buffer output at 4GHz                                                                        | . 79 |

| Figure 6.4: Feedback comparator structure to be tested.                                                  | . 80 |

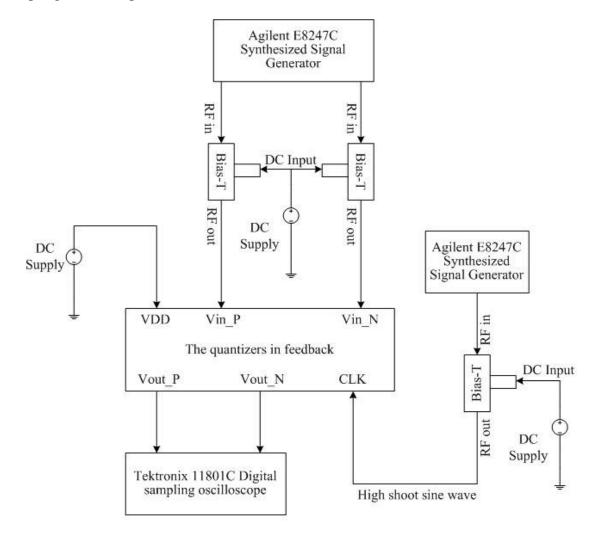

| Figure 6.5: Test setup                                                                                   | . 81 |

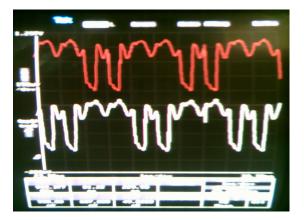

| Figure 6.6: Feedback comparator structure at 1GHz                                                        | .80  |

| Figure 6.7: Feedback comparator structure at 2.7GHz                                                      | . 82 |

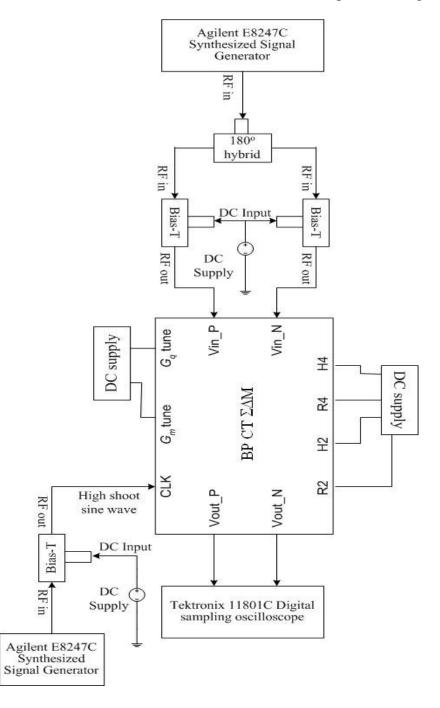

| Figure 6.8: Test setup for BP CT $\Sigma \Delta M$                                                       | . 84 |

# List of Tables

| Table 1.1: Modulator targeted performance                                          | 5 |

|------------------------------------------------------------------------------------|---|

| Table 2.1: Review of existing research in very high frequency CT $\Sigma \Delta M$ |   |

| Table 5.1: Simulation results                                                      |   |

| Table 5.2: Simulation results for higher sampling frequency                        |   |

| Table 6.1: Testing output buffer                                                   |   |

| Table 6.2: Test results of the feedback comparator structure                       |   |

# List of Abbreviations

| ADC    | Analog-to-Digital Converter                       |

|--------|---------------------------------------------------|

| BJT    | Bipolar Junction Transistor                       |

| СТ     | Continuous-Time                                   |

| DAC    | Digital-to-Analog Converter                       |

| ΣΔΜ    | Sigma Delta Modulator                             |

| BP     | Band Pass                                         |

| LP     | Low Pass                                          |

| STF    | Signal Transfer Function                          |

| NTF    | Noise Transfer Function                           |

| HBT    | Hetero-junction Bipolar transistor                |

| OSR    | Over Sampling Ratio                               |

| SNR    | Signal to Noise Ratio                             |

| RMS    | Root Mean Square                                  |

| PDM    | Pulse Density Modulation                          |

| DT     | Discrete-Time                                     |

| SC     | Switched Capacitor                                |

| SNDR   | Signal to Noise and Distortion Ratio              |

| RZ     | Return to Zero                                    |

| HZ     | Half return to Zero                               |

| NZ     | Non return to Zero                                |

| DR     | Dynamic Range                                     |

| VHF    | Very High Frequency                               |

| RF     | Radio Frequency                                   |

| IF     | Intermediate Frequency                            |

| DSP    | Digital Signal Processing                         |

| Gm-C   | Transconductor-Capacitor                          |

| OPAMP  | Operational Amplifier                             |

| Q      | Quality factor                                    |

| LO     | Local Oscillator                                  |

| CMOS   | Complementary Metal Oxide Semiconductor           |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PCB    | Printed Circuit Board                             |

# Chapter 1 Introduction

The Analog to Digital Converters (ADC) are well applied in many applications to function as converting an analog waveform into a digital waveform (digital codes) at particular sampling instances. The ADC is a key component in many electronic system, since by nature all waveforms exist inherently in analog domain while in electronic systems all computations are mainly carried out in digital domain which is a more robust, flexible and reliable domain for signal processing.

# 1.1 Role of ADC in Radio Receivers – Moving towards "Less Analog More Digital"

This thesis is much focused around the role of ADCs in radio receiver systems, which have become the part and parcel of everyday life. The position of ADC in a radio receiver is crucial in deciding whether a particular function of the receiver is to be implemented using analog or digital circuits. By studying the different radio receiver architectures the above fact becomes easier to understand.

#### 1.1.1 Superheterodyne Receiver with baseband ADC

Traditional superheterodyne receiver architecture is shown in Fig. 1.1(a). The antenna signal is filtered by a wide bandpass filter and amplified by a low-noise amplifier. The desired Radio Frequency (RF) channel is selected by tuning the  $F_{LO}$  and mixing it down to a lower intermediate frequency (IF). The channel filter passes the desired IF channel

suppressing the adjacent channels by about 30-40dB. After amplification the signal is quadrature mixed into In-phase and Quadrature-phase channels at baseband, which is then anti-alias filtered and digitized. Further signal processing is done using Digital Signal Processing (DSP). Requirements for such baseband ADC regarding dynamic range, bandwidth and linearity are relaxed due to the filters which are preceding it. Sampling the baseband signal also leads to lower sampling rate, resulting in low power consumption.

#### 1.1.2 Heterodyne receiver with IF digitizing ADC

The evolution of bandpass ADCs made them to be placed at a position closer to the antenna. An IF digitizing receiver is shown in Fig 1.1(b) where in, a bandpass wideband ADC sits well before the channel filter digitizing all the channels. The channel selection and quadrature modulation are implemented in DSP, with low-power consumption, prefect linearity and matching for excellent image rejection performance. Moreover IF ADC is insensitive to DC offset and low-frequency noise. But the lack of analog prefiltering by the channel filter and amplification by Variable Gain Amplifier (VGA) places a heavy linearity and dynamic range requirements on the IF ADC. The sampling rate is high due to IF digitization. This results in a systems that is less power efficient than a baseband ADC. Furthermore, the linearity and dynamic range requirements are more difficult to meet at higher frequencies [17].

#### 1.1.3 RF digitization

The RF digitizing receiver which is in focus of current research and also in this thesis is shown in the Fig. 1.1(c). The only analog components are the RF bandpass filter and the Low Noise Amplifier (LNA). All the other functions namely the IF frequency translation, channel filtering, and quadrature demodulation are done in DSP. This ADC should have a high dynamic range, high linearity and large bandwidth at RF frequencies. Since the sampling rate of the ADC is in GHz range the power consumption would be extremely heavy [13].

Figure 1.1: Radio receiver architectures

As illustrated in Fig. 1.1, the current research trend is moving from radio receiver architectures which had less digital components but more analog components to architectures employing more digital components than analog components. This is achieved generally (there might be unexplored other ways) by moving the ADC closer and closer to the antenna.

#### **1.2 Motivation and problem statement**

As discussed above, the state of art is to achieve an ADC which is very close to the antenna leading to an 'all-digital radio'. Pushing more functions of the receiver into DSP will tend to a system which is more robust to temperature and process variation with reduced cost, size, weight and power dissipation. Performing all the functions digitally leads to a 'Programmable Software Radio'. Such programmability allows a single set of hardware to be used for multi-standard receiver by just altering the software in it. A few implementations of very high frequency bandpass Sigma Delta modulators in bipolar RF transistors of SiGe HBT [7], AlGaAs/GaAs HBT [20] and InP HBT [21] have been reported. This limits the monolithic integration of the ADC and the digital signal processing modules (which are prevailingly designed in CMOS) on the same chip in a RF receiver as shown in Fig. 1.1(c).

#### **1.2.2** Objective and scope of the research

The Objective of this research is to implement a CMOS continuous–time bandpass  $f_s/4$ Sigma Delta modulator for RF front end, which digitizes signals centered at 1GHz with a sampling frequency of 4GHz. This is the first time that such a very high frequency is ever tried in CMOS bandpass Sigma Delta ADC. However, literature search shows that CMOS bandpass Sigma Delta modulators realized in the past were up to a maximum sampling frequency of 400MHz with the signal centered at 100MHz [40]. The targeted performance of the modulator to be designed in this thesis is shown in the Table 1.1.

| 0.18µm CMOS |

|-------------|

| 1GHz        |

| 4GHz        |

| 500kHz      |

| 6 bits      |

|             |

Table 1.1: Modulator targeted performance

The scope of the research would be,

- 1. To study and identify the suitability of CMOS over bipolar at very high frequencies.

- 2. The design issues involved when employing CMOS in very high frequencies.

- 3. System design and simulation of a band pass  $f_s/4$  Sigma Delta modulator to meet the above specification.

- 4. To simulate the non-idealities that may affect the above system when implemented practically for operating at high frequencies.

- 5. To investigate design solution for very high frequency CMOS applications.

- To design the system in 0.18µm CMOS technology, taking into account the practical non-idealities and simulation in HSpice.

- 7. Layout, fabrication and testing of the design.

#### **1.3 Organization of the thesis**

Following the above introduction to the role of ADCs in radio receivers and the motivation behind this research, chapter 2 provides the basics of quantization which is the key function of an analog to digital converter. The Sigma-Delta modulator is introduced with the oversampling and noise shaping concepts explained in detail. Among the in numerable choices of ADCs, the continuous-time bandpass  $f_s/4$  Sigma-Delta modulator is shown to be the better choice for RF digitization.

In chapter 3, the design of a continuous-time bandpass  $f_s/4$  Sigma-Delta modulator is discussed followed by development and simulation of an ideal model in MATLAB Simulink. Chapter 4 explains the different non idealities such as loop delay, quantizer metastability, clock jitter etc. that exist in practical circuit realization of a continuous time modulator. The performance degradation effects of such non idealities on the modulator are also described.

The modulator realization in circuit is elaborated in chapter 5. A circuit topology to realize the ideal modulator and which also circumvents most of the non ideal issues is explained in detail. The individual circuit components comprising the circuit topology are also discussed. Some layout issues in high speed mixed signal design are listed. The post-layout simulation performance of the modulator is also provided along with some analysis for the results obtained.

In an attempt to first test the different parts of the modulator individually, chapter 6 gives the test results of a output buffer and a feedback comparator structure fabricated in 0.18 $\mu$ m CMOS process. In chapter 7 a comparison of this work with the other reported very high frequency CT $\Sigma\Delta$ Ms is tabulated along with suggestions for future work.

### Sigma Delta Modulator – An Overview

In this chapter, the basic concepts involved in analog-to-digital conversion and in a Sigma-Delta modulator has an ADC are looked upon. The different types of  $\Sigma\Delta M$  are also discussed along with their respective advantages and disadvantages. Among the available design choices a suitable one is chosen for the purpose of analog to digital conversion in Radio Frequency (RF) receiver front ends.

#### 2.1 Quantization noise

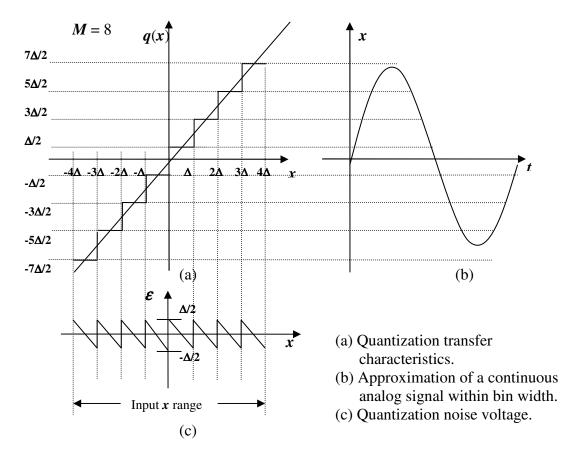

The quantization is often considered as the core of analog-to-digital conversion. A general quantization transfer characteristics is shown in Fig. 2.1(a). The quantization error noise ( $\varepsilon$ ) occurs due to the fact that while digitizing, the continuous analog waveform Fig. 2.1(b), is approximated within the quantization levels or the bin width ( $\Delta$ ). Let *M* be the no. of quantization levels and *x* be the input signal bonded between [- $M\Delta/2$ ,  $M\Delta/2$ ] so that the quantizer is not overloaded. The quantization noise rising from such a non-overloaded quantizer is called granular noise and the quantized signal q(x) can be written of the form [5],

$$q(x) = G x + \mathcal{E} \tag{2.1}$$

*G*, gain, is the slope of the straight line passing through the center of the quantization characteristics curve. And the granular noise  $\varepsilon$  is bounded between  $\pm \Delta/2$  as shown in Fig. 2.1(c). This noise error  $\varepsilon$  is completely defined by the input, but if the input changes

randomly between samples by amounts comparable with the threshold spacing without overloading, then the error is largely uncorrelated from sample to sample and has equal probability of lying anywhere in the range  $\pm \Delta/2$  and can be considered as a white noise.

It is reported in [3] that the white noise assumption of the quantization noise provided a good approximation to reality if in particular,

- 1. The quantizer does not overload,

- 2. The quantizer has a large number of levels,

- 3. The bin width is small and

- 4. The probability distribution of pairs of input samples is given by a smooth probability density function.

Figure 2.1: Quantization

If the quantization error  $\varepsilon$  is treated has a white noise then its mean square value can be calculated from,

$$\varepsilon_{\rm rms}^2 = \int_{-\Delta/2}^{+\Delta/2} \varepsilon^2 d\varepsilon = \frac{\Delta^2}{12}$$

(2.2)

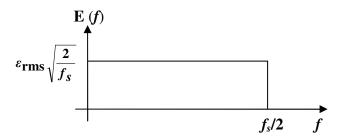

When a quantized signal is sampled at a frequency  $f_s = 1/T$ , all of its quantization noise power folds into the frequency band  $0 \le f \le f_s/2$ , assuming one-sided representation of frequencies. Then, if the quantization noise is white, the spectral density of the sampled noise is given by [3],

$$E(f) = \varepsilon_{\rm rms} \left(\frac{2}{f_s}\right)^{1/2} = \varepsilon_{\rm rms} \sqrt{2T}$$

(2.3)

The quantization noise spectral density is as shown in Fig. 2.2. Examining equation (2.3) it is evident that by increasing the sampling frequency, the amount of quantization noise that an ADC introduces to an analog signal can be reduced, as detailed in Sec. 2.2.2. Increasing the sampling frequency spreads out the quantization noise spectral density over a wider range of frequencies (see Fig. 2.2) with a corresponding reduction in amplitude. However the sampling frequency doesn't affect the total Root Mean Square (RMS) quantization voltage (i.e.) the area under the quantization noise spectrum.

Figure 2.2: Quantization noise spectral density.

#### 2.2 Sigma Delta Modulator – Pulse Density Modulation

The Evolution of Sigma Delta Modulator ( $\Sigma\Delta M$ ) dates back to 1962, when Inose et al. [18], [19] proposed the idea of including an integrator in front of a delta modulator, to eliminate slope overload. Hence the name "Sigma Delta Modulator", "Sigma" to denote the integrator, followed by a "Delta Modulator", was probably given to the system. The idea of reducing the quantization noise by using a feedback [33] also forms a basic operation of this system.

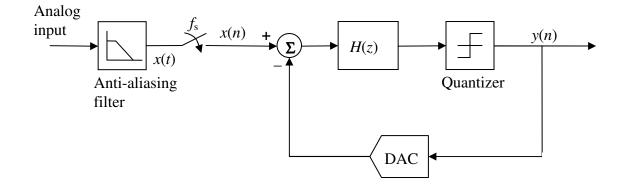

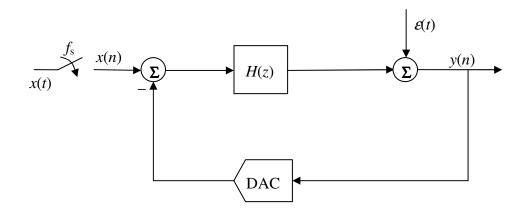

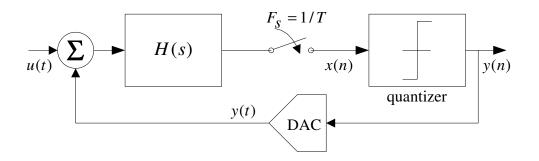

A  $\Sigma\Delta M$  has three basic components as shown in Fig. 2.3:

- 1. A loop filter or a loop transfer function H(z).

- 2. A clocked quantizer.

- 3. A feedback Digital-to-Analog Converter (DAC).

Figure 2.3: The basic components of Sigma Delta modulator

The  $\Sigma\Delta M$  shown in Fig. 2.3 is a Discrete-Time (DT) modulator. The sampled input x(n) is fed to the quantizer via a loop filter H(z), and the quantizer output y(n) is fed back through a DAC and subtracted from the input. This feedback forces the average value of the quantized signal to track the average input. Any difference between them accumulates

in the integrator and eventually corrects itself. In a single bit  $\Sigma\Delta M$ , the output of the quantizer oscillates between +1 and -1 and the input signal is represented by the density of ones. This signal is called a Pulse Density Modulated (PDM) signal. Figure 2.4 illustrates this fact, where a sine wave of 122.07Hz and 0.7V amplitude is sampled at 1MHz and the output from the quantizer is averaged over 16 samples. A loop filter of transfer function H(z) = 1 / (z-1) is used and the DAC is assumed to be unity. It is evident that the averaged value of the quantizer signal tracks the input sine wave. This averaging of the PDM signal output from a  $\Sigma\Delta M$  is nothing but a lowpass function and it is usually performed by a decimator following the modulator. The modulator plus the following decimator forms the whole ADC. All the discussions in this thesis will be pertaining to the modulator, which forms the important part of the ADC.

Figure 2.4: The averaged quantizer output signal tracking the modulator sine input

To reduce the quantization noise in the signal band, the  $\Sigma\Delta M$  uses two main concepts namely (i) Noise shaping and (ii) Oversampling, which are explained below.

#### 2.2.1 Noise Shaping

In Fig. 2.3, the quantizer is the only nonlinear circuit in an otherwise linear system. This makes the behavior of  $\Sigma\Delta M$  very complicated to investigate analytically [16]. Hence we assume that the quantization noise is independent of the modulator input signal x(n) (as explained in Sec. 2.1) and replace it with an additive white noise  $\varepsilon(t)$  as shown in the Fig. 2.5.

Figure 2.5: Linearizing the quantizer in  $\Sigma\Delta M$

The output y(n) can now be written in terms of two inputs x(n) and  $\varepsilon(t)$ .

$$Y(z) = \frac{H(z)}{1 + H(z)} X(z) + \frac{1}{1 + H(z)} \mathcal{E}(z)$$

(2.4)

$$Y(z) = STF(z)X(z) + NTF(z)\mathcal{E}(z)$$

(2.5)

where STF(z) and NTF(z) are the Signal Transfer Function and Noise Transfer Function respectively. From equations (2.4) and (2.5), two important conclusions can be deduced (i) the poles of loop filter H(z) becomes the zeros of noise transfer function NTF(z) (i.e.) if H(z) is lowpass filter then NTF(z) will be of high pass type. (ii) For any frequency where H(z) >> 1, then from equation (2.4)  $Y(z) \approx X(z)$  i.e. the output spectra equals to that of input at frequencies where the gain of H(z) is large.

Loop filter H(z) can be of a lowpass or a bandpass transfer function, which determines the type of modulator under design. Assuming a band pass case where,

$$H(z) = \frac{2z^2 + 1}{\left(z^2 + 1\right)^2}$$

(2.6)

then from eq. (2.4),

$$STF(z) = \frac{2z^2 + 1}{z^4 + 4z^2 + 2}$$

(2.7)

$$NTF(z) = \frac{(z^2 + 1)^2}{z^4 + 4z^2 + 2}$$

(2.8)

the magnitude response of STF(z) and NTF(z) from eq. (2.7) and (2.8) is plotted in the Fig. 2.6(a) and (b) respectively, against normalized frequency. It is evident that the STF(z) has a response similar to a band pass filter, while the response of NTF(z) resembles a band stop filter (this is due to the fact that the poles of H(z) becomes the zeros of NTF(z)).

If the input X(z) is centered at  $\omega_s/4$  where  $\omega_s$  is the sampling frequency, the signal transfer function STF(z) in eq. (2.7) passes the input without any attenuation as it is evident from Fig. 2.6(a). However, the quantization noise  $\varepsilon(z)$  rising due to the sampling of input X(z) is attenuated at  $\omega_s/4$  by the band stop nature of NTF(z) as shown in Fig. 2.6(b). Hence the resultant effect is that while passing the input signal undisturbed, the noise arising due to quantization is totally shaped away from the input signal band. This leads to an increase in Signal-to-Noise Ratio (SNR).

Figure 2.6(a): Magnitude of Signal Transfer Function STF(z)

Figure 2.6(b): Magnitude of Noise Transfer Function *NTF*(z)

#### 2.2.2 Oversampling

As observed from Fig. 2.6(b) the quantization noise  $\varepsilon$  is reduced only in a very small bandwidth when compared to the sampling frequency  $\omega_S$ . This needs that the sampling frequency to be very high. Say if a signal input *x* has a bandwidth of  $B_X$ , then its Nyquist frequency  $\omega_N = 2B_X$  should be such that,  $\omega_N \ll \omega_S$ . Hence the modulator samples the signal at a frequency much higher than its Nyquist frequency and such modulators are termed as over sampling modulators. A measure of how much the sampling frequency is higher than the Nyquist frequency is given by the Over Sampling Ratio (OSR),

$$OSR = \frac{\omega_S}{\omega_N} = \frac{\omega_S}{2B_X}$$

(2.9)

From equation (2.3) it is evident that as the sampling frequency  $\omega_S$  increases (or an increase in OSR), the quantization noise spectrum spreads out and the in band noise amplitude decreases. In general if *M* is the order of the loop filter H(z) then the rms noise in signal band is given by [5],

$$n_o = \mathcal{E}_{\rm rms} \frac{\pi^M}{\sqrt{2M+1}} \left(\frac{1}{\rm OSR}\right)^{M+1/2}$$

(2.10)

which falls by 3(2M+1) dB for every doubling of the sampling rate or the OSR, providing M+0.5 extra bits. In other words increasing OSR, decreases the in band noise and enhances the system performance.

To sum up, the basic idea of a  $\Sigma \Delta M$  can be stated as [6]: an analog input signal is modulated into a digital word sequence whose spectrum approximates that of the analog input well in a narrow frequency range, but which is otherwise noisy. The noise arising from the quantization of the analog signal is minimized by oversampling and noise shaping by the loop filter in the desired narrow frequency range.

#### 2.3 The choice of an ADC for RF front end

For an ADC to be used in RF front end of receivers, it should operate at very high frequencies, be highly tolerant to component mismatching and consume less power. Among the many types of ADCs reported, Flash and Sigma Delta are the well known very high speed ADCs. In an *N* bit Flash ADC [37], an input signal is compared with  $2^N$  reference voltages obtained with for instance a resistor string. The digital output word is obtained from the comparator outputs. The sampling rate is determined mainly by the comparator settling time and the accuracy is limited by the resistor matching and by the comparator offset voltages. Flash ADCs of 6-bit resolution, sampling at 1.3GHz have been reported [36]. Even though Flash ADCs can be used in very high speed conversion, their accuracy is ultimately limited by component matching and has a very complex circuitry compared to that of Sigma Delta converters.

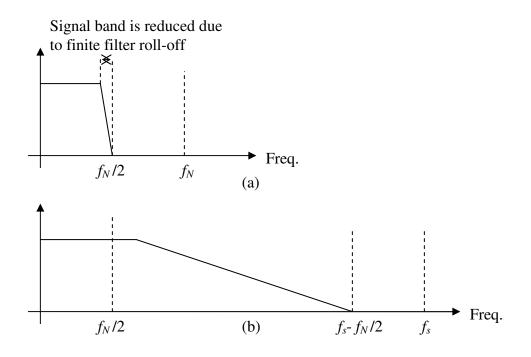

In the DT  $\Sigma\Delta M$  block diagram of Fig. 2.3, the analog input passes through an analog anti-aliasing filter first. This would be case for any ADC where the input signal is first band limited before sampling. In classical ADCs since the anti-aliasing filter has a finite filter roll-off, the signal band is smaller than half of the minimum Nyquist sampling rate (refer Fig. 2.7(a)). However in a Sigma Delta modulator the signal is sampled at a much higher rate than that of the Nyquist rate. From Fig. 2.7(b) it is clear that only signals above  $f_s$ - $f_N/2$  can alias with the signal band. As a result, a smoother pass band slope can be tolerated, which results in simpler filter design. Spurious signals at frequencies between  $f_N/2$  and  $f_s$ - $f_N/2$  are removed afterwards by the decimation filter. By this way comparing to other ADCs, in  $\Sigma\Delta$  ADC complex analog filter goes into digital domain, where things are much easier to design. Furthermore, the ability of a  $\Sigma\Delta M$  to perform narrowband conversion at a frequency other than dc make them particularly attractive than any other ADCs for radio applications (will be explained in the next section).

Figure 2.7: The anti-aliasing filter magnitude response

(a) Nyquist rate ADC(b) Over sampled ΣΔ ADC

#### 2.3.1 Band pass Sigma Delta modulator

The loop filter H(z) shown in Fig. 2.3 can be of a low pass type. In this case the quantization noise is shaped away from dc and the noise transfer function has a high pass shape. This modulator is called a Low Pass (LP)  $\Sigma\Delta M$ . Alternatively, the H(z) can be of bandpass type, say a resonator. In this case the quantization noise would be shaped away from the resonant frequency and the noise transfer function would be band stop function (as discussed in Sec. 2.2.1). Such a modulator is called a Band Pass (BP)  $\Sigma\Delta M$ . Given the two options, bandpass Sigma Delta modulators have been the best choice for ADC design, converting a very high frequency narrow band signal with high resolution [7], [13].

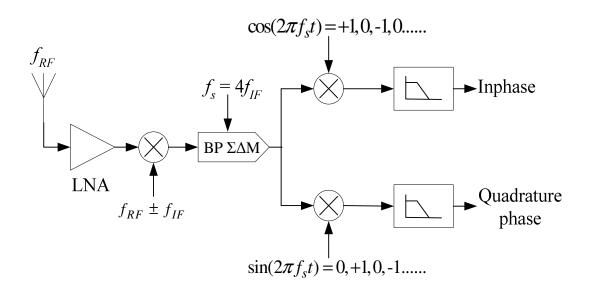

Further we choose the resonant frequency of the bandpass filter be at  $f_s/4$  for the reason stated below. Usually a bandpass ADC is used in conversion of an RF or IF signal to digital for processing and heterodyning in the digital domain, as shown in Fig. 2.8 [7]. Mixing to baseband digitally for In-phase and Quadrature-phase channel becomes particularly easy when the sampling frequency is chosen to be four times the input signal frequency because sine and cosine are sequences involving only ±1 and 0. This eliminates the complex multiplication in digital domain, because the processing on input digital bits would be easier and it is enough if we only change the sign (for multiplication with -1) or leave it as it is (for multiplication with +1) or make it zero (for multiplication with 0).

With the facts stated above, there are convincing reasons to choose a bandpass  $f_s/4$ Sigma Delta Modulator for digital conversion in RF front ends. But still one more design option, whether to choose a discrete time modulator or a continuous time modulator is yet to be decided upon, which will be detailed further.

Figure 2.8: An application of BP  $\Sigma \Delta M$

#### **2.3.2 DT ΣΔMs Vs CT ΣΔMs**

The bandpass loop filter in the  $\Sigma\Delta M$  can be implemented either as a Discrete-Time (DT) transfer function H(z) using Switched-Capacitor (SC) [24] circuits or as a Continuous-Time (CT) transfer function H(s) with transconductor-C [32] or LC [7] filters. A majority of reported  $\Sigma\Delta M$  are DT using switched capacitor loop filters. But to digitize signals at very high frequencies of GHz range continuous time modulator would be of a better choice for the reasons stated below.

- 1. At very high frequencies DT modulator becomes impractical as in that case the clock period is too short to charge the capacitors and to settle outputs of the op-amps of SC filters.

- 2. The sampling rate  $(f_s)$  of DT SC  $\Sigma\Delta M$  is limited to one-half or less of the unity gain bandwidth  $(f_u)$  of its opamps  $(f_s < f_u/2)$  [4]. However, it has been demonstrated that CT  $\Sigma\Delta M$  can have sampling rate greater than the unity gain bandwidth of its integrators  $(f_s > f_u)$  [10].

- 3. In a DT modulator, large glitches appear on op amp virtual ground nodes due to switching transients. While CT modulators are less prone to pickup digital noise.

- 4. To avoid aliasing, DT modulators usually require a separate anti-aliasing filter at their inputs as shown in Fig. 2.3. But in the case of CT modulators, the antialiasing is a built in inherent property of the modulator [32].

- 5. In a DT  $\Sigma \Delta M$ , the sampling occurs at the input and hence the sampling distortions are input referred, so they are not suppressed by the noise shaping behaviour of the feedback loop action. But in a CT modulator, sampling occurs inside the loop (described in the next chapter) and hence the sampling distortions

are shaped out of signal band by the noise shaping feedback loop action.

Considering the above facts, a continuous-time bandpass  $f_s/4$  Sigma Delta modulator seems to be a better choice for digitizing at RF frequencies and to achieve the performance shown in Table 1.1 of Chapter 1.

#### 2.3.3 Review of existing research in very high frequency CT $\Sigma \Delta M$

Hitherto research on design of very high frequency CT  $\Sigma\Delta M$  at gigahertz range has been an area which is very minimally explored. The literature search shows that all of the few reported implementations of such very high frequency Sigma Delta modulators were in bipolar RF transistors and no single implementation was in CMOS. This limits the monolithic integration of the ADC and the digital signal processing modules which are prevailingly designed in CMOS, on the same chip in a RF receiver. The table below shows the existing research work in very high frequency CT Sigma Delta modulator,

| Design               | Kaplan<br>[21]                    | Cherry<br>[7]                     | Jensen<br>[45]                    | Raghavan<br>[44]                  | Jayaraman<br>[20]                 | Olmos<br>[43]                    | Gao<br>[42]                       |

|----------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|----------------------------------|-----------------------------------|

| Process              | InP<br>HBT                        | 0.5μm<br>SiGe HBT                 | AlInAs /<br>GaInAs<br>SHBT        | AlInAs /<br>GaInAs<br>HBT         | AlGaAs /<br>GaAs<br>HBT           | InGaP /<br>InGaAs<br>HEMT        | 0.5µm<br>BJT                      |

| Type of modulator    | 4 <sup>th</sup> order<br>Bandpass | 2 <sup>nd</sup> order<br>Lowpass | 2 <sup>nd</sup> order<br>Bandpass |

| f <sub>s</sub> (GHz) | 4.3                               | 4                                 | 4                                 | 4                                 | 3.2                               | 5                                | 3.8                               |

| $f_c(GHz)$           | 1.3                               | 1                                 | 0.21                              | 0.18                              | 0.8                               | 0.04                             | 0.95                              |

| $f_b(MHz)$           | 200                               | 20                                | 60                                | 1                                 | 25                                | 100                              | 0.2                               |

| Performan<br>ce (dB) | 39<br>(SNDR)                      | 37<br>(SNR)                       | 50<br>(SNDR)                      | 75.8<br>(SNDR)                    | 41<br>(SNDR)                      | 43<br>(SNR)                      | 49<br>(SNDR)                      |

Table 2.1: Review of existing research in very high frequency CT  $\Sigma \Delta M$

### 2.4 Summary

The Sigma Delta modulator is a pulse density modulator, where the input signal is represented by the density of ones at the outputs. The fact that increasing the sampling frequency decreases in-band quantization noise is made used in the Sigma Delta modulator by oversampling the signal above Nyquist rate by an amount given by OSR. The in-band quantization noise is also further reduced by the noise shaping action of the feedback loop. The superiority of  $\Sigma\Delta Ms$  over other Nyquist rate modulators by having less complex circuitry and more tolerance to component mismatch makes them suitable for very high frequency applications. Based on the reported work, a CT BP  $\Sigma\Delta M$  with  $f_s/4$ as center frequency would be the better choice for sampling a bandpass signal at GHz frequencies in RF front ends.

## **Continuous-Time Bandpass Sigma Delta Modulator: System Design and Simulation**

This chapter discusses the design of continuous-time bandpass Sigma Delta modulator. The technique of transforming a DT  $\Sigma\Delta M$  into a CT  $\Sigma\Delta M$  according to the DAC pulse shape is explained by making use of impulse invariant transformation and state space method.

#### **3.1 Equivalence of continuous-time and discrete-time modulator**

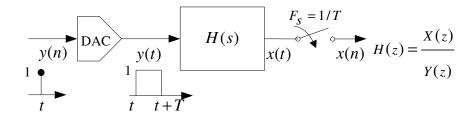

A continuous time sigma delta modulator is shown in Fig. 3.1. Unlike a DT  $\Sigma \Delta M$  where the sampling occurs at the input as shown in Fig. 2.3, in CT  $\Sigma \Delta M$  the sampling occurs inside the feedback loop before quantization. The open loop transfer function of CT  $\Sigma \Delta M$ , from the output of the quantizer y(n) to its input x(n) is shown in Fig. 3.2. Due to the presence of a sampler inside the feedback loop, the continuous time open loop transfer function has an exact equivalent discrete time transfer function H(z).

Figure 3.1: Block diagram of a continuous time Sigma Delta modulator

Figure 3.2: Open loop continuous time Sigma Delta modulator.

Hence the samples of the continuous time waveform at sampling instants as seen by the quantizer at its input is the same as the samples from a discrete time system of Fig. 2.3 with the equivalent DT transfer function H(z) as the loop filter. In other words a DT modulator can be transformed into a CT modulator provided that the quantizer sees the same samples for both the modulators. This is called impulse invariant transformation and can be expressed as [14],

$$Z^{-1}\{H(z)\} = L^{-1}\{G_D(s)H(s)\}\Big|_{t=nT}$$

(3.1)

or in time domain [31],

$$h(n) = [g_D(t) \otimes h(t)]|_{t=nT}$$

(3.2)

ensuring that the quantizer sees the same samples for both DT and CT systems. Here,  $G_D(s)$  is the impulse response of the DAC in feedback.

Due to the above equivalence of the DT and CT modulators, the noise shaping behavior, stability and other system performance of the continuous time  $\Sigma\Delta M$  can be designed and analyzed entirely in z domain. The resulting DT transfer function can be converted back to an equivalent CT system using the above impulse invariant transformation. It is worth noting that due to the presence of the impulse response of DAC in eq. (3.1), the transformation of a DT system to a CT system depends specifically on the feedback DAC pulse shape to be used.

#### **3.2 Design of a bandpass continuous-time modulator**

To design a continuous time modulator, we start with a discrete time lowpass transfer function which can be converted to a bandpass transfer function through the transformation [28],

$$z^{-1} \to -z^{-1} \frac{z^{-1} - \alpha}{1 - \alpha z^{-1}}$$

, where  $-1 < \alpha < 1$  (3.3)

To reduce the complexity of the decimation filter which follows the  $\Sigma\Delta M$  and to simplify the mixing done in a radio receiver in digital domain (explained in Sec. 2.3.1), a sampling frequency of  $f_s = 4f_o$ , where  $f_o$  is the modulator center frequency is chosen. This corresponds to the special case of  $\alpha = 0$  in eq. (3.3), leading to a low pass to bandpass transformation of  $z^{-1} \rightarrow -z^{-2}$ . The order of the bandpass transfer function obtained will be twice as that of the lowpass prototype, with the same SNR and identical stability properties. Applying the above transformation to a double integration low pass prototype,

$$H_{LP}(z) = \frac{-2z^{-1} + z^{-2}}{(1 - z^{-1})^2} \to H_{BP}(z) = \frac{2z^{-2} + z^{-4}}{(1 + z^{-2})^2}$$

(3.4)

$$H_{BP}(z) = z^{-1} \cdot \hat{H}_{BP}(z)$$

, where  $\hat{H}_{BP}(z) = \frac{2z^{-1} + z^{-3}}{(1+z^{-2})^2}$  (3.5)

a bandpass modulator with the same performance and stability as the low pass prototype is obtained.

To implement the above mentioned bandpass modulator in eq. (3.4), in continuous time either a transconductance-C (G<sub>m</sub>-C) filter or a LC resonator can be chosen. But the traditional G<sub>m</sub>-C filters cannot handle very high frequencies due to its limited bandwidth, hence the later choice of LC resonator structures of the form  $H(s) = As/(s^2+(\pi/2T)^2)$ , is

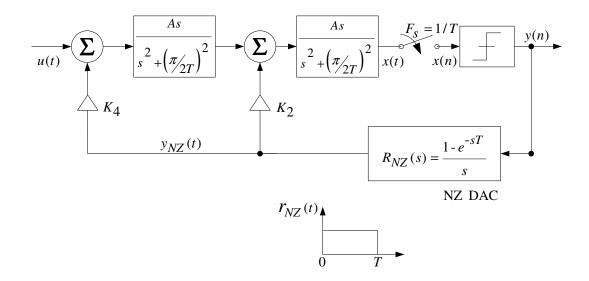

chosen to implement the bandpass loop filter. Cascading two such resonators would give a fourth order bandpass transfer function, which could be used to implement the required  $H_{BP}(z)$  in eq. (3.4), by applying a impulse invariant transform. Fig. 3.3 shows such a cascade, with a single feedback loop from a Non-return-to-Zero (NZ) DAC.

Figure 3.3: The fourth order bandpass CT  $\Sigma \Delta M$  which is not fully controllable.

This system is not fully controllable to implement the  $H_{BP}(z)$  as discussed further. The NZ DAC time domain pulse and its impulse response are also given in Fig. 3.3. Assuming  $A = \pi/2$  and normalizing the sampling time to T = 1, the open loop transfer function of the two loops that exist in Fig. 3.3 are,

$$K_{2} \cdot Z \left[ L^{-1}(R_{NZ}(s)H(s)) \Big|_{t=nT} \right] = K_{2} \frac{z^{-1}(1-z^{-1})}{1+z^{-2}}$$

(3.6)

second order loop with  $R_{NZ}(s)$ ,

$$K_4 \cdot Z \left[ L^{-1}(R_{NZ}(s)H(s)H(s)) \Big|_{t=nT} \right] = K_4 \frac{0.7854z^{-1} \left(1 - z^{-1} - z^{-2} + z^{-3}\right)}{\left(1 + z^{-2}\right)^2} \quad (3.7)$$

fourth order loop with  $R_{NZ}(s)$ ,

following the impulse invariant transformation, if we apply superposition to the above two open loops and equate them to  $H_{BP}(z)$  as in eq. (3.4), we end up in a situation were there are four numerator coefficients, but only two independent variables  $K_2$  and  $K_4$  to control them. In other words eq. (3.8) below cannot be solved

$$K_{2}\frac{z^{-1}(1-z^{-1})}{1+z^{-2}} + K_{4}\frac{0.7854z^{-1}(1-z^{-1}-z^{-2}+z^{-3})}{(1+z^{-2})^{2}} = \frac{2z^{-2}+z^{-4}}{(1+z^{-2})^{2}}$$

(3.8)

and so impulse invariance cannot be applied to the above modulator in Fig. 3.3 because the system is not fully controllable.

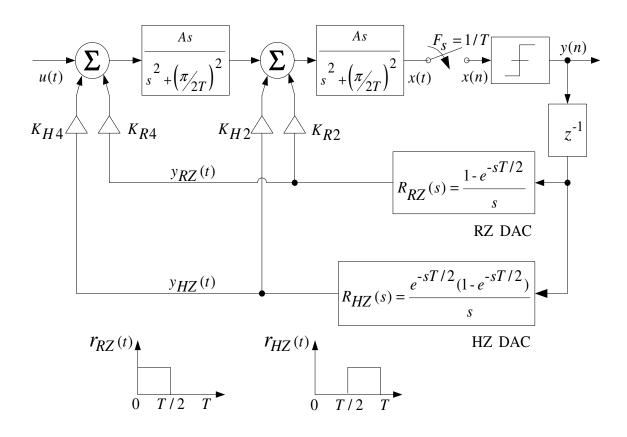

Hence a multi-feedback continuous time bandpass architecture [30] as shown in Fig. 3.4 is used to implement the fourth order discrete time transfer function  $H_{BP}(z)$ .

Figure 3.4: A multi feedback CT bandpass  $\Sigma\Delta M$  architecture.

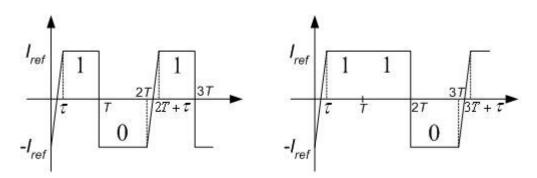

The DACs in the feedback produce a Return-to-Zero (RZ) and Half-return-to-Zero (HZ) pulse waveforms. The  $r_{RZ}(t)$  and  $r_{HZ}(t)$  waveforms with their respective impulse responses  $R_{RZ}(s)$  and  $R_{HZ}(s)$  are also shown in Fig. 3.4. Assuming again  $A = \pi/2$  and normalizing the sampling time to T = 1, the loop transfer functions of the four loops that exist in the multi feedback architecture are [31],

$$K_{R2} \cdot Z \left[ L^{-1} (R_{RZ}(s)H(s)) \Big|_{t=nT} \right]$$

=  $K_{R2} \frac{z^{-1} \left( \left( 1 - \frac{1}{\sqrt{2}} \right) - \frac{1}{\sqrt{2}} z^{-1} \right)}{1 + z^{-2}}$  (3.9)

second order loop with  $R_{RZ}(s)$ ,

$$K_{H2} \cdot Z \left[ L^{-1} (R_{HZ}(s)H(s)) \Big|_{t=nT} \right]$$

$$= K_{H2} \frac{z^{-1} \left( \frac{1}{\sqrt{2}} - \left(1 - \frac{1}{\sqrt{2}}\right) z^{-1} \right)}{1 + z^{-2}}$$

(3.10)

second order loop with  $R_{HZ}(s)$ ,

$$K_{R4} \cdot Z \left[ L^{-1} (R_{RZ}(s)H(s)H(s)) \Big|_{t=nT} \right]$$

$$= K_{R4} \frac{z^{-1} \left( 0.5077 \cdot 0.8330 z^{-1} + 0.0476 z^{-2} + 0.2777 z^{-3} \right)}{\left( 1 + z^{-2} \right)^2}$$

(3.11)

fourth order loop with  $R_{RZ}(s)$ ,

$$K_{H4} \cdot Z \left[ L^{-1} (R_{HZ}(s)H(s)H(s)) \Big|_{t=nT} \right]$$

$$= K_{H4} \frac{z^{-1} \left( 0.2777 + 0.0476z^{-1} - 0.8330z^{-2} + 0.5077z^{-3} \right)}{\left( 1 + z^{-2} \right)^2}$$

(3.12)

fourth order loop with  $R_{HZ}(s)$ .

The feedback coefficients  $K_{R2}$ ,  $K_{H2}$ ,  $K_{R4}$ ,  $K_{H4}$  can be obtained by applying superposition to the four feedback paths in eq. (3.9), (3.10), (3.11) and (3.12) then equating them to the DT bandpass transfer function  $\hat{H}_{BP}(z)$  as in eq. (3.5). In order to implement  $H_{BP}(z)$ , the remaining  $z^{-1}$  in eq. (3.5) is realized digitally in the feedback loop as shown in Fig. 3.4, with two latches. This reduces quantizer metastability by providing enough regeneration time for the quantizer to resolve small inputs.

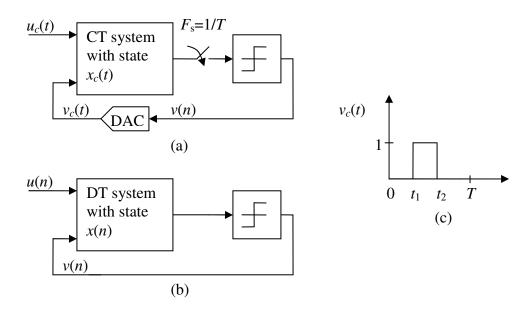

## **3.3** Designing the modulator using state space technique

Alternatively, the coefficients can be calculated using State-Space technique [27].

Figure 3.5: State space representation of  $\Sigma \Delta M$

(a) Continuous time modulator (b) Discrete time modulator(c) DAC pulse of the CT modulator

The state equations for the linear parts of the continuous time modulator shown in Fig.3.5 (a) is,

$$x'_{c}(t) = A_{c}x_{c}(t) + B_{c}\begin{bmatrix} u_{c}(t) \\ v_{c}(t) \end{bmatrix}$$

(3.13)

where  $x_c(t)$  is vector of N states of the modulator and  $x'_c(t)$  being its time derivative.  $A_c$  is a  $N \times N$  matrix,  $B_c$  is a  $N \times 1$  vector,  $u_c(t)$  is the input to the modulator and  $v_c(t)$  is the DAC pulse. Correspondingly the state equation for the linear parts of discrete time modulator shown in Fig. 3.5(b) is,

$$x(n+1) = A_d x(n) + B_d \begin{bmatrix} u(n) \\ v(n) \end{bmatrix}$$

(3.14)

If the DAC waveform  $v_c(t)$  is of the form shown in Fig. 3.5(c), then the continuous and discrete systems are equivalent provided,

$$A_d = e^{A_c} \text{ and } B_d = A_c^{-1} \left( e^{A_c \left( 1 - t_1 \right)} - e^{A_c \left( 1 - t_2 \right)} \right) B_c$$

(3.15)

With the help of MATLAB 'c2d' function one can easily find the zero order hold discrete equivalent of a continuous time system. The  $B_d$  matrix of the result can be modified according to eq. (3.15), so as to incorporate the DAC pulse shape. Note that for RZ pulse shape  $t_1 = 0$  and  $t_2 = 0.5$ , while for HZ pulse  $t_1 = 0.5$  and  $t_2 = 1$  in eq. (3.15) (assuming a normalization of sampling frequency to 1Hz). The MATLAB code to solve the above four equations (3.9), (3.10), (3.11) and (3.12) in state space is given in Appendix A.

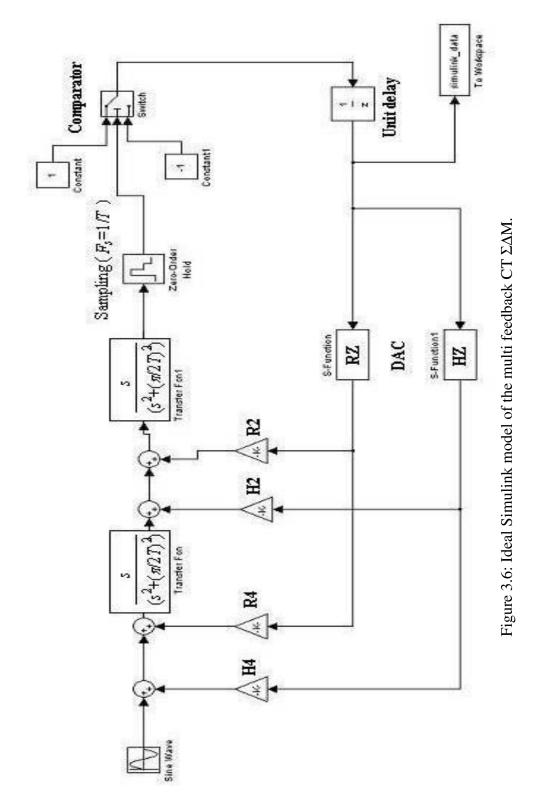

### 3.4 System modeling and simulation

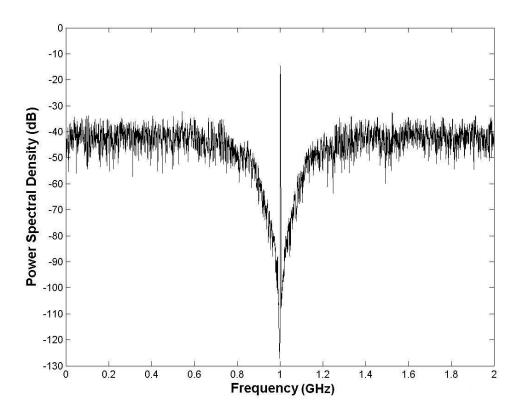

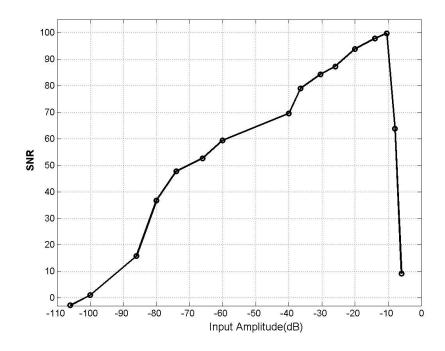

Using MATLAB the above multi feedback architecture was simulated with a Simulink model [34] as shown below in Fig. 3.6. The RZ and HZ DACs were modeled with S-functions (given in Appendix B) as available in Simulink. The power spectral density of the output bit stream is shown in Fig. 3.7 and the Dynamic Range (DR) is also plotted in Fig. 3.8. Using the ideal model, a DR of 90dB with a signal of bandwidth 500 kHz

centered at 1GHz is achieved (at a bandwidth of 20MHz a DR of 62dB is obtained), while sampling at 4GHz frequency.

Figure 3.7: Power spectral density of output from Simulink model

Figure 3.8: Dynamic range plot for the Simulink model of CT  $\Sigma \Delta M$ .

# 3.5 Summary

A better and easier way to design a CT  $\Sigma\Delta M$  is to choose a DT loop filter transfer function which meets the performance specifications, and then transform it to a CT loop filter using the impulse-invariant transformation based on the CT  $\Sigma\Delta M$  DAC pulse shape. At very high frequencies LC resonators are used to implement bandpass loop filters to obtain a BP CT  $\Sigma\Delta M$ . When using LC resonators in designing a fourth order bandpass modulator, two feedback paths with different DAC pulse shapes should be employed to have a fully controllable system. Its is easier to use MATLAB built in functions in designing the BP CT  $\Sigma\Delta M$  using impulse-invariant transformation through state space technique.

# Non-Idealities of Continuous-Time Sigma Delta Modulator and Design Issues at High Frequencies