**BEAMFORMING ULTRA-WIDEBAND TRANSMITTER**

### SAISUNDAR SANKARANARAYANAN (B.E., ANNA UNIVERSITY)

# A THESIS SUBMITTED

# FOR THE DEGREE OF MASTER OF ENGINEERING

### **DEPARTMENT OF ELECTRICAL & COMPUTER**

## ENGINEERING

## NATIONAL UNIVERSITY OF SINGAPORE

2009

### ACKNOWLEDGEMENTS

I would like to express my deep gratitude to my research supervisor, Dr. Heng Chun Huat, for the guidance and support that he gave me throughout the course of this research. I thank him for providing me an opportunity to work on this project. The ideas and feedback that he shared with me are invaluable to my research. Without his encouragement, support and guidance, this work would not have been possible.

I am grateful to all administrative and technical staff for the help and support they provided me. I would like to thank from the bottom of my heart all those who have supported me through their friendship and thoughtfulness.

I would finally like to thank my parents for their unwavering support and love which has been the source of strength for me.

## TABLE OF CONTENTS

| ABSTRACTix                                                                                               |

|----------------------------------------------------------------------------------------------------------|

| CHAPTER 1 : INTRODUCTION1                                                                                |

| 1.1 UWB and its applications1                                                                            |

| 1.2 Motivation                                                                                           |

| 1.3 Thesis contribution5                                                                                 |

| 1.4 Thesis organization5                                                                                 |

| CHAPTER 2 : UWB BEAMFORMING7                                                                             |

| 2.1 Advantages of UWB Beamforming7                                                                       |

| 2.2 UWB beamforming system basics and requirements10                                                     |

| CHAPTER 3 : EXISTING BEAMFORMING UWB TRANSMITTER                                                         |

| ARCHITECTURES                                                                                            |

|                                                                                                          |

| 3.1 Literature Review13                                                                                  |

| 3.1 Literature Review                                                                                    |

|                                                                                                          |

| CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE17                                                   |

| CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE17<br>4.1 Beamforming UWB transmitter architecture17 |

| CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE 17<br>4.1 Beamforming UWB transmitter architecture  |

| CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE17<br>4.1 Beamforming UWB transmitter architecture   |

| CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE17<br>4.1 Beamforming UWB transmitter architecture   |

| CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE17<br>4.1 Beamforming UWB transmitter architecture   |

| 4.2.5 All-digital UWB transmitter block             |    |

|-----------------------------------------------------|----|

| CHAPTER 5 : CMOS IMPLEMENTATION                     |    |

| 5.1 Digital delay element for beam former subsystem |    |

| 5.2 Fractional –N sigma-delta delay lock loop       |    |

| 5.2.1 Phase frequency detector and startup circuit  |    |

| 5.2.2 Charge pump                                   |    |

| 5.2.3 Loop filter                                   | 40 |

| 5.2.4 Voltage controlled delay line                 | 42 |

| 5.2.5 Sigma-delta modulator                         | 44 |

| 5.3 SAR delay lock loop                             | 44 |

| 5.4 Digital calibration circuit                     | 45 |

| 5.5 All-digital UWB transmitter                     | 54 |

| 5.5.1 Transmitter delay line                        | 54 |

| 5.5.2 Edge combiner                                 | 55 |

| 5.5.3 Digital PA and pulse shaping                  | 57 |

| 5.6 Full system simulation results and discussion   | 62 |

| CHAPTER 6 : CONCLUSION                              | 76 |

| 6.1 Thesis summary                                  | 76 |

| 6.2 Future recommendations                          | 77 |

| REFERENCES                                          | 79 |

| APPENDIX A : MATLAB MODELS AND CODES                |    |

| APPENDIX B : VERILOG CODES                          | 91 |

## LIST OF FIGURES

| Figure 1.1: Applications of UWB in short range wireless communications and ranging  |

|-------------------------------------------------------------------------------------|

| [33]                                                                                |

| Figure 1.2: Typical imaging system                                                  |

| Figure 1.3: Beamforming in imaging system4                                          |

| Figure 2.1: Indoor UWB emission mask                                                |

| Figure 2.2: Comparison of UWB and narrow band array pattern10                       |

| Figure 2.3: UWB beamforming system                                                  |

| Figure 2.4: UWB array with true time-delay element                                  |

| Figure 3.1: UWB beamforming system from [4]13                                       |

| Figure 3.2: Electronic beam steering subsystem from [1]14                           |

| Figure 4.1: Proposed beamforming UWB transmitter architecture                       |

| Figure 4.2: UWB pulse and its spectrum from MATLAB simulations19                    |

| Figure 4.3: UWB beam steering from MATLAB simulations20                             |

| Figure 4.4: Beamforming delay subsystem                                             |

| Figure 4.5: Fractional-N sigma-delta DLL architecture                               |

| Figure 4.6: VCDL used in sigma-delta DLL                                            |

| Figure 4.7: 2 <sup>nd</sup> order sigma-delta modulator                             |

| Figure 4.8: 2 <sup>nd</sup> order sigma-delta modulator spectrum                    |

| Figure 4.9: Fractional-N sigma-delta DLL settling and delay generation              |

| Figure 4.10: SAR DLL architecture                                                   |

| Figure 4.11: All-digital UWB transmitter architecture                               |

| Figure 5.1: Digital delay element for beam former subsystem architecture (6-bits)34 |

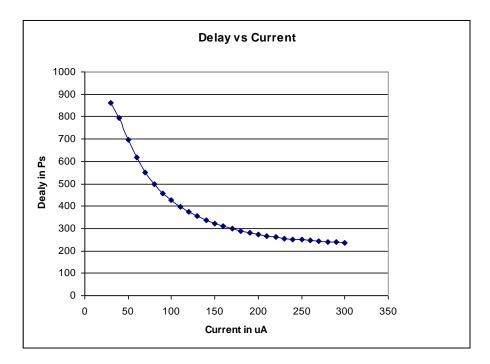

| Figure 5.2: Delay vs. Current in current starved inverters                          | 35    |

|-------------------------------------------------------------------------------------|-------|

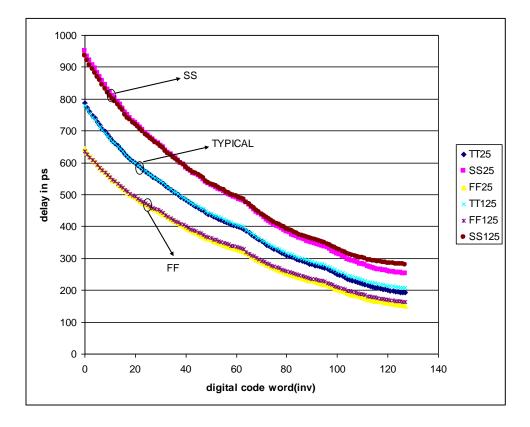

| Figure 5.3: Cadence corners/temperatures simulation of digital delay element        | 37    |

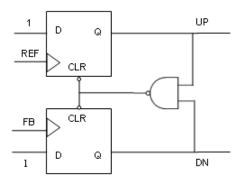

| Figure 5.4: Conventional phase frequency detector                                   |       |

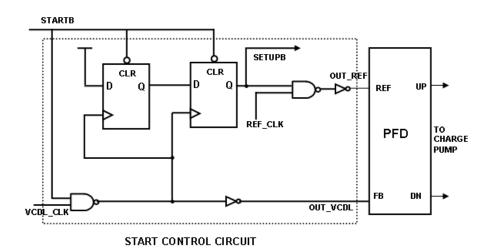

| Figure 5.5: PFD and start-controlled circuit                                        |       |

| Figure 5.6: Simulation of start controlled circuit with PFD                         | 39    |

| Figure 5.7: Schematic of charge pump adopted from [29].                             | 40    |

| Figure 5.8: Loop filter                                                             | 41    |

| Figure 5.9: Schematic of voltage controlled delay element                           | 43    |

| Figure 5.10: Cadence corners/temperatures simulation of voltage controlled delay ce | ell43 |

| Figure 5.11: SAR controller                                                         | 45    |

| Figure 5.12: Digital calibration FSM                                                | 46    |

| Figure 5.13: Digital calibration algorithm                                          | 49    |

| Figure 5.14: Fractional-N sigma-delta & SAR calibration result from Cadence         | 52    |

| Figure 5.15: Fractional-N sigma-delta –settling of control voltage                  | 52    |

| Figure 5.16: Digital code word from SAR DLL (MSB bottom -LSB top)                   | 53    |

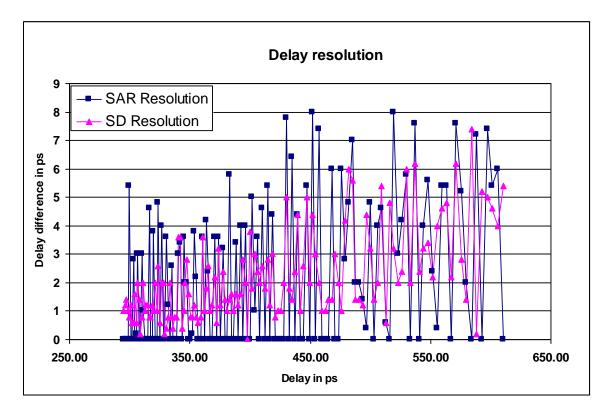

| Figure 5.17: Delay resolution of Sigma-delta and SAR DLL                            | 54    |

| Figure 5.18: 7-bit digitally controlled transmitter delay from [2]                  | 55    |

| Figure 5.19: Time interleaved edge combiner from [12]                               | 56    |

| Figure 5.20: UWB pulse generation                                                   | 57    |

| Figure 5.21: Dual capacitively coupled digital PA from [3]                          | 58    |

| Figure 5.22: Pulse shaping logic                                                    | 59    |

| Figure 5.23: UWB four level pulse and pulse shaping signals generated in Cadence.   | 60    |

| Figure 5.24: Spectrum of the four level UWB pulse generated in Cadence              | 61    |

| Figure 5.25: Spectrum of the UWB pulse generated in Cadence                         | 62    |

| Figure 5.26: Digital calibration result for a configuration to obtain 10ps delay difference   |

|-----------------------------------------------------------------------------------------------|

|                                                                                               |

| Figure 5.27: Simulated output of the four UWB transmitters showing 13ps delay                 |

| difference65                                                                                  |

| Figure 5.28: Spectrum of UWB pulse showing the centre frequency is 3.581GHz66                 |

| Figure 5.29: Digital calibration result for a configuration to obtain 0ps delay difference 67 |

| Figure 5.30: Simulated output of the four UWB transmitters showing 0ps delay difference       |

|                                                                                               |

| Figure 5.31: Digital calibration result for a configuration to obtain 600ps delay difference  |

|                                                                                               |

| Figure 5.32: Simulated output of the four UWB transmitters showing 597ps delay                |

| difference                                                                                    |

| Figure 5.33: Spectrum of UWB pulse showing the centre frequency is 4.074GHz70                 |

| Figure 5.34: Spectrum of the output pulse with three different centre frequencies71           |

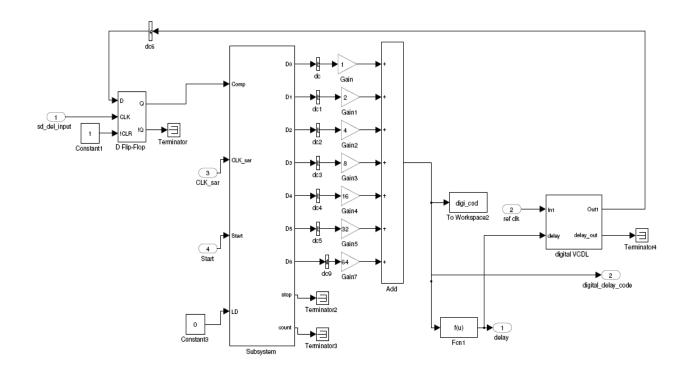

| Figure A.1: Digital calibration subsystem -SIMULINK model                                     |

| Figure A.2: Sigma-delta DLL-SIMULINK model                                                    |

| Figure A.3: SAR DLL –SIMULINK model                                                           |

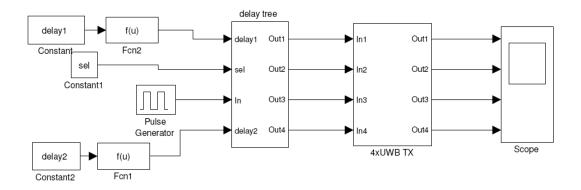

| Figure A.4: Beamforming UWB transmitter –SIMULINK model                                       |

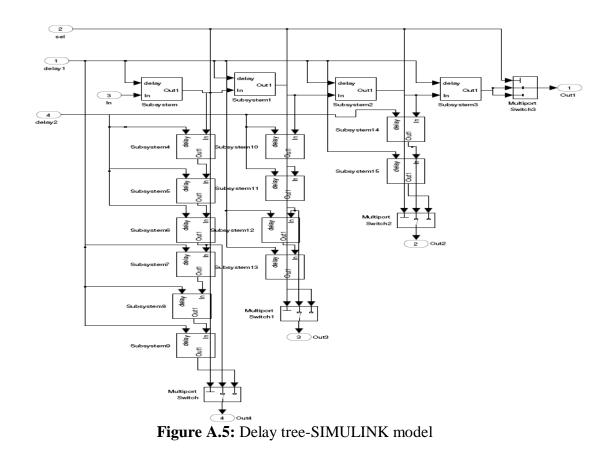

| Figure A.5: Delay tree-SIMULINK model                                                         |

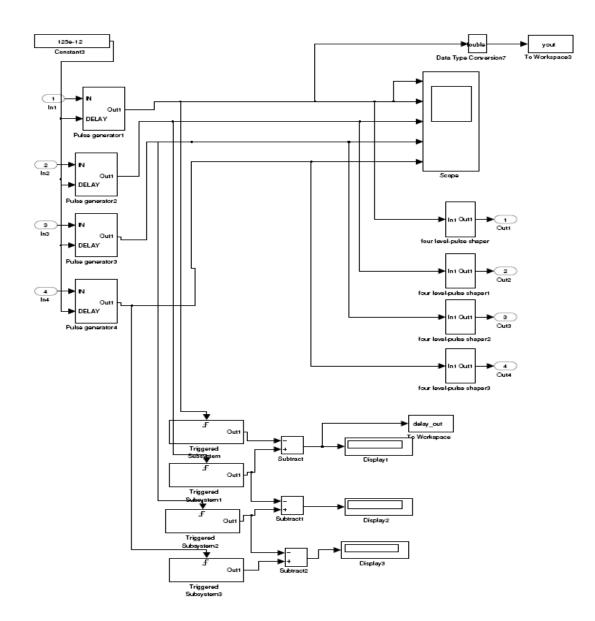

| Figure A.6: 4xUWB transmitter-SIMULINK model                                                  |

## LIST OF TABLES

| Table 2.1: FCC emission limits for indoor UWB [9]                            | 7   |

|------------------------------------------------------------------------------|-----|

| Table 4.1: Sigma-delta delay lock loop – MATLAB simulation results           | 28  |

| Table 5.1: Transmitter delay centre frequency calibration from Cadence       | 50  |

| Table 5.2: Beamforming delay calibration results from Cadence                | 51  |

| Table 5.3: Inputs used configure the delay difference                        | .63 |

| Table 5.4: Power consumption of the blocks of all-digital UWB transmitter    | 71  |

| Table 5.5: Comparison of a single all-digital UWB transmitter with other UWB |     |

| transmitters                                                                 | .72 |

| Table 5.6: Comparison with other beamforming UWB transmitters                | .74 |

# LIST OF ABBREVIATIONS AND SYMBOLS

| UWB               | - Ultra-Wideband                               |

|-------------------|------------------------------------------------|

| IR-UWB            | - Impulse Radio UWB                            |

| EIRP              | - Effective Isotropically Radiated Power       |

| DLL               | - Delay Locked Loop                            |

| FSM               | - Finite State Machine                         |

| PVT               | - Process, Voltage and Temperature             |

| VCDL              | - Voltage Controlled Delay Line                |

| SAR               | - Successive Approximation Register controlled |

| DPA               | - Digital Power Amplifier                      |

| LO                | - Local Oscillator                             |

| MUX               | - Multiplexer                                  |

| F <sub>REF</sub>  | - Reference Frequency                          |

| $\Delta T$        | - Pulse Width                                  |

| T <sub>REF</sub>  | - Reference Period                             |

| V <sub>CTRL</sub> | - Loop Filter control voltage                  |

| K <sub>VCDL</sub> | - Gain of Voltage controlled delay line        |

| I <sub>CP</sub>   | - Charge pump current                          |

| $f_{BW}$          | - Loop Bandwidth                               |

| ΣΔ                | - Sigma-Delta                                  |

| Vp-p              | - Peak to peak voltage                         |

#### ABSTRACT

This thesis presents a beamforming ultra-wideband transmitter capable of providing very fine angular resolution for imaging applications in the frequency range of 3-5GHz. This beamforming UWB transmitter employs baseband processing to save area and power. The transmitter uses a novel digital delay calibration technique to obtain the precise delay difference. The digital delay calibration system consists of a serial to parallel programming interface (SPI), a digital calibration Finite State Machine (FSM), a fractional-N sigma-delta delay locked loop ( $\Sigma\Delta$ DLL) and a (Successive Approximation Register) SAR delay locked loop. The sigma-delta delay locked loop will provide fine delay resolution as well as large delay range required in beamforming applications. This analog delay is then converted to a digital code word with the help of a SAR DLL. The FSM stores the digital code words corresponding to different delay values. These digital code words are then applied to a beam former delay subsystem to generate baseband signals with precise delay difference. The UWB pulse is generated from these signals with the help of all-digital UWB transmitters. The whole transmitter architecture is implemented in 0.13µm CMOS process. It provides a delay resolution of less than 10ps and consumes about 35.4mW of power from a 1.2V supply. The all-digital UWB transmitter implemented in the design provides the flexibility to shape the output UWB pulse and consumes 80pJ/pulse.

### **CHAPTER 1 : INTRODUCTION**

Ultra-Wideband (UWB) technology is an emerging field of research. This field has gained a lot of focus in recent years, especially after the Federal Communications Commission (FCC) approved the use of 3.1-10.6GHz band for unlicensed communication using UWB. UWB has many appealing features such as robustness, flexibility, high data-rate capability as well as high-precision ranging capability. These features make it very attractive for applications like radar, imaging, wireless USB, sensor networks, RFID tags etc. In radar and imaging applications, Impulse Radio UWB (IR-UWB) is carving a place for itself because of the ranging resolution it can provide. UWB is emerging as a low cost and high data rate alternative in the field of wireless communications [1]. This chapter provides an introduction to UWB, its applications and outlines the important contributions of this thesis.

#### **1.1 UWB and its applications**

Recognizing the potential advantages of ultra-wideband (UWB) communication, Federal Communications Commission (FCC) issued a report that permitted the use of 3.1 to 10.6GHz spectrum for UWB wireless communication [9]. According to the FCC, a signal is considered ultra-wideband if it has a fractional bandwidth greater than 0.2 or has an absolute -10dB bandwidth greater than or equal to 500MHz.The fractional bandwidth is defined as the ratio of -10dB bandwidth of the signal to its centre frequency.

The 802.15.3a task group had categorized UWB into two categories, i.e. the Orthogonal Frequency Division Multiplexing (OFDM) standard and the Impulse Radio UWB (IR-UWB) standard. The OFDM standard has been adopted by Wi-media alliance for implementing high data rate communication. The IR-UWB standard is very useful for energy efficient designs. Low data rate transmitters with low energy consumption have been built using the IR-UWB proposal [2, 3].

Some of the applications that can benefit from low power, low cost and high data rate provided by UWB are Wireless Personal Area Network (WPAN) applications which provide wireless connectivity to all personal computing devices, consumer electronics and mobile devices. The maximum data rate that can be achieved on a RF link is given by the Shannon capacity theorem as

$$C = BW\log(1 + SNR), \tag{1.1}$$

where, *C* is the channel capacity, *BW* is the bandwidth and *SNR* is the signal to noise ratio. The wide bandwidth offered by UWB helps to attain a high data rate which is required for high-speed data transfer applications. The low power and low data rate applications like sensors and biomedical applications exploit the low energy consuming architectures of the IR-UWB. It is very useful in RFID tags for patient and asset tracking in hospitals. In radar and imaging applications, IR-UWB is very attractive because of the ranging resolution it can provide. It is very useful for range finders and biomedical imaging [5]. Ranging resolution is the minimum separation distance between the two objects that can be detected by the radar system. The ranging resolution is given by

$$R = \frac{c}{2BW} \tag{1.2}$$

where, BW is the bandwidth of the signal and c is the speed of light.

Since UWB signals provide the user a potentially wide bandwidth, the ranging resolution that can be obtained could be very good. By utilizing the 7.5 GHz bandwidth from 3.1-10.6GHz, resolution as low as 2cm can be achieved.

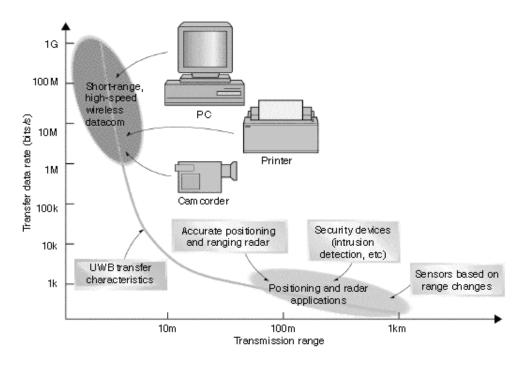

UWB is considered for a wide range of applications as shown in Figure 1.1 [33].

Figure 1.1: Applications of UWB in short range wireless communications and ranging

[33]

UWB and radar based imaging are used in military applications [4]. UWB imaging is also used for detecting cardiac and pulmonary signals generated from the heart and lungs [8].

### **1.2 Motivation**

UWB has a very high-precision ranging capability. This is predominantly the driving force for using UWB in imaging and ranging applications. In a typical imaging system, a

transmitter would transmit an electromagnetic pulse train towards objects of interest. A receiver would collect the signals that are reflected and/or scattered from the objects as shown in Figure 1.2.

Figure 1.2: Typical imaging system

The magnitude and shape of the received signals and their time of arrival are used to identify the target and its relative distance and speed respectively [5]. Beamforming helps to focus the beam in a particular direction as indicated in Figure 1.3. This helps in improving the spatial resolution of the image. The electromagnetic beam can be scanned mechanically or electronically to improve spatial coverage.

Figure 1.3: Beamforming in imaging system

An antenna array capable of electronic beam steering can adapt and focus its Radio Frequency (RF) beam at specific directions [1]. This helps to locate targets in radar and imaging systems. Angular resolution is defined as minimum angle by which the beam can be steered. Systems capable of providing very fine beam steering are needed for the high precision imaging applications. This thesis presents a beamforming ultra-wide band transmitter architecture capable of providing high angular and depth resolutions required for the imaging systems in the frequency range of 3-5GHz.

### **1.3 Thesis contribution**

The major contributions of this thesis are

- 1. A novel beamforming ultra-wideband transmitter architecture capable of achieving very fine beam steering angles.

- 2. A novel digital delay calibration technique that uses a digital FSM, sigma-delta delay locked loop, SAR delay locked loop and a vernier delay line to generate the precise delay required for beam forming. This helps to calibrate and control the beam angle and the centre frequency of the UWB transmitter.

- 3. An improved pulse shaping logic circuit which provides additional flexibility to control the shape of the output UWB signal.

#### 1.4 Thesis organization

This thesis presents a beamforming UWB transmitter implemented in 0.13µm IBM CMOS process. The organization of this thesis would be as follows. Chapter 2 provides the basic theory and advantages of beam forming in UWB. Chapter 3 reviews the existing beamforming UWB transmitter architectures. The proposed beamforming UWB

transmitter architecture is presented in chapter 4. Chapter 5 presents the CMOS implementation of the transmitter and chapter 6 concludes with a summary.

### **CHAPTER 2 : UWB BEAMFORMING**

### 2.1 Advantages of UWB Beamforming

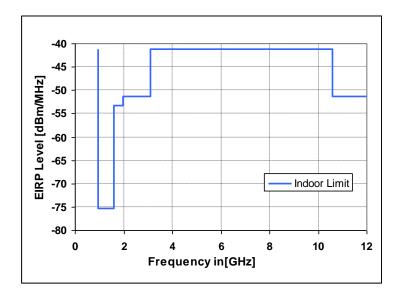

The power that can be emitted in the approved UWB band from 3.1GHz to 10.6GHz is very limited. The FCC limits for indoor communications are indicated in Table 2.1 [9] while the indoor emission mask of UWB is shown in Figure 2.1.

| Frequency in MHz | EIRP in dBm |

|------------------|-------------|

| 960-1610         | -75.3       |

| 1610-1990        | -53.3       |

| 1990-3100        | -51.3       |

| 3100-10600       | -41.3       |

| Above 10600      | -51.3       |

Table 2.1: FCC emission limits for indoor UWB [9]

Figure 2.1: Indoor UWB emission mask

In order to avoid interference to other existing narrow band systems, FCC has restricted the output power that can be transmitted from an UWB system. Because of this low output power restriction, the coverage in an UWB system is limited to only a few meters. However, this disadvantage of UWB can be overcome by using beamforming.

For a given power level at the receiver, the power that has to be generated in a phased array system is lower than in an isotropic system. In an N-element transmitter radiating P watts of power, the total power in the focused direction will be  $N^2P$ . The  $N^2$  factor is due to the coherent addition of the electromagnetic waves in the desired direction [10]. Beamforming can provide 20log(N) improvement in transmitter EIRP where N is the number of antenna elements used in the system.

Besides improving the range, beamforming can also minimize the interference to other narrow band systems. It can also avoid narrow band interferers at the receiver [10]. Beamforming helps to obtain the theoretically achievable highest data rate. The range and data rate obtained in beamforming transmitters are higher than their single antenna counterparts [11].

When compared to narrow band systems, beamforming in UWB also provides an additional degree of freedom in choosing the antenna spacing. In case of a narrow band system the antenna array factor is given by the equation

$$AF(\theta) = \frac{\sin(N(kd\sin\theta - \beta)/2)}{N\sin((kd\sin\theta - \beta)/2)}$$

(2.1)

where,  $\theta$  is the polar co-ordinate, N is the number of antenna elements, d is the spacing between the antenna elements,  $\beta$  is the angle at which the main lobe of the beam is focused and k is the propagation vector of the transverse electromagnetic wave and it is related to the wavelength( $\lambda$ ) by

$$k = \frac{2\pi}{\lambda} \tag{2.2}$$

This is a very well known equation for the antenna pattern of a narrow band system. An analysis of this equation would show that the antenna pattern would have side lobes and grating lobes. To obtain minimum side lobes, the antenna spacing has to be half-wavelength ( $\lambda/2$ ).

The array pattern equation for a Gaussian UWB signal is obtained in [13-15] and the approximate array pattern expression for the UWB signal is indicated in [4] and the equation is as follows

$$AF(\theta) = \frac{erf\left(\sqrt{\pi L\sin\theta/(2\Delta Tc)}\right)}{\left(\sqrt{\pi L\sin\theta/(2\Delta Tc)}\right)}$$

(2.3)

where,  $\theta$  is the polar co-ordinate, *c* is the velocity of light,  $\Delta T$  is the pulse width and *L* is the antenna array length. For an antenna array with *N* elements each separated by a distance of *d*, the array length is given by

$$L = (N-1)d \tag{2.4}$$

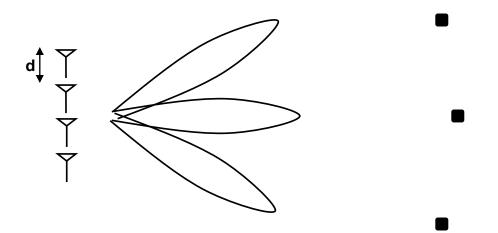

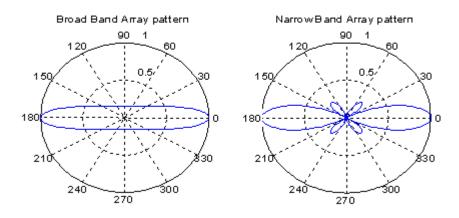

The polar plot of the array factors given by equations 2.1 and 2.3 for the narrow band and the broad band systems respectively were obtained using MATLAB and the result is as shown Figure 2.2.

Figure 2.2: Comparison of UWB and narrow band array pattern

It can be clearly seen that the UWB beamforming array pattern does not have the grating lobes and side lobes that are present in narrowband systems [4]. Therefore, it is no longer necessary to restrict the antenna spacing to half-wavelength spacing. Larger spacing can be used for obtaining higher spatial selectivity [5].

### 2.2 UWB beamforming system basics and requirements

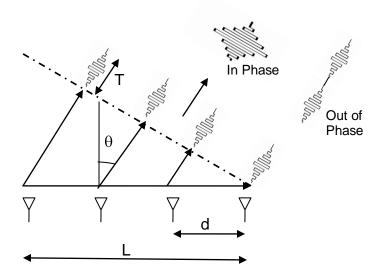

The properties of UWB beamforming systems have been discussed in the literature [13-15]. In an UWB beamforming system consisting of a linear array of antennas, the scanning angle depends on the spacing between antenna elements and the radio pulse width ( $\Delta T$ ) of the UWB signal. The angle between the direction where the beam is focused normal to the antenna array is indicated as  $\theta$  as shown in Figure 2.3.

Figure 2.3: UWB beamforming system.

In a linear array of antennas, with a spacing of d between the antenna elements, in order to achieve a maximum signal in the direction  $\theta$ , the relative delay between the signals fed to the adjacent antenna elements is given by

$$\Delta = (d\sin\theta)/c \tag{2.5}$$

where, c is the velocity of electromagnetic wave in free space.

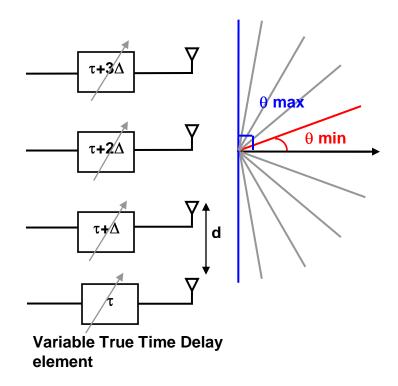

UWB arrays require true time-delay elements to steer the RF beam as indicated in the Figure 2.4. The delay difference between the adjacent antenna paths decides the scanning angle.

Figure 2.4: UWB array with true time-delay element

The requirements for the design of true time-delay elements for an UWB beam forming system were summarized as follows [1]:

1) The relative time-delay between adjacent antenna elements should be a fraction of the pulse width of the UWB radio pulses to steer a fine scanned angle. Longer delays are required for wider scanned angles.

2) The true time-delay element should be variable to change the scanned angle adaptively; hence, electronic control is desirable.

3) Timing jitter or deviation of the true time-delay element should be minimized.

These requirements listed for the design of true time-delay elements, serve as guideline in selecting the architecture for beamforming UWB transmitter.

### CHAPTER 3 : EXISTING BEAMFORMING UWB TRANSMITTER ARCHITECTURES

### **3.1 Literature Review**

Electronic beam steering in UWB phased array transmitters can be done in baseband or RF. The following summarizes some of the existing beamforming UWB transmitter architectures and investigates their advantages and disadvantages.

In design [16], beamforming was implemented by connecting the true time-delay elements between the transceiver and power splitter/combiner. The delay elements were implemented using passive elements like RC or transmission line components. But obtaining a large delay using transmission line components consumes a large area and is not economical.

Figure 3.1: UWB beamforming system from [4]

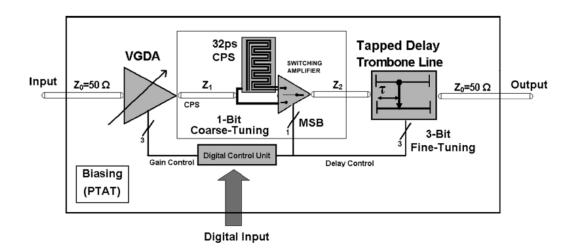

The UWB beam former in [4], implemented in 0.18µm BiCMOS SiGe process can obtain a ranging resolution of 20mm and an angular resolution of 7 degrees. This

architecture employs trombone delay elements at the RF path as depicted in Figure 3.1. The beamformer can provide a maximum delay of 64ps with a step size of 4ps. The trombone delay elements were constructed using lumped LC. This chip has an area of 2.25mm<sup>2</sup> and consumes 87.5mW from a 2.5V supply. The major drawbacks of this scheme are the huge area due to inductors and the large power required for compensating the loss incurred by the LC delay elements.

Ultra-wideband timed array receiver implemented in [5] uses a path-sharing delay architecture. This beamforming system has a resolution of 15ps and can provide 11 angles with 9 degrees of spatial resolution. The delay line was implemented using fully differential constant -k LC ladder. Each ladder section provides a resolution of 7.5ps. This chip suffers from the same drawbacks as [4]. It has a die area of 9.92mm<sup>2</sup> and consumes 555mW of power.

Figure 3.2: Electronic beam steering subsystem from [1]

In an effort to reduce the die area and power consumption, electronic beam steering in UWB phased array transmitter was implemented at baseband [1]. As shown in Figure 3.2, the beam steering subsystem consisted of a digital PLL that controlled a variable delay to provide the required phase shift. The input baseband signal was delayed using this beam steering subsystem. The relative delay between the paths decides the beam angle and these delayed signals were directed to an external UWB pulse forming network to produce the UWB pulses. This beam steering system was implemented in 0.25µm process and it can produce a delay in the range of 100ps to 500ps. The system can obtain a delay step size of 100ps and a minimum scan angle of 9 degrees per step with an antenna spacing of 18cm. It consumes about 100mW of power and has an area of 0.9mm<sup>2</sup>. The main drawbacks of this architecture are the higher jitter and poorer resolution due to the employed PLL for delay control.

The UWB timed array transmitter implemented in [6] uses the path-sharing architecture at baseband to provide the delay. This architecture uses long and short inverter chain paths to obtain the delay difference between the adjacent channels. The delay resolution obtained is 180ps with a maximum delay of 880ps. With an antenna spacing of 30cm, this design can steer the beam with an angular resolution of 10 degrees within a range of  $\pm$ 60degrees. However, there is no mechanism to change or tune the delay of the inverter chains to compensate for PVT variations and the achievable delay resolution is limited to 180ps. In addition, it requires phase shifters to align the VCO phases which might not be trivial. The UWB pulse forming switch employed in this architecture also leads to undesirable LO leakage to the output of the transmitter. By investigating these architectures, it is clear that beamforming UWB transmitters utilizing baseband processing is advantageous in terms of both area and power. However, they mainly suffer from poor delay resolution. On the other hand, beamforming transmitters utilizing RF processing will result in better delay resolution but they demand larger area and power consumption.

This calls for the development of a beamforming UWB transmitter with baseband processing, which can provide good delay resolution. The better the delay resolution the better will be the angular resolution. For example, with an antenna spacing of 18cm and a delay resolution of 20ps, scanning angle resolution of the order of 2 degrees can be achieved.

This work presents a beamforming UWB transmitter architecture dedicated to achieve good angular resolution without too much power and area penalty.

## CHAPTER 4 : BEAMFORMING UWB TRANSMITTER ARCHITECTURE

This chapter presents the proposed beamforming UWB transmitter architecture. The whole transmitter was modeled and proven in the MATLAB simulation.

### 4.1 Beamforming UWB transmitter architecture

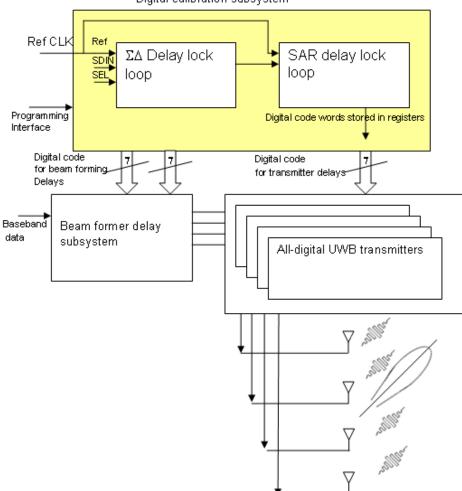

The proposed architecture employs baseband processing and improves the delay resolution to obtain good angular resolution. This architecture will result in a compact design. The proposed architecture is shown in Figure 4.1.

Digital calibration subsystem

Figure 4.1: Proposed beamforming UWB transmitter architecture.

The proposed architecture consists of a beam former delay subsystem to generate the delay required for beamforming. To generate the beamforming delays, the vernier delay line architecture was chosen. This architecture is quite popular [23, 24] to generate delay in the range of picoseconds. The concept is based on the fact that the delay difference between two paths can generate picoseconds delay. The digitally controlled delay elements used in the beam former subsystem have been designed to generate delay difference in the range of 0-600ps. These digitally controlled delay cells have been designed to give a resolution of the order of 5-10 picoseconds per bit change in the input digital code word. In order to generate the accurate delay, calibration is required.

The digital calibration circuitry consists of a fractional-N sigma-delta DLL and a Successive Approximation Register controlled DLL (SAR DLL). The sigma-delta DLL architecture can provide fine delay resolution as well as large delay range required for the beamforming subsystem. The PVT variations will be compensated through the digital calibration employing sigma-delta DLL. In order to minimize the power consumption, sigma-delta DLL is only used for the calibration phase and will be turned off subsequently. The calibration result will be captured by the additional SAR DLL. The SAR DLL will convert the analog delay calibrated by sigma-delta DLL into a digital code word through a digital calibration FSM. The code words obtained from the calibration will then be used to control the beam former delay subsystem and generate the required delay difference.

A baseband signal fed to the beam former delay subsystem will produce four delayed signals and the relative delay between the signals will decide the angle of the main beam.

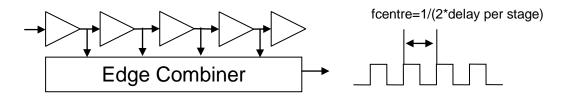

These delayed signals are fed to the all-digital UWB transmitters that generate the required IR-UWB pulses. IR-UWB pulses are generated by combining the edges that are output from a transmitter delay line [2]. The centre frequency of the UWB pulse depends on the delay generated by the transmitter delay line. A delay line that is controlled by sigma-delta DLL would provide the precise delay required by these systems and the edges can be combined as in [2] to produce the IR-UWB pulses with desired centre frequency. The generated pulses need further shaping in order to be FCC compliant. Hence, the digital power amplifier with capacitively controlled pulse shaping driver architecture [3] is adopted with a new pulse shaping logic circuit to obtain the required pulse shaping. The architecture has the flexibility to control most of the parameters of the output pulse, there by giving the flexibility to obtain a FCC compliant UWB pulse. The choice of these architectures was based on considerations of power and area.

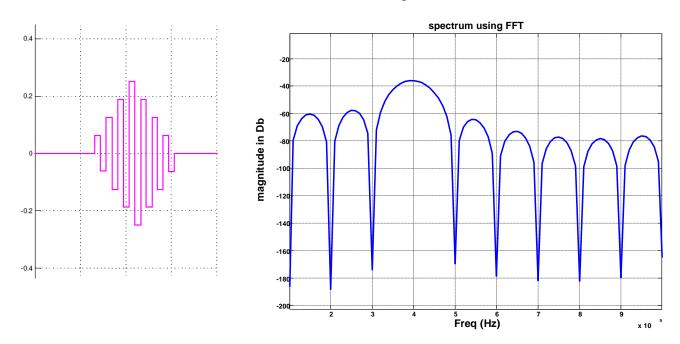

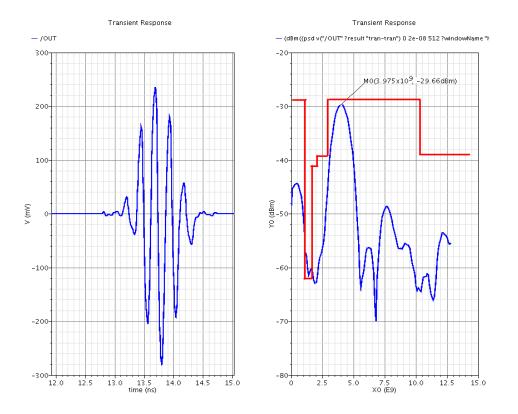

Figure 4.2: UWB pulse and its spectrum from MATLAB simulations

The whole transmitter was modeled in MATLAB and the pulse shape of the signal and its spectrum are as shown in Figure 4.2. The pulse shaping implemented in the MATLAB model was just a four level pulse shaping. The spectrum obtained is not FCC compliant. Changing the pulse shape further can result in a FCC compliant spectrum.

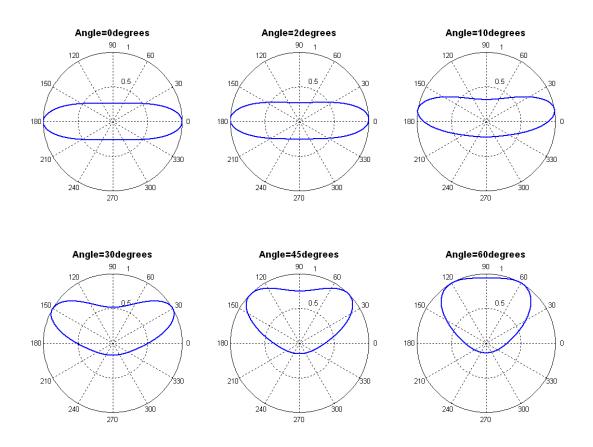

The MATLAB simulations of the sigma-delta DLL shows accurate control of the delay. Hence, by using this new architecture, a delay resolution of the order of 5-10ps can be obtained in the MATLAB simulation. This results in minimum steering angle of close to 1 degree with an antenna spacing of 18cm. The beam steering obtained in the MATLAB model for some angles are shown in Figure 4.3.

Figure 4.3: UWB beam steering from MATLAB simulations

If the CMOS delay resolution is relaxed to 20ps, the corresponding angular resolution would be 2 degrees. In the next section a detailed description of the various blocks, their workings and the MATLAB results will be presented.

### 4.2 Detailed description of the blocks in the proposed architecture

#### 4.2.1 Beamforming delay subsystem

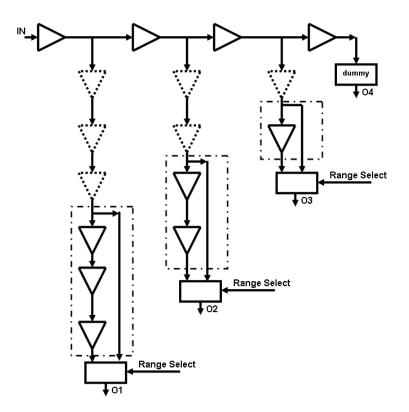

In order to steer the beam through an angle of 0 to 90 degrees, (though 90 degrees is not feasible due to the beam spreading) with a particular antenna spacing, the required delay range can be calculated using the equation (2.5). With an antenna spacing of 18cm, the required delay range is from 0-600ps. To get an angle of 0, the relative delay should be zero ps. This is not achievable using a single delay cell. Using a single delay element to generate the beamforming delay limits the delay resolution to the minimum delay achievable in the process. Hence, the vernier delay line architecture is adopted to overcome this limitation. In the vernier delay line architecture, the delay resolution depends on the delay difference between the paths. It depends on how fine the delay cells determines the delay resolution. Since a very fine tuning of the delay is needed, a digitally controlled current starved inverter was used. Current starved inverter can generate the required fine delay. The delay tree structure used in this design is shown in Figure 4.4.

Figure 4.4: Beamforming delay subsystem

The delay cells indicated by solid lines are controlled by one set of digital code words and the delay cells in dotted lines are controlled by another set of code words. But these delay cells are identical. When both the delay elements have the same input code word, a relative delay of close to zero ps can be obtained in the design. When the delay of the two delay elements differ by 10ps then the relative delay between each path will be this delay difference of 10ps. The delay resolution that can be obtained depends on the minimum delay difference that can be obtained between the two delay elements. With this architecture, delay in the order of tens of picoseconds can be obtained which is a significant improvement compared to [1]. The beam forming delay tree can generate a delay difference in the range of 0-300ps. To double this range, additional set of delay elements as indicated within the dotted rectangular boxes in Figure 4.4 are used, to obtain the required delay range of 0-600ps. The range can be selected with the help of a range select input. In order to provide the accurate delay, the help of the digital calibration system with the fractional-N sigma-delta DLL and SAR DLL is required.

#### 4.2.2 Fractional –N sigma-delta delay lock loop

The requirements of the true time-delay elements were listed in Chapter 2. From the requirements, it can be seen that to implement a beamforming UWB system, the timing jitter should be minimized. In [1], a digitally controlled PLL was used to control the delay line. But when compared to PLL, DLL has no cycle to cycle jitter. The DLL is more stable than PLL and easier to design [34].Hence, using a DLL instead of a PLL can improve the jitter performance. A DLL normally locks to one period of the reference clock. It can provide the required delay based on the reference clock period and the number of delay elements used. With a fixed frequency reference signal, the number of delay locked loop. A large number of delay cells are needed to obtain a very fine resolution.

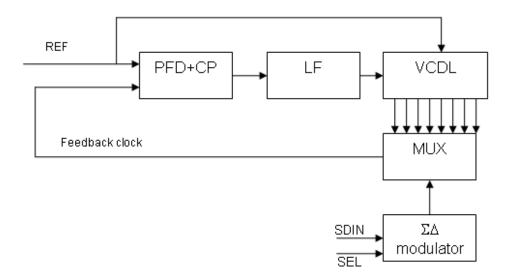

Fractional-N PLLs were designed to obtain higher frequency resolution [18]. And sigma –delta fractional-N PLLs were used to randomize the division ratio to eliminate the spurious tones as well as achieving better frequency resolution[19]. Same concepts can also be applied to the DLL to improve the delay resolution. The architecture of the sigma-delta DLL used in this transmitter is shown in Figure 4.5.

Figure 4.5: Fractional-N sigma-delta DLL architecture

A DLL normally would adjust the delay line to provide one cycle delay. The fractional-N sigma-delta DLL is similar to a normal DLL except that the sigma-delta modulator controls the feedback clock. The multi-phase clocks produced by the DLL are fed to a multiplexer that is controlled by the sigma-delta modulator. The output of this multiplexer is fed to the PFD. This DLL is based on the principle that the sigma-delta modulator controls the feedback clock from the VCDL and hence it controls the number of delay cells. The sigma-delta modulator would generate an average feedback clock clock controllable by the modulator input. Based on the average feedback clock generated, the DLL would settle to produce the delay. Therefore by controlling the average number of delay cells present in the DLL loop, the desired delay can be generated. The primary advantage of using the fractional-N sigma-delta delay locked loop is that it has the capability to generate a fractional delay without the need of additional phase interpolator. It also does not require a long delay chain to produce delay with very fine resolution. For example, with a reference clock frequency of 200 MHz and a delay line consisting of 20

delay cells, by using the output phases from delay cells 8 to 20, delay per cell in the range of 625ps to 250ps can be obtained respectively. By averaging the phases with a sigmadelta modulator that can generate 16 average phases, a theoretical delay resolution in the order of 5ps can be achieved.

#### 4.2.3 Sub-block models of sigma-delta DLL

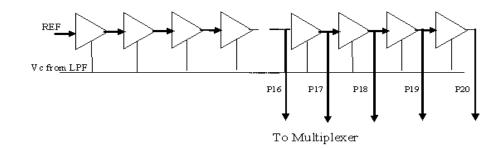

#### **4.2.3.1** Voltage controlled delay line (VCDL)

The DLL consists of an analog voltage controlled delay line covering the range of delay required for beamforming. This work uses 20 delay cells to obtain the required delay range and resolution for beamforming. The delay cells are identical and the voltage from the loop filter controls the delay.

Figure 4.6: VCDL used in sigma-delta DLL.

The delay model in MATLAB simulations is assumed to have a nominal delay of 200ps and a gain of 1ns/volt. The nonlinearity of the delay line transfer characteristic does not affect the operation of the DLL. Hence, a simple current starved inverter delay is sufficient for the purpose.

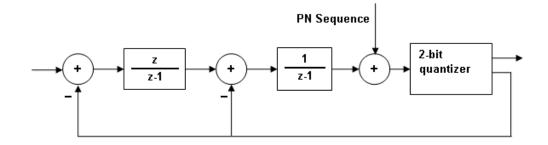

#### 4.2.3.2 Sigma-delta modulator

The DLL uses a second order sigma-delta modulator to produce the average feedback clock. The noise shaping provided by the sigma-delta is higher with higher order modulators. However, using a higher order modulator in the DLL would require a higher order loop filter which might render the loop unstable. Hence, a second order sigma-delta modulator with a 2-bit quantizer is used in the design which can switch between 4 phases of the clock signals to produce the average feedback clock.

Figure 4.7: 2<sup>nd</sup> order sigma-delta modulator

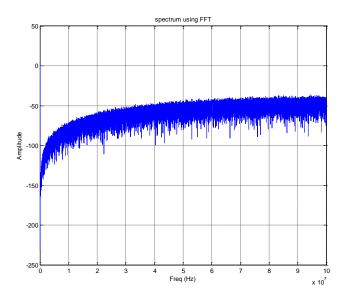

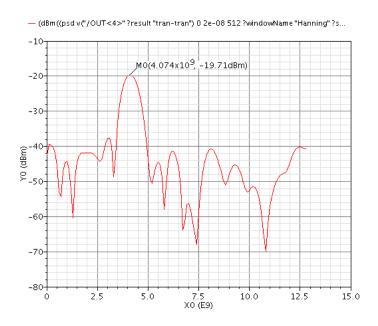

The pseudo-random noise was added to dither the output of the sigma-delta modulator to eliminate the spurious tones. The presence of spurious tones would worsen the jitter performance. The simulated output spectrum of the sigma-delta modulator block is as shown in Figure 4.8.

Figure 4.8: 2<sup>nd</sup> order sigma-delta modulator spectrum

The sigma-delta DLL shown in figure 4.5 was constructed in MATLAB. The sigma-delta modulator takes two inputs. The 'SEL' input is used to choose the group of clock phases for averaging. The 'SDIN' will set the average value. The 'SDIN' can take values in the range of -8 to 7 and the sigma-delta modulator can produce 16 different average phases by controlling the average number of delay cells in the DLL loop. The mapping between the inputs 'SDIN', 'SEL' and the average number of delay cells is given by

Avg. No. of delay cells

$$(ND) = 7 + SEL + (8 + SDIN)/16$$

(4.1)

and the delay generated per delay cell is given by

$$Delay/cell(D) = T_{REF}/ND$$

(4.2)

where,  $T_{REF}$  is the period of the reference clock and *ND* is the average number of delay cells. This design uses a reference clock with a period of 5ns. The delay corresponding to different modulator control words are shown in Table 4.1

| SDIN | SEL | Avg. No. of | Expected  | MATLAB          |

|------|-----|-------------|-----------|-----------------|

| SDIN |     | delay cells | delay(ps) | simulation (ps) |

| 0    | 1   | 8.5         | 588.2     | 588.6           |

| -5   | 2   | 9.1875      | 544.2     | 544.4           |

| -8   | 4   | 11          | 454.5     | 454.8           |

| -2   | 5   | 12.375      | 404.0     | 404.6           |

| -4   | 7   | 14.25       | 350.8     | 351.0           |

| -8   | 10  | 17          | 294.1     | 294.3           |

Table 4.1: Sigma-delta delay lock loop – MATLAB simulation results

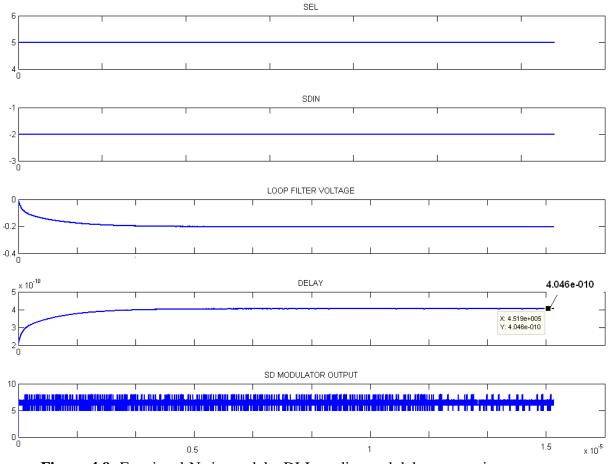

The results of the sigma-delta DLL obtained from MATLAB simulation for a particular input of -2, 5 are shown in Figure 4.9. This result depicts that the sigma-delta DLL settles down and produces a delay of 404.6ps per delay element corresponding to the input. This clearly shows that the fractional-N sigma-delta DLL architecture can generate fractional values of delay and the resolution no longer depends on the number of delay elements in the delay line.

Figure 4.9: Fractional-N sigma-delta DLL settling and delay generation

## 4.2.4 SAR delay lock loop

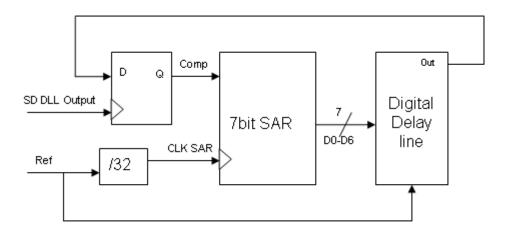

Successive Approximation Register controlled (SAR) DLLs are very popular in digital delay lock loop architectures [21, 22]. A SAR digital delay lock loop uses a binary search algorithm to find the digital code word that would generate the required delay.

Using the sigma-delta DLL directly to generate the delay required for beamforming would require the delay lock loop to run continuously. This results in power consumption. To minimize the power consumption, a SAR delay lock loop is coupled with the sigma-delta delay lock loop to convert the analog delay into a digital code word.

Figure 4.10: SAR DLL architecture

First, the sigma-delta delay lock loop will generate the desired precise delay for calibration. The SAR DLL compares the reference clock signal with the delayed signal obtained from sigma-delta DLL. The SAR will output the digital control word that will produce the delay that closely matches the delay produced by the sigma-delta DLL. The mismatch will be due to the limited resolution of the digital delay element employed in the SAR DLL. In order to minimize the mismatch, the digital delay element designed for the SAR DLL should have a very good delay resolution. The resulting control word can then be stored in the registers after calibration and used for controlling the beamforming transmitter. After calibration, both sigma-delta DLL and SAR DLL can be turned off. This will minimize the power consumption.

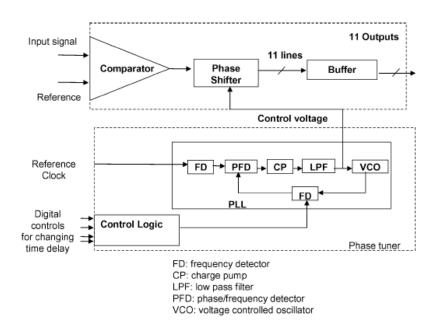

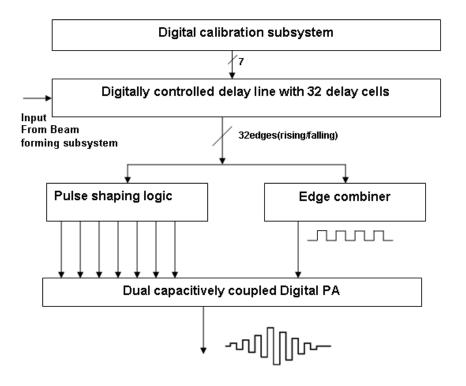

# 4.2.5 All-digital UWB transmitter block

The objective of this project was to develop a beamforming ultra-wideband transmitter. The beamforming is implemented in baseband as discussed in the previous sections. Now, an all-digital UWB transmitter that can form the UWB pulses and deliver to the antenna is required. There are several architectures which generate FCC compliant UWB pulses for transmission. Pulse shaping is one of the prominent techniques adopted to obtain an UWB pulse compliant to the FCC mask.

In [25], the transmitter generates an amplitude modulated UWB signal by multiplying baseband signal with an UWB monocycle train. The major drawback of this architecture is the leakage of the LO signal to the output which requires lowering of output power to meet the FCC mask. The architecture in [27] uses a phase lock loop with LC VCO and FIR filters to generate a FCC compliant UWB pulse. However, it is very power consuming and not suitable for burst mode operation due to long start-up delay in PLL. Tuned amplifiers with LC pulse shaping ladder can easily achieve spectral compliance but with significant area and power penalty [26]. The pulse shaping and power amplifier can also be implemented digitally by using a triangular pulse generator [28]. However, this architecture needs an external balun to form the UWB pulse.

The architecture in [2] is energy efficient and combines the edges from the output of a delay line to form the UWB pulse, but it needs an external filter to make the UWB pulse FCC compliant. The architecture in [3] is an all-digital architecture, which does not need any external filter or balun to form the UWB pulse and is energy efficient. The all-digital UWB transmitter implemented in this work uses a combination of both these architectures. This architecture consists of a digitally controlled delay line calibrated by the digital calibration subsystem. The UWB pulse is formed by combining the edges that are output from this delay line. Pulse shaping is done with help of a pulse shaping logic circuit that generates signals to control the pulse shape and a dual capacitively coupled

digital power amplifier. The pulse shaping logic circuit used in this transmitter provides more flexibility to tune the pulse shape when compared to the logic implemented in [3]. The advantage of using this architecture is that it does not need any inductor or external balun to form the UWB pulses and hence is less area consuming, which is critical for a beamforming transmitter. The architecture used to implement the all-digital UWB transmitter block is shown in Figure 4.11.

Figure 4.11: All-digital UWB transmitter architecture

The reason for using the delay line and edge combiner to form UWB pulse instead of using the ring oscillator as in [3] is that the delay line can be accurately calibrated with the help of the sigma-delta delay lock loop. Hence, the centre frequency can be controlled precisely. Also, the DLL jitter is better than the ring oscillator jitter [34]. This architecture can control the number of pulses that should be formed per bit at the output. The shape of the pulses can be controlled with help of the pulse shaping logic and the power amplifier. The gain is also tunable giving us a flexibility to change all parameters of the output pulse to obtain the FCC compliant UWB pulse.

# **CHAPTER 5 : CMOS IMPLEMENTATION**

The beamforming UWB transmitter was implemented in IBM 0.13µm CMOS process. This chapter gives the details of the implementation as well as the results obtained from Cadence simulations.

# 5.1 Digital delay element for beam former subsystem

The 7-bit digital delay element was implemented as a current starved inverter with digital PMOS switches (only 6-bit control is shown in Figure 5.1 for simplicity). The delay element was designed as per the guidelines indicated in [31].

Figure 5.1: Digital delay element for beam former subsystem architecture (6-bits)

This architecture of using a current source to set the current for the delay element is more robust in terms of the temperature and process variations [31]. It is better than controlling

the delay by just varying the size of the switches. The resolution of the digital delay element determines the achievable resolution.

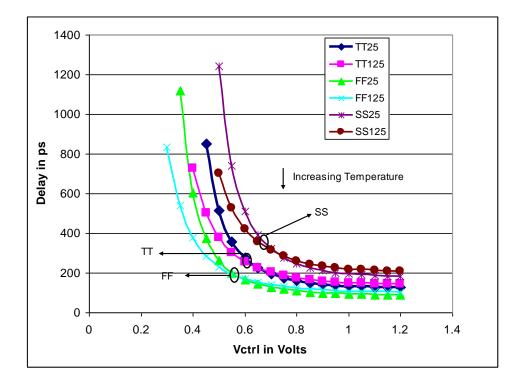

Since fractional–N sigma-delta delay locked loop can generate a delay with precise delay resolution, the bottleneck is the resolution provided by the digital delay element. Resolution in the order of 5-10ps is required for the current system. The current starved delay element has a nonlinear characteristic with respect to the current. Hence, resolution of the order of 5-10ps is not obtainable at low currents. The curve is as shown in Figure 5.2.

Figure 5.2: Delay vs. Current in current starved inverters

In order to overcome this nonlinearity and obtain a more linear curve which can provide a delay resolution of about 5-10ps, additional transistors were added to make the characteristics more linear.

The following procedure was adopted to obtain the sizing for the transistors. The required delay range for the digital delay element is from 300ps to 600ps. Taking into account the process variations; the delay element was designed in the typical corner with a margin to satisfy a range of 200ps to 790ps. This margin helps to obtain the required delay range in all process corners. A resolution of 10ps is needed for the beam forming system to steer the beam by 1 degree. To achieve this, a resolution of the order of 5ps is needed from the digital delay element. Hence, the number of bits required to cover the delay range of 200 to 790ps in typical corner with a resolution of 5ps is determined to be 7 bits.

With 7 bits of control, there are 128 combinations for the input. The delay range to be achieved was broken down into four groups. The maximum and minimum delay for each range was calculated based on the total maximum delay and the resolution to be obtained. The 5 bits controlling each range was then designed based on the procedure in [31]. Then the transistors controlling the four groups were merged appropriately to obtain the complete 7-bit controlled digital delay element. The resulting delay element has a delay characteristic that is more linear than the conventional characteristics.

This linearization of the delay characteristics was done by just adding a few more transistors. These transistors need to be added only for the biasing circuit that would generate the biasing voltage for the current starved inverters. They need not be replicated in each delay cell. The delay cells will consist of just the current starved inverter section with the current mirror section as indicated in the Figure 5.1 by the rectangular dotted box. This linearization guarantees a resolution of 5-10ps as required by the system. The

delay line was simulated in various temperatures and corners, and it covers the range of 300-600ps in all temperatures and corners. The result is shown in Figure 5.3.

Figure 5.3: Cadence corners/temperatures simulation of digital delay element

This delay cell will also be used in SAR DLL for beamforming delay calibration.

# 5.2 Fractional –N sigma-delta delay lock loop

# 5.2.1 Phase frequency detector and startup circuit

In the sigma-delta delay locked loop, a phase frequency detector is used to compare the phases between the reference clock and the output feedback clock. The phase frequency detector implemented is a conventional phase frequency detector consisting of two D flip-flops and a nand gate as shown in Figure 5.4.

Figure 5.4: Conventional phase frequency detector

The phase frequency detector (PFD) generates the UP and DN signals based on the phase difference between the reference clock and the feedback clock. When both the reference clock and feedback clock are in phase, the UP and DN signals generated from the PFD will have the same pulse width. This is the smallest pulse width that these signals can have. This smallest pulse width has been designed to be around 250ps to avoid dead-zone problem. This normal phase frequency detector suffers from the false lock problem because of the limited initial condition. Hence, a start controlled circuit is necessary to set the initial condition of the phase frequency detector [29].

Figure 5.5: PFD and start-controlled circuit

The start controlled circuit was adopted from [29]. The addition of this start control circuit sets the initial condition. When the 'startb' signal is low the two clocks are masked off. Hence, the PFD is disabled. When the 'startb' signal goes high the two clocks propagate to the PFD for comparison. Also, the 'setupb' signal is used to pull the initial filter voltage to VDD through a PMOS transistor. This sets the initial delay at the minimum value, since higher control voltage gives lower delay.

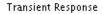

Figure 5.6: Simulation of start controlled circuit with PFD

The simulation result of the start controlled circuit with the PFD is indicated in Figure 5.6. The start controlled circuit avoids the false lock problem that would exist otherwise.

### 5.2.2 Charge pump

The charge pump circuit converts the phase difference to a current. Based on the UP and DN signals from the phase detector, the charge pump circuit will provide the current to

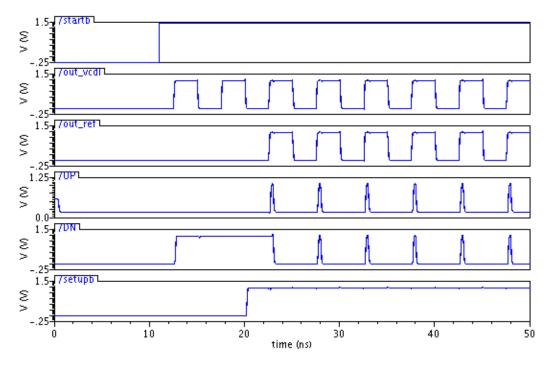

charge or discharge the loop filter and thereby generating the control voltage  $V_{CTRL}$ . The charge pump circuit used here is adopted from [29] and its schematic is shown below.

Figure 5.7: Schematic of charge pump adopted from [29].

The charge pump uses long length transistors to obtain good mirroring of current. The switches controlled by the UP and DN signals uses smaller length transistors ( $0.5\mu$ m) to provide faster switching with lesser parasitic capacitances. This charge pump design mitigates charge injection errors induced by the parasitic capacitance of the switches and current source transistors [30]. The charge pump implemented in the design uses a current of 80µA.

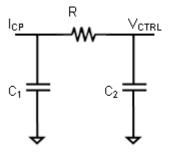

## 5.2.3 Loop filter

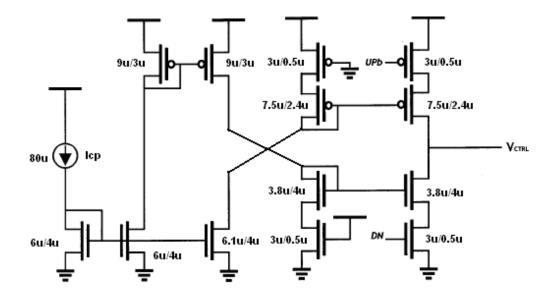

The loop filter used is a passive second order filter network consisting of a resistor and 2 capacitors as indicated in Figure 5.8.

Figure 5.8: Loop filter

The transfer function of the loop filter is given by

$$F(s) = \frac{V_{CTRL}}{I_{CP}} = \frac{1}{s^2 (C_1 C_2 R) + s(C_1 + C_2)}$$

(5.1)

The transfer function of a DLL is given in [30] as

$$D_{O}(s) = (D_{I}(s) - D_{O}(s))F_{REF}K_{VCDL}I_{CP}F(s)$$

(5.2)

Substituting the filter transfer function in the above equation and simplifying produces

$$\frac{D_O(s)}{D_I(s)} = \frac{F_{REF} K_{VCDL} I_{CP}}{s^2 (C_1 C_2 R) + s (C_1 + C_2) + (F_{REF} K_{VCDL} I_{CP})}$$

(5.3)

The above equation can be simplified by assuming that the second pole is far apart from the first pole. The two poles of the equation are given by

$$\omega_{P1} = \frac{F_{REF} K_{VCDL} I_{CP}}{C_1}$$

(5.4)

and

$$\omega_{P2} = \frac{1}{RC_2} \tag{5.5}$$

The first pole is also called the loop bandwidth. The loop bandwidth of the DLL determines the jitter performance of the DLL. To obtain less jitter, the loop band width should be small. Normally a loop bandwidth of the order of one-tenth of the reference

frequency is used. This design has a charge pump current of  $80\mu$ A, a reference frequency of the 200MHz is used and the  $K_{VCDL}$  gain of the analog delay element is approximately 1.7ns/V.Hence with a capacitor ( $C_I$ ) of 160pF, the loop bandwidth is given by

$$f_{BW} = \frac{\omega_{P1}}{2\pi} = 27kHz \tag{5.6}$$

Such a low value of loop bandwidth is selected to obtain a low value of jitter. The capacitor  $C_2$  is chosen to be one-tenth of  $C_1$  and the resistor is chosen to keep the second pole far from the first pole. The value of the resistor used in the design is  $12k\Omega$ . This gives a second pole frequency of 828kHz.

## **5.2.4 Voltage controlled delay line**

The voltage controlled delay line (VCDL) is one of the important blocks of a DLL. The performance of the VCDL is very critical as it directly affects the jitter performance of the DLL. Since a sigma-delta DLL is a feedback loop, it will always settle to give the required delay. The non-linearity in the characteristics of the delay element does not affect the performance of the DLL greatly. Hence, the analog voltage controlled delay line required in the sigma-delta DLL was designed using voltage controlled current starved inverters as shown in Figure 5.9.

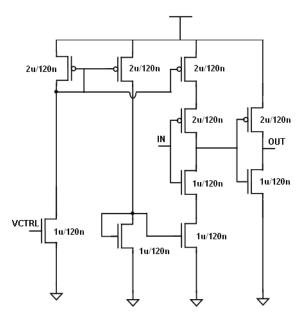

Figure 5.9: Schematic of voltage controlled delay element

Figure 5.10: Cadence corners/temperatures simulation of voltage controlled delay cell

The delay cells have been sized to obtain the required delay range of 300-600ps. The delay element was simulated in various process corners and temperatures. As illustrated

by the Figure 5.10, this delay cell is able to cover the required delay range. Hence, the sigma-delta DLL can provide the required delay in spite of PVT variations.

#### 5.2.5 Sigma-delta modulator

The second order digital sigma-delta modulator was built using verilog. The adders needed to implement the sigma-delta modulator have been designed as carry look-ahead adders. Carry look-ahead adders operate very fast and provide the capability for the sigma-delta modulator to operate at very high frequencies. In the current design the sigma-delta modulator operates at a frequency of 200MHz. The pseudo-random noise generator used to randomize the sigma-delta modulator output is designed as a 25-bit linear feedback shift register that implements the generator polynomial ( $z^{25}+z^{22}+1$ ). The verilog code of the sigma-delta modulator was used in Cadence mixed signal simulations.

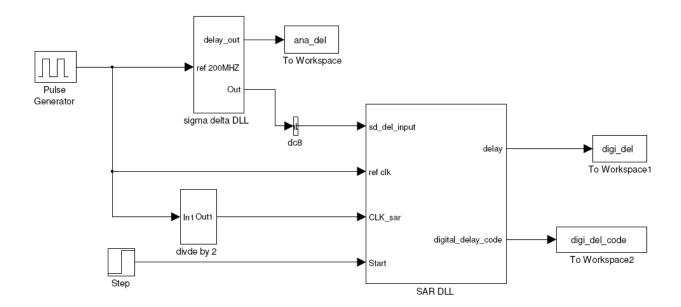

# 5.3 SAR delay lock loop

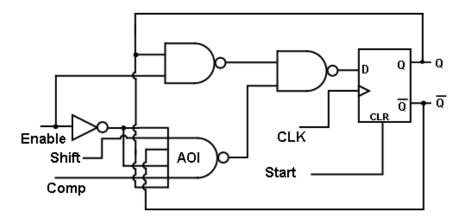

The SAR delay lock loop is a digital delay lock loop that converts the analog delay into a digital code word. The SAR DLL consists of a SAR controller and a digital delay line. This design uses two SAR DLLs namely, the beamforming SAR DLL and the transmitter SAR DLL. The digital delay line in the beamforming SAR DLL consists of 5 delay cells that resemble the delay cells used in the beam former subsystem. The digital delay line in transmitter SAR DLL is made up of 16 delay cells that replicate the transmitter delay line. During the calibration of the beam former subsystem and the transmitter, the respective SAR DLL is used. A simple D flip-flop serves as phase comparator for the DLL. This design uses a 7-bit SAR controller to determine the digital code word

corresponding to the delay generated by the sigma-delta DLL. The SAR controller is shown below [21].

Figure 5.11: SAR controller

The output of 5<sup>th</sup> delay cell of the sigma-delta DLL is fed to the SAR DLL. The SAR controller was custom designed in Cadence. The 7-bit SAR controller will control the digital delay line. It will try and produce the closest matched delay as generated by the sigma-delta delay lock loop and obtain the corresponding digital code word.

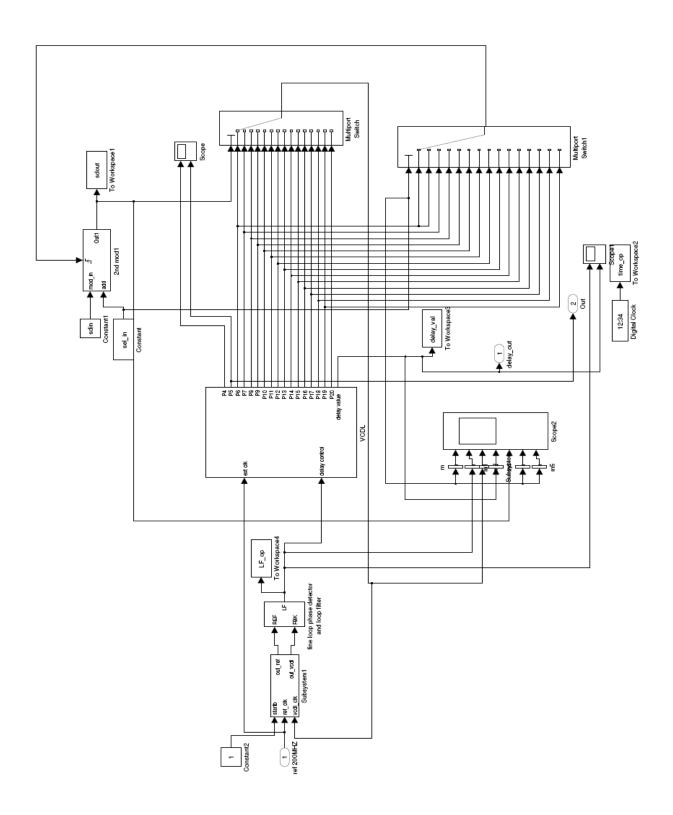

# 5.4 Digital calibration circuit

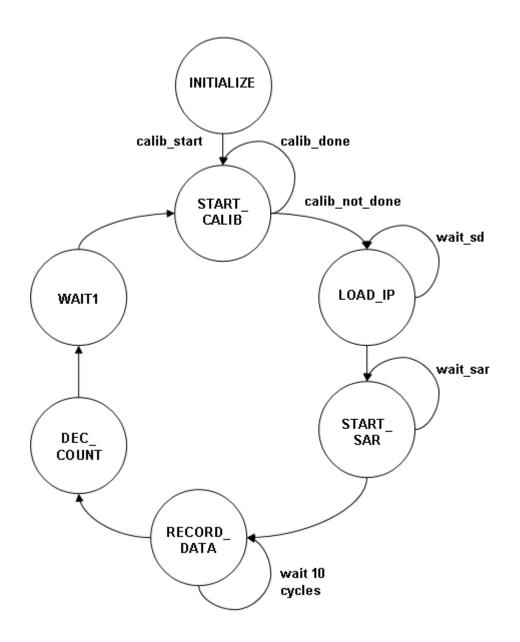

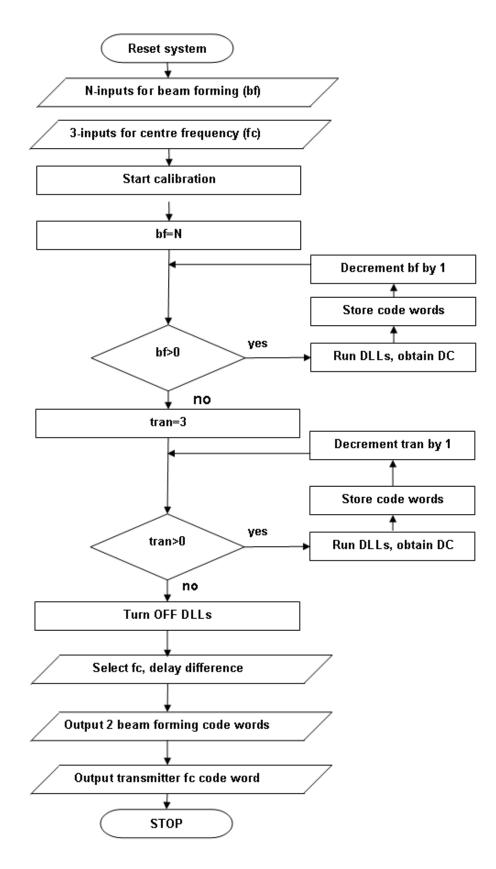

The digital calibration FSM was built in verilog. The FSM has registers that can be programmed through the serial to parallel interface. Based on the programming, the FSM will calibrate the beamforming delay subsystem and it will also calibrate the transmitter delay cell to produce the required centre frequency. The FSM implemented in verilog is depicted in Figure 5.12.

Figure 5.12: Digital calibration FSM

The FSM consists of 7 states. The descriptions of these states are as follows.

**INITIALIZE:** The FSM enters this state as soon as the system is reset. It remains in the same state until the calib\_start bit is set.

**START\_CALIB:** After programming the required calibration configuration and providing the inputs needed for calibration, the calib\_start bit is set and the FSM reaches

this state. If the calibration is complete, then the FSM stays in the same state. If calibration is not complete, then the FSM checks the calibration that needs to be done and proceeds to the LOAD\_IP state. The FSM also resets the sigma-delta DLL and SAR DLL in this state.

**LOAD\_IP:** This is the load input state. In this state the inputs needed for generating the required delay are fetched from the registers and the FSM provides them to the sigma-delta DLL and activates the latter. The FSM remains in the same state until the sigma-delta DLL settles. After the sigma-delta DLL settles the FSM proceeds to the START\_SAR state.

**START\_SAR:** This state activates the SAR DLL and waits for the SAR DLL to lock. Once it locks, the FSM obtains the digital code word corresponding to the required delay. It then moves to the RECORD\_DATA state.

**RECORD\_DATA:** This state records the digital code word obtained for the required delay into the register files. It waits about 10 cycles before proceeding to the next state.

**DEC\_COUNT:** This state decrements the calibration counter for every set of input that has been calibrated by the FSM. The calibration becomes complete when the calibration counter reaches zero.

**WAIT1:** The FSM waits for one clock cycle in this state before proceeding to the START\_CALIB state. This additional wait is to give sufficient time for the decrement operation to happen.

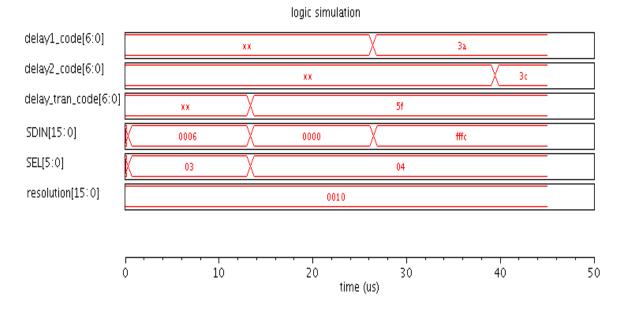

The inputs to the sigma-delta DLL control the beam former subsystem delay and the transmitter centre frequency. By programming the input, the centre frequency can be selected to be 3.5 GHz, 4 GHz or 4.5 GHz. The delay difference of the two delay elements used in the beam former subsystem can be controlled and hence the beam steering angle can be controlled. The calibration system feeds the digital code words to the beam forming delay subsystem and the transmitter. These in turn, generate four UWB signals with the desired centre frequency each separated by the required delay difference. Inputs corresponding to different delay values and three centre frequencies can be provided to the calibration FSM. From the results of the calibration obtained, the delay difference and the centre frequency to be used can be chosen. The complete digital calibration algorithm is summarized with help of a flowchart shown in Figure 5.13.

Figure 5.13: Digital calibration algorithm

The serial to parallel interface and the calibration algorithm were developed in verilog and they were implemented in FPGA and tested. The verilog models were also ported to Cadence. The digital calibration algorithm was verified in Cadence SpectreVerilog mixed signal simulation and was able to provide the required transmitter delay and beamforming delay code words. The sigma-delta DLL generates a delay in the range of 300ps to 600ps per delay cell, but the transmitter delay cell generates a delay in the range of 90 to 150ps. Hence, to utilize the same delay range generated by 5 delay cells of the sigma-delta DLL to calibrate the transmitter centre frequency, the SAR DLL compares the analog delay with the delay generated by 16 delay cells of the transmitter SAR delay line. The relation between the sigma-delta DLL inputs and the expected transmitter delay per cell can be obtained by

$$Transmitter \ delay/cell = 5(Delay/cell)/16$$

(5.6)

where, *Delay/cell* is given by equation 4.2.

The results obtained from Cadence simulation for the transmitter centre frequency calibration are tabulated in Table 5.1.

| SEL | SDIN | Expected<br>centre<br>frequency<br>(GHz) | Expected<br>delay<br>in ps | Transmitter<br>Delay Digital<br>Codeword | Obtained<br>delay(ps) | Obtained<br>centre<br>frequency<br>(GHz) |

|-----|------|------------------------------------------|----------------------------|------------------------------------------|-----------------------|------------------------------------------|

| 3   | 6    | 3.5                                      | 143.68                     | 1011111                                  | 140                   | 3.57                                     |

| 5   | -2   | 4.0                                      | 126.26                     | 1010010                                  | 123                   | 4.06                                     |

| 7   | -8   | 4.5                                      | 111.61                     | 1001100                                  | 109                   | 4.59                                     |

Table 5.1: Transmitter delay centre frequency calibration from Cadence

These results demonstrate the capability of the transmitter to generate the precise centre frequency. The results for the beamforming delay obtained for different modulator control words are as follows

|     |      |                           | Exp.                | Obtained            |                     |

|-----|------|---------------------------|---------------------|---------------------|---------------------|

| SEL | SDIN | Avg. No of delay<br>cells | delay/cell<br>in ps | Delay/cell in<br>ps | Digital<br>Codeword |

| 2   | -6   | 9.125                     | 547.95              | 540                 | 1010001             |

| 2   | -4   | 9.250                     | 540.54              | 530                 | 1001111             |

| 5   | -2   | 12.375                    | 404.04              | 398                 | 0110100             |

| 5   | 0    | 12.500                    | 400.00              | 392                 | 0110011             |

| 10  | -8   | 17.000                    | 294.12              | 292                 | 0010111             |

| 10  | -5   | 17.1875                   | 290.91              | 287                 | 0010011             |

**Table 5.2:** Beamforming delay calibration results from Cadence

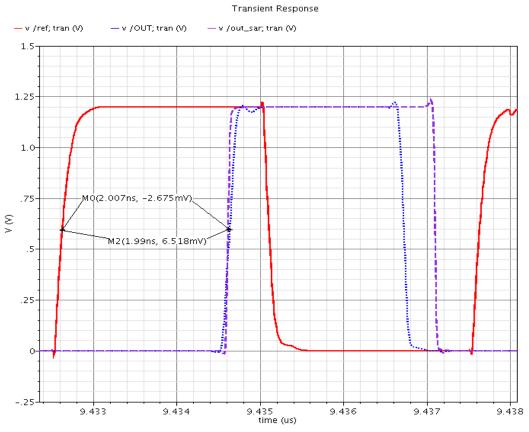

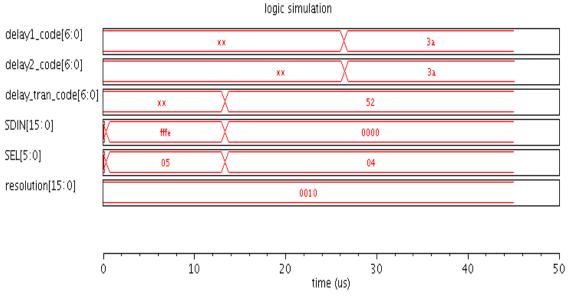

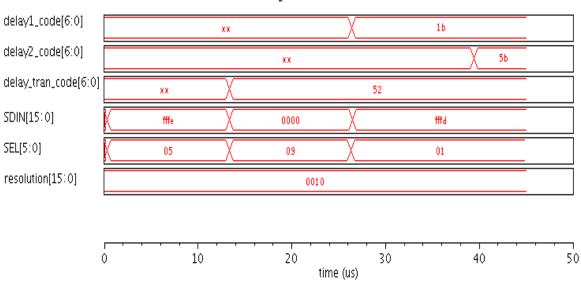

The Cadence simulation result obtained for a particular input of 5, -2 is depicted in Figure 5.14. The obtained delay between the reference signal and sigma-delta DLL output is 2.007ns. This is the delay of 5 delay cells. Hence, the delay of one delay cell produced by sigma-delta DLL is 401.4ps. The delay between reference signal and the output of SAR DLL is 1.99ns. Hence, the delay of one delay cell generated by the SAR DLL is 398ps which is very close to the required delay of 404ps differing by just the digital delay resolution.

Figure 5.14: Fractional-N sigma-delta & SAR calibration result from Cadence

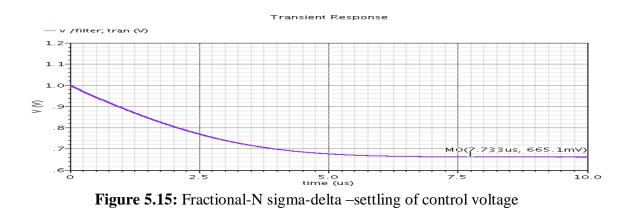

The settling of the loop filter control voltage is shown in Figure 5.15. In order to speed up the simulation, the filter voltage was set at 1V instead of 1.2V.

52

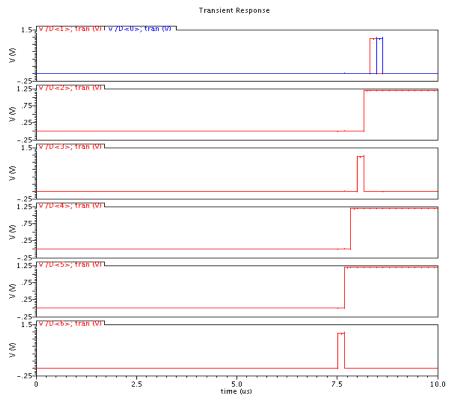

Figure 5.16: Digital code word from SAR DLL (MSB bottom -LSB top)

The figure 5.16 illustrates the digital code word obtained from the SAR DLL. Thus, the obtained digital code word for the required delay is 0110100. This digital code word is stored by the FSM.

The inputs to the sigma-delta DLL were varied to generate all possible delay values that can be generated by the system within the range of 300ps to 600ps. The delay difference between the different delay values obtained from the sigma-delta DLL and SAR DLL for adjacent inputs is plotted against the delay in Figure 5.17

Figure 5.17: Delay resolution of Sigma-delta and SAR DLL

This plot clearly depicts the capability of the system to generate very fine delay. From the plot, it can be observed that both the sigma-delta DLL and the SAR DLL can generate a delay resolution of less than 10ps. Hence, the beam former delay subsystem with the vernier delay architecture can provide a delay resolution of less than 10ps.

# 5.5 All-digital UWB transmitter

### 5.5.1 Transmitter delay line

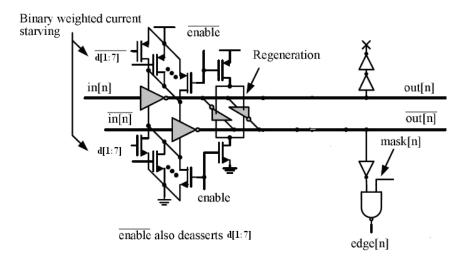

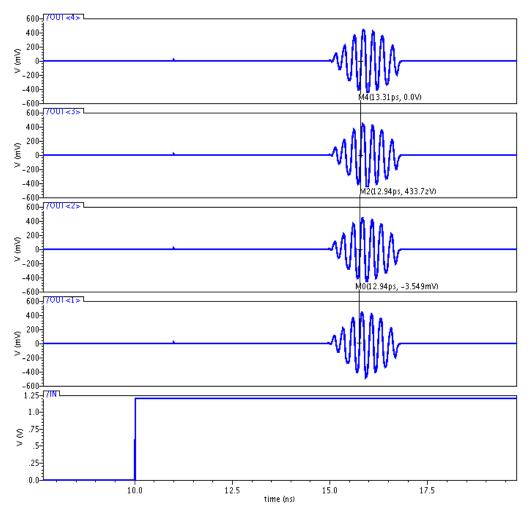

The digital transmitter consists of 7-bit digitally controlled pseudo differential current starved inverter delay line. This is based on reference [2]. This delay line uses only the sizing of the switches to control the delay. The switches are binary weighted.

Figure 5.18: 7-bit digitally controlled transmitter delay from [2]

No current source is used in this delay line in order to avoid static power consumption in the transmitter. The delay cell was designed to provide a delay in the range of 90ps to 150ps in all temperatures and corners. The cross coupled inverters connected at the output helps in regeneration and are used to equalize the rise and fall time of the signals [2]. The edges from the delay line are masked to control the pulse width of the output. With a 32-stage delay line, the pulse width can be tuned from 500ps to 4ns.

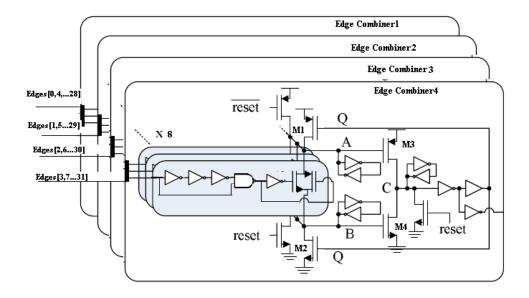

## 5.5.2 Edge combiner

The state preserving edge combiner was adopted from [12]. This edge combiner can work up to 5GHz. The edge combiner is shown in Figure 5.19.

Figure 5.19: Time interleaved edge combiner from [12]

After reset, the node A is charged to VDD and node B is discharged to ground. The node C is discharged to ground and the NMOS transistor M2 turns on. When a positive edge comes, it creates pulse of width equal to three inverter delays. This pulse will turn on the transmission gate for a short period and the node A will now discharge through the transmission gate and the NMOS transistor M2 to ground. Once the node A voltage reaches VDD-Vtp of the PMOS transistor, M3 turns on and the output node C is charged up and this will change the value stored by the latch at C to high. Once C becomes high, Q becomes low. It will turn on the PMOS transistor M1 and turn off the NMOS transistor M2, and node A is charged back to VDD. When the next edge comes, the transmission gate is on and the node B is charged through the transmission gate and the PMOS M1 to VDD. Once the node B voltage crosses the Vtn of the NMOS transistor, M4 turns on.

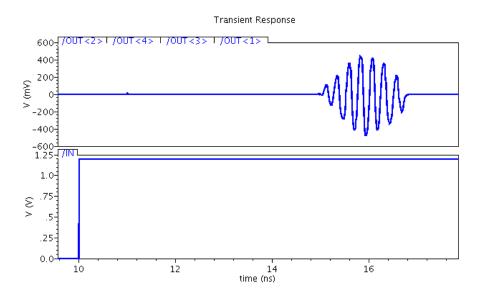

hence Q becomes high. Now the PMOS transistor M1 turns off and the NMOS transistor M2 turns on, and the same process repeats itself for every positive edge fed to the combiner. The delay of the transmitter delay cell decides the centre frequency of the transmitter. The edge combiner combines these delayed edges to produce the UWB pulse.

Figure 5.20: UWB pulse generation

Each edge combiner cell combines 8 edges to produce a pulse train. These pulses are then passed through a xor tree to produce the desired UWB signal.

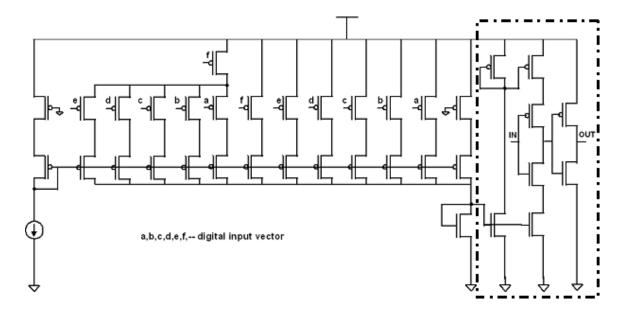

# 5.5.3 Digital PA and pulse shaping

One of the power hungry blocks in a UWB transmitter is the power amplifier. Hence, an energy efficient power amplifier is needed. In [3], they employ a digital power amplifier (PA) using capacitively coupled pulse shaper for BPSK signal generation. The architecture is all-digital and is energy efficient. In their architecture, they use ring oscillator to generate the RF pulses. A pulse shaping circuitry is used to provide pulses to the digital PA to shape the output pulse. It uses just two capacitors to generate the required UWB pulse and is thus area efficient. Therefore, the same architecture is adopted with modifications to the pulse shaping logic to give more freedom in controlling the shape of the generated UWB pulse.

Figure 5.21: Dual capacitively coupled digital PA from [3]

The pulse shaping logic implemented in this design generates 7 pulse shaping signals. In comparison to the pulse shaping logic implemented in [3], the pulse shaping logic used in this design provides additional flexibility to control the amplitude of each pulse individually. This modification was primarily done, because the UWB signal generated with dual capacitively coupled digital power amplifier would result in an asymmetric UWB pulse signal. This asymmetry is due to the change in average DC value of the capacitors during pulse generation. The individual amplitude control of each pulse of the output UWB signal helps in overcoming this issue. It also provides more flexibility in obtaining a FCC compliant UWB pulse.

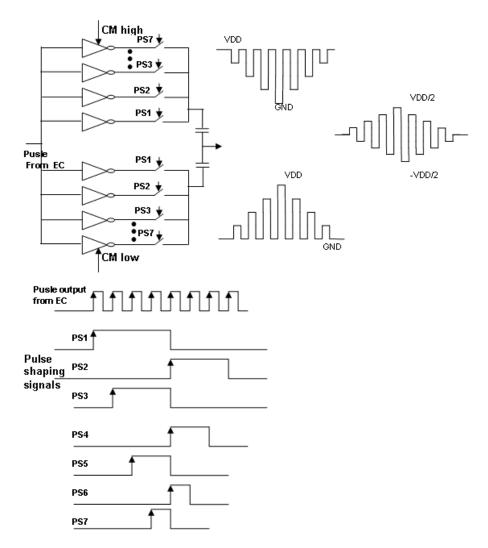

The basic concept on which the capacitively coupled pulse shaper [3] works is that when two pulses with in-phase RF components and out of phase common mode components are provided to the capacitors, the common mode components cancel each other and the RF components propagate to the output. The digital PA circuits consist of tri-state inverters and pulse shaping is obtained by controlling number of inverters that are ON at a particular time.

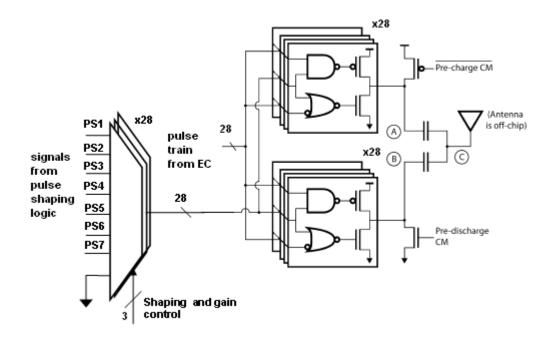

Figure 5.22: Pulse shaping logic

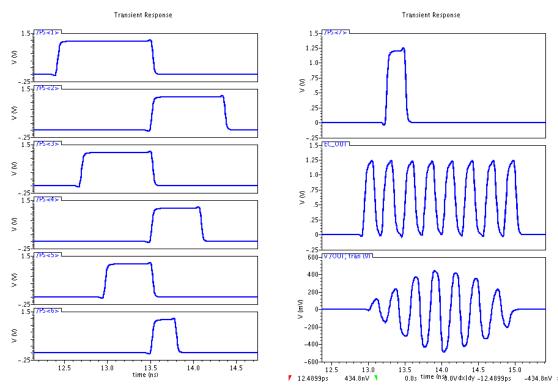

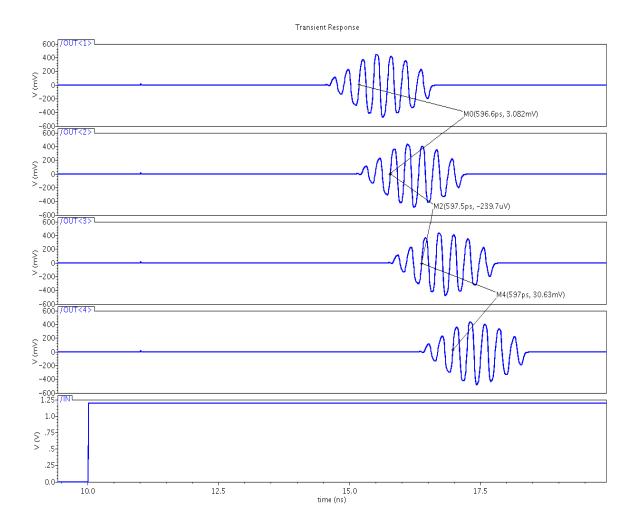

The edge combiner generates the RF pulse signal. Feeding the same RF pulse signal to both top and bottom paths of the digital PA ensures the in-phase RF signal. The differential baseband is generated by ensuring that the outputs of the two PAs are at opposite supply rails immediately before and after pulse generation [7]. The pulse shaping logic will generate the signals PS1 to PS7 as shown in Figure 5.22. These pulse shaping signals along with edge combiner output are fed to the digital PA. Since both capacitors are charging and discharging at the same rate, they approach the same average value during pulse generation. This can be seen as a low frequency transient at the two nodes A and B. However, the changes in average value in both paths are same. If the two paths match, then the low frequency transients get attenuated giving the output UWB pulse at node C with lesser low frequency components [7]. The shape of the pulse can be altered by selecting the number of inverters that would be ON at a particular time through the MUX network [7]. The result obtained with a simple four level shaping of the output pulse from Cadence simulation is as shown in Figure 5.23. The loading of the output antenna was modeled with a 50 ohms resistor in the simulations.

Figure 5.23: UWB four level pulse and pulse shaping signals generated in Cadence

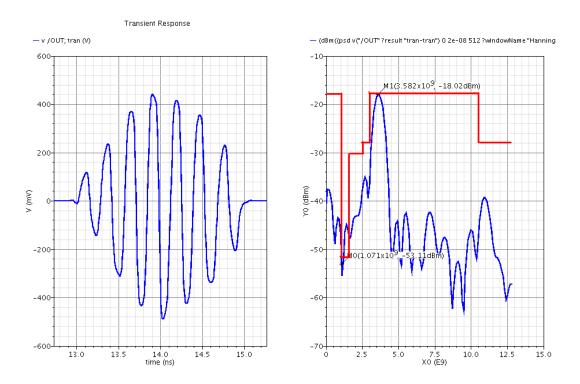

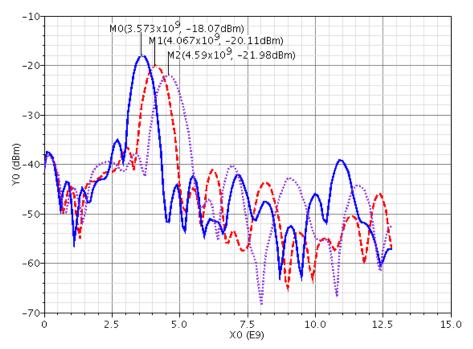

The power spectral density (PSD) plot provided by Cadence will produce the spectrum in terms of dBm/Hz. To obtain the PSD in terms of dBm/MHz, a value of 60dBm needs to be added to the spectrum of the signal. The resulting spectrum of the signal is shown in Figure 5.24. The UWB spectral mask is drawn to show the relative suppression that is required to meet the specifications.

Figure 5.24: Spectrum of the four level UWB pulse generated in Cadence

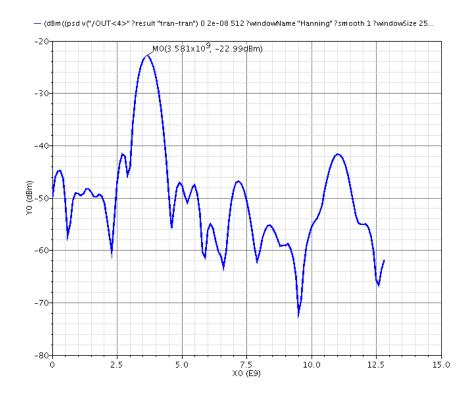

The spectrum of the output pulse is still not compliant to the FCC mask. The pulse spectrum violates the mask by about 8dB in the GPS band. The system provides the flexibility to control the output pulse shape, pulse width and gain. One such pulse obtained by varying the pulse shape and width is shown in Figure 5.25.

Figure 5.25: Spectrum of the UWB pulse generated in Cadence

The spectrum of this pulse is better than the spectrum of the signal with four level pulse shaping, as it violates the GPS band only by about 4dB. With the level of programmability offered by the system to control the shape, width and gain of the pulse it should be possible to satisfy the UWB mask without using any external filters. The mux network provides the flexibility to digitally control the pulse shape. It provides  $2^{28}$  combinations to tune the pulse shape and make it FCC compliant.

# 5.6 Full system simulation results and discussion