**Board Level Drop Testing of Advanced IC Packaging**

PEK WEE SONG ERIC

NATIONAL UNIVERSITY OF SINGAPORE

2004

# **Board Level Drop Testing of Advanced IC Packaging**

PEK WEE SONG ERIC (M.Eng, NUS)

# A THESIS SUMITTED FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF MECHANICAL ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2004

# Acknowledgements

The author would like to express his heart-felt gratitude to the following people without whom the project would not have been a success.

Associate Professor Lim Chwee Teck and Dr. Vincent Tan B.C. for their wisdom, guidance and supervision.

Mr. Tee Tong Yan, Dr. Luan Jing En, Mr. Daniel Yap and Mr. Goh Wee Lee from ST. Microelectronics for their assistance and guidance to the project.

Mr. Joe Low, Mr. Simon Seah and Mr. Alvin Goh from Impact Mechanics Lab for their patience and technical support during the course of experimentation.

Mr. Tan Long Bin, Mr. Ong Yeow Chon, Ms. Ang Chia Wei, Mr. Ridha, Mr. Alvin Ong and Mr. Norman Lee for their kind help in various issues of the project.

Ms. Ng Fong Kuan for her assistance in the conduct of experiment.

Huiying and my family members for their love and encouragement

People who have helped me in one way or another.

# **Table of Contents**

| Acknow    | vledgements                                                       | i  |

|-----------|-------------------------------------------------------------------|----|

| Table of  | f Contents                                                        | ii |

| List of S | Symbols and Abbreviations                                         | v  |

| List of I | Figures                                                           | vi |

| List of ] | Tables                                                            | x  |

| Summa     | ry                                                                | xi |

| Chapter   | 1 Introduction                                                    | 1  |

| 1.1       | Background and Motivation for Research                            | 1  |

| 1.2       | Objectives                                                        | 2  |

| 1.3       | Scope of Thesis                                                   | 2  |

| Chapter   | 2 Literature Review                                               | 4  |

| 2.1       | Overview of shock and drop test standards                         | 4  |

| 2.2       | Review of board level drop tests                                  | 6  |

| 2.2       | 2.1 High-speed photography                                        | 7  |

| 2.2       | 2.2 Effect of underfill material on drop reliability of packaging |    |

| 2.2       | 2.3 Effects of thermal aging on drop reliability                  | 9  |

| 2.3       | Review of board level drop test simulation                        |    |

| 2.4       | Review of other mechanical loading tests on PCBs                  | 13 |

| 2.4       | L1 Cyclic bending and vibration tests                             | 13 |

| 2.4       | A.2 Ball shear tests                                              | 15 |

| Chapter   | 23 Experimental Setup and Procedures                              | 17 |

| 3.1       | Experimental setup                                                | 17 |

| 3.2       | Test specimens                                                    |    |

| 3.3       | Basic mechanics of drop test                                      |    |

| 3.4       | Characterization of the drop tester                               |    |

| 3.4       | 1.1 Drop height characterization                                  | 24 |

| 3.4       | 1.2 Strike surface characterization                               | 27 |

| 3.4       | L3 Drop conditions for 1500G peak level                           |    |

| 3.4       | I.4   Repeatability of drop test                                  |    |

| 3.5       | Overview of drop test plan                                        |    |

| 3.5       | 5.1 Test plan for TFBGA components                                |    |

| 3.5     | 2 CABGA components test plan                                               | 31   |

|---------|----------------------------------------------------------------------------|------|

| Chapter | 4 Board Level Drop tests for TFBGA Packages                                | 33   |

| 4.1     | Setup of the TFBGA packages                                                | 34   |

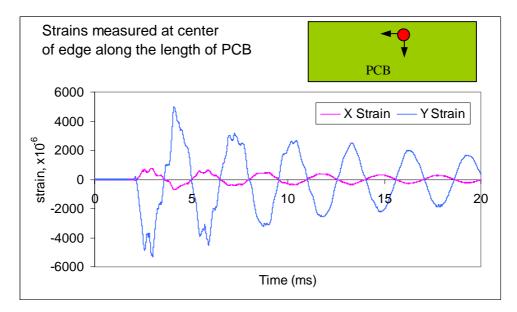

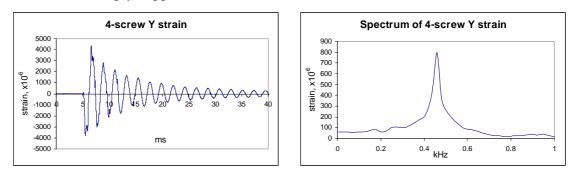

| 4.2     | Strain measurements during impact                                          | 35   |

| 4.3     | Study of board level drop test using high-speed photography                | 38   |

| 4.4     | Monitoring change of velocity during impact                                | 40   |

| 4.5     | In-situ resistance monitoring of solder interconnect during board level of | lrop |

|         | test                                                                       | 43   |

| 4.5     | 1 Setting a failure criteria                                               | 43   |

| 4.5     | 2 Resistance monitoring during drop impact                                 | 44   |

| 4.5     | .3 Crack initiation, propagation and opening of solder interconnects       | 46   |

| 4.6     | Batch testing on TFBGA/LFBGA packages                                      | 47   |

| Chapter | 5 Board Level Drop Tests for CABGA Packages                                | 50   |

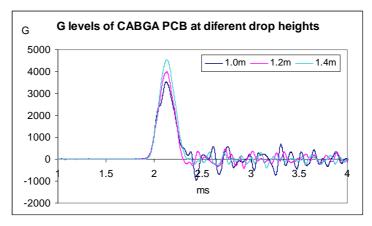

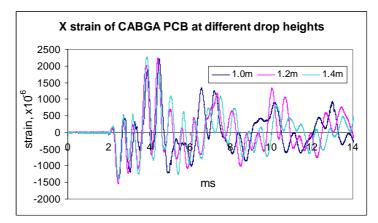

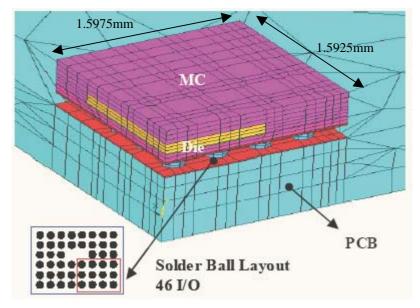

| 5.1     | Effect of drop height on drop responses of CABGA PCB                       | 50   |

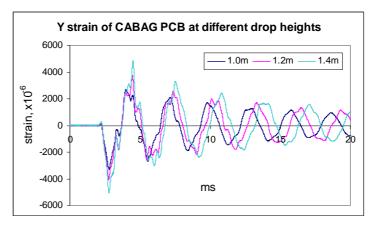

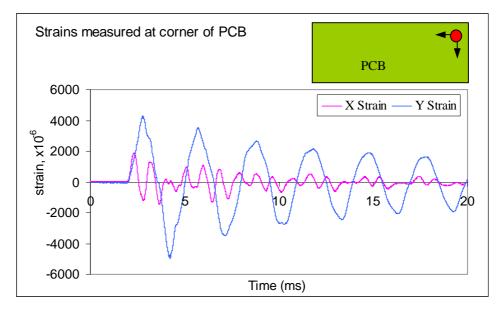

| 5.2     | Effect of board bending during drop impact                                 | 52   |

| 5.3     | Effect of different screw support configurations                           | 55   |

| 5.4     | Effect of other clamp fixations                                            | 58   |

| 5.5     | Dynamic resistance measurement                                             | 60   |

| 5.6     | Effect of board level mounted with components with underfill material      | 62   |

| 5.7     | Effect of knocking of the PCB                                              | 64   |

| 5.8     | Effect of the tightness of screws at the spacers                           | 66   |

| Chapter | 6 Numerical Simulation of Board Level Drop Tests                           | 68   |

| 6.1     | Input-G method                                                             | 68   |

| 6.2     | Correlation with dynamic responses of actual tests                         | 71   |

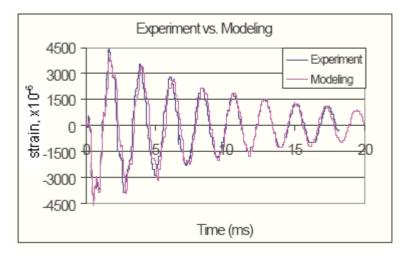

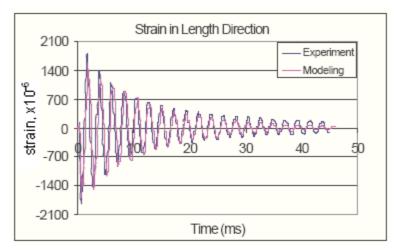

| 6.2     | 1 PCB strain in the length direction                                       | 71   |

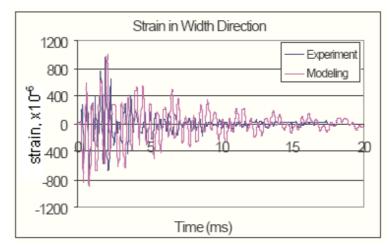

| 6.2     | 2 PCB strain in the width direction                                        | 72   |

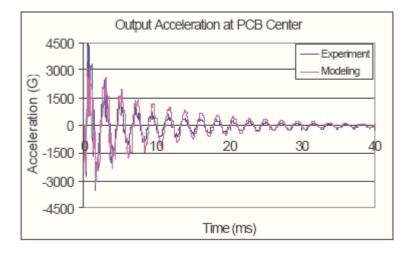

| 6.2     | .3 Acceleration at PCB center package                                      | 73   |

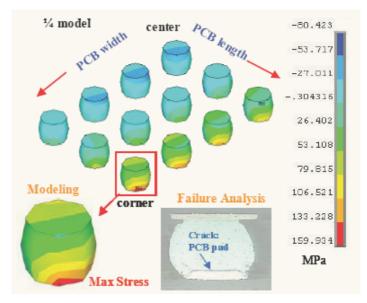

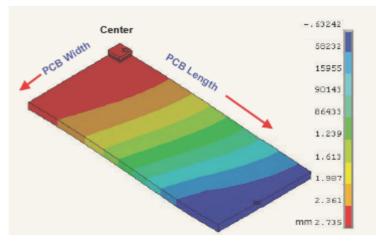

| 6.3     | Failure analysis of the model                                              | 74   |

| 6.4     | Natural bending frequency of PCB                                           | 76   |

| Chapter | 7 Conclusions                                                              | 79   |

| 7.1     | Drop test methodology                                                      | 79   |

| 7.2     | Experiment findings using TFBGA board                                      | 79   |

| 7.3     | Experiment findings using CABGA board                                      | 80   |

| 7.4     | Correlation of experimental results to modeling                            | 80   |

| 7.5              | Recommendations                                             | 80    |

|------------------|-------------------------------------------------------------|-------|

| List of <b>F</b> | References                                                  | 82    |

| Appendi          | ix A: Technical Drawings                                    | 89    |

| Appendi          | ix B: Experimental Plots                                    | 95    |

| Appendi          | ix C: High-speed camera images                              | 101   |

| C.1:             | High-speed images of PCB knocking effect                    | 101   |

| C.2:             | High-speed images of TFBGA board width side                 | 104   |

| C.3:             | High-speed images of TFBGA board mounted on nuts and screws | . 105 |

| Appendi          | ix D: Experimental Procedures                               | 106   |

# List of Symbols and Abbreviations

| $\mathbf{f}_{\mathbf{n}}$ | natural frequency of vibration                                           |

|---------------------------|--------------------------------------------------------------------------|

| v <sub>b</sub>            | rebound velocity                                                         |

| $G_m$                     | maximum G level of impulse profile                                       |

| X <sub>0</sub>            | initial amplitude of deflection of a vibrating beam                      |

| AFOP                      | Gold (Au) on Finger, Organic solderability Preservative on ball pad      |

| BLR                       | Board Level Reliability (pg. 10)                                         |

| BGA                       | Ball Grid Array                                                          |

| CABGA                     | Ceramic Array BGA                                                        |

| CRO                       | Cathode Ray Oscilloscope                                                 |

| CSP                       | Chip Scale Packaging                                                     |

| DNP                       | Distance to Neutral Point                                                |

| EIA                       | Electronic Industries Association                                        |

| FBGA                      | Fine-pitch BGA                                                           |

| FCOB                      | Flip Chip On Board                                                       |

| G level                   | $1G = 9.81 \text{ m/s}^2$                                                |

| JEDEC                     | Joint Electron Device Engineering Council                                |

| PDA                       | Personal Digital Assistant                                               |

| PCB                       | Printed Circuit Board                                                    |

| SMT                       | Surface Mount Technology                                                 |

| TFBGA                     | Thin Fine-pitch BGA                                                      |

| VFBGA                     | Very thin Fine-pitch BGA                                                 |

| X-, Y- strains            | strains in along the width and length directions of the PCB respectively |

# List of Figures

| Figure 2.1: Cross section of extremely thin CSP                                    | 7             |

|------------------------------------------------------------------------------------|---------------|

| Figure 2.2: Weibull plot of number of drops to failure for various preappli        | ed solders    |

| [36]                                                                               | 9             |

| Figure 2.3: Mean cycles to failure for board level drop test as a function o       | f aging time. |

|                                                                                    | 10            |

| Figure 2.4: Stress distribution of solder joints during maximum PCB bend           | ling11        |

| Figure 2.5: Hybrid model for FCOB assembly                                         | 12            |

| Figure 2.6: Von Mises Stress due to drop impact [31]                               | 13            |

| Figure 2.7: PCB setup with simulated masses and mounting position (sphe            | erical bend)  |

|                                                                                    | 14            |

| Figure 2.8: Spherical Bend, Diagonal Bend and Planar Bend                          | 14            |

| Figure 2.9: Schematics of (a) conventional shear test and (b) miniature Ch         | arpy test 15  |

| Figure 3.1: Lansmont drop tester                                                   |               |

| Figure 3.2: New Drop Table                                                         |               |

| Figure 3.3: APX High-Speed Camera Apparatus                                        | 19            |

| Figure 3.4: Endevco Accelerometers with Petrol Wax                                 |               |

| Figure 3.5: Coaxial strain gauge (1mm gauge length)                                | 21            |

| Figure 3.6: Charge Amplifiers, Strain Meters and a CRO                             |               |

| Figure 3.7: CABGA (left) and TFBGA (right) packages on PCBs                        |               |

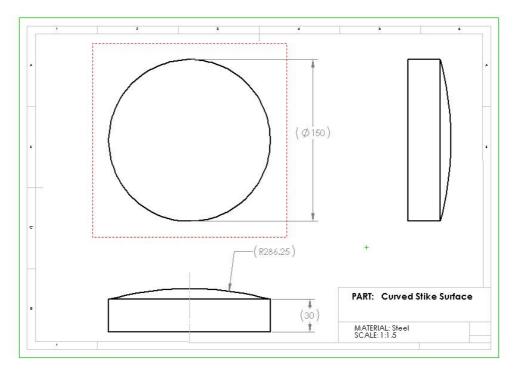

| Figure 3.8: Curved strike surface (toughened steel)                                | 23            |

| Figure 3.9: Impact pulses under different drop height                              |               |

| Figure 3.10: Comparing A and $G_m$ from plot of A against drop height, $H_{\dots}$ |               |

| Figure 3.11: Approximation of impact pulse shapes                                  |               |

| Figure 3.12: Impact pulse duration vs. drop height                                 |               |

| Figure 3.13: Effect of number of felt layers on impact pulse                       |               |

| Figure 3.14: JEDEC standard of 1500G using Lansmont drop tower                     |               |

| Figure 3.15: Plot of G level against time for peak acceleration of 1500G for       | or different  |

| number of layers of felt material                                                  |               |

| Figure 3.16: Repeatability of shock pulses at 1.5m drop height                     |               |

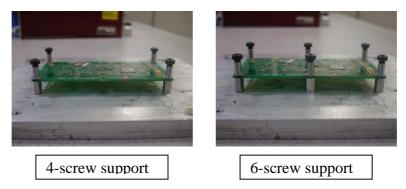

| Figure 3.17: 4-screw support layout                                                |               |

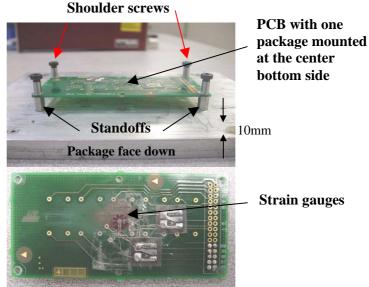

| Figure 4.1: Setup of board level drop test                                         |               |

| Figure 4.2: Types of screw fixations of PCB on fixture                                   |

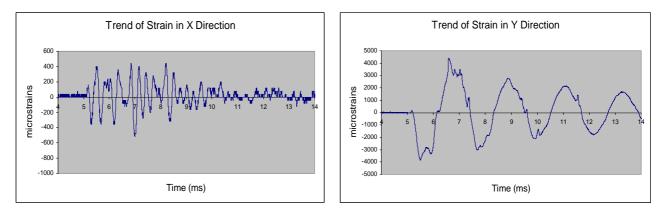

|------------------------------------------------------------------------------------------|

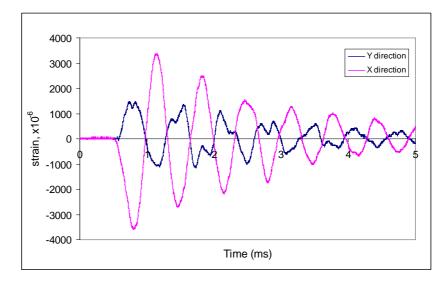

| Figure 4.3: Strains induced in the X and Y directions on the PCB for the 4-screw         |

| suppport                                                                                 |

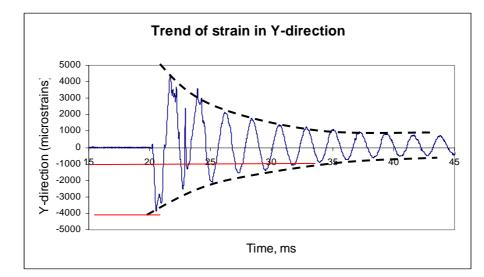

| Figure 4.4: Trend of the plot of Y-strain against time for the 4-screw support case 37   |

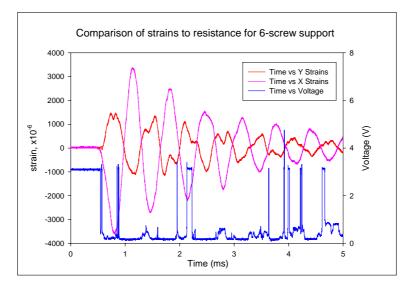

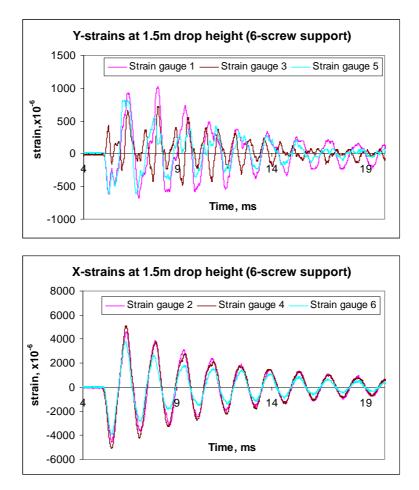

| Figure 4.5: Plots of strains against time for the 6-screw support case                   |

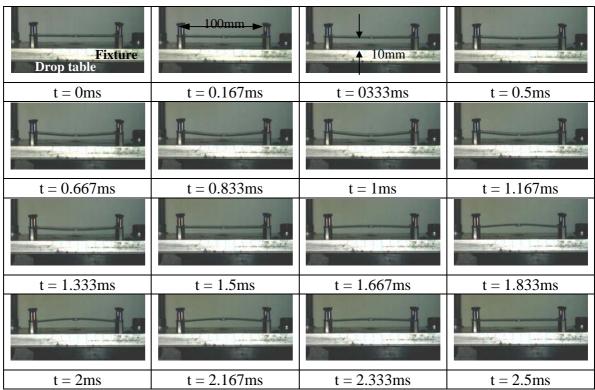

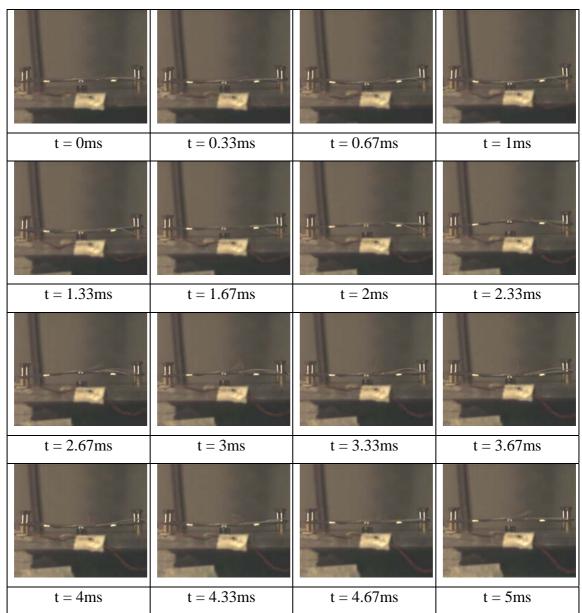

| Figure 4.6: High-speed images showing bending of PCB upon impact for the 4-screw         |

| support                                                                                  |

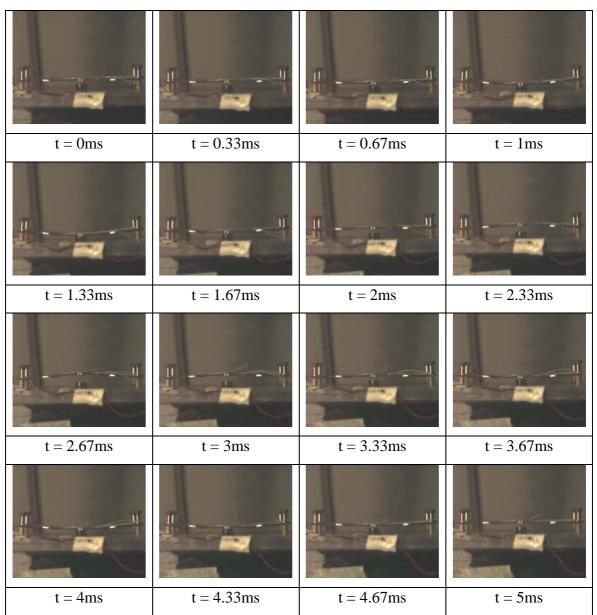

| Figure 4.7: High-speed images showing bending of PCB upon impact for the 6-screw         |

| support40                                                                                |

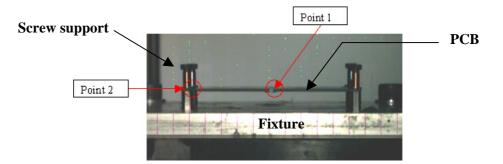

| Figure 4.8: Location of two tracking points on the PCB and near the screw support 41     |

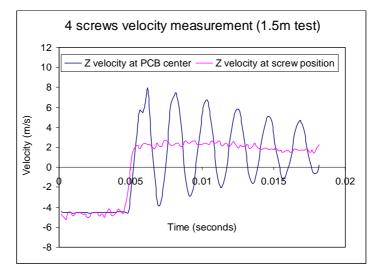

| Figure 4.9: Plot of velocity against time for the 4-screw support case at PCB center and |

| near screw support location41                                                            |

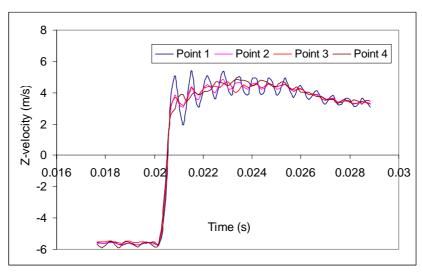

| Figure 4.10: Location of four tracking points along width of PCB for the 6-screw         |

| support case                                                                             |

| Figure 4.11: Plot of velocity against time for a 6-screw support at various locations    |

| along the width of the PCB                                                               |

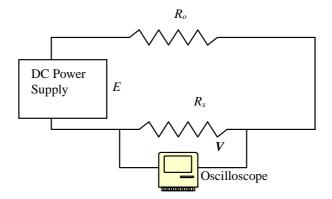

| Figure 4.12: Circuit setup of resistance monitoring of TFBGA packaging                   |

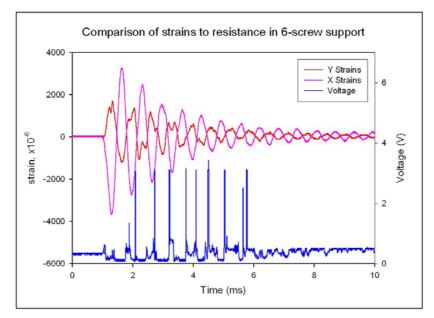

| Figure 4.13: Plot of in-situ resistance and strain readings for a 6-screw support        |

| Figure 4.14: Stress induced in solder joints during PCB bending                          |

| Figure 4.15: Plot of in-situ resistance and strain readings for 6-screw support (2)46    |

| Figure 4.16: Solder joint failure process as described by the change in resistance curve |

|                                                                                          |

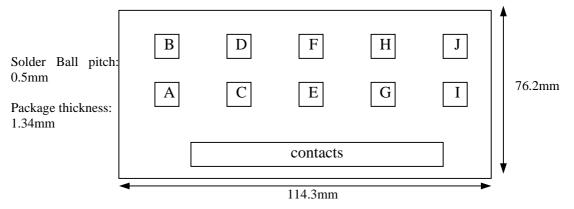

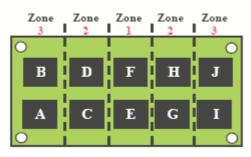

| Figure 5.1: Mounting and labeling of CABGA components in the PCB                         |

| Figure 5.2: Drop responses of CABGA mounted PCB at 1.0, 1.2 and 1.4m drop height         |

|                                                                                          |

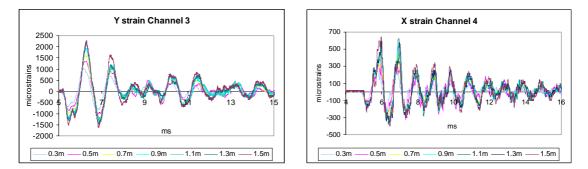

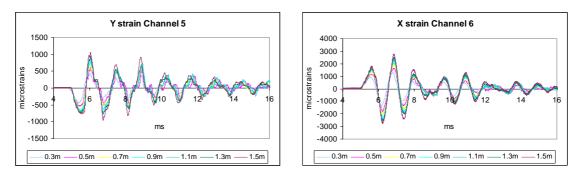

| Figure 5.3: Plot of in-plane strains against time at different locations of the PCB 54   |

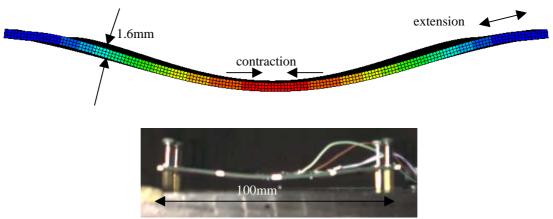

| Figure 5.4: Curvature of the bending of PCB during drop impact                           |

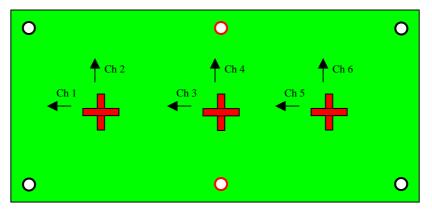

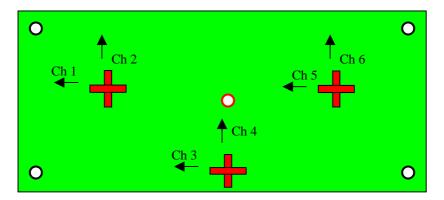

| Figure 5.5a: Position of strain gauges mounted for 4/6-screw support                     |

| Figure 5.5b: Position of strain gauges mounted for 5-screw support                       |

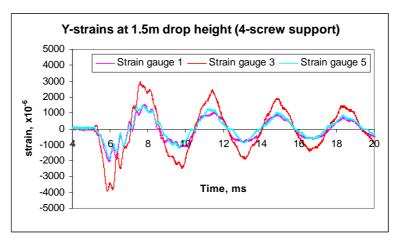

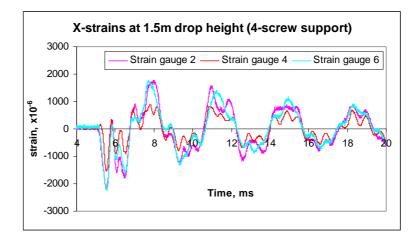

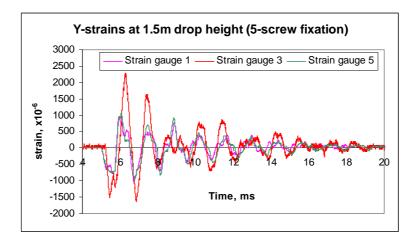

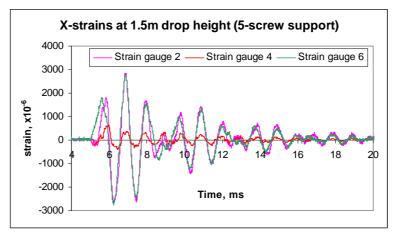

| Figure 5.6a: Plots of X- and Y-strains against time for the 4-screw support57            |

| Figure 5.6b: Plots of X- and Y-strains against time for the 5-screw support              |

| Figure 5.6c: Plots of X- and Y-strains against time for the 6-screw support              |

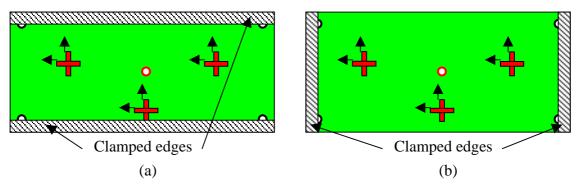

| Figure 5.7: (a) Clamping along lengthwise and (b) along the widthwise edges of PCB       |

|                                                                                          |

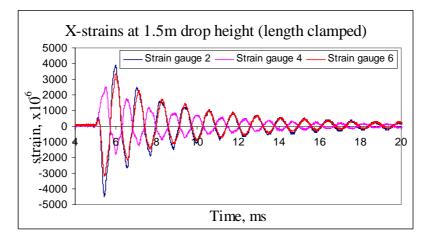

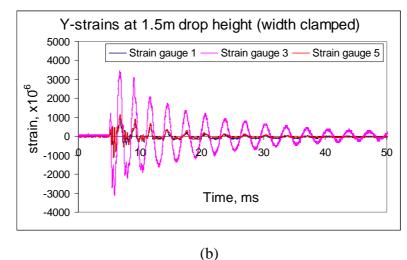

| Figure 5.8: Strains in length / width clamped configurations                           | . 59 |

|----------------------------------------------------------------------------------------|------|

| Figure 5.9: Package position on test board                                             | . 60 |

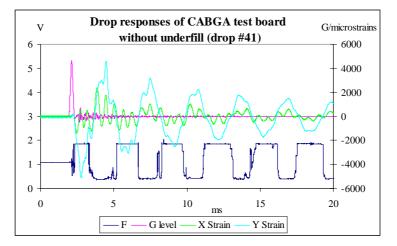

| Figure 5.10: Drop responses of CABGA components without underfill material             | . 61 |

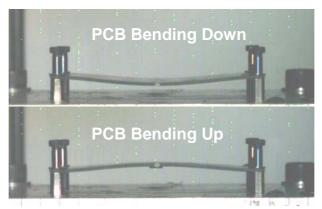

| Figure 5.11: Bending of PCB for the 4-screw support case                               | . 61 |

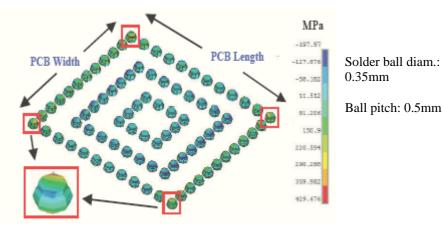

| Figure 5.12: Distribution of solder joint peeling stresses in from a numerical simulat | tion |

| [13]                                                                                   | . 62 |

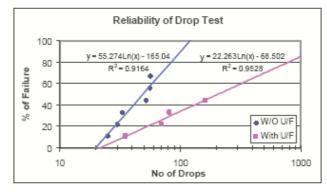

| Figure 5.13: Comparison of reliability results of CABGA components during drop t       | est  |

| (with and without underfill)                                                           | . 63 |

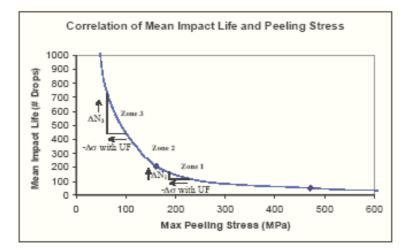

| Figure 5.14: Impact life prediction for CABGA components [13]                          | . 64 |

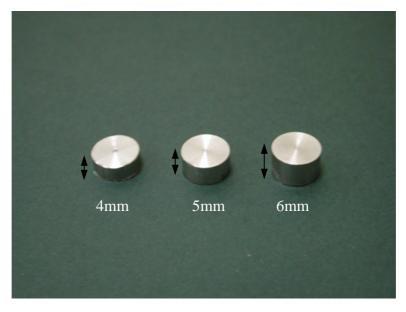

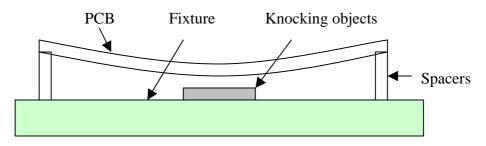

| Figure 5.15: Picture of knocking objects used at the fixture                           | . 65 |

| Figure 5.16: Schematic diagram of side view during drop impact                         | . 65 |

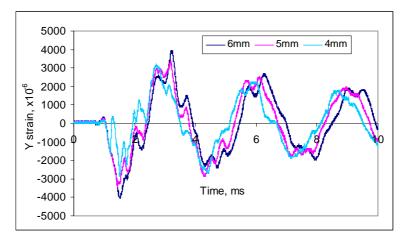

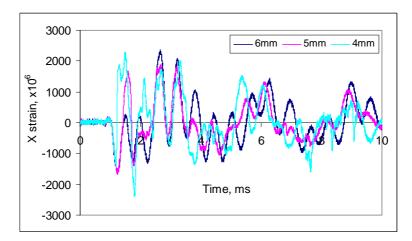

| Figure 5.17a: Plot of Y-strain with different clearance heights                        | . 66 |

| Figure 5.17b: Plot of X strain with different clearance heights                        | . 66 |

| Figure 5.18: Plot of Y-strain for both tightened and loosened screw configurations     | . 67 |

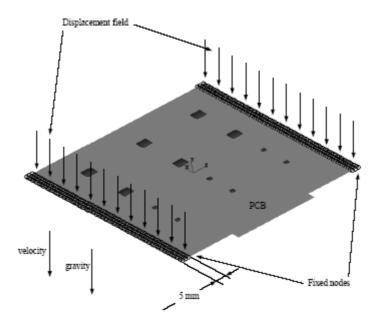

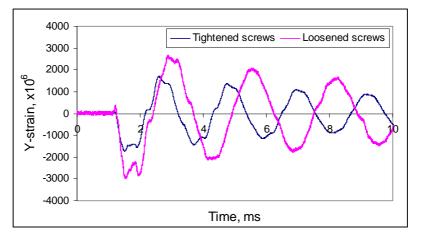

| Figure 6.1: Input-G method for 4-screw PCB subassembly                                 | . 69 |

| Figure 6.2: Board Level Drop Test for TFBGA46                                          | . 69 |

| Figure 6.3: Input acceleration curve for FE simulation                                 | . 70 |

| Figure 6.4: Comparison of strain (length) curves                                       | .71  |

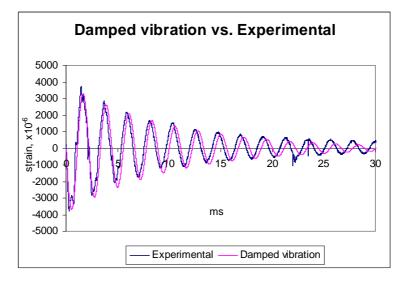

| Figure 6.5: Comparison of a damped vibration system and experimental result            | . 72 |

| Figure 6.6: Comparison of strain (width) curves                                        | . 72 |

| Figure 6.7a: Comparison of strain (length) curves from actual tests and simulation     | .73  |

| Figure 6.7b: Comparison of acceleration from actual tests and simulation               | .74  |

| Figure 6.8: Location of critical solder ball and failure interface                     | . 75 |

| Figure 6.9: PCB out-of-plane displacement distribution at maximum bending              | . 75 |

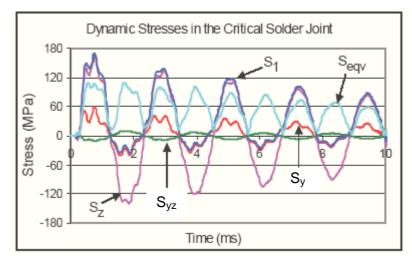

| Figure 6.10: Dynamic stresses during drop impact                                       | .76  |

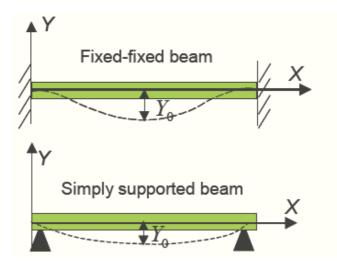

| Figure 6.11: Beams with different boundary conditions                                  | .77  |

| Figure 6.12: FFT of 4-screw fixation longitudinal strain                               | . 78 |

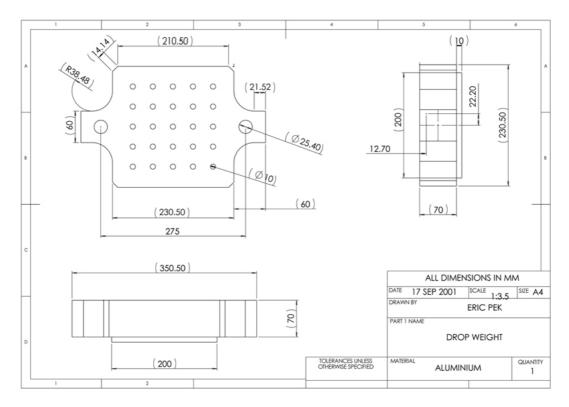

| Figure A.1: Drop table drawing                                                         | . 89 |

| Figure A.2: Curved strike surface drawing                                              | . 89 |

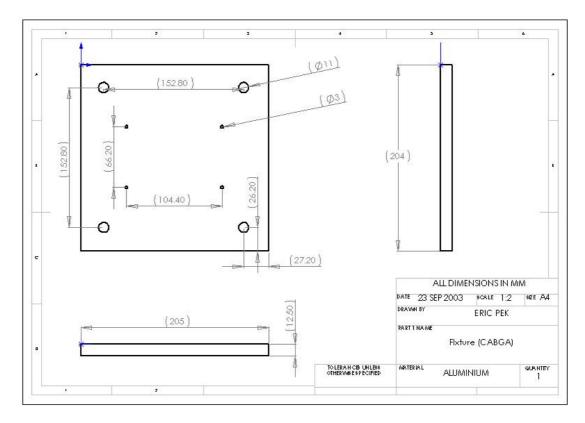

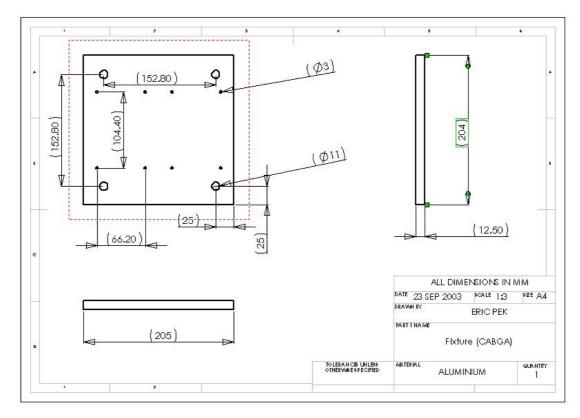

| Figure A.3: Fixture for CABGA board at center                                          | . 90 |

| Figure A.4: Fixture for 2 CABGA boards                                                 | . 90 |

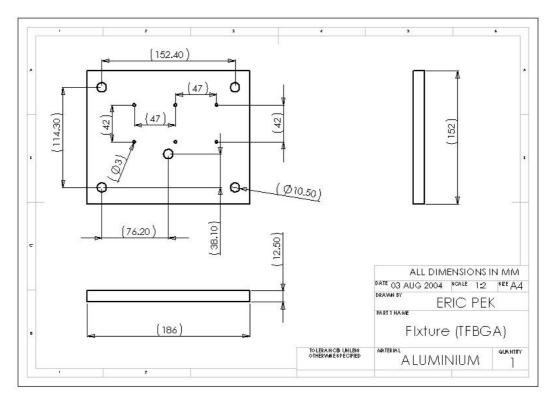

| Figure A.5: Fixture for TFBGA board                                                    | . 91 |

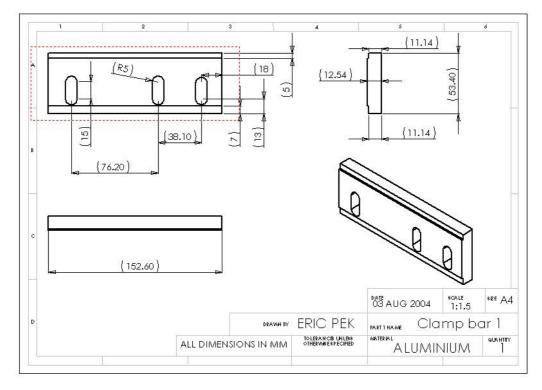

| Figure A.6: Clamping bar type 1                                                        | . 91 |

| Figure A.7: Clamping bar type 2                                                        | . 92 |

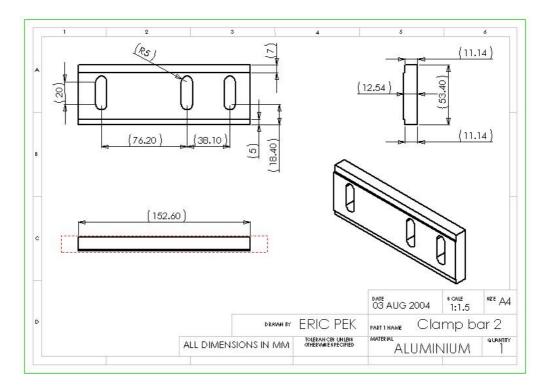

| Figure A.8: JEDEC Proposed Test Board Size and Layout                                                                      |

|----------------------------------------------------------------------------------------------------------------------------|

| Figure B.1: Plot of A and $G_m$ vs. drop height                                                                            |

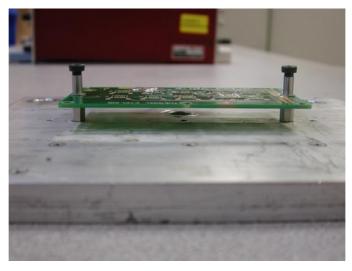

| Figure B.2: 2-screw support for TFBGA board96                                                                              |

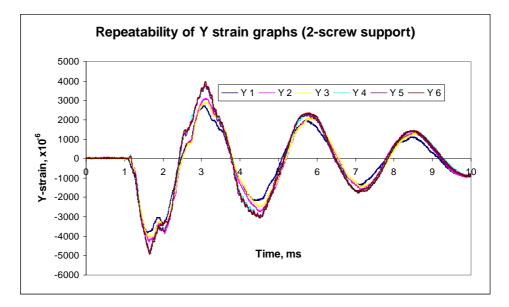

| Figure B.3: Plot vs time for Y-strain reading at the center of the board (2-screw                                          |

| support)                                                                                                                   |

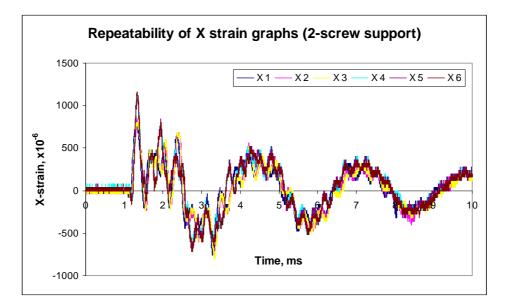

| Figure B.4: Plot vs time for X-strain reading at the center of the board (2-screw                                          |

| support)                                                                                                                   |

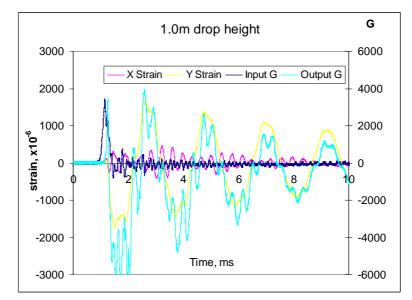

| Figure B.5: Plots of strains and output acceleration vs time for test on CABGA board                                       |

| conducted at 1m drop height97                                                                                              |

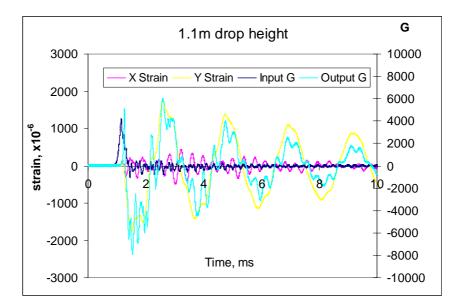

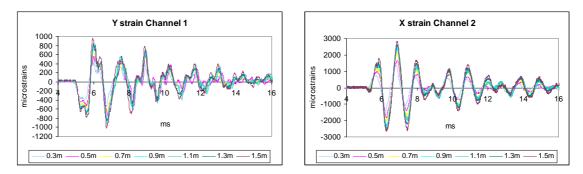

| Figure B.6: Plots of strains and output acceleration vs time for test on CABGA board                                       |

| conducted at 1.1m drop height98                                                                                            |

| Figure B.7: Plots of strains and output acceleration vs time for test on CABGA board                                       |

| conducted at 1.2m drop height                                                                                              |

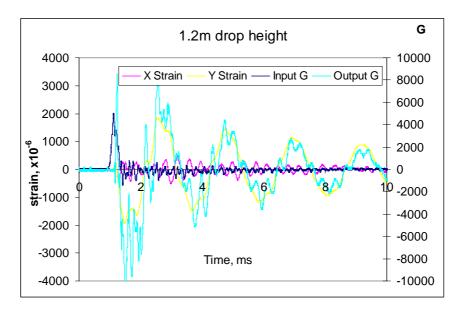

| Figure B.8: Plots of output acceleration vs time for tightened and loosened screw                                          |

| mounting                                                                                                                   |

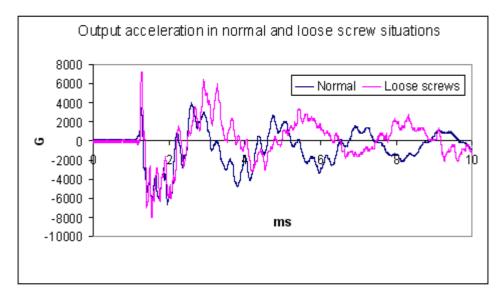

| Figure B.9: Drop height study of 5-screw support on CABGA board (ch 1 and 2) 99                                            |

| Figure B.10: Drop height study of 5-screw support on CABGA board (ch 3 and 4) 99                                           |

| Figure B.11: Drop height study of 5-screw support on CABGA board (ch 5 and 6). 100                                         |

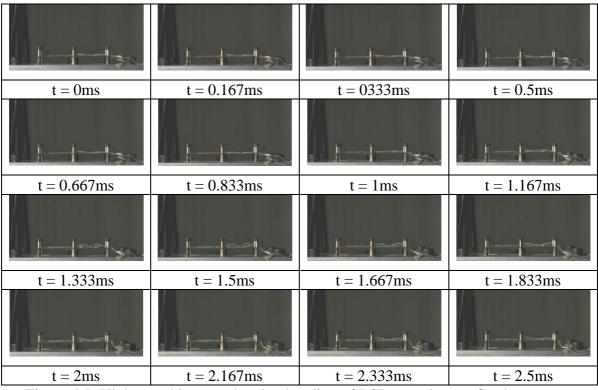

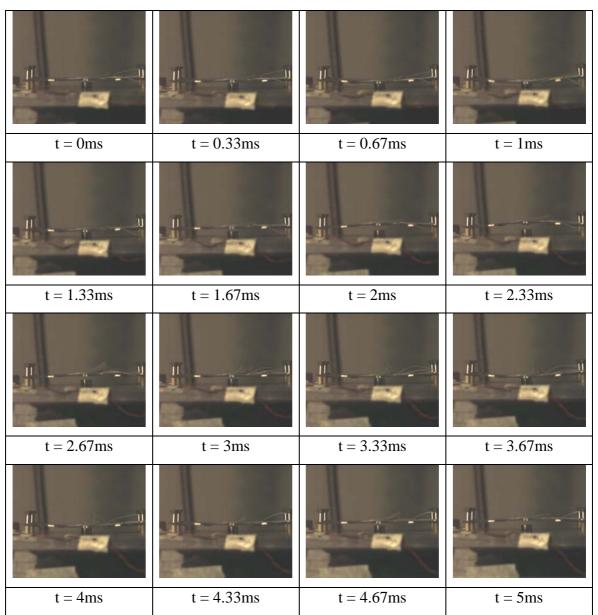

| Figure C.1: Investigating the knocking effect of PCB arising from clearance height of                                      |

| 6mm conducted at 1.5m drop height 101                                                                                      |

| Figure C.2: Investigating the knocking effect of PCB arising from clearance height of                                      |

| 5mm conducted at 1.5m drop height                                                                                          |

|                                                                                                                            |

| Figure C.3: Investigating the knocking effect of PCB arising from clearance height of                                      |

|                                                                                                                            |

| Figure C.3: Investigating the knocking effect of PCB arising from clearance height of                                      |

| Figure C.3: Investigating the knocking effect of PCB arising from clearance height of 4mm conducted at 1.5m drop height    |

| Figure C.3: Investigating the knocking effect of PCB arising from clearance height of<br>4mm conducted at 1.5m drop height |

# List of Tables

| Table 4.1: Drop test matrix of BGA packages                                   | 48 |

|-------------------------------------------------------------------------------|----|

| Table 4.2: Drop test results of BGA packages                                  | 49 |

| Table 5.1: Mean impact life and first failure life during drop test           | 63 |

| Table 6.1: Material properties used in model                                  | 70 |

| Table A.1: X, Y coordinates for the centers of the components                 | 93 |

| (Center of lower left screw hole used as datum)                               | 93 |

| Table A.2: Component locations for test boards                                | 93 |

| Table A.3: Component Test Levels                                              | 94 |

| Table B.1: Effect of drop height on peak acceleration / area under G(t) graph | 95 |

### Summary

With the increase in demand for smaller telecommunications products like cellular mobile phones and PDAs, the use of microelectronic packaging such as BGA in electronic products has been widespread. As a result, accidental drop of these products may contribute to failure of the microelectronic packaging.

This project aims to investigate the drop impact responses of the microelectronic packaging such as during a drop impact. The components are tested on different drop heights and drop orientations. A number of drops are conducted on each PCB to investigate the number of failures induced on the different types of packaging. Their corresponding position and the number of drops at which the packages fails are examined. Strain gauges are also mounted at the center of the PCB to find the maximum strains induced in the principal axes of the PCB.

Drop impact responses (input and output acceleration levels, strains, velocity, flexing of PCBs etc) are analyzed and correlated to gain insight into the failure mechanisms of these electronic packages. Drop tests are conducted according to the new standards proposed by JEDEC. In addition, the effects of using different strike surfaces and varying different drop heights are also studied to simulate the likely conditions that a product drop test can encounter during an accidental drop impact.

Failure analysis is done on the samples to examine the possible failure modes encountered during impact. This is done using the cross-sectioning methods on the failed samples. A greater depth of understanding of the most likely regions of failure at the solder interconnects can be obtained.

xi

# **Chapter 1** Introduction

#### **1.1 Background and Motivation for Research**

The usage of portable electronic products is getting more and more prevalent in the present society. Examples are portable digital assistants (PDAs), MP3 players, minidisc (MD) players and cellular phones. However, such mobility-enhancing products are susceptible to accidental drop impact. They are still expected to function even when that has occurred. Therefore robustness becomes an important issue in investigating the reliability of these products. A portable product normally houses a printed circuit board (PCB) with many components mounted on it. One common failure mode due to drop impact is the failure of the solder joints in some of these components. Testing for solder joint reliability is an important part in determining the failure of portable products during drop impact.

There are usually two main types of drop impact for these products. It could arise from mishandling during transportation of these products or from consumers who accidentally drop these products. Normally, for some products such as mobile phones, they are designed to withstand a few accidental drops onto a floor at a height of 1.5m, without causing major mechanical or functional failures [42-44].

Traditionally, board level reliability usually refers to solder joint fatigue strength during thermal cycling or thermal shock tests [13]. There are many researchers who have applied viscoplastic modeling to achieve accurate fatigue life prediction of solder interconnects in this area of research. However, there are few research work and publications related to drop test and modeling of solder joint reliability, although drop test should be as important as thermal tests, especially for the telecommunications industry. There is also very little study on correlation between simulation and experimental testing.

The motivation of this project lies in the fact that little is known on how microelectronic packages fail when electronic products are subjected to accidental drops. This study aims to find out how these components fail compared to other modes involving thermal cycling and key-press failures (usually found on mobile phones).

From this study, it is desired that we determine the factors that affect drop impact reliability and how these can help to obtain a more robust design of the IC package.

# 1.2 Objectives

The objectives of this research project are to:

- develop a standard methodology to study solder joint reliability by performing a board level drop test

- develop a method of in-situ resistance monitoring of the components during drop impact

- obtain relationship of the drop response parameters and the survivability of the components

- study how different mounting configurations of PCB can affect solder joint reliability

### 1.3 Scope of Thesis

This thesis comprises seven chapters. Chapter 2 presents an overview on the past research done on experimental board level drop tests and computational modeling of these tests. Past and recent board level drop test standards for different test conditions, size of PCBs and type of mounting are discussed. For board level drop tests, the effects of underfill, lead-free solders and thermally aged packages on drop reliability are discussed. Different board level modeling and simulation methodologies from various work and their correlation to actual experiment is studied. In addition, other mechanical tests closely related to board level drop tests are also reviewed.

Chapter 3 introduces the experimental setup and procedures for the drop tests. The drop test setup includes the drop tester, various fixtures, drop response monitoring equipment like strain gauges and accelerometers, and high-speed camera apparatus. The chapter also discusses the setup conditions to refine the board level drop tests in achieving consistency and ideal test requirements. Mechanics of drop impact are being discussed in detail and the maximum G level and impact time duration derived from momentum equations. Test plans for Thin Profile Ball Grid Array (TFBGA) and Chip Array BGA (CABGA) boards are also discussed.

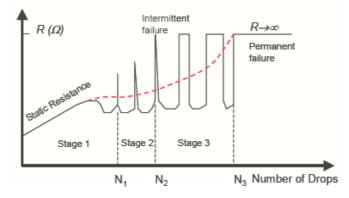

Chapter 4 discusses the drop impact responses obtained from experiments. These responses include the shock experienced by the whole drop table, which is termed input G level, the in-plane strains at the center of the PCB and other points of interest on the PCB and the electrical resistance level of the components during the duration of drop impact. Output G levels are measured directly on some of the components located at critical locations of the PCB. The damping effect of the board is investigated and the high-speed images captured during drop impact are used in calculating impact velocity and board bending frequency. In-situ resistance measurement is conducted on packages during drop impact and the trend of these measurements is discussed.

Chapter 5 discusses the effects of board bending arising from different mounting configurations. These include different screw mounting and clamped edges configurations. In addition, the effect of knocking of the PCB against the fixture is studied and compared to cases where the PCBs have clearance to bend during impact. For CABGA packages, the effect of having underfill encapsulation is investigated.

Chapter 6 presents a new modeling methodology of using G levels as input boundary conditions and numerical results obtained are correlated with experimental data. The extent of board bending, solder joint stresses and frequency of cyclic bending can be predicted from the model if the correlation of the drop impact responses from experiment to modeling is accurate. The deflection of the board bending can be estimated to a beam-bending situation under certain assumptions with appropriate boundary conditions. This is discussed at the end of Chapter 6.

Chapter 7 then concludes the thesis and also provides recommendations for future work.

# **Chapter 2** Literature Review

This chapter presents a review of the past research work done on drop impact and other mechanical related tests for components. The topics include current standards used for board level drop tests, drop tests done thus far on various kinds of packages and board sizes, an overview of vibration and cyclic bending tests of PCBs and their effects on packaging material, and other mechanical loading tests that have been used to evaluate solder reliability.

#### 2.1 Overview of shock and drop test standards

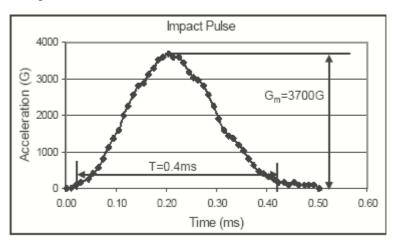

The EIA standard [1] suggests several acceleration waveforms for drop tests. For a half sine pulse waveform with time duration less than 3ms, the maximum value of the measured pulse must be within  $\pm 20\%$  of the specified ideal pulse amplitude and its duration must be within  $\pm 15\%$  of the specified ideal pulse duration. However, this standard does not provide much detail on how the test specimens are to be mounted and tested for reliability.

Military Standard for microelectronics [3] has various shock test conditions. Among these conditions, shock condition B requires an input of 1500G with impact duration of 0.5ms to be used in free-fall drop test conditions. This condition is in line with the JEDEC proposed standard [7] and is quite close to the shock levels experienced by small electronic products due to accidental drop as reported by Low [46].

The JEDEC standard "Board Level Drop Test of Components for Handheld Electronic Products" [7] is not to be used as a component qualification test. Instead, the test procedure is more suited for relative component performance against board level drop impact. Previous JEDEC standards [5, 6] did not provide enough details on the testing procedures nor specify a standardized board.

In [7], the specified overall board size is 132 mm x 77 mm. It has a nominal thickness of 1 mm and can accommodate up to 15 components (3 rows by 5 columns). It is not necessary to mount all 15 components on the board. 1-component and 5-component configurations are provided in this standard. The maximum component is limited to 15

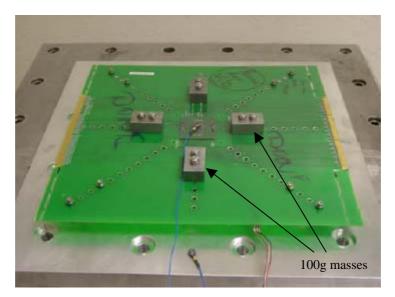

mm in length or width and there must be at least 5 mm and 8 mm gaps between the components in x- and y-directions, respectively. There are four holes on the board for mounting the board on the drop test fixture. The locations of these holes are shown in Figure A.8 of Appendix A. The board is tightened by 4 shoulder screws with washers and supported by 4 spacers. The spacers are fixed onto a fixture plate. In the actual testing of components reported in this thesis, a metric system is adopted instead of the suggested Imperial unit as hardware is more readily available in the metric system. While shoulder screws ensure a higher degree of tightening than normal screws, the test board must still be tightened at regular intervals as high G level drop tests causes large board flexure during and after drop impact which causes the shoulder screws to loosen.

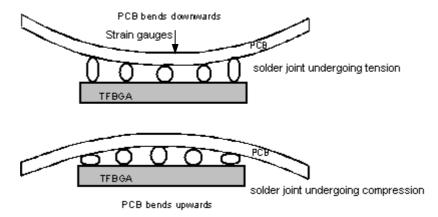

The horizontal board orientation with components facing downward results in greatest tensile force at the solder joints of a component placed at the center of the board due to the board flexure downwards after impact and the inertia of the whole component moving downwards. Thus, this is the orientation that is most likely to cause failures. Therefore, the standard requires that the board be fixed horizontally with components facing downwards during the test. Pre-test characterization is required to achieve JEDEC Condition B of 1500G amplitude and 0.5 milliseconds time duration with half sine waveform. The characterization requires monitoring of output acceleration and inplane strains of the component at the center region of the PCB. In this thesis, the input acceleration and the center in-plane strains are always monitored. The hardness of the strike surface is adjusted to achieve the desired impact time duration.

During drop testing, the board is to be dropped for a maximum of 30 times or until 80% of all devices have failed, whichever is earlier. If there are no failures, JEDEC also proposes other drop conditions like Condition H of amplitude 2900G with 0.3 ms duration. However, the failure rate depends on a lot of factors including weight of the components, adhesion strength of the solder joints and the number of I/O.

Initial testing was done on small lightweight BGA components in the facedown orientation and it was found that Conditions B and H are not severe enough to cause failures in these components. A more severe condition is required to accelerate the

failure rate of these components. Thus, the most severe condition possible from the available drop tester of amplitude 4000G with 0.3 ms duration is used most of the time.

### 2.2 Review of board level drop tests

In a typical drop test of boards that are shaped like motherboards in mobile telephones, maximum compressive board strain of about 3800 microstrains were measured when the motherboard experienced a direct fall of 1m drop height from Mishiro et al. [28]. Three types of packages were tested using the same motherboard for many drops and their failure rates recorded. It was found that proper underfilling reduced the motherboard strain and stress of the solder ball. Yasuhisa et al. [49] reported extensive reliability data on key pressing and drop testing of a mobile telephone. Different loading rates were applied in 3-point bending tests to evaluate the failure reliability of the CSP devices in the PCB. Strain gauges were mounted on a cellular phone to determine the strain at various points of interest (where the CSP is located) during drop test. These strain profiles are for cross comparing with other cellular phones of similar mounting specifications of the motherboard and size.

Challenges abound when conducting proper drop tests. For example, drop tests of packages with BGA solder joints by Yu et al. [29] did not achieve good repeatability of shock levels at drop heights 0.8m and higher due to air resistance. However, if the friction of the jigs' bushes with the sliding rods of the drop tester was kept constant, repeatability can still be ensured and the failure results will be more representative of the drop height used. Hiraiwai and Minamizawa [30] evaluated fine pitch ball grid array (FBGA) packages and good reliability was achieved when the packages are mounted above the PCB. Hiraiwai and Minamizawa also dropped PCBs on their edges and found surface cracks on the board side.

Another problem that researchers often overlook is that a large PCB is not representative of PCBs in miniaturized mobile products. Furthermore, different products will have PCBs with different components of different sizes [24]. Testing with large PCBs is not recommended in the JEDEC standard [7]. Larger PCBs generally experience higher deflection and should not be used to compare with product drop tests, where the PCBs are much smaller. The position of components on a large PCB and the size of the components are important factors in drop impact performance. It is therefore difficult to design a single board level drop test to evaluate the impact reliability of a component that may be used in different products.

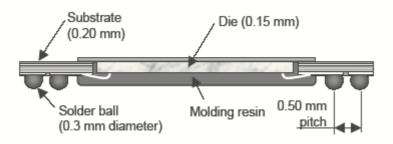

Extremely thin CSPs (etCSP), where the height from the top of the package to the surface of the board was only 0.5mm thick, were tested under JEDEC condition B by Yoshida et al. [33]. The cross section of the package is shown in Figure 2.1. This etCSP is cross-compared with that of a standard size CSP where the height of the package from the board is 1.2mm. In the cumulative failure plots given in the paper, it was found that etCSP had better drop reliability than the referenced CSP. This may be due to the heavier weight of the standard package resulting in greater inertia forces and higher peeling stresses at the solder joints. The etCSP is lighter and more flexible as its height is only 0.5mm and the molding area is just around the die. etCSPs were also found to be more reliable in cyclic bending tests.

Figure 2.1: Cross section of extremely thin CSP

#### 2.2.1 High-speed photography

High-speed imaging was deployed to monitor displacements of selected points of interest on the PCBs during drop impact testing by Wang et al. [27]. The frame rate used is 4500 frames per second. The velocity profile could be derived from the displacement plots. The displacement fluctuates in a cyclical manner at the center of the free edge, suggesting a dominant fundamental mode of vibration shortly after drop impact. Pradeep et al. [40] also used a high-speed camera setup to ensure good repeatability of the drop tests by monitoring the displacement and velocity of the PCBs. The velocity before impact could also be monitored so that the effects of friction along the guiding rods of the drop tower are taken into consideration. High-speed camera photography was also used to estimate the deflection of the PCB upon drop impact as done in Tan's work [18].

#### 2.2.2 Effect of underfill material on drop reliability of packaging

FCOB packages were reported to possess good drop impact reliability because of the presence of underfill encapsulation in these packages [27]. However, the input G level reported in the paper was too low to cause any failures. JEDEC recommends a minimum input of 1500G. In the experiment work presented in this thesis, much higher G levels are used to accelerate failures of BGA packages. Higher G levels will also mean higher maximum in-plane strains and higher deflection velocities of the PCB, resulting in higher strain rates in the solder joints eventually.

FCOB packages with underfill material generally have better drop reliability than FCOB packages without underfill as reported by Jang et al. [35]. Two conventional underfill technologies are capillary underfill and no-flow underfill. Jang et al. tested reworkable underfill for FCOB packages and found they had poor adhesion. However, they are still being used for SMT applications to reduce costs.

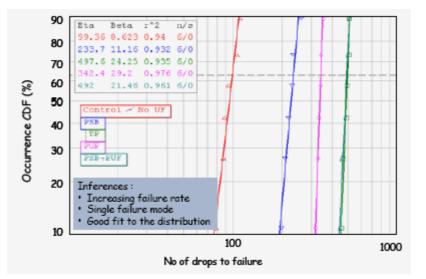

An alternative of using pre-applied underfill is discussed by Hannan et al. [36] where four different types of pre-applied underfill were evaluated. They are underfill preapplied to solder bumps (PSB), partial underfill (PUF), underfill preapplied to solder bumps with partial underfill (PSB-PUF) and perimeter underfill (TP). Drop tests were conducted on these four types of underfills with a CSP of dimensions 12 x 12 mm with 168 I/O at 0.8mm pitch. The test conditions were set at a G level of 1500G with a time duration of 30ms. Failures were detected using an event detector with a threshold limit of 1500 $\Omega$ . The Weibull plot of failures against number of drops is shown in Figure 2.2. In general, the drop reliability of the preapplied underfill CSPs is much better than similar CSPs without underfill. Figure 2.2 also summarizes the number of drops needed to get 63.2% failure for all cases. The number of drops for the control, i.e. no underfill, was around 100, compared to around 233 for PSB, 497 for TP, 342 for PUF and 492 for PSB-PUF. Additional drop test studies for evaluating underfill material are also found in [40] on lead and leadfree solders.

Figure 2.2: Weibull plot of number of drops to failure for various preapplied solders [36]

#### 2.2.3 Effects of thermal aging on drop reliability

Drop tests on lead-free solder showed that as the percentage of silver increases, the drop reliability generally decreases as reported in Amagai et al. [25]. This means that soft solder has an advantage over hard solder for drop test performance. However, it seems that in bending and thermal cycling tests [25], a relatively higher percentage of silver helps in the reliability of these solders. The suggested optimum solder composition for all three tests (drop, thermal cycling and bend tests) is about 1.0-1.5% Ag. Sn-Ag-Cu was also found to be better suited for dynamic loading as compared to Sn-Ag-Ni lead free solder. It is further shown that indium can reduce Kirkendall voids and nickel can reduce the thickness of the Cu<sub>3</sub>Sn layer in lead free solder [41]. With a correct solder composition, the drop performance can increase by 20% after thermal aging at 150°C.

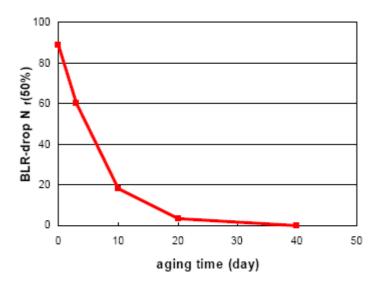

The effect of thermal aging on CSPs was studied in [38]. This study was conducted to investigate the influence of intermetallic compound (IMC) growth on the solder joint reliability of Pb-free BGA (SnAgCu solder on Cu pads) packages under drop loading conditions. Thermal aging of the test board assembly was performed at 125°C for 3, 10, 20 and 40 days to induce solid state IMC growth in solder joints. The shock pulse used for the drop condition is a triangular pulse with peak acceleration of 1500G and 1ms duration. It is found that the components near the test board mounting locations (at the corners) have higher drop lifetimes than components at the center of the test

board due to the lower vibration amplitude near board mounting points. Figure 2.3 shows the board level drop mean life as a function of aging time. It shows the drop performance (BLR- Board Level Reliability) degraded 80% from time 0 to 10 days of 125°C aging. After 40 days of thermal aging, the failure occurred at the first drop. This includes the corner components failing at the 1st drop. This is due to the formation of voids at the pad-solder interface under high temperature aging.

Figure 2.3: Mean cycles to failure for board level drop test as a function of aging time

#### 2.3 Review of board level drop test simulation

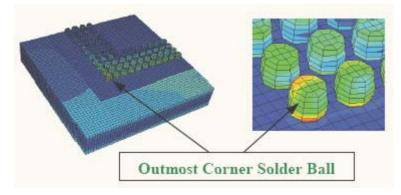

Zhu [19] used a sub-modeling method in LS-DYNA to analyze impact reliability to reduce CPU time. The time-history dynamic response from a macro global model is transferred to a micro local solder model in the sub-modeling approach. Two types of impact loading were tested. The first uses a guide tube to drop a sphere onto the center of the PCB. The second simulates a PCB free fall onto a hard surface. The second type of simulation is more relevant to the work presented in this thesis. The paper shows that the solder-to-component interface is where the maximum plastic strains occur and a crack is likely to initiate. This is in agreement with typical keypad loading tests. However, the failure location may not be the same for all cases as adhesion strength and degree of bending of the PCB are important factors as well. The sub-modeling technique was also used to evaluate the stresses in solder joints of different shape profiles. He found that a larger neck size at solder-to-component interface would decrease plastic strain as compared to a larger neck size at the solder-to-PCB interface. This will improve impact related

reliability. The simulation also determined that the solder ball most likely to fail is the one at the corner of the grid array.

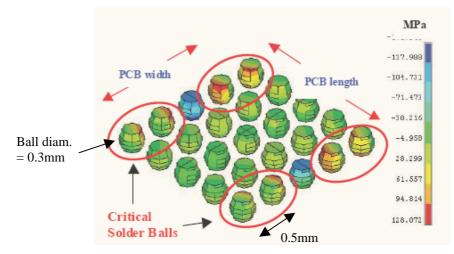

Tee et al. [17] did a simulation of board level drop test on Integrated Passive Devices (IPDs), using orthotropic properties for rectangular-shaped PCB and viscoelastic properties for eutectic and lead-free solder joints. The drop condition follows the JEDEC standard of an input acceleration peak of 1500G with time duration of 0.5ms. The results show the solder ball stress level is the highest when the PCB has the largest deflection, because of the inertia force after impact. High stress concentration is observed along both the solder/PCB and solder/IPD pad interfaces unlike [9] where high stress concentration is observed only at the solder/component interface. It is found that solder balls along the PCB length direction has a higher bending stress level (see Figure 2.4) because the board bends more along the length direction.

Figure 2.4: Stress distribution of solder joints during maximum PCB bending

Wang et al. [27] used a small hybrid model and a full detailed model to simulate board level drop tests Only the FCOB assembly including the PCB and silicon chips were modeled in the hybrid model (see Figure 2.5). The displacement data at the two longer clamped edges of PCB was obtained from video camera measurements. The results show that the detailed model yielded larger error than the hybrid model when compared to the experimental results. This is because a lot of factors in the detailed model are not considered such as friction along the guiding rods, effect of strike surface material and shape and rebound effect of the drop table. The hybrid model may pose some problems if the displacement profile used as the input for model does not have a small time step to accurately predict the level of acceleration in the FCOB

assembly. This gave results close to the output acceleration of the component itself, but it did not show a true picture of the stress levels in the solder joints because displacement was obtained from high-speed photographs. Acceleration data acquired by accelerometers is preferred as input data for simulation in the proposed G-input method mentioned in this thesis.

Figure 2.5: Hybrid model for FCOB assembly

Xu et al. [26] studied the effects of solder ball height and pad size on the stress levels of the solder joints under similar drop load conditions. The board is fixed with 4 screws at the corners with the component at the center of the board. Von Mises stresses and peeling stresses were compared. With 4-screw supports and the component at the center, peeling stress is more of a concern as board flexure is expected to be greatest at the center of the board. The difference in curvatures of the board and component induces large peeling stresses in the solder joints. It is believed that peeling stress in the joints (shown by the experiments in this thesis) is the dominant factor in the drop reliability of these packages. The paper shows that higher solder ball height, i.e. an increase in solder volume, results in higher peeling stress at the solder/component and solder/board interfaces. This is further supported by the simulations reported in [36]. Increasing the pad size decreases the peeling stress but increases the Von Mises stress on the board side [26]. Xu et al. also mentioned that while shorter solder ball height might have lower peeling stress, it is likely that it will experience higher shear stress, which is a concern when thermo-mechanical loading is present. The weight of

the package is also an important factor determining the magnitude of the peeling stress in the solder ball [36].

A model of PCB with mounted components using shell elements was proposed by Ren and Wang [31]. In the drop simulation, it was found that the relative difference in the peak Von Mises stress between the shell-element model and a solid-element model is only less than 3.5%. The computational time of the shell-element model only took 14% of the time to run the detailed 3D solid-element model. It is also found that the outermost corner solder experiences the most severe stress during drop impact, as shown in Figure 2.6.

Figure 2.6: Von Mises Stress due to drop impact [31]

#### 2.4 Review of other mechanical loading tests on PCBs

#### 2.4.1 Cyclic bending and vibration tests

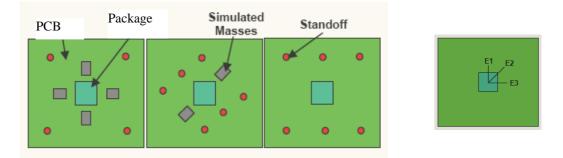

Bending and vibration tests were conducted by Hin et al. [51] to characterize the effect of board mounting locations as well as the mass effect on the PCB flexure. In the paper, three bend modes were studied, i.e. spherical bend, diagonal bend and planar bend as shown in Figure 2.8. The standoffs are spacers that give a specific clearance of the PCB to the fixture to allow board flexure. An example of the layout of the spherical bend test is shown in Figure 2.7. The rectangular rosette directions are shown next to the figure. For spherical bend, the bending effect due to the masses and mounting positions will induce equivalent strains for all three strain components E1, E2 and E3 due to symmetry. The strain component E2 is dominant in the diagonal bend test. However, components are seldom placed in the diagonal bend test configuration and thus the work discussed in this thesis will only focus on the spherical and planar layout for board level drop tests. In the planar bend tests, the dominant strain occurs on E1 direction while E3 strain is a result of Poisson's effect. Stresses are induced at the package edges.

Figure 2.7: PCB setup with simulated masses and mounting position (spherical bend)

Figure 2.8: Spherical Bend, Diagonal Bend and Planar Bend

A detailed vibration test was done on PCBs by Phil et al. [52]. They studied the mass effect at the center of PCB on the resonant frequency of the board by varying the weight at the PCB center. A comprehensive study of modal testing was also conducted by varying package sizes and orientations. Of the three variables tested, i.e. mass, orientation and package sizes, the mass on the board was determined to be the most dominant factor for resonant frequency. Larger masses yielded smaller board resonant frequencies. The experimental results also show good correlation to simulation results.

A 3-point cyclic bend test was conducted with maximum out-of-plane displacement of 1mm at the board center with a FBGA (Fine-pitch Ball Grid Array) component on the

other side of the board by Sidharth et al. [32]. The test was conducted for 3000 cycles. Failure was defined by the detection of an open circuit. There was no increase in the electrical resistance of the FBGA for the 1st 250 cycles and no failures were recorded after 3000 cycles although the resistance had increased. The board support span is only about 51mm and thus for a small board, the PCB will bend with a larger radius of curvature as compared to a longer board. Hence, the peeling stress at the solder joints is higher when the deflection is the same for a shorter support span.

#### 2.4.2 Ball shear tests

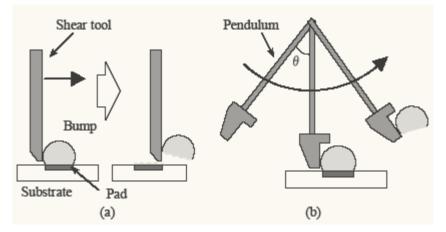

A miniature Charpy impact test was conducted by Date et al. [61] to evaluate the impact toughness of different types of lead-free and conventional solders. The Charpy test was compared to normal ball shear test. The Charpy test induces a high shear rate of 1 m/s while the conventional ball shear test gives a very slow shear rate of 0.2 mm/s. The schematics of the conventional shear test and the Charpy test are shown in Figure 2.9.

Figure 2.9: Schematics of (a) conventional shear test and (b) miniature Charpy test

The impact toughness, J, was calculated as the kinetic energy absorbed by the bump during fracture as follows:

$$J = \frac{1}{2}m_p \left( v_1^2 - v_2^2 \right)$$

where  $m_p$  is the weight of the pendulum, and  $v_1$  and  $v_2$  the velocities of the pendulum immediately before and after the impact, respectively. Four types of solders were tested in this paper; SnPb, SnAgCu, SnZn and SnZnBi. These solders were separated into two main groups - reflowed and aged. It was found that the solder joints had a greater tendency to break at the interface from the impact test than from the conventional shear test.

During the tests, SnPb solder showed lower shear strength and impact toughness (about 0.2-0.3 mJ) than the SnAgCu solders. The SnPb and the SnAgCu solders showed similar interfacial reactions, regardless of bond pads, but the latter was prone to fracture at the interface from the impact test because of higher solder bulk strength. The SnZn(Bi) solder on the Cu pad was degraded markedly with aging time, which is due to the rapid growth of  $\gamma$ -Cu<sub>5</sub>Zn<sub>8</sub> and substantial void formation at the interface. But the solder on the Au/Ni-P pad exhibited high shear strength and impact toughness even after aging, due to the formation of a Zn-rich phase. The effects of aging were also discussed in the paper. It showed that aging makes the solders brittle.

Ball shear and pull tests were conducted on SnAgCu lead free solder on Cu pads to investigate the effects of thermal aging by Chiu et al. [38]. In the shear tests, the shear strength dropped slightly after three days of thermal aging and no significant changes were found when the aging time increased beyond three days. Failure mode of the solder was dependent on the aging temperature for the shear tests. However, at higher temperatures, the pull strength did not reduce monotonically as the aging time increased. This may be attributed to the failure mode changing from pad-solder interfacial fracture to pad lift off.

Hanabe and Canumalla [62] performed shear tests on three packages (BGA1, BGA2 and LGA) mounted on a single board. BGA1 had 144 solder balls while BGA2 had 168 solder balls with a 4x4 solder ball array at the center of the component. The shear strength of BGA1 was relatively strain-rate insensitive and the failure was always at the buildup layer. The LGA packages showed the greatest strain-rate sensitivity because they had the lowest shear strength at low loading rates but the highest shear strength at high loading rates.

### **Chapter 3** Experimental Setup and Procedures

#### 3.1 Experimental setup

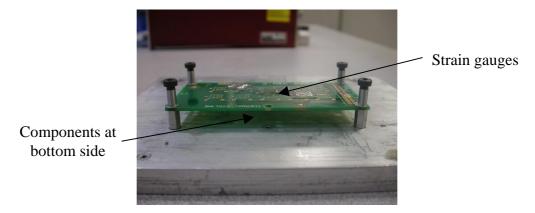

The experiment involves conducting board level drop tests using a drop tester. This involves mounting PCBs on a fixture. The fixture was screwed tightly to a drop table. Accelerometers were mounted on the fixture and the packages to monitor the acceleration levels during drop impact. Strain gauges were mounted on the bare side of the PCB without any components to monitor the in-plane strains of the board. The electrical resistances of the components on the boards were monitored in-situ during drop impact. A power supply of low voltage provides a potential difference across the components and any fluctuations in the potential difference during drop impact can be monitored through an oscilloscope. The fluctuations of the potential difference can be related to changes in electrical resistances of the drop table to monitor the board flexure during drop impact.

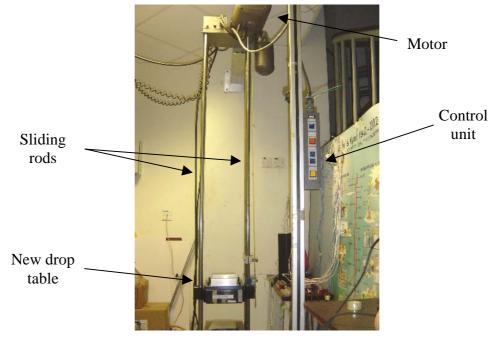

For this project, a Lansmont drop tester capable of dropping test specimens up to a maximum drop height of 1.5m is used. The drop tester consists of a motor for raising the drop table, a 15kg drop table with pneumatic brakes, a control panel for raising and lowering the drop table, two guiding rods for drop table to fall along and a base for mounting appropriate strike surfaces. A picture of the drop tester is shown in Figure 3.1.

The drop table is mounted on the drop tower by means of side jigs that slide along the guiding rods. The drop table is held tightly to the side jigs by means of cap screws. When the drop table drops is subjected to high-G level drops repetitively, the tightening screws tend to break off via shearing due to inertia of the side jigs falling downwards while the drop table rebounds upon impact. This problem occurs quite frequently and screw threads can deteriorate over time.

A new drop table is designed and fabricated to eliminate the problem of broken screws. The new drop table incorporates two side jigs together with the drop table into one piece. The main advantage is that there is no need to use screws to tighten the side jigs to the main block. In addition, it is lighter than the old drop table and thus prevents heavy impact damage to the drop tower apparatus. The same hole arrangement is used for fixing fixtures on top and has two side copper bushings for smooth free-falling motion along the sliding rods when the drop table is released.

Figure 3.1: Lansmont drop tester

The weight of the new drop weight is 12.5kg and is capable of reaching a maximum G level of 4500G using a single layer of felt as the strike surface. Figure 3.2 shows a picture of the new drop table aligned to the sliding rods of the drop tower. A technical drawing of the drop table is shown in Appendix A.1.

Hole to hole: 38.1mm Hole thread: 10mm

Figure 3.2: New Drop Table

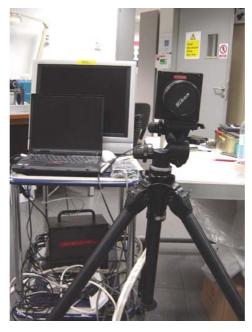

The high-speed camera setup is a novel method of monitoring velocity changes in the test specimens upon impact. An APX high-speed camera capable of capturing up to 100,000 frames per second is used. For this project, a frame rate of 6000 frames per second is used. Higher frame rates will require much stronger lighting for the high-speed images to be clear and resolution will also be smaller. Figure 3.3 shows a picture of the high-speed camera apparatus.

Figure 3.3: APX High-Speed Camera Apparatus

The camera is connected to a control unit and a controller. The controller is able to control the frame rate, resolution, type of triggering and other functions. The control unit is able to connect an external trigger switch if the activating is to be done from some distance away from the controller. The control unit also links to a laptop so that high-speed images can be instantly downloaded to the laptop for viewing and storage. Suitable lenses are used together with the camera for best effects. It is recommended that a lens with a good depth of view be used with the high-speed camera so that more details can be captured on the test specimens.

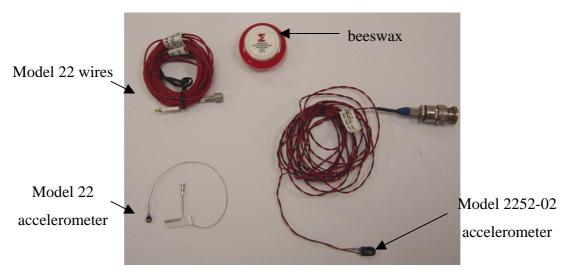

During drop impact of microelectronic packaging, drop responses and failure data are acquired by means of certain measuring devices. This data is important for comparing drop tests and evaluating the drop reliability of these components. Measuring devices include accelerometers, strain gauges and resistance checking through multimeters and oscilloscopes. Accelerometers are mounted either on the fixture itself or the package. As accelerometers are extremely susceptible to mechanical damage or mishandling, extra care is required to mount them properly to the places of interest. Figure 3.4 shows a picture of the accelerometers used in this experiment.

Figure 3.4: Endevco Accelerometers with Petrol Wax

The two types of accelerometers used are the Endevco Model 22 and Model 2252-02. Model 22 accelerometers and small and lightweight and thus useful for mounting on packages to monitor the output acceleration. Model 2252-02 accelerometers are bigger in size and more robust and are thus useful in monitoring the input acceleration of the drop table. Usually, the acceleration value measured at the fixture is similar to the acceleration level measured on the drop table if the fixture is secured tightly to the drop table.

Coaxial strain gauge rosettes used in experiment testing are of 1mm or 2mm gauge length. The small size is required because the PCBs tested usually have many components mounted on them. Smaller strain gauges are also more lightweight and do not affect the results of drop impact testing of PCBs. The rosettes are connected to strain bridges powered by strain meters and signals are registered on the oscilloscope. Figure 3.5 shows a picture of the strain gauges used.

Figure 3.5: Coaxial strain gauge (1mm gauge length)

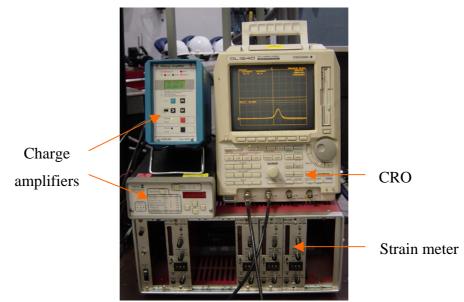

The strain gauges are connected to strain bridges and bridges connected to the strain meters. The strain meters are linked back to a cathode-ray oscilloscope (CRO) for capturing signals. The settings of the strain meters are to be calibrated with the CRO before testing. Similarly, the accelerometers are connected to a charge amplifier and then connected to the CRO. Figure 3.6 shows a picture of a strain meter, charge amplifier and CRO. The signals from the CRO could be extracted out in tabular form for analysis.

Figure 3.6: Charge Amplifiers, Strain Meters and a CRO

# 3.2 Test specimens

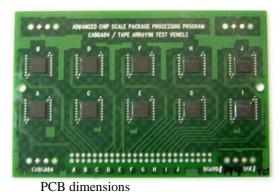

Several types of packages are being tested. They include mainly TFBGA/VFBGA and CABGA (with and without underfill) packages. Figure 3.7 shows the PCBs with the packages mounted on them. The TFBGA board has dimensions of 100x48x1.6mm, while the CABGA board size has dimensions of 115x77x1.6 mm. These two types of PCBs have different dimensions because of different sources from which these

packages are manufactured. Each PCB comes in two configurations; they either house 10 components or 1 component only.

Both types of packages are tested using the same testing procedures. Strain readings are taken usually at the center of the PCB where maximum deflection occurs in a typical 4-screw fixation. Their resistances at the interconnections are also monitored during drop impact through the CRO and their drop reliability evaluated. TFBGA/VFBGA packages do not have underfill material in them, and are separated by leaded and lead-free solders. CABGA packages have either no-underfill or with underfill material in them. Different types of underfill materials have been tested till the packages failed. Output acceleration is also monitored at the packages to correlate with simulation findings.

<u>PCB dimensions</u> length: 100mm, width: 48mm, thickness: 1.66mm

thickness: 1.6mm Figure 3.7: CABGA (left) and TFBGA (right) packages on PCBs

# 3.3 Basic mechanics of drop test

length: 114.3mm, width: 76.2mm,

Some background experiment is conducted to better understand the drop responses acquired during drop tests. First, it is important to achieve uniform G level throughout the whole drop table and fixture upon drop impact. This is to ensure the whole carriage experiences the same shock level so that consistency in the board level drop test can be achieved. The strike surface consists of a circular toughened steel plate with a round tip at the center as shown in Figure 3.8. The steel plate should be toughened as multiple drops might cause the steel plate to crack at the center and propagate outwards. The reason for the curved surface is to ensure a single impact between the drop table and the strike surface. If the strike surface is flat, it is difficult to ensure perfect contact between the two surfaces.

Figure 3.8: Curved strike surface (toughened steel)

Achieving appropriate G levels and impact time duration is another important element of control. Varying the height as well as the type of strike surface will vary the G level. From kinematics, theoretical impact velocity during free fall just before impact,  $V_b$ , can be related to drop height, H, by

$$V_b = \sqrt{2gH} \tag{3.1}$$

where *g* is free fall acceleration (9.81m/s<sup>2</sup>). Assuming the input will yield a half-sine acceleration curve (from JEDEC standard [7]) with the following equation:

$$G(t) = G_m \sin \frac{\pi t}{T}$$

(3.2)

where G(t) is acceleration at time *t*,  $G_m$  is peak acceleration, and *T* is impact duration. When the potential energy is fully converted into kinetic energy, the peak acceleration,  $G_m$ , for perfectly plastic case (no rebound) may be shown to be as

$$G_m = \frac{\pi\sqrt{gH}}{T\sqrt{2}} \tag{3.3}$$

For a perfectly elastic case (full rebound),  $G_m$  is 2 times larger than values given in the above equation.

Actual products experiencing accidental drops result in high acceleration forces induced in the product because the impact surface is usually rigid (ground). At fixed drop height, according to the law of conservation momentum and impulse, the product  $G_mT$  is a constant

$$G_{m1}T_1 = G_{m2}T_2 (3.4)$$

where  $G_{ml}T_l$  denotes a set of prescribed drop impact conditions of peak G and time duration and  $G_{m2}T_2$  denotes another set of impact conditions at the same drop height. Usually there is a need to fine-tune the felt thickness, drop height, and impact surface conditions (including type of material, shape and flatness of surface), so that desired acceleration profile ( $G_m$  and T values) can be achieved. Generally, thicker felt generates lower peak acceleration and longer impact duration. Other rubber materials have been tested but they cannot achieve a nice sinusoidal acceleration profile as felt material.

According to impulse and momentum theory, the velocity after impact,  $V_a$ , is in the range between 0 (zero rebound) and  $-V_b$  (full rebound). Assuming  $V_a$  is some fraction of  $V_b$ ,  $V_a = cV_b$ , then according to impulse-momentum theorem,

$$-mcV_{b} - mV_{b} = -\int_{0}^{T} mG(t)dt$$

$$V_{b} = \frac{1}{1+c}\int_{0}^{T} G(t)dt$$

(3.5)

(3.6)

where *c* is the coefficient of restitution, and its value is between 0 (perfectly plastic impact) and 1 (perfectly elastic impact), G(t) is the acceleration at time *t* during impact, *T* is the impact duration, and *m* is mass. By substituting Eq.(3.1) into Eq.(3.6),

$$A = \int_{0}^{T} G(t)dt = (1+c)\sqrt{2gH}$$

(3.7)

where A is the area under G(t).

## 3.4 Characterization of the drop tester

#### 3.4.1 Drop height characterization

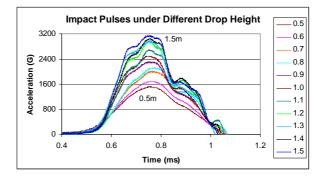

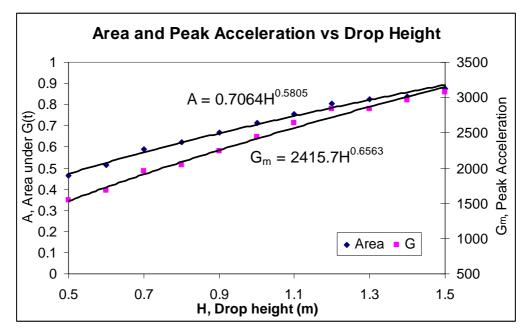

Figure 3.9 shows the impact pulses under different drop height from 0.5m to 1.5m. Larger sudden change of acceleration occurs at higher drop heights. The time duration varies very little compared to the change in G levels as the felt layer is thin and unable to cushion much of the drop impact.

Figure 3.9: Impact pulses under different drop height

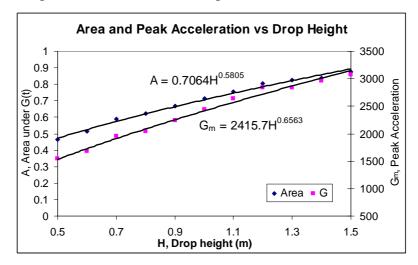

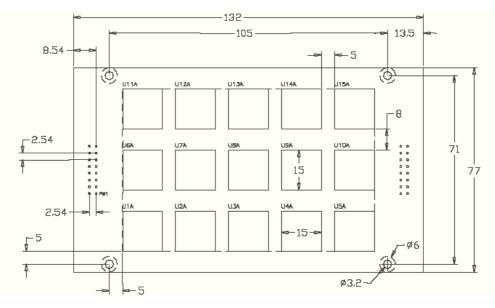

The relationship between drop height and A, which is actually the change in velocity during impact, can be described by a power law equation (see Figure 3.10). Equation (3.7) shows that A varies with  $H^{0.5}$ . Actual curve in Figure 3.10 has slightly higher coefficient of  $H^{0.58}$ , and the difference is partly due to the friction of the guiding rods that partially slows down the falling of the drop table. The peak acceleration,  $G_m$ , has a similar relationship with drop height as the two curves in Figure 3.10 are almost in parallel. This implies that the fluctuation in pulse duration is small in this case.

Figure 3.10: Comparing A and  $G_m$  from plot of A against drop height, H

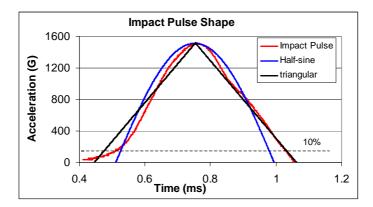

The drop height and strike surface are usually adjusted to achieve a specific G level and pulse duration. Figure 3.11 shows that the actual impact pulse measured can be approximated as a half-sine curve or a triangular curve. By assuming constant area under the curves and maintaining same peak acceleration, the area under G(t) is

$$A = \frac{2}{\pi} G_m T = 0.6366 G_m T \tag{3.8}$$

For a triangular impact pulse, the area is simply

$$A = 0.5 G_m T \tag{3.9}$$

*T* is the impact pulse duration. Actual impact pulse measured by the accelerometer is usually between a half-sine pulse and a triangular pulse (see Figure 3.11). The pulse durations of half-sine pulse and triangular pulse are computed using eqns (3.8) and (3.9), assuming constant *A* and  $G_m$ . For simplicity, either half-sine pulse or triangular pulse can be applied for quick approximation of actual impact pulse.

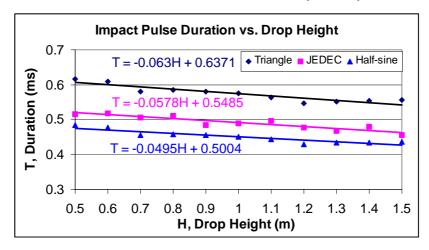

Figure 3.11: Approximation of impact pulse shapes

The relationship between pulse duration and drop height is linear and the slope of the line is very small (see Figure 3.12). Pulse durations for different drop heights are directly extracted from the measured impact pulses (see Figure 3.12), according to pulse duration definition of JEDEC standards, i.e. the interval between instance when the acceleration first reaches 10% of the specified peak level and the instant when the acceleration first returns to 10% of the peak level. It is less than the duration of a triangle pulse and more than the duration of a half-sine curve, according to eqns (3.8) and (3.9).

Comparing Figures 3.10 and 3.12, the sensitivity of peak acceleration is much higher than pulse duration to variation in drop height. This implies that if large variation in pulse duration is required (e.g., 0.3ms to 0.5ms), adjustment in drop height alone is insufficient. Instead, different felt material or extra felt layers may be needed.

Figure 3.12: Impact pulse duration vs. drop height

In actual experiment, there is some rebound of the drop table after impact. How much the drop table rebound is governed by the coefficient of restitution, c. The coefficient of restitution can be derived from Figure 3.10 (A vs. H), according to Eqns (3.2) and (3.5), as

$$c = \frac{A}{V_b} - 1 = \frac{V_a + V_b}{V_b} - 1 = \frac{V_a}{V_b}$$

(3.10)

and it is equal to 0.58 for this particular drop test configuration if theoretical impact velocity of 5.425m/s is achieved from drop height of 1.5m. The post impact velocity is measured through a high-speed camera apparatus. Due to friction effect along the guiding rods, the high-speed camera measures the actual impact velocity to be 4.78m/s. Thus, the actual value of *c* is found to be 0.79.

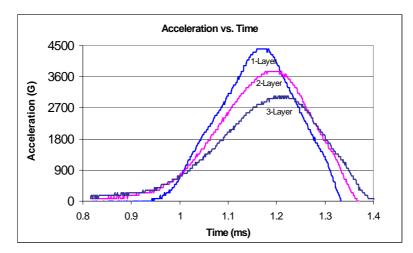

## 3.4.2 Strike surface characterization

Besides drop height, felt material, and strike surface, thickness or number of felt layer can also be used to adjust and achieve the required G level and pulse duration. Figure 3.13 shows the impact pulses using one, two, and three layers of felt material. The areas under G(t), peak accelerations, pulse durations, and coefficients of restitution for different number of felt layers (see Table 3.1) can be extracted. In general, with increasing number of felt layer, the peak acceleration is reduced and the pulse duration is longer (flatter impact pulse). In addition, the area under G(t) graph or change in velocity during impact, A, and coefficient of restitution, c, are lower with increasing number of felt layers. Pulse duration is more sensitive to variation in number of felt layers than to drop height (see Figure 3.12). Therefore, a combination of number of felt layer and drop height can help to vary both peak acceleration and pulse duration, and obtain a specific impact pulse. However, if a larger time duration (>1ms) is required, it may be necessary to change the felt material.

Figure 3.13: Effect of number of felt layers on impact pulse

| Number of Layer | A (m/s) | $G_m(\mathbf{G})$ | T (ms) | С     |

|-----------------|---------|-------------------|--------|-------|

| 1               | 8.524   | 4400              | 0.334  | 0.571 |

| 2               | 8.243   | 3760              | 0.393  | 0.519 |

| 3               | 7.852   | 3040              | 0.456  | 0.447 |

Table 3.1: Effects of number of felt layer

# 3.4.3 Drop conditions for 1500G peak level

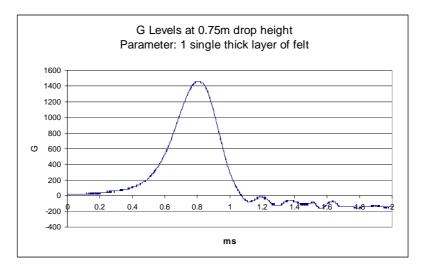

According to JEDEC standard in board level drop test [7], JEDEC requires an input of 1500G with an impact duration of 0.5 ms with a half sine pulse. Calibration of the drop tower was done using different layers of felt material at the strike surface to vary the time duration. Varying the drop height could easily vary the G levels. From Figure 3.14, a single layer of thick felt of thickness 10mm is used at the strike surface. At a drop height of 0.75m, the JEDEC requirement can be approximately achieved. Adjusting the time duration could be difficult as varying the thickness of felt material may not vary the time duration accurately as felt material tends to be flattened after many cycles.

Figure 3.14: JEDEC standard of 1500G using Lansmont drop tower

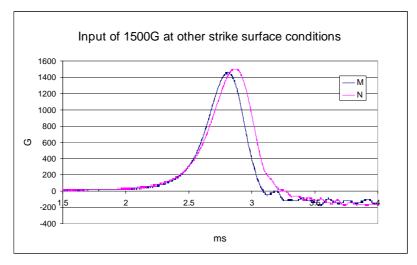

In addition, other conditions were also tested maintaining the same  $G_m$ . From Figure 3.15, thin layers of felt are placed on top of the thick layer of felt to increase the thickness. Condition M denotes the condition where a thin layer of felt is placed over the original thick layer of felt and the drop table dropped from a height of 0.9m. Condition N denotes the condition where two thin layers are used over the thick layer of felt and drop table dropped from a height of 1.3m However, the impact duration did not vary much as compared to the change in drop height to maintain the same G level using different numbers of felt layers. In actual board level test, this JEDEC condition might not be appropriate to yield failures within a reasonable number of drops for certain packages and thus higher G levels and shorter impact durations might be necessary for the tests.

Figure 3.15: Plot of G level against time for peak acceleration of 1500G for different number of layers of felt material

Once the tester is characterized and the relationships among drop height, area under acceleration curve, peak acceleration, and pulse duration are known, the drop height required can be estimated easily for a specific set of G levels and impact durations. Therefore, avoiding the "trial and error" approach can shorten the subsequent test setup time.

#### 3.4.4 Repeatability of drop test

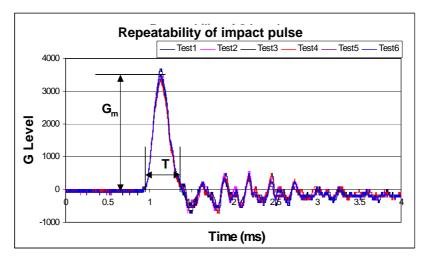

Six drops were conducted to ensure the repeatability of test results. Impact pulses as well as strains along the PCB length and width directions are measured. In this experiment, drop height is 1.5m with one layer of felt material and four corner PCB mounting screws. Figure 3.16 shows the six shock impact pulses. The tolerances of peak acceleration,  $G_m$ , and pulse duration, T, are within ±5% and ±1%, respectively.

Figure 3.16: Repeatability of shock pulses at 1.5m drop height

## **3.5** Overview of drop test plan

### **3.5.1** Test plan for TFBGA components