# A HIGH-FREQUENCY QUAD-MODULUS PRESCALER FOR FRACTIONAL-N FREQUENCY SYNTHESIZER

LAU WEE YEE WENDY (B. Eng. (Hons.), NTU)

A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2009

## ACKNOWLEDGEMENTS

Many people have played different roles in encouraging and inspiring me throughout my course of graduate study at National University of Singapore (NUS). The accomplishment of this thesis would not have been possible without the support and guidance from all of them.

I would like to express my utmost gratitude and appreciation towards my supervisor, Assistant Professor Yao Libin from Electrical & Computer Engineering (ECE) Department of NUS, for his invaluable guidance and encouragements during my course of study at NUS. This project would not have been completed without his immense support, advice and guidance. I would also like to thank the ECE Department for granting the commencement of this project. I am grateful towards the lecturers from ECE Department for their remarkable teachings, and my course-mates for their altruistic assistance.

I would like to express my heartfelt thanks to my former superiors, Mr. Fumio Muto and Mr. Ivan Foo, from Cyrips Pte. Ltd. for supporting the project and providing a conducive working environment which encourages research and development works. I am grateful towards Dr. Zheng Jia Jun and Mr. Cheong Ban Chuan for sharing their technical experiences, and providing advices and guidance. I wish to extend my sincere thanks to my other colleagues, Ms. Qi Xiao Fei, Mr. Zhang Liang and Ms. Chua Sue Suen, for their collaborations and understandings. All the skills and experiences shared by my experienced colleagues will definitely be beneficial in my future endeavours. I also wish to thank Associate Professor Siek Liter and Associate Professor Goh Wang Ling from School of Electrical and Electronic Engineering of Nanyang Technological University for encouraging me to further my study after my Bachelor's Degree graduation.

Last but not least, I would like to express my special thanks to my family members and friends for their supports, encouragement and reassurance.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS i |                                                     |  |

|--------------------|-----------------------------------------------------|--|

| SUMMARYvii         |                                                     |  |

| LIST OF FIG        | URES viii                                           |  |

| LIST OF TAE        | BLES xxi                                            |  |

| CHAPTER 1          | INTRODUCTION1                                       |  |

| 1.1                | Motivation1                                         |  |

| 1.2                | Thesis Organization                                 |  |

| CHAPTER 2          | FREQUENCY SYNTHESIZER4                              |  |

| 2.1                | Phase-Locked Loop (PLL)                             |  |

|                    | 2.1.1 Frequency Multiplication                      |  |

| 2.2                | Frequency Synthesizer Architectures9                |  |

|                    | 2.2.1 Direct Digital Frequency Synthesizer          |  |

|                    | 2.2.2 Integer-N Frequency Synthesizer 10            |  |

|                    | 2.2.3 Fractional-N Frequency Synthesizer            |  |

|                    | 2.2.4 Delay-Locked Loop (DLL) Frequency Synthesizer |  |

| CHAPTER 3          | PRESCALER17                                         |  |

| 3.1                | Divide-by-2 Topologies17                            |  |

| 3.2                | Synchronous and Asynchronous Dividers               |  |

| 3.3                | Dual-modulus Prescaler                              |  |

| 3.4                | Multi-modulus Prescaler                             |  |

|                    | 3.4.1 Ring Prescaler                                |  |

|                    | 3.4.2 Phase-switching Prescaler                     |  |

| CHAPTER 4          | CIRCUIT DESIGN AND IMPLEMENTATION                   |  |

| 4.1       | Fraction | al-N Frequency Synthesizer Circuit Overview, Architecture, |

|-----------|----------|------------------------------------------------------------|

| and       | Layout   |                                                            |

|           | 4.1.1    | Counters                                                   |

|           | 4.1.2    | MASH                                                       |

|           | 4.1.3    | Interface                                                  |

|           | 4.1.4    | Mode Register                                              |

|           | 4.1.5    | MUX_Output                                                 |

|           | 4.1.6    | PFD and Charge Pump                                        |

|           | 4.1.7    | Loop Filter and VCO                                        |

|           | 4.1.8    | Fast-lock Control Switch                                   |

|           | 4.1.9    | Quad-modulus Prescaler                                     |

| 4.2       | Quad-M   | lodulus Prescaler Circuit Design51                         |

| 4.3       | Frequen  | cy Synthesizer and Prescaler Layout61                      |

| 4.4       | Design   | Specifications                                             |

| 4.5       | PC Prog  | gram for PLL Frequency Synthesizer Setting                 |

|           | 4.5.1    | User Interface                                             |

|           | 4.5.2    | Hardware Interface                                         |

| CHAPTER 5 | SIMUL    | ATION AND MEASUREMENT RESULTS                              |

| 5.1       | Testben  | ches                                                       |

|           | 5.1.1    | Counters                                                   |

|           | 5.1.2    | MASH                                                       |

|           | 5.1.3    | Interface                                                  |

|           | 5.1.4    | Mode Register                                              |

|           | 5.1.5    | Fastlock                                                   |

|           | 5.1.6    | Prescaler                                                  |

| 5.2       | Simulat | ion Results                                      |

|-----------|---------|--------------------------------------------------|

|           | 5.2.1   | Prescaler                                        |

|           | 5.2.2   | Frequency Synthesizer Current Consumption        |

|           | 5.2.3   | PLL Settings                                     |

|           | 5.2.4   | Prescaler Controller                             |

|           | 5.2.5   | N-Counter and MASH96                             |

|           | 5.2.6   | Modulus Control 100                              |

|           | 5.2.7   | PFD and Charge Pump101                           |

|           | 5.2.8   | Loop Filter 104                                  |

| 5.3       | Measure | ement Results 109                                |

|           | 5.3.1   | Test Plan 109                                    |

|           | 5.3.2   | Operating Frequency Range 110                    |

|           | 5.3.4   | Reference Spurs111                               |

|           | 5.3.5   | Fractional Spurs113                              |

|           | 5.3.6   | Integer-N Boundary Spur115                       |

|           | 5.3.7   | Loop Filter                                      |

|           | 5.3.8   | Phase Noise 120                                  |

|           | 5.3.9   | Crystal Oscillating Frequency 120                |

|           | 5.3.10  | Effect of Loop Bandwidth on Settling Time 121    |

|           | 5.3.11  | Effect of Fastlock Function on Settling Time 121 |

|           | 5.3.12  | PC Program for PLL Setting (User Interface) 122  |

| CHAPTER 6 | CONCI   | LUSION                                           |

| BIBLIOGRA | РНҮ     |                                                  |

| APPENDICE | S       |                                                  |

| Appen     | ndix A  | Reference Spur Plots                             |

| Appendix B | Fractional Spur Plots139    |

|------------|-----------------------------|

| Appendix C | Integer-N Boundary Spurs150 |

| Appendix D | Phase Noise160              |

# SUMMARY

A fully integrated fractional-N frequency synthesizer which utilizes high-frequency, fast-switching quad-modulus prescaler is proposed and demonstrated in this thesis. In this proposed design, a quad-modulus prescaler with a divide-by-4/5/6 core is implemented to minimize dynamic power consumption, avoid glitches and jitter due to mismatch in input signals' phases whilst maintaining high-frequency, fast-switching capability. Besides, fast-lock function has been instigated in the synthesizer design to reduce the frequency-locking time, and Multi-stAge noise SHaping (MASH) technique has been utilized to reduce the overall phase noise and spurs. The proposed frequency synthesizer offers technological robustness, fast locking capability, versatility, low noise contribution, superior integration and deployment capacity, and multi-modulus flexibility.

The proposed design has been studied, simulated at both circuit and system levels and implemented to examine its performances. The actual circuit performances are verified via measurements conducted after fabrication and packaging.

# **LIST OF FIGURES**

| Figure 2.1:  | Role of frequency synthesizer in common transceiver                              | 4  |

|--------------|----------------------------------------------------------------------------------|----|

| Figure 2.2:  | Phase-locked loop                                                                | 5  |

| Figure 2.3:  | Characteristic of phase detector                                                 | 6  |

| Figure 2.4:  | Signals in a PLL                                                                 | 6  |

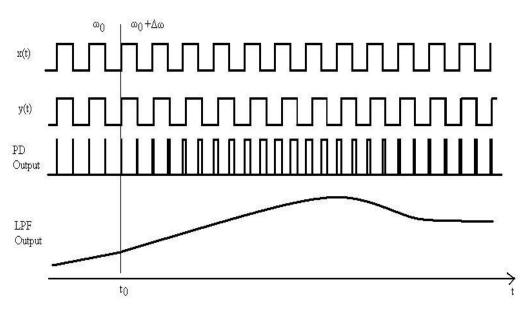

| Figure 2.5:  | Response of PLL to a small increase in frequency                                 | 7  |

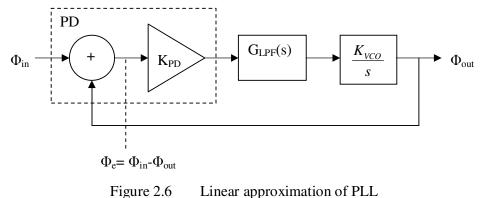

| Figure 2.6:  | Linear approximation of PLL                                                      | 8  |

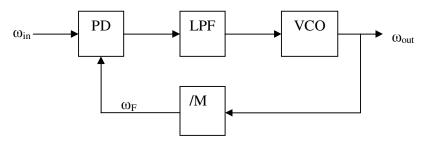

| Figure 2.7:  | Frequency multiplication of PLL                                                  | 8  |

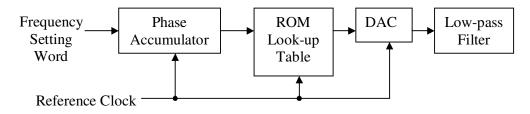

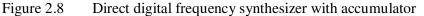

| Figure 2.8:  | Direct digital frequency synthesizer with accumulator                            | 9  |

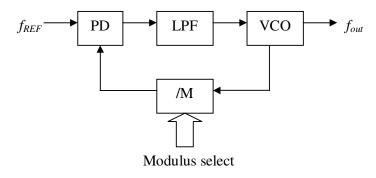

| Figure 2.9:  | An integer-N frequency synthesizer                                               | 10 |

| Figure 2.10: | Frequency synthesizer with single modulus prescaler                              | 11 |

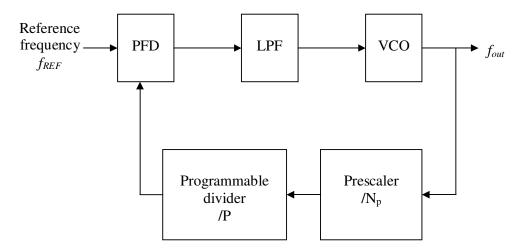

| Figure 2.11: | High-frequency programmable divider                                              | 12 |

| Figure 2.12: | Fractional-N synthesizer with: (a) pulse remover, (b) dual-<br>modulus prescaler | 13 |

| Figure 2.13: | Noise shaping using $\sum -\Delta$ modulator                                     | 14 |

| Figure 2.14: | First-order $\Sigma - \Delta$ modulator                                          | 15 |

| Figure 2.15: | Delay-locked loop frequency synthesizer                                          | 16 |

| Figure 3.1:  | Divide-by-2 circuit                                                              | 18 |

| Figure 3.2:  | Synchronous divider                                                              | 21 |

| Figure 3.3:  | Asynchronous divider                                                             | 21 |

| Figure 3.4:  | Synchronous divide-by-4/5 circuit                                                | 22 |

| Figure 3.5:  | A cascaded divide-by-2/3 programmable prescaler                                  | 23 |

| Figure 3.6:  | A divide-by-2/3 core circuit                                                     | 24 |

| Figure 3.7:  | A divide-by-2/3 using phase-switching                                            | 24 |

| Figure 4.1:  | Fractional-N frequency synthesizer block diagram | 28 |

|--------------|--------------------------------------------------|----|

| Figure 4.2:  | R_Counter block diagram                          | 31 |

| Figure 4.3:  | R_Counter_Bit schematic                          | 32 |

| Figure 4.4:  | N_Counter block diagram                          | 33 |

| Figure 4.5:  | Counter_Bit schematic                            | 34 |

| Figure 4.6:  | MASH block diagram                               | 35 |

| Figure 4.7:  | MASH_4order schematic                            | 35 |

| Figure 4.8:  | Interface block diagram                          | 37 |

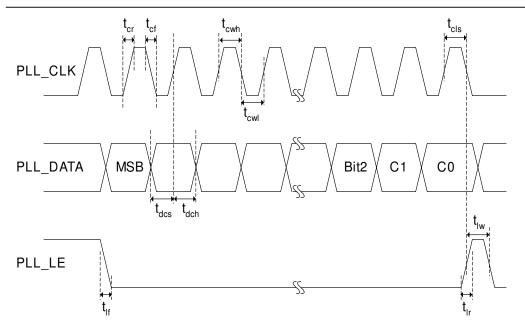

| Figure 4.9:  | PLL synthesizer serial interface timing diagram  | 38 |

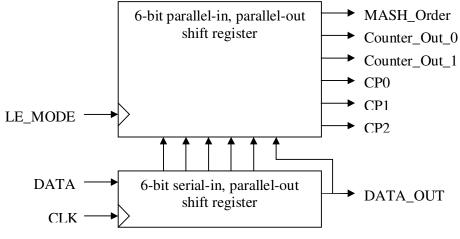

| Figure 4.10: | Mode Register block diagram                      | 38 |

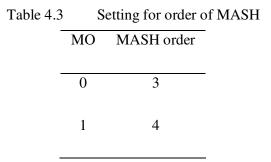

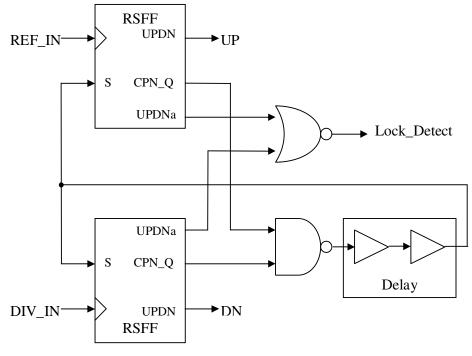

| Figure 4.11: | PFD state diagram                                | 41 |

| Figure 4.12: | PFD block diagram                                | 41 |

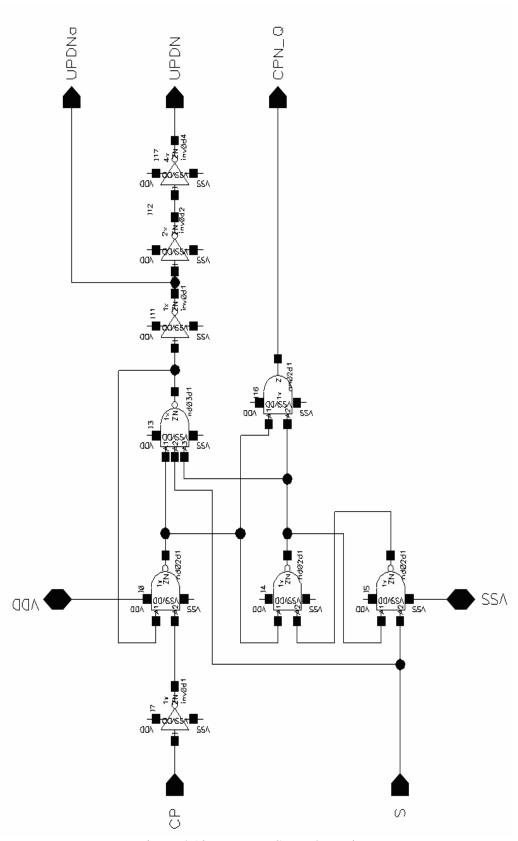

| Figure 4.13: | PFD_RSFF schematic                               | 42 |

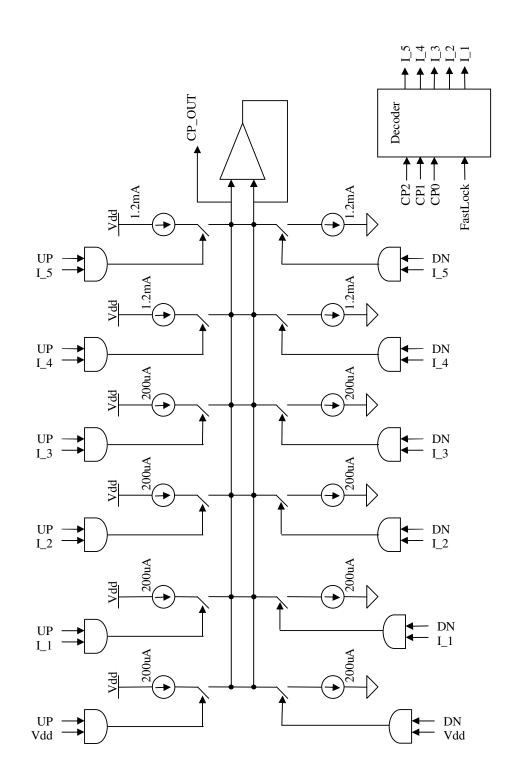

| Figure 4.14: | CP block diagram                                 | 43 |

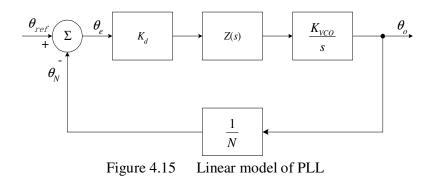

| Figure 4.15: | Linear model of PLL                              | 44 |

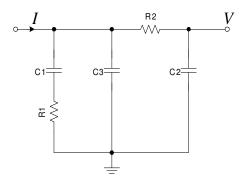

| Figure 4.16: | Schematic of third order loop filter             | 45 |

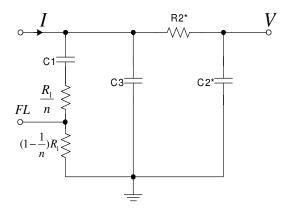

| Figure 4.17: | Schematic of loop filter with Fast-lock function | 48 |

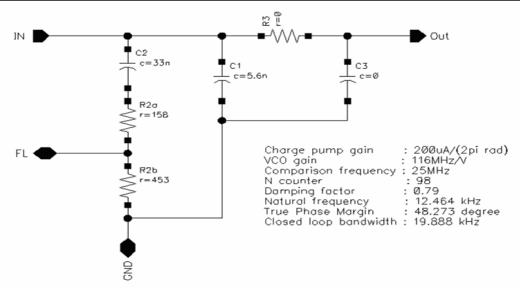

| Figure 4.18: | LP_Filter schematic                              | 49 |

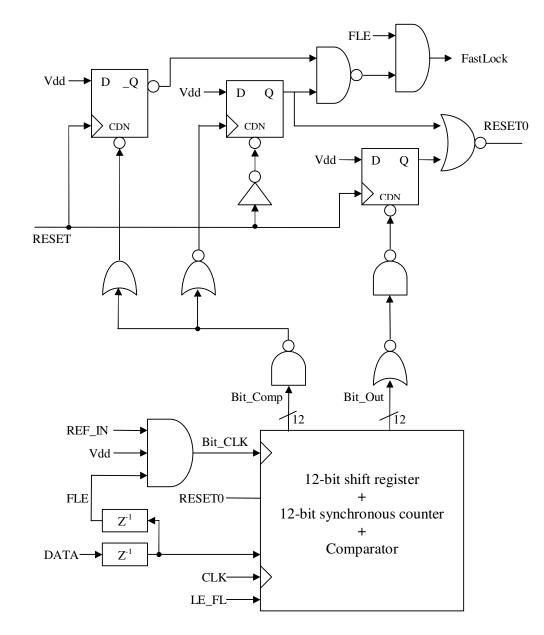

| Figure 4.19: | Fastlock_Counter block diagram                   | 50 |

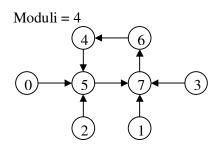

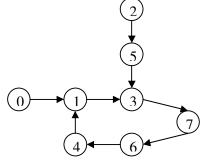

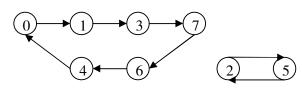

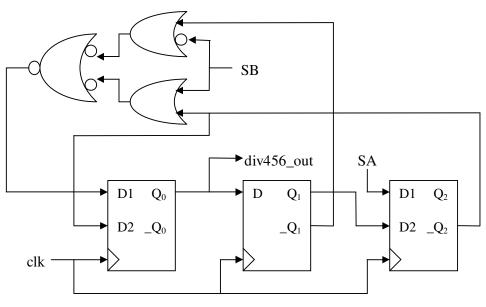

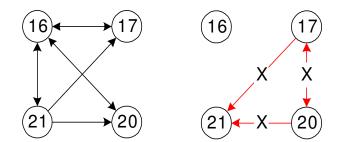

| Figure 4.20: | State diagrams prescaler core                    | 52 |

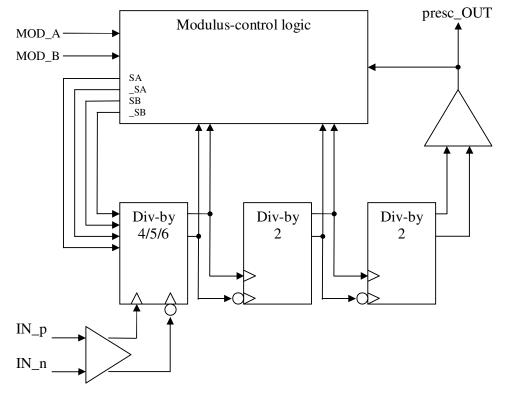

| Figure 4.21: | Div16172021_top diagram                          | 53 |

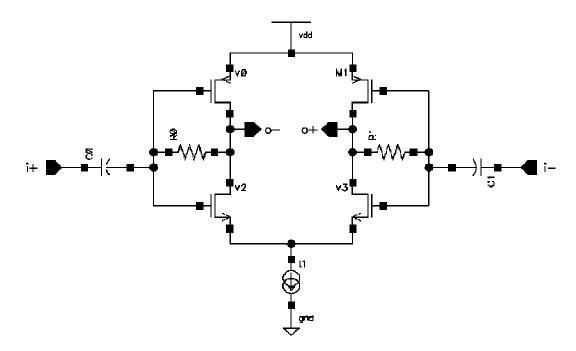

| Figure 4.22: | Input buffer schematic                           | 54 |

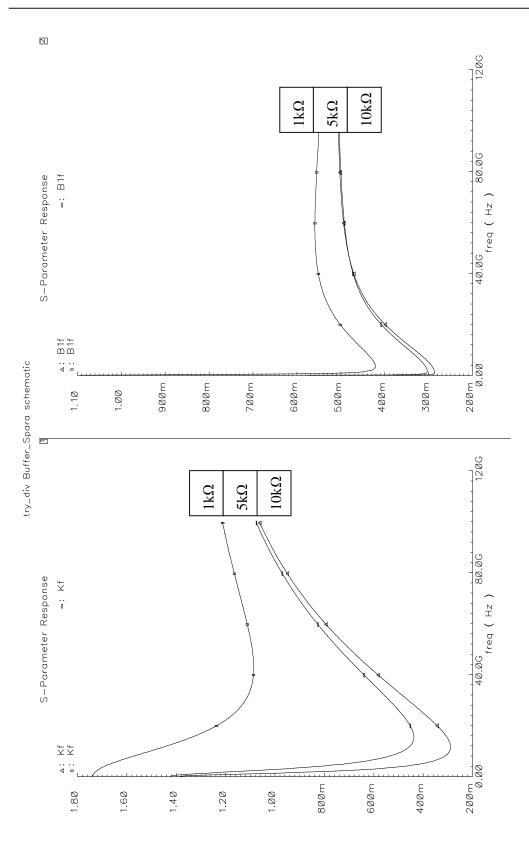

| Figure 4.23: | Effect of feedback resistor on buffer stability  | 55 |

| Figure 4.24: | Div456_top block diagram                         | 56 |

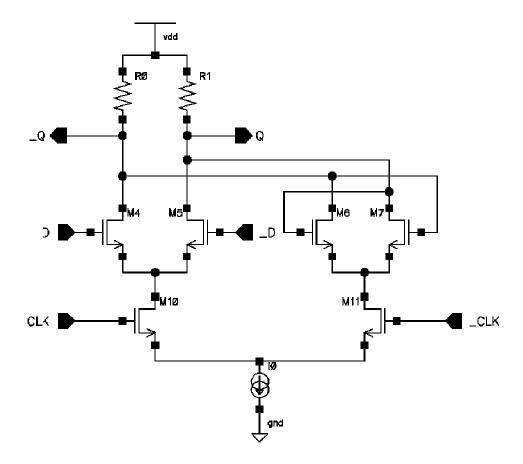

| Figure 4.25: | CML latch schematic                              | 57 |

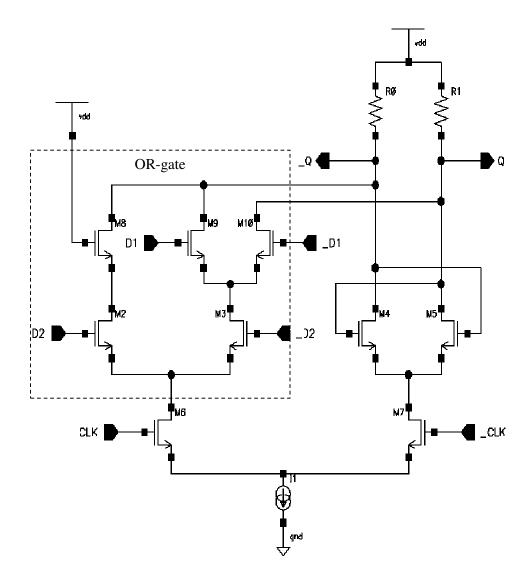

| Figure 4.26: | OR-embedded CML latch schematic                             | 59 |

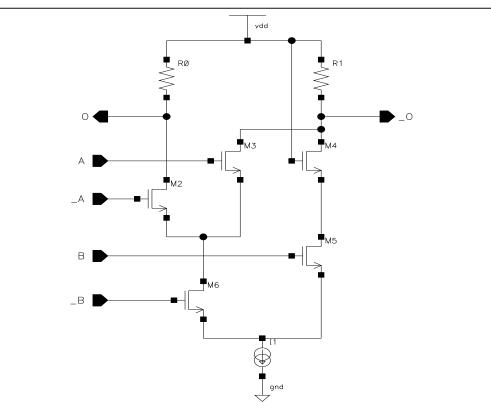

|--------------|-------------------------------------------------------------|----|

| Figure 4.27: | OR gate schematic                                           | 60 |

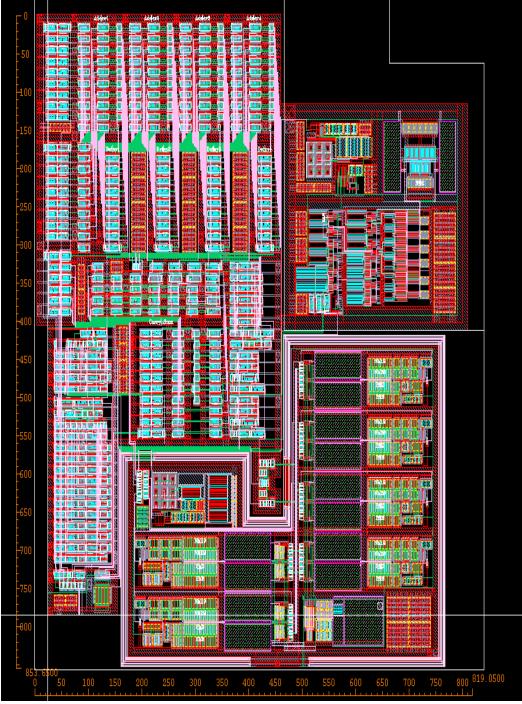

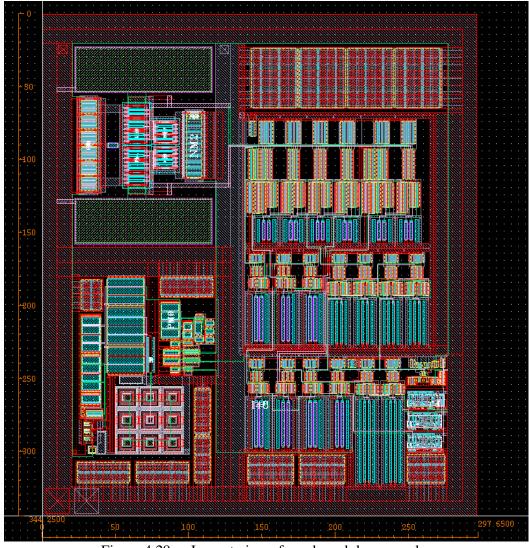

| Figure 4.28: | Layout view of fractional-N frequency synthesizer           | 61 |

| Figure 4.29: | Layout view of quad-modulus prescaler                       | 62 |

| Figure 4.30: | Main user interface for synthesizer setting                 | 65 |

| Figure 4.31: | Second user interface for synthesizer setting               | 66 |

| Figure 4.32: | Third user interface displaying "Help" information          | 66 |

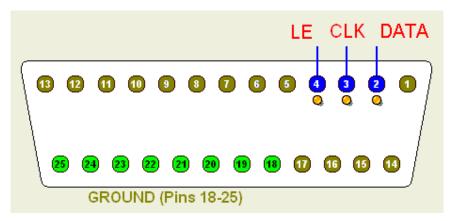

| Figure 4.33: | PLL setting through parallel port                           | 67 |

| Figure 5.1:  | PLL locking simulation testbench                            | 68 |

| Figure 5.2:  | Top level simulation testbench                              | 69 |

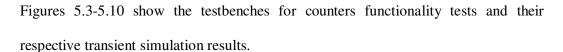

| Figure 5.3:  | Testbench for AB_Counter functionality test                 | 70 |

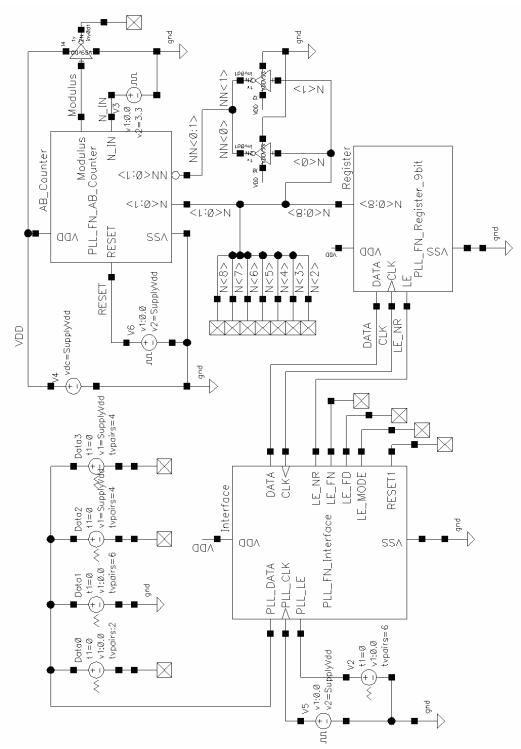

| Figure 5.4:  | Transient simulation results of AB_Counter                  | 71 |

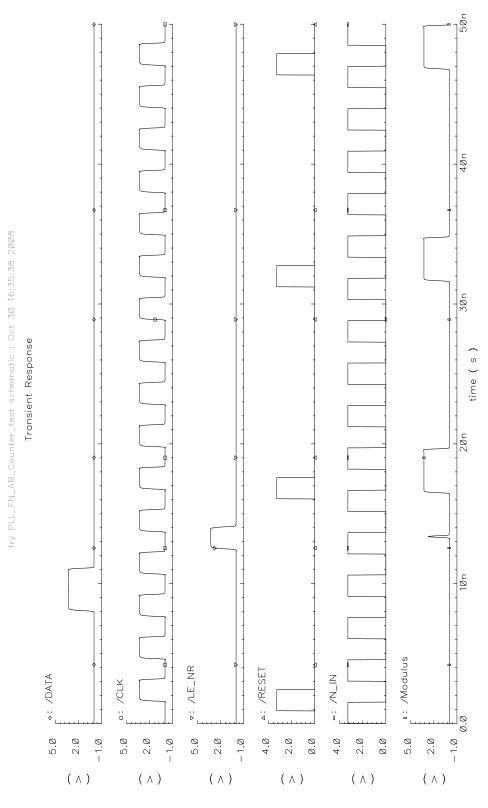

| Figure 5.5:  | Testbench for C_Counter functionality test                  | 72 |

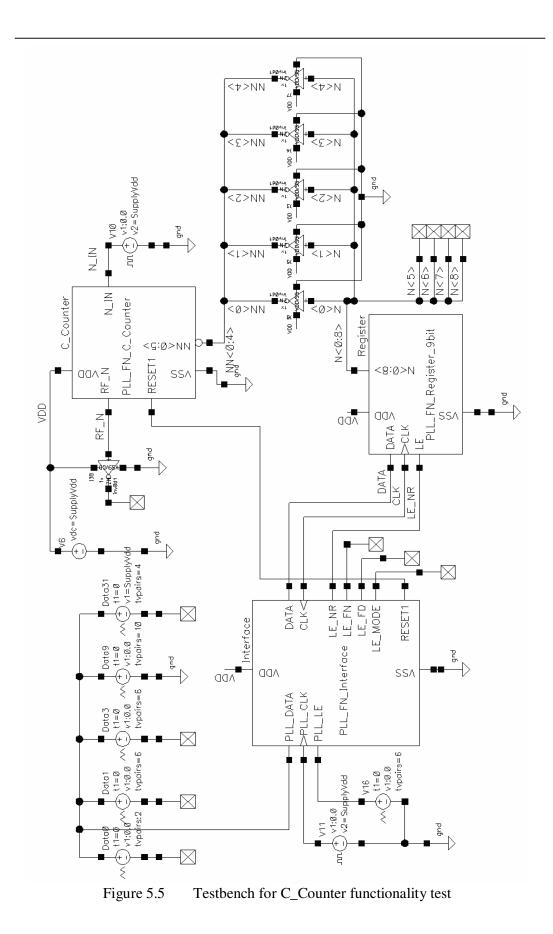

| Figure 5.6:  | Transient simulation results of C_Counter                   | 73 |

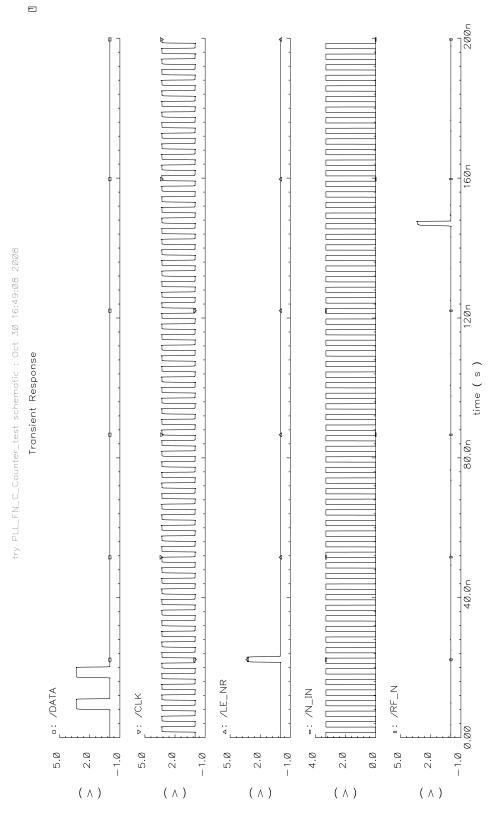

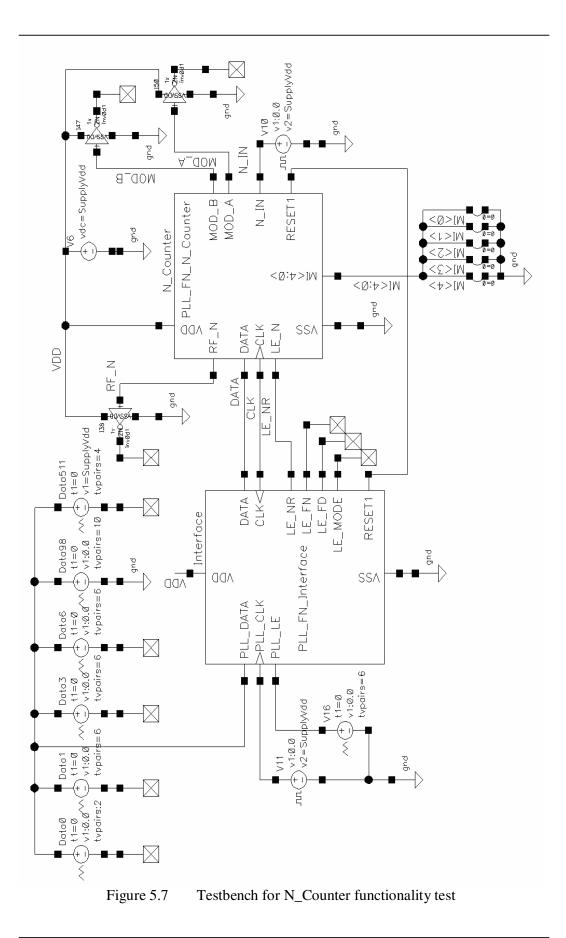

| Figure 5.7:  | Testbench for N_Counter functionality test                  | 74 |

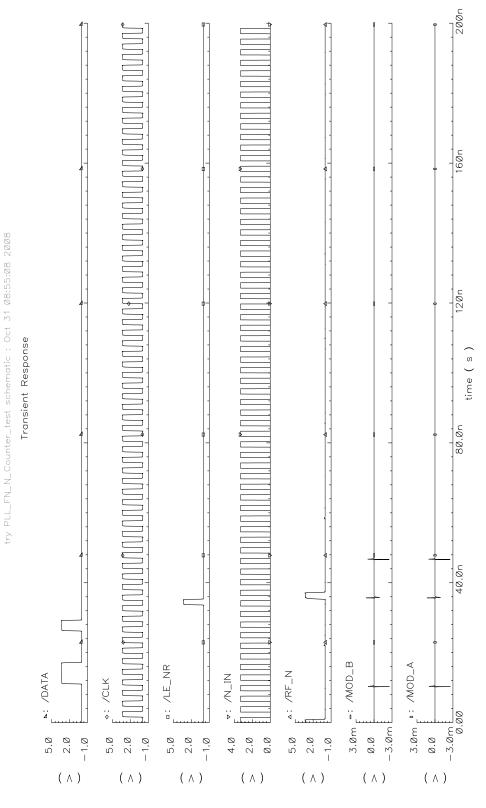

| Figure 5.8:  | Transient simulation results of N_Counter                   | 75 |

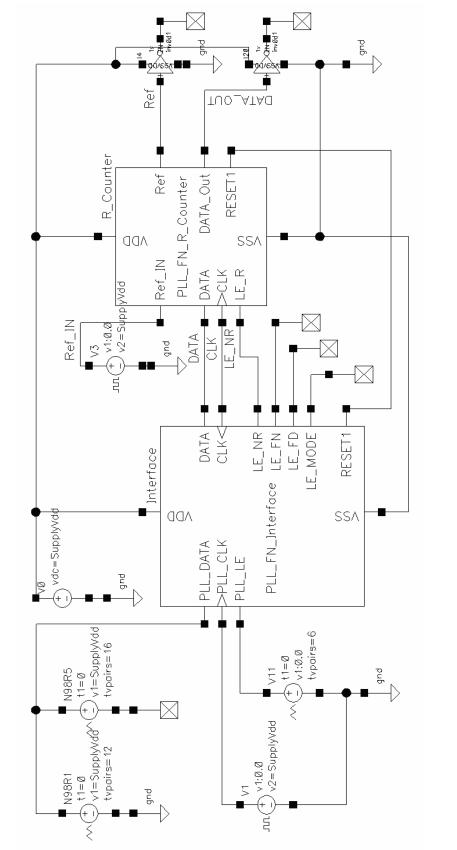

| Figure 5.9:  | Testbench for R_Counter functionality test                  | 76 |

| Figure 5.10: | Transient simulation results of R_Counter                   | 77 |

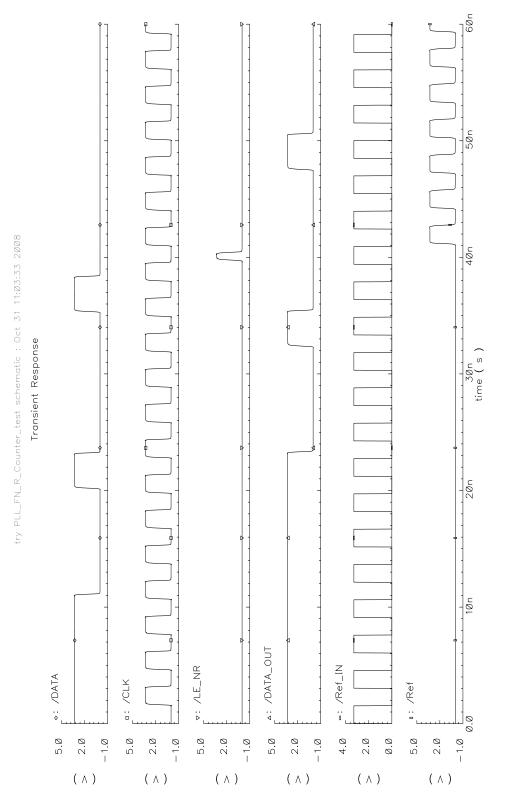

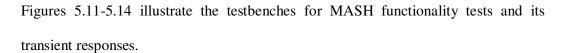

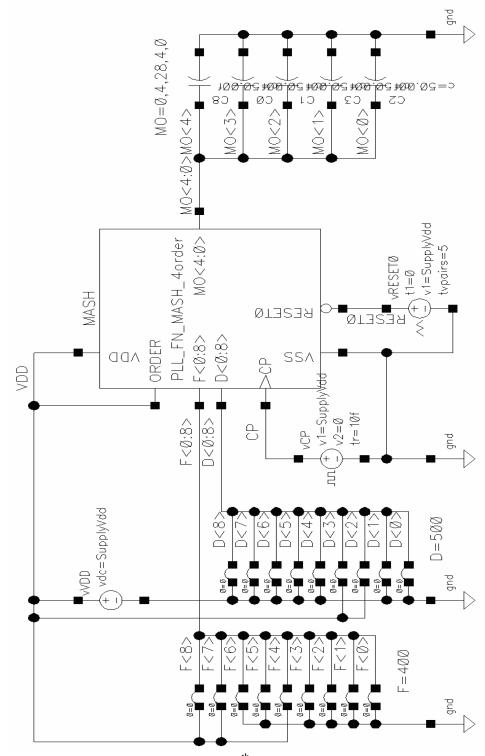

| Figure 5.11: | Testbench for 4 <sup>th</sup> order MASH functionality test | 78 |

| Figure 5.12: | Transient simulation result of MASH_4order                  | 79 |

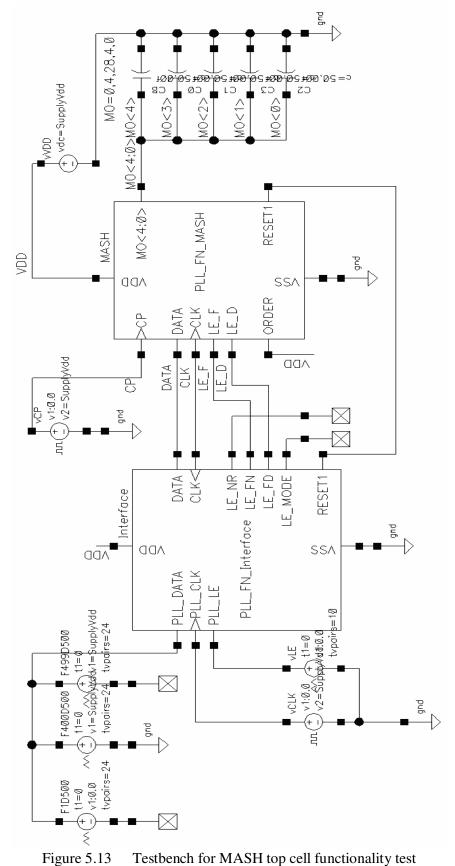

| Figure 5.13: | Testbench for MASH top cell functionality test              | 80 |

| Figure 5.14: | Transient response of MASH top cell                         | 81 |

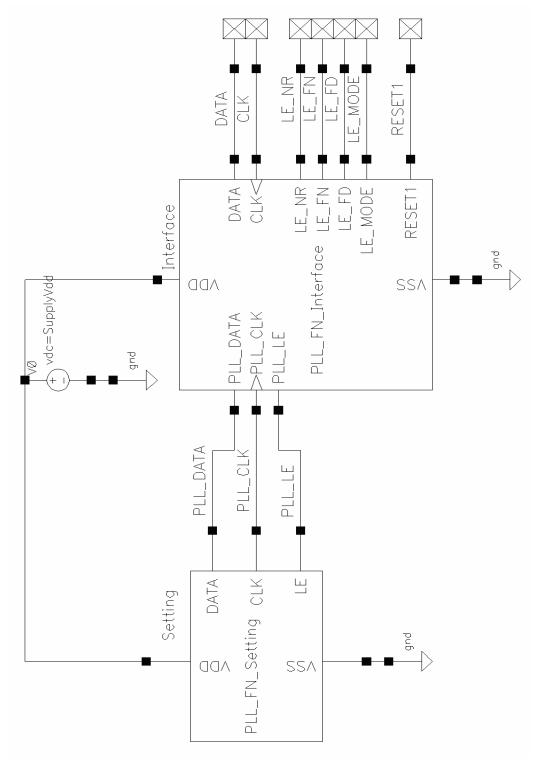

| Figure 5.15: | Testbench for Interface functionality test                  | 82 |

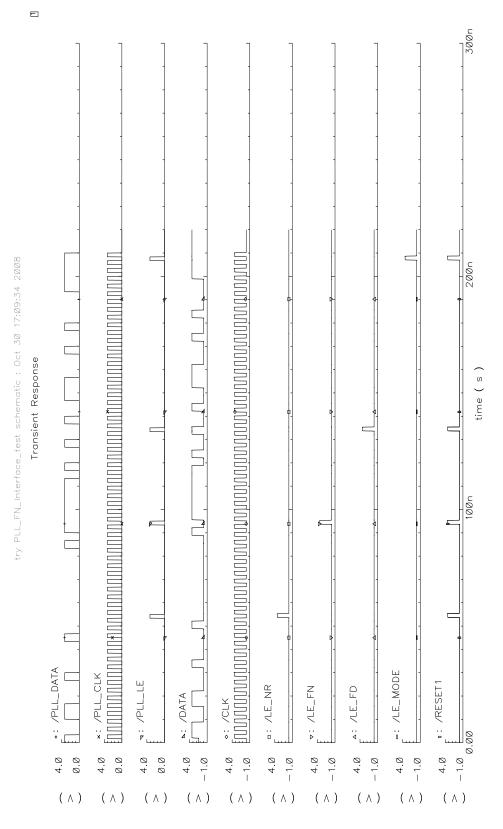

| Figure 5.16: | Transient simulation results of Interface                   | 83 |

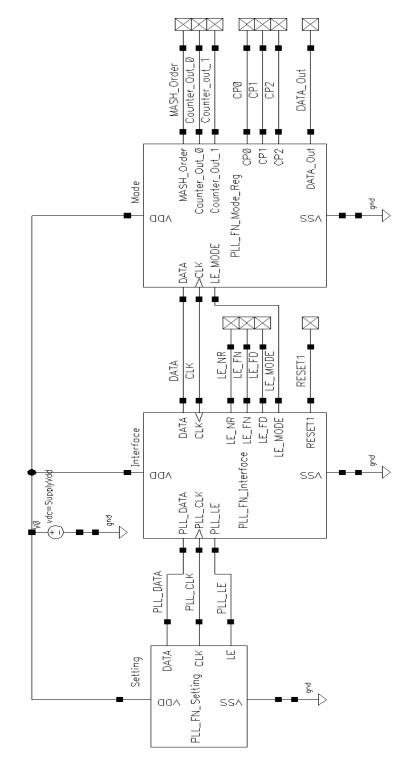

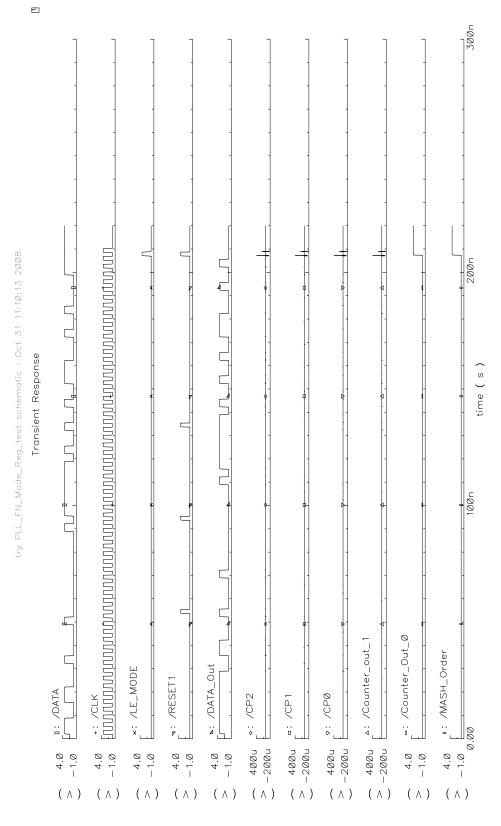

| Figure 5.17: | Testbench for Mode Register functionality test              | 84 |

| Figure 5.18: | Transient response of Mode_Reg                                       | 85  |

|--------------|----------------------------------------------------------------------|-----|

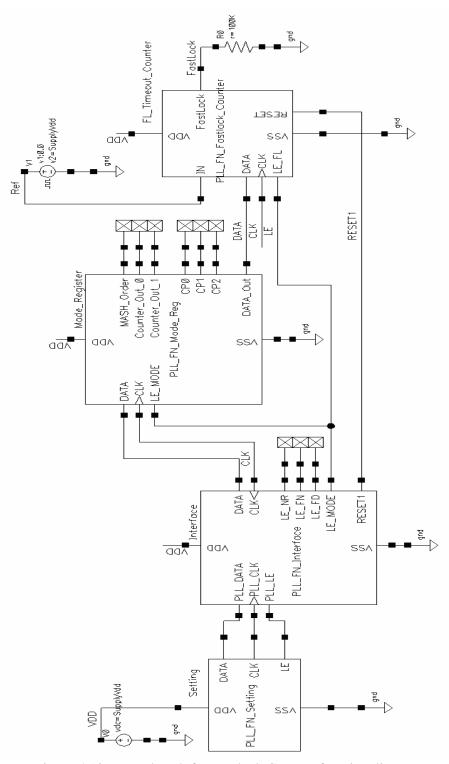

| Figure 5.19: | Testbench for Fastlock Counter functionality test                    | 86  |

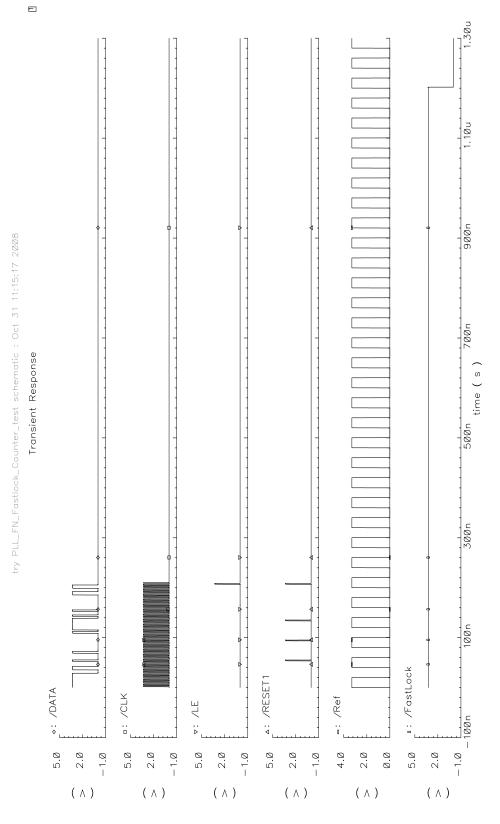

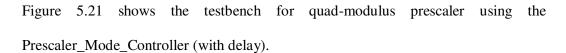

| Figure 5.20: | Transient response of Fastlock_Counter                               | 87  |

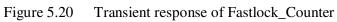

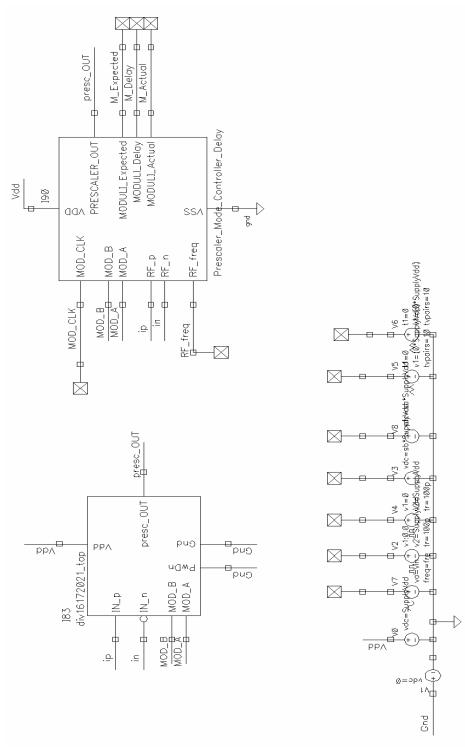

| Figure 5.21: | Testbench for div16172021_top functionality test                     | 88  |

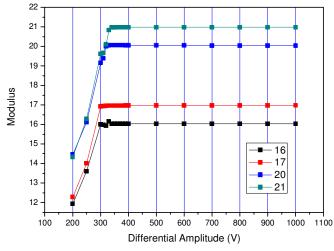

| Figure5.22:  | Minimum input signal amplitude requirement for prescaler             | 89  |

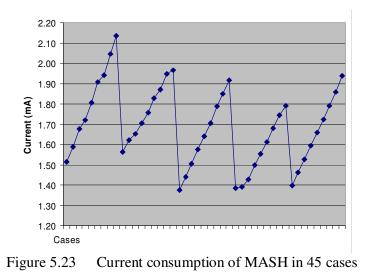

| Figure 5.23: | Current consumption of MASH in 45 cases                              | 93  |

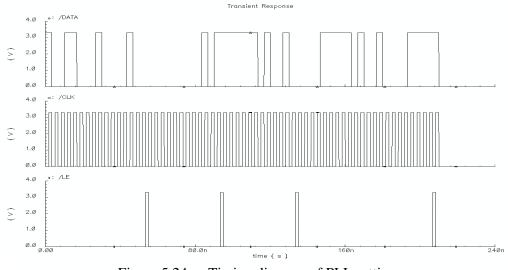

| Figure 5.24: | Timing diagram of PLL setting                                        | 94  |

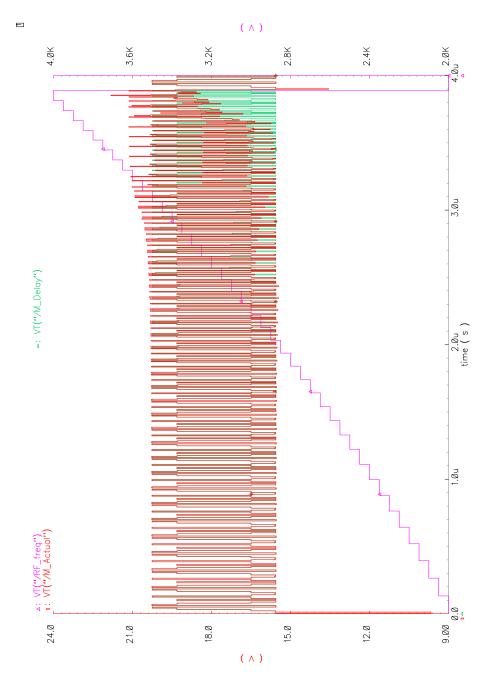

| Figure 5.25: | Dynamic characteristic of prescaler at Typical condition             | 95  |

| Figure 5.26: | Modulus-changing patterns in 2450MHz band                            | 96  |

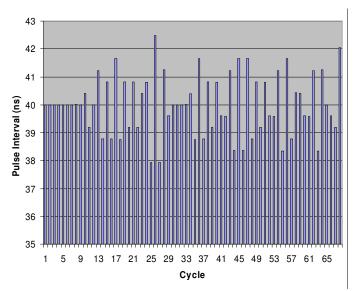

| Figure 5.27: | Pulse interval of N-Counter output                                   | 97  |

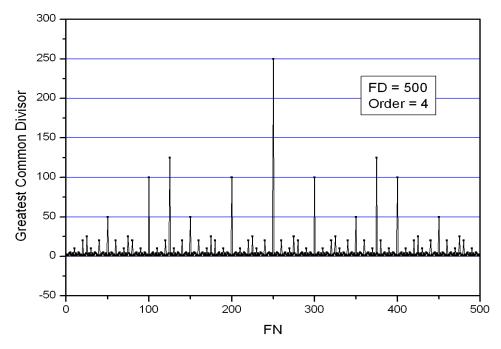

| Figure 5.28: | Greatest common divisor of FN and FD                                 | 97  |

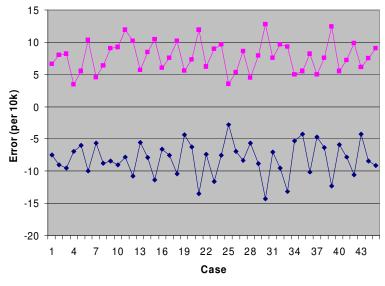

| Figure 5.29: | Error for pulse interval of N-Counter output                         | 98  |

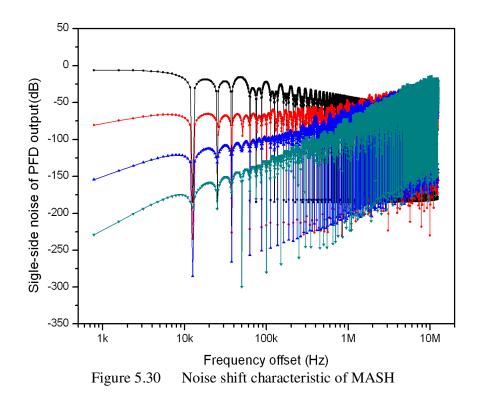

| Figure 5.30: | Noise shift characteristic of MASH                                   | 99  |

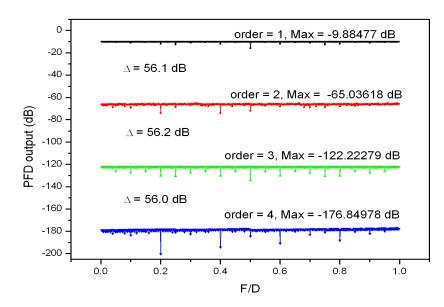

| Figure 5.31: | Noise level of PFD output at 6.25kHz ( $f_{REF} = 25$ MHz)           | 100 |

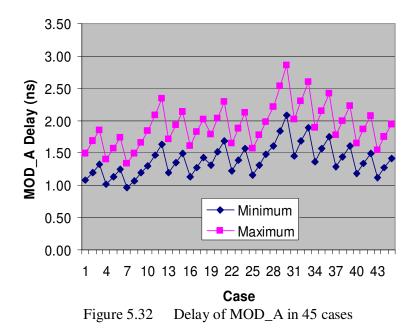

| Figure 5.32: | Delay of MOD_A in 45 cases                                           | 100 |

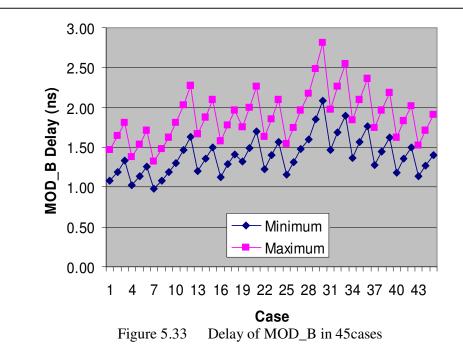

| Figure 5.33: | Delay of MOD_B in 45cases                                            | 101 |

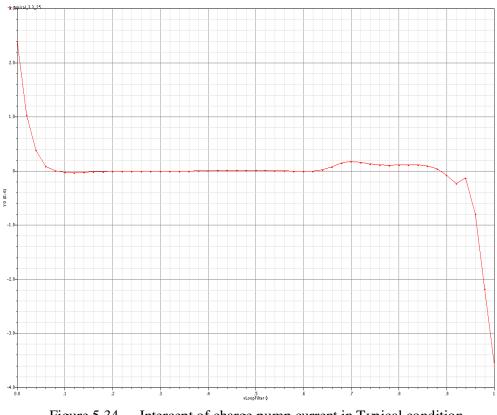

| Figure 5.34: | Intercept of charge pump current in Typical condition                | 101 |

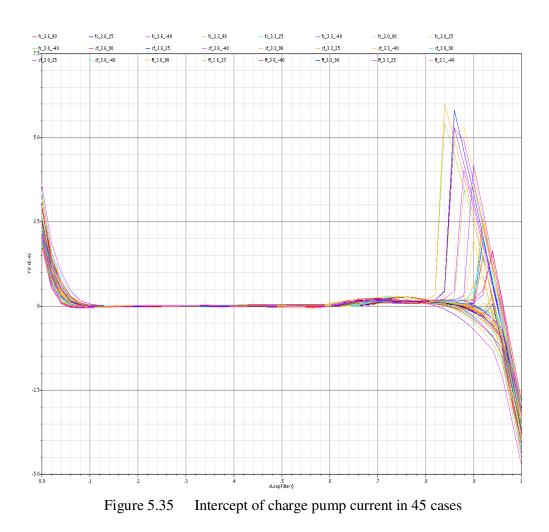

| Figure 5.35: | Intercept of charge pump current in 45 cases                         | 102 |

| Figure 5.36: | Linearity of charge pump current with PFD at Typical condition       | 103 |

| Figure 5.37: | Linearity of charge pump current with PFD at Typical condition       | 104 |

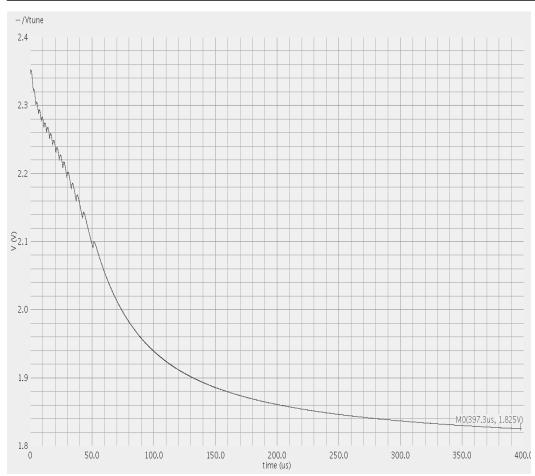

| Figure 5.38: | Locking curve of PLL without Fast-lock function at Typical condition | 105 |

| Figure 5.39: | Locking curve of PLL with Fast-lock function at Typical condition    | 106 |

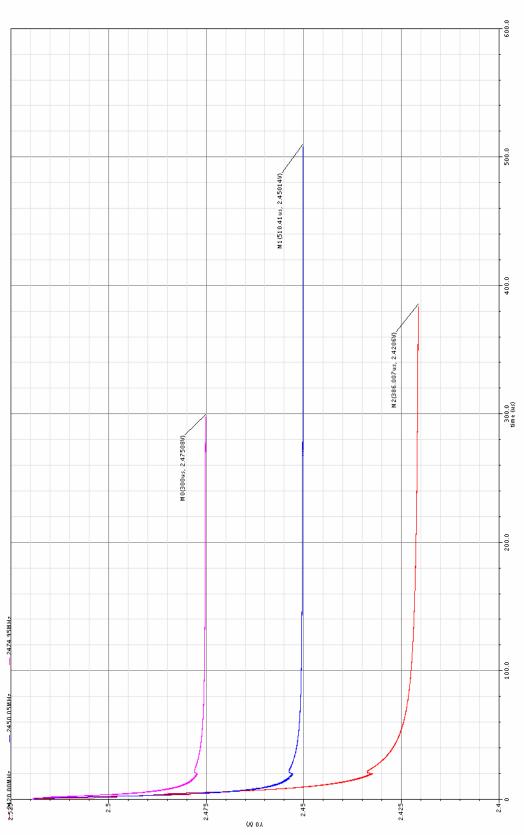

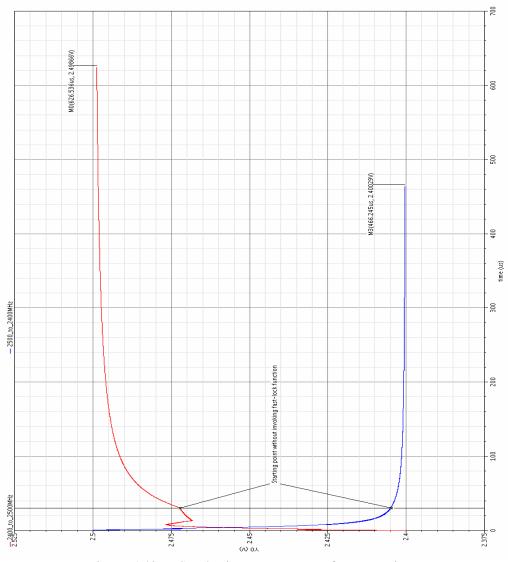

| Figure 5.40: | Synthesizer responses to frequency jumps                             | 107 |

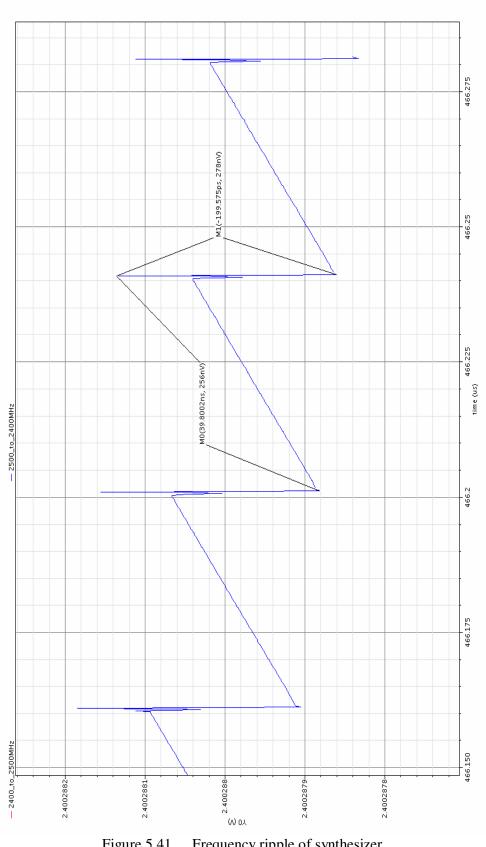

| Figure 5.41: | Frequency ripple of synthesizer                                                                               | 108 |

|--------------|---------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.42: | Timing diagram for PLL setting                                                                                | 111 |

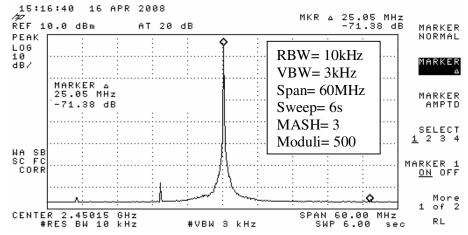

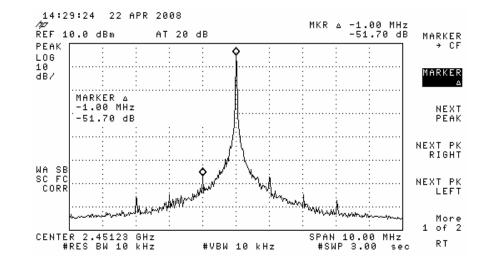

| Figure 5.43: | #5 frequency synthesizer reference spur plot at ~25MHz offset (right)                                         | 112 |

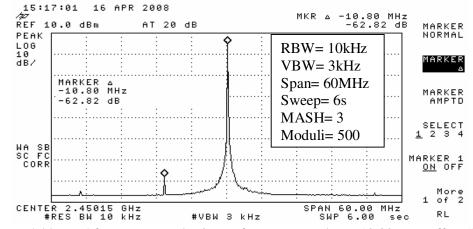

| Figure 5.44: | #5 frequency synthesizer reference spur plot at 10.80MHz offset (left)                                        | 112 |

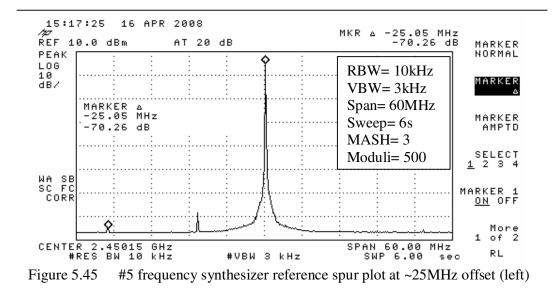

| Figure 5.45: | #5 frequency synthesizer reference spur plot at ~25MHz offset (left)                                          | 113 |

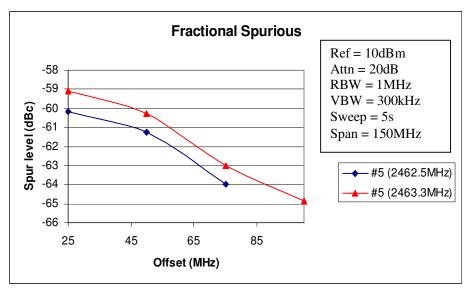

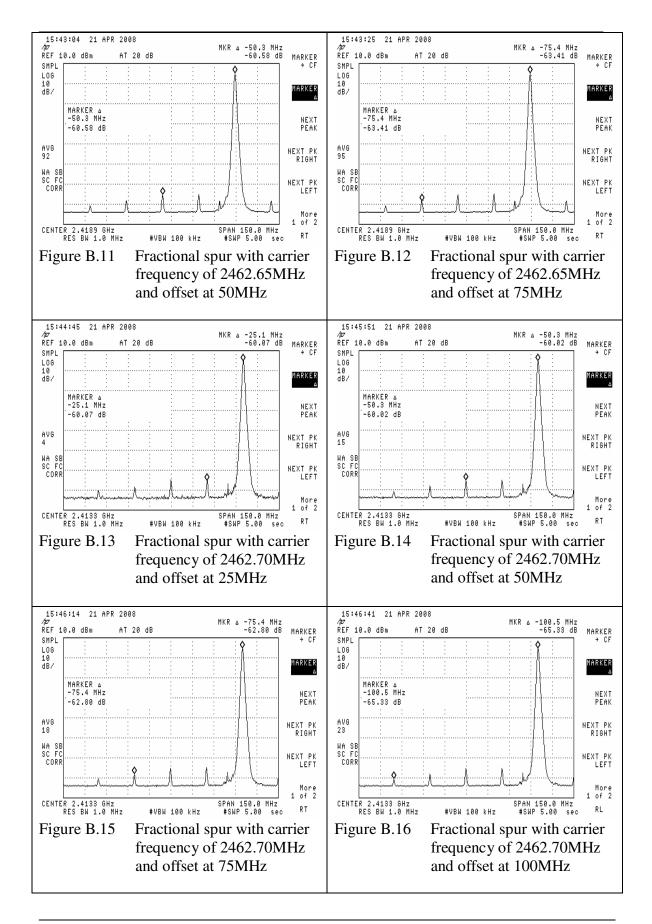

| Figure 5.46: | Fractional spurious levels at 2462.5MHz and 2463.3MHz                                                         | 113 |

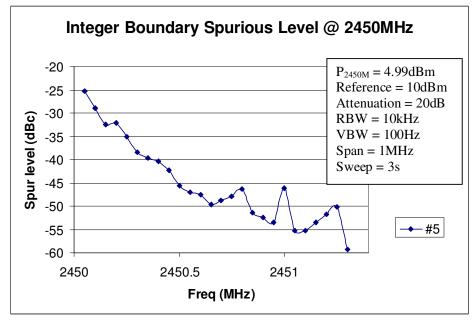

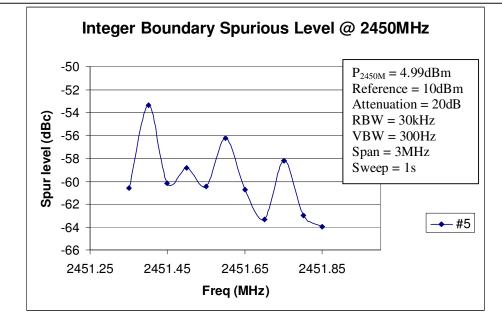

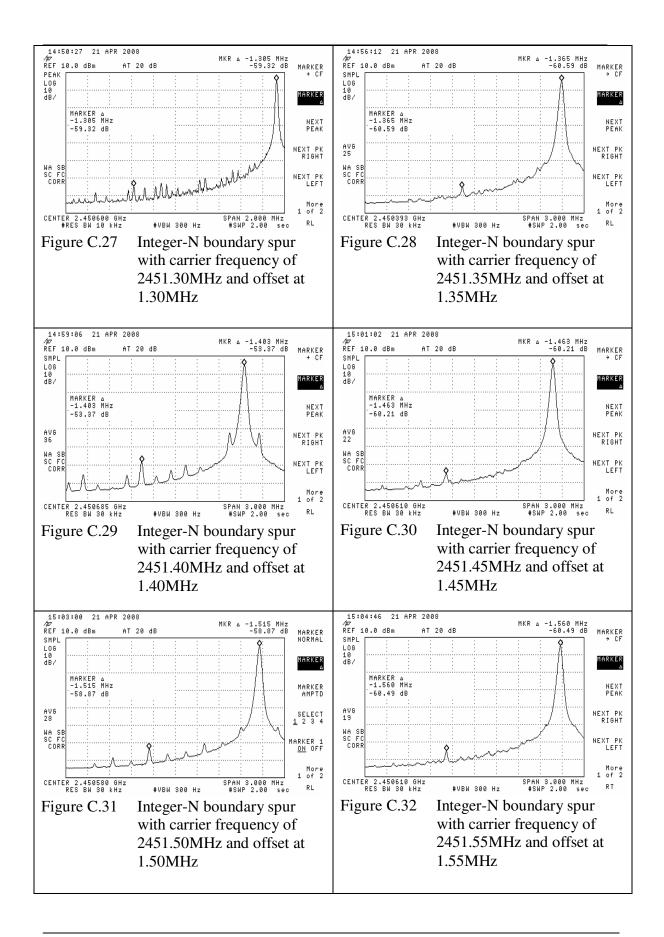

| Figure 5.47: | Integer-N boundary spurs for 2450.05MHz~2451.30MHz                                                            | 115 |

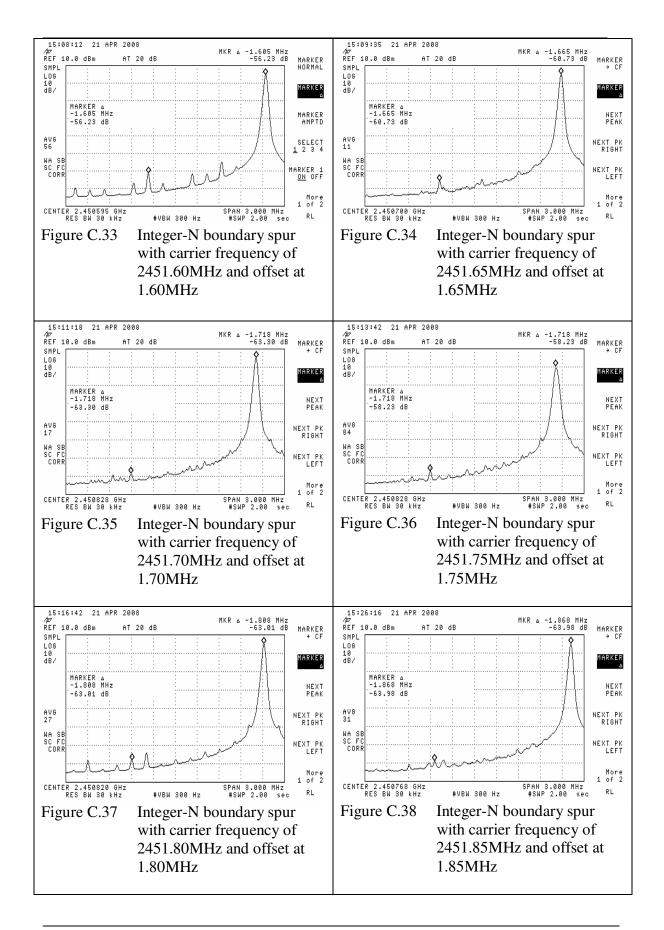

| Figure 5.48: | Integer-N boundary spurs for 2451.35MHz~2451.85MHz                                                            | 116 |

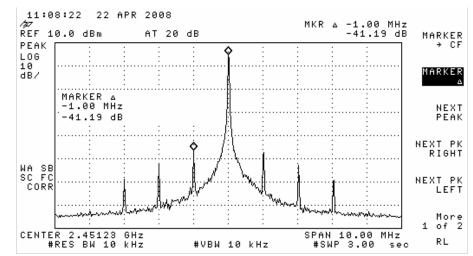

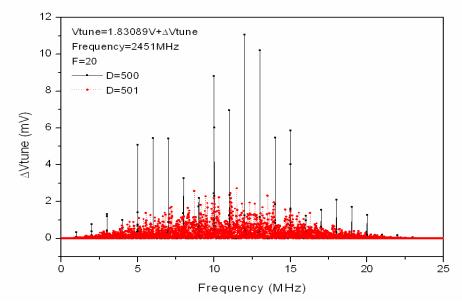

| Figure 5.49: | Integer-N boundary spurs at carrier frequency of 2451MHz and offset of 1MHz with Moduli= 500, MASH=3, FN= 20  | 116 |

| Figure 5.50: | Integer-N boundary spurs at carrier frequency of 2451MHz and offset of 1MHz with Moduli= 501, MASH= 3, FN= 20 | 117 |

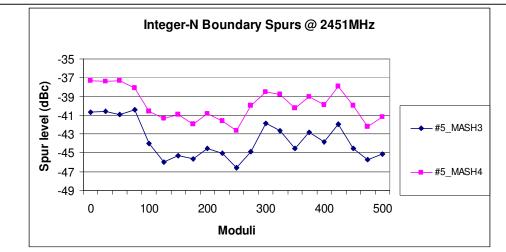

| Figure 5.51: | Effect of denominator on averaging the integer-N boundary spurious levels                                     | 117 |

| Figure 5.52: | Effect of MASH order on integer-N boundary spurious levels                                                    | 118 |

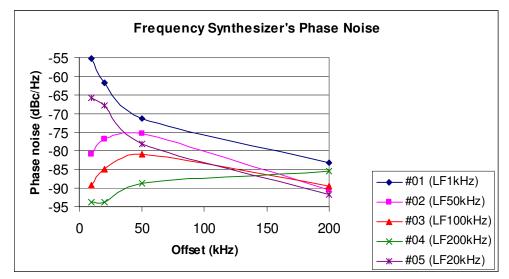

| Figure 5.53: | Frequency synthesizer's phase noise performances                                                              | 120 |

| Figure 5.54: | User interface for PLL setting                                                                                | 122 |

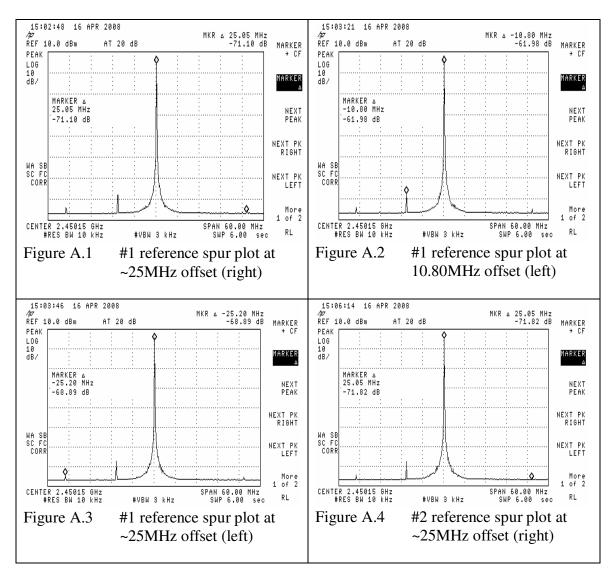

| Figure A.1:  | #1 reference spur plot at ~25MHz offset (right)                                                               | 136 |

| Figure A.2:  | #1 reference spur plot at 10.80MHz offset (left)                                                              | 136 |

| Figure A.3:  | #1 reference spur plot at ~25MHz offset (left)                                                                | 136 |

| Figure A.4:  | #2 reference spur plot at ~25MHz offset (right)                                                               | 136 |

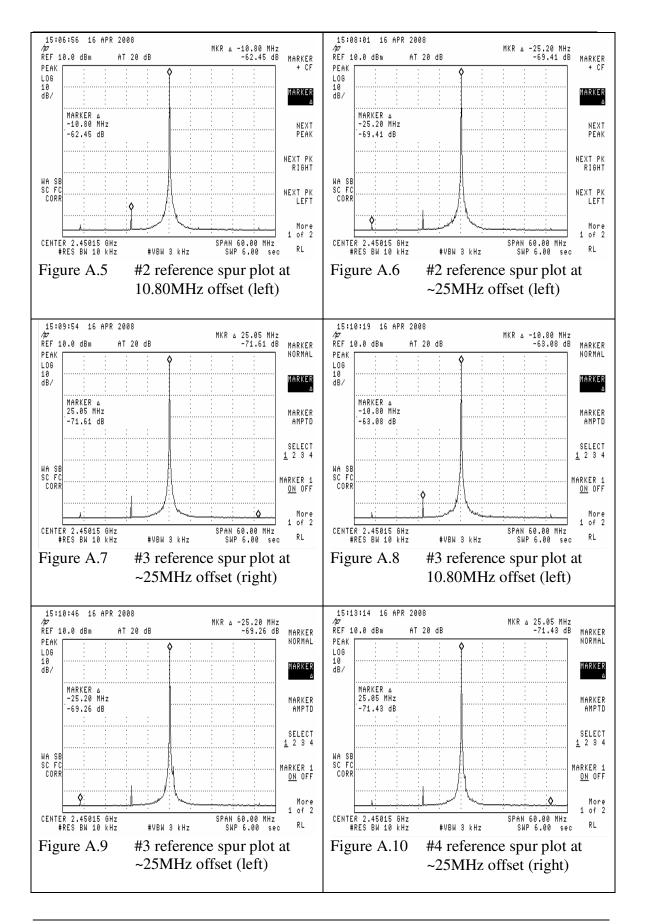

| Figure A.5:  | #2 reference spur plot at 10.80MHz offset (left)                                                              | 137 |

| Figure A.6:  | #2 reference spur plot at ~25MHz offset (left)                                                                | 137 |

| Figure A.7:  | #3 reference spur plot at ~25MHz offset (right)                                                               | 137 |

| Figure A.8:  | #3 reference spur plot at 10.80MHz offset (left)                                                              | 137 |

| Figure A.9:  | #3 reference spur plot at ~25MHz offset (left)                            | 137 |

|--------------|---------------------------------------------------------------------------|-----|

| Figure A.10: | #4 reference spur plot at ~25MHz offset (right)                           | 137 |

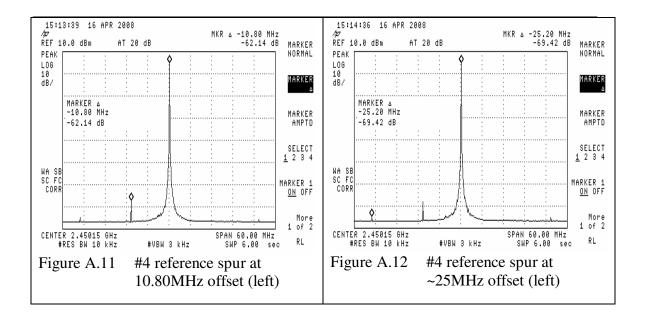

| Figure A.11: | #4 reference spur at 10.80MHz offset (left)                               | 138 |

| Figure A.12: | #4 reference spur at ~25MHz offset (left)                                 | 138 |

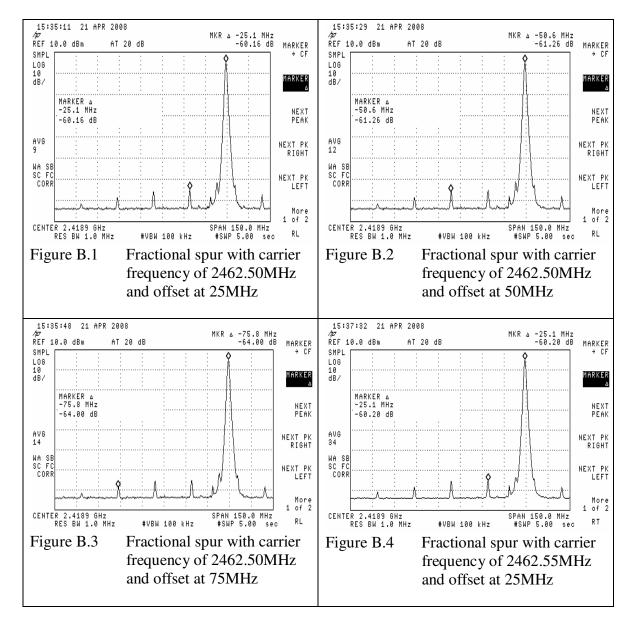

| Figure B.1:  | Fractional spur with carrier frequency of 2462.50MHz and offset at 25MHz  | 139 |

| Figure B.2:  | Fractional spur with carrier frequency of 2462.50MHz and offset at 50MHz. | 139 |

| Figure B.3:  | Fractional spur with carrier frequency of 2462.50MHz and offset at 75MHz. | 139 |

| Figure B.4:  | Fractional spur with carrier frequency of 2462.55MHz and offset at 25MHz. | 139 |

| Figure B.5:  | Fractional spur with carrier frequency of 2462.55MHz and offset at 50MHz. | 140 |

| Figure B.6   | Fractional spur with carrier frequency of 2462.55MHz and offset at 75MHz. | 140 |

| Figure B.7:  | Fractional spur with carrier frequency of 2462.60MHz and offset at 25MHz. | 140 |

| Figure B.8:  | Fractional spur with carrier frequency of 2462.60MHz and offset at 50MHz. | 140 |

| Figure B.9:  | Fractional spur with carrier frequency of 2462.60MHz and offset at 75MHz. | 140 |

| Figure B.10: | Fractional spur with carrier frequency of 2462.65MHz and offset at 25MHz. | 140 |

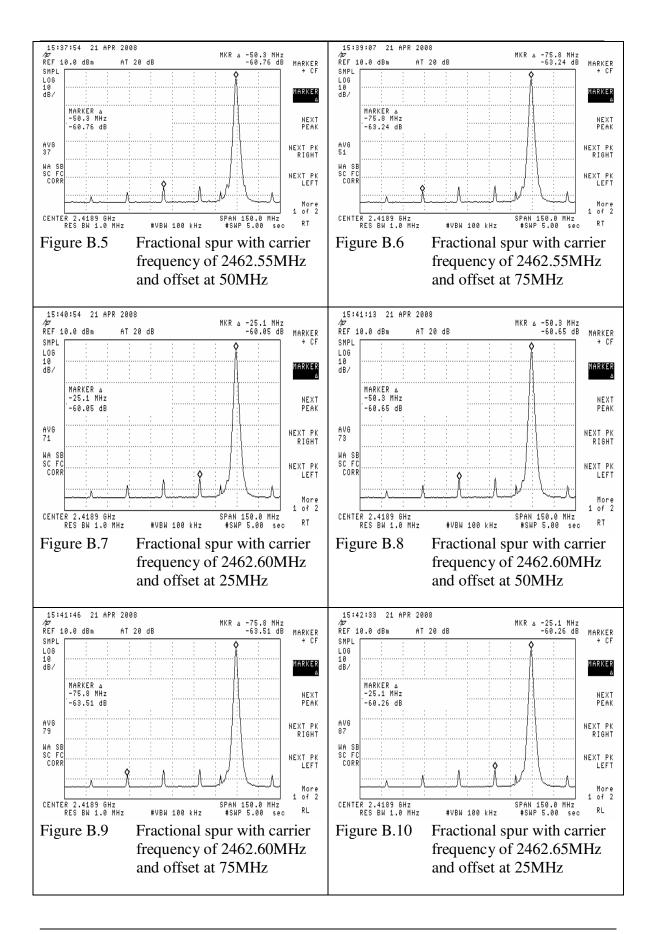

| Figure B.11: | Fractional spur with carrier frequency of 2462.65MHz and offset at 50MHz. | 141 |

| Figure B.12: | Fractional spur with carrier frequency of 2462.65MHz and offset at 75MHz. | 141 |

| Figure B.13: | Fractional spur with carrier frequency of 2462.70MHz and offset at 25MHz. | 141 |

| Figure B.14: | Fractional spur with carrier frequency of 2462.70MHz and offset at 50MHz  | 141 |

| Figure B.15: | Fractional spur with carrier frequency of 2462.70MHz and                   |     |

|--------------|----------------------------------------------------------------------------|-----|

| Tigure D.13. | offset at 75MHz                                                            | 141 |

| Figure B.16: | Fractional spur with carrier frequency of 2462.70MHz and offset at 100MHz. | 141 |

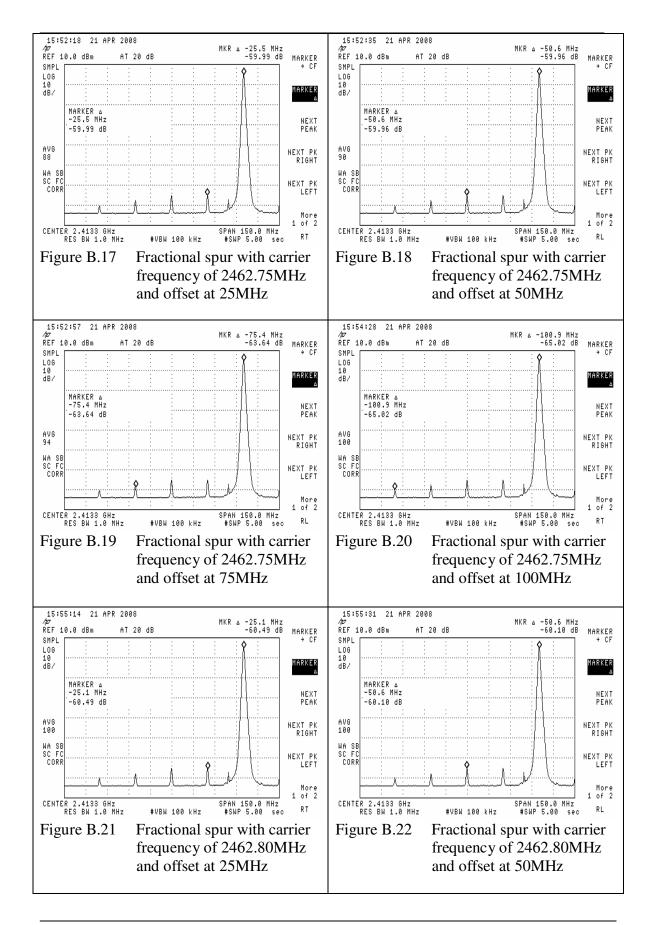

| Figure B.17: | Fractional spur with carrier frequency of 2462.75MHz and offset at 25MHz   | 142 |

| Figure B.18: | Fractional spur with carrier frequency of 2462.75MHz and offset at 50MHz.  | 142 |

| Figure B.19: | Fractional spur with carrier frequency of 2462.75MHz and offset at 75MHz.  | 142 |

| Figure B.20: | Fractional spur with carrier frequency of 2462.75MHz and offset at 100MHz. | 142 |

| Figure B.21: | Fractional spur with carrier frequency of 2462.80MHz and offset at 25MHz.  | 142 |

| Figure B.22: | Fractional spur with carrier frequency of 2462.80MHz and offset at 50MHz.  | 142 |

| Figure B.23: | Fractional spur with carrier frequency of 2462.80MHz and offset at 75MHz.  | 143 |

| Figure B.24: | Fractional spur with carrier frequency of 2462.80MHz and offset at 100MHz  | 143 |

| Figure B.25: | Fractional spur with carrier frequency of 2462.85MHz and offset at 25MHz.  | 143 |

| Figure B.26: | Fractional spur with carrier frequency of 2462.85MHz and offset at 50MHz   | 143 |

| Figure B.27: | Fractional spur with carrier frequency of 2462.85MHz and offset at 75MHz   | 143 |

| Figure B.28: | Fractional spur with carrier frequency of 2462.85MHz and offset at 100MHz  | 143 |

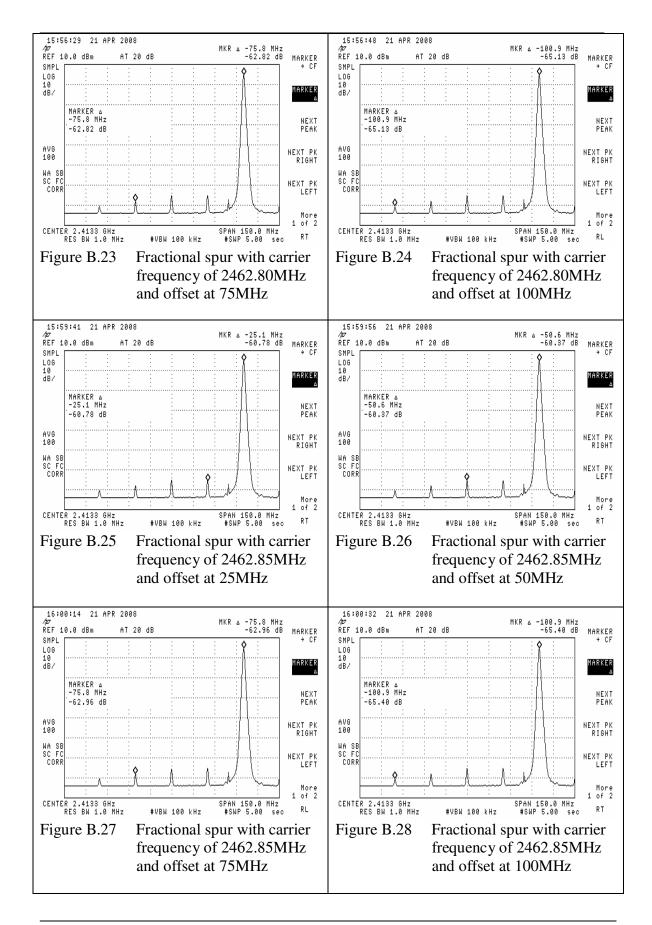

| Figure B.29: | Fractional spur with carrier frequency of 2462.90MHz and offset at 25MHz   | 144 |

| Figure B.30: | Fractional spur with carrier frequency of 2462.90MHz and offset at 50MHz   | 144 |

| Figure B.31: | Fractional spur with carrier frequency of 2462.90MHz and offset at 75MHz.  | 144 |

|--------------|----------------------------------------------------------------------------|-----|

| Figure B.32: | Fractional spur with carrier frequency of 2462.90MHz and offset at 100MHz  | 144 |

| Figure B.33: | Fractional spur with carrier frequency of 2462.95MHz and offset at 25MHz   | 144 |

| Figure B.34: | Fractional spur with carrier frequency of 2462.95MHz and offset at 50MHz.  | 144 |

| Figure B.35: | Fractional spur with carrier frequency of 2462.95MHz and offset at 75MHz.  | 145 |

| Figure B.36: | Fractional spur with carrier frequency of 2462.95MHz and offset at 100MHz  | 145 |

| Figure B.37: | Fractional spur with carrier frequency of 2463.00MHz and offset at 25MHz.  | 145 |

| Figure B.38: | Fractional spur with carrier frequency of 2463.00MHz and offset at 50MHz.  | 145 |

| Figure B.39: | Fractional spur with carrier frequency of 2463.00MHz and offset at 75MHz   | 145 |

| Figure B.40: | Fractional spur with carrier frequency of 2463.00MHz and offset at 100MHz  | 145 |

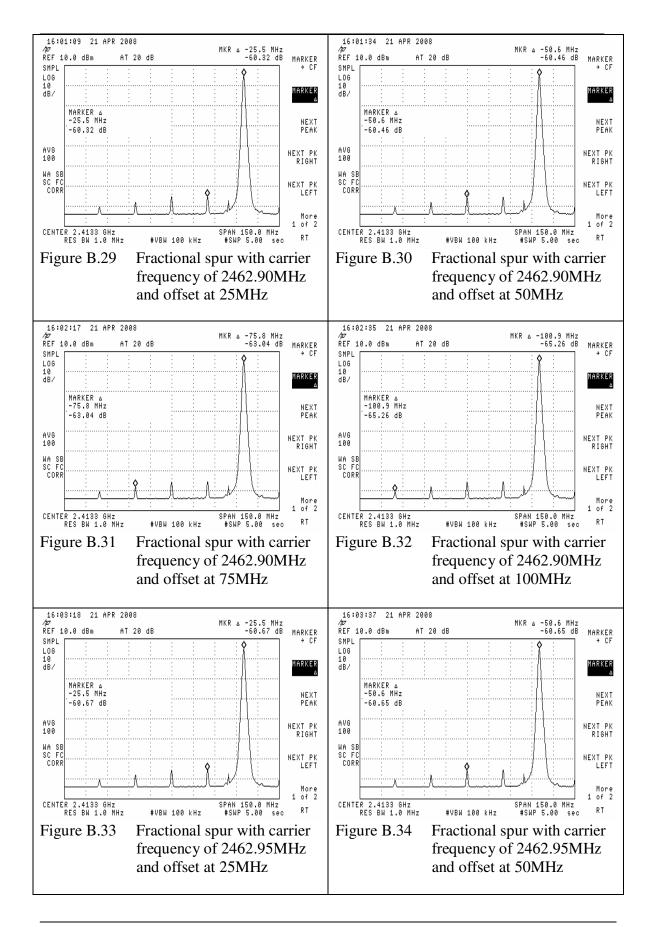

| Figure B.41: | Fractional spur with carrier frequency of 2463.05MHz and offset at 25MHz   | 146 |

| Figure B.42: | Fractional spur with carrier frequency of 2463.05MHz and offset at 50MHz   | 146 |

| Figure B.43: | Fractional spur with carrier frequency of 2463.05MHz and offset at 75MHz.  | 146 |

| Figure B.44: | Fractional spur with carrier frequency of 2463.05MHz and offset at 100MHz. | 146 |

| Figure B.45: | Fractional spur with carrier frequency of 2463.10MHz and offset at 25MHz.  | 146 |

| Figure B.46: | Fractional spur with carrier frequency of 2463.10MHz and offset at 50MHz.  | 146 |

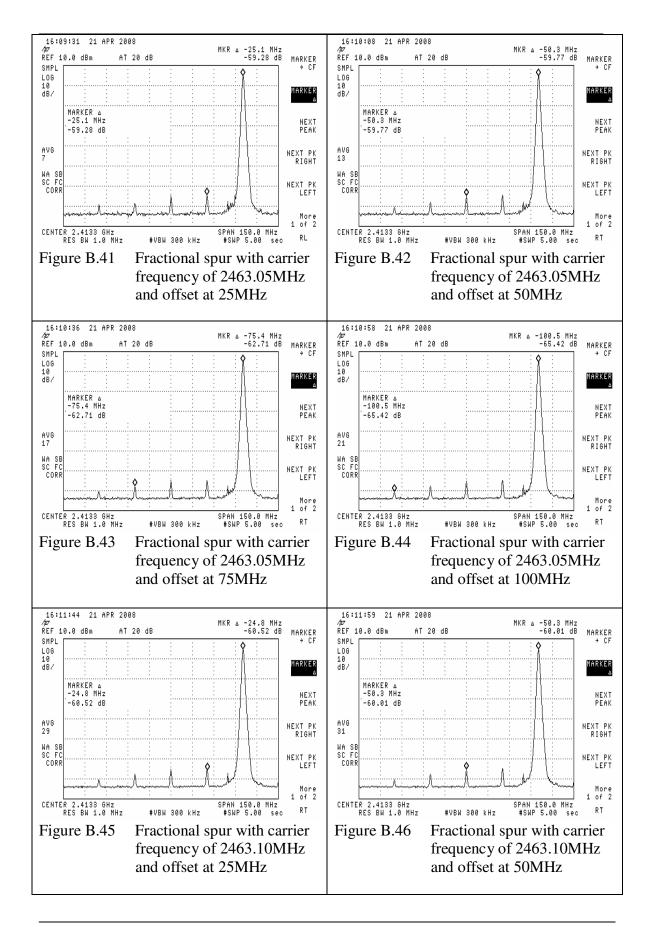

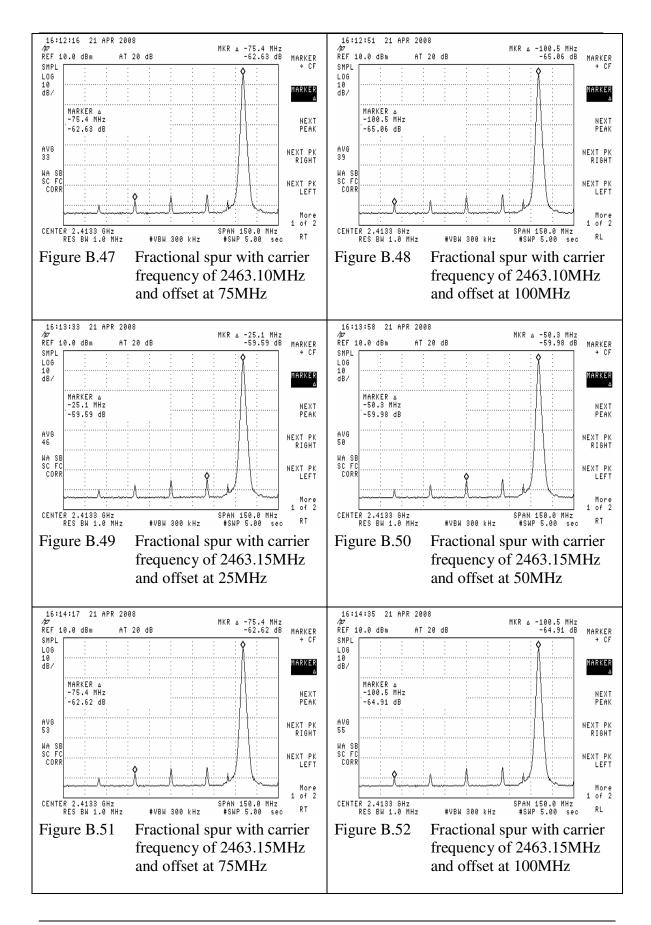

| Figure B.47: | Fractional spur with carrier frequency of 2463.10MHz and offset at 75MHz   | 147 |

|--------------|----------------------------------------------------------------------------|-----|

| Figure B.48: | Fractional spur with carrier frequency of 2463.10MHz and offset at 100MHz  | 147 |

| Figure B.49: | Fractional spur with carrier frequency of 2463.15MHz and offset at 25MHz   | 147 |

| Figure B.50: | Fractional spur with carrier frequency of 2463.15MHz and offset at 50MHz.  | 147 |

| Figure B.51: | Fractional spur with carrier frequency of 2463.15MHz and offset at 75MHz.  | 147 |

| Figure B.52: | Fractional spur with carrier frequency of 2463.15MHz and offset at 100MHz. | 147 |

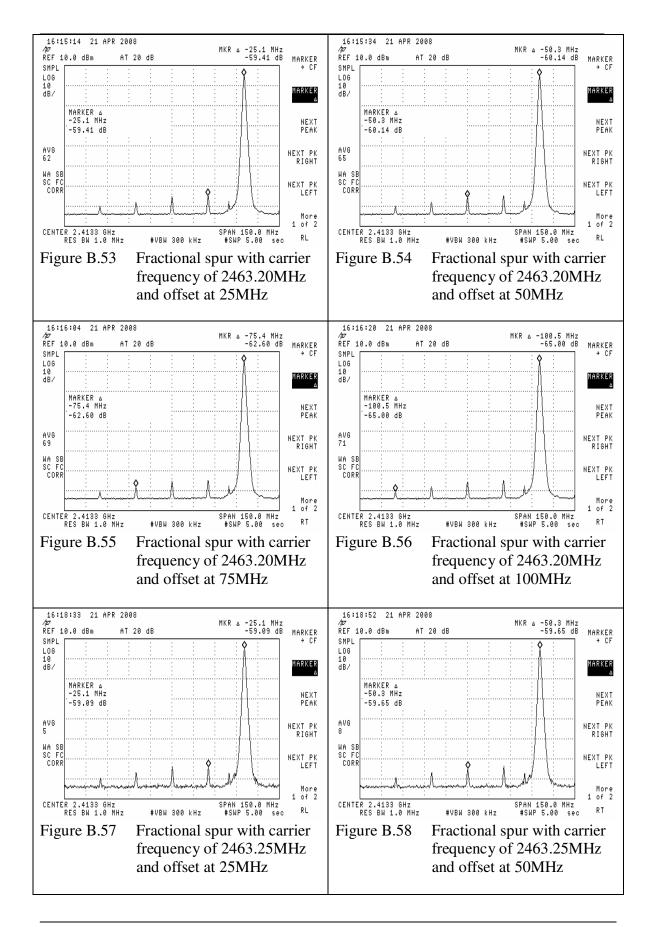

| Figure B.53: | Fractional spur with carrier frequency of 2463.20MHz and offset at 25MHz.  | 148 |

| Figure B.54: | Fractional spur with carrier frequency of 2463.20MHz and offset at 50MHz.  | 148 |

| Figure B.55: | Fractional spur with carrier frequency of 2463.20MHz and offset at 75MHz.  | 148 |

| Figure B.56: | Fractional spur with carrier frequency of 2463.20MHz and offset at 100MHz  | 148 |

| Figure B.57: | Fractional spur with carrier frequency of 2463.25MHz and offset at 25MHz   | 148 |

| Figure B.58: | Fractional spur with carrier frequency of 2463.25MHz and offset at 50MHz   | 148 |

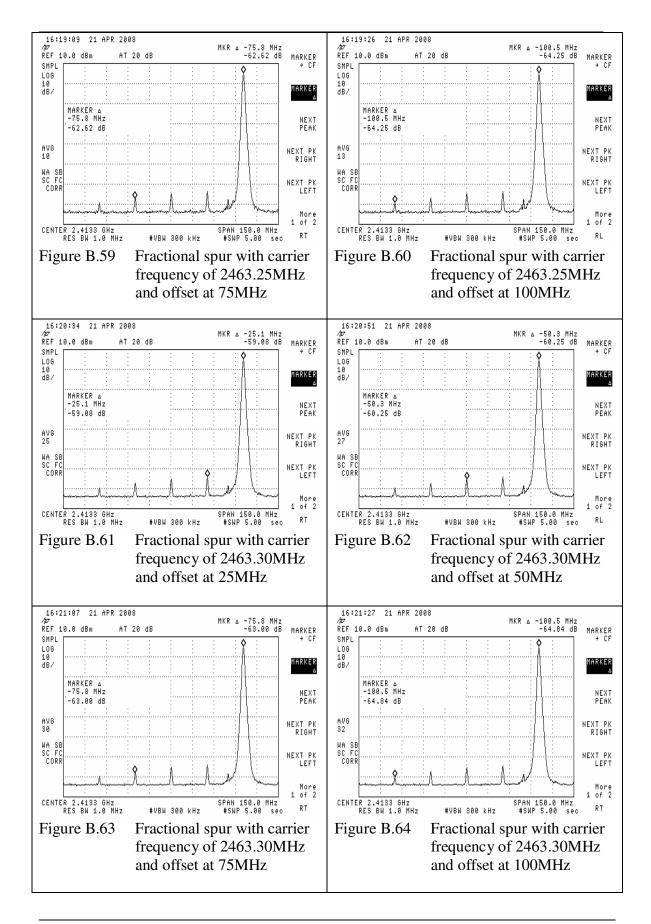

| Figure B.59: | Fractional spur with carrier frequency of 2463.25MHz and offset at 75MHz   | 149 |

| Figure B.60: | Fractional spur with carrier frequency of 2463.25MHz and offset at 100MHz  | 149 |

| Figure B.61: | Fractional spur with carrier frequency of 2463.30MHz and offset at 25MHz   | 149 |

| Figure B.62: | Fractional spur with carrier frequency of 2463.30MHz and offset at 50MHz   | 149 |

| Figure B.63: | Fractional spur with carrier frequency of 2463.30MHz and offset at 75MHz.         | 149 |

|--------------|-----------------------------------------------------------------------------------|-----|

| Figure B.64: | Fractional spur with carrier frequency of 2463.30MHz and offset at 100MHz.        | 149 |

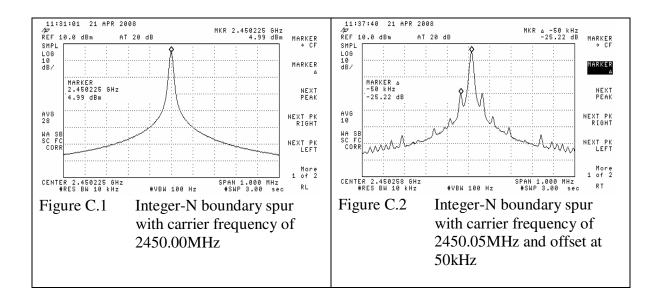

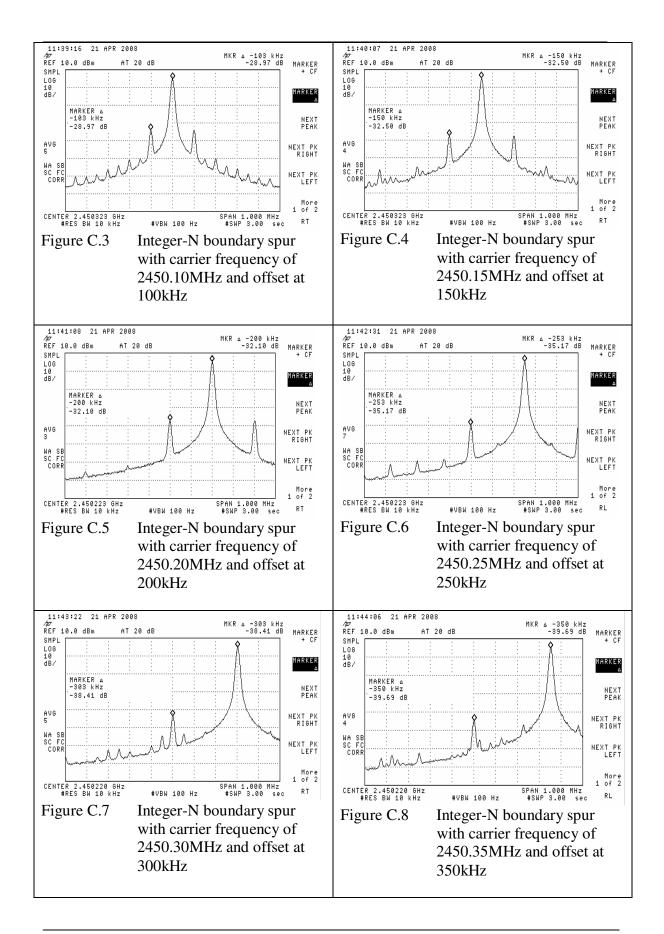

| Figure C.1:  | Integer-N boundary spur with carrier frequency of 2450.00MHz                      | 151 |

| Figure C.2:  | Integer-N boundary spur with carrier frequency of 2450.05MHz and offset at 50kHz  | 151 |

| Figure C.3:  | Integer-N boundary spur with carrier frequency of 2450.10MHz and offset at 100kHz | 152 |

| Figure C.4:  | Integer-N boundary spur with carrier frequency of 2450.15MHz and offset at 150kHz | 152 |

| Figure C.5:  | Integer-N boundary spur with carrier frequency of 2450.20MHz and offset at 200kHz | 152 |

| Figure C.6:  | Integer-N boundary spur with carrier frequency of 2450.25MHz and offset at 250kHz | 152 |

| Figure C.7:  | Integer-N boundary spur with carrier frequency of 2450.30MHz and offset at 300kHz | 152 |

| Figure C.8:  | Integer-N boundary spur with carrier frequency of 2450.35MHz and offset at 350kHz | 152 |

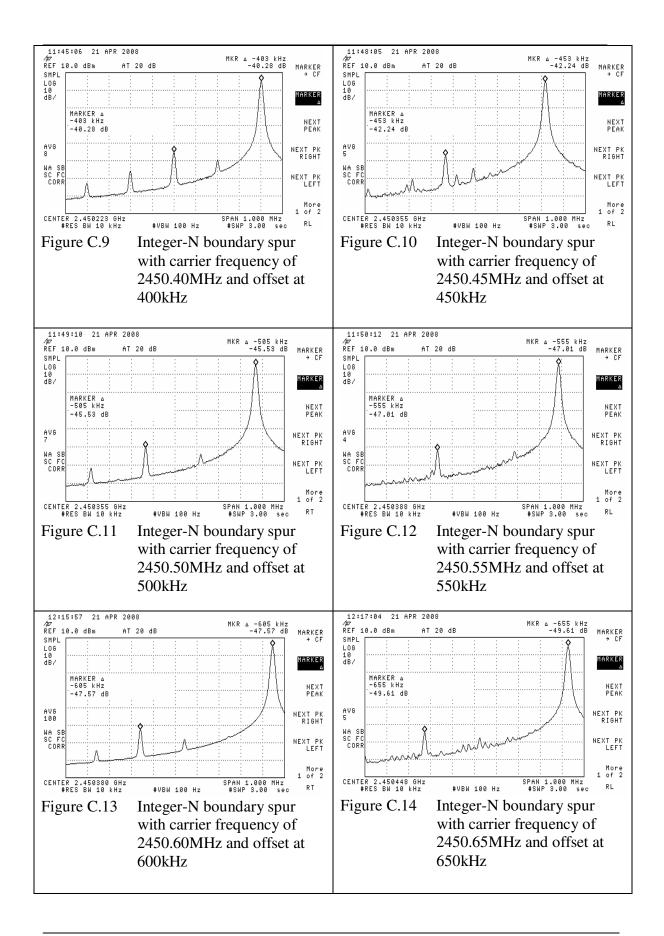

| Figure C.9:  | Integer-N boundary spur with carrier frequency of 2450.40MHz and offset at 400kHz | 153 |

| Figure C.10: | Integer-N boundary spur with carrier frequency of 2450.45MHz and offset at 450kHz |     |

| Figure C.11: | Integer-N boundary spur with carrier frequency of 2450.50MHz and offset at 500kHz | 153 |

| Figure C.12: | Integer-N boundary spur with carrier frequency of 2450.55MHz and offset at 550kHz | 153 |

| Figure C.13: | Integer-N boundary spur with carrier frequency of 2450.60MHz and offset at 600kHz | 153 |

| Figure C.14: | Integer-N boundary spur with carrier frequency of 2450.65MHz and offset at 650kHz | 153 |

| Figure C.15: | Integer-Nboundaryspurwithcarrierfrequencyof2450.70MHz and offset at 700kHz1          | 54 |

|--------------|--------------------------------------------------------------------------------------|----|

| Figure C.16: | Integer-N boundary spur with carrier frequency of 2450.75MHz and offset at 750kHz 1  | 54 |

| Figure C.17: |                                                                                      | 54 |

| Figure C.18: | Integer-N boundary spur with carrier frequency of 2450.85MHz and offset at 850kHz 1  | 54 |

| Figure C.19: | Integer-N boundary spur with carrier frequency of 2450.90MHz and offset at 900kHz 1  | 54 |

| Figure C.20: | Integer-N boundary spur with carrier frequency of 2450.95MHz and offset at 950kHz 1  | 54 |

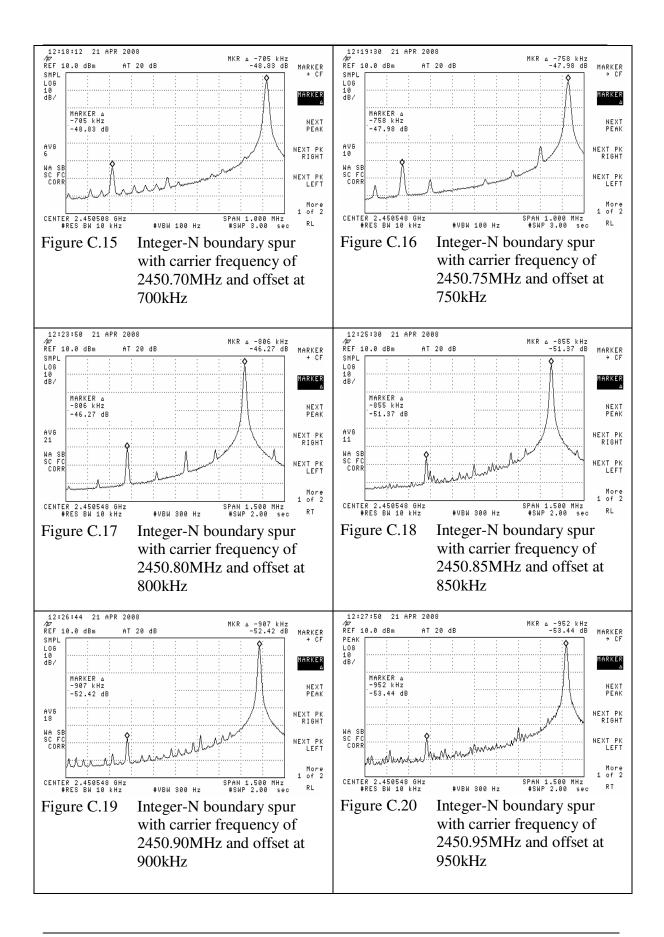

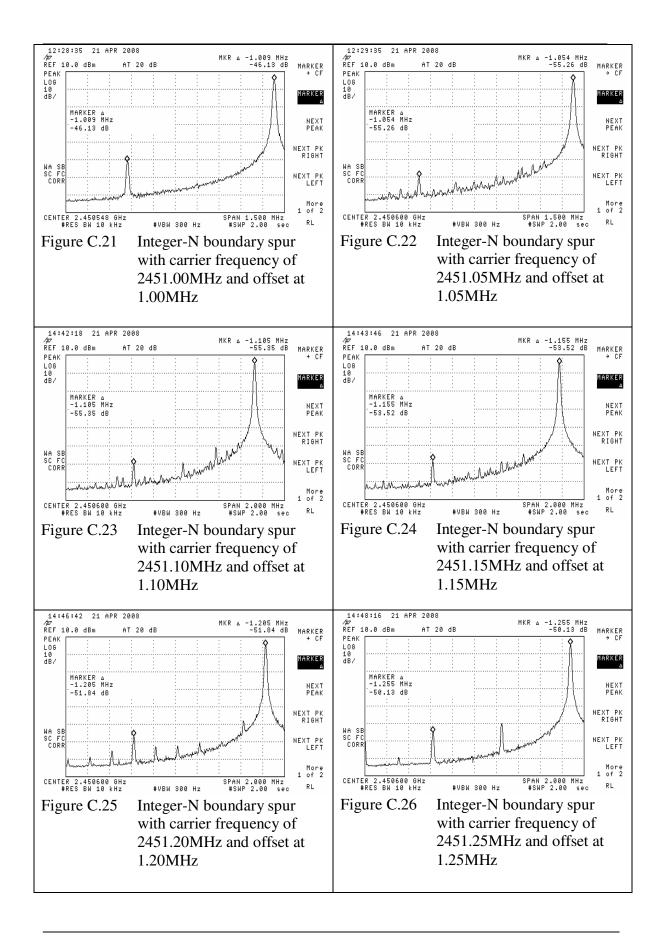

| Figure C.21: | Integer-N boundary spur with carrier frequency of 2451.00MHz and offset at 1.00MHz 1 | 55 |

| Figure C.22: | Integer-N boundary spur with carrier frequency of 2451.05MHz and offset at 1.05MHz 1 | 55 |

| Figure C.23: | Integer-N boundary spur with carrier frequency of 2451.10MHz and offset at 1.10MHz 1 | 55 |

| Figure C.24: | Integer-N boundary spur with carrier frequency of 2451.15MHz and offset at 1.15MHz 1 | 55 |

| Figure C.25: | Integer-N boundary spur with carrier frequency of 2451.20MHz and offset at 1.20MHz 1 | 55 |

| Figure C.26: | Integer-N boundary spur with carrier frequency of 2451.25MHz and offset at 1.25MHz 1 |    |

| Figure C.27: | Integer-N boundary spur with carrier frequency of 2451.30MHz and offset at 1.30MHz 1 | 56 |

| Figure C.28: | Integer-N boundary spur with carrier frequency of 2451.35MHz and offset at 1.35MHz 1 | 56 |

| Figure C.29: | Integer-N boundary spur with carrier frequency of 2451.40MHz and offset at 1.40MHz 1 | 56 |

| Figure C.30: |                                                                                      | 56 |

| Figure C.31: | Integer-N boundary spur with carrier frequency of 2451.50MHz and offset at 1.50MHz     |

|--------------|----------------------------------------------------------------------------------------|

| Figure C.32: | Integer-N boundary spur with carrier frequency of 2451.55MHz and offset at 1.55MHz     |

| Figure C.33: | Integer-N boundary spur with carrier frequency of 2451.60MHz and offset at 1.60MHz     |

| Figure C.34: | Integer-N boundary spur with carrier frequency of 2451.65MHz and offset at 1.65MHz 157 |

| Figure C.35: | Integer-N boundary spur with carrier frequency of 2451.70MHz and offset at 1.70MHz     |

| Figure C.36: | Integer-N boundary spur with carrier frequency of 2451.75MHz and offset at 1.75MHz 157 |

| Figure C.37: | Integer-N boundary spur with carrier frequency of 2451.80MHz and offset at 1.80MHz     |

| Figure C.38: | Integer-N boundary spur with carrier frequency of 2451.85MHz and offset at 1.85MHz 157 |

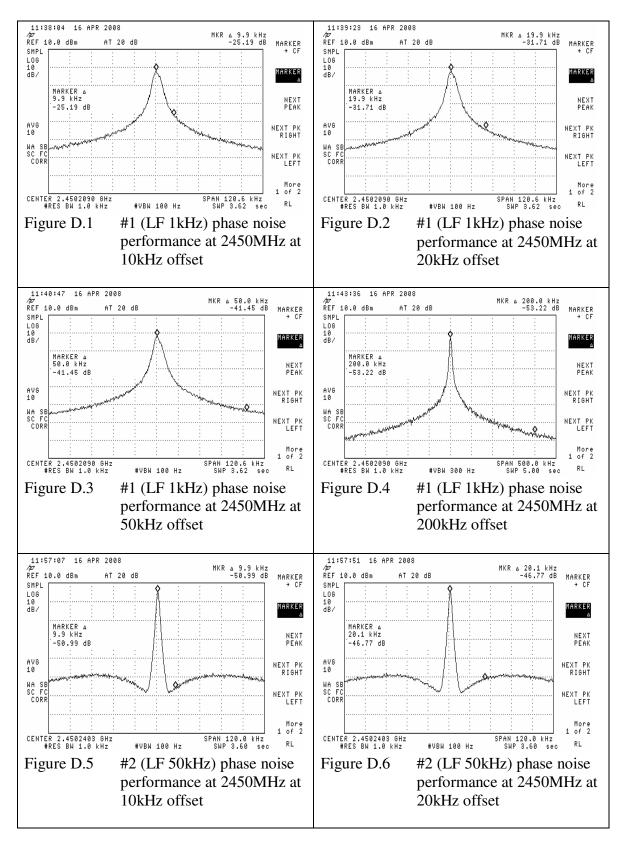

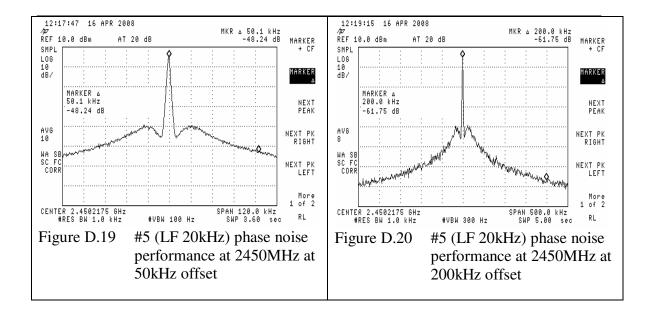

| Figure D.1:  | #1 (LF 1kHz) phase noise performance at 2450MHz at 10kHz offset                        |

| Figure D.2:  | #1 (LF 1kHz) phase noise performance at 2450MHz at 20kHz offset                        |

| Figure D.3:  | #1 (LF 1kHz) phase noise performance at 2450MHz at 50kHz offset                        |

| Figure D.4:  | #1 (LF 1kHz) phase noise performance at 2450MHz at 200kHz offset                       |

| Figure D.5:  | #2 (LF 50kHz) phase noise performance at 2450MHz at 10kHz offset                       |

| Figure D.6:  | #2 (LF 50kHz) phase noise performance at 2450MHz at 20kHz offset                       |

| Figure D.7:  | #2 (LF 50kHz) phase noise performance at 2450MHz at 50kHz offset                       |

| Figure D.8:  | #2 (LF 50kHz) phase noise performance at 2450MHz at 200kHz offset                      |

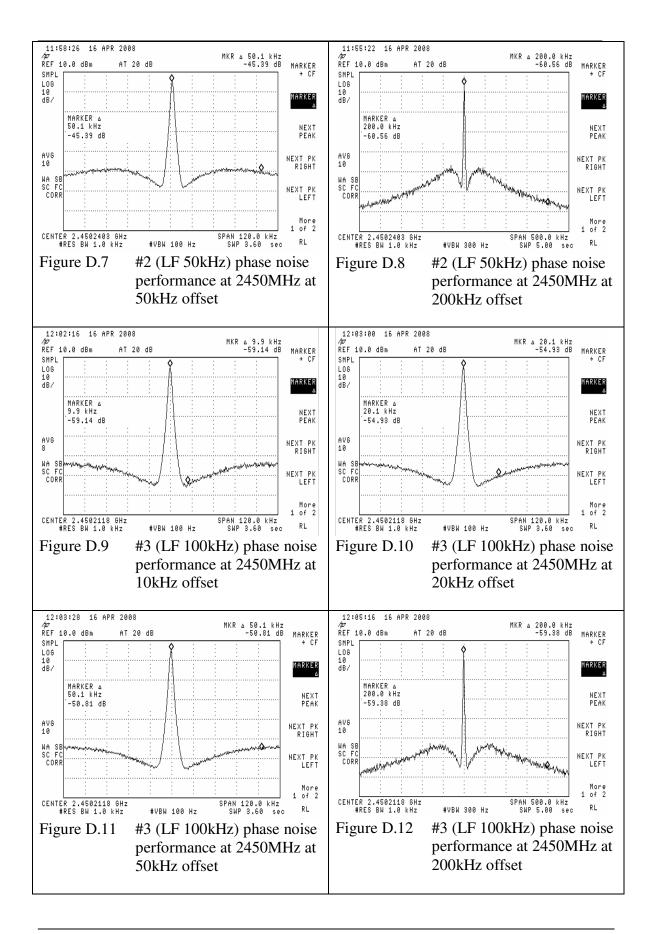

| Figure D.9:  | #3 (LF 100kHz) phase noise performance at 2450MHz at 10kHz offset   | 161 |

|--------------|---------------------------------------------------------------------|-----|

| Figure D.10: | #3 (LF 100kHz) phase noise performance at 2450MHz at 20kHz offset   | 161 |

| Figure D.11: | #3 (LF 100kHz) phase noise performance at 2450MHz at 50kHz offset   | 161 |

| Figure D.12: | #3 (LF 100kHz) phase noise performance at 2450MHz at 200kHz offset  | 161 |

| Figure D.13: | #4 (LF 200kHz) phase noise performance at 2450MHz at 10kHz offset   | 162 |

| Figure D.14: | #4 (LF 200kHz) phase noise performance at 2450MHz at 20kHz offset   | 162 |

| Figure D.15: | #4 (LF 200kHz) phase noise performance at 2450MHz at 50kHz offset.  | 162 |

| Figure D.16: | #4 (LF 200kHz) phase noise performance at 2450MHz at 200kHz offset. | 162 |

| Figure D.17: | #5 (LF 20kHz) phase noise performance at 2450MHz at 10kHz offset.   | 162 |

| Figure D.18: | #5 (LF 20kHz) phase noise performance at 2450MHz at 20kHz offset.   | 162 |

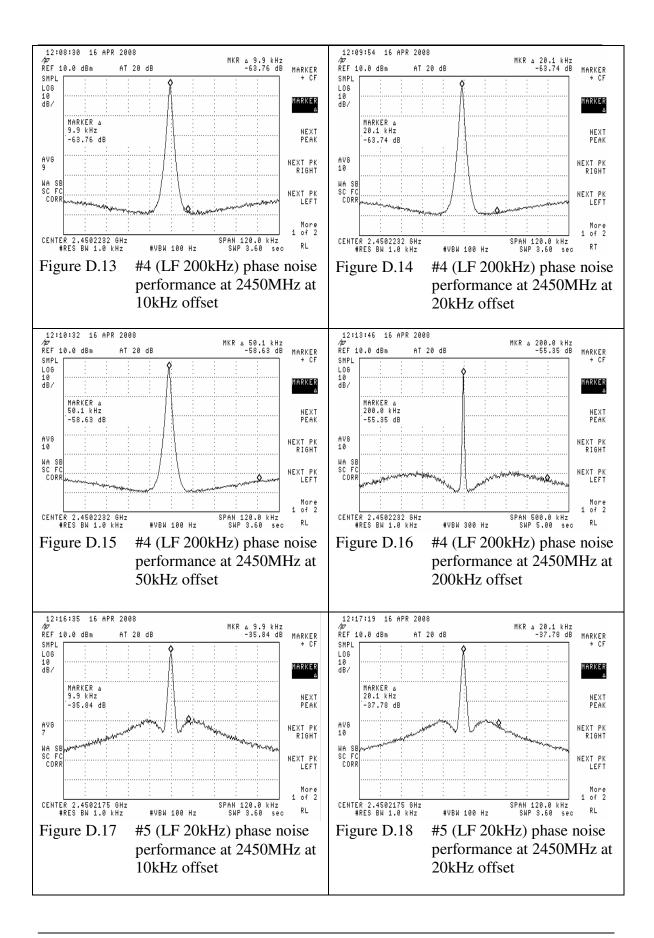

| Figure D.19: | #5 (LF 20kHz) phase noise performance at 2450MHz at 50kHz offset    | 163 |

| Figure D.20: | #5 (LF 20kHz) phase noise performance at 2450MHz at 200kHz offset   | 163 |

# **LIST OF TABLES**

| Table 3.1:  | Latch topologies                                                                                                    | 18  |

|-------------|---------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.1:  | Proposed design specification for frequency synthesizer                                                             | 29  |

| Table 4.2:  | PLL frequency synthesizer and operational mode register map                                                         | 30  |

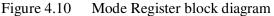

| Table 4.3:  | Setting for order of MASH                                                                                           | 39  |

| Table 4.4:  | Settings for output signal at "Counter_Out" pin                                                                     | 39  |

| Table 4.5:  | Charge Pump current control table                                                                                   | 40  |

| Table 4.6:  | Decoder control table                                                                                               | 44  |

| Table 4.7:  | Effect of prescaler moduli on minimum continuous divide ratio                                                       | 51  |

| Table 4.8:  | Moduli-control pins setting                                                                                         | 53  |

| Table 4.9:  | Control logic for divide-by-4/5/6                                                                                   | 56  |

| Table 4.10: | Power supply specification for PLL                                                                                  | 63  |

| Table 4.11: | Parameters of PLL counters, timer and registers                                                                     | 63  |

| Table 4.12: | Theoretical frequency range of frequency synthesizer                                                                | 64  |

| Table 4.13: | Specifications for timing diagram of frequency synthesizer settings                                                 | 64  |

| Table 5.1:  | Operating ranges of prescaler in 45 cases                                                                           | 90  |

| Table 5.2:  | Current consumptions of synthesizer building blocks at Typical conditions (TT, 3.3V, 25 <sup>o</sup> C, 2450.05MHz) | 92  |

| Table 5.3:  | Average current consumptions of synthesizer building blocks in 45 cases                                             | 93  |

| Table 5.4:  | Typical values of counters, registers and timer (crystal oscillator frequency= 25MHz)                               | 94  |

| Table 5.5:  | Period of pseudo-random series                                                                                      | 98  |

| Table 5.6:  | Pulse interval error of N-Counter output at various frequencies and MASH order (FD= 500)                            | 98  |

| Table 5.7:  | Test conditions for frequency synthesizer                                                                           | 109 |

| Table 5.8:  | Measurement equipments list                                         | 109 |

|-------------|---------------------------------------------------------------------|-----|

| Table 5.9:  | Simulation and measured operating frequency ranges                  | 110 |

| Table 5.10: | Frequency synthesizer reference spurs                               | 112 |

| Table 5.11: | Frequency synthesizer (Sample #5) fractional spurs                  | 114 |

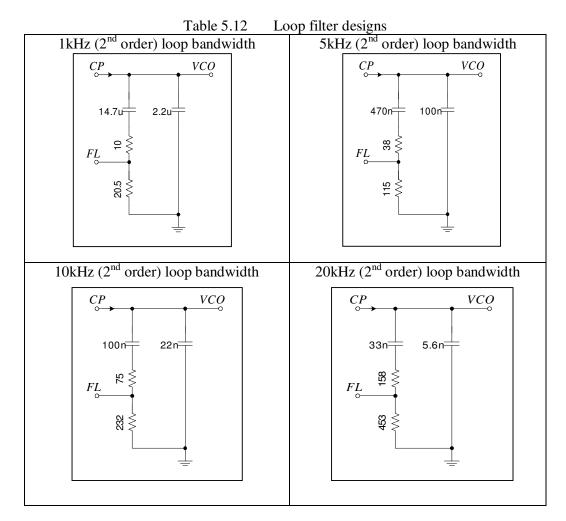

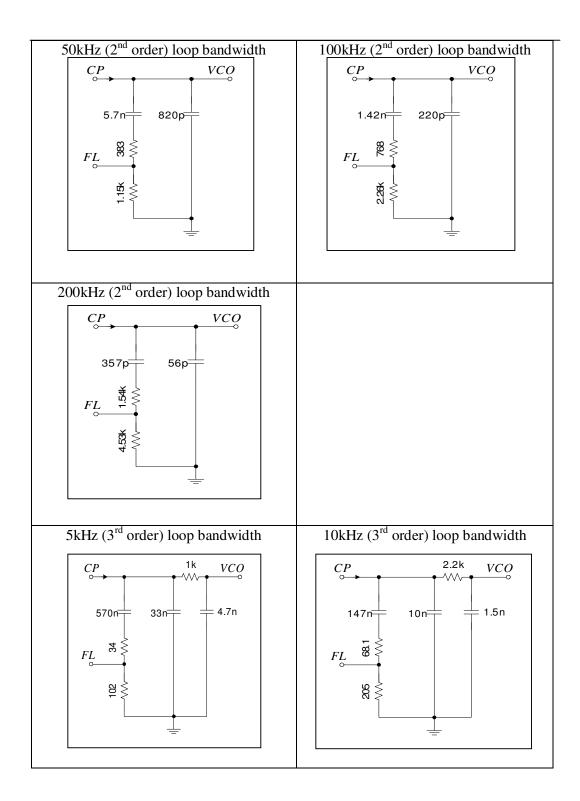

| Table 5.12: | Loop filter designs                                                 | 118 |

| Table 5.13: | Crystal oscillating frequency                                       | 120 |

| Table 5.14: | Effect of loop bandwidth on settling time                           | 121 |

| Table 5.15: | Effect of fastlock function on settling time                        | 122 |

| Table 6.1:  | Summary table for fractional-N frequency synthesizer performance    | 125 |

| Table 6.2:  | Performance comparison with a few reported frequency synthesizers   | 126 |

| Table C.1:  | Integer-N boundary spurious levels at 2450MHz                       | 150 |

| Table C.2:  | Integer-N boundary spurious levels at carrier frequency of 2451MHz. | 158 |

### **CHAPTER 1**

### **INTRODUCTION**

#### 1.1 Motivation

The wireless communication market has been expanding, resulting in increasingly stringent requirements for low cost, low power consumption, higher operating frequencies and miniaturization on circuits due to limited battery life and highly competitive market environment. Gallium Arsenide (GaAs) technology was used in the early 80's for implementation of circuits operating in the GHz bands. However, silicon wafers is still preferred for its lower manufacturing cost, and improved unity-gain bandwidth over the years via device scaling, new materials for interconnection, and additional metal layers. Recent publications have highlighted the increasing importance of CMOS RF circuits due to its compatibility with CMOS digital building block, enabling the implementation of full RF System-on-Chip (SoC) [1].

Frequency synthesizer is one of the critical building blocks in integrated transceivers. Conventional RF synthesizers are mostly integer-N synthesizers with output frequencies fixed at integer multiples of reference frequency. Fractional-N synthesizer is introduced because it allows deployment of higher reference frequency, contributing to higher loop bandwidth, better phase noise suppression, faster loop settling time and frequency flexibility. The only two blocks operating at full frequency in a synthesizer are the voltage-controlled oscillator (VCO) and prescaler. In current CMOS technology, it is easy to design high-frequency VCO but the prescaler remains as a major challenge in high-frequency synthesizer design [2]. High-speed multi-modulus prescaler are more intricate to be constructed as compared to fixed-division-ratio divider and dual-modulus prescaler because the additional logic gates might slow down the system.

Recent publications have demonstrated an increasing trend of proposing phaseswitching prescaler to rectify the lower operating speed inherited by conventional synchronous divider [2, 3, 4]. However, phase-switching technique has glitches and jitters due to phases mismatch issues which have to be addressed during implementation. Besides, the need for Multiplexer and switching control blocks increases the complexity of the circuit.

#### **1.2** Thesis Organization

In Chapter 2, the principles of frequency synthesizer and the functionality of PLL are discussed. Various frequency synthesizer architectures, together with their pros and cons, are examined.

In Chapter 3, the fundamentals of prescaler are reviewed. Various divide-by-2 topologies, and their advantages and disadvantages are discussed. Besides, the differences between synchronous and asynchronous dividers, dual-modulus and multi-modulus prescalers are highlighted.

In Chapter 4, the circuit overview and implementations of the proposed frequency synthesizer are presented, which includes counters, fast-lock timer, interface, mode register, PFD, charge pump, quad-modulus prescaler, loop filter, etc..

In Chapter 5, the testbench setups, simulation results and measurement results of the proposed design are presented.

In Chapter 6, a summary of the research has been outlined.

# **CHAPTER 2**

## **FREQUENCY SYNTHESIZER**

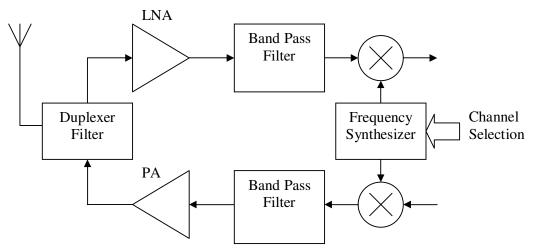

The output frequency of oscillator in an RF transceiver (transmitter-receiver) has to meet the stringent requirements of high precision and capability of varying in small, accurate steps. Hence, it is usually embedded in synthesizer which synthesizes clean, fast-switching and programmable frequencies from one or more fixed reference frequencies. Figure 2.1 shows the role of synthesizer in common transceiver architecture.

Figure 2.1 Role of frequency synthesizer in common transceiver

#### 2.1 Phase-Locked Loop (PLL)

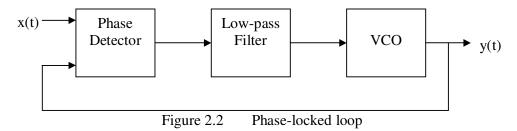

PLL is a feedback system operating on the excess phase of nominally periodic signals. Figure 2.2 shows a simple PLL comprising of phase detector (PD), low-pass filter (LPF), and voltage-controlled oscillator (VCO). The loop is locked when the phase difference,  $\Delta \Phi$ , is constant with time, resulting in equal input and output frequencies.

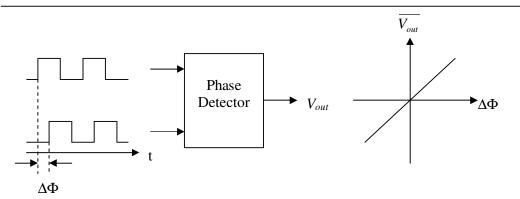

PD acts as "error amplifier" in the feedback loop by minimizing  $\Delta \Phi$  between x(t) and y(t). Under locked condition, it will produce an output with dc value that is proportional to  $\Delta \Phi$  (Figure 2.3),

$$v_{out} = K_{PD} * \Delta \Phi \tag{2.1}$$

where  $K_{PD}$  is the "gain" of the phase detector in V/rad. The LPF will pass the dc value of the PD output while suppressing the high-frequency components. The dc value is used to control the VCO such that it will oscillate at a frequency equals to the input frequency but with a phase difference of  $\Delta\Phi$  [5]. Hence, VCO can be characterized by

$$\omega_{out} = \omega_{FR} + K_{VCO} v_{out} \text{ and } y(t) = A_C \cos \left[ \left( \omega_{FR} * t \right) + K_{VCO} \int_{-\infty}^{t} v_{out}(t) dt \right], \text{ with the input-$$

output transfer function given by

$$\frac{\Phi_{out}}{V_{out}}(s) = \frac{K_{VCO}}{s}$$

(2.2)

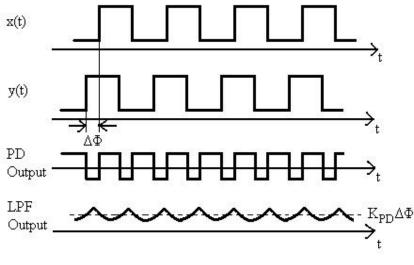

where  $\omega_{FR}$  is the "free-running" frequency and  $K_{VCO}$  is the "gain" of VCO in rad/s/V. Figure 2.4 shows an example of the signals at various points in a PLL with both input and output signals having same frequency but finite phase difference.

Figure 2.3 Characteristic of phase detector

Figure 2.4 Signals in a PLL

As shown in Figure 2.5, when a locked PLL experiences a small increase in frequency: the input frequency,  $\omega_{in}$ , will be greater than the output frequency,  $\omega_{out}$ , temporarily; x(t) will accumulate phase faster than y(t); PD will progressively generate wider pulses. Wider pulse contributes to higher dc value at the LPF output, resulting in an increase in VCO frequency. The increase in VCO frequency will reduce the difference between  $\omega_{in}$  and  $\omega_{out}$ , resulting in the reduction of the width of PD output pulses and the eventual settlement of dc value at a value which is slightly greater than its initial locked-phase value [6]. Hence, the loop is locked only after both "frequency acquisition" and "phase acquisition" are satisfied.

Figure 2.5 Response of PLL to a small increase in frequency

Although PLL has a nonlinear transient response, a linear approximation is used to estimate its performance as shown in Figure 2.6. The closed-loop transfer function, or jitter transfer function, is given by,

$$H(s) = \frac{\Phi_{out}(s)}{\Phi_{in}(s)} = \frac{K_{PD}K_{VCO}G_{LPF}(s)}{s + K_{PD}K_{VCO}G_{LPF}(s)}$$

(2.3)

If

$$G_{LPF}(s) = \frac{1}{1 + \frac{s}{\omega_{LPF}}}$$

and  $\omega_{LPF} = \frac{1}{RC}$ ,

$$H(s) = \frac{K_{PD}K_{VCO}}{\frac{s^2}{\omega_{LPF}} + s + K_{PD}K_{VCO}}$$

(2.4)

$$H(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(2.5)

where

$$\omega_n = \sqrt{\omega_{LPF} K} \tag{2.6}$$

$$\zeta = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K}}$$

(2.7)

where  $K_{PD}K_{VCO}$  is the "loop gain" in rad/sec,  $\zeta$  is the damping factor, and  $\omega_n$  is the natural frequency of the system. According to the equations,  $\omega_n$  depicts the gain-bandwidth product of the loop while  $\zeta$  shows the degree of loop stability.

rigure 2.0 Effical approximation of ri

#### 2.1.1 Frequency Multiplication

The output frequency of PLL is usually required to be multiple of input frequency, resulting in the need of a frequency divider to divide down the output signal in the feedback loop (Figure 2.7). In the process of frequency multiplication, input phase noise is also being amplified.

Figure 2.7 Frequency multiplication of PLL

#### 2.2 Frequency Synthesizer Architectures

The output frequencies,  $f_{out}$ , of frequency synthesizers vary in steps of multiplications of channel spacing:  $f_{out} = f_0 + kf_{ch}$ , where  $f_0$  is the lower limit of frequency, k is the number of channels and  $f_{ch}$  is the channel spacing. The use of PLL is often required due to the requirement for high precision in the definition of  $f_0$  and  $f_{ch}$ . Some of the frequency synthesizer architectures will be discussed in the following sections.

#### 2.2.1 Direct Digital Frequency Synthesizer

A Direct Digital Frequency Synthesizer (DDFS) generates signal in digital domain and uses a digital-to-analog converter (DAC) to convert the signal into waveform in analog domain. The counter counts in unity, increment steps until maximum count before it restarts from zero again, generating a periodic, saw-tooth output waveform. The ROM will convert the number generated by the counter to a digital amplitude value based on the lookup table stored in it. Then, the values are converted to analog waveform by the DAC, with high-frequency components being filtered-off by the LPF [7, 8, 9].

Figure 2.8 shows an example of DDFS with an accumulator. The output frequency is given by

$$f_{out} = P \frac{f_{CK}}{2^M} \tag{2.8}$$

where  $f_{CK}$  is the clock frequency, P is the programmable step and M is the register bit number.

DDFS has the following advantages: low phase noise due to avoidance of use of analog VCO; fine frequency increments but at the expense of complexity; faster channel switching capability as compared to PLL; continuous-phase channel switching; direct modulation of output signal in digital domain. However, DDFS has the following drawbacks: speed limitation due to highest-frequency limitation according to Nyquist's sampling theorem [5, 10, 11, 12]; spectral purity is limited by the speed, resolution and power dissipation of DAC.

#### 2.2.2 Integer-N Frequency Synthesizer

The integer-N frequency synthesizer is one of the most commonly used architecture. As shown in Figure 2.9, the output frequency is given by  $f_{out} = N * f_{REF} = f_0 + kf_{ch}$ , where  $N = N_L + k$ ; k=0, 1, ..., P. It shows that input reference frequency and channel spacing must be the same.

Figure 2.9 An integer-N frequency synthesizer

A low  $f_{REF}$ , which requires a narrow loop bandwidth to block the signal components at  $f_{REF}$  and its harmonics, is desired for small channel spacing. Settling time will increase

and VCO noise suppression capability will decrease as a result of narrow loop bandwidth. A divider with larger division value is needed for low  $f_{REF}$  but this will result in the increase of VCO in-band phase noise. Hence, this topology is not suitable for systems which require low phase noise, fast switching time and small frequency spacing [13].

A prescaler can be added when the VCO output frequency is higher than the programmable divider maximum clock frequency, as shown in Figure 2.10. Under locked condition,  $f_{out} = P * N_P * f_{REF}$ , where P is the programmable frequency divider division ratio,  $N_P$  is the prescaler division ratio, and  $N_P * f_{REF}$  is the frequency channel spacing. The drawbacks of this topology are larger frequency channel spacing, smaller reference frequency, longer lock-on time, and sidebands.

Figure 2.10 Frequency synthesizer with single modulus prescaler

Dual-modulus prescaler is able to solve the frequency resolution problem by providing two division ratios, i.e.  $N_P$  and  $(N_P+1)$ , with the control signal from additional logic circuit. Hence, a high-frequency programmable divider can be formed by combining a dual-modulus prescaler with two counters, as shown in Figure 2.11.

Figure 2.11 High-frequency programmable divider

The prescaler will first divide by  $(N_P+I)$  and the swallow counter will start counting till it overflows at S. Then, the overflow bit will set the division ratio of prescaler to  $N_P$  while the program counter will start counting till it overflows at P. Both the Scounter and P-counter will be reset and the division cycle repeats again. The overall division is given by

$$N = [(N_{P} + 1)S] + [N_{P}(P - S)] = PN_{P} + S$$

(2.9)

where P must be larger than S for proper reset operation by program counter, and

$$N_{\min} = (P_{\min}N_P) + S_{\min} = ((N_P - 1)N_P) + 0 = (N_P^2 - N_P)$$

(2.10)

$$N_{\max} = (P_{\max}N_P) + S_{\max} \tag{2.11}$$

This topology has the following drawbacks: occurrence of reference spur; limited loop bandwidth; higher close-in phase noise at the output.

#### 2.2.3 Fractional-N Frequency Synthesizer

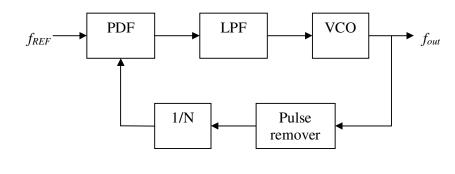

As shown in Figure 2.12 is two fractional-N frequency synthesizer topologies. The conventional design as shown in Figure 2.12(a) includes a pulse-remover which removes one output pulse upon activation. The average output frequency is given by

$$f_{out} = f_{ref} + \frac{1}{T_p}$$

(2.12)

where Tp is the period when pulse-remove command is activated. Figure 2.12(b) shows an alternative design using dual-modulus prescaler, with the phase accumulator being clocked at reference frequency. Assuming a word of length  $L_{div}$  represents a division-ratio setting at each clock cycle, the dual-modulus prescaler will divide by N while the phase accumulator accumulates its output. Once the phase-accumulator-output overflows, the prescaler will divide by (N+1). For an accumulator of length  $L_{acc}$ , the accumulator will overflow  $L_{div}$  times per cycle. Hence, the average division ratio is given by

$$N_{ave} = \frac{N(L_{acc} - L_{div}) + (N+1)L_{div}}{L_{acc}} = N + \frac{L_{div}}{L_{acc}}$$

(2.13)

$$f_{out} = f_{ref} \left( N + \frac{L_{div}}{L_{acc}} \right)$$

(2.14)

(a)

(b) Figure 2.12 Fractional-N synthesizer with: (a) pulse remover, (b) dual-modulus prescaler

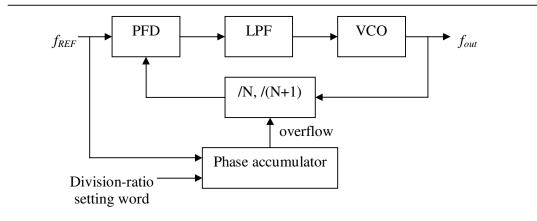

The fractional-N frequency synthesizer allows for higher PLL loop bandwidths but the main drawback is the appearance of fractional spurs. Under closed-loop condition, with VCO output of  $(N + \alpha) f_{REF}$  and periodic, ramp LPF output waveform of period  $1/(\alpha f_{REF})$ , sidebands will appear at  $\alpha f_{REF}$ ,  $2\alpha f_{REF}$ , etc. with respect to centre frequency. Fractional compensation can be implemented to suppress the fractional spurs by injecting another current pulse series of similar width but opposite direction to the low-pass filter. However, the major limitation is the inaccuracy due to mismatches in the compensation current. Alternatively,  $\Sigma - \Delta$  modulation method (Figure 2.13) can be used to average out the division factor and convert the fractional spurs to random noise before shaping the resultant noise spectrum and push it beyond the loop bandwidth [13-18].

Figure 2.13 Noise shaping using  $\Sigma - \Delta$  modulator

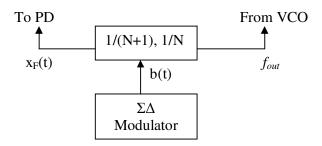

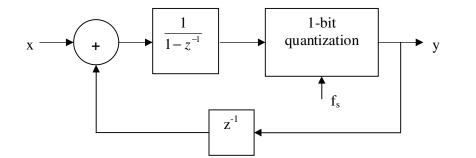

Figure 2.14 First-order  $\sum -\Delta$  modulator

As shown in Figure 2.14 is a first-order  $\sum -\Delta$  modulator. Input signal representing the fractional value is input to the integrator before passing through the quantizer, which is operating at higher sampling frequency with respect to the Nyquist frequency. The transfer function of the integrator is given by

$$H(z) = \frac{1}{1 - z^{-1}}$$

(2.15)

The output of the first-order  $\sum -\Delta$  modulator can be expressed as

$$y(z) = \left(\frac{H(z)}{1+z^{-1}H(z)}\right) x(z) + \left(\frac{1}{1+z^{-1}H(z)}\right) q(z)$$

(2.16)

$$= x(z) + (1 - z^{-1})q(z)$$

(2.17)

$$= x(z) + H_{noise}^{-1}(z)q(z)$$

(2.18)

where x(z) is the input signal and q(z) is the quantization noise.  $H_{noise}$ , which is a high-frequency component, can be filtered out by passing the signal via a low-pass filter.

A dithering enabled  $\Sigma$ - $\Delta$  modulator will further reduce the unwanted fractional spurs. Dithering is a method of introducing random noise to the  $\Sigma$ - $\Delta$  modulator. One technique involves one LSB dithering at the DC input but at the compromise of synthesizer resolution because any changes in the DC input will directly affect the output frequency. Another technique involves initializing the input word of first stage accumulator to a value which is independent to the long term average of the  $\Sigma$ - $\Delta$  modulator [19].

### 2.2.4 Delay-Locked Loop (DLL) Frequency Synthesizer

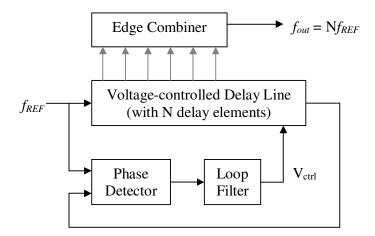

Figure 2.15 shows a DLL frequency synthesizer with a voltage controlled delay line in-place of the voltage controlled oscillator [20]. Under "locked" condition, the difference between input and output of delay line is one reference clock cycle,  $T_{REF}$ . Hence, a synthesizer with N-delay stages will experience a delay of  $T_{REF}/N$  for each stage. Each transition in the delay-line output will trigger a transition at the edge combiner, causing the latter to produce an output frequency of  $Nf_{REF}$ .

Figure 2.15 Delay-locked loop frequency synthesizer

This topology has the following advantages: jitter will not be carried forward to successive cycles; lower phase noise for adjacent frequencies; it does not require high Q. However, it is not suitable for applications that entail frequency tuning because of the fixed output frequency, which is determined by the number of delay stages.

# **CHAPTER 3**

# PRESCALER

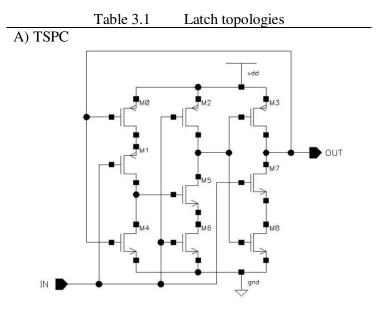

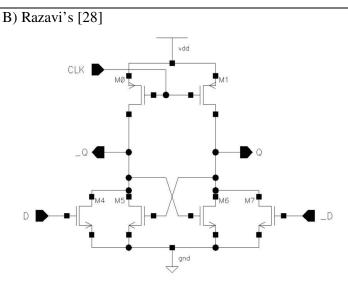

Due to the inherent limitation to switching speed of CMOS digital cells [21], prescaler is needed to divide down the VCO frequency before transmitting the signal to programmable divider in high-frequency PLL-based synthesizer system [22]. Despite the current advancement of CMOS process, the prescaler remains as a major challenge in high-frequency design due to the trade-off between functionality and operating speed [2, 3, 23, 24]. The various divider topologies and common implementations of prescaler will be discussed in the following sections. Usually, the first few divider blocks will utilize fast-switching, high-frequency divider topologies such as current mode logic (CML) (also called source-coupled logic (SCL)) [25] and injection-locked [26, 27]. Subsequent divider blocks, which operate at lower frequency, can utilize simpler topologies such as True Single-Phase Clock (TSPC) to minimize overall power consumption.

## 3.1 Divide-by-2 Topologies

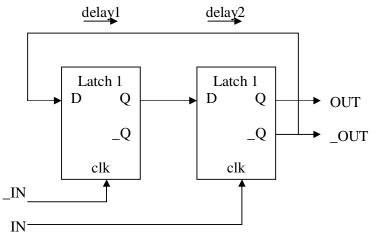

Figure 3.1 shows a divide-by-2 structure (also called Johnson Counter) that is formed using two cascaded latches. The maximum operating speed is determined by the propagation delay of latches (*delay*<sub>1</sub>, *delay*<sub>2</sub>), i.e. the time taken for the input signal of each latch to propagate to its respective output, and the setup time of latches ( $T_s$ )

$$\frac{T_{in}}{2} \langle delay_{1,2} + T_s \rangle$$

(3.1)

There are various ways of implementing the latch, depending on the speed and power consumption requirements of the system, as shown in Table 3.1.

Figure 3.1 Divide-by-2 circuit

- Advantages:

- i) moderately fast

- ii) compact

- iii) without static power dissipation

- iv) only requires single-ended clock input

Drawbacks:

- i) slower speed due to stacked PMOS

- ii) signal passes through three gates per cycle

- iii) requires full-swing input signal

Advantages:

i) fast due to absence of stacked PMOS

ii) signal passes through two gates per cycle

Drawbacks:

- i) presence of static power dissipation

- ii) requires full-swing, differential input signals

C) Wang's [29]

Advantages:

- i) fast due to absence of stacked PMOS

- ii) signal passes through two gates per cycle

Drawbacks:

- i) presence of static power dissipation

- ii) requires full-swing, differential input signals

Advantages:

- i) very fast due to absence of PMOS

- ii) signal passes through two gates per cycle

- iii) requires smaller input swing

## Drawbacks:

- i) presence of static power dissipation

- ii) requires differential input signals and biasing

- iii) occupies larger chip area

# 3.2 Synchronous and Asynchronous Dividers

A synchronous divider uses a single clock signal to feed all the clock inputs simultaneously, as shown in Figure 3.2. This approach introduces lower jitter but higher power consumption due to high frequency operation of all registers, and higher loading on the clock to drive all registers simultaneously. Figure 3.3 shows an asynchronous divider with each divide-by-2 stage being clock by the output of the preceding stage. Hence, this approach introduces lower power consumption with subsequent stages consume lesser power while operating at lower frequency, and lesser loading on the clock which only needs to drive the first stage but larger jitter.

Figure 3.2 Synchronous divider

Figure 3.3 Asynchronous divider

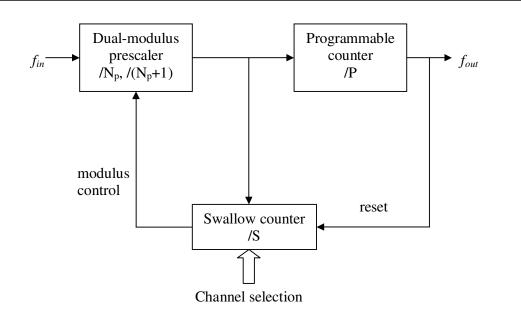

## 3.3 Dual-modulus Prescaler

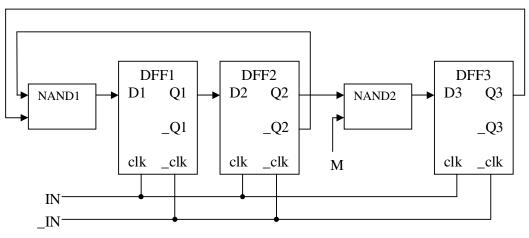

A dual-modulus prescaler provides two division ratios, N and N+1, e.g. 16/17, 32/33, 64/65, 128/129, etc. [4]. Figure 3.4 shows a traditional synchronous divide-by-4/5 design. A modulus control signal, M, is used to control the division ratio to divide by either N or N+1. As shown, when M='0', D1 and D2 will form a divide-by-4 with  $q_3$  remaining at 'High' and NAND1 behaving like a NOT gate. When M='1', NAND2 will behave like a NOT gate and NAND1 will output '0' when both  $q_2$  and  $q_3$  are at 'High'. Hence,  $q_1$  will change from high-to-low after 3 cycles of  $f_{clk}$ , forming a divide-by-5.

Figure 3.4 Synchronous divide-by-4/5 circuit

## 3.4 Multi-modulus Prescaler

A multi-modulus prescaler provides multiple division ratios that are selected via external control signals, which extend the functional frequency range of the system [2, 30].

### 3.4.1 Ring Prescaler

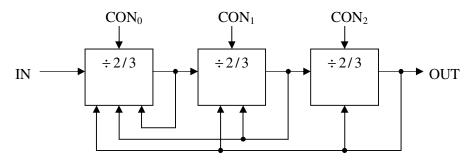

A series of divide-by-2/3 dividers can be cascaded to form a divider with division ratios ranging from  $2^{n}$  to  $2^{n+1}$ -1 [31, 32]. Figure 3.5 shows a cascaded divide-by-2/3 design [33, 34]. The asynchronous topology allows the divider to function at a higher speed with lower power consumption, but at the expense of accumulation of jitters.

Figure 3.5 A cascaded divide-by-2/3 programmable prescaler

### 3.4.2 Phase-switching Prescaler

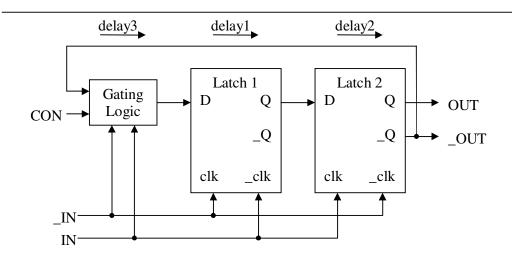

Referring to Figure 3.6, the maximum operating speed of a divide-by-2/3 structure is slower than basic divide-by-2 (Eqn. 3.1) due to the presence of gating logics

$$\frac{T_{in}}{2} \langle delay_{1,2} + delay_3 + T_s$$

(3.2)

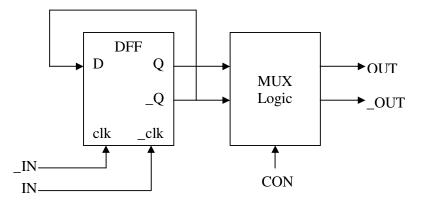

Hence, phase-switching topology is utilized to realize a divide-by-2/3 by multiplexing the outputs of a divide-by-2 circuit (Figure 3.7). The maximum operating speed of this structure is equivalent to the speed of a basic divide-by-2, with the multiplexer operating at half of the input frequency. However, conventional phase-switching prescaler that switches in "increasing cycle" (or anticlockwise) manner between output phases may suffer from glitches [2, 3], and special attention is needed to ensure that there is no mismatch in phases to avoid jitter.

Figure 3.6 A divide-by-2/3 core circuit

Figure 3.7 A divide-by-2/3 using phase-switching

Prescaler is required in high-frequency PLL system to overcome the issue of process limitations. Higher modulus prescaler is desired to achieve larger N-value range, especially the minimum N value [24]. The choice of prescaler architecture to be implemented in a system will depend on the system's requirements, such as power consumption, phase noise, spurious level, etc..

Although phase-switching topology seems to be the most preferred architecture recommended by literatures, it may face the issue of unwanted glitches during phase switching [23, 24]. Literatures have suggested various ways to remove the glitches [2-4, 35]. A re-timer circuit is suggested by [35] to synchronize the input signals of phase-switching control block at the expense of circuit complexity, power consumption and die size. In [36], glitches are removed by reversing the switching sequence but the switching control logic may not be sufficiently fast to detect the switching from one phase to another. In [24], "time borrowing" technique is suggested to overcome the switch-control-logic speed problem at the expense of power consumption and additional pulse-generator block. In [2, 3], 8 output phases are used to produce desired output signals and to reduce the error window but with increased circuit complexity. Unfortunately, all these glitch-removing techniques either increase circuit power consumption and/or reduce maximum operating frequency.

Other topologies possess respective shortcomings such as large power consumption, lower maximum operating frequency, narrow locking range, large die size, etc. [2, 3, 26]. In [37], injection-locked technique is proposed for very high frequency operation at the expense of very narrow operating range. In [38, 39], TSPC is used but this topology has low input sensitivity due to the need for rail-to-rail input signal swing and high switching noise. In [40], n divide-by-2/3 blocks are cascaded to form multimodulus prescaler. Although the cascaded structure provides option for power optimization and reusability, special care is required in the design of divider because reduction in time window between arrival of input feedback signal and successive input clock edge will limit the maximum operating frequency.

Hence, high-speed, low-power and robust prescaler design remains as a challenge in high-frequency synthesizer design.

# **CHAPTER 4**

# **CIRCUIT DESIGN AND IMPLEMENTATION**

As discussed in Chapter 2, fractional-N frequency synthesizer offers an improvement on the phase noise by  $20 \times \log(F)$ , theoretically, while remaining competitive in terms of current consumption, circuit complexity, and die size. The major concern with this implementation is the spurious signal at VCO, caused by the phase perturbation during divide-ratios switching. Delta-sigma modulation technique is a widely implemented solution to address this problem. If the divide-ratio remains unchanged with increasing switching frequency over F cycles, phase noise will be pushed to higher frequencies before being filtered out by loop filter. Hence, the remaining noise will only exist at low frequency, resulting in an overall improvement of phase noise performance. Instead of direct phase-noise cancellation, this noise-shaping technique utilizes switching-pattern modification to suppress the low frequency spectral caused by divide-ratio switching.

# 4.1 Fractional-N Frequency Synthesizer Circuit Overview, Architecture, and Layout

A high-frequency, fast-locking fractional-N PLL frequency synthesizer that utilizes quad-modulus prescaler has been designed. In this design, fast-lock timer has been incorporated to shorten the frequency locking time, Multi-stAge noise SHaping (MASH) technique is implemented to reduce the phase noise and spurs, and quadmodulus prescaler is employed to extend the system's functional frequency range. Hence, the proposed design offers technology robustness, versatility, fast locking ability, low noise contribution, high integration competency, multi-modulus flexibility, and ease of future expansion and deployment activities.

The design was realized using Chartered Semiconductor 0.35µm, 2P4M, CMOS technology with MIM capacitor option. The system and circuit levels' analyses, designs and simulations were carried out in Cadence IC5.0.33 under Redhat 8.0 and Cadence IC5.1.41 under Red Hat Enterprise Linux WS release 4 (Nahant Update 4). All the basic digital cells are Synopsys standard cells.

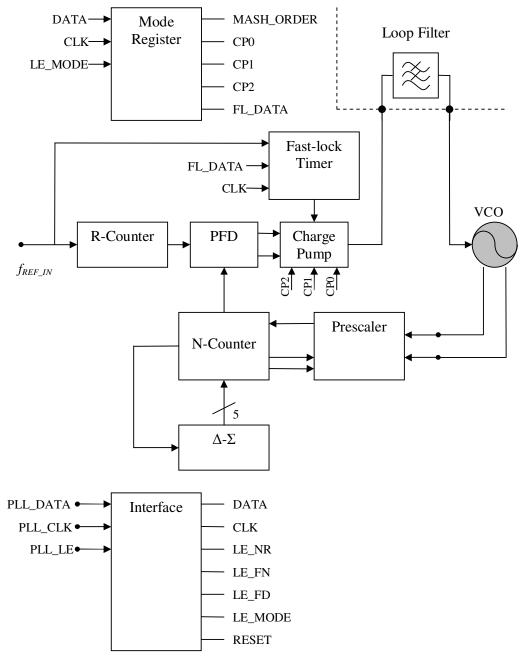

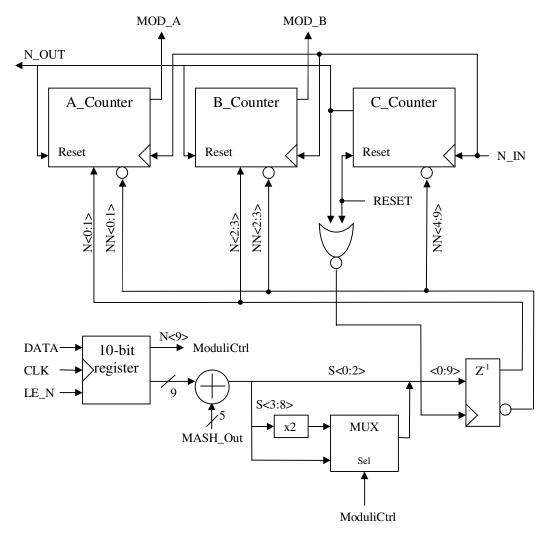

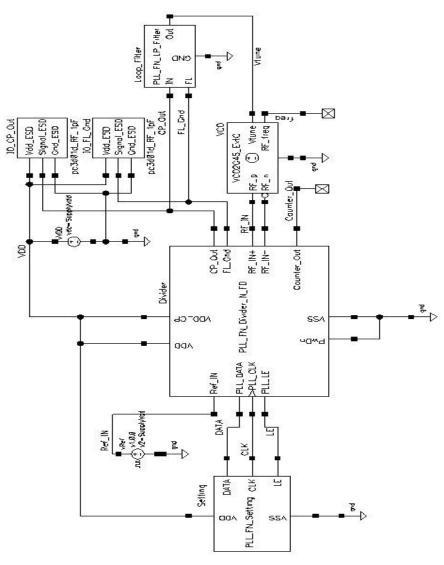

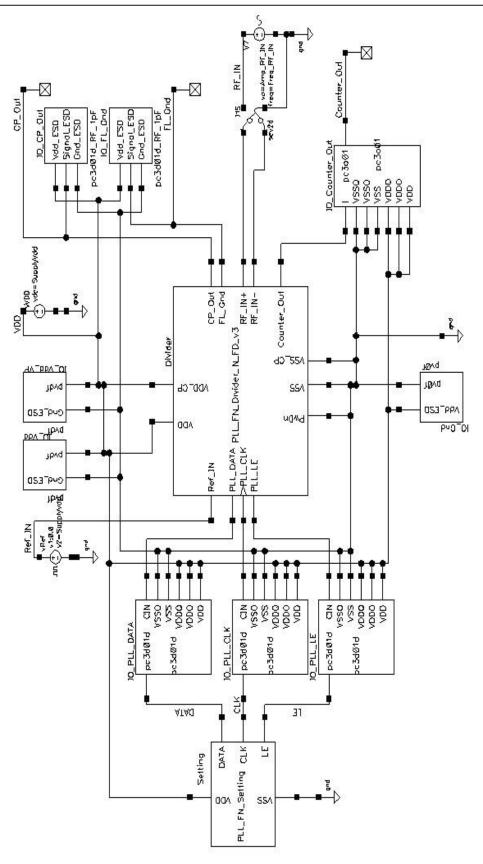

Figure 4.1 shows the topology of the fractional-N frequency synthesizer design. The design consists of the following building blocks: R-Counter, N-Counter, Fast-lock Timer, MASH, Interface, Mode Register, MUX\_Output, Phase-Frequency Detector (PFD), Charge Pump, Fast-lock Control Switch, Quad-modulus Prescaler, and Loop Filter. R-Counter will divide down the input reference frequency. Then, PFD will compare this divided reference signal with the divided Local Oscillator (LO) signal and generate two outputs which are not complementary. The PFD outputs are used to drive charge pump that provides several gains to cater for the variation in VCO gain. The variable charge pump gain ensures that the PLL loop gain is stable. Loop filter is implemented with fast-lock function to shorten the locking time significantly. Subsequently, the filtered signal is used to control the VCO frequency.

Then, the VCO differential output signals are divided by quad-modulus prescaler before transmitting to N-Counter because digital circuit usually has lower functional frequency. N-Counter, which supports 910MHz and 2450MHz operations, provides whole-number division to the signal while the 3<sup>rd</sup>/4<sup>th</sup> order MASH produces fractional output frequency. The divided signal is then compared with the divided reference frequency. Hence, frequency locking is accomplished through these procedures. Table 4.1 lists the proposed design specification for the frequency synthesizer design.

Figure 4.1 Fractional-N frequency synthesizer block diagram

| Table 4.1Proposed desides | ign speci: | fication for | · frequency | y synthesizer |

|---------------------------|------------|--------------|-------------|---------------|

| Parameter                 | Unit       | Min          | Тур         | Max           |

|                           |            |              |             |               |

| Operating frequency       | MHz        | 2400.0       | 2450.0      | 2500.0        |

|                           |            |              |             |               |

| Operating voltage         | V          | 3.0          | 3.3         | 3.6           |

|                           |            |              |             |               |

| Current consumption       | mA         |              | <25.0       |               |

|                           |            |              |             |               |

| Operating temperature     | $^{0}C$    | -40.0        |             | +85.0         |

|                           | 0          |              |             |               |

| Simulation temperature    | $^{0}C$    | -40.0        | +27.0       | +90.0         |

|                           |            |              |             |               |

| Reference frequency       | MHz        |              | 25.0        |               |

|                           |            |              |             |               |

| Channel spacing           | kHz        |              | 50.0        |               |

|                           |            |              |             |               |

| Modulus P                 |            | 1            | 6/17/20/21  |               |

|                           |            |              |             |               |

## 4.1.1 Counters

There are three counters, namely R-Counter, N-Counter and Fast-lock Timer. Both the R-Counter and Fast-lock Timer have same counting units, which are implemented using complete synchronous logic design for easy expansion to higher number of bits, but different control units. There are hardware handshaking signals between the counting unit and control unit, and there is no process-related delay cell involved so as to ease the deployment of the counters to other process. N-counter consists of A-Counter, B-Counter and C-Counter. It is capable of supporting 910MHz and 2450MHz operations, with its initial value varying according to the output of MASH.

Table 4.2 shows the register map for the six registers in the frequency synthesizer, namely: R-Counter Register, N-Counter Register, FN Register, FD Register, Fast-lock Timer Register, and Operational Mode Register.

| Ta                   | able 4 | 4.2 | Р   | PLL frequency synthesizer and operational mode register map |     |     |     |     |     |     |     |               |    |           |           |

|----------------------|--------|-----|-----|-------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|---------------|----|-----------|-----------|

| Counter/<br>Register | C0     | C1  | 2   | 3                                                           | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11            | 12 | 13/<br>18 | 14/<br>19 |

| RN                   | 0      | 0   | R0  | R1                                                          | R2  | R3  | N0  | N1  | N2  | N3  | N4  | N5            | N6 | N7        | N8        |

| FN                   | 1      | 0   | FN0 | FN1                                                         | FN2 | FN3 | FN4 | FN5 | FN6 | FN7 | FN8 | X(Don't Care) |    |           |           |

| FD                   | 0      | 1   | FD0 | FD1                                                         | FD2 | FD3 | FD4 | FD5 | FD6 | FD7 | FD8 | X(Don't Care) |    | e)        |           |

| MODE                 | 1      | 1   | MO  | CO0                                                         | CO1 | CP0 | CP1 | CP2 | FLE | FL0 | FL2 | FL3           |    | FL10      | FL11      |

The R-Counter Register has 4 bits, represented by R0 (least significant bit, LSB) to R3 (most significant bit, R3); N-Counter Register has 9 bits, represented by N0 (LSB) to N8 (MSB); FN Register has 9 bits, represented by FN0 (LSB) to FN8 (MSB); FD Register has 9 bits, represented by FD0 (LSB) to FD8 (MSB); Operational Mode Register has 7 bits, represented by M0, CO0, CO1, CP0, CP1, CP2 and FLE.

### **R-Counter**

R-Counter divides down the frequency of input reference signal, and PFD will compare the divided reference signal to the divided LO signal. Assuming the R-Counter input signal has frequency  $f_{REF_{-IN}}$ , R-Counter output signal has frequency  $f_{REF}$ , and R-Counter has value R,

$$f_{REF} = \frac{f_{REF\_IN}}{R} \tag{4.1}$$

If the built-in crystal PAD and external crystal are the reference source,  $f_{REF_{-IN}}$  is the oscillating frequency of the crystal.

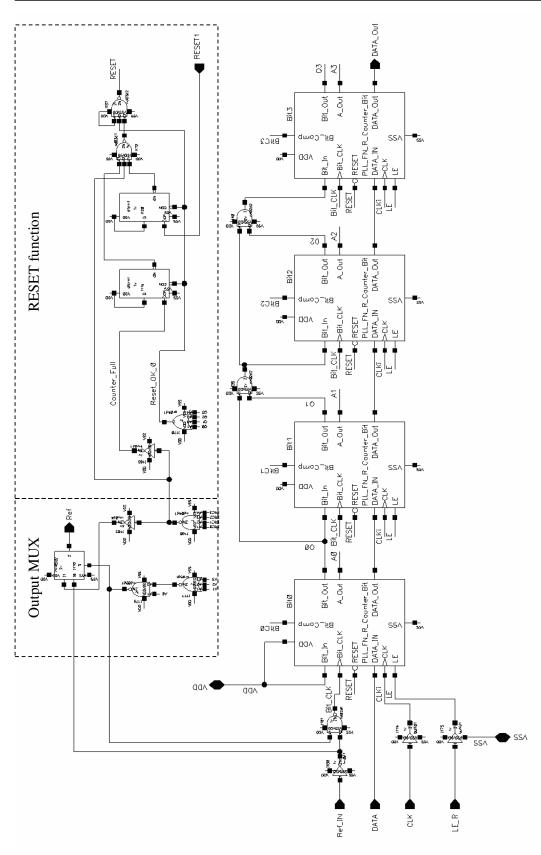

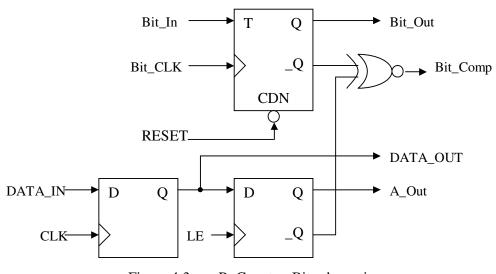

Figure 4.3 R\_Counter\_Bit schematic

Figure 4.2 shows the block diagram of reference counter (i.e. R\_Counter), which consists of 4-bit shift register, 4-bit synchronous counter, comparator and reset function when counter is full. Each bit counter (i.e. R\_Counter\_Bit) is implemented as shown in Figure 4.3. After the data (i.e. R0-R3) from the register has been latched onto R-Counter, bit-comparator will start comparing each data bit with the respective counter's output bit. The synchronous counter will start counting from "0000" until all DATA\_OUT=Bit\_Out, and  $f_{REF_IN}$  is being divided by R during the process and output as  $f_{REF}$ . Then, RESET function will send a "0" to all bit counters to clear the counter back to "0000". Once the reset is accomplished, signal will be fed back to the reset logic. RESET will send a "1" to all bit counters and R-Counter is ready for the next counting cycle.

### **N-Counter**

Figure 4.4 shows the implementation of N-Counter, which is formed by A-Counter, B-Counter and C-Counter. Assuming the minimum division ratio of prescaler is P and it is a multiple of 4, the counters must satisfy the following conditions:

$$C = N \operatorname{div} P, \ A = N \operatorname{mod} P \tag{4.2}$$

$$B = (N - A - P * C)/4 \tag{4.3}$$

$$N = (P * C) + (4 * B) + A \tag{4.4}$$

with  $C \ge \max\{A, B\}$ , A < 4 and B < P/4.

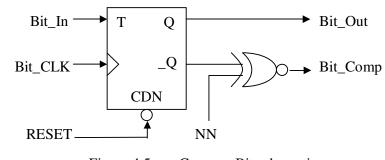

Both A-Counter and B-Counter are 2-bit synchronous counters, and C-Counter is a 6bit synchronous counter. Each counter bit is implemented as shown in Figure 4.5.

Figure 4.4 N\_Counter block diagram

Figure 4.5 Counter\_Bit schematic

The pseudo-random number from MASH is added to the N-Counter register value, and set as the initial value for N-Counter. N-Counter will divide down the Prescaler output frequency before feeding the signal back to MASH and PFD, and generate the Prescaler division-ratio control signals (MOD\_A and MOD\_B).

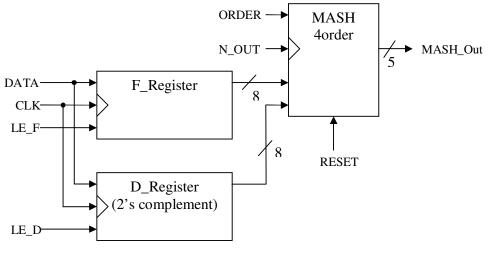

#### 4.1.2 MASH

MASH generates pseudo-random numbers based on the numerator and denominator value set by FN Register and FD Register respectively, and can function as a third-order or forth-order modulator. The generated pseudo-random number is added to the value indicated by N-Counter Register, and set as initial value of N-Counter. N-Counter divides down the frequency of LO signal, and PFD will compare the divided LO signal to the divided reference signal. Assuming LO signal has frequency  $f_{LO}$ , and prescaler has modulus value P,

$$f_{LO} = P * \left( N + \frac{FN}{FD} \right) * f_{REF}$$

(4.5)

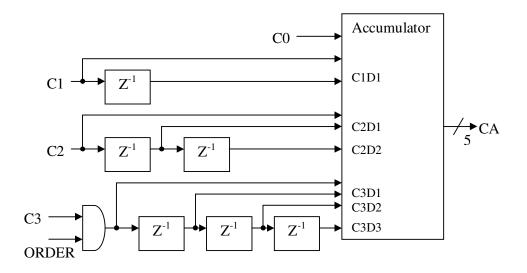

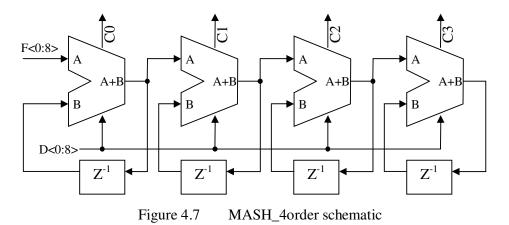

where N is the value of N-Counter Register, FN is the value of FN Register, and FD is the value of FD Register. Figure 4.6 shows the block diagram of MASH, and Figure  $\overline{4.7}$  shows the implementation of four order MASH with option of choosing either  $3^{rd}$  or  $4^{th}$  order via the "ORDER"pin.

MASH block diagram

After the DATA is latched to the outputs of F-register (denotes as FO) and D-register (denotes as DO) respectively, at the rising edge of N\_OUT pulse (i.e. the clock for MASH\_4order)

For i = 0, 1, 2, 3,

$$Sum(i) = pSum(i-1) + pSum(i)$$

(4.6)

If  $Sum(i) \ge DO$ ,

$$Ci = 1; \ pSum(i) = Sum(i) - DO \tag{4.7}$$

Else

$$Ci = 0; \ pSum(i) = Sum(i) \tag{4.8}$$

If ORDER = 3,

$$MO3 = C0 + C1 - C1D1 + C2 - (2 * C2D1) + C2D2$$

(4.9)

If ORDER = 4,

$$MO4 = MO3 + C3 - (3 * C3D1) + (3 * C3D2) - C3D3$$

(4.10)

where pSum(-1) = FO,  $MO3 = MASH_Out 3^{rd}$  order,  $MO4 = MASH_Out 4^{th}$  order.

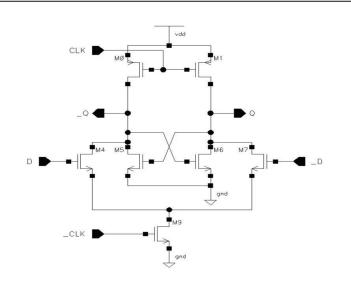

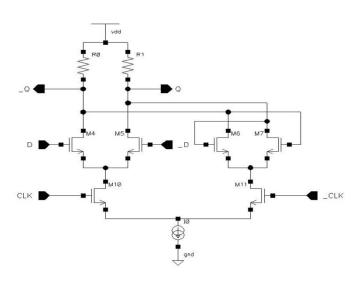

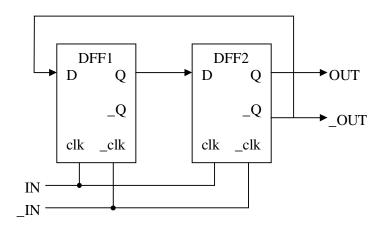

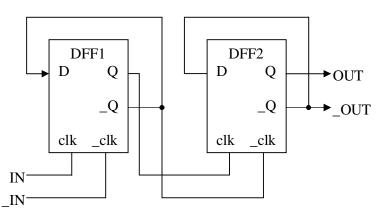

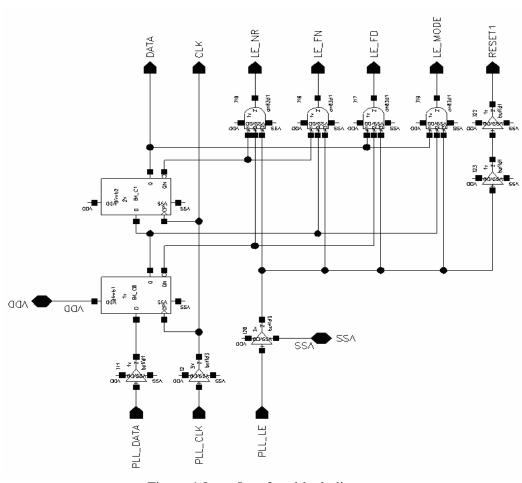

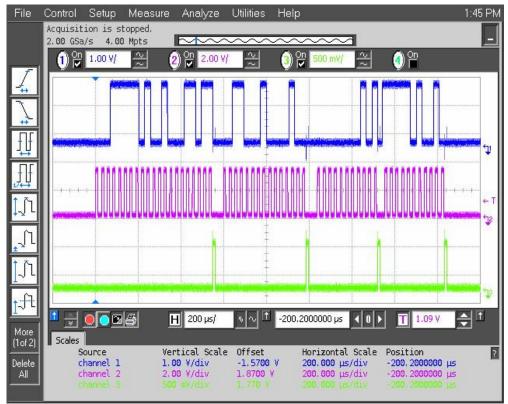

## 4.1.3 Interface