# **Investigation of the Scalability Limitations**

# of Phase Change Random Access Memory

## Wei Xiaoqian

(B. S. Huazhong University of Science and Technology, China 2003)

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2008

## Acknowledgements

First of all, I would like to thank my supervisor, Professor Chong Tow Chong, for his continual encouragement and support throughout my postgraduate studies in Data Storage Institute (DSI), Singapore. I have enjoyed every meeting and discussion with him and also benefited from his determined and enthusiastic personality.

I am also grateful to my Research Advisor, Dr Shi Luping for his tremendous support and invaluable advice in the completion of my post-graduate studies. His diligence and enthusiasm towards scientific pursuit has left a very deep impression on me, and he has taught me invaluable lessons on research in particular, and on life in general.

My thanks also go to Professor Wu Yihong and Professor B J Cho, as members of the qualifying examination committee, sharpened my learning curve, both by the thought-provoking questions they posed as well as by the information they provided on the diversity of courses available at the National University of Singapore (NUS).

I thankfully acknowledge the helpful suggestions and discussions provided by Dr Zhao Rong, Dr Miao Xiang Shui, Dr Lee Hock Koon, Dr Hu Xiang and Mr Tan Pik Yee, on my research work. In addition, I must also extend my thanks to my friends and colleagues: Mr Yang Hongxin, Ms Wang Qinfang, Mr Lim Kian Guan and many others, for their friendship, encouragement and kind advices, during my Ph.D study.

Great appreciation is also due to the NUS and its department of Electrical and Computer Engineering for providing a first-class educational environment; and especially to DSI for its first-class working environment and facilities as well as its generous financial support.

Finally, I am eternally grateful to my Grandma and my parents for their unwavering care and encouragement throughout the years. They are my strength and support now and in the future.

| Index                                                                                                                                                                                  |                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| ACKNOWLEDGEMENTS                                                                                                                                                                       | I               |

| SUMMARY                                                                                                                                                                                |                 |

| LIST OF TABLES                                                                                                                                                                         |                 |

| LIST OF FIGURES                                                                                                                                                                        |                 |

|                                                                                                                                                                                        |                 |

| LIST OF PUBLICATIONS                                                                                                                                                                   |                 |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                 |                 |

| 1.1 INTRODUCTION TO SEMICONDUCTOR MEMORIES         1.2 PHASE CHANGE RANDOM ACCESS MEMORY         1.2.1 Electrical Switching in Chalcogenide Glasses                                    | 10<br><i>10</i> |

| 1.2.2 Principles of PCRAM<br>1.2.3 Studies on PCRAM Technology                                                                                                                         |                 |

| 1.3 New Classification of Scaling Limitation of PCRAM                                                                                                                                  |                 |

| 1.4 OBJECTIVES.                                                                                                                                                                        |                 |

| 1.5 ORGANIZATION                                                                                                                                                                       |                 |

| CHAPTER 2 PHYSICAL LIMITATION OF PHASE CHANGE MATERIALS IN PC                                                                                                                          |                 |

|                                                                                                                                                                                        |                 |

| 2.1 INTRODUCTION                                                                                                                                                                       |                 |

| 2.2.1 Limitation for Phase Change in Free Scale                                                                                                                                        |                 |

| 2.2.2 Limitation for Phase Change in $Ge_2Sb_2Te_5$ Films Surrounded by ZnS-SiO <sub>2</sub>                                                                                           |                 |

| <ul> <li>2.2.3 Limitation for Reversible Phase Change in Thin Films Surrounded by ZnS-SiO<sub>2</sub></li> <li>2.3 CAUSES OF PHYSICAL LIMITATIONS OF PHASE CHANGE MATERIALS</li> </ul> |                 |

| 2.3.1 Causes of Limitation for phase change in Thin Films Surrounded by ZnS-SiO <sub>2</sub><br>2.3.2 Causes for Limitation for Reversible Phase Change                                | 38<br>43        |

| 2.4 POSSIBLE SOLUTION FOR EXTENDING PHYSICAL LIMITATIONS IN PHASE CHANGE MAT                                                                                                           |                 |

| 2.5 Summary                                                                                                                                                                            |                 |

| CHAPTER 3 THICKNESS DEPENDENT NANO-CRYSTALLIZATION                                                                                                                                     |                 |

| 3.1 BACKGROUND                                                                                                                                                                         |                 |

| 3.2 EXPERIMENTS                                                                                                                                                                        |                 |

| 3.2.1 Set-up and Samples                                                                                                                                                               |                 |

| 3.2.2 Exothermal Measurements                                                                                                                                                          |                 |

| 3.2.3 Isothermal Measurements<br>3.3 THICKNESS DEPENDENT NANO-CRYSTALLIZATION                                                                                                          |                 |

| 3.3.1 Crystallization Temperature                                                                                                                                                      |                 |

| 3.3.2 Crystallization Activation Energy                                                                                                                                                |                 |

| 3.3.4 Avrami Coefficient                                                                                                                                                               |                 |

| CHAPTER 4 SUPERLATTICE-LIKE PHASE CHANGE STRUCTURE                                                                                                                                     |                 |

|                                                                                                                                                                                        |                 |

| 4.1 INTRODUCTION                                                                                                                                                                       |                 |

| 4.2.1 Electrical Properties                                                                                                                                                            | 67              |

| 4.2.2 Crystallization Properties                                                                                                                                                       |                 |

| 4.2.3 Thermal Properties                                                                                                                                                               |                 |

| 4.3 CRYSTALLINE-AMORPHOUS-SUPERLATTICE (CASL)                                                                                                                                          |                 |

| 4.4 SUMMARY                                                                                                                                                                            |                 |

| CHAPTER 5 INTEGRATED CIRCUIT DESIGN OF 128 BIT PCRAM CHIP   |     |

|-------------------------------------------------------------|-----|

| 5.1 INTRODUCTION OF MEMORY IC DESIGN                        |     |

| 5.2 HSPICE MODELING OF PCRAM CELLS                          |     |

| 5.2.1 Binary Macromodel of PCRAM                            |     |

| 5.2.3 Multi-level Macromodel of PCRAM                       | 100 |

| 5.3 IC DESIGN OF 128-BIT PCRAM CHIP                         | 104 |

| 5.3.1 Architecture and Main Blocks                          |     |

| 5.3.3 Full Schematics, Simulations and Layouts              |     |

| 5.4 SUMMARY                                                 | 114 |

| CHAPTER 6 FABRICATION AND TESTING OF 128-BIT SLL_PCRAM CHIP | 116 |

| 6.1 INTRODUCTION                                            |     |

| 6.2 FABRICATION OF SLL_PCRAM                                | 118 |

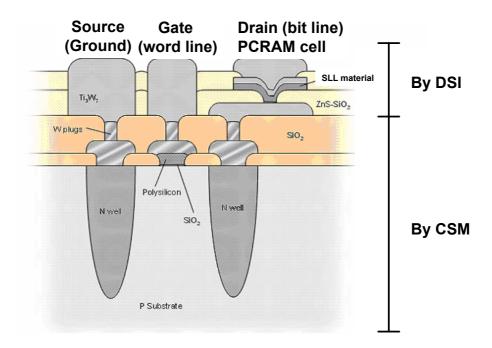

| 6.2.1 SLL Memory Cell Structure                             | 118 |

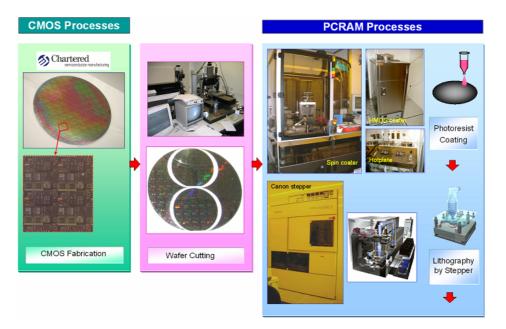

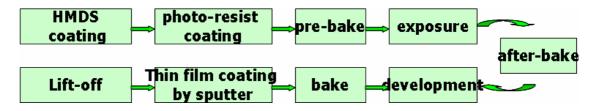

| 6.2.2 General Processes and Equipments                      |     |

| 6.2.3 Memory Cell and Memory Chip                           | 122 |

| 6.3 TESTING OF PCRAM CHIPS                                  |     |

| 6.3.1 Memory Chip Testing Bench                             |     |

| 6.3.2 Testing of SLL_PCRAM Chip                             |     |

| 6.3.3 Discussion                                            |     |

| 6.4 SUMMARY                                                 |     |

| CHAPTER 7 CONCLUSIONS                                       |     |

| 7.1 SUMMARY                                                 | 136 |

| 7.2 FUTURE RESEARCH                                         |     |

| REFERENCE                                                   | 141 |

### Summary

This dissertation addresses the scaling limitations of the Phase Change Random Access Memory (PCRAM) that is considered as one of the best candidates for meeting the scaling requirements for the next wave of memory technologies.

Chapter 1 establishes the background of this thesis, providing a fairly comprehensive description of memory technology and related scaling issues. This chapter proposes a new classification of the scalability limitations of PCRAM, including the lithography technology, the physical limitations of materials in PCRAM, the thermal-cross talk among memory cells and the current limitation of memory cells. Based on this classification, particular emphasis is paid to the physical limitations of the materials and the current limitation of memory cells in subsequent chapters.

The physical limitations of phase change material in PCRAM technology form the focus of Chapter 2. To thoroughly investigate this issue, a new classification of the phase change process is proposed and it includes (1) phase change in the free scale, (2) phase change sandwiched between metals/oxides and (3) reversible phase change sandwiched between metals/oxides. The limitations for phase change in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> material and physical mechanisms are studied according to each category. A thermal electrical methodology is developed to simplify the three-dimension (3D) issue to a thickness-dependent problem. The results show that the limitations for reversible phase change sandwiched between metals/oxides can be considered as a physical limitation of phase change material in PCRAM technology. The possible solutions for extending this physical limitation are proposed.

In the study of physical limitations, the interface effect on crystallization was found to play an important role in ultra-small sized PCRAM technology. A systematical study on this interface-dominant nano-crystallization is presented in Chapter 3. After the simplification of the 3D issue to the thickness-dependent crystallization issue by the methodology described in Chapter 2, crystallization kinetics including the crystallization mechanism, the corresponding activation barrier and the Avrami coefficient, were next investigated.

The limitation of current supplied to PCRAM cells, which is the subject of the subsequent chapters, refers to the high RESET current required for PCRAM cells. This would affect the scalability of PCRAM chips because a higher programming current requires bigger access transistor to supply sufficient current. In this study, superlattice-like (SLL) structure, which can reduce the current, is applied in a 128-bit PCRAM chip, which demonstrates low current and high-speed. In addition, a universal macro-model of PCRAM cells is developed for this chip's integrated circuit design. Its fabrication, based on 0.35 µm CMOS technology, also demonstrates a high degree of process compatibility. The circuit design and fabrication of this 128-bit SLL\_PCRAM is described in further detail in Chapter 5 and Chapter 6, respectively.

This thesis aims at providing a useful understanding of the scalability limitations of PCRAM technology. In addition to presenting the author's findings, it is expected that this document provides useful models and methodologies for other researchers, and serves as a useful reference.

**Keywords**: Semiconductor memory, phase change random access memory, chalcogenide material, physical limitation, nucleation and growth, scaling, integrated circuit design, device fabrication, testing

# List of Tables

## Chapter 2

| Table 2. 1 Layer parameters of ZnS-SiO <sub>2</sub> /Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> /ZnS-SiO <sub>2</sub> sandwich structures | 5  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| obtained by X-Ray refractor measurement.                                                                                                       | 44 |

## Chapter 3

| Table 3. 1 Activation energy $(E_a)$ and avrami coefficient (n) in publications                         |    |

|---------------------------------------------------------------------------------------------------------|----|

| Table 3. 2 Crystallization temperature (°C) measured by ETTM.                                           |    |

| Table 3. 3 E <sub>a</sub> in ultra-thin Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> films.          |    |

| Table 3. 4 Avrami coefficients in diffusion controlled growth.                                          | 59 |

| Table 3. 5 Avrami coefficients (n) for ultra-thin Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> films | 60 |

## Chapter 4

| Table 4. 1 The parameters of phase change thin films in artificial compound SLL_                                      |      |

|-----------------------------------------------------------------------------------------------------------------------|------|

| Ge <sub>6</sub> Sb <sub>2</sub> Te <sub>9</sub> structure.                                                            | . 69 |

| Table 4. 2 The parameters of phase change thin films in SLL-Ge <sub>2</sub> Sb <sub>2</sub> Ge <sub>5</sub> structure | . 72 |

| Table 5. 1 Logical Relationship of Switches in PCRAM Macromodel                   | 94    |

|-----------------------------------------------------------------------------------|-------|

| Table 5. 2 Parameters in PCRAM cell macromodel.                                   | 95    |

| Table 5.3 Logical relationship in the logical control circuit of four level PCRAM |       |

| macromodel                                                                        | . 103 |

# **List of Figures**

## Chapter 1

| Fig. | 1. 1 Forecast of the semiconductor memory market by Databeans Inc             | 3    |

|------|-------------------------------------------------------------------------------|------|

| Fig. | 1. 2 Schematic structure of (a) conventional Flash cell, (b) SONOS, (c) TANOS | 5    |

|      | and (d) nano-crystal Flash cell.                                              | 4    |

| Fig. | 1.3 (a) Three dimension view of a FinFET memory device (b) the cross-sectio   | nal  |

|      | view shows that the N+ poly gate surrounds the ONO stack that is deposited on |      |

|      | the two sidewalls and the top surface of the surface Fin                      | 6    |

| Fig. | 1. 4 The schematic structure and working principles of FeRAM cells.           | 9    |

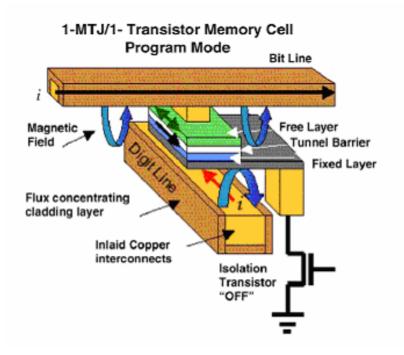

| Fig. | 1. 5 MRAM cell in the Magnetic Tunnel Junctions 1-MJT /1-transistor option,   |      |

|      | schematically showing the programming operation mode.                         | 9    |

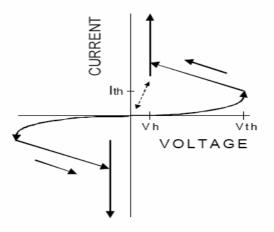

| Fig. | 1. 6 Electrical threshold switch in phase change material.                    | . 12 |

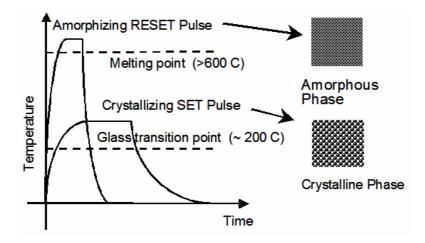

| Fig. | 1. 7 Phase change process of the chalcogenide material.                       | . 13 |

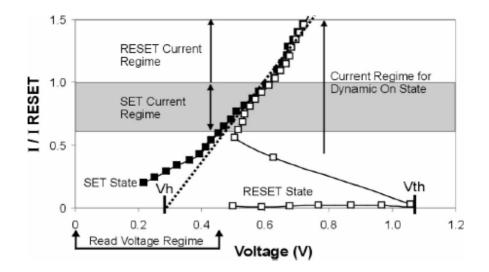

| Fig. | 1. 8 Electrical properties of PCRAM devices                                   | . 15 |

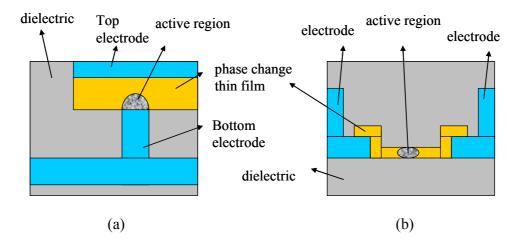

| Fig. | 1. 9 Vertical (a) and line-type (b) PCRAM memory cells.                       | . 16 |

| Fig. | 1. 10 Thermal cross talk in the PCRAM when the density of memory array        |      |

|      | increases.                                                                    | . 21 |

| Fig. | 1. 11 Maximum current by a minimum size MOS transistor.                       | . 22 |

| Fig. | 1. 12 Edge contact phase change memory cells (Ha, 2003).                      | . 23 |

| Fig. | 1. 13 RESET current scaling with the contact area scaling of a single PCRAM   |      |

| -    | memory cell.                                                                  | . 23 |

|      |                                                                               |      |

## Chapter 2

| Fig. | 2. 1 Schematic nucleation process of phase change material; the left figure shows the initial stage of embryo seed, the right figure shows the nucleus after gradual growth                                                                                           | 1 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

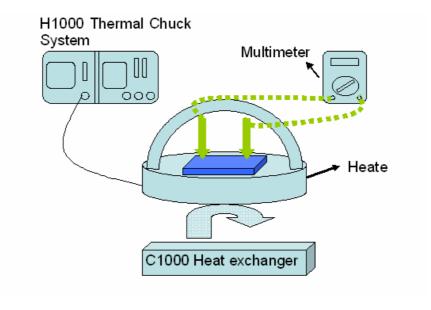

|      | <ul> <li>2. 2 Interface effects in phase change materials surrounded by oxides/metals 32</li> <li>2. 3 Sample (a) and set-up (b) for in-situ thermal electrical resistance measurement; the resistance of samples would be monitored during the annealing.</li> </ul> | • |

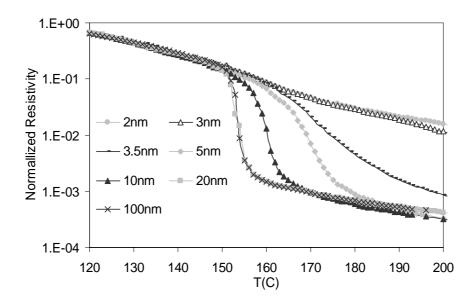

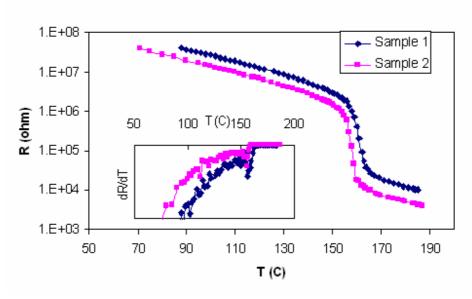

| Fig. | 2. 4 Exothermal electrical measurement of ultra-thin films; the crystallization process was delayed by a decrease in thin film thickness. When the thin film thickness became thinner than 3 nm, the crystallization did not occur                                    | 5 |

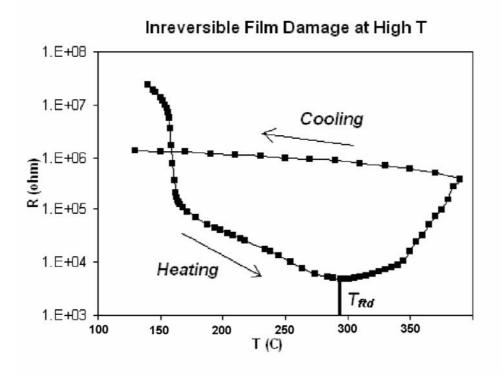

| Fig. | 2. 5 A thin film breakdown of $Ge_2Sb_2Te_5$ / oxide sandwiched structures at high temperature; the performance of phase change material would not be recovered after the breakdown of the film                                                                       |   |

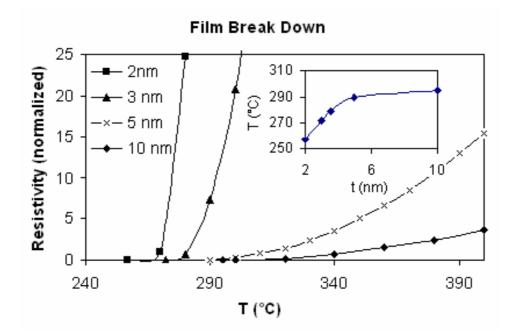

| Fig. | 2. 6 T <sub>fbd</sub> in different phase change thin films of different thickness                                                                                                                                                                                     | 8 |

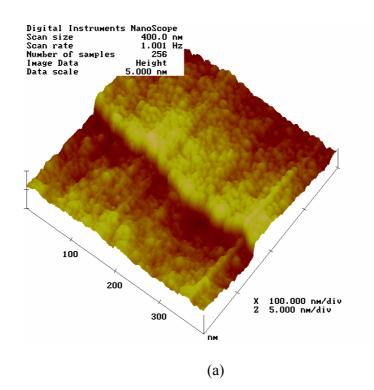

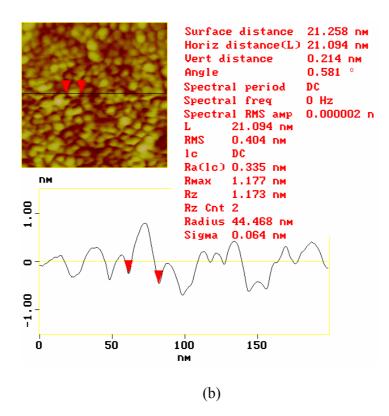

| Fig. | 2. 7 Topography and cross-section of a 3nm thick Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> thin film measured by AFM.                                                                                                                                           | 0 |

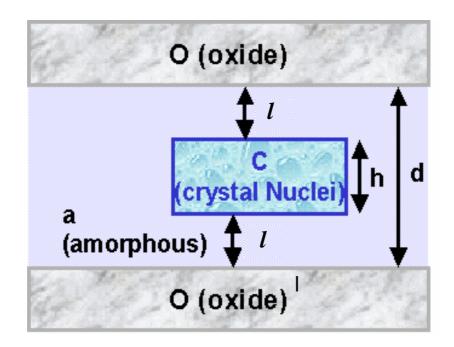

| Fig. | 2. 8 Model of a cylindrically shaped nano-crystal embedded in an amorphous film with oxide interfaces                                                                                                                                                                 |   |

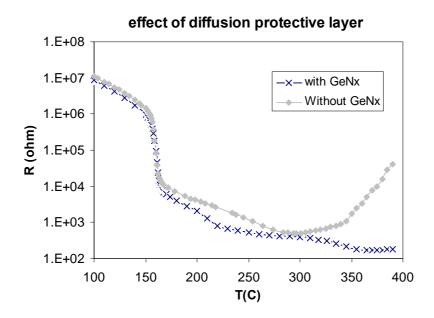

| Fig. | 2. 9. The electrical resistance of samples with and without 20 nm thick GeNx layer during annealing; the $Ge_2Sb_2Te_5$ thin film was kept the same thickness 10 nm in both same last                                                                                 | ~ |

|      | nm in both samples                                                                                                                                                                                                                                                    | b |

| Fig. 3. 1 Resistance measurement by two-probe set-up                                                                     | 52 |

|--------------------------------------------------------------------------------------------------------------------------|----|

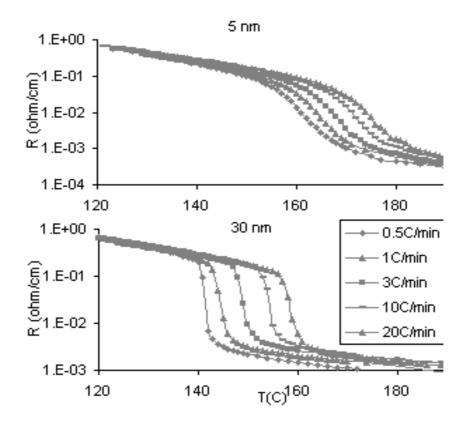

| Fig. 3. 2 ETTM of 5 nm and 30 nm Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> thin films at different heating rate    | 53 |

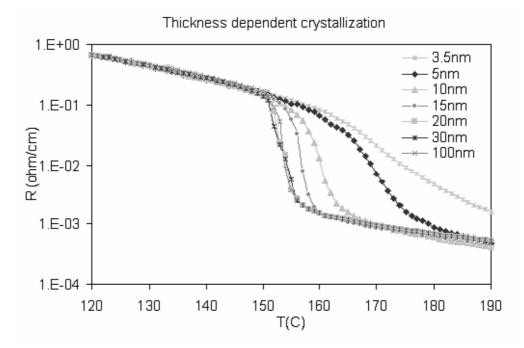

| Fig. 3. 3 ETTM of different thick Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> thin films at 10 °C/min                | 54 |

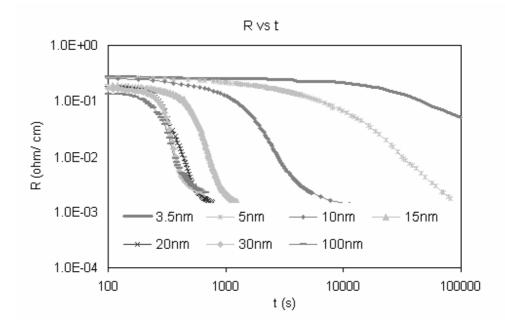

| Fig. 3. 4 Resistivity as function of time when Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> thin films under 143.5 °C | 55 |

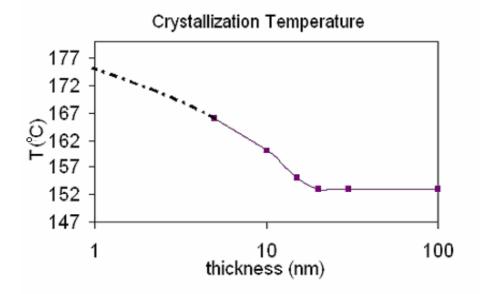

| Fig. 3. 5 The dependence of the crystallization temperature dependence on thickness                                      | at |

| a heating rate of 10 °C/min.                                                                                             | 56 |

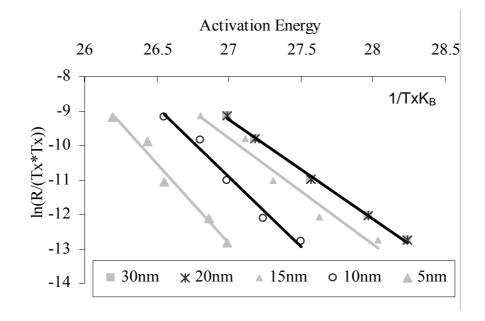

| Fig. 3. 6 ETTM kissinger plot of ultra-thin GeSbTe films measured by ETTM                                                | 57 |

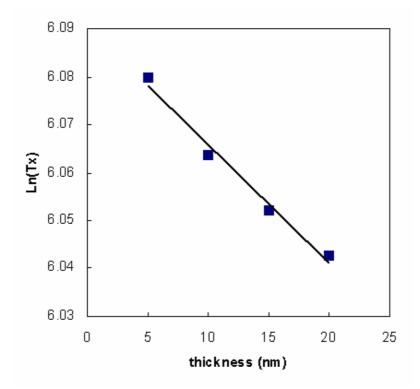

| Fig. 3. 7 The linear relationship between $Ln(T_x)$ and thin film thickness.                                             | 58 |

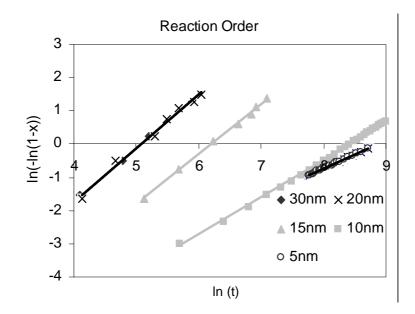

| Fig. 3. 8 Avrami plot of ultra-thin Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> films derived by ITTM measurements   |    |

| and the slopes of these plots found to correspond with the Avrami coefficients                                           | 60 |

## Chapter 4

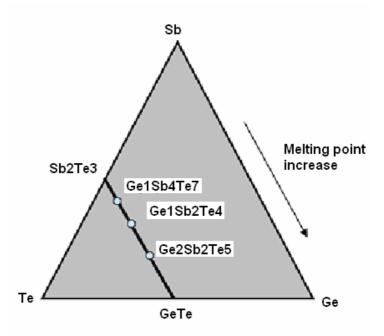

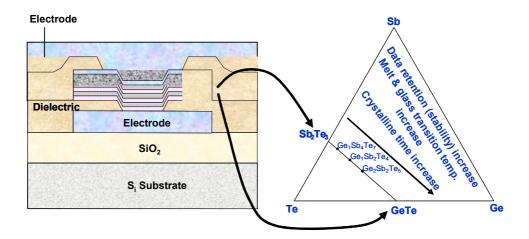

| Fig. | 4. 1 The GeTe-Sb <sub>2</sub> Te <sub>3</sub> pseudobinary system, the compounds on the line between $Sb_2Te_3$ and GeTe are the most popular materials used in phase change technologies. |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                                                                                            |

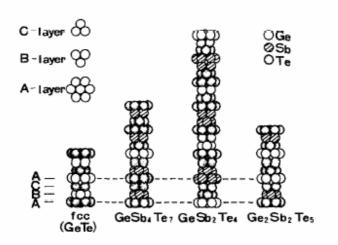

| Fig. | 4. 2 Stacking models of three ternary compounds in GeTe-Sb <sub>2</sub> Te <sub>3</sub> pseudobinary system and GeTe (Yamada, et. al., 1991)                                               |

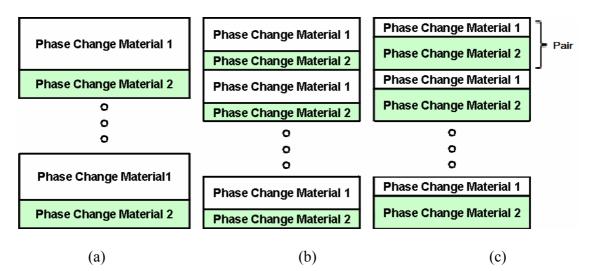

| Fig. | 4. 3 SLL phase change material structure and the structural engineering of SLL medium (a) 2-pair SLL structure (b) 3-pair SLL structure (c) 3-pair SLL structure                           |

| ъ.   | with compositionally different artificial structure                                                                                                                                        |

| -    | 4. 4 Schematic cross-sectional view of SLL sample in ETTM measurement 68                                                                                                                   |

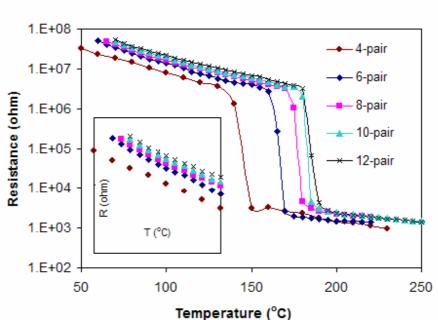

| Fig. | 4. 5 ETTM measured electrical resistance of the SLL-Ge <sub>6</sub> Sb <sub>2</sub> Ge <sub>9</sub> structures during annealing                                                            |

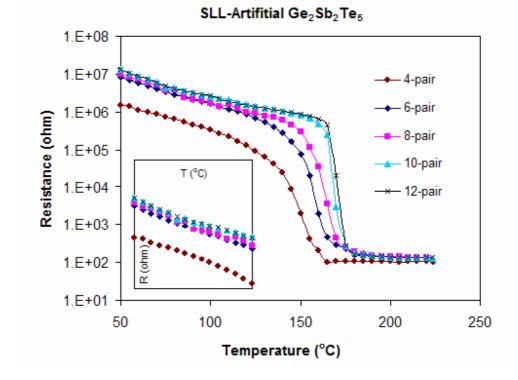

| Fig. | 4. 6 ETTM measured electrical resistance of the SLL-Ge <sub>2</sub> Sb <sub>2</sub> Ge <sub>5</sub> structures during annealing                                                            |

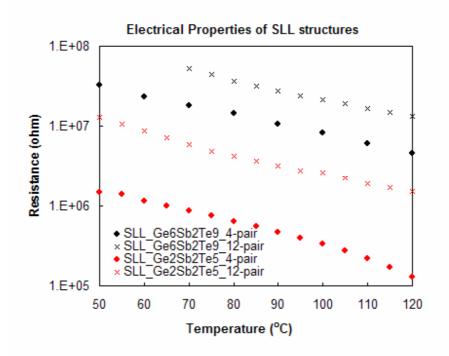

| Fig. | 4. 7 Compositional dependent effect in ETTM measured electrical resistance of                                                                                                              |

| Ũ    | the SLL $Ge_6Sb_2Ge_9$ and SLL $Ge_2Sb_2Te_5$ structures                                                                                                                                   |

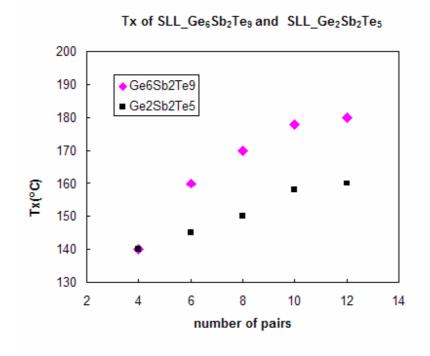

| Fig. | 4. 8 $T_x$ vs the number of pairs in the SLL Ge <sub>6</sub> Sb <sub>2</sub> Ge <sub>9</sub> structures and                                                                                |

| 0    | SLL Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> structures                                                                                                                             |

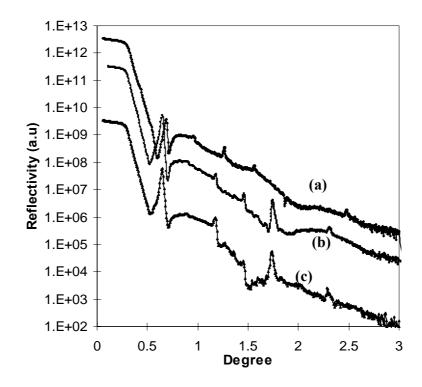

| Fig. | 4. 9 Small angle X-ray diffraction results: (a) as deposited samples (b) the sample was heated to 100°C in an vacuum furnace for 5 minutes, (c) the sample was                             |

|      | heated to 150°C in an vacuum furnace for 5 minutes                                                                                                                                         |

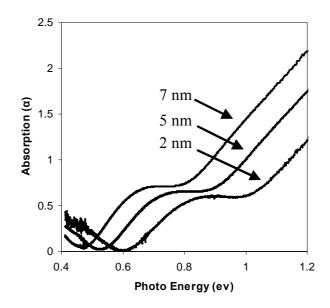

| Fig. | 4. 10 Blue shift of absorption edges in m-CASL structures                                                                                                                                  |

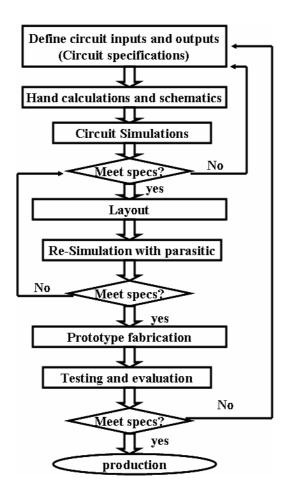

| Fig. 5. 1 Integrated circuit design flow chart.                                  | 86     |

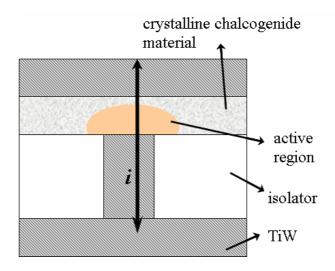

|----------------------------------------------------------------------------------|--------|

| Fig. 5. 2 Schematic structure of the PCRAM element, the active region is the re- | d area |

| above the bottom electrode.                                                      | 88     |

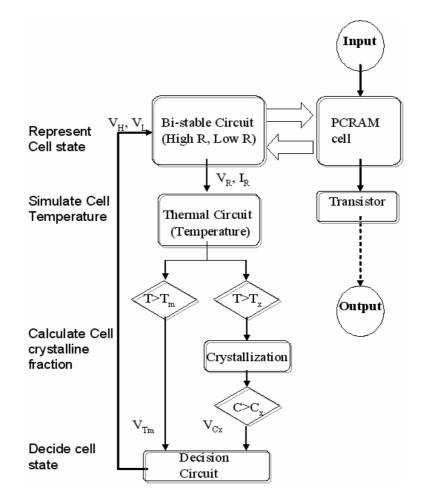

| Fig. 5. 3 Flowchart of macromodel binary phase change memory cells               | 91     |

| Fig. 5. 4 Schematic of binary macromodel of phase change memory cells            | 91     |

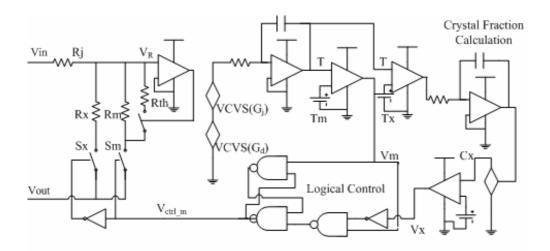

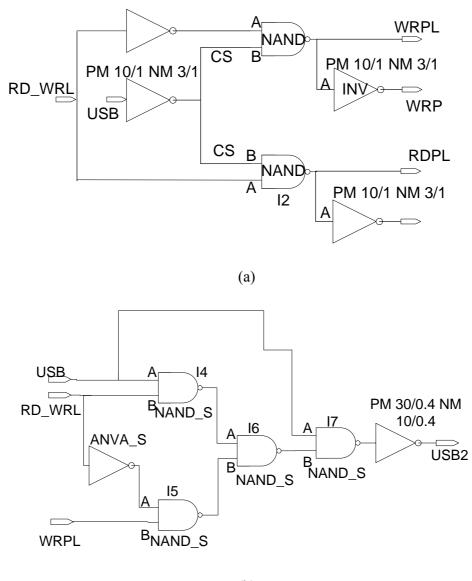

| Fig. 5. 5 Voltage programming circuit for PCRAM element.                         |        |

| Fig. 5. 6 Simulation results of I-V characteristics of PCRAM elements            |        |

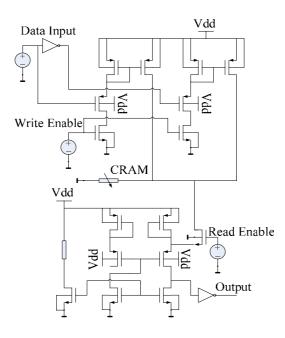

| Fig. 5. 7 Circuit of standard read/ write operation of PCRAM                     |        |

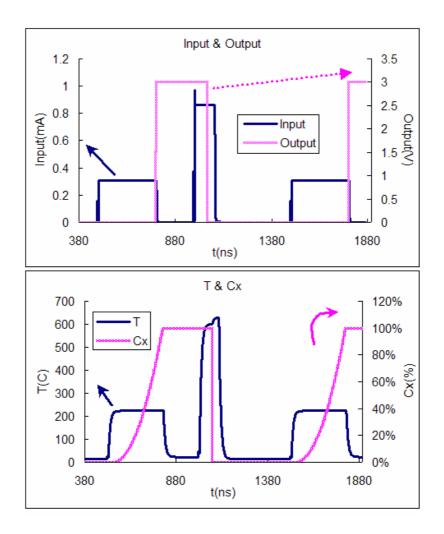

| Fig. 5. 8 PCRAM operation with standard read/write circuit; (Upper) Input and    | Output |

| Data with programming pulses; (Lower) simulated temperature and crystal          | -      |

| fraction of the active region.                                                   |        |

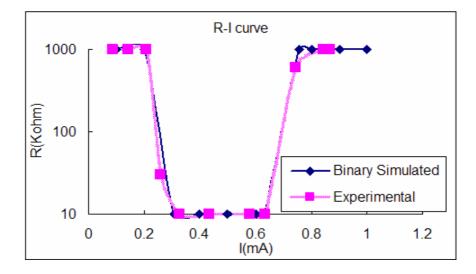

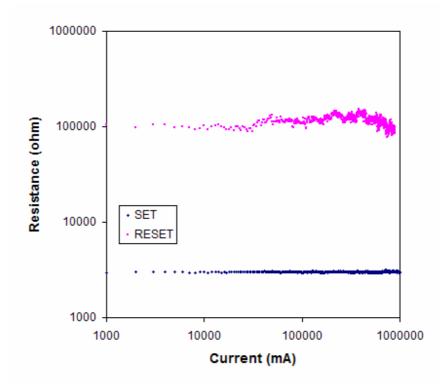

| Fig. 5. 9 R-I curve of PCRAM elements based on binary macromodel.                |        |

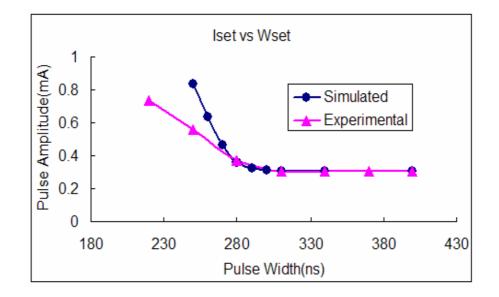

| Fig. 5. 10 Relationship between amplitude and width of programming pulses of t            | the   |

|-------------------------------------------------------------------------------------------|-------|

| SET operation.                                                                            | 100   |

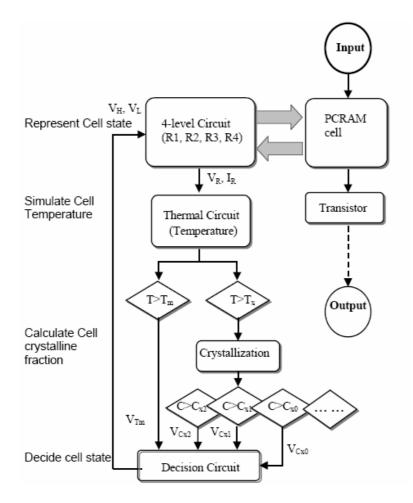

| Fig. 5. 11 Flow chart of the macromodel of four level PCRAM cells                         | 102   |

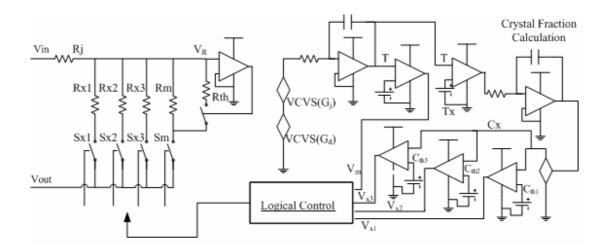

| Fig. 5. 12 Schematics of the macromodel of four-level phase change memory cel             |       |

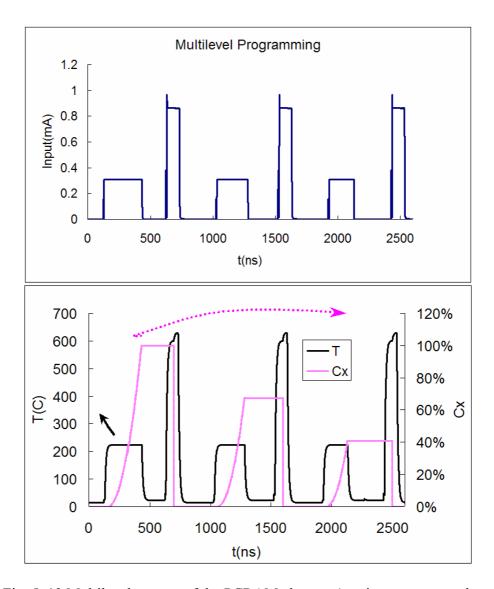

| Fig. 5. 13 Multilevel storage of the PCRAM element (top-input current pulses, b           |       |

| temperature and crystal fraction of active region); the fraction of crystalline           |       |

| in the active region would increase with a longer SET pulse width                         |       |

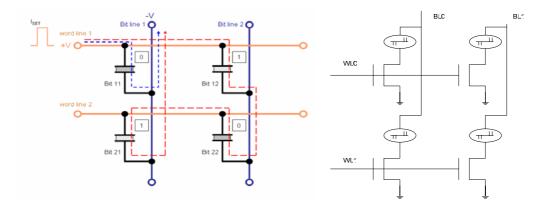

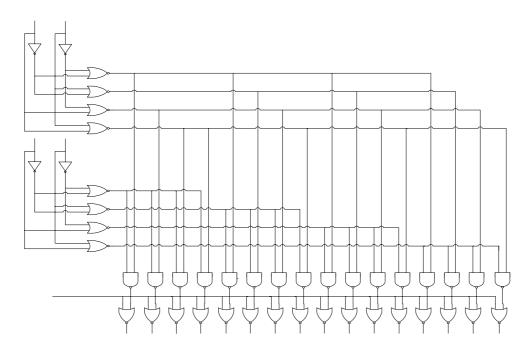

| Fig. 5. 14 Architecture of 128-bit SLL_PCRAM chip                                         |       |

| Fig. 5. 15 (a) Leakage current in PCRAM memory array without the selecting                |       |

| elements, (b) Schematic of PCRAM array with transistors. The leakage amo                  | ng    |

| memory cells in array was eliminated by the NMOS selective elements                       | •     |

| Fig. 5. 16 Schematics of a row decoder; it requires an <i>n</i> -bit address and produces |       |

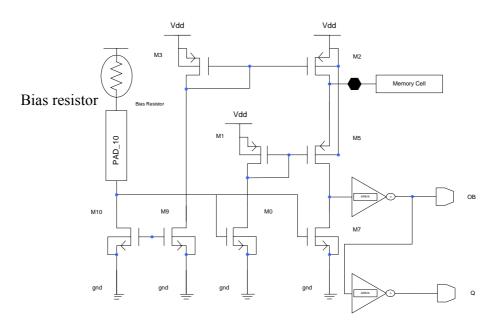

| outputs, one of which is activated.                                                       |       |

| Fig. 5. 17 The schematics of a single ended sense amplifier with external bias res        |       |

|                                                                                           | 108   |

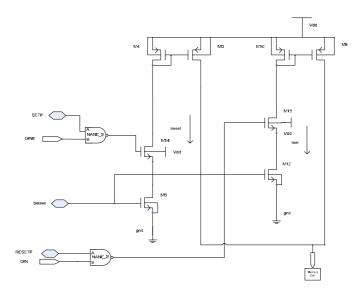

| Fig. 5. 18 The schematics of the current generator; the external bias was also inc        | luded |

| to adjust the programming current.                                                        |       |

| Fig. 5. 19 Logic control circuit schematic.                                               |       |

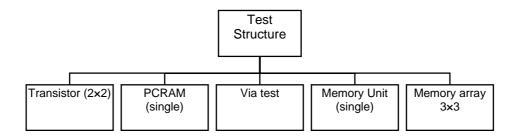

| Fig. 5. 20 Testing structure of memory array.                                             |       |

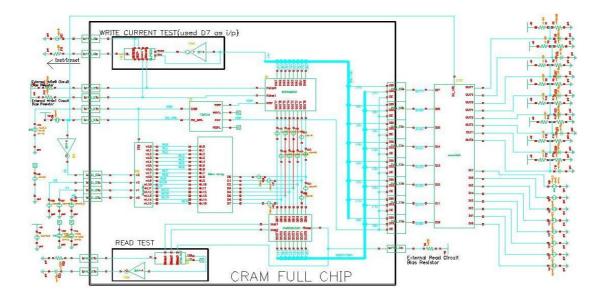

| Fig. 5. 21 Full schematics of 128-bit memory chip, including key blocks, such as          |       |

| memory array, decoder, sense amplifier, programming circuit, control logic                |       |

| I/O pad.                                                                                  |       |

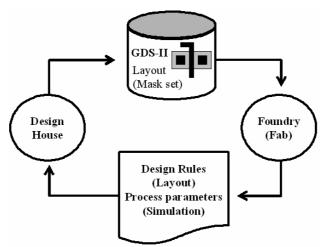

| Fig. 5. 22 The flow of data between the design house and the foundry.                     |       |

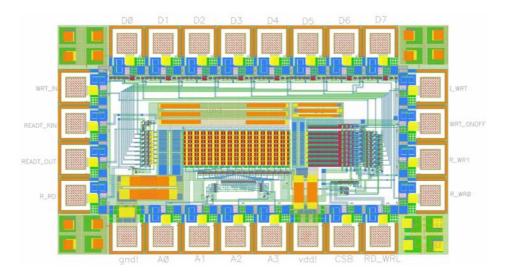

| Fig. 5. 23 The full layout of transistor version.                                         |       |

| 1.6.6.26 The full happened of transition (efficiency efficiency efficiency)               |       |

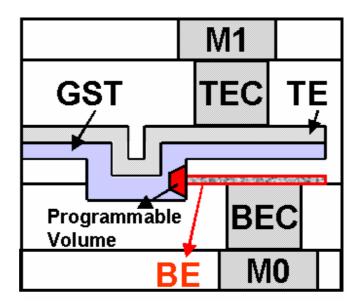

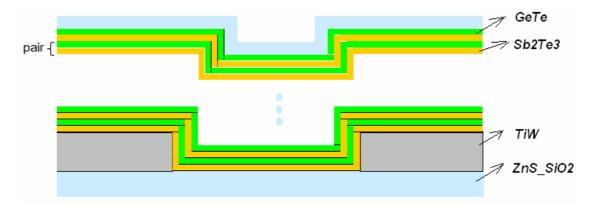

| Fig. 6 | 5. 1 Schematic cross-section of SLL_PCRAM memory bits.                                                             | 117  |

|--------|--------------------------------------------------------------------------------------------------------------------|------|

| Fig. 6 | 5. 2 Schematic of PCRAM fabrication flow                                                                           | 118  |

| Fig. 6 | 5. 3 Schematic cross section of SLL_PCRAM memory cells                                                             | 119  |

| Fig. 6 | 5. 4 Schematic process flow for SLL_PCRAM memory cells                                                             | 120  |

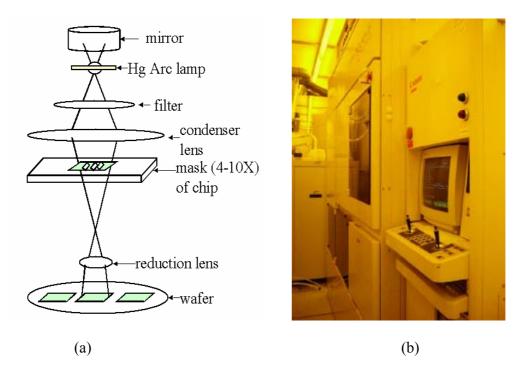

| Fig. 6 | 5. 5 (a) The principle and (b) the picture of Canon i-line Aligner used for                                        |      |

| S      | SLL_PCRAM fabrication.                                                                                             | 121  |

| Fig. 6 | 6. 6 Balzers sputtering machine used to deposit phase change, dielectric and me                                    | etal |

| t      | hin films                                                                                                          | 122  |

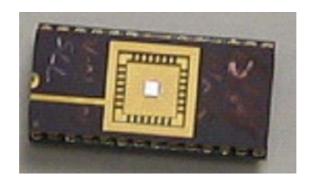

| Fig. 6 | 5. 7 The top view of 128-bit SLL_PCRAM memory chip after wire bonding                                              | 122  |

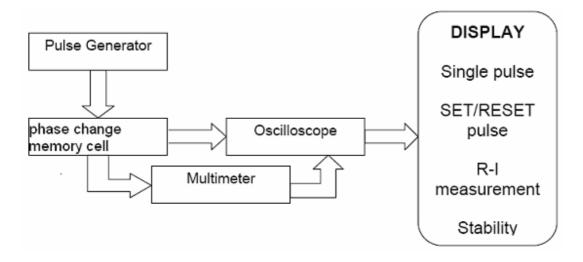

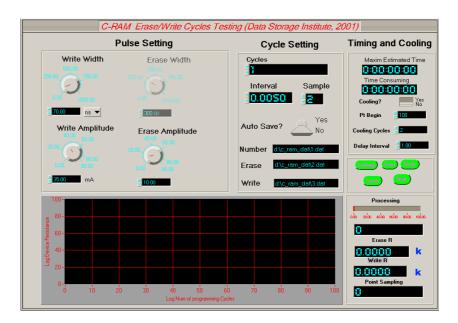

| Fig. 6 | 5. 8 Schematic diagram of the testing system.                                                                      | 123  |

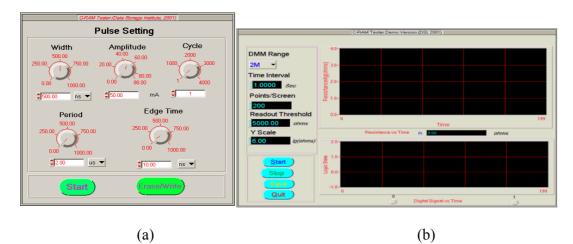

| Fig. 6 | 5. 9 Single pulse operation and resistance monitor of testing bench (a) single pu                                  | ılse |

|        |                                                                                                                    | 124  |

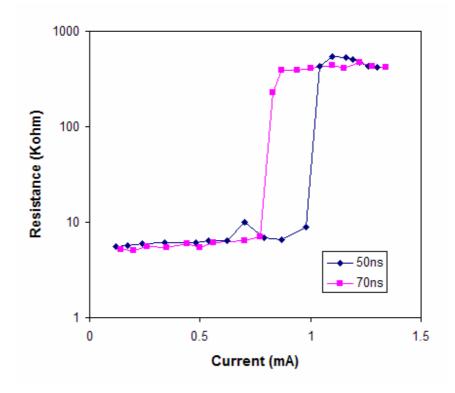

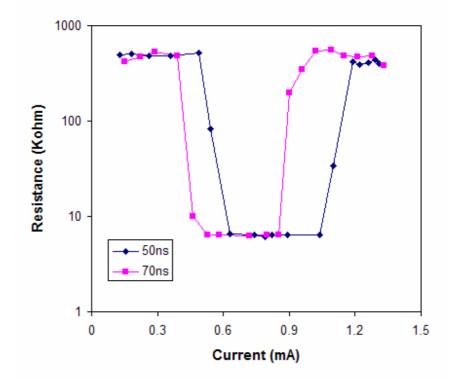

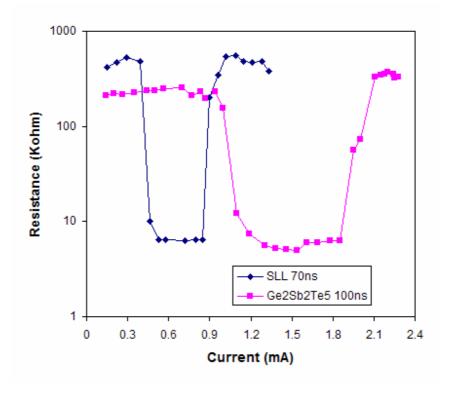

| Fig. 6 | 5. 10 The low current operation of the SLL_PCRAM (a) programming from the                                          | Э    |

| с      | rystalline state (b) U curve (c) the R-I curve compared with Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> PCRAM | М.   |

|        |                                                                                                                    | 127  |

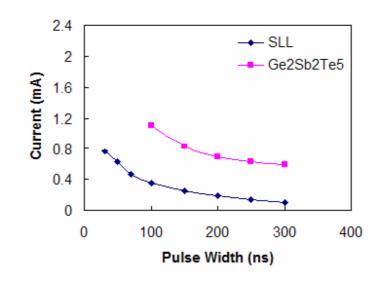

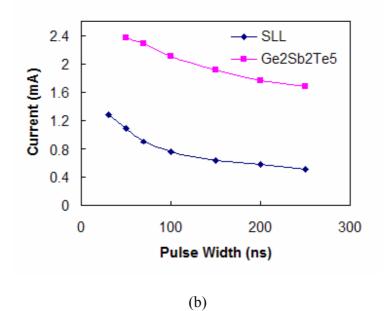

| Fig. 6 | 5. 11 (a) SET programming current as a function of pulse width (b) RESET                                           |      |

| р      | rogramming current as a function of pulse width.                                                                   | 128  |

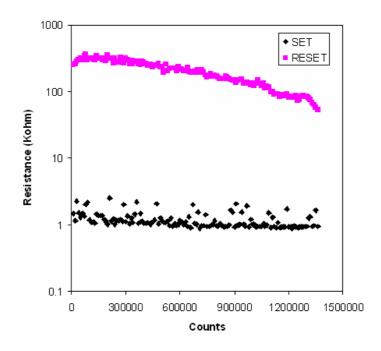

| Fig. 6 | 5. 12 The life-cycle measurement of memory testing bench                                                           | 129  |

| Fig. 6 | 5. 13 Overwriting cycles of SLL_PCRAM chips                                                                        | 130  |

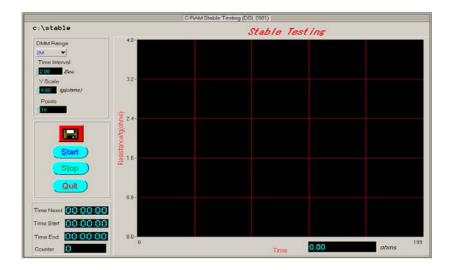

| Fig. 6 | 5. 14 The reliability measurement of memory testing bench.                                                         | 131  |

| Fig. 6 | 5. 15 Reliability cycles of SLL_PCRAM chips                                                                        | 132  |

|        |                                                                                                                    |      |

## **List of Publications**

#### **Publications in Journals:**

- Wei, X.Q., Shi, L.P., Walia, R., Chong, T.C., Zhao, R., Miao, X.S. and Quek, B.S, "HSPICE macromodel of PCRAM for binary and multilevel storage", IEEE Transactions Electron Devices, Vol. 53, pp. 56 - 62, Jan. 2006.

- Wei, X. Q., Shi, L. P., Chong, T. C., Zhao, R. and Lee, H. K., "Thickness Dependent Nano-Crystallization in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Films and Its Effect on Devices", Jpn. J. Appl. Phys., Vol. 46, pp. 2211- 2214, 2007.

- 3. T.C. Chong, Shi L.P, Wei X.Q., Zhao R., Lee H. K., "Crystalline amorphous semiconductor superlattices", Phys. Rev. Lett., Vol. 100, pp.136101, 2008.

- Shi, L.P., Chong, T.C., Wei, X.Q., Zhao, R., Wang, W.J., Yang, H.X., Lee, H.K., Li, J.M., Yeo, N.Y., Lim, K.G., Miao, X.S., Song, W.D., "Investigation of nanophase change for phase change random access memory", IEEE proceedings, Nonvolatile Memory Technology Symposium 2006, Vol., 5-8, pp.76 – 80, 2006.

- Shi, L.P., Chong, T.C., Li, J. M., Koh, S.C., Zhao, R., Yang, H. X., Tan, P.K., Wei, X.Q., and Song, W. D., "Thermal modeling and simulation of nonvolatile and non-rotating phase change memory cell", IEEE proceedings, Nonvolatile Memory Technology Symposium, 2004, Vol.15-17, pp. 83 87, 2004.

- Shi, L.P., Chong, T.C., Zhao, R., Li, J.M., Tan, P.K., Miao, X. S., Wang, W. J., Lee, H.K., Wei, X.Q., Yang, H.X., Lim, K.G., Song, W.D., "Investigations on non volatile and non rotational phase change random access memory", IEEE proceedings, Nonvolatile Memory Technology Symposium, 2005, Vol. 7-10, pp.115 – 120, 2005.

- Zhao, R., Chong, T. C., Shi, L. P., Tan, P. K., Lim, K.G., Yang, H. X., Lee, H. K., Hu, X., Li, J. M., Miao, X. S., Wei, X. Q., Wang, W. J., Song, W. D., "Study of geometric effect on phase change random access memory", IEEE proceedings, Nonvolatile Memory Technology Symposium, pp. 7-10, pp.110 – 114, 2005.

#### **Publications in Conferences:**

- Wei, X. Q., Shi, L. P., Chong T. C., and Zhao, R., "Thickness dependent nanocrystallization in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> films", International Conference on Solid State Devices and Materials (SSDM), Tokyo, Japan, pp. 91-94, 2007.

- Wei, X.Q., Shi, L. P., Zhao, R., Miao, X.S., Chong, T.C., Rajan, W., Quek, B.S., "Universal HSPICE model for chalcogenide based phase change memory elements", IEEE proceedings, Nonvolatile Memory Technology Symposium 2001, Vol. 15 – 17, pp. 88 – 91, 2004.

# CHAPTER 1 INTRODUCTION

The recent rapidly growing demand for portable and mobile products has seen an equally rapidly growing demand for nonvolatile memories (NVMs). The most popular NVM, Flash memory, is believed to face the scalability limitations below 32 nm. Therefore, new memories are being widely studied for the next generation NVM technologies. Among all emerging memories, Phase Change Random Access Memory (PCRAM) is believed to be the best candidate for the nonvolatile technology, because of its superior overall performance and good scalability. This chapter will briefly review different existing memory technologies and provide a detailed description of PCRAM technology.

### **1.1 Introduction to Semiconductor Memories**

Currently, semiconductor memories constitute the most attractive segment in the global semiconductor market: they occupy one-third of the entire semiconductor market and maintain the fastest growing rate. Generally, there are two categories of semiconductor memories: volatile memories and nonvolatile memories.

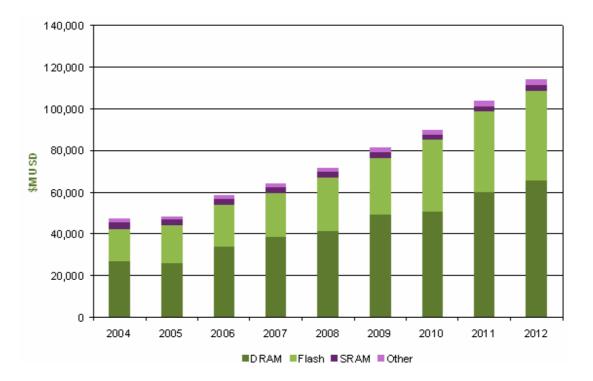

Volatile memories are memories that would lose data with the interruption of power supply. The main components are Dynamic Random Access Memory (DRAM) and Static Random Access Memory (SRAM). DRAM is the most cost and space efficient memory because each DRAM cell consists of only one transistor and one capacitor (Lueck, et. al, 1973). DRAMs have been dominating the largest market segment of the semiconductor memory market for more than 10 years (Databeans, 2007). The second component, SRAM, is the fastest memory with a lower standby current compared to DRAM. However, in SRAM, a single memory cell includes four or six transistors (Lage, et. al, 1996), resulting in a very low chip density and relatively high cost. For a long time, SRAM had been ranked the second in the semiconductor memory market; however, its market already shrank to the third largest due to the fast development of NVM (Databeans, 2007).

The dominant technologies for NVM include EEPROM and Flash memory, which can store the data at least for 10 years, even when the power supply is disturbed. EEPROM is electrically-erasable-and-programmable (Mukherjee, et. al, 1985). The device programmer writes data to the device one bit at a time by applying an electrical charge to the input pins of the chip. Any byte within an EEPROM may be erased and rewritten. From a software viewpoint, Flash and EEPROM technologies are very similar. The major difference is that Flash devices can only be erased one sector at a time, not bitby-bit.

Fig. 1. 1 Forecast of the semiconductor memory market by Databeans Inc.

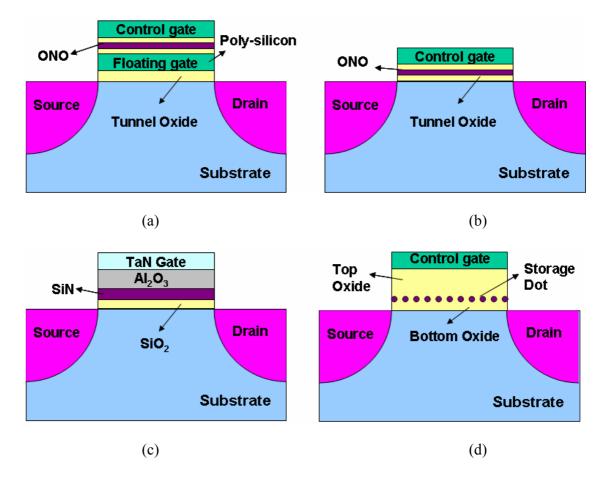

Flash memory combines the best features of the memory devices described thus far. Since 1999, it has exceeded SRAM, occupying the second largest segment of the market for semiconductor memories. It is projected to be in top position in the 2010s (Databeans, 2007), according to Fig. 1.1. The conventional structure of a Flash memory is shown in Fig. 1.2 (a), in which the cell consists of a Metal-Oxide-Semiconductor (MOS) transistor, which has an additional floating gate between the channel and the control gate. The programming of cells is realized by channel hot electrons within a programming time of 1-10  $\mu$ s. However, a high programming current is required because of low efficiency of hot electron injection. Erasing is realized by Fowler-Nordheim (FN) tunneling, while recently it has become common for erasing to be carried out by tunneling to the source junction of the transistor. This leads to smaller possible channel lengths and therefore the

better scalability of the cells (Keeney, 2001).

Fig. 1. 2 Schematic structure of (a) conventional Flash cell, (b) SONOS, (c) TANOS and (d) nano-crystal Flash cell.

Although demand for Flash memory is experiencing fast growth, it is not an entirely ideal option because of (1) its relatively long programming time of 1  $\mu$ s - 1 ms (She, 2003); (2) limited cycle endurance at smaller than 10<sup>6</sup> (Cappelletti, 1994); and, (3) especially its scaling limitation below 45 nm or 32 nm node (Roberto, 2004). The scaling limitation is due to the tunneling of electron through the floating gate, which would cause the data lost. Although the direct tunneling, preventing the ten-year retention time, occurs at 6-7 nm, stress induced leakage current push the tunnel thickness limit to no less than 8-

9 nm. Moreover, the effective width reduction could be limited by the read current reduction, then impacting the access time (Bez, et.al, 2003). Advanced technologies, such as SONOS (silicon-oxide-nitride-oxide-silicon), TANOS (Si-Oxide-SiN-Al<sub>2</sub>O<sub>3</sub>-TaN), nano-crystal and FinFETs, were proposed to extend the limitation.

Based on the fact that silicon nitride contains intrinsic defects that trap charges, SONOS uses silicon nitrite to replace the silicon used to build a memory cell's floating gate structure as shown in Fig. 1.2 (b). It helps to reduce the thickness of gate from about 1000 angstroms to as small as 100 angstroms - thus allowing it to reduce the size and voltage requirements of Flash cells without taking a hit in performance and reliability (White, et. al, 2000). However with thin tunneling oxide (2-3 nm) the stored charge induces a moderate electric field that is sufficient to cause substrate hole direct tunneling. There is also evidence that electron may tunnel from the nitride trap to the Si/SiO<sub>2</sub> interface trap. Thus, data retention is difficult to achieve both from charge loss and from direct hole tunneling (Lu, et. al, 2006).

To solve the problem addressed above in SONOS, high-k blocking oxide  $(Al_2O_3)$  and TaN gate with high work function are adopted to make a thicker tunneling oxide possible (Shin, et. al, 2005). TANOS (Park, et. al, 2006) is essentially a non-floating gate NAND SONOS. As shown in Fig. 1.2 (c), structure consists of tantalum (metal), aluminum oxide (high k material), nitride, oxide and silicon. However, the data retention is still an issue when the device keeps being scaled. In addition, as MOS devices are scaled, atomic level effects will become increasingly important. Thus, a number of sources of variation become increasingly important.

Another approach, which has been heavily investigated to break the scaling constrains

set by the tunnel oxide thickness, is the nano-crystal device as shown in Fig. 1.2 (d). It breaks up the floating gate into many nano-crystals of polysilicon (or metal) in a floating gate device (Muralidhar, 2003; Salvo, 2003). Electrons are trapped into silicon nanocrystals, which can help to greatly reduce charge leakage through localized oxide defects. Hence the floating gate structures can be built with much thinner tunneling oxide layers, indicating a better scalability. Another major benefit of the nano-floating gate approach is the improved reliability. However, some concerns still remain about the low threshold voltage shift, data retention capabilities, and the intrinsic scalability of nano-crystals.

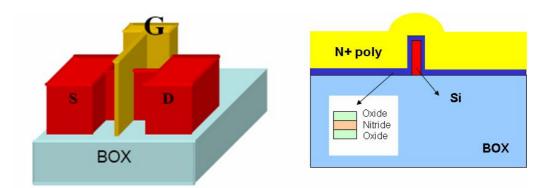

Recently, FinFET SONOS Flash memory was proposed for embedded application (Xuan, et. al. 2003). FinFET concept is a double-gate device proposed to suppress shortchannel effects for sub-100nm CMOS technologies in 1999 (Huang, et. al, 1999). It attracts great interests because of its quasi-parallel structure and relatively simple fabrication process, which helps to reduce the gate length to 10 nm (Yu, et. al, 2002). The combination of FinFET and SONOS is expected to extend the scaling limitation of Flash memory to 22 nm.

Fig. 1. 3 (a) Three dimension view of a FinFET memory device (b) the crosssectional view shows that the N+ poly gate surrounds the ONO stack that is deposited on the two sidewalls and the top surface of the surface Fin.

Beyond 22 nm, the intrinsic limitation of electron tunneling, which reduces the data retention, remains to be the problem for Flash memory technology. Going beyond nanocrystals, in order to offer better performance and scalability, new materials and alternative memory concepts than charge-based storage are mandatory to boost the NVM industry. Generally, three technologies have been widely investigated: Magnetoelectric Random Access Memory (MRAM), Ferroelectric Random Access Memory (FeRAM), and PCRAM (Bez, 2004).

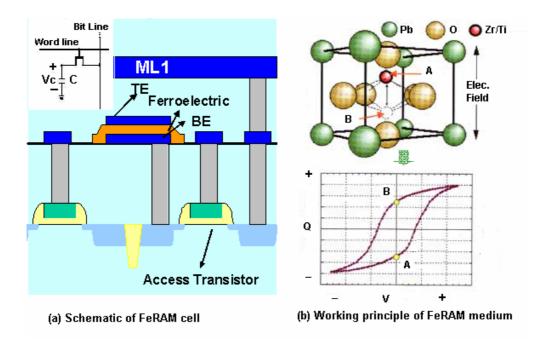

FeRAM has a sandwich structure shown in Fig. 1.4 (a), in which ferroelectric material can be polarized spontaneously by an electrical field. The polarization occurs as a lattice deformation of the cubic form, corresponding to a hysteresis loop, shown in Fig. 1.4 (b). In TbOsZnPt, the most popular ferroelectric material, the Ti atom can be moved by an electric field into two stable positions, inducing two different charges across the ferroelectric capacitor. The difference between the two charges is used to store data. Furthermore, the deformation is permanent unless a high writing voltage is applied to change it. This technology has a quick writing speed and low cost, and a much larger read signal (Jung, 1999). However, the read endurance (electric fatigue) is low and the programming voltage is high.

In contrast to FeRAM, MRAM cell comprises a transistor and a resistor 1T/1R (Durlam, 2003), rather than a capacitor. It can be seen in Fig. 1.5, that the adoption of a tunnel junction is coupled to magneto-resistive materials that exhibit changes in the electric resistance when a magnetic field is applied. The main advantages of this technology are its fast writing speed, well-understood material, and low voltage writing. Moreover, the structure is radiation-hard with an unlimited read/write endurance, which

makes an MRAM suitable for write intensive storage applications. However, its main problems include a high writing current, a small read signal and difficult process integration with CMOS.

Despite the previously mentioned issues, another major challenge for MRAM and FeRAM is the scalability, which is critical to maximize the capacity of the memory chip in the limited space. For FeRAM, the potential limitation is due to the superparaelectric limit. Although, theoretically and experimentally, films made from ferroelectric oxides keep their ferroelectric properties to thickness as low as 2 to 3 nm. Lateral scaling is limited to the size above approximately 20 nm (Zschench, et. al, 2005). High current used to write the device is the limiting factor for the scaling of MRAM. This high current is due to the intrinsic requirement of the magneto-resistive materials (Tehrani, et. al, 1999). Compared to FeRAM and MRAM, the phase change material showed the best scalability. It is believed to be the technology that can lead the NVM technology to 20 nm and below.

Besides the good scalability, the PCRAM is also superior in speed, stability and density. Therefore, it is the best candidate for covering different NVM application fields, matching both high density as well as high performance specifications. The comparison among different NVM technologies is shown in Table 1.1. The PCRAM has shown predominant advantages in scaling and multilevel storage capabilities. This technology, which exploits thermally reversible phase transitions of chalcogenide alloys to store data, will be introduced in detail in the following section.

Fig. 1. 4 The schematic structure and working principles of FeRAM cells.

Fig. 1. 5 MRAM cell in the Magnetic Tunnel Junctions 1-MJT /1-transistor option, schematically showing the programming operation mode.

| Memory<br>Type                       | DRAM            | SRAM                      | Flash-NOR                             | Flash-<br>NAND              | FeRAM                     | MRAM                | PCRAM               |

|--------------------------------------|-----------------|---------------------------|---------------------------------------|-----------------------------|---------------------------|---------------------|---------------------|

| Cell size<br>factor(F <sup>2</sup> ) | 6 – 12          | 90 - 150                  | 8-10                                  | 4                           | 18                        | 10-20               | 4-8                 |

| Volatility                           | Volatile        | Volatile                  | NV                                    | NV                          | NV                        | NV                  | NV                  |

| Endurance<br>write/read              | ∞ /∞            | ∞ / ∞                     | $10^6 \ / \ \infty$                   | $10^6 / \infty$             | $10^{12}/10^{12}$         | $10^{14}/\infty$    | $10^{12}/\infty$    |

| Read                                 | Destructive     | Partially-<br>destructive | Non-<br>destructive                   | Non-<br>destructive         | Destructive               | Non-<br>destructive | Non-<br>destructive |

| Read/<br>Program<br>Voltage          | ~ 1             | ~ 1                       | 2/ 10                                 | 2/18                        | 1.5/ 1.5                  | 3.3/ 3.3            | 0.4/ 1              |

| Program/<br>Erase/ Read<br>speed, ns | 50/ 50/ 8       | 8/ 8/ 8                   | 1us/ 1-<br>100ms<br>(block)/ 60<br>ns | 1 ms/ 1-<br>100ms/ 60<br>ns | 80/ 80/ 80                | 30/ 30/ 30          | 50/ 50/ 50          |

| Direct over-<br>write                | Yes             | Yes                       | No                                    | No                          | Yes                       | Yes                 | Yes                 |

| Bit/byte<br>Write/ Erase             | Yes             | Yes                       | Yes                                   | Block erase                 | Yes                       | Yes                 | Yes                 |

| Read<br>dynamic<br>range<br>(margin) | 100-<br>200mV   | 100- 200mV                | Delta<br>current                      | Delta<br>current            | 100-<br>200mV             | 10-40%R             | 100XR               |

| Programming<br>energy                | Medium          | Medium                    | High                                  | Low                         | Medium                    | Medium              | Low                 |

| Transistor                           | Low performance | High<br>performance       | High<br>voltage                       | High<br>voltage             | Low performance           | High<br>performance | High<br>performance |

| CMOS logic compatibility             | Bad             | Good                      | Ok, but<br>High V<br>need             | Ok, but<br>High V<br>need   | Ok, but<br>High V<br>need | OK                  | Good                |

| New material                         | Yes             | No                        | No                                    | No                          | Yes                       | Yes                 | Yes                 |

| Scalability<br>limit                 | Capacitor       | 6T/ 4T                    | Tunnel<br>oxide/ HV                   | Tunnel<br>oxide/ HV         | Polarizable<br>capacitor  | Current density     | Lithography?        |

| SER<br>susceptibility                | Yes             | Yes                       | No                                    | No                          | Yes                       | No                  | No                  |

| Relative cost<br>per bit             | Low             | High                      | Medium                                | Medium                      | High                      | Medium              | Low                 |

Table 1.1 Performance comparison between volatile memory (DRAM and SRAM) and NVM (Flash, FeRAM, MRAM and PCRAM) devices.

\*Cells highlighted in yellow are the superior properties among all memories listed above

## **1.2 Phase Change Random Access Memory**

### **1.2.1 Electrical Switching in Chalcogenide Glasses**

Studies on the electrical switching in chalcogenide glasses were started in the 1960s (Ovshinsky, 1968). Currently, it is widely used in different technologies, such as sensors

and semiconductor memories. It has been a common practice to separate the switching into two classes according to whether the high resistance amorphous state can be resuscitated after the low resistance state has been maintained for a given length of time. The first type, threshold switching, is a field-assisted transition, which makes an amorphous semiconductor switch from a highly resistive to a conductive state when a threshold voltage is reached. Once the amorphous resistivity drops, the current flowing through the device may heat up the device and lead to a second reversible transformation, called memory switching, corresponding to the phase change transition from the amorphous to the crystalline state.

Threshold switching was firstly discovered by Ovshinsky in 1959 (Ovshinsky, 1959). He succeeded in making a switch based on a tantalum film, which had an amorphous layer of tantalum oxide about 900 Å thick. Switching occurred when the film was sufficiently polarized. It is characterized by a snap-back effect in a IV curve and largely reduced resistance after switching as shown in Fig. 1.6. However, the low resistance conduction state needs to be maintained by a sustaining current. Since this state is reached when a threshold voltage is achieved, it is called threshold switching.

Both the physical mechanism and the nature of threshold switching have been debated for years. However, recently, Redaelli, et al investigated threshold switching in amorphous chalcogenide materials through modeling and experiments (Redaelli, 2004). Their numerical simulation provides a quantitative description of the current-voltage curve of the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> resistor, which is in close agreement with measurements performed on test devices. Their experimental data demonstrated the electronic nature. The physical mechanisms responsible for switching to the highly conductive state are discussed in their paper. At equilibrium state, the conductivity of  $Ge_2Sb_2Te_3$  is p type with the lone-pair band located near the valence band edge and extending for a bout 200meV. At low voltages, electron recombination takes place and quasi-Fermi levels remain close to their equilibrium positions. Structural defects along the Te-Te chains in the amorphous  $Ge_2Sb_2Te_5$  giving a high density of donor/acceptor defect pairs. As the voltage across the cell increases, so do the carrier densities, the electron generation rate will be exponentially increased. As the bias rises, it is more and more difficult for the recombination to balance generation. The critical point is reached at V<sub>th</sub>. Increasing the bias above V<sub>th</sub>, the electron recombination rate can not balance the generation anymore, and the only way to reach a new steady state condition is to decrease the voltage drop across the device, thus to reduce the generation rate. In this case, the generated carriers have filled all the traps, the electron quasi-Fermi level moves close to the conduction band, thus increasing the free electron carrier concentration and reducing the material resistivity. The electron generation is therefore mainly sustained by the high free carrier concentration, when the voltage drops, the electronic switching snap-back takes place.

Fig. 1. 6 Electrical threshold switch in phase change material.

Different from threshold switching, the memory switching does not require a sustaining current because the resistance drop during memory switching is caused by a change in the material's atomic structure (Fig. 1.7). These different atomic structures have different physical properties, such as electrical conductivity. Relative to the amorphous state, the crystalline state has a lower resistance. It was initially obtained by the use of a suitable metalized electrode. The result was demonstrated at a lecture given at the Detroit Physiological Society Meeting in the 1959 (Ovshinsky, 1959). A pulse of one polarity set the memory, and a pulse of different amplitude or opposite polarity shut it off. Consequently, the devices can remain indefinitely in either the ON or OFF states without any need for sustaining energy input. The ON state (low resistance) is normally the crystalline state with an ordered atomic structure, while the OFF state (high resistance) is normally the amorphous state with a disordered atomic structure. Generally speaking, the basic difference between two kinds of electrical switching is whether the atomic structure is changed during the switching.

Fig. 1. 7 Phase change process of the chalcogenide material.

#### **1.2.2 Principles of PCRAM**

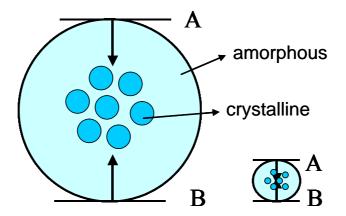

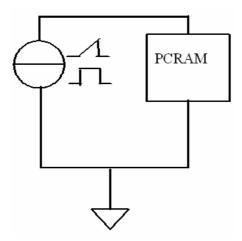

The most prominent use of electrical switching is PCRAM technology that is based on a rapid reversible phase change effect in chalcogenide glasses. The most commonly used phase change material is Germanium-Antimony-Tellurium (GeSbTe) alloy, which belongs to the same material family used in optical re-writable discs. During the operation, phase change material changes between its amorphous and crystalline states by electrical pulses. The rapid and reversible structural change results in a change in material resistivity. The transition from the low conductive amorphous state to the high conductive crystalline state is generally referred to as SET, while the transition from the high conductive crystalline state to the low conductive amorphous state is referred as RESET. The small volume of phase change material in the active region acts as a programmable resistor. Its high and low resistances are measured and recorded as data "0" and "1".

To switch to the amorphous state, a short and high RESET current pulse increases the temperature to above melting temperature. After the pulse, the molten state cools rapidly  $(10^9 \text{ K/s})$  and is quenched into the amorphous state. To convert the material back into the crystalline state, a long and low SET current pulse is used to heat the material to above its crystallization temperature (but below its melting temperature). The duration for the SET pulse should be longer than that required by the material-dependent crystallization. A much lower current with little Joule heat is used for reading the cell. The electrical properties of PCRAM are shown in Figure 1.8. In view of the high amorphous resistance, one would expect to need very long SET voltage pulses to dissipate enough energy to induce the crystallization. Therefore, it is critical that the phase-change material is able to conduct 'threshold switching'. This means that when the electric field over the

amorphous volume exceeds the threshold field, highly conductive filaments are formed within the amorphous material. Based on these filaments, Joule heat will be rapidly generated, inducing the desired phase transition at relatively low voltages.

PCRAM cells can be programmed to intermediate resistance values that can be used for multi-state data storage. Since the energy required for phase transformation decreases with cell size, the write current scales with cell size, thus facilitating memory scaling. PCRAM devices have fast access time, long endurance, and good data retention.

Fig. 1. 8 Electrical properties of PCRAM devices.

The most popular structures of PCRAM memory cells are shown in Fig.1.9. The conventional structure shown in Fig. 1.9 (a) is vertical type. The phase change material is sandwiched between two metal electrodes. Electrical pulses are applied to provide the energy for the crystallization and amorphizing processes. Rather than taking place in the whole phase change film, the phase change only occurs in the active region, which is defined by the area of the bottom electrode. Because of the ultra small contact interface

between the phase change material and bottom electrode, there is a very high current density in the active region, which acts as a programmable resistor.

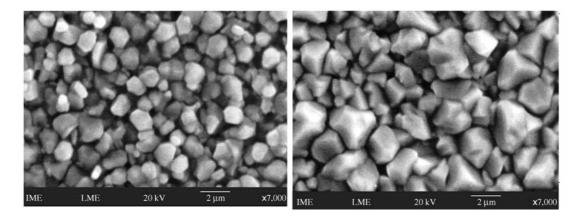

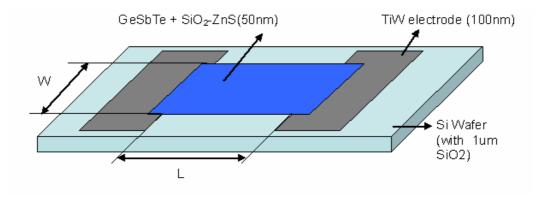

A recent advanced line-type PCRAM structure as shown in Fig. 1.9 (b) has attracted great interest (Lankhorst et.al, 2005). This line-type PCRAM has an ultra-thin line of phase change material surrounded by a dielectric (SiO<sub>2</sub>). An electric current is used to heat the material to its phase-change temperature, where it switches reversibly between the crystalline and amorphous phases. This structure has three advantages (Wuttig, 2005). Firstly, it allows the removal of the electrodes from the active region, hence the constraints on the thermal stability of electrode does not exist any more. Secondly, because the active region is surrounded by the dielectric, which has a lower thermal conductivity, this line-type PCRAM dissipates less power and current. Thirdly, the fabrication is with less additional lithography steps compared to vertical structure. However, the ultra-thin films used in line-type PCRAM may bring the problems to the device reliability when the high speed and large overwrite cycle are required by certain application.

Fig. 1. 9 Vertical (a) and line-type (b) PCRAM memory cells.

#### 1.2.3 Studies on PCRAM Technology

The early studies on PCRAM technology between 1960s and 1980s mostly focused on the physical nature of the threshold switch. Many researchers supported the idea that threshold switch was essentially a thermal effect (Popescu, 1975; Owen, et.al, 1979). Later, Adler's model suggested that the generation of the carrier, which was driven by an electrical field, induced the switching (Adler, et.al, 1978, 1980). More recently, a breakthrough was made through modeling and experiments based on Adler's research (Pirovano, et.al, 2004). It was reported that, during process, carrier concentration competed with a strong Shockley–Hall–Read (SHR) recombination via localized states was proven by the modeling and experiments.

With regards to memory switching, the investigation of physical mechanisms and models mainly began in 1990s. This was followed by the thorough exploration of the crystallization behavior of chalcogenide material and the crystalline structures (Jeong, et.al, 1999; Senkader and Wright, 2003; Alexander, 2004). Two crystalline phases: Face-Center-Cubic (fcc) and Hexagonal-Closed-Packed (hcp), were reported to exist in the GeSbTe material. In fact, it was postulated that fcc is the dominant phase in PCRAM because with an anealing rate around  $10^9 \,^{\circ}$ C/s generated by nano-second electrical pulses, only the amorphous to fcc transformation is allowed (Chiang, 1999).

In 1990s, with the great success of optical discs based on the use of chalcogenide materials and the intense need from portable electronic device markets, PCRAM became a hot topic again. Researchers became eager to change this technology from single memory cell to embedded/stand-alone memory chips (Tyson, et.al, 2000; Lai and Lowery, 2001; Takaura, et.al, 2006; Bedeschi, et. al, 2004; Ahn, et. al, 2004). Based on the

development of memory chips, reliability (Pirovano, et.al, 2004), process compatibility (Hwang, et.al, 2003) and scalability (Pirovano, 2003) became the topics for PCRAM researchers. Most recently, more innovative PCRAM ideas have emerged; one example is the lateral phase change memory cell, which can be programmed by both optical and electrical pulses (Brian, 2007). In addition, it was found that the structural phase of gallium nanoparticles could be switched by optical excitation and read via their cathodoluminescence (CL) when excited by a scanning electron beam (Denisyuk, et. al, 2007). At the same time, reports have been published on conventional material engineering for the PCRAM technology (Feng, et. al, 2007; Byoung, et.al. 2007), device engineering (Rao, et. al, 2007) and multilevel storage application (Rao, et. al, 2007; Dong, et. al, 2007) were also reported.

As the basis for memory technology, the development of innovative phase change memory cells is still the focus for researchers. The material engineering has been the most important approach. Doping of Bismuth (Yeo, et. al, 2006), Nitrogen (Horii, 2003; Seo, 2000), Oxygen (Matsuzaki, et.al, 2005) and Si (Feng, et. al, 2007) into the chalcogenide materials has been found to be helpful in reducing programming current and enhancing reliability. Studies on the better performance of other materials, such as Superlattice-like phase change structure (Chong, et.al., 2002), AgInSbTe (Iwasaki, et.al, 1992), GeTeAsSi (Bunton, 1973), GeTeBi (Bhatia, 1995), GeSbCu/Ag (Ramesh, 1999), GeTeAs (Tsendin, 2001), In-Te (Rajesh, 2003), AsSbTe (Nakayama, 1993), SeSbTe (Nakayama, 2003), PbGeSb (Saheb, 2003), SnGeSbTe (Song, et.al., 2007) have also been undertaken. Recently, after finding the criterion facilitates the search for new phase change materials (Welnic, et. al., 2006), Wuttig took a big step towards the ability to

18

design novel phase-change materials (Wuttig and Yamada, 2007; Wuttig, et.al., 2006). Phase change magnetic material is also proposed for wider application (Shi, et. al., 2007). Engineering of device structure has been proposed to another important approach. Ringtype contact (Chang, et. al, 2005) helped to improve the reliability. Edge contact (Ha, et.al, 2003) has been reported to reduce the programming current. In addition, trench structure (Pellizzer, et.al, 2004) has been proposed to optimize array density and cell performance. Another proposal was for the inclusion of an additional tungsten heater (Takaura, et.al, 2003) for low-power, high stable and short-read-cycle operations.

### **1.3 New Classification of Scaling Limitation of PCRAM**

Lithography technology had been believed to be a scaling limitation for the PCRAM technology for years (Lai, 2001). However, with fast development of advanced lithography technologies, the transistor and device size could reach 20 nm and below. At such a small space, the limitations due to the nano-effect in the materials will become more and more important. First of all, the phase change happens between amorphous state and crystalline state: the former one is short-range ordered, long-range disordered, while the latter one is both short-range and long-range ordered. When the memory cell shrank to the atomic short-range of the phase change material, which is few nanometers, the structural difference between amorphous state and crystalline state becomes unobvious, then further affect the data storage of PCRAM devices. Secondly, various nano-effects, both in the phase change material or at the interface of the devices, would affect the device performance when the memory cell size reaches nano-scale. Therefore, the more broad study of scalability limitations in PCRAM, especially at nano-scale, are

necessary. The scaling limitations for PCRAM include four categories and can be defined as (1) lithography technology, (2) physical limitation of phase change materials in PCRAM, (3) thermal-cross talk among memory cells and (4) current limitation of memory cells.

Although semiconductor lithography was developed in 1960s, the basic equations governing the imaging process have been known for about a century. The resolution of any optical tool is limited by the wavelength of the light source and the numerical aperture of optical lens. It was believed that the lithography technology faced great challenges below 32 nm because of wavelength limitations (Hirose, et al., 2002). Ultraviolet, deep ultra-violet, extreme ultra-violet, electron beam and X-ray are believed to be the alternative technologies for optical lithography (Ito and Okazaki, 2000). Besides the optical approaches, immense lens (Kunz, et.al, 2003), nano-printing (Zhao, et.al, 1997) and near-field optical microscopy (Wang, et.al, 2005) are emerging to reduce the critical size.

Physical limitation of phase change materials in PCRAM refers to the limitation directly caused by certain physical mechanisms that disable the expected phase change in PCRAM devices. A good example is the minimum size requirement on critical nucleus, below which, the crystallization would not happen. However, before scaling to the size of critical nucleus, phase change material would face other limitations caused by the diffusion, stress or phase separation. Till now, to the best of our knowledge few researches were on this topic. Some studies do note that the crystallization would be different in ultra-thin films (Martens, et.al, 2004; Miao, et.al, 1999; Raoux, et.al, 2006). But the minimum size at which phase change material would not function in typical

PCRAM operation is still an open issue. This thesis aims to focus on this topic in chapter 2 and 3.

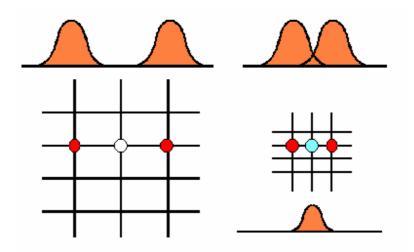

Thermal cross talk refers to the thermal disturbance among adjacent memory cells. Because memory switching can be induced thermally, thus the heat dissipated from adjacent cells could cause the data to be lost. As shown in Fig. 1.10, when the distance of adjacent cells is big enough, the heat dispersed from neighboring memory cells would not accumulate enough to affect stored data. However, with the increase of memory array density, the heat profile would overlap seriously, and it might change the phase of the phase change material in the center cell and change the data. Simulation studies have shown that below 65 nm, thermal cross talk would not affect the data retention time of PCRAM cells (Pirovano, 2003; Lai, 2003).

Fig. 1. 10 Thermal cross talk in the PCRAM when the density of memory array increases.

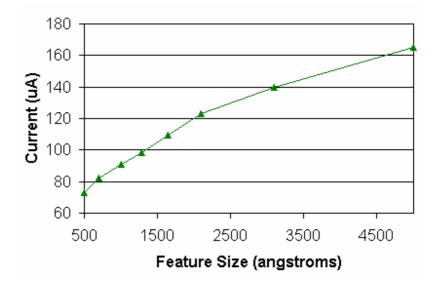

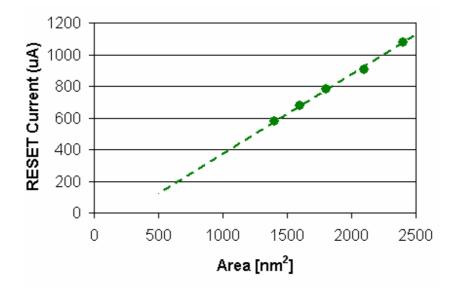

Current limitation refers to the relatively high RESET current in PCRAM memory cells. High programming current can increase the power consumption and reduce the memory density. Because every single memory cell needs a transistor as the selective element, which can support 1 mA reset current should occupy a very large area (Fig. 1.11). For instance, the maximum current controlled by the smallest transistor at 0.35  $\mu$ m technology node is only around 140  $\mu$ A (Tyson, et al., 2000). Material engineering, such as nitrogen doping introduced previously, is a way to reduce the current. Device engineering, edge contact (Ha, et.al, 2003) was also proposed to minimize the programming area (Fig. 1.12), thus reducing the RESET current (Fig. 1.13). However, the contact of the bottom electrode edge was not satisfactory for reliable and long-cycle programming.

Fig. 1. 11 Maximum current by a minimum size MOS transistor.

Fig. 1. 12 Edge contact phase change memory cells (Ha, 2003).

Fig. 1. 13 RESET current scaling with the contact area scaling of a single PCRAM memory cell.

## 1.4 Objectives

This thesis aims to study the scalability limitations of PCRAM. In the previous

sections, four kinds of limitations for PCRAM scaling were proposed: lithography technology, physical limitation of phase change materials, thermal-cross talk among memory cells and current limitation of PCRAM cells. Because lithography and thermal cross talk has been widely studied by researchers from different area and achieved great progress, this work would mainly focus on the other two limitations, physical limitation of phase change material and current limitation of PCRAM cells. Their root causes are to be studied by the research on materials and on device structure engineering. The solutions for extending these limitations will also be provided.

The objectives of this thesis are listed below:

(1) Studying the physical limitation of phase change material in PCRAM based on proposed classification and providing solutions for extending these limitations

(2) Investigating the thickness dependent nano-crystallization of phase change materials limited by interfaces and its effects on the PCRAM performance

(3) Exploring advanced phase change material structures to reduce the current

# **1.5 Organization**

To investigate the scaling limitations of PCRAM technology, this thesis elaborates on the physical limitation of the phase change materials and the current limitation of memory cells, based on the previously proposed classification.

Chapter 2 focuses on exploring the physical limitation of phase change material in PCRAM technology. To provide a comprehensive analysis of the limitation, three categories of phase change processes are proposed. Theoretical and experimental researches in different categories are carried out. Additionally, the solutions for extending physical limitation are explored. In the study of physical limitation in ultra-small size PCRAM cells (2-3 nm), a thermal electrical method is developed to simplify this 3D problem to thickness-dependent issue, which is only considered at thickness direction, to simplify the experiments simple and with efficiency.

The research in Chapter 2 proves that the interfaces have great effects on the crystallization process. Hence Chapter 3 focuses on the interface-affected nano-crystallization. The in-situ thermal electrical measurement developed in the Chapter 2 is used to study the crystallization in ultra-thin films to prove that it is thickness dependent. Kinetics, including the crystallization mechanism, the corresponding activation barrier and the Avrami coefficient are investigated in Chapter 3.

In Chapter 4, an advanced material structure, known as the superlattice-like (SLL) phase change material structure is explored in details. The electrical, crystallization and thermal properties are studies based on different artificial structures.

To demonstrate the performance of SLL structure at chip level, the development of a 128-bit SLL\_PCRAM is to be discussed in Chapter 5 and 6. Chapter 5 introduces the integrated circuit design, while Chapter 6 presents the fabrication and testing of this design. Finally, the current reduction capability and the superior performance of 128-bit SLL\_PCRAM will be demonstrated.

Chapter 5 also introduces the development of the macromodeling of a PCRAM memory cell into the integrated circuit design. Furthermore, it provides a description of the circuit of the SLL\_PCRAM chip, such as the architecture, blocks, simulation and layout.

In Chapter 6, both conventional Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> and SLL structure PCRAM are fabricated

for comparison. These chips are tested on a self-developed testing bench to measure the electrical properties, stability, W/R cycles and other memory characteristic parameters. It aims to show that a SLL structure PCRAM has the advantages of low current and good overall performance.

Chapter 7 summarizes the research findings of this dissertation, ranging from the study of basic material to stand-alone chip development. The results in this dissertation should provide a reference on for the study of scalability of PCRAM technology.

# CHAPTER 2 PHYSICAL LIMITATION OF PHASE CHANGE MATERIALS IN PCRAM

Physical limitation of phase change materials in PCRAM is one category of the scalability limitations of PCRAM technology proposed in this thesis. In this chapter, it aims at three aspects in the study of the physical limitations of phase change materials in PCRAM: (1) categorizing the physical phase change process to explore the limitations; (2) investigating the reasons of the limitations; (3) providing solutions to extend the limitations.

### **2.1 Introduction**

Traditionally, it was widely accepted that PCRAM technology is only limited by the lithography process (Lai, 2001). Hence most studies focused on improving the lithography technology. Following the fabrication of 180-nm PCRAM by Intel in 2001 (Lai, 2001), Samsung successfully developed a 90-nm node PCRAM chip (Takaura, 2006). Various advanced lithography technologies, such as the Electron Beam (Vieu, 2000) and Near-field Optical Microscopy (Wang, et.al, 2005), have also been used to fabricate PCRAM cells of a smaller size than 50 nm.

In fact, in Chapter 1, it has been proposed that lithography technology is only one of the four categories of scaling limitations of PCRAM technology. With the emergence of advanced lithography tools, other limitations, such as physical limitation of phase change materials, are likely to become more and more important for the PCRAM research. In the PCRAM application, the physical limitation of phase change materials in PCRAM is considered as the minimum volume of the phase change material, which could achieve stable and reversible phase change. It can be affected by various factors: the material used, the capping material, the diffusion or environment radiation. However, few studies have so far focused on the physical limitation of phase change materials. Studies based on in-situ X-ray diffraction measurement have reported that a thickness of 3.6 nm is the limitation for the amorphous-fcc transition of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin films capped by Al<sub>2</sub>O<sub>3</sub> (Raoux, et. al, 2006). It is also found that Si and Ge have failed to show crystallization at very high temperatures with thin films of 2 nm thickness (Zacharias et. al, 1999; Williams et.al, 1990). In addition, an effective interfacial energy model was proposed for the physical limitations of Si and Ge. Thus Zacharias' work calls for further research on interface-affected phase change in chalcogenide glasses.

# 2.2 Three Categories of Phase Change for a Study on Physical Limitation