# INSTRUCTION AND DATA CACHE MODELING FOR TIMING ANALYSIS IN REAL-TIME SYSTEMS

# YANHUI LI

NATIONAL UNIVERSITY OF SINGAPORE

2008

# INSTRUCTION AND DATA CACHE MODELING FOR TIMING ANALYSIS IN REAL-TIME SYSTEMS

#### **YANHUI LI**

(B.Eng., NORTHEASTERN UNIVERISTY)

#### A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

NUS GRADUATE SCHOOL FOR INTEGRATIVE

**SCIENCES AND ENGINEERING**

NATIONAL UNIVERSITY OF SINGAPORE

#### **ABSTRACT**

Caches in Embedded Systems improve average case performance, but they are a source of unpredictability, especially in the worst case software timing analysis with the consideration of data caches. This is a critical problem in real-time systems, where tight Worst Case Execution Time (WCET) is required for their schedulability analysis. Several works have studied the data cache impacts on the WCET of programs, but they can only handle programs with no input-dependent data accesses.

To provide an efficient and accurate analysis for input-dependent data caches, we develop classified cache architecture and a WCET framework for the architecture. Our work classifies predictable and unpredictable accesses, then allocates them into predictable caches and unpredictable caches accordingly, and uses CME (Cache Miss Equations) and our reuse-distance-based algorithm for their timing analysis respectively. Compared with simulation, our analysis framework produces a very good WCET tightness, and our architecture creates almost no hardware overhead or performance degradation. In addition, we examine NP-completeness for theoretical support and proved WCET analysis is NP-complete. We also explore data allocation techniques to improve system performance, and our algorithm improves cache hit ratios efficiently according to our experimental results.

#### Keywords:

WCET, Cache, Real-time System, input-dependent data access, NP-completeness, System Performance

#### **ACKNOWLEDGMENTS**

This work is mainly carried out in Signal Processing and VLSI Lab, Department of Electrical and Computer Engineering, National University of Singapore, under research scholarship from National University of Singapore. Chapter 4 is mainly carried out in Computer Engineering and Networks Laboratory, ETH Zurich, under scholarship from NNCR MICS<sup>1</sup>.

I would like to express my deep gratitude to my advisors: Dr. Ha Yajun and Dr. Tay Teng Tiow. I sincerely thank them for many insightful discussions, continuous motivation and constant patient guidance on my research. I am actually guilty that I occupied much discussion time of Prof. Dr. Ha. Thank you!

Many colleagues and groups have contributed to this work through discussions, reviews, questions or other support. I benefited a lot from the weekly seminars of our research group under guidance of Dr. Ha Yajun. It has been an essential discussion forum for us to exchange ideas and get inspired. I have practiced and learned much from presenting my work and meditating on the talks from our group members. I would like to take the chance to thank: Chen Xiaolei, Yu Heng, Shakith Devinda Fernando, Zhang Wenjuan, Lok Weiting, Akash Kumar, Dong Bo, Pu Yu and many more. I also would like to thank the embedded systems research group under guidance of Dr. Samarjit Chakraborty and Prof. P.S. Thiagarajan from School of Computing, National University of Singapore. I

<sup>&</sup>lt;sup>1</sup> NNCR MICS: http://www.mics.org/

attended their seminars every week, which are both useful and interesting, I would certainly also miss this great forum.

I would like to take this opportunity to thank the National University of Singapore for funding me with research scholarship and for providing such an excellent environment and services. My thanks also go to the administrative and support staff in Department of Electrical and Computer Engineering, NUS.

I thank all my friends for having a joyful time and their constant support: Zou Xiaodan, Tian Feng, Tian Xiaohua, Wei Ying, Jiang Jing, Chen Jianzhong, Lahlou Kitane Driss, Wu Liqun, Yu Rui, Hu Yingping, Xu Xiaoyuan, Cheng Xiang, Tan Jun, Zhang Fei, He Lin, Benoit Mortgat, Suybeng Voreak, and many other friends. Apart from being good friends, they were extremely supportive and were always there with me when I need accompany. I would also thank many friends for keeping in touch, sharing daily chaos, motivating me and pretending to be interested in my research: Zhao Yi, Wang Fumin, Hao Lijie, Yang Zhaohui, Zhou Haihua, Wu Xinhui and many others.

I would like to thank my parents, Wenwu and Guiyun, and my brother Li Lei for their love and support. I am always grateful for their encouragement and support for my academic choice and during my entire education and life.

And finally thanks to anyone who knows deep research, never underestimate the power of your encouragement.

# **TABLE OF CONTENTS**

| ABSTRACT                                                            | I    |

|---------------------------------------------------------------------|------|

| ACKNOWLEDGMENTS                                                     | II   |

| TABLE OF CONTENTS                                                   | IV   |

| LIST OF TABLES                                                      | VI   |

| LIST OF FIGURES                                                     | VII  |

| LIST OF ABBREVIATIONS                                               | VIII |

| SUMMARY                                                             | IX   |

| CHAPTER.1 INTRODUCTION                                              | 1    |

| 1.1 REAL-TIME EMBEDDED SYSTEMS                                      | 4    |

| 1.1.1 Functional Behavior Requirements                              |      |

| 1.1.2 Timing Behavior Requirements                                  |      |

| 1.1.3 Other Requirements                                            |      |

| 1.2 MEMORY HIERARCHY IN REAL-TIME EMBEDDED SYSTEMS                  |      |

| 1.2.1 Why Cache Memories and Memory Hierarchy?                      |      |

| 1.2.2 Cache Memories                                                | 9    |

| 1.2.3 Difficulty in Analyzing Timing Behavior of Caches and Systems | 12   |

| 1.2.4 Importance of Analyzing Timing Behavior of Caches             | 13   |

| 1.3 WCET ANALYSIS                                                   |      |

| 1.4 DATA MEMORY MANAGEMENT                                          | 17   |

| 1.5 Contributions                                                   | 18   |

| 1.6 ORGANIZATION OF THESIS                                          | 19   |

| CHAPTER.2 LITERATURE REVIEW                                         | 21   |

| 2.1 WCET Introduction                                               | 22   |

| 2.1.1 Exhaustive Simulation Approach                                |      |

| 2.1.2 Static WCET Analysis Approach                                 |      |

| 2.2 THREE PHASES OF WCET ANALYSIS                                   | 23   |

| 2.2.1 WCET Calculation Approaches                                   | 26   |

| 2.2.2 Microarchitecture Modeling                                    | 28   |

| 2.2.3 Flow Analysis                                                 | 30   |

| 2.3 RELATED WORKS ON STATIC WCET ANALYSIS                           | 30   |

| 2.3.1 Related Works on Micro-architecture Modeling                  | 31   |

| 2.3.2 Related Works on Flow Analysis                                |      |

| 2.3.3 Related Works on WCET Calculation                             |      |

| 2.4 CACHE TIMING ANALYSIS                                           |      |

| 2.4.1 Instruction Cache Analysis                                    |      |

| 2.4.2 Data Cache Analysis Progress and Current Situation            |      |

| 2.4.3 Input Independent Data Cache Analysis                         | 38   |

| 4.                                                                   | 4.4 Input Dependent Data Cache Analysis                                                                                                                                                                                                                                                         | 39 |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5                                                                  | OUR WCET ANALYSIS FRAMEWORK OVERVIEW                                                                                                                                                                                                                                                            |    |

| 2.6                                                                  | OUR UNDERLYING ARCHITECTURE MODEL                                                                                                                                                                                                                                                               | 45 |

| CHAP                                                                 | TER.3 CACHE TIMING ANALYSIS                                                                                                                                                                                                                                                                     | 46 |

| 3.1                                                                  | PRINCIPLE OF CACHE-AWARE WCET ANALYSIS                                                                                                                                                                                                                                                          | 47 |

| 3.                                                                   | 1.1 More Predictable Cache Architectures                                                                                                                                                                                                                                                        | 47 |

| 3.                                                                   | 1.2 Cache Miss Equations (CME)                                                                                                                                                                                                                                                                  |    |

| 3.2                                                                  | OUR WCET ANALYSIS FRAMEWORK                                                                                                                                                                                                                                                                     |    |

| 3.                                                                   | 2.1 Proposed Cache-Classified Memory Architecture                                                                                                                                                                                                                                               | 53 |

| 3.                                                                   | 2.2 Classification and Reuse Distance Extraction                                                                                                                                                                                                                                                |    |

| 3.                                                                   | 2.3 Cache Analysis for Input Independent References                                                                                                                                                                                                                                             |    |

| 3.                                                                   | 2.4 Cache Analysis for Input Dependent References                                                                                                                                                                                                                                               |    |

| 3.3                                                                  |                                                                                                                                                                                                                                                                                                 |    |

| 3.                                                                   | 3.1 Experimental Setup                                                                                                                                                                                                                                                                          | 60 |

| 3.                                                                   | 3.2 Experimental Results and Analysis                                                                                                                                                                                                                                                           | 62 |

| 3.4                                                                  | CONCLUSIONS AND FUTURE WORKS                                                                                                                                                                                                                                                                    | 64 |

| СНАР                                                                 | TER.4 PROVING NP-COMPLETENESS                                                                                                                                                                                                                                                                   | 67 |

|                                                                      |                                                                                                                                                                                                                                                                                                 |    |

|                                                                      | ECHNIOUES FOR PROVING NP-COMPLETENESS                                                                                                                                                                                                                                                           | 69 |

| 4.1                                                                  | TECHNIQUES FOR PROVING NP-COMPLETENESS                                                                                                                                                                                                                                                          |    |

| 4.1 7.<br>4.                                                         | 1.1 Restriction Technique                                                                                                                                                                                                                                                                       | 70 |

| 4.1 7.<br>4.                                                         |                                                                                                                                                                                                                                                                                                 |    |

| 4.1 7.<br>4.<br>4.                                                   | 1.1 Restriction Technique                                                                                                                                                                                                                                                                       |    |

| 4.1 7.<br>4.<br>4.2<br>4.3                                           | 1.1 Restriction Technique                                                                                                                                                                                                                                                                       |    |

| 4.1 7.<br>4.<br>4.2<br>4.3<br><b>CHAP</b>                            | 1.1 Restriction Technique                                                                                                                                                                                                                                                                       |    |

| 4.1 7.<br>4.<br>4.2<br>4.3<br><b>CHAP</b><br>5.1                     | 1.1 Restriction Technique  1.2 Local Replacement Technique PROVING WCET ANALYSIS IS NP-COMPLETE SUMMARY  TER.5 DATA ALLOCATION PROBLEM DESCRIPTION                                                                                                                                              |    |

| 4.1 7. 4. 4. 4.2 4.3 <b>CHAP</b> 5.1 5.2                             | 1.1 Restriction Technique  1.2 Local Replacement Technique PROVING WCET ANALYSIS IS NP-COMPLETE SUMMARY  TER.5 DATA ALLOCATION  PROBLEM DESCRIPTION  DATA MEMORY ALLOCATION FOR SCALAR VARIABLES                                                                                                |    |

| 4.1 7.<br>4.<br>4.2<br>4.3<br><b>CHAP</b><br>5.1                     | 1.1 Restriction Technique 1.2 Local Replacement Technique PROVING WCET ANALYSIS IS NP-COMPLETE SUMMARY  TER.5 DATA ALLOCATION  PROBLEM DESCRIPTION  DATA MEMORY ALLOCATION FOR SCALAR VARIABLES DATA MEMORY ALLOCATION FOR ARRAY VARIABLES                                                      |    |

| 4.17.<br>4.<br>4.2<br>4.3<br><b>CHAP</b><br>5.1<br>5.2<br>5.3<br>5.4 | 1.1 Restriction Technique  1.2 Local Replacement Technique PROVING WCET ANALYSIS IS NP-COMPLETE SUMMARY  TER.5 DATA ALLOCATION  PROBLEM DESCRIPTION  DATA MEMORY ALLOCATION FOR SCALAR VARIABLES                                                                                                |    |

| 4.1 7. 4. 4.2 4.3 <b>CHAP</b> 5.1 5.2 5.3 5.4 <b>CHAP</b>            | 1.1 Restriction Technique  1.2 Local Replacement Technique PROVING WCET ANALYSIS IS NP-COMPLETE SUMMARY  TER.5 DATA ALLOCATION  PROBLEM DESCRIPTION  DATA MEMORY ALLOCATION FOR SCALAR VARIABLES DATA MEMORY ALLOCATION FOR ARRAY VARIABLES EXPERIMENT RESULTS AND CONCLUSION                   |    |

| 4.1 7. 4. 4.2 4.3 <b>CHAP</b> 5.1 5.2 5.3 5.4 <b>CHAP</b>            | 1.1 Restriction Technique 1.2 Local Replacement Technique PROVING WCET ANALYSIS IS NP-COMPLETE SUMMARY  TER.5 DATA ALLOCATION  PROBLEM DESCRIPTION  DATA MEMORY ALLOCATION FOR SCALAR VARIABLES DATA MEMORY ALLOCATION FOR ARRAY VARIABLES EXPERIMENT RESULTS AND CONCLUSION.  TER.6 CONCLUSION |    |

# LIST OF TABLES

| 3.1 Relationship between Cache Miss Types and Reuse Distance | 58 |

|--------------------------------------------------------------|----|

| 3.2 Reuse Distance and Cache Miss Types Example              | 60 |

| 3.3 WCET Analysis Benchmark Profile                          | 61 |

| 3.4 Our Analysis Framework Experiment Results                | 63 |

| 5.1 Data Allocation Benchmark Profile                        | 83 |

| 5.2 Data Allocation Experiment Results                       | 84 |

# LIST OF FIGURES

| 1.1 Examples of Embedded System Applications                     | 2  |

|------------------------------------------------------------------|----|

| 1.2 Structure of Worldwide Electronic Production in 2010         | 3  |

| 1.3 Basic Structure of a Memory Hierarchy                        | 6  |

| 1.4 How Is Data Stored in Main Memory and Cache                  | 10 |

| 2.1 Example with Input Dependent Access (ExchangeSort)           | 40 |

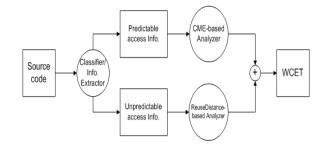

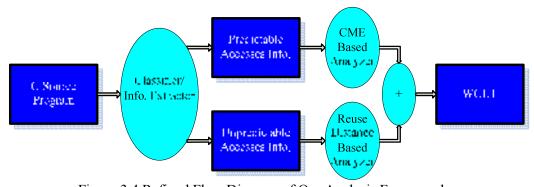

| 2.2 Flow Diagram of the Analysis Framework                       | 44 |

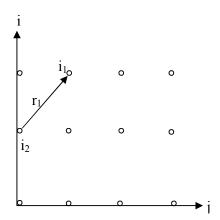

| 3.1 Illustration Example of Iteration Point and Iteration Space  | 49 |

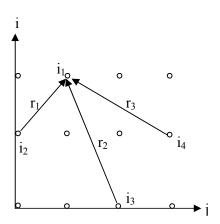

| 3.2 Cache Misses of a Reference along a Reuse Vector             | 51 |

| 3.3 All Cache Misses of a Reference                              | 51 |

| 3.4 Refined Flow Diagram of Our Analysis Framework               | 52 |

| 3.5 Memory Access Classification as Predictable/Unpredictable    | 56 |

| 3.6 Reuse-Distance Algorithm for Input-Dependent Access Analysis | 59 |

| 5.1 Cluster Scalar Variables into Memory Lines                   | 80 |

| 5.2 Assign Memory Location to Scalar Variables                   | 81 |

| 5.3 Cost of Assigning the Start Address of Array u to Addr       | 82 |

| 5.4 Assign Memory Locations to Array Variables.                  | 82 |

# LIST OF ABBREVIATIONS

| 1.  | BB, B       | Basic Block                          |

|-----|-------------|--------------------------------------|

| 2.  | CFG         |                                      |

| 3.  | ILP         | Integer Linear Programming           |

| 4.  | WCET        |                                      |

| 5.  | WCTA        |                                      |

| 6.  | CME         |                                      |

| 7.  | NP-Complete | Nondeterministic Polynomial Complete |

| 8.  | IPET        |                                      |

| 9.  | CSTG        |                                      |

| 10. | AST         |                                      |

| 11. | X3C         | Exact Cover By 3-SETS                |

| 12. | 3DM         | 3-Dimensional Matching               |

| 13. | CNF:        |                                      |

| 14  | SAT         | Satisfiability                       |

#### **SUMMARY**

Caches are small memories embedded close to processors that can improve their average system performance. However, caches incur the timing predictability problem in real-time systems, where the tight WCET (Worst Case Execution time) is required for their schedulability analysis. As it is unaffordable to obtain WCET of a program by exhaustive simulations, the design of efficient and accurate static WCET analysis has been a heated research topic.

To obtain an accurate WCET, past efforts have been made in two directions. One direction tries to develop more predictable new architectures, such as using cache partitioning and cache locking. These approaches require large caches and have not solved the general problem of predicting cache behavior if all tasks shared the cache. The other tries to develop more accurate analysis techniques. Previous analysis techniques focus on modeling instruction caches, and have obtained fruitful results to the extent where instruction cache timing behavior can be accurately modeled and analyzed. However, it remains tough for modeling and analyzing data caches. Very few works have studied data cache impacts on WCET of programs, and they can only handle programs without input-dependent data accesses.

To solve this problem, we develop a new cache-classified architecture. This architecture classifies predictable and unpredictable accesses, and allocates them into the classified predictable cache and the unpredictable cache respectively. For this architecture, we build a WCET analysis framework. Our framework analyses these two classified data cache accesses independently: it uses the CME-based analyzer for analyzing predictable

accesses and our reuse-distance-based analyzer for analyzing unpredictable accesses. Combining the results from the above two parallel analyzers, our framework obtains the desired WCET results. Compared with simulation results, our analysis framework shows that:

- (1) Our analysis is conservative, i.e. it gives a safe upper bound of execution times, and has a low time complexity;

- (2) Our analysis framework outputs an appreciable WCET tightness;

- (3) Our new architecture gives little overhead in terms of complexity and execution time.

To support the WCET analysis theoretically, we explore NP (Nondeterministic Polynomial)-completeness proving techniques. We prove that the WCET analysis is NP-complete.

In addition, we examine techniques to improve system performance by allocating data in programs to increase their locality. Our goal is to apply data management technology to minimize compulsory and conflict misses in direct-mapped caches. We first cluster data accesses into memory lines based on their space locality, in the way that accesses with high space locality get allocated in the same cache line so that cache compulsory misses get minimized; and then we map these memory lines to cache lines, in the way that memory lines with minimized conflicts share the same cache lines so that cache conflict misses are minimized. Our algorithm demonstrates its good ability in improving the cache hit ratio, especially for codes with much conflicts on the given architecture.

In summary, this thesis provides a comprehensive framework to analyze instruction and data caches for single-task real-time systems with input data dependency, explores the NP-completeness as a theoretical support, and designs a cache conscious data allocation technique to improve the cache performance.

# CHAPTER.1

#### INTRODUCTION

Nowadays, there is an increasing demand of computing devices, with a large portion of them serving as components of other systems. These devices are called *embedded systems*, deployed for the purpose of data processing, control or communication. An embedded system<sup>2</sup> is a special-purpose computer system designed to perform one or a few dedicated functions, often with real-time computing constraints. It is usually *embedded* as part of a complete device including hardware and mechanical parts. In contrast, a general-purpose computer, such as a personal computer, can do many different tasks depending on programming. Embedded systems control many of the common devices in use today.

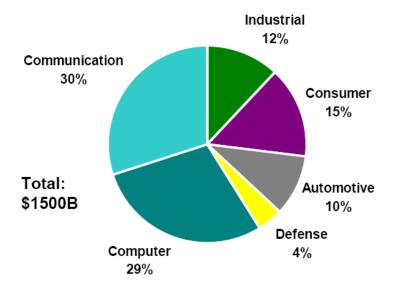

Embedded systems are becoming more and more prevalent in our society and this trend promises to continue in the near future 0. We need not go far to seek examples (Figure 1.1) of embedded systems applications: mission critical systems such as airplane jets, power plant monitoring systems and vehicle engine controllers, communication devices such as cellular phones and consumer electronics such as mobile phones, mp3 players, pacemaker, set-top boxes, to name but a few. Let's have a look at a market forecast (Figure 1.2) to comprehend this trend and also the development trend of embedded systems.

<sup>&</sup>lt;sup>2</sup> http://en.wikipedia.org/wiki/Embedded system

Figure 1.1a Voice Communication System, Figure 1.1b Pacemaker

Figure 1.1c Engine Controllers; Figure 1.1d Airplane Monitor and Control Systems

Source: http://images.google.com

Figure 1.1 Examples of Embedded System Applications

Source: Jean-Philippe Dauvin, MEDEA / DAC, May 2005

Figure 1.2 Structure of Worldwide Electronic Production in 2010 [2]

Figure 1.2 shows the market forecast [2] of the structure of worldwide electronic production in 2010. It tells that 60% of electronic production will be about embedded applications, among which communications occupies the most (30%), while consumer (15%), industrial (12%) and automotive and defense (14%) have similar percentages. These figures demonstrates that the market share for embedded systems is growing and a high portion of industrial research and development activities will be dominated by embedded systems. In order to meet numerous demanding requirements of functional, timing and low power sides, the complexity of embedded systems will inevitably increase.

Because of the steadily increasing number of functional requirements, embedded hardware and software architectures are becoming more and more complex. Usually embedded applications not only need to generate correct results but also have to achieve the results within a given time period. Timing behavior is essential if the application has to react to signals from the environment. And therefore to safely and tightly analyze timing behavior is very important and also challenging for today's complex embedded designs.

#### 1.1 Real-time Embedded Systems

Embedded systems have to satisfy an increasing number of requirements, including both functional and non-functional requirements.

#### 1.1.1 Functional Behavior Requirements

- 1) Correctness: this is a fundamental requirement of an embedded system.

Functional behavior of embedded applications has to be guaranteed in any case.

- 2) Reliability: this requirement depends on the embedded applications. For example, while a system breakdown of a cellular phone is tolerable once a year, a similar rate for safety critical systems like aerospace applications would be disastrous.

- 3) Flexibility: it has two different senses—configurability and reconfigurability. A configurable system can enable the manufacturer to simplify the development for a variety of product lines while a reconfigurable one gives the customer the ability to use a device for different applications. For example, a firmware update is much less expensive than the exchange of hardware components in case software errors are detected.

#### 1.1.2 Timing Behavior Requirements

For most embedded applications, a result has not only to be correct but has to be rendered before a specified deadline. This is the timing behavior requirement, i.e. the system has to interact with the environment in a timely fashion. In literature, these systems are called *real-time systems* and this timely response property is named timing behavior which denotes the time delay a software task takes to finish.

Real-time systems can be further classified into: soft real-time systems and hard real-time systems.

In soft real-time systems, timing behavior is an important aspect but is not essential to correct functional behavior. Occasional misses of deadlines can be tolerated. This kind of deadline-misses would not affect the functional correctness but as a price the quality can be reduced. In other words, the software task could be switched to a different processing mode, which takes shorter time to render a less accurate result. For example, voice communication systems (Figure 1.1a) or multimedia streaming applications can tolerate the loss or delay of a few frames.

However in hard real-time systems, a pre-defined deadline has to be obeyed by the application in order to guarantee the functional correctness. The term deadline denotes the longest acceptable time the computation can take to finish. Any failure to meet the deadlines would violate the timing behavior requirement and affect the functional correctness, and may even cause catastrophic results. This hard real-time system is usually mission-critical systems, such as engine control software (Figure 1.1c, Figure 1.1d) in automotive, flight control software in avionics systems automated manufacturing and sophisticated medical devices such as pacemakers (Figure 1.1b).

#### 1.1.3 Other Requirements

There are also many other requirements of the embedded systems, such as low power consumption, size, weight and design fashion.

Note that in this thesis, we are concerned only with hard real-time systems and focus on timing behaviors of advanced embedded hardware—especially caches.

#### 1.2 Memory Hierarchy in Real-time Embedded Systems

Let's first have a brief look at the properties of memory hierarchy in modern embedded architectures. And then we discuss its impact on the timing behavior of software applications.

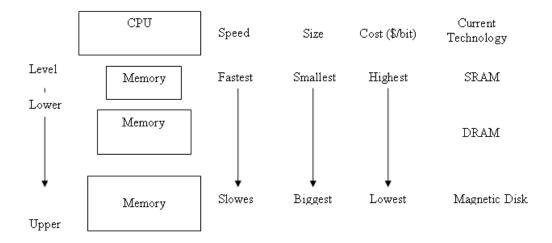

*Memory hierarchy* is a structure that uses multiple levels of memories; as the distance from the CPU increases, the size of the memories and the access time both increase [3]. We have a large variety of storage devices in a computer system, which are organized in a hierarchy (see Figure 1.3) according to either their speed or their cost.

Figure 1.3 Basic Structure of a Memory Hierarchy

Note that in this thesis, we number the memory level lower to higher as distance from CPU increases.

#### 1.2.1 Why Cache Memories and Memory Hierarchy?

Thanks to increasing clock frequencies and the exploitation of parallelism at different levels, microprocessors processing speed continues to increase exponentially at the speed of about 60% per year [4]. However, relatively slow memory access makes processor speed increase meaningless and has become a bottleneck in a general system's performance. Though memory access speed is also increasing exponentially, it is at a much lower increase rate, to be more exact, at increase rate of less than 10% per year for the last twenty years [4].

This leads to the widening gap between processor speed and main memory access speed. The overall effect is called in literature: anti-law of Moore<sup>3</sup> which illustrates that the speed between processor and main memory doubles every two years. The difference between diverging exponentials also grows exponentially. Thus, although the disparity between processor and memory speed is already an issue, downstream someplace it will be a more serious one. Therefore memory has become a primary obstacle in improving system performance, and how to avoid its limiting data transfer between memory and processor has become an intense interest for research works [5].

A dream processor design would be a system consisting of high processor speed and a memory with high capacity and fast speed at lower cost. To achieve this goal, we need to exploit the properties of hardware and software. Besides the gap between CPU speed and main memory speed is widening, there are another two fundamental properties of hardware and software [6]:

(1) Fast storage technologies cost more per byte and have less capacity.

\_

<sup>&</sup>lt;sup>3</sup> Moore's Law: http://en.wikipedia.org/wiki/Moore's Law

(2) Well-written programs tend to exhibit good locality.

These three fundamental properties complement each other beautifully and they suggest a memory hierarchy approach for organizing memory and storage systems. That's why cache is adopted. *Cache* is a small, fast storage device that acts as a staging area for a subset of the data in a larger, slower device. To achieve the low cost as main memory and to achieve fast access speed as cache, caches are embedded between CPU and main memory forming a memory hierarchy.

The fundamental idea of a memory hierarchy is that for each level k, the faster, smaller device at level k serves as a cache for the larger, slower device at level k+1. The reasons why memory hierarchy architecture can render system an illusion memory of large size, fast speed and cheep price are as follows:

- (1) Programs tend to access the data at level k more often than the data at level k+1.

- (2) Thus, the storage at level k+1 can be slower, and thus larger and cheaper per bit.

The main property that makes the memory hierarchy work well in the general case is called *locality*, which states that programs access a relatively small portion of their address space. There are two types of locality: temporal locality and spatial locality.

- (1) *Temporal locality*: a data location tends to be referenced again soon after referenced recently;

- (2) *Spatial locality*: addresses nearby a recently referenced data location tend to be referenced in the near future.

Therefore, memory architecture with high speed, low cost and large storage of the system can be achieved using this memory hierarchy idea consisting of multiple levels memories with increasing size and access time as their distance from the CPU increases.

By implementing the memory system as a hierarchy as in Figure 1.2, the system gives the user an illusion that the user obtains a memory as large as the largest memory in the largest level of the hierarchy, but as if at the access speed of the fastest memory in the smallest level of the hierarchy.

#### 1.2.2 Cache Memories

Cache memories are smaller and faster expensive storage device that acts as a staging area for a subset of the data in a larger, slower device. They are situated between processor and main memory to store the frequently used memory blocks in order to bridge the gap between fast processor speed and slow main memory [6].

#### **Cache Terminology:**

#### (1) Cache blocks:

Caches are built in the unit of cache blocks or cache lines.

In a memory hierarchy of multiple levels, data is copied between two adjacent levels at a time, the lower level (closer to the processor) is smaller and faster than the upper level (farther away from the processor). The minimum unit of information that can be transferred between two adjacent levels is called *a (memory) block or a line*.

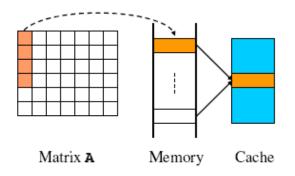

Usually the size of a cache block is the same as the main memory block. Typically in embedded systems, a block size consists of 4 memory words, 8 memory words or 16 memory words. Storing several memory words rather than one in a block is to make advantage of the spatial locality of program accesses (Figure 1.4).

Figure 1.4 How Is Data Stored in Main Memory and Cache

#### (2) Cache associativity:

According to the number of cache blocks in a cache set, there are three cache structures: direct-mapped cache, set associative cache and fully associative cache.

A *cache set* is a set of continuous cache blocks where one main memory block maps to.

A memory block can be placed in any block in the cache set it is mapped to.

- 1) For an *n-way associative cache*, n cache blocks are organized in a cache set.

- 2) In a *direct mapped cache* each cache set has exactly one cache block, e.g. the associativity is one.

- 3) For *fully associative cache*, the whole cache is one cache set.

The relationship between the memory block number, the number of sets in a cache and the set number the memory block can be represented as an equation as follows:

Mapped Set Number = (Block Number) Modulo (Number of Sets)

#### (3) Cache hit and Cache miss:

The memory access has two types of operations: read and write. When the processor requests data (either read or write), the corresponding address of the data is compared from the lower level to higher level to see if there is a match. If the data requested by the processor appears in some block in the lower level, this level has *a hit*. Otherwise, we

have a miss in this level, and the inquiry of the data goes to its next higher level. The hit ratio or hit rate of a cache level is the fraction of memory accesses found in it over in its adjacent upper level. The miss rate is (1 - hit rate), i.e. the fraction of memory accesses not found in the cache.

For a cache miss, we have two types: cold (compulsory and capacity) miss and conflict miss [3].

- 1) Compulsory misses—when a memory word is accessed for the first time;

- 2) *Capacity misses*—when cache data that would be needed in the future are displaced due to the working data set being larger in size than the cache;

- Conflict misses—when cache data are replaced by other data, in spite of the presence of usable cache space.

For example, caches limit blocks at level k+1 to a small subset (sometimes a singleton) of the block positions at level k. Conflict misses occur when multiple data objects all map to the same level k block.

On a cache miss, the needed data is to be placed in the cache by copying from its adjacent upper level. If the placement of the data is to be set in a cache set which is not empty, a cache block may need to be replaced out. But which cache block in the set needs to be replaced out? This also depends on the cache structure.

- For direct mapped cache, it's quite easy to implement, just replace out the cache block to which the requested data is mapped to.

- 2) For set associative or fully associative, there are two block replacement policy: random and LRU (Least Recently Used).

- a) Random replacement policy is to randomly replace out one cache block in the cache set the requested data is mapped to;

b) *LRU replacement* policy is to replace out the cache block which is least recently used among the cache set the requested data is mapped to.

#### 1.2.3 Difficulty in Analyzing Timing Behavior of Caches and Systems

Cache memories hide in part the speed gap between processor and main memory, and to some degree offset the widening speed gap by making use of program locality and by rendering data at fast speed. Therefore, they improve the average performance. Unfortunately meanwhile they complicate timing analysis and incur unpredictable problems of system performance.

The main reason is rooted in caches' probabilistic nature as well as the speed difference between cache and main memory. The time to access data in the cache from the processor is very fast, e.g. a single clock cycle, if the requested data is available in the cache. Otherwise, the cache controller has to request the data from main memory, which takes much longer, typically 20-100 or more clock cycles (as also can been seen in Figure 1.3). As caches are taking advantage of the temporal and spatial locality of programs, caching scheme attempts to capture in cache memory the data and instructions that are most likely to be accessed in the near future. This leads to the probabilistic nature of cache' s hit ratio and thus causing some (possibly transient) uncertainties in the execution times of the tasks. Because of this, caches have become a hindrance in usage and in the timing analysis of real times systems.

Behind this probabilistic nature rooted uncertainty is the very basic: the cache resources are too limited compared to main memory blocks. This resource limitation causes two types of interference.

- Intra-cache interference: interferences between a task's memory addresses in a single tasking environment;

- 2) *Inter-task interference*: interferences between multi-programmed tasks in multi-tasking preemptive environment.

These interference lead to uncertainty of a cache block's content and thus resulting in the unpredictable cache hit or miss.

Therefore, timing behavior of caches gets unpredictable.

In addition, the demanding requirements for embedded systems and the complexity of the software and hardware architecture of embedded systems adds to the challenging performance analysis in real-time systems. And there is great difficulty in estimating the WCET accurately and scheduling tasks properly to meet the system timing requirements.

#### 1.2.4 Importance of Analyzing Timing Behavior of Caches

To cushion the speed gap between slow memory access speed and high processor frequency, caches have been popular in today's embedded systems.

Caches are used to improve the average case timing behavior, but could not guarantee the worst case timing behavior and they also complicate worst case timing analysis. There is one typical saying in literature to represent the importance of worst case performance over average case performance in hard real-time systems: an adult got drown in a lake whose average depth is 0.5 meters.

However, it is essential to be able to accurately measure the timing feature of applications, in presence of cache memories, so as to schedule tasks properly to meet the system timing requirements. There are many computer applications in which computations must satisfy stringent timing constraints, i.e. it must guarantee that those computations must be completed before specified deadlines. Failure to meet the specified deadlines in such applications can lead to intolerable system degradation, and can, in some applications, result in catastrophic loss of life or property. Examples of these systems include embedded tactical systems for military applications, flight mission control, production control, robotics, etc. It is essential to guarantee that critical timing constraints will be met. A safe WCET analysis is essential in guaranteeing real-time performance. To enable caches to be largely adopted in real-time systems, the capacity to analyze their timing behavior has become urgently indispensable.

A conservative approach is to assume all memory accesses being cache misses. This is clearly overly pessimistic; in fact, some of the memory accesses could be determined whether they would be cache miss or hit before running the program in absence of input data. Too pessimistic WCET estimation would cause a waste of hardware resources.

So modeling data cache timing behavior accurately has become a critical issue in WCET analysis.

In the Harvard architecture<sup>4</sup>, a cache is separated for instructions and data, i.e. the architecture would have split instruction caches and data caches.

1) Instruction caches hold only the program code and are only read from the

-

<sup>&</sup>lt;sup>4</sup> http://en.wikipedia.org/wiki/Harvard\_architecture

processor.

2) Data caches hold the data, which are read and written from the processor.

While many researches have been carried out to model the timing behavior of instruction caches effectively, predicting timing behavior of caches remains as a tough job. It's especially difficult to model data cache behavior. Few works have attempted model data caches' timing behavior, but only limited to no input dependent accesses involved. It still remains as one open problem to design an efficient and effective method to model data cache behavior considering input dependent accesses.

Our work is trying to improve this situation and give attempts to model data caches with input dependent accesses.

#### 1.3 WCET Analysis

A hard real-time system usually is a collection of tasks running on a set of hardware resources. Each task can be characterized by a release time, a deadline, and a computation time and every task can repeat periodically or stochastically. WCET analysis is important for the schedulability analysis of real-time embedded systems, which have stringent application constraints compared to other embedded systems in needing the timing correctness on top of functional correctness. This requires that all tasks be scheduled such that all task does not miss their deadlines. This requirement necessitates schedulability analysis which checks whether there exists a schedule for the tasks so that they all finish executions within their deadlines for every release (ready to execute). As a consequence, priori knowledge of the computation time for each task is required. Furthermore, to guarantee that the deadline is met in any circumstance, the WCET should be used as input for the schedulability analysis, making WCET

estimation. To estimate a priori WCET of a given program on a given architecture is called *WCET analysis* in the literature.

It's often quite hard to know an exact WCET of a task and a conservative estimate is often used. However, tight WCET estimates are essential for schedulability analysis as they reduce the waste of hardware resources for a successful schedule.

In this thesis, we study efficient methods for WCET estimations. The WCET to be studied in this thesis is defined as the maximum possible memory access time of a task running on a hardware platform.

There are several points for this definition to be noted.

- 1) This thesis deals with single task real-time systems where one task is executed without interruption. While a task may be interrupted by a higher priority task in multi-tasking real-time systems, it is beyond the focus of our research scope.

- 2) WCET is the longest execution time of a task among all possible sets of data input.

- 3) WCET of a task depends on the underlying hardware architecture.

There are two general approaches to estimate the WCET of a task or program. As we would be dealing with a single task context of WCET determination, we will use the term program instead of task from now on.

1) Exhaustive simulation: to obtain the WCET by actually running the program on the target hardware over all sets of possible data input or on a processor simulator using stimuli data. However, this approach is impossible to guarantee the essential requirement of WCET analysis-safety. Because it's unaffordable to carry out an exhaustive simulation over all possible sets of data input which is

tremendous, but if not simulating all the possibilities the estimated WCET may be underestimated, i.e. estimated WCET does not cover the worst case and therefore is not safe.

- 2) Static analysis: to examine the program, derive its timing properties and makes estimation on the WCET without actually running the program. Static WCET analysis is expected to be:

- a) Conservative (safe): Safety is essential because underestimated WCET may lead to smaller execution time assignment to a task, and thus gets blamed for failure to meet the deadline of the task as opposed to be predicted.

- b) Tight: close to the actual WCET so as to save computation and other resources

- c) Efficient: in both time and space occupation.

Our WCET estimation is the static analysis approach. Please note the first property is compulsory and the latter two are desirable. Our work obeys the three properties. Readers may refer to Section 2.1 in Chapter 2 for more details on WCET estimation.

# 1.4 Data Memory Management

Data allocation is possible because that Code generation in embedded systems can be tuned to the given cache configuration (cache line size, cache size etc). Therefore cache performance can be improved by allocating data in the program in the way that program locality is increased. There have been researches on code placement for improving cache performance [7, 8]. However, [8] only deals with scalar variables, and [7] does not differentiate between scalar and array variables, which may cause failure to exploit array placement based on their index and expression. Our data management strategy

introduces placing scalar variables first and then gives an extension to place array by analyzing the array reference indices.

#### 1.5 Contributions

This thesis is dedicated to obtain tight WCET in the presence of caches in real-time system. This thesis makes several contributions to modeling instruction and data cache timing behavior. Especially we provide a platform that can analyze data cache behavior with input dependency.

We develop a new architecture, which has parallel predictable caches and unpredictable caches. The architecture classifies input-independent and input-dependent accesses and allocates them into predictable caches and unpredictable caches respectively. On top of this architecture, we build our WCET analysis framework. It has two analyzers: one for analyzing input-independent accesses, and another for analyzing input-dependent accesses. For the analyzer of input-independent accesses, we use CME (cache miss equations) for timing analysis; for the analyzer of input-dependent accesses, we develop an algorithm based on the accesses' reuse distances for timing analysis.

We lead the simulation and compare the simulation results with our framework analysis results. Comparison shows that:

- Our analysis is conservative, e.g. determines a safe upper bound of the execution time, and has a low time complexity;

- 2) Our analysis framework produces an appreciable WCET tightness compared with simulation;

- 3) Our architecture caused ignorable overhead in hardware complexity and almost no difference in execution time.

To support our WCET timing analysis theoretically, we examined NP-completeness proving techniques: restriction and local replacement. We present WCET analysis NP-completeness proof using restriction technique.

In addition, we examine data management and devise an algorithm with low complexity to increase program locality to reduce cache misses and improve cache and system performance. We target at minimizing compulsory and conflict misses in direct-mapped cache using data management technology. We cluster data accesses into memory lines in the way that accesses with high spatial locality get allocated in the same line—this is to minimize compulsory cache misses; we then map these memory lines to cache lines in the way that memory lines with minimized conflicts share same cache lines—this is to minimize cache conflict misses. Our experiment shows that we achieved good performance improvement especially for programs with poor locality.

In summary, this thesis provides a sophisticated framework to analyze effects of instruction and data caches for single task real-time systems considering input dependent accesses. It also explores NP-completeness for theoretical supports and data allocation techniques to improve cache performances.

#### 1.6 Organization of Thesis

The rest of the thesis is organized as follows. Chapter 2 gives background information and a literature survey on cache memories, cache timing analysis and WCET analysis techniques. Chapter 3 presents our WCET analysis framework for single tasking real-time systems in presence of instruction and data caches with input dependent accesses. Chapter 4 provides NP-completeness proving technique and proof for WCET analysis

problem. Chapter 5 renders a data allocation algorithm to improve cache and system performance. Chapter 6 concludes the thesis work and points out possible future works.

# CHAPTER.2

# LITERATURE REVIEW

Many embedded systems are safety critical (e.g., automotive controller) and have timing constraints on the execution time of embedded software. *Schedulability analysis* is to verify whether all timing constraints are satisfied for all possible runs of a system, by taking into account the timing constraints and application's parameters such as execution times, deadlines and periods. This would require the input of the execution times of different tasks, thus the accurate estimation of execution time becomes indispensable. As a result, WCET of a program is essential for the schedulability analysis in real-time embedded systems.

WCET analysis computes an upper bound on programs' execution time on particular hardware architecture for all possible inputs. It involves both program path analysis and modeling the timing effects of processor micro-architectural features such as caches, pipelines and branch-predictors.

This chapter surveys the literature of WCET analysis in presence of cache memories. In Section 2.1, we introduce WCET simulation, static analysis and their properties. In Section 2.2, we present three phrases of WCET analysis, among which we focus on the WCET calculation phase and this phase's three approaches (Tree-based approach Pathbased approach Implicit path enumeration approach). In Section 2.3, we present related works on static WCET analysis considering instruction caches, data caches without/with input dependent accesses. In Section 2.4, we introduce cache timing analysis. In Section 2.5, we present overview of our WCET analysis framework. And f in Section 2.6, we describes our architecture of the underlying model.

#### 2.1 WCET Introduction

From Chapter 1, we are sure that estimating WCET is essential for schedulability analysis for real-time systems. Actually the importance of WCET analysis has been recognized by the real-time community and substantial progress has been made over the past twenty years. And we have two approaches for estimating WCET: exhaustive simulation and static-analysis.

#### 2.1.1 Exhaustive Simulation Approach

Simulation is state-of-the-art in industry to determine the timing behavior of a program on a given architecture. Though typical timing behavior can be obtained this way, execution time guarantees cannot be made as it is unaffordable to cover all relevant execution scenarios using simulation. This is also unsafe because typical timing behavior can not guarantee covering the worst case as not all program paths can be covered by the limited simulation. A full coverage would require an exponential number of test data and would be too time consuming. Therefore, only a subset of all program paths is tested. However, safety is essential for WCET estimation in order to guarantee a sufficient time assignment to a task so that all tasks can meet their deadlines and a successful schedule can be obtained.

Therefore, static-analysis of WCET has gained much popularity in the literature researches.

#### 2.1.2 Static WCET Analysis Approach

WCET analysis computes an upper bound on the program's execution time on particular hardware architecture for all possible inputs.

#### **Properties of WCET Analysis**

Let's restate the properties of a desired static-analysis of WCET more detailed in order to understand the WCET analysis criteria better:

- Conservative: The analysis should not underestimate the actual WCET; otherwise a supposed 'successful' schedule may assign a task a computation time above the estimated WCET but not sufficient for the actual worst case. This leads to the task missing its deadline and the system failing the requirements in some circumstances.

- 2) Tight: The analysis should be reasonably close to the actual WCET; otherwise the task will require an unnecessarily long computation time as it will be assigned a computation time no less than the estimated WCET. This much overestimation would obviously cause a waste of hardware resources in order to guarantee a successful schedule, which is undesirable especially as the resources are stringent and expensive in embedded systems.

- (3) Efficient: The static analysis should be efficient in both time and space consumption.

# 2.2 Three Phases of WCET Analysis

To achieve these properties of a WCET analysis, we have to examine what affects the execution time of a program so that efforts can be directed to these factors for pursuit of a good WCET analysis.

## **Factors Affecting Execution Time**

There are two factors:

- Data input for the program: different input sets may have different execution

paths of a program, for example, taking different branches and resulting in

different execution times

- 2) The hardware architecture on which the program is running: hardware resources have a great influence on how long an instruction would execute.

#### **WCET Analysis Phases**

Correspondingly, static WCET analysis can be divided into three phases [9]:

1) Flow analysis: to extract the dynamic behavior of the program. This includes information as: identify loop bounds, how many times loops iterate, which functions get called and exclude infeasible program paths from the source program or the compiled code of the program. If there are dependencies between if-statements, the information much be a safe (over) approximation including all possible program execution paths. The information can be obtained by manual annotations (integrated in the programming language [10] or provided separately [11], [12]), or by automatic flow analysis methods [13], [14], [15].

The more infeasible paths get excluded, the more accurate a WCET can be obtained from the analysis and also with more efficiency. This step is also called *program path analysis*.

2) Micro-architecture modeling: to determine the timing behavior of instructions given the architectural feature of the target system. For modern processors, it is especially important to study the effects of various performance enhancing hardware components such as pipeline, cache, branch prediction etc[16], [17], [18], [19]. While improving the average system performance, these advanced

hardware features cause difficulties for instruction timing prediction. They make instruction execution time not constant any more, for example a cache hit may take a much shorter execution time than a cache miss. Furthermore, the instruction execution time can be history dependent, for example a cache access resulting in a cache hit or miss depends on if that to-be-accessed data is already in the cache or not.

This step studies these impacts and provides instruction timing information so that the execution times of different execution paths can be obtained by counting in each this step's timing schema.

3) WCET calculation: to calculate an upper bound on the WCET. With the results of flow and timing information from the first two steps, the costs of feasible program paths are evaluated, and the maximum one will be taken as the estimated WCET.

#### Relationship between WCET Analysis Properties and Three Phases

Let's examine the relationship between WCET analysis properties and these three phases.

1) Conservativeness: it relies on the first two WCET phases to guarantee no underestimation of the WCET. During flow analysis phase, it should be made sure that no feasible paths are excluded, otherwise the worst case execution path which is feasible might be excluded out and lead to an underestimation of WCET (failure of WCET analysis); During micro-architecture modeling phase, instruction timing estimation should also be conservative in order that the overall cost of a program path (for every feasible path) will not be

underestimated.

2) Tightness: it also depends on the first two phases. As we mentioned above in the three phases, the more infeasible paths get excluded, the more accurate the estimation of WCET can be obtained. This is because infeasible paths counted out might have longer execution times, excluding these execution times can give a smaller estimation of WCET which is tighter. And the more accurate the instruction timing from step two, the tighter the estimation of execution time for the paths can be obtained as a path execution time is the sum evaluation of the instruction timing for all timing nodes along this path.

Also from the three phases, we can see that static WCET analysis is more efficient than simulation as the latter individually analyzes every possible program path, while the former considers a much smaller set of paths, simultaneously.

Recall that static WCET analysis consists of three phase: flow analysis or program path analysis, micro-architecture modeling and WCET calculation. Since WCET calculation step directly concerns the aim of the program's WCET analysis and the other two steps are performed for a better WCET calculation in WCET calculation step, we will start from WCET calculation methods, then the rest two topics.

#### 2.2.1 WCET Calculation Approaches

There are primarily three WCET calculation methods: timing schema, path-based calculation, and Implicit Path Enumeration Technique (IPET). They are classified based on the way program paths are evaluated and the way instruction timing information is used. Let's have a look how they differ in these two perspectives.

1) Tree-based approach: it estimates builds a syntax tree of the program and

traversing the tree from bottom to up meanwhile applying timing rules at the nodes of the tree (called "timing schema") and the estimated WCET is obtained at the root of the tree (top node). This approach is quite simple to implement while being efficient. However, it is difficult to exploit infeasible paths this way because the timing rules (timing schema) are limited to local program statements, which implies that finding timing conflicts in the execution paths are not easy.

- 2) Path-based approach: it computes the execution time for every feasible path in the flow graph of the program, and then searches for the largest one as the estimated WCET. While path-based approach can handle various flow information, it enumerates a large amount of paths which leads to inefficiency and large space consumption. Recent works have sought to reduce this expensive path enumeration by removing infeasible paths from the flow graph [20].

- (3) Implicit path enumeration Technique (IPET): it uses arithmetical constraints to model the program flow and low-level execution times: first it builds linear equations or inequalities (constraints) to represent the program flows and the execution time of the program is represented using variables in these constraints, then maximizes the execution time equation, and that maximization value is the estimated WCET [11], [15], [21]. This maximization calculation is normally done using ILP (Integer Linear Programming) solver. Unfortunately it is prohibitively computing expensive to solve ILP problem, which actually was proven to be NP-hard [22], [7]. A second concern with this approach is that the constraints count in all the program paths including all the false ones, this would incur two results: a huge number of equations/inequalities to solve and the estimated WCET not tight.

We will discuss in detail these three approaches in the related work on WCET calculation approaches in Section 2.3.3.

## 2.2.2 Microarchitecture Modeling

Micro-architectural features, such as pipelining, caching and branch prediction, improve the average system performance a lot and have caught a lot of attention on their modeling for accurate WCET analysis. We review the various Micro-architecture modeling techniques in this Section and focus on cache modeling.

## Pipelining

The execution of an instruction can be divided into several stages. MIPS instructions classically take five steps: fetch instruction from memory, decode instruction and read registers, execute the operation or calculate an address, access an operand in data memory, and write the result into a register. Instead of executing instructions one after another, we can overlap the execution of multiple instructions where each one of the instructions is at a particular execution stage at a time. This approach is called pipelining. It improves the throughput by executing several instructions in parallel. If each stage of the instructions takes about the same amount of time and there are enough instructions to carry out, the speedup due to pipelining is equal to the number of stages in the pipeline. However, this ideal speedup of pipelined execution normally is not achieved because of some events preventing the instructions from preceding though the pipeline smoothly. These events are called hazards in the literature [6], which are classified into three types: Structural hazards, Data hazards and Control hazards.

## **Branch Prediction**

An instruction must be fetched at every clock cycle to sustain the pipeline, yet the decision about whether to branch does not occur until the 4<sup>th</sup> stage of instruction execution-access an operand in data memory. This delay in determining the proper instruction to fetch is called a control hazard or branch hazard [6]. Branch prediction is to address control hazards, by computing as early as possible the address of the subsequent instruction to be executed to decide whether the conditional branch is taken or not taken. If prediction is correct, we can save the processor idle wait time between the start of the branch instruction and its production of the outcome (which is called a branch penalty); if prediction is wrong, the wrong path instruction effects must be undone and correct path gets resumed (the time in between is called *misprediction penalty*, which is usually equal to or slightly higher than the branch penalty).

#### Caching

Caching is a mechanism to cushion the speed gap between processor and main memory, by embedding in between small and fast cache memories. There are two types of architecture: *Von Neumann architecture*<sup>5</sup> and *Harvard architecture*. The former has unified cache (program instructions and data are stored in a single storage) and the latter has split instruction cache and data cache to store instructions and data separately. The Harvard architecture is widely used in embedded systems and it enables analyzing instruction cache and data cache separately. In the thesis, we deal with Harvard architecture, and focus on data cache timing analysis which is more challenging and has not had an efficient solution yet.

-

<sup>&</sup>lt;sup>5</sup> http://en.wikipedia.org/wiki/Von Neumann architecture

#### 2.2.3 Flow Analysis

To estimate WCET of a program analytically, all possible paths must be analyzed. Program flow analysis is to determine the possible paths through a program. Thereafter, for each generated path, the execution time can be estimated for a particular architecture.

Definition 2.1 **Path**: a path from node u to node v in the control flow graph of a program is a sequence of directed edges  $n_0$ ,  $n_1$ ,...,  $n_k$  such that  $n_0 = u$ ,  $n_k = v$  and  $(n_i, n_{i+1})$  is an edge in the graph.

Flow analysis yields information about loop bounds, which functions are called and exclude infeasible program paths from the source program or the compiled code of the program. Approximation during computation is necessary to reduce path explosion, for example a simple loop with an if-then-else statement that iterates 100 times would generate 2<sup>100</sup> possible paths. [23] and [24]carry out this approximation to reduce the number of paths to be analyzed by removing infeasible paths whenever it is possible. Another approach is to merge paths where a path enumeration is needed [25], [26], [27], [28]. This approach is to further reduce the path explosion and merging is applied to points of data-dependent conditionals, loop with multiple paths inside and loops with unknown loop bounds.

## 2.3 Related Works on Static WCET Analysis

WCET is the upper bound on the execution time of a program over all possible data inputs on a specific hardware platform. WCET of a task is an essential input to the schedulability analysis of hard real-time systems. It is difficult to estimate the WCET through simulation for any non-trivial program due to the very large number of possible

inputs. Thus static analysis techniques are employed to derive an upper bound on the WCET of a program.

Let's have a review of related works/achievements on performing timing analysis of embedded software through static analysis.

#### 2.3.1 Related Works on Micro-architecture Modeling

One important yet difficult problem for static timing analysis is to model the timing effects of complex micro-architectural features present in modern processors. There are some other techniques on the modeling instruction caches and data caches. There are also some works on the modeling of other Micro-architecture features such as branch prediction, pipelining, prefecting etc.

## **Integer Linear Programming (ILP)**

ILP is an established method to find the worst case execution path in timing analysis [29], [30]. Based on the control flow graph of a program, a linear optimization problem is constructed that maximizes the flow through the program. Li et al. [31], [32], [33] used ILP for instruction cache modeling and integrated it with their ILP-based WCET calculation framework. Their Micro-architecture modeling tool models direct-mapped instruction cache using a set of graphs called Cache Conflict Graphs (CCG), which models flow transfer information (instruction sequence in a basic block) among memory blocks mapping to the same cache line. Cache misses are captured by flow transfer between conflicting memory blocks. For set associative instruction caches, they introduced an extra set of graphs called Cache State Transition Graphs (CSTG) to model the more complicated behaviors of set-associative instruction caches. This ILP-based instruction cache modeling utilizes more detailed flow information and obtains good accuracies; however, its tight integration with WCET calculation results in an increase in

analysis time, especially for set associative caches. Li [34] models out-of-order pipeline execution, branch prediction and instruction cache and their interactions for WCET analysis in a framework named 'Chronos<sup>6</sup>'. Timing information for basic blocks of the program subject to some execution contexts and constraints on the occurrences of execution contexts (instruction cache state, branch prediction information, etc.) are generated from the modeling tool and combined with the flow constraints and user constraints to form a complete ILP problem.

## **Abstract Interpretation**

Ferdinand [35], Theiling [36] used abstract interpretation [37], [38] for instruction cache analysis. After abstract cache states get collected at program points, program flow is traversed to update abstract cache state for each cache access and combine abstract cache states at program joints. Then memory references are classified by the abstract cache states into four categories: always hit, always miss, persistent and not classified, which will be combined with cache information for subsequent analysis.

## **Timing Schema**

Timing schema [39]was extended by [40], [41], [42] to model pipelining and caching. The extended timing schema uses a data structure called worst case timing abstraction (WCTA) for the time-bound for a program construct. To model instruction cache effects, it divides memory accesses in a path of a construct into three groups: first/last/other references to the cache lines. Cache hits/misses of the first references uses execution information preceding the path and the last references are needed by paths succeeding it, thus they are remembered by augmenting the WCTA. At concatenating two paths across program constructs, the last references of the earlier path are used to resolve some of the

6 http://www.comp.nus.edu.sg/~rpembed/chronos/

-

hits/misses in the first references in the later path, and the first/last references of the concatenated path will be computed from the first/last references of the two concatenating paths. To combine pipelining and caching effects, it simply superimposes cache miss penalties to the execution obtained from the pure pipeline analysis.

Many other static timing analysis approaches have also been proposed, such as symbolic simulation [43], implicit path enumeration [37], timing analysis language [39], and Engblom [44] provides a comprehensive study of various pipelines for WCET analysis in his doctoral dissertation.

## 2.3.2 Related Works on Flow Analysis

WCET calculation evaluates the costs of the program paths and takes the maximum one as the WCET. In contrast to simulation, where each program path is evaluated separately (the major drawback of the simulation approach), WCET analysis evaluates multiple program paths simultaneously. The key problem is how the program paths are grouped for evaluation, which is what flow analysis concerns about.

Flow analysis technique is used in optimizing compilers to statically analyze the properties of the source code for exploration of common sub-expressions or dead-code elimination [45]. It has been applied to single task analysis by [46].

In [48], [49], **Error! Reference source not found.**, flow analysis techniques are used in optimizing compilers to analyze timing behavior of pipelines and instruction caches.

(1) First, they use a static cache simulator [50], [51] to analyze instruction caches. The simulator examines the program control flow and categorizes instructions into four classes: always hit, always miss, first hit, and first miss.

- (2) Next, pipeline analysis is carried out by using the cache category information.

- (3) Last, the timing analyzer predicts the WCET of the program by using the worst case execution times of the code segments containing loops, function calls etc from bottom to up. [52]adopts data flow analysis for data cache analysis. After code generation and all optimizations, the address range of data references is obtained on low-level representation. Unknown data references are not considered and array ranges should be manually annotated.

Let's compare approaches in Section 2.3.1 (micro-architecture modeling) and 2.3.2 (flow analysis). When only concerning instruction cache analysis, the flow analysis approach and the abstract interpretation approach perform instruction cache analysis before WCET calculation phase; while in the extended timing schema, ILP and symbolic simulation approaches, instruction cache analysis is integrated with WCET calculation. The latter integrated approaches can be more accurate results at the price of using more program path information (i.e. a higher computation cost).

#### 2.3.3 Related Works on WCET Calculation

There are primarily three WCET calculation methods: timing schema, path-based calculation, and Implicit Path Enumeration Technique (IPET). They are classified based on how program paths are evaluated and how instruction timing information is used.

#### 1) Timing Schema

A tree-based approach [53], [54], [55], [56] is proposed to estimate the WCET of a program through a bottom-up traversal of its syntax tree and applying different timing rules at the nodes (called "timing schema"). Once the times of lower level constructs have been obtained, the time of the higher level construct containing them can be

estimated. This approach is very simple and efficient. However, it's difficult to exploit infeasible paths in this approach, because the local estimation in timing schema cannot account for infeasible paths which are defined by constraints across multiple constructs.

#### 2) Path-based Calculation