# SYSTEM-LEVEL MODELING AND ANALYSIS OF MULTIMEDIA-SOC PLATFORMS

YANHONG LIU

(M.Eng., Institute of Computing Technology, Chinese Academy of Sciences)

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE

2007

## Acknowledgments

Numerous people have supported me during the development of this dissertation, and my graduate experience more generally. Mentioning a few words here cannot adequately capture all my appreciation.

I would like to show my sincerest gratitude to my advisor Dr. Samarjit Chakraborty. I thank him for his devoted guidance and constant encouragement. I think I can never stop learning from his insight into the research area, intellect and inspiration. I also benefit a lot from the fact that Dr. Samarjit Chakraborty, as a generous and kind advisor, always helps students not only on academic growth, but also on their lives.

I also thank my other advisor Dr. Wei Tsang Ooi. I thank him for his generous help and guidance at the beginning of my life at the university. I am very impressed by his academic strictness. I would like to thank him for the continuous advising, suggestions and comments on the work related to this dissertation as well.

I have been lucky to have the opportunity of working with Dr. Radu Marculescu (from CMU) and Dr. Tulika Mitra and learnt a lot from them. I want to give my special thanks to Dr. Alexander Maxiaguine (from ETH). The cooperative work with him helps me to get a quick start of the simulation platforms used.

I would also like to thank the members of my dissertation committee, Dr. Wong Weng Fai and Dr. Ee-Chien Chang, for many useful interactions, and for contributing their broad perspective in refining the ideas in this dissertation.

I would like to thank the National University of Singapore for the research scholarship that makes this study possible and the administrative staff here for their support in the various aspects of academy and life.

Of many other friends and colleagues, I want to thank Dr. Yongxin Zhu for the help on some issues of simulations. Thanks also go to Lin Ma, Balaji Raman, Huaxin Xu, Qinghua Shen, Zhiguo Ge, NGUYEN Dang Kathy, Yun Liang, Jimin Feng, Yu Pan etc. for the help and fun.

As always, I thank my family for their love and continuous encouragement. My parents always do whatever to avoid me to distract from the study. My brother helps to take care of my parents and to manage the family matters, which I should have shared with. My sister always devotes her help to me whenever need and often encourages me to do my best. I also thank the extended family members for their support.

Last, my most tender and sincere thanks go to my wife, Lili Zhang. Thanks for her self-giving help and support in innumerable ways.

## **List of Publications**

- Alexander Maxiaguine, Yanhong Liu, Samarjit Chakraborty and Wei Tsang Ooi. Identifying "Representative" Workloads in Designing MpSoC Platforms for Media Processing. In 2nd Workshop on Embedded Systems for Real-Time Multimedia (ES-TIMedia), Stockholm, Sweden, September 2004.

- Yanhong Liu, Alexander Maxiaguine, Samarjit Chakraborty and Wei Tsang Ooi. Processor Frequency Selection for SoC Platforms for Multimedia Applications. In *IEEE Real-Time Systems Symposium (RTSS)*, Lisbon, Portugal, December 2004. (Rank 1 Conference)

- Yanhong Liu, Samarjit Chakraborty and Wei Tsang Ooi. Approximate VCCs: A New Characterization of Multimedia Workloads for System-level MpSoC Design. In *Proceedings of the Design Automation Conference (DAC)*, Anaheim, California, June 2005. (Rank 1 Conference, Best Paper Award Nomination)

- 4. Yanhong Liu, Samarjit Chakraborty, Wei Tsang Ooi, Ashish Gupta, and Subramanian Mohan. Workload Characterization and Cost-Quality Tradeoffs in MPEG-4 Decoding on Resource-Constrained Devices. In *3nd Workshop on Embedded Systems for Real-Time Multimedia (ESTIMedia)*, New York Metropolitan area, September 2005.

- Yanhong Liu, Samarjit Chakraborty, and Radu Marculescu. Generalized Rate Analysis for Media-Processing Platforms. In 12th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), Sydney, August 2006.

- 6. Samarjit Chakraborty, Yanhong Liu, Nikolay Stoimenov, Lothar Thiele, and Ernesto

Wandeler. Interface-Based Rate Analysis of Embedded Systems. In *IEEE Real-Time Systems Symposium (RTSS)*, Rio de Janeiro, December 2006. (Rank 1 Conference)

# Contents

| List of 7 | ſables                                    | vi  |

|-----------|-------------------------------------------|-----|

| List of l | ligures                                   | vii |

| Chapte    | r 1 Introduction                          | 1   |

| 1.1       | Motivation                                | 1   |

| 1.2       | Thesis Contributions                      | 2   |

| 1.3       | Organization of the Thesis                | 4   |

| Chapte    | r 2 Background and Related Work           | 5   |

| 2.1       | MpSoC Platforms                           | 5   |

| 2.2       | Y-chart Scheme of Designing SoC Platforms | 6   |

|           | 2.2.1 Models of Computation               | 8   |

|           | 2.2.2 Models of Architecture              | 9   |

|           | 2.2.3 Performance Analysis                | 9   |

| 2.3       | SoC Design for Multimedia Applications    | 10  |

| 2.4       | Characterization of Multimedia Workloads  | 13  |

| 2.5       | Network Calculus Theory                   | 14  |

| Chapte    | r 3 Fundamental Models and Techniques     | 16  |

| 3.1       | Models of Application and Architecture    | 16  |

| 3.2       | Multimedia Workload Characterization      | 18  |

| 3.3       | Performance Analysis                      | 23  |

| 3.4       | Experimental Setup                        | 25  |

| Chapter | ·4 Ch   | aracterizing Multimedia Workloads: Obtaining VCCs                                         | 26 |

|---------|---------|-------------------------------------------------------------------------------------------|----|

| 4.1     | Measu   | ring VCCs for Single Stream                                                               | 29 |

| 4.2     | Classif | ication of Streams                                                                        | 30 |

|         | 4.2.1   | Measuring Dissimilarity between Two Streams                                               | 31 |

|         | 4.2.2   | Clustering of Similar Streams                                                             | 32 |

| 4.3     | Empiri  | cal Validation                                                                            | 32 |

| 4.4     | Summa   | ary                                                                                       | 39 |

| Chapter | 5 Sys   | stem Design Case I: Processor Frequency Selection                                         | 41 |

| 5.1     | Our Re  | esults and Relation to Previous Work                                                      | 43 |

| 5.2     | Problem | m Formulation                                                                             | 45 |

| 5.3     | Compu   | ting Bounds on Service Requirements                                                       | 48 |

|         | 5.3.1   | Computing Service Bounds for a <i>Class</i> of Streams                                    | 50 |

|         |         | 5.3.1.1 Computing the Bound on $\beta^l$                                                  | 51 |

|         |         | 5.3.1.2 Computing the Bound on $\beta^u$                                                  | 52 |

|         | 5.3.2   | Computing Service Bounds in Terms of Number of Processor Cycles                           | 52 |

|         | 5.3.3   | Bounding the Analysis Interval                                                            | 54 |

|         | 5.3.4   | Extending the Analysis to Other PEs                                                       | 55 |

| 5.4     | Compu   | ting Processor Frequency Range                                                            | 56 |

| 5.5     | Case S  | tudy                                                                                      | 59 |

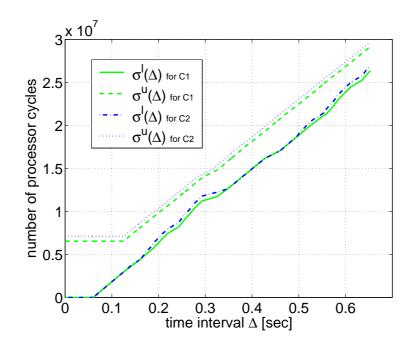

|         | 5.5.1   | Computing the Service Bounds and the Frequency Range for $\ensuremath{\textit{PE}}_2\;$ . | 61 |

|         | 5.5.2   | Validation of the Analytical Bounds                                                       | 65 |

|         | 5.5.3   | Selection of the Analysis Interval                                                        | 66 |

| 5.6     | Summa   | ary                                                                                       | 67 |

| Chapter | 6 Sys   | stem Design Case II: Generalized Rate Analysis                                            | 71 |

| 6.1     | Problem | m Formulation                                                                             | 73 |

| 6.2     | Rate A  | nalysis                                                                                   | 76 |

|         | 6.2.1   | The Single Stream Case                                                                    | 76 |

|         | 6.2.2   | The Case of Multiple Streams                                                              | 79 |

|         | 6.2.2.1 Fixed-Priority Scheduling                                | 80 |

|---------|------------------------------------------------------------------|----|

|         | 6.2.2.2 Time Division Multiplexing                               | 85 |

|         | 6.2.3 Multiple Processing Elements                               | 85 |

| 6.3     | Experimental Evaluation                                          | 86 |

|         | 6.3.1 The Single Stream Case                                     | 89 |

|         | 6.3.2 The Case of Multiple Streams                               | 91 |

| 6.4     | Related Work                                                     | 92 |

| 6.5     | Summary                                                          | 94 |

| Chapter | r 7 Approximate VCCs: A New Characterization of Multimedia Work- |    |

| load    | ls 1                                                             | 01 |

| 7.1     | Formulation of VCCs                                              | 05 |

| 7.2     | Approximate VCCs                                                 | 06 |

| 7.3     | Error Analysis                                                   | 08 |

|         | 7.3.1 On-Chip Buffer Sizing                                      | 08 |

|         | 7.3.2 Processor Frequency Selection                              | 11 |

| 7.4     | Empirical Validation                                             | 14 |

|         | 7.4.1 Buffer Sizing                                              | 14 |

|         | 7.4.2 Frequency Selection                                        | 18 |

| 7.5     | Summary                                                          | 19 |

| Chapter | r 8 Conclusion 1                                                 | 20 |

| 8.1     | Modeling of Multimedia Workloads                                 | 20 |

| 8.2     | Design and Analysis                                              | 21 |

| 8.3     | New Characterization of Multimedia Workloads                     | 22 |

| 8.4     | Future Work                                                      | 23 |

## Summary

Currently there is a considerable interest in designing general-purpose configurable Systemon-Chip (SoC) platforms specifically targeted towards implementing multimedia applications. Determining the optimal configuration for such platforms is especially difficult due to the various kinds of variabilities arising out of multimedia processing, such as the high variability in the execution requirements of multimedia streams and the burstiness in the on-chip traffic. System-level design and analysis methods are then desired for such platforms, which take into account such variabilities.

In this thesis we propose an analytical framework that can be used in the design space exploration and performance analysis of multimedia SoC platforms. Our work includes the following contributions.

Firstly, we adopt the concept of *variability characterization curves* to characterize the worst-case behaviours of multimedia workloads. An analytical scheme is also presented to obtain such characterization curves for a large library of potential inputs to the system.

Secondly, to illustrate the utility of our framework, we present analytical approaches for two typical system design cases. In the first case, we address the problem of identifying the frequency ranges that should be supported by different processors of a platform in order to run a target multimedia workload. In the other case, we determine tight bounds on the arrival rates of different multimedia streams at a platform such that predefined quality-ofservice (QoS) constraints are met.

Finally, we propose the concept of *approximate variability characterization curves* to characterize the average-case behaviours of multimedia workloads. "Average-case" analysis using this concept can be used to derive tradeoffs between resource savings and QoS constraints. In this thesis we present error analysis algorithms to bound the extent to which such QoS constraints can be satisfied.

Our proposed framework can be used to precisely model multimedia workloads and estimate various performance parameters for multimedia SoC platforms in a seamless manner. Compared to purely simulation-oriented approaches, our framework provides provable performance guarantees and involves analysis times which are significantly shorter.

# **List of Tables**

| 4.1 | MPEG-2 video clips used in our experiments.                                      | 34  |

|-----|----------------------------------------------------------------------------------|-----|

| 4.2 | Maximum dissimilarity between fragments of the same scene                        | 36  |

| 4.3 | Measured maximum buffer backlogs.                                                | 40  |

| 5.1 | The maximum buffer fill levels obtained by simulating a static frequency         |     |

|     | schedule for $PE_2$ that was derived using the proposed framework. $video_1$     |     |

|     | $(video_3)$ and $video_2$ $(video_4)$ are 4 Mbps and 8 Mbps MPEG-2 video streams |     |

|     | respectively.                                                                    | 69  |

| 6.1 | Summary of the input arrival bounds                                              | 84  |

| 6.2 | Summary of the bounds on buffer overflow.                                        | 85  |

| 6.3 | Scenarios for the single stream case.                                            | 89  |

| 6.4 | Scenarios for the multiple streams case.                                         | 89  |

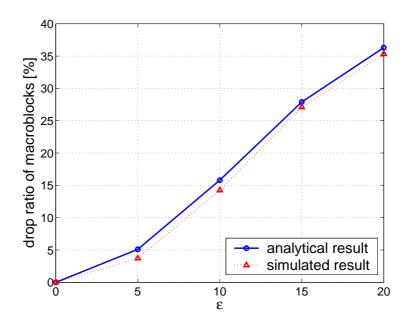

| 7.1 | Analytical bounds and simulation results on the percentage of macroblocks        | 110 |

|     | that miss their deadlines, for different values of $\varepsilon$ .               | 119 |

# **List of Figures**

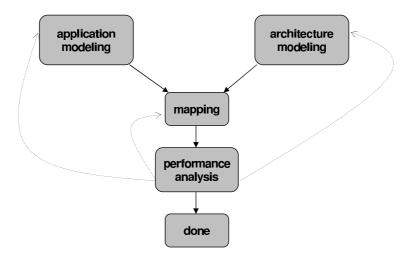

| 2.1 | Y-chart scheme.                                                                                | 7  |

|-----|------------------------------------------------------------------------------------------------|----|

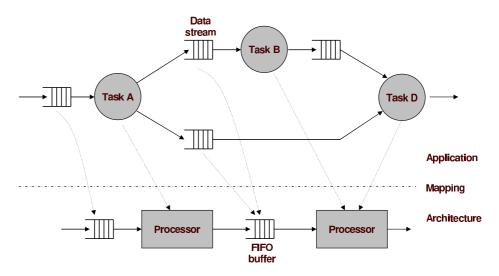

| 3.1 | Illustration of the mapping of a multimedia application modeled as a KPN                       |    |

|     | onto an MpSoC platform architecture modeled at abstract level                                  | 17 |

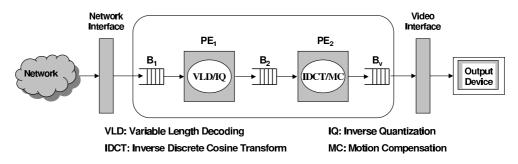

| 3.2 | An MpSoC platform onto which an MPEG-2 decoder application is parti-                           |    |

|     | tioned and mapped.                                                                             | 17 |

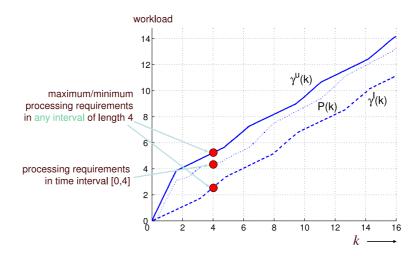

| 3.3 | Illustration of workload curve $\gamma$                                                        | 20 |

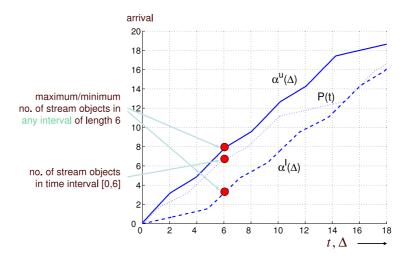

| 3.4 | Illustration of arrival curve $\alpha$                                                         | 21 |

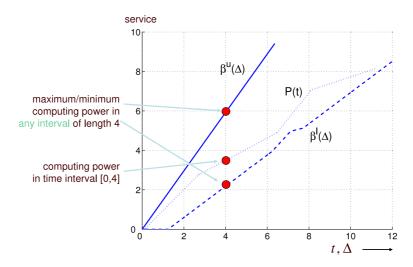

| 3.5 | Illustration of service curve $\beta$ .                                                        | 22 |

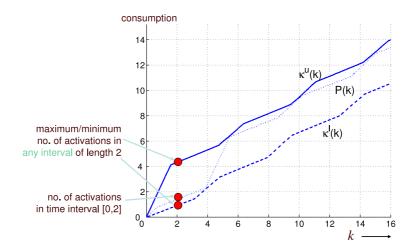

| 3.6 | Illustration of consumption curve $\kappa$ .                                                   | 23 |

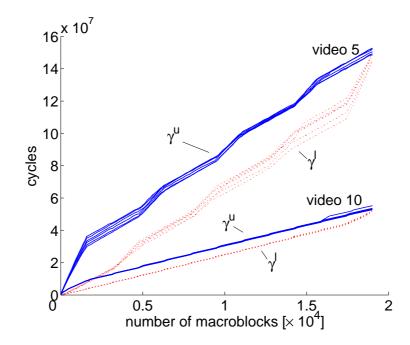

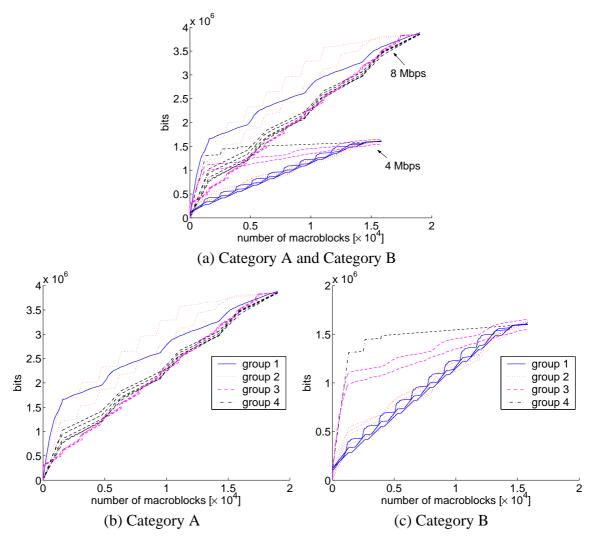

| 4.1 | $(\gamma_{vld}^u, \gamma_{vld}^l)$ for different fragments of video 5 and video 10             | 35 |

| 4.2 | Classification based on $\kappa^u_{vld}$ only for all the clips                                | 37 |

| 4.3 | Classification based on $\gamma^u_{vld}$ only for the clips in Category A                      | 38 |

| 4.4 | Classification based on $\gamma^u_{idct}$ only for the clips in Category A                     | 39 |

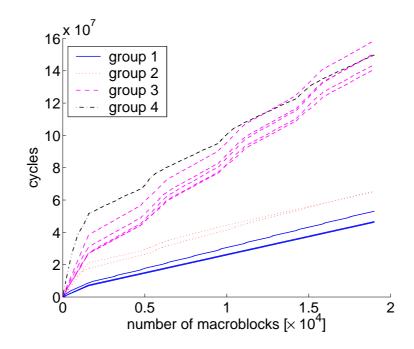

| 4.5 | Cluster tree                                                                                   | 39 |

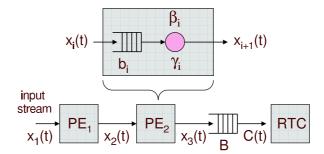

| 5.1 | System-level view of multimedia processing on a multiprocessor SoC plat-                       |    |

|     | form                                                                                           | 46 |

| 5.2 | Algorithm of Computing Frequency Range.                                                        | 60 |

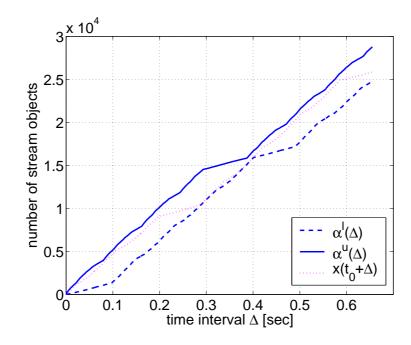

| 5.3 | Arrival curves $(\alpha_x^l, \alpha_x^u)$ of the macroblock stream on the output of $PE_1$ for |    |

|     | the video sequence $video_1$ . A fragment of the function $x(t)$ for $video_1$ is              |    |

|     | shown in this figure. Note that it is bounded by the corresponding arrival                     |    |

|     | curves                                                                                         | 62 |

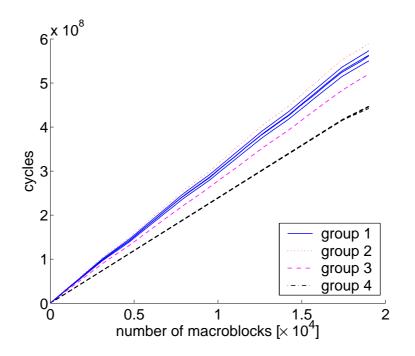

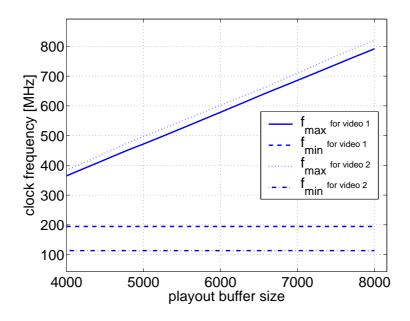

- 5.6 Dependency of frequency ranges on the playout buffer size for two different classes of the MPEG-2 video streams with more motion: 4 Mbps (*video*<sub>1</sub>) and 8 Mbps (*video*<sub>2</sub>). The size of buffer B<sub>2</sub> is fixed to 3000 macroblocks.

65

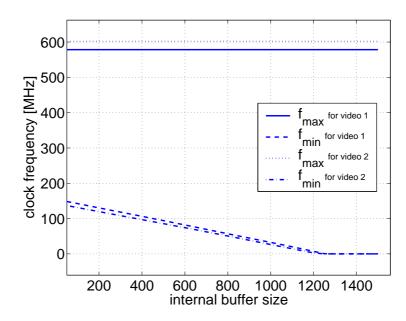

- 5.8 Dependency of frequency ranges on the internal buffer size for two different classes of the MPEG-2 video streams with more motion: 4 Mbps (*video*<sub>1</sub>) and 8 Mbps (*video*<sub>2</sub>). The size of buffer B<sub>v</sub> is fixed to 6000 macroblocks.

67

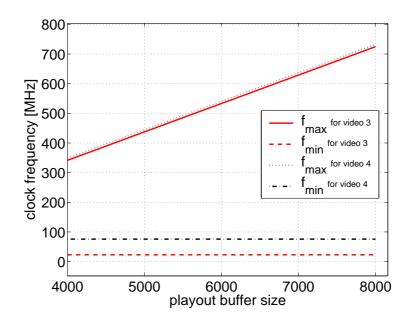

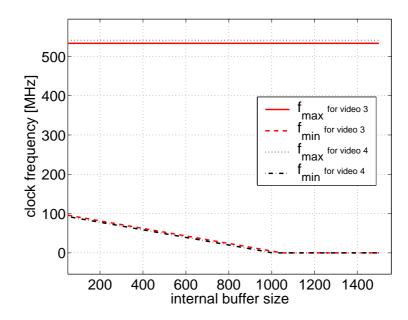

- 5.9 Dependency of frequency ranges on the internal buffer size for two different classes of the MPEG-2 video streams with less motion: 4 Mbps (*video*<sub>3</sub>) and 8 Mbps (*video*<sub>4</sub>). The size of buffer B<sub>v</sub> is fixed to 6000 macroblocks.

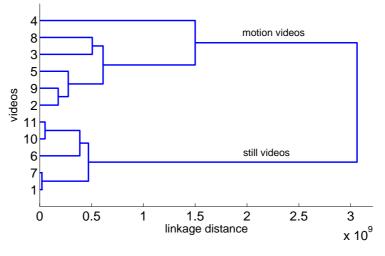

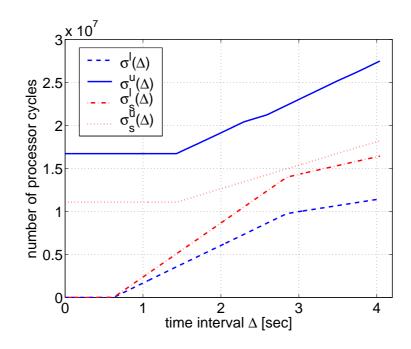

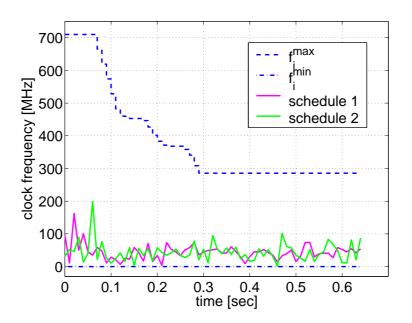

5.10 Two randomly generated schedules obtained from the service bounds σ.

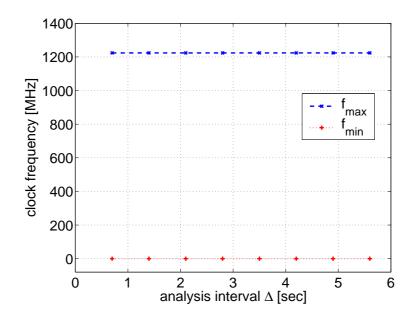

- 5.12 The frequency ranges computed for different values of the analysis interval. 70

70

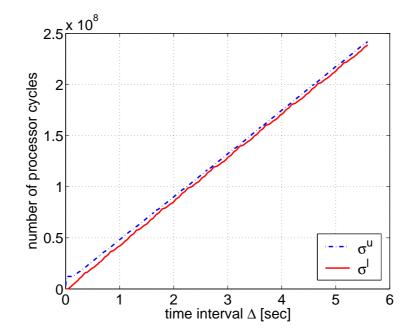

5.11 An illustration of the service bounds  $\sigma$  for a longer time interval. . . . .

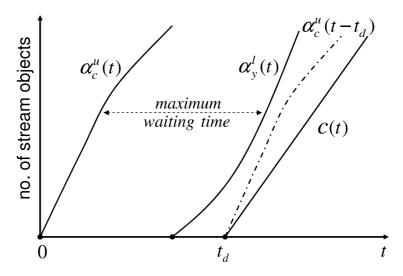

| 6.4  | A graphical illustration of the playout buffer underflow constraint in terms                          |

|------|-------------------------------------------------------------------------------------------------------|

|      | of $\alpha_c^u$ , $\alpha_y^l$ and the playback delay $t_d$                                           |

| 6.5  | Illustration of deriving an upper bound on $\alpha_{x1}^u$                                            |

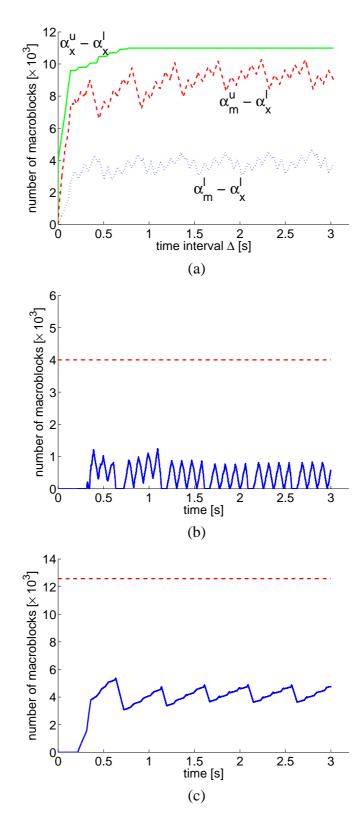

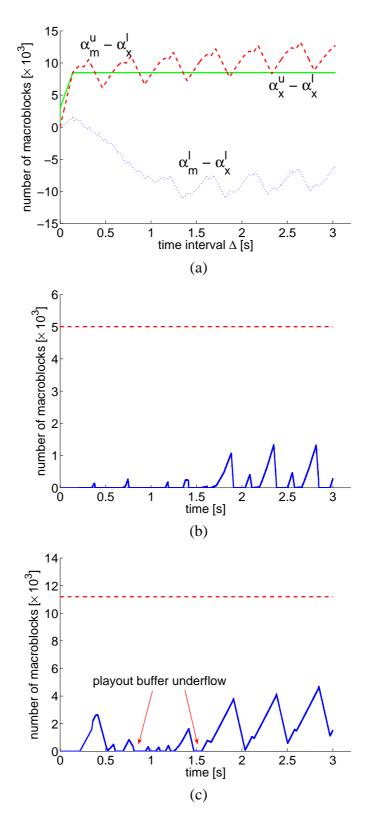

| 6.6  | Scenario 1: (a) Computed and measured bounds on the arrival rate, (b)                                 |

|      | Measured input buffer fill level, (c) Measured playout buffer fill level 95                           |

| 6.7  | Scenario 2: (a) Computed and measured bounds on the arrival rate, (b)                                 |

|      | Measured input buffer fill level, (c) Measured playout buffer fill level 96                           |

| 6.8  | Scenario 4: (a) Computed and measured bounds on the arrival rate, (b)                                 |

|      | Measured input buffer fill level, (c) Measured playout buffer fill level 97                           |

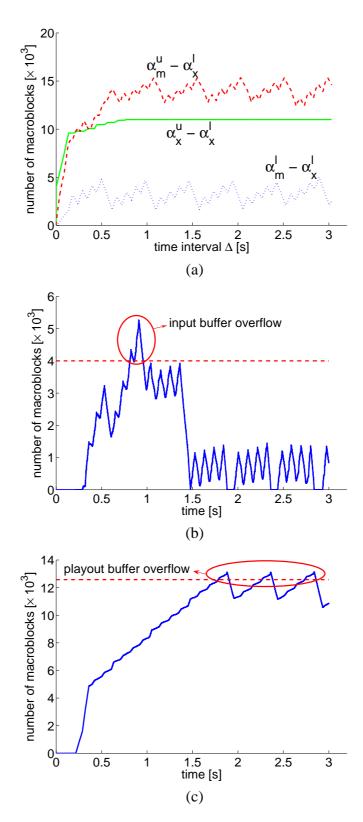

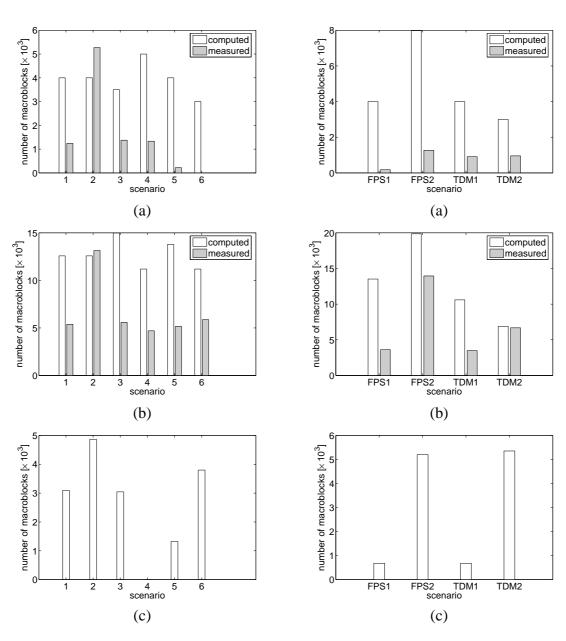

| 6.9  | Buffer fill levels in the single stream case: (a) Computed versus measured                            |

|      | maximum fill level of the input buffer, (b) Computed versus measured max-                             |

|      | imum fill level of the playout buffer, (c) Measured minimum playout buffer                            |

|      | fill level                                                                                            |

| 6.10 | Buffer fill levels in the multiple streams case: (a) Computed versus mea-                             |

|      | sured maximum fill level of the input buffer, (b) Computed versus measured                            |

|      | maximum fill level of the playout buffer, (c) Measured minimum playout                                |

|      | buffer fill level                                                                                     |

| 6.11 | Bounds on the arrival rate computed using VCCs and a simple modeling                                  |

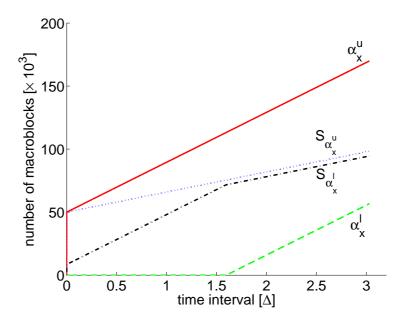

|      | scheme: $(\alpha_x^l, \alpha_x^u)$ and $(S_{\alpha_x^l}, S_{\alpha_x^u})$                             |

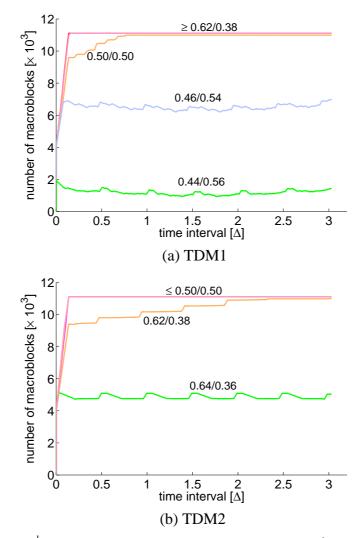

| 6.12 | $\alpha_x^u - \alpha_x^l$ for two scenarios, with different values $w_1/w_2$ for a TDM scheduler. 99  |

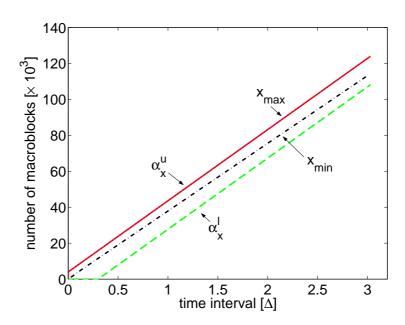

| 6.13 | Bounds on the arrival rate of a stream $(x_{min}, x_{max})$ and $(\alpha_x^l, \alpha_x^u)$ with play- |

|      | back delay value of 0.3 sec                                                                           |

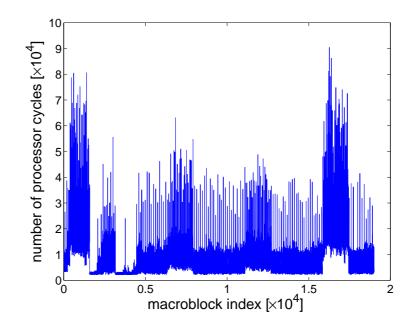

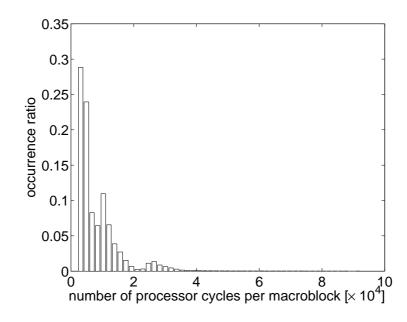

| 7.1  | Processor cycle requirements of a sequence of macroblocks for an MPEG-2                               |

| ,,,, | decoder application.                                                                                  |

| 7.2  | Histogram of the processor cycle demand per macroblock for an MPEG-2                                  |

|      | video. The minimum and the maximum cycle demands are 2218 and 92247                                   |

|      | respectively                                                                                          |

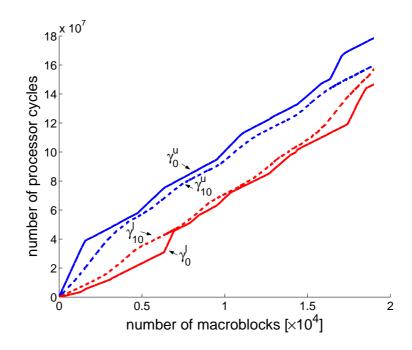

| 7.3  | Approximate workload curves                                                                           |

|      | 11                                                                                                    |

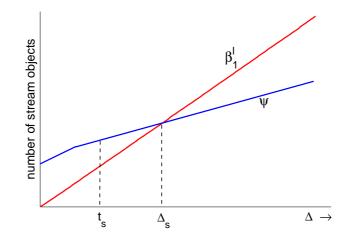

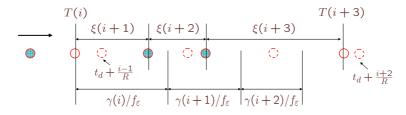

| 7.4 | Illustration of frequency analysis                                                     |

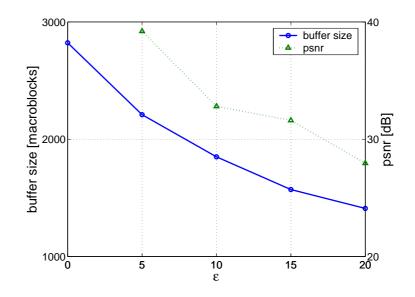

|-----|----------------------------------------------------------------------------------------|

| 7.5 | Computed buffer sizes for different values of $\varepsilon$                            |

| 7.6 | Percentage of macroblocks dropped from $B_2$ for different values of $\varepsilon$ 116 |

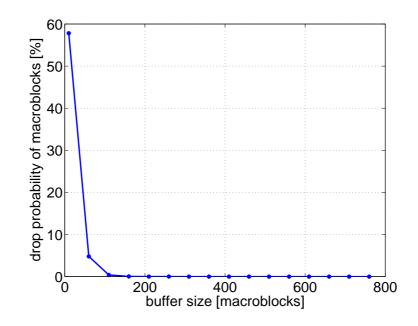

| 7.7 | Probability of macroblocks dropped from $B_2$ for different values of buffer           |

|     | sizes                                                                                  |

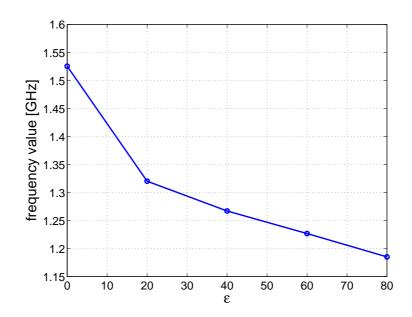

| 7.8 | Frequency values of $PE_2$ for different values of $\varepsilon$                       |

# Chapter 1

# Introduction

### **1.1 Motivation**

Today multimedia applications run on a wide range of consumer electronic devices, ranging from set-top boxes to PDAs and mobile phones. Because of flexibility, low design costs and time-to-market advantages, very often such devices are now designed using general-purpose configurable multiprocessor System-on-Chip (MpSoC) platforms. Examples of such platforms are the Eclipse architecture template [77, 79] and the Viper SoC architecture [31] from Philips that target advanced set-top box and DTV markets, OMAP from Texas Instruments [67] and PrimeXsys from ARM [71]. Many of these platforms are typically designed to process concurrent streams of audio and video data associated with broadband multimedia services and, at the same time, perform network packet processing to support high-speed Internet access.

One of the major problems that a designer has to address while using such platforms is the issue of platform configuration. Such platforms are typically designed for a *class* of applications. Given a particular application belonging to this class, the platform is tuned (or configured) to perform optimally when running this application. Configuring a platform may involve determining the size of on-chip buffers, bus width, cache configurations, etc. and also the parameters for different schedulers and bus arbitration policies.

Determining an optimal platform configuration is typically not easy and involves several design tradeoffs and constraints imposed by the platform itself. It should be fully considered about the flexibility, cost, performance and power consumption characteristics of the designed platform. For example, lowering the power consumption may imply degraded performance, and increasing flexibility is usually associated with increased cost and low performance. Additionally, a designer may face challenges due to rapidly changing protocols and time-to-market pressure. This problem becomes even more challenging in the context of *designing* SoC platforms for multimedia devices, because of the high computational demands, real-time constraints, and low power consumption requirements of such devices and various kinds of variabilities associated with multimedia processing. Also, the underlying *design space* is quite large and purely simulation-based techniques involve prohibitively high running time. Such considerations have led to an increasing demand for analysis techniques and system-level design tools for MpSoC platforms.

Research efforts have been paid to design multimedia SoC platforms using analytical techniques. Very little work, however, has fully taken into account the characterization of multimedia workloads during the design of SoC platforms. As we have mentioned, multimedia applications exhibit high computational requirements and various kinds of datadependent variability. For example, arrival patterns of multimedia streams at the input of the system may have a bursty nature. The number of bits to encode a frame or macroblock is highly variable. The execution demand of a task may vary a lot from activation to activation due to data-dependent program flow. Such kinds of variabilities have a great impact on the selection of configuration parameters of SoC platforms and should be fully explored. Stochastic models (e.g. queuing models) fail to accurately model these variabilities and can only provide stochastic performance guarantees. A powerful analytical framework is desired for the design of multimedia SoC platforms that can fully capture the characteristics of multimedia workloads.

#### **1.2 Thesis Contributions**

This thesis presents an analytical framework for the system-level design of SoC platform architectures for multimedia applications. The proposed framework is based on the theory of *Network Calculus* [16], which was originally developed and is still largely used in the

context of analyzing communication networks. Recently, it was extended to the domain of real-time systems. It was developed to analyze the SoC architectures in the context of network processors [21, 85] and further extended to the domain of general SoC platform architectures [20]. This research follows this line of development and extends the theory to analyze the SoC platforms for multimedia applications.

Firstly, we borrow the concept of *variability characterization curves* (VCCs) [63] to characterize the worst-case characteristics of multimedia workloads, which are based on the various concepts of "curves" introduced in the theory of network calculus. Using the concept of VCCs, we propose a methodology of identifying "representative" workloads from a large library of multimedia streams that can potentially run on the platform, the amount of which may be too huge to analyze all these streams. The VCCs measured for these set of selected streams are then used to represent the workloads imposed on the platform.

Secondly, based on the accurate model of the multimedia workloads (i.e. VCCs), we propose system-level analytical solutions for two typical cases of SoC platform design: on-chip processor frequency selection and rate analysis. In the first case, our analytical approaches can guide a system designer in identifying the frequency ranges that should be supported by the different processors of a platform architecture. In the latter case, we address the problem of determining tight bounds on the rates at which different multimedia streams can be fed into a platform architecture. We believe that under our proposed framework, effective analytical solutions can also be developed to determine other configuration parameters for SoC platforms.

Finally, we propose a novel concept of *approximate variability characterization curves* (or approximate VCCs) to characterize the "average-case" behavior of multimedia work-loads. The concept is defined in a parameterized fashion, which denotes the amount of the worst-case scenarios that is discarded. Analysis algorithms are also developed to quantita-tively account for the performance degradation and the associated resource savings corresponding to different values of the parameter.

The proposed analytical framework provides powerful and effective analytical approaches

for the SoC platform design in the context of multimedia applications. It should be helpful in the design space exploration of such platforms and to greatly reduce the design cycle. It should help a system designer to achieve the various kinds of tradeoffs in the platform design, by considering multimedia workload characterization and the platform design in a uniform way. The proposed framework captures fully the characteristics of multimedia workloads imposed on the platforms, such as various kinds of variability arising from multimedia processing. It should be able to analyze various performance metrics for the targeted platforms and to determine various configuration parameters for a platform, given the applications to be supported by the platform. On the other hand, it should be able to determine the characteristics that the applications should satisfy given the platform whose parameters are known. The proposed scheme of average-case characterization of multimedia workloads may achieve great resource savings when applied in the design of SoC platforms, due to the high variability presented in multimedia processing.

### **1.3** Organization of the Thesis

The organization of the thesis is as follows. In the next chapter, we introduce the background and review the related literature. In Chapter 3, we conduct the overview of fundamental models, the concept of VCCs, basic methodologies and experimental setup that we have used. In Chapter 4, we present our methodology of identifying "representative" workloads, from which VCCs are measured. It is followed by the analytical approaches proposed for two typical system design problems: on-chip processor frequency selection and rate analysis, which are presented in Chapters 5 and 6 respectively. The concept of approximate VCCs is then introduced in Chapter 7 and algorithms are presented to quantify the performance degradation and resource savings for two system design cases. Finally, we summarize the thesis and talk about the future work.

# **Chapter 2**

# **Background and Related Work**

## 2.1 MpSoC Platforms

The ever increasing complexity of SoCs and the pressures of short time-to-market and low cost requirements for SoC designs, has led to new design paradigms such as platformbased design [47]. This paradigm encourages the extensive reuse of common architectural components that can be shared among a variety of applications as well as can support the future evolutions of applications, in order to reduce the overwhelming cost of chip design and manufacturing. Based on this idea, general-purpose configurable SoC platforms use complex on-chip networks to integrate multiple intellectual property (IP) blocks or cores from some libraries (such as the IBM Blue Logic Core Library [43]) (or a third-party vendor) on a single chip. Example of the IP blocks or cores that might be included in such a platform are configurable processors, parameterized caches, specialized memory hierarchies, flexible bus architectures, programmable logic and parameterized coprocessors etc. These IP blocks or cores are already predesigned and verified and hence the designer need not take care of the specific implementation of these individual components, while only concentrating on the overall system.

In a general-purpose configurable SoC platform, the interconnected components and/or architecture parameters can be customized towards the requirements of the target application (or applications) that might run on this platform. Examples of such generic platforms are PrimeXsys from ARM [71] and AcurX from Planchip [3]. These platforms are targeted towards a wide range of applications starting from DVD players and set-top boxes,

to network routers and network security processors.

Although application-specific hardware (e.g., ASICs and custom SoCs) are customized for a particular application domain and have the benefits of high performance capacity, low power consumption, and small size, they are usually associated with heavy engineering costs, slow time-to-market and inability to make provision for post-deployment upgrades (hence reduced time-in-market). On the other end, solutions purely based on generalpurpose processors have the advantage of high degree of flexibility, enabling upgrades, and shorter design cycles, but often fall short of performance and power requirements. General-purpose configurable platforms, when used in a naive manner, still show a significant difference in the performance and power utilization characteristics, compared to more specialized solutions.

To bridge this gap, techniques are proposed to customize general-purpose configurable platforms for specific applications. Such application-specific platforms are customized for a particular application domain, but still support sufficient flexibility to allow them to be configured for specific products belonging to that domain. An example of such a platform is OMAP from Texas Instruments [67], which allow multimedia capabilities to be included in 2.5G and 3G wireless handsets and PDAs. The Eclipse architecture template [77] and the Viper SoC architecture [31], from Philips, are also examples of such application-specific platforms which target advanced set-top box and DTV markets.

## 2.2 Y-chart Scheme of Designing SoC Platforms

To get the optimal configuration of a complex SoC platform for target applications, the design space should be effectively explored, by taking fully into account both the application and architecture aspects of the platform under study. A common approach to follow in the design of SoC platforms is the Y-chart scheme [33, 48], as shown in Figure 2.1. This scheme requires to make a clear distinction between application and architecture to allow more effective exploration of alternative solutions, which is encouraged by the system design paradigm of *orthogonalization of concerns* [47]. Firstly, the designer characterizes the

Figure 2.1: Y-chart scheme.

target application (applications), makes some initial calculations and proposes a candidate architecture. Then the application is partitioned and explicitly mapped onto the different architectural components. Next, performance analysis is conducted to quantitatively evaluate the application-architecture combination. According to the resulting performance numbers, the designer may decide to go ahead with the chosen architecture, or try to get better performance numbers by reconfiguring the architecture, restructuring the application or modifying the mapping of the application. This process is reiterated until satisfactory performance figures are achieved.

In Figure 2.1, both the application and the architecture are modeled separately. The application model is used to represent the application's functional behavior, which is often called *model of computation*. Model of computation is a mathematical model that specifies the semantics of computation and of concurrency for the application. The architecture model captures performance constraints of architecture resources, by defining architectural components that represent processors or coprocessors, memories, buffers, buses, and so on. An application model is independent from the specific architectural characteristics and hence a single application model can be used for evaluating different architecture models.

To explore the design space of complex SoC platforms, it is required that the performance analysis of the platform architecture is done at multiple abstraction levels for target applications. This makes it possible to control the speed, required modeling effort and attainable accuracy of the performance evaluations. Higher-level abstraction models are used to efficiently explore the large design space in the early design stages. More detailed models are applied at later stages to allow focused architectural exploration. Hence the models of the application and architecture should also be made at various levels of abstraction respectively to enable the stepwise refinement approach in the design space exploration. In this thesis, we are concerned with the modeling and performance analysis of multimedia SoC platforms at system-level.

#### 2.2.1 Models of Computation

System-level models of computation typically describe the functional behaviors of an application as a hierarchical collection of tasks that are communicating with each other by means of events carried by channels. Based on the specification of the behaviors, the communication method, the implementation and validation mechanisms, and how the interconnected tasks are composed into a single one, the most important models of computation that have been proposed to date can be classified into being based on three basic models [56]: Discrete Event, Finite State Machines (FSMs) and Data Flow.

**Discrete Event Model:** In discrete event model, tasks communicate through multiplewriter and single-reader channels that carry globally ordered and time-tagged events. Task behavior is usually specified by a sequential language. As a task receives input events, it is executed and produces output events with the same or a larger time tag.

**Finite State Machines:** In finite state machines, task behavior is specified by a finite labeled transition system which is composed of states, transitions and actions. A state stores information that reflects the input changes from the system start to the present moment. The state executes the action (description of an activity) that is incurred when the required conditions (for example, entering/exiting the state, input conditions, certain transition) are satisfied. A transition indicates a state change, which is enabled only when a condition is fulfilled.

**Data Flow Model:** Data flow model is a special case of *Kahn Process Network* (KPN) computational model [45]. In a data flow process model, tasks communicate through one-way

FIFO channels. Each channel has unbounded capacity and carries a sequence (a stream) of data object. Each data object is written into the channel exactly once and read from the channel exactly once. Writes to channels are non-blocking, but reads are blocking (the read stalls when the input channel is empty). A task in data flow model is specified by a mapping from one or more input streams to one or more output streams.

#### 2.2.2 Models of Architecture

The architecture is modeled as a set of interconnected modules and components along with their associated software to implement the functions imposed by applications. A module or component in the architecture model is defined with specified interfaces and explicit context dependency. The architecture is desired to be modeled in multiple abstraction levels. When the level of abstraction is closer to the final implementation, it is more effective in reducing cost and design cycles by reusing designs. Minimal variations in specification, however, may result in very different implementations. The models with higher-level abstraction can be more easily shared among different specifications and only a minimal amount of work is needed to achieve final implementation. Having multiple levels of abstraction, however, is important, since the lower levels may change due to the advances in technology, while the higher levels stand stable across product versions.

#### 2.2.3 Performance Analysis

The application model is mapped onto the architecture model after both of these models are obtained, which is then followed by performance analysis of the application-architecture combination. The most common techniques for performance evaluation applied in industrial practice are simulation-based (e.g. VCC [88] and Seamless [80]). However, simulation possesses several disadvantages: it involves extensive running time, which fall behind the tight time-to-market demands today; it is also extremely difficult to find simulation patterns that lead to worst-case situations; it is hard to identify corner cases by simulation.

A great amount of research efforts have been put on presenting analytical techniques

for performance analysis of SoC platforms as simulation-based methods fall short. Formal analysis guarantees full performance corner-case coverage and bounds for critical performance parameters, based on well-defined models.

Most of the formal analysis techniques are proposed for individual architectural components and a general framework for analyzing system-level designs is not offered, especially in the presence of heterogeneity. Few exceptions consider special cases of more complex architectures, for example, analysis of response times for static-priority process scheduling combined with a TDMA bus protocol [70]. Recently, an event stream interface model is introduced [76, 73, 74] and functions are provided for event model transformations. Based on identifying architectural components for which appropriate analysis methods already exist in the literature, a unified framework is presented to couple different local analysis techniques into a global compositional description of the complex system-level properties. These works have been extended [44], where standard event models are extracted from realistic systems that exhibit complex task dependencies such as multi-rate data dependencies, data rate intervals and multiple activating inputs. It is shown [58] that advanced performance analysis techniques can take into account *system contexts*, i.e. correlations between successive computation or communication requests as well as correlated load distribution, to yield tighter analysis bounds.

## 2.3 SoC Design for Multimedia Applications

Various methods and tools have been developed for SoC design, examples of which are Ptolemy [1], Milan [64], Metropolis [10], Mesh [13], Koski [46], etc. Due to the proliferation of consumer electronics products that support media processing, attentions have also been paid to design SoC platforms for multimedia applications. In the following, we introduce two directly related work. The first [68] is the project of *Architectures and Methods for Embedded Media Systems* (Artemis). The other is from Philips during the design of Eclipse architecture templates for media processing SoCs [78, 79, 86]. **Application modeling:** Artemis and Eclipse model multimedia applications using the KPN computational model. KPNs fit nicely with multimedia processing application domain, where application is structured by a directed graph with each node representing a task and each edge representing a data channel. Each data channel is a FIFO buffer, with one producer and one or more consumers. Tasks are executed concurrently and exchange information solely through the unidirectional data channels. The functional behavior of the KPN model, which is observed as the sequence of data items that communicate through channels, is independent of the order in which the tasks are executed. This deterministic property means that the same input always results in the same application output and the application behavior is independent of architecture models. Hence an application's performance metrics and resource constraints can be analyzed in isolation from the architecture. **Architecture modeling:** Artemis aims to develop an architecture modeling and simulation environment for the efficient design space exploration of heterogeneous embedded-systems architectures at multiple abstraction levels.

In Artemis, the underlying architecture model does not model functional behavior, which has been caught by the application model. The architecture model is constructed from generic building blocks provided by a library, which contains performance models for various platform components such as processing cores, communication buses and different memory types. At a high abstraction level, various processing cores such as a programmable processor, reconfigurable component or dedicated hardware unit are abstracted as a processing-core model which functions as a *black-box*. To model the execution of an application event on a processing core, the architecture simulator assigns parameterizable latencies to the input events and thus simulates the timing behavior of the specific architectural implementation. The communication component within the architecture model (e.g. buses, memories), which the communicating Kahn channel is mapped onto, will account for the latencies associated with the data transfers.

Eclipse defines a heterogenous architecture template for designing high performance streaming-processing SoCs. This heterogenous architecture consists of fully programmable processor cores and various sophisticated hardwired function modules (coprocessors) optimized for high performance with minimum power consumption and silicon area.

Eclipse aims to present an architecture template that is flexible, scalable and costeffective. The configuration flexibility of programmable cores is combined with high performance of hardwired modules. It achieves scalability by avoiding centralized control in the system. It allows hardwired modules to operate in parallel and independently, and can also run multiple applications concurrently. By introducing such high levels of parallelism and multi-tasking, cost-effectiveness is achieved.

**Performance analysis.** Artemis applies trace-driven cosimulation technique to achieve an interface that includes the mapping specification between application models and architecture models. Each executed task produces a trace of events that represents the application workload that this task imposes on the architecture. The trace events correctly reflect data-dependent functional behavior and refer to the computation and communication operations an application task performs. Hence the architecture models, driven by the traces, can simulate the performance consequences of the application events and then evaluate the architecture's performance.

Eclipse models the architecture as a flexible, cycle-accurate simulator. It obtains the performance measurements such as buffer filling, coprocessor utilization and data access latency at the application level (i.e. for each task and stream) through application simulation and tuning for particular architectural instance.

Artemis and Eclipse rely on simulation to measure the performance metrics. Simulationbased approaches, however, are known to suffer from the disadvantages of high running time, incomplete coverage and failure to identify corner cases, which are even severe in the context of designing multimedia systems.

Efforts have been put on presenting analytical solutions for performance analysis of multimedia SoC platforms. Mathematical algorithms have been presented [69] to explore the design space of system buses, the usage of which is believed to affect greatly performances and power consumption of the system. These algorithms are used to optimize the system bus usage by finding pareto-optimal solutions (supporting the target applications at

the minimum cost in the sense of die area and energy consumption).

A formal technique for system-level power/performance analysis is presented [66], based on a proposed model called *Stochastic Automata Networks* (SANs). A process graph is used to model the application of interest and is translated to a network of automata, which is then used to generate the underlying Markov chain. The steady-state behavior of the SAN model is solved and performance measures are then derived. The technique, however, is purely probability-based and does not give any type of performance guarantees.

### 2.4 Characterization of Multimedia Workloads

A large amount of work has been conducted to model the video traffic in the context of network communications. A first model of *variable bit rate* video traffic models a video source as a first-order autoregressive process with marginal *probability distribution function* and an exponential autocorrelation function [57]. Later, a new methodology called *transform-expand-sample* is proposed to generate the number of bits in a frame following an arbitrary distribution and to model the frame correlation structure [55]. Lazar et al. [53] models the distribution and autocorrelation of a source bit stream accurately at the scene, the frame and the slice level.

The frame-size distribution for the three types of frames (i.e. I, P, and B) is also studied [81, 37, 40]. For example, a comprehensive characterization of MPEG video streams that captures the bit rate variations at multiple time scales is presented [50]. The sizes of different types of frames are modeled and intermixed as a complete model according to a given *group of pictures* pattern. The impact of scene changes on the long-term bit rate variations is also incorporated, in addition to modeling the marginal distribution and autocorrelation structure.

The above work concentrates on modeling the video traffic (i.e. the bit rate variations), but does not consider the variation in the execution time of multimedia streams.

Some previous work has been presented to predict the execution time of multimedia processing applications in order to employ real-time scheduling for efficiently implementing quality-of-service guarantees. Worst-case execution times (WCETs) of the MPEG-2 video decoding process are estimated [17] by integrating the WCET analysis into the decoder and taking into account of the actual input data. By considering frame type and size, a linear model of MPEG decoding is presented [11] to predict the actual decoding time for a frame.

Research has also been done on modeling the traffic and analyzing the execution time variability for multimedia applications in the context of computer systems design. The variability in the frame-level execution time on general-purpose architectures is analyzed for several multimedia applications [42]. It is concluded that execution time variability is mostly resulted from the application algorithm and the media input, and architectural features only contribute little to the variability in the execution time.

A recent work [87] addresses the modeling of on-chip traffic for the design of platforms for embedded multimedia appliances. It introduces that a fundamental property of selfsimilarity is exhibited by the bursty traffic between on-chip modules in typical MPEG-2 video applications. It quantifies the degree of self-similarity using the Hurst parameter and finds the optimal buffer-length distribution. In this work, a technique is also proposed to synthetically generating traces having statistical properties similar to real video clips and to speed up buffer simulations.

The above studies have mainly focused on modeling the video traffic and/or the execution time. They have not studied the design issues of the computer systems comprehensively and applied fully these modeling techniques to the design practice.

## 2.5 Network Calculus Theory

Network calculus is originally proposed as a theory of deterministic queuing systems for analyzing delay and backlog in a communication network, where the traffic and the service are characterized as envelope functions. This theory has been pioneered in the early 1990s for providing worst-case performance bounds for packet networks [28]. It is later developed to be placed in the *min-plus algebra* formulation [22, 15, 4], where the concept of *service*

*curves* is used to express service guarantees to a flow. A comprehensive understanding of this theory can be referred to referred to the following textbooks [23, 16].

Recently, network calculus has been extended to analyze SoC architectures in the context of network processors [21, 85]. Analytical frameworks based on this theory are developed to explore the design space of network processor architectures in the early design stages. After a relatively small set of potential architectures are identified through analytical approaches, simulation techniques are used to get more accurate performance measures in the later design stages.

Network calculus theory is further extended [20] to the domain of general SoC platform architectures. It extends and generalizes the standard event models used in previous work [73, 76], as well as presents a framework for analyzing various system properties like timing analysis, on-chip memory demand and resource loads of heterogenous platform-based architectures.

The concept of *workload curves* is proposed [60] to characterize the variable execution demands of tasks, which provides tighter best-/worst-case bounds on the execution times of tasks than traditional WCET analysis mechanisms. This concept is generalized [63] to characterize (give best-/worst-case bounds on) the various kinds of variability arising from multimedia processing on an MpSoC platform, the result of which is a new abstraction called VCCs. This concept of VCCs is used to identify how the buffer requirements change with different scheduling mechanisms implemented on the processors, and to achieve the tradeoffs between savings on on-chip buffer sizes and scheduling overheads through analytical methods.

Our work in this thesis follows this line of development and concentrates on proposing a framework for system-level design and analysis of SoC platforms for multimedia applications. We will study the modeling techniques and effective analytical solutions for the design space exploration of such platforms. In the next chapter, we will introduce the fundamental concepts, models and techniques that are used in this thesis.

# **Chapter 3**

# **Fundamental Models and Techniques**

## 3.1 Models of Application and Architecture

Our models of multimedia application and architecture follows the traditional modeling techniques that have been extensively used in the literature [68, 78, 79, 86]. We model the multimedia application using the KPN computational model. Since we concentrate on the system-level study of the SoC platforms, we model the MpSoC platform architecture at higher abstract level. The KPN model representing a multimedia application is partitioned and mapped onto an abstract architecture model, as shown in Figure 3.1.

In this thesis, we consider the following system-level view of multimedia stream processing on an MpSoC platform. Here we discuss the processing of one stream, which can be easily extended to the case that multiple streams are processed. The platform architecture consists of multiple processing elements (PEs) onto which different parts of an application are mapped. An input multimedia stream enters a PE, gets processed by the task(s) implemented on this PE, and the processed stream enters another PE for further processing. At the input of each PE is a buffer (a FIFO channel of fixed capacity) used to store the incoming stream to be processed. Finally, the fully processed stream is written into a *playout buffer* which is read by some *real-time client* (RTC) such as an audio or a video output device. For the sake of generality, we consider any multimedia stream to be made up of a sequence of *stream objects*. A stream object might be a bit belonging to a compressed bitstream representing a coded video clip, or a macroblock, or a video frame, or an audio sample—depending on where in the architecture the stream exists.

Figure 3.1: Illustration of the mapping of a multimedia application modeled as a KPN onto an MpSoC platform architecture modeled at abstract level.

Figure 3.2: An MpSoC platform onto which an MPEG-2 decoder application is partitioned and mapped.

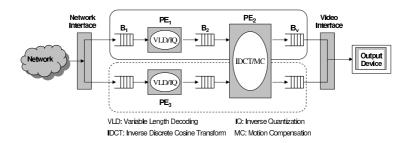

As an example, Figure 3.2 shows an architecture with two PEs ( $PE_1$  and  $PE_2$ ), implementing an MPEG-2 decoder application. The variable length decoding (VLD) and inverse quantization (IQ) tasks have been mapped onto  $PE_1$ , and the inverse discrete cosine transform (IDCT) and motion compensation (MC) tasks onto  $PE_2$ . A video stream, after being downloaded over a network, enters buffer  $B_1$ .  $PE_1$  reads from  $B_1$  and writes the resulting partially decoded macroblocks into buffer  $B_2$ .  $PE_2$  reads from  $B_2$  and writes the fully decoded macroblocks into the playout buffer  $B_v$ . The video output device reads from  $B_v$ at a pre-specified rate.

#### 3.2 Multimedia Workload Characterization

To design MpSoC platform architectures for multimedia processing, the first task is to characterize the workloads imposed on the platforms by the target multimedia applications. Clearly, workload characterization should be based on key properties that are important in a particular design context. Usually these are properties that have a strong impact on the performance of the architecture being designed. For instance, in microarchitectural design such properties would be instruction mix, branch prediction accuracy and cache miss rates [32]. In this thesis, we hypothesize that on the system level the performance of multimedia MpSoC architectures is largely influenced by various kinds of *data-dependent variability* associated with the processing of multimedia data streams. This hypothesis rests on the observation that such variability is the major source of the burstiness of on-chip traffic in such multimedia MpSoC platforms [87]. The burstiness of the on-chip traffic necessitates the insertion of additional buffers between architectural entities processing the multimedia streams, and the deployment of sophisticated scheduling policies across the platform. Both of these inevitably translate into increased design costs and power consumption [42]. Therefore, it is certainly meaningful to characterize multimedia workloads with respect to their variability properties.

What are the sources of variability that are usually associated with the processing of multimedia streams on such MpSoC platforms? Firstly, arrival patterns of multimedia streams at the input of the system may have a bursty nature, i.e. stream objects may arrive on the system's input in highly irregular intervals. A typical example of this is a multimedia device receiving streams from a congested network. Secondly, each activation of a task may consume and produce a variable number of stream objects from the associated streams. For example, each activation of the VLD task in Figure 3.2 consumes a variable number of bits from the network interface, although, it always produces one macroblock at its output. Thirdly, the execution demand of a task may vary from activation to activation due to data-dependent program flow. Both the tasks in our running example of the MPEG-2 decoder—VLD and IDCT—possesses this property. Finally, stream objects belonging to

the same stream may require different amounts of memory to store them in the communication channels. Again, in the example architecture shown in Figure 3.2, we note that the partially decoded macroblocks stored in buffer  $B_1$ , depending on their type, may or may not include motion vectors.

All these types of variability must be carefully considered and characterized during the workload design process. The concept of VCCs is a generic model that allows us to quantitatively capture the variability found in multimedia streams. In the following we describe this concept and give several examples of VCCs.

Variability characterization curves: VCCs are used to quantify best-/worst-case characteristics of *sequences*. These can be sequences of consecutive stream objects belonging to a stream, sequences of consecutive executions of a task implemented on a PE while processing a stream, or sequences of consecutive time intervals of some specified length. A VCC  $\mathcal{V}$  is composed of a tuple  $(\mathcal{V}^l(k), \mathcal{V}^u(k))$ . Both these functions take an integer k as the input parameter, which represents the *length* of a sequence. Function  $\mathcal{V}^l(k)$  then returns a *lower bound* on some property that holds for *all* subsequences of length k within some larger sequence. Similarly,  $\mathcal{V}^u(k)$  returns the corresponding *upper bound* that holds for *all* subsequences of length k within the larger sequence. Let the function P be a *measure* of some property over a sequence  $1, 2, \ldots$ . If P(n) denotes the measure of this property for the first n items of the sequence (i.e.  $0, \ldots, n$ ), then we have  $\mathcal{V}^l(k) \leq P(i + k) - P(i) \leq \mathcal{V}^u(k)$ for all  $i \geq 0$  and  $k \geq 1$ . By default, P(0) is assumed to be equal to 0. As examples, let us now consider the following different realizations of a VCC.

Workload curve  $\gamma = (\gamma^l, \gamma^u)$ : The VCC  $\gamma$  is used to characterize the variability in the execution requirements of a sequence of stream objects to be processed by a PE. In this case, given a sequence of stream objects, P(n) denotes the total number of processor cycles required to process the first *n* stream objects. Hence,  $\gamma^l(k)$  and  $\gamma^u(k)$  denote the minimum and the maximum number of processor cycles that might be required by *any k* consecutive stream objects within the given sequence. Let us see an example as illustrated in Figure 3.3,  $\gamma^l(4)$  ( $\gamma^u(4)$ ) denotes the minimum (maximum) number of processor cycles required by

Figure 3.3: Illustration of workload curve  $\gamma$ .

any 4 consecutive stream objects within the given sequence, which records the minimum (maximum) value of P(i+4) - P(i) for all  $i \ge 0$ . Hence, P(4), which denotes the number of cycles required by the first 4 stream objects, is lower and upper bounded by  $\gamma^{l}(4)$  and  $\gamma^{u}(4)$  respectively.

Let  $e_{\min}$  and  $e_{\max}$  be the minimum and the maximum number of processor cycles required by any single stream object belonging to a sequence. For any reasonably large value of k,  $\gamma^{l}(k)$  is clearly greater than  $k \times e_{\min}$ . Further, the difference between them increases with increasing values of k. Similarly,  $\gamma^{u}(k)$  is clearly smaller than  $k \times e_{\max}$ . Hence, the VCC  $\gamma$  is more expressive compared to simple best- or worst-case characterizations commonly used in the real-time systems domain.

It is also meaningful to construct a *pseudo-inverse* of a VCC  $\mathcal{V}$ , which we denote as  $\mathcal{V}^{-1}$ . In the case of a workload curve,  $\gamma^{l^{-1}}(e) = \min_{k\geq 0}\{k \mid \gamma^l(k) \geq e\}$  and  $\gamma^{u^{-1}}(e) = \max_{k\geq 0}\{k \mid \gamma^u(k) \leq e\}$ . Hence,  $\gamma^{l^{-1}}(e)$  denotes the maximum number of stream objects that may be processed using *e* processor cycles.  $\gamma^{u^{-1}}(e)$  denotes the minimum number of stream objects that are guaranteed to be processed using *e* processor cycles.

Arrival curve  $\alpha = (\alpha^l, \alpha^u)$ : This VCC is used to characterize the burstiness in the arrival pattern of stream objects. Given a trace of the arrival times of a sequence of stream objects at buffer *b* (e.g. the partially processed macroblocks being written into the buffer  $B_2$  in Figure 3.2),  $\alpha^l(\Delta)$  and  $\alpha^u(\Delta)$  denote the minimum and the maximum number of stream objects that arrive within *any* time interval of length  $\Delta$ . Given a PE that is processing

Figure 3.4: Illustration of arrival curve  $\alpha$ .

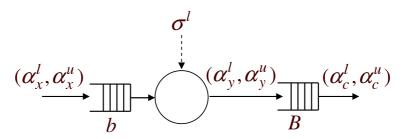

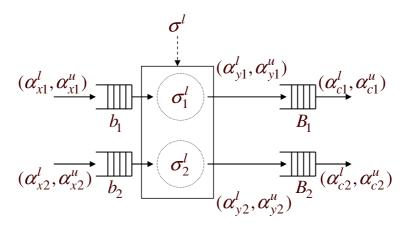

a single stream,  $(\alpha_x^l, \alpha_x^u)$  are used to represent the incoming stream,  $(\alpha_y^l, \alpha_y^u)$  represent the processed stream and  $(\alpha_c^l, \alpha_c^u)$  represent the bounds on the rate at which the stream is consumed from the playout buffer. We will often refer to  $(\alpha_c^l, \alpha_c^u)$  as the *consumption bounds*. As illustrated in Figure 3.4,  $\alpha^l(6)$  and  $\alpha^u(6)$  respectively record the minimum and maximum number of stream objects that may arrive at buffer *b* over any time interval of length 6. Therefore,  $\alpha^l(6)$  and  $\alpha^u(6)$  show lower and upper bounds on the number of stream objects over any time interval of length 6 (e.g. [0, 6]).

Let us see one more example, let  $\alpha_x^l(10) = \alpha_x^u(10) = 5$ , which essentially means that within any time interval of length 10, at least and at most 5 stream objects can arrive at buffer b. Hence, the average arrival rate is one stream object in every two time units. Now suppose that we are also given that  $\alpha_x^u(2) = 4$ , which means that within a time interval of length 2 there might be a burst of at most 4 stream objects. Following this specification, if 4 stream objects arrive at b during the time interval [0, 2], then over the time interval (2, 10] at most 1 stream object can arrive. Hence, although the "long-term" arrival rate of the stream is 0.5 stream objects per unit time, there might be occasional bursts. The arrival curves  $\alpha^l$ and  $\alpha^u$  allow for the precise characterization of such bursts.

Service curve  $\beta = (\beta^l, \beta^u)$ : Due to the variability in the execution requirements of stream objects, the number of stream objects that can potentially be processed within any specified time interval varies (even when the processor runs at a constant frequency). We will use

Figure 3.5: Illustration of service curve  $\beta$ .

$\beta^{l}(\Delta)$  and  $\beta^{u}(\Delta)$  to denote the minimum and the maximum number of stream objects that can be processed (or served) by a processor within *any* time interval of length  $\Delta$ . The curves  $\beta^{l}$  and  $\beta^{u}$  may also be derived from a trace of execution requirements of stream objects and the clock frequency with which the processor is being run. Figure 3.5 shows an example for service curves. The number of stream objects that can be served within any time interval of length 4 is lower and upper bounded by  $\beta^{l}(4)$  and  $\beta^{u}(4)$  respectively.

Note that this specification of *service* is stream dependent. It is also possible to specify the service offered by a processor in a stream-independent manner. Towards this, let  $\sigma^l(\Delta)$ and  $\sigma^u(\Delta)$  denote the minimum and the maximum number of processor cycles available within any time interval of length  $\Delta$ . It is then easy to see that  $\beta^l(\Delta) = \gamma^{u-1}(\sigma^l(\Delta))$  where  $\gamma^u$  is the workload curve associated with the stream (which was described above).

Consumption and production curves  $\kappa = (\kappa^l, \kappa^u)$  and  $\pi = (\pi^l, \pi^u)$ : Let an input stream be processed by a task T. Each activation of T consumes a variable number of stream objects belonging to the input stream, and results in the production of a variable number of output stream objects, possibly of a different type. This variability in the consumption and production rates of T can be quantified using two VCCs  $\kappa$  and  $\pi$ , which we refer to as the consumption and the production curves respectively.

$\kappa^{l}(k)$  takes an integer k as an argument and returns the minimum number of activations of T that will be required to completely process any k consecutive stream objects.

Figure 3.6: Illustration of consumption curve  $\kappa$ .

Similarly,  $\kappa^u(k)$  returns the maximum number of activations of T that might be required to process any k consecutive stream objects. Let us see an example. As shown in Figure 3.2, the bit stream at buffer  $B_1$  is processed by  $PE_1$ . Each activation of the VLD/IQ task processes one macroblock from buffer  $B_1$ . As illustrated in Figure 3.6,  $\kappa^l(k)$  ( $\kappa^u(k)$ ) returns the minimum (maximum) number of activations of the VLD/IQ task (i.e. number of macroblocks) that is required to process any k consecutive bits from buffer  $B_1$ .

On the other hand, we define  $\pi^l(k)$  to be the minimum number of stream objects guaranteed to be produced due to any k consecutive activations of T.  $\pi^u(k)$  is the maximum number of stream objects that can be produced due to any k consecutive activations of T. Therefore, k consecutive stream objects at the input of T will result in at least  $\pi^l(\kappa^l(k))$ and at most  $\pi^u(\kappa^u(k))$  stream objects at its output. As an example, the production curves  $\pi^l(k)$  and  $\pi^u(k)$  for  $PE_1$  shown in Figure 3.2, are straight lines with slopes that correspond to the constant-rate production of one macroblock per task activation.

### 3.3 Performance Analysis

Given the MpSoC platform architecture that multimedia applications are mapped onto, the workloads imposed on the architecture are firstly characterized and represented by VCCs. We then evaluate the performance of this architecture and design/configure the architectural parameters, by taking into account the cost, application and architectural constraints etc.

Typical design constraints for a multimedia MpSoC platform architecture that we have modeled (e.g. the one shown in Figure 3.2) are (i) the playout buffers should not underflow, and (ii) none of the buffers should overflow. The constraint on the playout buffer underflow is to ascertain that stream objects can be read out by the audio/video output devices at the specified playback rate, and hence the output quality is guaranteed. The constraints on buffer overflow are motivated by the fact that typically on-chip PEs use static voltage and task scheduling policies. This is because using blocking write/read mechanisms efficiently to prevent buffer overflows/underflows either require a multithreaded processor architecture or substantial run-time operating system support for context switching.

We present an analytical framework for the performance analysis and design space exploration of multimedia MpSoC platform architectures. In contrast to simulation-based approaches, which usually follow a trial-and-error approach and is very time-consuming, our proposed framework can help a system designer to explore the design space in a very short time and to systematically tune a platform architecture. Our framework is based on the network calculus theory and extends this theory by developing new algorithms and models. In the following, we introduce some notation and a technical result that will be used in later chapters.

**Notation.** Throughout this thesis, all functions f are assumed to be wide-sense increasing, meaning that  $f(x_1) \le f(x_2)$  for  $x_1 \le x_2$  and f(x) = 0 for  $x \le 0$ . For any two functions fand g, the *min-plus convolution* of f and g is denoted by

$$(f \otimes g)(t) = \inf_{0 \le s \le t} \{f(t-s) + g(s)\}$$

and the *min-plus deconvolution* of f and g is denoted by

$$(f \oslash g)(t) = \sup_{u \ge 0} \{ f(t+u) - g(u) \}$$

We will use  $f \wedge g$  to denote the infimum or minimum (if it exists) of f and g, and  $f \vee g$  to denote the supremum or maximum (if it exists) of f and g.

**Lemma 1** For any functions f, g and h,  $g \otimes h \geq f$  if and only if  $h \geq f \otimes g$ .

This lemma follows from the definitions of the min-plus convolution and deconvolution operations and shows the relation between them.

## **3.4 Experimental Setup**

We have conducted experiments to illustrate and validate our analytical framework. Since MPEG-2 streams have a complex nature and a rich set of characteristics [50], they represented an interesting target for our experiments. We studied the MpSoC platform architectures with an MPEG-2 decoder application mapped onto, one of which is that shown in Figure 3.2.

Our experimental setup consisted of the SimpleScalar instruction set simulator, a system simulator and an MPEG-2 decoder program. The MPEG-2 decoder program was used as an executable for the simulator and as a means to obtain traces of bit allocation to macroblocks.

The instruction set simulator was used to obtain traces of execution times for the VLD/IQ and IDCT/MC tasks of the MPEG-2 decoding algorithm. All the tasks processed the data stream at the macroblock granularity. The *sim-profile* configuration of the SimpleScalar simulator and the PISA instruction set were used to model on-chip processors of the architecture. Although this configuration does not model advanced microarchitectural features of the processor, it allows fast simulation and was therefore the most suitable choice. This choice is also justified by the fact that advanced features in the microarchitecture of a general-purpose processors do not have significant impact on the variability of multimedia workloads [42].

The system simulator consisted of a SystemC transaction-level model of the architecture. We used it to measure backlogs in the buffers resulting from the execution of the MPEG-2 decoder application on the platform.

# **Chapter 4**

# Characterizing Multimedia Workloads: Obtaining VCCs

To conduct performance analysis for given MpSoC platforms, we firstly have to characterize the workloads for the application that can be run on the platforms. In this chapter, we obtain the various kinds of characterization curves (VCCs) that represent the workloads imposed on the architecture. Due to the large volume of potential inputs to the system, it is impossible to cover every input stream and it is also time consuming. Hence good "representative" multimedia inputs should be selected and VCCs are then measured for these set of representative workloads. The measured VCCs are used to represent the workloads imposed by the large library of potential inputs, in the sense of best-/worst-case bounds.

Selecting a good "representative" input set is of course not a new concern—benchmark selection or workload design is a well recognized problem in the domain of microprocessor design. However, the main issues in that domain are microarchitecture-centric, where a designer is mostly concerned with program characteristics like instruction mix, data and instruction cache miss rates and branch prediction accuracy. On the other hand, the concerns in the case of system-level design of platform architectures are very different and these are not suitably reflected in a benchmark suite designed for microarchitecture evaluation.

In this chapter we attempt to address this issue of workload design in the specific context of system-level design of platform architectures for multimedia processing. Although simulation-oriented design and evaluation are widespread in the domain of system-level design, to the best of our knowledge the issue of methodically selecting representative inputs for architecture evaluation has not received any attention so far. Most of the work reported in the Embedded Systems literature, on novel system models or simulation schemes, shirk off this problem and leave the responsibility of choosing a representative input or stimuli to the architecture on the system designer (see, for example, [52]).

There are many reasons why this problem is interesting in the specific case of multimedia processing on MpSoC platforms. Firstly, many multimedia applications exhibit a large degree of data-dependent variability that complicates the problem of choosing a representative input set. Secondly, in contrast to general-purpose architectures, MpSoC platforms that are optimized for stream processing have heterogeneous parallel architectures. This fact further complicates the problem. Thirdly, multimedia processing is in general computationally intensive, which makes workload selection an important problem.

Arbitrarily selecting inputs to form the "representative" input set is certainly not a good idea. The goal of "representative" workload design should be to select inputs that represent *corner cases* for the target architecture, i.e. those inputs which impose worst- and best-case loads on different parts of the architecture. However, determining what constitutes a "corner case" is not a trivial undertaking due to the complex nature of most multimedia workloads. Attempts towards using some qualitative technique to judge the properties of multimedia streams based on their content (for example, by simply viewing video clips to be processed by the architecture and classifying them based on experience or intuition) might easily fail. Hence, a quantitative methodology is necessary, using which it should be possible to objectively assess and compare the properties of a large library of samples can then be chosen.