## SPACE VECTOR PULSEWIDTH MODULATION FOR MULTILEVEL INVERTERS AND SOLUTIONS TO MODULATION DEPENDENT PROBLEMS

AMIT KUMAR GUPTA (B. ENG. IIT-ROORKEE, INDIA)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE AUGUST, 2008

## Acknowledgments

It is indeed a wonderful opportunity to thank and cheer for everyone who directly or indirectly contributed towards the success of this thesis. First of all, I thank my thesis supervisor A/P Ashwin M. Khambadkone for his guidance and suggestions throughout my thesis work. As a mentor, he believes in making his students independent and professionally capable. His regular interaction always kept me focused in my research work. I believe his training will help me in building my future career as well.

I express my sincere gratitude and thanks to A/P R. Oruganti and A/P S. K. Panda who have been my module lecturers, lab supervisors and qualifying examiners. I would also like to thank Mr. Y. C. Woo, and Mr. M. Chandra of Electrical machines and Drives lab, National University of Singapore (NUS). Their willingness to help in any problem is beyond appreciation. My thanks to Mr. Teo, Mr. Seow and Mr. Jalil for their help during my research work. Thanks to my fellow research scholars also, for their cooperation in the laboratory. I would also like to thank the thesis examiners for their invaluable time to examine my thesis.

I would like to thank National University of Singapore for giving me the

opportunity for doing graduate studies and for awarding research scholarship. I would like to thank Department of Electrical and Computer Engineering, NUS for the wonderful laboratory facilities and support. I am also thankful to the department for giving me opportunity for the part time tutoring job.

I am greatly indebted to my parents for making me capable to pursue this task. Their support and confidence in me, even in the most difficult times at home during my Ph.D., is indescribable. Their constant encouragement and patience always kept me motivated to finish my work in time. The love and support from my wife Anjali during thesis writing period has been truly helpful. I also admire and thank my friends in India, Singapore, Korea and elsewhere for their encouragement and help whenever required.

Above all, I thank almighty for giving me this opportunity and strength to accomplish this task. I dedicate this thesis to Sri Radhe Govind.

# Contents

|     | Ack   | knowledgement                              | i     |

|-----|-------|--------------------------------------------|-------|

|     | Tab   | ble of Contents                            | iii   |

|     | Sun   | nmary                                      | xi    |

| Lis | st of | Tables                                     | xiv   |

| Lis | st of | Figures                                    | xvi   |

|     | List  | t of Symbols                               | xxiii |

|     | List  | t of Abbreviations                         | xxvi  |

| 1   | Intr  | roduction                                  | 1     |

|     | 1.1   | Multilevel Inverters                       | 1     |

|     |       | 1.1.1 Applications of Multilevel Inverters | 2     |

|     | 1.1.2 | Main Features and Drawbacks                       | 2  |

|-----|-------|---------------------------------------------------|----|

|     | 1.1.3 | Functional Diagram of the Multilevel Inverters    | 3  |

| 1.2 | Topol | ogies of Multilevel Inverters                     | 4  |

|     | 1.2.1 | Neutral Point Clamped (NPC) Topology              | 5  |

|     | 1.2.2 | Cascaded H-bridge Topology                        | 6  |

|     | 1.2.3 | Capacitor Clamped Topologies                      | 7  |

| 1.3 | Motiv | ation - Problem Description                       | 9  |

|     | 1.3.1 | Common Mode Voltage                               | 9  |

|     | 1.3.2 | Asynchronous PWM Harmonics                        | 12 |

|     | 1.3.3 | Required Features in a PWM Technique              | 16 |

|     | 1.3.4 | Multilevel Space Vector PWM (SVPWM)               | 18 |

|     | 1.3.5 | Overmodulation for Multilevel Inverters           | 21 |

|     | 1.3.6 | Neutral Point Fluctuation Problem in NPC Inverter | 22 |

|     | 1.3.7 | Summary                                           | 24 |

| 1.4 | Backg | round Work - Literature Survey                    | 25 |

|     | 1.4.1 | Multilevel Space Vector PWM                       | 25 |

|     | 1.4.2 | Overmodulation for Multilevel Inverters           | 28 |

|     | 1.4.3 | Common Mode Voltage Reduction                     | 29 |

|   |     | 1.4.4  | Asynchr     | onous PWM Harmonics                                                                            | 35 |

|---|-----|--------|-------------|------------------------------------------------------------------------------------------------|----|

|   |     | 1.4.5  | Neutral     | Point Fluctuation Reduction in NPC Inverter                                                    | 38 |

|   | 1.5 | Contri | ibution of  | the Thesis                                                                                     | 39 |

|   | 1.6 | Organ  | ization of  | the Thesis                                                                                     | 43 |

| 2 |     |        |             | M Algorithm for Multilevel Inverters based on<br>Tector PWM                                    | 44 |

|   | 2.1 | Introd | uction .    |                                                                                                | 44 |

|   | 2.2 | Propo  | sed Algor   | ithm of On-time Calculation                                                                    | 47 |

|   |     | 2.2.1  | The On-     | time Calculation for two-level SVPWM                                                           | 47 |

|   |     | 2.2.2  | The On-     | time Calculation for 3-level SVPWM                                                             | 48 |

|   |     | 2.2.3  | The On-     | time Calculation for 5-level SVPWM                                                             | 50 |

|   | 2.3 | Simpli | ified Struc | eture of the Proposed Scheme                                                                   | 51 |

|   | 2.4 | Implei | mentation   | of the Proposed Scheme                                                                         | 53 |

|   |     | 2.4.1  | Processi    | ng Unit                                                                                        | 53 |

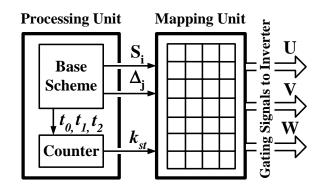

|   |     |        | 2.4.1.1     | Determination of Sector                                                                        | 54 |

|   |     |        | 2.4.1.2     | Determination of Small Vector $\boldsymbol{v}^{\boldsymbol{s}}$ and Triangle Number $\Delta_j$ | 54 |

|   |     |        | 2.4.1.3     | Calculation of On-times                                                                        | 59 |

|   |     | 2.4.2  | Mapping     | g Unit                                                                                         | 59 |

|   |            | 2.4.3                            | Experim                                                                        | nental results                                                                                                                                                                                                                                                                                                                                                                                                         | 61                                                                     |

|---|------------|----------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|   |            |                                  | 2.4.3.1                                                                        | Experimental Results for 3-level NPC Inverter                                                                                                                                                                                                                                                                                                                                                                          | 62                                                                     |

|   |            |                                  | 2.4.3.2                                                                        | Experimental Results for 5-level Cascaded H-Bridge<br>Inverter                                                                                                                                                                                                                                                                                                                                                         | 63                                                                     |

|   | 2.5        | Exten                            | sion of Sc                                                                     | wheme for a $n$ -level Inverter $\ldots$                                                                                                                                                                                                                                                                                                                                                                               | 64                                                                     |

|   |            | 2.5.1                            | Processi                                                                       | ng Unit for $n$ -level                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                     |

|   |            | 2.5.2                            | Mapping                                                                        | g Unit for $n$ -level                                                                                                                                                                                                                                                                                                                                                                                                  | 68                                                                     |

|   | 2.6        | Summ                             | ary                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                        | 72                                                                     |

| 3 | -          |                                  |                                                                                | M Algorithm for Multilevel Inverters for Oper-<br>ulation Range                                                                                                                                                                                                                                                                                                                                                        | 73                                                                     |

|   | auto       |                                  | vermou                                                                         | ulation Mange                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                     |

|   | 3.1        |                                  |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                        | 74                                                                     |

|   |            | Introd                           | luction .                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|   | 3.1        | Introd<br>Modu                   | luction .<br>lation Ind                                                        | -<br>                                                                                                                                                                                                                                                                                                                                                                                                                  | 74                                                                     |

|   | 3.1<br>3.2 | Introd<br>Modu                   | luction .<br>lation Ind<br>tion in O                                           | lex and Modes of Modulation                                                                                                                                                                                                                                                                                                                                                                                            | 74<br>75<br>76                                                         |

|   | 3.1<br>3.2 | Introd<br>Modu<br>Opera          | luction .<br>lation Ind<br>tion in O                                           | lex and Modes of Modulation         vermodulation         Mode                                                                                                                                                                                                                                                                                                                                                         | 74<br>75<br>76                                                         |

|   | 3.1<br>3.2 | Introd<br>Modu<br>Opera          | luction .<br>lation Ind<br>tion in O<br>Overmo                                 | lex and Modes of Modulation $\dots \dots \dots \dots \dots \dots \dots$<br>vermodulation Mode $\dots \dots \dots$<br>dulation Mode I (0.907 $\leq m_i < 0.9535$ ) $\dots \dots \dots \dots \dots \dots$                                                                                                                                                    | 74<br>75<br>76<br>76                                                   |

|   | 3.1<br>3.2 | Introd<br>Modu<br>Opera          | luction .<br>lation Ind<br>tion in O<br>Overmo<br>3.3.1.1<br>3.3.1.2           | lex and Modes of Modulation $\dots \dots \dots \dots \dots \dots$<br>vermodulation Mode $\dots \dots \dots \dots \dots \dots \dots \dots \dots$<br>dulation Mode I (0.907 $\leq m_i < 0.9535$ ) $\dots \dots \dots \dots \dots \dots$<br>Hexagonal Portion ( $\alpha_c \leq \gamma < \pi/3 - \alpha_c$ ) $\dots \dots \dots \dots \dots$                                                                               | <ul> <li>74</li> <li>75</li> <li>76</li> <li>76</li> <li>78</li> </ul> |

|   | 3.1<br>3.2 | Introd<br>Modu<br>Opera<br>3.3.1 | luction .<br>lation Ind<br>tion in O<br>Overmo<br>3.3.1.1<br>3.3.1.2<br>Overmo | lex and Modes of Modulation $\dots \dots \dots \dots \dots$<br>vermodulation Mode $\dots \dots \dots \dots \dots \dots \dots \dots$<br>dulation Mode I (0.907 $\leq m_i < 0.9535$ ) $\dots \dots \dots \dots \dots$<br>Hexagonal Portion ( $\alpha_c \leq \gamma < \pi/3 - \alpha_c$ ) $\dots \dots \dots \dots$<br>Circular Portion ( $0 \leq \gamma < \alpha_c$ and $\pi/3 - \alpha_c \leq \gamma < \pi/3$ ) $\dots$ | 74<br>75<br>76<br>76<br>78<br>79                                       |

|   |                   | 3.4.2                               | Mapping                                                                       | g Unit                                                                                                                                                           | 85                                      |

|---|-------------------|-------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|   |                   |                                     | 3.4.2.1                                                                       | Memory unit for Circular Track (M-CR)                                                                                                                            | 87                                      |

|   |                   |                                     | 3.4.2.2                                                                       | Memory unit for Hexagonal Track (M-HX)                                                                                                                           | 90                                      |

|   |                   |                                     | 3.4.2.3                                                                       | Memory unit for Hold Mode (M-HL) $\hdots$                                                                                                                        | 91                                      |

|   | 3.5               | Exper                               | imental R                                                                     | esults                                                                                                                                                           | 92                                      |

|   | 3.6               | Exten                               | sion of the                                                                   | e algorithm to $n$ -level inverter $\ldots \ldots \ldots \ldots$                                                                                                 | 95                                      |

|   |                   | 3.6.1                               | Processi                                                                      | ng Unit                                                                                                                                                          | 95                                      |

|   |                   | 3.6.2                               | Mapping                                                                       | g unit                                                                                                                                                           | 97                                      |

|   |                   |                                     |                                                                               |                                                                                                                                                                  |                                         |

|   | 3.7               | Summ                                | ary                                                                           |                                                                                                                                                                  | 99                                      |

| 4 | Spa               | ce Ve                               | ctor PW                                                                       | M Scheme to Reduce Common Mode Voltage                                                                                                                           | 99<br>. <b>00</b>                       |

| 4 | Spa               | ce Ve<br>Casca                      | ctor PW<br>ded Mult                                                           | M Scheme to Reduce Common Mode Voltage                                                                                                                           | .00                                     |

| 4 | Spa<br>for        | ce Veo<br>Cascao<br>Introc          | ctor PW<br>ded Mult                                                           | M Scheme to Reduce Common Mode Voltage<br>tilevel Inverters 1                                                                                                    | - <b>00</b><br>101                      |

| 4 | Spa<br>for<br>4.1 | ce Veo<br>Cascao<br>Introd<br>Prope | ctor PW<br>ded Mult<br>luction<br>sed Schen                                   | M Scheme to Reduce Common Mode Voltage         tilevel Inverters       1                                                                                         | - <b>00</b><br>101<br>103               |

| 4 | Spa<br>for<br>4.1 | ce Veo<br>Cascao<br>Introd<br>Prope | ctor PW<br>ded Mult<br>luction<br>sed Schen<br>Equilate                       | M Scheme to Reduce Common Mode Voltage         tilevel Inverters       1          1          1          1          1          1          1          1          1 | . <b>00</b><br>101<br>103<br>106        |

| 4 | Spa<br>for<br>4.1 | ce Veo<br>Cascao<br>Introd<br>Prope | ctor PW<br>ded Mult<br>luction<br>sed Schen<br>Equilate<br>4.2.1.1            | M Scheme to Reduce Common Mode Voltage         tilevel Inverters       1                                                                                         | . <b>00</b><br>101<br>103<br>106        |

| 4 | Spa<br>for<br>4.1 | ce Veo<br>Cascao<br>Introd<br>Prope | ctor PW<br>ded Mult<br>luction<br>sed Schen<br>Equilate<br>4.2.1.1<br>4.2.1.2 | M Scheme to Reduce Common Mode Voltage         tilevel Inverters       1                                                                                         | - <b>00</b><br>101<br>103<br>106<br>107 |

|   |                   | 4.2.2.2 Switching Sequence                                                                                                                                                                                                                                                                                                                                                               |              | 109                                                                                                   |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------|

|   | 4.3               | 3 Implementation for a 5-level inverter                                                                                                                                                                                                                                                                                                                                                  |              | 110                                                                                                   |

|   | 4.4               | 4 Experimental Results for 5-level Inverter                                                                                                                                                                                                                                                                                                                                              |              | 113                                                                                                   |

|   | 4.5               | 5 The scheme at higher level                                                                                                                                                                                                                                                                                                                                                             |              | 121                                                                                                   |

|   |                   | 4.5.0.3 Processing Unit                                                                                                                                                                                                                                                                                                                                                                  |              | 122                                                                                                   |

|   |                   | 4.5.0.4 Mapping Unit                                                                                                                                                                                                                                                                                                                                                                     |              | 123                                                                                                   |

|   |                   | 4.5.1 Normalization with respect to two-level in                                                                                                                                                                                                                                                                                                                                         | verter       | 124                                                                                                   |

|   | 4.6               | 6 Summary                                                                                                                                                                                                                                                                                                                                                                                |              | 125                                                                                                   |

|   |                   |                                                                                                                                                                                                                                                                                                                                                                                          |              |                                                                                                       |

| 5 | •                 | ynchronous Space Vector Modulation Based<br>ontrol of a Grid Connected Cascaded Multiley                                                                                                                                                                                                                                                                                                 | -            | x<br>126                                                                                              |

| 5 | •                 | ontrol of a Grid Connected Cascaded Multilev                                                                                                                                                                                                                                                                                                                                             | vel Inverter | 126                                                                                                   |

| 5 | Con               | Image: Addition of a Grid Connected Cascaded Multilev         1       Introduction                                                                                                                                                                                                                                                                                                       | vel Inverter | <b>126</b><br>128                                                                                     |

| 5 | <b>Con</b><br>5.1 | Introduction       Introduction         Principle of Flux Error Based SVPWM                                                                                                                                                                                                                                                                                                              | vel Inverter | <b>126</b><br>128<br>131                                                                              |

| 5 | Con<br>5.1<br>5.2 | Introduction       Introduction         Principle of Flux Error Based SVPWM                                                                                                                                                                                                                                                                                                              | vel Inverter | <ul><li>126</li><li>128</li><li>131</li><li>133</li></ul>                                             |

| 5 | Con<br>5.1<br>5.2 | Introduction       Introduction         Principle of Flux Error Based SVPWM         Proposed Close Loop Scheme                                                                                                                                                                                                                                                                           | vel Inverter | <ul> <li>126</li> <li>128</li> <li>131</li> <li>133</li> <li>134</li> </ul>                           |

| 5 | Con<br>5.1<br>5.2 | Introduction       Introduction         Principle of Flux Error Based SVPWM          Proposed Close Loop Scheme          5.3.1       Block 'S': Synchronous SVPWM                                                                                                                                                                                                                        | vel Inverter | <ol> <li>126</li> <li>128</li> <li>131</li> <li>133</li> <li>134</li> <li>135</li> </ol>              |

| 5 | Con<br>5.1<br>5.2 | Pontrol of a Grid Connected Cascaded Multilev         1       Introduction         2       Principle of Flux Error Based SVPWM         3       Proposed Close Loop Scheme         3       Proposed Close Loop Scheme         5.3.1       Block 'S': Synchronous SVPWM         5.3.2       Block 'E': Estimation of Flux $\psi_c$ 5.3.3       Block 'P': Prediction of Flux $\psi_{pc}^*$ | vel Inverter | <ul> <li>126</li> <li>128</li> <li>131</li> <li>133</li> <li>134</li> <li>135</li> <li>138</li> </ul> |

|   |      | 5.5.1 Processing Unit                                                                                                                                |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 5.5.2 Mapping Unit                                                                                                                                   |

|   | 5.6  | Experimental Results, and Their Analysis                                                                                                             |

|   | 5.7  | Summary                                                                                                                                              |

| 6 | at H | pace Vector PWM Scheme to Operate a 3-level NPC Inverter<br>High Modulation Index Including Over-modulation Range, with<br>Itral Point Balancing 175 |

|   | 6.1  | Introduction                                                                                                                                         |

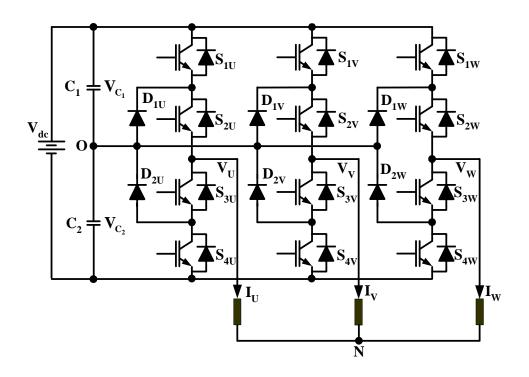

|   | 6.2  | Neutral Point Fluctuation Problem                                                                                                                    |

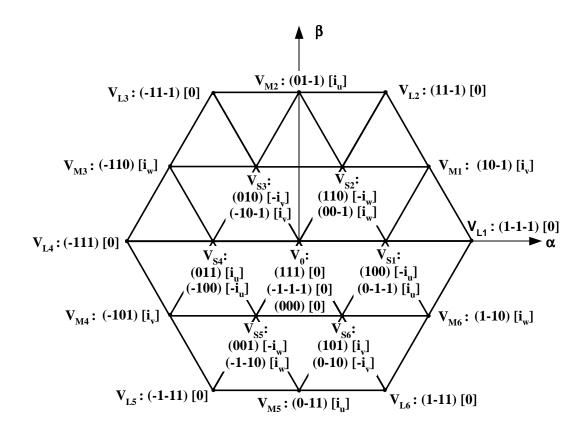

|   |      | 6.2.1 Switching Vectors Vs. Neutral Point Fluctuation 179                                                                                            |

|   |      | 6.2.2 Effect of Varying PF on the Neutral Point Current 182                                                                                          |

|   | 6.3  | Proposed Scheme                                                                                                                                      |

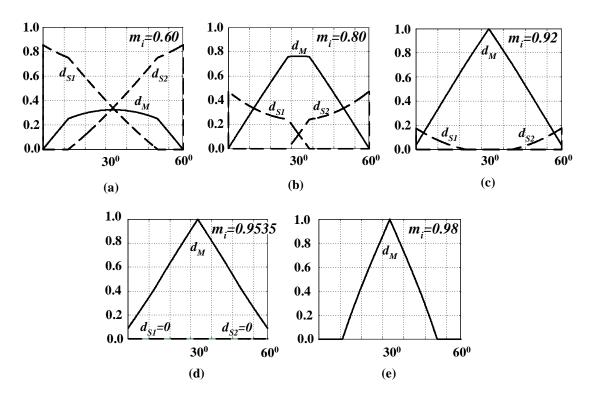

|   | 6.4  | Linear Modulation Mode ( $m_i < 0.907$ )                                                                                                             |

|   |      | 6.4.1 N3V Scheme                                                                                                                                     |

|   |      | 6.4.2 S3V Scheme                                                                                                                                     |

|   | 6.5  | Overmodulation Mode - I $(0.907 \le m_i < 0.9535)$                                                                                                   |

|   |      | 6.5.1 Circular Portion $(0 \le \gamma < \alpha_c \text{ and } \pi/3 - \alpha_c \le \gamma < \pi/3)$                                                  |

|   |      | 6.5.1.1 N3V Scheme                                                                                                                                   |

|   |      | 6.5.1.2 S3V Scheme                                                                                                                                   |

|   |     | 6.5.2   | Hexagon     | al Portion $(\alpha_c \leq \gamma < \pi/3 - \alpha_c)$ | 193 |

|---|-----|---------|-------------|--------------------------------------------------------|-----|

|   |     |         | 6.5.2.1     | N2V Scheme                                             | 194 |

|   |     |         | 6.5.2.2     | S2V Scheme                                             | 194 |

|   | 6.6 | Overn   | nodulatior  | n Mode II $(0.9535 \le m_i)$                           | 195 |

|   | 6.7 | Struct  | sure of the | e Scheme                                               | 196 |

|   | 6.8 | Exper   | imental a   | nd Simulation Results                                  | 198 |

|   | 6.9 | Summ    | ary         |                                                        | 206 |

| 7 | Des | criptic | on of Exp   | perimental Platform, Software and Hardware             | 208 |

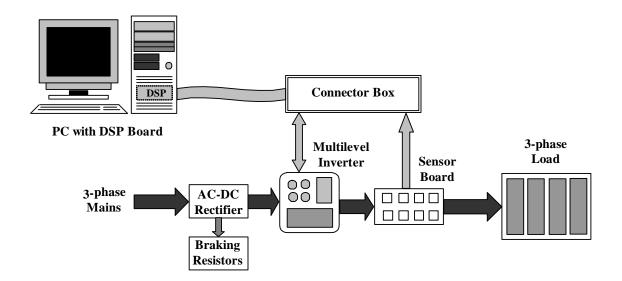

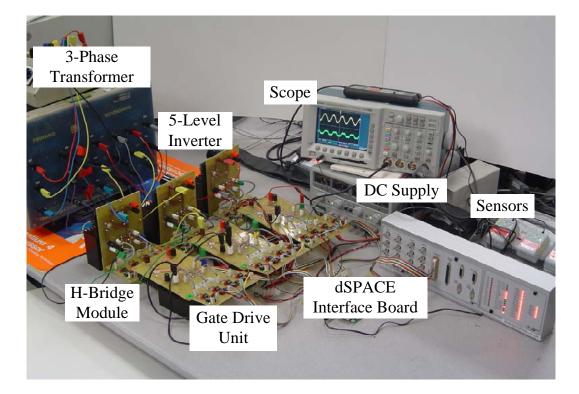

|   | 7.1 | Overv   | iew of the  | e Experimental Platform                                | 208 |

|   | 7.2 | dSPA    | CE DS110    | 04 R&D Controller board                                | 210 |

|   | 7.3 | The P   | eripheral   | Interface Circuit                                      | 211 |

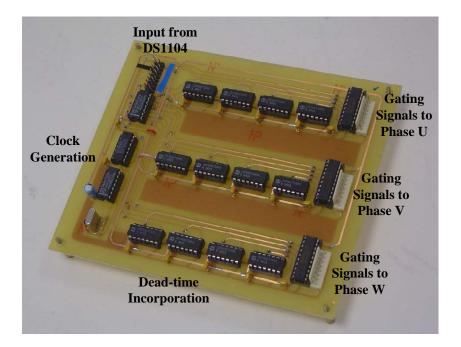

|   |     | 7.3.1   | Interfaci   | ng Board                                               | 211 |

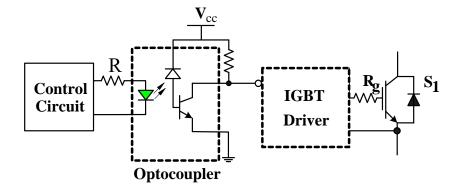

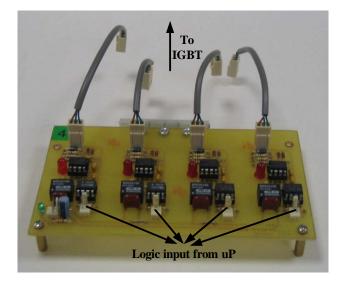

|   |     | 7.3.2   | Gate Dr     | ive Circuit                                            | 212 |

|   | 7.4 | Multil  | evel Inver  | ter Hardware                                           | 214 |

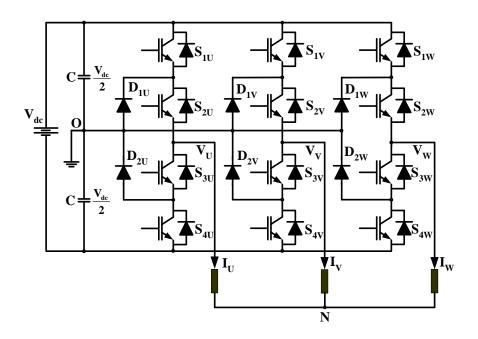

|   |     | 7.4.1   | 3-level N   | leutral Point Clamped Inverter                         | 215 |

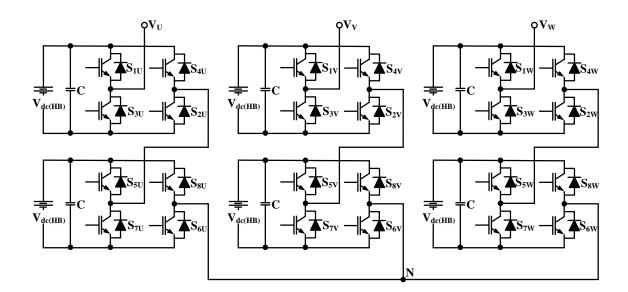

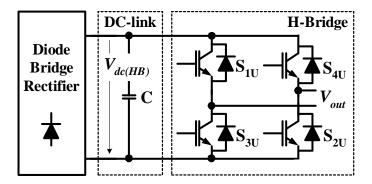

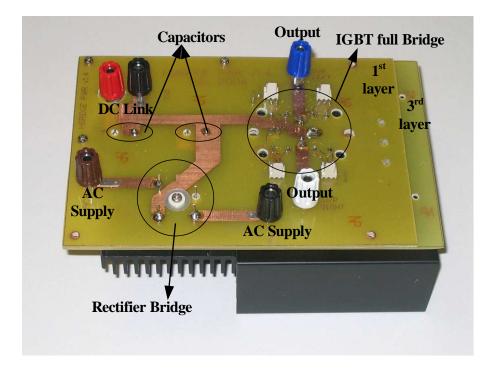

|   |     | 7.4.2   | 5-level C   | Cascaded H-Bridge Inverter                             | 215 |

| 8 | Con | clusio  | ns and F    | uture Work                                             | 218 |

х

| Bibliogr | aphy    |                                                                                                 | 225 |

|----------|---------|-------------------------------------------------------------------------------------------------|-----|

| 8        | 8.2.2   | Bidirectional Power Control                                                                     | 224 |

| 8        | 8.2.1   | Common Mode Voltage Reduction                                                                   | 223 |

| 8.2      | Future  | Work                                                                                            | 223 |

| 8.1      | Conclus | sions $\ldots$ | 218 |

## Summary

The Space vector PWM (SVPWM) is a prominent modulation technique for multilevel inverters similar to two-level inverters. However, due to complex geometry of the space vector diagram and a large number of switching states, the implementation of SVPWM for multilevel inverters is considered complex. The complexity is due to the difficulty in determining the location of reference vector, the calculation of on-times and the determination and selection of switching states.

In linear range, maximum obtainable voltage is 90.7% of six-step. It can be increased further by properly utilizing the DC link capacity through overmodulation. However, the aforementioned complexity of SVPWM implementation increases further in the overmodulation range due to the nonlinearities of this region.

To deal with these problems, a general SVPWM algorithm is proposed for multilevel inverters. The proposed algorithm is based on standard two-level SVPWM which greatly simplifies the modulation process. In the proposed algorithm, irrespective of the level n, the computations remain same. The implementation of the proposed algorithm is experimentally shown for two widely used topologies of multilevel inverter, namely neutral point clamped (NPC) and cascaded H-bridge. Similar to two-level inverter, multilevel inverters produce common mode voltage. This results in bearing currents that can lead to bearing failure. Schemes have been reported for multilevel inverters to reduce the common mode voltage. However, most of the schemes result in reduced modulation depth, high switching losses and high harmonic distortion. In this thesis, a scheme to reduce common mode voltage for cascaded inverters is proposed which is based on the proposed general SVPWM algorithm. This scheme can increase the voltage range of operation by about 17% and can produce lower THD than the previously proposed schemes.

The use of asynchronous PWM technique for the inverter produces subharmonics and interharmonics. These harmonics lead to several undesired effects on grid connected applications. This necessitates the need for synchronous PWM. The close loop control of synchronous PWM is complex especially during dynamics. The PWM for multilevel inverter is fairly complicated as compared to two-level inverter. Hence, aforementioned problem is more severe when multilevel inverter is used as a voltage source inverter. To deal with these problems a scheme is proposed for the close loop flux control of a grid connected cascaded multilevel inverter.

The 3-level NPC inverter is widely used topology. However, it is known to have neutral point fluctuation problem. At low modulation index, the fluctuations can be compensated using redundant switching states. But at higher modulation index and in overmodulation region, the neutral point fluctuation deteriorates the performance of the inverter. A simple SVPWM scheme is proposed for operating a three-level NPC inverter at higher modulation indices including overmodulation range while maintaining the neutral point balance.

# List of Tables

| 1.1 | The number of components in NPC topology                                                                                                                                                           | 6  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Switching Sequence for $\triangle_2, \triangle_3$ and $\triangle_4$ of sector 1 of 3-level Inverter                                                                                                | 61 |

| 2.2 | Steps Required for SVPWM of 3-level, 5-level and 7-level 6                                                                                                                                         | 66 |

| 2.3 | Switching States for a vertex of a $n$ -level Inverter in sector I $\ldots$ 7                                                                                                                      | 70 |

| 2.4 | Switching States Mapping Between Sector 1 and Other Sectors 7                                                                                                                                      | 70 |

| 4.1 | Switching sequence for the equilateral triangles                                                                                                                                                   | )8 |

| 4.2 | Switching sequence for the isosceles triangles                                                                                                                                                     | 10 |

| 4.3 | Possible duty-ratio orders                                                                                                                                                                         | 11 |

| 4.4 | Identified order for the complete space vector diagram 11                                                                                                                                          | 11 |

| 4.5 | Comparison of key features in Fig. 4.7 and Fig. 4.8                                                                                                                                                | 14 |

| 5.1 | Clamped phases for $60^{\circ}$ clamping technique $\ldots \ldots \ldots \ldots \ldots \ldots 15$                                                                                                  | 58 |

| 5.2 | Clamped phases for $30^{\circ}$ clamping technique $\ldots \ldots \ldots$          | 59 |

| 5.3 | Switching sequence for the triangles                                                                                                                                                               | 52 |

| 5.4 | Switching sequence for the triangles $\triangle_6$ and $\triangle_{12}$                                                                                                                            | 52 |

| 5.5 | Identified order for the $60^{\circ}$ phase clamping method $\ldots \ldots \ldots$ | 33 |

| 6.1 | Implementation | of S3V | scheme i | for th | ne first | sector | • | • |  | • | <br>188 |  |

|-----|----------------|--------|----------|--------|----------|--------|---|---|--|---|---------|--|

|     |                |        |          |        |          |        |   |   |  |   |         |  |

# List of Figures

| 1.1  | The Functional Diagram of Multilevel Inverters                                                                                                                                                                                                  | 3  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

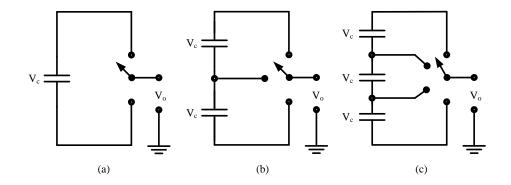

| 1.2  | Three-level Neutral Point Clamped topology                                                                                                                                                                                                      | 5  |

| 1.3  | The 5-level Cascaded H-Bridge Topology                                                                                                                                                                                                          | 7  |

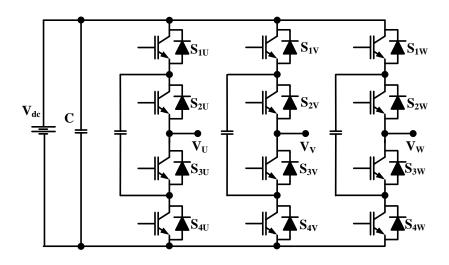

| 1.4  | The 3-level Capacitor Clamped topology                                                                                                                                                                                                          | 8  |

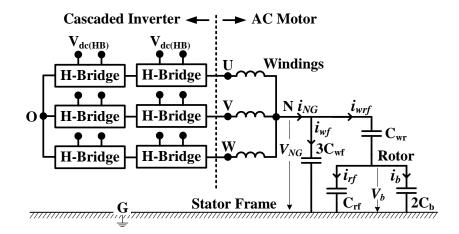

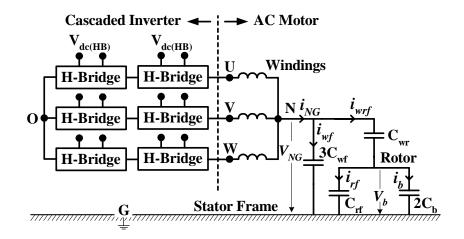

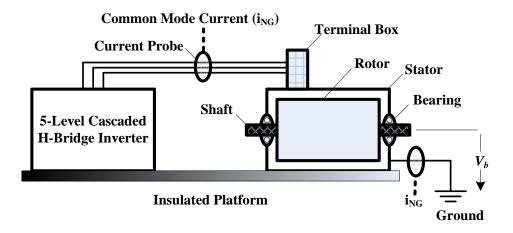

| 1.5  | Circuit layout of inverter and motor system $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                | 10 |

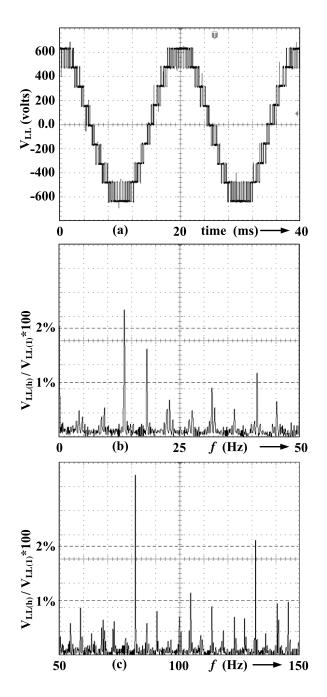

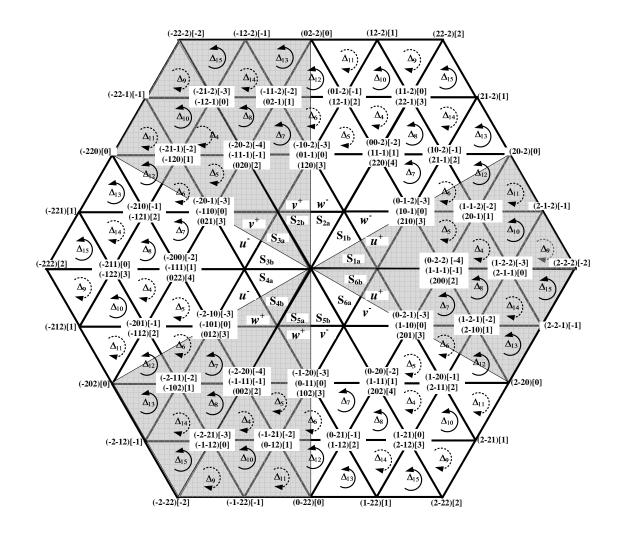

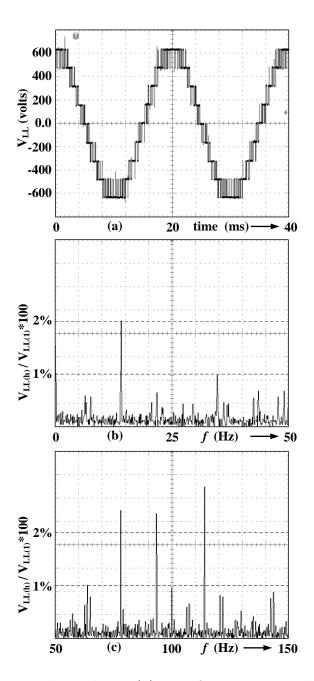

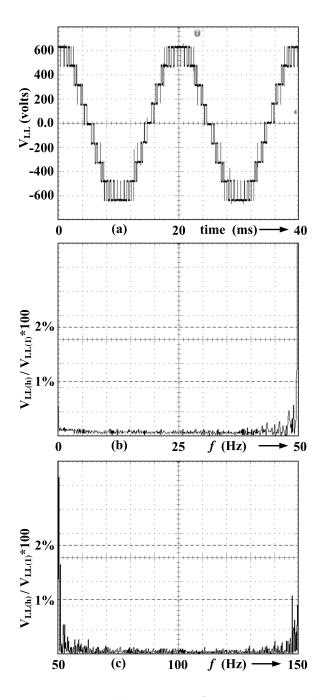

| 1.6  | Experimental Results (a) Inverter line voltage, (b) FFT for $0\rightarrow 50$ Hz to show subharmonics, (c) FFT for $50$ Hz $\rightarrow 150$ Hz to show interharmonics for conventional SVPWM at $V_{dc(HB)}=160$ V, $m_i=0.9$ , $T_s=550\mu$ s | 14 |

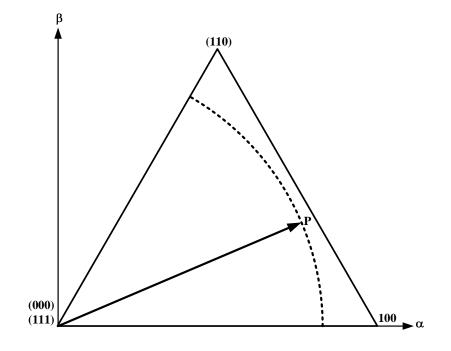

| 1.7  | The Space Vector Diagram of a two-level Inverter                                                                                                                                                                                                | 18 |

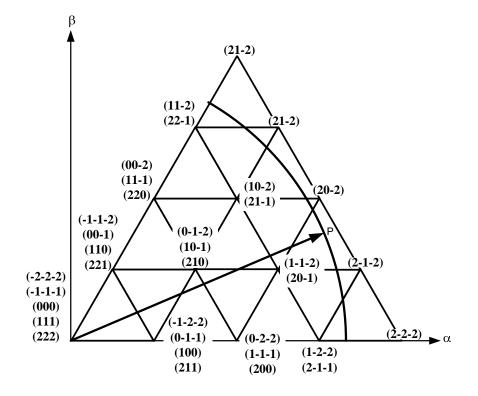

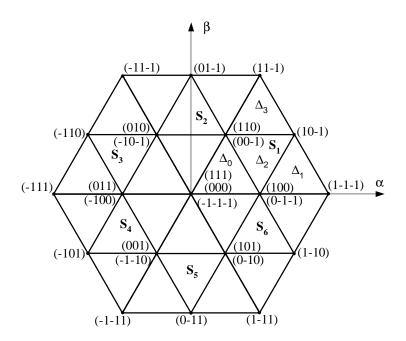

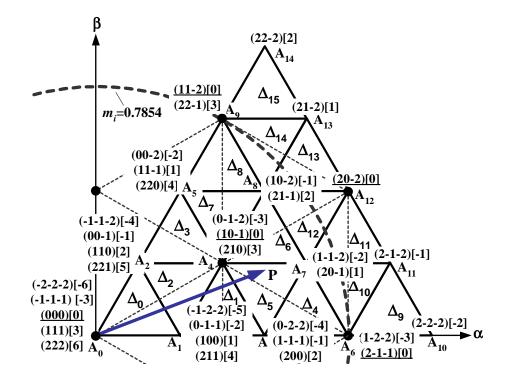

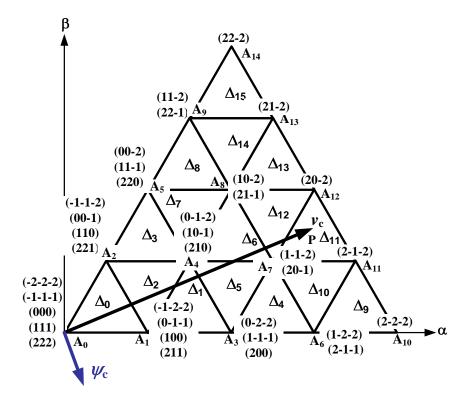

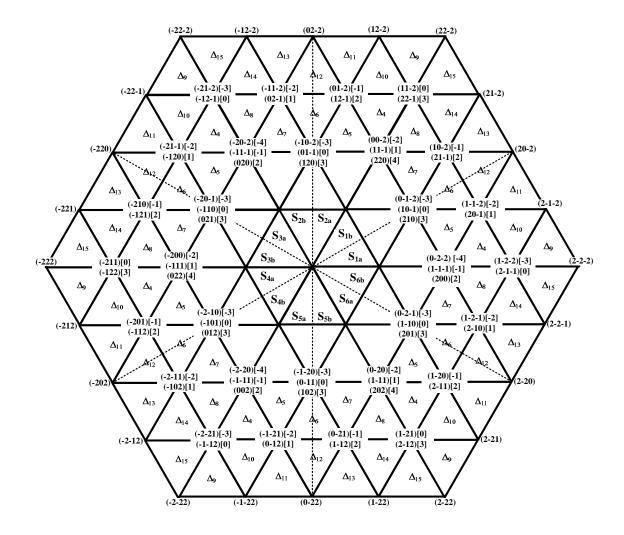

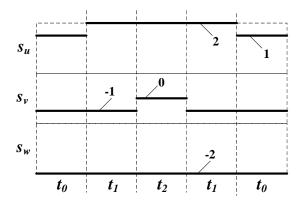

| 1.8  | The Space Vector Diagram of a 5-level Inverter                                                                                                                                                                                                  | 19 |

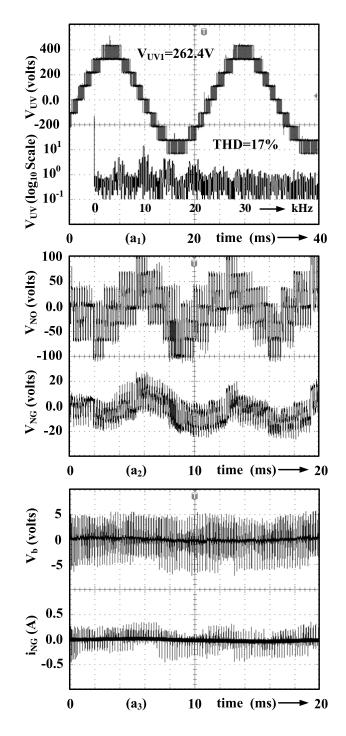

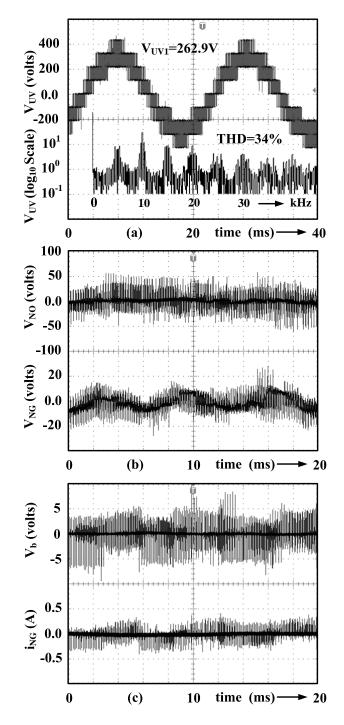

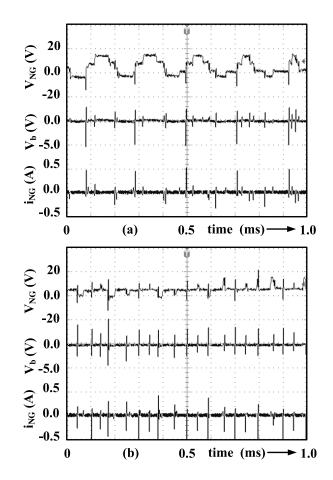

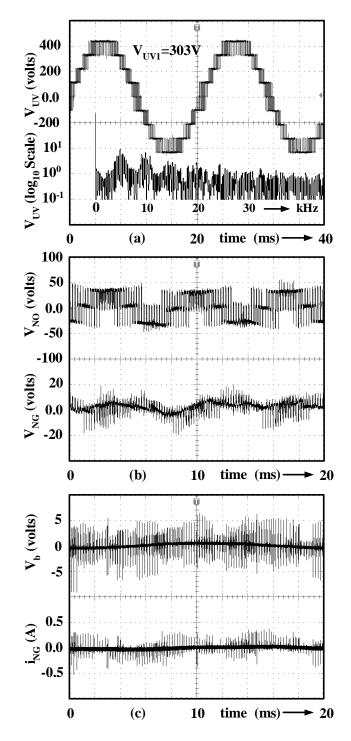

| 1.9  | Line voltage $V_{UV}$ , Semi-logarithmic FFT of line voltage $V_{UV}$ , voltage $V_{NO}$ , voltage $V_{NG}$ , voltage $V_b$ and current $i_{NG}$ at $m_i=0.78$ for conventional SVPWM scheme.                                                   | 31 |

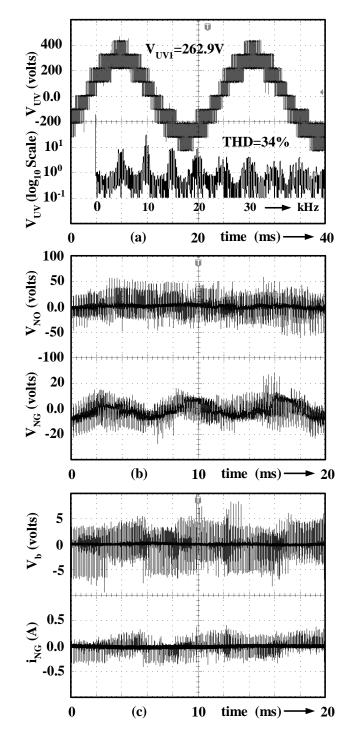

| 1.10 | Line voltage $V_{UV}$ , Semi-logarithmic FFT of line voltage $V_{UV}$ , voltage $V_{NO}$ , voltage $V_{NG}$ , voltage $V_b$ and current $i_{NG}$ at $m_i=0.78$ for zero- $V_{NO}$ scheme.                                                       | 32 |

| 1.11 | Voltage $V_{NG}$ , voltage $V_b$ and current $i_{NG}$ at $m_i=0.78$ for (a) conventional SVPWM scheme (b) zero- $V_{NO}$ scheme                                                                                                                 | 33 |

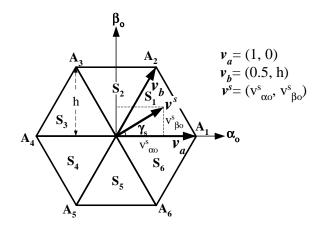

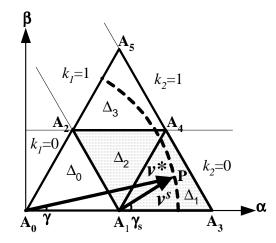

| 2.1  | Space Vector Diagram of a 3-level Inverter                                                                                                                                                                                                      | 45 |

| 2.2  | Space Vector Diagram for two-level inverter                                                                                                                                                                                                | 47 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3  | Space Vector Diagram - Virtual two-level from 3-level                                                                                                                                                                                      | 49 |

| 2.4  | Space Vector Diagram - Virtual two-level from 5-level                                                                                                                                                                                      | 51 |

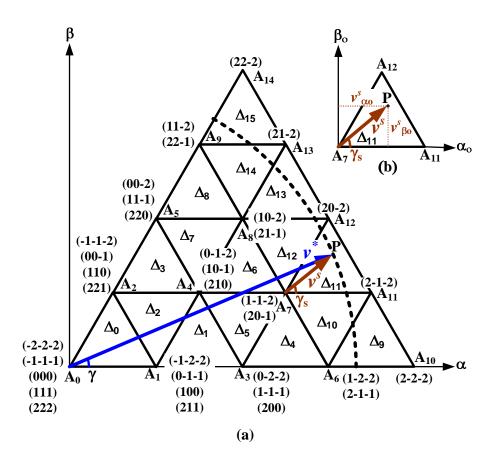

| 2.5  | Block Diagram of the Proposed Scheme                                                                                                                                                                                                       | 52 |

| 2.6  | Space Vector Diagram - Sector 1 of a 3-level Inverter                                                                                                                                                                                      | 55 |

| 2.7  | Space Vector Diagram - Sector 1 of a 5-level Inverter                                                                                                                                                                                      | 58 |

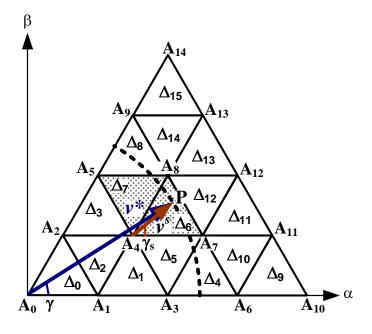

| 2.8  | Flow chart for the proposed scheme                                                                                                                                                                                                         | 60 |

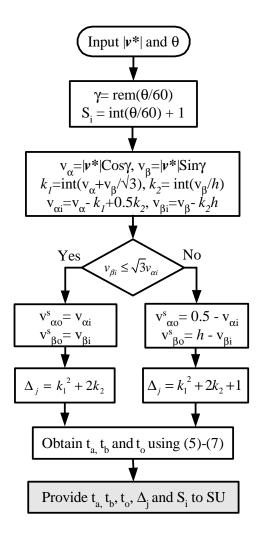

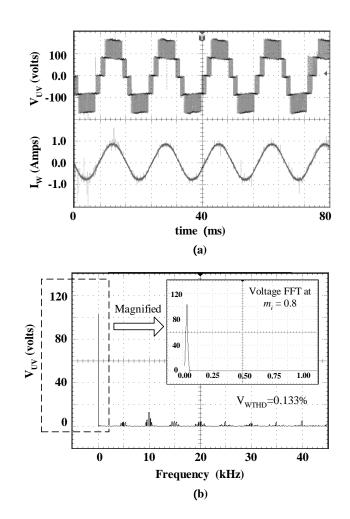

| 2.9  | Experimental results for 3-level NPC inverter (a) Line voltage and current waveforms (b) FFT of the line voltage                                                                                                                           | 62 |

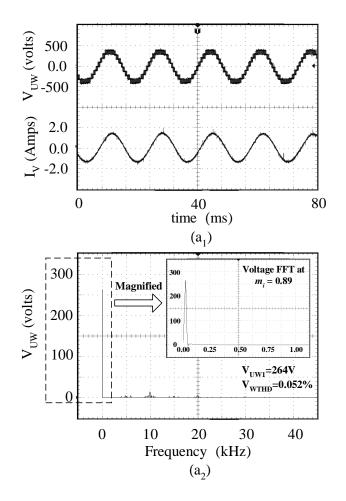

| 2.10 | Experimental results for a 5-level inverter (a1) Voltage $V_{UW}$ and current $I_V$ at $m_i=0.89$ (a2) FFT of voltage $V_{UW}$ at $m_i=0.89$                                                                                               | 64 |

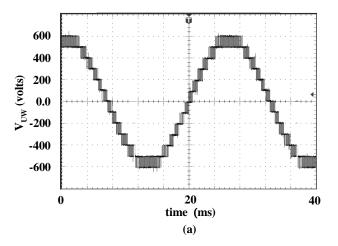

| 2.11 | Line voltage for 7-level cascaded H-bridge inverter at $m_i = 0.89$                                                                                                                                                                        | 71 |

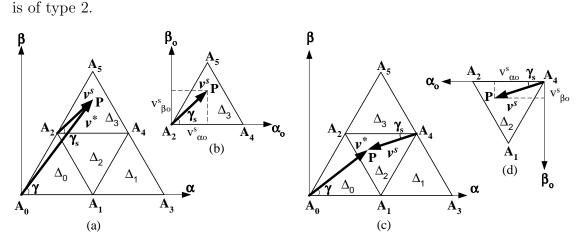

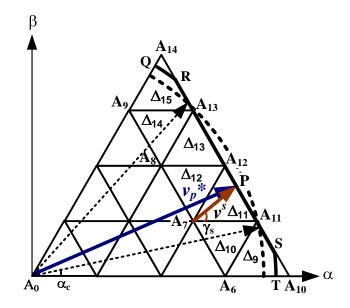

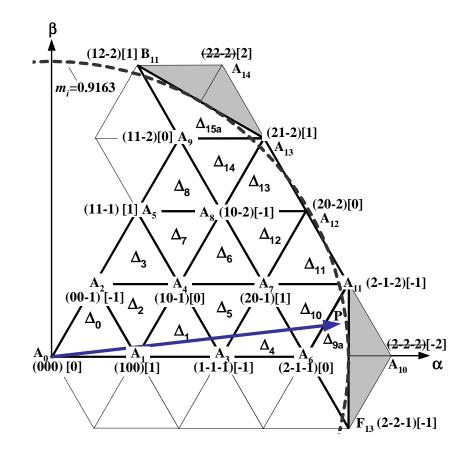

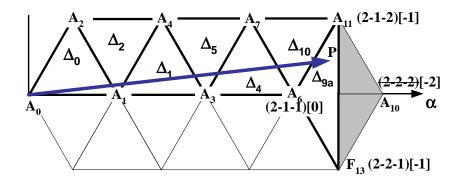

| 3.1  | Space Vector Diagram of the first sector of a 5-level inverter showing Overmodulation Mode I, $0.907 \le m_i < 0.9535$                                                                                                                     | 77 |

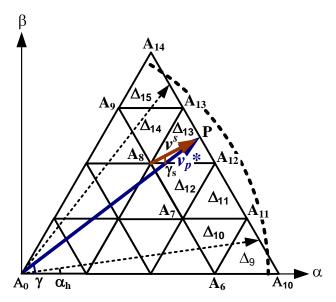

| 3.2  | Space Vector Diagram of the first sector of a 5-level inverter showing Overmodulation Mode II, $0.9535 \le m_i < 1$                                                                                                                        | 81 |

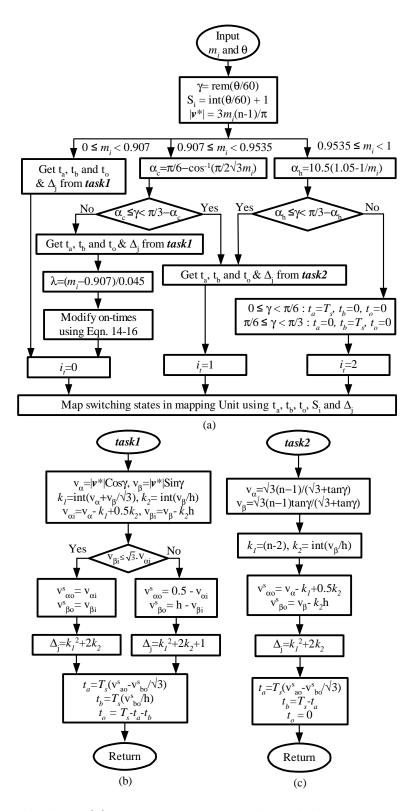

| 3.3  | Flowchart (a) Main routine: overall modulation process (b) task<br>1: Subroutine to calculate on-times and triangle number for circu-<br>lar track (c) task 2: Subroutine to calculate on-times and triangle<br>number for hexagonal track | 83 |

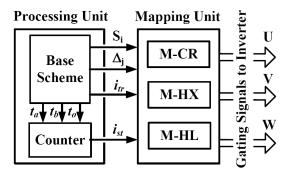

| 3.4  | Simplified block diagram of the proposed algorithm                                                                                                                                                                                         | 85 |

| 3.5  | Switching state at a memory location - $ON/OFF$ signals for switches                                                                                                                                                                       | 86 |

| 3.6  | Memory address for circular track                                                                                                                                                                                                          | 89 |

| 3.7  | Memory address for hexagonal track                                                                                                                                                                                                         | 90 |

| 3.8  | Memory address for hold mode                                                                                                                                                                                                               | 91 |

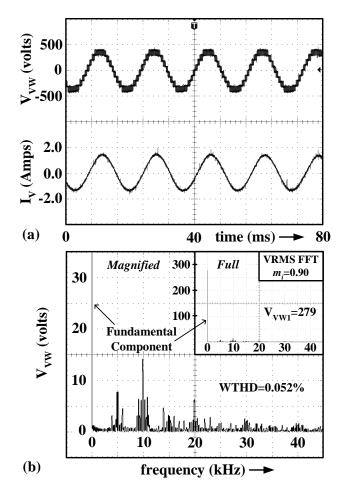

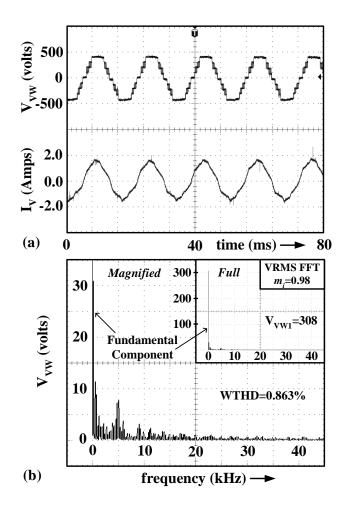

| 3.9 Voltage $V_{VW}$ , current $I_V$ and FFT of voltage $V_{VW}$ at $m_i=0.90$ 92                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

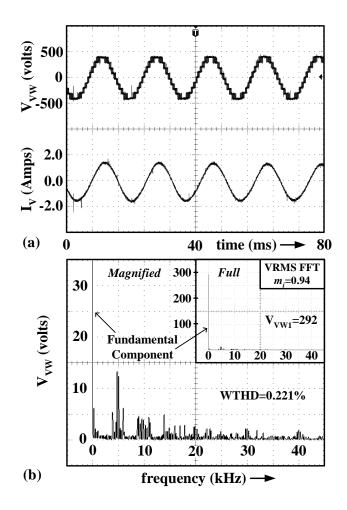

| 3.10 Voltage $V_{VW}$ , current $I_V$ and FFT of voltage $V_{VW}$ at $m_i=0.94$ 93                                                                                                                                                                                                                                                           |

| 3.11 Voltage $V_{VW}$ , current $I_V$ and FFT of voltage $V_{VW}$ at $m_i=0.98$ 94                                                                                                                                                                                                                                                           |

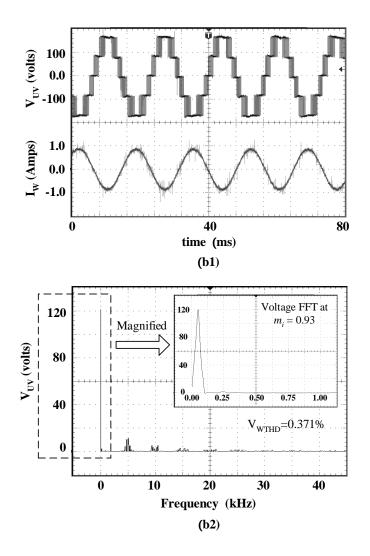

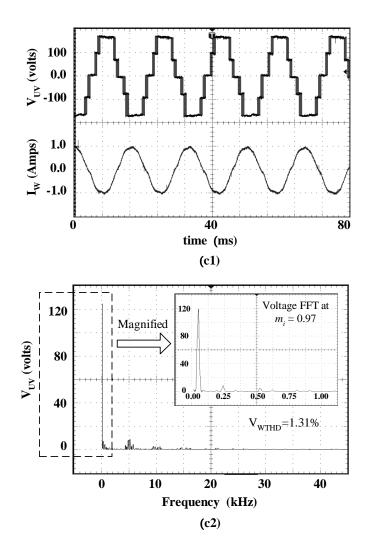

| 3.12 Voltage $V_{VW}$ , current $I_V$ and FFT of voltage $V_{VW}$ at $m_i=0.93$ 96                                                                                                                                                                                                                                                           |

| 3.13 Voltage $V_{VW}$ , current $I_V$ and FFT of voltage $V_{VW}$ at $m_i=0.97$ 97                                                                                                                                                                                                                                                           |

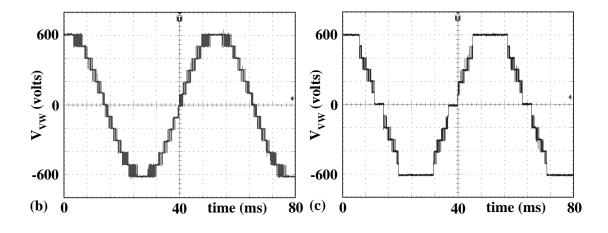

| 3.14 Line voltage for 7-level inverter at (b) $m_i=0.93$ (c) $m_i=0.97$ 98                                                                                                                                                                                                                                                                   |

| 4.1 Circuit layout of inverter and motor system                                                                                                                                                                                                                                                                                              |

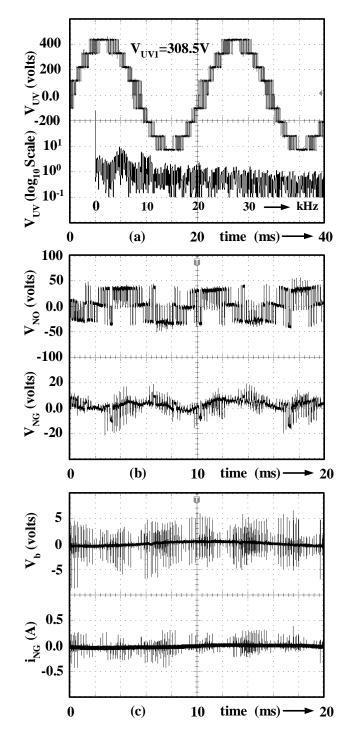

| 4.2 First sector of a 5-level inverter showing all the switching states $\therefore$ 104                                                                                                                                                                                                                                                     |

| 4.3 First sector of 5-level inverter showing selected switching states $\therefore$ 106                                                                                                                                                                                                                                                      |

| 4.4 Part of the first sector to emphasize operation in triangle $\triangle_{9a}$ 109                                                                                                                                                                                                                                                         |

| 4.5 Memory address to access a memory location (switching state) 112                                                                                                                                                                                                                                                                         |

| 4.6 Common Mode Current $(i_{NG})$ Measurement $\ldots \ldots \ldots$                                                                                                                                                        |

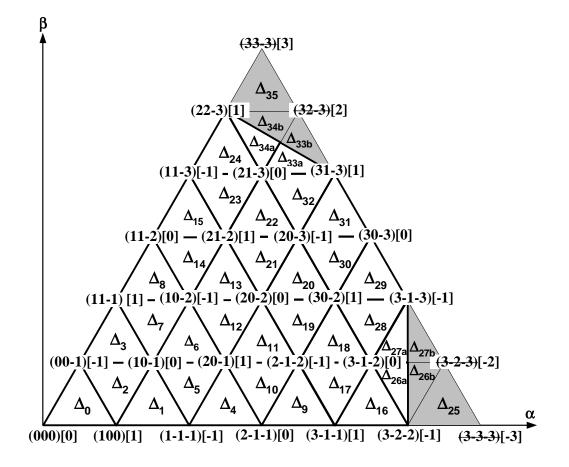

| 4.7 (a) Line voltage $V_{UV}$ , Semi-logarithmic FFT of line voltage $V_{UV}$ ,<br>(b) voltage $V_{NO}$ , voltage $V_{NG}$ , voltage (c) $V_b$ and current $i_{NG}$ at $m_i=0.78$ for zero- $V_{NO}$ scheme                                                                                                                                  |

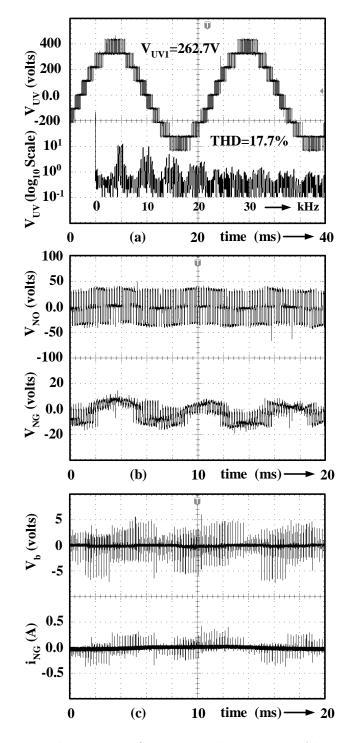

| 4.8 (a) Line voltage $V_{UV}$ , Semi-logarithmic FFT of line voltage $V_{UV}$ ,<br>(b) voltage $V_{NO}$ , voltage $V_{NG}$ , voltage (c) $V_b$ and current $i_{NG}$ at $m_i=0.78$ for proposed scheme $\ldots \ldots \ldots$ |

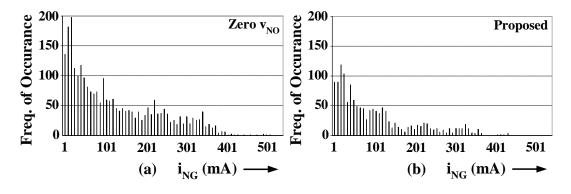

| 4.9 Frequency of occurrence versus current $i_{NG}$ (a) Zero $V_{NO}$ Method<br>(b) Proposed Method at $m_i=0.78$                                                                                                                                                                                                                            |

| 4.10 (a) Line voltage $V_{UV}$ , Semi-logarithmic FFT of line voltage $V_{UV}$ ,<br>(b) voltage $V_{NO}$ , voltage $V_{NG}$ , (c) voltage $V_b$ and current $i_{NG}$ at $m_i=0.9$ for proposed scheme                                                                                                                                        |

| 4.11 (a) Line voltage $V_{UV}$ , Semi-logarithmic FFT of line voltage $V_{UV}$ ,<br>(b) voltage $V_{NO}$ , voltage $V_{NG}$ , (c) voltage $V_b$ and current $i_{NG}$ at $m_i=0.915$ for proposed scheme                                                                                                                                      |

| 4.12 Space vector diagram of 7-level inverter with selected states $\ldots$ 122                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13 Line voltage and $\mathcal{V}_{NO}$ for 7-level cascaded inverter at $m_i{=}0.78$ 124                                                                                                                     |

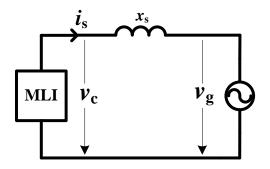

| 5.1 Multilevel inverter (MLI) and grid connection                                                                                                                                                              |

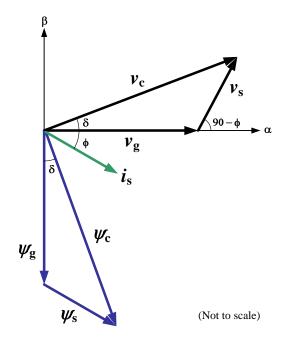

| 5.2 The phasor diagram for grid connected multilevel inverter in Fig. 5.1 131                                                                                                                                  |

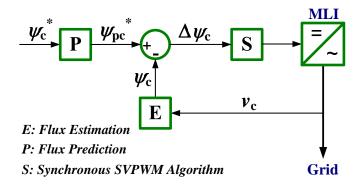

| 5.3 The block diagram for predictive flux vector based close loop scheme 133                                                                                                                                   |

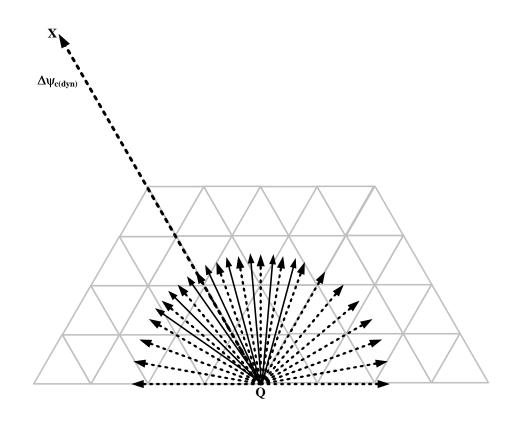

| 5.4 The first sector of the space vector diagram                                                                                                                                                               |

| 5.5 Sampling instants for non-predictive flux scheme at $\tau_s{=}555.55\mu\mathrm{s}$ 137                                                                                                                     |

| 5.6 Sampling instants for predictive flux scheme at $\tau_s = 555.55 \mu s$ 138                                                                                                                                |

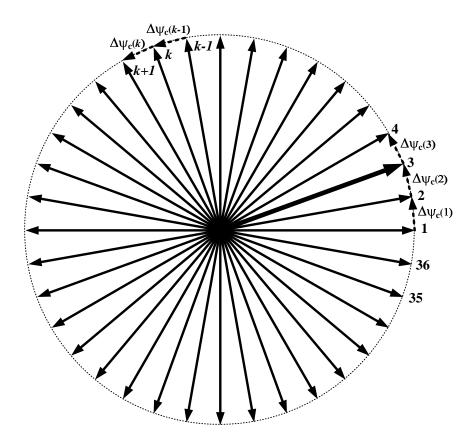

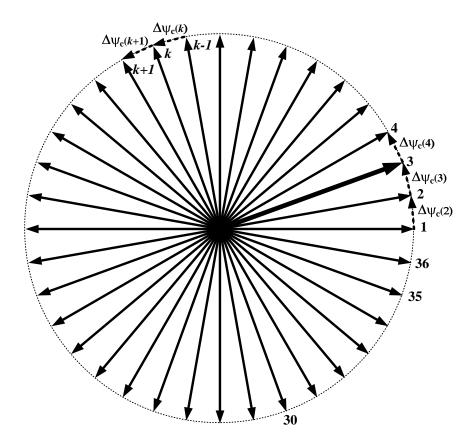

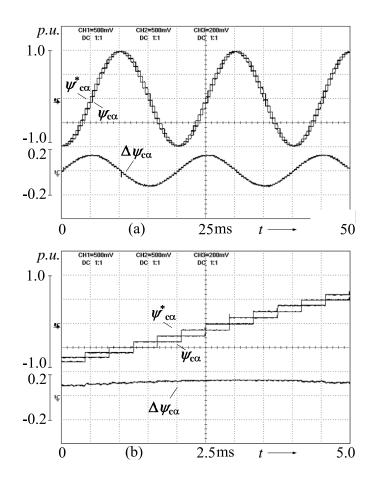

| 5.7 The $\alpha$ component of predicted converter flux $\psi_{c\alpha}^*$ , actual converter flux $\psi_{c\alpha}$ and flux error $\Delta \psi_{c\alpha}$ at $\psi_c = 1.0  p.u$ . and $\delta = 45^\circ$ 139 |

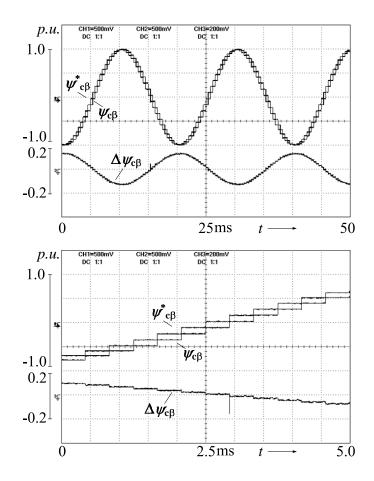

| 5.8 The $\beta$ component of predicted converter flux, actual converter flux<br>and their difference at $v_c=1.0$ p.u. and $\delta=45^{\circ}$                                                                 |

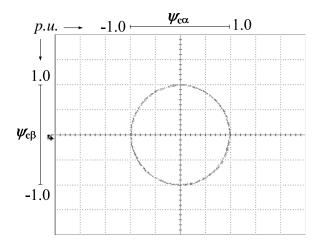

| 5.9 The $\psi_{c\alpha}$ vs. $\psi_{c\beta}$ at $v_c=1.0$ p.u. and $\delta=45^o$                                                                                                                               |

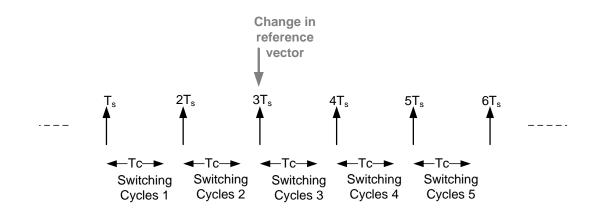

| 5.10 Change in reference vector at one of the sampling instant 142                                                                                                                                             |

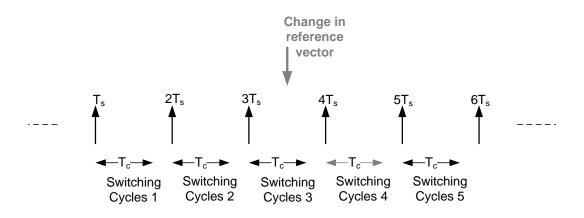

| 5.11 Change in reference vector in between two sampling instants $\ldots$ 142                                                                                                                                  |

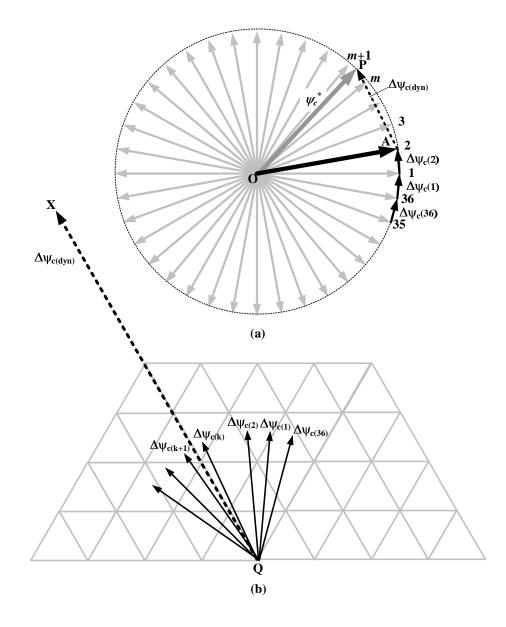

| 5.12 Dynamics for the proposed scheme at $\tau_s = 555.55 \mu s$                                                                                                                                               |

| 5.13 New discrete instants for the proposed scheme at $\tau_s = 555.55 \mu s$ 146                                                                                                                              |

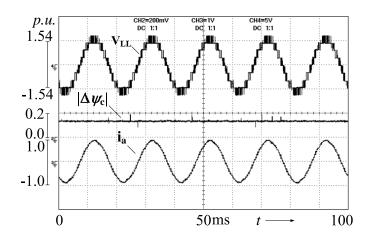

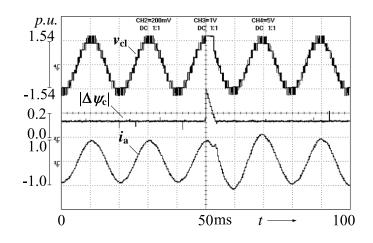

| 5.14 Output voltage, $\Delta \psi_c$ and $i_a$ for $v_c=1.0$ p.u. and $\delta=45^o$                                                                                                                            |

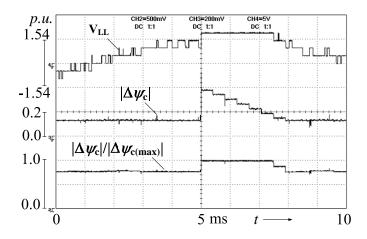

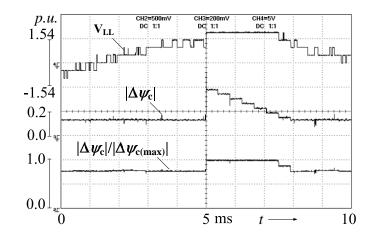

| 5.15 Inverter line voltage $\boldsymbol{v_{cl}}$ , $ \Delta\psi_c $ and $ \Delta\psi_c / \Delta\psi_{c(max)} $ at $\psi_c=1.0$ p.u.<br>and $\delta=45^{\circ}\rightarrow 59.5^{\circ}$                         |

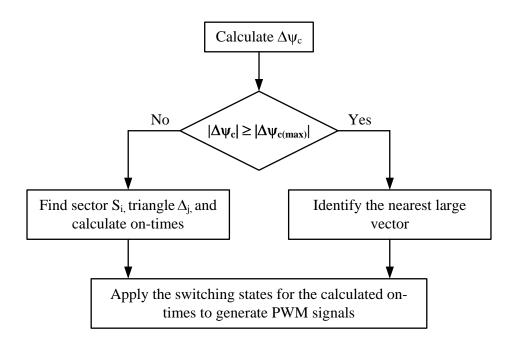

| 5.16 Simplified flowchart of the scheme                                                                                                                                                                        |

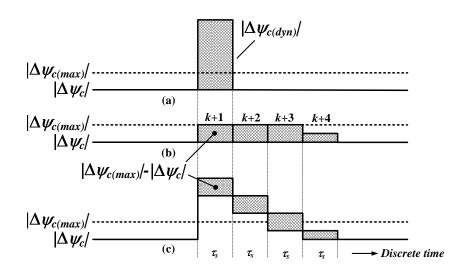

| 5.17 Fast flux error compensation in dynamic condition 152                                                                                                                                                     |

| 5.18 The $\alpha$ and $\beta$ component of predicted converter flux, actual converter flux and their difference at $v_c=1.0$ p.u. and $\delta=45^{\circ}\rightarrow 59.5^{\circ}$ 154                          |

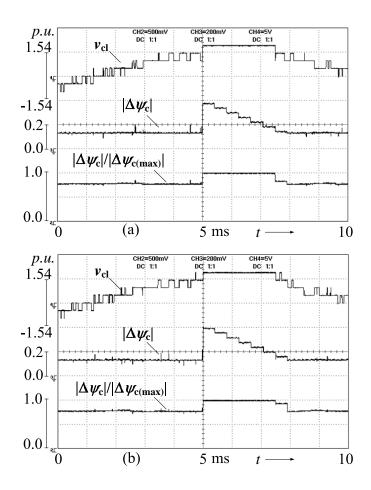

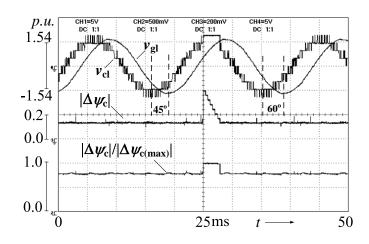

| 5.19 | Inverter line voltage $\boldsymbol{v_{cl}}$ , $ \Delta\psi_c $ and $ \Delta\psi_c / \Delta\psi_{c(max)} $ at $\psi_c=1.0$ p.u. and $\delta=45^{\circ}\rightarrow 59.5^{\circ}$                                                                                   | 154 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.20 | Inverter line voltage $\boldsymbol{v_{cl}}$ , $ \Delta\psi_c $ and $ \Delta\psi_c / \Delta\psi_{c(max)} $ at $\psi_c=1.0$ p.u. for the change (a) $\delta=45^{\circ}\rightarrow59^{\circ}$ , (b) $\delta=45^{\circ}\rightarrow60^{\circ}$                        | 155 |

| 5.21 | Space Vector Diagram for 5-level Inverter - Conventional                                                                                                                                                                                                         | 158 |

| 5.22 | The transitions in $\triangle_{11}$ for 60° clamping technique                                                                                                                                                                                                   | 159 |

| 5.23 | The transitions in $\triangle_{11}$ for 30° clamping technique                                                                                                                                                                                                   | 159 |

| 5.24 | Space Vector Diagram - Emphasizing $60^o$ clamping technique                                                                                                                                                                                                     | 160 |

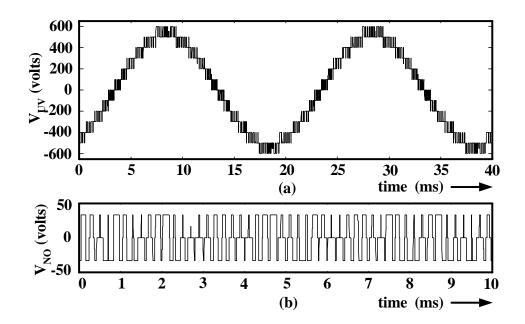

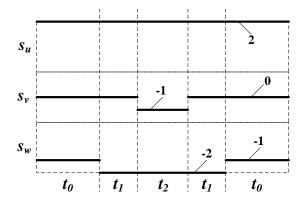

| 5.25 | (a) Inverter line voltage, (b) FFT for $0 \rightarrow 50$ Hz to show subharmonics,<br>(c) FFT for 50Hz $\rightarrow$ 150Hz to show interharmonics for conventional<br>SVPWM at $V_{dc(HB)}$ =160V, $m_i$ =0.9, $\tau_s$ =550 $\mu$ s                             | 165 |

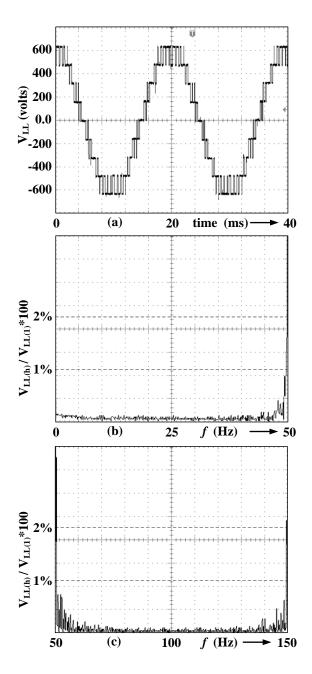

| 5.26 | (a) Inverter line voltage, (b) FFT for $0 \rightarrow 50$ Hz to show subharmonics,<br>(c) FFT for $50$ Hz $\rightarrow 150$ Hz to show interharmonics for conventional<br>SVPWM at $V_{dc(HB)}=160$ V, $m_i=0.9$ , $\tau_s=560\mu$ s                             | 166 |

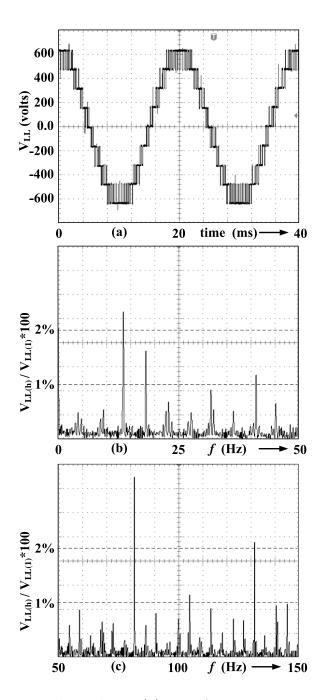

| 5.27 | (a) Inverter line voltage, (b) FFT for $0 \rightarrow 50$ Hz to show subharmonics,<br>(c) FFT for 50Hz $\rightarrow$ 150Hz to show interharmonics for proposed $60^{\circ}$ clamped SVM at $V_{dc}$ =160V, $m_i$ =0.9, $\tau_s$ =555.55 $\mu$ s                  | 167 |

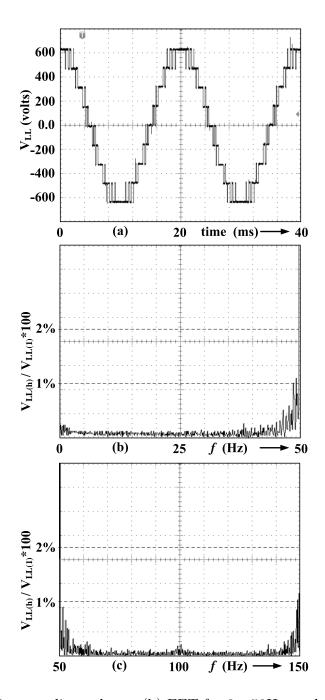

| 5.28 | (a) Inverter line voltage, (b) FFT for $0 \rightarrow 50$ Hz to show subharmonics, (c) FFT for 50Hz $\rightarrow$ 150Hz to show interharmonics for proposed 60° clamped SVM at V <sub>dc</sub> =160V, m <sub>i</sub> =0.93, $\tau_s$ =555.55 $\mu$ s             | 168 |

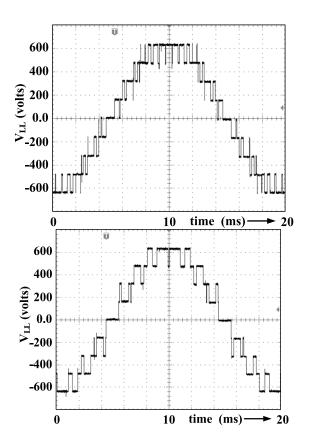

| 5.29 | Converter output voltage showing symmetry at $V_{dc}=160V$ , $m_i=0.9$ for $f_s=1.8kHz$ and $f_s=0.9kHz$                                                                                                                                                         | 169 |

| 5.30 | Converter output voltage, FFT for $0 \rightarrow 50$ Hz to show subharmonics<br>and FFT for $50$ Hz $\rightarrow 150$ Hz to show interharmonics for proposed $30^{\circ}$<br>clamped SVM at V <sub>dc</sub> =160V, m <sub>i</sub> =0.9, $\tau_s$ =555.55 $\mu$ s | 170 |

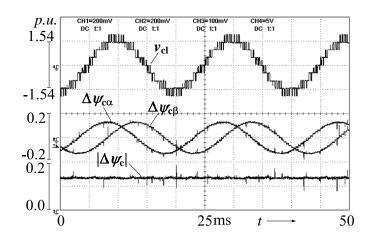

| 5.31 | Output voltage, $\Delta \psi_{c\alpha}$ , $\Delta \psi_{c\beta}$ and $ \Delta \psi_c $ at $v_c$ =1.0 p.u. and $\delta$ =45°.                                                                                                                                     | 171 |

| 5.32 | Output voltage, $\Delta \psi_c$ and $i_a$ for $v_c=1.0$ p.u. and $\delta=45^o$                                                                                                                                                                                   | 171 |

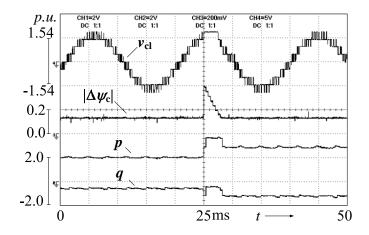

| 5.33 | Inverter line voltage $\boldsymbol{v_{cl}}$ , grid voltage $\boldsymbol{v_{gl}}$ , $ \Delta\psi_c $ and $ \Delta\psi_c / \Delta\psi_{c(max)} $ for $\delta=45^{\circ}\rightarrow60^{\circ}$ at $\psi_c=1.0$                                                      | 172 |

| 5.34 | Inverter line voltage $\boldsymbol{v_{cl}},  \Delta \psi_c , p \text{ and } q \text{ for } \delta = 45^o \rightarrow 60^o \text{ at } \psi_c = 1.0$ .                                                                                                                                                                                                                               | 172 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.35 | Inverter line voltage $\boldsymbol{v_{cl}}$ , $ \Delta \psi_c $ , $i_a$ for $\delta = 45^o \rightarrow 60^o$ at $\psi_c = 1.0$                                                                                                                                                                                                                                                      | 173 |

| 6.1  | Neutral Point Clamped 3-level Inverter                                                                                                                                                                                                                                                                                                                                              | 179 |

| 6.2  | Space Vector Diagram of a 3-level Inverter                                                                                                                                                                                                                                                                                                                                          | 180 |

| 6.3  | Variation of $d_M$ , $d_{S1}$ and $d_{S2}$ with angle at (a) $m_i = 0.6$ (b) $m_i = 0.8$ (c) $m_i = 0.92$ (d) $m_i = 0.9535$ (e) $m_i = 0.98$                                                                                                                                                                                                                                       | 181 |

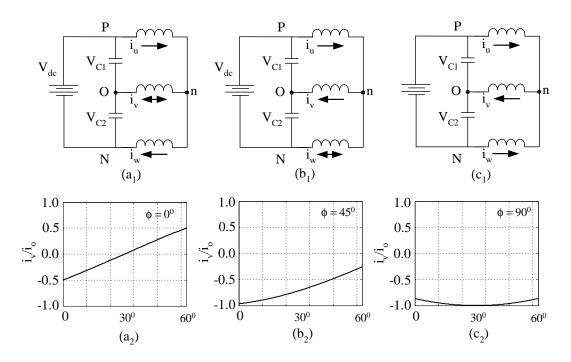

| 6.4  | The analysis of the effect of medium vector $(1,0,-1)$ $(a_1)(b_1)(c_1)$ Actual circuit connections and current directions at $\phi=0^o$ , 45° and 90° respectively $(a_2)(b_2)(c_2)$ Neutral point current at $\phi=0^o$ , 45° and 90° respectively $\ldots$                                                                                                                       | 182 |

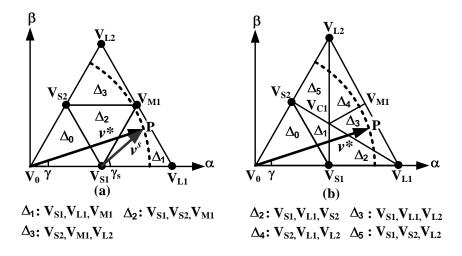

| 6.5  | Space Vector Diagram of the first sector of a 3-level inverter to show linear mode for (a) N3V Scheme (b) S3V Scheme                                                                                                                                                                                                                                                                | 186 |

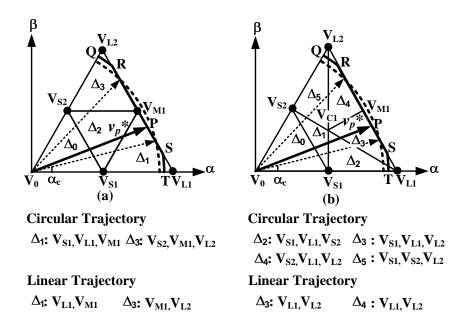

| 6.6  | Space Vector Diagram of the first sector of a 3-level inverter to show overmodulation mode-I for (a) N3V + N2V Scheme (b) S3V+S2V Scheme                                                                                                                                                                                                                                            | 191 |

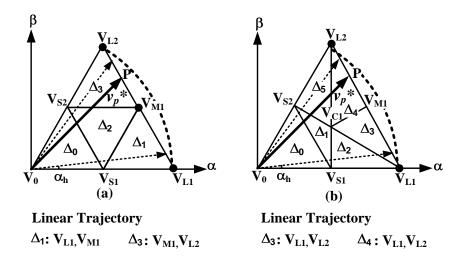

| 6.7  | Space Vector Diagram of the first sector of a 3-level inverter to show<br>overmodulation mode-II for (a) N2V Scheme + Discrete Movement<br>(b) S2V Scheme + Discrete Movement                                                                                                                                                                                                       | 195 |

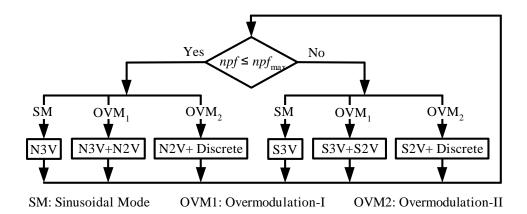

| 6.8  | Flowchart of the balancing scheme                                                                                                                                                                                                                                                                                                                                                   | 197 |

| 6.9  | Block diagram of the balancing scheme                                                                                                                                                                                                                                                                                                                                               | 197 |

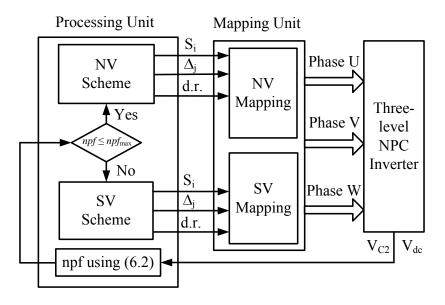

| 6.10 | Modulation index $m_i$ versus percentage $V_{WTHD}$                                                                                                                                                                                                                                                                                                                                 | 199 |

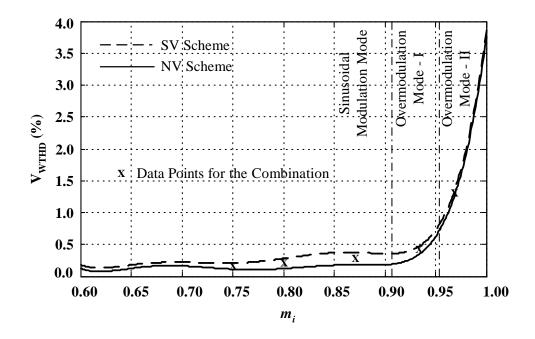

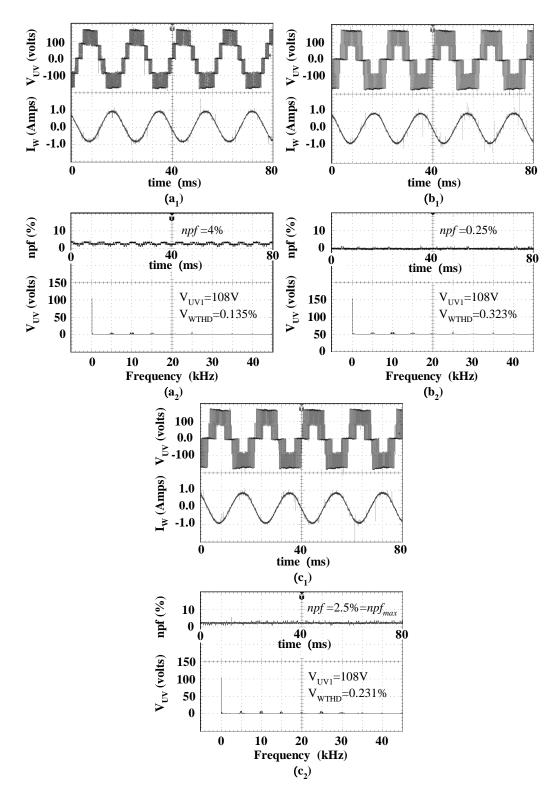

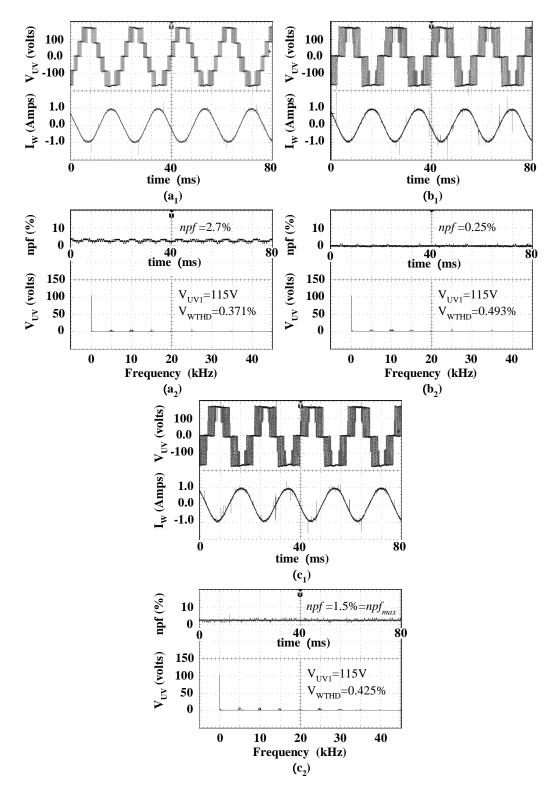

| 6.11 | At $m_i=0.87$ (a <sub>1</sub> ) V <sub>UV</sub> and I <sub>W</sub> for NV scheme (a <sub>2</sub> ) $npf$ and FFT for<br>NV scheme (b <sub>1</sub> ) V <sub>UV</sub> and I <sub>W</sub> for SV scheme (b <sub>2</sub> ) $npf$ and FFT for<br>SV scheme (c <sub>1</sub> ) V <sub>UV</sub> and I <sub>W</sub> for NV + SV scheme (c <sub>2</sub> ) $npf$ and FFT<br>for NV + SV scheme | 200 |

| 6.12 | At $m_i=0.93$ (a <sub>1</sub> ) V <sub>UV</sub> and I <sub>W</sub> for NV scheme (a <sub>2</sub> ) $npf$ and FFT for<br>NV scheme (b <sub>1</sub> ) V <sub>UV</sub> and I <sub>W</sub> for SV scheme (b <sub>2</sub> ) $npf$ and FFT for<br>SV scheme (c <sub>1</sub> ) V <sub>UV</sub> and I <sub>W</sub> for NV + SV scheme (c <sub>2</sub> ) $npf$ and FFT<br>for NV + SV scheme | 201 |

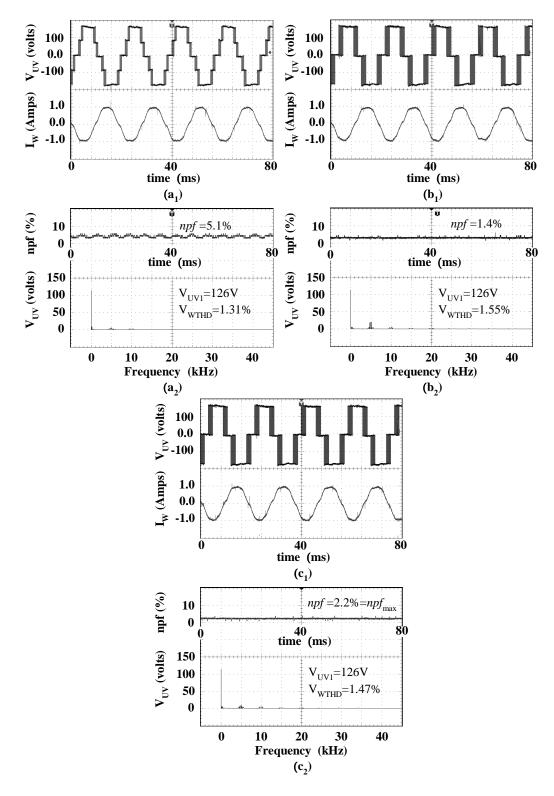

| 6.13 | At $m_i=0.97$ (a <sub>1</sub> ) $V_{UV}$ and $I_W$ for NV scheme (a <sub>2</sub> ) $npf$ and FFT for<br>NV scheme (b <sub>1</sub> ) $V_{UV}$ and $I_W$ for SV scheme (b <sub>2</sub> ) $npf$ and FFT for<br>SV scheme (c <sub>1</sub> ) $V_{UV}$ and $I_W$ for NV + SV scheme (c <sub>2</sub> ) $npf$ and FFT<br>for NV + SV scheme | 202 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

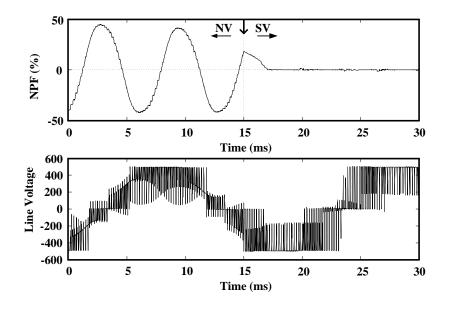

| 6.14 | At $m_i=0.9$ transition from NV $\rightarrow$ SV scheme at t=15ms                                                                                                                                                                                                                                                                   | 203 |

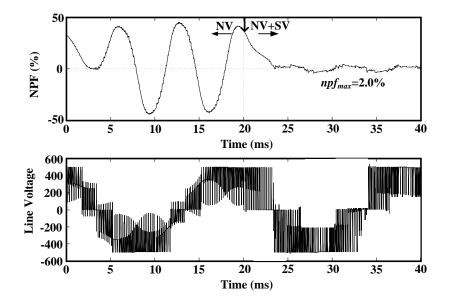

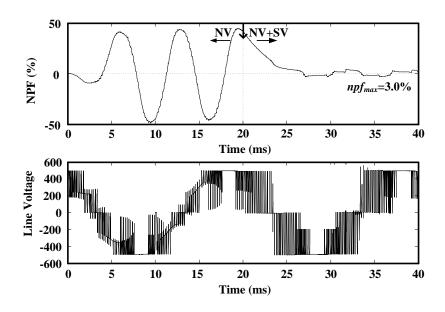

| 6.15 | At $m_i=0.9$ transition from NV $\rightarrow$ NV+SV scheme at t=20ms                                                                                                                                                                                                                                                                | 204 |

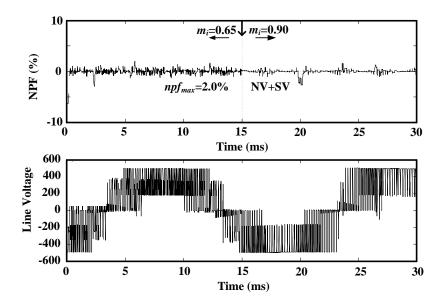

| 6.16 | NV+SV scheme at $npf_{max}$ =1% for $m_i$ =0.65 $\rightarrow$ m_i=0.90 t=15ms                                                                                                                                                                                                                                                       | 204 |

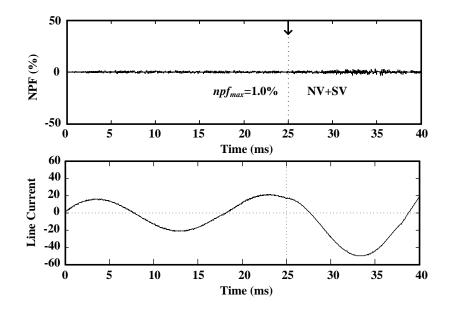

| 6.17 | NV+SV scheme at $npf_{max}$ =1% for 150% increase in load at t=25ms                                                                                                                                                                                                                                                                 | 205 |

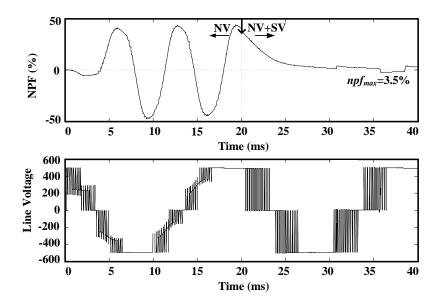

| 6.18 | At $m_i=0.94$ transition from NV $\rightarrow$ NV+SV scheme at t=20ms                                                                                                                                                                                                                                                               | 205 |

| 6.19 | At $m_i=0.96$ transition from NV $\rightarrow$ NV+SV scheme at t=20ms                                                                                                                                                                                                                                                               | 206 |

| 7.1  | Platform used for hardware implementation                                                                                                                                                                                                                                                                                           | 209 |

| 7.2  | Interfacing the controller board with inverter                                                                                                                                                                                                                                                                                      | 210 |

| 7.3  | Interface board - between DS1104 board and gate drive circuit                                                                                                                                                                                                                                                                       | 212 |