# Thermal Processing in Lithography: Equipment Design, Control and Metrology

Wang Yuheng (M.Eng.,BIT)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE 2008

## Acknowledgments

I would like to express my deepest gratitude and appreciation to my research advisor, Professor Arthur Tay, for his consistent support and supervision in every detail of my research and education at National University of Singapore. I have benefited tremendously from many discussions I had with him, without whose help this thesis would have been impossible. I would also like to express my sincere appreciation to Professor Hui Tong Chua and Professor Tuck Wah Ng for their insightful guidance and advices to this work. Their consistent support and instruction in the heat transfer analysis and optical system analysis respectively make this project enjoyable and successful. I am also extremely thankful to Professor Abdullah Al Mamun for his help and nice direction in both my research and study in National University of Singapore.

I would like to thank my friends and colleagues: Dr Zhao Shao, Dr Fu Jun, Dr Wang Xiaolin, Wu Xiaodong, Hu Ni, Kiew Choonmeng, Chen Ming, Shao Lichun, Lim Li Hong, Yan Han, Feng Yong, Teh Siew Hong, Ngo Yit Sung, and many others working in the Advanced Control Technology (ACT) Lab. Their friendship, advice and encouragement make my experience at ACT lab unforgettable in my life.

Special thanks to my parents, brother and brother's wife for their love and support. Their care always gives me the warmest support to my life and work, wherever I am.

Finally and most importantly, I would like to express my gratitude and love to my husband, Luo Zhenzhong, for his companion and love. I would have never reached so far without his constant encouragement and support.

## Contents

| A  | ckno  | wledgements                                      | i   |

|----|-------|--------------------------------------------------|-----|

| Su | ımm   | ary                                              | vii |

| Li | st of | Tables                                           | x   |

| Li | st of | Figures x                                        | vii |

| 1  | Intr  | roduction                                        | 1   |

|    | 1.1   | Motivation                                       | 1   |

|    | 1.2   | Contributions                                    | 10  |

|    | 1.3   | Organization                                     | 14  |

| 2  | In-s  | situ Real-time Spatial Wafer Temperature Control | 16  |

|    | 2.1   | Introduction                                     | 16  |

|   | 2.2                      | Thermal Modeling of the System                                                                                                                                                            | 19                                                                                 |

|---|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|   |                          | 2.2.1 Wafer and Air Gap Modeling                                                                                                                                                          | 22                                                                                 |

|   |                          | 2.2.2 Bake-Plate Modeling                                                                                                                                                                 | 24                                                                                 |

|   |                          | 2.2.3 Cartridge and Heater Modeling                                                                                                                                                       | 26                                                                                 |

|   | 2.3                      | Experimental Result                                                                                                                                                                       | 31                                                                                 |

|   |                          | 2.3.1 Experimental Setup                                                                                                                                                                  | 31                                                                                 |

|   |                          | 2.3.2 Control Structure                                                                                                                                                                   | 33                                                                                 |

|   |                          | 2.3.3 Experimental Result                                                                                                                                                                 | 34                                                                                 |

|   |                          |                                                                                                                                                                                           |                                                                                    |

|   | 2.4                      | Conclusion                                                                                                                                                                                | 41                                                                                 |

| 3 |                          |                                                                                                                                                                                           | 41<br><b>43</b>                                                                    |

| 3 |                          |                                                                                                                                                                                           | 43                                                                                 |

| 3 | <b>Pro</b><br>3.1        | grammable Integrated Bake/Chill System                                                                                                                                                    | <b>43</b><br>43                                                                    |

| 3 | <b>Pro</b><br>3.1        | grammable Integrated Bake/Chill System                                                                                                                                                    | <b>43</b><br>43<br>45                                                              |

| 3 | <b>Pro</b><br>3.1<br>3.2 | grammable Integrated Bake/Chill System Introduction                                                                                                                                       | <b>43</b><br>43<br>45<br>47                                                        |

| 3 | <b>Pro</b><br>3.1<br>3.2 | grammable Integrated Bake/Chill System         Introduction         Proposed Thermal Processing Model         Thermal Modeling of the System                                              | <b>43</b><br>43<br>45<br>47<br>48                                                  |

| 3 | <b>Pro</b><br>3.1<br>3.2 | grammable Integrated Bake/Chill System         Introduction         Proposed Thermal Processing Model         Thermal Modeling of the System         3.3.1         Heat Transfer in Wafer | <ul> <li>43</li> <li>43</li> <li>45</li> <li>47</li> <li>48</li> <li>50</li> </ul> |

|   | 3.5                  | Model Based Controller                                          | 60  |

|---|----------------------|-----------------------------------------------------------------|-----|

|   | 3.6                  | Experimental Results                                            | 64  |

|   | 3.7                  | Conclusion                                                      | 67  |

| 4 | Bea                  | m Size Effect on the Spectroscopic Ellipsometric Measurement    |     |

|   | $\operatorname{Res}$ | ult                                                             | 69  |

|   | 4.1                  | Introduction                                                    | 69  |

|   | 4.2                  | Principle of Ellipsometry                                       | 72  |

|   | 4.3                  | Direct Measurement of Beam Size in a Spectroscopic Ellipsometry |     |

|   |                      | Setup                                                           | 76  |

|   | 4.4                  | Spot Focus Size Effect in Spectroscopic Ellipsometry Result     | 84  |

|   |                      | 4.4.1 Geometric Ray Analysis of Spot Focusing                   | 86  |

|   |                      | 4.4.2 Numerical Analysis                                        | 92  |

|   |                      | 4.4.3 Experimental Result                                       | 94  |

|   | 4.5                  | Conclusion                                                      | 99  |

| 5 | Con                  | clusions                                                        | 101 |

|   | 5.1                  | Summary                                                         | 101 |

|   | 5.2                  | Future Work                                                     | 103 |

| References            | 107 |

|-----------------------|-----|

| Addendix A1           | 118 |

| Addendix A2           | 124 |

| Author's Publications | 129 |

### Summary

Lithography is the key technology driver in semiconductor manufacturing. In lithography, the most important variable to be controlled is the critical dimension (CD) uniformity. As transistor dimension continues to scale down, lithography process equipment and materials are stretched towards their limits, thus making the process very sensitive to even small perturbations of process conditions. Advanced control, process/equipment modeling and metrology are widely believed to be the enabling technology needed to enhance CD uniformity in lithography. In this thesis, the application of advanced process control (APC) techniques, new equipment design and sensing technology for the processes in the lithography sequence are investigated to meet the stringent requirement of CD uniformity control.

As the final CD value is very sensitive to the wafer temperature during the thermal processing steps in lithography, it is important to control the wafer spatial temperature uniformity for enhancing the CD uniformity. Based on the detailed thermal model of baking process and the real-time measurement of bake-plate temperature, an in-situ approach is developed to estimate and control the wafer temperature. Using the proposed approach, the wafer spatial temperature uniformity during the entire thermal cycle can be improved more than 80% when compared to the existing methods.

Although the wafer temperature uniformity was successfully improved by the proposed advanced control technique, the performance gain is ultimately limited by the inherent drawbacks of the conventional hot plate. To overcome this limitation, a new programmable integrated bake/chill thermal processing module is designed and implemented. By employing a set of thermoelectric devices (TEDs), resistance temperature detectors (RTDs) and model-based control method, the spatial wafer temperature non-uniformity can be well-controlled during the transient and steady-state period of thermal cycle respectively.

In real-time process control system, CD metrology is also critical in enabling the application of APC in lithography. Hence in this thesis, we investigated the CD metrology offered by scatterometer. For the very small CD value measurement using scatterometer, the beam size effect on the measurement result is not neglectable. Based on the direct beam size measurement method in a spectroscopic ellipsometry setup, the ray path of the scatterometer is numerically calculated for different beam sizes. The analysis shows that both the average optical path lengths and the optical path length differences are sensitive to the focus beam size. Experimental results also show that the difference in beam size led to different ellipsometric measurement results for both uniform film and patterned wafer.

# List of Tables

| 1.1 | Lithography technology requirements                                                | 3  |

|-----|------------------------------------------------------------------------------------|----|

| 2.1 | Physical parameters of the thermal processing system [54]                          | 28 |

| 2.2 | Estimated air-gap thickness and wafer warpage using the real-time con-             |    |

|     | trol method with the proximity pin height of $210\mu m$                            | 40 |

| 2.3 | Maximum temperature nonuniformity and root mean square (RMS) er-                   |    |

|     | ror during the thermal processing using the steady-state and real-time             |    |

|     | control method.                                                                    | 40 |

| 3.1 | Physical parameters of the integrated bake/chill thermal processing                |    |

|     | system [54], [59]                                                                  | 56 |

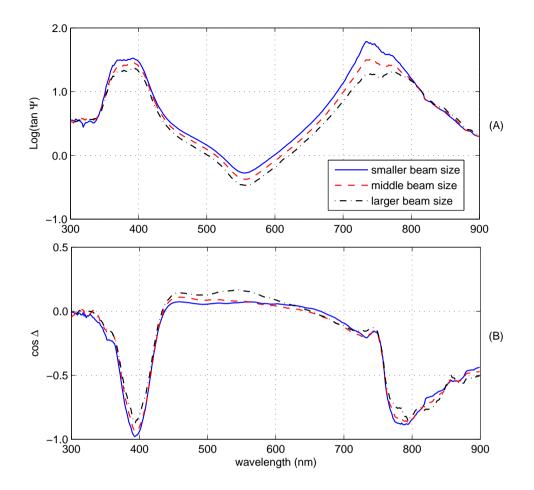

| 4.1 | Wavelengths locations and values corresponding to the peaks of the $log(\tan\Psi)$ | r) |

|     | and $\cos \Delta$ distributions in Figure 4.13 for wafer with a relatively thick   |    |

|     | photoresist layer                                                                  | 96 |

| 4.2 | Wavelengths locations and values corresponding to the peaks of the $log(\tan \Psi)$ | ') |

|-----|-------------------------------------------------------------------------------------|----|

|     | and $\cos\Delta$ distributions in Figure 4.14 for wafer with a relatively thin      |    |

|     | photoresist layer.                                                                  | 96 |

# List of Figures

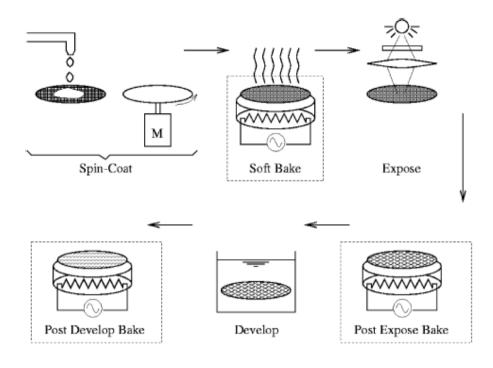

| 1.1 | Typical steps in the lithography sequence [7]                          | 2  |

|-----|------------------------------------------------------------------------|----|

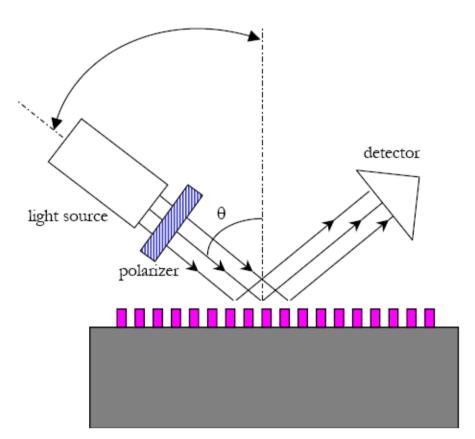

| 1.2 | Single wavelength, variable angle reflectometer                        | 8  |

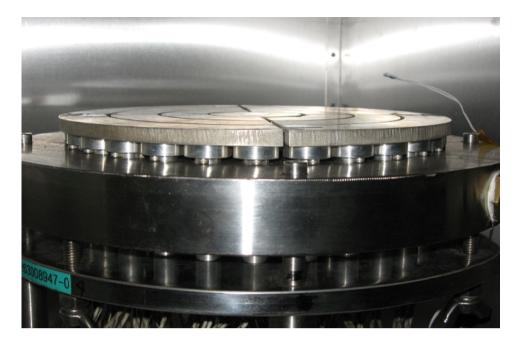

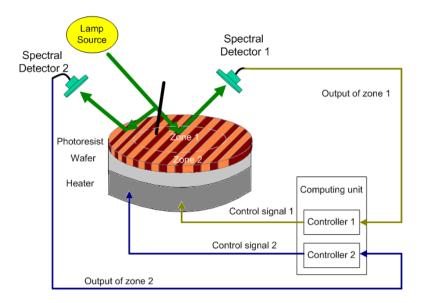

| 2.1 | Programmable multi-zone thermal processing system                      | 19 |

| 2.2 | Schematic diagram of the thermal processing system                     | 20 |

| 2.3 | Thermal model discretization of wafer and bake-plate                   | 21 |

| 2.4 | Plate and wafer temperature in simulation and experiment with air-gap  |    |

|     | thickness be 140 $\mu$ m using the calculated model                    | 30 |

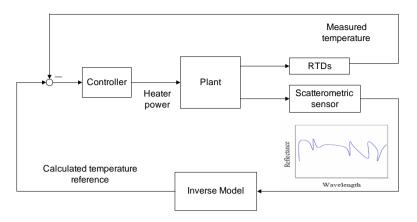

| 2.5 | Block diagram of control structure.                                    | 34 |

| 2.6 | Estimated air-gap thickness using real-time control method when a flat |    |

|     | wafer is dropped on bake-plate with proximity pin height of $210\mu m$ | 36 |

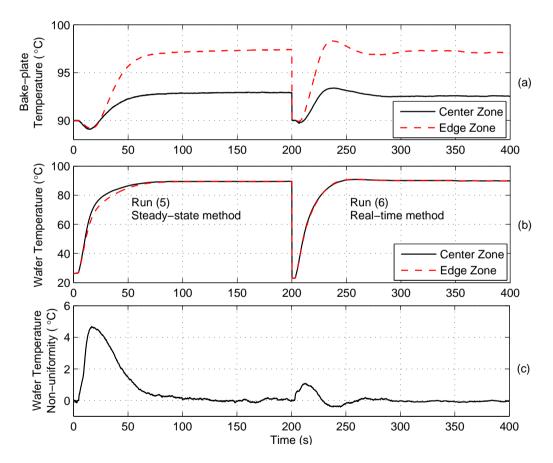

- 2.7 Temperature profile of bake-plate and wafer when a flat wafer is dropped on bake-plate with proximity pin height 210μm. The bake-plate temperatures, wafer temperatures and wafer temperature non-uniformity during the baking process are shown in subplots (a), (b) and (c) respectively. . 36

- 2.10 Estimated air-gap thickness using real-time control method when a wafer

with center-to-edge warpage of 140μm is dropped on bake-plate with

proximity pin height of 210μm.

39

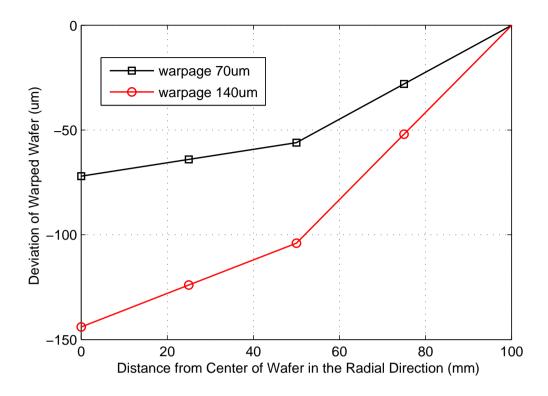

- 2.12 Estimated profile of the warped wafers with center-to-edge warpage of  $70\mu m$  and  $140\mu m$  based on experimental run (4) and (6) respectively. . . 41

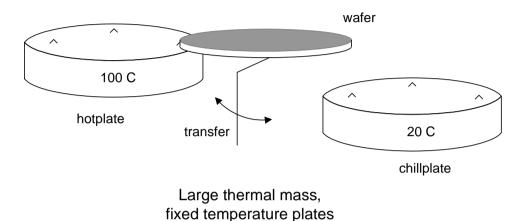

- 3.1 The conventional approach for lithography baking and chilling involves substrate transfer between large thermal mass, fixed temperature plates [38]. 44

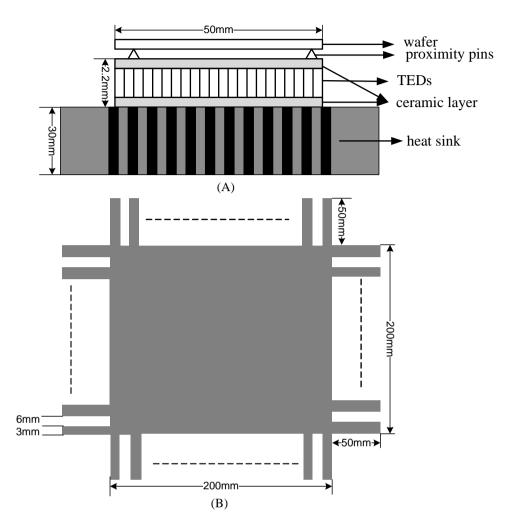

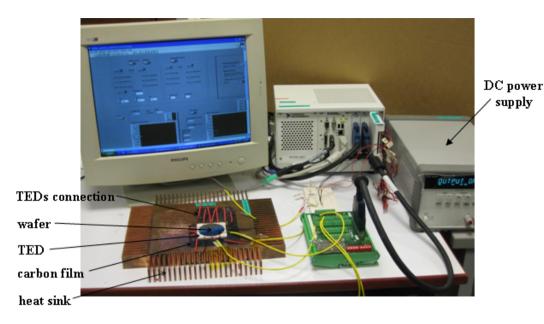

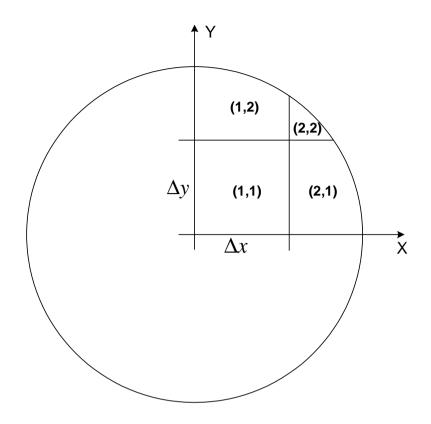

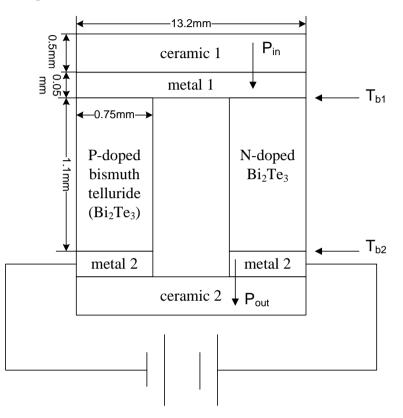

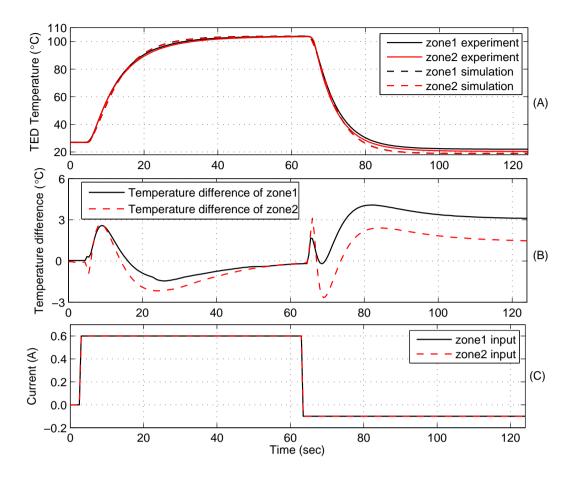

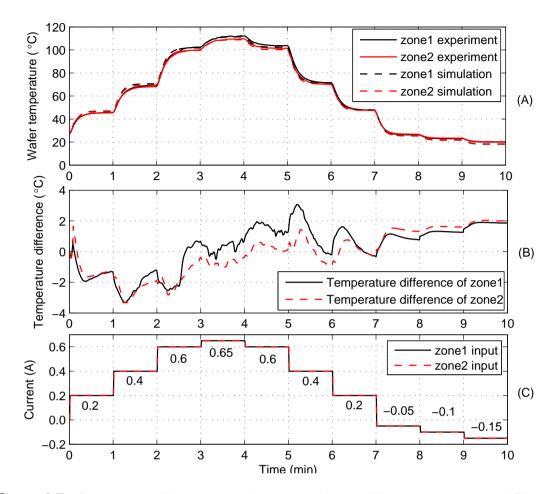

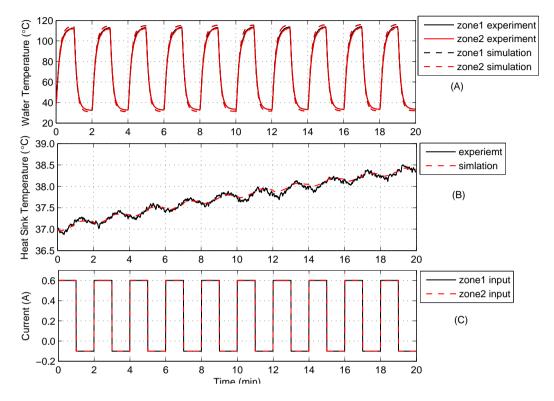

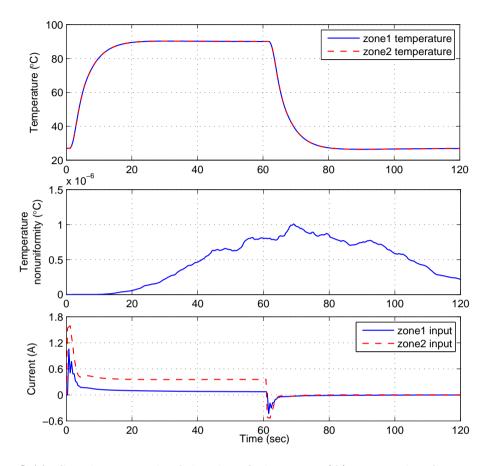

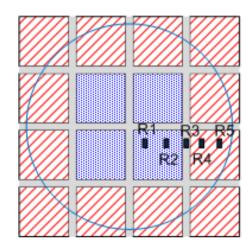

- 3.2Schematic diagram of the integrated bake/chill design. (A) schematic drawing of the system, (B) plan view of the heat sink. (Note: Figures 46are not drawn to scale).  $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$ 3.3 473.449Illustration of wafer discretization in system modeling ..... 3.5Schematic diagram of a thermoelectric element. (Note: Figure is not 513.6 Comparison of experimental and simulated TED temperatures in a heating and cooling cycle. (A) experimental and simulated TED temperature response, the solid line shows the experimental zone1 and zone2 TED temperatures and the dashed line shows the simulated zone1 and zone2 TED temperatures, (B) TED temperature difference between experiment and simulation, the solid line shows the temperature difference of zone1 and the dashed line shows the temperature difference of zone2, (C) input 57currents during the process.

58

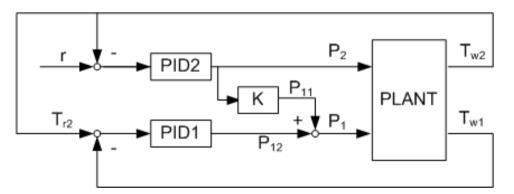

- 3.9 Block diagram of the proposed model based control scheme. . . . . . . 60

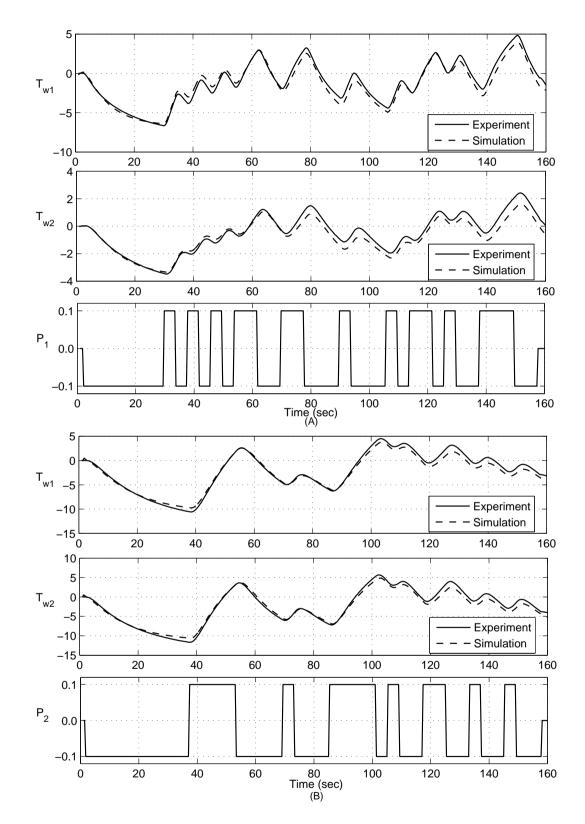

- 3.10 System identification result with two independent pseudo-binary random sequences injected into two control zones respectively. The solid line shows the resulting change in wafer temperature in experiment and the dotted line shows the calculated response using the identified model. . . 63

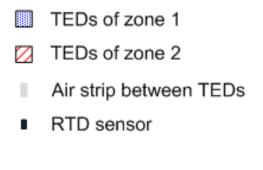

| 3.11 | Simulation result of the identified system. (A) temporal wafer temper-    |    |

|------|---------------------------------------------------------------------------|----|

|      | ature in the simulation, (B) wafer temperature difference of the control  |    |

|      | zones during the entire thermal cycle, (C) input current of the TEDs in   |    |

|      | the two control zones.                                                    | 65 |

| 3.12 | Location of temperature sensors for the integrated bake/chill experiment. |    |

|      | R1 and R5 are used as feedback variables                                  | 66 |

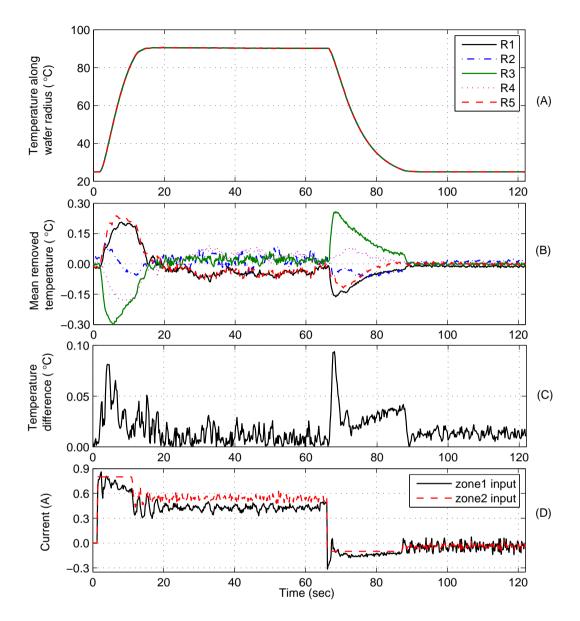

| 3.13 | Experimental wafer temperature along the wafer radius with the tem-       |    |

|      | peratures of sensors R1 and R5 being treated as feedback variables using  |    |

|      | model based control method. (A) wafer temperature response at the five    |    |

|      | points during the whole thermal cycle, (B) mean removed wafer tem-        |    |

|      | perature of the five points, (C) temperature difference between the two   |    |

|      | feedback points on the wafer in the process, (D) control current inputs   |    |

|      | of TEDs during the thermal cycle                                          | 68 |

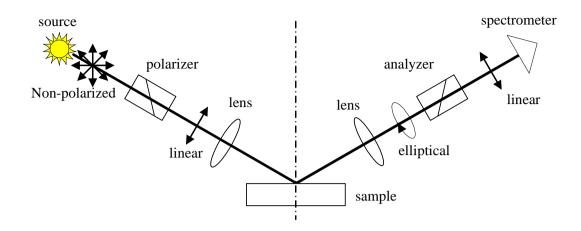

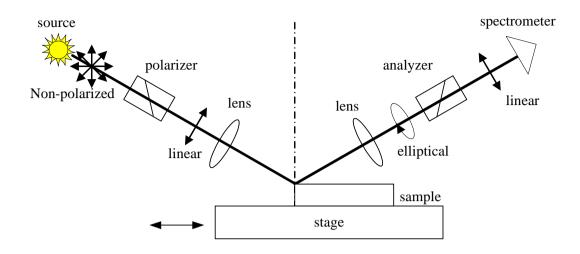

| 4.1  | Illustration of the rotating-polarizer ellipsometer setup                 | 74 |

| 4.2  | Schematic description of the (A) boundary diffraction wave and (B) knife  |    |

|      | edge methods for beam size measurement.                                   | 77 |

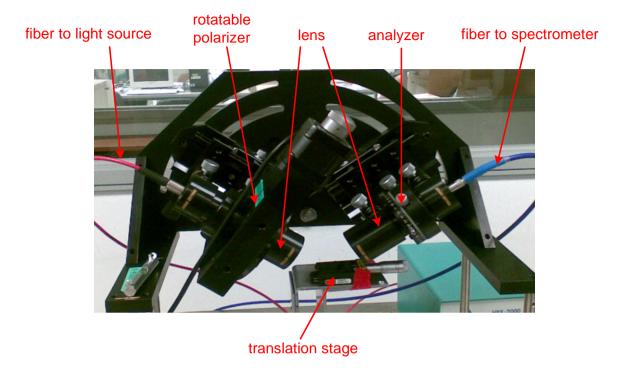

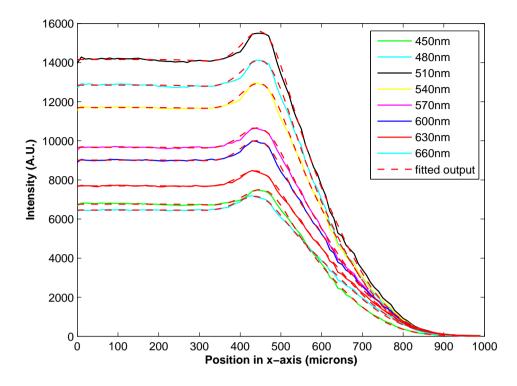

| 4.3  | Schematic description of the Experimental Setup                           | 78 |

| 4.4  | Photograph of the experimental setup used                                 | 80 |

| 4.5  | Plots of experimental (solid) and simulation (dashed) results obtained    |    |

|      | with recording at selected wavelengths from 420nm to 750nm                | 81 |

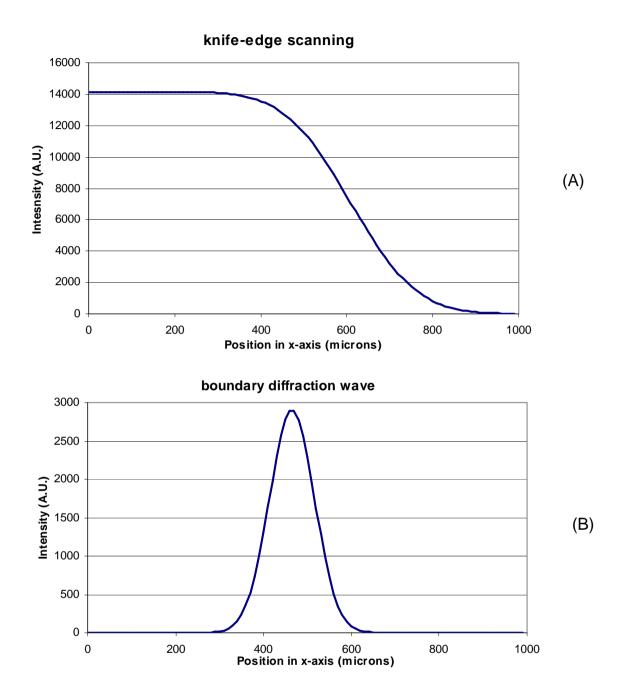

| 4.6  | Reconstruction of knife-edge and boundary diffraction wave components        |    |

|------|------------------------------------------------------------------------------|----|

|      | for 520nm light.                                                             | 82 |

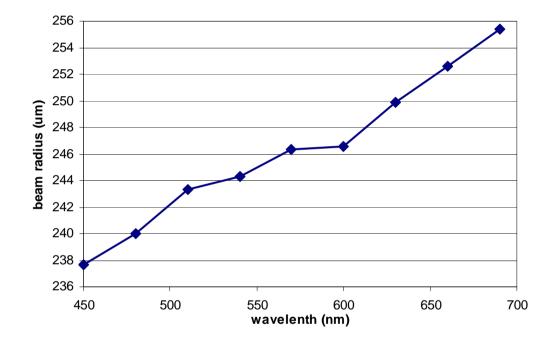

| 4.7  | Plots of beam sizes computed using different wavelengths                     | 83 |

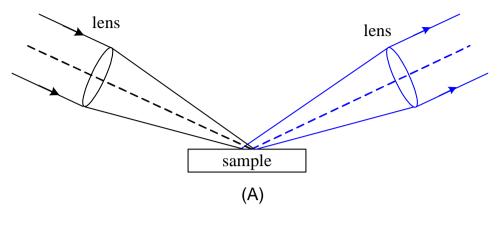

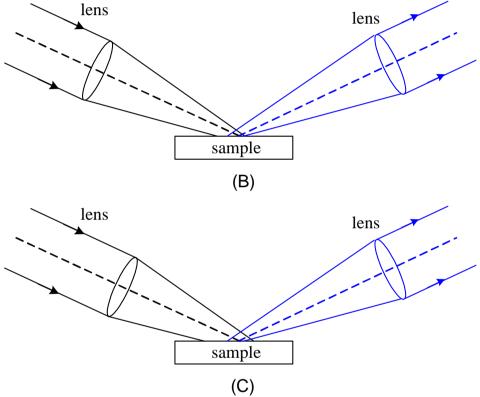

| 4.8  | Various SE incident lens positions for the different beam size: (A) dis-     |    |

|      | tance between lens and sample is 55mm to form small beam size; (B)           |    |

|      | distance between lens and sample is 45mm to form medium beam size;           |    |

|      | (C) distance between lens and sample is 35mm to form large beam size.        | 87 |

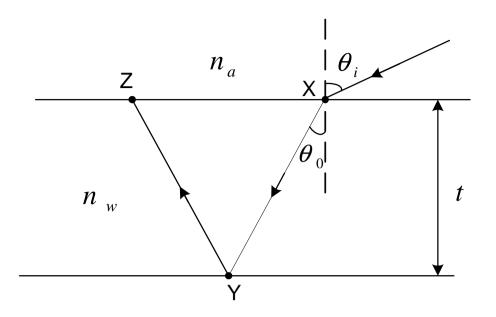

| 4.9  | Illustration of optical path length calculation for the thin film with uni-  |    |

|      | form thickness.                                                              | 88 |

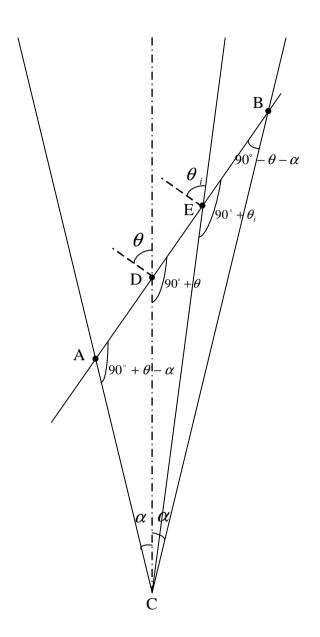

| 4.10 | Illustration of incident angle calculation for different point of the light  |    |

|      | beam on sample top surface.                                                  | 89 |

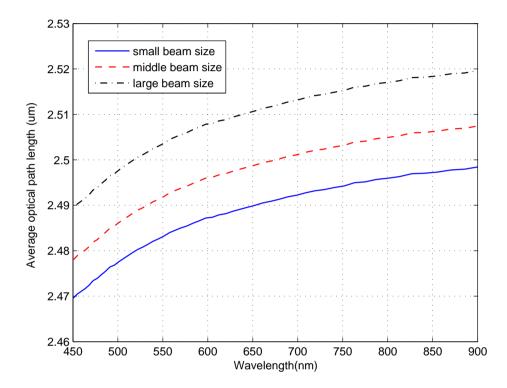

| 4.11 | Simulation result of the average optical path length for different beam      |    |

|      | sizes at different wavelengths                                               | 92 |

| 4.12 | Simulation result of optical path length difference for different beam sizes |    |

|      | at different wavelengths                                                     | 93 |

| 4.13 | Experimental result of the wafer with thick photoresist layer for different  |    |

|      | beam sizes.                                                                  | 95 |

| 4.14 | Experimental result of the wafer with thin photoresist layer for different   |    |

|      | beam sizes.                                                                  | 97 |

| 4.15 | Grating structure used in experiment                                         | 98 |

| 4.16 | Experimental result of the wafer with patterned structure photoresist for |

|------|---------------------------------------------------------------------------|

|      | different beam sizes                                                      |

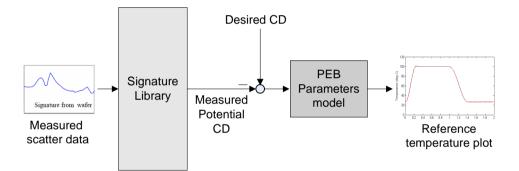

| 5.1  | Schematic diagram of the CD control strategy                              |

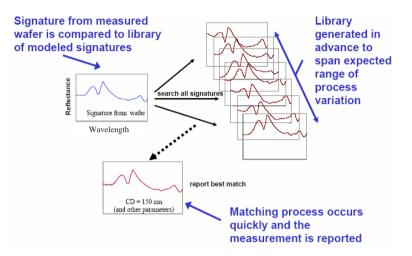

| 5.2  | Diagram of the inverse model                                              |

| 5.3  | Library-based method for inverse problem                                  |

| 5.4  | Schematic diagram of a 2-zone system                                      |

## Chapter 1

## Introduction

### 1.1 Motivation

Lithography has been extensively used in the manufacturing process of Very Large Scaled Integrated (VLSI) circuit and Micro-electromechanical system (MEMS) [1]-[3]. In semiconductor manufacturing, lithography alone takes up about 40% to 50% of the total wafer-processing time [4] and accounts for 30% to 35% of the chip manufacturing cost [5,6]. The demand for faster and larger scale integrated circuits (IC) has pushed the continuing down-scaling of the transistors printed on the silicon wafer. As a result, the IC production equipments and materials are stretched towards their limits and the lithography process is seen as the key driver in feature shrinkage.

Figure 1.1 shows a typical lithography sequence [7]. This sequence of opera-

Figure 1.1. Typical steps in the lithography sequence [7].

tions begins with a priming step to promote adhesion of the polymer photoresist material to the substrate. The solvent is evaporated from the photoresist by a soft-bake process. In the exposure step, the resist-coated substrate is exposed to project the desired patterns from the photomask to the resist film. After patterning with deep ultraviolet (DUV) radiation, a post-exposure bake (PEB) is performed to stimulate the chemical reaction that alters the resist solubility of the exposed areas. A subsequent chemical development step then removes the exposed/reacted photoresist material while keeps the non-exposed areas in place (or vice versa for negative resists). The developed resist is then baked to promote etching stability. In a typical IC fabrication process, these steps could be repeated up to 30 times [7].

The accuracy of circuit patterns generated by the lithography process is assessed by critical dimension (CD) or line-width of the patterned feature on the photoresist. Both gate delay and drive current are proportional to the inverse of the gate length which is determined by CD. It is estimated that 1nm variation in channel CD is equivalent to 1MHz chip-speed variation, and is thus worth about US\$7.50 in the chip's unit selling price [8]. Yu *et al.* [9] have concluded that CD variation is mostly attributed to the lithography step, rather than the other process steps. It is therefore of great importance to precisely control and monitor the dimensions of these resist features in lithography, as these features that determine the dimensions of the actual device features may be reworked upon detecting a deviation from the process specification [10].

Table 1.1 shows the lithography technology node as outlined by the International Technology Roadmap for Semiconductors (ITRS) [11]. A 20% to 30% shrinkage in CD value is projected every two or three years. The drive towards smaller device geometries has placed much tighter control limits on the various semiconductor manufacturing processes. As the industry transitions to sub-100 nm, maintaining adequate and affordable lithographic process latitude becomes an increasingly challenging and difficult task.

Table 1.1. Lithography technology requirements

| Year of Production                | 2007 | 2009 | 2011 | 2013 | 2015 | 2017 |

|-----------------------------------|------|------|------|------|------|------|

| DRAM $1/2$ pitch (Linewidth) (nm) | 65   | 50   | 40   | 32   | 25   | 20   |

| CD control (3 sigma) (nm)         | 6.6  | 5.3  | 4.2  | 3.3  | 2.6  | 2.1  |

| PEB Sensitivity (nm/°C)           | 1.75 | 1.5  | 1.5  | 1    | 1    | 1    |

The application of advanced process control (APC) methodology has been increasingly utilized in recent years to enable the lithography process to print smaller devices [12]- [14]. However, the APC method alone can not meet the stringent CD uniformity requirements because of the inherent drawbacks of the traditional equipments and lack of real-time sensing technology.

Thermal processing system in lithography is conventionally designed with large thermal mass and sluggish dynamics so that it is robust to large temperature fluctuations and loading effects, and demonstrate good long-term stability. These advantages however become shortcomings in terms of process control and achievable performance when tight tolerances must be maintained. Although advanced control can be used to improve performance [15]- [18], it has been shown that the conventional hotplate design has poor controllability [19] due to its inherent sluggish dynamic response and that ultimately limits the achievable performance. Moreover, to achieve demanding CD control tolerances, the process parameters need to be real-time adjusted based on in-situ sensors monitoring the conditions of the process [12]. The lack of in-situ metrology has become a major bottle-neck to meet the more and more stringent requirements [11].

Consequently, the prossing control system in lithography requires careful consideration, including advanced process control techniques, equipment design and process monitoring. In this thesis we will investigate the application of APC, new equipment design and sensing technology for the processes in the lithography sequence.

#### (A) Process Control & Equipment Design

As shown in Figure 1.1, the lithography sequence includes numerous baking steps such as the soft bake, post-exposure bake and post-develop bake [20]. In some cases, additional bake steps are employed. Each of these baking steps serve different roles in transferring latent image into the substrate. To meet the stringent CD control specification, temperature uniformity is critical in photoresist processing, and the most important or temperature sensitive step is post-exposure bake among all of the bake steps in lithography [21]. Zhang et al. [22] showed that the CD variation reduction of 40% can be realized by employing advanced thermal processing system and control method in PEB step. Ho et al. [23] also demonstrated that real-time control of the PEB temperature to give nonuniform temperature distribution across the wafer can reduce CD nonuniformity to as small as 1nm across the wafer. Masahide et al. [24] further verified that the resist pattern CD uniformity improvement through PEB control can contribute to device performance improvement. It was reported that the temperature variation in PEB step can result in more than 10% of target CD [25]. For every degree variation in wafer temperature uniformity during the baking process, CD can vary by as much as 20nm [26]. Parker and Renken [21] list the temperature specifications for resist processing steps which include a uniformity requirement of 0.12°C for DUV PEB. A number of recent investigations also show the importance of proper temperature uniformity, during both transient and steady-state conditions, in significantly enhancing the CD uniformity across the wafer [27]- [32]. According to the ITRS lithography report [11], the post-exposure bake resist sensitivity to temperature will be more stringent for each new lithography generation as depicted in Table 1.1. By the year 2013, the post-exposure bake resist sensitivity is expected to be 1nm/°C, making temperature control even more critical. One approach is to make less temperature sensitive resist materials. Our approach is to apply control and signal processing technologies together with equipment design to reduce wafer temperature variation. With precise temperature control, existing resists can be used for future technology nodes.

The conventional PEB step is conducted by transferring the cold wafer to the hot bake-plate where it is baked at a temperature typically between 70°C and 150°C for a time period between 60s and 90s. The heated wafer is then mechanically transferred to a chill-plate where it is cooled to a temperature between 18°C and 30°C [33]. Even with state-of-the-art wafer tracks, the across-wafer PEB temperature range can be as much as 9°C during the heating and cooling transient and 0.7°C during the steady-state [29]. While better performance has been recorded [34]- [37], it is very difficult to achieve good uniformity, especially during the transient phase, due to the lack of temperature control during wafer transport, heating and cooling transients. Our objective is to provide an effective control method to improve the dynamic performance of the wafer temperature the baking process using conventional bake-plate.

As discussed previously, the application of advanced control algorithm alone is not sufficient to meet the stringent CD uniformity requirement. The poor controllability of the conventional hotplate design ultimately limits the achievable performance of APC method. Other disadvantages of the hot plates include uncontrolled and non-uniform temperature fluctuation during the mechanical transfer of the substrates from the bake plate to chill plate, and spatial temperature nonuniformities during the entire thermal cycle [13], [38]. The lacking of a real-time, distributed and closed-loop temperature control method in the conventional hot plate is a source of process error in the lithography chain. Our objective is to design a new thermal processing system to achieve rapid dynamic temperature response and minimize the temperature nonuniformity during the transfer from heating to cooling process by real-time wafer temperature control method.

#### (B) Integrated Metrology

Real-time process control requires in-situ measurement. CD metrology plays a key role enabling productivity gains made through APC in lithography. The continuing decreasing of CD size has also led to smaller process control windows that drive a need for higher precision metrology to maintain an acceptable precisionto-tolerance ratio. According to the metrology report of ITRS [11], the next generation lithographic technology requires advances in the area of metrology for CD measurement.

Various techniques have been both proposed and implemented for these purposes. Among them, scatterometry is considered as an ideal candidate for in-situ process monitoring. The optical instrument can be made small enough to fit in the space of the bake module on a wafer track, enabling a true wafer-by-wafer metrology scheme. Furthermore, the quality (full profile versus top-town view) and quantity (accuracy, precision, and throughput) of the collected data underscore its clear advantage for inline application [39].

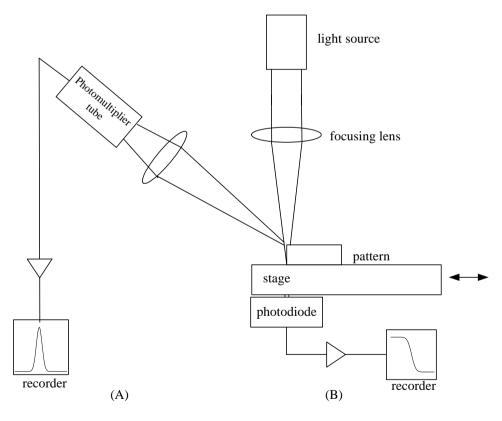

Scatterometry is based on the reconstruction of the index of refraction grating profile from its optical diffraction responses. Single-wavelength variable-angle reflectometer is the first optical configuration used on commercial scatterometry systems [40]. The system shines a beam of light perpendicular to the direction of the grating lines, and analyzes the reflectance from the grating at multiple angles of incidence.

Figure 1.2. Single wavelength, variable angle reflectometer

Figure 1.2 illustrates a typical single-wavelength variable-angle reflectometer system. A laser light source directs single-wavelength light on the sample structure after passing a polarizer. Depending on the grating pitch and the light wavelength, there can be multiple orders of diffraction from the grating (which are not drawn in the figure), but only the zeroth-order of diffracted light is collected by the detector. When the angle of incidence is varied, the detector angle varies accordingly. Therefore, this configuration is also called  $2 - \theta$  scatterometry.

Since a laser source can be used for  $2 - \theta$  scatterometry, its optical setup is relatively easy compared to configurations with broadband light sources, and the signal to noise ratio can be quite high. The key drawback of the  $2-\theta$  scatterometry configuration is also due to its single-wavelength light source. For most of the grating structures, the sensitive wavelength range can vary from UV to IR depending on the structure, and very often it does not cover the wavelength of the  $2-\theta$  scatterometry light source. Furthermore, it is unable to distinguish neighboring film stacks with similar refractive indices at the measurement wavelength. The other disadvantage is that only the intensity of the reflectance signal is obtained, which may contain less profile information than those systems such as the ellipsometer that can also get phase information from the reflectance.

In contrast to variable-angle scatterometry, Niu *et al.* [41] proposed a specular spectroscopic scatterometry, which makes use of the existing spectroscopic ellipsometry (SE) equipment to measure intensity and phase of the zeroth-order diffraction at a fixed incident angle and multiple wavelengths. This type of information, coupled with a very efficient rigorous coupled-wave analysis (RCWA) [42] implementation, seems to be adequate for detailed reconstruction of the profiles of periodic gratings.

Spectroscopic ellipsometry is a surface analytical technique that provides the reflected light amplitude and phase information through measurement of states of polarization of the reflected light. This technique is widely used in thin film analysis [43]- [46] due to its ability to provide easily conducted nondestructive measurements without the need for vacuum environments. It has been established that the measured ellipsometric signal will vary according to the probing light beam size and its collimation under the presence of optical inhomogeneity in the film [46]. Thus, using the specular spectroscopic scatterometry to measure photoresist layer thickness and CD value, the beam size effect of the ellipsometer must be taken into consideration.

### **1.2** Contributions

In this thesis, advanced process control, equipment design and metrology design are applied to the lithography sequence. The thesis contributions are summarized as follows.

#### (A) Real-time Spatial Wafer Temperature Control

As discussed in section 1.1, the wafer temperature spatial uniformity, in both transient and steady-state phase, plays an important role in final CD uniformity. A real-time wafer temperature control method is thus proposed to minimize temperature nonuniformity in the whole heating process and improve the dynamic performance of the wafer temperature. To control the wafer temperature uniformity, we developed a detailed simulation model based on first principle heat transfer analysis of the system. By adopting the model, the average air-gap thickness between the bake-plate and wafer in each of the heating zones can be extracted and consequently the wafer temperature can be estimated online. Experimental result shows that the estimated wafer warpage and temperature are accurate, with which the wafer temperature nonuniformity can be controlled in real time.

Comparing to the steady-state wafer temperature control approach [47], the proposed real-time control approach takes the dynamic properties of the system into consideration. A detailed physical model of the thermal system is first developed with unknown air-gap thickness. Next, by monitoring the bake-plate temperature and fitting these data into the model, the air-gap thickness can be estimated and the wafer temperature can be calculated and controlled in real-time. This is useful as production wafers usually do not have temperature sensors embedded on it, these bake-plates are usually calibrated based on test wafers with embedded sensors. However, as processes are subjected to process drifts, disturbances, and wafer warpages, real-time correction of the bake-plate temperatures to achieve uniform wafer temperature is not possible in current baking systems. Any correction is done based on run-to-run control techniques which depend on the sampling frequency of the wafers. The approach is real-time and can correct for any variations in the desired wafer temperature performance during both transient and steady-state phase. The proposed approach is applied to a conventional multi-zone thermal processing system, where the root mean square (RMS) of temperature nonuniformity in the entire thermal cycle was improved by more than 80%. The profile of the warped wafer can also be estimated from the extracted air-gap thickness during the steady-state phase.

### (B) Design and Implementation of Programmable Integrated Bake/Chill System

The real-time spatial wafer temperature control method provides an effective way to improve wafer transient temperature uniformity. However, the achievable performance gain is ultimately limited by the drawbacks of the conventional baking system. Firstly, the wafer dynamic response is constrained by the inherent sluggish dynamic of the bake plate due to its large thermal mass. Secondly, the mechanical wafer transfer from hot plate to chill plate results in the uncontrollable wafer temperature fluctuations.

To solve the above mentioned problems, we developed a novel design of bake/chill integrated thermal processing module to achieve rapid dynamic response and good wafer temperature controllability throughout the entire processing temperature cycle of ramp, hold and quench in lithography. The system integrates the baking and chilling processes of the lithography sequence, and thus eliminates the undesirable and uncontrollable temperature fluctuations during the substrate transfer process. Moreover, the system is also physically compact and easy to implement. In the designed bake/chill integrated thermal processing module, a set of thermoelectric devices (TEDs) are employed as the main mode of heat transfer. The TEDs can provide rapid distributing heating to the substrate for facilitating uniformity and transient temperature control. Besides, the TEDs are also used to provide active cooling for chilling the substrate to a temperature suitable for subsequent processing steps. In the designed module, the resistance temperature detectors (RTDs) are embedded in the proximity pins to provide in-situ temperature measurement.

The proposed module is analyzed via first principle heat transfer analysis and backed up by experimental validation. By adopting a new proposed model based feedback control algorithm, the temperature difference between the feedback points can be minimized to less than  $0.1^{\circ}$ C in the entire thermal process. In addition, the wafer spatial temperature nonuniformity can be well-controlled within the range of  $\pm 0.3^{\circ}$ C and  $\pm 0.1^{\circ}$ C during the transient and steady-state phase respectively.

#### (C) Investigation of Beam Size Effect on Scatterometer Measurement

As discussed in section 1.1, scatterometer, which makes use of the existing spectral ellipsometry, has been considered as an ideal candidate for in-situ process monitoring. Our ultimate objective is to integrate SE-based CD metrology in the real-time control process in lithography. For the decreasing CD value measurement, the effect of beam size on the ellipsometry measurement result must be taken into consideration. In this thesis, the beam size effect on ellipsometry result is investigated.

A new direct beam size measurement method in a spectroscopic ellipsometry setup is firstly proposed to define the beam size value. The technique uses the existing detection facilities in a spectroscopic ellipsometry setup to determine the beam size without the need to rearrange the optical components. The change of the reflected light when the incident light illuminates on the moving sample's edge is recorded in experiment. In this case the recorded intensity signal comprises a coupled boundary diffraction and knife edge wave that can be isolated using nonlinear fitting. This then permits an accurate measurement of the beam size with the stronger knife edge component.

Based on the beam size measurement method, geometric ray at the illumination and recording ends of spectroscopic ellipsometry is then analyzed for different beam size values. The numerical analysis and further experimental results revealed substantial changes ellipsometry result with different beam sizes for both uniform thickness films and patterned samples.

### 1.3 Organization

This thesis is organized as follows. In Chapter 2, a real-time and in-situ approach to control the wafer spatial temperature uniformity in both transient and steady-state phase of the thermal process using a multi-zone baking system. A programmable multi-zone integrated bake/chill thermal processing system for across-wafer temperature uniformity control is designed and developed in Chapter 3. Chapter 4 describes a direct beam size measurement method based on the spectroscopic ellipsometry setup and investigates the beam size effect on the ellipsometer measurement result for both uniform film and patterned wafer. Conclusions and future work are given in Chapter 5.

### Chapter 2

# In-situ Real-time Spatial Wafer Temperature Control

### 2.1 Introduction

Thermal processing of semiconductor substrate is common and critical to photoresist processing in the lithography sequence. As discussed in Chapter 1, temperature uniformity control is an important issue in photoresist processing with stringent specifications and has a significant impact on the linewidth or CD. The most temperature sensitive step in the lithography sequence is the PEB step. Requirements call for temperature to be controlled within 0.1°C at temperatures between 70°C and 150°C. A number of recent investigations also showed the importance of proper bake-plate operation, both in steady-state and transient, on CD control [48], [49]. Thermal processing of semiconductor wafers is commonly performed by placement of the substrate on a heated bake-plate for a given period of time. The heated bake-plate is usually of large thermal mass and is held at a constant temperature by a feedback controller that adjusts the heater power in response to a temperature sensor embedded in the bake-plate near the surface. The wafers are usually placed on proximity pins. When a wafer at room temperature is placed on the bake-plate, the temperature of the bake-plate drops at first but recovers gradually because of closed-loop control. Different air-gap sizes will result in different wafer and plate temperature due to the difference in the air-gap thermal resistance between the substrates and the bake-plate. A warped wafer will thus affect the various baking processes in the lithography sequence and cause temperature nonuniformity across wafer.

A fast in-situ approach to estimating wafer warpage profile during thermal processing [50] was developed to deal with the problem. It demonstrates that information of the average air-gap between the wafer and the bake-plate can be obtained with the use of system theory tools. The relationship between the wafer and plate temperature at steady-state can be derived from physical modeling of the baking process. By monitoring the maximum plate temperature drop, the average air-gap in each bake-plate zone can be estimated, and the new bake-plate temperature set point to achieve desirable wafer steady-state temperature [47]. In this way, the wafer steady-state temperature nonuniformity can be controlled to less than 0.1°C, but one of the major drawbacks of the mentioned approach is that it does not take into account the dynamic performance of the wafer temperature. It has been reported that even though the steady-state temperature ranges was minimized, the resulting gains in CD uniformity cannot be realized attributed to the temperature distribution while rising to the PEB temperature [51].

In this work, we present an in-situ approach to real-time estimation of wafer warpage and control of both the transient and the steady-state wafer temperature uniformity during the baking steps in the lithography process. Our objective is to control the wafer temperature to its desired value and minimize the spatial temperature nonuniformity across the wafer during the whole thermal cycle using the multi-zone bake-plate as shown in Figure 2.1. Based on the detailed thermal model of baking process and the real-time measurement of bake-plate temperature, an in-situ approach is developed to estimate and control the wafer temperature. Using the proposed approach, the wafer spatial temperature uniformity during the entire thermal cycle achieved an improvement of more than 80% when compared to the existing methods.

This chapter is organized as follows, in section 2.2 the detailed model of the thermal processing system is developed based on first principle of heat transfer. The control structure and experimental result are given in section 2.3 to demonstrate the effectiveness of the proposed method. Finally, conclusions are given in section 2.4.

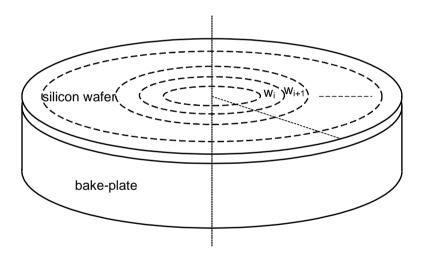

Figure 2.1. Programmable multi-zone thermal processing system.

# 2.2 Thermal Modeling of the System

The distributed thermal processing system used in this work is shown in Figure 2.2. In this section, a physical model will be derived for a N-zone bake-plate based on first principle of heat transfer. Analysis of the thermal processing system can be done with a model considering radial as well as the axial effects of heat transfer in the module. The bake-plate is discretized into different zones and separated with a small air-gap of approximately 1mm for thermal insulation. The fact that the zones are spatially disjoint ensures no direct thermal coupling between the zones, enhancing controllability.

In the baking process, the bake-plate is heated up by the cartridge heater attached to it. Resistive heating elements are embedded in each of the heater. Each heating zone is configured with its own temperature sensor and electronics

Figure 2.2. Schematic diagram of the thermal processing system.

embedded in the cartridge for feedback control. Depending on application, the number of zones of the bake-plate can be easily configured.

Spatial distribution of temperature and other quantities in a silicon wafer are most naturally expressed in a cylindrical coordinate system as shown in Figure 2.3. Energy balances on the elements in the system can then be carried out to obtain a thermal model as follows:

$$C_w \dot{T}_w = q_w^{in} + q_w^{out} + q_w^{top} + q_w^{bottom}$$

$$\tag{2.1}$$

$$C_{ag}\dot{T}_{ag} = q_{ag}^{in} + q_{ag}^{out} + q_{ag}^{top} + q_{ag}^{bottom}$$

(2.2)

$$C_p \dot{T}_p = q_p^{in} + q_p^{out} + q_p^{top} + q_p^{bottom}$$

$$\tag{2.3}$$

$$C_{ap}\dot{T}_{ap} = q_{ap}^{in} + q_{ap}^{out} + q_{ap}^{top} + q_{ap}^{bottom}$$

(2.4)

$$C_c \dot{T}_c = q_c^{side} + q_c^{top} + q_c^{bottom}$$

$$\tag{2.5}$$

$$C_h \dot{T}_h = q_h^{side} + q_h^{top} + q_h^{bottom} + q^{input}$$

(2.6)

where T is the temperature above the ambient,  $q^{in}$ ,  $q^{out}$ ,  $q^{top}$ , and  $q^{bottom}$  the heat flow into the element from inner zone, outer zone, top surface and bottom surface respectively,  $q^{side}$  the heat flow rate from side surface,  $q^{input}$  the heater input power, and the subscribe w, ag, p, ap, c, and h represent the wafer, the air-gap, the bake-plate, the air-gap separating the bake-plate, the cartridge and the heater respectively, C is the thermal capacitance, for each element,  $C = \rho c_v V$ , where  $\rho$  is the density,  $c_v$  the specific heat capacity, and V the volume of the element.

Figure 2.3. Thermal model discretization of wafer and bake-plate.

### 2.2.1 Wafer and Air Gap Modeling

For the wafer in the system,  $q_w^{in}$  and  $q_w^{out}$  are the conduction heat flow from the inner and outer adjacent wafer element, for the wafer of zone *i*, we have

$$q_{w(i)}^{in} = \frac{k_w A_{ws(i-1)}}{\Delta_r} (T_{w(i-1)} - T_{w(i)}), \qquad 2 \le i \le N$$

(2.7)

$$q_{w(i)}^{out} = \begin{cases} \frac{k_w A_{ws(i)}}{\triangle_r} (T_{w(i+1)} - T_{w(i)}), & 1 \le i \le N - 1\\ h_w A_{ws(N)} (-T_{w(N)}), & i = N \end{cases}$$

(2.8)

where k is the thermal conductivity coefficient,  $A_{s(i)}$  the contact area between the adjacent elements i and i + 1,  $A_{s(N)}$  the side surface area, and  $\Delta_r$  the distance between the centroid of the adjacent element, h the convection coefficient, which can be calculated from [52] as

$$h = \frac{k}{L}\overline{N_u} \tag{2.9}$$

where  $\overline{N_u}$  is the Nusselt number, L is the characteristic length, and from [52], we have

$$\overline{N_u} = \{0.60 + \frac{0.387Ra^{1/6}}{[1 + (0.559/Pr)^{9/16}]^{8/27}}\}^2$$

(2.10)

The wafer top surface is exposed to the surroundings and so we have

$$q_{w(i)}^{top} = h_w A_{wz(i)}(-T_w), \qquad 1 \le i \le N$$

(2.11)

where  $A_{wz(i)}$  the top area of wafer element *i* exposed to the ambient.

The air-gap between the wafer and bake-plate is about  $210\mu$ m. Since it is much less than 5.8mm, and their temperature difference is considerably smaller than 200°C [53], the heat transfer mechanism is essentially conductive and given by

$$q_{w(i)}^{bottom} = -k_{ag} A_{ag} \frac{\partial T_{ag}}{\partial z_{ag}}|_{boundary}$$

(2.12)

where z is the thickness.

The above equation can be expressed in difference equation as

$$q_{w(i)}^{bottom} = \frac{A_{wag(i)}(T_{ag(i)} - T_{w(i)})}{z_{ag}/2k_{ag} + z_w/2k_w}, \qquad 1 \le i \le N$$

(2.13)

where  $A_{wag(i)}$  is the contact cross-sectional area between wafer and air-gap layer of element *i*.

For the air-gap layer, similarly, we have,

$$q_{ag(i)}^{in} = \frac{k_{ag}A_{ags(i-1)}}{\triangle_r} (T_{ag(i-1)} - T_{ag(i)}), \qquad 2 \le i \le N$$

(2.14)

$$q_{ag(i)}^{out} = \begin{cases} \frac{k_{ag}A_{ags(i)}}{\triangle_r} (T_{ag(i+1)} - T_{ag(i)}), & 1 \le i \le N - 1\\ h_{ag}A_{ags(N)} (-T_{ag(N)}), & i = N \end{cases}$$

(2.15)

$q_{ag(i)}^{top}$  is the heat flow from the wafer layer by conduction,

$$q_{ag(i)}^{top} = \frac{A_{wag(i)}(T_{w(i)} - T_{ag(i)})}{z_{ag}/2k_{ag} + z_w/2k_w}, \qquad 1 \le i \le N$$

(2.16)

For the bottom of the air-gap layer, one part of the layer contact with the bake-plate and the other part contact with the air-gap inside the bake-plate, so we have

$$q_{ag(i)}^{bottom} = \frac{A_{agp(i)}(T_{p(i)} - T_{ag(i)})}{z_{ag}/2k_a + z_p/2k_p} + 2k_a A_{agap(i)} \frac{T_{ap(i)} - T_{ag(i)}}{z_{ag} + z_p}, \qquad 1 \le i \le N \quad (2.17)$$

where  $A_{agp(i)}$  is the contact cross-sectional area between air-gap layer and the bakeplate of element *i*, and  $A_{agap(i)}$  the contact cross-sectional area between air-gap layer and the air-gap in the bake-plate of element *i*.

### 2.2.2 Bake-Plate Modeling

The bake-plate in different zones are separated by small air-gaps with thickness of 1mm, so  $q_p^{in}$  and  $q_p^{out}$  are the conduction heat flow from the inner and outer air-gap, thus we have

$$q_{p(i)}^{in} = \frac{A_{ips(i)}}{t_{p(i)}/2k_p + t_{ap(i-1)}/2k_a} (T_{ap(i-1)} - T_{p(i)}), \qquad 2 \le i \le N$$

(2.18)

$$q_{p(i)}^{out} = \begin{cases} \frac{A_{ops(i)}}{t_{p(i)}/2k_p + t_{ap(i)}/2k_a} (T_{ap(i)} - T_{p(i)}), & 1 \le i \le N - 1 \\ h_p A_{ps(N)} (-T_{p(N)}), & i = N \end{cases}$$

(2.19)

where  $A_{ips(i)}$  is the contact area between the bake-plate of zone i and the inner adjacent air-gap,  $A_{ops(i-1)}$  the contact area between the bake-plate of zone i and the outer adjacent air-gap, and  $t_{p(i)}$  and  $t_{ap(i)}$  represent the horizontal thickness of the bake-plate and the air-gap inside the bake-plate of element *i* respectively.

$$q_{p(i)}^{top} = \frac{A_{agp(i)}(T_{ag(i)} - T_{p(i)})}{z_{ag}/2k_a + z_p/2k_p}, \qquad 1 \le i \le N$$

(2.20)

For the bottom of the air-gap layer, one part of the layer contact with the cartridge via epoxy layer and the other part contact with the ambient, so we have

$$q_{p(i)}^{bottom} = \frac{T_{c(i)} - T_{p(i)}}{\frac{z_p/2k_p + z_c/2k_c}{A_{pc(i)}} + R_{ex(i)}} + h_p A_{pa(i)}(-T_{p(i)}), \qquad 1 \le i \le N$$

(2.21)

where  $A_{pc(i)}$  is the contact cross-sectional area between the bake-plate and the cartridge of element i, and  $A_{pa(i)}$  the contact cross-sectional area between the bake-plate and the bottom ambient of element i,  $R_{ex(i)}$  the thermal resistance of epoxy layer of element i,  $R_{ex(i)} = \frac{z_{ex}}{k_{ex}A_{pc(i)}}$ .

For the air-gap separating the bake-plates, we have

$$q_{ap(i)}^{in} = \frac{A_{ops(i)}}{t_{p(i)}/2k_p + t_{ap(i)}/2k_a} (T_{p(i)} - T_{ap(i)}), \qquad 1 \le i \le N - 1$$

(2.22)

$$q_{ap(i)}^{out} = \frac{A_{ips(i+1)}}{t_{p(i+1)}/2k_p + t_{ap(i)}/2k_a} (T_{p(i+1)} - T_{ap(i)}), \qquad 1 \le i \le N - 1 \qquad (2.23)$$

$$q_{ap(i)}^{top} = 2k_a A_{agap(i)} \frac{T_{ag(i)} - T_{ap(i)}}{z_{ag} + z_p}, \qquad 1 \le i \le N - 1 \qquad (2.24)$$

$$q_{ap(i)}^{bottom} = h_{ap} A_{agap(i)}(-T_{ap(i)}), \qquad 1 \le i \le N-1$$

(2.25)

### 2.2.3 Cartridge and Heater Modeling

The cartridge's side surface are exposed to the ambient air, so the heat transfer on the side surface is convection with the air,

$$q_{c(i)}^{side} = h_c A_{cs(i)}(-T_{c(i)}), \qquad 1 \le i \le N$$

(2.26)

The cartridge top surface is attached to the bake-plate via epoxy layer, so we have

$$q_{c(i)}^{top} = \frac{T_{p(i)} - T_{c(i)}}{\frac{z_p/2k_p + z_c/2k_c}{A_{pc(i)}} + R_{ex(i)}}, \qquad 1 \le i \le N$$

(2.27)

For the bottom surface of the cartridge, one part of the bottom heat flow is the conduction with the heater and the other part is the convection with the ambient air,

$$q_{c(i)}^{bottom} = \frac{A_{ch(i)}(T_{h(i)} - T_{c(i)})}{z_c/2k_c + z_h/2k_h} + h_c A_{ca(i)}(-T_{c(i)}), \qquad 1 \le i \le N$$

(2.28)

where  $A_{ch(i)}$  is the contact cross-sectional area between the cartridge and the heater of element i, and  $A_{ca(i)}$  the area of the cartridge bottom surface of element i exposed to the ambient.

Similarly, for the heater, we have

$$q_{h(i)}^{side} = h_h A_{hs(i)}(-T_{h(i)}), \qquad 1 \le i \le N$$

(2.29)

$$q_{h(i)}^{top} = \frac{A_{ch(i)}(T_{c(i)} - T_{h(i)})}{z_c/2k_c + z_h/2k_h}, \qquad 1 \le i \le N$$

(2.30)

$$q_{h(i)}^{bottom} = h_h A_{ha(i)}(-T_{h(i)}), \qquad 1 \le i \le N$$

(2.31)

where  $A_{ha(i)}$  is the area of the heater bottom surface of element *i* exposed to the ambient.

Most thermophysical properties are temperature dependent. However, for the temperature range of interest from 15°C to 150°C, it is reasonable to assume that they remain fairly constant and can be obtained from handbooks [54] as tabulated in Table 2.1.

From the heat transfer differential equations, we can derive the state-space format model of the system as Equation 2.32 (See Appendix A1 for details).

|                       | Property                                 | Value                    |  |

|-----------------------|------------------------------------------|--------------------------|--|

| Wafer (silicon)       | Density, $\rho$                          | $2330 \rm kgm^{-3}$      |  |

|                       | Specific heat capacity, $c_v$            | $750 J K^{-1} kg^{-1}$   |  |

|                       | Thermal conductivity, $k$                | $99 Wm^{-1} K^{-1}$      |  |

|                       | Convection coefficient, $h$              | $3.3824 Wm^{-2} K^{-1}$  |  |

|                       | Thickness, $z$                           | 0.700mm                  |  |

| Air                   | Density, $\rho$                          | $1.1 \mathrm{kgm}^{-3}$  |  |

|                       | Specific heat capacity, $c_v$            | $1000 J K^{-1} kg^{-1}$  |  |

|                       | Thermal conductivity, $\boldsymbol{k}$   | $0.03 Wm^{-1} K^{-1}$    |  |

| Bake-plate (aluminum) | Density, $\rho$                          | $2700 \mathrm{kgm}^{-3}$ |  |

|                       | Specific heat capacity, $c_{v}$          | $917 J K^{-1} kg^{-1}$   |  |

|                       | Thermal conductivity, $\boldsymbol{k}$   | $250 Wm^{-1} K^{-1}$     |  |

|                       | Convection coefficient, $h$              | $7.271 Wm^{-2} K^{-1}$   |  |

|                       | Thickness, $z$                           | 6.8mm                    |  |

| Epoxy                 | Thermal conductivity, $k$                | $0.35 Wm^{-1} K^{-1}$    |  |

|                       | Thickness, $z$                           | $0.02 \mathrm{mm}$       |  |

| Cartridge (aluminum)  | Density, $\rho$                          | $2700 \mathrm{kgm}^{-3}$ |  |

|                       | Specific heat capacity, $c_{v}$          | $917 J K^{-1} kg^{-1}$   |  |

|                       | Thermal conductivity, $\boldsymbol{k}$   | $250 Wm^{-1} K^{-1}$     |  |

|                       | Convection coefficient, $\boldsymbol{h}$ | $4.86 Wm^{-2}K^{-1}$     |  |

|                       | Thickness, $z$                           | 4.4mm                    |  |

| Heater (aluminum)     | Density, $\rho$                          | $2700 \mathrm{kgm}^{-3}$ |  |

|                       | Specific heat capacity, $c_{v}$          | $917 J K^{-1} kg^{-1}$   |  |

|                       | Thermal conductivity, $\boldsymbol{k}$   | $250 Wm^{-1} K^{-1}$     |  |

|                       | Convection coefficient, $\boldsymbol{h}$ | $5.7828 Wm^{-2} K^{-1}$  |  |

|                       | Thickness, $z$                           | 5.4mm                    |  |

Table 2.1. Physical parameters of the thermal processing system [54].

$$\dot{T} = \begin{bmatrix} \dot{T}_{w} \\ \dot{T}_{ag} \\ \dot{T}_{p} \\ \dot{T}_{ap} \\ \dot{T}_{c} \\ \dot{T}_{h} \end{bmatrix} = \begin{bmatrix} F_{ww} & F_{wag} & 0_{NN} & 0_{NN} & 0_{NN} \\ F_{agw} & F_{agag} & F_{agp} & F_{agap} & 0_{NN} & 0_{NN} \\ 0_{NN} & F_{pag} & F_{pp} & F_{pap} & F_{pc} & 0_{NN} \\ 0_{NN} & F_{apag} & F_{app} & 0_{NN} & 0_{NN} \\ 0_{NN} & 0_{NN} & F_{cp} & 0_{NN} & F_{cc} & F_{ch} \\ 0_{NN} & 0_{NN} & 0_{NN} & 0_{NN} & F_{hc} & F_{hh} \end{bmatrix} \begin{bmatrix} T_{w} \\ T_{ag} \\ T_{p} \\ T_{c} \\ T_{c} \\ T_{h} \end{bmatrix} + \begin{bmatrix} 0_{N} \\ 0_{N} \\ 0_{N} \\ 0_{N} \\ 0_{N} \\ 0_{N} \\ 0_{N} \end{bmatrix}_{q^{input}}$$

$$= FT + Gq^{input} \qquad (2.32)$$

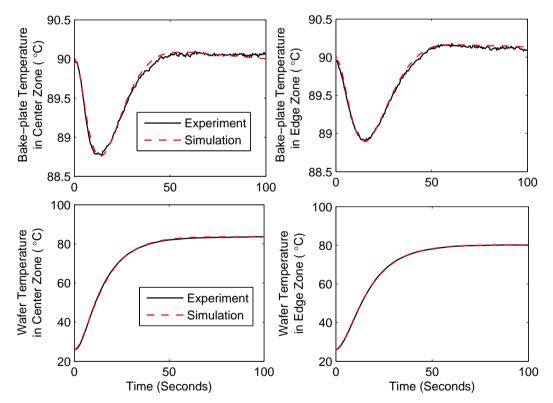

To assess the quality of the proposed system model, we perform conventional baking process experiment and compare the simulation with the experimental results. The programmable thermal system can be configured up to 13 zones. Without loss of generality, we will verify the system dynamics for a two-radial-zone system. Our objective is to demonstrate that the proposed model succeeds in predicting the experimental wafer temperatures using bake-plate temperature data and the input signal without resorting to the use of any fitting parameter and is therefore useful for scaling up.

In the experiment, a room temperature flat 200mm wafer is dropped on the baking system with proximity pin height of  $140\mu$ m. This causes the bake-plate temperature drop at first but recovers gradually because of closed-loop control. Two proportional-integral (PI) controllers are used to control the two zones of the bake-plate. Figure 2.4 shows the comparison result of the simulation and experimental bake-plate and wafer temperature when the air-gap thickness is  $140\mu$ m.

Figure 2.4. Plate and wafer temperature in simulation and experiment with air-gap thickness be  $140\mu m$  using the calculated model.

It can be seen that the fit between of both the wafer and the bake-plate tem-

perature from simulation and experimental results are very closed, which verify the effectiveness of the proposed thermal model. This result demonstrates that by monitoring the bake-plate temperatures,  $T_p$ , and making use of system identification techniques, we are able to extract the air-gap information,  $z_a$ , between *ith* wafer and bake-plate elements from the system model. Then we will be able to calculate the wafer temperature and fulfill real-time control experiment to minimize the wafer temperature nonuniformity in the baking process.

## 2.3 Experimental Result

### 2.3.1 Experimental Setup

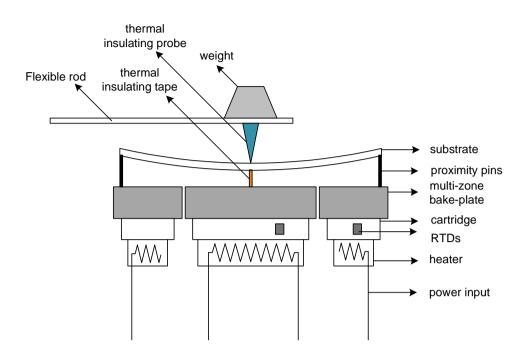

For experimental verification, warpage must be known. Wafer warpage is created mechanically as shown in Figure 3.2. We ensure minimal warpage during the baking experiment by mechanically pressing the center of the wafer against a thermal insulating tape of known thickness. The center-to-edge warpage is given by the difference between height of proximity pin and thermal tape thickness.

To guarantee the temperature accuracy in experiment, the temperature sensors (RTDs) are calibrated using a constant temperature heat bath NESLAB EX251HT. Measurements are taken from a range of temperatures between 25°C and 95°C and at intervals of 5°C. At every temperature interval, 50 readings are recorded for each of the sensors. An average value is then calculated for that sensor and that particular temperature. For temperatures below 150°C, RTDs show strong linearity in the resistance-temperature relationship. Hence, a linear equation can be written as follows:

$$Y_T = \alpha T + \beta \tag{2.33}$$

where  $Y_T$  is the averaged temperature reading at temperature T,  $\alpha$  and  $\beta$  are the coefficients to be determined. Least Squares Linear Regression can be used to calculate the coefficients  $\alpha$  and  $\beta$ . Let

$$\theta = \begin{bmatrix} \alpha \\ \beta \end{bmatrix}, \Phi = \begin{bmatrix} T_1 & 1 \\ T_2 & 1 \\ \vdots & \vdots \\ T_2 & 1 \end{bmatrix} and Y = \begin{bmatrix} Y_{T_1} \\ Y_{T_2} \\ \vdots \\ Y_{T_n} \end{bmatrix}$$

Hence,  $\theta$  can be found by

$$\theta = (\Phi^T \Phi)^{-1} \Phi^T Y \tag{2.34}$$

Obtaining  $\alpha$  and  $\beta$  and using backward calculation

$$T = \frac{1}{\alpha}Y - \frac{\beta}{\alpha} \tag{2.35}$$

we can get the calibrated temperature from RTDs measurement.

The RTDs are attached to the wafer [33], [37] for temperature measurement. A control-system software was developed using the National Instruments LabView programming environment [55] to create a multivariable PI control framework and a dynamic temperature control system. Two PI controllers of the following form are used to control the two zones of the bake-plate:

$$u(t) = K_{ci}\left(e(t) + \frac{1}{T_{Ii}}\int e(t)dt\right)$$

(2.36)

where u(t) is the heating power injected in to the heater and e(t) is the error between the desired and actual bake-plate temperatures. The experiments were conducted at a temperature setpoint of 90°C with a sampling and control interval of 0.2 seconds.

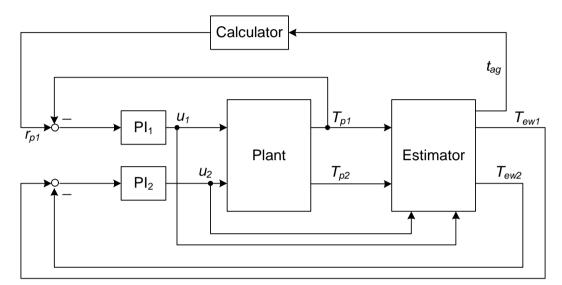

### 2.3.2 Control Structure

The proposed approach required detailed information of the system in order to identify the average air-gap during subsequent processing. We have got accurate state-space model in section 2.2. Based on the model, we can develop a greybox state-space model with the air-gap thickness of the two zones as unknowns. In the experiment, the bake-plate temperature readings and input control signals are collected and fitted into the model to extract the air-gap thickness and wafer temperature.

Figure 2.5 shows the control systems framework, the bake-plate temperature,  $T_{p1}$  and  $T_{p2}$ , and the control signal,  $u_1$  and  $u_2$ , in the two zones system are measured and sent to the estimator. The grey-box-model-based estimator will then estimate the air-gap thickness and the wafer temperature of the two zones. The estimated air-gap thickness  $t_{ag}$  is then used to determine the set point  $r_{p1}$  of the bake-plate and the estimated wafer temperatures  $T_{ew1}$  and  $T_{ew2}$  are used to control the wafer temperature uniformity in the process.

Figure 2.5. Block diagram of control structure.

Using this method, we can real-time estimate the air-gap thickness and wafer temperature and consequently regulate the control signal on-line to achieve desired wafer temperature and minimize temperature nonuniformity in the whole process. Furthermore, with the estimated air-gap thickness in steady-state, we can extract the wafer warpage profile.

### 2.3.3 Experimental Result

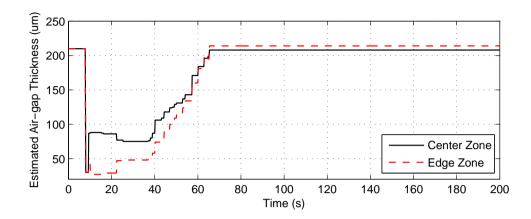

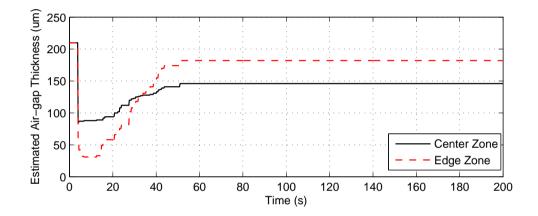

To demonstrate our approach, a flat wafer is firstly dropped on the bake-plate with a proximity pin height of  $210\mu$ m. Figure 2.6 shows the estimated air-gap thickness with real-time control method. The final estimated air-gaps are tabulated in Table 2.2. A good measure of extent warpage is to measure the deviation of the average air-gap from the proximity pin height. For the flat wafer, we can see that deviations are close to zero as expected.

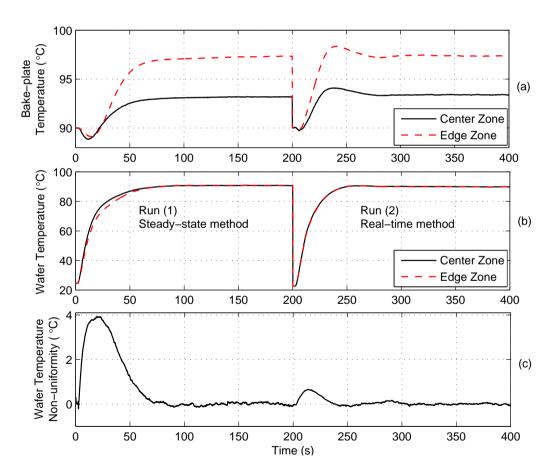

Figure 2.7 shows the bake-plate and wafer temperature profiles using the steadystate temperature control method [47] and the proposed real-time control method. To validate our results, two temperature sensors (in this case RTDs) are embedded on the wafer surface corresponding to the center of each zone to monitor the wafer temperature. Figure 2.7 consists of two experimental runs, (1) and (2). Run (1)corresponds to the steady-state control approach when the wafer is dropped on the bake-plate. The air-gaps are first estimated based on the maximum bakeplate temperature drops. Then the new bake-plate temperature are set based on the estimated air-gap thickness as shown in Figure 2.7(a). Notice that the wafer temperature is controlled 90°C with a steady-state temperature nonuniformity of about  $0.1^{\circ}$ C as shown in Figure 2.7(b) and (c) .However, since the new bakeplate temperature set-points are implemented about 20 seconds after the wafer is dropped to allow the maximum temperature drop point to occur as well as for computational delay of the corresponding air-gap, the wafer can only reach steadystate after about 80 seconds as shown in Figure 2.7(b). Furthermore, the wafer has a temperature nonuniformity of about 4°C in transient period as shown in Figure 2.7(c).

Next, real-time control of the wafer temperature is implemented. Figure 2.7(b) and (c) of run (2) shows that the wafer temperature is controlled to 90°C within

Figure 2.6. Estimated air-gap thickness using real-time control method when a flat wafer is dropped on bake-plate with proximity pin height of  $210\mu$ m.

Figure 2.7. Temperature profile of bake-plate and wafer when a flat wafer is dropped on bake-plate with proximity pin height  $210\mu$ m. The bake-plate temperatures, wafer temperatures and wafer temperature non-uniformity during the baking process are shown in subplots (a), (b) and (c) respectively.

50 seconds with the maximum temperature nonuniformity less than 1°C during the transient and steady-state temperature nonuniformity less than 0.1°C. The corresponding maximum temperature nonuniformity and root mean square (RMS) error during the thermal processing for experimental runs (1) and (2) are also shown in Table 2.3. It can be seen that the temperature nonuniformity RMS in the heating process is decreased form 1.4806°C to 0.1842°C, an improvement of over 80%.

Figure 2.8. Estimated air-gap thickness using real-time control method when a wafer with center-to-edge warpage of  $70\mu$ m is dropped on bake-plate with proximity pin height of  $210\mu$ m.

The feasibility of the approach is further demonstrated by heating warped wafer. Firstly, the wafer with center-to-edge warpage of  $70\mu$ m is dropped on the same bake-plate with the proximity pin height of  $210\mu$ m. Wafer warpage is created mechanically as shown in Figure 2.2. The corresponding estimated air-gap thickness is plotted in Figure 2.8 and tabulated in Table 2.2. Based on the final estimated air-gap thickness together with the proximity pin height, the profile of the wafer can be obtained by extrapolation as shown in Figure 2.12. An estimated warpage of  $72\mu$ m from center-to-edge for the warped wafer is obtained which is close to the known warpage of  $70\mu m$ .

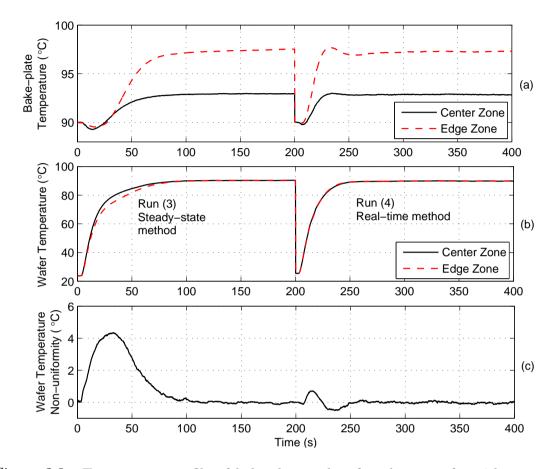

Figure 2.9. Temperature profile of bake-plate and wafer when a wafer with centerto-edge warpage of  $70\mu$ m is dropped on bake-plate with proximity pin height of  $210\mu$ m. The bake-plate temperatures, wafer temperatures and wafer temperature non-uniformity during the baking process are shown in subplots (a), (b) and (c) respectively.

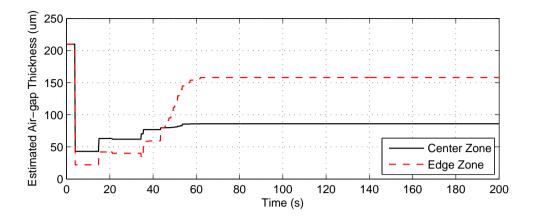

The temperature results using the steady-state and real-time control methods are tabulated in Table 2.3 and shown in Figure 2.9 experimental run (3) and run (4). It can be seen that for the warped wafer, using the real-time control method, wafer temperature can reach the steady-state temperature within 50 seconds, with a maximum temperature nonuniformity less than 1°C during the transient and steady-state temperature nonuniformity less than 0.1°C.

Then, the wafer with center-to-edge warpage of  $140\mu m$  is dropped on the same

Figure 2.10. Estimated air-gap thickness using real-time control method when a wafer with center-to-edge warpage of  $140\mu$ m is dropped on bake-plate with proximity pin height of  $210\mu$ m.

Figure 2.11. Temperature profile of bake-plate and wafer when a wafer with center-toedge warpage of  $140\mu$ m is dropped on bake-plate with proximity pin height of  $210\mu$ m. The bake-plate temperatures, wafer temperatures and wafer temperature non-uniformity during the baking process are shown in subplots (a), (b) and (c) respectively.

|              |       | Estimated air-gap |                | Deviation from pin |                | Estimated      |

|--------------|-------|-------------------|----------------|--------------------|----------------|----------------|

| Wafer        | Expt. | center zone       | edge zone      | center zone        | edge zone      | warpage        |

|              | run   | $(\mu m)$         | $(\mu { m m})$ | $(\mu m)$          | $(\mu { m m})$ | $(\mu { m m})$ |

| Flat         | (2)   | 208               | 214            | 2                  | 4              | 4              |

| wafer        | (2)   | 200               | 214            | Δ.                 | 4              | 4              |

| $70 \ \mu m$ | (4)   | 146               | 182            | -64                | -28            | 72             |

| warpage      | (4)   | 140               | 102            | -04                | -20            | 12             |

| $140 \mu m$  | (6)   | 86                | 158            | -124               | -52            | 144            |

| warpage      | (0)   |                   | 100            | -124               | -52            | 144            |

Table 2.2. Estimated air-gap thickness and wafer warpage using the real-time control method with the proximity pin height of  $210\mu$ m

Table 2.3. Maximum temperature nonuniformity and root mean square (RMS) error during the thermal processing using the steady-state and real-time control method.

| Wafer        | Method       | Expt. | Maximum            | Nonuniformity |

|--------------|--------------|-------|--------------------|---------------|

|              |              | run   | nonuniformity (°C) | RMS (°C)      |

| Flat         | Steady-state | (1)   | 3.92               | 1.48          |

| wafer        | Real-time    | (2)   | 0.66               | 0.18          |

| $70 \ \mu m$ | Steady-state | (3)   | 4.35               | 1.78          |

| warpage      | Real-time    | (4)   | 0.71               | 0.19          |

| $140 \mu m$  | Steady-state | (5)   | 4.68               | 1.62          |

| warpage      | Real-time    | (6)   | 1.07               | 0.29          |

bake-plate with the proximity pin height of  $210\mu$ m to verify the effectiveness of the method in detecting different warped wafer. The estimated air-gap thickness is plotted in Figure 2.10 and tabulated in Table 2.2 and the extracted wafer profile is also shown in Figure 2.12. An estimated warpage is  $144\mu$ m from center-to-edge which is also close to the known warpage of  $140\mu$ m.

The corresponding temperature results are tabulated in Table 2.3 and shown in Figure 2.11 experimental run (5) and run (6). As expected, using the realtime control method, the  $140\mu$ m warped wafer can also reach the steady-state

Figure 2.12. Estimated profile of the warped wafers with center-to-edge warpage of  $70\mu$ m and  $140\mu$ m based on experimental run (4) and (6) respectively.

temperature within 50 seconds, with much better temperature uniformity than steady-state control method.

# 2.4 Conclusion

In this chapter, we have demonstrated an in-situ approach to real-time detect wafer warpage and control of the wafer temperature uniformity in baking process. Wafer temperature uniformity in transient period has been improved greatly compared to the previous steady-state method. With the proposed approach, the wafer spatial temperature uniformity in the whole baking process achieved an improvement of more than 80% when compared to the existing steady-state control method. The proposed approach can also be scaled up for larger wafers by increasing the number of sensors, actuators, and controllers.

# Chapter 3

# Programmable Integrated Bake/Chill System

# 3.1 Introduction

In Chapter 2, we have proposed an in-situ approach to real-time detect wafer warpage and wafer temperature by monitoring the bake-plate temperature in baking process. We also demonstrated experimentally that the wafer transient temperature uniformity can be improved greatly using the proposed control method. However, in conventional resist processing, after the baking step, the wafer will then be mechanically moved to a fixed temperature chill-plate where it is cooled to a temperature between 18°C and 30°C [33] as shown in Figure 3.1. Thus, the uncontrolled and non-uniform temperature fluctuation during the mechanical transfer of the substrates from the bake to chill plates will result in spatial temperature non-uniformities during the entire thermal cycle [13], [38]. Moreover, constrained by the inherent sluggish dynamic response of the conventional bake-plate, the wafer temperature response is not fast enough in the transient period.

Figure 3.1. The conventional approach for lithography baking and chilling involves substrate transfer between large thermal mass, fixed temperature plates [38].

To deal with the problems, in this chapter, we propose an integrated bake/chill system to provide fast dynamic response and achieve spatial temperature uniformity of a silicon wafer throughout the entire processing temperature cycle of ramp, hold and quench. In the proposed system, a set of thermoelectric devices is employed to provide spatial and temporal temperature uniformity control. The TEDs sit on the surface of a heat sink and together forming an active cooling system so that we completely eliminate substrate movement and the attendant temperature uncontrollability between the baking and chilling processes.

In this work, a mathematical model of the system is developed via detailed modeling and simulations based on first principle heat transfer analysis to ascertain the performance of the proposed design. To improve the temperature uniformity in the process, we propose a model based control method using the dynamic model identified the by injecting two independent pseudo-random-binary sequence (PRBS) to the system.

This chapter is organized as follows. In Section 3.2, the proposed integrated bake/chill thermal processing system is illustrated. The thermal modeling of the system is presented in Section 3.3 and the effectiveness of the model is verified in Section 3.4. In Section 3.5, the model-based controller is designed to achieve temperature uniformity in the thermal process. Experimental results are given in Section 3.6 to demonstrate the effectiveness of the proposed method. Finally, conclusions are given in Section 3.7.

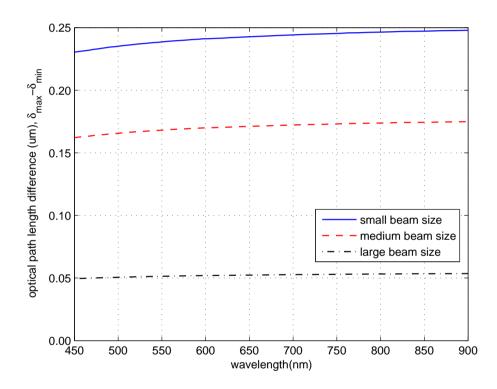

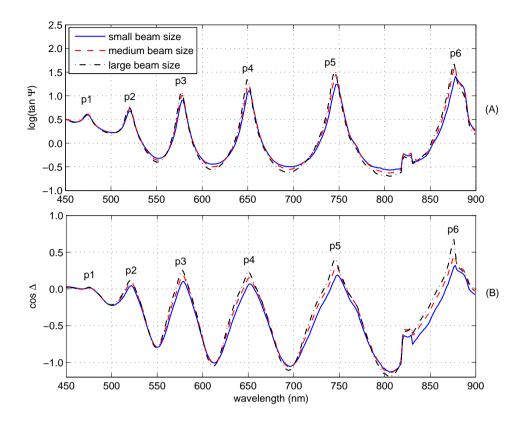

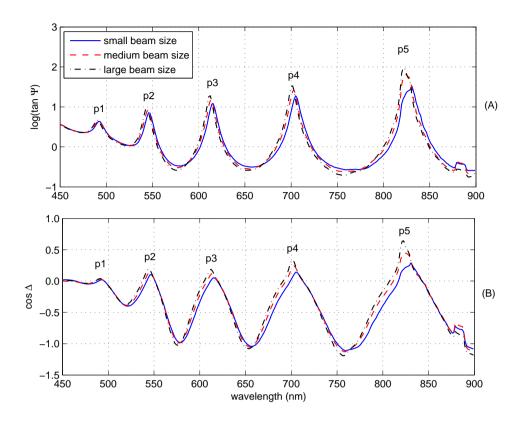

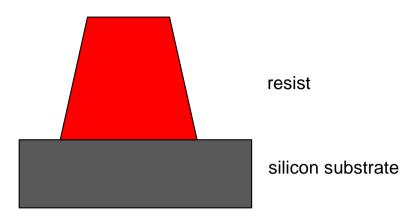

### 3.2 Proposed Thermal Processing Model