### A GENERAL FRAMEWORK TO REALIZE AN ABSTRACT MACHINE AS AN ILP PROCESSOR WITH APPLICATION TO JAVA

#### WANG HAI CHEN

(B. Eng. (Hons.), NWPU) (M.Sci., NUS)

#### A THESIS SUBMITTED

# FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

DEPARTMENT OF COMPUTER SCIENCE

NATIONAL UNIVERSITY OF SINGAPORE

2006

## **Acknowledgments**

My heartfelt gratitude goes to my supervisor, Professor Chung Kwong YUEN, for his insightful guidance and patient encouragement through all my years at NUS. His broad and profound knowledge and his modest and kind personal characters influenced me deeply.

I am deeply grateful to the members of the Computer System Lab, A/P Dr. Weng Fai WONG, and A/P Dr. Yong-Meng TEO, who provided me some good advices and suggestions. In particular, Dr. Weng Fai WONG in later period gave me some good suggestions which are useful to enhance my experiment results.

Appreciation also goes to the School of Computing at National University of Singapore that gave me a chance and provided me the resources for my study and research work. Thanks Soo Yuen Jien for his discussion on some of the stack simulator architecture design work. Also thank the labmates in Computer Systems Lab who gave me a lot of help in my study and life at NUS.

I am very grateful to my beloved wife, who supported and helped me in my study and life and stood by me in difficult times. I would also like to thank my parents, who supported and cared about me from a long distance. Their love is a great power in my life.

# **Table of Contents**

| Chapter 1                                                  | 1  |

|------------------------------------------------------------|----|

| Introduction                                               | 1  |

| 1.1 Motivation and Objectives                              | 2  |

| 1.2 Contributions                                          | 7  |

| 1.3 Organization                                           | 9  |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

| Chapter 2                                                  | 11 |

| Background Review                                          | 11 |

| 2.1 Abstract Machine                                       | 11 |

| 2.2 ILP                                                    | 12 |

| 2.2.1 Data Dependences                                     | 13 |

| 2.2.2 Name Dependences                                     | 14 |

| 2.2.3 Control Dependences                                  | 16 |

| 2.3 Register Renaming                                      | 17 |

| 2.4 Other Techniques to Increase ILP                       |    |

| 2.5 Alpha 21264 a Out-Of-Order Superscalar Processor       |    |

| 2.6 The Itanium Processor – a VLIW/EPIC In-Order Processor |    |

| 2.7 Executing Java Programs on Modern Processors           |    |

| 2.8 Increasing Java Processors' Performance                |    |

| 2.9 PicoJava a Real Java Processor                         | 34 |

|                                                            |    |

|                                                            |    |

|                                                            |    |

| Chapter 3                                                  | 37 |

| Implementing Tag-based Abstract Machine Translator in      |    |

| Register-based Processors                                  |    |

| 3.1 Design a TAMT                                          |    |

| 3.2 Design a TAMT Using Alpha Engine                       |    |

| 3.3 Design a TAMT Using Pentium Engine                     |    |

| 3.4 Discussion on Implementation Issues                    |    |

| 3.4.1 Implementing Issues using Alpha Engine               |    |

| 3.4.2 Implementing Issues Using Pentium Engine             |    |

| Cnapter 4                                               | 49         |

|---------------------------------------------------------|------------|

| Realizing a Tag-based Abstract Machine Translato        | r in Stack |

| Machines                                                |            |

| 4.1 Introduction                                        |            |

| 4.2 Stack Renaming Review                               |            |

| 4.3 Proposed Stack Renaming Scheme                      |            |

| 4.4 Implementation Framework                            |            |

| 4.4.1 Tag Reuse                                         |            |

| 4.4.2 Tag Spilling                                      | 59         |

| 4.5 Hardware Complexity                                 |            |

| 4.6 Stack Folding with Instruction Tagging              | 61         |

| 4.6.1 Introduction to Instruction Folding               | 61         |

| 4.6.2 Stack Folding Review                              | 65         |

| 4.7 Implementing Tag-based Stack Folding                | 71         |

| 4.8 Performance of Tag-based POC Scheme                 | 76         |

| 4.8.1 Experiments Setup                                 |            |

| 4.8.2 Performance Results                               | 77         |

| Chapter 5                                               | 80         |

| Exploiting Tag-based Abstract Machine Translator to Imp | olement a  |

| Java ILP Processor                                      | 80         |

| 5.1 Overview                                            | 80         |

| 5.2 The Proposed Java ILP Processor                     |            |

| 5.2.1 Instruction Fetch and Decode                      |            |

| 5.2.2 Instruction Issue and Schedule                    |            |

| 5.2.3 Instruction Execution and Commit                  |            |

| 5.2.4 Branch Prediction.                                |            |

| 5.3 Relevant Issues                                     |            |

| 5.3.1 Tag Retention Scheme                              |            |

| 5.3.2 Memory Load-Delay in VLIW In-Order Scheduling     |            |

| 5.3.3 Speculation-Support                               |            |

| 5.3.4 Speculation Implementation                        | 93         |

| Chapter 6                                             | 95                       |

|-------------------------------------------------------|--------------------------|

| Performance Evaluation                                |                          |

| 6.1 Experimental Methodology                          |                          |

| 6.1.1 Trace-driven Simulation                         |                          |

| 6.1.2 Java Bytecodes Trace Collection                 |                          |

| 6.1.3 Simulation Workloads                            |                          |

| 6.1.4 Performance Evaluation and Measurement          |                          |

| 6.2 Simulator Design and Implementation               | 98                       |

| 6.3 Performance Evaluation                            |                          |

| 6.3.1 Exploitable Instruction-Level-Parallelism (ILP) | 101                      |

| 6.3.2 ILP Speedup Gain                                |                          |

| 6.3.3 Overall Performance Enhancement                 | 106                      |

| 6.3.4 Performance Effects with Tag Retention          |                          |

| 6.3.5 Performance Enhancement with Speculation        |                          |

| 6.4 Summary of the Performance Evaluation             |                          |

| Chapter 7                                             | 117                      |

| •                                                     |                          |

| Tolerating Memory Load Delay                          |                          |

| 7.1 Performance Problem in In-Order Execution Model   |                          |

| 7.2 Out-of-Order Execution Model                      |                          |

| 7.3 VLIW/EPIC In-Order Execution Model                |                          |

| 7.3.1 PFU Scheme                                      |                          |

| 7.4 Tag-PFU Scheme                                    |                          |

| 7.4.1 Architectural Mechanism                         |                          |

| 7.4.2 Architectural Comparison                        |                          |

| 7.5.1 Experimental Methodology                        | 1 4 /                    |

| 7.5.2 Performance Results                             |                          |

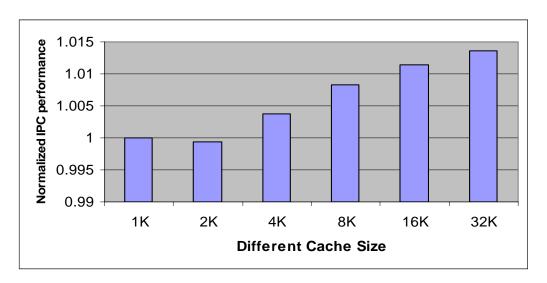

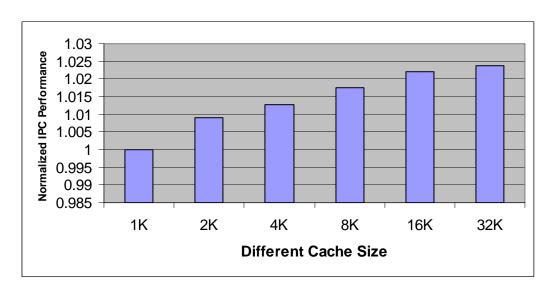

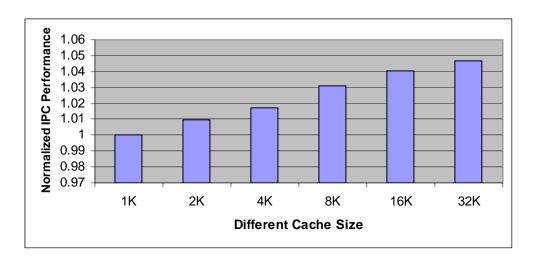

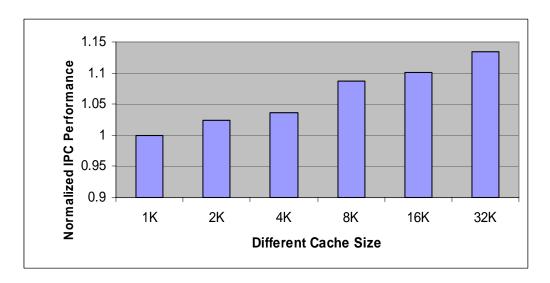

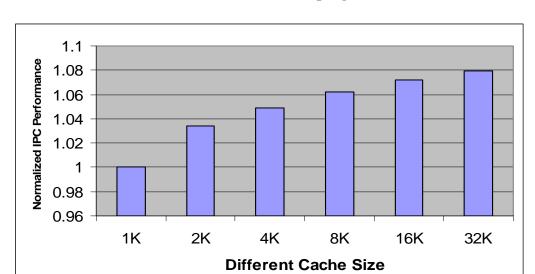

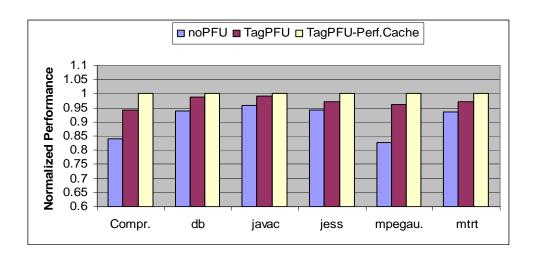

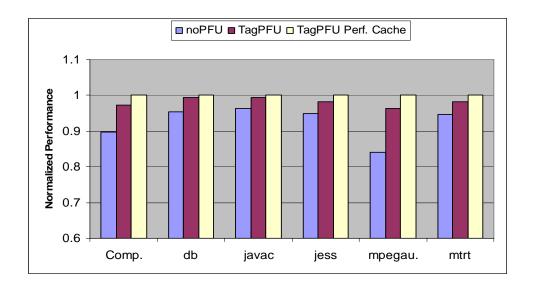

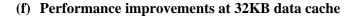

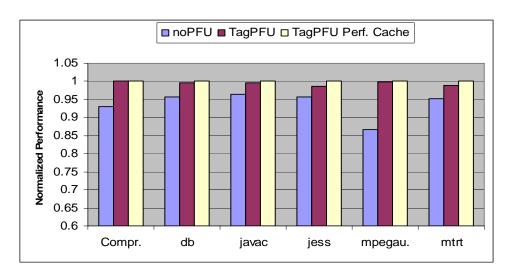

| 7.5.2.1 IPC Performance with Different Cache Size     | 127                      |

|                                                       | 127<br>128               |

|                                                       | 127<br>128<br>129        |

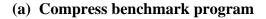

| 7.5.2.2 Cache Miss Rate vs. Cache Size                | 127<br>128<br>129<br>132 |

|                                                       | 127<br>128<br>129<br>132 |

| Chapter 8                                        | 142 |

|--------------------------------------------------|-----|

| Conclusions                                      |     |

| 8.1 Conclusions                                  |     |

| 8.2 Future Work                                  | 145 |

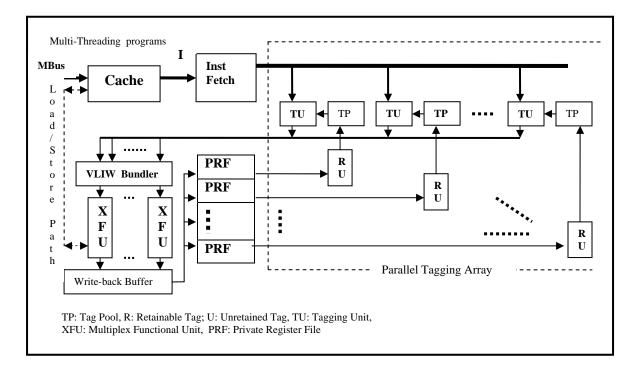

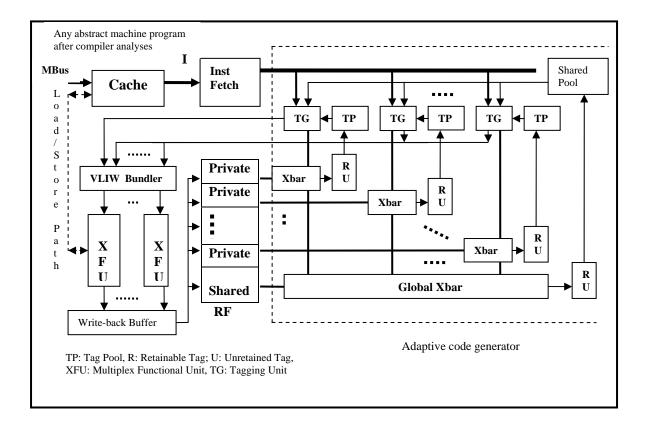

| 8.2.1 SMT Architectural Support                  | 145 |

| 8.2.2 Scalability in Tag-based VLIW Architecture | 148 |

| 8.2.3 Issues of pipeline efficiency              | 149 |

|                                                  |     |

|                                                  |     |

|                                                  |     |

| Bibliography                                     | 153 |

## **Summary**

Abstract machines bridge the gap between a programming language and real machines. This thesis proposes a general purpose tagged execution framework that may be used to construct a processor. The processor may accept code written in any (abstract or real) machine instruction set, and produce tagged machine code after data conflicts are resolved. This requires the construction of a tagging unit, which emulates the sequential execution of the program using tags rather than actual values. The tagged instructions are then sent to an execution engine that maps tags to values as they become available and sends ready-to-execute instructions to arithmetic units. The process of mapping tag to value may be performed using Tomasulo scheme, or a register scheme with the result of instructions going to registers specified by their destination tags, and waiting instructions receiving operands from registers specified by their source tags.

The tagged execution framework is suitable for any instruction architecture from RISC machines to stack machines. In this thesis, we demonstrate a detailed design and implementation with a Java ILP processor using a VLIW execution engine as an example. The processor uses instruction-tagging and stack-folding to generate the tagged register-based instructions. When the tagged instructions are ready, they are bundled depending on data availability (i.e., out of order) to form VLIW-like instruction words and issued in-order. The tag-based mechanism accommodates memory load delays as instructions are scheduled for execution only after operands are available to allow tags to be matched to values with less added complexity. The detailed performance simulations related to cache memory are conducted and the results indict that the tag-based mechanism can mitigate the effects of memory load access delay.

## **List of Tables**

| 3.1. A sample of RISC instructions renaming process                | 40  |

|--------------------------------------------------------------------|-----|

| 3.2. The tag-based RISC-like instruction format                    | 41  |

| 3.3. A sample of tag-based renaming for Alpha processor            | 43  |

| 3.4. A sample of tag-based renaming for Pentium processor          | 44  |

| 4.1. A sample of stack renaming scheme                             | 53  |

| 4.2. A sample of stack renaming scheme with tag-based instructions | 55  |

| 4.3. Bytecode folding example                                      | 64  |

| 4.4. Instruction types in picoJava                                 | 66  |

| 4.5. Instruction types in POC method                               | 67  |

| 4.6. Advanced POC instruction types                                | 69  |

| 4.7. Instruction folding patterns and occurrences in APOC          | 69  |

| 4.8. Instruction types in OPE algorithm.                           | 70  |

| 4.9. A sample for dependence information generation                | 72  |

| 4.10. Instruction type for POC folding model                       | 72  |

| 4.11. Description of the benchmark programs                        | 76  |

| 6.1. Input parameters in the simulator                             | 100 |

| 6.2. Percentage of instructions executed in parallel in our scheme | 102 |

| <u>6.3.</u> | Percentage of instructions executed in parallel using stack disambiguation 103 |

|-------------|--------------------------------------------------------------------------------|

| <u>6.4.</u> | Percentage of instructions executed in parallel with unlimited resources 105   |

| <u>6.5.</u> | Branch predictor effectiveness                                                 |

| 8.1.        | DSS simulation execution results                                               |

# **List of Figures**

| 1.1. The concept of general tagged execution framework                 | 2   |

|------------------------------------------------------------------------|-----|

| 2.1. Stages of the Alpha 21264 instruction pipeline                    | 22  |

| 2.2. Basic pipeline of the PicoJava-II                                 | 34  |

| 3.1. A conceptual tagged execution framework                           | 38  |

| 3.2. Common register renaming scheme in RISC processors                | 46  |

| 3.3. Tag-based renaming mechanism                                      | 46  |

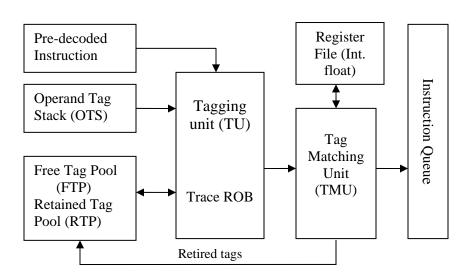

| 4.1. Architectural diagram for stack tagging scheme                    | 57  |

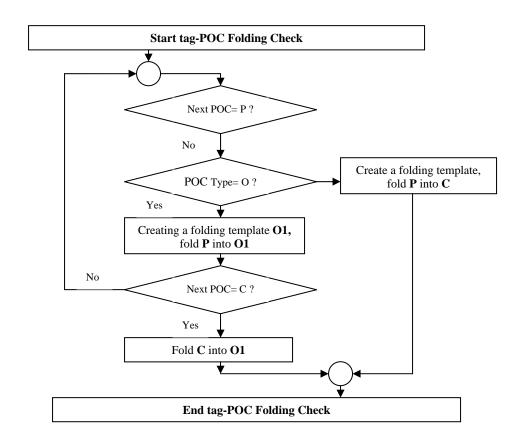

| 4.2. A sample of tag-POC instruction folding model                     | 73  |

| 4.3. The process of tag-POC instruction folding scheme                 | 74  |

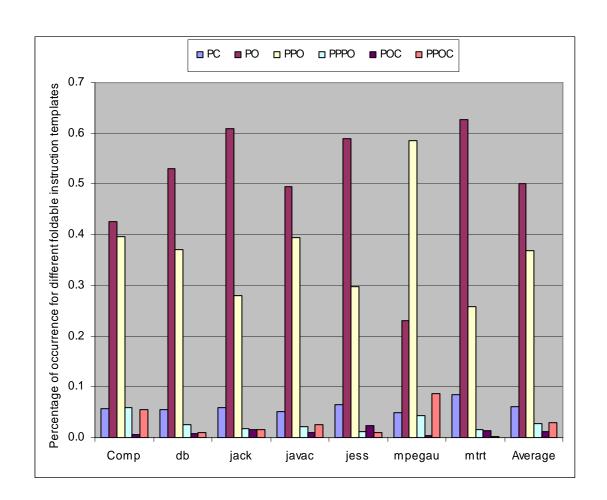

| 4.4. Percentage of different foldable templates occurred in benchmarks | 78  |

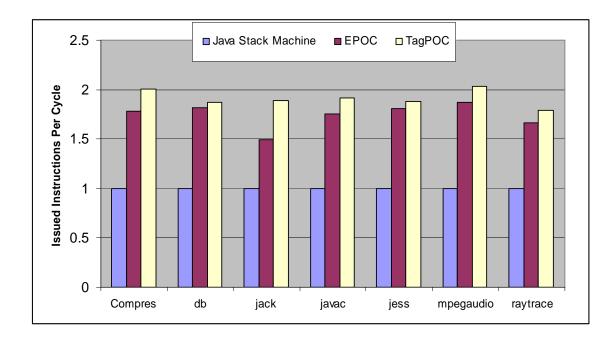

| 4.5. IIPC performance for stack folding                                | 79  |

| 5.1. The proposed Java ILP processor architecture                      | 81  |

| 6.1. Basic pipeline of TMSI Java processor                             | 99  |

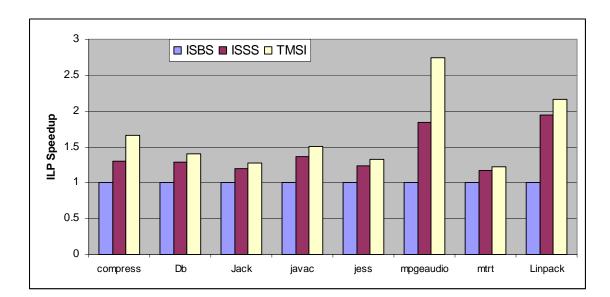

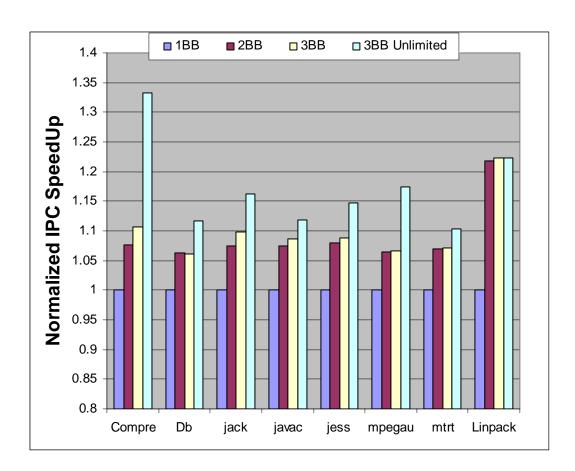

| 6.2. ILP speedup gain: TMSI vs. base Java stack machine                | 106 |

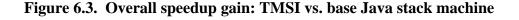

| 6.3. Overall speedup gain: TMSI vs. base Java stack machine            | 107 |

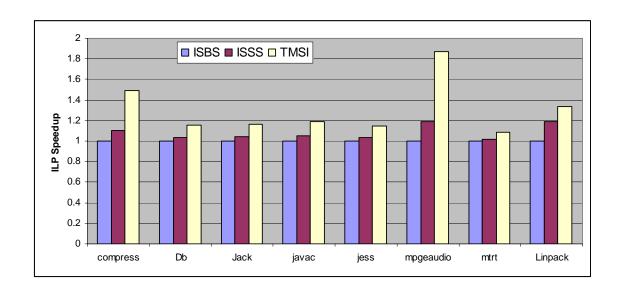

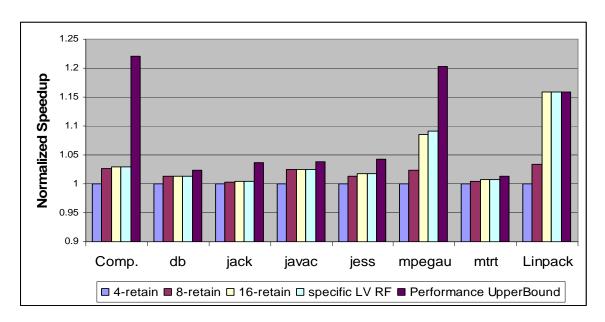

| 6.4. Normalized speedup with different amount of retainable tags       | 110 |

| 6.5. Normalized IPC speedup with speculation scheduling                | 112 |

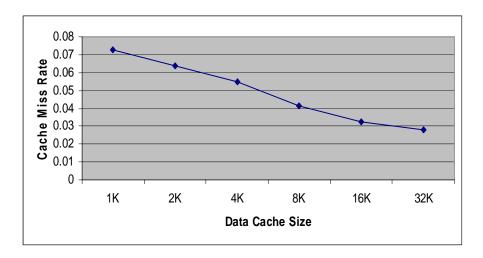

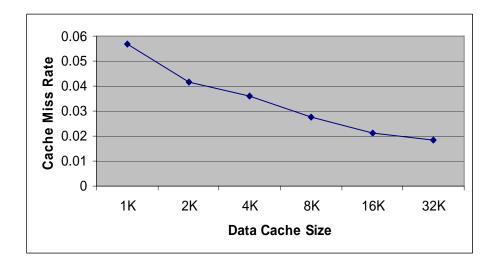

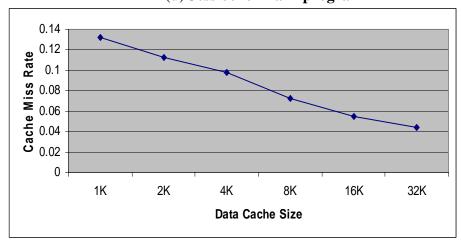

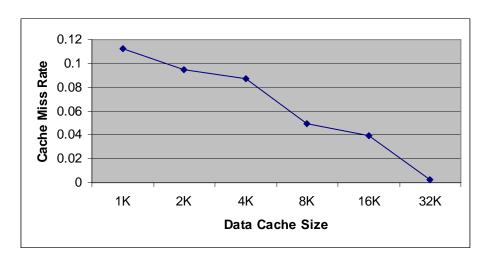

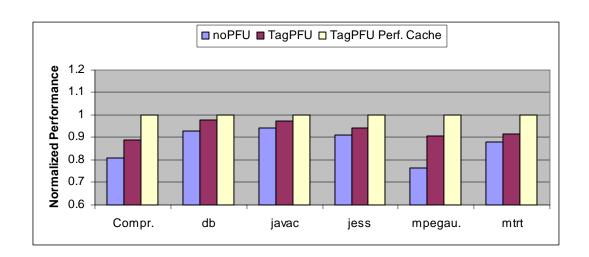

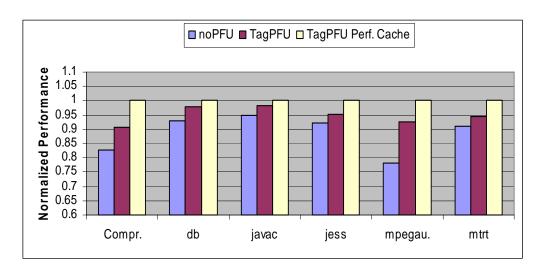

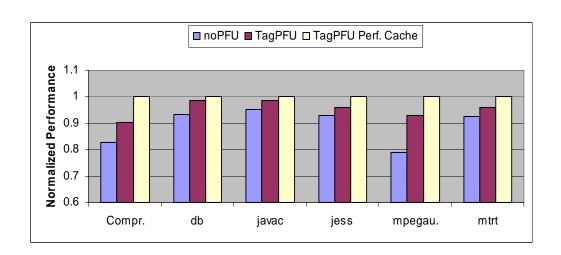

| 7.1. IPC performances with different cache sizes       | 129 |

|--------------------------------------------------------|-----|

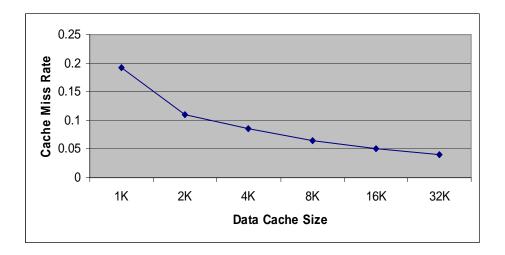

| 7.2. Cache miss rate vs. cache size                    | 133 |

| 7.3. IPC performances with different scheduling scheme | 137 |

| 8.1. The schematic for a SMT execution engine          | 147 |

| 8.2. The schematic for a dynamic VLIW execution engine | 149 |

## Chapter 1

## Introduction

Von Neumann stored-program computers work in instruction-stream driven or controlflow driven style, which is the dominating architecture in modern computer industry [95]. This computer architecture model comprises register-style machines, and stackstyle machines. Stack machines [77], which once enjoyed some commercial success (Burroughs 6700, HP3000, ICL2900), are no longer popular among computer architects.

All processors since about 1985 have been using pipelining to overlap the execution of instructions and improve performance. This potential overlap among instructions is called *instruction-level parallelism* (**ILP**). A pipeline acts like an assembly line with instructions being processed in phases as they pass down the pipeline. With simple pipelining, only one instruction is initiated into the pipeline at a time, but multiple instructions may be in some phases of execution concurrently. By issuing more than one instruction at a time into multiple pipelines, modern processors are able to achieve high performance with ILP supported.

#### 1.1 Motivation and Objectives

ILP is widely exploited in modern out-of-order processors. An out-of-order processor has the ability to execute instructions by utilizing its ILP potential and identifying dependences among instructions at run time, either through compiling grouping instructions into bundles of non-conflicting members, or through hardware register renaming that resolves data conflicts at execution time. The conventional out-of-order processors in general adopt a superscalar architecture (e.g. PowerPC, Alpha 21264, or MIPS R10000), whereas VLIW (e.g. IA64) processors discover ILP at the compiling stage.

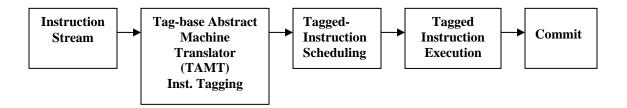

Figure 1.1. The concept of General Tagged Execution Framework (GTEF)

After investigating the architecture of many modern processors, we propose a conceptual framework for designing high performance pipelined processors, which exploits existent instruction-level-parallelism (ILP) execution components, namely superscalar or VLIW execution engines. This conceptual framework (Figure 1) is referred to as *General Tagged Execution Framework (GTEF)*, which is suited for

multiple computer architectures, whatever register-based or stack-based processors. The proposed framework is characterized by the concept of hardware abstract machine [4] that converts instructions for a particular abstract machine into a general tag-based instruction format.

The introduction of the concept of Abstract Machine makes GTEF scheme cater for multiple computer architectures. Abstract machines are commonly used to provide an intermediate language stage for compilation. They bridge the gap between the high-level of a programming language and the low-level of a real machine. They are abstract because they omit many details of real (hardware) machines [92]. Most common abstract machines are designed to support some underlying structures of a programming language, often using a stack, but it is also possible to define abstract machines with registers or other hardware components. An interpreter or translator is often used to convert abstract machine instructions to actual machine codes, and can be viewed as a kind of abstract machine pre-processor. A processor could be considered a concrete hardware implementation for an abstract machine that requires no pre-processor [92]. This can be a stack machine or a general-purpose RISC register machine.

In GTEF scheme, instructions of the machine are first converted by a predefined hardware pre-processor into tag-based instructions. The pre-processor (or a tagging unit) may be regarded as an "abstract machine" realized in simplified hardware that goes through a "mock execution" – execution with tags rather than values. In the

process of "mock execution", there is no actual execution which inputs values into arithmetic pipeline to produce output values, and only tags are removed from stack/registers and new tags representing results are put onto stack/registers. The tagging unit processes the instruction stream sequentially, but much faster than actual sequential execution; because it uses tags only, it can keep up with parallel execution that will take place later when tags have been mapped into values.

In GTEF scheme, the tag-based abstract machine translator (TAMT) is a critical component, which converts any abstract or real machine programs into tag-based instructions for ILP execution, including one or more stages preceding the execution stage that can be implemented in either hardware or software. Almost all modern processors have mechanisms to achieve ILP, either through grouping instructions into bundles of non-conflicting members with compiler support, or through the hardware register renaming (tagging) technique that resolves data conflicts at execution time (and register renaming enables out of order execution more effective.)

The hardware renaming/tagging scheme is specifically designed for different CPUs. For multi-issue superscalar machines that employ Tomasulo [85] scheme (e.g. PowerPC, Alpha), a hardware TAMT would be implemented at the tagging and scheduling stage and a superscalar execution engine would be exploited at execution stage; For VLIW machines (e.g. IA64), a similar conversion would be performed with limited scheduling

by hardware at tagging and schedule stages, and a VLIW execution engine to process bundled instructions will be at the instruction execution stage.

The objective of the thesis is to investigate and demonstrate the applicability of the proposed framework. In the thesis we will introduce with GTEF framework, how to design the special-purposed TAMT for different processors including general-purpose register-based processors (RISC or CISC machines) and stack-based processors. In register-based processors, the TAMT will exploit register renaming techniques to implement an instruction mapping from registers to tags, but to fulfill the instruction tagging a "mock" execution technique using tags will be used. In stack machines, the TAMT will simulate the behavior of a virtual stack machine with tags, and translate stack instructions into tag-based RISC-like instructions, then to use existent ILP execution components which may be superscalar or VLIW execution engine to achieve high performance.

For stack machines, a prominent problem was believed to be the presence of a single architectural bottleneck – stack is viewed as a significant performance obstacle in the dynamic extraction of instruction level parallelism (ILP). That is, with instructions taking operands from the top of the stack and leaving results there, stack programs appear to have a high level of data dependency, and with instructions displaying no source and destination register references (even though the source and destination reference are hidden in stack locations), data dependency relations are supposed to be

difficult to analyze. Under GTEF scheme, we proposed a novel bytecode instruction tagging-scheme. The proposed scheme solves the problem of stack bottleneck in stack machines, and in Java processors. In addition, our proposed Java ILP processor is able to extract more ILP in Java programs, and support out-of-order execution.

We demonstrate how the GTEF scheme works on a stack machine by using a Java processor as an example. In the thesis, the GTEF Framework is applied to design the Java processor which adopts a pipelined architecture. It is essential to create a real TAMT in order to implement a Java processor using GTEF scheme. The TAMT to be used is a hardware "abstract" machine that "mock" executes Java bytecodes with assigning each bytecode instruction a tag, and analyzing the data dependency of the instructions to enable hardware scheduling of execution. The design and implementation of the tagging unit and the Java ILP processor will be discussed in Chapter 4 and 5 respectively.

Now we look at how to apply the GTEF scheme extensively. To fulfill a detailed implementation of a processor, some related issues need to be solved. The first is how to attach available data to the tagged instructions. The attachment can be implemented through the use of real registers that correspond to tags, or through a matching mechanism like the Tomasulo machine. The second is how to schedule the executable instructions and send them to arithmetic units. This can be through multiple synchronized pipes like VLIW, or through individually activating them as in Tomasolu

machines from reservation stations [85] next to the arithmetic units. The third is that if the output of load units and arithmetic units are not buffered using real registers with one register per tag, whether there is need for something like a reorder buffer with locations that may be shared by different tagged data at different times, in order to guarantee that the data that become available before instructions are ready to use, have somewhere to go. The fourth is, since a stack machine with operands used once only, how to retain a repeatedly needed value. The solutions to above mentioned issues will be discussed in Chapter 3, 4 and 5.

#### 1.2 Contributions

The thesis has done extensive research on computer architecture and ILP techniques. To explore the applicability of the proposed GTEF scheme, several state-of-the-art out-of-order processors are investigated, such as MIPS R10000 [43], Alpha 21264 [81], and Pentium [24] processor based on x86 architecture. Stack machines have their special features. Since stack is often viewed as the bottleneck to support ILP in stack machines. To solve this problem, we conducted an extensive investigation on stack machine architecture, and using a Java ILP processor as an example. The proposed Java ILP processor exploits a novel stack renaming (or tagging) scheme to overcome the issue of stack bottleneck and be able to expose more ILP within stack programs. In addition, the relevant issues are discussed.

The thesis has the following contributions:

- A novel general processor design framework is proposed. The novelty lies in that it can be used to build a new processor by exploiting existent ILP hardware components and suitable for multiple processor architectures, register-based or stack-based. In this framework, the concept of tag-based abstract machine translator (TAMT) is introduced.

- A stack instruction tagging scheme is proposed to implement stack renaming in stack machines, overcome the stack bottleneck and expose more ILP. After stack instruction tagging, stack dependencies are converted to tag-based data dependencies. One of the advanced ILP techniques – dataflow -- may be exploited to extract ILP in stack programs.

- Stack instruction folding, an efficient technique to reduce stack instruction dependencies in Java processors, is investigated in the thesis. To integrate instruction folding into the proposed Java ILP processor, we proposed a new tag-based POC (Producer-Operator-Consumer) approach which combines POC [50] scheme with stack instruction tagging and can fold almost all bytecode instruction sequence with simple hardware support.

- To apply the GTEF scheme, we designed and implemented a Java ILP processor in which the proposed stack instruction tagging technique is exploited and a VLIW execution engine is used to execute tag-based instructions. Using a VLIW execution engine causes a simpler hardware architecture than using a Superscalar execution engine. Such related issues as instruction schedule, tag management, branch prediction, and speculation support are investigated.

- A trace-driven architectural simulator to model the proposed Java processor architecture was developed. The simulation experiments demonstrate that the proposed Java ILP processor can extract most ILP, and out-of-order execution technique can be exploited to achieve high performance.

- An alternative method called Tag-PFU, to PFU scheme [55] was proposed to tolerate unpredictable memory load delay in VLIW processors. The Tag-PFU scheme realizes the same function as PFU but with tag-based mechanism to accommodate the effects of unpredicted memory load delay. The proposed scheme is more productive and simpler than the previous PFU [55] scheme.

#### 1.3 Organization

The rest of the thesis is organized as follows. Chapter 2 gives a brief review on abstract machine, ILP techniques, and related works in Java processor and Java technologies including software / hardware scheme, and stack folding, etc. Chapter 3 describes how to apply the GTEF scheme to design new processor architecture by exploiting existing superscalar execution engines, such as Alpha execution engine and Pentium x86 execution engine. Chapter 4 describes how to implement a hardware TAMT in stack machines by using a stack renaming mechanism. Also, a new stack folding scheme is elaborated which combines stack instruction tagging with stack folding technique and a detailed review of stack folding technique is given. Chapter 5 designed and implemented a Java ILP processor by exploiting the TAMT designed in Chapter 4. The

performance evaluation of the Java ILP processor is presented in Chapter 6. Chapter 7 proposes a suspending Instruction buffer (SIB) scheme to solve the memory load delay problem in the proposed Java ILP processor, and cache performance simulation results are given. Chapter 8 gives the concluding remarks of the research work as well as the recommendations for future work.

# Chapter 2 Background Review

In this chapter, we will conduct a detailed review of the related techniques to our researches in the thesis, which are abstract machine, ILP, register renaming, etc. We also investigated latest Java-related technologies, e.g. stack folding [28], JIT [1, 6, 15], binary translation [46], multi-threading [82] and some developed Java processors. These techniques have been proposed and implemented by many researchers. After reviewing them, we will get to know a basic research background on microprocessor and Java technology.

#### 2.1 Abstract Machine

Abstract Machines are widely used to implement software compilers. Abstract machines provide an intermediate target language for compilation. First, a compiler generates code for the abstract machine, then this code can be further compiled into real machine code or it can be interpreted. By dividing compilation into two stages, abstract machines increase the portability and maintainability of compilers.

A processor could be considered a concrete hardware realization for an abstract machine that defines the processor's instruction set architecture. This can be a stack machine or a general-purpose RISC processor. From the early 1970s to the late 1980s, since it was believed that efficient implement of symbolic languages would require special-purpose hardware, several special hardware implementation were undertaken [92]. However, with the rapid development of conventional computer hardware, and advances in compiler and program analysis technology, such as special-purpose hardware was no longer to be built due to their very expensive price. Typical such processors are Burroughs B5000 processor – a stack machine architecture, which has hardware support for efficient stack manipulation; the Pascal Micro-engine Computer [103] for the use of UCSD P-code abstract machine; the Transputer [30], a specialpurpose microprocessor for the execution of Occam, and some Java processors (picoJava-I, picoJava-II [28, 39]) which directly execute Java bytecode based on Java Virtual Machine, etc. Recently due to its platform independence, compact code size, object-oriented nature and security, Java programming language [104], a static-typed class-based object-oriented language, is widely used from embedded system to high end servers.

#### **2.2 ILP**

Instruction-level parallelism (ILP) [22] in the form of pipelining has been around for decades, with systems exploiting ILP dynamically using hardware to locate the parallelism, or using compiler techniques. The amount of parallelism available within a

basic-block is usually quite small. Here a basic block means a contiguous block of instructions, with a single entry point and a single exit point [5]. To obtain substantial performance enhancements, we must exploit ILP across multiple basic blocks.

To achieve ILP we must determine which instructions can be executed in parallel, and determine how much parallelism exists in a program and how that parallelism can be exploited. The key point is to see how one instruction depends on another. Thus we need to discuss dependences and data hazards. There are three different types of dependences in a program: data dependences, name dependences, and control dependences. In the following we will discuss them individually.

#### 2.2.1 Data Dependences

An instruction *j* is *data dependent* on instruction *i* if either of the following holds:

- $\triangleright$  Instruction i produces a result that may be used by instruction j, or

- $\blacktriangleright$  Instruction j is data dependent on instruction k, and instruction k is data dependent on instruction i.

The first condition states the *data dependence* is a producer-consumer relationship. The second condition simply states that the relationship of data dependence can be recursively constructed a chain of dependences of the first type between the two instructions. And this dependence chain can be as long as the entire program.

To give an example:

Chapter 2. Background Review

14

ADD R3, R1, R2; instruction i

ADD R3, R3, R4; instruction j

As can be seen, instruction i produces the result of addition in register R3, which is used by instruction j. If two instructions are data dependent they cannot execute simultaneously or be completely overlapped. Dependences are a property of programs, and their effect of the dependences must be preserved. This is the read-after-write (RAW) hazard.

The presence of the dependence is a potential limit to the amount of ILP we can exploit. Whether a given dependence results in an actual hazard being detected and whether that hazard actually causes a stall are dependent on the properties of the pipeline organization. To overcome a data dependence generally has two different ways: maintaining the dependence but avoiding a hazard, and eliminating the dependence by transforming the code. Different computer architectures adopt different techniques. We will discuss the detailed implementation in the later sections.

#### 2.2.2 Name Dependences

A name dependence occurs when two instructions use the same register or memory location (i.e. resource with same name), but there is no flow of data between the instructions associated with that name. In another words, this dependence stems from the utilization conflict of resource, which is partially caused by scarcity of a particular

resource. For example, name dependence may be created when limited number of registers forced the compiler to reuse the same register for an unrelated instruction.

Between an instruction i that precedes instruction j in program order, there are two possible types of name dependences: anti-dependence and output dependence.

- When instruction j writes a register or memory location that instruction i reads, and anti-dependence between instruction i and instruction j occurs. In this case, the original ordering must be preserved to ensure that i reads the correct value.

- When instruction *i* and instruction *j* writes the same register or memory location, an output dependence occurs. To ensure that the value finally written corresponds to instruction *j* is correct, the ordering between the instructions must be preserved.

Since there is no value being transmitted between the instructions, both antidependences and output dependences, are name dependences, as opposed to true data dependences. The name dependence, often called WAR or WAW hazard, is not a true dependence, instructions involved can be executed in parallel or reordered provided that the name (register number or memory location) is changed. The renaming can be easily done for register operands, called register renaming. Register renaming can be done either statically by a compiler or dynamically by the hardware. Section 2.3 will discuss the related issues and approaches on register renaming.

#### **2.2.3 Control Dependences**

As opposed to the previous two types of dependences, which deal mainly with data values and/or resources, the other type of dependence -- Control Dependences study dependences created by program order (control flow). In brief, the ordering of an instruction is studied with respect to a branch instruction to ensure that execution only occurs for instructions in the correct control path.

The basic rules for control dependence are:

- An instruction i that is control dependent on a branch cannot be moved before the branch. This movement breaks the dependence and allow instruction i to be executed regardless of the outcome of the branch instruction.

- An instruction i that is not control dependent on a branch cannot be moved after the branch. Clearly, this rule is the reverse of the previous one.

Examine the example below (which is written in a C-like syntax):

```

s1;

if (condition){

s2;

}

```

Moving the statement s1 into the if-block violate the first rule, whereas moving the second statement s2 before or after the if-block violates the second. The rules help to preserve the correctness of the execution by imposing a correct ordering of instructions.

Since most programs are non-linear, which involves multiple control paths, most instructions are under the influence of one branch instruction or the other. If control dependence can be weakened, more instructions will be available for execution. In particular, program loops represents the biggest potential source of speedup.

#### 2.3 Register Renaming

Register renaming is an aggressive way to deal with false data dependences, which assign different physical register names to the multiple definitions of an architected register. Register renaming was first introduced for the float-point unit of the IBM 360/91 by Tomasulo in 1967 [85]. The 360/91 renamed floating-point registers to preserve the logic consistency of the program execution rather than to remove false data dependencies. Nowadays, register renaming becomes a key issue for the performance of out-of-order execution processors and is extensively used.

In out-of-order processors, a typical instruction set architecture may have 32 architected registers while the micro-architecture implements 128 rename physical registers in order to exploit more ILP by simultaneous examining a large window of instructions which have been transformed into a single-assignment language. These rename physical registers contains not only current state but also speculative state (because of speculated branches, loads, etc.)

There are several different register renaming approaches in commercial processors. Here we describe them briefly and the detailed survey can be seen in [20].

The first approach is called the merged register file, in which architectural registers and rename registers are mingled in a single large register file which we call it the physical register file (one for integer and another for FP) to hold both non-committed and committed data. This approach is used in Alpha 21264 [81] and MIPS R1000 [43].

The second approach of register renaming separates rename registers from architectural registers, each have their own register file and are updated appropriately. The non-committed data and committed data are kept in two different register files. This approach is used in PowerPC 603 [94].

The third is similar to the second approach in that non-committed data and committed data are kept in two different register files, but the non-committed data are stored in the reorder buffer (ROB), while copying these data to the register file is needed at commit. This technique is used in the Intel Pentium [24, 51].

Register renaming requires the use of hardware mechanisms at run time to undo the effects of register recycling by reproducing the one-to-one correspondence between registers and values for all the instructions that might be simultaneously in flight. In merged register file approach, it holds that the number of rename registers is greater

than the number of logical registers. This can be simply explained that the rename storage must have enough registers to contain all of the architected state plus some number of registers with speculative state. The other two approaches can completed decouple the rename storage from the logic view of the architecture.

To implement register renaming, a mapping table [84] is often needed to associated limited architectural registers with physical registers in a large physical register file. For example, Intel Pentium 4 exploits a Register Alias Table (RAT), a kind of mapping table, to allow the small, 8-entry, register file architecturally defined in IA-32 to be dynamically expanded to use the 128 physical registers.

#### 2.4 Other Techniques to Increase ILP

Register renaming techniques can reduce data dependences and increase ILP. Besides register renaming, modern high performance processors often exploit multiple-instruction issuing and out-of-order instruction execution technique to improve ILP.

Multi-issue processors are categorized as two basic flavors: superscalar and *VLIW* (very long instruction word) processors. Superscalar processors may issue varying numbers of instruction per clock cycles from zero to the maximum issue rate, and they can be statically scheduled with compiler support or dynamically scheduled with Tomasulo scheme. Statically scheduled processors use in-order execution, while dynamically scheduled processors use out-of-order execution. The early superscalar processors, such

as Sun UltraSPARC II/III adopt static instruction scheduling and recently almost all superscalar processors, such as MIPS R10000 [43], Alpha 21264 [81], PowerPC, and Pentium 4 [24] processor series, use dynamically instruction scheduling.

In contrast to superscalar processors, VLIW processors package multiple operations into one very long instruction word, and the instruction word is inherently statically scheduled by the compiler. VLIW instructions are formatted either as one large instruction or as a fixed instruction packet with the parallelism among instructions explicitly indicated by the instruction word. The latter often are known as EPIC – Explicitly Parallel Instruction Computers.

Superscalar processors dynamically can decide how many instructions to issue. A statically scheduled superscalar must check for any dependencies between instructions in the issue packet and between any issue-ready candidates and any instructions already in the pipeline. In order to achieve good performance, it requires significant compiler assistances. However, dynamically scheduled superscalar processors check for any dependencies on the fly with less compiler assistance, but with significant hardware costs.

Alternatively, VLIW processors are to rely on compilers to minimize potential data hazard stalls, as well to actually format instructions in a potential issue packet. To do so, the processor hardware need not check explicitly for dependence. Such an approach

allows VLIW processors to be implemented in simpler hardware through extensive compiler optimization to achieve a good performance.

A major limitation of simple pipelining technique is that they all use in-order instruction issue and execution. Instructions are issued in program order, so that if an instruction is stalled in the pipeline, no later instructions can proceed. The idea of dynamical instruction scheduling is to rely on the based hardware to rearrange instructions' execution to reduce stalls while maintaining data flow and exception behavior but come with hardware costs.

Tomasulo scheme eliminates WAR and WAW hazards by renaming all destination registers, including those with a pending read or write for an earlier instruction, so that out-of-order write does not affect any instructions that depend on an earlier value of an operand. Register renaming is often implemented with the use of the reservation stations (RS) and issue logic. RSs can fetch and buffer operands of instructions waiting to issue, eliminating the need to get the operand from a register. Meanwhile, pending instructions designate the RS that will provide their input. Finally, when successive writes to a register overlap in execution, only the last write is actually used to update the register. The use of RSs has two advantages: one is that it distributes hazard detection and execution control, and the other is that execution results are passed directly to functional units from the RSs.

By now, we have reviewed some ILP techniques in modern high performance processors because exploiting ILP is the major technique in processor design to improve processors' performance. Subsequently, we discuss a typical out-of-order superscalar RISC processor -- DEC Alpha 21264 [81] and a VLIW processor -- Itanium [29] processor. Its pipeline can be modified to fit for our tag-based GTEF scheme; while our tag-based scheme has features of superscalar processors.

#### 2.5 Alpha 21264 -- a Out-Of-Order Superscalar Processor

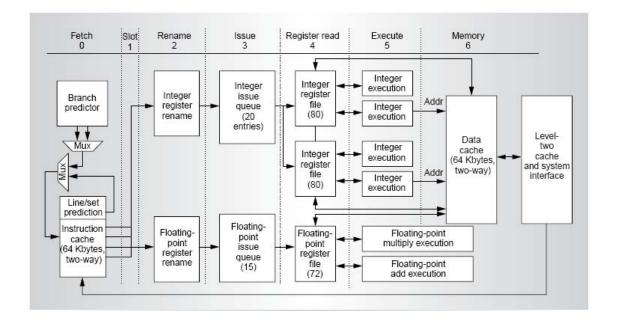

Figure 2.1. Stages of the Alpha 21264 instruction pipeline

The Alpha 21264 is a superscalar microprocessor that can fetch and execute up to four instructions per cycle. It also features out-of-order execution and using speculative

execution to maximize performance. The instruction pipeline of the Alpha 21264 (shown in Figure 2.1) has six stages [81]: Fetch, Rename, Issue, Register Read, Execute and Retire.

Instructions are fetched from a 64-Kbyte, two way set-associative instruction cache which offers much-improved level-one hit rates compared to the 8-Kbyte, direct-mapped instruction cache in the Alpha 21164. Four instructions can be delivered to the out-of-order execution engine each cycle.

The 21264 implements a sophisticated tournament branch prediction scheme, which uses two types of branch predictors – local history and global history predictor to predict the direction of a given branch. The tournament branch predictor is a two-level predictor. The first level holds 10 bits of branch pattern history for up to 1024 branches. The global predictor is a 4096-entry table of a 2-bit prediction counters indexed by the path history.

The capability of out-of-order execution contains register renaming, instruction issue logic, and instruction retire logic. The out-of-order execution logic receives four instructions every cycle, renames registers, and queues the instructions until operands or functional units become available. The 21264 can dynamically issues up to six instructions every cycle. It has four integer ALUs, and two float-point units. Although it

issues instructions out-of-order, it provides an in-order execution model via in-order instruction retire.

The issue queue logic in the 21264 maintains two pending instruction lists to separate integer and float-point instructions. As their operands of the pending instructions become available, the queue logic selects from these instructions using register scoreboards. These scoreboards maintain the status of the internal registers by tracking the progress of all kinds of different latency instructions. The dependent ready-instructions can issue as soon as the bypassed result become available from the functional unit or load.

The 21264 fetches and retires instructions in-order. The retire mechanism assigns each mapped instruction a slot in a circular in-flight window (in fetch order). After an instruction starts executing, it can retire whenever all previous instructions have retired. An exception causes all younger instructions in the in-flight window to be squashed, and these instructions are removed from all queues in the system.

#### 2.6 The Itanium Processor – a VLIW/EPIC In-Order Processor

The Itanium processor [29] is the first implementation of the IA-64 architecture which is a VLIW processor. The processor core has the ability of up to six issues per clock, with up to three branches and two memory references. The memory hierarchy consists

of a three-level cache. The first level splits instruction and data caches. The second and third levels are unified caches, and the third level is an off-chip 4MB cache.

The IA-64 architecture introduces the concept of the instruction group, which is a sequence of consecutive instructions with no register data dependences among them. All the instructions in a group could be executed in parallel if there are sufficient hardware resources. Instructions within an instruction group are divided into instruction bundle, which contains three instructions each. The instruction bundles format the fixed instruction formatting. There is a stop bit to differentiate different instruction groups. To simply the decoding and instruction issue process, the template field is used to specify what types of execution unit each instruction in the bundle requires. The ISA architecture designed in this way can achieve implicit parallelism among operations in an instruction and fixed formatting of the operation field, while maintaining greater flexibility than a VLIW normally allows.

The Itanium processor uses a 10-stage pipeline which is divided into four major parts: Front-end, Instruction delivery, Operand delivery and Execution. The Itanium processor can prefetch up to 32 bytes (2 bundles) per clock into a prefetch buffer, which can hold up to 24 instructions. It uses a multilevel adaptive predictor like in P6 micro-architecture. In delivery stage, it distributes up to six instructions to the execution engine. Within this stage, register renaming for both rotation and register stacking are implemented. In operand delivery stage, the following operations will be completed:

accessing the register file, performing register bypassing, accessing and updating a register scoreboard, and checking predicate dependences. The scoreboard is used to detect when an independent instruction can proceed, so that a stall of one instruction in a bundle need not cause the entire bundle to stall. There are nine functional units in the Itanium, two integer units, two memory units, three branch units, and two float-point units, they are all pipelined. In execution stage, it also detects exceptions and posts NaTs, retires instructions and performs write-back.

The high performance of the IA-64 depends on the coordination of compiler and hardware architecture. IA-64 extended the capability of ILP by providing predicate execution semantics. Predicate execution semantics allows compiler to execute instructions from multiple conditional paths at the same time, and to eliminate the branches that could have caused misprediction. Predication is performed in IA-64 by evaluating conditional expressions values in a special set of 1-bit predicate registers. Nearly all instructions can be predicated. The concept of predicate execution provides a very powerful way to increase the ability of an IA-64 processor to exploit parallelism, reduce the performance penalties of branches, and support advanced code motion. Besides that, IA-64 also provides effective register sets to support software pipelining to expose as much as loop-level parallelism as possible.

In the following, we will review some Java and related technologies for increasing the performance of Java execution since our major work involves in the design and implementation of a Java ILP processor.

# 2.7 Executing Java Programs on Modern Processors

Java [104] is widely used from high end servers to low end hand-held gadgets. Java applications running on high-end server are typically executed using JIT compilers to achieve high performance. In this section we will first discuss the JIT related issues.

However, the memory requirement of JIT compilers is prohibitively expensive for embedded systems and pervasive computing application. So the dedicated Java processors are favored for embedded applications. Java processor adopts a typical stack machine's architecture, thus direct execution of the bytecodes on stack based embedded processors is invariably constrained by the limitations of the stack architecture for accessing operands. In the next section we will discuss related issues of Java processors. In the following we will discuss them accordingly.

#### a. JIT – Just-In-Time Execution

Java bytecodes may be executed on various platforms by interpretation or Just-In-Time (JIT) compiling. The first Java virtual machine (VM) available was interpreter-based, but it was neither efficient nor well-suited to high performance applications. The JIT

compiler translates bytecodes to the native code of the host machine dynamically. Several variants of the JIT concept [6, 15] have been proposed.

Unfortunately, the JIT method suffers some drawbacks. They can usually only perform limited optimizations because time for more sophisticated analysis is not available. Furthermore, JIT systems often optimize only selected sections of code, leaving many segments to continue executing in the interpreter. Finally JIT systems are sufficiently large and complex that they incur runtime overhead in translating bytecodes to native codes, although acceptable performance for Java applications can be provided. Especially in embedded field, using JIT compilation causes an unacceptable wait between application launch and an application actually running on an embedded device. Thus dynamic adaptive compilation (DAC) [46] is proposed to overcome these drawbacks of JIT.

#### b. Dynamic Compilation Techniques

In DAC scheme, Java method classes that are most heavily used are compiled and optimized in traditional compiler technique in order to obtain more efficient native machine code. A DAC combines a JIT compiler and a bytecode interpreter. The heavily used code sections are often identified by a software profiler. When performed statically, a single profiling run is taken to be representative of the program's behavior. Within a dynamic optimization system, the ongoing profiling identifies which part of

codes are currently hot, allowing optimizations to focus only where they will be most effective. However, DAC scheme still has the following problems.

First, an application will run in a slow interpreter mode until code has been profiled, then pause to generate compiled code. When an application is launched, many methods are only run once, so ideally should never be compiled. This impact can be very significant, particularly at application start-up. Second, because software interpretation is very slow, most DAC solutions do very little profiling and compile almost all methods immediately, making guess that a method is not about to be executed for the last time, but will be executed many times. This guess is very costly if it is incorrect.

To overcome the above drawbacks, ARM proposed a scheme of hardware-based dynamic compilation – ARM Jazelle technology, which can directly execute Java instructions on ARM RISC architecture [109]. ARM designers added a new Java instruction set to the classic ARM architecture. The Java ISA is executed in a Java mode, which is entered on a branch. In the Java mode, the CPU executes Java bytecode instructions. Bytecodes are fetched and decoded in two stages. Use of Jazelle technology, the compiler can afford to compile less code and interpret more. Jazelle technology can also be used to improve the speed performance of a DAC compiler by holding off compilation. Jazelle technology improves the performance a lot according to ARM's white paper [109].

# 2.8 Increasing Java Processors' Performance

Hardware processors to execute bytecode directly are becoming popular. The designs of Java processors, such as picoJava [28, 39], are mainly based on stack processors, and generally Java VM is used as their instruction set architecture. A major issue in implementing Java processor is the existent limitation of ILP by the stack dependence. Several techniques to overcome the limitation in Java bytecode have been investigated [53, 28, 88, 44].

### A. Stack Folding

Stack operation folding is one technique to reduce the limitation by converting a set of bytecodes into a RISC-like register-based instruction [4, 48, 50, 70]. In Sun's picoJava-II processor, simple instruction folding in hardware is done by using pattern matching at decode stage of its pipeline [28, 88], and the stack folding is supported by the stack cache as a register file for parallel access of stack operands to eliminate redundant stack operations. More sophisticated folding techniques, such as nested folding [4, 48, 50, 53, 70], may further reduce stack operand dependence. The more detailed stack instruction folding techniques will be discussed in Chapter 4.

#### **B.** Multiple Instruction Issue

Combining multiple in-order issue with stack folding is proposed in ILP [88], which proposes to improve the performance of Sun's picoJava-II processor with in-order,

dual-issue bytecode execution, a fill unit, and stack disambiguation, but this work does not consider out-of-order bytecode execution, which would naturally exploit a greater degree of ILP in Java programs. To support out-of-order execution, SMTI [79] is proposed with software involved to extract independent bytecode trace and implement bytecode folding, but special fetch logic is needed to identify independent traces from instruction cache.

### C. Multi-threading

To meet the requirement of high-performance network application with Java, thread level parallelism (TLP) can be exploited to extract coarse-grained parallelism. Sun's MAJC processor adopts a vertical multithreading technique, in which Java methods are treated as a thread in hardware and speculative execution of multiple threads is included to exploit TLP [69]. But MAJC needs a JIT compiler to convert bytecodes to native codes. The Java Multi-Threaded Processor (JMTP) [82] architecture is a similar hardware implementation, which is a single-chip CPU containing an off-the-shelf general purpose processor core coupled with an array of Java Thread Processors (JTPs). However an intelligent compiler is needed to identify the set of concurrent threads that can be forked as JTP threads.

#### **D. Dynamic Translation**

DAISY [47] is designed on VLIW architecture with dynamic translation, which combines JIT with native compilation techniques by appropriate hardware primitives designed to execute Java efficiently. It dynamically translates Java bytecodes with JIT

into VLIW instructions and exploits a VLIW engine. This approach can take advantage of the increased ILP possible in VLIW machines to achieve high performance [46].

The Femtojava [8] and Delft-Java [40] are another two dynamic-translation-supported Java processors. The FemtoJava processor is a stack-based architecture with replicated functional units and instruction decoders, and employs a VLIW as its execution engine. In FemtoJava [8], the bytecodes in the entire Java program are divided into the instruction groups, the instructions within the same group are translated into VLIW word to be executed. The grouping algorithm is to find those instructions that depend on the result of the previous one, and group them in one instruction block. The Delft-Java [40] processor provides hardware assisted dynamic translation, and the bytecodes are translated on-the-fly into the Delft-Java instruction set. Hardware support for Java language constructs are incorporated into the processor's ISA. This allows application level parallelism inherent in Java language to be utilized ILP.

#### E. Some Dedicated Java Processors

Along with the Java widely used in embedded field, some dedicated Java processors are proposed and built. We will introduce them in the following.

## Espresso [110]

Aurora VLSI's Espresso Java processor is a superscalar RISC engine. The CPU has two operational units, each with an integer and a floating-point processing unit. Espresso supports a 32-bit 128-entry stack. It has 32 to 256 on-chip registers (configurable) and supports 16k to 32k instruction and data caches with 64-bit interfaces. It executes four instructions/cycle or seven bytecodes/cycle.

## Lightfoot Java CPU [111]

Digital Communications Technologies' Lightfoot is a direct-execution Java CPU with a one-to-one mapping between bytecodes and lightfoot instructions. This design tactic eliminates the interpreter and keeps Java's small program memory footprint. The 32-bit Harvard RISC processor provides stack execution for both Java and C. It implements an eight-register-deep stack, with extensions to data memory. The soft core supports J2ME, JavaCard, KVM, and JINI.

#### **JStar** [112]

Nazomi Communications' JStar can work with ARM, and MIPS. JStar's Java translation mechanism is automatically invoked whenever the main processor's instruction pointer falls within a specified memory address range. Java code is simply placed in this memory and can be called directly. JStar uses the processor's registers, including the stack registers, to handle calls just like native code.

# 2.9 PicoJava -- a Real Java Processor

In this section we will discuss a typical stack processor – picoJava [28,39], which directly execute Java bytecode based on a stack processor architecture. The processor uses a pipeline structure to achieve good performance. The Figure 2.2 shows the basic pipeline of the PicoJava-II [28] core.

Figure 2.2. Basic pipeline of the PicoJava-II

| FETCH           | DECODE       | REGISTER      | EXECUTE         | CACHE      | WRITEBACK        |

|-----------------|--------------|---------------|-----------------|------------|------------------|

| Fetch fixed     | Predecode &  | Access the    | Execute for one | Access the | Write back       |

| size cache      | group        | register file | or more cycles  | data cache | results into the |

| lines to the I- | instructions | (stack cache) |                 |            | operand stack,   |

| Buffer          |              | for operands  |                 |            | Forward results  |

|                 |              |               |                 |            |                  |

PicoJava is a comparable RISC processor architecture. PicoJava core contains the integer execution unit and a compact floating-point unit with separated instruction and data caches, which are 16Kbytes. A Java processor must execute all 226 bytecode instructions defined for the Java virtual machine. The 226 instructions can be divided into 15 different functional categories. To efficient execute Java bytecode, picoJava categories bytecodes into three classes: simple, moderately complicated, or very complicated. The simple instructions are RISC-like in the sense that they readily lend themselves to hardware implementation. These instructions are hardwired and execute in a single clock cycle. The majority of instructions executed by a typical program would fall into this category, such as all the integer arithmetic operations. The group of

moderately complicated instructions contains about 30 bytecode instructions, and they are implemented using microcode. Microcode offers a good balance between the need to keep the hardware implementation simple and the need for good performance. The last group of about 30 instructions are either very complicated or require services from the underlying operating systems. They can be executed by a software emulation trap.

A stack processor must spend cycles moving operands to the top of stack in order that the compute operations can get at them, and moving results off the top of stack for storage. These stack manipulation operations makes stack processors pay an overhead burden of up to 30 percent more than RISC processors. To reduce this overhead, PicoJava adopts a register file with 64 entries to support stack operations. The register file treats as a circular buffer, with a pointer to the top of stack. The register file has three read and two write ports. Compute operations can simultaneously read out two operands and write back one result. All data from the constant pool, from local variables, or loaded from objects, are first pushed onto the stack and all compute instructions then access their operands from the stack, and push the results back onto the stack.

The register file, functioned as stack cache, provides a powerful solution to the problem of access inefficiency in stack machines. This leads to an execution technique called instruction folding. The instruction folding can fold up to four bytecode instructions into a RISC-like register-based instruction, by taking the operation to be performed from the compute instruction, the source of the operands from the local variable loads,

and the destination of the results from the local variable store. The instruction folding eliminates essentially all of the computational overhead of stack processors, achieving the same sort of single-cycle execution efficiency found in RISC processor architecture.

# Chapter 3

# Implementing Tag-based Abstract Machine Translator in Register-based Processors

Chapter 1 proposed a concept of General Tagged Execution Framework (GTEF). The tag-based abstract machine translator (TAMT) is a critical component for GTEF scheme, which converts any abstract or real machine programs into tag-based instructions for ILP execution. The concept of TAMT is similar like a software-supported dynamic instruction translator, and the one of merits of TAMT is that it can support dynamic instruction translation and easily collaborate with existing RISC / CISC processors. For example, after designing a TAMT to dynamically translate RISC instruction into tag-based instruction formats, we can only design and implement different TAMT to translate different register-based ISA into a common tag-based instruction formats. Then we can use existing ILP execution engine, PowerPC or Pentium execution engine to tag-based instructions with micro-code support.

In this Chapter, we first discuss a general design methodology of TAMT for registerbased processor architecture, and then with several general-purpose register-based processors – Alpha 21264 and Pentium processor as examples to discuss how to design different TAMT in order to use them as the execution engine.

# 3.1 Design a TAMT

The key-point of the proposed GTEF scheme is to convert any machine program (abstract or real) into tag-based instructions. Conceptually, the instruction execution procedure in GTEF can be described as in Figure 3.1. The conceptual framework captures many existing computer architectures, since one or more stages preceding the execution stage can be implemented either in hardware or software. For superscalar (multi-issue) machines that employ Tomasulo scheme (e.g. PowerPC, Alpha), the tagging and scheduling stage would be implemented by reorder buffer and common data bus in hardware and the execution stage would be utilizing a superscalar execution engine; For VLIW machines (e.g. IA64), the tagging and schedule stage would be performed in software (the compiler) while with limited scheduling in hardware and the fourth stage will be a VLIW execution engine to process bundled instructions.

Figure 3.1. A conceptual tagged execution framework

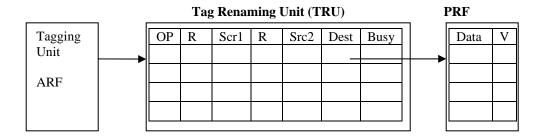

In the conceptual framework, a TAMT is built in stage two which is responsible for instruction tagging and/or dependence resolution, and after this stage any inputted instructions are translated into a tag-based instruction format which can be employed by modern ILP execution engines, superscalar or VLIW processors.

TAMT executes with tags rather than values. In TAMT, there is no actual execution which inputs values into arithmetic pipeline to produce output values; only tags are removed from stack/registers and new tags representing results are put onto stack/registers. The TAMT processes the instruction stream much faster than sequential execution. i.e., it can keep up with parallel execution that will take place later when tags have been mapped into values. That's why we name it as "tag-based abstract machine translator". Based on the functional descriptions on TAMT, we know that in addition to playing tag renaming, TAMT is also responsible for dependence resolution among instructions, and instruction scheduling. Thus, in general, a TAMT may consist of a tagging unit (TU), a tag matching unit (TMU), and a free tag pool (FTP). TU can be a virtual tag execution unit, which is a core unit in TAMT. TMU can be responsible for dependence checking and tagged instruction scheduling. FTP is used to store free tags.

In the following we use an example to illustrate the instruction tagging – "mock execution" scheme of implementing with RISC machines.

The TU adds tags to register numbers in order to distinctly represent changing register contents. Given the expression e = a\*b+(c+d), the compiler produces the following RISC instructions:

ld r1,a; ld r2,b; mul r1,r1,r2; ld r3,c; ld r4,d; add r3,r3,r4; add r1,r1,r3; st r1, e

Each register is renamed by attaching an additional tag (which recycles 0,1,2,3 etc). The renaming and "mock execution" process can be seen in Table 3.1. Now observe that the "mock execution" taking place in the tag-renaming unit. For any instruction that modifies a register, the tag-renaming unit merely attaches a new tag to the instruction that will later produce a value, or attaches the same tag to the register being modified, or attaches the same tag later to any instruction that will need the value of the instruction. In actual execution an instruction may be delayed by cache miss, long arithmetic computation or busy units etc, holding back progress, whereas the mock execution proceeds much faster. However, every different value is represented by a tag and an instruction that produces a value can be recognized by the one that consumes it as related.

Table 3.1. A sample of RISC instructions renaming process

| Instructions | Tag Renaming Unit  | Actual Execution (Later; assume superscalar)             |

|--------------|--------------------|----------------------------------------------------------|

| ld r1, A     | Ld r1-1,A          | ld to load unit; tag 1 added to r1 to denote new value   |

| ld r2,B      | ld r2-1,B          | ld goes to load unit, tag 1 is added to r2               |

| mul r1,r1,r2 | mul r1-2,r1-1,r2-1 | goes to reservation station of multiplier – r1 reused so |

|              |                    | gets new tag                                             |

| ld r3, C     | ld r3-1,C          | goes to load unit                                        |

| ld r4, D     | ld r4-1,D          | goes to load unit                                        |

| add r3,r3,r4 | add r3-2,r3-1,r4-1 | goes to adder                                            |

| add r1,r1,r3 | add r1-3,r1-2,r3-2 | goes to reservation station of adder                     |

| st r1, E     | st r1-3,E          | waiting at store unit and executes when previous         |

|              |                    | finishes                                                 |

Table 3.2. The tag-based RISC-like instruction format

| Opcode | Src1 Tag | Src2 Tag | Dest Tag |

|--------|----------|----------|----------|

|        |          |          |          |

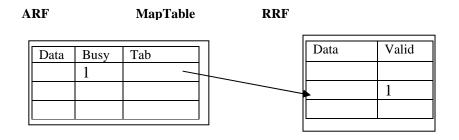

The above tag-based renaming scheme may work with a processor's pipeline architecture, e.g. implementing between decoding unit and issue logic. The tagging unit collaborated with decoding unit to assign each instruction a tag, which will store the result the instruction executes. With instructions' "mock execution" with tags, a new tag-based instruction format (Table 3.2) is generated and stored in Tag-Matching-Unit (TMU). TMU may be a Reorder Buffer (ROB) structure with attaching a mapping table, which indexed from tag number to physical registers. In the mean time the dependent information among instructions within TMU is generated with tags. The tag-based instruction formats are very similar as that used in most RISC processors, thus it will be easily employed by existing RISC processors. The instruction tagging scheme contains a mapping from old ISA with old architectural registers to a new tag-based ISA with tag number, and another mapping from the tag number to physical registers. For example, tags correspond to individual registers. A value loaded from memory or computed by an arithmetic instruction is retained in a tag / registers till it is de-allocated. In a stack machine, however, a tag for a value loaded onto the stack may be de-allocated after use, as we shall see later.

To make our tag-based scheme easy to be understood, in the following we will illustrate how to implement the TAMT in two conventional RISC processors -- DEC Alphas 21264 [81] and Intel Pentium [51]. Both of processors use different register reaming techniques. We will explain individually.

# 3.2 Design a TAMT Using Alpha Engine

Table 3.3 illustrates the process of the tag-based instruction renaming in 21264. In this sample, we assume the number of tag registers is greater than that of architectural registers in order that more instructions can be tagged in the instruction window. For load and store instructions, the related data must be read / written to the register first in order that they can be operated continually. Each Alpha instruction is assigned a tag, at the same time register renaming is implemented. Here we follow the Alpha instruction definition, put the destination field at the right most. The register renaming in 21264 has separate integer and float-point renaming unit. A unique tagging unit may be implemented in the architecture, and it executes instructions "mock" with tags. Tag is un-typed, so which can pointer to both integer and float-point values.

| Instructions     | TAMT Renaming            | Tag-based Instructions |  |  |  |

|------------------|--------------------------|------------------------|--|--|--|

|                  | Unit                     | Generated              |  |  |  |

| ldl \$1, (A)     | ldl \$1-1, (A)           | ldl T1, (A)            |  |  |  |

| ldl \$2, (B)     | ldl \$2-2, (B)           | ldl T2, (B)            |  |  |  |

| mull \$1,\$1,\$2 | mull \$1-3, \$1-1, \$2-2 | mull T1, T2, T3        |  |  |  |

|                  |                          |                        |  |  |  |

| ldl \$3, (C)     | ldl \$3-4, (C)           | ldl T3, (C)            |  |  |  |

| dl \$4, (D)      | ldl \$4 -5, (D)          | ldl T4, (D)            |  |  |  |

| addl \$3,\$3,\$4 | addl \$3-6, \$3-4, \$4-5 | addl T4, T5, T6        |  |  |  |

| addl \$1,\$1,\$3 | addl \$1-7, \$1-3, \$3-6 | addl T3, T6, T7        |  |  |  |

| stl \$1, (E)     | stl \$1-7, (E)           | stl T7, (E)            |  |  |  |

Table 3.3. A sample of tag-based renaming for Alpha processor

From the Table 3.3, we can see that the Alpha instructions are dynamically translated into the tag-based RISC instruction format, and this format is similar as the RISC instruction format for Alpha processors, so it is easy to be integrated with the previous design. The previous used superscalar execution engine can be continually employed. Here we can see that our TAM scheme is easy to be applied with the existent out-of-order execution engine.

# 3.3 Design a TAMT Using Pentium Engine

X86 instruction set is a CISC instruction set with variable instruction length. To execute x86 at high performance, Intel's Pentium [24, 51] dynamically translates x86 instructions into simple, fixed-length instructions that Intel calls micro-operations or uops. These uops are then executed in a decoupled superscalar core capable of register renaming and out-of-order execution. Like RISC instructions, uops use a load / store

mode [51]. Those x86 instructions operating on memory must be broken into a load uop, an ALU uop, and possibly a store uop [51]. Uops use a regular structure to encode an operation, two sources, and a destination like RISC instruction.

Table 3.4 shows how to apply our proposed instruction tagging scheme to convert uops after x86 instruction translation process into the tag-based RISC-like instruction format. Here the same sample program in Table 3.1 is used. We run *gcc* to get the assembly code in first column, after instruction translation, we get the tag-based code in the column 4. The code is similar like in Table 3.3, and the instruction format follows the definition in Table 3.2.

Table 3.4. A sample of tag-based renaming for Pentium processor

| Instructions    | Convert to UOPs | TAMT Renaming Unit         | Tag-based<br>Instructions |  |

|-----------------|-----------------|----------------------------|---------------------------|--|

|                 |                 |                            | Generated                 |  |

| Movl (a), %eax  | load (a), %eax  | load (a), %eax-1           | load (a), T1              |  |

| movl %eax, %ecx | mov %eax, %ecx  | mov %eax-1, %ecx-2,        | mov T1, T2                |  |

| imul (b), %ecx  | load temp, (b)  | load temp-3, (b)           | load T3, (b)              |  |

|                 | imul temp, %ecx | imul temp-3, %ecx-4,%ecx-5 | imul T3, T4, T5           |  |

| movl (d), %edx  | load (d), %edx  | load (d), %edx-6           | load (d), T6              |  |

| movl (c), %eax  | load (c), %eax  | load (c), %eax-7           | load (c), T7              |  |

| addl %edx, %eax | add %edx, %eax  | add %edx-6, %eax-7, %eax-8 | add T6, T7, T8            |  |

| addl %ecx, %eax | add %ecx, %eax  | add %ecx-5,%eax-8,%eax-9   | add T5, T8, T9            |  |

| movl %eax, (e)  | store %eax, (e) | store %eax-9, (e)          | store T9, (e)             |  |

The above tag-based instruction format may be easily used by Pentium execution engine through combining the register renaming logic, since the instruction format is followed the common RISC instruction format. The register renaming logic in Pentium