## MICRO-ARCHITECTURE LEVEL LOW POWER DESIGN FOR MICROPROCESSORS

XIA XIAO XIN

(B.Eng., HuaZhong University of Science and Technology)

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

## Acknowledgements

I would like to thank first and foremost my supervisor, Prof. Tay Teng Tiow, for supporting me throughout this work and for his constant advice and encouragement over the past four years. After leading me to the proposal of this project, he has provided valuable guidance, suggestions and support throughout the course of research. During times of difficulties, he has also shown much understanding and patience, which makes this four years study a memorable part of my life.

I would also like to thank everyone in the Digital and System Application lab for interest, advice and support. In no particular order they are Mr. Zhu Xiaoping, Mr. Pan Yan, Miss. Sun Yang, Mr. Xu Ce and all other members, for their times in constructive discussions over technical and academic problems. These discussions helped very much to clarify questions that are related to the research interest.

I would like to thank everyone in National University of Singapore with whom I have studied and worked over this time, and express my deepest gratitude to all those who have directly or indirectly provided advice and assistance during the course of my research work.

Last, and by no means least, thanks to my dear parents and my dear sister for their endless love and the constant support in my work whilst I've been studying.

## **Table of Contents**

| Acknowledgements                                            | I    |

|-------------------------------------------------------------|------|

| Table of Contents                                           | II   |

| Summary                                                     | VI   |

| List of Tables                                              | VIII |

| List of Figures                                             | IX   |

| Chapter 1                                                   | 1    |

| Introduction                                                | 1    |

| 1.1 The Problem                                             | 1    |

| 1.2 Structure                                               | 4    |

| Chapter 2 Power Dissipation Source and Low Power Techniques | 7    |

| 2.1 Static Power Dissipation                                | 7    |

| 2.1.1 Static Power Dissipation Sources                      | 7    |

| 2.1.2 Static Power Reduction Techniques                     | 11   |

| 2.2 Dynamic Power Dissipation                               |      |

| 2.2.1 Dynamic Power Dissipation Sources                     | 22   |

| 2.2.2 Dynamic Power Dissipation Reduction                   |      |

| 2.3 Summary                                                 |      |

| Chapter 3 Motivation and Analysis Model                     | 35   |

| 3.1 Motivation                                              |      |

| 3.1.1 OS Level DVS Algorithms                               | 36   |

| 3.1.2 Source-code Level DVS Algorithms             |    |

|----------------------------------------------------|----|

| 3.1.3 Our Micro-architecture Level DVS Algorithms  | 40 |

| 3.2 Analysis Model                                 | 44 |

| 3.2.1 Basic Model                                  | 44 |

| 3.2.2 Basic Analysis                               | 47 |

| 3.3 Summary                                        | 51 |

| Chapter 4 Infrastructure                           |    |

| 4.1 Benchmarks                                     | 52 |

| 4.2 Simulation Environment                         | 53 |

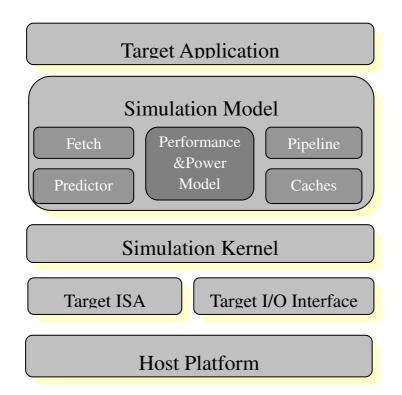

| 4.2.1 The Simulator                                | 53 |

| 4.2.2 Energy Measurements                          | 56 |

| 4.3 Summary                                        | 58 |

| Chapter 5 IPC-Driven Online Power Reduction Method | 59 |

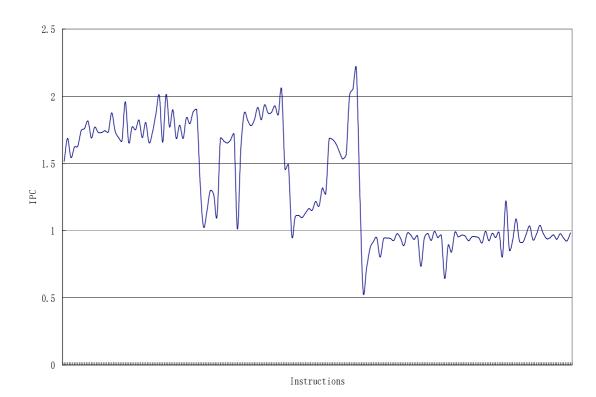

| 5.1 Motivation for IPC Indicator                   | 61 |

| 5.1.1 IPC variations                               | 61 |

| 5.1.2 IPC Indicator                                | 62 |

| 5.2 Methodology                                    | 65 |

| 5.2.1 Identification                               | 65 |

| 5.2.2 Prediction                                   | 67 |

| 5.2.3 Speed-setting                                | 68 |

| 5.3 Results                                        |    |

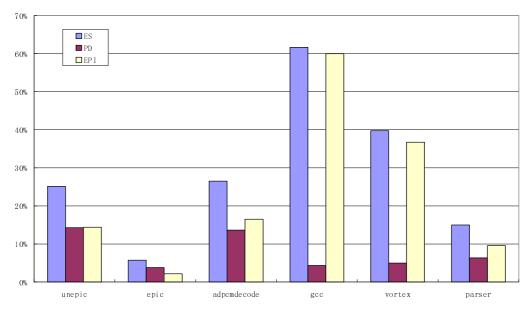

| 5.3.2 Principal results                                             | 71  |

|---------------------------------------------------------------------|-----|

| 5.3.3 Impact of interval length                                     | 73  |

| 5.3.4 Sensitivity to Slowdown Threshold                             | 75  |

| 5.3.5 Overhead                                                      | 79  |

| 5.3.6 Comparison                                                    | 81  |

| 5.4 Summary                                                         | 82  |

| Chapter 6 IPC-Driven Offline Power Reduction Method                 | 84  |

| 6.1 Methodology                                                     | 86  |

| 6.1.1 Phase Identification                                          | 86  |

| 6.1.2 Code Matching                                                 | 88  |

| 6.1.3 Slowdown Process                                              | 91  |

| 6.2 Results                                                         |     |

| 6.2.1 Evaluation metric                                             |     |

| 6.2.2 Principal results                                             |     |

| 6.2.3 Impact of Phase Interval Length                               |     |

| 6.2.4 Sensitivity to Slowdown Threshold                             |     |

| 6.2.5 Overhead                                                      | 103 |

| 6.2.6 Comparison with the IPC-driven online Method                  | 105 |

| 6.2.7 Comparison with Other Offline Methods                         | 107 |

| 6.3 Summary                                                         | 108 |

| Chapter 7 Methods to Identify Related Micro-architecture Parameters | 110 |

| 7.1 Application Power Behavior Identification Method                | 111 |

| 7.1.1 Introduction                                                  | 111 |

| 7.1.2 Methodology112                                 |

|------------------------------------------------------|

| 7.1.3 Results117                                     |

| 7.1.4 Conclusion 122                                 |

| 7.2 Data Dependence Length Identification Method 124 |

| 7.2.1 Introduction                                   |

| 7.2.2 Methodology                                    |

| 7.2.3 Results                                        |

| 7.2.6 Conclusion                                     |

| 7.3 Summary                                          |

| Chapter 8 Conclusions and Future Work                |

| 8.1 Summary of Work                                  |

| 8.2 Summary of Contributions                         |

| 8.3 Future work                                      |

| Bibliography                                         |

## Summary

With rapid advances in CMOS technology, power dissipation has become a great concern in modern microprocessor design, not only for battery-operated potable devices but also for high-end computer systems. Minimizing power dissipation of processors leads to many benefits, such as prolonging the battery lifetime of portable devices and reducing the heat dissipation and cooling cost of computer systems.

In this thesis, we are going to propose efficient designs for reducing power dissipation of the microprocessor. First of all, we investigate background and techniques for reducing microprocessor power dissipation. Then we attempt to address power dissipation issue of the microprocessor at the micro-architecture level, and present a realistic analysis model to discuss and identify possible power reduction opportunities during application execution. Finally, based on our analysis model, we propose two novel schemes at the micro-architecture level to reduce runtime power dissipation of microprocessors. Both methods make use of a micro-architecture parameter-IPC to identify potential power reduction opportunities during application execution.

Firstly, an IPC-driven online power reduction scheme is presented. This design employs the micro-architecture parameter (IPC) as the runtime performance indicator to dynamically scale the voltage and frequency of a processor. The basic idea in this interval-based identification and prediction design is to trace the current interval's performance activity level and predict the coming interval at which certain power-performance trade-off would be profitable.

Then, by using the same micro-architecture parameter, an IPC-driven offline power reduction

scheme is presented. This code analysis and reconfiguration design first identifies code sections that have appropriate IPC values and could make contributions to microprocessor power reduction, and then profiles them to dynamically scale the voltage and frequency of the microprocessor at appropriate points during application execution. For both low-power design schemes, simulation results showed that they significantly reduced the processor runtime energy consumption with minimal application performance degradation. Furthermore, both schemes could achieve better results when comparing with other state-of-the-art related works.

Beside the two micro-architecture level low-power designs, we also propose two methods to identify related micro-architecture parameters: runtime power behavior and data dependence length of applications. The two micro-architecture parameters could be used to evaluate the two low-power designs proposed by us.

# **List of Tables**

| Table 4.1: Summary of selected benchmarks               | 53 |  |

|---------------------------------------------------------|----|--|

| Table 4.2: Wattch Baseline Simulation Model             | 56 |  |

| Table 5.1: Transition times for different IPC threshold | 80 |  |

# **List of Figures**

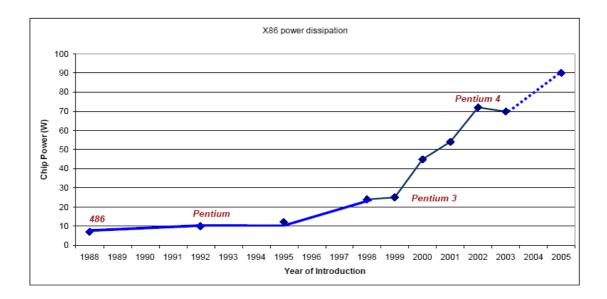

| Fig. 1.1: Trends in power dissipation and the cost of cooling [6]      | 3   |

|------------------------------------------------------------------------|-----|

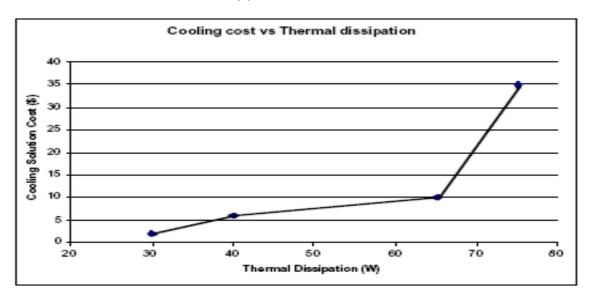

| Fig. 2.1: ITRS projections for device power dissipation [7]            | 8   |

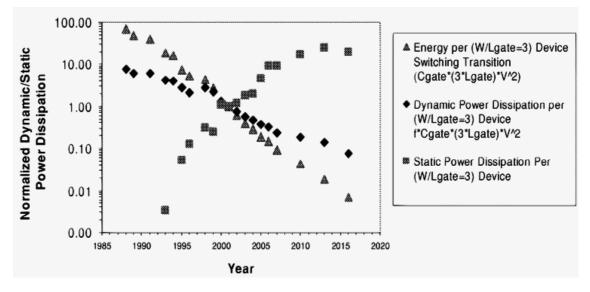

| Fig. 2.2: Leakage current mechanisms of deep-submicron transistors [8] | 8   |

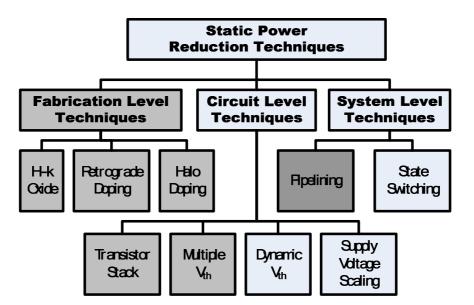

| Fig. 2.3: Static Power Reduction Techniques                            | 11  |

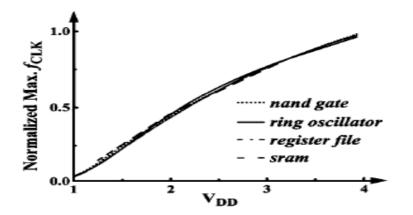

| Fig. 2.4: Maximum Clock Frequency vs. Supply Voltage [41]              | 24  |

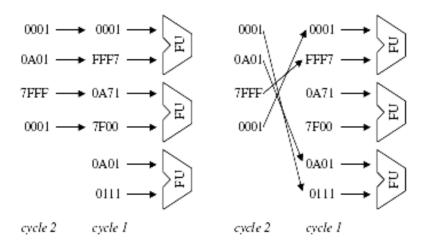

| Fig. 2.5: Dynamic Functional Unit Assignment [60]                      | 31  |

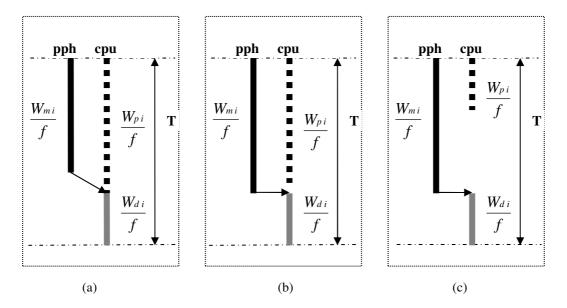

| Fig. 3.1: Possible overlaps in peripheral and CPU computing operations | 46  |

| Fig. 4.1: Architecture of the Wattch Simulator                         | 54  |

| Fig. 5.1: IPC variations during a short execution period of "gcc"      | 61  |

| Fig. 5.2: Analysis model                                               | 63  |

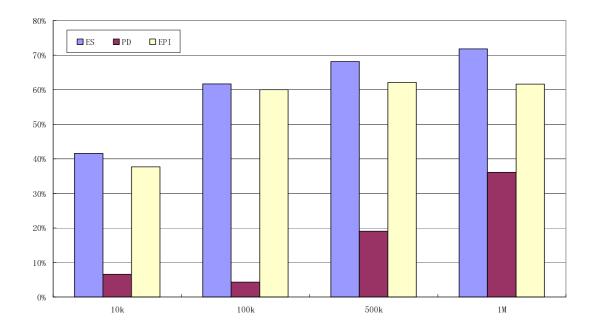

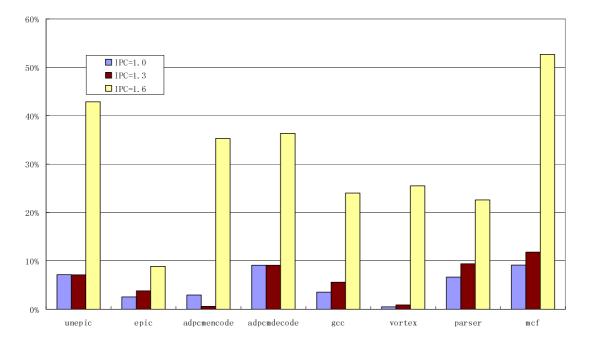

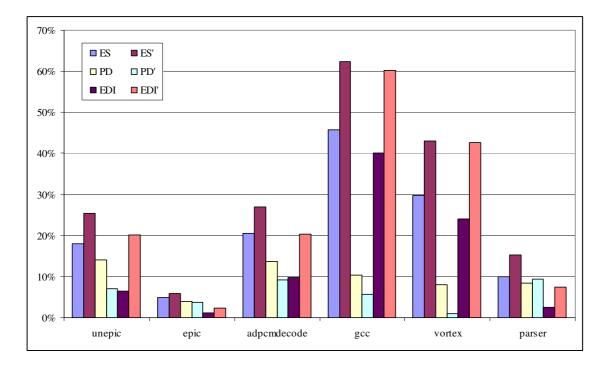

| Fig. 5.3: Principal results: ES, PD, and EPI                           | 71  |

| Fig. 5.4: The impact of different interval length on "gcc"             | 74  |

| Fig. 5.5: Energy savings for different IPC thresholds                  | 76  |

| Fig. 5.6: Performance degradations for different IPC thresholds        | 77  |

| Fig. 5.7: Energy*performance improvement for different IPC threshold   | 78  |

| Fig. 5.8: Comparison between Our algorithm and Weiser's algorithm      | 81  |

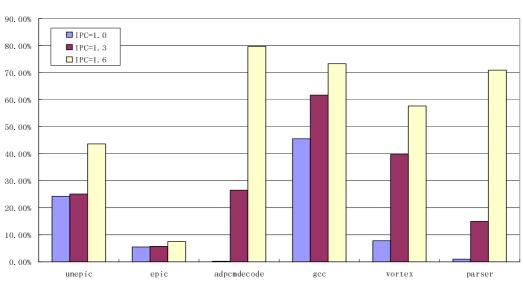

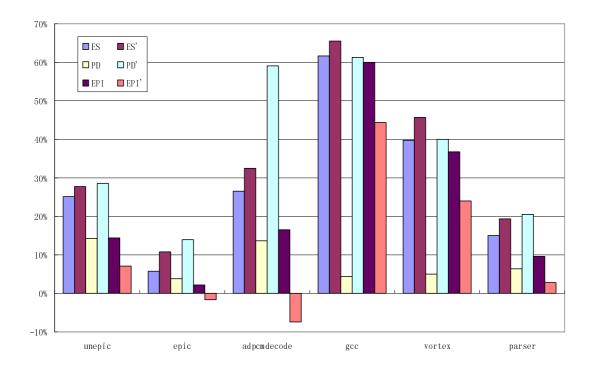

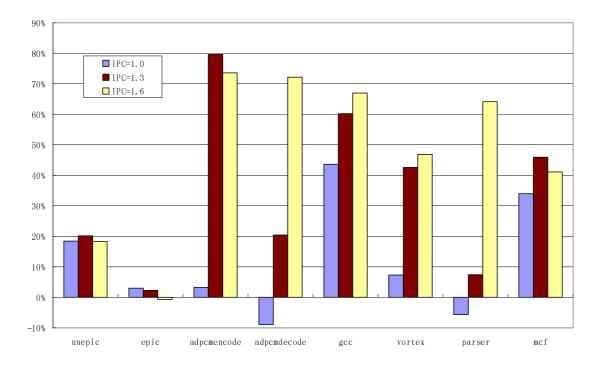

| Fig. 6.1: Principal results: ES, PD, EPI                               | 94  |

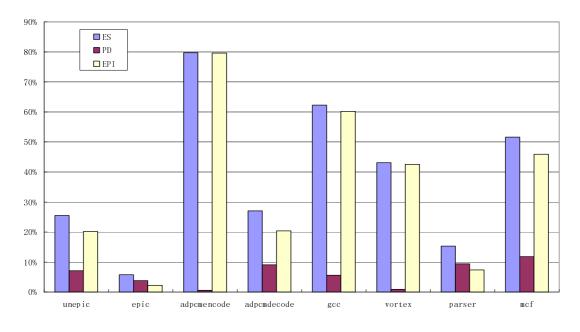

| Fig. 6.2: The impact of different interval length on "gcc"             | 98  |

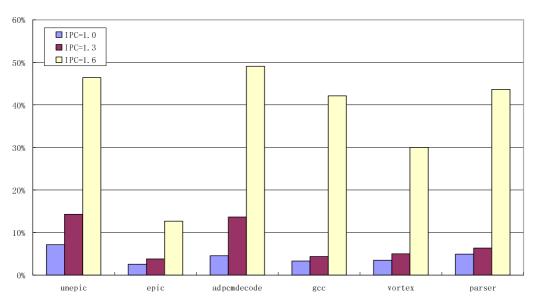

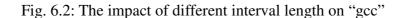

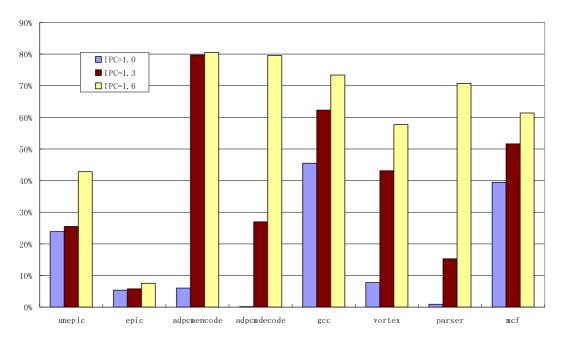

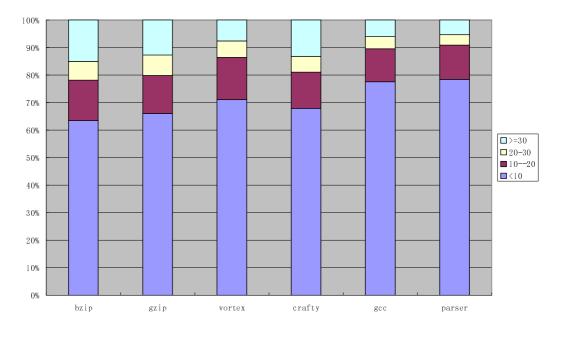

| Fig. 6.3: Energy saving results                                        | 100 |

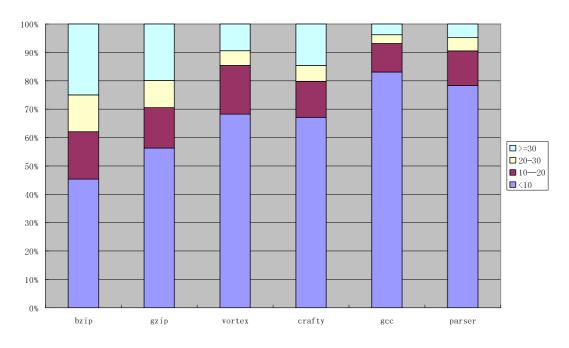

| Fig. 6.4: Performance degradation results                              | 101 |

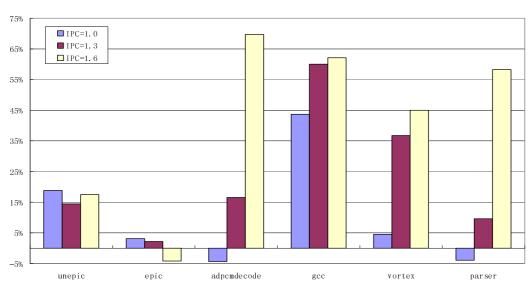

| Fig. 6.5: Energy*performance improvement results                       | 102 |

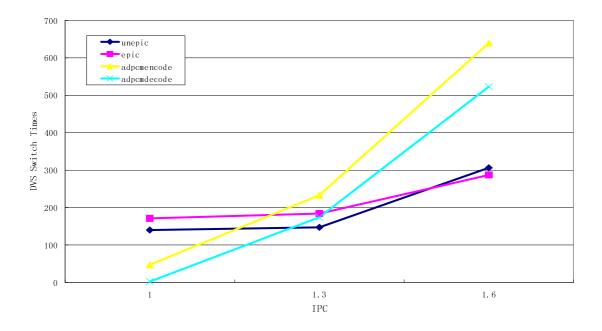

| Fig. 6.6: Transition times for different IPC threshold                 | 104 |

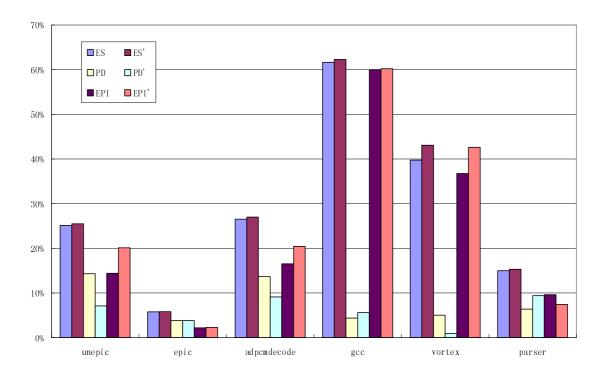

| Fig. 6.7: Comparison between the online and offline algorithms   |     |

|------------------------------------------------------------------|-----|

| Fig. 6.8: Comparison between our and Hsu's offline DVS algorithm | 107 |

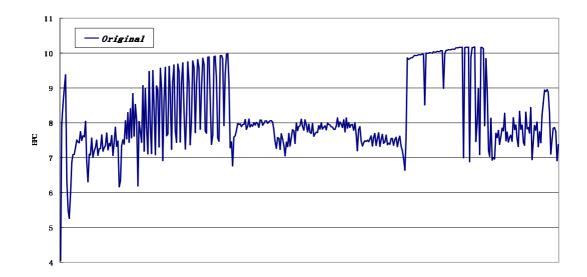

| Fig. 7.1(a): Measured runtime power behavior for "vortex"        | 118 |

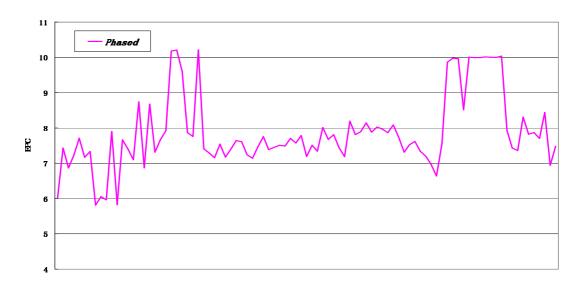

| Fig. 7.1(b): Phase estimated power behavior for "vortex"         | 118 |

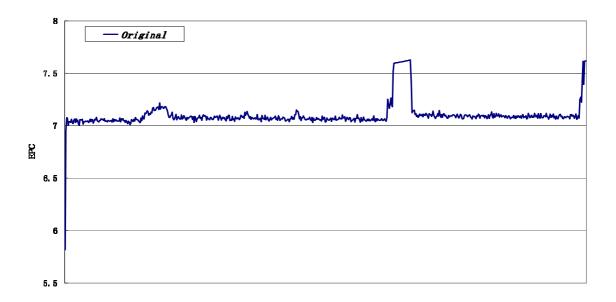

| Fig. 7.2(a): Measured runtime power behavior for "adpcmencode"   | 120 |

| Fig. 7.2(b): Phase estimated power behavior for "adpemencode"    |     |

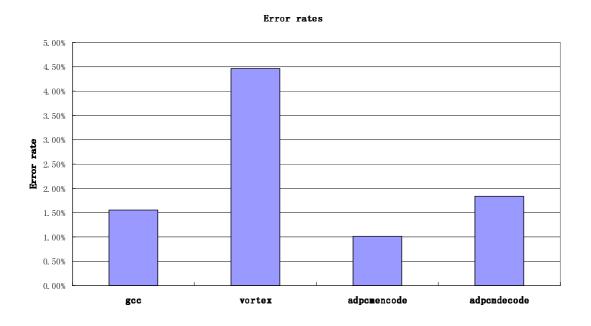

| Fig. 7.3: Error rates                                            | 121 |

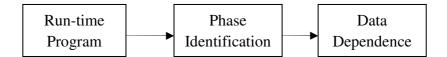

| Fig. 7.4: Steps for DDL identification method                    |     |

| Fig. 7.5: DDL Example                                            | 127 |

| Fig. 7.6: Pseudocode for DDL Identification Algorithm            | 129 |

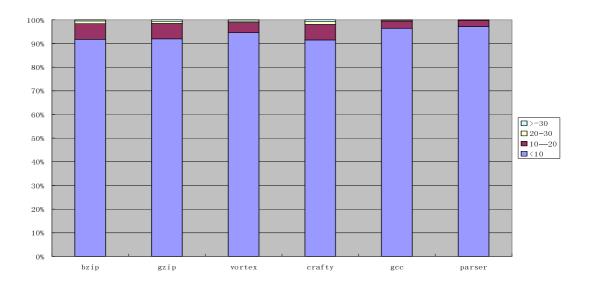

| Fig. 7.7(a): MAX_DDL of the complete application execution       | 130 |

| Fig. 7.7(b): MAX_DDL of the representative phases                | 130 |

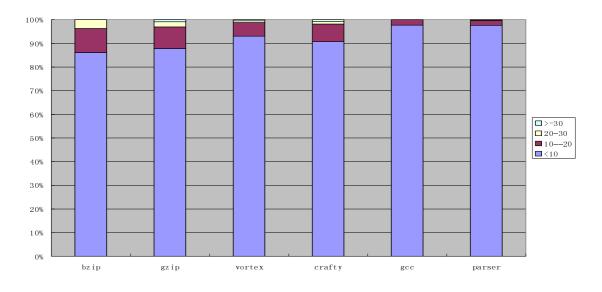

| Fig. 7.8(a): TOTAL_DDL of the complete application execution     | 132 |

| Fig. 7.8(b): TOTAL_DDL of the representative phases              |     |

## **Chapter 1**

## Introduction

Power dissipation is becoming a crucial design constraint for modern microprocessors. This thesis investigates low power design schemes at the micro-architecture level to reduce power dissipation of microprocessors. In this chapter, we shall define the problem to be addressed, and describe the structure of the thesis.

### **1.1 The Problem**

With the rapid growth of the internet and computer technology, portable devices, such as cellular phones, Personal Digital Assistants (PDA) and Global Positioning System (GPS) navigators, have become increasingly popular and widely-used. For these widespread portable electronic products, modern consumers require not only mobile computing ability, but also fast executing speed and various entertainment functions. The ability to fulfill these requirements usually lies on microprocessors embedded in the portable devices. To achieve faster computing speed, modern microprocessors have been pushed to higher clock speed and implemented with greater parallelisms. On the other hand, to accomplish more complicated functions, modern microprocessors have been packed with larger on-chip caches and more complex logic structures.

However, with the dramatic increase in executing speed and on-chip functions in a

microprocessor, power dissipation also increases significantly. For example, maximum power dissipation of recent microprocessors has reached 130watts [1]. Such high power dissipation of microprocessors causes problems in at least two aspects.

Firstly, high power dissipation of microprocessors limits the "battery-life" of portable products. As is well known, battery-life is an important factor in the adoption of these battery-powered portable devices. In general, the battery life-time depends on both the battery capacity and the power dissipation in a portable device. However, improvements in the capacity of batteries can not keep pace with the increasing power demand of today's portable devices [2, 3, 4]. Thus, minimizing power dissipation of the portable devices is an efficient approach to prolong the battery life. As the microprocessor is a key component in a portable device, minimizing its high power dissipation could contribute much to the total power dissipation reduction of a portable device, and it is also very helpful to increase the battery life of the battery-powered device.

Secondly, high power dissipation of microprocessors leads to high chip temperature during operation. High operating temperature may lead to phenomena such as *electromigration* and *hotelectron* effects in the circuit, thereby reducing reliability of the whole system. As studied in [5], researchers found that every 10°C increase in operating temperature roughly doubles the failure rate of an Integrated Circuit (IC). To reduce the failure rate caused by high temperature, large and expensive cooling systems have to be incorporated into computer systems to ensure proper operation.

2

(a): Power trends

(b): Cooling cost

Fig. 1.1: Trends in power dissipation and the cost of cooling [6]

Figure 1.1(a) shows the trends in power dissipation of Intel processors over the past fifteen years. As shown in the graph, more recent processors have much higher maximum power dissipation, increasing by a factor of 2 every four years [6]. Figure 1.1(b) shows the costs involved in removing this power (converted to heat) from the processors. This graph shows how the cost of cooling has increased as the amount of

heat produced has risen. It can be seen that the cooling cost rises non-linearly with the power of the processor [6]. From the two graphs, it is obvious that: reducing the amount of power dissipation in a processor would decrease the overall system cost.

To address the above two issues, a lot of research effort has been focused on developing microprocessors with high performance and minimal power consumption. To achieve this goal, various low-power technologies, from transistor and gate levels to operating system and application levels, have been proposed in the past years, and we will present and discuss them in the next chapter. In this thesis, we focus on reducing power dissipation of microprocessors at the micro-architecture level, and successfully propose two new and efficient low-power strategies, which will be presented in the following chapters.

### **1.2 Structure**

The remainder of this thesis is organized as follows. Chapter 2 describes the basic issues of processor power dissipation and investigates various types of power dissipation sources in microprocessors. In particular, this chapter focuses on reviewing distinguished low-power techniques to reduce power dissipation induced by these sources in microprocessors.

In Chapter 3, firstly, the motivation for our micro-architecture level low-power design schemes is presented. Following that, an analysis model for our schemes is described in detail, and then the trade-off between power and performance of microprocessors in our schemes are studied. In Chapter 4, the benchmark applications used to evaluate our proposed schemes in this thesis are presented. In addition, the simulation environment and the processor architecture of the simulator are also described in this chapter.

Chapter 5 describes a scheme that employs a micro-architecture parameter (IPC) as the performance indicator for specific processor runtime periods, and implements an interval-based identification and prediction mechanism for processor demand to reduce its power dissipation with minimal performance degradation. The basic idea for this design is to trace the current interval's performance activity level in terms of the IPC value and then use it to predict the processor demand for the coming interval at which certain power-performance trade-off would be profitable. Results show that this design scheme takes advantage of energy reduction as well as provides fine-grained, tight control over performance loss.

In Chapter 6, using the same micro-architecture parameter (IPC), a code analysis and reconfiguration scheme for microprocessor power reduction is presented. This trace-based low power design is implemented to identify code sections in an application that have appropriate IPC values and could make contributions to program runtime power reduction. These traced code sections are then profiled to dynamically scale the voltage and frequency of the microprocessor at appropriate points during execution. Experiment results show that our trace-based code analysis and reconfiguration mechanism significantly reduces the energy consumption of microprocessors without degrading the performance very much.

Chapter 7 presents two efficient methods to identify two useful micro-architecture

parameters, which are runtime power behaviors and data dependence length (DDL) of an application. Firstly, a method to identify application runtime power behaviors is presented. This method employs a phase-based analysis approach to obtain the runtime power dissipation information of an application and then characterize its runtime power behaviors. Then, a data dependence length identification method is presented. This method also uses the phase analysis technique to identify dynamic data dependence information among runtime instructions of a program and then use data dependence length (DDL) to characterize dynamic data dependence of the whole program. Experiment results demonstrate that both methods could identify the target micro-architecture parameter accurately and speedily.

Finally, Chapter 8 concludes this thesis, summarizing the main results and contributions, and describing directions that future work could pursue in this research area.

## **Chapter 2**

# Power Dissipation Source and Low Power Techniques

In general, power dissipation of microprocessors can be divided into two categories:

- 1) Static power dissipation, which arises from leakage currents and is generally independent of logic switching of circuits.

- Dynamic power dissipation, which arises from the switching activities of logic circuits.

In this chapter, we will investigate both static power dissipation and dynamic power dissipation. In Section 2.1, we shall review leakage-induced static power dissipation. We shall examine the various sources for static power dissipation and the techniques to reduce static power dissipation. In Section 2.2 we shall describe the switching-induced dynamic power dissipation. We investigate sources for dynamic power dissipation and present low-power techniques to minimize them.

## 2.1 Static Power Dissipation

### **2.1.1 Static Power Dissipation Sources**

In deep sub-micrometer regimes, leakage current increases with reduced threshold voltage, channel length and gate oxide thickness. The high leakage current is becoming a significant contributor to the overall power dissipation of CMOS circuits. Figure 2.1 shows the projection of the International Technology Roadmap for Semiconductors (ITRS) for the trend of static and dynamic power dissipation with respect to technology progress [7]. It can be seen that the static power dissipation is expected to exceed the dynamic power dissipation unless effective static power reduction techniques are properly applied.

Fig. 2.1: ITRS projections for device power dissipation [7]

As known, for deep-submicron transistors, there are six major leakage mechanisms that contribute to the static power dissipation, as illustrated in Figure 2.2.

Fig. 2.2: Leakage current mechanisms of deep-submicron transistors [8]

As is shown in Figure 2.2, the six leakage mechanisms [8] are: PN junction reverse-bias current ( $I_1$ ), sub-threshold leakage ( $I_2$ ), tunneling into and through gate oxide ( $I_3$ ), injection of hot carriers from substrate to gate oxide ( $I_4$ ), gate-induced drain leakage ( $I_5$ ) and punch-through ( $I_6$ ). In general, currents  $I_2$ ,  $I_5$ , and  $I_6$  are off-state leakage mechanisms, while  $I_1$ ,  $I_3$ , and  $I_4$  occur in both ON and OFF states.

#### 2.1.1.1 PN-junction reverse-bias current $(I_1)$

Normally, PN junction leakage current is generated when drain and source to well junctions are reverse-biased. A reverse-bias PN junction leakage ( $I_1$ ) has two main components: 1) minority carrier diffusion and drift near the edge of the depletion region; 2) electron-hole pair generation in the depletion region of the reverse-biased junction [9]. As is studied in [9], PN-Junction reverse-bias leakage is a complex function of junction area and doping concentration.

#### 2.1.1.2 Sub-threshold leakage $(I_2)$

The sub-threshold leakage is the leakage between source and drain in an off-state transistor. In modern MOSFETs, weak inversion leakage is the dominant part in the sub-threshold leakage. Other effects like Drain Induced Barrier Lowering (DIBL), Body Effect, Narrow-Width Effect, Channel Length Effect and Temperature Effect may also add to the sub-threshold leakage [8].

#### 2.1.1.3 Tunneling into and through gate oxide $(I_3)$

The gate oxide tunneling current is incurred from the tunneling of electrons between substrate and gate through the gate oxide. Basically, the tunneling effect occurs when the high electric field is coupled with low oxide thickness. In general, the mechanism of tunneling between substrate and gate can be primarily divided into two parts: Fowler-Nordheim (FN) tunneling and direct tunneling.

#### 2.1.1.4 Injection of hot carriers from substrate to gate oxide $(I_4)$

In a short-channel transistor, the hot-carrier injection leakage occurs when electrons or holes gain sufficient energy from the electric field to cross the interface potential barrier and enter into the oxide layer. Usually, this effect is due to high electric field near the Si-SiO<sub>2</sub> interface. Since electrons have a lower effective mass than that of holes and the barrier height for electrons is also less than that for holes, the injection from substrate (Si) to gate oxide (SiO<sub>2</sub>) is more likely for electrons than holes.

#### 2.1.1.5 Gate-induced drain leakage $(I_5)$

Gate-induced drain leakage (GIDL) is due to high field effect in the drain junction of an MOS transistor. As is presented in [96], a path for the GIDL is completed when the substrate is at a lower potential for minority carriers and the induced minority carriers underneath the gate are swept laterally to the substrate. Generally, GIDL is increased by thinner oxide thickness and higher potential V<sub>dd</sub> between gate and drain.

#### 2.1.1.6 Punch-through $(I_6)$

In short-channel devices, punch-through occurs when the combination of channel length and reverse bias leads to the merging of the depletion regions. In sub-micrometer MOSFETs, V<sub>th</sub> adjust implant is usually used to have a higher doping at the surface. This causes a greater expansion of the depletion region below the surface, and thus the punch-through leakage current is generated below the surface.

#### 2.1.1.7 Static power dissipation model

From the above discussion, it can be seen that the static power dissipation is very complex and thus is not easy to model. However, the static power dissipation can be simplified and represented by the following formula:

$$P_{static} = I_{leak} \times V_{DD} \tag{2.1}$$

Where  $I_{leak}$  is the cumulative leakage current due to all the components ( $I_1$  to  $I_6$ ) described previously.

## **2.1.2 Static Power Reduction Techniques**

Fig. 2.3: Static Power Reduction Techniques

There is a wide range of low power techniques addressing static power dissipation, from fabrication level engineering to system level design. As a quick summary, we illustrate them in Figure 2.3. Each of these techniques will be presented in the following sub-sections.

#### 2.1.2.1 Fabrication Level Techniques

To minimize the overall static power dissipation, a straightforward way is to minimize the leakage current in each transistor. This can be done through fabrication techniques of transistors. Currently, fabrication techniques, such as high-k insulating materials, retrograde doping and halo doping, are already in use to provide transistors with the best performance and reduce the leakage at the same time. Here we present some examples for these fabrication techniques, illustrated as below:

#### • Y. Taur (2000)

In [10], Y. Taur found that with deep submicron transistors, to maintain performance, scaling happens not only in the lateral dimension (channel length), but also in the vertical dimension, doping concentration and supply voltage. Thus, as gate oxide thickness got thinner, this results in increased leakage through gate node. To solve this problem, the author proposed to use high-k insulating materials, which increases physical thickness of the insulator while keeping reduced equivalent electrical thickness and eventually minimizes the leakage current through gate node.

#### • S. Thompson et al. (1998)

As the channel length is scaled down, punch-through current becomes a big issue. At the same time, to maintain device performance, the mobility of the channel surface should be good enough. Thus, a better channel doping profile should be with a low surface doping concentration followed with a highly doped sub-surface doping region. This is called "Retrograde Doping".

In the study of [11], S. Thompson et al. illustrated the retrograde doping technique and its useful effect on minimizing the punch-through leakage current. As they found, the low surface doping is to make sure less impurity presented in the surface, and hence the mobility will be higher. Furthermore, the higher sub-surface concentration can counteract the nearing of source and drain regions, which consequently reduces the punch-through leakage current in the channel.

#### • D. Fotty (1997)

In the study of [12], D. Fotty suggested using the halo doping technology to reduce the sub-threshold leakage. In general, halo doping is introduced to provide a way to control the dependence of threshold voltage on channel length. As the author found, below the edge of the gate, which is also the end of the source or drain region, the introduced halo doping results in a narrower depletion region, and thus reduces the charge-sharing effect and the threshold voltage degradation, and eventually reduces the sub-threshold leakage.

The designs presented in this section have focused on fabrication techniques to minimize the static leakage current in each transistor. In these fabrication techniques, high-k gate dielectrics are expected to lower the static leakage [13]. On the other hand, retrograde and halo doping are also used as a means to decrease the static leakage current, by scaling the channel length and increasing the transistor drive current [ 14, 15, 16, 17]. More detailed discussion of these fabrication techniques can be found in [8]. So far, the fabrication techniques are commonly employed in transistors to provide good performance, and also minimize the overall static leakage. With the advance of technology, more and more fabrication techniques are predicted to be used to reduce the leakage-induced power dissipation in future.

#### 2.1.2.2 Circuit Level Techniques

With the fabrication level techniques applied to extremes, additional leakage power reduction can be achieved by carefully designing the circuit structures. In this section, we will present several popular circuit level techniques which are used to reduce the static leakage current.

#### A) Transistor Stack

One promising way to reduce static leakage is by intentionally turning off a series-connected transistor. In general, sub-threshold leakage current can be reduced when more than one transistor in the stack is turned off. This is known as the stacking effect [18]. Furthermore, according to the study in [19], the leakage of a two-transistor stack is an order of magnitude less than the leakage in a single transistor. Thus, researchers proposed to use transistors stack to reduce the static leakage current and its induced power dissipation. Some applications using transistors stack are presented in the following.

• M. C. Johnson et al. (1999)

As studied in [20], to reduce the leakage current in transistors, researchers proposed an off-state transistor stack approach. By identifying a low-leakage state and inserting leakage-control transistors only where needed, this method carefully selected the input vector so as to allow more off-state transistors in series. According to their experiment results, it was proven to be an effective way to control the sub-threshold leakage.

• M. Powell et al. (2000)

In the work of [21], to reduce leakage power dissipation, M. Powell et al. proposed a circuit-level technique to implement the transistor stack in processors. They employed additional transistors to gate a circuit structure from the power supply, as done with the Gated-VDD circuit technique. Their results indicated that Gated-VDD together with a resizable cache architecture reduced energy-delay very much with minimal impact on performance.

• S. Mukhopadhyay et al. (2003)

As presented in [22], S. Mukhopadhyay et al. first modeled the overall leakage in a stack of transistors, and then explored the opportunities for leakage reduction in the standby mode of operation for scaled technologies. To implement the transistor stack, the researchers proposed a novel technique of input vector selection to reduce total leakage in a circuit. Results showed that their technique achieved 44% savings in total leakage in 50-nm devices compared to the conventional stacking technique.

15

The designs presented in this section have focused on using transistor stack to minimize the leakage in transistors. Some schemes simply inserted transistor stack to control the leakage power dissipation [23, 24, 25]. As showed in their results, transistor stack is efficient to reduce the leakage current. However, as a result of introducing additional transistors into a chip circuit, this technique increased the transistor number in a chip and made its architecture more complex, thereby leading to additional dynamic power.

#### **B)** Multiple V<sub>th</sub> and Dynamic V<sub>th</sub>

As the sub-threshold leakage has an exponential dependence upon the threshold voltage, multiple threshold voltages can be provided in a single chip for proper use to reduce the leakage current. In general, higher threshold transistors can suppress the leakage while the lower threshold transistors can provide higher performance. There are various ways to achieve the varied threshold voltage. For example, changing the channel doping, gate oxide thickness, channel length, and body bias [26, 27] can all affect the final threshold voltage of a transistor. Thus, we can change the  $V_{th}$  either statically or dynamically. There are some useful strategies proposed by former researchers, as illustrated in the following.

• H. Makino et al. (1998)

In 1998, H. Makino et al. [28] suggested an auto-backgate-controlled MT-CMOS circuit to provide multi-threshold voltages for both p-channel and n-channel transistors. This design is similar to transistor stack. Additional

high-threshold transistors were put in series to low  $V_{th}$  circuit and these additional transistors reduce leakage of a circuit in sleep mode. Experiments showed their method achieved good results.

• N. Tripathi et al. (2001)

In [29], researchers proposed an algorithm to realize dual threshold CMOS circuits. In their algorithm, it employed transistors to lower thresholds in critical paths and thus guarantee best performance while applying higher threshold elsewhere. The results showed that their algorithm reduced the leakage current with better results for ISCAS benchmark circuits compared to other reported results.

• T. Inukai et al. (2001)

As is well-known, by changing the body bias of transistors, the threshold voltage can be manipulated at run time. In [30], researchers investigated characteristics of variable threshold voltage CMOS (VT-CMOS) in series connected circuits, and found that the leakage power dissipation of transistors is minimized by utilizing VT-CMOS while the performance degradation is suppressed due to the body effect in series connected circuits.

The designs presented in this section have focused on using multiple  $V_{th}$  and dynamic  $V_{th}$  to reduce the leakage current in transistors. Some designs employed inserted control transistors or circuits to implement multiple  $V_{th}$  and reduce the leakage [31, 32]. Other schemes utilized back-gate bias control to carry out dynamic  $V_{th}$  adjustment to minimize the leakage current [33, 34]. Results of these examples proved that it is an effective way to control the leakage current of transistors by changing the  $V_{th}$  statically or dynamically. Although achieving good power reduction, similar to the problem in transistor stack design, it also introduced additional transistors/devices and consequently increased the complexity of chip circuits.

#### C) Supply Voltage Scaling

Designed to reduce dynamic power dissipation, voltage scaling technique is the most successful and widely used low-power technique. However, as found, it is also an effective method for static leakage reduction. There are some applications by using supply voltage scaling to reduce static power dissipation, described as below.

• A. J. Bhavnagarwala et al. (2000)

In [35], researchers found that the sub-threshold leakage can be reduced when the supply voltage is scaled down. As is identified by them, the reason is that Drain Induced Barrier Lowering (DIBL) also decreases as the supply voltage decreases. Moreover, their results of experiments proved that supply voltage scaling is helpful to minimize the sub-threshold leakage and static power dissipation.

• S. Tyagi et al. (2000)

In the study of [36], S. Tyagi et al. presented that supply voltage scaling achieved sub-threshold and gate leakage reduction in the orders of  $V^3$  and  $V^4$  respectively. In their experiments, results showed that it significantly reduced the static power dissipation by scaling supply voltage.

• M. Takahashi et al (1998)

In [37], researchers proposed to use clustered voltage scaling to reduce the leakage-induced power dissipation for mobile multimedia circuits. In their design, transistors for critical and non-critical paths were separately clustered and powered by higher and lower supply voltages, respectively. By using the clustered voltage scaling, they found that the overall static power dissipation of the design was much smaller since the leakage current in circuits was reduced.

The designs presented in this section have focused on using supply voltage scaling to reduce leakage current in transistors. To achieve low-power benefits, some researchers used static supply scaling to lower supply voltage [38, 39, 40]. On the other hand, researchers employed dynamic supply scaling to minimize the leakage [41]. All these techniques showed that supply voltage scaling is useful to minimize the leakage current and hence reduce the static power dissipation. Thus, although supply voltage scaling is originally designed to reduce dynamic power dissipation, it has an additional and effective purpose for static power dissipation reduction.

#### 2.1.2.3 System Level Techniques

Even higher level low power techniques are proposed by researchers to further reduce static power dissipation. The nature of static power dissipation indicates that it is independent of switching activities and is "static" all the time. Thus, if the total time needed by a specific job can be considerably reduced, the amount of static energy can also be saved. There are some techniques which attempted to reduce static power dissipation at system level, as is illustrated in the following.

#### A) Pipelining

Pipelining saves energy in a straightforward way. When using pipelining, it significantly reduces the overall execution time of a certain program. As a result, the time of leakage flowing is also reduced, thereby leading to a reduction in leakage-induced static power dissipation.

• N. S. Kim et al. (2003)

In the work of [42], N. S. Kim et al. compared the overall power dissipation of pipelined systems with that of series systems, and concluded that "pipelining's combined dynamic and static power leakage will be less than that of the serial case". Thus, their conclusion has proven that pipelining can reduce the leakage-induced static power dissipation.

The design presented in this section has focused on using pipelining to reduce static power dissipation at the system level. As showed in the above example, pipelining is helpful to reduce the static leakage time and consequently achieve energy reduction. Therefore, although pipelining usually is used for improving the performance of processors, it also is an effective method to reduce static energy consumption.

#### **B)** Phase Switching

In general, modern day microprocessors are designed for the best performance. However, such best performance is not always needed in most applications. If certain periods of an application can be identified as "standby" or "dormant", many circuit level techniques can be applied to significantly reduce the leakage power. Then, identifying such phases in applications is a system level effort toward low power design. Some examples by using phase switching to reduce static power dissipation are presented in the following.

• M. Powell et al. (2000)

In [21], the authors found that there is a large variability in active cell usage both within and across applications. Thus, by using Gated- $V_{DD}$  Caches, they proposed to identify phases with unused SRAM cells and gate their supply voltage and reduce their leakage. Their results indicated that it highly reduces leakage-induced power dissipation with minimal impact on performance.

• E. Rohou et al. (1999)

E. Rohou et al. in [43] presented an adaptive approach that used feedback information to identify jobs in some phases which consume less power, and then switch phase contexts to manage processor temperature and reduce the leakage-induced static power dissipation. Their technique was implemented in the operating system so that it can both access hardware statistics and control the interleaving of processes. Results showed that their method could significantly reduce the static power dissipation with little cost in performance.

The designs presented in this section have focused on using phase switching to reduce static power dissipation at the system level. As known, the functioning of certain applications can be divided into various phases in which the processors can be of different level of activity. Therefore, identifying these phases helps in minimizing the static power dissipation. Designs discussed above attempted to switch the processor setting according to phases with different level of activities. Usually, the phase switching design is combined with other schemes, for example DVS, to reduce the static power dissipation.

In summary, many low-power techniques, varied from the fabrication engineering level to the system design level, have been proposed to address static power dissipation. However, there is a trade-off among product cost, system complexity and power saving when applying these static power reduction techniques discussed above. Therefore, careful designing is needed for static power dissipation optimizations. Even though we do not target the leakage reduction in our research work presented in this thesis, it is also important to know that there are so many techniques which could be combined to further reduce the overall power dissipation of a microprocessor.

## **2.2 Dynamic Power Dissipation**

### 2.2.1 Dynamic Power Dissipation Sources

For many years, efforts toward power reduction are mostly focused on reducing dynamic power dissipation, due to the extensive use of CMOS technology where leakage-induced power dissipation in the static state is many orders of magnitude smaller compared to power dissipated in dynamic switching of states. In general, dynamic power dissipation of microprocessors mainly arises from two circuit sources:

1) transient short-circuit current; 2) repeated charging and discharging of capacitive loads.

#### 2.2.1.1 Transient short-circuit current

The short-circuit current is incurred due to transient conduction in both the pull-up and pull-down circuits in the CMOS circuit. Because such transitions can not realistically be instant, it is possible that the shut-off network is turned on before the previously turned-on network is shut off. However, as is discussed in [42] and [44], this transient short-circuit current is not significant in most circuits, and thus it is often ignored.

#### 2.2.1.2 Repeated charging and discharging of capacitive loads

The major dynamic power dissipation comes from the charging and discharging of the state-keeping nodes. A low-to-high state transition corresponds to the charging up of all the capacitors associated with that node; while a high-to-low transition corresponds to the discharging of the node. With scaled feature sizes in modern transistors, the capacitance per unit area increases, accompanied by the increased switching frequency. Therefore, these trends lead to significant dynamic power dissipation in modern-day processors.

#### 2.2.1.3 Dynamic Power Dissipation model

In the conventional process technology, the dynamic power dissipation involved in the switching is estimated by

$$P_{dynamic} = \alpha \bullet C_{L} \bullet V_{DD} \bullet \Delta V \bullet f_{CLK}$$

(2.2)

Where  $\alpha$  is a constant of average activities and less than 1, C<sub>L</sub> is the load capacitance involved, V<sub>DD</sub> is the supply voltage,  $\Delta V$  is the swing of voltage between two states and f<sub>CLK</sub> is the switching frequency. For a normal switching in a CMOS circuit, the swing range is the full supply voltage. Supposing an amount of work that takes N clock cycles to finish, the time to finish the work is given by

$$T = \frac{N}{f_{CLK}}$$

(2.3)

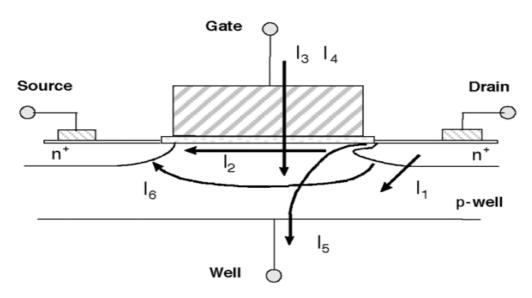

Furthermore, as is presented in [41], the maximum clock frequency achievable shows a nearly linear dependence upon the supply voltage, which is illustrated in Figure 2.4 below.

Fig. 2.4: Maximum Clock Frequency vs. Supply Voltage [41]

Thus we can approximately put:

$$f_{CLK} = k \bullet V_{DD} \tag{2.4}$$

As a result, the dynamic power can be estimated by:

$$P_{dynamic} = \left( \alpha \bullet C_{L} \bullet k \right) \bullet V_{DD}^{-3}$$

$$(2.5)$$

Obviously, the supply voltage has a very strong effect on the dynamic power dissipation. This leads to the wide-spread employment of voltage scaling techniques to reduce dynamic power dissipation.

## 2.2.2 Dynamic Power Dissipation Reduction

In this section we review the low power techniques that target dynamic power dissipation. From the design strategy, these techniques are also grouped into either circuit-level or system level.

#### 2.2.2.1 Circuit-level Techniques

As shown in the previous section, the dynamic power dissipation can be modeled by:

$$P_{dvnamic} = \alpha \bullet C_{L} \bullet V_{DD} \bullet \Delta V \bullet f_{CLK}$$

(2.6)

As we can see from the above formula, it is natural to think of reducing the voltage swing ( $\Delta V$ ) and supply voltage ( $V_{DD}$ ) to minimize the dynamic power dissipation. In general, the voltage swing can be reduced by the use of low-swing signaling, while the supply voltage can be reduced by the use of dynamic voltage scaling. We will detail the two low-power schemes in the following section.

#### A) Low-swing Signaling

As is discussed in the above, a straight-forward method to achieve dynamic power reduction is to reduce the signal swing. As known, low-swing technology provides high speed and low power at the same time. Instead of driving signals rail-to-rail, special drivers allow reduced signal swing. This may directly result in linearly reduced dynamic power, as expressed by the above equation. At the same time, the time needed to charge or discharge a node is also reduced, enabling faster state switching. In the following, we will present some research work using this technique to reduce dynamic power dissipation of microprocessors.

• T. Sakurai et al. (1997)

In 1997, T. Sakurai et al. [45] described some circuit level techniques for low-power CMOS designs. In particular, the authors discussed the low swing signaling technique, and presented its applications to a clock system, logic part, and I/O's. They concluded that the low swing signaling technique is useful to reduce dynamic power dissipation.

• H. Zhang et al. (2000)

In the study of [46], H. Zhang et al. reviewed a number of low-swing on-chip interconnect schemes and presents a thorough analysis of their effectiveness and limitations, especially on energy efficiency and signal integrity. After that, they proposed several new interface circuits which employed low swing signaling, and achieved more energy savings and better reliability in experiments than former schemes.

• F. Worm et al. (2002)

In [47], F. Worm et al. introduced and showed the results of a interconnect system using low-swing signaling, which minimized the interconnect voltage swing and frequency subject to workload requirements and S/N conditions. Results showed that their scheme can attain tangible savings in energy, at the same time, achieving more robustness to large variations in actual workload,

noise, and technology quality.

• W. Jeong et al. (2004)

Recently, in 2004, W. Jeong et al. [48] proposed an adaptive supply voltage technique for low swing interconnects. To implement a low swing signaling design, their proposed technique assigned different supply voltages to drive interconnects based on their delay. Simulation results showed that their design could obtain very high power saving.

The designs presented in this section have focused on using the low-swing signaling technique to reduce dynamic power dissipation at the circuit level. As found by researchers, current-mode low-swing signaling techniques provide an attractive alternative to conventional full-swing voltage mode signaling in terms of delay and power dissipation [49, 50]. All these example designs presented here showed that low-swing technology is very useful to minimize the dynamic power dissipation, and provides both high speed and low power. For example, the low-swing signaling technique is already employed in the arithmetic core of Pentium 4 Processors [51].

#### **B)** Dynamic Voltage Scaling

Dynamic Voltage Scaling (DVS) is by far the most popular technique in use to reduce dynamic power dissipation. As is deducted in Section 2.2.1, dynamic power has a cubic relationship with the supply voltage in conventional CMOS circuits, while the maximum clock frequency is approximately proportional to supply voltage. Thus, supply voltage reduction, which usually implies a frequency reduction, could produce a significant power saving. Over the past years, many researchers worked in DVS to reduce dynamic power dissipation of computer systems, which will be presented in the following.

• T. Ishihara et al. (1998)

In [52], T. Ishihara et al. presented a theoretical study on dynamic voltage scheduling. In their work, they set up a model of dynamically variable voltage processor and analyzed it for power/energy reduction. Eventually, based on their model, they gave basic theorems for power-delay optimization of DVS.

• I. Hong et al. (1999)

In 1999, I. Hong et al. [53] developed a design methodology for the low power core-based system, based on dynamically variable voltage hardware. Their synthesis technique addressed the selection of the processor core and the determination of the instruction and data cache size and configuration so as to fully exploit dynamically variable voltage hardware, which resulted in significantly lower power dissipation for a set of target applications than existing techniques. As they showed, their approach was effective in a variety of modern industrial-strength multimedia and communication applications.

• K. Flautner et al. (2001)

In [54], the authors described a software approach to automatically control dynamic voltage scaling in order to optimize energy use, which was implemented in the Linux kernel and required no modification of user programs.

Their method worked equally with irregular and multi-programmed workloads and ensured that the quality of interactive performance is within user specified parameters. Their experiments showed a good result of high energy savings and only a minimal impact on the user experience.

• A. Azevedo et al. (2002)

In 2002, A. Azevedo et al. [55] proposed an intra-task DVS technique under compiler control using program checkpoints. Their defined checkpoints, which carried user-defined time constraints, were generated at compile time and indicated places in the code where the processor speed and voltage should be re-calculated. Checkpoints also carried user-defined time constraints. Their technique handled multiple intra-task performance deadlines and modulated power dissipation according to a run-time power budget. Results showed that their technique resulted in 82% energy savings over the execution of the program without employing DVS.

• K. Choi et al. (2005)

Recently in 2005, K. Choi et al. [56] presented an intra-process dynamic voltage and frequency scaling (DVFS) technique targeted toward non real-time applications running on an embedded system platform. Their DVFS technique relied on dynamically-constructed regression models that allow the CPU to calculate the expected workload and slack time for the next time slot, and thus, adjust its voltage and frequency in order to save energy while meeting soft

timing constraints. This was in turn achieved by estimating and exploiting the ratio of the total off-chip access time to the total on-chip computation time. Results showed that their scheme achieved very high CPU energy saving and low performance degradation for both memory-bound programs and CPU-bound programs.

The designs presented in this section have focused on using DVS to reduce dynamic power dissipation at the circuit level. DVS is the technique for exploiting this tradeoff whereby an appropriate clock rate and voltage is determined in response to dynamic application behavior. A number of DVS algorithms have been proposed to address power/energy optimization issues [57, 58, 59]. As known, DVS has been widely used in modern commercial chips such as Pentium 4 [51]. Furthermore, it is highly compatible with all kinds of circuit structures from memory to logics. It can also be combined with many other dynamic and static power reduction techniques to further minimize power dissipation. Currently, the key challenge is to develop effective DVS scheduling techniques that treat voltage as a variable to be determined, in addition to the conventional task scheduling and allocation. In the next chapter, we will discuss some algorithms for DVS and talk about the motivation for our low power design schemes using DVS.

#### 2.2.2.2 System-level Techniques

At a higher system level, some techniques have also been proposed to reduce dynamic power dissipation. In general, these techniques all make use of system level information to reduce either the voltage swing or the supply voltage.

#### A) Signal Swing

As is well-known, in CMOS circuits, frequent signal switching consequently produce much voltage swing. Therefore, some researchers suggested reducing the signal swing to minimize the overall voltage swing.

• S. Haga et al. (2003)

Signal switching usually happens at the input port, output port and inside of the functional unit (FU). In [60], S. Haga et al. proposed a hardware method for functional unit assignment, based on the principle that a functional unit's power dissipation is approximated by the switching activity of its inputs. It dynamically assigned instructions to carefully selected Functional Units to minimize signal switching that happens in the FU. In their design, instructions are preferably issued to FU where the previous operands are similar to the current operands. This is illustrated in Figure 2.5.

#### Default routing

Alternative routing (57% less energy)

Fig. 2.5: Dynamic Functional Unit Assignment [60]

By using their design, voltage switching happening at the FU is reduced. The

simulation results showed a high reduction of switching activities in various FU and consequently achieved high power reduction.

The design presented in this section has focused on minimizing signal swing to reduce dynamic power dissipation at the system level. Some researchers proposed to use low-voltage swing circuits and techniques for microprocessors to reduce its power dissipation [61, 62]. As showed above, although the dynamic power dissipation is reduced, this is achieved at the price of extra hardware that carries out the comparing of the operands. Therefore, additional algorithms are needed to minimize the hardware cost.

#### **B) State Switching**

Scaling the supply voltage can considerably reduce the dynamic voltage at the price of slower execution speed. Thus, the best trade-off between power and performance can be achieved by switching between a spectrum of "active" and "standby" states. Therefore, some designs are suggested to reduce dynamic power dissipation by carefully switching states during system execution, which are presented in the following.

• W. Kim et al. (2002)

In [63], W. Kim et al. proposed a DVS algorithm for periodic hard real-time tasks based on an improved slack estimation algorithm. By deciding the state of different tasks and executing switches between states, their proposed method took advantage of the periodic characteristics of the real-time tasks under priority-driven scheduling, such as EDF. Experimental results showed that their algorithm reduced the energy consumption by 20~40% over the other DVS algorithms. Their experiment results also showed that their algorithm based on state switching gave comparable energy savings to the DVS algorithm based on the theoretically optimal (but impractical) slack estimation method.

• A. Sinha et al. (2001)

In [64], A. Sinha and A. P. Chandrakasan proposed an adaptive approach to switch states of processors for dynamic voltage scheduling, based on workload prediction by filtering a trace history. In this work, a performance hit metric is defined and a state-switching technique to minimize energy under a given performance requirement is outlined. Their results demonstrated that up to two orders of magnitude energy savings is possible with dynamic voltage scheduling depending on workload statistics.

The designs presented in this section have focused on using state switching to reduce dynamic power dissipation at the system level. These approaches all lead to better power-performance results in microprocessors. In general, this state switching decision can be made by either hardware or software. If it is done by the hardware, additional hardware has to be added and consequently increase the hardware complexity.

## 2.3 Summary

In this chapter, both static and dynamic power dissipation are discussed. Firstly, we reviewed different sources for static and dynamic power dissipation. Following that, various existing techniques for static and dynamic power reduction have been discussed. In general, many of these static and dynamic power reduction techniques can be combined to minimize the overall power dissipation. For example, our low power design schemes presented in following chapters are going to combine phase switching, state switching and dynamic voltage scaling to reduce the overall runtime power dissipation of microprocessors. The detailed implementation of our schemes will be introduced later in this thesis.

## **Chapter 3**

## **Motivation and Analysis Model**

This chapter describes the motivation and the analysis model for our low-power design schemes presented in this thesis. It is structured as follows. In Section 3.1 we describe the motivation for our approaches. In Section 3.2, we first present the analysis model for our schemes, and then discuss the trade-off between power and performance in our low-power designs. In Section 3.3, we summarize this chapter.

## **3.1 Motivation**

As is discussed in the previous chapter, Dynamic Voltage Scaling (DVS) is by far one of the most popular power reduction techniques in use. Basically, DVS is a technique that varies the supply voltage and frequency of a microprocessor to provide a desired performance with the minimum amount of energy consumption. As an efficient technique to reduce energy consumption, dynamic voltage/frequency scaling (DVFS) has already been used in many computer systems, such as those based on the Transmeta Crusoe[65] and Intel XScale[66] processors.

Various algorithms had been proposed to use DVS to match the changing demands for microprocessor processing speed to achieve reduction of runtime power dissipation. In general, these approaches analyzed system or program dynamic behaviors, adjusted microprocessor settings to better match its performance requirements, and consequently reduced system/application power dissipation. As known, previous work has been studied exhaustively at the operating system (OS) level and the source code level to employ DVS to achieve power-performance trade-off optimization.

## **3.1.1 OS Level DVS Algorithms**

Algorithms running at the OS level usually use heuristic methods to reduce power dissipation in response to variations in workload during runtime. In general, OS level runtime algorithms use prediction approaches to monitor the current system load and estimate the future demand by using interval-based schedulers with a time window. In 1994, M. Weiser et al. [67] suggested an interval-based predicting algorithm to dynamically scale the frequency and voltage of the processor. Their algorithm divided time into fixed-length intervals and set each interval's speed so that most work is completed by the interval's end. Thereafter, E. Chan et al. [68] in 1995 refined the idea by separating it into two parts: prediction and speed-setting. At the front of an interval, the prediction part estimates how busy the CPU will be during the interval, which is measured via the non-idle fraction of the last interval. The speed setting part uses this information to set the speed of processor.

As known, M. Weiser et al. are the pioneers of the DVS research by first designing the interval-based prediction DVS algorithm at the OS level. Since then, following their idea, many interval-based DVS algorithms [69, 70] have been proposed. Recently in 2008, Seo et al. [105] presented a time-slice based DVS algorithm to adjust processor performance at every context switch in order to match the performance demand of the next scheduled task. In general, evaluations of these algorithms through simulations showed that they all achieved good results in power savings.

As discussed above, all these OS-based predictive algorithms aim to reduce power dissipation without degrading application performance. However, in a recent study in 2000, D. Grunwald et al. [71] used actual measurements and observed noticeable performance loss for some interval-based algorithms running at the OS level. One possible reason is the misunderstanding about future performance demand of CPU, and it could be caused by inaccurate predictions at the high OS level. As studied in [72], researchers found that the OS itself could have a strong impact on application performance sometimes; hence it will also affect the prediction results in these algorithms, thereby leading to wrong decisions by DVS scheduler and the accompanying performance penalty.

This observation motivates us to estimate the future performance demand of CPU at a lower micro-architecture level to avoid such misunderstandings, because at the micro-architecture level it relies solely on the hardware to identify current performance of CPU and thus obtain a more reliable prediction for future performance demand. Therefore, we propose a micro-architecture level identification and prediction algorithms in the following of this thesis.

## **3.1.2 Source-code Level DVS Algorithms**

Beside DVS approaches employed at the OS level, researchers have addressed low-power

DVS designs at the source-code level, and proposed that applications themselves provide information about their future performance demands, such as deadlines of real-time tasks and other timing constraints.

For applications used in the real-time system, researcher usually utilized hard real-time constraints of tasks as their performance demands to direct DVS scheduling to reduce power dissipation of microprocessors. For example, J. Pouwelse et al. [73] proposed an approach for real-time applications: it indicated the required number of clock cycles (instructions) for the next deadline and allowed the CPU to compute with the lowest speed at which this application could also meet its deadline.

For non real-time applications, researchers suggest using mode-set instructions as performance indicators for the CPU to dynamically schedule its setting. In the work of [74], C. H. Hsu et al. proposed a compiler-based method to reduce the power dissipation in microprocessors. First of all, the authors identified single or multiple regions of a program, which may be memory-bound regions where the CPU can be slowed down without significant performance impact. Then, they employed a nonlinear optimization formulation to insert their defined power-down instructions at regular intervals in the program. Finally, they lowered the voltage and frequency of CPU when encountering these instructions during application execution. Similarly, in [75], M. Huang et al. implemented a profile-based method. It first identified the most frequently executed functions/modules of an application during its training runs, and then used a selection algorithm to choose the best low-power configuration for each module after profiling its runs with mode-set instructions. In both methods, the researchers directed the voltage scaling of microprocessors by their defined indicators, and eventually reduced the energy consumed by microprocessors. Recently, Zhou et al. [106] in 2005 suggested a combination of optimal speed and limited preemption as mode settings for a dynamic task scheduling algorithms for periodic tasks that minimize the system-level energy; Malani et al. [107] in 2007 proposed a profile-based low power scheduling by using conditional task graph to differentiate different modes.

In [76], D. Mosse et al. presented a method that profiles program regions by mode-set instructions and simultaneously meets their hard time constraint--the worst case execution time (WCET) assumption when determining a voltage scaling schedule. Actually, this method combined the two approaches discussed above, integrating the mode-set indicator into the real-time applications that have hard deadlines, to direct DVS to decrease the total energy consumption.

All the above DVS algorithms running at the source-code level gained power-performance tradeoffs by using various performance indicators to direct DVS scheduling. During execution time of applications, an optimal processor setting, such as appropriate voltage and frequency, can be chosen to minimize its power dissipation and still meet application performance requirement. For all these source-code level DVS algorithms, their evaluations through experiments showed that they most often achieved good results with high power reduction.

However, in the above algorithms running at the source-code level, all the applications must be aware of their processing performance demands in advance. For

applications of real-time systems, there is no problem because they could use hard real-time constraints, which have been clearly defined in the source code, as performance indicators to direct DVS scheduling. But, for applications used in general-purpose systems, such performance demands are usually unknown in advance since these applications have no explicit deadline or other hard timing constraints.

This observation motivates us to employ the micro-architecture parameters, which could be obtained from execution results of non real-time applications, as performance indictors to direct DVS scheduling and thus void limitations of former source-code level algorithms. Therefore, in this thesis, we propose a code analysis and reconfiguration mechanism by using the micro-architecture parameters to direct DVS scheduling.

## 3.1.3 Our Micro-architecture Level DVS Algorithms

As discussed above, in this thesis, we propose two novel algorithms to schedule DVS at the micro-architecture level to achieve successful low-power designs for microprocessors.

#### A) Identification and Prediction Algorithm

To estimate a reliable future performance demand of microprocessors, we propose a micro-architecture level identification and prediction algorithm.

This algorithm employs a micro-architecture parameter, Instructions per Cycle (IPC), as the runtime performance indicator to dynamically scale the voltage and frequency of a processor. In this design, we obtain the micro-architecture parameter (IPC)

40

through hardware support in the processor, and use it to quantify the knowledge of the most recent performance requirements for each program interval and guide the voltage and frequency scaling. Thus, it avoids the impact of the OS on the prediction results in former OS level DVS algorithms. Therefore, the DVS decisions made by our micro-architecture level identification and prediction algorithm are more reliable, resulting in bigger energy reduction and smaller performance losses.

#### **B)** Code Analysis and Reconfiguration Algorithm

Using the micro-architecture parameters as performance indicators, we propose a code analysis and reconfiguration mechanism to direct DVS scheduling.

In this mechanism, we first identify code regions of an application that have low performance requirements and could make contributions to runtime power reduction. We utilize the micro-architecture parameter (IPC), which is obtained from execution results of application training runs, as the performance indicator to identify such code regions. Then, we profile these code regions to dynamically scale the voltage and frequency of the microprocessor during application execution.

In our design, the micro-architecture parameter (IPC) could be estimated from execution results of non real-time applications, thereby avoiding the limitations of former source-code level algorithms. Furthermore, based on execution results of application training runs, our mechanism practically identifies power-performance tradeoff opportunities in applications and thus avoid inappropriate switch points for DSV scheduling. Thus, our micro-architecture level code analysis and reconfiguration mechanism is more reliable, thereby leading to more power reduction and less performance degradation.

However, for any profile-driven algorithms based on application training runs, a common question is how much the quality of the execution results is affected by the training runs.

To answer the above question, it is very important to identify how many factors affect the execution results of a program. Firstly, the results may be affected by the program source code. Different source codes to implement the same function in a program will lead to variations of the execution results. Secondly, the results may be affected by the compiler. Different compilers may have distinguishing strategies to optimize the program source code, resulting in differences in the binary files and the execution results. Thirdly, the results may be affected by the processor architecture implementations. For the same binary file of a program, the execution results may be quite different when executing on processor architecture with different implementations. Lastly, the results may be affected by different input data sets. The execution process of any application may also be data-sensitive, and different input data will lead to many differences in the execution results. Overall, there are many factors that can influence the execution results of an application. Therefore, it is quite difficult for profile-based methods to guarantee the capture all execution behaviors through training runs.

However, for these profile-based methods, some approaches could be applied to avoid or reduce these influences on the execution results, Firstly, to avoid the

42

affections from the source code and compilers, we can made use of the same binary file of applications in both training runs and later executions. Secondly, to avoid the affection from the processor architecture, we can perform the binary file on a processor with the same architecture implementation. Lastly, we can minimize the affection from input data sets by using good training inputs, which could well match the real instance of application execution and thus well capture the execution behavior of applications. As is well known, it is impossible to eliminate the affection caused by the input data sets since different input files have to be used between the training runs and later executions.

In our code analysis and reconfiguration mechanism, we applied the above approaches to avoid or diminish such affections. For this aim, we chose the well-developed benchmarks (SPEC [77] and MediaBench [78]) in our experiments. In both the training runs and the subsequent actual executions, we performed the same object files, which are supplied by the benchmark suits, on a processor with the same architecture. Thus, we avoid the first three factors. Furthermore, in the benchmark suits, the reference inputs for training runs can well capture the execution behaviors of applications. Thus, we well identified power optimization opportunities in applications from the results of training runs, which is proved by the good results in our experiments.

Overall, our proposed micro-architecture level low-power designs in this thesis could reduce the power dissipation of microprocessors, at the same time, with little performance degradation. Results of our designs show that it is more efficient to

43

address low-power optimizations at the micro-architecture level.

## **3.2 Analysis Model**

As is discussed in the previous section, the primary idea of our low-power design schemes is an attempt to identify power reduction opportunities in an application where a possible CPU slowdown will not significantly affect the performance. In the following, we will first present a realistic model for our low-power designs. Then, based on the model, we will analyze potential code regions in an application which have such possible opportunities. Lastly, we will discuss the constraints and the resulting penalty for using the model in our low-power strategies.

To derive our analysis model, first of all, we make the following assumptions about the application and the micro-architecture implementation of microprocessors:

- The logical behavior of an application does not change with the voltage and frequency scaling of microprocessors.

- ✓ Peripheral components, such as I/O and memory, are asynchronous with the microprocessor.

- $\checkmark$  The clock is gated when the processor is idle.

## **3.2.1 Basic Model**

Since the goal of our designs is to identify power reduction opportunities in an application, this model is going to define and analyze the problem from the aspect of program code.

Firstly, we shall identify different types of code regions in a program, corresponding

to various operations related to CPU. In general, any program is a union of code regions. In our model, an entire program is divided into two major code regions: CPU computing operation region and peripheral operation region. For the CPU computing operation region, it again can be divided into two sub-sets: parallel computing operation region, which can run concurrently with the peripheral operations; dependent computing operation region, which has to be pended and wait for the results of peripheral operations.

For the above three operations in a code region, we make use of three corresponding parameters ( $W_{di}$ ,  $W_{pi}$ ,  $W_{mi}$ ) to quantify their workload (in cycles). In the following, we will describe the detailed definitions for the three parameters employed in our model:

$W_{m \ i}$ : the number of execution cycles cost in region  $R_i$  where peripheral operations are executed, including memory-bound and I/O-bound operations. For memory-bound operations, both cache hit and cache miss operations are taken into account.

$W_{p\,i}$ : the number of execution cycles cost in region  $R_i$  where CPU computing operations can run in parallel with peripheral operations, which means both operations are active at the same time during execution.

$W_{d}$  *i*: the number of execution cycles cost in region  $R_i$  where the CPU computing operation is stalled while waiting for data from peripheral operations, which means that is dependent on peripheral operations.

Then, the total workload for code region  $R_i$  is defined as  $W_i = W_{di} + W_{pi} + W_{mi}$ ,

45

and the total workload for program *P* is defined as  $W = \sum_{i} W_i$ .

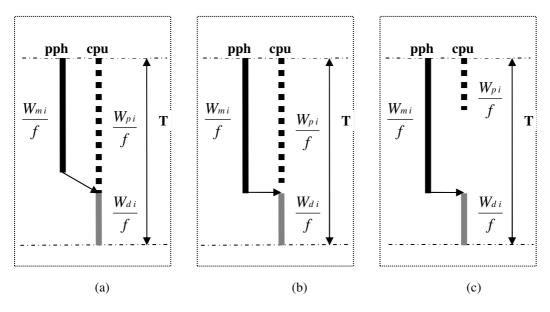

Fig. 3.1: Possible overlaps in peripheral and CPU computing operations.

As shown in Figure 3.1, we can illustrate the execution of any code region in a program within the three cases, corresponding to different relative workload of the above defined three operations. In these figures, "T" is the execution time to complete the code region, "pph" is the peripheral operations, "CPU" is the CPU computing operations, and "f" is the frequency of a processor.

In the case shown in Figure 3.1(a), the parallel CPU computing operations dominate the overlap part, and they take relatively longer time than the peripheral operations. Thus, the execution time of the overlap part is determined by the parallel computing operations. For a code region in this case, its total execution time is decided by the time for CPU to finish the computing operations, and could be expressed as  $W_{pi}/f + W_{di}/f$ . Thus, for this case, we define it as a computation-dominated case.

In the case shown in Figure 3.1(b), the peripheral operations dominate the overlap part, but the time cost by the peripheral operations nearly equals that of the parallel