### INTERACTIVE DESIGN SPACE EXPLORATION

### OF

### **REAL-TIME EMBEDDED SYSTEMS**

### UNMESH DUTTA BORDOLOI

### NATIONAL UNIVERSITY OF SINGAPORE

$\boldsymbol{2008}$

# INTERACTIVE DESIGN SPACE EXPLORATION OF REAL-TIME EMBEDDED SYSTEMS

#### **UNMESH DUTTA BORDOLOI**

(B. Tech., Computer Science Engineering, National Institute of Technology, Rourkela, India)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE

$\boldsymbol{2008}$

# List of Publications

- U. D. Bordoloi and S. Chakraborty. Accelerating System-Level Design Tasks using Commodity Graphics Hardware: A Case Study. Accepted to International Conference on VLSI Design (8th International Conference on Embedded Systems), January 2009.

- U. D. Bordoloi. Interactive Performance Debugging of Real-Time Embedded Systems, SIGDA PhD Forum, *Design Automation Conference (DAC)*, June 2008.

- U. D. Bordoloi and S. Chakraborty. Interactive Schedulability Analysis. *ACM Transactions on Embedded Computing Systems (TECS)*, pages 1-27, Volume 7, Issue 1, December 2007.

- 4. U. D. Bordoloi, S. Chakraborty, and A. Hagiescu. Performance Debugging of Heterogeneous Real-Time Systems. Book Chapter in Next Generation Design and Verification Methodologies for Distributed Embedded Control Systems, pages 285-300, Springer Netherlands, 2007.

- 5. J. Feng, S. Chakraborty, B. Schmidt, W. Liu, and U. D. Bordoloi. Fast Schedulability Analysis Using Commodity Graphics Hardware. In Proc. 13th International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), pages 400-408, IEEE Computer Society, 2007.

- A. Hagiescu, U. D. Bordoloi, S. Chakraborty, P. Sampath, P. V. V. Ganesan, and S. Ramesh. Performance Analysis of FlexRay-based ECU Networks. *In Proc.* 44th Design Automation Conference (DAC), pages 284 - 289, ACM, 2007.

- U. D. Bordoloi and S. Chakraborty. Performance Debugging of Real-Time Systems using Multicriteria Schedulability Analysis. In Proc. 13th Real-Time and Embedded Technology and Applications Symposium (RTAS), pages 193-202, IEEE Computer Society, 2007.

- 8. U. D. Bordoloi and Samarjit Chakraborty. Interactive Schedulability Analysis. In Proc. 12th Real-Time and Embedded Technology and Applications Symposium (RTAS), pages 147-156, IEEE Computer Society, 2006. (Invited to a special issue of ACM Transactions on Embedded Computing Systems, on selected best papers from RTAS'06).

# Acknowledgments

These past few years as a doctoral researcher have been one of the most memorable and enjoyable times of my life. I would like to acknowledge the wonderful people without whom this experience would not have been possible.

Throughout my PhD candidature, I have received valuable guidance and stimulating suggestions from Dr. Samarjit Chakraborty and I am grateful to him for this. His positive outlook and zeal for research has inspired me on countless occasions. I also appreciate his patience for thoroughly revising my written manuscripts and providing insightful feedback. Dr. Samarjit Chakraborty has also been a friend and I have immensely benefited from his help and advice. Indeed, it is rare to meet personalities with such unassuming nature.

I am grateful to all the members of my dissertation committee for writing the reports in such short time inspite of their busy schedules. I would like to thank Dr. P. S. Thiagarajan and Dr. Weng Fei Wong for suggesting significant improvements. Thanks are also due to Dr. Marco Platzner for being my external reviewer and for his valuable remarks and corrections.

This thesis would be incomplete without the contributions of my colleagues Jimin Feng and Andrei Hagiescu, colleagues at Embedded Systems Lab. Discussions with researchers at Nanyang Technical University and at General Motors, India Science Lab have lead to fruitful projects, and I gratefully acknowledge their help. I also thank Dr. S. Ramesh at General Motors, India Science Lab, for useful advice and encouragement during my research work.

It was my good fortune to have amazing lab-mates in the Embedded Systems Lab. I have fully exploited the privilege of being a part of this truly enjoyable environment to ask anyone for all kinds of help, without thinking twice. Indeed, without all the help that you guys offered, I would have been overwhelmed with my numerous issues with latex, code, and what not! I also appreciate all the enlightening discussions, technical and non-technical, with all of you that were so much a part of my graduate life.

Thanks to the responsive and capable workforce at Technical Helpdesk, there were hardly any issues with any technical equipment that I had to use. I also appreciate the efficient administrative work of the Graduate Office, School of Computing, especially Ms. Loo Line Fong.

I sincerely thank the National University of Singapore for supporting me financially, and encouraging me with generous Fellowships.

Unlimited love has been showered on me from all my relatives, uncles, aunts, and cousins, and I have been blessed with an incredible family. I have a terrific Kokaideo (elder brother), one with a PhD in computer science. His wisdom has benefited me all my life, and because of his wise words, I knew from day one what to expect in a PhD. I have a spirited and smart sister, Xuwodi, and her cheerfulness always keeps my spirits up.

Finally, there is no means by which I may repay all the sacrifices that my parents made for me. Without their far-sightedness, and broad-mindedness, this journey would have been never possible.

# Contents

| Li            | st of           | Publications                                                     | i          |

|---------------|-----------------|------------------------------------------------------------------|------------|

| C             | onter           | nts i                                                            | ii         |

| A             | cknov           | wledgments i                                                     | ii         |

| $\mathbf{A}$  | bstra           | ict                                                              | x          |

| $\mathbf{Li}$ | List of Figures |                                                                  |            |

| Li            | st of           | Tables xv                                                        | / <b>i</b> |

| 1             | Intr            | roduction                                                        | 1          |

|               | 1.1             | Design Space Exploration                                         | 3          |

|               |                 | 1.1.1 Role of Performance Analysis in Design Space Exploration . | 4          |

|               |                 | 1.1.2 Challenges                                                 | 5          |

|               | 1.2             | Thesis Contributions                                             | 7          |

|               | 1.3             | Organization of this Thesis                                      | 2          |

| <b>2</b> | Inte | ractive | e Schedulability Analysis                                      | 13 |

|----------|------|---------|----------------------------------------------------------------|----|

|          | 2.1  | The R   | ecurring Real-Time Task Model and its Schedulability Analysis  | 19 |

|          |      | 2.1.1   | Task Sets and Schedulability Analysis                          | 22 |

|          |      | 2.1.2   | The demand-bound function                                      | 23 |

|          |      | 2.1.3   | Computing the demand-bound function                            | 25 |

|          | 2.2  |         | ctive Schedulability Analysis for the Recurring Real-Time Task | 27 |

|          |      | 2.2.1   | Relaxing the Deadline of a Vertex                              | 29 |

|          |      | 2.2.2   | Constraining the Deadline of a Vertex                          | 36 |

|          |      | 2.2.3   | Running Times                                                  | 39 |

|          | 2.3  | Experi  | imental Results                                                | 40 |

|          |      | 2.3.1   | Experiments with Step (i)                                      | 40 |

|          |      | 2.3.2   | Experiments with Step (ii)                                     | 46 |

|          | 2.4  | Provid  | ling Feedback to the System Designer                           | 46 |

|          |      | 2.4.1   | Illustration of the Feedback Provided for an Example Task Set  | 49 |

|          | 2.5  | Summ    | ary                                                            | 51 |

vi

| 3 | Effi           | ciently Computing Performance Tradeoffs using Multicriteria        |    |

|---|----------------|--------------------------------------------------------------------|----|

|   | $\mathbf{Sch}$ | edulability Analysis                                               | 53 |

|   | 3.1            | Task Model                                                         | 61 |

|   | 3.2            | The Single-Criteria Problem                                        | 62 |

|   |                | 3.2.1 NP-hardness                                                  | 64 |

|   |                | 3.2.2 Approximating the Minimum Cost Schedulable Solution $\ldots$ | 65 |

|   | 3.3            | Multicriteria Schedulability Analysis                              | 69 |

|   |                | 3.3.1 The GAP Problem                                              | 70 |

|   | 3.4            | Experimental Results                                               | 75 |

|   |                | 3.4.1 Running Times                                                | 76 |

|   |                | 3.4.2 Size of the Pareto Curves                                    |    |

|   | 3.5            | Summary                                                            | 79 |

| 4 | GP             | U-Based Acceleration of System-Level Analysis Tools                | 81 |

|   | 4.1            | GPU Architectures                                                  | 84 |

|   | 4.2            | Case Study 1: GPU-based Acceleration of Schedulability Analysis    |    |

|   |                | Problem                                                            | 87 |

|   |                | 4.2.1 Schedulability Analysis of Recurring Real-Time Task Sets .   | 87 |

|   |                | 4.2.2 Schedulability Analysis on GPUs                              | 89 |

|   |     | 4.2.3 Results and Discussion                                     |

|---|-----|------------------------------------------------------------------|

|   | 4.3 | Case Study 2: GPU-based Acceleration of Design Space Exploration |

|   |     | Problem                                                          |

|   |     | 4.3.1 Task Model                                                 |

|   |     | 4.3.2 The Problem Statement                                      |

|   |     | 4.3.3 A Pseudo-polynomial Time Algorithm                         |

|   |     | 4.3.4 The Design of GPUPareto                                    |

|   |     | 4.3.5 Experimental Results                                       |

|   | 4.4 | Summary                                                          |

| 5 | Per | formance Analysis of FlexRay-based ECU Networks 109              |

|   | 5.1 | Overview of FlexRay                                              |

|   | 5.2 | Basic Framework                                                  |

|   |     | 5.2.1 Difficulties in Modeling FlexRay                           |

|   | 5.3 | Illustrative Examples                                            |

|   | 5.4 | Modeling FlexRay                                                 |

|   | 5.5 | Adaptive Cruise Control Application: A Case Study                |

|   | 5.6 | Summary                                                          |

| 6 | Cor | clusion 145                                                      |

|   | 6.1 | Future Work                                                      |

# Abstract

A typical design of a real-time embedded system involves an iterative design space exploration process. In general, the design space exploration strategy needs to address two separate concerns.

- 1. How to cover the entire design space during the exploration process? Typically, the designer is confronted with a prohibitively large design space, where the design points are associated with conflicting tradeoffs with respect to various performance metrics like real-time response, costs etc.

- 2. How to quantitatively evaluate a single design point with respect to the various performance metrics? The designer needs to run a *performance analysis* to evaluate each design point, and for most realistic system models such *performance analysis* is time consuming.

The above issues lead to tedious iterations during design space exploration of realtime embedded systems. A system designer would choose the values of the system parameters and define an initial design point. The designer would then invoke a *performance analysis* tool to evaluate the performance metrics corresponding to the design point. If the designer is not satisfied with the resulting performance numbers, then he/she would modify some of the parameters and invoke the *performance analysis* once again. This iterative design space exploration is repeated until a satisfactory design is found. Unfortunately, as discussed above, each time the *performance analysis* tool is invoked it takes a long time to run — which might be in the tune of several hours – and this critically impacts the usability of the tool in the interactive design space exploration sessions.

Current approaches rely mostly on ad-hoc techniques like genetic algorithms to handle the high running times associated with such iterative design space exploration processes. In this thesis we present systematic/formal approaches which provide provable performance guarantees. We propose (i) novel algorithmic techniques (both exact and approximate), as well as (ii) hardware-based techniques to accelerate the computationally expensive *performance analysis* in each iteration. We also introduce (i) a scheme to approximate the potentially exponential sized design space with only a polynomial number of points and (ii) techniques to provide insightful feedback to the designer regarding the design parameters he may choose to modify in each iteration. In particular, this thesis makes the following contributions.

• We introduce the novel concept of "interactive" design space exploration to accelerate each iteration in an interactive design session. We demonstrate our idea with respect to a schedulability analysis problem. Our algorithm is based on the observation that if only a small number of system parameters are changed in each iteration, then it is not necessary to re-run the full schedulability analysis algorithm, thereby making the iterative design process considerably faster. We demonstrate that using our scheme can lead to more than 20× speedup for each invocation of the schedulability analysis algorithm, compared to the case where the full algorithm is run. Such fast iterations also allow the designer to evaluate the schedulability for much larger design space within a short time. We also outline some techniques for

providing feedback on the potential system parameters that can be changed to obtain a schedulable system when a task set is not schedulable.

- Design space exploration for hardware/software co-design involves identifying all possible implementations to expose the different possible performance tradeoffs associated with each of them. Unfortunately, the problem of optimally computing even one feasible solution in most common setups is computationally intractable (NP-hard). In this thesis we derive a polynomial-time approximation algorithm for solving it. Furthermore, our scheme also approximates the potentially exponential sized solution set with only a polynomial number of points. This is more meaningful from a practical perspective, as the designer is presented with a reasonably few well-distinguishable tradeoffs, rather than an exponentially large number of solutions, many of which are similar to each other.

- We introduce the new technique of employing graphics processing units (GPUs) to lower the high running times associated with heavy duty kernels of design space exploration problems. To demonstrate our idea, we present GPU-based engines to diminish the long running times associated with an expensive hardware/software design space exploration problem and a schedulability analysis problem. Our experiments on the GPU demonstrate tremendous speed up (upto 100×) of the expensive kernel of our problems.

- Apart from the above, we have also been concerned real-life design issues, specially in the automotive domain. In this regard, we have developed novel analytical methods which facilitate fast design space exploration of system parameters for safety-critical applications in the automotive domain. In contrast to traditional simulation methods which take hours to run, our analytical model returns results in a matter of few seconds, and is ideal for interactive design sessions.

To summarize, this thesis is concerned with issues arising in design space exploration of real-time embedded systems. Interactive design cycles associated with design space exploration techniques are known to be tedious, and this thesis proposes novel algorithmic, analytic and hardware-based techniques to ease the tedious design cycles.

# List of Figures

| 1.1  | Role of Performance Analysis in Interactive Design Space Exploration                                                                                                                                                  | 4  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | An example recurring real time task                                                                                                                                                                                   | 20 |

| 2.2  | Finding $T.dbf(t)$ for "small" values of $t. \ldots \ldots \ldots \ldots \ldots$                                                                                                                                      | 25 |

| 2.3  | The task graph $T$                                                                                                                                                                                                    | 33 |

| 2.4  | The task graph $T'$                                                                                                                                                                                                   | 34 |

| 2.5  | Graph $T'$ after relaxing the deadline associated with the vertex $v_4$ from 2 to 3                                                                                                                                   | 34 |

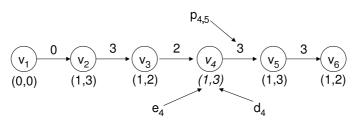

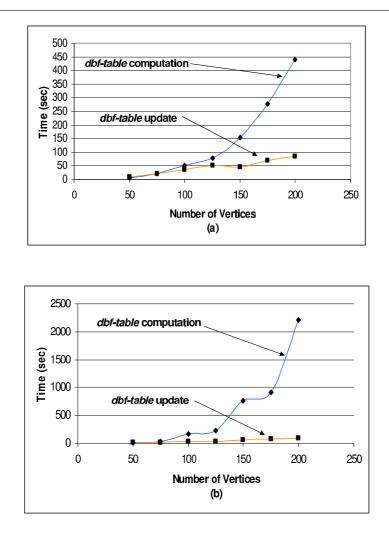

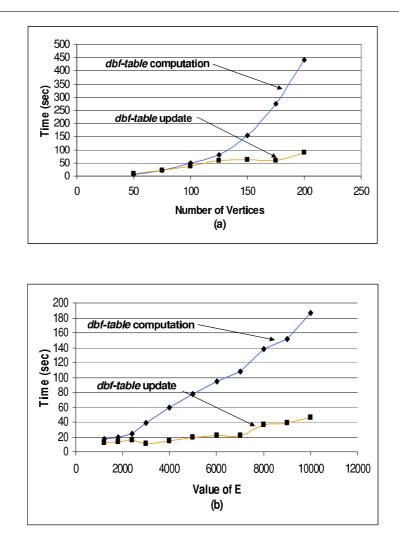

| 2.6  | Running times for updating the <i>dbf-table</i> when the deadline of a vertex was relaxed (a) $E = 200$ and (b) $E = 600. \dots \dots \dots \dots \dots \dots \dots$                                                  | 41 |

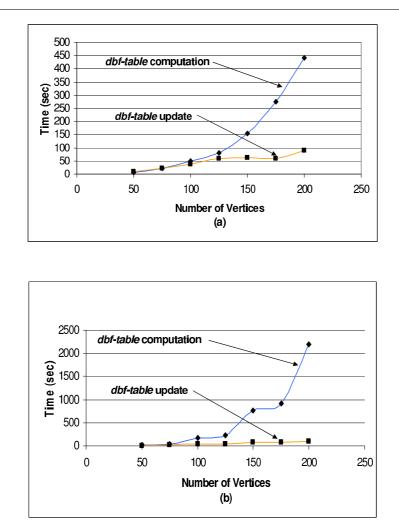

| 2.7  | Running times for updating the <i>dbf-table</i> when the deadline of a vertex was constrained (a) $E = 200$ and (b) $E = 600$                                                                                         | 43 |

| 2.8  | Running times for updating the $dbf$ -table for a task graph with 50 vertices, as the maximum execution requirement associated with a vertex $(E)$ is increased. (a) Deadline of a randomly chosen vertex is relaxed, |    |

|      | and (b) Deadline of a randomly chosen vertex is constrained                                                                                                                                                           | 44 |

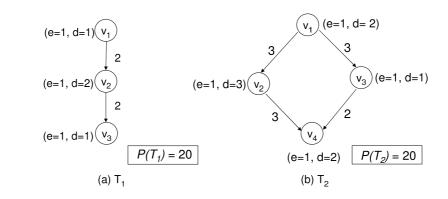

| 2.9  | Task graphs (a) $T_1$ and (b) $T_2$ of our example task set $\tau$                                                                                                                                                    | 49 |

| 2.10 | Task graphs (a) $T_1'$ and (b) $T_2'$ obtained from $T_1$ and $T_2$ respectively                                                                                                                                      | 50 |

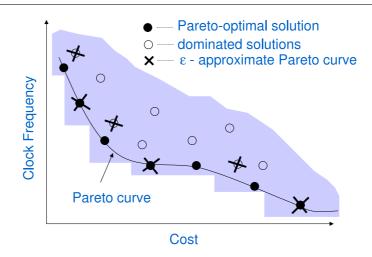

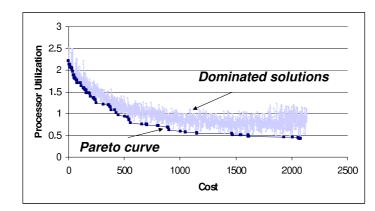

| 3.1  | Pareto-optimal solutions                                                                                                                                                                                              | 56 |

| 3.2  | The GAP problem corresponding to our <i>cost-utilization</i> tradeoff problem.                                                                                                                                        | 70 |

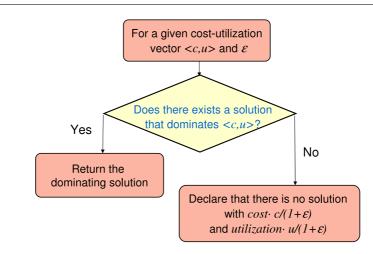

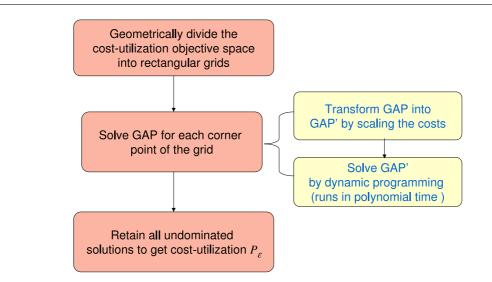

| 3.3  | An FPTAS for computing $\mathcal{P}_{\epsilon}$ using an algorithm for solving GAP                                                                                                                                    | 71 |

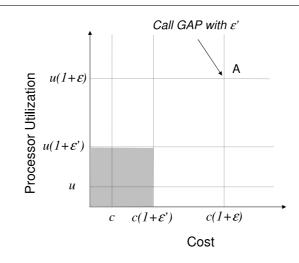

| 3.4  | Solving the GAP problem for the corner point $A$ will either return a dominating solution or declare that there is no solution in the shaded area.                                 | 73  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

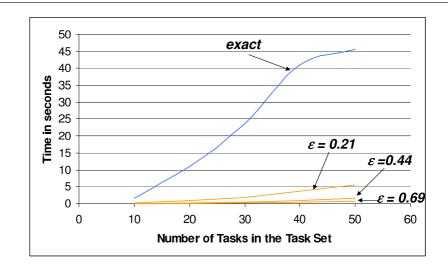

| 3.5  | Graph comparing the running times of the exact and the approximate algorithms for various task sets with $C = 10000$                                                               | 76  |

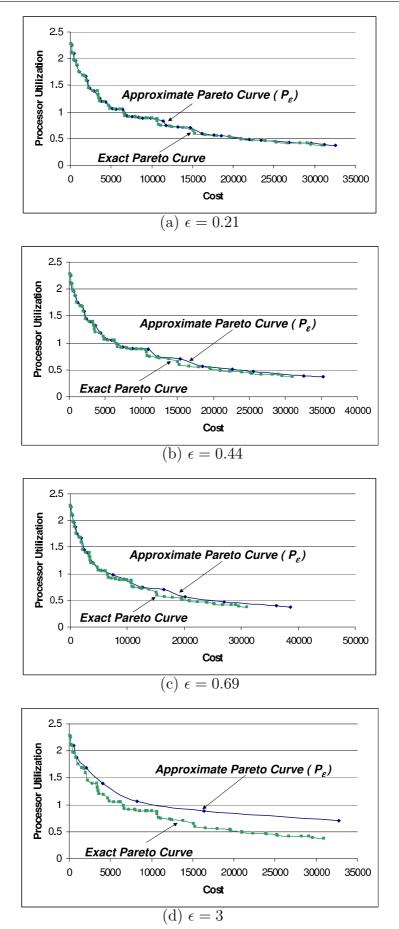

| 3.6  | The exact and approximate Pareto curves for a task set with 10 tasks. $% \left( {{{\bf{n}}_{\rm{a}}}} \right)$ .                                                                   | 78  |

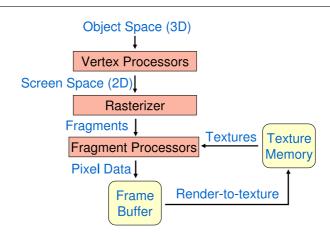

| 4.1  | The GPU graphics pipeline.                                                                                                                                                         | 85  |

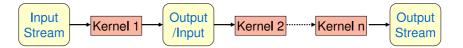

| 4.2  | Streaming model that applies kernels to an input stream and writes to<br>an output stream.                                                                                         | 86  |

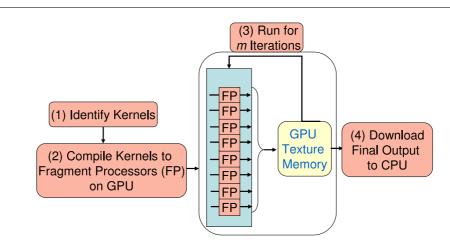

| 4.3  | The overall scheme to design and implement a GPU based algorithm                                                                                                                   | 89  |

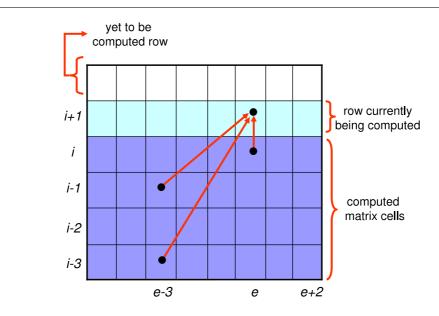

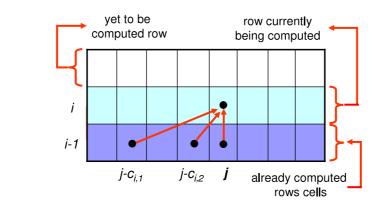

| 4.4  | Data dependency graph for Algorithm 7. Computation of a cell in the DP matrix is dependent on texture fetching from already computed cells.                                        | 90  |

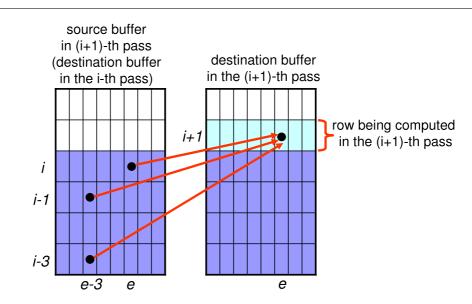

| 4.5  | Data buffers in the GPU memory during the $(i + 1)$ -th pass through the rendering pipeline. Filling the destination buffer requires rendering a $(i + 1) \times nE$ quadrilateral | 92  |

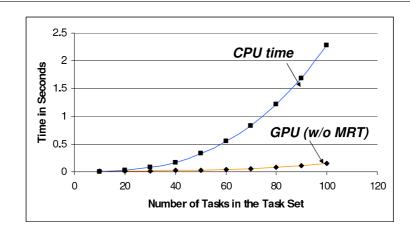

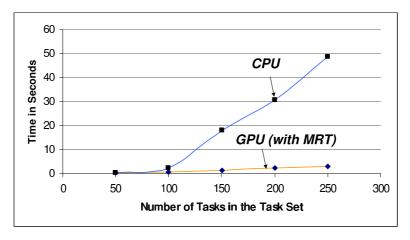

| 4.6  | Running times of the schedulability analysis algorithm for a purely CPU-<br>based implementation, versus a GPU-based implementation with a single<br>render target                 | 95  |

| 4.7  | Running times of the schedulability analysis algorithm for a purely CPU-<br>based implementation, versus a GPU-based implementation with multi-<br>ple render targets.             | 95  |

| 4.8  | Data dependency graph for Algorithm 9                                                                                                                                              | 103 |

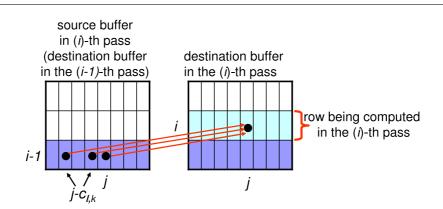

| 4.9  | Data buffers in the GPU memory during the $(i)$ -th pass through the rendering pipeline                                                                                            | 104 |

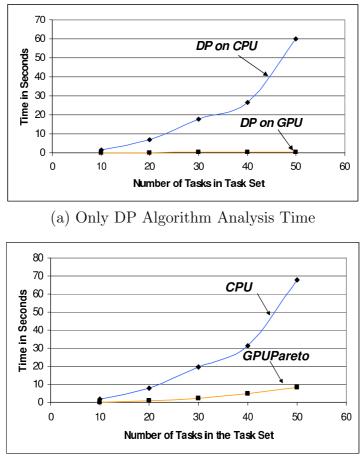

| 4.10 | Running times for a purely CPU-based implementation, versus a GPU-<br>based implementation - GPUPareto                                                                             | 105 |

| 4.11 | The Pareto curve obtained for a task set of 10 tasks                                                                                                                               | 107 |

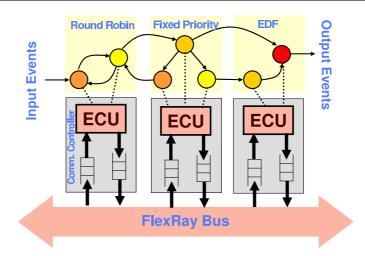

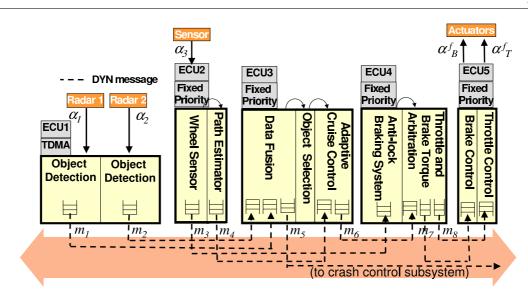

| 5.1  | A FlexRay-based network of ECUs, with an application partitioned and mapped onto multiple ECUs                                                                                     | 112 |

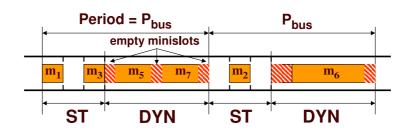

| 5.2  | Two typical FlexRay communication cycles                                                                                                                                           | 116 |

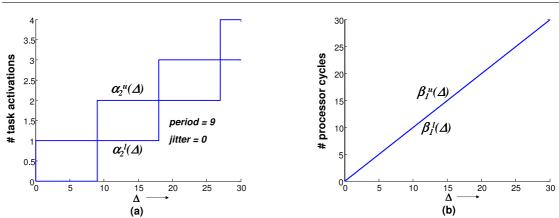

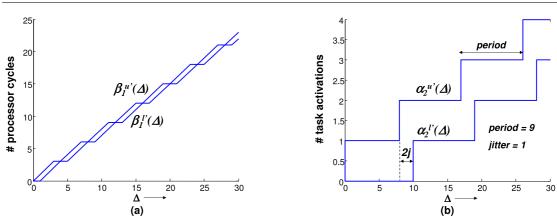

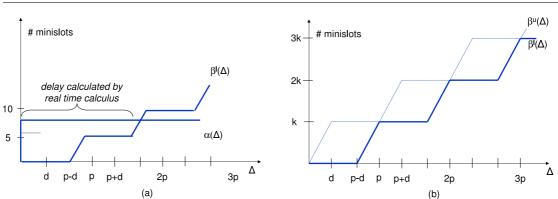

| 5.3  | (a) $\alpha^u$ and $\alpha^l$ corresponding to a periodic activation. (b) $\beta^u$ and $\beta^l$ of an unloaded processor.                                                                   | 118 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

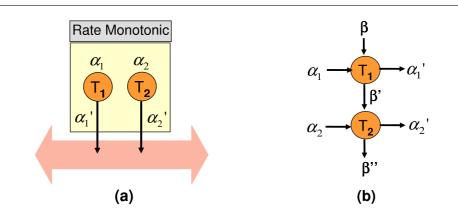

| 5.4  | (a) Rate monotonic scheduling of two tasks. (b) Corresponding schedul-<br>ing network                                                                                                         | 120 |

| 5.5  | (a) Bounds on the <i>remaining</i> service after processing task $T_1$ . (b) Bounds on the messages generated by $T_2$ .                                                                      | 122 |

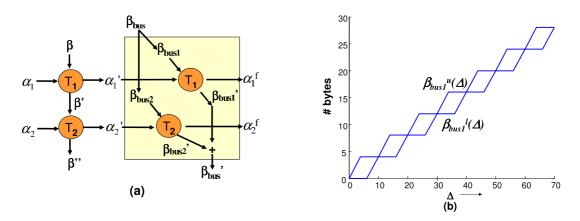

| 5.6  | (a) Performance model of the complete architecture (b) The bounds on the service available on the $TDMA$ bus to messages from $T_1$                                                           | 122 |

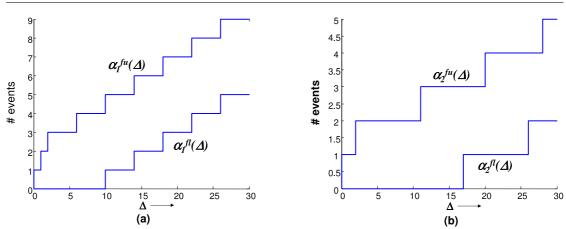

| 5.7  | (a) Upper and lower bounds on the transmitted messages over the bus arising from $T_1$ . (b) Bounds on the transmitted messages from $T_2$                                                    | 123 |

| 5.8  | (a) Computing maximum delay from $\alpha^u$ and $\beta^l$ . (b) Total service offered by the DYN segment.                                                                                     | 124 |

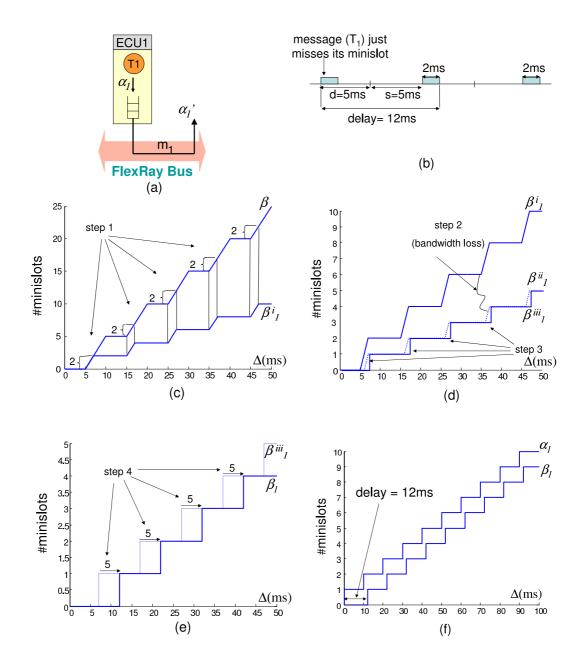

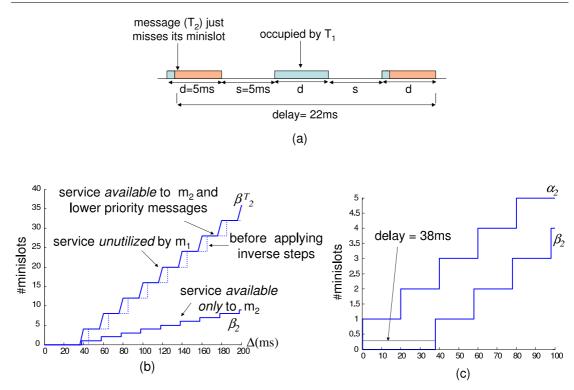

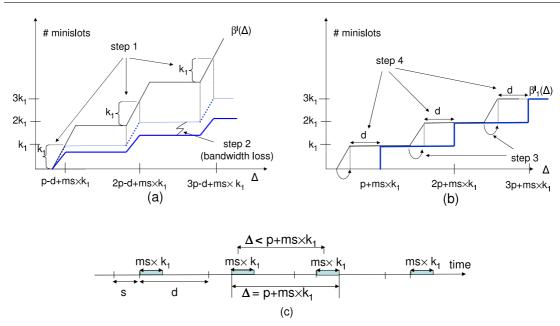

| 5.9  | Example 1 (a) Architecture. (b) Analyzing actual delay of $m_1$ . (c) Step 1. (d) Steps 2 and 3. (e) Step 4. (f) Delay of $m_1$ computed by our framework.                                    | 127 |

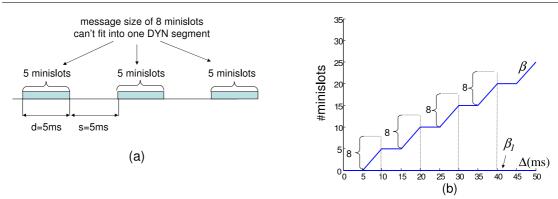

| 5.10 | Example 2 (a) Message does not fit into one DYN segment. (b) Step 1 results in nullified $\beta_1$                                                                                            | 129 |

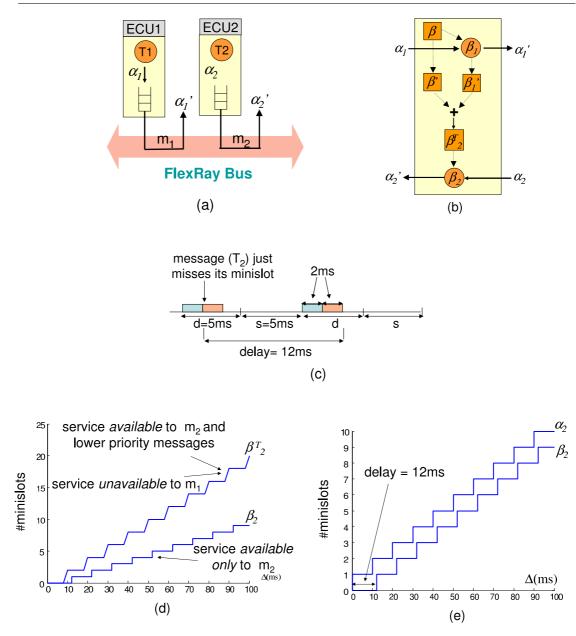

| 5.11 | Example 3 (a) Architecture. (b) Overview of our scheme. (c) Analyzing actual delay of $m_2$ . (d) Transformation. (e) Delay of $m_2$ computed by our framework.                               | 130 |

| 5.12 | Example 4 (a) Analyzing actual delay of $m_2$ . (b) Transformation. (c) Delay of $m_2$ computed by our framework                                                                              | 133 |

| 5.13 | (a) Steps 1 and 2 for transforming $\beta^l$ . (b) Shifting the resulting service bound. (c) Blocking time.                                                                                   | 134 |

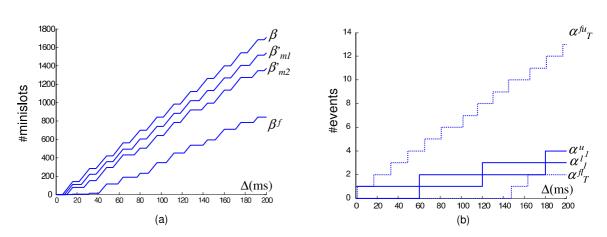

| 5.14 | The system architecture of an Adaptive Cruise Control subsystem                                                                                                                               | 138 |

| 5.15 | (a) The bounds on the resource curves for the DYN segment. (b) The bounds on the input and the output signals for the system                                                                  | 141 |

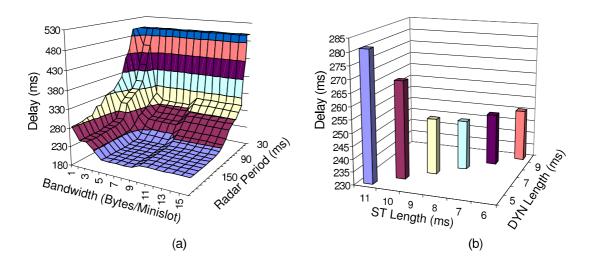

| 5.16 | Design Space Exploration: (a) Influence of sampling rates and band-<br>width on the end-to-end delay. (b) Influence of lengths of the static and<br>dynamic segments on the end-to-end delay. | 142 |

# List of Tables

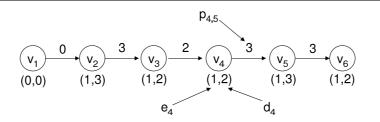

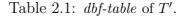

| 2.1 | dbf-table of $T'$                                                                                                                                                                                                                                                    | 34  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | The updated $dbf$ -table after relaxing the deadline associated with the vertex $v_4$ from 2 to 3.                                                                                                                                                                   | 35  |

| 2.3 | Number of checks required in <i>Step</i> ( <i>ii</i> ) of the proposed interactive schedulability analysis, versus $t_{\text{max}}$ , which is equal to the number of checks that a regular schedulability analysis algorithm would perform                          | 45  |

| 3.1 | Implementation choices for three different tasks in a task set. Each row<br>of this table shows the new execution requirement (on a programmable<br>processor) because of a part of the task being implemented in hardware,<br>along with the incurred hardware cost | 62  |

| 3.2 | Number of points in $\mathcal{P}_{\epsilon}$ generated by our proposed approximation algorithm, versus the number of points in the optimal Pareto curve                                                                                                              | 79  |

| 4.1 | Comparing the running times of a purely CPU-based schedulability analy-<br>sis versus a GPU-accelerated analysis.                                                                                                                                                    | 94  |

| 4.2 | Illustration of the table built by Algorithm 9. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                         | 101 |

| 4.3 | Detailed breakdown of time taken by GPUPareto and comparison with<br>a purely CPU-based analysis.                                                                                                                                                                    | 106 |

| 5.1 | The workload on the bus and the ECUs for the ACC subsystem. $\ . \ . \ .$                                                                                                                                                                                            | 139 |

| 5.2 | Delay and buffer requirement of each message stream on the FlexRay bus.                                                                                                                                                                                              | 142 |

|     |                                                                                                                                                                                                                                                                      |     |

# Chapter 1

# Introduction

An embedded system is an electronic device which contains a special-purpose computing system embedded within it. Typically, such a device is a combination of hardware and software designed to meet the special functionality of the system. These systems are found in numerous application domains ranging from brake controllers in automobiles and controllers in industrial plants, to mobile health monitoring devices.

Most of the embedded systems, such as those mentioned above, need to continuously interact with their physical environment through sensors and actuators. Once the embedded system receives an input on the sensors, it needs to do some computation and if required, send an output signal on the actuators. As most of these applications are safety-critical, failure of the system to reply within the expected time interval might lead to a catastrophic accident, possibly loss of human-life. For instance, a delayed response of an automated brake-controller in a moving car might result in a fatal crash. Thus, apart from guaranteeing correct computation, many embedded systems must also meet real-time constraints, i.e. they must finish the computation and react to stimuli within a definite time interval. Furthermore, due to considerations such as limited space and costs, the amount of memory available is scarce in most of these real-time embedded devices. Also, these devices are often mobile and have to run on batteries, which means that the power consumption should be limited as much as possible for longer life of the devices.

### System-Level Performance Analysis

From the above discussion, we note that apart from being functionally correct, a real-time embedded system must conform to certain non-functional or *performance metrics* like timing constraints, memory size restrictions, power limitations, etc. To check whether all such performance metrics of a system are satisfied, the design of real-time embedded system typically starts with a *system-level performance analysis*.

Thus, in a design cycle, the designer would typically invoke a system-level performance analysis to seek answers to questions related to performance metrics like: Given a set of jobs chosen to run on a processor, does there exist an execution order or schedule which satisfies the timing constraints (*Schedulability Analysis*)? Which functions should be implemented in hardware and which in software to maximize performance and minimize the hardware costs (*Partitioning*)? Do the system-level timing properties meet the design requirements (*Timing Analysis*)? What would be the total response time or the *end-to-end delay* of the system once the system receives an input on the sensors, till it sends an output signal on the actuators?

In the next section, we introduce the problem of design space exploration of realtime embedded systems, and discuss the role of system-level performance analysis in design space exploration cycles.

## 1.1 Design Space Exploration

Because of the many alternatives for mapping and partitioning, application optimization, and architecture selection during the system design process, a designer of a complex embedded system is confronted with a large design space. Each point in the design space is associated with conflicting tradeoffs with respect to various performance metrics like real-time response, costs etc. For instance, response time (performance) of a system may be improved by implementing larger portions of task for a given application in the hardware (providing that the application offers enough "hardware realizable" functionalities) at the expense of an silicon area overhead. By extensively playing around with system parameters, designers can generate the trade-off curves in the design space defined by performance and area costs. Such a process of systematically altering design parameters has been recognized as an exploration of the design space.

Broadly, the design space exploration process consists of two orthogonal issues [36].

- 1. Firstly, the designer has to identify all the design points. Typically, the designer is confronted with a large design space, where a large number of implementation choices have to be investigated in order to determine design trade-offs between various possibly conflicting performance metrics.

- 2. The designer also needs to run a performance analysis to quantitatively evaluate each design point in order to compare their relative merits with respect to various performance metrics. For most realistic system models the performance analysis is time consuming and involves running one or more computationally expensive cores. We discuss this role of performance analysis in design space exploration elaborately in the following section.

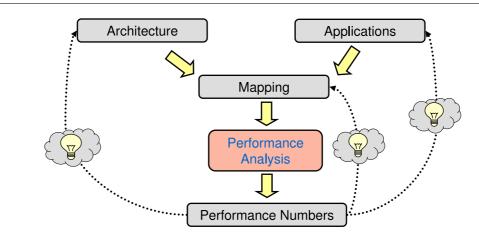

Figure 1.1: Role of Performance Analysis in Interactive Design Space Exploration.

# 1.1.1 Role of Performance Analysis in Design Space Exploration

Design space exploration of a real-time embedded system is not a one-step procedure, but rather an iterative procedure (see Figure 1.1). This process is well-known as the Y-chart methodology [42, 50, 86], and involves the following steps. The process starts with a specification of a set of representative target *applications*, which must be implemented on an *architecture* such that predefined performance constraints with respect to cost, real-time response, etc. are satisfied. In an explicit mapping step, the target application is mapped onto the candidate architecture. The designer then invokes a *performance analysis* tool to evaluate the performance metrics corresponding to the design point. If the designer is not satisfied with the resulting performance numbers, then he/she would modify some of the parameters and invoke the *performance analysis* once again. The designers might interpret the performance numbers manually, or might be inspired by feedback provided by the performance analysis tools to propose the new parameter values (this interpretation process is indicated in Figure 1.1 by the lightbulb). The designer may modify (i) the application parameters (worst-case *execution* times, *deadlines* and *periods*), (ii) the selection of architecture building blocks (number of processors, processor frequencies, hardware costs (in terms of ASIC/FPGA area)), or (iii) the mapping strategy itself. This iterative design space exploration is repeated until a satisfactory design is found. Thus, a real-life design session of a embedded system for a system-level designer is *interactive*; they repeatedly invoke system-level performance analysis tools during the design exploration cycles.

Unfortunately, it turns out that interactive design space exploration is quite tedious. The prime reason for this being the fact that for most realistic system models the system-level performance analysis involves running one or more computationally expensive cores. Hence, each time the tool is invoked, the system designer has to wait for a long time (which might be in the tune of several hours) to let the analysis run to completion and this critically impacts the usability of the tool in the interactive design sessions.

### 1.1.2 Challenges

In the above we discussed the two major concerns in design space exploration: (i) a prohibitively large design space that must be covered during the exploration process, and (ii) a heavy-duty performance analysis to evaluate each design point. In this section, we shall discuss the particular reasons behind long and exhaustiing interactive design space exploration sessions associated with some common computationally expensive system-level performance analysis problems.

#### • Schedulability Analysis

Schedulability analysis is used to determine if the temporal properties of a real-time system are satisfied. If the analysis returns a negative answer, the designer repeatedly changes system parameters and re-runs the analysis. However, for most realistic task models, schedulability analysis algorithms often involves running one or more computationally expensive cores [47, 11, 9]. Hence, each time the schedulability analysis tool is invoked, it takes a long time to run and this hampers the productivity of the designer in the iterative design sessions.

Apart from making the iterative design sessions faster, there are additional challenges involved with interactive schedulability analysis. For example, in each iteration of the design, if the designer randomly chooses a system parameter and makes a change, this change might not lead to a feasible system. The challenge is to develop a mechanism such that the tool provides the designer with some concrete feedback regarding what system parameter should be changed that would likely yield a feasible solution.

#### • Hardware/Software Partitioning

Design space exploration plays an integral part in hardware/software partitioning; it involves evaluating the possible performance versus area trade-offs associated with all possible design points. Unfortunately, optimally computing even one feasible design point in most common setups is computationally expensive [36, 60]. Moreover, typically, there might be infinitely many points in the design space. Thus, the straightforward approach to determine the design points by an exhaustive search is intractable and not practical enough to be used in an interactive design cycle.

Traditionally, researchers have been using different techniques to get around the high running times associated with such problems. The most notable amongst these are heuristics like genetic and evolutionary algorithms [37, 48]. However, these algorithms do not yield exact solutions and neither do they offer any kind of performance guarantee. Therefore, new techniques are necessary which are efficient as well as provide formal guarantees on the optimality of the design points that are returned.

#### • Timing Analysis of Distributed Real-Time Applications

Over the past decade, embedded systems have increasingly become distributed in nature with different scheduling and arbitration schemes being used on the different processors and buses. One foremost example of such distributed real-time systems may be found in today's automobiles where electronic systems have gradually replaced mechanical ones in cars and trucks. Such distributed systems are rapidly increasing in size, communication complexity and software content. For example, today's vehicles can have more than 70 control units or processors, connected by multiple communication buses and running millions of lines of software [5]. Analysing such heterogeneous systems to verify timing and other system-level properties pose a major challenge. Traditional traditional design processes do not handle such complexity; system-level design methodology is required [65, 70]. Important system-level design decisions here involve identifying optimal scheduling policies, parameters of the bus protocol, end-to-end timing delays, buffer sizes, etc. Commercially available design tools for automotive electronics like Decomsys [27] and Dspace [28] rely on simulation techniques to provide such answers. Such simulation tools take long running times and coupled with naive design space exploration techniques, the total design cycle becomes very long.

## 1.2 Thesis Contributions

In the above discussion, we have identified two broad issues. Firstly, despite high running times associated with computationally expensive kernels of the performance analysis machinery (which lead to tedious interactive design cycles), current high-level design methodologies and tools have no support to address the problem. Moreover, so far only ad-hoc solutions like evolutionary algorithms and exhaustive search techniques have been used in order to cope the prohibitively large design space to cope with multi-objective optimization design problems. In this thesis we present systematic/formal approaches which provide provable performance guarantees. We propose (i) novel algorithmic techniques, both exact and approximate, as well as (ii) hardware-based techniques to accelerate the computationally expensive *performance analysis* in each iteration. We also introduce (i) a scheme to approximate the potentially exponential sized design space with only a polynomial number of points and (ii) techniques to provide with insightful feedback to the designer regarding the design parameters he may choose to modify in each iteration. In particular, this thesis proposes novel techniques for interactive design space exploration by addressing the challenges associated with common systemlevel performance analysis problems discussed in Section 1.1.2.

#### • Interactive Schedulability Analysis

We propose a novel approach to bring down the high running times associated with schedulability analysis algorithms, especially in the context of an iterative design process. It is based on the observation that if only a small number of design parameters are changed, then it is not required to invoke the full schedulability analysis machinery. Rather, certain data structures can be created when the algorithm is run for the first time, and on subsequent invocations of the algorithm it is possible to exploit these data structures and run only a small subset of the regular schedulability analysis algorithm. We refer to this as *interactive* schedulability analysis because it would typically be used in an interactive mode—a designer would keep on modifying the values of a small number of system parameters and use this algorithm to test whether the system becomes schedulable.

This concept of interactive schedulability analysis is fairly general and can

be applied to a number of well-known task models. In this thesis, we have chosen the recently proposed recurring real-time task model [9] to illustrate this scheme. It has been shown in [9] that this model generalizes a number of task models. Further, it can be used to model realistic applications with conditional branches and fine-grained deadline constraints. Our experimental results show that using our scheme can lead to more than  $20 \times$  speedup for each invocation of the schedulability analysis algorithm, compared to the case where the full algorithm is run.

Note that the designer repeatedly changes system parameters so that the schedulability analysis may yield a feasible solution. If the designer randomly chooses a system parameter and makes a change it might not lead to a feasible system. In our work, we also devise a technique using which a system designer can be provided some feedback regarding which system parameter(s) should be changed that would likely yield a feasible solution.

#### • Hardware/Software Partitioning

We develop an efficient scheme for design space exploration in the context of hardware/software co-design of real-time systems. Such systems nowadays consist of a heterogeneous mix of fully-programmable processors, fixedfunction components or hardware accelerators, and partially-programmable engines. Hence, system designers are faced with an array of implementation possibilities for an application at hand. Such possibilities typically come with different tradeoffs involving cost, power consumption and packaging constraints. As a result, a designer is no longer interested in *one* implementation that meets the specified real-time constraints (i.e. is schedulable), but would rather like to identify *all* schedulable implementations that expose the different possible performance tradeoffs formally known as the Pareto front. In this thesis we formally define this multicriteria schedulability analysis problem and derive a polynomial-time approximation algorithm for solving it. This result is interesting because the problem of optimally computing even one schedulable solution in our setup (and in most common setups) is computationally intractable (NP-hard).

The second reason which makes our work interesting is that there can be an exponentially large number of points in the Pareto front, which makes it impossible to compute this entire set in polynomial time. Hence, our polynomial-time approximation algorithm by default also implies approximating the (potentially exponential size) set with only a polynomial number of points. In a typical design cycle, a system designer inspects all the tradeoffs in the set and then selects one, or at most a few implementations. Hence, from a practical perspective, it is more meaningful if the designer is presented with a reasonably few well-distinguishable tradeoffs in the set, rather than an exponentially large number of solutions, many of which are very similar to each other. Our approximation algorithm is therefore not only attractive in terms of time-complexity, but also returns more meaningful solutions.

#### • Accelerating Performance Analysis Using GPUs

We introduce the novel idea of using commodity graphics hardware (more specifically, graphics processing units or GPUs) to accelerate the expensive cores associated with heavy-duty kernels of design space exploration problems. The two foremost reasons why GPUs are an attractive platform for such non-graphics computations are—(i) modern GPUs are extremely powerful (e.g. high-end GPUs such as nVIDIA GeForce 8800 GTX have a FLOPS rating of around 330 GigaFLOPS, whereas high-end general-purpose processors are only capable of around 25 GigaFLOPS) (ii) GPUs are now commodity items as their costs have dramatically reduced over the last few years. Thus, the attractive price-performance ratios of GPUs gives us an enormous opportunity to change the way system-level performance analysis tools perform, with almost no additional cost. In fact, recent years have seen the increasing use of graphics processing units (GPUs) for a wide variety of general-purpose computing tasks. Examples of these include scientific computing [35, 45], computational geometry [2], database processing [3], image processing [56, 58], astrophysics [67] and bioinformatics [53].

In this thesis, we use the schedulability analysis of the recurring real-time task model problem and the hardware/software co-design problem to establish the utility of the GPUs in accelerating system-level performance analysis algorithms. Our experiments on the GPU demonstrate tremendous speed up (upto  $16\times$ ) of the schedulability analysis algorithm and (upto  $100\times$ ) speedup of the hardware/software co-design problem.

#### • Performance Analysis of Applications in Automotive Electronics

We have also been concerned with practical cases of embedded system design, and in this regard, we have specifically worked in the automotive domain. Our contributions in this direction are discussed below.

We propose an analytical framework for compositional performance analysis of a network of processors that communicate via a FlexRay bus. FlexRay is fast emerging as the predominant protocol for in-vehicle automotive communication systems. Given a specification of the applications running on the system, their partitioning and mapping on the different processors, their activation rates or periods and the message priorities, our framework can be used to answer various performance analysis related questions. These include the maximum end-to-end delay experienced by the different message types, the amount of buffer space required within a communication controller associated with a processor and the utilizations of the different processors and the FlexRay bus. In contrast to traditional simulation methods which takes hours to run, our analytical model returns results in a matter of few seconds, and is ideal for fast analysis in interactive design cycles. The framework allows the designer to extensively play around with the FlexRay protocol parameters in order to identify the suitable performance metric. Also, it can help in resource dimensioning (e.g. designing the various processors) and determining optimal scheduling policies for multitasking processors.

### **1.3** Organization of this Thesis

In the following we give a brief overview of the contents of this thesis. Chapter 2 presents our scheme for "interactive" schedulability analysis. We also describe a technique using which a system designer can be provided some feedback on potential modifications that may be done when a task set is not schedulable.

Our work on design space exploration using approximation techniques is presented in Chapter 3. We formally define the single criteria version of the problem, prove that it is NP-hard and derive a polynomial-time approximation scheme for solving it. This is followed by our solution to the multicriteria problem.

Chapter 4 deals with our idea of accelerating performance analysis problems using commodity graphics processor units (GPUs). Towards this, we propose two GPUbased engines — (i) for a hardware/software co-design and (ii) for a schedulability analysis algorithm.

Chapter 5 contains the results related to performance analysis of FlexRay based automotive networks. Finally, we summarize this thesis in Chapter 6 with directions for future work.

# Chapter 2

# Interactive Schedulability Analysis

Schedulability analysis plays an integral role in the system-level design of realtime embedded systems. Once a designer chooses the values of the relevant system parameters, schedulability analysis is used to determine whether it is possible to assign to each job a processor time equal to its worst-case execution requirement, between its ready time and its deadline. If such an analysis returns a negative result (i.e. there exist legal scenarios where certain jobs might miss their deadlines), then some of the system parameters are relaxed and the analysis is invoked once again. On the other hand, if such an analysis returns a positive result (i.e. all jobs definitely meet their deadlines), the designer might want to constrain some of the system parameters and re-invoke the analysis to find a tighter set of design parameters where the system is schedulable. Thus, in a typical system design process, this iteration is repeated a number of times where the designer evaluates the schedulability for a extensive set of design parameters.

Unfortunately, the schedulability analysis problem for most task models is intractable (usually co-NP hard). Therefore, known algorithms for these models have an exponential time complexity and at best run in pseudo-polynomial time. As a result, the above-mentioned iterative design process can become overly tedious for even reasonably-sized problems. To get around this, recent research in the real-time systems area has focused on either obtaining efficient pseudo-polynomial time algorithms or on *approximately* solving the schedulability analysis problem [4, 21, 32].

In this chapter, we propose another possible approach to bring down the high running times associated with schedulability analysis algorithms, especially in the context of an iterative design process. It is based on the observation that if only a small number of design parameters are changed, then it is not required to invoke the full schedulability analysis machinery. Rather, certain data structures can be created when the algorithm is run for the first time, and on subsequent invocations of the algorithm it is possible to exploit these data structures and run only a small subset of the regular schedulability analysis algorithm. We refer to this as *interactive* schedulability analysis because it would typically be used in an interactive mode—a designer would keep on modifying the values of a small number of system parameters and use this algorithm to test whether the system becomes schedulable.

This concept of interactive schedulability analysis is fairly general and can be applied to a number of well-known task models. In this thesis, we have chosen the recently proposed recurring real-time task model [9] to illustrate this scheme. It has been shown in [9] that this model generalizes a number of task models. Further, it can be used to model realistic applications with conditional branches and fine-grained deadline constraints.

Before proceeding further, we would like to clarify what we mean by "modifying the values of system parameters" in the context of scheduling a set of task graphs. The relevant system parameters are determined by the underlying task model. For example, in the recurring real-time task model, vertices of task graphs are annotated with worst-case *execution times* and *deadlines*. The edges are annotated with *minimum intertriggering separation times* and each task graph is associated with a *period*, which specifies the minimum time interval between two consecutive triggerings of the graph. When the schedulability analysis of a task set returns a negative answer (i.e. *not* schedulable), a designer would typically relax a few deadline constraints associated with some of the vertices of the task graphs and run the algorithm once again. Other possible modifications might consist of increasing the values of some intertriggering separations, or increasing the period associated with a task graph, or decreasing the execution times associated with some of the vertices (possibly by rewriting/optimizing the code corresponding to those vertices). It might even be possible to split a vertex into two or more vertices, i.e. change the structure of a task graph.

Note that once a task set becomes schedulable, it is possible that a designer might now want to *constrain* (or reduce) the values of some of the above-mentioned parameters like deadlines, intertriggering separations, or task periods. This is in order to test whether the task set still remains schedulable with a tighter deadline, intertriggering separation, or period constraint. Often such an iterative process is used to obtain the tightest set of constraints under which a task set remains schedulable.

### **Overview of the Proposed Scheme**

In this thesis, we discuss our proposed interactive scheme in the context of dynamic priority feasibility analysis in a preemptive uniprocessor environment. A standard methodology based on the *processor demand criteria* (see [10] and [17]) has emerged

for the feasibility analysis of such systems. Towards this, the worst-case workload that can possibly be generated by a task (graph) is represented by a function called the *demand-bound function*. The demand-bound function of a task T, denoted by T.dbf(t), takes as an argument a positive real number t and returns the maximum possible cumulative execution requirement of jobs that can be legally generated by T and which have their ready-times and deadlines both within a time interval of length t. A set of concurrently executing tasks T is then schedulable under a fully preemptive uniprocessor model if and only if for all  $0 < t \le t_{\max}$ ,  $\sum_{T \in \mathcal{T}} T.dbf(t) \le t$ , where  $t_{\max}$  is a function of the execution requirements of the tasks in T and their periods. This scheme therefore involves two stages:

(i) Computing

$$T.dbf(t)$$

for all  $t \leq t_{\text{max}}$  and  $T \in \mathcal{T}$ , and

(ii) Checking that  $\sum_{T \in \mathcal{T}} T.dbf(t) \leq t, \ \forall \ 0 < t \leq t_{\max}$ .

For the recurring real-time task model, it turns out that for an arbitrary task graph T, computing T.dbf(t) for any t is NP-hard (see [20]). Further,  $t_{\text{max}}$  is pseudo-polynomial in the size of problem. Hence, a pseudo-polynomial number of checks have to be performed in stage (ii).

While computing T.dbf(t) for different values of t in stage (i), we construct a table for each task graph  $T \in \mathcal{T}$  (the details of which are described later in this chapter). In an iterative design cycle, once the deadline d(v) of a vertex  $v \in T$  is changed and the schedulability analysis algorithm is invoked, the table corresponding to T need not be recomputed from scratch. Rather, only parts of it are updated—which is significantly faster than recomputing the entire table. For any t, T.dbf(t) (where Tis the task graph with the changed d(v)) can now be computed from this updated table. Similarly, we also avoid checking the condition  $\sum_{T \in \mathcal{T}} T.dbf(t) \leq t$  for all  $0 < t \leq t_{\max}$ . When the deadline d(v) of a vertex  $v \in T$  is changed, we compute the values of t at which the condition for schedulability i.e.  $\sum_{T \in \mathcal{T}} T.dbf(t) \leq t$  can possibly change due to d(v). We then check the schedulability condition only for these values of t, which again can be considerably faster than checking this condition for all  $t \leq t_{\max}$ .

#### **Related Work**

To the best of our knowledge, the concept of interactive schedulability analysis—in the form that we present in this thesis—has not been investigated before. The need for appropriate tool sets for interactive timing analysis has been emphasized in [79] and several other papers. [79] introduced an interactive tool, which helps to debug timing errors in real time programs. However, no formal or algorithmic results were presented. Neither did [79] present any result on how to speedup *interactive* timing analysis.

Most of the previous research on obtaining efficient algorithms for schedulability analysis for different real-time task models focused on designing either efficient pseudo-polynomial algorithms, or polynomial time solutions for restricted versions of task models. More recently, the concept of *approximate schedulability analy*sis has been investigated in a number of papers (see, for example, [21], [4], and [32]). Unlike exact schedulability analysis, approximate schedulability analysis might return false positives or false negatives. Here, the basic idea is that if the schedulability analysis algorithm is occasionally allowed to return a false answer, then such an algorithm can be designed to run in polynomial time. For example, if the algorithm is allowed to return false positives then in some cases although a task set is *not* schedulable, the algorithm incorrectly returns *schedulable*. However, it can be guaranteed that even in such cases no task will miss its deadline by more than a prespecified time interval. Further, for *most* task sets the algorithm will return the correct answer. A similar algorithm that only returns false negatives can also be designed.

None of the above research directions however exploit the fact that often the schedulability analysis algorithm is repeatedly invoked, with minor modifications in the task graphs. This is the scenario we address in this thesis. Although not directly related to the problem we address in this thesis, recently there has been some work on computing the *space* of task periods and worst-case execution times that lead to schedulable systems (this is often referred to as computing the *schedulable region*) [14]. The problem we address here, on the other hand, is an online or an interactive debugging scenario, where the designer is concerned with identifying *one* set of system parameters that lead to a schedulable design.

#### Organization of this Chapter

The rest of this chapter is organized as follows. In the next section we give some necessary background and an overeview of our scheme. This is followed by the related work in this domain. In Section 2.1, we describe the recurring real-time task model and its schedulability analysis. Towards this, we present a dynamic programming algorithm for computing the *demand-bound function* for this model in Sections 2.1.2 and 2.1.3. In Section 2.2 we then present our scheme for interactive schedulability analysis, which partly makes use of the dynamic programming algorithm. Our experimental results are described in Section 2.3. When a task set is not schedulable, it is often helpful if the system designer can be provided feedback on the potential system parameters that can be changed to obtain a schedulable system. In Section 2.4 we outline some techniques for providing such feedback,

and finally, we conclude this chapter in Section 2.5.

# 2.1 The Recurring Real-Time Task Model and its Schedulability Analysis

The recurring real-time task model was recently proposed by Baruah in [8, 9]. It is especially suited for accurately modeling conditional real-time code with recurring behavior, i.e. where code blocks have conditional branches and run in an infinite loop, as is the case in many embedded applications. Further, this model also generalizes a number of well-known task models such as the multiframe model [55], the generalized multiframe model [10] and the recurring branching task model [7].

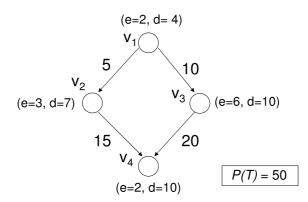

A recurring real-time task T is represented by a task graph which is a directed acyclic graph with a unique source (a vertex with no incoming edges) and a unique sink (a vertex with no outgoing edges) vertex. Associated with each vertex v of this graph is its execution requirement e(v), and deadline d(v). Whenever the vertex v is triggered, it generates a job which has to be executed for e(v) amount of time within d(v) time units from the triggering-time. Each directed edge (u, v) in the graph is associated with a minimum intertriggering separation p(u, v), denoting the minimum amount of time that must elapse before the vertex v can be triggered after the triggering of the vertex u.

The semantics of the execution of such a task graph state that the source vertex can be triggered at any time, and if some vertex u is triggered then the next vertex v can be triggered only if there exists a directed edge (u, v) and at least p(u, v)amount of time has passed since the triggering of the vertex u. If there are directed edges  $(u, v_1)$  and  $(u, v_2)$  from the vertex u (representing a conditional branch) then

Figure 2.1: An example recurring real time task.

only one among  $v_1$  and  $v_2$  can be triggered, after the triggering of u. The triggering of the sink vertex can be followed by the source vertex getting triggered again but any two consecutive triggerings of the source vertex should be separated by at least P(T) units of time, called the *period* of the task graph.

Therefore, a sequence of vertices  $v_1, v_2, \ldots, v_k$  getting triggered at time instants  $t_1, t_2, \ldots, t_k$ , is legal if and only if there are directed edges  $(v_i, v_{i+1})$ , and  $t_{i+1} - t_i \ge p(v_i, v_{i+1})$  for  $i = 1, \ldots, k - 1$ . The only exception is that  $v_{i+1}$  can also be the source and  $v_i$  the sink vertex, and in that case if there exists some vertex  $v_j, j < i$ , in the sequence such that  $v_j$  is also the source vertex then  $t_{i+1} - t_j \ge P(T)$  must be additionally satisfied. The real-time constraints require that the job generated by triggering vertex  $v_i, i = 1, \ldots, k$ , be assigned the processor for  $e(v_i)$  amount of time within the time interval  $(t_i, t_i + d(v_i)]$ .

Once jobs are generated, they execute independently of each other (and therefore a restriction like first-come-first-served can not hold). Therefore, to ascertain that a job generated by a vertex u completes execution before a job generated by a vertex v, when u and v belong to the same task graph and there is a directed edge from u to v, then either of the following conditions must hold:  $p(u, v) \ge d(u)$ , which guarantees that the vertex v can be triggered only after the job generated by vertex u has completed execution, or that  $d(u) \le p(u, v) + d(v)$ , which guarantees that the absolute deadline of the job generated by vertex v is larger than or equal to the absolute deadline of the job generated by vertex u. In the real-time systems literature the first requirement is referred to as the *frame separation property* [74] and the second as the *localized Monotonic Absolute Deadlines property* (*l-MAD*) [10]. In this thesis, we assume either one of these two properties to hold.

Two points may be noted here. First, the original recurring real-time task model and its schedulability analysis, as proposed by Baruah in [9], is based on the *frame separation property* assumption. Second, our assumption that the *l-MAD* property leads to a job generated by a vertex u completing its execution before a job generated by a vertex v (when there is a directed edge from u to v) is based on the implicit assumption of the underlying scheduler uses the earliest deadline first (EDF) policy. We believe that this is a realistic assumption because EDF is known to be the optimal preemptive scheduling policy (i.e. if a task set is schedulable then EDF results in a feasible schedule) and it is widely used in real-life systems. Clearly, if the scheduling policy is not EDF then the *l-MAD* property along with the *processor demand criteria* for schedulability does not guarantee that a job generated by a vertex u will complete its execution before a job generated by vwhenever there is a directed edge from u to v. Hence, we will from now on assume that the scheduling policy being used is EDF whenever the *l-MAD* property is assumed to hold true.

Figure 2.1 illustrates an example recurring real-time task. In this task, vertex  $v_3$ , for instance, has an execution requirement  $e(v_3) = 6$ , which must be met within 10 time units (its deadline) from its triggering time. The edge  $(v_1, v_3)$  has been labeled 10, which implies that the vertex  $v_3$  can be triggered only after a minimum of 10 time units from the triggering of  $v_1$  (i.e. the minimum intertriggering separation time). Edges  $(v_1, v_2)$  and  $(v_1, v_3)$  from vertex  $v_1$  imply that either  $v_2$  or  $v_3$  can be triggered after  $v_1$ . The period of the task (the minimum time interval between two consecutive triggerings of the source vertex) is 50.

#### 2.1.1 Task Sets and Schedulability Analysis

A task set  $\mathcal{T} = \{T_1, T_2, \ldots, T_n\}$  consists of a collection of task graphs, the vertices of which can get triggered independently of each other. A triggering sequence for such a task set  $\mathcal{T}$  is legal if and only if for every task graph  $T_i$ , the subset of vertices of the sequence belonging to  $T_i$  constitute a legal triggering sequence for  $T_i$ . In other words, a legal triggering sequence for  $\mathcal{T}$  is obtained by merging together (ordered by triggering times, with ties broken arbitrarily) legal triggering sequences of the constituting tasks.

The schedulability analysis of a task set  $\mathcal{T}$  is concerned with determining whether the jobs generated by all possible legal triggering sequences of  $\mathcal{T}$  can be scheduled such that their associated deadlines are met. Algorithms for the schedulability analysis of such task sets, in a preemptive uniprocessor setup, are based on certain task independence assumptions. These are: (i) The runtime behavior of a task is independent of any other tasks in the system. (ii) The constraints according to which legal job sequences are generated can be specified without any references to absolute time. Assumption (i) states that each task generates jobs independently of the jobs generated by other tasks in the system. Therefore, it is not permissible, for example, to require a task to generate a job in response to a job generated by another task. Assumption (ii) states that all temporal specifications defining the rules according to which jobs are generated by a task can only be relative to the time at which the task begins execution, or can be relative to the ready-time of another job of the same task. Therefore, a constraint like the ready-times of two consecutive jobs of a task must be separated by at least p time units, conforms to this requirement. Lastly, the time at which a task begins execution (i.e. the first job is generated) is not a priori known. For example, a task can begin execution in response to some external event.

Note that although the task independence assumptions restrict the job generation process of a task (for example, by specifying the minimum separation between the generation of two jobs), they make no assumptions about the interactions between the jobs once they are generated. Once a job is generated, it executes independently of any other job in the system, including those generated by the same task.

Given a sequence of jobs generated by a task set  $[(T_i, a_i, e_i, d_i), (T_j, a_j, e_j, d_j), \ldots]$ ( $T_i$  refers to a task,  $a_i$  is the ready time of a job,  $e_i$  is its execution requirement, and  $d_i$  is its absolute deadline), the task independence assumptions imply that the sequence is legal if and only if all subsequences formed by jobs from the individual tasks are also legal (follows from Assumption (i)). Assumption (ii) implies that if  $[(a_1, e_1, d_1), (a_2, e_2, d_2), \ldots]$  is a legal sequence of jobs generated by a task, then the sequence  $[(a_1 - t, e_1, d_1 - t), (a_2 - t), e_2, d_2 - t), \ldots]$  is also legal, where t is any real number.

It directly follows from the description of the recurring real-time task model in Section 2.1 that the model indeed satisfies the above task independence assumptions (and so does a wide variety of other task models such as the sporadic, multiframe, generalized multiframe, and the recurring branching models). The recurring real-time task model therefore lends itself to schedulability analysis based on the *processor demand criteria*, that we outlined in Section 2.

#### 2.1.2 The demand-bound function

Recall from Section 2 that a task set  $\mathcal{T}$  is schedulable if and only if  $\sum_{T \in \mathcal{T}} T.dbf(t) \leq t$  for all  $0 < t \leq t_{\text{max}}$ . It can be proved that

$$t_{\max} = \frac{\sum_{T \in \mathcal{T}} 2E(T)}{1 - \sum_{T \in \mathcal{T}} \frac{E(T)}{P(T)}}$$

where E(T) is the maximum cumulative execution requirement arising from a sequence of vertices on any path from the source to the sink vertex of the task graph T (see [9] for details).

For any task graph T, computing the value of T.dbf(t) for some (large) value of  $t \leq t_{\text{max}}$  might involve multiple traversals (loops) through the task graph. It was shown in [9] that if for a task graph T, T.dbf(t) is known for all "small values" of t then it is possible to calculate from these, the value of T.dbf(t) for any t. "Small values" of t for a task graph T are those for which the sequence of vertices that contribute towards computing T.dbf(t) contain the source vertex at most once. The value of T.dbf(t) for larger values of t is made up of some multiple of E(T) plus T.dbf(t') where t' is "small" in the sense described above. T.dbf(t) for any t (9]).

$$T.dbf(t) = \max\{\lfloor t/P(T) \rfloor E(T) + T.dbf(t \mod P(T)), \\ (\lfloor t/P(T) \rfloor - 1)E(T) + T.dbf(P(T) + t \mod P(T))\}$$

(2.1)

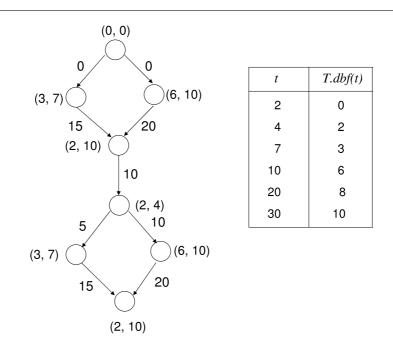

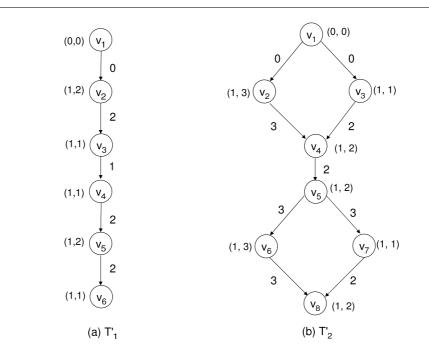

To compute T.dbf(t) for "small" values of t, [9] constructs a new task graph by taking two copies of the task graph of T and adding an edge from the sink vertex of the first graph to the source vertex of the second and finally replacing the source vertex of the first with a "dummy" vertex with execution requirement and deadline equal to zero. The intertriggering separations on all edges outgoing from this source vertex is also made equal to zero. (Two copies of the task graph in Figure 2.1 are joined in the fashion described above, and the resulting task graph is shown in Figure 2.2). T.dbf(t) for all values of t are then calculated by enumerating all possible paths in this new graph. For arbitrary task graphs, this incurs a computation time which is exponential in the number of vertices in the task graph. The list alongside the task graph in Figure 2.2 gives us few values of T.dbf(t) corresponding to some selected "small" values of t for this task graph.

Figure 2.2: Finding T.dbf(t) for "small" values of t.

For instance, when t = 4, the T.dbf(t) is 2, implying that within any time interval of 4 units the total execution requirement of jobs which have both their ready times and deadlines within this interval is 2. This means that there is no other permissible sequence of jobs which will have a demand greater than 2 within an time interval of 4. Similar explanation applies to other pairs of values listed in the table.

#### 2.1.3 Computing the demand-bound function

In this section we present a dynamic programming algorithm for computing the demand-bound function T.dbf(t) for any task graph T. It was shown in [20] that computing T.dbf(t) for any t is NP-hard for an arbitrary task graph T and a dynamic programming algorithm for computing it was given. The algorithm that we present here includes a minor extension of the algorithm in [20], so that it may be used by our interactive framework. The algorithm runs in pseudo-polynomial

time and constructs a table, which is then used by our interactive schedulability analysis framework that we describe in Section 2.2.

The algorithm given below (Algorithm 1) constitutes stage (i) of the two stages that we listed in Section 2. We first give an algorithm for computing the demandbound function of a task graph for "small values" of t. Using this, we then compute the demand-bound function for any value of t as explained in Section 2.1.2.

Given a task graph T, let T' denote the graph formed by joining two copies of T by adding an edge from the sink vertex of the first graph to the source vertex of the second, and replacing the source vertex of the first copy by a "dummy" vertex. If the frame separation property is followed then the newly added edge is labeled with an intertriggering separation of  $p = d(v_{sink})$ , and if the l-MAD property is followed then it is labeled with  $p = \max\{0, d(v_{sink}) - d(v_{source})\}$ , where  $v_{source}$  and  $v_{sink}$ denotes the source and the sink vertices of T. Now we give a pseudo-polynomial time algorithm based on dynamic programming, for computing T'.dbf(t) for values of t that do not involve any looping through T', i.e. we consider only "one-shot" executions of T'.

Let there be *n* vertices in T' denoted by  $v_1, \ldots, v_n$ , and without any loss of generality we assume that there can be a directed edge from  $v_i$  to  $v_j$  only if i < j. Following our notation described in Section 2.1, associated with each vertex  $v_i$  is its execution requirement  $e(v_i)$  which here is assumed to be integral (a pseudo-polynomial algorithm is meaningful only under this assumption), and its deadline  $d(v_i)$ . Associated with each edge  $(v_i, v_j)$  is the minimum intertriggering separation  $p(v_i, v_j)$ .

Let  $t_{i,e}$  be the minimum time interval within which the task T' can have an execution requirement of exactly e time units due to some legal triggering sequence, considering only a subset of vertices from the set  $\{v_1, \ldots, v_i\}$ , if all the triggered vertices are to meet their respective deadlines. Let  $t_{i,e}^i$  be the minimum time interval within which a sequence of vertices from the set  $\{v_1, \ldots, v_i\}$ , and ending with the vertex  $v_i$ , can have an execution requirement of exactly e time units, if all the vertices have to meet their respective deadlines. Lastly, let  $E = \max_{i=1,\ldots,n} e(v_i)$ . Clearly, nE is an upper bound on T'.dbf(t) for any  $t \ge 0$  for one-shot executions of T'.