## DESIGN METHODOLOGIES FOR INSTRUCTION-SET EXTENSIBLE PROCESSORS

YU, PAN

NATIONAL UNIVERSITY OF SINGAPORE

### Design Methodologies for Instruction-Set Extensible Processors

Yu, Pan

(B.Sci., Fudan University)

A thesis submitted for the degree of Doctor of Philosophy in Computer Science

Department of Computer Science

National University of Singapore

### List of Publications

- Y. Pan, and T. Mitra, Characterizing embedded applications for instruction-set extensible processors, In the Proceedings of *Design Automation Conference (DAC)*, 2004.

- Y. Pan, and T. Mitra. Scalable custom instructions identification for instruction-set extensible processors. In the Proceedings of International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES), 2005.

- Y. Pan and T. Mitra. Satisfying real-time constraints with custom instructions. In the Proceedings of International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), 2005.

- Y. Pan and T. Mitra. Disjoint pattern enumeration for custom instructions identification. In the Proceedings of International Conference on Field Programmable Logic and applications (FPL), 2007.

### Acknowledgement

I would like to thank my advisor professor Tulika Mitra for her guidance. Her broad knowledge and working style as a scientist, care and patience as a teacher have always been the example for me. I feel very fortunate to be her student. I wish to thank the members of my thesis committee, professor Wong Weng Fai, professor Samarjit Chakraborty and professor Laura Pozzi for their discussions and encouraging comments during the early stage of this work. This thesis would not have been possible without their support.

I would like to thank my fellow colleagues in the embedded system lab. They are, Kathy Nguyen Dang, Phan Thi Xuan Linh, Ge Zhiguo, Edward Sim Joon, Zhu Yongxin, Li Xianfeng, Liao Jirong, Liu Haibin, Hemendra Singh Negi, Hariharan Sandanagobalane, Ramkumar Jayaseelan, Unmesh Dutta Bordoloi, Liang Yun, and Huynh Phung Huynh. The common interests shared among the brothers and sisters of this big family have been my constant source of inspiration. My best friends Zhou Zhi, Wang Huiqing, Miao Xiaoping, Ni Wei and Ge Hong have given me tremendous strength and back up all along. And most importantly, thanks to Yang Xiaoyan, my fiancee, for her accompany and endurance during all these years.

My parents and my grand parents, they raised, inspired me, and always stand by me no matter what. My love and gratitude to them is beyond words. I wish my grand parents in heaven would be proud of my achievements, and to hug my parents tightly in my arms — at home.

### Contents

| Li            | List of Publications |                     |                                            |     |

|---------------|----------------------|---------------------|--------------------------------------------|-----|

| A             | cknov                | wledge              | ement                                      | ii  |

| C             | onter                | nts                 |                                            | iii |

| A             | bstra                | $\operatorname{ct}$ |                                            | ix  |

| Li            | ist of               | Figure              | es                                         | х   |

| ${f L}_{f i}$ | ist of               | Table               | s                                          | xv  |

| 1             | Intr                 | roducti             | ion                                        | 1   |

|               | 1.1                  | Specia              | dization                                   | 2   |

|               |                      | 1.1.1               | Inefficiency of General Purpose Processors | 3   |

|               |                      | 1.1.2               | ASICs — the Extreme Specialization         | 5   |

|               |                      | 1.1.3               | Software vs. Hardware                      | 6   |

CONTENTS iv

|   |      | 1.1.4  | Spectrum of Specializations              | 6  |

|---|------|--------|------------------------------------------|----|

|   |      | 1.1.5  | FPGAs and Reconfigurable Computing       | 11 |

|   | 1.2  | Instru | ction-set Extensible Processors          | 14 |

|   |      | 1.2.1  | Hardware-Software Partitioning           | 16 |

|   |      | 1.2.2  | Compiler and Intermediate Representation | 18 |

|   |      | 1.2.3  | An Overview of the Design Flow           | 19 |

|   | 1.3  | Contri | ibutions and Organization of this Thesis | 20 |

| 2 | Inst | ructio | n-Set Extensible Processors              | 24 |

|   | 2.1  | Past S | Systems                                  | 24 |

|   |      | 2.1.1  | DISC                                     | 25 |

|   |      | 2.1.2  | Garp                                     | 26 |

|   |      | 2.1.3  | PRISC                                    | 28 |

|   |      | 2.1.4  | Chimaera                                 | 30 |

|   |      | 2.1.5  | CCA                                      | 31 |

|   |      | 2.1.6  | PEAS                                     | 33 |

|   |      | 2.1.7  | Xtensa                                   | 34 |

|   | 2.2  | Design | Issues and Options                       | 36 |

|   |      | 2.2.1  | Instruction Encoding                     | 36 |

|   |      | 2.2.2  | Crossing the Control Flow                | 38 |

CONTENTS v

| 3 | Rela | ated W  | Vorks                                                       | 41 |

|---|------|---------|-------------------------------------------------------------|----|

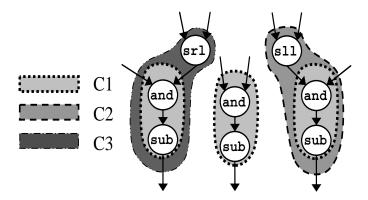

|   | 3.1  | Candi   | date Pattern Enumeration                                    | 42 |

|   |      | 3.1.1   | A Classification of Previous Custom Instruction Enumeration |    |

|   |      |         | Methods                                                     | 43 |

|   | 3.2  | Custo   | m Instruction Selection                                     | 46 |

| 4 | Sca  | lable C | Custom Instructions Identification                          | 50 |

|   | 4.1  | Custo   | m Instruction Enumeration Problem                           | 51 |

|   |      | 4.1.1   | Problem Definition                                          | 52 |

|   | 4.2  | Exhau   | stive Pattern Enumeration                                   | 56 |

|   |      | 4.2.1   | SingleStep Algorithm                                        | 56 |

|   |      | 4.2.2   | MultiStep Algorithm                                         | 57 |

|   |      | 4.2.3   | Generation of Cones                                         | 59 |

|   |      | 4.2.4   | Generation of Connected MIMO Patterns                       | 61 |

|   |      | 4.2.5   | Generation of Disjoint MIMO Patterns                        | 69 |

|   |      | 4.2.6   | Optimizations                                               | 73 |

|   | 4.3  | Exper   | imental Results                                             | 79 |

|   |      | 4.3.1   | Experimental Setup                                          | 79 |

|   |      | 4.3.2   | Comparison on Connected Pattern Enumeration                 | 80 |

CONTENTS vi

|   |     | 4.3.3   | Comparison on All Feasible Pattern Enumeration    | 82  |

|---|-----|---------|---------------------------------------------------|-----|

|   | 4.4 | Summ    | ary                                               | 85  |

| 5 | Cus | tom Ir  | nstruction Selection                              | 87  |

|   | 5.1 | Custon  | m Instruction Selection                           | 88  |

|   |     | 5.1.1   | Optimal Custom Instruction Selection using ILP    | 88  |

|   |     | 5.1.2   | Experiments on the Effects of Custom Instructions | 90  |

|   | 5.2 | A Stud  | dy on the Potential of Custom Instructions        | 94  |

|   |     | 5.2.1   | Crossing the Basic Block Boundaries               | 95  |

|   |     | 5.2.2   | Experimental Setup                                | 98  |

|   |     | 5.2.3   | Results and Analysis                              | 100 |

|   | 5.3 | Summ    | ary                                               | 107 |

| 6 | Imp | proving | WCET with Custom Instructions                     | 108 |

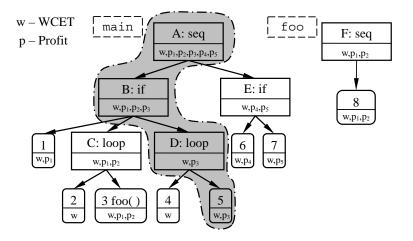

|   | 6.1 | Motiva  | ation                                             | 109 |

|   |     | 6.1.1   | Related Work to Improve WCET                      | 110 |

|   | 6.2 | Proble  | em Formulation                                    | 111 |

|   |     | 6.2.1   | WCET Analysis using Timing Schema                 | 112 |

|   | 6.3 | Optim   | al Solution Using ILP                             | 113 |

CONTENTS vii

|              | 6.4 | Heuristic Algorithm                  | 116 |

|--------------|-----|--------------------------------------|-----|

|              |     | 6.4.1 Computing Profits for Patterns | 117 |

|              |     | 6.4.2 Improving the Heuristic        | 119 |

|              | 6.5 | Experimental Evaluation              | 122 |

|              | 6.6 | Summary                              | 126 |

| 7            | Con | nclusions                            | 127 |

| $\mathbf{A}$ | ISE | Tool on Trimaran                     | 141 |

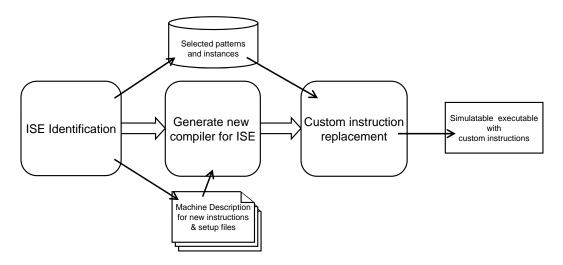

|              | A.1 | Work Flow                            | 142 |

|              | A 2 | Limitations of the Tool              | 144 |

### Abstract

The machine unmakes the man. Now that the machine is so perfect, the engineer is nobody. – Ralph Waldo Emerson

Customizing the processor core, by extending its instruction set architecture with application specific custom instructions, is becoming more and more popular to meet the increasing performance requirement of embedded system design. The proliferation of high performance reprogrammable hardware makes this approach even more flexible. By integrating custom functional units (CFU) in parallel with standard ALUs in the processor core, the processor can be configured to accelerate different applications. A single custom instruction encapsulates a frequently occurring computation pattern involving multiple primitive operations. Parallelism and logic optimization among these operations can be exploited to implement the CFU, which leads to improved performance over executing the operations individually in basic function units. Other benefits of using custom instructions, such as compact code size, reduced register pressure, and less memory hierarchy overhead, contribute to improved energy efficiency.

The fundamental problem of the instruction-set extensible processor design is the hardware-software partitioning problem, which identifies the set of custom instructions for a given application. Custom instructions are identified on the dataflow graph of the application. This problem can be further divided into two subproblems: ABSTRACT ix

(1) enumeration of the set of feasible subgraphs (patterns) of the dataflow graph as candidates custom instructions, and (2) choosing a subset of these subgraphs to cover the application for optimized performance under various design constraints. However, solving both subproblems optimally are intractable and computationally expensive. Most previous works impose strong restrictions on the topology of patterns to reduce the number of candidates, and then use heuristics to choose a suitable subset.

Through our study, we find that the number of all the possible candidate patterns under relaxed architectural constraints is far from exponential. However, the current state-of-the-art enumeration algorithms do not scale well when the size of dataflow graph increases. These large dataflow graphs pack considerable execution parallelism and are ideal to make use of custom instructions. Moreover, modern compiler transformations also form large dataflow graphs across the control flow to expose more parallelism. Therefore, scalable and high quality custom instruction identification methodologies are required.

The contributions of this thesis are the following. First, we propose efficient and scalable subgraph enumeration algorithms for candidate custom instructions. Through exhaustive enumeration, isomorphic subgraphs embedded inside the dataflow graphs, which can be covered by the same custom instruction, are fully exposed. Second, based on our custom instruction identification methodology, we conduct a systematic study of the effects and correlations between various design constraints and system performance on a broad range of embedded applications. This study provides a valuable reference for the design of general extensible processors. Finally, we apply our methodologies in the context of real-time systems, to improve the worst-case execution time of applications using custom instructions.

# List of Figures

| 1.1 | Performance overhead of using general purpose instructions, for a bit                                                                                                                                        |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | permutation example in DES encryption algorithm (adapted from [44]).                                                                                                                                         | 3  |

| 1.2 | Architecture of a 16-bit, 3-input adder (adapted from [32])                                                                                                                                                  | 5  |

| 1.3 | Spectrum of system specialization                                                                                                                                                                            | 8  |

| 1.4 | MAC in a DSP. (a) Chaining basic operations on the dataflow, (b) Block diagram of a MAC unit                                                                                                                 | 9  |

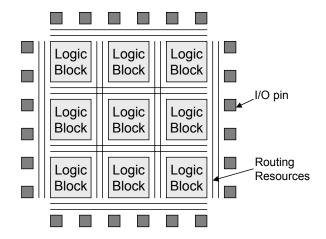

| 1.5 | General structure of a FPGA                                                                                                                                                                                  | 11 |

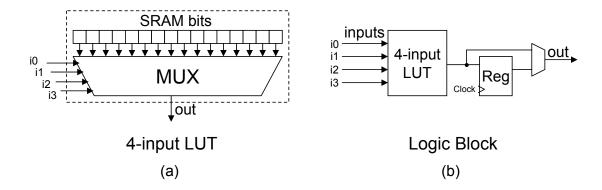

| 1.6 | Typical LUT based logic block. (a) A widely used 4-input 1-output LUT, (b) Block diagram of the logic block                                                                                                  | 13 |

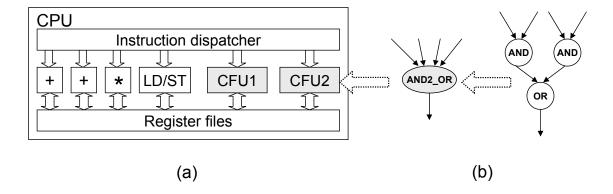

| 1.7 | General architecture of instruction-set extensible processors. (a) Custom functional units (CFU) embedded in the processor datapath, (b) A complex computation pattern encapsulated as a custom instruction. | 15 |

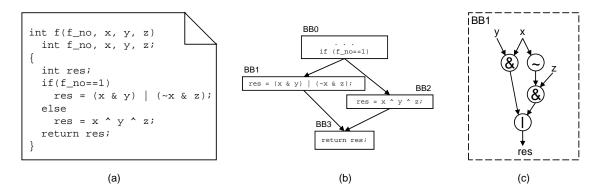

| 1.8 | Intermediate representation. (a) Source code of a function (adapted from Secure Hash Algorithm), (b) Its control flow graph, (c) Dataflow                                                                    |    |

|     | graph of basic block 1                                                                                                                                                                                       | 19 |

LIST OF FIGURES xi

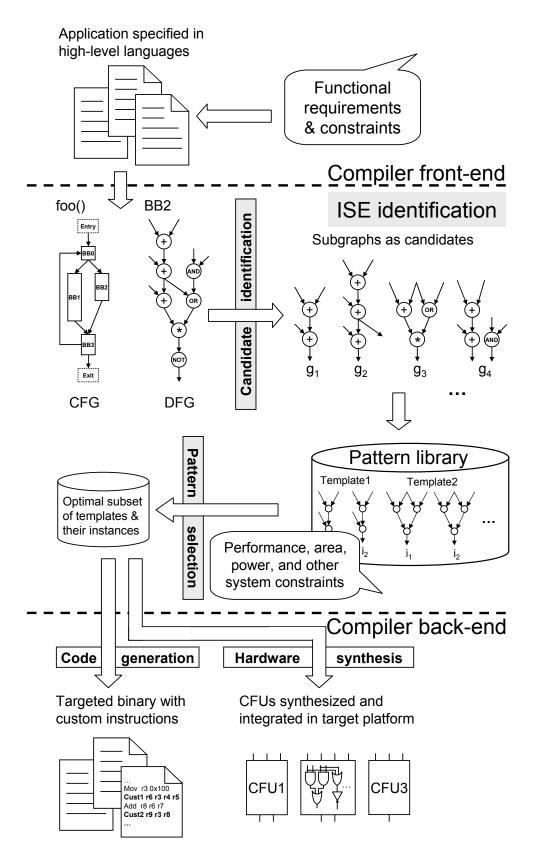

| 1.9 | Compile time instruction-set extension design flow                                                                                                                                                               | 21 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

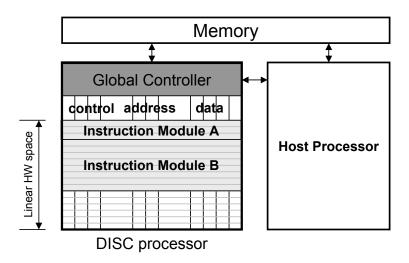

| 2.1 | DISC system (adapted from [81])                                                                                                                                                                                  | 25 |

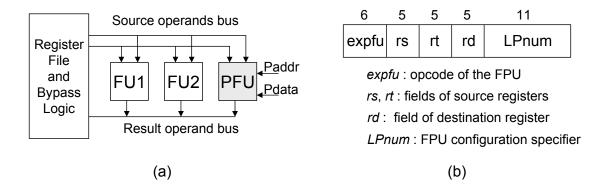

| 2.2 | PRISC system (adapted from [70]). (a) Datapath, (b) Format of the 32-bit FPU instruction                                                                                                                         | 28 |

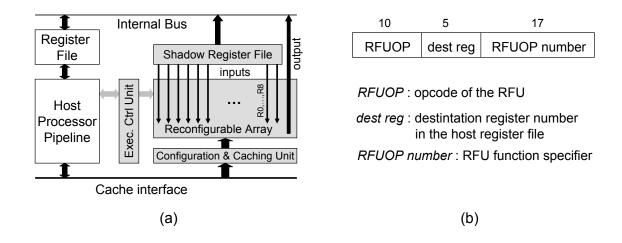

| 2.3 | Chimaera system (adapted from [82, 33]). (a) Block diagram, (b) RPUOP instruction format                                                                                                                         | 30 |

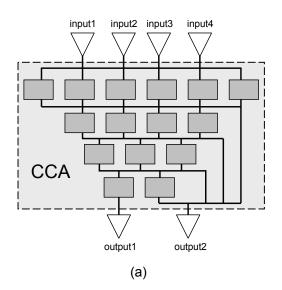

| 2.4 | The CCA system (adapted from [21, 20]). (a) The CCA (Configurable Compute Accelerator), (b) System architecture                                                                                                  | 31 |

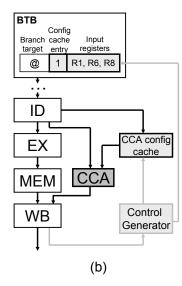

| 2.5 | The PEAS environment (adapted from [71, 46]). (a) Main functions of the system, (b) Micro-operation description of the ADDU instruction.                                                                         | 33 |

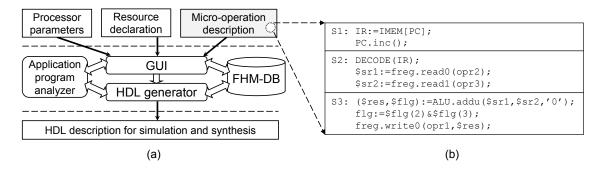

| 2.6 | Ways of forming custom instructions across the control flow. (a)  Downward code motion, (b) Predicated execution, (c) Control localization                                                                       | 38 |

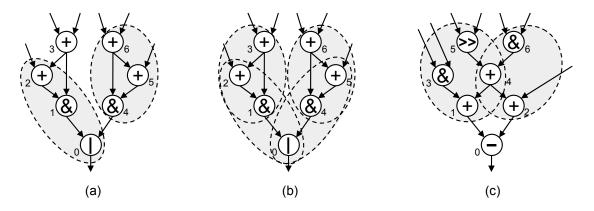

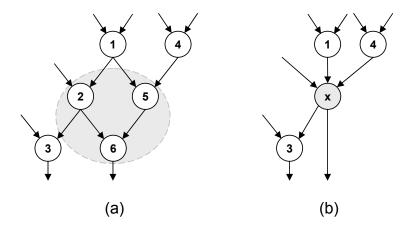

| 3.1 | Dataflow graph. (a) Two non-overlapped candidate patterns, (b)  Overlapped candidate patterns, (c) Overlapped patterns cannot be scheduled together                                                              | 43 |

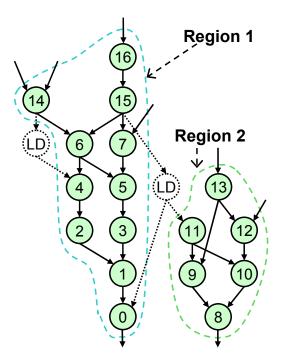

| 4.1 | An example dataflow graph. Valid nodes are numbered according to reverse topological order. Invalid nodes corresponding to memory load operations (LD) are unshaded. Two regions are separated by a LD operation | 52 |

LIST OF FIGURES xii

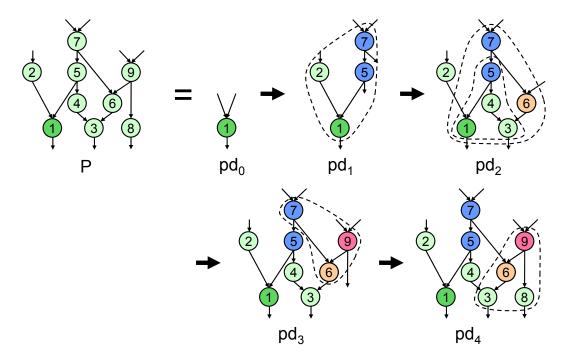

| 4.2 | Forming a feasible connected MIMO pattern through partial decom-            |    |

|-----|-----------------------------------------------------------------------------|----|

|     | position. Decomposition cones are dashed on each step. Trivial de-          |    |

|     | composition cones, like $\{1\}$ for every downward extension and $\{2\}$ in |    |

|     | $pd_3$ , are omitted. They are eliminated in the algorithm                  | 62 |

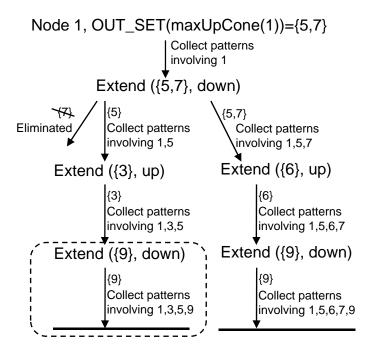

| 4.3 | Generating all feasible connected patterns involving node 1                 | 64 |

| 4.4 | A recursive process of collecting patterns for the example in Fig. 4.3.     | 64 |

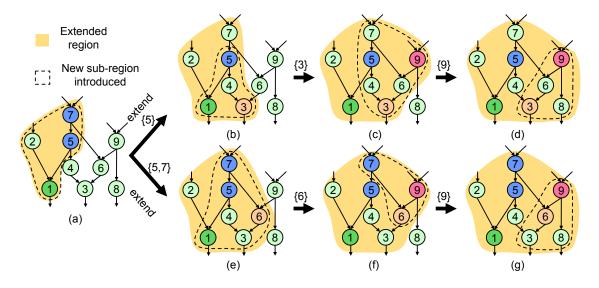

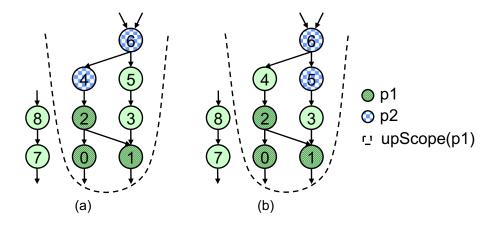

| 4.5 | Non-connectivity/Convexity check based on upward scope. (a) p2              |    |

|     | connects with p1. (b) p2 introduces non-convexity                           | 71 |

| 4.6 | Bypass pointers (dashed arrows) on a linked list of patterns                | 78 |

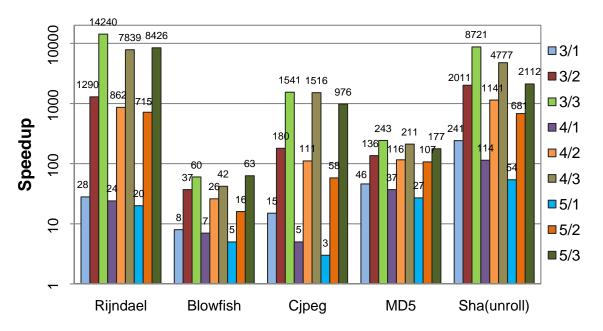

| 4.7 | Run time speedup (MultiStep/SingleStep) for connected patterns              | 82 |

| 4.8 | Run time speedup (MultiStep/SingleStep) for all feasible patterns           | 84 |

| 5.1 | Subgraph convexity. (a) A non-convex subgraph, (b) Two interde-             |    |

|     | pendent convex subgraphs, (c) The left subgraph turns non-convex            |    |

|     | after the right one is reduced to a custom instruction; consequently        |    |

|     | the left subgraph cannot be selected                                        | 89 |

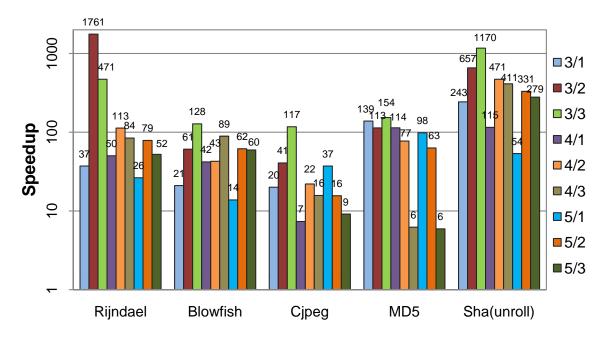

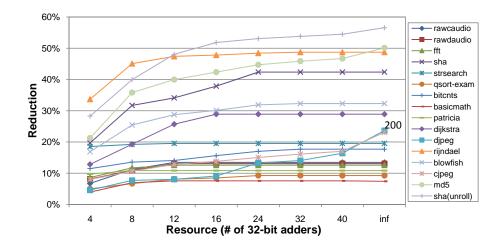

| 5.2 | Potential effect of custom instructions                                     | 92 |

| 5.3 | Effect of custom instructions                                               | 93 |

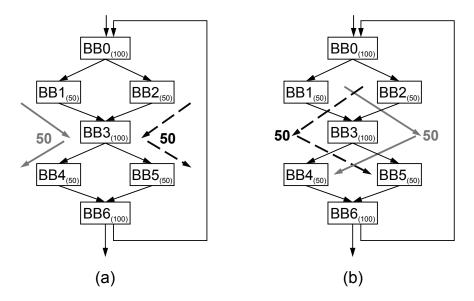

| 5.4 | Possible correlations of branches. (a) Left (right) side of the 1st         |    |

|     | branch is always followed by the left (right) side of the 2nd one,          |    |

|     | (b) Left (right) side of the 1st branch is always followed by the right     |    |

|     | (left) side of the 2nd one                                                  | 96 |

|     |                                                                             |    |

LIST OF FIGURES xiii

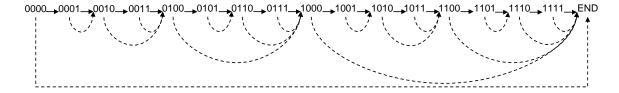

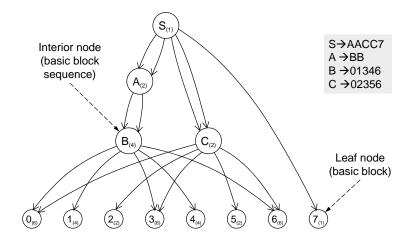

| 5.5  | WPP for basic block sequence $0134601346013460134602356023567$                                                      |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

|      | with execution count annotations                                                                                    |  |  |  |

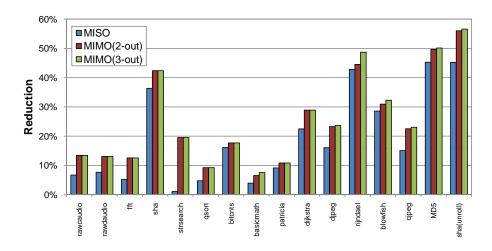

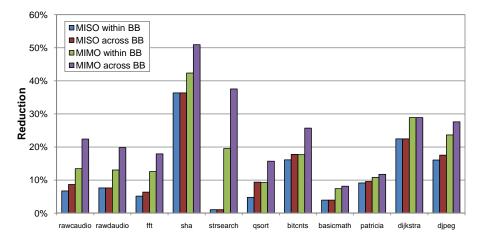

| 5.6  | Comparison of MISO and MIMO                                                                                         |  |  |  |

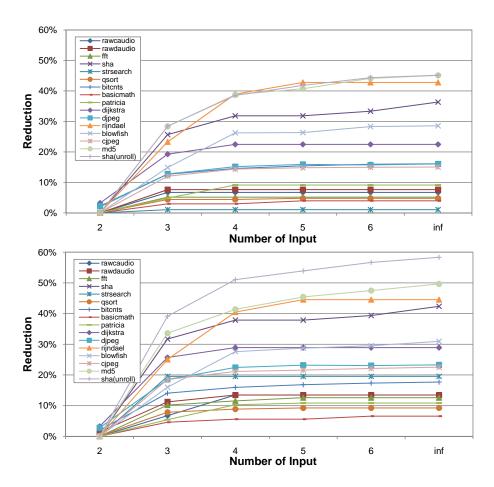

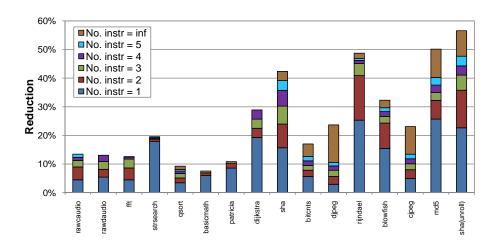

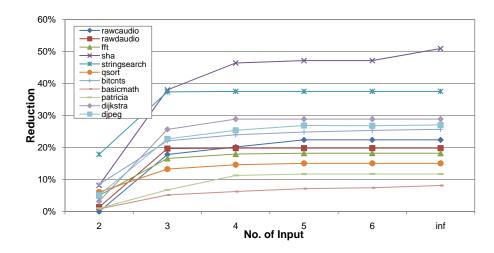

| 5.7  | Effect of Number of Input Operands                                                                                  |  |  |  |

| 5.8  | Effect of area constraint                                                                                           |  |  |  |

| 5.9  | Effect of constraint on total number of custom instructions                                                         |  |  |  |

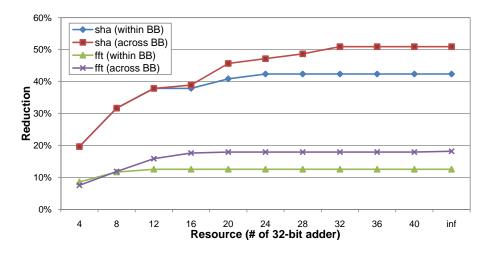

| 5.10 | Effect of relaxing control flow constraints                                                                         |  |  |  |

| 5.11 | Reduction across basic blocks under varying area budgets 105                                                        |  |  |  |

| 5.12 | Effect of number of input operands under 3 outputs across basic blocks.105                                          |  |  |  |

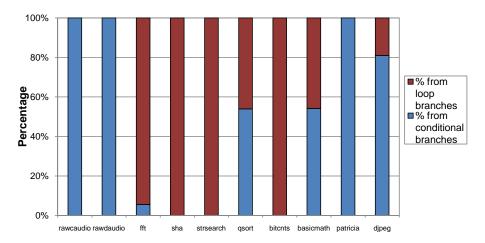

| 5.13 | Contributions of cycle count reduction due to custom instructions across <i>loop</i> or <i>if</i> branches          |  |  |  |

| 6.1  | An motivating example                                                                                               |  |  |  |

| 6.2  | CFG and syntax tree corresponding to the code in Figure 6.1 112                                                     |  |  |  |

| 6.3  | Efficient computation of profit function                                                                            |  |  |  |

| 6.4  | Limitation of the heuristic                                                                                         |  |  |  |

| A.1  | Pattern {1, 3} cannot be used without resolving WAR dependency between node 2 and 3 (caused by reusing register R3) |  |  |  |

| A.2  | Work flow of ISE enabled compilation                                                                                |  |  |  |

LIST OF FIGURES xiv

A.3 Order of custom instruction insertion. (a) Original operations is topologically ordered correctly (adapted from [22]), (b) The partial order is broken (node 4 and 3) after custom instruction replacement. . . . 144

### List of Tables

| 1.1 | Software vs. Hardware                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------|

| 1.2 | GPP vs. ASIC                                                                                                       |

| 4.1 | Benchmark characteristics. The size of basic block and region are given in terms of number of nodes (instructions) |

| 4.2 | Comparison of enumeration algorithms – connected patterns 82                                                       |

| 4.3 | Comparison of enumeration algorithms – disjoint patterns 83                                                        |

| 5.1 | Benchmark characteristics                                                                                          |

| 5.2 | Characteristics of benchmark programs                                                                              |

| 6.1 | Benchmark Characteristics                                                                                          |

| 6.2 | WCET Reduction under 5 custom instruction constraint with constrained topology                                     |

| 6.3 | WCET Reduction under 5 custom instruction constraint with relaxed topology                                         |

LIST OF TABLES xvi

| 6.4 | WCET Reduction under resource constraint of 20 32-bit full adders |

|-----|-------------------------------------------------------------------|

|     | with relaxed topology                                             |

| 6.5 | WCET Reduction under 10 custom instruction constraint with re-    |

|     | laxed topology. 125                                               |

### Chapter 1

### Introduction

The breeding of distantly related or unrelated individuals often produces a hybrid of superior quality. – The American Heritage Dictionary, in the paraphrase of "outbreeding".

Driven by the advances of semiconductor industry during the past three decades, electronic products with computation capability have permeated into every aspect of our daily work and life. Such devices like industrial machines, household appliances, medical equipments, automobiles, or recently popular cell phones, MP3 player and digital cameras, are very different from general purpose computer systems such as workstations and PCs in both appearance and functions. As their cores of computation are usually small and hidden behind the scenes, they are called *Embedded Systems*. In fact, there are far more embedded applications than those using general purpose computers. There is research showing that everyone among the urban population is surrounded by more than 10 embedded devices.

Though there is no standard definition for embedded systems, the most important characteristic is included in a general one: an *Embedded System* is any computer system or computing device that performs a **dedicated function** or is designed for use with a **specific embedded software application**. Most embedded computers run the same application during their entire lifetime, and such applications usually have relatively small and well-defined computation kernels and more regular data sets than general-purpose applications [69]. The additional knowledge of the determinacy, on the one hand, offers more opportunities to explore system effectiveness; on the other hand, it raises the design challenges in that the hardware architecture should be specialized to best suit the given application.

#### 1.1 Specialization

An effective embedded system for a given application is always designed around various constraints. A product should not only meet its computational requirements, i.e., the performance constraints, but also needs to be cost effective and efficient, in terms of silicon area and power consumption constraints. A general purpose computer for a simple task like operating a washing machine is overkill and very expensive. On the other hand, the same general purpose computer may be inefficient or even infeasible for certain I/O, data or computational intensive applications requiring very high throughput, such as network processing, image processing, encryption among others. Power consumption is frequently a major concern of many portable devices, which renders power hungry general purpose computers less favorable. For real-time embedded systems, timing constraints must be assured for task executions to meet their deadlines. Ideally, an embedded system should provide sufficient performance at minimum cost and power consumption. One way to achieve this is specialization — the exploitation and translation of application peculiarities into the system design. Specialization involves many aspects such as the design of processing unit, memory system, interconnecting network topology and others. This thesis focuses on the processing unit design — the heart of the computation.

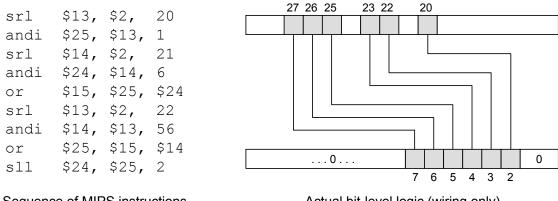

Sequence of MIPS instructions

Actual bit-level logic (wiring only)

Figure 1.1: Performance overhead of using general purpose instructions, for a bit permutation example in DES encryption algorithm (adapted from [44]).

#### Inefficiency of General Purpose Processors 1.1.1

A General Purpose Processor (GPP) is mostly designed with its generality in mind, achieved through the following sources. First, an application is broken down into a set of most fine grained vet general operations (e.g., 32-bit integer addition). A proper combinations of these fine grained general operations can be used to express any sorts of computations. This set of general operations defines the interface between the software and the processor, and is referred to as the Instruction-Set Architecture (ISA). Single operations or the instructions are executed through temporal reuse of a set of Functional Units (FU) inside the processor. Second, the sequence of instructions (and data), referred to as the program, is stored in a separate storage (i.e., the memory hierarchy). Each instruction is loaded and executed by the GPP at run time through a fetch-decode-execute cycle. In this Von Neumann architecture, computations can be changed simply by replacing the programs in the storage, without modifying the underlining hardware. The programs are hence referred to as Software due to the ultra flexibility and fluidity of realizing and switching among different computations.

The efficiency degradation of a GPP is largely caused by the requirement to

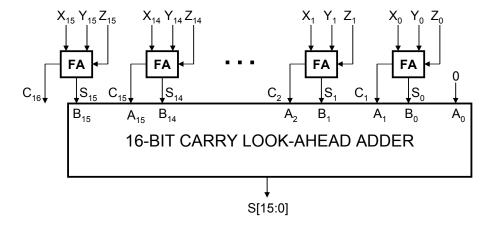

maintain generality. First, using general purpose instructions can lead to large performance overhead. A very good example is shown in Figure 1.1, where sparse yet simple bit permutations need to be encoded with a long instruction sequence. Moreover, a uniform bit length (e.g., 32-bit) of operands is under utilized in most occasions. Second, computation on a GPP needs to be sequentialized to reuse a handful of FUs. In this process, dependencies, from both dataflow and control flow, slow down the performance. As an example, the sum of 3 variables needs to be broken down into 2 consecutive 2-input additions. With the second addition data-dependent on the result of the first one, the execution on a general purpose 2-input FU requires two cycles to finish. On the other hand, the delay of a 3-input adder implemented directly with hardware increases only marginally. Figure 1.2 shows the block diagram of a 16-bit 3-input adder, which is composed of a layer of full adders on top of a 16-bit 2-input carry look-ahead adder. While the 16-bit 2-input carry look-ahead adder usually involves 8 gate levels (implemented in four 4-input carry look-ahead adders with a lookahead carry unit), the full adders on top involve only 2 gate levels. Therefore, the delay of a 16-bit 3-input adder is increased roughly 25% compared to that of a 2-input one. For a 32-bit 3-input adder, the relative delay increase is even less. If the clock cycle of the processor is not constrained by the FU, as is often the case, the 3-input addition can be executed within the same processor cycle. The sequential model of GPP execution marks the key difference between the implementations in software and specialized hardware<sup>1</sup>. Third, the energy efficiency of the instruction fetch-decode-execute cycle is quite poor. Comparing with the energy consumed by the real computations, much more energy is spent on the memory hierarchy and complicated mechanisms to fill the

<sup>&</sup>lt;sup>1</sup>Modern GPP architectures are able to exploit, to some extent, the lateral dataflow parallelism. Superscalar processors utilize large reservation stations and wide multi-issue units; VLIW processors rely on instruction packages containing multiple parallel instructions. Both architectures are restricted by the number of FUs that can execute concurrently, where a linear increase in number of FUs increase the overall circuit complexity significantly. Control flow parallelism faces the same restrictions as the dataflow part.

Figure 1.2: Architecture of a 16-bit, 3-input adder (adapted from [32]).

execution pipeline (to name a few, branch prediction, out-of-order execution and predicated execution) for sustained performance.

#### 1.1.2 ASICs — the Extreme Specialization

As opposed to software running on a GPP, the Application-Specific Integrated Circuit (ASIC) is referred to as the *Hardware* implementation of the application. ASICs hard-wire the application logic across the hardware space — a "sea of gates". The hardware logic can be directly derived from the application (e.g., the application fragment in Figure 1.1 only needs simple wiring), combined for gate level optimizations and adapted to exact bit-widths. Most importantly, unlike GPPs that rely on the reuse of FUs over time, ASICs exploit spatial parallelism offered in the hardware space. The inherently concurrent execution model is able to exploit virtually all the parallelism. Without the instruction fetch-decode-execute cycle, high performance and low power consumption can be achieved simultaneously.

However, the efficiency of ASICs does come at the cost of programmability. ASICs are totally inflexible. Once the device is fabricated, its functionalities are fixed. Every new product, even with small differences, needs to go through a new

design and mask process<sup>2</sup>, which drastically increases the design time and Non-Recurring Engineering (NRE<sup>3</sup>) cost. Updating existing equipments for new standards is not possible without hardware replacement. This inflexibility is especially undesirable for small volume products with minor functional changes (e.g., different models of cell phones in the same series), or under tight time-to-market pressure.

#### 1.1.3 Software vs. Hardware

The differences between software and hardware are further elaborated in Table 1.1. Table 1.2 summarizes and expands a little on the general pros and cons of using GPPs or ASICs over common design concerns.

As we can imagine, GPPs and ASICs sit at the very two ends of the spectrum with exactly opposite pros and cons. Either choice causes sacrifice of the benefits from the other one. Consequently, the current industrial practice couples GPPs and ASICs to different extents so as to take advantage of the combined strength, yielding a spectrum of possible choices.

#### 1.1.4 Spectrum of Specializations

Specialized circuits can be integrated to cooperate with the processor at various levels. Fine grained specialization can be done at the instruction level of the processor. In this way, frequently occurring computational patterns (which include multiple operations) can be executed more efficiently as complex instructions in specialized functional units directly on the processor's datapath.

<sup>&</sup>lt;sup>2</sup>Mask process creates photographic molds for multi-layered IC, and is usually very expensive.

<sup>&</sup>lt;sup>3</sup>NRE refers to the one-time cost of researching, designing, and testing a new product, and is supposed to be amortized in the later per-product sales.

|                       | Software                         | Hardware                        |

|-----------------------|----------------------------------|---------------------------------|

| Execution model       | Sequential model.                | Concurrent model.               |

| Logic encoding        | As formatted instructions in     | As hard-coded gates on the      |

|                       | the system memory.               | chip space.                     |

| Logic decoding        | On-the-fly by the decoding       | Not needed.                     |

|                       | logic in the processor pipeline. |                                 |

|                       | Generated signals control the    |                                 |

|                       | actual function of the FU for    |                                 |

|                       | the instruction.                 |                                 |

| Logic granularity     | Coarse, operations being "gen-   | Fine, exact bit-level manipula- |

|                       | eral" and operating on stan-     | tions and bit-length.           |

|                       | dard bit-length operands.        |                                 |

| Execution granularity | Fine, each instruction per-      | Coarse, a single hardware       |

|                       | forms a single operation.        | function packs a portion of     |

|                       |                                  | computations.                   |

Table 1.1: Software vs. Hardware.

| Design Concern    | Using GPP                        | Using ASIC                      |

|-------------------|----------------------------------|---------------------------------|

| Performance       | Low, due to logic overhead, in-  | High, due to bit-level manip-   |

|                   | struction fetch and decode over- | ulation, exact bit-width, logic |

|                   | head, and most importantly       | combination and optimization,   |

|                   | lack of concurrency.             | and concurrent execution.       |

| Power consumption | High, due to instruction load-   | Low, no instruction overhead,   |

|                   | ing, pipelining with high clock  | lower clocking.                 |

|                   | frequency, cache, out-of-order   |                                 |

|                   | execution, etc.                  |                                 |

| NRE cost          | Low, given off-the-shelf GPP,    | High, requiring intimate hard-  |

|                   | this mainly involves software    | ware design knowledge, expen-   |

|                   | development, supported by ro-    | sive development and verifi-    |

|                   | bust and fully automated com-    | cation equipments and tools,    |

|                   | pilation tools.                  | mask cost.                      |

| Manufactory cost  | High, GPP system cost more       | May cost less silicon.          |

|                   | silicon than ASICs.              |                                 |

| Time-to-market    | Fast, less development time.     | Slow, long development and      |

|                   |                                  | pre-manufacturing process.      |

| Risk              | Small, low NRE cost and fast     | Big, high NRE cost and slow     |

|                   | time-to-market.                  | time-to-market.                 |

| Maintainability   | Good, software maintenance is    | Poor, any faults found after    |

|                   | easier, bug fix and functional   | fabrication may cause produc-   |

|                   | changes can be applied easily.   | tion recall.                    |

Table 1.2: GPP vs. ASIC

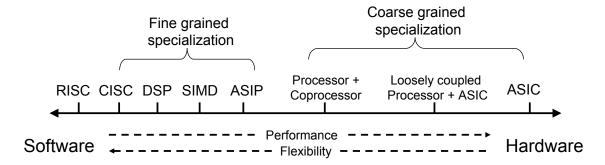

Figure 1.3: Spectrum of system specialization.

CISC, DSP, SIMD, ASIP architectures in Figure 1.3 are light weight fine grained specialization of processor's instruction set. For a RISC (Reduced Instruction-set Computer) processor on the leftmost side, each operation is executed with a single word-level instruction. A CISC (Complex Instruction-set Computer) processor allows a computational instruction to operate directly on operands in the system memory. This essentially is a coarser grained instruction consisting of both the memory access operations for the operands and the computational operation.

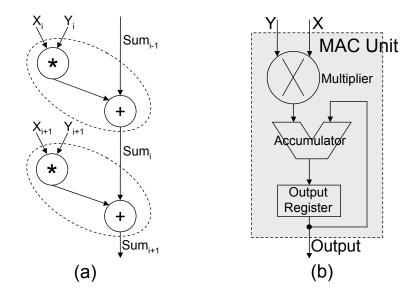

Digital Signal Processors (DSP) employ the single cycle MAC (Multiply-Accumulate) instruction to accelerate intensive product accumulations, i.e.,  $Sum = \sum X_i * Y_i$ . A MAC instruction computes the repeating pattern  $Sum_i = X_i * Y_i + Sum_{i-1}$  each in a single cycle, and accumulate the sum in an internal register progressively in the MAC unit. Note that in a GPP, the same pattern will be executed as a multiply instruction (maybe multi-cycle) followed by an add instruction, with the result of each instruction output to the register file. The block diagram and computation logic of a MAC unit are depicted in Figure 1.4. In order to achieve high performance, MAC units often use high speed combinational multipliers at the cost of the number of transistors.

Unlike collapsing data dependent operations as the MAC instruction, a SIMD (Single Instruction, Multiple Data) architecture exploits the parallelism among the operations. A single SIMD instruction applies the same operation on several in-

Figure 1.4: MAC in a DSP. (a) Chaining basic operations on the dataflow, (b) Block diagram of a MAC unit.

dependent data sources concurrently. Instructions of this kind are employed in supercomputers for long vector operations in scientific computation. They are also widely adapted in multimedia instruction-set extensions, such as MMX, SSE and 3DNOW!, to enhance short vector operations in multimedia and communication applications. SIMD units are usually assisted by wide registers and register ports for larger operand bandwidth.

ASIPs (Application Specific Instruction-set Processor) have their instruction-set tailored to a specific application or application domain. For example, special instructions are used in processors specialized in encryption for bit permutation and s-box operations [72], and in fast fourier transform to perform or assist butterfly operations [52]. In fact, DSPs and SIMDs are instances of ASIPs originally in the domain of digital signal processing and scientific computation, even though their functions tend to become an integral part of general purpose processors for wide range of consumer applications.

In a coarse grained specialization approach, computationally intensive tasks or kernel loops are mapped to the hardware, loosely coupled with the host processor as a co-processor. The host processor works with the co-processor in a "master/slave" fashion. Special communication instruments are used for data transfer and synchronization via system bus or network in between. The co-processor has a higher degree of independence but it incurs longer communication latency with the processor, compared to specialized functional units. Computation kernels mapped to the co-processor usually require intensive algorithmic and hardware oriented optimizations to exploit full performance potential. In this sense, the intimate knowledge of hardware and effort required from the designers and tools are comparable to that of a pure ASIC design. However, the decoupling of computation kernels does provide opportunities of reusing the hardware component. Through proper parametrization and interfacing, verified high performance hardware components of useful algorithms can be plugged into a different system with less design and manufacturing effort. An example of loosely coupled hardware module is reviewed in Section 2.1.2.

In general, specialization on larger execution granularity carries more performance advantages. More effort, mainly focusing on loop transformation and optimization to expose more parallelism or even algorithm changes to adapt to the concurrent execution model, is needed to achieve optimized performance. On the other hand, fine grained specialization is more flexible, as smaller computation patterns strike a more balanced distribution of software/hardware execution, and can be reused wherever they appear. Computation patterns can be deduced from the software implementation of the application, which fits well in the software compilation process. The trade-off goes to the less performance gain compared to a coarse grained approach.

Figure 1.5: General structure of a FPGA.

#### 1.1.5 FPGAs and Reconfigurable Computing

Coupling hard-wired logic with microprocessors strikes the balance between performance and design effort. However, it does not break the "fixed once fabricated" model. A more flexible solution has only unfolded with recent availability of high density, high performance reconfigurable hardware, which is capable of being reprogrammed conveniently and swiftly after fabrication. Reconfigurable hardware is also able to achieve high performance through concurrent execution model of computation. Therefore, it is considered as the glue technology connecting the worlds of software and hardware. The methodologies and applications of utilizing hardware reconfigurability are known as *Reconfigurable Computing*.

The basis of reconfigurable computing is reconfigurable devices, a common example being Field-Programmable Gate Arrays (FPGAs). As indicated with the phrase "Field-Programmable", the functionality of an FPGA can be determined on-site, rather than at the time of its fabrication. An FPGA contains an array of small computational elements known as logic blocks, surrounded and connected by programmable routing resources. The functionality of logic blocks and connectivity of routing resources are determined through multiple programmable configuration

points. Each configuration point is associated with SRAM bits in SRAM based FPGAs. Reconfiguration is merely the process of loading organized bitstream to the SRAM. Figure 1.5 shows the general structure of a FPGA. In a real product, hundreds of thousands of logic blocks can be integrated on a single chip (e.g., 330K logic blocks on a Xilinx Virtex-5 chip [41] comparable roughly to the logic capacity of a million gates), onto which even large and complex algorithms can be mapped.

The logic blocks of most commercially available FPGAs are based on Lookup Tables (LUT). LUTs express fine-grained bit-level logic, and are hence very flexible to implement random digital logic and bit-level manipulations. As depicted in Figure 1.6 (a), an LUT is simply a piece of  $2^N$  bit memory indexed by its inputs of size N. By loading the values of the memory bits, an LUT is capable of performing any N-input logic functions. Besides the LUT, a logic block usually contains additional logic for clocking (Figure 1.6 (b)). Functions of more than N inputs and 1 outputs are implemented by stacking multiple logic blocks through the routing resource. For example, a binary full adder involving 3 inputs (2 addends and 1 carry-in) and 2 outputs (sum and carry-out) can be implemented using two 4-input LUTs for sum and carry-out respectively<sup>4</sup>, each leaving one input unused. A standard 16-bit carry ripple adder can be obtained by properly connecting 16 binary full adders. However, certain operations, e.g., multiplication and floating-point computations, cannot be implemented efficiently on LUTs due to the very regular on-chip routing structure and massive amount of resource required. Some FPGAs embed small hard-wired multipliers with logic blocks to assist multiplications [41]. Designers also need to transform float-point computations to fix-point ones whenever possible. Otherwise, it is better to avoid mapping those computations onto FPGAs.

FPGAs can be coupled with a host processor at different levels [14, 23], replac-

<sup>&</sup>lt;sup>4</sup>Most current FPGAs [39, 41] include fast carry logics within logic blocks with dedicated carryin and carry-out routings to speed up carry based computations. In this case, a binary fulladder requires only a single logic block.

Figure 1.6: Typical LUT based logic block. (a) A widely used 4-input 1-output LUT, (b) Block diagram of the logic block.

ing the functions of hard-wired components. The processor is not only used for non-intensive computations and flow control, but also as an agent to set up and reconfigure the FPGA. SRAM based FPGAs need to be configured at system start-up. Reconfigurations can be performed at run-time to timeshare the limited reconfigurable resources among different phases of the execution or different applications.

FPGAs are able to achieve substantial performance improvement over a pure general purpose processor based system. Although reconfigurability of FPGAs comes at the cost of penalties on performance, area and power consumption compared to hard-wired solutions, it is however well justified especially under the following circumstances:

- Maintaining, upgrading or modifying the functionalities are desirable after device deployment.

- Small volume products based on existing reconfigurable systems could bypass the expensive and time consuming manufacturing process.

- The concept of "virtual hardware" helps radically reduce hardware cost, where components operating under different scenarios do not need to co-exist physically and can be instantiated on demand, sharing the same reconfigurable resource.

• For an application with certain data values changing slowly over time, e.g., a key-specified encrypter, the set of values lasting for a period of time can be used to create an optimized configuration for the time window. By treating those data values as constants, logic of the configuration can be greatly simplified through partial evaluation techniques. As inputs are instantiated, such a customized system may achieve even higher performance than the ASICs.

#### 1.2 Instruction-set Extensible Processors

The efforts of this thesis go to the fine grained specialization of the processor's instruction-set. In particular, we focus on the processors with configurable instruction-set. Such a processor core is usually divided into two parts: the static logic for the basic ISA, and the configurable logic for the application specific instructions. The configurable part of the processor can either be implemented in reconfigurable logic for flexibility and run-time reconfigurability, or hard-wired for higher performance and lower power consumption. In either case, with well defined hardware interfaces between the two parts, the complexity of the design effort to tailor the processor for a particular application is narrowed down to defining the new instructions [47].

As the set of configurable application specific instructions is usually referred to as the *Instruction-set Extension* (ISE), we call such a processor, under the category of ASIP, an *Instruction-set Extensible Processor* (ISEP), or *Extensible Processor*. While instructions from the basic ISA are base instructions, an instruction customizable for specific applications is a *Custom Instruction*.

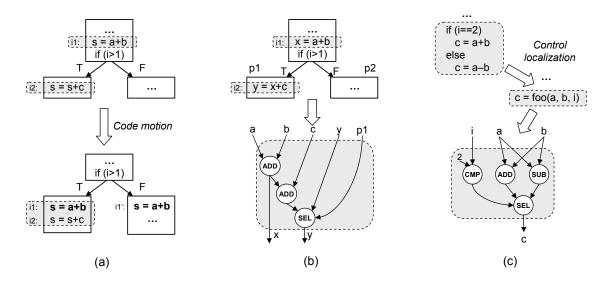

The general architecture of an extensible processor is shown in Figure 1.7. Custom Functional Units (CFU) are integrated in the base processor core at the same level as other base functional units, and access the input and output operands stored

Figure 1.7: General architecture of instruction-set extensible processors. (a) Custom functional units (CFU) embedded in the processor datapath, (b) A complex computation pattern encapsulated as a custom instruction.

in the register file. A custom instruction is an encapsulation of a frequently occurring computation pattern involving a cluster of basic operations (see Figure 1.7(b)), and can be executed with a single fetch-decode-execute pass. Hardware implementation of the operation cluster with the CFU exploits the concurrency among parallel operations (e.g., the two ANDs in Figure 1.7(b)), optimizes performance of chained (dependent) operations at the gate level (e.g., a 3-input adder); thus it is able to improve the overall execution time. Besides, as the clock period of the processor pipeline is often not constrained by the ALUs<sup>5</sup>, the increase of actual latency of the combined logic may not prolong the clock period or require extra cycles. For example, logic operations as in Figure 1.7(b) are only one level logic, and several of them can be easily chained within a clock period.

A custom instruction may require more input and output operands than the typical 2-input 1-output instructions; but it also brings about better register usage by eliminating the need to output intermediate values, which otherwise need to

<sup>&</sup>lt;sup>5</sup>For example, the out-of-order issue logic of a superscalar processor often becomes the bottleneck for the clock period since its latency increases quadratically with the size of the issue window [78]. Also, while gate level logic benefits much from process technology advances, bypass network latency does not [62], and can become the bottleneck as well. After all, most processors run at frequencies lower than their technology limits. For portable embedded systems, a slower clock frequency is often required and essential to reduce power consumption. Reduced execution overhead due to custom instructions also creates opportunities to lower the clock frequency.

be written back to the register file (e.g., the results of the two AND operations in Figure 1.7(b)). The denser code leads to smaller code size. Energy consumption can also be reduced due to improved memory hierarchy performance (code size reduction, less cache footprints) and other factors mentioned earlier.

In specific designs, coarser grained ALU based logic blocks can be used to implement the reconfigurable CFUs, trading off bit-level manipulation flexibility against faster reconfiguration and execution performance. Instead of using a single unified register file with large number of read/write ports for CFU inputs and outputs, multiple or dedicated register banks can be used. The design space has conflicting objective functions such as performance, flexibility and complexity. We will study specific extensible processors and some of the design options later in Chapter 3.

#### 1.2.1 Hardware-Software Partitioning

The main design effort of tailoring an extensible processor is to define the custom instructions for the given application to meet design goals. Identifying suitable custom instructions is the hardware-software partitioning process that divides the computations between the processor execution (using base instructions) and hardware execution (using custom instructions). Various design constraints must be satisfied in order to deliver a viable system, including performance, silicon area cost, power consumption and architectural limitations. This problem is frequently modeled as a single objective optimization procedure by optimizing a certain aspect (usually performance), while putting constraints on the others. Specifically, the custom instruction identification process extracts suitable computation patterns from the application to derive the ISE for the maximal performance under design constraints.

A general hardware-software partitioning practice usually starts with the software implementation of the application written in high-level languages (e.g., C/C++, FORTRAN). The application is compiled, and profiled by executing it with typical data sets on the target processor. Based on the profiling information, hot spots, which occupy noticeable potions of the total execution time, are located. These hot spots indicate the code locations that may benefit from hardware execution, and are candidates for hardware implementations. The designer then tries to map the functionality corresponding to the hot spots to hardware (custom instructions, in our case). If the hardware area exceeds the preset budget, the designer will need to optimize the hardware functions for area while possibly trading off some performance. Unfortunately, the process of mapping software code to the hardware is tedious, time consuming and highly dependent on the knowledge of the designer. Although an experienced designer can even perform algorithmic changes to expose more opportunities for efficient hardware implementation, regularities embedded inside large and complicated computation paths are sometimes hard to discover. Manual effort is therefore unlikely to cover the computation optimally with limited hardware resource.

In order to overcome these difficulties of manual partitioning, we present a compiler based automatic custom instruction identification flow. In a software development environment, the compiler breaks down high-level language statements into basic operations and map these operations to processor instructions to produce the machine executable. In our design flow, the compiler in addition performs ISE identification to find suitable computation patterns and generates the executable with custom instructions. Instead of manual algorithmic changes, we rely on modern compiler transformations to expose potential parallelism among base operations. Large computation paths can be efficiently explored by methodologies devised in this thesis. Software programmers can also easily adapt to the ISEP design flow

without in depth hardware knowledge.

#### 1.2.2 Compiler and Intermediate Representation

A generic compiler processes the code of the application as follows. High-level language statements are first transformed by the compiler front-end to the Intermediate Representation (IR), structured internally as graphs. Various analysis and re-arrangements of operations known as machine independent optimizations are carried out on the IR. Then, the back-end of the compiler generates binary executables for the target processor by binding IR objects to actual architectural resources, operations to instructions, operands to registers or memory locations, concurrencies and dependencies to time slots, through instruction binding, register allocation, and instruction scheduling, respectively. Various machine dependent optimizations are also performed at the back-end.

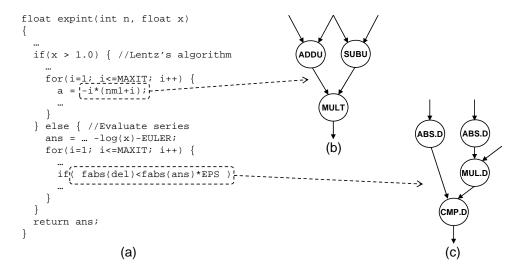

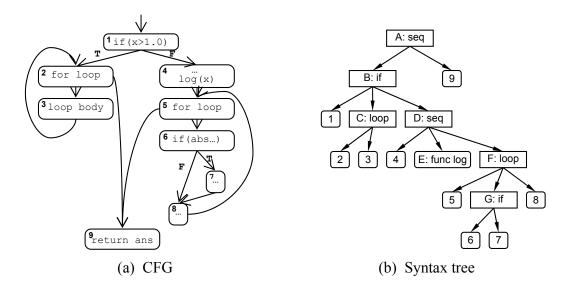

The IR consists of Control Flow Graph (CFG) and Dataflow Graph (DFG, also called Data Dependence Graph) that are used for the ISE identification. CFG expresses the structure of the application's logic flow (if-else, loops and function calls) by partitioning the code into basic blocks over control flow altering operations, i.e., jumps and branches. An edge between two basic blocks indicates a possible control flow direction to take, depending on the outcome of the branch condition (if any). For each basic block, DFG is constructed to express the dataflow<sup>6</sup>, with operations as nodes and edges attributing the dependencies among the operands. Figure 1.8 shows an example of CFG and DFG corresponding to a code segment. For a GPP, each operation on the DFG is usually covered with one machine instruction

<sup>&</sup>lt;sup>6</sup>A basic blocks is the basic unit for instruction scheduling because control flow within it does not change. However, basic blocks are usually very small (average 4-5 instructions each) and severely constraint the performance of modern Instruction Level Parallelism processors (superscalars and VLIWs). Larger blocks containing multiple basic blocks, e.g., traces, superblocks and hyperblocks, are exploited with architectural support. DFGs can be built upon those blocks as well. We will see how custom instructions can be used in those cases in Section 2.2.2.

Figure 1.8: Intermediate representation. (a) Source code of a function (adapted from Secure Hash Algorithm), (b) Its control flow graph, (c) Dataflow graph of basic block 1.

during instruction binding. However, a custom instruction intends to cover a cluster of operations and is hence captured as a *Subgraph* of the DFG.

#### 1.2.3 An Overview of the Design Flow

In our design flow, the compiler should perform three additional tasks: identifying the ISE, generating the binary executables under the new instruction-set, and producing the new CFUs.

ISE identification is essentially a problem of regularity extraction, which attempts to find common substructures in a set of graphs. Topologically equivalent DFG subgraphs perform the same logic function, forming a template pattern for a potential custom instruction. Each occurrence is an instance of the template. The target of ISE identification problem is to find a small number of templates along with their instances to cover the DFGs for the fastest execution. This problem involves the following two subproblems. (1) Candidate pattern enumeration — enumerate a set of subgraphs from the application's DFG and build the pattern library of templates and their instances. (2) Custom instruction selection — evaluate each candidate in the library and select an optimal subset under various design con-

straints. The first subproblem is a subgraph enumeration problem, while the second is an optimization problem.

The work flow of the partitioning process is depicted in Figure 1.9. ISE identification is plugged in between the compiler front-end and back-end. Heavily executed hot spots of the application, identified through program profiling, are processed by ISE identification algorithms. The resultant templates are then passed to the compiler back-end. During instruction binding, the instances of these templates will be mapped to custom instructions, either by simple peephole substitution or by the pattern matcher that recognizes the new templates, to produce the executables. Hardware description of the templates are generated and fed to the synthesis tool chain to build the CFUs on the target hardware. Decoding logic of the processor also needs to be modified for the new instructions.

#### 1.3 Contributions and Organization of this Thesis

The main contributions of this thesis are the efficient and scalable custom instruction identification methodologies. The capabilities of handling very large dataflow graphs and subgraphs with relaxed architectural constraints are essential for the custom instructions to exploit greater parallelism and operation chaining opportunities exposed by modern compiler transformations. Thus it is crucial for the automatic design flow to generate high quality solution for the given application. Specific contributions are listed as follows:

1. We present efficient and scalable subgraph enumeration algorithms for the candidate pattern enumeration problem. Through exhaustive enumeration, isomorphic subgraphs embedded inside the dataflow graphs, which can be

Figure 1.9: Compile time instruction-set extension design flow.

covered by the same custom instructions, are fully exposed to the selection process. Our custom instruction selection method based on integer linear programming (ILP) is able to exploit subgraph isomorphism optimally. Given this, the resulting effect indicates that a small set of custom instructions can usually achieve most performance improvement of the applications.

- 2. Based on our custom instruction identification methodology, we then conduct a systematic study of the effects and correlations between various design constraints and system performance on a broad range of embedded benchmark applications. In particular, a dynamic execution trace based method is adapted to broaden the scope of custom instruction identification beyond basic blocks, which allows us to characterize the limit potential of using custom instructions. This study provides a valuable reference for the design of general extensible processors.

- 3. We explore a novel application of using custom instructions to meet timing constraints of real-time systems. Custom instructions are selected using a modified ILP formulation to minimize the worst-case execution time of the application. We also devise high quality heuristic selection algorithms to avoid the complexity of solving ILP formulations, which yield identical selections to the optimal ones most of the times within very short run time.

This thesis is organized as follows. We discuss existing extensible processors and several important design issues in Chapter 2 in order to provide a more comprehensive background for the ISEP scene. Related works on the custom instruction identification problem are reviewed in Chapter 3. In Chapter 4, we present the scalable subgraph enumeration algorithms for the candidate pattern enumeration problem. We describe the optimal custom instruction selection based on integer linear programming in Chapter 5. In the same chapter, we present the study on

the performance impact using custom instructions under various design constraints. Methodologies of applying custom instructions to improve worst-case execution time for real-time applications are presented in Chapter 6. Finally, Chapter 7 concludes the thesis.

# Chapter 2

## Instruction-Set Extensible

# Processors

A huge gap exists between what we know is possible with today's machines and what we have so far been able to finish. – Donald E. Knuth

We review previous works on instruction-set extensible processors in this chapter. Note that this review does not intend to be exhaustive, but highlights different options and important design issues, and serve as a more comprehensive background of the ISEP scene.

#### 2.1 Past Systems

The order of the presentation in this section shows the trace of system evolvement. We study seven systems, which grow in features and sophistication. The focus of systems with reconfigurable ISE are mainly on the architecture design of effective reconfigurable CFUs that can be swiftly reconfigured, and relaxing the I/O constraints

of the CFUs. The focus of configurable extensible processors with synthesized CFUs are on the design environment which provides a high-level interface to specify the logic of custom instructions and evaluate their effects, the automatic generation of the compilation tool chain and hardware descriptions. The techniques studied in this section merely show the possibilities. Again, a real life extensible processor is a trade-off among different aspects, satisfying various design constraints.

#### 2.1.1 DISC

Figure 2.1: DISC system (adapted from [81]).

DISC [81], standing for "Dynamic Instruction Set Computer", is one of the earliest attempts in reconfigurable instruction set customization at Brigham Young university. In the DISC processor (Figure 2.1), custom instructions along with most primitive instructions are executed in the reconfigurable "instruction modules". The instructions are controlled and sequenced by the global controller, which is also in charge of memory accesses and reconfiguration requests. An instruction module is implemented on the linear reconfigurable hardware space, occupies multiple consecutive rows of fixed width (e.g., a constant shifter consumes 1 row, while an adder/subtracter takes 3 rows), and communicates with the global controller

through the underlining bus. The instruction modules are also relocatable, such that they can fit into consecutive rows available anywhere on the RA (Reconfigurable Array). In fact, the row based RA design turns out to be very effective for relatively small dataflow computations due to its simplicity and predictable timing model, and is adapted in most later systems, such as Garp [34], PRISC [70] and Chimaera [82].

At run time, the global controller takes an instruction from the memory, executes it if its corresponding instruction module is available. Otherwise, the global controller halts the execution, and sends a request to the host processor for the missing instruction module. According to the current status of the resource occupation, the host processor either allocates the rows if available, or free up other instruction modules using simple LRU (Least-Recently-Used) algorithm to make room for the new instruction module. After the instruction module is loaded from the pre-synthesized instruction library to the allocated space of the RA, the global controller resumes execution.

The problem of DISC is its uniform treatment of custom instructions and simple primitive instructions. Primitive operations executing on hard-wired ALUs can be more efficient than executing them on reconfigurable logic. Executing primitive operations on hard-wired ALUs will also reduce the complexity of run-time resource management. The full fledged host processor used for only resource allocation and reconfiguration is highly under utilized. Instead, a much simpler processor, even integrated with the global controller, can achieve the same functionality.

#### 2.1.2 Garp

The Garp project at UC Berkeley [34] has a similar reconfiguration array architecture as DISC (linear hardware space and row based reconfiguration), and addresses

several of DISC's limitations. Instead of executing primitive operations on the RA, the host – a MIPS II processor takes over the primitive operations. The MIPS II instruction set is augmented to manage the RA. There is no explicit run-time resource management in Garp, partially because mapping only the computational intensive kernels reduces total resource requirement and hence configuration swaps. In addition, Garp can cache upto four configurations, allowing fast configuration switches in a transparent fashion. This way, resource management is replaced by cache management.

Some additional instructions are added to the MIPS II core to control the RA. A configuration in the main memory is loaded (or switched to if cached) through a gaconf instruction. Input data is set up by mtga instructions, which transfers the value of a MIPS II register to an RA register. Meanwhile, mtga is able to set the internal clock counter of RA to a positive value, indicating the cycles needed to complete the custom function. Finally, mfga waits the counter to decrease to zero, and reads the result data back to a MIPS II register from an RA register.

As the RA has no direct access to MIPS II registers, small dataflow graph computation would carry communication overhead due to the use of explicit data transfer instructions (e.g., mtga and mfga). This may offset the performance improvements. In fact, the RA is built with direct access to the memory, targeting coarser grained innermost loop computations [13], where communication overhead can be amortized. Although the RA in DISC processor also has memory access (through the global controller), all instruction modules (primitive and custom operations) are architecturally equal. In contrast, custom functions in Garp are executed differently from the normal instructions; the RA works more like a slave to the MIPS II processor. Technically, Garp is a loosely coupled reconfigurable architecture. However, the improvements over DISC project as suggested above do provide useful guidelines for later extensible processor designs.

Figure 2.2: PRISC system (adapted from [70]). (a) Datapath, (b) Format of the 32-bit FPU instruction.

#### 2.1.3 PRISC

PRISC (PRogrammable Instruction Set Computer) [70] is the very first work that defines the typical architectural of an ISEP (see Section 1.2). As depicted in Figure 2.2(a), a single 2-inputs 1-output PFU (Programmable Functional Unit) is added at the execution stage of a RISC processor pipeline in parallel with standard FUs. The PFU behaves the same way as other FUs that have direct access to the register file and bypassing network, and is restricted to 1 cycle execution latency for simpler synchronization.

The PFU instruction is encoded with a standard 32-bit format shown in Figure 2.2(b). expfu is the opcode triggering the PFU, while LPnum specifies a certain PFU configuration, each corresponding to a different custom function. At run time, the current PFU configuration specifier is hold in a special 11-bit register. A mismatch between the register and the LPnum field of a PFU instruction causes an exception. The exception handler will then reconfigure the PFU to the configuration specified by LPnum, and update the special register accordingly. Configuration bits are sent to the PFU via Paddr and Pdata ports (Figure 2.2(a)). This is done either by the processor using augmented load instructions sequentially for a low speed solution, or by a dedicated configuration controller with fast memory access

for a high speed solution. The minimum reconfiguration latency is reported to be around 100 cycles. As there is only 1 PFU and configuration switches within a loop body is highly undesirable, a 1 configuration per loop restriction is imposed.

Automatic but straight forward hardware-software partitioning is used to group operations for the PFU. At first, the operations of the target application are analyzed, and the ones not suitable for mapping to the PFU are marked (i.e., memory operations, floating-point operations, multiplication and division). Starting with a suitable operation on the dataflow graph, the algorithm follows the data dependencies backwards and greedily includes suitable operations in the function along the way. The backward traversal terminates when the next operation is a non-suitable one, or including it yields a function requiring more than 2 source operands or more than 1 destination operand. The resultant group of suitable operations is called a maximal, and will be fed to the hardware synthesizer to produce the corresponding configuration image.

The main limitation of PRISC is that the PFU is restricted to 2-input 1-output functions. Even though this simplifies operands encoding and minimizes modification to the register file, it severely restrains the PFU from implementing larger groups of operations with more number of input/output operands which stand for higher performance improvements. Furthermore, no reuse of equivalent logic function at different locations with the same PFU is considered, even though encoding input/output registers in the PFU instruction format already provides this flexibility. However, this kind of reuse may not really be beneficial due to the single PFU setup, unless the equivalent functions occur consecutively without being replaced by the other configurations in the middle.

Figure 2.3: Chimaera system (adapted from [82, 33]). (a) Block diagram, (b) RPUOP instruction format.

#### 2.1.4 Chimaera

The Chimaera reconfigurable functional unit [82, 33] (RFU) developed at Northwestern University is inspired by PRISC, but is more sophisticated and integrated inside an out-of-order superscalar processor core. The main innovation of the Chimaera RFU is its capability of using up to 9 input registers and producing 1 result in an output register. This is achieved through a special design of the RA, where the values of all the registers (in fact the shadow registers in Figure 2.3(a)) are propagated through out the RA and hard-wired in the configurations so that they can be accessed simultaneously (see [82] for details). Hard-wiring the inputs on the one hand eliminates the need of encoding input registers explicitly in the RFU instruction (see the instruction format in Figure 2.3(b)). In fact, it is not possible to encode so many input operands in a single 32-bit instruction. On the other hand, as a trade-off, RFU instructions cannot be reused upon any changes in the input operands. This inflexibility is partially compensated by accommodating multiple RFU configurations on the RA, with its resource managed by the configuration and caching unit (similar to the DISC processor).

In order to interface with the out-of-order core, a shadow register file of size equal

Figure 2.4: The CCA system (adapted from [21, 20]). (a) The CCA (Configurable Compute Accelerator), (b) System architecture.

to the number of logical registers (9, in Chimaera) is used<sup>1</sup>. A shadow register is read-only to the RA and is synchronized with the corresponding physical register for the RFU operation through the register renaming logic. The single result is written back to the host register file like normal instructions. Due to register renaming, extra read/write ports must be added to the host register file to communicate with the RA, which implies drastic increase in power and area of the host register file. However, cost is a secondary concern in the design of Chimaera.

#### 2.1.5 CCA

A CCA (Configurable Compute Accelerator) is used instead of the reconfigurable array in the system developed at University of Michigan [21, 20]. Unlike the fine-grained configurable RA, CCA is composed of a layered network of FUs, each capable of several fast word-level dataflow operations, i.e., logical, addition/subtraction, move or shift (see Figure 2.4(a)). The function of each FU and their connectivity

<sup>&</sup>lt;sup>1</sup>In a out-of-order core, usually there are more physical registers than logical registers to solve false dependencies through register renaming.

can be specified by only a few bits, while hundreds are needed in an LUT based RA. Coarser logic granularity guarantees faster reconfiguration time. In fact, the whole CCA can be defined using around 200 bits, such that configuring the CCA on-the-fly with control signals rather than writing to the associated SRAM is made possible<sup>2</sup>. The trade-off here is that the CCA is unable to exploit bit/sub-word level optimizations, and only the subgraphs, which are able to fit in the fixed CCA topology, can be used.

In the first CCA system, the CCA configuration is conventionally encoded in the instruction stream [21]. Under the assumption of a Pentium P6 microarchitecture, where a  $\mu$ op takes 118 bits, each custom instruction can be encoded with 2 consecutive  $\mu$ ops. However, it easily takes 6, 7 consecutive instructions in a normal 32-bit format, which carries large overhead. The problem of lengthy encoding is tackled in the second CCA system [20], where the control bits for a particular CCA function is generated during program execution. Here, the original group of instructions is not directly replaced by a custom instruction, but wrapped up in a small function that remains in the code space. In particular, it is replace by a modified brl (branch and link instruction for function calls) instruction jumping to the small function. The br1 instruction indicates a custom function. The architecture of this CCA system is depicted in Figure 2.4(b). During the first encounter of a custom function, the brl instruction is executed as a normal function call. The control generator records the corresponding group of instructions and generates the control bits for the custom function. It also marks live-in registers as input registers for the custom function. The control bits are later sent to an entry in the config cache, while the index of the config cache entry and input registers are encoded in the Branch Target Buffer (BTB) entry corresponding to the brl instruction. Upon later encounters of the brl instruction, the additional encoded information is retrieved from its BTB entry

<sup>&</sup>lt;sup>2</sup>For fine-grained RA, it is impractical to generate the control signals simultaneously for the large number of configuration points. Writing to the SRAM, a.k.a., reconfiguration, is needed to accumulate the control signals.

Figure 2.5: The PEAS environment (adapted from [71, 46]). (a) Main functions of the system, (b) Micro-operation description of the ADDU instruction.

during instruction decoding, according to which the CCA is configured and used in the execution stage.

#### 2.1.6 PEAS