## SCHOTTKY SOURCE/DRAIN TRANSISTOR INTEGRATED WITH HIGH-K AND METAL GATE FOR SUB-TENTH NM TECHNOLOGY

LI RUI

NATIONAL UNIVERSITY OF SINGAPORE

2008

### SCHOTTKY SOURCE/DRAIN TRANSISTOR INTEGRATED WITH HIGH-K AND METAL GATE FOR SUB-TENTH NM TECHNOLOGY

### LI RUI

(B. Sc., Univ. of Science and Technology of China, CHINA)

### A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2008

## ACKNOWLEDGMENTS

I wish to express my sincere appreciation to my supervisors Dr. Sung-Joo Lee (Department of Electrical and Computer Engineering) and Dr. Dong-Zhi Chi (Institute of Materials Research and Engineering) for their continuous encouragement, advice and support throughout this research project.

I would like to thank Dr. Shiyang Zhu from the Institute of Microelectronics for his helpful advice and guidance during the first year of my PhD study. My gratitude also goes to Dr. Minghui Hong and Dr. Wendong Song from the Laser Microprocessing Lab for their great help on laser annealing.

I gratefully acknowledge all of my lab fellows for their help on research, learning, and many other aspects during the past a few years: Fei Gao, Sung Jin Whang, Nan Wu, Qingchun Zhang, Xiongfei Yu, Chi Ren, Moon Sig Joo, Jinghao Chen, Sung Jung Kim, Yingqian Wang, Chen Shen, Jingde Chen, Xinpeng Wang, Yan Song, Rinus Tek-Po Lee, Kian Ming Tan, Wan Sik Hwang, Andy Eu-Jin Lim, Zerlinda Tan, Chia Ching Yeo, Debora Poon, Samanta Santanu Kumar, Eric Yeow-Hwee Teo, Jia Fu, Wei He, Hui Zang, Gang Zhang, Yi Tong, Jing Pu, Hoon-Jung Oh, Yu Fu Yong, Patrick Tang, Wai Linn O-Yan, Boon Tech Lau and many others from the Silicon Nano Device Lab; In particular, I wish to express my sincere thanks to Fei Gao, Sung Jin Whang, Rinus Tek-Po Lee, Kian Ming Tan, Wan Sik Hwang, Chen Shen, for their innumerable helpful discussion and constructive suggestions on device fabrications, characterizations as well as data analyses in this project. The financial support from the National University of Singapore is also gratefully acknowledged.

My special recognition goes to Jidong Huang for his help. He has always been with me during the most difficult moments in this journey.

Finally, I would like to thank my parents for their love, constant support and encouragement in all of my life.

# CONTENTS

| ACKNOWLEDGMENTS                                                              | I    |

|------------------------------------------------------------------------------|------|

| CONTENTS                                                                     |      |

| SUMMARY                                                                      | V    |

| List of Figures and Tables                                                   | VII  |

| List of Symbols and Abbreviations                                            |      |

| Chapter 1                                                                    |      |

| Introduction                                                                 |      |

| 1.1 Introduction to MOSFET                                                   |      |

| 1.2 High-k gate dielectrics and metal gate                                   |      |

| 1.3 High mobility channel materials                                          |      |

| 1.4 Schottky barrier source/drain MOSFET                                     | 10   |

| 1.4.1 Motivation                                                             |      |

| 1.4.2 Operation principles                                                   |      |

| 1.4.3 Literature review                                                      |      |

| 1.5 Thesis organization                                                      |      |

| References                                                                   |      |

| Chapter 2                                                                    |      |

| Device fabrication and characterization                                      |      |

| 2.1 Device fabrication process                                               | 30   |

| 2.1.1 Fabrication process for metal-germanide Schottky source/drain Ge       |      |

| MOSFETs integrated with TaN/Hf $O_2$ gate stack                              | 30   |

| 2.1.2 Fabrication process for metal germanide/Ge Schottky diodes             |      |

| 2.2 Device characterization                                                  |      |

| 2.2.1 Chemical and physical properties                                       |      |

| 2.2.2 Electrical properties                                                  |      |

| References:                                                                  |      |

| Chapter 3                                                                    |      |

| Metal germanide Schottky source/drain Ge channel p-MOSFETs integrated with   |      |

| TaN/HfO <sub>2</sub> gate stack                                              | 58   |

| 3.1 Ni- and Pt-germanides investigation for Ge channel p-SSDT application    |      |

| 3.1.1 Experiment introduction                                                |      |

| 3.1.2 Results and discussion                                                 |      |

| 3.2 Metal germanide Schottky source/drain Ge pMOSFETs integrated with        |      |

| TaN/HfO <sub>2</sub> gate stack                                              | 67   |

| 3.2.1 Experiment introduction                                                | 67   |

| 3.3 Process integration issues in Schottky source/drain Ge p-MOSFETs integra | ted  |

| with TaN/HfO <sub>2</sub> gate stack                                         |      |

| 3.2.1 Simulation of NiGe Schottky source/drain Ge p-MOSFET with diffe        | rent |

| spacer thickness                                                             |      |

| 3.2.2 A robust, self-aligned Pt germanide process                            |      |

| 3.4 Conclusion                                                               |      |

| References:                                                                        | 83     |

|------------------------------------------------------------------------------------|--------|

| Chapter 4                                                                          | 87     |

| Metal germanides with low electron barrier height for Ge n-MOSFET application      | 87     |

| 4.1 REM metal (Er, Yb) germanide/p-Ge (100) contacts and Er- germanide Scl         | nottky |

| S/D Ge n-MOSFETs                                                                   |        |

| 4.1.1 Introduction                                                                 | 88     |

| 4.1.2 Experiment                                                                   | 88     |

| 4.1.3 Results and discussion                                                       |        |

| 4.1.4 Conclusion                                                                   | 95     |

| 4.2 Ni-Ge barrier height modulation by Sb segregation                              | 96     |

| 4.2.1 Introduction                                                                 |        |

| 4.2.2 Experiment                                                                   | 97     |

| 4.2.3 Result and discussion                                                        | 98     |

| 4.2.4 Conclusion                                                                   | 105    |

| References:                                                                        | 106    |

| Chapter 5                                                                          |        |

| Laser application in metal germanide formation as an alternative annealing method. | 109    |

| 5.1 Introduction                                                                   | 109    |

| 5.2 Experiment                                                                     | 110    |

| 5.2.1 Laser annealed Pt-germanide/n-type Ge (100) Schottky contacts                | 110    |

| 5.2.2 Laser annealed Pt-germanide Schottky source/drain Ge p-MOSFET                |        |

| integrated with TaN/HfO <sub>2</sub> gate stack                                    | 110    |

| 5.3 Results and discussion                                                         | 112    |

| 5.3.1 Electrical and material characterization of laser annealed Pt-germani        | de/n-  |

| type Ge (100) Schottky contacts                                                    | 112    |

| 5.3.2 Electrical characterization of laser annealed Pt-germanide Schottky          | S/D    |

| Ge p-MOSFET                                                                        | 119    |

| 5.4 Conclusion                                                                     | 122    |

| References:                                                                        | 123    |

| Chapter 6                                                                          | 125    |

| Conclusion                                                                         | 125    |

| 6.1 Conclusion                                                                     | 125    |

| 6.2 Suggestions for future work                                                    | 128    |

| References:                                                                        |        |

| Appendix I: List of Publications                                                   | 131    |

## SUMMARY

As complementary metal-oxide semiconductor (CMOS) transistors scale beyond 45 nm technology node, several key innovations become more and more attractive in different aspects, including: high-k gate dielectric and metal gate to provide the possibility that equivalent oxide thickness scales to less than 1 nm, high mobility channel materials for increment of carrier saturation velocity, and Schottky barrier source/drain structure for shallow and sharp junction with low resistance. This project explores the feasibility of integration of germanide Schottky source/drain Ge channel MOSFET with high-k gate dielectric and metal gate for sub-tenth nm technology application.

The comprehensive knowledge on metal germanide properties is essential for the successful replacement of doped source/drain with metal germanide Schottky source/drain. Therefore systematic studies on Ni- and Pt- germanide for Ge p-MOSFET application have been carried out. Both the germanides offer promising merits: low effective hole barrier height, morphological stability, low resistance and abrupt junction with germanium. Ge p-MOSFETs with Ni- or Pt- germanide Schottky source/drain are also successfully fabricated on n-Ge-substrate with chemical vapor deposition (CVD)-HfO<sub>2</sub>/TaN gate stack. Improved junction forward and reverse current were obtained from Ni- and Pt- germanide source/drain junction compared to conventional B-doped  $p^+/n$  junction. In addition, the higher drive-on current and lower drive-off current were also obtained from Pt-germanide MOS field effect transistor (MOSFET) than conventional Ge-pMOSFET.

Exploration of metal germanide for Ge n-MOSFET application has been focused in two material groups: i) rare earth metal germanide, such as Er- and Yb- germanide, which has a low metal work function, and ii) NiGe with modified electron barrier height. By introducing an interfacial Sb layer, NiGe was found to show low resistivity and low electron barrier height simultaneously, which make NiGe with such modification a good ohmic contact material to  $n^+$  source/drain regions as well as a promising Schottky source/drain candidate for Ge n-MOSFETs.

Laser annealing was introduced as an alternative germanide source/drain formation technique to conventional rapid thermal annealing, providing the advantages of local selective heating of specific regions and reduced thermal budget. A smooth and uniform Pt-germanide film has been obtained through laser annealing, with effective hole barrier height as low as 0.12~0.14 eV. A Ge p-MOSFET with Pt-germanide Schottky source/drain formed by laser annealing was successfully demonstrated with well-behaved output and transfer characteristics.

# List of Figures and Tables

| Figure 1.1<br>Figure 1.2 | Technology and transistor feature size and transistor cost versus year (after [1.2]). Schematic illustration of a complementary MOSFET (CMOSFET).                                                                                                                                                                                | 2<br>3 |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 1.3               | Schematics of a CMOS inverter where $V_{dd}$ and $V_s$ serve as the source and drain                                                                                                                                                                                                                                             | 4      |

| Figure 1.4               | voltages, respectively.<br>Sketch of a typical MOSFET structure on a bulk (B) substrate, in which L and W represent the channel length and width, respectively. When the channel is inverted with a voltage applied on the gate (G), carriers can flow from the source (S) to drain (D) forming the drive current of the MOSFET. | 5      |

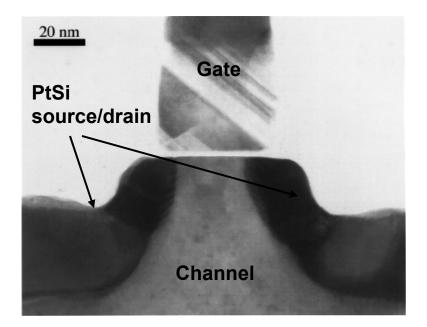

| Figure 1.5               | XTEM of a PtSi source/drain device with 27 nm channel length, 19 Å gate oxide, and $n^+$ poly gate (after [1.31]).                                                                                                                                                                                                               | 13     |

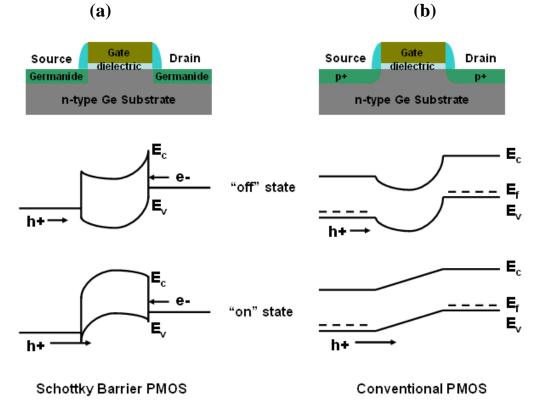

| Figure 1.6               | Band diagrams of (a) Schottky barrier PMOS device and (b) conventional impurity-doped source/drain MOS device.                                                                                                                                                                                                                   | 14     |

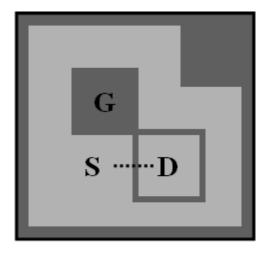

| Figure 2.1               | A sketch of single mask ring-shaped MOSFET where G, S and D presenting gate, source and drain regions, respectively.                                                                                                                                                                                                             | 31     |

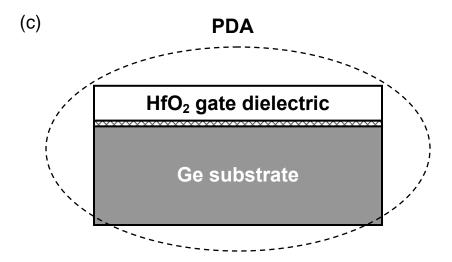

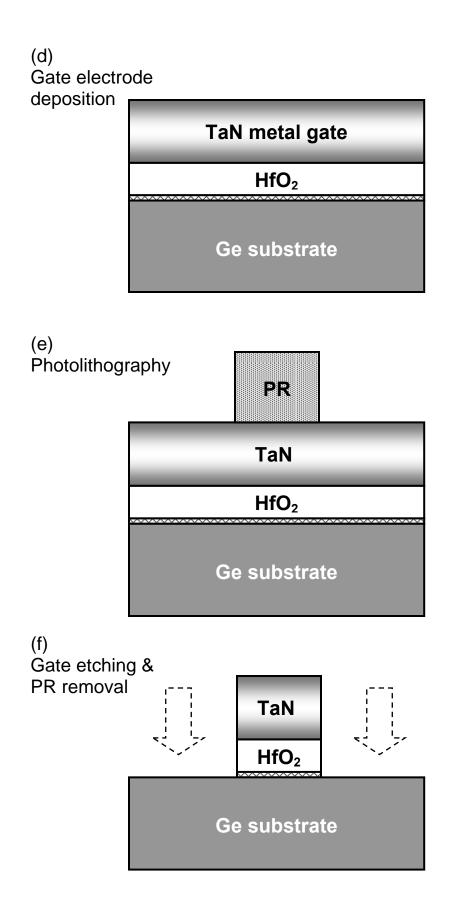

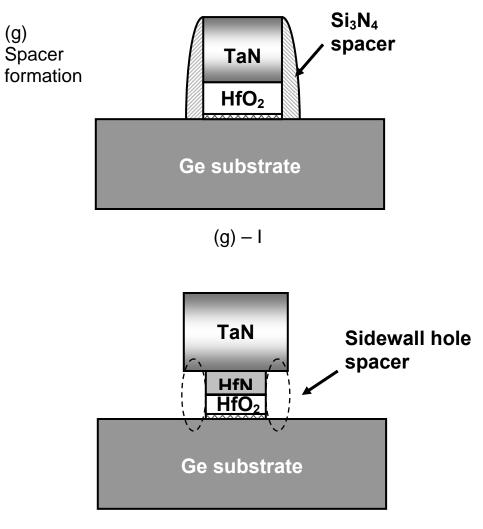

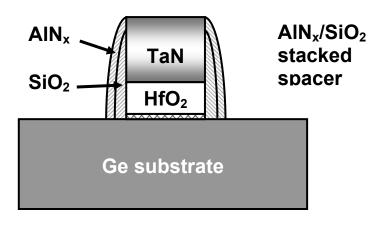

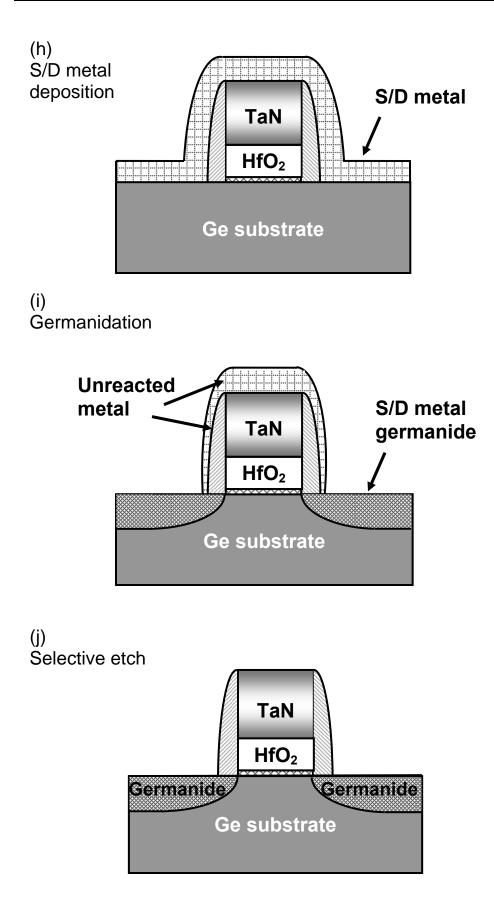

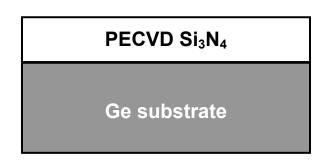

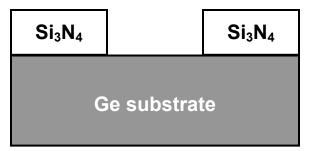

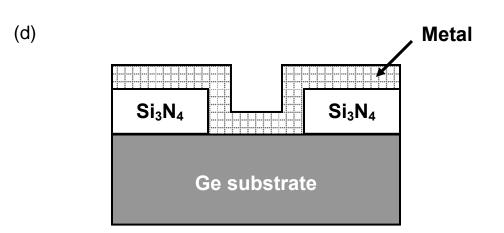

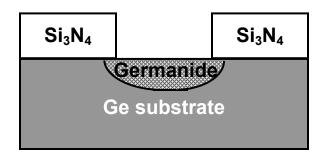

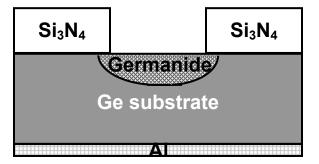

| Figure 2.2               | A typical fabrication process flow of a Schottky source/drain MOSFET in this project.                                                                                                                                                                                                                                            | 41     |

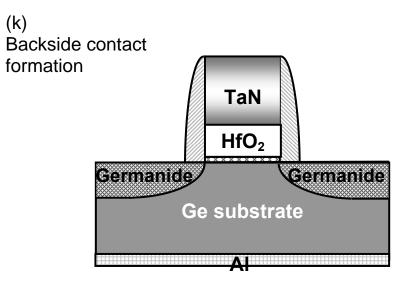

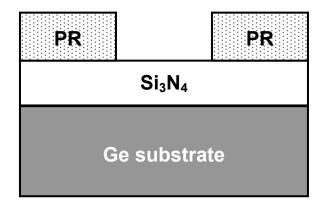

| Figure 2.3               | A typical fabrication process flow of a metal germanide/Ge Schottky diode in this project.                                                                                                                                                                                                                                       | 44     |

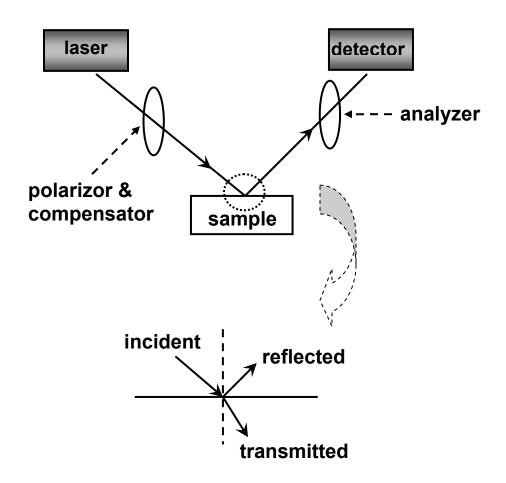

| Figure 2.4               | A schematic sketch of spectroscopic ellipsometer.                                                                                                                                                                                                                                                                                | 45     |

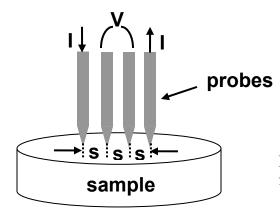

| Figure 2.5               | A typical collinear four-point probe set up.                                                                                                                                                                                                                                                                                     | 47     |

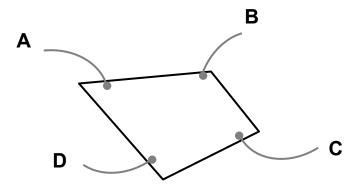

| Figure 2.6               | Sample of irregular shape with four contacts at arbitrary places along the circumference.                                                                                                                                                                                                                                        | 48     |

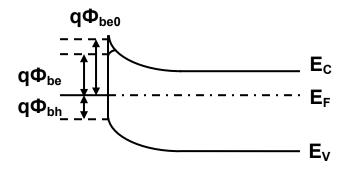

| Figure 2.7               | Schottky barrier energy band diagram on an n-type substrate.                                                                                                                                                                                                                                                                     | 49     |

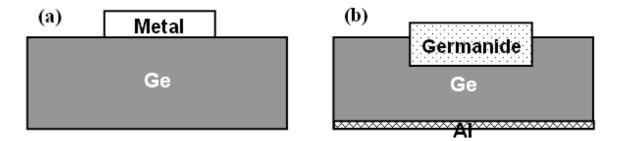

| Figure 3.1               | Schottky contact structure cross section view (a) as metal deposited (b) after RTA and germanide formation, and (c) top view of contacts.                                                                                                                                                                                        | 60     |

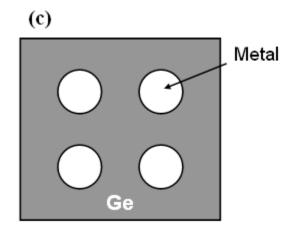

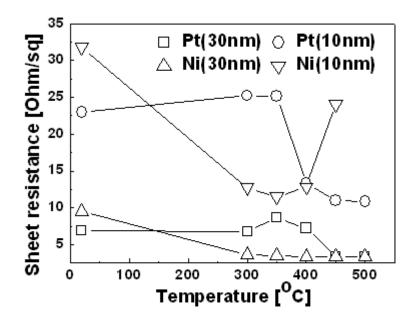

| Figure 3.2               | XRD results of Ni- and Pt-germanides formed from (a) 30 nm Ni, (b) 10 nm Ni, (c) 30 nm Pt, and (d) 10 nm Pt on Ge and annealed at 300~500°C for one minute.                                                                                                                                                                      | 61     |

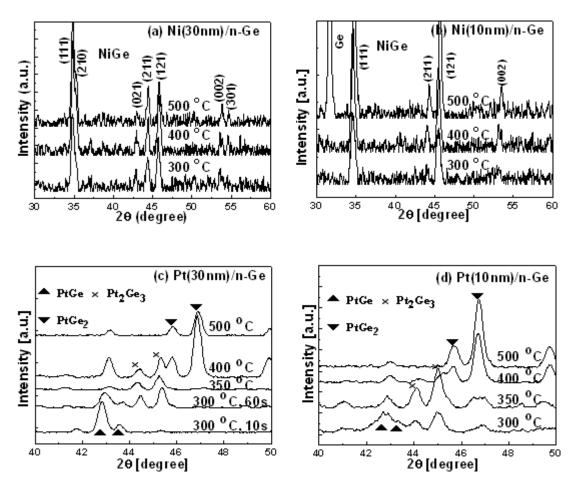

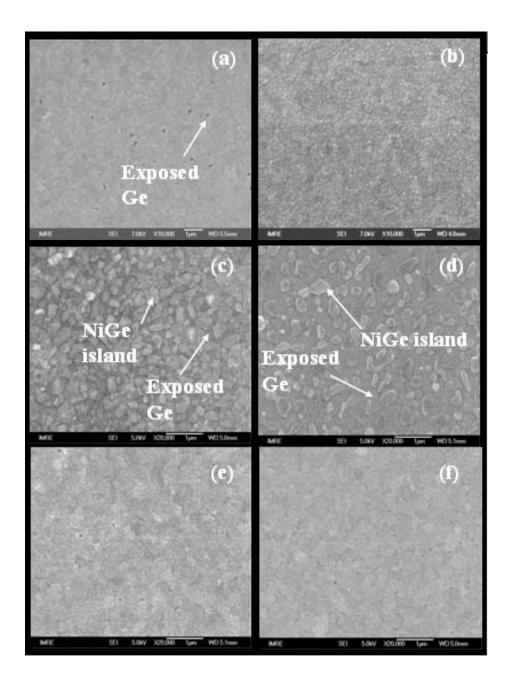

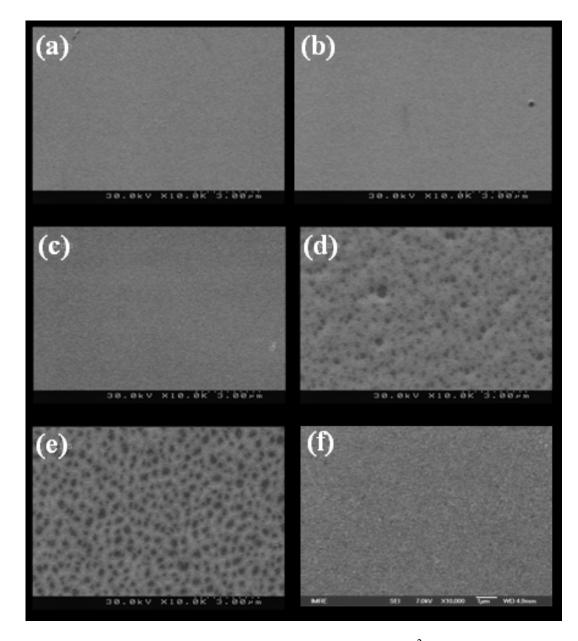

| Figure 3.3               | SEM images of Ni- and Pt-germanides formed by (a) 30 nm Ni at 500°C, (b) 30 nm Pt at 500°C, (c) 10 nm Ni at 450°C, (d) 10 nm Ni at 500°C, (e) 10 nm Pt at 450°C and (f) 10 nm Pt at 500°C.                                                                                                                                       | 62     |

| Figure 3.4               | Sheet resistance of Ni- and Pt-germanides formed from 10 and 30 nm Ni and Pt at 300~500°C, respectively.                                                                                                                                                                                                                         | 63     |

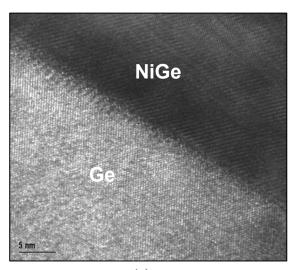

| Figure 3.5               | HRTEM pictures of (a) NiGe and (b) PtGe <sub>2</sub> formed at 400°C.                                                                                                                                                                                                                                                            | 64     |

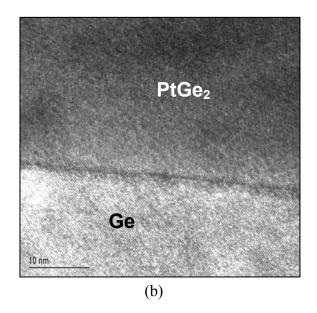

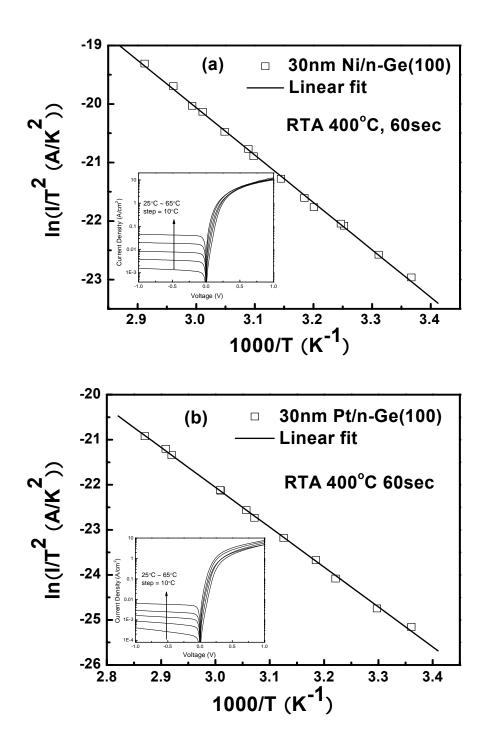

| Figure 3.6               | Richardson plots of forward current of (a) NiGe/n-Ge (100) and (b) PtGe <sub>2</sub> /n-Ge (100) contacts with inset temperature dependent $I - V$ curves.                                                                                                                                                                       | 65     |

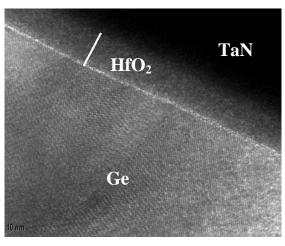

| Figure 3.7               | HRTEM image of the TaN/HfO <sub>2</sub> /n-Ge (100) gate stack of a fully processed Schottky source/drain Ge p-MOSFET.                                                                                                                                                                                                           | 68     |

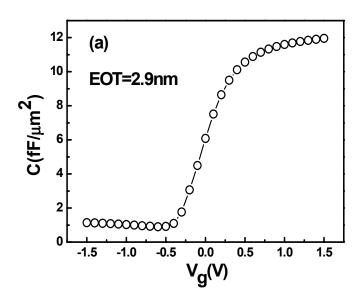

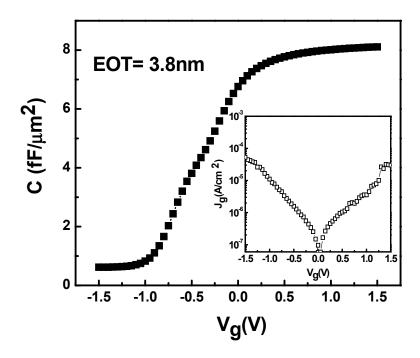

| Figure 3.8               | (a) capacitance-voltage and (b) current-voltage characteristics of TaN/HfO <sub>2</sub> /n-Ge (100) gate stack.                                                                                                                                                                                                                  | 69     |

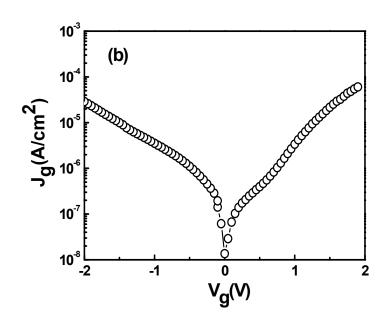

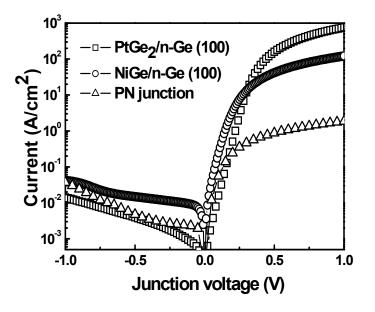

| Figure 3.9               | Forward and reverse current at junctions of Ni- & Pt-germanide source/drain and B-doped $p^+/n$ junction.                                                                                                                                                                                                                        | 69     |

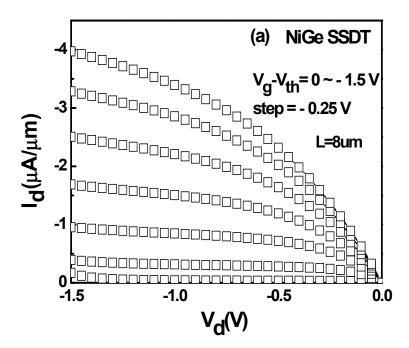

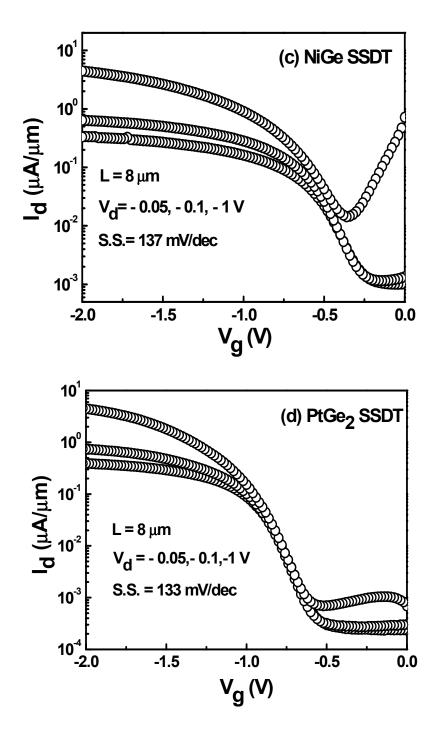

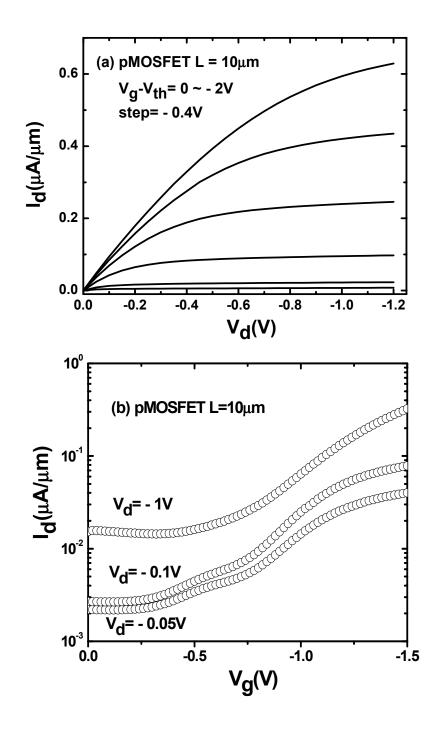

| Figure 3.10              | Output characteristics of (a) NiGe and (b) PtGe <sub>2</sub> Schottky source/drain Ge p-MOSFETs; and transfer characteristics of (c) NiGe and (d) PtGe <sub>2</sub> Schottky source/drain Ge p-MOSFETs.                                                                                                                          | 73     |

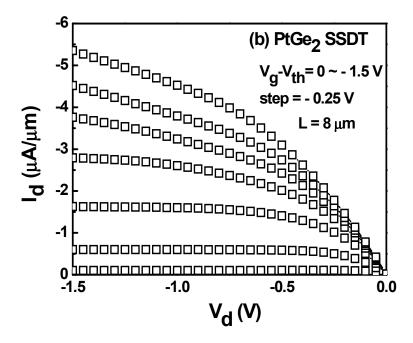

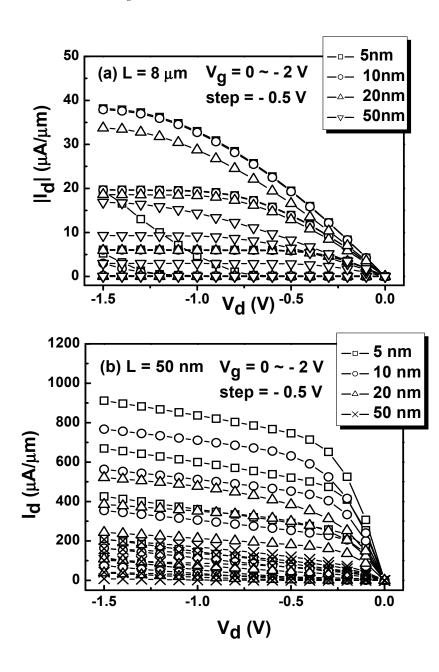

| Figure 3.11              | Simulated output characteristics ( $I_d - V_d$ ) of NiGe Schottky p-MOSFETs with                                                                                                                                                                                                                                                 | 75     |

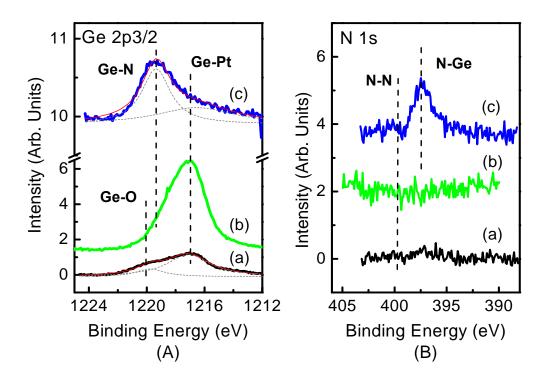

| Figure 3.12              | gate length of (a) 8 $\mu$ m and (b) 50 nm for different spacer thickness.<br>XPS data of (A) Ge 2p3/2 and (B) N 1s spectra for Pt/Ge substrate with RTA at                                                                                                                                                                      | 77     |

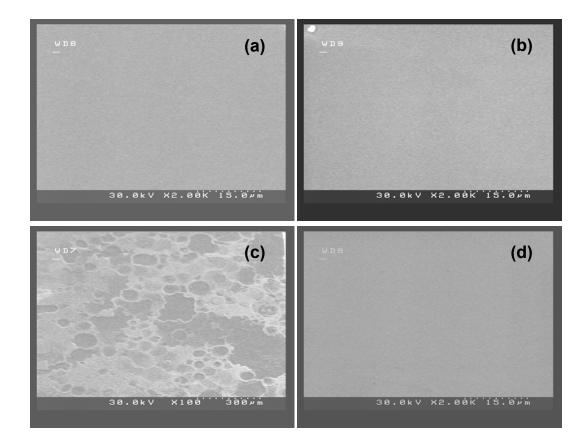

| Figure 3.13 | 400°C for 1 minute [curve (a)], and the substrate with RTA and nitridation without [curve (b)] or with [curve (c)] substrate bias.<br>Figure 3.13 Surface morphology (by SEM) of Pt/Ge substrates with RTA and (a) one min nitridation without bias, (b) one min nitridation with bias, (c) one min nitridation without bias and wet etch for one min, and (d) one min nitridation with bias and wet etch for 5 minutes. | 80  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

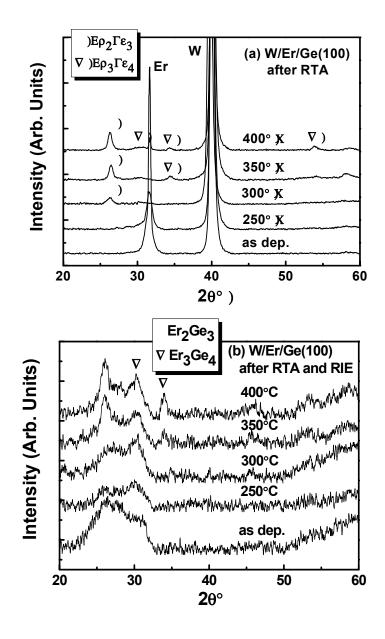

| Figure 4.1  | XRD results of (a) Er germanide formed by 50nm W/30 nm Er/p-Ge (100) after RTA at 300°C, 400°C and 500°C, respectively, and (b) Er germanide in (a) after W removal by RIE.                                                                                                                                                                                                                                              | 91  |

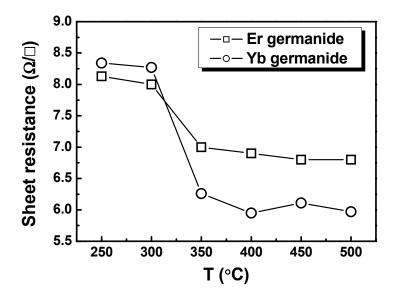

| Figure 4.2  | Sheet resistance of 30 nm Er/p-Ge (100) after annealing at temperature from 250°C to 500°C.                                                                                                                                                                                                                                                                                                                              | 92  |

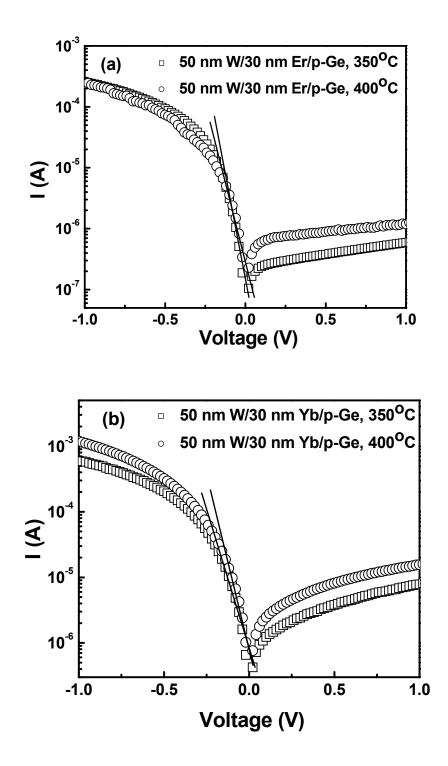

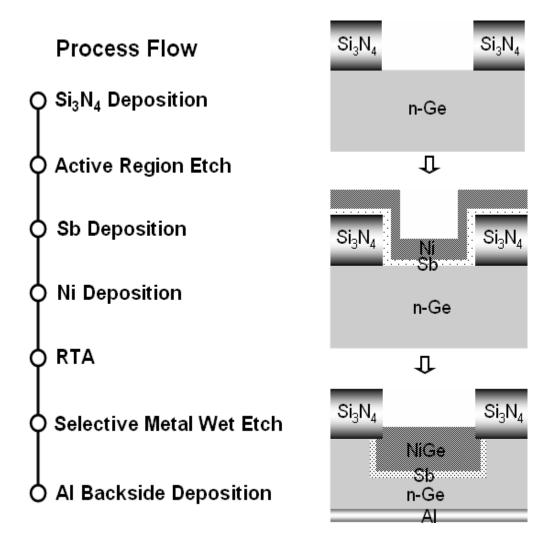

| Figure 4.3  | Current-voltage ( $I - V$ ) characteristics at room temperature for (a) 50 nm W/ 30 nm Er/p-Ge (100) and (b) 50 nm W/ 30 nm Yb/p-Ge (100) contacts after anneal at 350°C and 400°C, respectively.                                                                                                                                                                                                                        | 93  |

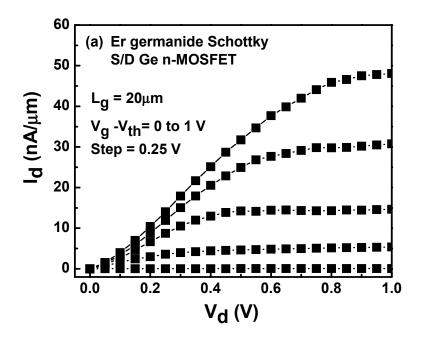

| Figure 4.4  | (a) output characteristics and (b) transfer characteristics of Er germanide Schottky source/drain Ge n-MOSFET.                                                                                                                                                                                                                                                                                                           | 95  |

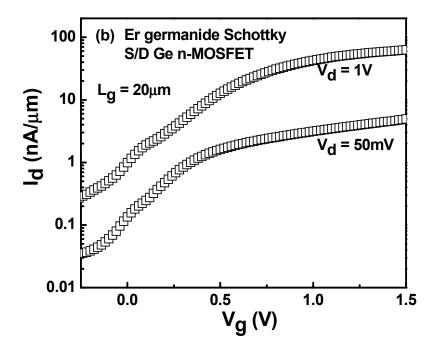

| Figure 4.5  | Process flow for fabricating low Schottky barrier height diodes using Sb segregation and device final structure after fabrication.                                                                                                                                                                                                                                                                                       | 99  |

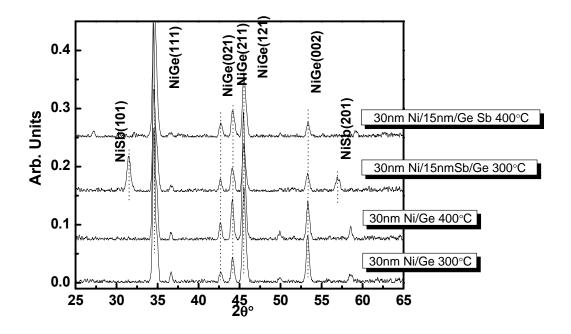

| Figure 4.6  | XRD profiles of 30 nm Ni/n-Ge (100) and 30 nm Ni/15 nm Sb/n-Ge (100) after RTA at 300°C and 400°C, respectively.                                                                                                                                                                                                                                                                                                         | 100 |

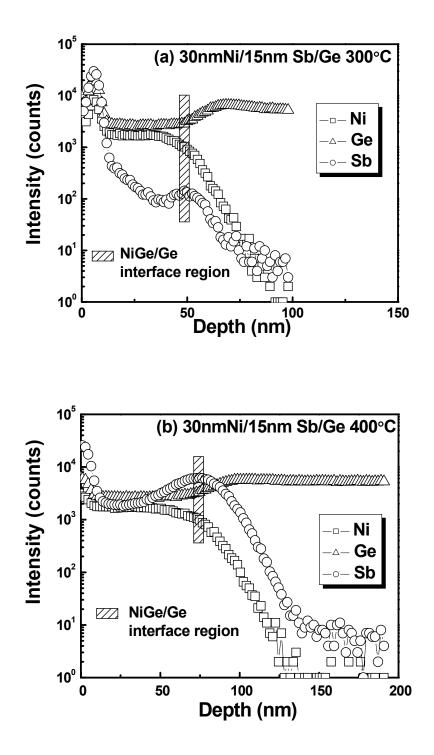

| Figure 4.7  | SIMS depth profile of Ni, Ge and Sb for the device with 30 nm Ni and 15 nm Sb interlayer annealed at (a) 300°C and (b) 400°C, respectively.                                                                                                                                                                                                                                                                              | 102 |

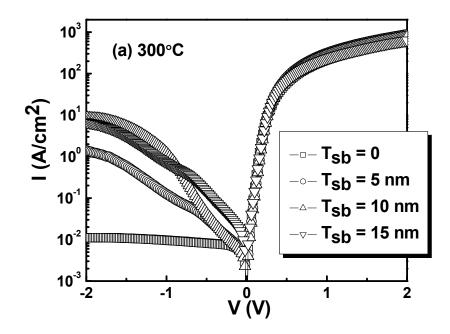

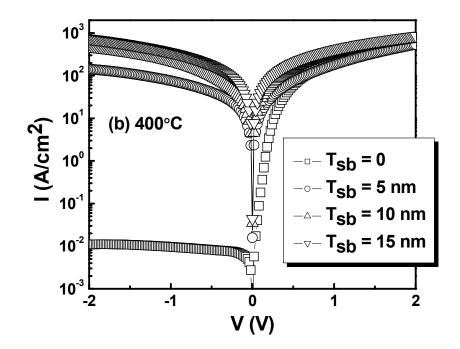

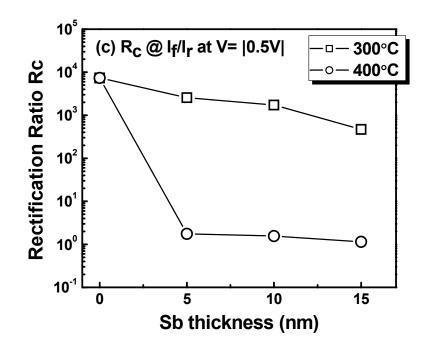

| Figure 4.8  | Current-voltage $(I - V)$ characteristics at room temperature for NiGe/n-Ge (100) diodes with and without Sb interlayer annealed at (a) 300°C and (b) 400°C,                                                                                                                                                                                                                                                             | 104 |

|             | respectively, and (c) rectification ratio $R_c (I_f / I_r)$ as a function of Sb interlayer                                                                                                                                                                                                                                                                                                                               |     |

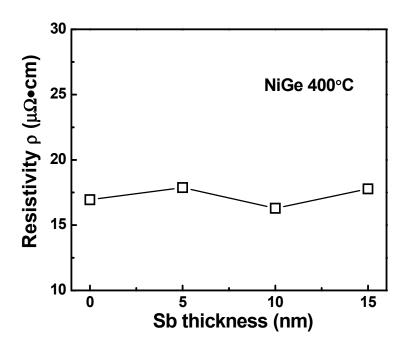

| Figure 4.9  | thickness ( $T_{sb}$ ).<br>Electrical resistivity of Ni/n-Ge (100) as a function of Sb interlayer thickness after annealing at 400°C.                                                                                                                                                                                                                                                                                    | 105 |

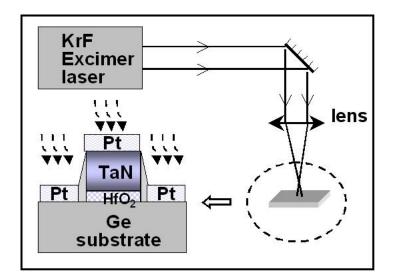

| Figure 5.1  | A schematic sketch of the laser annealing experimental setup and transistor structure.                                                                                                                                                                                                                                                                                                                                   | 112 |

| Figure 5.2  | SEM images of Pt/Ge by laser annealing at (a) $0.10 \text{ J/cm}^2$ for 1pulse, (b) $0.18 \text{ J/cm}^2$ for 1pulse, (c) $0.18 \text{ J/cm}^2$ for 10 pulses, (d) $0.20 \text{ J/cm}^2$ for 1pulse, (e) $0.22 \text{ J/cm}^2$ for 1pulse and by RTA at (f) 400°C.                                                                                                                                                       | 114 |

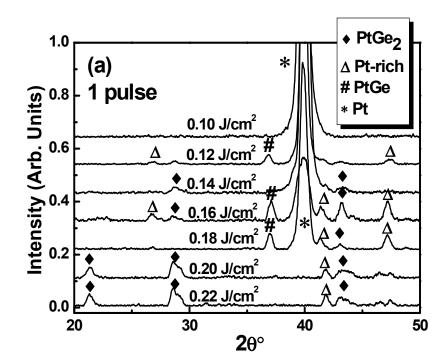

| Figure 5.3  | XRD results of Pt germanide formed by laser annealing at a laser fluence of (a) $0.10 \sim 0.22$ J/cm <sup>2</sup> for 1 pulse, (b) $0.10 \sim 0.18$ J/cm <sup>2</sup> for 10 pulses, and (c) $0.12$ J/cm <sup>2</sup> for 10 pulses, $0.14$ J/cm <sup>2</sup> for 10 pulses, $0.16$ J/cm <sup>2</sup> for 5 pulses and $0.20$ J/cm <sup>2</sup> for 1 pulse, respectively.                                              | 116 |

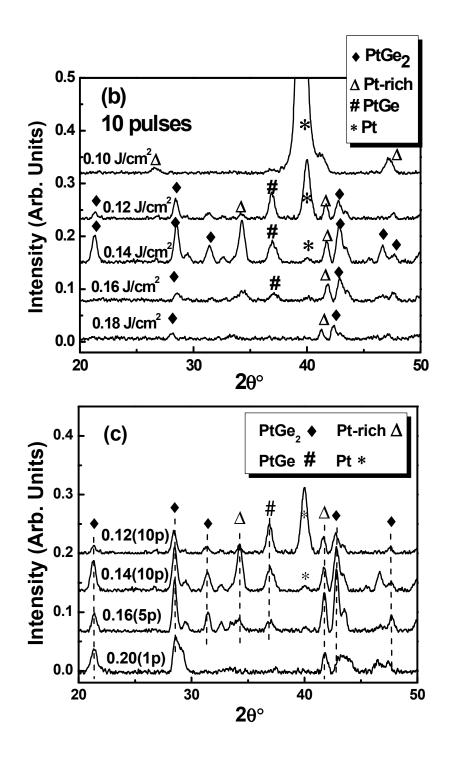

| Figure 5.4  | (a) TEM and (b) high resolution TEM pictures of Pt germanide formed by laser annealing at $0.14 \text{ J/cm}^2$ for 5 pulses.                                                                                                                                                                                                                                                                                            | 117 |

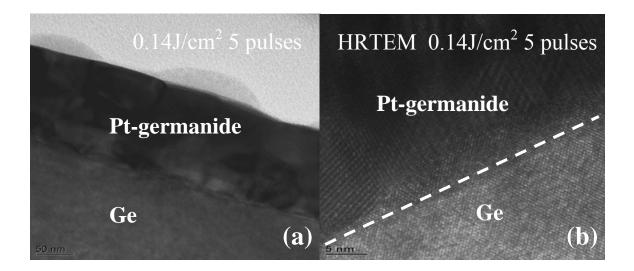

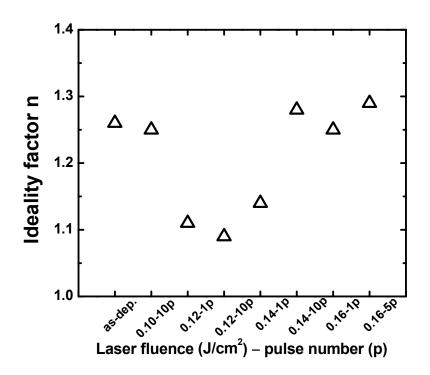

| Figure 5.5  | Ideality factor $n$ value of Pt germanide/ n-type Ge (100) contacts annealed at laser fluence from 0.10 to 0.16 J/cm <sup>2</sup> with different pulse number, as well as as-<br>deposited Pt/n-type Ge (100) contact.                                                                                                                                                                                                   | 119 |

| Figure 5.6  | Capacitance-voltage ( $C-V$ ) and current-voltage ( $I-V$ ) characteristics of TaN/HfO <sub>2</sub> /Ge gate stack of Ge p-MOSFET with laser annealing Pt germanide Schottky source/drain.                                                                                                                                                                                                                               | 121 |

| Figure 5.7  | Output (a) and transfer (b) characteristics of Ge p-MOSFET with laser annealing Pt germanide Schottky source/drain.                                                                                                                                                                                                                                                                                                      | 122 |

| Table 1.1 | Near-term high-performance logic technology requirements in ITRS 2005 [1.7]  | 8 |

|-----------|------------------------------------------------------------------------------|---|

| Table 1.2 | Properties of common semiconductor materials (Si, Ge, GaAs, InAs, and InSb). | 9 |

$\mu_{electron}$  and  $\mu_{hole}$  represent electron mobility and hole mobility respectively.

- Table 1.3

Introduction of roadmap challenges addressed by Schottky barrier MOSFET 11 (SBMOS). Most of the categories have multiple line items in the detailed roadmap tables. The box color for a given year and category above reflects the worst case, considering all of the roadmap line items within each category. (red) = manufacturable solution not known; (yellow) = manufacturable solutions are known; = manufacturable solutions exist and being optimized (after [1.24]).

- Table 1.4Table 1.4 Summary of sub-250-nm-gate length Schottky barrier NMOS and<br/>PMOS literature. The column labeled "Technology" has a comma-separated list<br/>for each row with the format "Type, device structure, source/drain silicide type,<br/>source/drain engineering type". (N=NMOS, P=PMOS; B= bulk, S= SOI, F=<br/>FinFET; 1= standard, 2= interfacial layer) [1.23].

- Table 1.5 Table 1.5 Summary of barrier heights of various metal germanide/Ge contacts and 20 pure metal/Ge contacts in the literature.  $\phi_m$  is the metal work function,  $\phi_{be}$  is barrier height for electron,  $\phi_{bh}$  is barrier height for hole, and S is slope parameter.

- Table 2.1 A comparison between Schottky barrier height measurements by I V and 52 I T methods.

- Table 3.1

Summary of Rs values for samples with different treatments before and after

81

diluted aqua regia etching.

81

- Table 4.1 Ideality factor (*n*),  $\phi_{bh}$  and  $\phi_{be}$  for Er-Ge/p-Ge (100) and Yb-Ge/p-Ge (100) 94 contacts after RTA at 350°C and 400°C, respectively.

- Table 5.1Calculated effective electron barrier height of Pt germanide/n-type Ge (100)118contacts annealed at different laser fluence and pulse numbers.

# List of Symbols and Abbreviations

| A                              | Area of the capacitor                                           |

|--------------------------------|-----------------------------------------------------------------|

| $A^{*}$                        | Richardson's constant                                           |

| Å                              | Angstrom                                                        |

| CET                            | capacitive equivalent thickness                                 |

| CMOS                           | Complementary metal-oxide-semiconductor                         |

| C <sub>inv</sub>               | Gate to channel capacitance under inversion per unit area       |

| DHF                            | Diluted HF solution                                             |

| $D_s$                          | Density of interface states                                     |

| $\sigma$                       | Thickness of interfacial layer                                  |

| $\boldsymbol{\mathcal{E}}_{0}$ | Permittivity of the vacuum ( $8.85 \times 10^{-3} fF / \mu m$ ) |

| $E_{C}$                        | Conduction band edge of semiconductor                           |

| $E_{_V}$                       | Valence band edge of semiconductor                              |

| $E_{F}$                        | Fermi level of semiconductor                                    |

| EOT                            | Equivalent oxide thickness                                      |

| ER                             | Etching rate                                                    |

| $\phi_{b}$                     | Barrier height of the metal/Ge contacts                         |

| $\phi_{_m}$                    | metal work function                                             |

| $\pmb{\phi}_{bh}$              | Hole barrier height from metal to semiconductor                 |

| $\pmb{\phi}_{be}$              | Electron barrier height from metal to semiconductor             |

| HRTEM                          | High resolution TEM                                             |

| IC                             | Integrated circuit                                              |

| ICP                            | Inductively coupled plasma                                      |

| ITRS                           | International Technology Roadmap for Semiconductors             |

| Ι                              | Current                                                         |

| $I_d^n$                        | Drive current of nMOSFETs                                       |

| $I_d^p$                        | Drive current of pMOSFETs                                       |

| $I_d$                               | Drive current of MOSFETs                                  |

|-------------------------------------|-----------------------------------------------------------|

| $I_{d,sat}$                         | MOSFET saturation current                                 |

| $I_{f}$                             | Diode forward current                                     |

| $I_{o\!f\!f}$                       | MOSFET off-state current                                  |

| $I_{on}$                            | MOSFET on-state current                                   |

| $I_s$                               | Diode saturation current                                  |

| $I_r$                               | Diode reverse current                                     |

| Κ                                   | Boltzmann constant                                        |

| k                                   | Relative permittivity (dielectric constant) of dielectric |

| $k_{{\scriptscriptstyle high-k}}$   | Relative permittivity of the high-k gate dielectric       |

| L                                   | Length of transistor channel                              |

| LPCVD                               | Low-pressure chemical vapor deposition                    |

| MIGS                                | Metal-induced gap states                                  |

| MOSFET                              | Metal-oxide-semiconductor field effect transistor         |

| MOCVD                               | Metal-organic chemical vapor deposition                   |

| n                                   | Ideality factor                                           |

| μ                                   | Channel carrier mobility                                  |

| $\mu_{\scriptscriptstyle electron}$ | Mobility of electron                                      |

| $\mu_{\scriptscriptstyle hole}$     | Mobility of hole                                          |

| ρ                                   | Resistivity of material                                   |

| PC                                  | Photocurrent                                              |

| PDA                                 | Post deposition anneal                                    |

| PECVD                               | Plasma Enhanced Chemical Vapor Deposition                 |

| PR                                  | Photo-resist                                              |

| PVD                                 | Physical vapor deposition                                 |

| q                                   | Electronic charge                                         |

| QMCV                                | Quantum-Mechanical CV simulator                           |

| $R_s$                               | Sheet resistance,                                         |

| REM                                 | rear earth metal                                          |

| RIE                                 | Reactive Ion Etch                                         |

| RTA                         | Rapid thermal annealing                                           |

|-----------------------------|-------------------------------------------------------------------|

| RTO                         | Rapid thermal oxidation                                           |

| RTP                         | Rapid thermal process                                             |

| S                           | Slope parameter of $\phi_b$ as function of $\phi_m$               |

| SEM                         | Scanning Electron Microscopy                                      |

| SIA                         | Semiconductor Industry Association                                |

| SIMS                        | Secondary ion mass spectrometry                                   |

| SSDT                        | Schottky Source and Drain Transistor                              |

| S/D                         | Source/drain                                                      |

| GOI                         | Ge-On-Insulator                                                   |

| Т                           | Temperature                                                       |

| TEM                         | Transmission Electron Microscopy                                  |

| $t_{high-k}$                | Physical thickness of the high-k gate dielectric                  |

| t <sub>inv</sub>            | CET of the gate dielectric                                        |

| $t_{poly}$                  | CET contribution from poly depletion effect from the poly-Si gate |

| t <sub>QM</sub>             | CET contribution from quantum mechanical effect from the channel. |

| $t_{ox}$                    | EOT of the gate dielectric                                        |

| $ar{	au}$                   | Average switching response time of the IC                         |

| V                           | Voltage                                                           |

| $V_{d}$                     | Drain voltage                                                     |

| $V_{f}$                     | Forward voltage bias to diode                                     |

| $V_{g}$                     | Voltage applied to the transistor gate                            |

| $V_{_{th}}$                 | Threshold voltage of transistor                                   |

| $V_r$                       | Reverse voltage bias to diode                                     |

| $V_{\scriptscriptstyle FB}$ | Flatband voltage                                                  |

| W                           | Width of the transistor channel                                   |

| XPS                         | X-ray photoelectron spectroscopy                                  |

| XRD                         | X-Ray Diffraction                                                 |

# Chapter 1 Introduction

As the beginning of this thesis, in this chapter I will start with a brief introduction to metal-oxide-semiconductor field effect transistor (MOSFET) and its scaling trend. The challenges associated with MOSFET scaling down will be discussed. Subsequently, to overcome the challenges, high-k gate dielectric, metal gate and Schottky source/drain structure will be introduced respectively. Finally the objectives to be achieved in this project and organization of this thesis will be given.

### **1.1 Introduction to MOSFET**

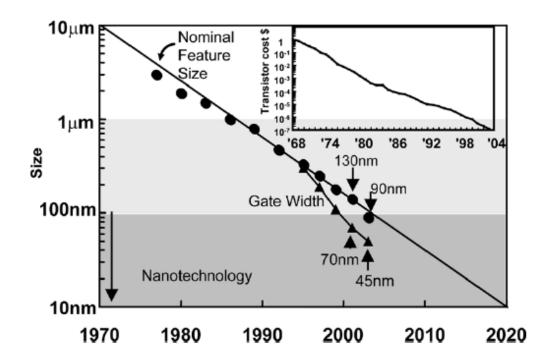

Since the invention of the integrated circuit (IC) some forty years ago, engineers and researchers around the world have been continuously working on realization of better circuit performance with a smaller chip size and lower manufacturing cost. Actually, the semiconductor industry has been very successful in providing continuous achievements on system performance improvement year after year. In 1992, the Semiconductor Industry Association (SIA) published the international technology roadmap for semiconductors (ITRS) which basically affirms the development to follow closely with Moore's law [1.1], i.e. the number of transistors per unit area on IC doubles approximately every 18 months. It was also pointed out by Moore that reduction of cost per function is the driving force behind the exponential increase in transistor density. This exponential reduction in cost per function, which driving improvement of microprocessor performance and growth of the information technology and semiconductor industry, however, leads to the shrinking of the transistor feature size approaching its fundamental limits in the traditional silicon-based IC technology today. The dramatic decrease in transistor feature size and cost per transistor during the last three decades are shown in Fig 1.1.

Figure 1.1 Technology and transistor feature size and transistor cost versus year (after [1.2]).

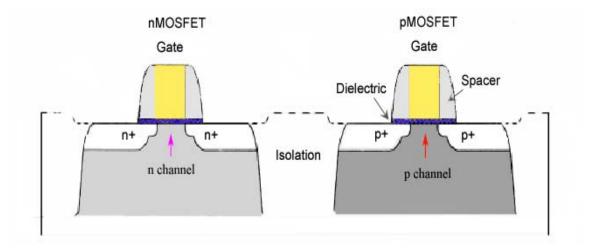

Figure 1.2 Schematic illustration of a complementary MOSFET (CMOSFET).

Among various semiconductor devices, the most important device used in modern circuits is the MOSFET. A schematic illustration of a complementary metal-oxide-semiconductor (CMOS) consists of an n-MOSFET and a p-MOSFET is shown in Fig. 1.2.

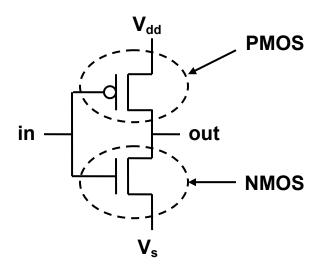

One of the most important parameter to evaluate the performance of an IC is the dynamic response (i.e. charging and discharging) of load capacitance, associated with a specific circuit element and the supply voltage provide to the element at a representative (clock) frequency. A common element employed to examine such switching time effects is a CMOS inverter where the input signal is attached to the gates and the output signal is connected to both an NMOS and a PMOS transistor as shown in Fig. 1.3. The switching time is limited by both the fall time required to discharge the load capacitance by the NMOS drive current and the rise time required to charge the load capacitance by the PMOS drive current. The average switching response time ( $\bar{\tau}$ ) of an inverter is given by [1.3]

$$\bar{\tau} \propto \frac{1}{I_d^n + I_d^p} \tag{1.1}$$

where  $I_d^n$  and  $I_d^p$  are the drive current of n- and p-MOSFETs, respectively. The performance of an IC then can be characterized through this switching response time. It is easily seen that to achieve a decrease in  $\overline{\tau}$  (higher switching speed, better IC performance), increase in the drive current  $I_d$  of the n- and p-MOSFETs is required. Therefore, the improvement of IC performance can be taken as linked to the enhancement of drive current  $I_d$  associated with the MOSFETs.

Figure 1.3 Schematics of a CMOS inverter where  $V_s$  and  $V_{dd}$  serve as the source and drain voltages, respectively.

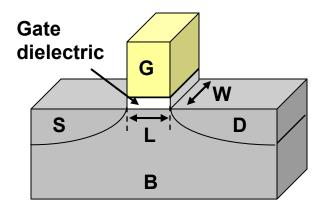

Figure 1.4 Sketch of a typical MOSFET structure on a bulk (B) substrate, in which L and W represent the channel length and width, respectively. When the channel is inverted with a voltage applied on the gate (G), carriers can flow from the source (S) to drain (D) forming the drive current of the MOSFET.

Figure 1.4 shows a sketch of a typical MOSFET structure on a bulk substrate. When a voltage is applied on the gate to invert the channel and a potential drops between source and drain, carriers flow from the source to drain and form the drive current of the transistor. The saturation drive current  $I_{d sat}$  is given by [1.4]

$$I_{d,sat} = \frac{W}{L} \mu C_{inv} \frac{(V_g - V_{th})^2}{2}$$

(1.2)

where

- *W*: the width of the transistor channel

- L: the length of transistor channel

- $\mu$ : the channel carrier mobility

- $C_{inv}$ : the capacitance density associated with the gate dielectric when the underlying channel is in the inverted state

- $V_{g}$ : the voltage applied to the transistor gate

$V_{th}$ : the threshold voltage of transistor.

According to Eq. (1.2), to achieve an increase of drive current  $I_{d,sat}$  for a given power supply voltage can be taken as to modify the values of the parameters in the right side of the equation. However, increase of the term  $(V_g - V_{th})$  is limited in range due to reliability considerations and room temperature operation constraints. Increase of the channel width W is contrary to the scaling of device dimension. The channel length L has been continually reduced and is approaching its fundamental limits today. Therefore, the remaining approaches to enhance the drive current  $I_{d,sat}$  and eventually improve MOSFET performance are increases of either the gate dielectric capacitance density  $C_{inv}$ or the channel carrier mobility  $\mu$ , or both of them.

### **1.2** High-k gate dielectrics and metal gate

The MOS gate structure in a transistor (see Fig. 1.4) can be simplified as a parallel plate capacitor. The gate capacitance  $C_{inv}$  can be given by [1.5]

$$C_{inv} = \frac{k \cdot \mathcal{E}_0 \cdot A}{t_{inv}}$$

(1.3)

where

- k: the relative permittivity (i.e. dielectric constant) of dielectric ( $\kappa = 3.9$  for SiO<sub>2</sub>)

- $\varepsilon_0$ : the permittivity of free space (8.85×10<sup>-3</sup> *fF* /  $\mu m$ )

- *A* : the area of the capacitor

$t_{inv}$ : the capacitive equivalent thickness (CET) of the gate dielectric.

With a traditional ploy-Si gate,  $t_{inv}$  consists of the following three CET components:

$$t_{inv} = t_{poly} + t_{ox} + t_{QM} \tag{1.4}$$

where

- $t_{poly}$ : contribution from poly depletion effect from the poly-Si gate

- $t_{OM}$ : contribution from quantum mechanical effect from the carriers channel.

- $t_{ox}$ : the main part of  $t_{inv}$  attributes to the gate dielectric, also known as equivalent oxide thickness (EOT).

Therefore, an increase of  $C_{inv}$  requires the decrease in  $t_{inv}$ . Among the three CET components of  $t_{inv}$ ,  $t_{QM}$  is attributed to intrinsic mechanism which cannot be eliminated;  $t_{poly}$  comes from the poly-Si gate, thus can be eliminated by replacing poly-Si gate with metal gate. One of the most widely studied metal gate materials, Tantalum Nitride (TaN), was used as metal gate in this project. The down scaling of  $t_{ox}$ , the main component of  $t_{inv}$ , has been continuous during the past several decades with the thinning of the physical thickness of SiO<sub>2</sub> gate dielectric. However, it is known that a minimum thickness of 7 Å for SiO<sub>2</sub> is required to maintain its bulk properties, such as its band gap. Furthermore, when gate leakage current is taken into consideration, the practical limit for SiO<sub>2</sub> thickness scaling becomes 10-12 Å [1.6], which makes industry face a great challenge on high performance device scaling after 2007 as shown in Table 1.1.

| Year of Production                                                                                         | 2006 | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 |  |

|------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|

| DRAM 1/2 Pitch (nm)<br>(contacted)                                                                         | 70   | 65   | 57   | 50   | 45   | 40   | 36   |  |

| MPU/ASIC Metal1 1/2<br>Pitch (nm) (contacted)                                                              | 78   | 68   | 59   | 52   | 45   | 40   | 36   |  |

| MPU Physical Gate<br>Length (nm)                                                                           | 28   | 25   | 23   | 20   | 18   | 16   | 14   |  |

| EOT for extended planar<br>bulk (Å)                                                                        | 11   | 11   | 9    | 7.5  | 6.5  | 5    | 5    |  |

| Effective NMOS<br>$I_{d,sat}(\mu A/\mu m)$ (extended<br>planar bulk) ( $I_{d,sat}$ of<br>PMOS is ~ 40-50%) | 1130 | 1200 | 1570 | 1810 | 2050 | 2490 | 2300 |  |

| Mobility Enhancement<br>Factor for $I_{d,sat}$ (extended<br>planar bulk)                                   | 1.10 | 1.10 | 1.12 | 1.11 |      |      |      |  |

| Manufacturable solutions exist, and are being optimized                                                    |      |      |      |      |      |      |      |  |

Table 1.1. Near-term high-performance logic technology requirements in ITRS 2005 [1.7].

Manufacturable solutions are known

Manufacturable solutions are NOT known

Fortunately, the application of high-k gate dielectrics in recent decade allows people to use physically thicker dielectric film therefore reduce the gate direct tunneling current while maintains the same EOT of a thin SiO<sub>2</sub> gate dielectric. The physical thickness of an alternative high-k dielectric to achieve the equivalent capacitance density with  $t_{ax}$  of a SiO<sub>2</sub> can be obtained from the expression

$$t_{high-k} = \frac{t_{ox}(EOT)}{3.9} \cdot k_{high-k}$$

(1.5)

where

contribution from quantum mechanical effect from the carriers channel.  $t_{QM}$ :

$t_{high-k}$ : the physical thickness of the high-k gate dielectric

$k_{high-k}$ : the relative permittivity of the high-k gate dielectric

In the past few years, a number of studies has been carried out on high-k metal oxides and several promising high-k gate dielectric candidates have been identified, such as  $La_2O_3$ ,  $HfO_2$  and Hf-based pseudo-binary alloys (HfSiO, HfSiON, HfTaO, and HfLaO). In this project,  $HfO_2$  was used as gate dielectric for its higher k value, relatively simple formation techniques and good interface with Ge after substrate passivation.

### **1.3** High mobility channel materials

As stated in Section 1.1, another way to enhance the drive current  $I_{d,sat}$  and eventually improve MOSFET performance is to increases the channel carrier mobility  $\mu$ . Novel channel materials such as germanium and III-V semiconductors provide potential solution for mobility enhancement by replacing conventional silicon channel. Table 1.2 lists the properties of common semiconductor materials.

|                                      | Si   | Ge   | GaAs | InAs  | InSb  |

|--------------------------------------|------|------|------|-------|-------|

| $\mu_{electron} ({ m cm}^2/{ m Vs})$ | 1400 | 3900 | 8000 | 33000 | 77000 |

| $\mu_{hole}$ (cm <sup>2</sup> /Vs)   | 470  | 1600 | 340  | 460   | 1000  |

| Bandgap (eV)                         | 1.12 | 0.66 | 1.42 | 0.36  | 0.17  |

| Melting point (K)                    | 1685 | 1231 | 1510 | 1215  | 798   |

Table 1.2 Properties of common semiconductor materials (Si, Ge, GaAs, InAs, and InSb).  $\mu_{electron}$  and  $\mu_{hole}$  represent electron mobility and hole mobility respectively.

From Table 1.2, it is noted that germanium is the only material that offers mobility enhancement for both electron and hole with appropriate bandgap and melting points compared to other semiconductor materials, making it an attractive channel material for both NMOS and PMOS devices application. However, although the first MOSFET and IC were fabricated on Ge half century ago [1.8], the poor properties of germanium oxides and lack of good quality gate dielectric greatly hindered the development of Ge MOS device. Until recent years, Ge MOS devices with various high-k gate dielectrics were reported with the progress in high-k deposition and surface passivation techniques [1.9]-[1.12]. Ge pMOSFET with an EOT of 6-10 Å has also been demonstrated [1.13].

### 1.4 Schottky barrier source/drain MOSFET

### 1.4.1 Motivation

The idea of completely replacing doped source/drain with metal was first proposed by Nishi in 1966 in a Japanese patent which was issued four years later [1.14]. The first paper on the topic, however, was published in 1968 by Lepselter and Sze [1.15], focusing on a PMOS bulk device employing PtSi for the source/drain regions. Although a variety of Schottky barrier MOS devices were studied in the 1980s [1.16]-[1.20], the poor performance due to device architecture and process technology issues, hindered the progress of Schottky barrier MOSFET until the advantages of Schottky barrier MOSFET for device scaling were realized by Tucker [1.21] and Snyder [1.22] in 1994. In recent years, Schottky barrier MOSFET have received tremendous attention due to its numerous

benefits in making CMOS technology scalable to sub-10-nm gate length dimensions

[1.23], which will be briefly introduced as following.

Table 1.3 Introduction of roadmap challenges addressed by Schottky barrier MOSFET (SBMOS). Most of the categories have multiple line items in the detailed roadmap tables. The box color for a given year and category above reflects the worst case, considering all of the roadmap line items within each category. (red) = manufacturable solution not known; (yellow) = manufacturable solutions are known; = manufacturable solutions exist and being optimized (after [1.24]).

| Roadmap Challenge                                                                     | Roadmap                | 2005 | 2007 | 2010 | SBMOS |

|---------------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| Technology Node (nm) [DRAM ½ Pitch ]                                                  |                        | 80   | 65   | 45   |       |

| MPU Physical Gate Length (nm) [High-performance logic]                                |                        | 32   | 25   | 18   | Help  |

| Gate dielectric requirements                                                          | Front End              |      |      |      | Help  |

| Source-drain shallow implant requirements                                             | Front End              |      |      |      | Solve |

| Source-drain junction resistivity requirements                                        | Front End              |      |      |      | Solve |

| Source-drain lateral abruptness requirements                                          | Front End              |      |      |      | Solve |

| Gate requirements (e.g. metal gates)                                                  | Front End              |      |      |      | Help  |

| Channel doping requirements                                                           | Front End              |      |      |      | Help  |

| Sub-threshold leakage current requirements (High performance and Low operating power) | Process<br>Integration |      |      |      | Help  |

| Mobility/Transconductance requirements and technologies (e.g. strained silicon)       | Process<br>Integration |      |      |      | Help  |

| MOS RF Device requirements (e.g. fT)                                                  | Proc. Int.             |      |      |      | Help  |

| Soft error rates                                                                      | Design                 |      |      |      | Help  |

Figure 1.5 shows an XTEM (cross-sectional transmission electron microscope) image of a 27 nm channel length PtSi source/drain device with 19 Å gate oxide. It is obvious that in a Schottky barrier MOSFET, the metallic source/drain replace doped source/drain and form a Schottky barrier with the semiconductor substrate and channel region. Table 1.3 summarized the impact of Schottky barrier MOSFET in a variety of general ITRS roadmap categories, including "Process Integration, Devices and Structures", "Front End Processes" and "Design.". ITRS roadmap indicates predicts that there is no known solution to meet the requirements for the source/drain parasitic

resistance, shallow implant and lateral abruptness within the next two years. By replacing doped source/drain with metal silicide source/drain, challenge for the source/drain resistance can be easily solved since the metal silicide has low sheet resistance and the contact resistance is very low in metal-to-metal contacts. Without the difficulties in achieving shallow implant, the junction depth in metal silicide source/drain can be easily controlled from metal-Si reaction with atomically sharp interface (see Fig. 1.5). Since Schottky barrier source/drains require no impurity doping, the carrier concentration is no longer limited by the dopant solid solubility in the substrate material, which has been a bottleneck for some high mobility substrate material such as germanium and GaAs. On the other hand, the implantless Schottky barrier MOSFET process also eliminates the high-temperature 1000° C spike or flash anneals to activate the source/drain dopants. Instead, the formation temperature of metallic source/drain is usually less than 600° C, which enables the integration of other new critical materials into CMOS process flows, such as high-k gate dielectrics, metal gate, strained silicon and germanium. The properties of these new materials tend to degrade upon high-temperature anneal in doped source/drain technology, but are more stable when the process thermal budget is less than 600° C [1.25]-[1.30]. With the elimination of implantation, the manufacturing process becomes simpler and cost is also reduced especially for short channel devices.

Figure 1.5 XTEM of a PtSi source/drain device with 27 nm channel length, 19 Å gate oxide, and  $n^+$  poly gate (after [1.31]).

Another advantage of Schottky barrier MOS device is the latchup immunity. In the1980s, Sugino and Swirhun first realized that Schottky barrier MOSFET can naturally eliminate parasitic bipolar gain [1.19] [1.32]-[1.34], due to the reduction in theoretical emitter efficiency at the source by eight orders of magnitude from 10<sup>4</sup> for a conventional MOS device to 10<sup>-4</sup> for a Schottky barrier MOS device. Therefore a Schottky barrier MOS device is inherently radiation tolerant. Consequently, circuits manufactured with Schottky barrier MOSFET technology will benefit from unconditional latchup immunity and substantially reduced soft error rates, thereby improving field level product reliability for both memory and logic applications, especially as device dimensions scale into the sub-50 nm regime [1.35].

### **1.4.2** Operation principles

The operation principles are fundamentally different between Schottky barrier source/drain MOSFET and doped source/drain MOSFET although technically these two kinds of devices have many similarities in the fabrication process. The main difference is the nature of the junction between the source/drain regions to the semiconductor substrate: the junction is a metal/semiconductor Schottky diode in Schottky barrier MOSFET, while it is a PN junction in doped source/drain MOSFET.

Figure 1.6 Band diagrams of (a) Schottky barrier PMOS device and (b) conventional impurity-doped source/drain MOS device.

Band diagrams of germanide Schottky barrier source/drain p-MOSFET and conventional impurity-doped source/drain Ge p-MOSFET are shown in Figure 1.6. In the Schottky barrier PMOS device in Fig. 1.6 (a), the Fermi level of the source and drain germanide are attached to the Ge band gap close to the valence band in the "off" and "on" state respectively. The band diagrams for Schottky barrier PMOS and conventional MOS are quite similar except at the source and drain region, where the metal germanide Fermi level is replaced by the germanium bands in conventional PMOS, and the Schottky barrier PMOS bands have a built in Schottky barrier at the source and drain interface with the channel. In the off-state, the built-in Schottky barrier and substrate doping combine to limit electron and hole thermal emission into the channel. Compared to a Schottky barrier MOS device, a conventional MOS device requires a much higher channel doping concentration to achieve the same effective barrier to thermal emission in the off-state. Therefore to achieve a given off-state leakage current, channel doping in Schottky barrier MOSFET can be reduced compared to conventional MOS. As the gate voltage become more negative and the Schottky barrier MOS device is turned on, a gate induce electric field renders the source barrier virtually transparent and carriers are injected into the channel region. The net field emission current through the source Schottky barrier is exponentially sensitive to the electric field intensity at the source.

The band diagrams for a Schottky barrier NMOS device are the mirror image of those of PMOS as shown in Fig. 1.6. Similar discussion on device operation principles can also be applied.

### 1.4.3 Literature review

During the past ten years, the development of Schottky barrier MOSFET technology has advanced significantly in the aspects of device architectures, Schottky barrier height engineering and integration of new silicide materials such as  $ErSi_x$  and  $YbSi_x$  into device-fabrication process flows [1.36]-[1.38]. Table 1.4 summarized the

Schottky barrier NMOS and PMOS in the literature with gate length less than 250 nm. As one can see, high-performance Schottky barrier NMOS using thin dopant-segregation junctions and PMOS with a PtSi source/drain have been demonstrated. However, the oncurrent of these devices does not yet meet the ITRS requirements. Naturally, integration of Schottky barrier source/drain with other unconventional approaches (see Eq. 1.2) needs to be considered for further enhancement of the device on-current.

Among these unconventional approaches, Schottky barrier MOSFET fabricated on high mobility channel materials has received more and more attentions since past a few years. Germanium is one of the most promising channel materials as it offers mobility enhancement for both electron and hole with appropriate bandgap and melting points as shown previously. However, on the road to Schottky source/drain transistors, the metal Fermi level pinning is always a big challenge in work function and Schottky barrier tuning, especially at metal/germanium interface. This is the reason why low Schottky barrier is difficult to achieve, and extremely low work function metals such as Yb, Er have to be used for NMOS. A simulation work shows that for typical Schottky source and drain transistor, it is the carrier tunneling through the metal-semiconductor barrier height that limits the on-current. Thus only a negative metal-semiconductor barrier height could deliver the on-current of a ballistic MOSFET [1.40]. However, this simulation ignored the Schottky barrier lowering, phonon- and defect-assisted tunneling, band structure effects, etc, which could increase the transmission of the barrier. Recently, simulation studies suggest a finite positive barrier of 0.06-0.1 eV is needed for Schottky barrier PMOS and NMOS to make Schottky barrier CMOS technology speed performance competitive with doped source/drain technology [1.41] [1.42].

Table 1.4 Summary of sub-250-nm-gate length Schottky barrier NMOS and PMOS literature. The column labeled "Technology" has a comma-separated list for each row with the format "Type, device structure, source/drain silicide type, source/drain engineering type". (N=NMOS, P=PMOS; B= bulk, S= SOI, F= FinFET; 1= standard, 2= interfacial layer) [1.23].

| #   | Year | Technology   | Lg<br>[nm] | Gate<br>type   | EOT<br>[Å] | V <sub>ds</sub><br>[V] | V <sub>gs</sub><br>[V] | <i>I</i> on<br>[μΑ/μm] | <i>I<sub>off</sub></i><br>[nA/μm] | $I_{on}/I_{off}$     | Swing<br>[mV/dec] | gm<br>[mS/mm] |

|-----|------|--------------|------------|----------------|------------|------------------------|------------------------|------------------------|-----------------------------------|----------------------|-------------------|---------------|

| 1   | 1999 | N,B,ErSi,1   | 35         | Au/Cr          | 35         | 2.0                    | 2.0                    | 45                     | 7500                              | 6                    | -                 | 20            |

| 2   | 2004 | N,B,CoSi,1   | 65         | -              | 60         | 1.5                    | 3.0                    | 350                    | 2000                              | 175                  | 320               | -             |

| 3   | 1999 | N,S,ErSi,1   | 25         | Au/Cr          | 35         | 2.0                    | 2.0                    | 75                     | 3.75x10 <sup>4</sup>              | 2                    | -                 | 9.5           |

| 4   | 2000 | N,S,ErSi,1   | 15         | N <sup>+</sup> | 40         | 1.5                    | 1.2                    | 190                    | 19                                | 104                  | 150               | -             |

| 5   | 2004 | N,S,ErSi,1   | 50         | N <sup>+</sup> | 50         | 1.0                    | 3.0                    | 120                    | 10                                | 1.2x10 <sup>4</sup>  | -                 | -             |

| 6   | 2004 | N,S,ErSi,1   | 25         | Au/Cr          | 35         | 1.5                    | 2.0                    | 11                     | 2000                              | 6                    | -                 | -             |

| 7   | 2004 | N,S,CoSi,1   | 65         |                | 60         | 1.5                    | 3.0                    | 25                     | 70                                | 357                  | 1500              |               |

| 8   | 2005 | N,S,CoSi,2   | 50         | -              | 25         | 2.0                    | 2.0                    | 1670                   | 100                               | $1.7 x 10^4$         | -                 | -             |

| 9   | 1997 | P,B,TiGeSi,1 | 250        | Al             | 70         | -2.0                   | -2.0                   | 350                    |                                   | -                    | 70                | 210           |

| 10  | 1997 | P,B,PtGeSi,1 | 250        | Si/Al          | 70         | -2.0                   | -2.0                   | 250                    |                                   | -                    | 78                | 145           |

| 11  | 1999 | P,B,PtSi,1   | 27         | P <sup>+</sup> | 19         | -1.2                   | -1.2                   | 350                    | 1.0x10 <sup>4</sup>               | 35                   | -                 | -             |

| 12  | 1999 | P,B,PtSi,1   | 40         | P+             | 19         | -1.2                   | -1.2                   | 350                    | 1.5x10 <sup>4</sup>               | 23                   | -                 | -             |

| 13  | 2002 | P,B,PtGeSi,1 | 50         | N <sup>+</sup> | 20         | -1.5                   | -1.5                   | 339                    | 1.0x10 <sup>4</sup>               | 34                   | -                 | 285           |

| 14  | 2004 | P,B,PtSi,1   | 25         | $N^+$          | 20         | -1.1                   | -2.6                   | 314                    | 168                               | 1869                 | 117               | 500           |

| 15  | 2005 | P,B,PtSi,1   | 25         | $N^+$          | 18         | -1.1                   | -1.8                   | 460                    | 168                               | 2700                 | 117               | 500           |

| 16  | 2005 | P,B,PtSi,1   | 25         | N <sup>+</sup> | 18         | -1.1                   | -1.8                   | 629                    | 6149                              | 102                  | -                 | 558           |

| 17  | 2005 | P,B,PtSi,1   | 60         | $N^+$          | 18         | -1.2                   | -1.7                   | 311                    | 12                                | 2.6x10 <sup>4</sup>  | 96                | 400           |

| -18 | 2005 | P,B,PtSi,1   | 80         | $N^+$          | 18         | -1.4                   | -1.7                   | 300                    | 6                                 | 5.0x10 <sup>4</sup>  | 91                | 417           |

| -19 | 2004 | P,F,NiSi,2   | 25         | $P^+$          | 40         | -1.0                   | -2.0                   | 250                    | 2.5x10 <sup>-4</sup>              | 1.0x10 <sup>9</sup>  | 83                | -             |

| 20  | 1999 | P,S,PtSi,1   | 35         | Au/Cr          | 35         | -1.2                   | -1.2                   | 70                     | 167                               | 420                  | -                 | 216           |

| 21  | 1999 | P,S,PtSi,1   | 56         | Au/Cr          | 35         | -1.2                   | -1.2                   | 60                     | 20                                | 3000                 | -                 | 220           |

| 22  | 2000 | P,S,PtSi,1   | 38         | Au/Cr          | 35         | -1.5                   | -1.5                   | 168                    | 457                               | 368                  | -                 | 175           |

| 23  | 2000 | P,S,PtSi,1   | 25         | Au/Cr          | 35         | -1.5                   | -1.5                   | 293                    | 8879                              | 33                   | -                 | 431           |

| 24  | 2000 | P,S,PtSi,1   | 20         | N <sup>+</sup> | 40         | -1.5                   | -1.2                   | 270                    | 1                                 | 5.0 x10 <sup>4</sup> | 100               | -             |

| 25  | 2004 | P,S,PtSi,1   | 25         | Au/Cr          | 35         | -1.5                   | -2.0                   | 16                     | 30                                | 533                  | -                 | -             |

Heine, in 1965, pointed out that any intrinsic electron states which may be present on a free semiconductor surface will be replaced by metal-induced gap states (MIGS) when a metal is deposited on that surface [1.43] [1.44]. Besides MIGS, for a surface which is imperfect, defects such as steps or vacancies may lead to additional localized states. The energy levels associated with these defects may lie in the band gap of the semiconductor. Both of them may present at metal-semiconductor interface in densities sufficient to cause strong pinning of the metal Fermi level.

Table 1.5 summarized measured barrier height values of the metal germanide/Ge contacts and pure metal/Ge contacts in the literature. The dependence of the barrier height on the metal work function is reflected by the equation

$$\phi_b = S \cdot \phi_m + C \tag{1.6}$$

where

- *S* : slope parameter

- $\phi_{h}$ : the barrier height of the metal/Ge contacts

- $\phi_m$ : the metal work function

- *C*: a constant

The value of S is a direct reflection of interface states density  $D_s$  given by

$$S = \frac{1}{1 + (q^2 D_s \sigma) / (\varepsilon \varepsilon_0)}$$

(1.7)

where

- q: the electronic charge

- $\sigma$ : the thickness of interfacial layer

- $\varepsilon$ : the absolute permittivity of interfacial layer

- $\varepsilon_0$ : the permittivity of free space

In an ideal metal/semiconductor system, according to the Schottky-Mott theory, Schottky barrier height can be controlled by the metal work function. However, the low values of *S* in Table 1.5 indicate a high density of interface states at the metal/Ge interface and the Fermi level is pinned at between 0.54 and 0.61 eV below the conduction-band edge, independent of the contacting metallization [1.45].

The lowest values of  $\phi_{bh}$  and  $\phi_{be}$  in Schottky source/drain Si MOSFET technology are achieved both ~ 0.27 eV by using PtSi [1.23] [1.37] and YbSi<sub>2-x</sub> [1.46] for PMOS and NMOS device respectively. The strong Fermi level pinning near valence band of germanium in metal/Ge contacts makes it much easier to achieve lower  $\phi_{bh}$  ( $\phi_{bh} < 0.1$ eV) compared to in metal/Si case, implying Schottky source/drain Ge PMOS device is promising to be realized with improved performance than Schottky source/drain Si PMOS device. However, the Fermi level pinning at metal/Ge interface also provides high  $\phi_{be}$  for NMOS device, which is a great challenge to the realization of NMOS device.

Various attempts have been carried out to alleviate the Fermi level pinning phenomenon. M. Tao [1.47]-[1.49] and D. Udeshi [1.50] demonstrated that, by terminating dangling bonds and relaxing strained bonds on the silicon (001) surface with a monolayer of selenium, low Schottky barriers can be obtained. Dan Grupp *et al.* [1.51] has proposed x-junction structure by inserting thin insulator between metal and semiconductor to reduce pinning while still maintaining high conductance. Another way to modify barrier height is to introduce a thin, highly doped interfacial region at metal/semiconductor interface by shallow ion implantation, epitaxial growth or diffusion form a doped layer [1.45]. However, the low  $\phi_{be}$  in metal/Ge contacts has not yet been reported so far in the literature.

| Metal | $\phi_m$ (eV) | Contact               | $\phi_{be}$ (eV) | $\phi_{bh}$ (eV) | S    | Ref.   |

|-------|---------------|-----------------------|------------------|------------------|------|--------|

| Pt    | 5.65          | Pt/Ge                 | 0.62             | 0.04             |      |        |

|       |               | Pt <sub>2</sub> Ge/Ge | 0.61             | 0.05             |      |        |

|       |               | PtGe/Ge               | 0.62             | 0.04             |      |        |

|       |               | PtGe <sub>2</sub> /Ge | 0.62             | 0.04             |      |        |

| Ni    | 5.15          | Ni/Ge                 | 0.57             | 0.09             |      |        |

|       |               | Ni <sub>2</sub> Ge/Ge | 0.58             | 0.08             | 0.02 | [1.39] |

|       |               | NiGe/Ge               | 0.59             | 0.07             |      | [1.39] |

| Pd    | 5.12          | Pd/Ge                 | 0.61             | 0.05             |      |        |

|       |               | Pd <sub>2</sub> Ge/Ge | 0.61             | 0.05             |      |        |

|       |               | PdGe/Ge               | 0.61             | 0.05             |      |        |

| Er    | 3.12          | Er/Ge                 | 0.54             | 0.12             |      |        |

|       |               | ErGe <sub>2</sub> /Ge | 0.52             | 0.14             |      |        |

| Ni    | 5.15          | Ni/Ge                 | 0.44             | 0.22             | 0.40 | [1.53] |

| Pb    | 4.20          | Pb/Ge                 | 0.38             | 0.28             |      |        |

| Au    | 4.70          | Au/Ge                 | 0.54             | 0.12             |      |        |

| Pd    | 5.12          | Pd/Ge                 | —                | _                | 0.16 | [1.55] |

| Ni    | 5.15          | Ni/Ge                 | —                | _                |      |        |

| Ag    | 4.26          | Ag/Ge                 | 0.54             | 0.12             | 0.11 | [1.56] |

|       |               | Ge/Ag                 | 0.48             | 0.18             |      |        |

| Ni    | 5.15          | Ni/Ge                 | 0.49             | 0.17             |      |        |

|       |               | Ge/Ni                 | 0.49             | 0.17             |      |        |

Table 1.5 Summary of barrier heights of various metal germanide/Ge contacts and pure metal/Ge contacts in the literature.  $\phi_m$  is the metal work function,  $\phi_{be}$  is barrier height for electron,  $\phi_{bh}$  is barrier height for hole, and S is slope parameter.

### **1.5** Thesis organization

As discussed in Section 1.2 to Section 1.4, high-k gate dielectric, metal gate, high mobility germanium channel and Schottky barrier source/drain structure are all attractive elements for future CMOS technology in different aspects. Therefore the main objective of this project is to explore the feasibility of integration of germanide Schottky

source/drain MOSFET with high-k gate dielectric (HfO<sub>2</sub>) and metal gate (TaN) for subtenth nm technology.