# ANALYSIS, DESIGN AND MANAGEMENT OF MULTIMEDIA MULTI-PROCESSOR SYSTEMS

### AKASH KUMAR

NATIONAL UNIVERSITY OF SINGAPORE 2009

# ANALYSIS, DESIGN AND MANAGEMENT OF MULTIMEDIA MULTI-PROCESSOR SYSTEMS

#### AKASH KUMAR

(Master of Technological Design (Embedded Systems),

National University of Singapore and Eindhoven University of Technology)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2009

## Acknowledgments

I have always regarded the journey as being more important than the destination itself. While for PhD the destination is surely desired, the importance of the journey can not be underestimated. At the end of this long road, I would like to express my sincere gratitude to all those who supported me all through the last four years and made this journey enjoyable. Without their help and support, this thesis would not have reached its current form.

First of all I would like to thank Henk Corporaal, my promoter and supervisor all through the last four years. All through my research he has been very motivating. He constantly made me think of how I can improve my ideas and apply them in a more practical way. His eye for details helped me maintain a high quality of my research. Despite being a very busy person, he always ensured that we had enough time for regular discussions. Whenever I needed something done urgently, whether it was feedback on a draft or filling some form, he always gave it utmost priority. He often worked in holidays and weekends to give me feedback on my work in time.

I would especially like to thank Bart Mesman, in whom I have found both a mentor and a friend over the last four years. I think the most valuable ideas during the course of my Phd were generated during detailed discussions with him. In the beginning phase of my Phd, when I was still trying to understand the domain of my research, we would often meet daily and go on talking for 2-3 hours at a go pondering on the topic. He has been very supportive of my ideas and always pushed me to do better.

Further, I would like to thank Yajun Ha for supervising me not only during my stay in the National University of Singapore, but also during my stay at TUe. He gave me useful insight into research methodology, and critical comments on my publications throughout my PhD project. He also helped me a lot to arrange the administrative things at the NUS side, especially during the last phase of my PhD. I was very fortunate to have three supervisors who were all very hard working and motivating.

My thanks also extend to Jef van Meerbergen who offered me this PhD position as part of the PreMaDoNA project. I would like to thank all members of the PreMaDoNA project for the nice discussions and constructive feedback that I got from them.

The last few years I had the pleasure to work in the Electronic Systems group at TUe. I would like to thank all my group members, especially our group leader Ralph Otten, for making my stay memorable. I really enjoyed the friendly atmosphere and discussions that we had over the coffee breaks and lunches. In particular, I would like to thank Sander for providing all kinds of help from filling Dutch tax forms to installing printers in Ubuntu. I would also like to thank our secretaries Rian and Marja, who were always optimistic and maintained a friendly smile on their face.

I would like to thank my family and friends for their interest in my project and the much needed relaxation. I would especially like to thank my parents and sister without whom I would not have been able to achieve this result. My special thanks goes to Arijit who was a great friend and cooking companion during the first two years of my PhD. Last but not least, I would like to thank Maartje who I met during my PhD, and who is now my companion for this journey of life.

Akash Kumar

# Contents

| $\mathbf{A}$  | ckno  | wledgments                                  | 1   |

|---------------|-------|---------------------------------------------|-----|

| Sı            | ımm   | ary                                         | vii |

| $\mathbf{Li}$ | st of | Tables                                      | ix  |

| $\mathbf{Li}$ | st of | Figures                                     | xi  |

| 1             | Tre   | nds and Challenges in Multimedia Systems    | 1   |

|               | 1.1   | Trends in Multimedia Systems Applications   | 3   |

|               | 1.2   | Trends in Multimedia Systems Design         | 5   |

|               | 1.3   | Key Challenges in Multimedia Systems Design | 12  |

|               |       | 1.3.1 Analysis                              | 13  |

|               |       | 1.3.2 Design                                | 15  |

|               |       | 1.3.3 Management                            | 17  |

|               | 1.4   | Design Flow                                 | 19  |

|               | 1.5   | Key Contributions and Thesis Overview       | 21  |

| 2             | App   | plication Modeling and Scheduling           | 23  |

|               | 2.1   | Application Model and Specification         | 24  |

|               | 2.2   | Introduction to SDF Graphs                  | 27  |

|               |       | 2.2.1 Modeling Auto-concurrency             | 28  |

|   |     | 2.2.2   | Modeling Buffer Sizes                           | 30 |

|---|-----|---------|-------------------------------------------------|----|

|   | 2.3 | Comp    | arison of Dataflow Models                       | 30 |

|   | 2.4 | Perfor  | mance Modeling                                  | 34 |

|   |     | 2.4.1   | Steady-state vs Transient                       | 35 |

|   |     | 2.4.2   | Throughput Analysis of (H)SDF Graphs            | 37 |

|   | 2.5 | Sched   | uling Techniques for Dataflow Graphs            | 38 |

|   | 2.6 | Analy   | zing Application Performance on Hardware        | 41 |

|   |     | 2.6.1   | Static Order Analysis                           | 41 |

|   |     | 2.6.2   | Dynamic Order Analysis                          | 46 |

|   | 2.7 | Comp    | osability                                       | 48 |

|   |     | 2.7.1   | Performance Estimation                          | 50 |

|   | 2.8 | Static  | vs Dynamic Ordering                             | 53 |

|   | 2.9 | Conclu  | usions                                          | 55 |

| 3 | Dno | babilia | etic Performance Prediction                     | 56 |

| 3 | 3.1 |         | Probabilistic Analysis                          |    |

|   | 3.1 | 3.1.1   | ·                                               |    |

|   |     |         | Generalizing the Analysis                       | 60 |

|   |     | 3.1.2   | Extending to N Actors                           | 63 |

|   | 2.0 | 3.1.3   | Reducing Complexity                             | 67 |

|   | 3.2 |         | ve Analysis                                     | 70 |

|   |     | 3.2.1   | Terminating Condition                           | 74 |

|   |     | 3.2.2   | Conservative Iterative Analysis                 | 75 |

|   |     | 3.2.3   | Parametric Throughput Analysis                  | 76 |

|   |     | 3.2.4   | Handling Other Arbiters                         | 77 |

|   | 3.3 | Exper   | iments                                          | 77 |

|   |     | 3.3.1   | Setup                                           | 78 |

|   |     | 3.3.2   | Results and Discussion – Basic Analysis         | 78 |

|   |     | 3.3.3   | Results and Discussion – Iterative Analysis     | 80 |

|   |     | 3.3.4   | Varying Execution Times                         | 88 |

|   |     | 3.3.5   | Mapping Multiple Actors                         | 89 |

|   |     | 3.3.6   | Mobile Phone Case Study                         | 90 |

|   |     | 3.3.7   | Implementation Results on an Embedded Processor | 92 |

|        | 3.4                                                       | Related Work                                                                                                                                                                                                                                                                                                                        | -        |

|--------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|        | 3.5                                                       | Conclusions                                                                                                                                                                                                                                                                                                                         | I        |

| 4      | Res                                                       | source Management 97                                                                                                                                                                                                                                                                                                                | ,        |

|        | 4.1                                                       | Off-line Derivation of Properties                                                                                                                                                                                                                                                                                                   | j        |

|        | 4.2                                                       | On-line Resource Manager                                                                                                                                                                                                                                                                                                            | )<br>(   |

|        |                                                           | 4.2.1 Admission Control                                                                                                                                                                                                                                                                                                             | )        |

|        |                                                           | 4.2.2 Resource Budget Enforcement                                                                                                                                                                                                                                                                                                   | j        |

|        | 4.3                                                       | Achieving Predictability through Suspension                                                                                                                                                                                                                                                                                         | ;        |

|        |                                                           | 4.3.1 Reducing Complexity                                                                                                                                                                                                                                                                                                           | ,<br>•   |

|        |                                                           | 4.3.2 Dynamism vs Predictability                                                                                                                                                                                                                                                                                                    | ŧ        |

|        | 4.4                                                       | Experiments                                                                                                                                                                                                                                                                                                                         | )        |

|        |                                                           | 4.4.1 DSE Case Study                                                                                                                                                                                                                                                                                                                | )<br>)   |

|        |                                                           | 4.4.2 Predictability through Suspension                                                                                                                                                                                                                                                                                             | ı        |

|        | 4.5                                                       | Related Work                                                                                                                                                                                                                                                                                                                        | <u>;</u> |

|        | 4.6                                                       | Conclusions                                                                                                                                                                                                                                                                                                                         | :        |

|        |                                                           |                                                                                                                                                                                                                                                                                                                                     |          |

| 5      | Mu                                                        | altiprocessor System Design and Synthesis 125                                                                                                                                                                                                                                                                                       | 1        |

| 5      | <b>Mu</b> 5.1                                             | Performance Evaluation Framework                                                                                                                                                                                                                                                                                                    |          |

| 5      |                                                           |                                                                                                                                                                                                                                                                                                                                     | ,        |

| 5      | 5.1                                                       | Performance Evaluation Framework                                                                                                                                                                                                                                                                                                    | ,<br>)   |

| 5      | 5.1                                                       | Performance Evaluation Framework                                                                                                                                                                                                                                                                                                    | ,<br>)   |

| 5      | 5.1                                                       | Performance Evaluation Framework                                                                                                                                                                                                                                                                                                    | )        |

| 5      | 5.1                                                       | Performance Evaluation Framework                                                                                                                                                                                                                                                                                                    |          |

| 5      | 5.1<br>5.2                                                | Performance Evaluation Framework 127  MAMPS Flow Overview 129  5.2.1 Application Specification 130  5.2.2 Functional Specification 131  5.2.3 Platform Generation 132                                                                                                                                                               |          |

| 5      | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Performance Evaluation Framework127MAMPS Flow Overview1295.2.1 Application Specification1305.2.2 Functional Specification1315.2.3 Platform Generation132Tool Implementation133                                                                                                                                                      |          |

| 5      | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Performance Evaluation Framework 127  MAMPS Flow Overview 129  5.2.1 Application Specification 130  5.2.2 Functional Specification 131  5.2.3 Platform Generation 132  Tool Implementation 133  Experiments and Results 134                                                                                                         |          |

| 5      | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Performance Evaluation Framework 127  MAMPS Flow Overview 129  5.2.1 Application Specification 130  5.2.2 Functional Specification 131  5.2.3 Platform Generation 132  Tool Implementation 133  Experiments and Results 134  5.4.1 Reducing the Implementation Gap 135                                                              |          |

| 5      | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Performance Evaluation Framework 127  MAMPS Flow Overview 129  5.2.1 Application Specification 130  5.2.2 Functional Specification 131  5.2.3 Platform Generation 132  Tool Implementation 133  Experiments and Results 134  5.4.1 Reducing the Implementation Gap 135  5.4.2 DSE Case Study 138                                    |          |

| 5<br>6 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                    | Performance Evaluation Framework 127  MAMPS Flow Overview 129  5.2.1 Application Specification 130  5.2.2 Functional Specification 131  5.2.3 Platform Generation 132  Tool Implementation 133  Experiments and Results 134  5.4.1 Reducing the Implementation Gap 135  5.4.2 DSE Case Study 138  Related Work 141                  |          |

|        | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                    | Performance Evaluation Framework 127  MAMPS Flow Overview 129  5.2.1 Application Specification 130  5.2.2 Functional Specification 131  5.2.3 Platform Generation 132  Tool Implementation 133  Experiments and Results 134  5.4.1 Reducing the Implementation Gap 135  5.4.2 DSE Case Study 138  Related Work 141  Conclusions 142 |          |

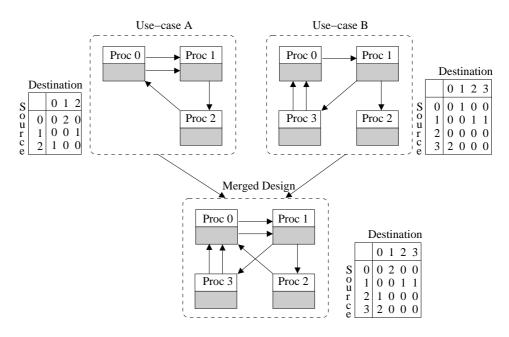

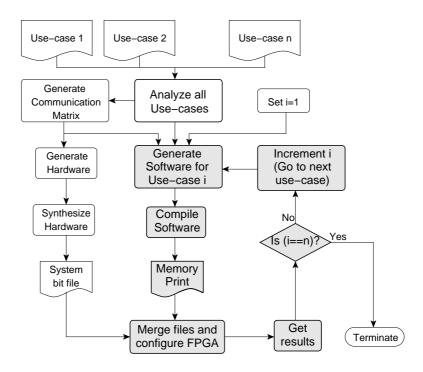

|                |                     | 6.1.2                  | Generating Software for Multiple Use-cases | . 147 |

|----------------|---------------------|------------------------|--------------------------------------------|-------|

|                |                     | 6.1.3                  | Combining the Two Flows                    | . 148 |

|                | 6.2                 | Use-ca                 | ase Partitioning                           | . 149 |

|                |                     | 6.2.1                  | Hitting the Complexity Wall                | . 151 |

|                |                     | 6.2.2                  | Reducing the Execution time                | . 151 |

|                |                     | 6.2.3                  | Reducing Complexity                        | . 152 |

|                | 6.3                 | Estim                  | ating Area: Does it Fit?                   | . 153 |

|                | 6.4                 | Exper                  | iments and Results                         | . 157 |

|                |                     | 6.4.1                  | Use-case Partitioning                      | . 157 |

|                |                     | 6.4.2                  | Mobile-phone Case Study                    | . 158 |

|                | 6.5                 | Relate                 | ed Work                                    | . 160 |

|                | 6.6                 | Concl                  | usions                                     | . 160 |

| 7              | Con                 | clusio                 | ns and Future Work                         | 162   |

|                | 7.1                 | Concl                  | usions                                     | . 162 |

|                | 7.2                 | Future                 | e Work                                     | . 165 |

| Bi             | bliog               | graphy                 |                                            | 168   |

| $\mathbf{G}$   | lossa               | $\mathbf{r}\mathbf{y}$ |                                            | 181   |

| $\mathbf{C}_1$ | urriculum Vitae 185 |                        |                                            |       |

| Li             | st of               | Public                 | cations                                    | 186   |

## Summary

Modern multimedia systems need to support a large number of applications or functions in a single device. To achieve high performance in such systems, more and more processors are being integrated into a single chip to build Multi-Processor Systems-on-Chip. The heterogeneity of such systems is also increasing with the use of specialized digital hardware, application domain processors and other IP blocks on a single chip, since various standards and algorithms are to be supported. These embedded systems also need to meet performance and other non-functional constraints like low power and design area. The concurrent execution of these applications causes interference and unpredictability in the performance of these systems.

In this thesis, a run-time performance prediction methodology is presented that can accurately and quickly predict the performance of concurrently executing multiple applications before they execute in the system. Synchronous data flow (SDF) graphs are used to model applications, since they fit well with characteristics of multimedia applications, and at the same time allow analysis of application performance. While a lot of techniques are available to analyze performance of single applications, this task is a lot harder for multiple applications and little work has been done in this direction. This thesis presents one of the first attempts to analyze performance of multiple applications executing on heterogeneous non-preemptive multiprocessor platforms. A run-time iterative probabilistic analysis is used to estimate the time spent by tasks during the contention phase, and thereby predict the performance of applications. An admission controller is presented using this analysis technique.

Further, a design-flow is presented for designing systems with multiple applications.

A hybrid approach is presented where the time-consuming application-specific computations are done at design-time, and in isolation with other applications, and the use-case-specific computations are performed at run-time. This allows easy addition of applications at run-time. A run-time mechanism is presented to manage resources in a system. This mechanism enforces budgets and suspends applications if they achieve a higher performance than desired. A resource manager is presented to manage computation and communication resources, and to achieve the above goals of performance prediction, admission control and budget enforcement.

With high consumer demand the time-to-market has become significantly lower. To cope with the complexity in designing such systems, a largely automated design-flow is needed that can generate systems from a high-level architectural description such that they are not error-prone and consume less time. This thesis presents a highly automated flow – MAMPS (Multi-Application Multi-Processor Synthesis), that synthesizes multiprocessor platforms for multiple use-cases. Techniques are presented to merge multiple use-cases into one hardware design to minimize cost and design time, making it well-suited for fast design space exploration of MPSoC systems. The above tools are made available on-line for use by the research community. The tools allow anyone to upload their application descriptions and generate the FPGA multiprocessor platform in seconds.

# List of Tables

| 2.1 | Comparison of static vs dynamic schedulers                               |

|-----|--------------------------------------------------------------------------|

| 2.2 | Table showing the deadlock condition                                     |

| 2.3 | Estimating performance: iteration-count for each application 53          |

| 2.4 | Properties of Scheduling Strategies                                      |

| 3.1 | Probabilities of different queues with $a$                               |

| 3.2 | Comparison of predicted vs actual time in different states 83            |

| 3.3 | Measured inaccuracy for period in percentage                             |

| 3.4 | Analysis techniques executing on an embedded processor                   |

| 4.1 | Achieving predictability using budget enforcement                        |

| 4.2 | Load on processing nodes due to each application                         |

| 4.3 | Performance of JPEG and H263 decoders and processor utilization 118      |

| 4.4 | Time weights computed statically for predictable performance             |

| 4.5 | Summary of related work for resource management                          |

| 5.1 | Comparison of various methods to achieve performance estimates 128       |

| 5.2 | Comparison of throughput obtained on FPGA with simulation 138            |

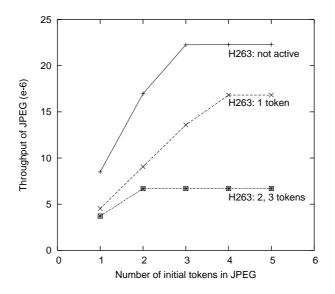

| 5.3 | Effect of varying initial tokens on throughput of H263 and JPEG 140      |

| 5.4 | Time spent on DSE of JPEG-H263 combination                               |

| 5.5 | Comparison of various approaches for providing performance estimates 142 |

| 6.1 | Resource utilization for different components in the design           | 156 |

|-----|-----------------------------------------------------------------------|-----|

| 6.2 | Evaluation of heuristics used for use-case reduction and partitioning | 159 |

# List of Figures

| 1.1  | Growth in Multimedia Systems: Odyssey vs Sony PlayStation3                      | 2  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Increasing processor speed and reducing memory cost                             | 6  |

| 1.3  | Comparison of speedup in homogeneous vs heterogeneous systems                   | 8  |

| 1.4  | The intrinsic computational efficiency of silicon and microprocessors $\dots$   | 9  |

| 1.5  | Platform-based design approach – system platform stack                          | 11 |

| 1.6  | Application performance with full virtualization vs simulation result $\dots$ . | 15 |

| 1.7  | System design flow: specification to implementation                             | 20 |

|      |                                                                                 |    |

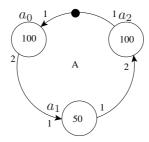

| 2.1  | Example of an SDF Graph                                                         | 27 |

| 2.2  | SDF Graph after modeling auto-concurrency                                       | 29 |

| 2.3  | SDF Graph after modeling buffer-size                                            | 30 |

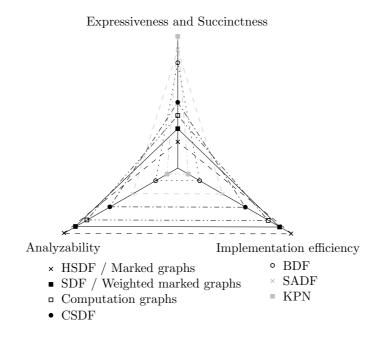

| 2.4  | Comparison of different models of computation                                   | 31 |

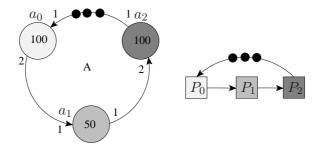

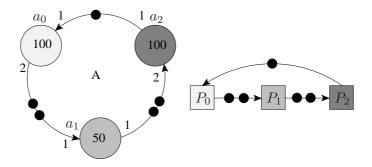

| 2.5  | SDF Graph and the multi-processor architecture                                  | 36 |

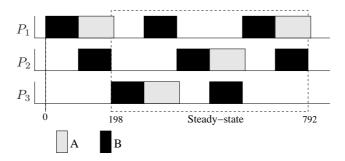

| 2.6  | Steady-state is achieved after two executions of $a_0$ and one of $a_1$         | 36 |

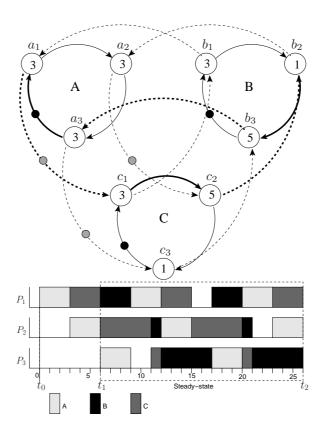

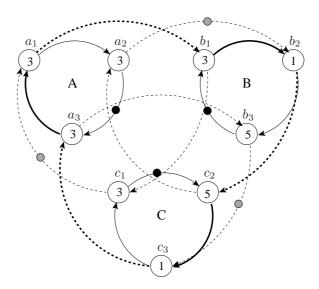

| 2.7  | A 3-application system mapped on a 3-processor platform                         | 42 |

| 2.8  | Graph with clockwise schedule (static) gives MCM of 11 cycles                   | 43 |

| 2.9  | Graph with anti-clockwise schedule (static) gives MCM of 10 cycles              | 44 |

| 2.10 | Deadlock situation when a new job arrives in the system                         | 46 |

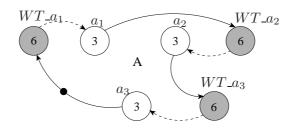

| 2.11 | Modeling worst case waiting time for an application                             | 48 |

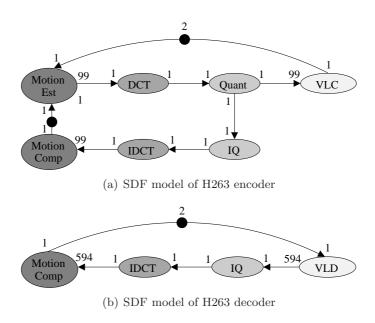

| 2.12 | SDF graphs of H263 encoder and decoder                                          | 50 |

| 2.13 | Two applications running on same platform and sharing resources                        | 51  |

|------|----------------------------------------------------------------------------------------|-----|

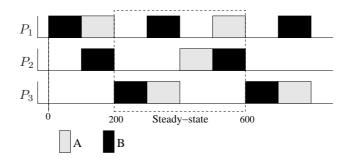

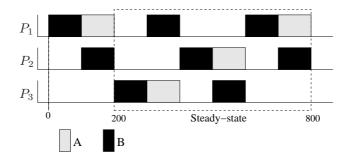

| 2.14 | Static-order schedule of applications executing concurrently                           | 52  |

| 2.15 | Schedule of applications executing concurrently when $B$ has priority $\ \ . \ \ .$    | 53  |

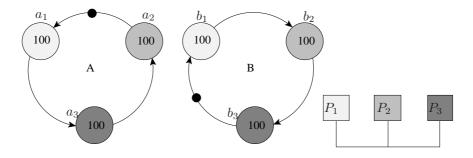

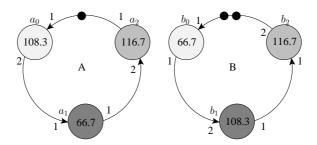

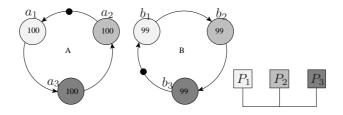

| 3.1  | Two application SDFGs A and B                                                          | 59  |

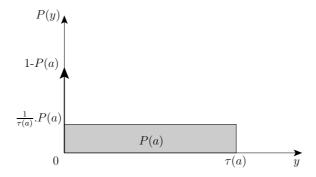

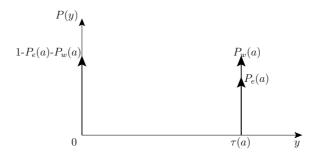

| 3.2  | Probability distribution of waiting time due to contention                             | 62  |

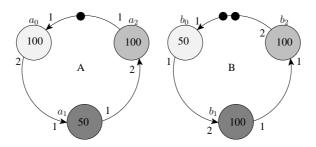

| 3.3  | SDFGs A and B with response times                                                      | 62  |

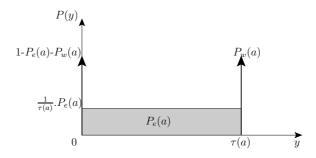

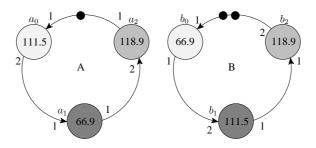

| 3.4  | Probability distribution of waiting time in iterative analysis                         | 72  |

| 3.5  | SDF application graphs A and B updated after iterative analysis                        | 73  |

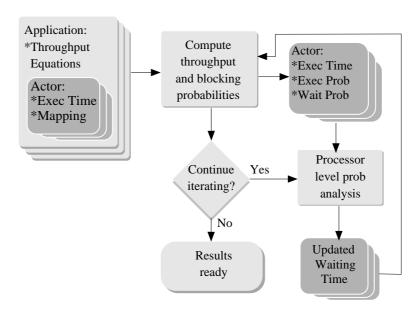

| 3.6  | Iterative probability method                                                           | 73  |

| 3.7  | Probability distribution of waiting time in conservative iterative analysis .          | 75  |

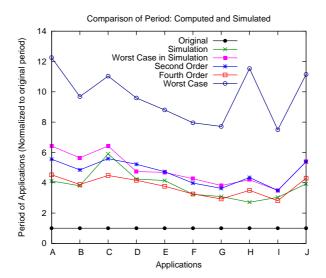

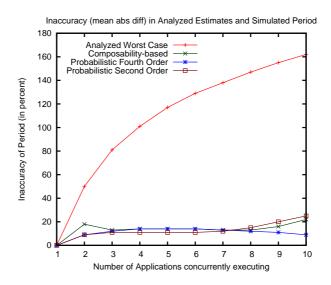

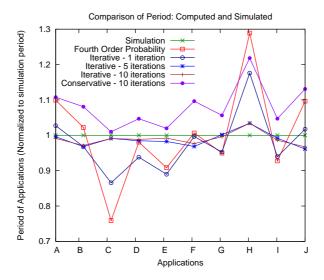

| 3.8  | Comparison of periods using different analysis techniques                              | 79  |

| 3.9  | Comparison of inaccuracy in application periods                                        | 80  |

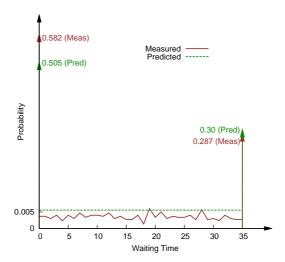

| 3.10 | Validating the probability distribution – actor $a2$ of application F                  | 81  |

| 3.11 | Validating the probability distribution – actor $a5$ of application G $$               | 81  |

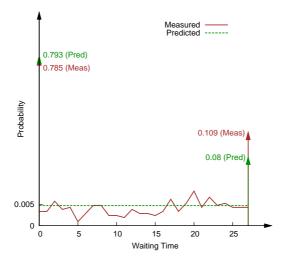

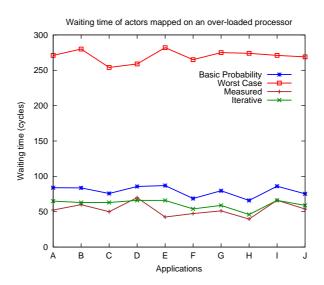

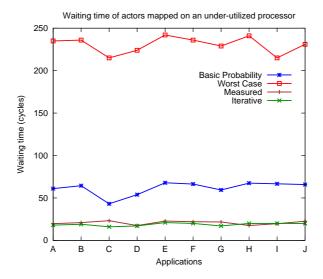

| 3.12 | Waiting time of actors mapped on a over-loaded processor                               | 84  |

| 3.13 | Waiting time of actors mapped on an under-utilized processor                           | 84  |

| 3.14 | Comparison of iterative analysis results with simulation                               | 85  |

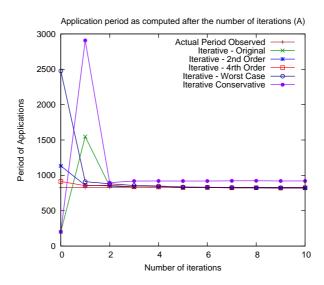

| 3.15 | Change in application $A$ period with number of iterations                             | 87  |

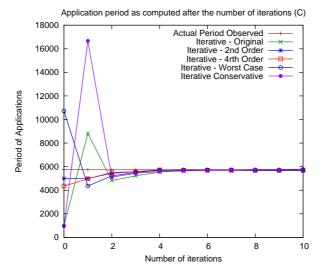

| 3.16 | Change in application $C$ period with number of iterations                             | 87  |

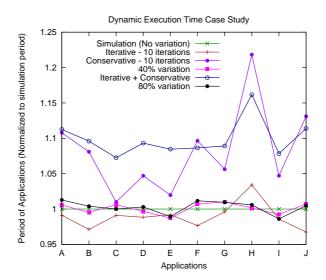

| 3.17 | Comparison of periods with variable execution times                                    | 89  |

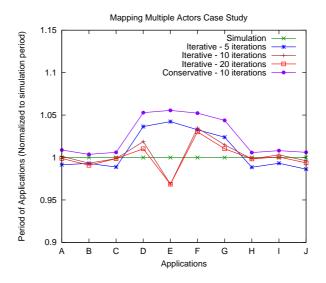

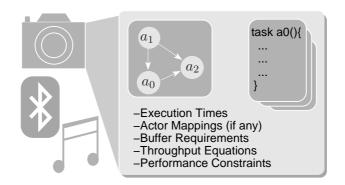

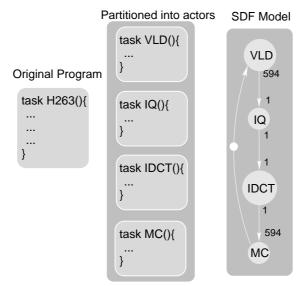

| 3.18 | Comparison of periods with multiple actors mapped                                      | 90  |

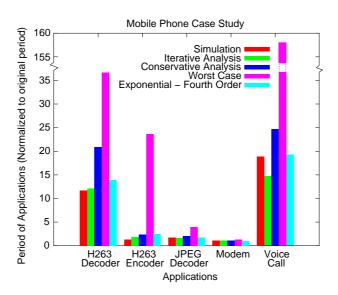

| 3.19 | Mobile phone case study results                                                        | 91  |

| 4.1  | Application(s) partitioning, and computation of their properties                       | 99  |

| 4.2  | The properties of H263 decoder application computed off-line                           | 101 |

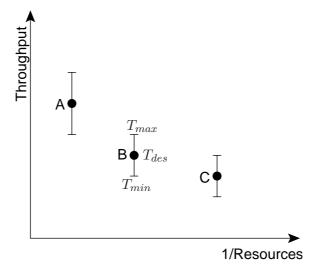

| 4.3  | Boundary specification for non-buffer critical applications                            | 101 |

| 4.4  | Boundary specification for buffer-critical applications                                | 102 |

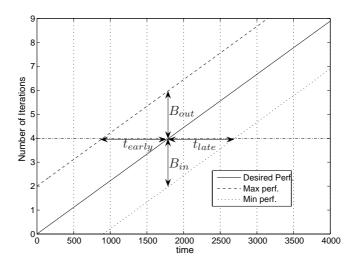

| 4.5  | On-line predictor for multiple application(s) performance $\ \ldots \ \ldots \ \ldots$ | 104 |

| 4.6  | Two applications running on same platform and sharing resources                        | 107 |

| 4.7  | Schedule of two concurrently executing applications                                    | 107 |

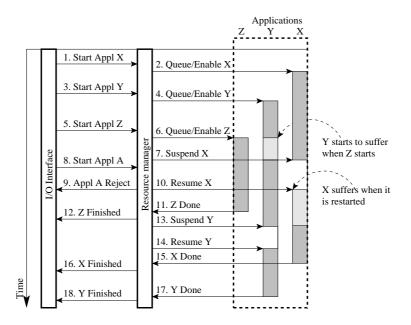

| 4.8  | Interaction diagram between various components in a system                             | 109 |

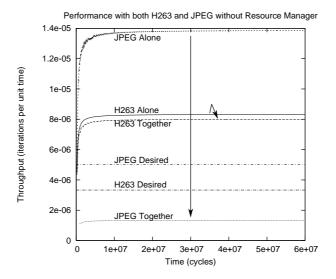

| 4.9  | Benefit of using a resource manager                                                    | 110 |

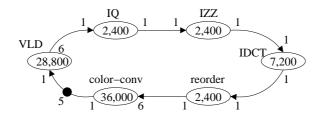

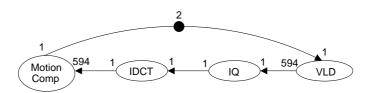

| 4.10 | SDF graph of JPEG decoder                                                             | 115 |

|------|---------------------------------------------------------------------------------------|-----|

| 4.11 | Performance of H263 and JPEG decoders                                                 | 116 |

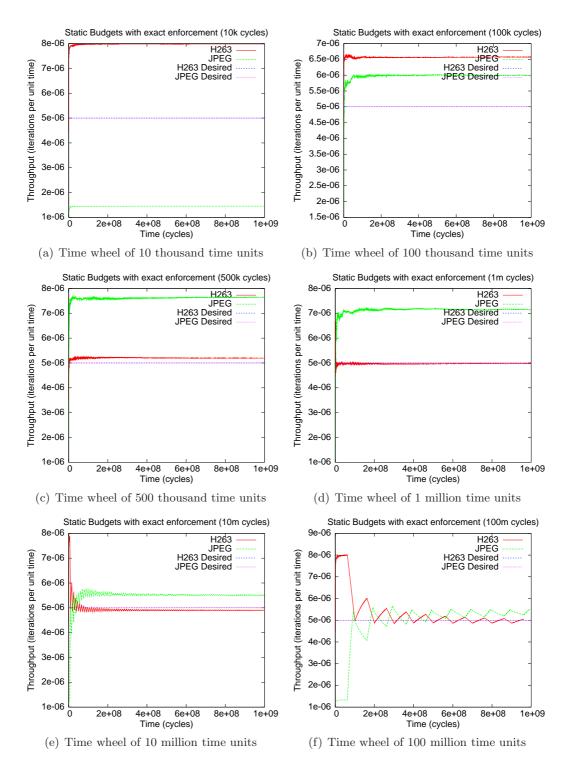

| 4.12 | Effect of using resource manager – coarse grain                                       | 117 |

| 4.13 | Effect of using resource manager – fine grain                                         | 118 |

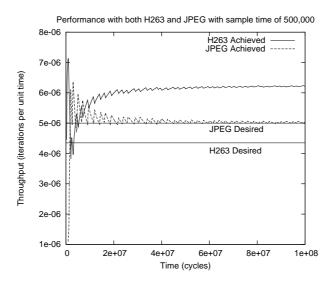

| 4.14 | The time wheel showing the ratio of time spent in different states. $\dots$           | 120 |

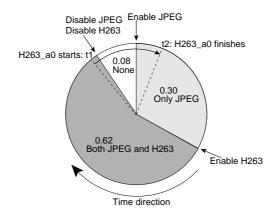

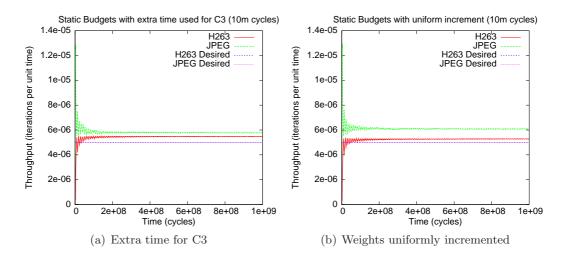

| 4.15 | Performance with static weights when extra time is used for C0                        | 121 |

| 4.16 | Performance with time-wheel of 10 million time units                                  | 122 |

| 5.1  | Ideal design flow for multiprocessor systems                                          | 126 |

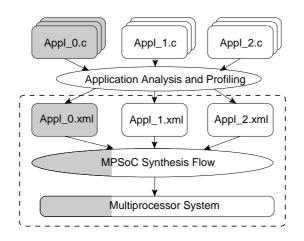

| 5.2  | MAMPS design flow                                                                     | 129 |

| 5.3  | Snippet of H263 application specification                                             | 130 |

| 5.4  | SDF graph for H263 decoder application                                                | 130 |

| 5.5  | The interface for specifying functional description of SDF-actors $\ \ldots \ \ldots$ | 131 |

| 5.6  | Example of specifying functional behaviour in C $$                                    | 132 |

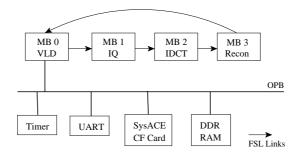

| 5.7  | Hardware topology of the generated design for H263                                    | 133 |

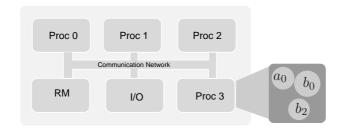

| 5.8  | Architecture with Resource Manager                                                    | 134 |

| 5.9  | Design flow to analyze an application and map it on hardware                          | 135 |

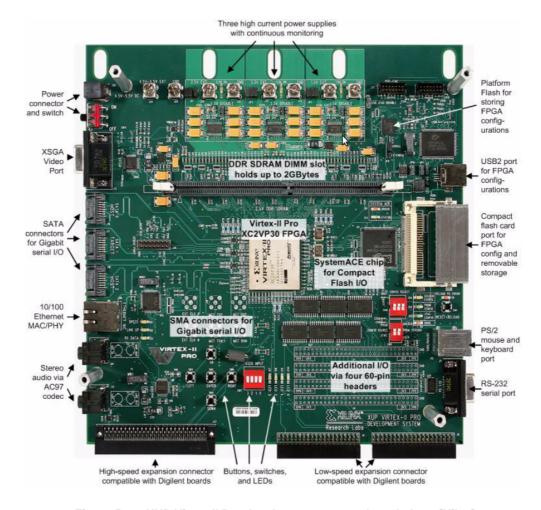

| 5.10 | XUP Virtex-II Pro development system board photo                                      | 136 |

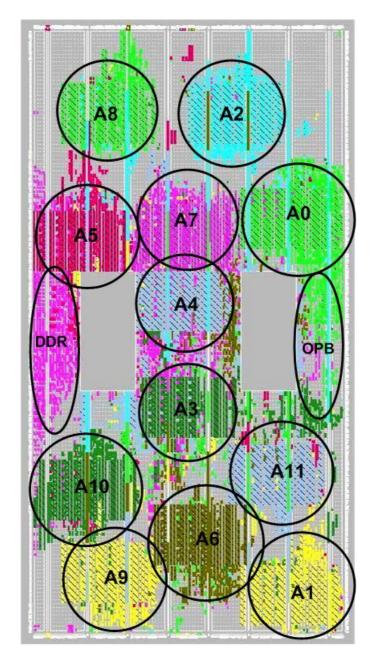

| 5.11 | Layout of the Virtex-II Pro FPGA with 12 Microblazes $\ \ldots \ \ldots \ \ldots$     | 137 |

| 5.12 | Effect of varying initial tokens on JPEG throughput                                   | 139 |

| 6.1  | Merging hardware for multiple use-cases                                               | 146 |

| 6.2  | The overall flow for analyzing multiple use-cases                                     | 148 |

| 6.3  | Putting applications, use-cases and feasible partitions in perspective                | 150 |

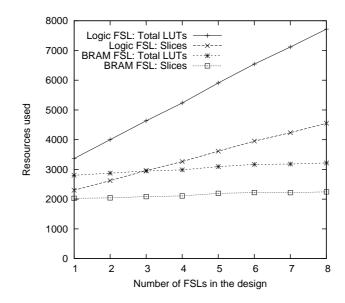

| 6.4  | Variation in LUTs and slices with increasing number of FSLs                           | 155 |

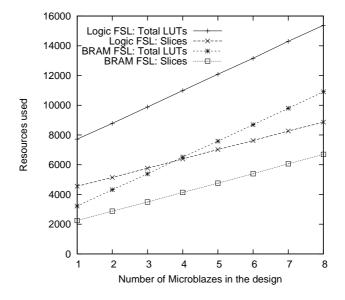

| 6.5  | Variation in LUTs and slices with increasing number of processors                     | 155 |

## Trends and Challenges in Multimedia Systems

Odyssey, released by Magnavox in 1972, was the world's first video game console [Ody72]. This supported a variety of games from tennis to baseball. Removable circuit cards consisting of a series of jumpers were used to interconnect different logic and signal generators to produce the desired game logic and screen output components respectively. It did not support sound, but it did come with translucent plastic overlays that one could put on the TV screen to generate colour images. This was what is called as the first generation video game console. Figure 1.1(a) shows a picture of this console, that sold about 330,000 units. Let us now forward to the present day, where the video game consoles have moved into the seventh generation. An example of one such console is the PlayStation3 from Sony [PS309] shown in Figure 1.1(b), that sold over 21 million units in the first two years of its launch. It not only supports sounds and colours, but is a complete media centre which can play photographs, video games, movies in high definitions in the most advanced formats, and has a large hard-disk to store games and movies. Further, it can connect to one's home network, and the entire world, both wireless and wired. Surely, we have come a long way in the development of multimedia systems.

A lot of progress has been made from both applications and system-design perspective.

The designers have a lot more resources at their disposal – more transistors to play with,

better and almost completely automated tools to place and route these transistors, and

(a) Odyssey, released in 1972 – an example from first generation video game console [Ody72].

(b) Sony PlayStation3 released in 2006 – an example from the seventh generation video game console [PS309]

Figure 1.1: Comparison of world's first video console with one of the most modern consoles.

much more memory in the system. However, a number of key challenges remains. With increasing number of transistors has come increased power to worry about. While the tools for the back-end (synthesizing a chip from the detailed system description) are almost completely automated, the front-end (developing a detailed specification of the system) of the design-process is still largely manual, leading to increased design time and error. While the cost of memory in the system has decreased a lot, its speed has little. Further, the demands from the application have increased even further. While the cost of transistors has declined, increased competition is forcing companies to cut cost, in turn forcing designers to use as few resources as necessary. Systems have evolving standards often requiring a complete re-design often late in the design-process. At the same time, the time-to-market is decreasing, making it even harder for the designer to meet the strict deadlines.

In this thesis, we present analysis, design and management techniques for multimedia multi-processor platforms. To cope with the complexity in designing such systems, a largely automated design-flow is needed that can generate systems from a high-level system description such that they are not error-prone and consume less time. This thesis presents a highly automated flow -MAMPS (Multi-Application Multi-Processor

Synthesis), that synthesizes multi-processor platforms for not just multiple applications, but multiple use-cases. (A use-case is defined as a combination of applications that may be active concurrently.) One of the key design automation challenges that remain is fast exploration of software and hardware implementation alternatives with accurate performance evaluation. Techniques are presented to merge multiple use-cases into one hardware design to minimize cost and design time, making it well-suited for fast design space exploration in MPSoC systems.

In order to contain the design-cost it is important to have a system that is neither hugely over-dimensioned, nor too limited to support the modern applications. While there are techniques to estimate application performance, they often end-up providing a high-upper bound such that the hardware is grossly over-dimensioned. We present a performance prediction methodology that can accurately and quickly predict the performance of multiple applications before they execute in the system. The technique is fast enough to be used at run-time as well. This allows run-time addition of applications in the system. An admission controller is presented using the analysis technique that admits incoming applications only if their performance is expected to meet their desired requirements. Further, a mechanism is presented to manage resources in a system. This ensures that once an application is admitted in the system, it can meet its performance constraints. The entire set-up is integrated in the MAMPS flow and available on-line for the benefit of research community.

This chapter is organized as follows. In Section 1.1 we take a closer look at the trends in multimedia systems from the applications perspective. In Section 1.2 we look at the trends in multimedia system design. Section 1.3 summarizes the key challenges that remain to be solved as seen from the two trends. Section 1.4 explains the overall design flow that is used in this thesis. Section 1.5 lists the key contributions that have led to this thesis, and their organization in this thesis.

#### 1.1 Trends in Multimedia Systems Applications

Multimedia systems are systems that use a combination of content forms like text, audio, video, pictures and animation to provide information or entertainment to the user. The video game console is just one example of the many multimedia systems that abound

around us. Televisions, mobile phones, home theatre systems, mp3 players, laptops, personal digital assistants, are all examples of multimedia systems. Modern multimedia systems have changed the way in which users receive information and expect to be entertained. Users now expect information to be available instantly whether they are traveling in the airplane, or sitting in the comfort of their houses. In line with users' demand, a large number of multimedia products are available. To satisfy this huge demand, the semiconductor companies are busy releasing newer embedded, and multimedia systems in particular, every few months.

The number of features in a multimedia system is constantly increasing. For example, a mobile phone that was traditionally meant to support voice calls, now provides video-conferencing features and streaming of television programs using 3G networks [HM03]. An mp3 player, traditionally meant for simply playing music, now stores contacts and appointments, plays photos and video clips, and also doubles up as a video game. Some people refer to it as the convergence of information, communication and entertainment [BMS96]. Devices that were traditionally meant for only one of the three things, now support all of them. The devices have also shrunk, and they are often seen as fashion accessories. A mobile phone that was not very *mobile* until about 15 years ago, is now barely thick enough to support its own structure, and small enough to hide in the smallest of ladies-purses.

Further, many of these applications execute concurrently on the platform in different combinations. We define each such combination of simultaneously active applications as a use-case. (It is also known as *scenario* in literature [PTB06].) For example, a mobile phone in one instant may be used to talk on the phone while surfing the web and downloading some Java application in the background. In another instant it may be used to listen to MP3 music while browsing JPEG pictures stored in the phone, and at the same time allow a remote device to access the files in the phone over a bluetooth connection. Modern devices are built to support different use-cases, making it possible for users to choose and use the desired functions concurrently.

Another trend we see is increasing and evolving standards. A number of standards for radio communication, audio and video encoding/decoding and interfaces are available. The multimedia systems often support a number of these. While a high-end TV supports a variety of video interfaces like HDMI, DVI, VGA, coaxial cable; a mobile phone supports

multiple bands like GSM 850, GSM 900, GSM 180 and GSM 1900, besides other wireless protocols like Infrared and Bluetooth [MMZ<sup>+</sup>02, KB97, Blu04]. As standards evolve, allowing faster and more efficient communication, newer devices are released in the market to match those specifications. The time to market is also reducing since a number of companies are in the market [JW04], and the consumers expect quick releases. A late launch in the market directly hurts the revenue of the company.

Power consumption has become a major design issue since many multimedia systems are hand-held. According to a survey by TNS research, two-thirds of mobile phone and PDA users rate two-days of battery life during active use as the most important feature of the ideal converged device of the future [TNS06]. While the battery life of portable devices has generally been increasing, the active use is still limited to a few hours, and in some extreme cases to a day. Even for other plugged multimedia systems, power has become a global concern with rising oil prices, and a growing awareness in people to reduce energy consumption.

To summarize, we see the following trends and requirements in the application of multimedia devices.

- An increasing number of multimedia devices are being brought to market.

- The number of applications in multimedia systems is increasing.

- The diversity of applications is increasing with convergence and multiple standards.

- The applications execute concurrently in varied combinations known as use-cases, and the number of these use-cases is increasing.

- The time-to-market is reducing due to increased competition, and evolving standards and interfaces.

- Power consumption is becoming an increasingly important concern for future multimedia devices.

#### 1.2 Trends in Multimedia Systems Design

A number of factors are involved in bringing the progress outlined above in multimedia systems. Most of them can be directly or indirectly attributed to the famous Moore's

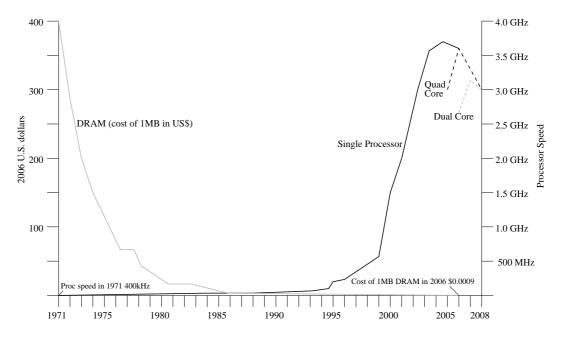

Figure 1.2: Increasing processor speed and reducing memory cost [Ade08].

law [Moo65], that predicted the exponential increase in transistor density as early as 1965. Since then, almost every measure of the capabilities of digital electronic devices – processing speed, transistor count per chip, memory capacity, even the number and size of pixels in digital cameras – are improving at roughly exponential rates. This has had two-fold impact. While on one hand, the hardware designers have been able to provide bigger, better and faster means of processing, on the other hand, the application developers have been working hard to utilize this processing power to its maximum. This has led them to deliver better and increasingly complex applications in all dimensions of life – be it medical care systems, airplanes, or multimedia systems.

When the first Intel processor was released in 1971, it had 2,300 transistors and operated at a speed of 400 kHz. In contrast, a modern chip has more than a billion transistors operating at more than 3 GHz [Int09]. Figure 1.2 shows the trend in processor speed and the cost of memory [Ade08]. The cost of memory has come down from close to 400 U.S. dollars in 1971, to less than a cent for 1 MB of dynamic memory (RAM). The processor speed has risen to over 3.5 GHz. Another interesting observation from this figure is the introduction of dual and quad core chips since 2005 onwards. This indicates the beginning of multi-processor era. As the transistor size shrinks, they can be clocked faster. However, this also leads to an increase in power consumption, in turn making chips hotter. Heat dissipation has become a serious problem forcing chip

manufacturers to limit the maximum frequency of the processor. Chip manufacturers are therefore, shifting towards designing multiprocessor chips operating at a lower frequency. Intel reports that *under-clocking* a single core by 20 percent saves half the power while sacrificing just 13 percent of the performance [Ros08]. This implies that if the work is divided between two processors running at 80 percent clock rate, we get 74 percent better performance for the same power. Further, the heat is dissipated at two points rather than one.

Further, sources like Berkeley and Intel are already predicting hundreds and thousands of cores on the same chip [ABC+06, Bor07] in the near future. All computing vendors have announced chips with multiple processor cores. Moreover, vendor road-maps promise to repeatedly double the number of cores per chip. These future chips are variously called *chip multiprocessors*, *multi-core chips*, and *many-core chips*, and the complete system as *multi-processor systems-on-chip* (MPSoC).

Following are the key benefits of using multi-processor systems.

- They consume less power and energy, provided sufficient task-level parallelism is present in the application(s). If there is insufficient parallelism, then some processors can be switched off.

- Multiple applications can be easily shared among processors.

- Streaming applications (typical multimedia applications) can be more easily pipelined.

- More robust against failure a Cell processor is designed with 8 cores (also known as SPE), but not all are always working.

- Heterogeneity can be supported, allowing better performance.

- It is more scalable, since higher performance can be obtained by adding more processors.

In order to evaluate the true benefits of multi-core processing, Amdahl's law [Amd67] has been augmented to deal with multi-core chips [HM08]. Amdahl's law is used to find the maximum expected improvement to an overall system when only a part of the system is improved. It states that if you enhance a fraction f of a computation by a speedup S,

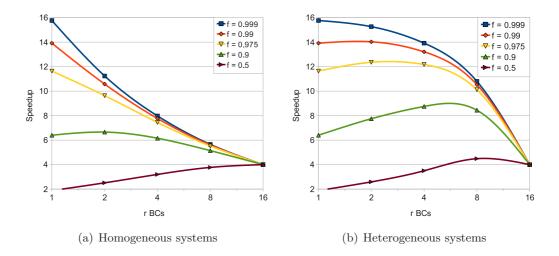

Figure 1.3: Comparison of speedup obtained by combining r smaller cores into a bigger core in homogeneous and heterogeneous systems [HM08].

the overall speedup is:

$$Speedup_{enhanced}(f, S) = \frac{1}{(1 - f) + \frac{f}{S}}$$

However, if the sequential part can be made to execute in less time by using a processor that has better sequential performance, the speedup can be increased. Suppose we can use the resources of r base-cores (BCs) to build one bigger core, which gives a performance of perf(r). If perf(r) > r i.e. super linear speedup, it is always advisable to use the bigger core, since doing so speeds up both sequential and parallel execution. However, usually perf(r) < r. When perf(r) < r, trade-off starts. Increasing core performance helps in sequential execution, but hurts parallel execution. If resources for n BCs are available on a chip, and all BCs are replaced with n/r bigger cores, the overall speedup is:

$$Speedup_{homogeneous}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f \cdot r}{perf(r) \cdot n}}$$

When heterogeneous multiprocessors are considered, there are more possibilities to redistribute the resources on a chip. If only r BCs are replaced with 1 bigger core, the overall speedup is:

$$Speedup_{heterogeneous}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f}{perf(r) + n - r}}$$

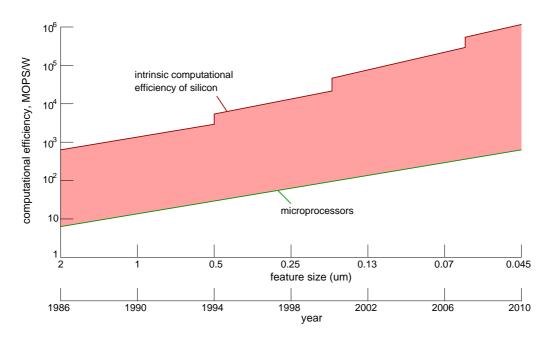

Figure 1.4: The intrinsic computational efficiency of silicon as compared to the efficiency of micro-processors.

Figure 1.3 shows the speedup obtained for both homogeneous and heterogeneous systems, for different fractions of parallelizable software. The x-axis shows the number of base processors that are combined into one larger core. In total there are resources for 16 BCs. The origin shows the point when we have a homogeneous system with only base-cores. As we move along the x-axis, the number of base-core resources used to make a bigger core are increased. In a homogeneous system, all the cores are replaced by a bigger core, while for heterogeneous, only one bigger core is built. The end-point for the x-axis is when all available resources are replaced with one big core. For this figure, it is assumed that  $perf(r) = \sqrt{r}$ . As can be seen, the corresponding speedup when using a heterogeneous system is much greater than homogeneous system. While these graphs are shown for only 16 base-cores, similar performance speedups are obtained for other bigger chips as well. This shows that using a heterogeneous system with several large cores on a chip can offer better speedup than a homogeneous system.

In terms of power as well, heterogeneous systems are better. Figure 1.4 shows the intrinsic computational efficiency of silicon as compared to that of microprocessors [Roz01]. The graph shows that the flexibility of general purpose microprocessors comes at the cost of increased power. The upper staircase-like line of the figure shows Intrinsic Computational Efficiency (ICE) of silicon according to an analytical model from [Roz01]  $(MOPS/W \approx \alpha/\lambda V_{DD}^2)$ ,  $\alpha$  is constant,  $\lambda$  is feature size, and  $V_{DD}$  is the supply volt-

age). The intrinsic efficiency is in theory bounded on the number of 32-bit mega (adder) operations that can be achieved per second per Watt. The performance discontinuities in the upper staircase-like line are caused by changes in the supply voltage from 5V to 3.3V, 3.3V to 1.5V, 1.5V to 1.2V and 1.2 to 1.0V. We observe that there is a gap of 2-to-3 orders of magnitude between the intrinsic efficiency of silicon and general purpose microprocessors. The accelerators – custom hardware modules designed for a specific task – come close to the maximum efficiency. Clearly, it may not always be desirable to actually design a hypothetically maximum efficiency processor. A full match between the application and architecture can bring the efficiency close to the hypothetical maximum. A heterogeneous platform may combine the flexibility of using a general purpose microprocessor and custom accelerators for compute intensive tasks, thereby minimizing the power consumed in the system.

Most modern multiprocessor systems are heterogeneous, and contain one or more application-specific processing elements (PEs). The CELL processor [KDH<sup>+</sup>05], jointly developed by Sony, Toshiba and IBM, contains up to nine-PEs – one general purpose PowerPC [WS94] and eight Synergistic Processor Elements (SPEs). The PowerPC runs the operating system and the control tasks, while the SPEs perform the compute-intensive tasks. This Cell processor is used in PlayStation3 described above. STMicroelectronics Nomadik contains an ARM processor and several Very Long Instruction Word (VLIW) DSP cores [AAC<sup>+</sup>03]. Texas Instruments OMAP processor [Cum03] and Philips Nexperia [OA03] are other examples. Recently, many companies have begun providing configurable cores that are targeted towards an application domain. These are known as Application Specific Instruction-set Processors (ASIPs). These provide a good compromise between general-purpose cores and ASICs. Tensilica [Ten09, Gon00] and Silicon Hive [Hiv09, Hal05] are two such examples, which provide the complete toolset to generate multiprocessor systems where each processor can be customized towards a particular task or domain, and the corresponding software programming toolset is automatically generated for them. This also allows the re-use of IP (Intellectual Property) modules designed for a particular domain or task.

Another trend that we see in multimedia systems design is the use of *Platform-Based Design* paradigm [SVCBS04, KMN<sup>+</sup>00]. This is becoming increasingly popular due to three main factors: (1) the dramatic increase in non-recurring engineering cost

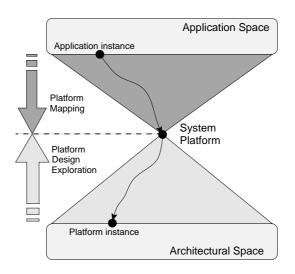

Figure 1.5: Platform-based design approach - system platform stack.

due to mask making at the circuit implementation level, (2) the reducing time to market, and (3) streamlining of industry – chip fabrication and system design, for example, are done in different companies and places. This paradigm is based on segregation between the system design process, and the system implementation process. The basic tenets of platform-based design are identification of design as meeting-in-the-middle process, where successive refinements of specifications meet with abstractions of potential implementations, and the identification of precisely defined abstraction layers where the refinement to the subsequent layer and abstraction processes take place [SVCBS04]. Each layer supports a design stage providing an opaque abstraction of lower layers that allows accurate performance estimations. This information is incorporated in appropriate parameters that annotate design choices at the present layer of abstraction. These layers of abstraction are called platforms. For MPSoC system design, this translates into abstraction between the application space and architectural space that is provided by the systemplatform. Figure 1.5 captures this system-platform that provides an abstraction between the application and architecture space. This decouples the application development process from the architecture implementation process.

We further observe that for high-performance multimedia systems (like cell-processing engine and graphics processor), non-preemptive systems are preferred over preemptive ones for a number of reasons [JSM91]. In many practical systems, properties of device hardware and software either make the preemption impossible or prohibitively expensive due to extra hardware and (potential) execution time needed. Further, non-preemptive

scheduling algorithms are easier to implement than preemptive algorithms and have dramatically lower overhead at run-time [JSM91]. Further, even in multi-processor systems with preemptive processors, some processors (or co-processors/ accelerators) are usually non-preemptive; for such processors non-preemptive analysis is still needed. It is therefore important to investigate non-preemptive multi-processor systems.

To summarize, the following trends can be seen in the design of multimedia systems.

- *Increase in system resources:* The resources available for disposal in terms of processing and memory are increasing exponentially.

- *Use of multiprocessor systems:* Multi-processor systems are being developed for reasons of power, efficiency, robustness, and scalability.

- *Increasing heterogeneity:* With the re-use of IP modules and design of custom (co-) processors (ASIPs), heterogeneity in MPSoCs is increasing.

- *Platform-based design:* Platform-based design methodology is being employed to improve the re-use of components and shorten the development cycle.

- Non-preemptive processors: Non-preemptive processors are preferred over preemptive to reduce cost.

#### 1.3 Key Challenges in Multimedia Systems Design

The trends outlined in the previous two sections indicate the increasing complexity of modern multimedia systems. They have to support a number of concurrently executing applications with diverse resource and performance requirements. The designers face the challenge of designing such systems at low cost and in short time. In order to keep the costs low, a number of design options have to be explored to find the optimal or near-optimal solution. The performance of applications executing on the system have to be carefully evaluated to satisfy user-experience. Run-time mechanisms are needed to deal with run-time addition of applications. In short, following are the major challenges that remain in the design of modern multimedia systems, and are addressed in this thesis.

• Multiple use-cases: Analyzing performance of multiple applications executing concurrently on heterogeneous multi-processor platforms. Further, this number of usecases and their combinations is exponential in the number of applications present in the system. (Analysis and Design)

- Design and Program: Systematic way to design and program multi-processor platforms. (Design)

- Design space exploration: Fast design space exploration technique. (Analysis and Design)

- Run-time addition of applications: Deal with run-time addition of applications keep the analysis fast and composable, adapt the design (-process), manage the resources at run-time (e.g. admission controller). (Analysis, Design and Management)

- Meeting performance constraints: A good mechanism for keeping performance of all applications executing above the desired level. (Design and Management)

#### 1.3.1 Analysis

We present a novel probabilistic performance prediction  $(P^3)$  algorithm for predicting performance of multiple applications executing on multi-processor platforms. The algorithm predicts the time that tasks have to spend during contention phase for a resource. The computation of accurate waiting time is the key to performance analysis. When applications are modeled as synchronous dataflow (SDF) graphs, their performance on a (multi-processor) system can be easily computed when they are executing in isolation (provided we have a good model). When they execute concurrently, depending on whether the used scheduler is static or dynamic, the arbitration on a resource is either fixed at design-time or chosen at run-time respectively (explained in more detail in Chapter 2). In the former case, the execution order can be modeled in the graph, and the performance of the entire application can be determined. The contention is therefore modeled as dependency edges in the SDF graph. However, this is more suited for static applications. For dynamic applications such as multimedia, dynamic scheduler is more suitable. For dynamic scheduling approaches, the contention has to be modeled as waiting time for a task, which is added to the execution time to give the total response time. The performance can be determined by computing the performance (throughput) of this resulting SDF graph. With lack of good techniques for accurately predicting the time

spent in contention, designers have to resort to worst-case waiting time estimates, that lead to over-designing the system and loss of performance. Further, those approaches are not scalable and the over-estimate increases with the number of applications.

In this thesis, we present a solution to performance prediction, with easy analysis. We highlight the issue of *composability* i.e. mapping and analysis of performance of multiple applications on a multiprocessor platform in isolation, as far as possible. This limits computational complexity and allows high dynamism in the system. While in this thesis, we only show examples with processor contention, memory and network contention can also be easily modeled in SDF graph as shown in [Stu07]. The technique presented here can therefore be easily extended to other system components as well. The analysis technique can be used both at design-time and run-time.

We would ideally want to analyze each application in isolation, thereby reducing the analysis time to a linear function, and still reason about the overall behaviour of the system. One of the ways to achieve this, would be complete *virtualization*. This essentially implies dividing the available resources by the total number of applications in the system. The application would then have exclusive access to its share of resources. For example, if we have 100 MHz processors and a total of 10 applications in the system, each application would get 10 MHz of processing resource. The same can be done for communication bandwidth and memory requirements. However this gives two main problems. When fewer than 10 tasks are active, the tasks will not be able to exploit the extra available processing power, leading to wastage. Secondly, the system would be grossly over-dimensioned when the peak requirements of each application are taken into account, even though these peak requirements of applications may rarely occur and never be at the same time.

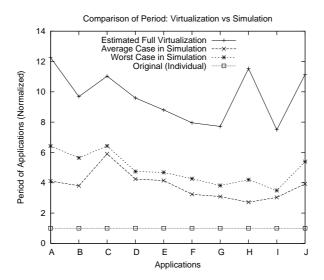

Figure 1.6 shows this disparity in more detail. The graph shows the period of ten streaming multimedia applications (inverse of throughput) when they are run concurrently. The period is the time taken for one iteration of the application. The period has been normalized to the original period that is achieved when each application is running in isolation. If full virtualization is used, the period of applications increases to about ten times on average. However, without virtualization, it increases only about five times. A system which is built with full-virtualization in mind, would therefore, utilize only 50% of the resources. Thus, throughput decreases with complete virtualization.

Figure 1.6: Application performance as obtained with full virtualization in comparison to simulation.

Therefore, a good analysis methodology for a modern multimedia system

- provides accurate performance results, such that the system is not over-dimensioned,

- is fast in order to make it usable for run-time analysis, and to explore a large number of design-points quickly, and

- easily handles a large number of applications, and is composable to allow run-time addition of new applications.

It should be mentioned that often in applications, we are concerned with the long-term throughput and not the individual deadlines. For example, in the case of JPEG application, we are not concerned with decoding of each macro-block, but the whole image. When browsing the web, individual JPEG images are not as important as the entire page being ready. Thus, for the scope of this thesis, we consider long-term throughput i.e. cumulative deadline for a large number of iterations, and not just one. However, having said that it is possible to adapt the analysis to individual deadlines as well. It should be noted that in such cases, the estimates for individual iteration may be very pessimistic as compared to long-term throughput estimates.

#### 1.3.2 Design

As is motivated earlier, modern systems need to support many different combinations of applications – each combination is defined as a *use-case* – on the same hardware. With

reducing time-to-market, designers are faced with the challenge of designing and testing systems for multiple use-cases quickly. Rapid prototyping has become very important to easily evaluate design alternatives, and to explore hardware and software alternatives quickly. Unfortunately, lack of automated techniques and tools implies that most work is done by hand, making the design-process error-prone and time-consuming. This also limits the number of design-points that can be explored. While some efforts have been made to automate the flow and raise the abstraction level, these are still limited to single-application designs.

Modern multimedia systems support not just multiple applications, but also multiple use-cases. The number of such potential use-cases is exponential in the number of applications that are present in the system. The high demand of functionalities in such devices is leading to an increasing shift towards developing systems in software and programmable hardware in order to increase design flexibility. However, a single configuration of this programmable hardware may not be able to support this large number of use-cases with low cost and power. We envision that future complex embedded systems will be partitioned into several configurations and the appropriate configuration will be loaded into the reconfigurable platform (defined as a piece of hardware that can be configured at run-time to achieve the desired functionality) on the fly as and when the use-cases are requested. This requires two major developments at the research front: (1) a systematic design methodology for allowing multiple use-cases to be merged on a single hardware configuration, and (2) a mechanism to keep the number of hardware configurations as small as possible. More hardware configurations imply a higher cost since the configurations have to be stored in the memory, and also lead to increased switching in the system.

In this thesis, we present *MAMPS* (Multi-Application Multi-Processor Synthesis) – a design-flow that generates the entire MPSoC for multiple use-cases from application(s) specifications, together with corresponding software projects for automated synthesis. This allows the designers to quickly traverse the design-space and evaluate the performance on real hardware. Multiple use-cases of applications are supported by merging such that minimal hardware is generated. This further reduces the time spent in system-synthesis. When not all use-cases can be supported with one configuration, due to the hardware constraints, multiple configurations of hardware are automatically generated,

while keeping the number of partitions low. Further, an area estimation technique is provided that can accurately predict the area of a design and decide whether a given system-design is feasible within the hardware constraints or not. This helps in quick evaluation of designs, thereby making the DSE faster.

Thus, the design-flow presented in this thesis is unique in a number of ways: (1) it supports multiple use-cases on one hardware platform, (2) estimates the area of design before the actual synthesis, allowing the designer to choose the right device, (3) merges and partitions the use-cases to minimize the number of hardware configurations, and (4) it allows fast DSE by automating the design generation and exploration process.

The work in this thesis is targeted towards heterogeneous multi-processor systems. In such systems, the mapping is largely determined by the capabilities of processors and the requirements of different tasks. Thus, the freedom in terms of mapping is rather limited. For homogeneous systems, task mapping and scheduling are coupled by performance requirements of applications. If for a particular scheduling policy, the performance of a given application is not met, mapping may need to be altered to ensure that the performance improves. As for the scheduling policy, it is not always possible to steer them at run-time. For example, if a system uses first-come-first-serve scheduling policy, it is infeasible to change it to a fixed priority schedule for a short time, since it requires extra hardware and software. Further, identifying the ideal mapping given a particular scheduling policy already takes exponential time in the total number of tasks. When the scheduling policy is also allowed to vary independently on processors, the time taken increases even more.

#### 1.3.3 Management

Resource management, i.e. managing all the resources present in the multiprocessor system, is similar to the task of an operating system on a general purpose computer. This includes starting up of applications, and allocating resources to them appropriately. In the case of a multimedia system (or embedded systems, in general), a key difference from a general purpose computer is that the applications (or application domain) is generally known, and the system can be optimized for them. Further, most decisions can be already taken at design-time to save the cost at run-time. Still, a complete design-time analysis is becoming increasingly harder due to three major reasons: 1) little may

be known at design-time about the applications that need to be used in future, e.g. a navigation application like Tom-Tom may be installed on the phone after-wards, 2) the precise platform may also not be known at design time, e.g. some cores may fail at run-time, and 3) the number of design-points that need to be evaluated is prohibitively large. A run-time approach can benefit from the fact that the exact application mix is known, but the analysis has to be fast enough to make it feasible.

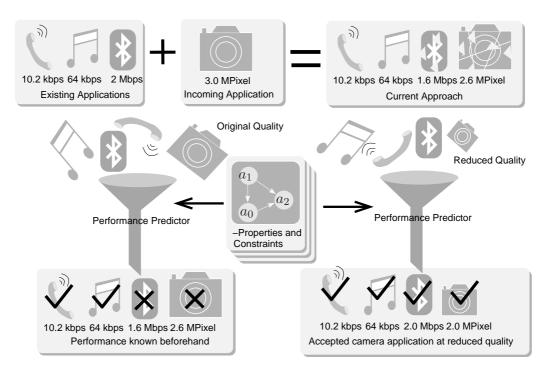

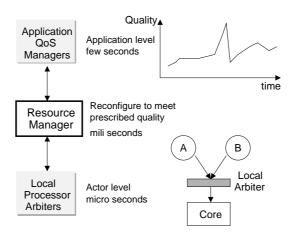

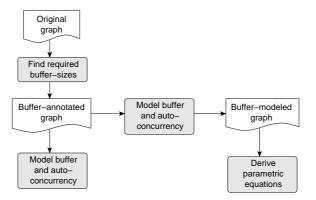

In this thesis, we present a hybrid approach for designing systems with multiple applications. This splits the management tasks into off-line and on-line. The time-consuming application specific computations are done at design-time and for each application independent from other applications, and the use-case specific computations are performed at run-time. The off-line computation includes tasks like application-partitioning, application-modeling, determining the task execution times, determining their maximum throughput, etc. Further, parametric equations are derived that allow throughput computation of tasks with varying execution times. All this analysis is time-consuming and best carried out at design-time. Further, in this part no information is needed from the other applications and it can be performed in isolation. This information is sufficient enough to let a run-time manager determine the performance of an application when executing concurrently on the platform with other applications. This allows easy addition of applications at run-time. As long as all the properties needed by the run-time resource manager are derived for the new application, the application can be treated as all the other applications that are present in the system.

At run-time, when the resource manager needs to decide, for example, which resources to allocate to an incoming application, it can evaluate the performance of applications with different allocations and determine the best option. In some cases, multiple quality levels of an application may be specified, and at run-time the resource manager can choose from one of those levels. This functionality of the resource manager is referred to as admission control. The manager also needs to ensure that applications that are admitted do not take more resources than allocated, and starve the other applications executing in the system. This functionality is referred to as budget enforcement. The manager periodically checks the performance of all applications, and when an application does better than the required level, it is suspended to ensure that it does not take more resources than needed. For the scope of this thesis, the effect of task migration is not

considered since it is orthogonal to our approach.

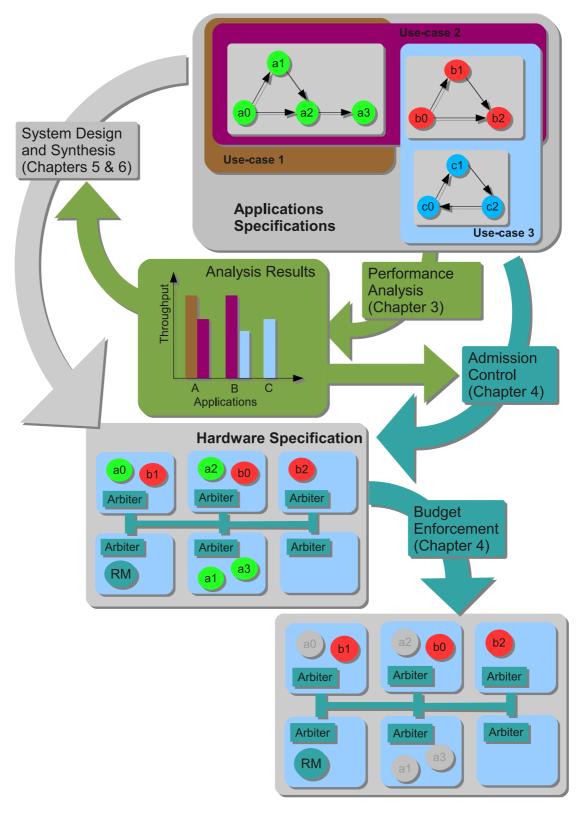

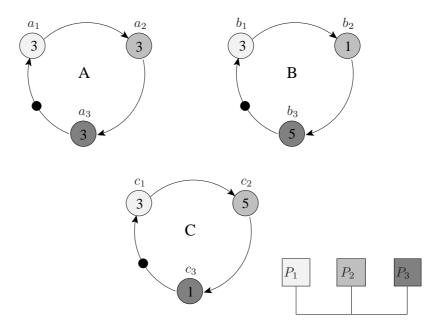

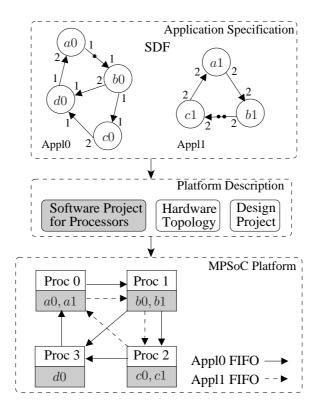

#### 1.4 Design Flow

Figure 1.7 shows the design-flow that is used in this thesis. Specifications of applications are provided to the designer in the form of Synchronous Dataflow (SDF) graphs [SB00, LM87]. These are often used for modeling multimedia applications. This is further explained in Chapter 2. As motivated earlier in the chapter, modern multimedia systems support a number of applications in varied combinations defined as use-case. Figure 1.7 shows three example applications – A, B and C, and three use-cases with their combinations. For example, in *Use-case 2* applications A and B execute concurrently. For each of these use-cases, the performance of all active applications is analyzed. When a suitable mapping to hardware is to be explored, this step is often repeated with different mappings, until the desired performance is obtained. A probabilistic mechanism is used to estimate the average performance of applications. This performance analysis technique is presented in Chapter 3.

When a satisfactory mapping is obtained, the system can be designed and synthesized automatically using the **system-design** approach presented in Chapter 5. **Multiple use-cases** need to be merged on to one hardware design such that a new hardware configuration is not needed for every use-case. This is explained in Chapter 6. When it is not possible to merge all use-cases due to resource constraints (slices in an FPGA, for example), use-cases need to be partitioned such that the number of hardware partitions are kept to a minimum. Further, a fast area estimation method is needed that can quickly identify whether a set of use-cases can be merged due to hardware constraints. Trying synthesis for every use-case combination is too time-consuming. A novel area-estimation technique is needed that can save precious time during design space exploration. This is explained in Chapter 6.

Once the system is designed, a run-time mechanism is needed to ensure that all applications can meet their performance requirements. This is accomplished by using a resource manager (RM). Whenever a new application is to be started, the manager checks whether sufficient resources are available. This is defined as **admission-control**. The probabilistic analysis is used to predict the performance of applications when the new

Figure 1.7: Complete design flow starting from applications specifications and ending with a working hardware prototype on an FPGA.

application is admitted in the system. If the expected performance of all applications is above the minimum desired performance then the application is started, else a lower quality of incoming application is tried. The resource manager also takes care of **budget-enforcement** i.e. ensuring applications use only as much resources as assigned. If an application uses more resources than needed and starves other applications, it is suspended. Figure 1.7 shows an example where application A is suspended. Chapter 4 provides details of two main tasks of the RM – admission control and budget-enforcement.

The above flow also allows for run-time addition of applications. Since the performance analysis presented is fast, it is done at run-time. Therefore, any application whose properties have been derived off-line can be used, if there are enough resources present in the system. This is explained in more detail in Chapter 4.

#### 1.5 Key Contributions and Thesis Overview

Following are some of the major contributions that have been achieved during the course of this research and have led to this thesis.

- A detailed analysis of why estimating performance of multiple applications executing on a heterogeneous platform is so difficult. This work was published in [KMC<sup>+</sup>06], and an extended version is published in a special issue of the Journal of Systems Architecture containing the best papers of the Digital System Design conference [KMT<sup>+</sup>08].