# STRAIN ENGINEERING FOR ADVANCED TRANSISTOR STRUCTURE

TAN KIAN MING

NATIONAL UNIVERSITY OF SINGAPORE 2008

### STRAIN ENGINEERING FOR ADVANCED TRANSISTOR STRUCTURE

TAN KIAN MING

(B. ENG. (HONS.)), NUS (M. ENG.), NUS

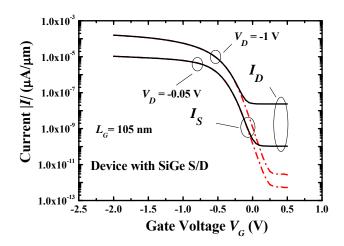

### A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTING ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2008

### Acknowledgements

First and foremost, I would like to thank my supervisor, Dr. Yeo Yee-Chia who has provided much support and encouragement throughout the course of my Ph.D candidature. I have benefited a lot from the numerous discussions that we have. I would also like to thank all my co-supervisors, A/P Yoo Won Jong, Dr Lap Chan, Dr Narayanan Balasubramanian and Dr Patrick Lo who have always been generous in helping me in whatever ways they can. In addition, I will also like to thank A/P Ganesh S. Samudra for giving his advice and suggestions during our research group meetings. Special thanks to Dr Yang Mingchu for constantly provide the support and help, which we need in using the FCVA system.

My work is mainly done in 2 laboratories in this period of time, Semiconductor Processing Technology (SPT) Lab at the Institute of Microelectronics (IME), and the Silicon Nano Device Lab (SNDL) at the National University of Singapore (NUS). I am very grateful to all the staffs in both laboratories as they have provided assistance in one way or another which made my work possible.

I have also learnt a lot from the friends that I have made from Chartered, SNDL and IME. In particularly, I am extremely thankful that the development of FinFET process flow is done together with Tsung-Yang (Jason). We practically started the FinFET process from scratch and spend countless night in the cleanroom developing all the necessary process steps.

I will also like to express my deepest gratitude to my family, especially my parents who have been very supportive ever since I started my graduate studies

i

from MASTER to Ph.D. It has been a very long journey, and I truly hope I can spend more time with them in the future.

## **Table of Contents**

| Acknowled<br>Table of Co |                                                                                                      | i         |

|--------------------------|------------------------------------------------------------------------------------------------------|-----------|

| Abstract                 | intents                                                                                              | 111<br>vi |

| List of Figu             | res                                                                                                  | viii      |

| List of Tabl             |                                                                                                      | xvii      |

| List of Sym              | bols                                                                                                 | XVIII     |

| Chapter 1.               | Introduction                                                                                         | 1         |

| 1.1 Backgro              | und                                                                                                  | 1         |

| 1.2 Objectiv             | e of Research                                                                                        | 7         |

| 1.3 Organiza             | ation of Thesis                                                                                      | 7         |

| 1.4 Referen              | ces                                                                                                  | 9         |

| Chapter 2.               | Drive Current Enhancement in FinFETs<br>Using Gate-Induced Stress                                    | 14        |

| 2.1 Backgro              | und                                                                                                  | 14        |

| 2.2 Device I             | Fabrication                                                                                          | 15        |

| 2.3 Results a            | and Discussion                                                                                       | 19        |

| 2.4 Summar               | у                                                                                                    | 24        |

| 2.5 Reference            | ces                                                                                                  | 25        |

| Chapter 3.               | Plasma Etching of Gate Electrode and Gate-Stringer<br>for the Fabrication of Nanoscale Multiple-Gate | 27        |

| 3.1 Backgro              | und                                                                                                  | 27        |

| 3.2 Experim              | ent                                                                                                  | 28        |

| 3.3 Results a            | and Discussion                                                                                       | 29        |

| 3.4 Summar               | У                                                                                                    | 34        |

| 3.5 Reference            | ces                                                                                                  | 35        |

| Chapter 4.               | Strained P-channel FinFET with Enhanced SiGe<br>S/D Stressor                                         | 37        |

| 4.1 Sub-30 r             | nm Strained p-Channel FinFETs with Condensed                                                         |           |

| SiGe So                  | urce/Drain Stressors                                                                                 | 37        |

| 4.1.1 Ba                 | ckground                                                                                             | 37        |

| 4.1.2 Device Fabrication                                                                                            | 39 |

|---------------------------------------------------------------------------------------------------------------------|----|

| 4.1.3 Ge Condensation Process                                                                                       | 41 |

| 4.1.4 Results and Discussion                                                                                        | 45 |

| 4.1.5 Summary                                                                                                       | 48 |

| 4.2 Novel Extended-Pi Shaped Silicon-Germanium (eП-SiGe)                                                            |    |

| Source/Drain Stressors for Strain and Performance Enhancement                                                       |    |

| in P-Channel FinFET                                                                                                 | 48 |

| 4.2.1. Background                                                                                                   | 48 |

| 4.2.2 Device Fabrication                                                                                            | 49 |

| 4.2.3 Results and Discussion                                                                                        | 51 |

| 4.2.4. Summary                                                                                                      | 58 |

| 4.3 References                                                                                                      | 59 |

| Chapter 5. Diamond-Like Carbon (DLC): A New Liner Stressor<br>with Very High Intrinsic Compressive Stress (> 6 GPa) | 62 |

| 5.1 Integration of DLC on P-Channel SOI Transistors for Strain and                                                  |    |

| Device Performance Enhancement                                                                                      | 62 |

| 5.1.1 Background                                                                                                    | 62 |

| 5.1.2 Properties of Diamond-Like Carbon                                                                             | 64 |

| 5.1.3 Device Fabrication                                                                                            | 69 |

| 5.1.4 Results and Discussion                                                                                        | 70 |

| 5.1.5 Summary                                                                                                       | 75 |

| 5.2 Integration of DLC on P-Channel Multiple-Gate Transistors for                                                   |    |

| Advanced Device Scaling                                                                                             | 76 |

| 5.2.1 Background                                                                                                    | 76 |

| 5.2.2 Device Fabrication                                                                                            | 78 |

| 5.2.3 Results and Discussion                                                                                        | 79 |

| 5.2.3.1 Impact of DLC Stressed Liner on FinFET Devices with                                                         |    |

| Si S/D Raised with Different Thicknesses                                                                            | 83 |

| 5.2.4. Summary                                                                                                      | 85 |

| 5.3 References                                                                                                      | 86 |

| Chapter 6. Diamond-like Carbon Liner: Integration with SiGe<br>Source/Drain for Multiple-Stressors Effect           | 91 |

| 6.1 Background                                                      | 91  |

|---------------------------------------------------------------------|-----|

| 6.2 Effects of Deposition Conditions on the Intrinsic Stress of DLC |     |

| 6.3 Device Fabrication                                              | 94  |

| 6.4 Results and Discussion                                          | 96  |

| 6.4.1 Integration of DLC with SiGe Source/Drain Stressors           |     |

| in Planar Transistors                                               | 96  |

| 6.4.2 Impact of a Recessed SiGe S/D on the Strain transfer of DLC   | 101 |

| 6.5 Summary                                                         |     |

| 6.6 References                                                      | 105 |

| Chapter 7. Conclusion and Future Work                               | 108 |

| 7.1 Conclusion                                                      | 108 |

| 7.2 Future Work                                                     |     |

| 7.3 References                                                      |     |

| APPEDNIX: Publication List                                          | 114 |

### Abstract

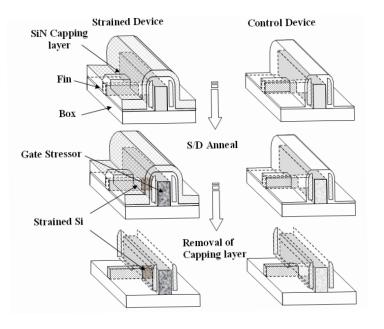

With the aggressive scaling of device dimensions to meet performance requirements, various techniques have been proposed to improve device performance and among them, strained silicon technology has been very successful and is currently implemented and used in manufacturing. However, the scaling of technologies node is still on-going and researchers from all over the world are still trying to push silicon to its limit. Advanced transistors structure like FinFET or multiple-gate devices are also introduced to control the short channel effects which increase significantly as the physical gate length approach sub-50 nm. In this thesis, various approaches are also explored to enhance the device performance for sub-32 nm technology node. The effect of having a SiN capping layer on a tantalum nitride (TaN) metal gate FinFET during source/drain anneal was studied. Enhancement in drive current is observed when compared to a similar but un-capped FinFET device. The increased in drive current is attributed to the constraint in the expansion of TaN which result in a residual stress being induced in the channel that improve electron mobility. Therefore, strain effect due to the introduction of new materials for metal gate and high-k gate dielectric should be taken into considerations

SiGe source/drain (S/D) which is lattice mismatched to Si has been used to induce compressive stress in the channel to enhance the performance of p-channel transistors. Recently, this has also been applied on FinFET device demonstrating larger drive current performance. Improving the performance of FinFET device with SiGe S/D is also investigated in thesis. Ge condensation is adopted to form a FinFET device with an embedded SiGe S/D showing better performance than the control device. In addition, a novel extended-pi ( $\Pi$ ) shaped SiGe S/D stressor is also formed for the first time on FinFET device which shows an increase in drive current over FinFET with pi-shaped SiGe S/D stressor, attributed to the enhancement of strain effect and lower series resistance.

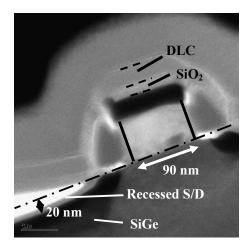

With the decrease in gate pitch, strain induced in the channel by highly stressed contact etch stop liner (CESL) also decreases. Therefore, it will be advantageous that the intrinsic stress of CESL can be tuned to a much higher level. In this thesis, a new CESL liner material, diamond-like carbon (DLC) is introduced which has a much greater intrinsic compressive stress than SiN ever reported. The properties of DLC are characterized and enhancement in drive current on both p-channel SOI and FinFET devices are demonstrated experimentally. In addition, studies of DLC on bulk planar device having an embedded SiGe were also made and it is observed that the strain effect couple to the channel can be larger when the DLC stressed liner is integrated on to a device with an intentionally recessed S/D profile. The efficiency of the transfer stress is higher with the closer proximity of the DLC stress liner to the channel.

#### **List of Figures**

- Fig. 2.3 SEM images of the pattern gate line running across the fin. Resist trimming were also used here to achieve small gate length......16

- Fig. 2.5 (a) SEM image showing a FinFET structure with an improved gate profile. The inset shows an image of the fin profile. (b) SEM image of the FinFET structure after spacer formation.....18

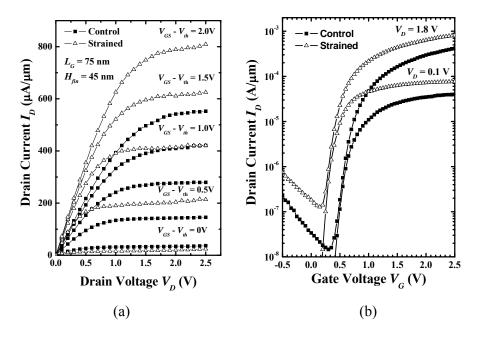

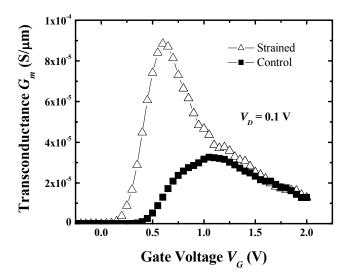

| Fig. 2.7 | (a) $I_D$ - $V_D$ characteristics of control and strained FinFET devices at various gate over-drives. The strained FinFET has significantly higher drive current. (b) Subthreshold characteristics of the control and strained FinFET devices at $V_D = 0.1$ V and $V_D = 1.8$ V                                                                                                                                           |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.8 | Comparison of transconductance of the strained and control devices. The higher peak transconductance seen for the strained device, indicate a higher mobility                                                                                                                                                                                                                                                              |

| Fig. 3.1 | Illustration of the various steps and the requirement in a typical gate etch process                                                                                                                                                                                                                                                                                                                                       |

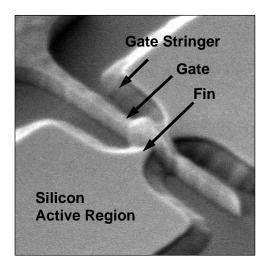

| Fig. 3.2 | SEM image of a FinFET device formed without an extended gate over-etch step, showing the existence of an uncleared gate stringer surrounding the active region. This leads to increased overlap capacitance and reduced circuit speed                                                                                                                                                                                      |

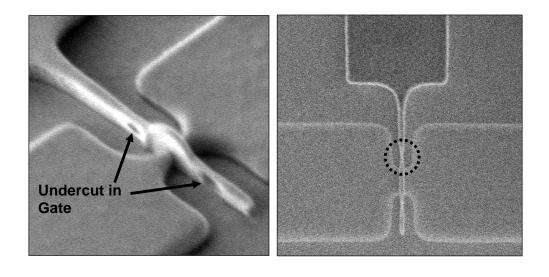

| Fig. 3.3 | <ul> <li>(a) SEM image of a FinFET that underwent excessive gate overetch process. The lateral etch component during the overetch step leads to significant gate uncut. The gate line can be broken at the narrowest portion or where there is severe line-edge roughness.</li> <li>(b) SEM image showing the top-view of a FinFET with gatepattern. The gate line is narrowest at both sides of the silicon fin</li></ul> |

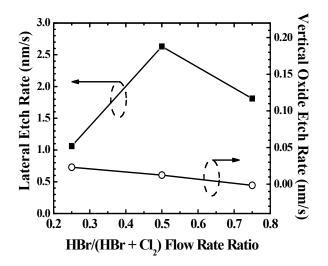

| Fig. 3.4 | Lateral etch rate of a silicon gate electrode (left axis) and vertical etch rate of silicon oxide (right axis) with varying HBr/(HBr + $Cl_2$ ) flow rate ratio                                                                                                                                                                                                                                                            |

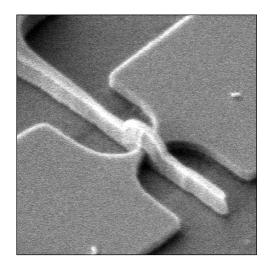

| Fig. 3.5 | By increasing the He- $O_2$ flow rate in the main etch step from 5 to 18 sccm, increased sidewall surface passivation was achieved. This contributed to adequate sidewall protection during the over-<br>etch step. Consequently, the FinFET gate electrode did not suffer from an undercut even during the extended over-etch step, as shown in the SEM image                                                             |

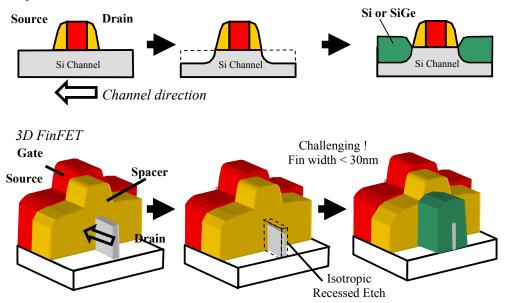

| Fig. 4.1 | Illustration of the scheme for FinFET with SiGe S/D stressor based on that of the bulk devices                                                                                                                                                                                                                                                                                                                             |

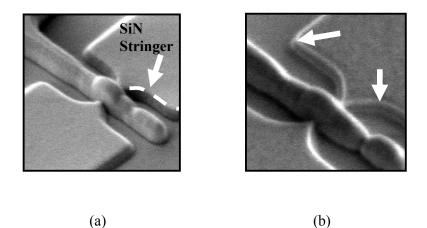

| Fig. 4.2 | SEM images of FinFET devices showing (a) SiN spacer etch to<br>end-point with the nitride stringer remaining at the sides of the fin.<br>(b) Extensive spacer over etch is done to remove the nitride<br>stringer as shown                                                                                                                                                                                                 |

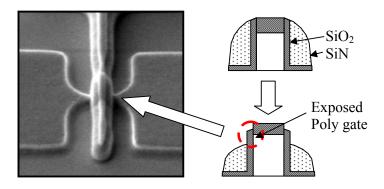

| Fig. 4.3 | SEM image of the FinFET device showing the expose of the gate corner when excessive spacer nitride is done. This result in the risk of shorting between the gate and S/D regions when selective epitaxy is performed                                                                                                                                                                                                       |

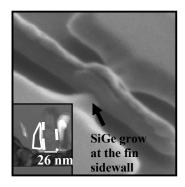

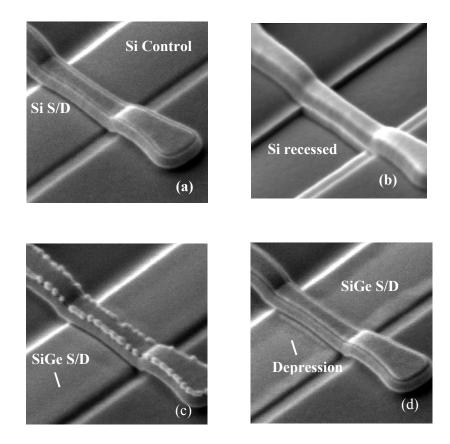

| Fig. 4.4  | SEM image of the FinFET device with SiGe raised S/D grown<br>even at the side of the fin at the S/D regions. The inset shows a<br>TEM image of the gate having a gate length of 26<br>nm                                                                                                                                                                                                                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

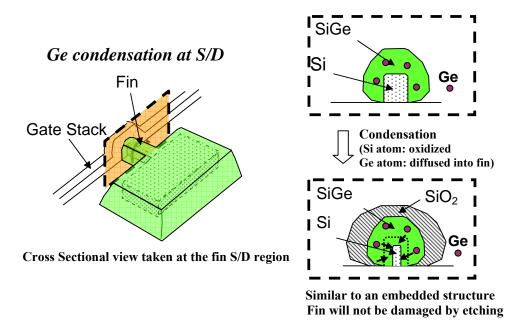

| Fig. 4.5  | Schematics of propose scheme using Ge condensation to form FinFET with embedded SiGe at the fin S/D regions42                                                                                                                                                                                                                                                                                                                                                                                 |

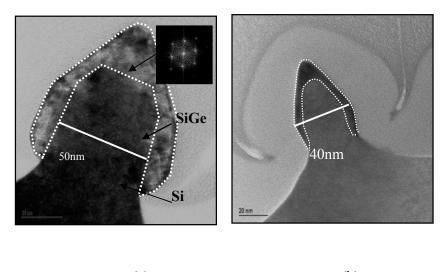

| Fig. 4.6  | (a) TEM image of a fin structure with SiGe grown on the top (100) and the sidewall (110) surfaces. (b) Ge diffuses into the fin after condensation at $950^{\circ}$ C for 20 mins in an oxygen ambient                                                                                                                                                                                                                                                                                        |

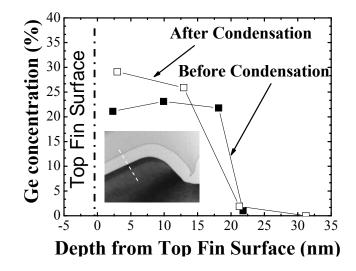

| Fig. 4.7  | EDX taken from the top of a larger fin test structure showing the increase in Ge concentration after condensation44                                                                                                                                                                                                                                                                                                                                                                           |

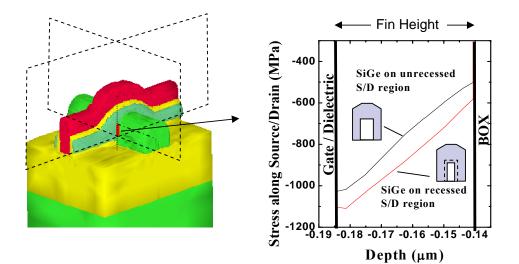

| Fig. 4.8  | Stress simulation for FinFET (fin width = $20 \text{ nm}$ ) with recessed profile (embedded SiGe) shows a larger compressive strain in the channel when compare to an unrecessed S/D45                                                                                                                                                                                                                                                                                                        |

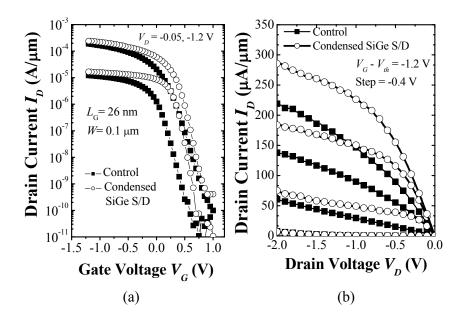

| Fig. 4.9  | (a) $I_D$ - $V_G$ characteristics of FinFET devices having an $L_G$ of 26 nm.<br>(b) $I_D$ - $V_D$ characteristics of FinFET devices at various gate overdrives ( $V_G$ - $V_{th}$ ). FinFET with condensed SiGe S/D shows a higher drive current                                                                                                                                                                                                                                             |

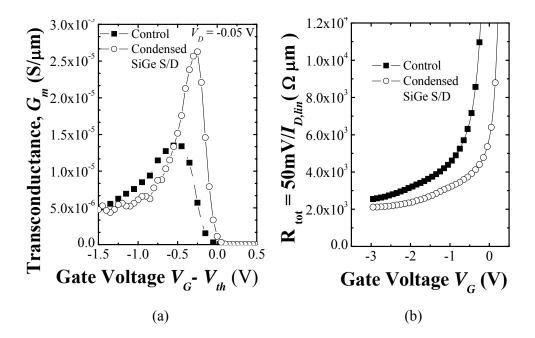

| Fig. 4.10 | (a) Comparison of transconductance $G_m$ at the same gate overdrive, illustrating an enhancement of 91% for the FinFET with condensed SiGe S/D over the control device. (b) Extraction of series resistance by examining the asymptotic behavior of the total resistance at large gate bias                                                                                                                                                                                                   |

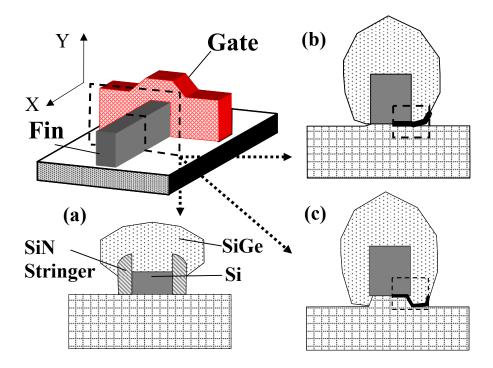

| Fig. 4.11 | (a) SiGe S/D stressor from ref. 4.3. This work realizes (b) $\Pi$ -SiGe S/D stressor. (c) $e\Pi$ -SiGe S/D stressor with SiGe growth below the BOX                                                                                                                                                                                                                                                                                                                                            |

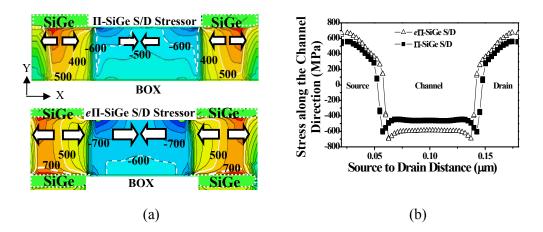

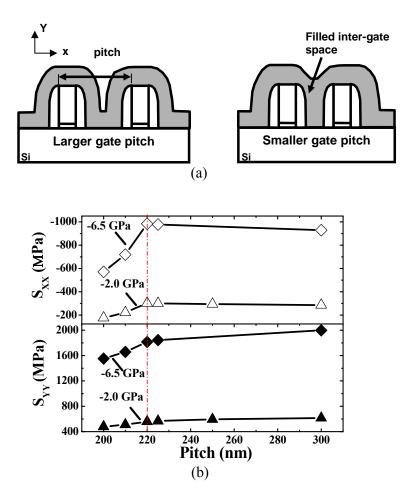

| Fig. 4.12 | (a) Simulated stress (in MPa) for $\Pi$ -SiGe (top) and $e\Pi$ -SiGe S/D stressor (bottom) stressors. Contour interval is 100 MPa. $L_g = 30$ nm, $W_{fin} = 30$ nm. Si at S/D and channel region is under tensile and compressive strain respectively. (b) Simulated stress along the channel direction taken near the bottom of the fin. $e\Pi$ -SiGe S/D stressor has a larger tensile stress near to the BOX at the S/D region which result in a higher compressive stress in the channel |

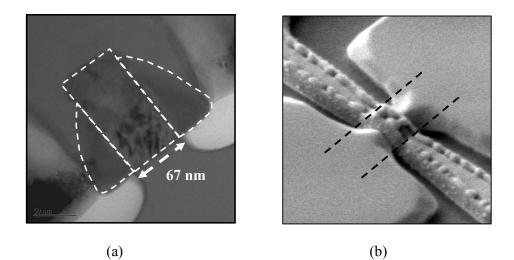

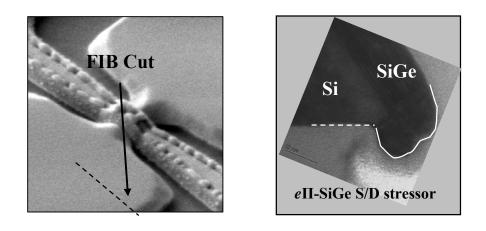

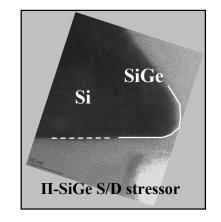

| Fig. 4.13 | (a) TEM image of the gate profile taken along the S/D direction shows a gate length of 67 nm. (b) SEM image shows the FinFET having a raised SiGe S/D                                                                                                                                                                                                                                                                                                                                         |

Х

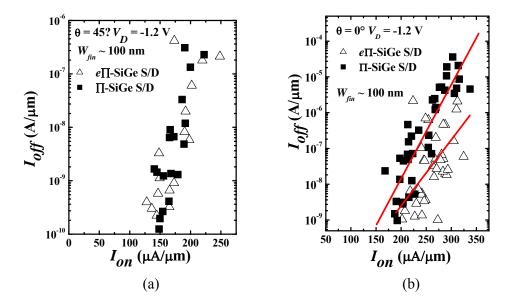

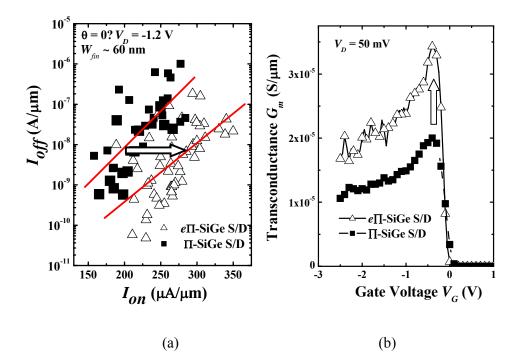

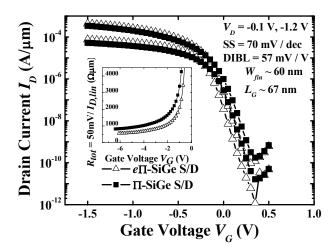

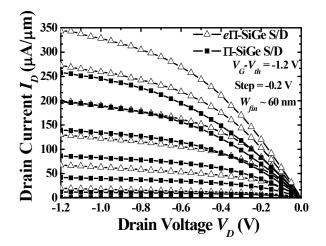

- Fig. 4.15 (a)  $I_{off}$  ( $V_G = 0.15$  V)  $I_{on}$  ( $V_G = -1.05$  V) comparison showing not muchdifference between  $e\Pi$  and  $\Pi$ -SiGe S/D stressors for FinFETs having <100> channel direction. (b)  $I_{off}$  ( $V_G = 0.15$  V) - $I_{on}$  ( $V_G = -1.05$  V) comparison shows an  $I_{on}$  enhancement of 21% at  $I_{off} = 1 \times 10^{-7}$  A/µm for FinFET having  $e\Pi$ -SiGe S/D stressor over  $\Pi$ -SiGe S/D stressor. Channel direction is <110>......54

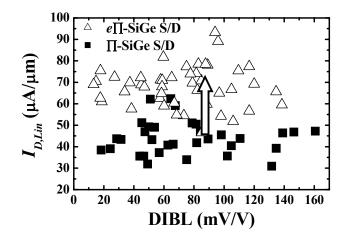

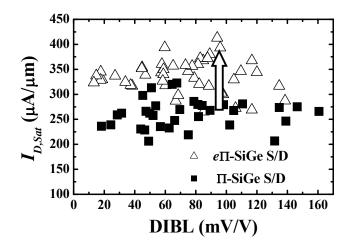

- Fig. 4.20  $I_{D,Sat}$  obtained at  $V_G V_{th} = V_D = -1.2$  V. 33% enhancement in drive current can be observed at a fixed DIBL......57

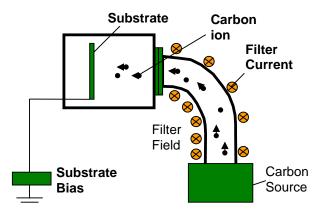

| Fig. 5.3 | Schematic of a FCVA system showing the deposition of DLC by     |

|----------|-----------------------------------------------------------------|

|          | carbon ions. The carbon ions are guided by a filter field and a |

|          | voltage bias is applied to the substrate                        |

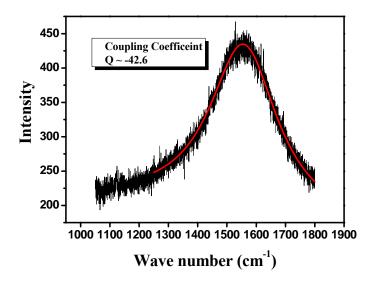

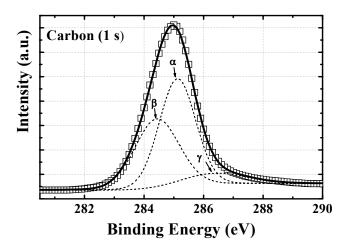

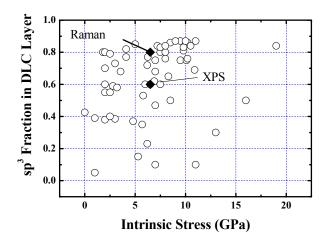

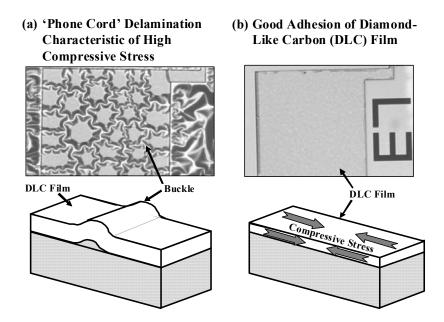

- Fig. 5.5 (a) X-ray Photoelectron Spectra of Diamond-Like Carbon (DLC) film showing the Carbon 1 s core level. The spectrum is fitted with curves having peaks corresponding to  $sp^3$ -hybridized carbon ( $\alpha$ ),  $sp^2$ -hybridized carbon ( $\beta$ ), and C-O ( $\gamma$ ) bonds......67

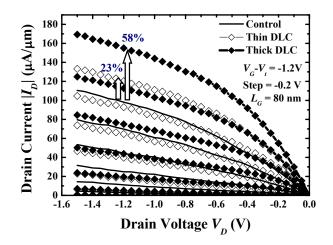

| Fig. 5.12 | $I_D$ - $V_D$ characteristics of p-channel SOI devices with different I | DLC   |

|-----------|-------------------------------------------------------------------------|-------|

|           | layer thicknesses. The p-FET with thicker DLC shows 58% c               | drive |

|           | current enhancement over a control p-FET without 1                      | iner  |

|           | stressor                                                                | 72    |

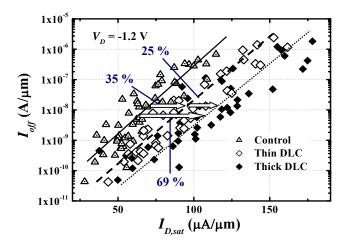

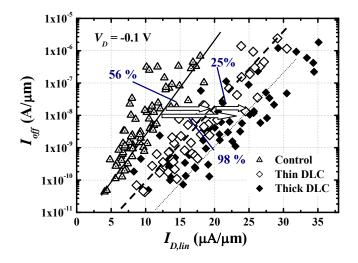

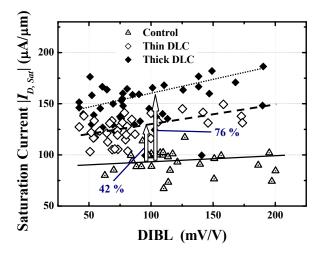

- Fig. 5.16  $I_{D,Sat}$  taken at  $V_G$ - $V_{th}$  = -1.2 V and  $V_D$  = -1.2 V. At a fixed DIBL of 0.1 V/V, 42% and 76%  $I_{D,Sat}$  enhancement can be observed for p-FETs with thin and thick DLC, respectively......74

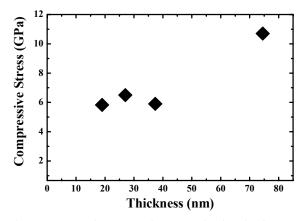

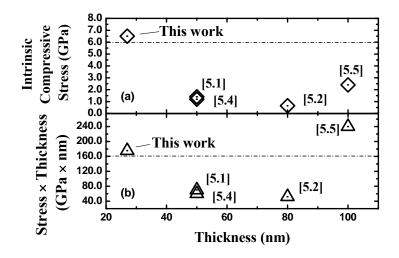

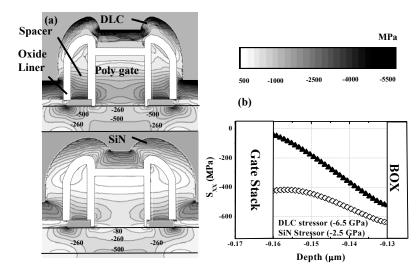

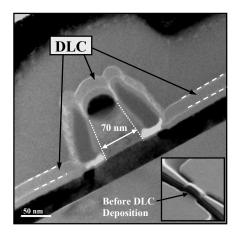

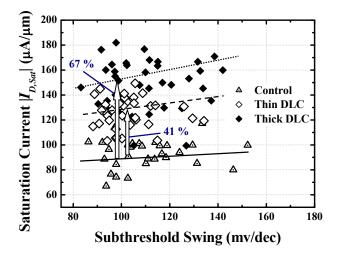

- Fig. 5.18 Comparison of reported intrinsic compressive stress levels in high-stress liners employed in transistor demonstrations. Open symbols represent integration of such high-stress liners on planar transistors, while closed symbols represent integration of highstress liners on multiple-gate transistors or FinFETs. Silicon nitride high-stress liners are plotted in circles and diamond-like carbon (DLC) liners are plotted in diamonds. Intrinsic compressive stress of DLC is much higher than that of SiN...... 76

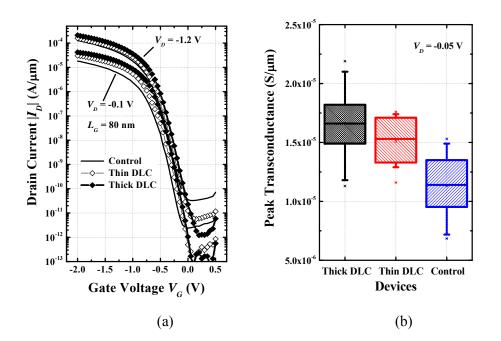

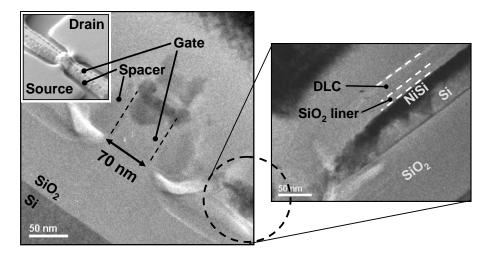

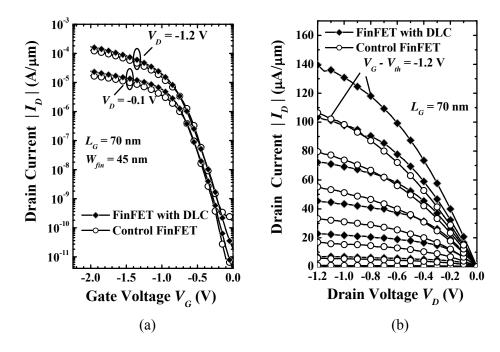

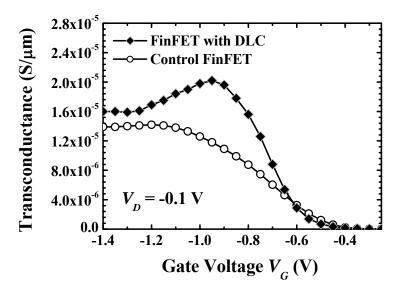

- Fig. 5.21 Comparison of (a)  $I_D$ - $V_G$  and (b)  $I_D$ - $V_D$  characteristics for FinFETs with and without DLC liner, showing similar subthreshold swing and drain-induced barrier lowering.  $I_D$ - $V_D$  curves with gate overdrive  $V_G V_{th}$  from 0 to -1.2 V in steps of -0.2 V are shown. A 31% enhancement in saturation drain current is observed for the FinFET with DLC liner stressor over the control FinFET......79

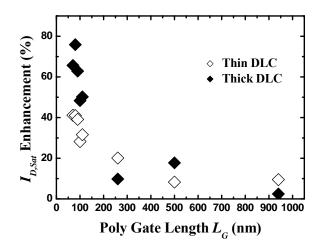

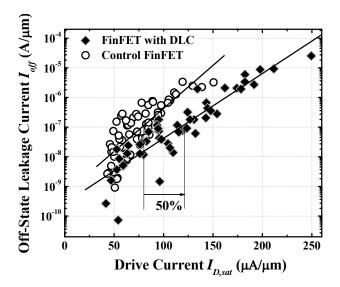

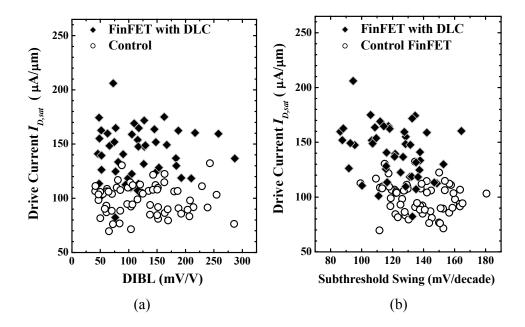

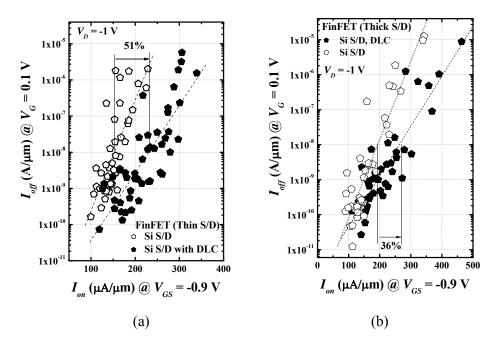

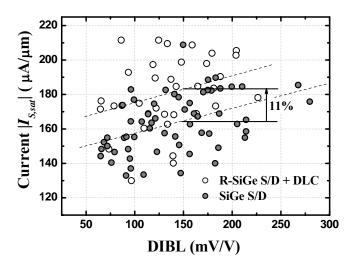

- Fig. 5.25 (a) DLC liner stressor significantly enhances the drive current  $I_{Dsat}$  of FinFET at various values of drain-induced barrier lowering (DIBL). Devices with gate lengths ranging from 50 nm to 80 nm were characterized. The  $I_{D,sat}$  was measured at gate over-drive  $(V_G V_{th}) = -1.2$  V and  $V_D = -1.2$  V. At a fixed DIBL of 0.1 V/V, stress from DLC liner contributed to a 42%  $I_{D,sat}$  enhancement. (b) At a fixed subthreshold swing of 120 mV/decade, DLC liner stressor contributes to a significant  $I_{Dsat}$  enhancement of 39%....82

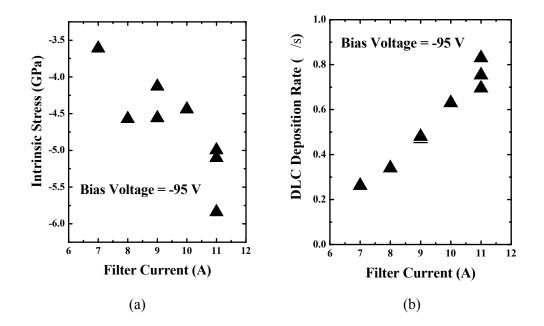

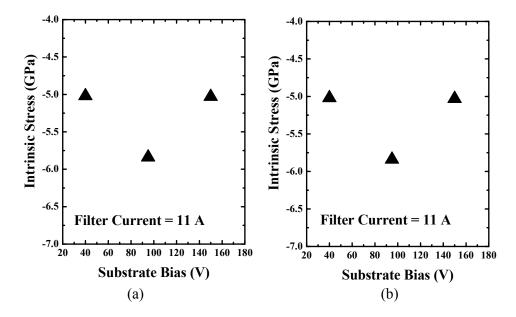

- Fig. 6.1 Effect of filter current on the (a) intrinsic stress and (b) deposition rate of DLC. Higher intrinsic compressive stress and deposition rate are obtained with the used of a larger filter current.......92

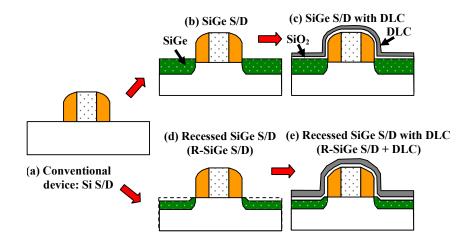

| Fig. 6.3 | Schematics showing the various planar structures fabricated and |

|----------|-----------------------------------------------------------------|

|          | compared in this chapter. The respective transistors are (a)    |

|          | conventional device with Si S/D, (b) device with SiGe S/D, (c)  |

|          | device with SiGe S/D and DLC, (d) device with intentionally     |

|          | recessed SiGe S/D (R-SiGe S/D), and (e) device with R-SiGe S/D  |

|          | and DLC                                                         |

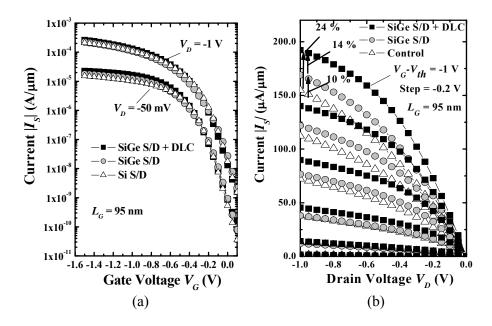

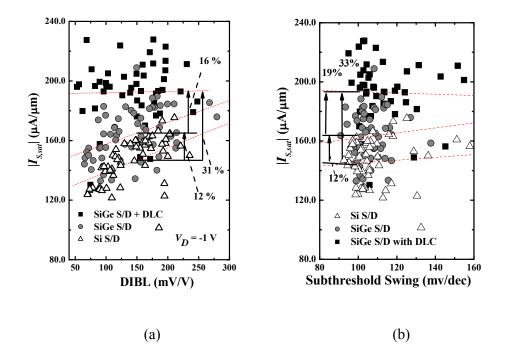

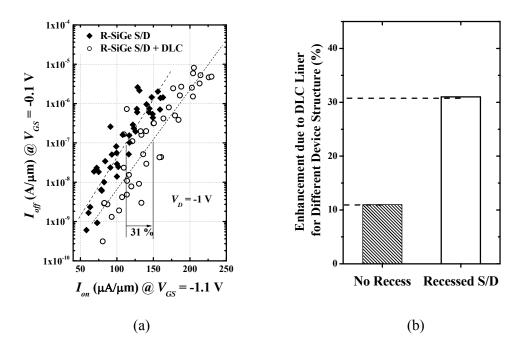

- Fig. 6.12  $I_{S,sat}$  taken at  $V_G$ - $V_{th}$  = -1 V and  $V_D$  = -1 V. (a) At a fixed DIBL of 150 mV/V and (b) SS of 100 mV/dec, device with DLC show 31% and 33% enhancement of  $I_{sat}$  over the control device......101

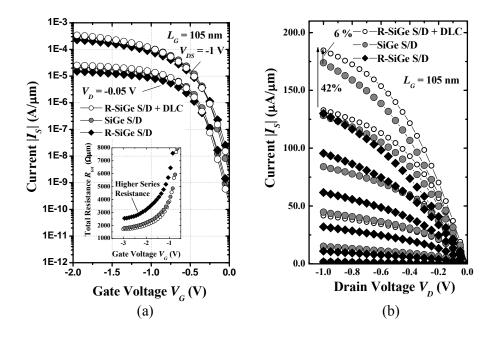

- Fig. 6.14 (a)  $I_S$ - $V_G$  characteristics of various planar devices showing similar subthreshold swing (SS) and DIBL. The inset in the graph show a higher series resistance for R-SiGe S/D device (b) Comparison of  $I_S$ - $V_D$  characteristics of the devices, where P-FET with R-SiGe S/D and DLC shows 42% enhancement over device with R-SiGe S/D. The performance of devices with R-SiGe S/D is comparable or better than device with SiGe S/D......102

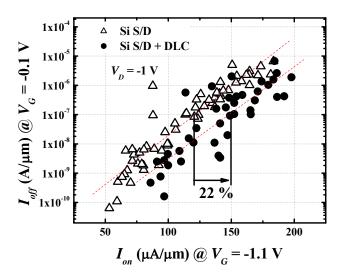

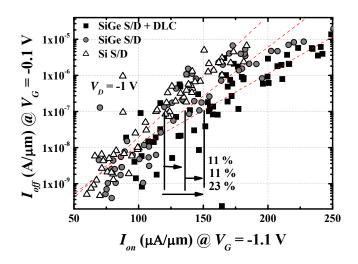

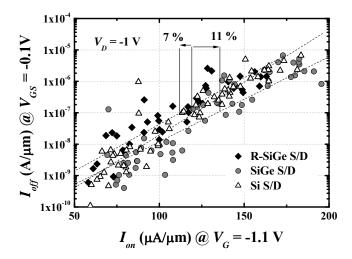

- Fig. 6.15 (a) *I<sub>off</sub>-I<sub>on</sub>* plot showing *I<sub>on</sub>* enhancement of 31% for p-FETs recessed SiGe S/D integrated with DLC as compared to one that does not have. (b) Comparison of enhancement due to DLC liner on devices with SiGe S/D, having two different S/D profiles (without and with recess S/D topology)......103

### List of Table

| Table 3.1 | Gate-etch process conditions used to form the FinFET structur  | e in |

|-----------|----------------------------------------------------------------|------|

|           | Fig. 3.3. Etchants used and the flow-rates are included. The n | nain |

|           | etch employed end-point detection                              | 32   |

| Table 3.2 | The newly developed poly gate etch recipe has neither poly     |      |

|           | stringer nor poly gate line breakage issues                    | 34   |

# List of Symbols

| $C_{ox}$                            | Gate oxide capacitance                                   | F/cm <sup>2</sup>   |

|-------------------------------------|----------------------------------------------------------|---------------------|

| $G_m$                               | Transconductance                                         | S                   |

| $H_{fin}$                           | Fin height                                               | nm                  |

| К                                   | Permittivity dielectric                                  |                     |

| I <sub>D,sat</sub>                  | Saturation drain current                                 | $\mu A/\mu m$       |

| $I_{D,Lin}$                         | Linear drain current                                     | $\mu A/\mu m$       |

| $I_D$                               | Drain Current                                            | $\mu A/\mu m$       |

| $I_S$                               | Source Current                                           | $\mu A/\mu m$       |

| $I_{off}$                           | Off-state leakage current                                | A/µm                |

| Ion                                 | On-state leakage current                                 | $\mu A/\mu m$       |

| т                                   | body-effect factor                                       |                     |

| $p_{fin}$                           | Fin pitch                                                | nm                  |

| ρ                                   | Resistivity                                              | Ωcm                 |

| $r_c$                               | back scattering coefficient                              |                     |

| S <sub>xx</sub>                     | Stress Component in x-direction                          | MPa                 |

| $\mathbf{S}_{\mathbf{y}\mathbf{y}}$ | Stress Component in y-direction                          | MPa                 |

| u <sub>eff</sub>                    | Effective mobility                                       | cm <sup>2</sup> /Vs |

| $V_G$                               | Gate Voltage                                             | V                   |

| $V_D$                               | Drain Voltage                                            | V                   |

| $V_{th}$                            | Threshold voltage                                        | V                   |

| $v_T$                               | Thermal velocity                                         | cm/s                |

| $v_{sat}$                           | Saturation velocity                                      | cm/s                |

| $W_{fin}$                           | Fin width                                                | nm                  |

| $X_{\lambda}$                       | Component of the stress in six-component vector notation | MPa                 |

| $\Phi_m$                            | Gate work function                                       | eV                  |

| $\Pi_l$                             | Longitudinal piezoresistance coefficient                 |                     |

| $\Pi_t$                             | Transverse piezoresistance coefficient                   |                     |

| $\Pi_{\omega\lambda}$               | Component of the piezoresisance tensor.                  |                     |

# **Chapter 1**

# Introduction

### **1.1 Background**

The scaling of CMOS technology which allows higher packing density and better device performance has become more challenging as we approach sub-100 nm node. While the transistor dimension has become smaller, more of them can be packed per unit area (Moore's law: double of chip components for every 24 months), the electrical performance will have to be improved at the same time. For high performance device, there are several requirements to meet and among them are the control of short channel effects (SCEs) to give a low off-state leakage current ( $I_{off}$ ) and also high drive current ( $I_{on}$ ) to booast the speed of the circuit.

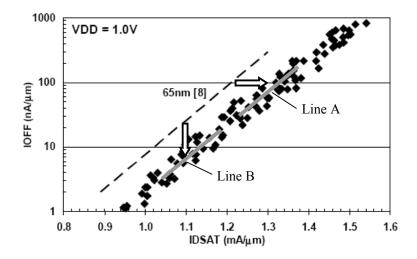

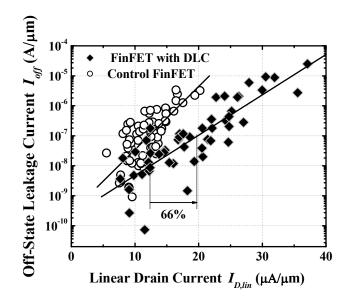

Very often, a plot of  $I_{on}$  in linear scale on the x-axis and  $I_{off}$  in log scale on the y-axis is used to describe and compare the performance of different devices. A typical plot of this is shown in Fig 1.1 where the data points are taken from transistors having different  $L_G$  characterized by each  $I_{on}$  and  $I_{off}$ . The data points formed a straight line as seen in Fig. 1.1. Transistor with smaller  $L_G$  demonstrates higher  $I_{on}$  and  $I_{off}$ . For each technology node, the objective is to push the "line" further to right. This means that either at the same  $I_{off}$ , the device will demonstrate higher drive current (line A) or alternatively, at the same  $I_{on}$ , the device will give a smaller  $I_{off}$  (line B).

Fig. 1.1 A typical plot of  $I_{off}$ - $I_{on}$  for 65 nm technology node taken from Ref. [1.1]. Additional arrows and lines are added for illustration purpose.

For a MOSFET, the drive current can be simply increased by decreasing  $L_G$  as suggested by the following equation

$$I_{D,Sat} = \mu_{eff} C_{ox} \frac{W}{L_G} \frac{(V_{GS} - V_{th})^2}{2m}, \qquad \text{--- eq. (1.1)}$$

where *m*: body-effect factor, typically lies between 1.1 and 1.4.

However, with the scaling down of the supplied voltage at the same time to maintain an appropriate electric field in the transistor, the increase of drive current is reduced. Increasing the gate oxide capacitance ( $C_{ox}$ ) by scaling down the thickness of the conventionally used SiO<sub>2</sub> gate dielectric has also become more challenging. As the thickness of SiO<sub>2</sub> gate dielectric approaches 1 nm, the gate leakage current increases mainly due to direct tunneling. This render the used of high- $\kappa$  gate dielectric materials to give a thicker physical thickness for the control of gate leakage issues. Therefore, to increase drive current, enhancing the mobility ( $u_{eff}$ ) of the carrier has been proposed.

Replacing Si with other materials having a much higher intrinsic mobility has been suggested. Candidates like Ge [1.2]-[1.3] and III-V compounds eg. GaAs [1.4]-[1.5] are currently being investigated. However, adopting these materials for device fabrication has problems of their own. Finding a compatible gate dielectric, source/drain contact and several other issues will have to be overcome before it can be used in manufacturing. A more near-term solution is to boost the electron and hole mobility of Si, which can be achieved by straining the Si channel [1.6]-[1.7]. When Si is under strain, the Si lattice crystal gets distorted and this changes the electronic band structure. Splitting of the bands can occur and the effective mass can also be modified. A review paper on this phenomenon and application was reported by *Lee et al.* [1.8]. Different strain techniques have been explored to induce strain in the device channel, some of them are listed as followed,

- making use of the lattice mismatch between Si and Si<sub>1-x</sub>Ge<sub>x</sub> [1.9], Si and Si<sub>1-y</sub>C<sub>y</sub> [1.10]-[1.11] for PMOS and NMOS devices, respectively,

- making used of a highly tensile or compressive stress contact etch stop liner (CESL), typically SiN [1.12],[1.13],

- 3) stress induced by a fully silicided (FUSI) gate [1.14],

- stress memorization techniques which until now is only reported for NMOS device [1.15],

- 5) reverse embedded SiGe structure [1.16],

- and also instinctively, a combination of the above stressors (multiple stressors) [1.17].

With the scaling down of device dimension below sub-micron regime (eg.  $L_G$  at 100 nm for a  $V_D$  of 1.2 V), the lateral electric field now (1.2×10<sup>5</sup> V/cm) becomes larger than the critical field of velocity saturation and eq. 1.1 becomes

$$I_{D,Sat} = v_{sat} C_{ox} W (V_{GS} - V_{th}) \frac{\sqrt{1 + 2\mu_{eff} (V_{GS} - V_{th}) / (m v_{sat} L_G)} - 1}{\sqrt{1 + 2\mu_{eff} (V_{GS} - V_{th}) / (m v_{sat} L_G)} + 1}, \quad \text{--- eq. (1.2)}$$

where  $v_{sat}$  is around 7-8×10<sup>6</sup> cm/s for electrons.

In Equation 1.2, the carriers are treated to be in thermal equilibrium with the Si lattice. When  $L_G$  is scaled down further to sub 100 nm, it has been reported that velocity overshoot can occurred [1.18] where the velocity of the carrier can exceed that that of  $v_{sat}$ . For 90 nm technology node and beyond, the physical  $L_G$  of the transision is in fact smaller than 50 nm and thus the carrier should no longer be treated to be in thermal equilibrium with the Si lattices. For MOSFET, the current is mainly dependent on the average carrier velocity at the source end of the channel and a simple one-flux scattering is introduced [1.19] as follows

$$I_{D,Sat} = v_T C_{ox} W \left( \frac{1 - r_c}{1 + r_c} \right) (V_{GS} - V_{th}) , \qquad \text{--- eq. (1.3)}$$

where  $v_T$  is the thermal velocity and  $r_c$  is the back scattering coefficient. Treatment of eq. 1.3 for the case of degenerate condition is described in [1.20]. It has been reported that the effect of strain can change both  $v_T$  and  $r_c$  [1.21]. Therefore, with careful optimization of the process, even for extremely small  $L_G$ the technique of strain will still be useful in improving the  $I_{on}$ .

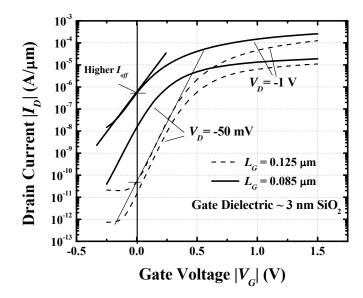

A major issue accompaning  $L_G$  scaling is the increase in off-state leakage current. This is usually due to an increase in subthreshold swing (SS) and larger drain induced barrier lowering (DIBL) effect as illustrated in Fig 1.2. To control

Fig. 1.2 A typical plot of  $I_D$ - $V_G$  comparing short and long  $L_G$  devices. Device with small  $L_G$  shows smaller  $V_{th}$ , and larger SS, DIBL and  $I_{off}$ .

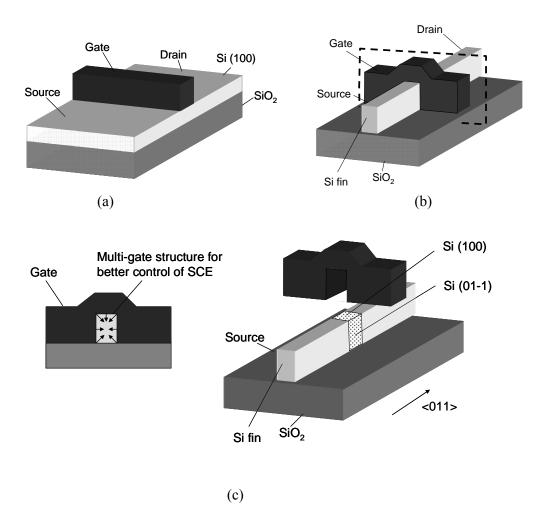

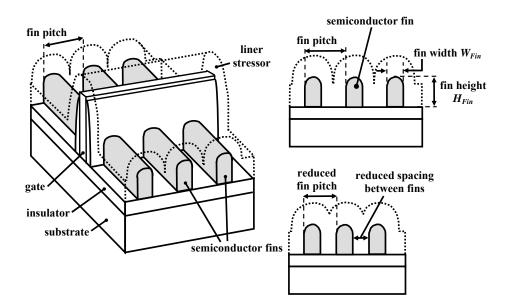

the short channel effect (SCEs) at small  $L_G$ , higher channel doping, and halo implants are used. However, incorporating more dopants in the channel degrades mobility. Efforts have been put in to push the device  $L_G$  to sub-10 nm, however the DIBL and SS observed are still very large [1.22]. Devices fabricated on ultrathin silicon-on insulator (SOI) wafer (Fig. 1.3(a)) is able to achieve a smaller  $I_{off}$ by eliminating the leakage path which is far away from the gate control. When  $L_G$ is scaled down to less than 15 nm, according to the International Technology Roadmap for Semiconductors (ITRS) 2008 Update PIDS, FinFET or multi-gate device structure as shown in Fig. 1.3(b) will be required to control the  $I_{off}$  more effectively.

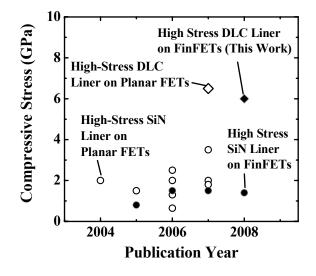

Fig. 1.3 Schematics of a (a) planar device fabricated on SOI wafer, (b) a FinFET or multiple-gate device, and (c) cross-section showing the control by multi-gate structure and the different planes of conduction.

As shown in Fig. 1.3(c), the drain current can flow from the source to the drain on the top surface and on both sidewall surfaces of the fin. The surface orientations are different with the top surface being (100) and the sidewall surfaces being (110). The mobility of the carriers travelling in the different surfaces will be also different. For example, it is well-known that the hole mobility is higher on a (110) plane when compared to the (100) [1.23]. The performance of the multi-gate device will depend a lot on the dimension of the fin

width ( $W_{fin}$ ). Devices with smaller  $L_G$  will usually require smaller  $W_{fin}$  for better SCEs control. However, the decrease in  $W_{fin}$  is accompanied by an increase in series resistance and this degrades the drive current. Therefore, performing selective epitaxy raised source/drain (S/D) on the multiple-gate device has been proposed for the reduction of series resistance [1.24]. To give even better device performance, SiGe [1.25] or Si:C which is lattice mismatched to Si can be grown instead to induce strain in the channel for mobility improvement. In addition, SiGe can also be exploited to lower the contact resistance due to the smaller bandgap of SiGe as Ge concentration increases [1.26].

### **1.2 Objective of Research**

The objection of this thesis work is to investigate and demonstrate novel device structure and idea that can improve the device performance for sub-32 nm node and beyond. Study of strain engineering on bulk, planar SOI and multiple-gate or FinFET device is being made based on each device structure.

### **1.3 Organization of Thesis**

Chapter 2 of this thesis investigates the effect of having a silicon nitride (SiN) capping layer on a TaN metal gate FinFET device during the high temperature S/D anneal. Comparison of performance is made to a similar device but without the capping SiN. In this thesis work, the  $I_D$ - $V_D$  is plotted with different gate overdrive ( $V_G$ - $V_{th}$ ) biasing. Saturation  $V_{th}$  is used here, where  $V_{th}$  is taken at high  $V_D$ . The  $V_{th}$  is taken based on a constant  $I_D$  value chosen from the plot of Log  $I_D$  against  $V_G$  curve below the turning point where the subthreshold slope start to

flatten which is an indication that the transistor is about to "turn on". In chapter 3, poly-Si gate etching issues on FinFET device are discussed. Due to the 3D topography which results in the formation of gate stringer, conventionally gate etch recipe used for the planar device is not suitable and thus a new gate etch recipe specifically for the FinFET structure is developed.

In chapter 4, strained FinFET with SiGe S/D was studied. By having a better understanding of the FinFET device structure and fabrication process, enhanced versions of FinFET with SiGe S/D was proposed which demonstrated better device performance. With the rapid shrinking of device dimension, strained techniques employing highly stress contact etch-stop liner (CESL) becomes less efficient. In chapter 5, a novel material diamond-like carbon (DLC) having an extremely high intrinsic compressive stress is introduced for high stress CESL application. Performance enhancement on p-channel planar SOI and FinFET devices are also discussed.

Further investigations of DLC are made in chapter 6. Process conditions affecting the intrinsic stress of DLC are reported and integration with planar device having an embedded SiGe S/D was also demonstrated for the first time. In addition, DLC integrated with an intentionally recessed S/D profile show better coupling of strain from the DLC stressor to the channel. Lastly, in chapter 7, a conclusion is made and future work with regards to this thesis are suggested.

### **1.4 References**

- [1.1] K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi, G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hicks, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parsons, C. Prasad, L. Pipes, M. Prince, P. Ranade, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, S. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams, K. Zawadzki, "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free," *IEDM Tech. Dig.* 2007, pp. 247-250.

- [1.2] J.J. Rosenberg, and S.C. Martin, "Self-Aligned Germanium MOSFET's Using a Nitride Native Oxide Gate Insulator," *IEEE Electron Device Letters*, vol. 12, no. 9, pp. 639-640, Dec. 1988.

- P. Zimmerman1, G. Nicholas, B. De Jaeger, B. Kaczer, A. Stesmans, L.-Å Ragnarsson, D. P. Brunco1, F. E. Leys, M. Caymax, G. Winderickx, K. Opsomer, M. Meuris, and M. M. Heyns, "High Performance Ge pMOS Devices Using a Si-Compatible Process Flow," *IEDM Tech. Dig.* 2006, pp. 655-658.

- [1.4] I. Ok, H. Kim, M. Zhang, T. Lee, F. Zhu, L. Yu, S. Koveshnikov1, W. Tsai1,V. Tokranov, M. Yakimov, S. Oktyabrsky, and J. C. Lee, "Self-Aligned n- and p-channel GaAs MOSFETs on Undoped and P-type Substrates Using HfO<sub>2</sub> and Silicon Interface Passivation Layer," *IEDM Tech. Dig.* 2006, pp. 829-832.

- [1.5] M. Passlack, J. K. Abrokwah, R. Droopad, Z. Yu, C. Overgaard, S. I. Yi, M. Hale, J. Sexton, and A. C. Kummel, "Self-aligned GaAs p-channel

enhancement mode MOS heterostructure field-effect transistor," *IEEE Electron Device Letters*, vol. 23, no. 9, pp. 508-510, Sep. 2002.

- [1.6] R. W. Keyes, "High-Mobility FET in Strained Silicon," *IEEE Trans. Electron Devices*, 33, 6, pp. 863, Jun. 1986.

- [1.7] C. S. Smith, "Piezoresistance effects in germanium and silicon," *Phys. Rev.*, vol. 94, 1, pp. 42-49, Apr. 1954.

- [1.8] M. L. Lee and E. A. Fitzgerald, "Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors," J. Appl. Phys., 97, 011101, 2005.

- [1.9] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntryre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadki, S. Thompson and M. Bohr, "A 90 nm high volume maufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors," *IEDM Tech. Dig.* 2003, pp. 978-990.

- [1.10] K. W. Ang, K. J. Chui, V. Blimetsov, A. Du, N. Balasubramanian, M. F. Li, G. Samudra, and Y.-C. Yeo, "Enhanced Performance in 50 nm N-MOSFETs with Silicon-Carbon Source/Drain Regions," *IEDM Tech. Dig.* 2004, pp. 1069-1071.

- [1.11] Y. Liu, O. Gluschenkov, J. Li, A. Madan, A. Ozcan, B. Kim, T. Dyer, A. Chakravarti, K. Chan, C. Lavoie, I. Popova, T. Pinto, N. Rovedo, Z. Luo, R. Loesing, W. Henson, and K. Rim, "Strained Si Channel MOSFETs with Embedded Silicon Carbon Formed by Solid Phase Epitaxy," *Symp. VLSI Tech.* Dig., 2007, pp. 44-45.

- [1.12] S. Ito, H. Namba, K. Yamaguchi, T. Hirata, K. Ando, S. Koyama, S. Kuroki, N. Ikezawa, T. Suzuki, T. Saitoh and T. Horiuchi, "Mechanical

stress effect of etch-stop nitride and its impact on deep submicron transistor design," *IEDM Tech. Dig.*, 2000, pp. 247-250.

- [1.13] H. S. Yang, R. Malik, S. Narasimha, Y. Li, R. Divakaruni, P. Agnello, S. Allen, A. Antreasyan, J. C. Arnold, K. Bandy, M. Belyansky, A. Bonnoit, G. Bronner, V. Chan, X. Chen, Z. Chen, D. Chidambarrao, A. Chou, W. Clark, S. W. Crowder, B. Engel, H. Harifuchi, S. F. Huang, R. Jagannathan, F. F. Jamin, Y. Kohyama, H. Kuroda, C. W. Lai, H. K. Lee, W-H. Lee, E. H. Lim, W. Lai, A. Mallikarjunan, K. Matsumoto, A. McKnight, J. Nayak, H. Y. Ng, S. Panda, R. Rengarajan, M. Steigerwalt, S. Subbanna, K. Subramanian, J. Sudijono, G. Sudo, S-P. Sun, B. Tessier, Y. Toyoshima, P. Tran, R. Wise, R. Wong, I.Y. Yang, C. H. Wann, and L.T. Su, "Dual Stress Liner for High Performance sub-45nm Gate Length SOI CMOS Manufacturing," *IEDM Tech. Dig.*, 2004, pp. 1075-1077.

- [1.14] Z. Krivokapic, C. Tabery, W. Maszara, Q. Xiang, and M.-R. Lin, "High Performance 45 nm CMOS Technology with 20 nm Multi-Gate Devices," *SSDM*, 2003, pp. 760-761.

- [1.15] C.-H. Chen, T. L. Lee, T. H. Hou, C. L. Chen, C. C. Chen, J. W. Hsu, K. L. Cheng, Y. H.Chiu, H. J. Tao, Y. Jin, C. H. Diaz, S. C. Chen, and M.-S. Liang, "Stress Memorization Technique (SMT) by Selectively Strained-Nitride Capping for Sub-65nm High-Performance Strained-Si Device Application," *Symp. VLSI Tech.* Dig., 2004, pp. 56-57

- [1.16] R. A. Donaton, D. Chidambarrao, J. Johnson, P. Chang, Y. Liu, W. K. Henson, J. Holt, X. Li, J. Li, A. Domenicucci, A. Madan, K. Rim, and C. Wann, "Design and fabrication of MOSFETs with a reverse embedded SiGe (Rev. e-SiGe) structure," *IEDM Tech. Dig.*, 2006, pp. 465–468.

- [1.17] H. C.-H. Wang, S.-H. Huang, C.-W. Tsai, H.-H. Lin, T.-L. Lee, S.-C. Chen, C. H. Diaz, M.-S. Liang, and J. Y.-C. Sun, "High-Performance PMOS Devices on (110)/<111> Substrate/Channel with Multiple Stressors," *IEDM Tech. Dig.*, 2006, pp. 1–4.

- [1.18] G. A. S.-Halaza, M. R. Wordeman, D. P. Kern, S. Rishton, and E. Ganin, "High Transconductance and Velocity Overshoot in NMOS Devices at the 0. l-µm Gate-Length Level." *IEEE Electron Device Letters*, vol. 9, no. 9, pp. 464-466, Sep. 1999.

- [1.19] M. Lundstrom, "Elementary Scattering Theory of the Si MOSFET," IEEE Electron Device Letters, vol. 18, no. 7, pp. 361-363, Jul. 1997.

- [1.20] F. Assad, Z. Ren, D. Vasileska, S. Datta, and M. Lundstrom, "On the Performance Limits for Si MOSFET's: A Theoretical Study," *IEEE Trans. Electron Devices*, 47, 1, pp. 232-240, Jan. 2000.

- [1.21] H.-N. Lin, H.-W. Chen, C.-H. Ko, C.-H. Ge, H.-C. Lin, T.-Y. Huang, and W.-C. Lee, "Channel Backscattering Characteristics of Uniaxially Strained Nanoscale CMOSFETs," *IEEE Electron Device Letters*, vol. 26, no. 9, pp. 676-678, Sep. 2005.

- [1.22] N. Yasutake, K. Ohuchi, M. Fujiwara, K. Adachi, A. Hokazono, K. Kojima, N. Aoki, H. Suto, T. Watanabe, T. Morooka, H. Mizuno, S. Magoshi, T. Shimizu, S. Mori, H. Oguma, T. Sasaki, M. Ohmura, K. Miyano, H. Yamada, H. Tomita, D. Matsushita, K. Muraoka, S. Inaba, M. Takayanagi, K. Ishimaru, and H. Ishiuchi, "A hp22 nm Node Low Operating Power (LOP) Technology with Sub-10 nm Gate Length Planar Bulk CMOS Devices," Symp. VLSI Tech., 2004, pp. 84-85.

- [1.23] L. Chang, M. Ieong, and Min Yang, "CMOS Circuit Performance Enhancement by Surface Orientation Optimization," *IEEE Trans. Electron Devices*, 51, 10, pp. 1621-1627, Oct. 2004.

- [1.24] J. Kedzierski, M. Ieong, E. Nowak, T. S. Kanarsky, Y. Zhang, R. Roy, D. Boyd, D. Fried, and H.-S. P. Wong, "Extension and Source/Drain Design

for High-Performance FinFET Devices," *IEEE Trans. Electron Devices*, 50, 4, pp. 952-958, Apr. 2003.

- [1.25] P. Verheyen, N. Collaert, R. Rooyackers, R. Loo, D. Shamiryan, A. De Keersgieter, G. Eneman, F. Leys, A. Dixit, M. Goodwin, Y. S. Yim, M. Caymax, K. De Meyer, P. Absil, M. Jurczak, and S. Biesemans, "25% drive current improvement for p-type multiple gate FET (MuGFET) devices by the introduction of recessed Si<sub>0.8</sub>Ge<sub>0.2</sub> in the source and drain regions," Symp. VLSI Tech., 2005, pp. 194-195.

- [1.26] J. Liu, and M. C. Ozturk, "Nickel Germanosilicide Contacts Formed on Heavily Boron Doped Si<sub>1-x</sub>Ge<sub>x</sub> Source/Drain Junctions for Nanoscale CMOS," *IEEE Trans. Electron Devices*, 52, 7, pp. 1535-1540, Jul. 2005.

# Chapter 2

# Drive Current Enhancement in FinFETs Using Gate-Induced Stress

### 2.1 Background

As mentioned in chapter 1, the multiple-gate transistor or FinFET device structure [2.1]-[2.4] has superior scalability over conventional planar metal-oxidesemiconductor (MOS) transistor structures, and enables gate length scaling well beyond the 32 nm technology generation. In addition, the FinFET device structure allows the use of low channel dopant concentration, and avoids problems associated with random dopant fluctuation. The threshold voltage  $V_{th}$  of FinFETs can be set through gate work function  $\Phi_m$  engineering using metal gates, which additionally eliminate the gate depletion effect and dopant penetration problem for improved drive current  $I_{D,sat}$  performance. For n-channel FinFET devices, the optimal gate work function lies between the mid-gap and the conduction band of Si, which necessitates the use of metal gates. It has been reported that fullysilicided metal gate can induce strain in the transistor channel [2.2], and the localized strain could be exploited to enhance the performance of aggressively scaled transistors. While many approaches to strained-Si has been demonstrated, strain introduction by metal-nitride gate has not been experimentally reported. In this chapter, we report the first demonstration of a strained n-channel FinFET with a tantalum nitride (TaN) gate stressor. We also report a novel and simple process that exploits the stress developed in the metal gate during an anneal process to introduce strain in the Si channel. The resulting drive current enhancement in FinFET devices will be discussed

### **2.2 Device Fabrication**

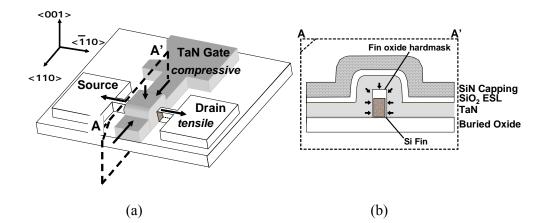

Fig. 2.1. Process flow and schematics showing the FinFET fabrication process and the incorporation of metal-gate stressor. The introduction of an additional SiN layer prior to the S/D dopant activation anneal serves to induce high stress in the channel by constraining the gate structure's volume expansion. The strain is retained even after SiN removal.

Mesa-isolated n-channel FinFETs with TaN gates were fabricated on SOI wafers. The process sequence adopted is illustrated in Fig. 2.1. Silicon on insulator (SOI) wafers with (001) surface and 45 nm thick Si were used. Gate etching development was first done to see the feasibility of etching TaN gate

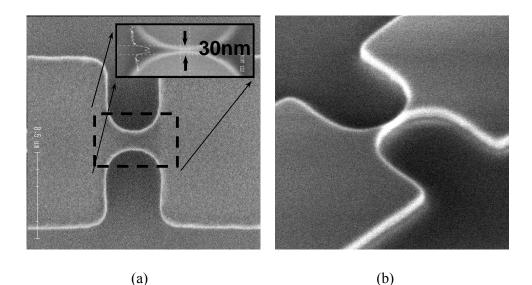

Fig. 2.2. (a) Top view SEM images of the fin pattern before and after resist trim as shown in the inset. Fin width as small 30 nm can be achieved using a mixture of  $O_2$  and Ar plasma. (b) Tilted SEM images of the fin after dry etch where the fin pattern is transferred down to the Si.

Fig. 2.3. SEM images of the pattern gate line running across the fin. Resist trimming were also used here to achieve small gate length.

electrode on FinFET. After fin patterning using 248 nm lithography, resist trimming is applied to achieve fin width of sub-30 nm as shown by the Scanning

Electron Microscopy (SEM) image in Fig. 2.2(a). This is later transferred to the Si as observed in Fig. 2.2(b). Figure 2.3 shows the gate pattern running over the fin and small gate line was achieved by adopting a similar scheme as in the fin definition.

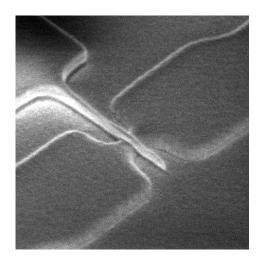

The etching of metal gate was done using an Applied Material Centura etch system. Figure 2.4 shows the SEM images of the FinFET structure after TaN metal gate etch, using a mixture of HBr/Cl<sub>2</sub> and Ar. The stopping of the metal gate etch on the thin dielectric can be quite challenging and even if this can be done, there is still some metal gate stringers which remained and surround the FinFET device as seen from Fig. 2.4(a). In the attempt to remove the stringer by increasing the metal gate etched time, it results in the etching away of the fin as observed in Fig. 2.4(b). While the Si at the source/drain (S/D) pad remain, Si

(a)

(b)

Fig. 2.4. (a) SEM image showing the FinFET structure after TaN gate etch. The fin height is 45 nm and 3 nm  $SiO_2$  is used as the gate dielectric. TaN gate stringer can be seen surrounding the FinFET structure. (b) An extended gate etch was done to remove the stringer, but the gate etch selectivity to  $SiO_2$  dielectric is not sufficient high too protect the fin from getting etch away.

at the edges of the S/D pads was already gone as seen in Fig. 2.4(b). The faster etch rate at the Si fin corners make the etching of TaN gate on FinFET even more challenging. A thicker  $SiO_2$  (60 nm) was therefore deposited as a hard mask for the definition of the Si fin. The hard mask was retained for the protection of the fin in a subsequent gate etch process.

A 2 nm sacrificial oxide was then grown on the fin sidewalls to repair the damage caused by plasma etching. Following its removal,  $SiO_2$  with a target EOT of 25 Å was used as the gate dielectric before depositing 100 nm of TaN as the gate electrode. Gate etch profile has improved after the new approach was adopted as shown Fig. 2.5(a). After S/D extension implant, spacer formation, and the deep S/D implant, the resulting structure is shown in the SEM image in Fig. 2.5(b). PECVD SiO<sub>2</sub> liner layer (6 nm) was then deposited on all wafers. On one wafer in which the metal gate stress is to be introduced to form the strained-

(a)

(b)

Fig. 2.5. (a) SEM image showing a FinFET structure with an improved gate profile. The inset shows an image of the fin profile. (b) SEM image of the FinFET structure after spacer formation.

channel FinFET, an additional PECVD SiN capping layer with a thickness of 50 nm was deposited over the gate stack [Fig. 2.1]. The SiN capping layer has a relatively low intrinsic compressive stress of about -100 MPa. On another wafer where the control FinFETs is to be fabricated, the SiN capping layer deposition was skipped. This was followed by S/D anneal (1000°C for 5 s) on all wafers. The SiN capping layer on the strained-channel FinFET was then removed by hot phosphoric acid at 150°C. The PECVD SiO<sub>2</sub> liner layer was removed on both wafers. Forming gas anneal was carried out at 420°C for 30 min to complete the device fabrication.

### **2.3 Results and Discussion**

Figure 2.6 illustrates the mechanism by which channel stress could be induced by the metal gate. This mechanism is different from the stress memorization technique reported for poly-Si gate in [2.5]. In the strained- channel FinFET

Fig. 2.6. Schematic showing how the TaN gate layer can compressively stress the Si fin channel from 3 directions. The cross-section schematic illustrates the compressive stress exerted perpendicular to fin body during S/D implant activation anneal.

reported in this work, the metal gate electrode tends to expand more than the SiN capping layer or the Si fin during the S/D anneal. The thermal coefficient of expansion(TCE) is  $2.44 - 2.48 \times 10^{-6}$ /°C for Si<sub>x</sub>N<sub>y</sub> [2.6], and  $2.5 \times 10^{-6}$ /°C for Si. For the gate electrode, the TCE ranges from  $3.6 \times 10^{-6}$ /°C (for TaN [2.7]) to  $7 \times 10^{-6}$ /°C (for Ta [2.8]), depending on the stoichiometry.

With the presence of the SiN capping layer during the S/D anneal, limited expansion of the TaN gate in the upward direction is allowed. This results in a compressive stress being exerted onto the Si fin, as illustrated in Fig. 2.6(a). This compressive stress in the channel can be retained even after the SiN capping layer is removed. Figure 2.6(b) illustrates that due to the unique structure of the FinFET device, a constrained expansion of the metal gates on both the left and the right side of the fin effectively compresses or squeezes the fin on at least two sides. The stress is exerted perpendicularly to the fin sidewall with a (110) surface orientation, and the current conduction occurs in the  $<\overline{1}$  10> direction. To study this effect, one can look at the piezoresistance coefficient [2.9] which relate the effect of resistivity and stress as shown by

$$\frac{\Delta \rho_{\omega}}{\rho} = \sum_{\lambda=1}^{6} \Pi_{\omega\lambda} X_{\lambda} , \qquad (2.1)$$

where  $X_{\lambda}$  is the component of the stress in six-component vector notation and  $\Pi_{\omega\lambda}$ is the component of the piezoresisance tensor. The tensor  $\Pi_{\omega\lambda}$  is given by

$$\left[ \Pi_{\omega\lambda} \right] = \begin{bmatrix} \Pi_{11} & \Pi_{12} & \Pi_{12} & 0 & 0 & 0 \\ \Pi_{12} & \Pi_{11} & \Pi_{12} & 0 & 0 & 0 \\ \Pi_{12} & \Pi_{12} & \Pi_{11} & 0 & 0 & 0 \\ 0 & 0 & 0 & \Pi_{44} & 0 & 0 \\ 0 & 0 & 0 & 0 & \Pi_{44} & 0 \\ 0 & 0 & 0 & 0 & 0 & \Pi_{44} \end{bmatrix}$$

In particular, we are interested in the longitudinal piezoresistance coefficient ( $\Pi_l$ ) when the current and field are in the same direction as the applied stress and also the transverse piezoresistance coefficient ( $\Pi_l$ ) where the current and field are perpendicular to the applied stress. We have

$$\Pi_{l} = \Pi_{11} - 2(\Pi_{11} - \Pi_{12} - \Pi_{44})(l_{1}^{2}m_{1}^{2} + m_{1}^{2}n_{1}^{2} + n_{1}^{2}l_{1}^{2}),$$

$$\Pi_{t} = \Pi_{12} + \left(\Pi_{11} - \Pi_{12} - \Pi_{44}\right) \left(l_{1}^{2} l_{2}^{2} + m_{1}^{2} m_{2}^{2} + n_{1}^{2} n_{2}^{2}\right),$$

$$c\phi \equiv \cos\phi$$

,  $s\phi \equiv \sin\phi$ ,

and

$$\begin{bmatrix} l_1 & m_1 & n_1 \\ l_2 & m_{21} & n_2 \\ l_3 & m_3 & n_3 \end{bmatrix} = \begin{bmatrix} c\phi c\theta c\varphi - s\phi s\psi & s\phi c\theta c\psi + c\phi s\psi & -s\theta c\psi \\ -c\phi c\theta s\psi - s\phi c\psi & -s\phi c\theta s\varphi + c\phi c\psi & s\theta s\psi \\ c\phi s\theta & s\phi s\theta & c\theta \end{bmatrix}$$

It can thus be seen from eq. 2.1 that when the stress applied is compressive (negative), depending on the configuration (direction of applied stress with respect to the direction of current flow, surface orientation, and type of carrier), a positive value of  $\Pi_l$  or  $\Pi_t$  is desired for a reduction of resistivity and hence an increase in the mobility of carriers.

Under this configuration, the transverse piezoresistance coefficient is positive  $(+52 \times 10^{-12} \text{ cm}^2/\text{dyne})$  for electron conduction, and given that the applied stress is compressive (negative), a reduction in the channel resistance can be deduced from the above simple consideration of the piezoresistance effect. In addition, the transverse compressive strain component in the Si fin is related to the longitudinal tensile strain component by the Poisson's ratio, both of which contribute to mobility enhancement.

The  $I_D$ - $V_D$  characteristics of a 75 nm gate length  $L_G$  FinFET is shown in Fig. 2.7(a) with the current being normalized by 2 times of the fin height  $H_{fin}$ . The strained-channel FinFET gives a significantly higher drive current compared to the control FinFET. The subthreshold swing of the devices is comparable, as shown in Fig. 2.7(b). Furthermore, they also demonstrate similar drain-induced barrier lowering (DIBL). Transconductance measurements, as plotted in Fig. 2.8

Fig. 2.7. (a)  $I_D$ - $V_D$  characteristics of control and strained FinFET devices at various gate over-drives. The strained FinFET has significantly higher drive current. (b) Subthreshold characteristics of the control and strained FinFET devices at  $V_D = 0.1$  V and  $V_D = 1.8$  V.

Fig. 2.8. Comparison of transconductance of the strained and control devices. The higher peak transconductance seen for the strained device, indicate a higher mobility.

shows a higher peak linear transconductance for the strained-channel FinFET compared to the control FinFET, indicating electron mobility enhancement as a result of the strain. It can also be observed that the strained FinFET exhibits a lower threshold voltage compared to the control FinFET. This could be contributed by the lowering of the conduction band energy due to the strain effect.

In this work, it is shown that the metal gate can affect the transistor performance through the stress developed during the fabrication process. While gate work function tuning, process integration, and compatibility with gate dielectric continue to be major challenges in metal gate technology development, stress contribution from the metal gate should not be disregarded, particularly since stress-induced mobility variation could result in degradation in device performance. Although the drive current of n-channel FinFETs can be enhanced by this process, the performance of p-channel devices would be degraded. For CMOS fabrication, a selective removal of the SiN capping layer over the pchannel devices should be performed prior to the S/D anneal to achieve overall performance enhancement.

## 2.4 Summary

A simple and cost-effective technique was used to incorporate strain in the channel region of FinFET devices. Annealing of a TaN gate electrode capped with a SiN layer leads to the exertion of a compressive stress on the Si fin. This results in a significant enhancement of the drive current in n-channel FinFETs. This approach may be applicable to other metal gate materials having a mismatch in thermal expansion coefficient with surrounding materials like silicon oxide and silicon nitride.

## **2.5 References**

- [2.1] X. Huang, W. C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y.-K. Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, C. Hu, "Sub-50 nm p-channel FinFET," *IEEE Trans. Electron Devices*, vol. 48, no. 5, pp. 880 886, May 2001.

- [2.2] Z. Krivokapic, C. Tabery, W. Maszara, Q. Xiang and M.-R. Lin, "High performance 45 nm CMOS technology with 20 nm multi-gate devices," *SSDM*, 2003, pp. 760-761.

- [2.3] N. Collaert, A. De Keersgieter, K. G. Anil, R. Rooyackers, G. Eneman, M. Goodwin, B.Eyckens, E. Sleeckx, J.–F. de Marneffe, K. DE Meyer, P. Absil, M. Jurczak, and S. Biesemans, "Performance improvement of tall triple gate devices with strained SiN layers," *IEEE Electron Device Letters*, vol. 26, no. 11, pp. 820-822, 2005.

- [2.4] F.-L. Yang, H.-Y. Chen, C.-C. Huang, C.-H. Ge, K.-W. Su, C.-C. Huang, C.-Y. Chang, D.-W. Lin, C.-C. Wu, J.-K. Ho, W.-C. Lee, Y.-C. Yeo, C. H. Diaz, M.-S. Liang, J. Y.-C. Sun, and C. Hu, "Strained FIP-SOI (FinFET/FD/PD-SOI) for sub-65 nm CMOS scaling," *Symp VLSI Tech. Dig.*, 2003, pp. 137-138.

- [2.5] C.-H. Chen, T. L. Lee, T. H. Hou, C. L. Chen, C. C. Chen, J. W. Hsu, K. L. Cheng, Y. H. Chiu, H. J. Tao, Y. Jin, C. H. Diaz, S. C. Chen and M. S. Liang, "Stress memorization technique (SMT) by selectively strained-nitride capping for Sub-65 nm high performance strained-Si device application," *Symp VLSI Tech. Dig.*, 2004, pp. 56-57.

- [2.6] A. K. Sinha, H. J. Levinstein, and T. E. Smith, "Thermal stresses and cracking resistance of dielectric films (SiN, Si3N4, and SiO2) on Si substrates," *J. Apply. Phys.*, April 1978, pp. 2423-2426.

- [2.7] M. Kadoshima, K. Akiyama, K. Yamamoto, H. Fujiwara, T. Yasuda, T. Nabatame, A. Toriumi, "Improved C-V characteristics of metal-oxide-semiconductor capaacitors with tantalum nitride gate electrode grown by ultra-low-pressure chemical vapor deposition," *J. Vac. Sci. Technol. B*, 23(1) Jan/Feb 2005, pp. 42-47.

- [2.8] J. Jung, H. Nam, B. Lee, J. O. Byun and N. S. Kim, "Fiber bragg grating temperature sensor with controllable sensitivity," *Applied Optics*, Vol. 38, No. 13, 1 May 1999, pp. 2752-2754.

- [2.9] Y. Kanda,"A graphical representation of the piezoresistance coefficients in silicon," *IEEE Trans Electron Devices*, Vol. 29, No. 1, Jan 1982, pp. 64-70.

## **Chapter 3**

# Plasma Etching of Gate Electrode and Gate-Stringer for the Fabrication of Nanoscale Multiple-Gate

## 3.1 Background

Advanced transistor structures such as multiple-gate transistors or FinFETs enable scalability to sub-10 nm gate lengths due to improved control of shortchannel effects. Major gate-etch issues in fabricating planar transistors relate to the achievement of a vertical gate sidewall profile, high etch selectivity between gate electrode and gate dielectric materials, and the control of critical dimension (CD) or gate length variability. In the fabrication of FinFETs, the fin topology over which the gate material straddles introduces additional gate etch challenges. While the gate etch process for FinFET fabrication was recently modeled [3.1], there are few reports discussing the gate etch challenges [3.2]-[3.3]. Except in one report where the removal of gate hardmask stringers [3.4] is discussed, most reports focus on the electrical characteristics of FinFETs [3.5]-[3.9]. There is also little discussion on the enabling etching technology that allows gate formation over fin structures. Issues related to the increased topography need to be considered. In particular, the gate electrode material is deposited over a step introduced by the fin, and a gate stringer is typically formed by the sidewalls of the fins or active regions as seen earlier in chapter 2. Removal of the gate stringer can be performed in a gate over-etch step, but this could lead to either etching away of the fin or gate-line breakage, especially for aggressive gate dimensions when the etch process is not optimized.

In this chapter, we report an improved gate etch process technology for FinFET fabrication that enables a prolonged gate over-etch for gate stringer removal. The gate etch process was experimentally verified using FinFETs with sub-50 nm gate lengths.

## **3.2 Experiment**

Experiments were performed using 8-inch silicon-on-insulator (SOI) wafers with 140 nm of buried silicon oxide and 50 nm of Si. A reactive ion etching (RIE) system (Applied Material P5000 Etcher) was employed for patterning the mesa-isolated active regions. The active regions comprise silicon fins with a fin width  $W_{Fin}$  of about 30 nm. SiO<sub>2</sub> with a thickness of 6 nm was then deposited using PECVD to act as a dummy gate dielectric. Silicon with a thickness of 100 nm was then deposited using LPCVD as the gate electrode material. A 50 nm SiO<sub>2</sub> hardmask covered the gate electrode material prior to the optical lithography step. Sub-50 nm linewidths were patterned using 248 nm lithography and resist trimming. The pattern was transferred to the hardmask and the photoresist was removed before the etching of the gate electrode using a RIE system. Tilted- SEM and CD-SEM measurements were used to characterize the transistor structure and the etching rate. In this study, HBr, Cl<sub>2</sub>, and He/O<sub>2</sub> gas chemistries were used for the gate etch process.

#### **3.3 Results and Discussion**

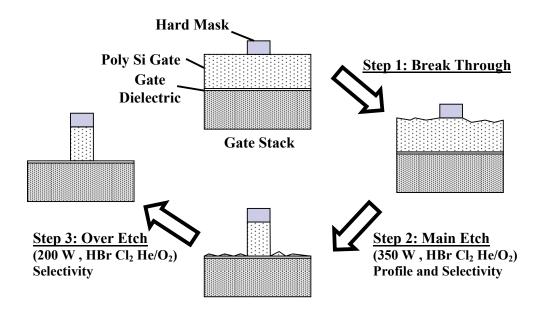

Fig. 3.1. Illustration of the various steps and the requirement in a typical gate etch process.

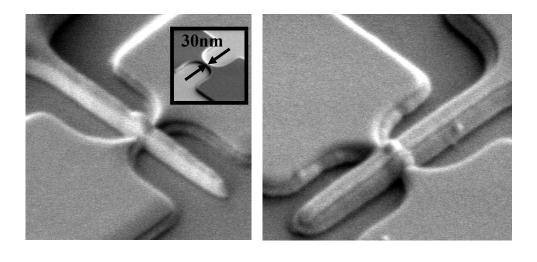

The gate-etch process typically comprises several steps, including the breakthrough step, the main etch, and the over-etch step. A simply illustration of these steps are seen in Fig 3.1. High anisotropy in the main etch ensures a good gate electrode profile, while high selectivity in the over-etch step maintains minimum loss of the gate dielectric. During the fabrication of the FinFET structure, however, a gate stringer can be formed adjacent to the fin structure due to the topography created by the fin step height, as shown in the SEM image in Fig. 3.2.

The gate stringer is formed in the same way as the formation of the silicon nitride spacer adjacent to the gate. If un-removed, the gate stringer would result in a large overlap capacitance between the gate and the source/drain regions, and is therefore detrimental for circuit applications. The amount of over-etching to be

Fig. 3.2. SEM image of a FinFET device formed without an extended gate overetch step, showing the existence of an uncleared gate stringer surrounding the active region. This leads to increased overlap capacitance and reduced circuit speed.

performed in this case depends on the fin height  $H_{Fin}$ , and also on the uniformity of the gate deposition process. From a device perspective, the device width of a triple-gate FinFET is given by  $(2H_{Fin} + W_{Fin})$  [3.7]. Since a taller fin gives a higher drive current and better layout efficiency, tall fins are desirable. Nevertheless, the gate-stringer will be thicker when the fin is taller.

An extended over-etch step for gate stringer removal is required and this places a greater process challenge on the FinFET gate-etch. Furthermore, in the fabrication of a triple-gate transistor where the top surface of the fin is cover by an ultrathin gate dielectric, a higher etch selectivity between the gate electrode and the gate dielectric material is required since the gate dielectric on the top surface of the fin would have been exposed during the gate stringer removal or over-etch step. Alternatively, a thick fin hardmask can be adopted and this can helps to protect the fin during the extended over-etch process for the clearing of the gate residue. This method was actually adopted in chapter 2 to protect the fin during metal gate etch process. However, due to the thicker fin hardmask at the top surface, the effective conduction channel will only be from the 2 sidewalls, making this a double-gate FinFET device. For better short channel effects control, a Tri-gate FinFET is preferred over the double-gate FinFET structure [3.8] and hence the process development done in this chapter allows us to fabricate a Tri-gate FinFET device to be used in later works.

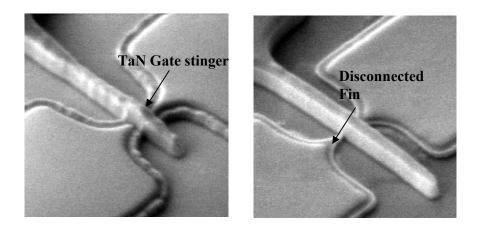

Figure 3.3(a) shows a SEM image of a FinFET structure that underwent excessive gate over-etch step with a long over-etch time. The gate etch process used to form the structure in Fig. 3.3 is detailed in Table 3.1. As observed in the SEM image, the gate stringer can be cleared but this resulted in a broken gate line.

(a)

(b)

Fig. 3.3. (a) SEM image of a FinFET that underwent excessive gate over-etch process. The lateral etch component during the over-etch step leads to significant gate uncut. The gate line can be broken at the narrowest portion or where there is severe line-edge roughness. (b) SEM image showing the top-view of a FinFET with gate-pattern. The gate line is narrowest at both sides of the silicon fin.

| Step         | Power (W) | Etchants (sccm)                                       | Time (s) |

|--------------|-----------|-------------------------------------------------------|----------|

| Breakthrough | 300       | CF <sub>4</sub> (35)                                  | 5        |

| Main Etch    | 350       | HBr (70), Cl <sub>2</sub> (30), He-O <sub>2</sub> (5) | Endpoint |

| Over Etch    | 200       | HBr (60), Cl <sub>2</sub> (20), He-O <sub>2</sub> (6) | 20       |

Table 3.1. Gate-etch process conditions used to form the FinFET structure in Fig. 3.3. Etchants used and the flow-rates are included. The main etch employed end-point detection.

Fig. 3.4. Lateral etch rate of a silicon gate electrode (left axis) and vertical etch rate of silicon oxide (right axis) with varying HBr/(HBr +  $Cl_2$ ) flow rate ratio.

This is because the extended gate over-etch step is significantly isotropic and the lateral etch component leads to an under-cut etch occurring at the sidewalls of the gate. This causes the gate line to break for very small linewidths or where there is significant line-edge roughness. An example is shown in Fig. 3.3(b) where the narrowest portion of the gate lines is broken.

In order to reduce the lateral etch rate in the over-etch step, the etchant composition was varied. To monitor the amount of lateral etch, the hardmask CD was measured prior to the gate etch, and the poly gate CD was measured after etch and hardmask removal using dilute HF. The difference between the hardmask CD and the gate CD after etch was used to obtain the lateral etch rate. Figure 3.4 plots the lateral etch rate as a function of the HBr/(HBr +  $Cl_2$ ) flow rate ratio. The maximum lateral etch rate occurs at 50% HBr composition in a mixture of HBr and  $Cl_2$ . The vertical etch rate of silicon oxide is not affected much by changing the gas composition, which may be attributed to the low RF power used. By tuning the over-etch step, we could effectively reduce the amount of gate undercut, achieving a minimum undercut etch rate of about 1 nm/s for the range of HBr/(HBr +  $Cl_2$ ) flow rate ratio used in this work.

Another approach to limit the extent of lateral etch of the FinFET gate electrode is investigated in this work: increase the amount of gate sidewall passivation layer which provides some protection of the gate electrode from a

Fig. 3.5. By increasing the He- $O_2$  flow rate in the main etch step from 5 to 18 sccm, increased sidewall surface passivation was achieved. This contributed to adequate sidewall protection during the over-etch step. Consequently, the FinFET gate electrode did not suffer from an undercut even during the extended over-etch step, as shown in the SEM image.