### HIGH PERFORMANCE CONTROL OF VRM CIRCUITS

MARECAR HADJA

NATIONAL UNIVERSITY OF SINGAPORE

2006

#### HIGH PERFORMANCE CONTROL OF VRM CIRCUITS

#### MARECAR HADJA

(B. Eng., Supélec, France)

### A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF ENGINEERING

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE 2006

#### ACKNOWLEDGEMENTS

I would like to thank all the people who have helped me during my study at the National University of Singapore. First and foremost, I would like to express my sincere appreciation to my advisor Prof. Ramesh Oruganti for his guidance, encouragement and support throughout the course of this work. His integrity and creativeness has always amazed me above all. The research attitude I learned from him is maybe even more important than the knowledge of power electronics.

I am also grateful to Dr Kanakasabai Viswanathan, research fellow at the Center for Power Electronics, and to my colleague Cao Xiao for their countless instances of help. The continuous interaction with them has helped me a lot in my research work, which would have taken much longer time without their assistance. My sincere thank to the lab officers, Mr. Teo Thiam Teck, Mr Seow Heng Cheng, Mr Woo Ying Chee and Mr Chandra, who readily extended me help whenever I needed. I would like to extend my sincere appreciations to Mr Abdul Jalil Bin Din for his prompt PCB fabrication services.

It has been a great pleasure to work in the Center for Power Electronics, not only because of the talented colleagues but also the numerous friendships I made there. I would like to thank all my colleagues and friends in the Center for Power Electronics for their kindness and professionalism, which made my stay at the National University of Singapore pleasant and unforgivable. Among them, special thanks are due to my colleagues Krishna Mainali, Yin Bo, Deng Heng, Singh Ravinder Pal and Chen Yu to name a few, for the countless discussion both related and non-related to power electronics. I am also thankful to my French university Supélec, and the National University of Singapore, for having provided me such an opportunity and having granted me the research scholarship.

My heartfelt appreciation goes towards my parents and family. This work would not have been possible without their constant support and encouragements. I would like to thank in particular, my cousin Hassana Maraicar Amir Aly and his wife Meher Nissa who helped me in many ways during my stay here, in Singapore. I enjoyed much pleasant time with them and their two children, Arshad and Zayed. The energy and stamina of these two little boys has amazed me more than once.

Finally, I would like to dedicate this work to my mother, Mrs Marecar Maimoune Oumalle. Her encouragement and support have been precious in many difficult times. She is a constant source of inspiration for me in real life, and I know I can always count on her. I can never thank God enough for having provided me such a nice mother, and for all the other things I cannot enumerate.

All praise belong to Him alone.

# **Table of Contents**

| SUM  | SUMMARY vi      |                                                                  |      |

|------|-----------------|------------------------------------------------------------------|------|

| LIST | LIST OF FIGURES |                                                                  |      |

| LIST | г оғ Тав        | LES                                                              | xvii |

| CHA  | APTER 1         | INTRODUCTION                                                     | 1    |

| 1.0  | Back            | ground                                                           | 1    |

| 1.1  | Com             | puter power delivery architecture                                | 7    |

| 1.2  | VRM             | I topologies                                                     | 9    |

| 1.3  | Thesi           | s motivation and outline                                         | 18   |

| 1.4  | Thesi           | is Contributions                                                 | 20   |

| Сна  | APTER 2         | VOLTAGE MODE CONTROL METHOD                                      | 22   |

| 2.0  | Intro           | duction                                                          | 22   |

| 2.1  | Selec           | tion of power stage components                                   | 24   |

|      | 2.1.1           | MOSFET selection                                                 | 24   |

|      | 2.1.2           | Output capacitor selection                                       | 27   |

|      | 2.1.3           | Inductor selection                                               | 28   |

|      | 2.1.4           | Switching frequency selection                                    | 28   |

|      | 2.1.5           | Simulation parameters                                            | 29   |

| 2.2  | Inves           | tigation of the power stage dynamics for step load changes       |      |

|      | with            | VMC                                                              | 30   |

|      | 2.2.1           | VMC presentation and equivalent single phase converter           | 30   |

|      | 2.2.2           | Proposed averaged linear large signal model                      | 33   |

|      | 2.2.3           | Voltage controller design                                        | 42   |

|      | 2.2.4           | Simulation results according to the equivalence inductance value | 45   |

|      | 2.2.5           | Critical inductance analysis                                     | 48   |

| 2.3  | Four            | phase interleaved converter: simulation results                  | 54   |

|      |                 |                                                                  | iii  |

| 2.4                                  | Conc              | lusion                                                          | 60  |  |

|--------------------------------------|-------------------|-----------------------------------------------------------------|-----|--|

| Сна                                  | APTER 3           | CURRENT MODE CONTROLS                                           | 61  |  |

| 3.0                                  | Intro             | duction                                                         | 61  |  |

| 3.1                                  | Aver              | age current mode control                                        | 62  |  |

|                                      | 3.1.1             | Presentation                                                    | 62  |  |

|                                      | 3.1.2             | Current Controller design                                       | 63  |  |

|                                      | 3.1.3             | Voltage Controller design                                       | 70  |  |

|                                      | 3.1.4             | Critical inductance analysis                                    | 73  |  |

|                                      | 3.1.5             | Simulation results for the dynamic performance of the converter | 77  |  |

| 3.2                                  | Peak              | current mode control                                            | 82  |  |

|                                      | 3.2.1             | Peak current mode control presentation                          | 82  |  |

|                                      | 3.2.2             | Implementation of the PCMC scheme in the multiphase converter   | 86  |  |

|                                      | 3.2.3             | Control design                                                  | 87  |  |

|                                      | 3.2.4             | Critical inductance                                             | 90  |  |

|                                      | 3.2.5             | PCMC simulation results                                         | 95  |  |

| 3.3                                  | Com               | parison of the VMC, ACMC, PCMC schemes                          | 99  |  |

| 3.4 Conclusion 10                    |                   |                                                                 | 100 |  |

| CHAPTER 4 CURRENT SENSING IN VRM 101 |                   |                                                                 | 101 |  |

| 4.1                                  | Intro             | duction                                                         | 101 |  |

| 4.2                                  | Resis             | tive sensing                                                    | 102 |  |

| 4.3                                  | R <sub>DS</sub> s | ensing                                                          | 105 |  |

| 4.4                                  | Sensi             | ng the inductor voltage                                         | 109 |  |

| 4.5                                  | RC n              | etwork across $Q_2$                                             | 111 |  |

| 4.6                                  | Conc              | lusion                                                          | 113 |  |

| Cha                                  | pter 5            | Novel Current Transformer based Current Sensor                  | 115 |  |

| 5.0                                  | Intro             | duction                                                         | 115 |  |

| 5.1                                  | Curre             | ent Transformer (CT)                                            | 116 |  |

|                                      |                   |                                                                 |     |  |

| 5.3 Design issues in the proposed method125.3.1 AC attenuation125.3.2 Transient error135.3.3 Core saturation13a. DC flux estimation13b. Flux ripple estimation135.3.4 Current sensor power loss analysis135.4 Experimental results135.5 Conclusion14 | 23     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 5.3.2Transient error135.3.3Core saturation13a.DC flux estimation13b.Flux ripple estimation135.3.4Current sensor power loss analysis135.4Experimental results13                                                                                       | :9     |

| 5.3.3Core saturation13a.DC flux estimation13b.Flux ripple estimation135.3.4Current sensor power loss analysis135.4Experimental results13                                                                                                             | :9     |

| a. DC flux estimation13b. Flux ripple estimation135.3.4Current sensor power loss analysis135.4Experimental results13                                                                                                                                 | 1      |

| b.Flux ripple estimation135.3.4Current sensor power loss analysis135.4Experimental results13                                                                                                                                                         | 3      |

| 5.3.4Current sensor power loss analysis135.4Experimental results13                                                                                                                                                                                   | 4      |

| 5.4 Experimental results 13                                                                                                                                                                                                                          | 5      |

|                                                                                                                                                                                                                                                      | 7      |

| 5.5 Conclusion 14                                                                                                                                                                                                                                    | 9      |

|                                                                                                                                                                                                                                                      | -5     |

| CHAPTER 6 CONCLUSION 14                                                                                                                                                                                                                              | 6      |

| 6.0 Background 14                                                                                                                                                                                                                                    | 6      |

| 6.1 Thesis Overview 14                                                                                                                                                                                                                               | -6     |

| 6.1.1 Interleaved VRMs 14                                                                                                                                                                                                                            | 7      |

| a. Modeling, Design, and Control 14                                                                                                                                                                                                                  | 7      |

| b. Comparison of Various Control Techniques 14                                                                                                                                                                                                       | -8     |

| 6.1.2 Current Transformer Based Current Sensor 14                                                                                                                                                                                                    | 9      |

| 6.2Future Works14                                                                                                                                                                                                                                    | .9     |

| REFERENCE 15                                                                                                                                                                                                                                         | 1      |

| PUBLICATION 15                                                                                                                                                                                                                                       | 7      |

| APPENDIX A SIMULATION DETAILS 15                                                                                                                                                                                                                     | 8      |

| A.1 Steady state duty cycle estimation 15                                                                                                                                                                                                            | 8      |

| A.2 PLECS converter circuit diagrams 159                                                                                                                                                                                                             | 9      |

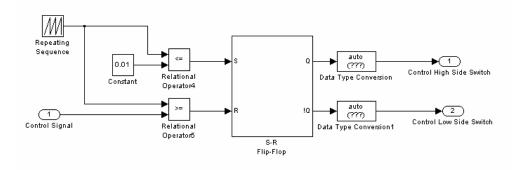

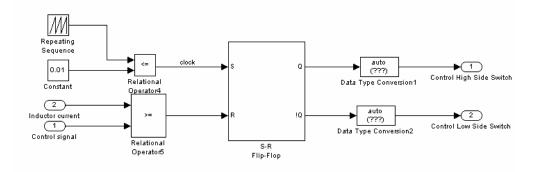

| A.3 Control logic circuit diagram 16                                                                                                                                                                                                                 | 0      |

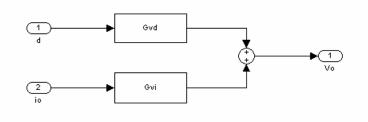

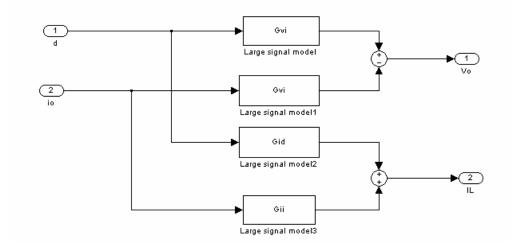

| A.4 Large signal model comparison 16                                                                                                                                                                                                                 | 1      |

| A.5 Control diagrams 164                                                                                                                                                                                                                             | 4      |

| A.6 Switch current estimation circuit diagrams 16                                                                                                                                                                                                    | 9<br>v |

| APPEN | DIX B HARDWARE DETAILS                                   | 170 |

|-------|----------------------------------------------------------|-----|

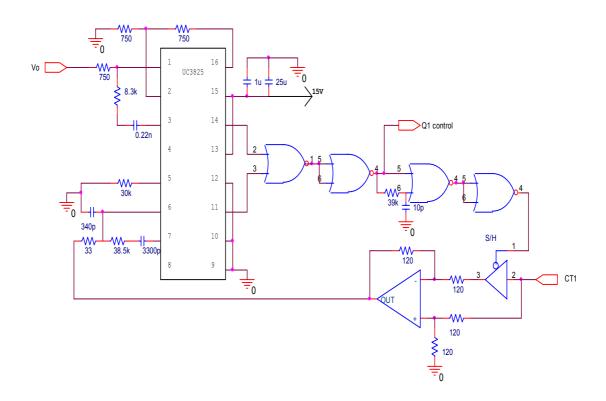

| B.1   | Inductor current estimating scheme                       | 170 |

| B.2   | PCMC scheme using the proposed current sensing technique | 171 |

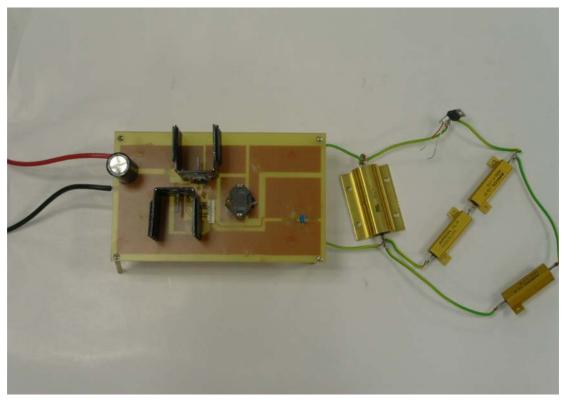

| B.3   | Converter circuit                                        | 172 |

#### **SUMMARY**

Voltage Regulator Modules (VRM), which are used to power advanced microprocessors, have stringent efficiency and transient response requirements. The multiphase buck converter scheme is a popular topology for use in this application because of its ability to handle large load currents and to achieve fast dynamic transient response under large step-load conditions. However, its various advantages are compromised should a significant current unbalance occur either under steady-state or transient conditions among the different phases of the circuit. The first part of this thesis fully investigates this issue for three popular control schemes used currently: Voltage Mode Control (VMC), Average Current Mode Control (ACMC), and Peak Current Mode Control (PCMC).

The concept of critical inductance plays an important part in analyzing the dynamic performance of the converter with each of these schemes. The critical inductance can be defined as the largest inductance capable of achieving the fastest transient response for a given load transient. Analytical results are presented in this thesis which allows one to estimate accurately the critical inductance value for the three control schemes. Simulation results have also been provided to confirm the analytical results.

Among the three control schemes, the VMC was found to be the simplest since only the knowledge of the output voltage is needed for implementing the control scheme. Furthermore, in the multiphase converter, the output voltage ripple frequency in considerably increased using the interleave technique. This allows a higher overall system bandwidth to be realized with the VMC scheme as compared to the current mode control schemes. This has been shown in this work to improve the converter transient response. However, due to the absence of any control over the inductor current, it is also shown that large current unbalances can occur in practice due to component parameter variations. On the other hand, it has been demonstrated that the ACMC and PCMC schemes ensure accurate load sharing between the phases of the converter both during transient and steady state. Among the two current control schemes, the overall bandwidth with the ACMC scheme is significantly lower than that obtained with the PCMC scheme and this results in slow operation of the converter during load induced transients. Thus, it is shown in the first part of the thesis that in modern VRMs where equal current sharing between phases and good dynamic performance are essential, the PCMC scheme is the best candidate.

A critical bottleneck in realizing VRMs with the PCMC scheme is the need for a small, efficient and accurate current sensor for sensing the instantaneous current for implementing the peak current mode control. The second part of the thesis focuses on this topic.

The thesis contains a detailed investigation of current sensing schemes that can be used for current mode control of VRMs. The resistive current sensing scheme is generally popular and used for PCMC schemes. This may be attributed to its accuracy and large bandwidth and also due to its ease of use. However, it can lead to increased losses especially due to the low output voltages involved. Other available current sensing methods for DC-DC converters are also not shown to be very suitable.

In this thesis, a novel current sensing technique capable of high performance based on current transformers is proposed. Current transformers are generally not used in DC-DC converters due their inability to sense DC current. Nevertheless, in this thesis, it is shown that by placing the current transformers at appropriate locations, the lost DC component can be recovered through simple signal processing. The proposed scheme exhibits much higher efficiency than the classical current sense resistor. Besides, if properly designed, the high accuracy and the high bandwidth of the proposed current sensing method allow its use in PCMC schemes. The design issues regarding the novel current sensing method when used in multiphase converters are also covered in this thesis. The requirements and the obtainable accuracy of the proposed current sensor are in particular investigated.

Finally, experimental results on a step down buck converter, controlled in PCMC using such a sensor, are provided to confirm the sensor's performance and suitability with PCMC scheme. The proposed current sensing technique can also be applied to several other types of power converters besides the multiphase buck converter.

# **List of Figures**

| Fig.1.1   | Exponential increase of the number of transistors integrated in a single chip                                                 | 1  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.1. 2  | Evolution of power consumption in the microprocessor [5]                                                                      | 2  |

| Fig.1. 3  | Intel roadmap of the 32-bit CPU load at CPU-system connector [5]                                                              | 3  |

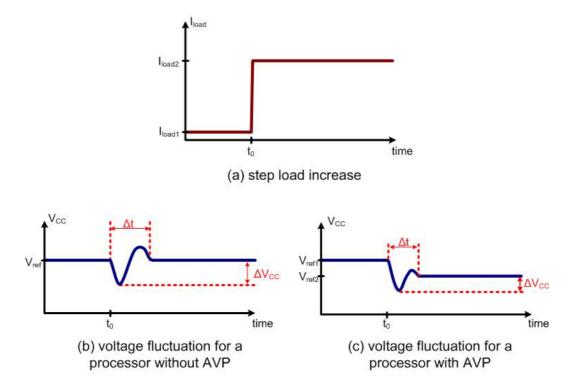

| Fig. 1.4  | Processor equipped with AVP load line [9]                                                                                     | 6  |

| Fig. 1.5  | Comparison of voltage fluctuations during a step load increase between processors with and without AVP                        | 6  |

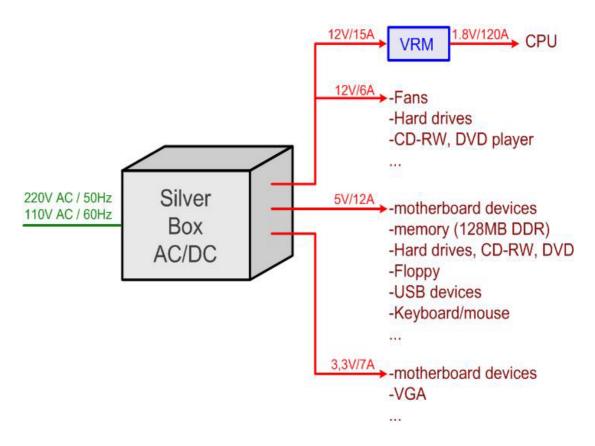

| Fig. 1.6  | Power system architecture commonly used in current desktops                                                                   | 8  |

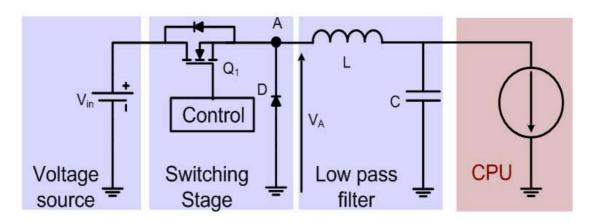

| Fig.1. 7  | Conventional buck converter                                                                                                   | 10 |

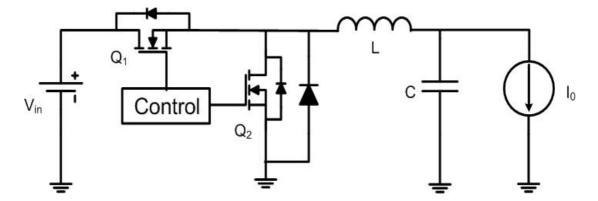

| Fig.1. 8  | Synchronous buck converter with fast recovery diode                                                                           | 10 |

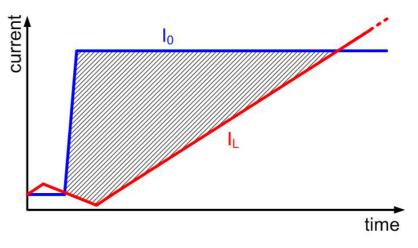

| Fig.1. 9  | Large unbalanced charges during load transient                                                                                | 12 |

| Fig. 1.10 | n-phase interleaved converter                                                                                                 | 13 |

| Fig. 1.11 | Each inductor and overall inductor current in a two phase buck converter                                                      | 14 |

| Fig. 1.12 | Overall current ripple cancellation for a 2-6 phase buck converter [34]                                                       | 14 |

| Fig.1.13  | Basic configuration of stepping inductance based VRM                                                                          | 16 |

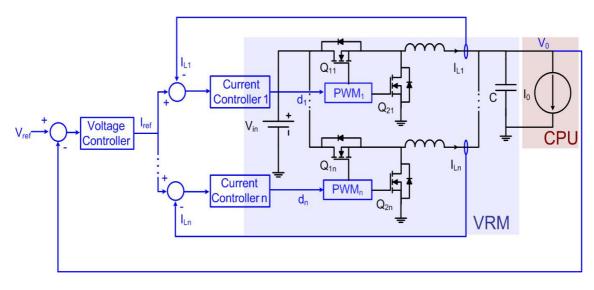

| Fig. 2.1  | Voltage Mode Control scheme in an n-phase buck converter                                                                      | 31 |

| Fig. 2.2  | Average circuit model of the n-channel interleaving buck converter                                                            | 31 |

| Fig. 2.3  | Single phase equivalent model                                                                                                 | 34 |

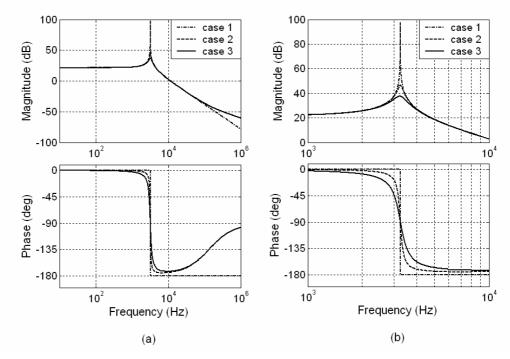

| Fig. 2.4  | Output voltage to duty cycle transfer function for the three cases                                                            | 38 |

| Fig. 2.5  | Output voltage to load transfer function for the three cases                                                                  | 38 |

| Fig. 2.6  | Small signal output voltage to duty cycle transfer function for different average inductor current                            | 39 |

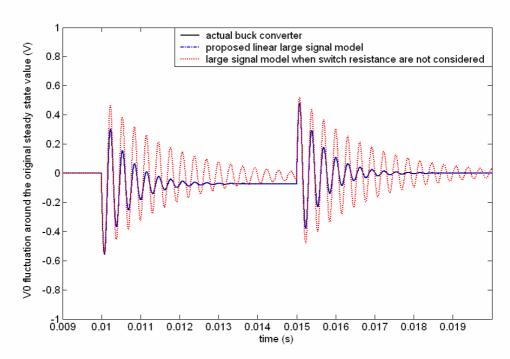

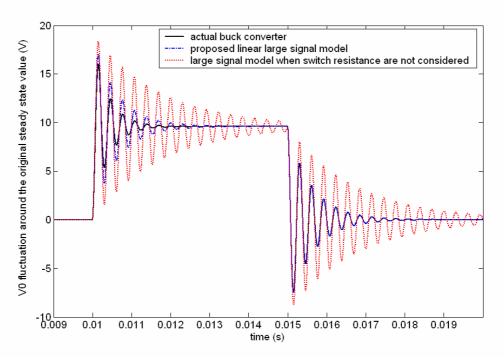

| Fig. 2.7  | Output voltage fluctuation due to a step load from 10A to 100A in the normal buck converter for different large signal models | 41 |

| Fig. | 2.8  | Output voltage fluctuation due to a step variation in the duty cycle from $0.16$ to $0.96$ in the normal buck converter for different large signal model | 41 |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

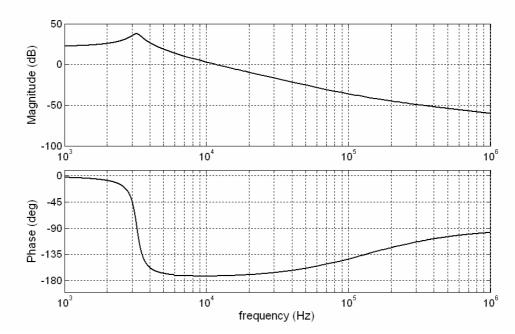

| Fig. | 2.9  | Output voltage to duty cycle transfer function $G_{vd}$ for an equivalent inductance value of 300 nH                                                     | 42 |

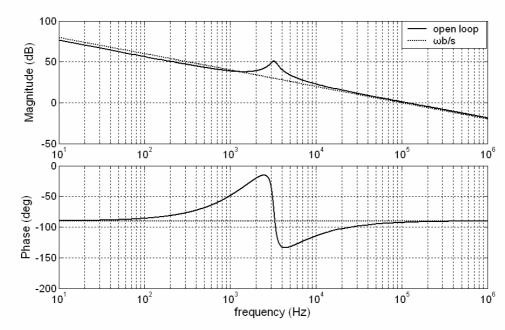

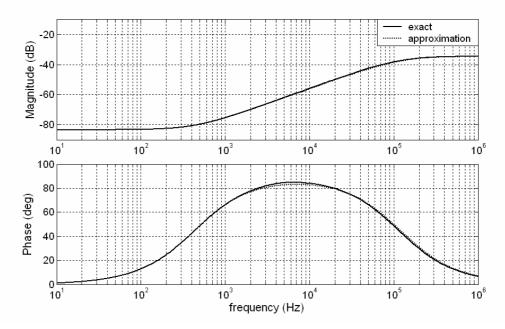

| Fig. | 2.10 | Open loop corrected system and its approximation                                                                                                         | 44 |

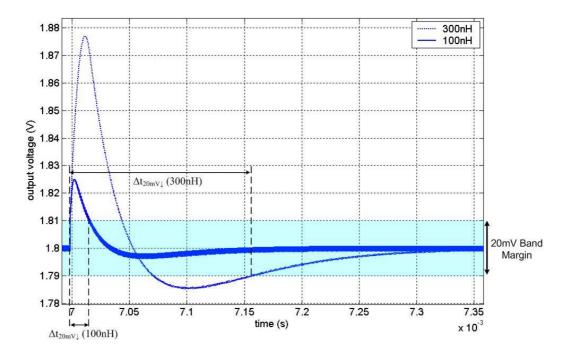

| Fig. | 2.11 | Output voltage waveforms during a load step down for two different inductor values                                                                       | 46 |

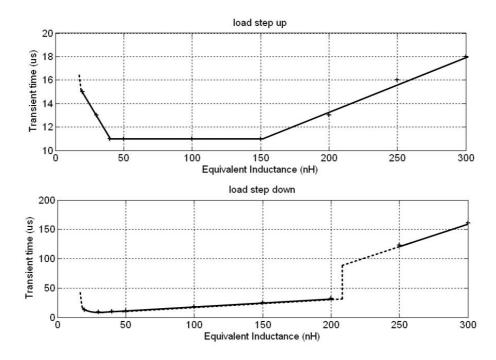

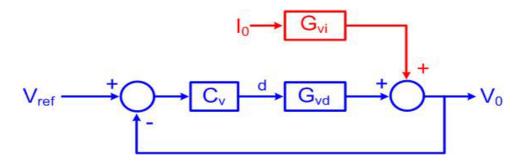

| Fig. | 2.12 | 20 mV-band transient time vs inductance for load step-up and step down                                                                                   | 48 |

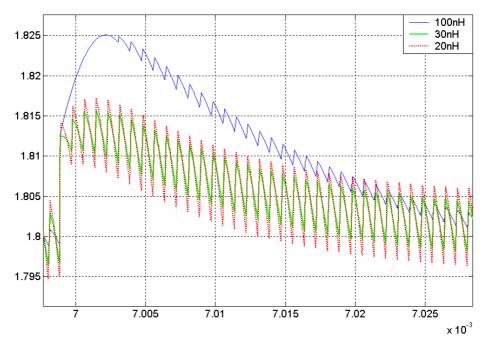

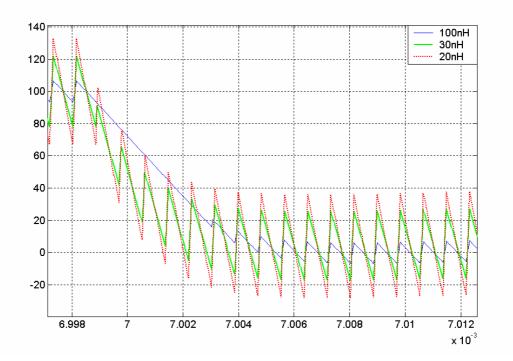

| Fig. | 2.13 | Output voltage fluctuation for three different inductances for a load step up of 90 A                                                                    | 49 |

| Fig. | 2.14 | Inductor current variation during load step down of 90 A for<br>three different inductances                                                              | 49 |

| Fig. | 2.15 | VMC block diagram                                                                                                                                        | 51 |

| Fig. | 2.16 | Bode plot comparison between d/i0and its approximation for an equivalent inductor of 300nH                                                               | 52 |

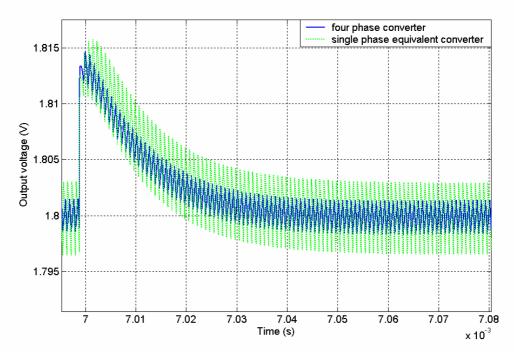

| Fig. | 2.17 | Output voltage response to a load decrease of 90A, in a multiphase converter, and its equivalent single-phase converter                                  | 55 |

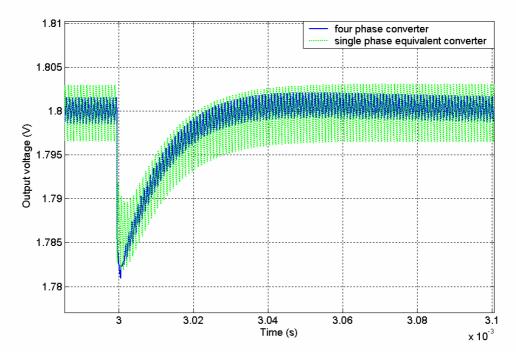

| Fig. | 2.18 | Output voltage response to a load increase of 90A, in a multiphase converter, and its equivalent single-phase converter                                  | 55 |

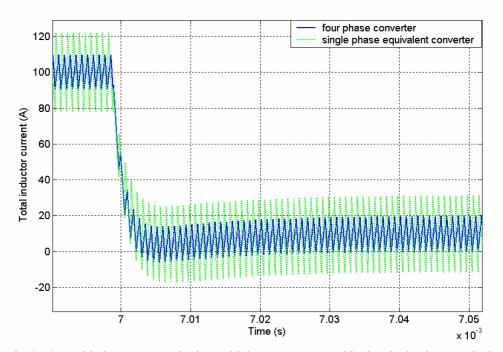

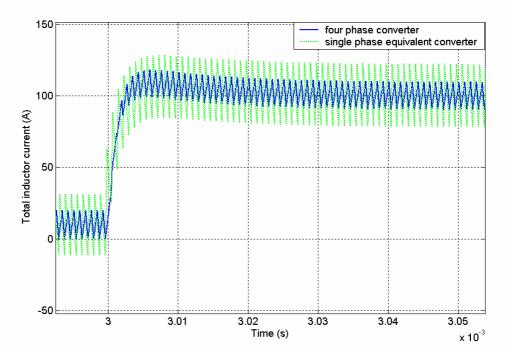

| Fig. | 2.19 | Total inductor current in the multiphase converter and in the single phase equivalent converter                                                          | 56 |

| Fig. | 2.20 | Total inductor current in the multiphase converter and in the single phase equivalent converter                                                          | 56 |

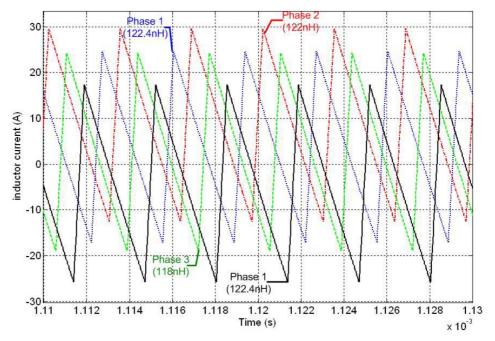

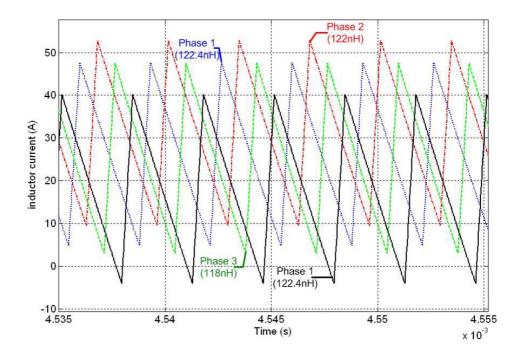

| Fig. | 2.21 | Inductor current in each phase for a light load of 10A                                                                                                   | 58 |

| Fig. | 2.22 | Inductor current in each phase for a high load of 100A                                                                                                   | 58 |

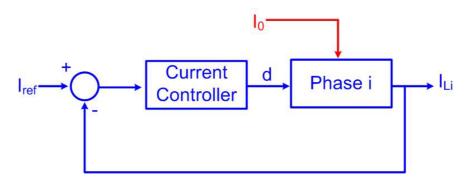

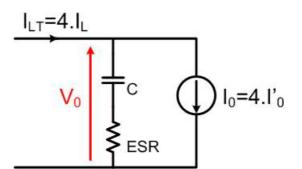

| Fig. | 3.1  | Average Current Mode Control scheme in an n-phase buck converter                                                                                         | 62 |

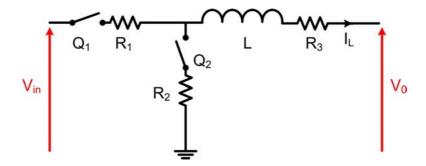

| Fig. | 3.2  | Current loop scheme                                                                                                                                      | 64 |

| Fig. | 3.3  | One channel circuit diagram                                                                                                                              | 64 |

| Fig. | 3.4  | Output Voltage System                                                                                                                                    | 64 |

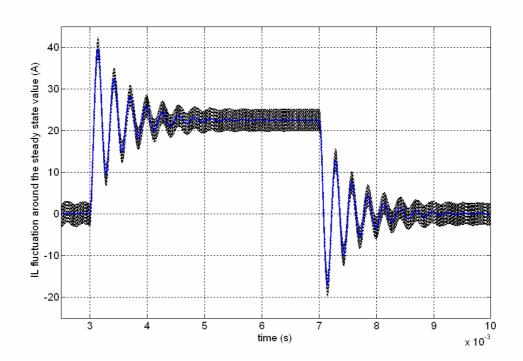

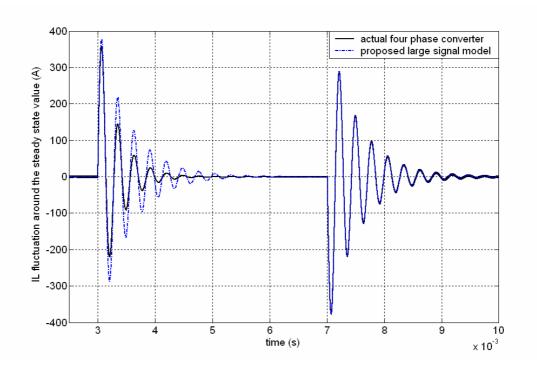

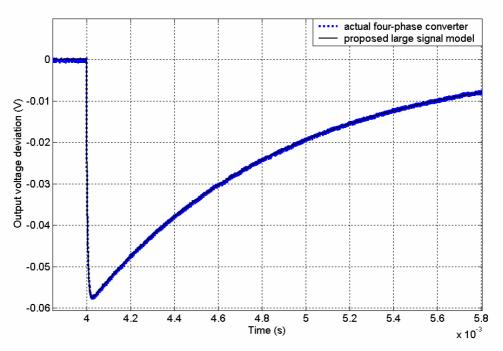

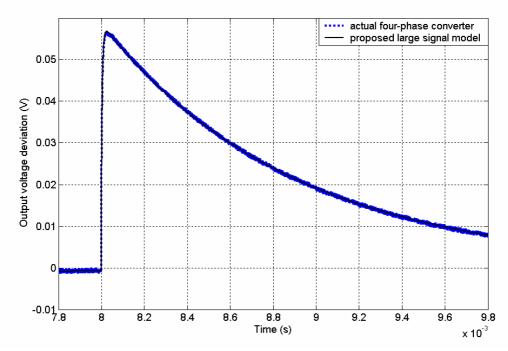

| Fig. 3.5    | Inductor current fluctuation in one channel due to a step load from 10 A A to 100 A using the actual multiphase converter and the large signal model (3.2)                         | 67      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Fig. 3.6    | Inductor current fluctuation in one channel due to a step variation in the duty cycle from $0.16$ to $0.96$ using the actual multiphase converter and the large signal model (3.2) | 67      |

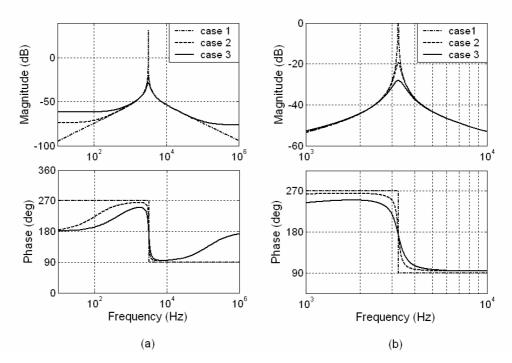

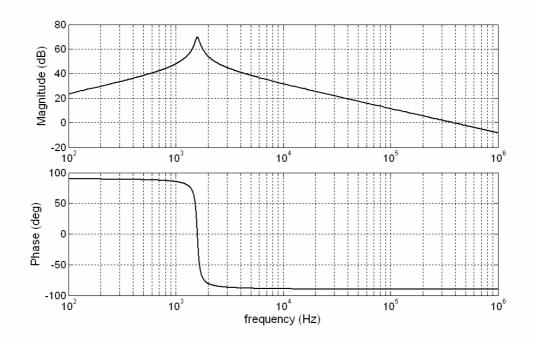

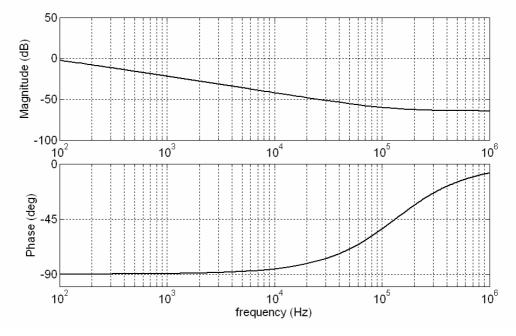

| Fig. 3.7    | Inductor current to duty cycle transfer function for $5\mu$ H inductance                                                                                                           | 69      |

| Fig. 3.8    | Open loop corrected system for the current loop and its approximation                                                                                                              | 69      |

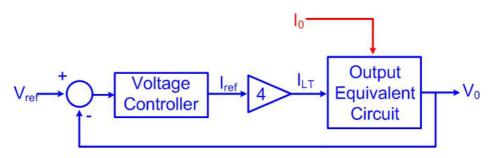

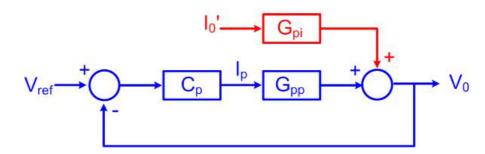

| Fig. 3.9    | Simplified voltage loop scheme for the four-phase converter                                                                                                                        | 70      |

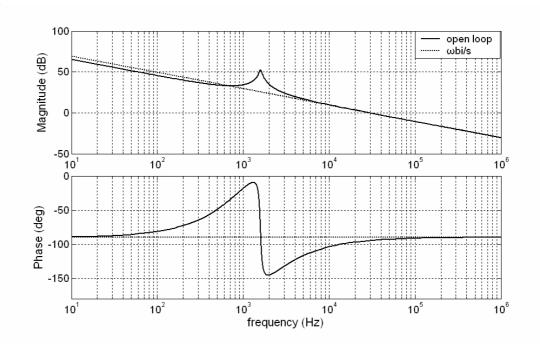

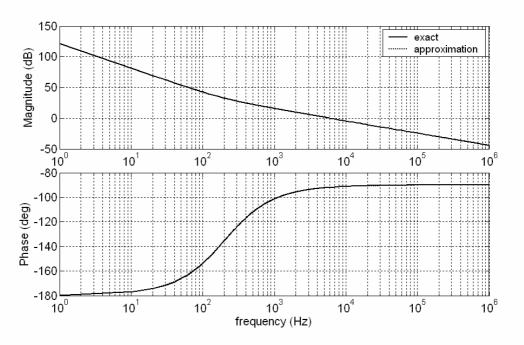

| Fig. 3.10   | $v_0/i_{ref}$ Bode diagram                                                                                                                                                         | 71      |

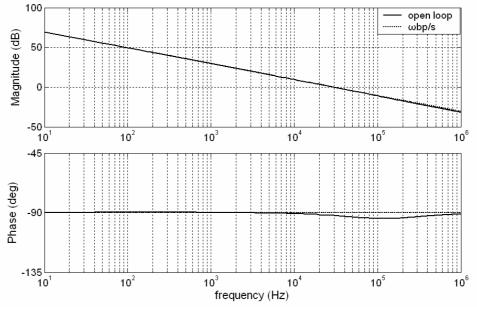

| Fig. 3.11   | Open loop corrected system for the simplified voltage loop and its approximation                                                                                                   | 72      |

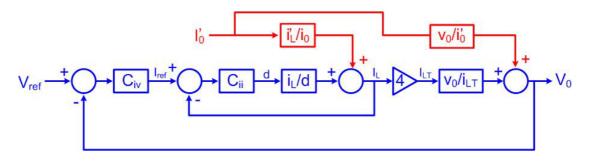

| Fig. 3.12   | Overall ACMC scheme                                                                                                                                                                | 74      |

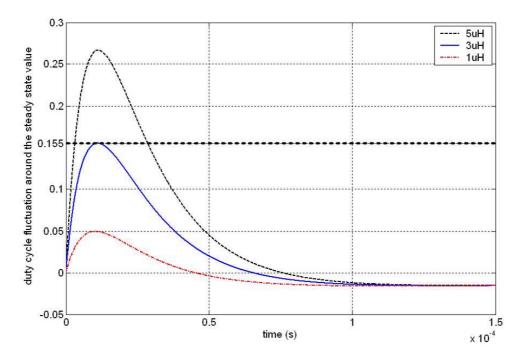

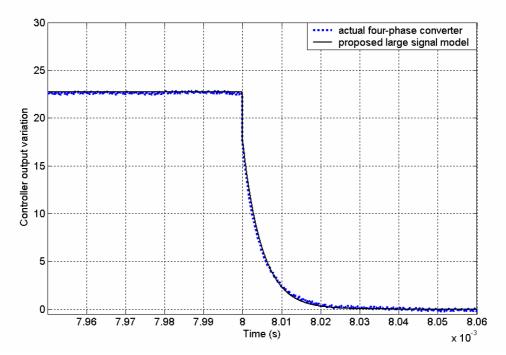

| Fig. 3. 13  | Duty ratio fluctuation around the original steady state due to a step change in the load of 90A                                                                                    | 76      |

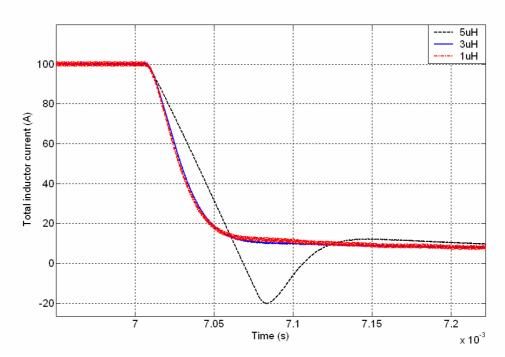

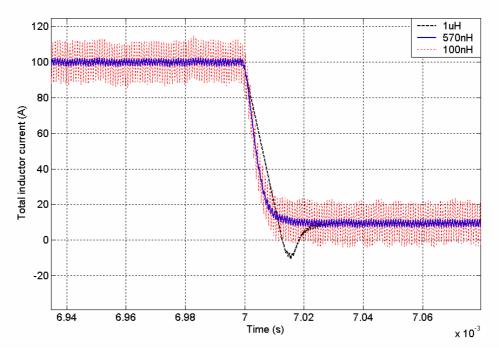

| Fig. 3.14   | Total inductor current waveforms for a load decrease from 100 A to 10 A in the four phase converter for three different values of inductance per Phase                             | 79      |

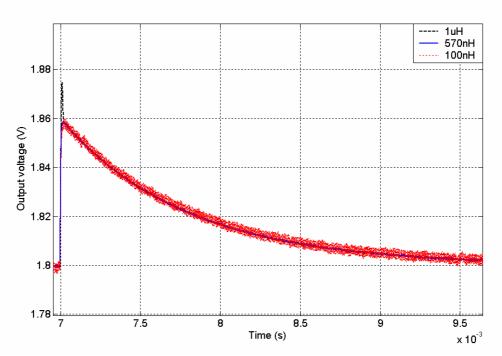

| Fig. 3.15   | Output voltage waveform during a load decrease from 100 A to 10 A in the four phase converter for three different values of inductance values per phase                            | 79      |

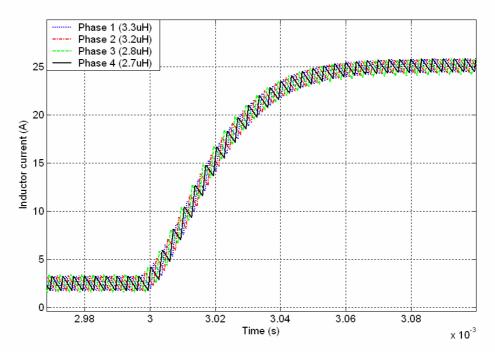

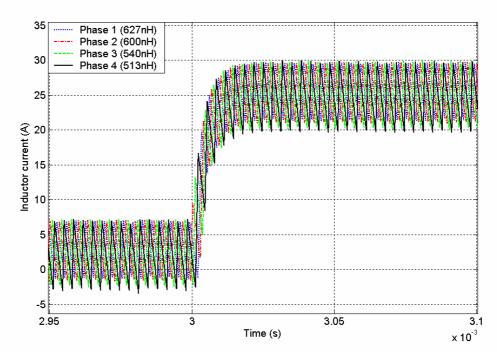

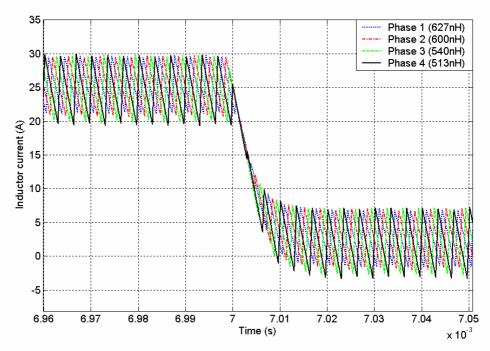

| Fig. 3.16   | Inductor current variation in each phase for a load increase from 10 A to 100 A                                                                                                    | )<br>81 |

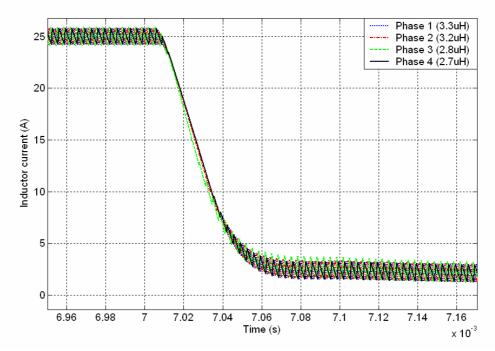

| Fig. 3.17 I | nductor current variation in each phase for a load decrease from 100 A to 10 A                                                                                                     | )<br>81 |

| Fig. 3.18   | PCMC logic scheme                                                                                                                                                                  | 82      |

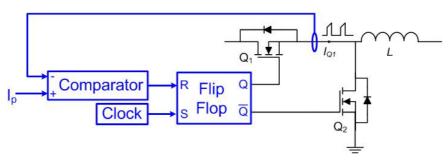

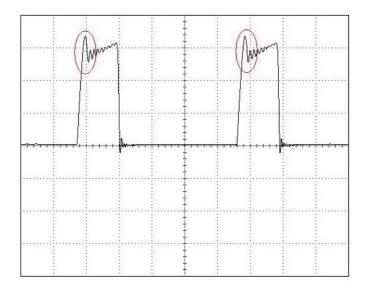

| Fig. 3.19   | Peak in the input current due to reverse recovery current of $Q_2$ 5A/DIV, 1µs/DIV                                                                                                 | 84      |

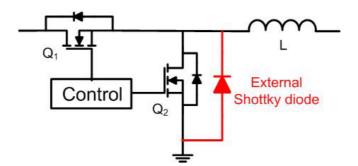

| Fig. 3. 20  | External Shottky diode placed in parallel with the synchronous MOSFET                                                                                                              | 84      |

| Fig. 3.21   | Inductor current instability in PCMC                                                                                                                                               | 84      |

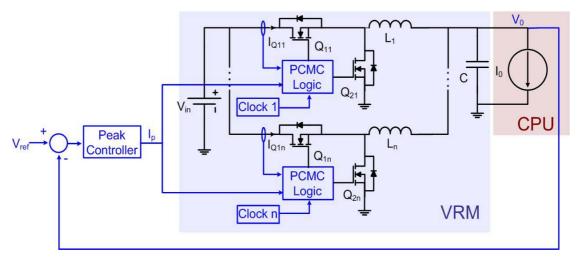

| Fig. 3. 22  | Peak current mode control scheme in an n-phase buck converter                                                                                                                      | 86      |

|             |                                                                                                                                                                                    |         |

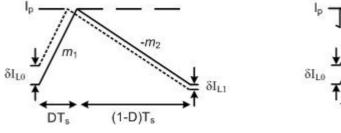

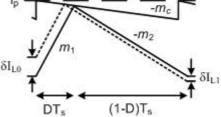

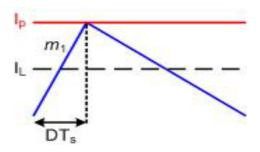

| Fig. 3. 23 | Inductor current in a PCMC scheme                                                                                                                                  | 87  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

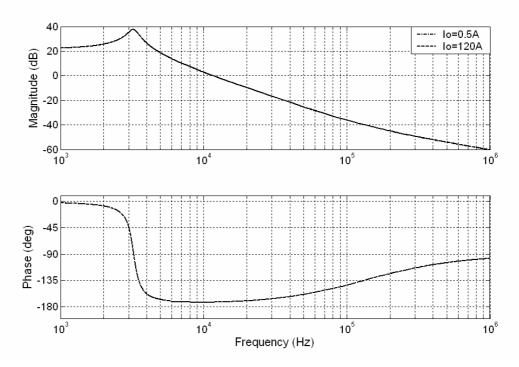

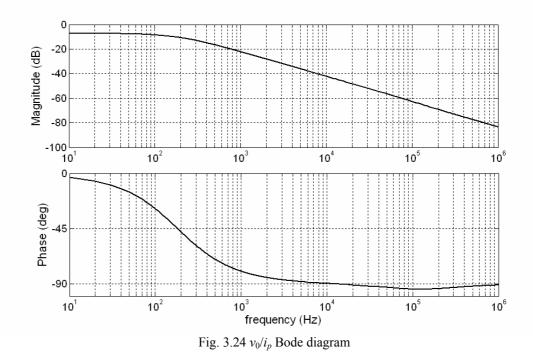

| Fig. 3.24  | $v_0/i_p$ Bode diagram                                                                                                                                             | 89  |

| Fig. 3.25  | Open loop compensated system for the PCMC and its approximation                                                                                                    | 90  |

| Fig. 3. 26 | PCMC simplified block diagram for the four phase converter                                                                                                         | 91  |

| Fig. 3.27  | Output voltage fluctuation comparison for a step change from 10 A to 100 A                                                                                         | 92  |

| Fig. 3. 28 | Output voltage fluctuation comparison for a step change from 100 A to 10 A                                                                                         | 92  |

| Fig. 3.29  | Controller output variations comparison for a load step up from 10 A to 100 A                                                                                      | 93  |

| Fig. 3.30  | Controller output variations comparison for a load step down from 100 A to 10 A                                                                                    | 93  |

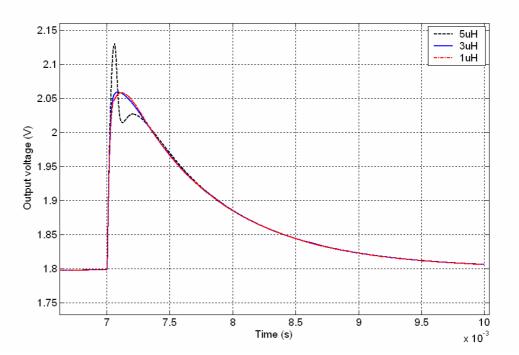

| Fig. 3.31  | Output voltage waveform during a load decrease from 100 A to 10 A in the four phase converter for three different inductance values per phase                      | 97  |

| Fig. 3.32  | Total inductor current waveforms for a load decrease from 100 A to 10 A in the four phase converter for three different inductance values per phase                | 97  |

| Fig. 3.33  | Inductor current variation in each phase for a load increase from 10 A to 100 A                                                                                    | 98  |

| Fig. 3. 34 | Inductor current variation in each phase for a load decrease from 100 A to 10 A                                                                                    | 98  |

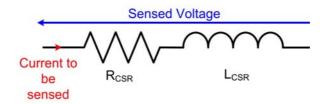

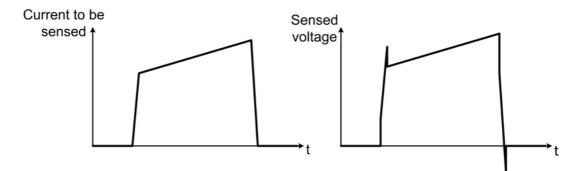

| Fig. 4.1   | CSR model with its self inductance                                                                                                                                 | 104 |

| Fig. 4.2   | Voltage spikes in the sensed signal due to the CSR self inductance                                                                                                 | 104 |

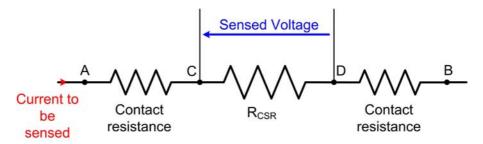

| Fig. 4.3   | Four point sensing technique                                                                                                                                       | 105 |

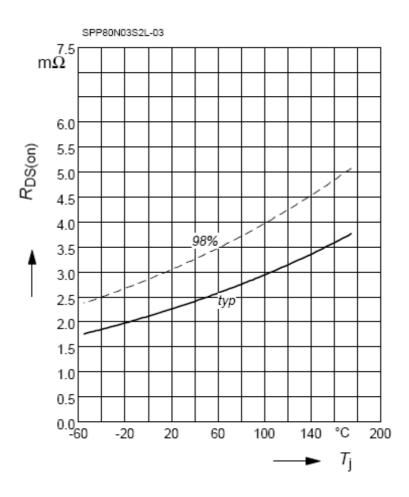

| Fig. 4.4   | On-state resistance variation according to the temperature for a constant drain current of 80A and a gate source voltage of 10V for SPP80N03S2L-03 Infineon MOSFET | 107 |

| Fig. 4.5   | Drain source resistance variation according to the drain current for<br>a given gate source voltage, for SPP80N03S2L-03 Infineon MOSFET                            | 108 |

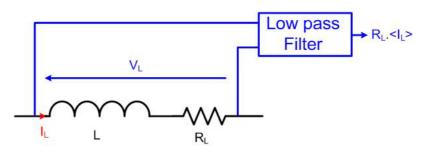

| Fig. 4.6   | Inductor current sensing using a low pass filter                                                                                                                   | 110 |

|            |                                                                                                                                                                    |     |

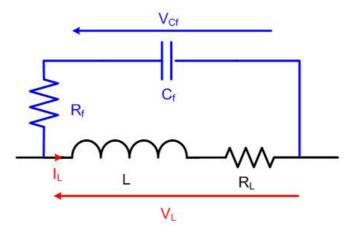

| Fig. 4.7  | Inductor current sensing using resistance and capacitor across the inductor                                                  | 110      |

|-----------|------------------------------------------------------------------------------------------------------------------------------|----------|

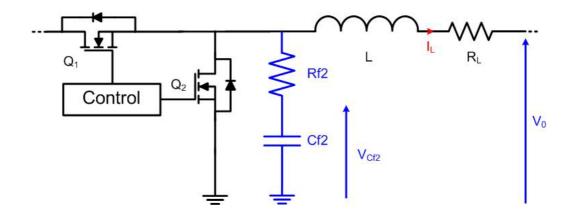

| Fig. 4. 8 | Current sensor using RC network across Q <sub>2</sub>                                                                        | 112      |

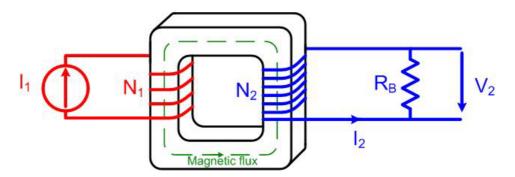

| Fig. 5.1  | Current transformer                                                                                                          | 117      |

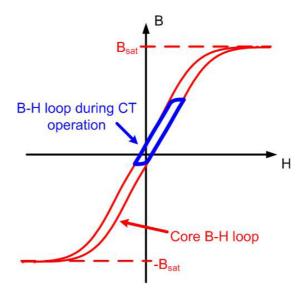

| Fig. 5.2  | B-H characteristics of a typical magnetic core material                                                                      | 117      |

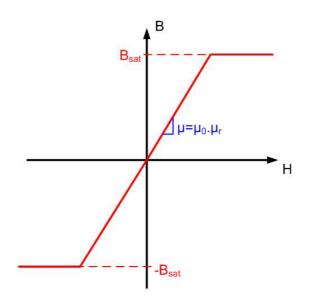

| Fig. 5.3  | Approximation of the B-H characteristics of a typical magnetic core material by neglecting the hysteresis                    | 117      |

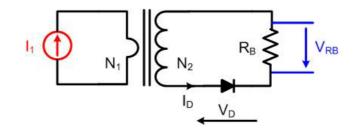

| Fig. 5.4  | Switch current sensing technique using current transformer and a diode                                                       | 121      |

| Fig. 5.5  | A simple model for the CT-diode current sensing technique                                                                    | 121      |

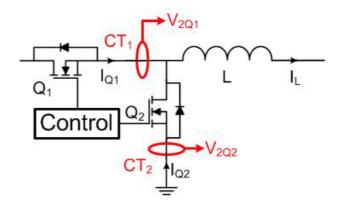

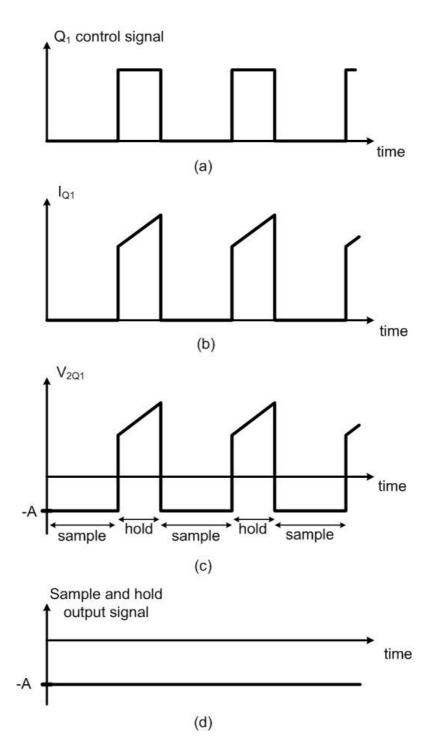

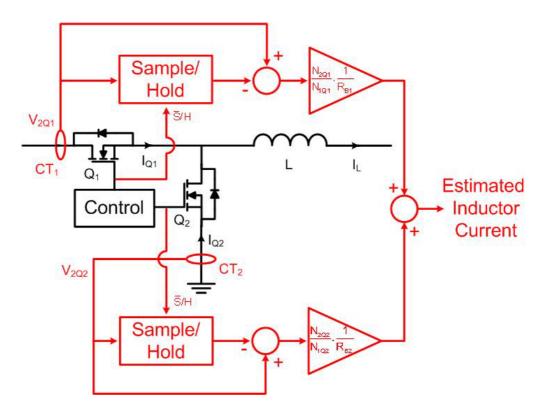

| Fig. 5.6  | One channel of the multiphase converter with current transformers $CT_1$ and $CT2$                                           | 124      |

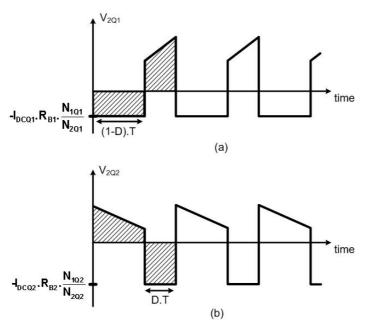

| Fig. 5.7  | Waveforms corresponding to sensing of high side switch $(Q_1)$ current                                                       | 125      |

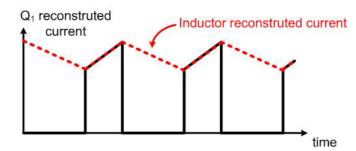

| Fig. 5.8  | Inductor current reconstruction by joining the minimum and the maximum of the high side switch current during switch turn-on | 127      |

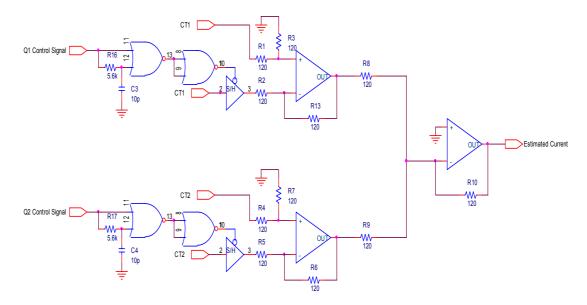

| Fig. 5.9  | Overall inductor current estimation circuit using two current transformers                                                   | 127      |

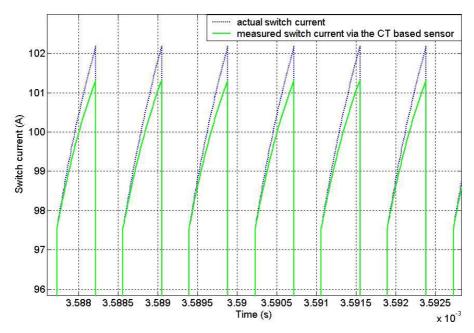

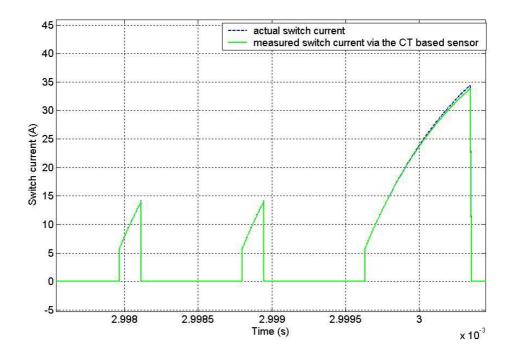

| Fig. 5.10 | Steady state measurement error for a current transformer having 5 turns<br>in the secondary and 50 burden resistance         | s<br>130 |

| Fig. 5.11 | Transient measurement error for a current transformer having 5 turns<br>in the secondary and 50 burden resistance            | 132      |

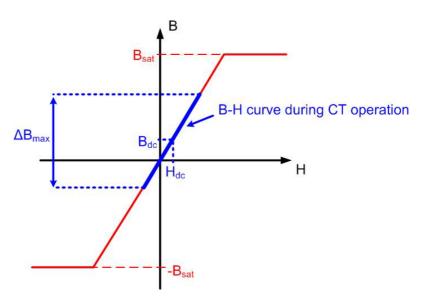

| Fig. 5.12 | B-H curve during CT operation                                                                                                | 134      |

| Fig. 5.13 | Secondary side voltages for the current transformers on (a) the high side and (b) the low side switches                      | 136      |

| Fig. 5.14 | Typical core loss data for a high-frequency power ferrite material [28]                                                      | 138      |

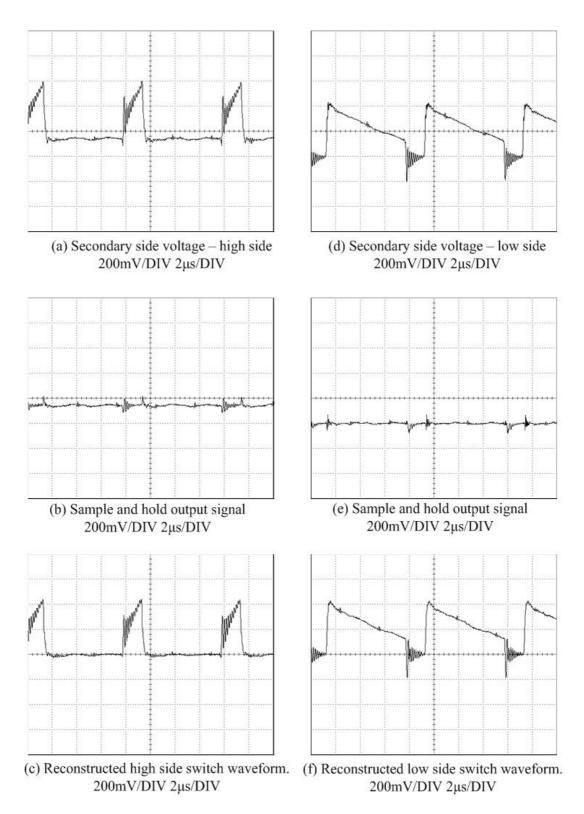

| Fig. 5.15 | Reconstruction of current signal waveform                                                                                    | 141      |

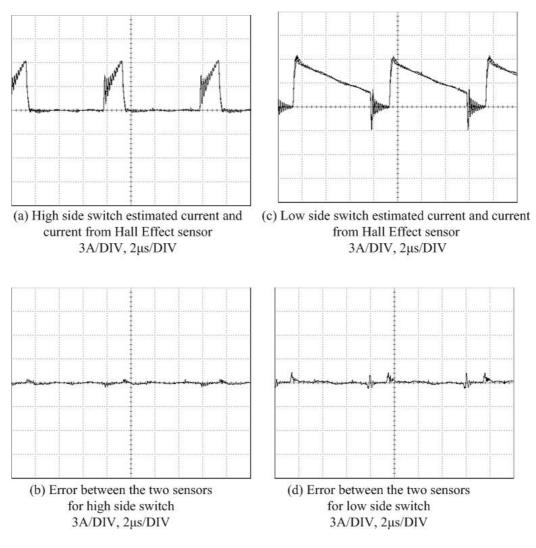

| Fig. 5.16 | Comparison between the current transformer sensor and Hall Effect sensor                                                     | 142      |

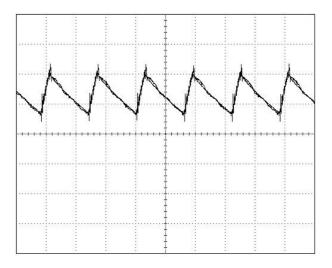

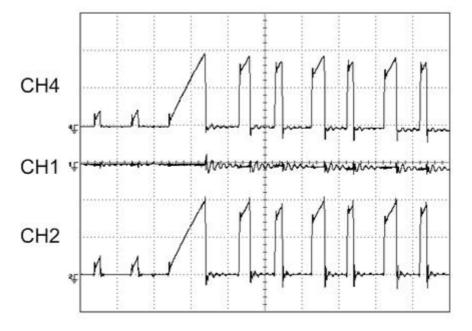

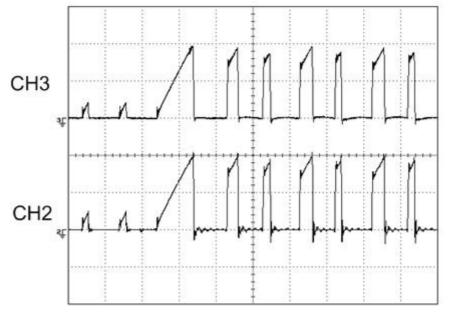

| Fig. 5.17 | Estimated inductor current 200mV/DIV⇔3A/DIV, 5µs/DIV                                                                         | 142      |

| Fig. 5.18 | Experimental waveforms for a step-up load from 4A to 25A;                                                                    | 144      |

| Fig. 5.19  | Experimental waveforms for a step-up load from 3.5A to 25.6A;                                                                         | 144 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

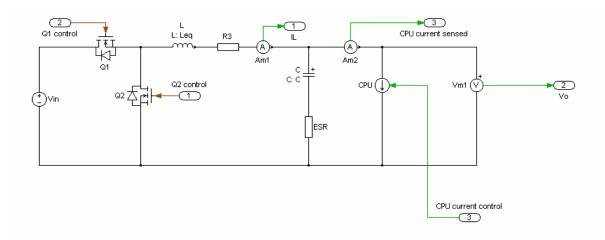

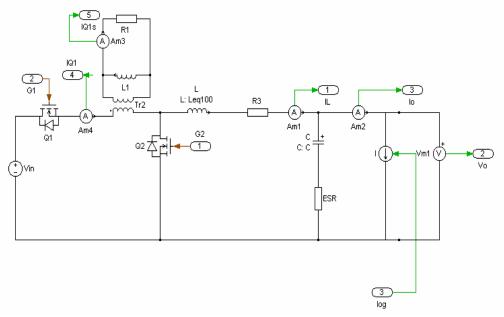

| Fig. A.1   | Single phase equivalent circuit used in the simulation for the VMC                                                                    | 159 |

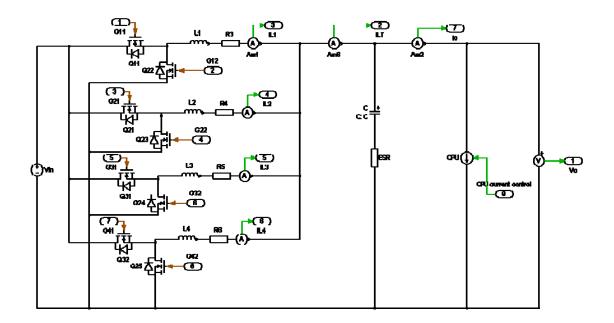

| Fig. A.2   | Multiphase converter circuit used in the simulations                                                                                  | 160 |

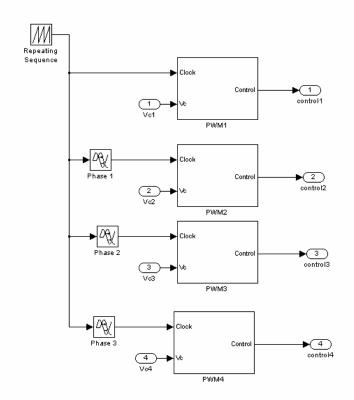

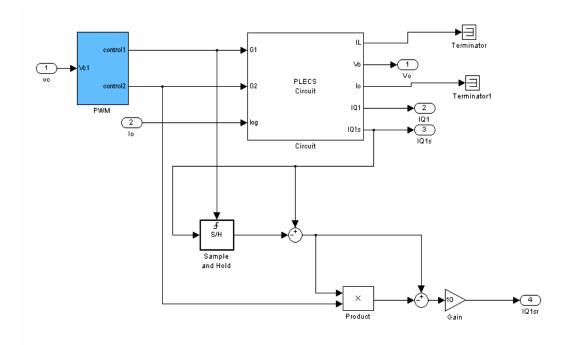

| Fig. A. 3  | PWM logic diagram                                                                                                                     | 160 |

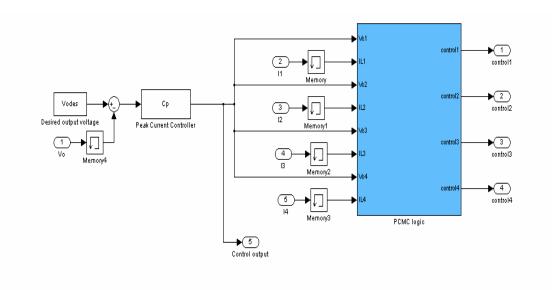

| Fig. A.4   | Peak Current Mode Control logic diagram                                                                                               | 161 |

| Fig. A.5   | Large signal model used in VMC                                                                                                        | 161 |

| Fig. A.6   | Large signal model used in ACMC                                                                                                       | 161 |

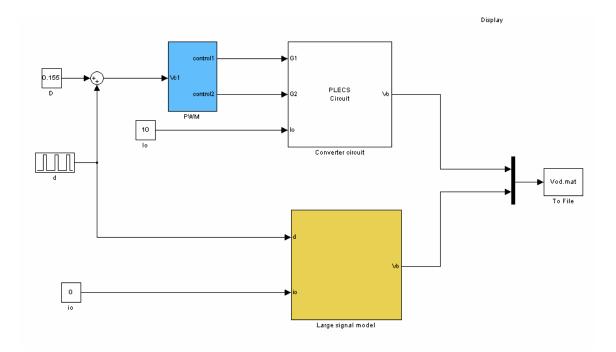

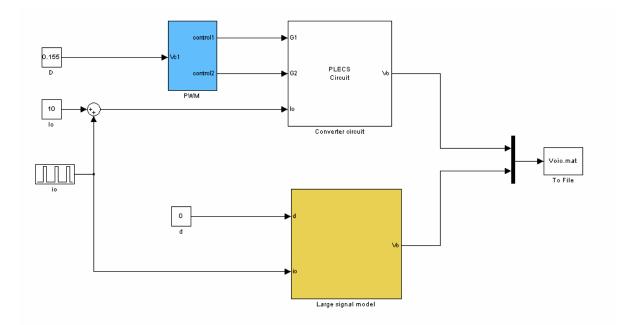

| Fig. A.7   | Simulation diagram used to compare the large signal model in VMC with the actual converter when the duty cycle vary in a step manner  | 162 |

| Fig. A.8   | Simulation diagram used to compare the large signal model in VMC with the actual converter when the load vary in a step manner        | 162 |

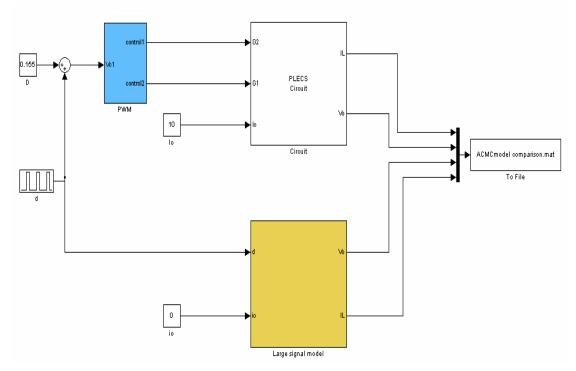

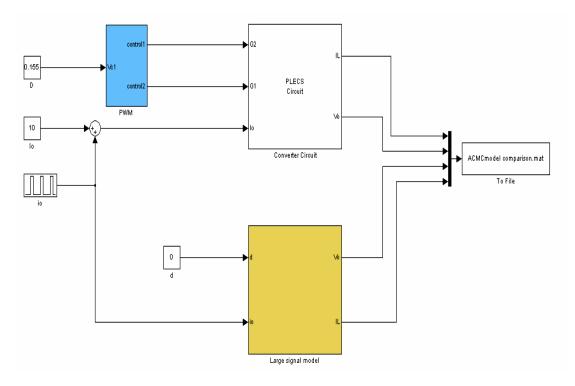

| Fig. A.9   | Simulation diagram used to compare the large signal model in ACMC with the actual converter when the duty cycle vary in a step manner | 163 |

| Fig. A.10  | Simulation diagram used to compare the large signal model in ACMC with the actual converter when the load vary in a step manner       | 163 |

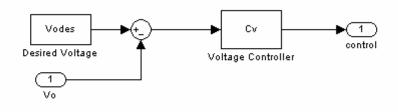

| Fig. A.11  | VMC Control diagram used in the single phase equivalent circuit                                                                       | 164 |

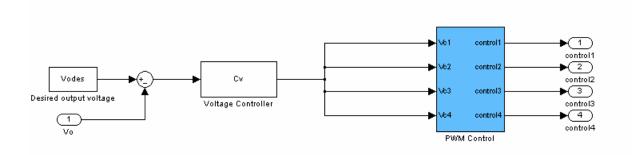

| Fig. A.12  | Overall simulation diagram for the single phase equivalent circuit in VMC                                                             | 164 |

| Fig. A. 13 | PWM Control diagram used for VMC and ACMC in the multiphase converter                                                                 | 165 |

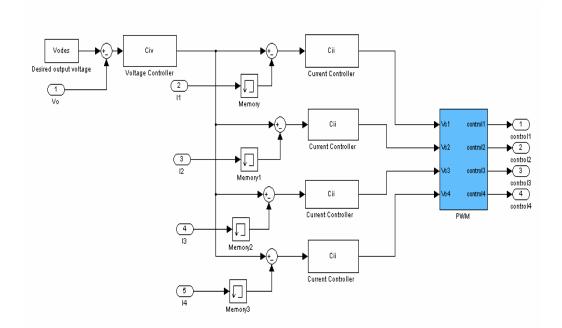

| Fig. A.14  | VMC Control diagram used in the multiphase converter                                                                                  | 165 |

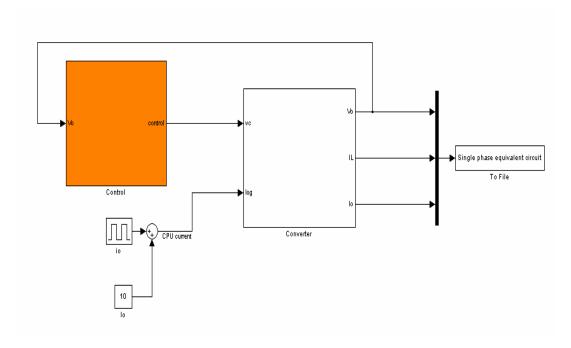

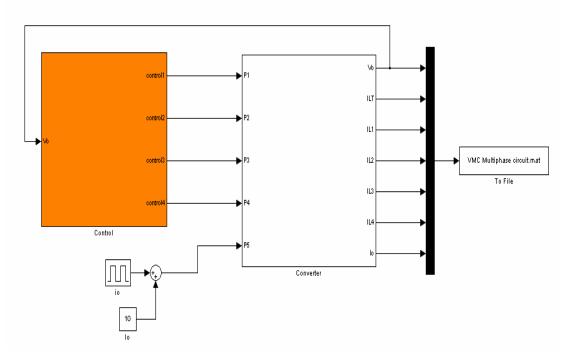

| Fig. A.15  | Overall simulation diagram used for VMC in the multiphase converter                                                                   | 166 |

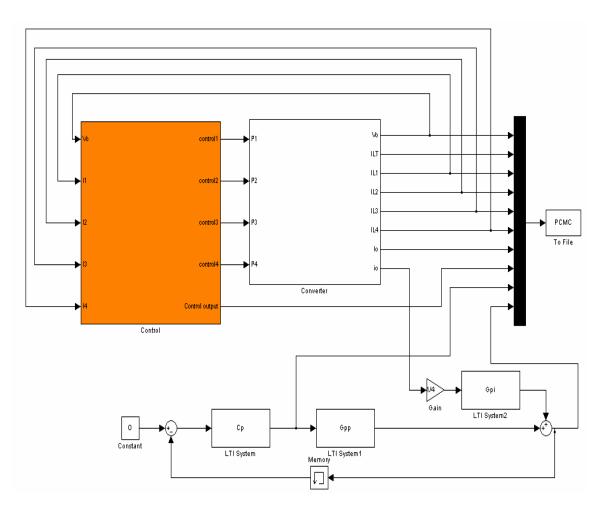

| Fig. A.16  | ACMC Control diagram used in the multiphase converter                                                                                 | 166 |

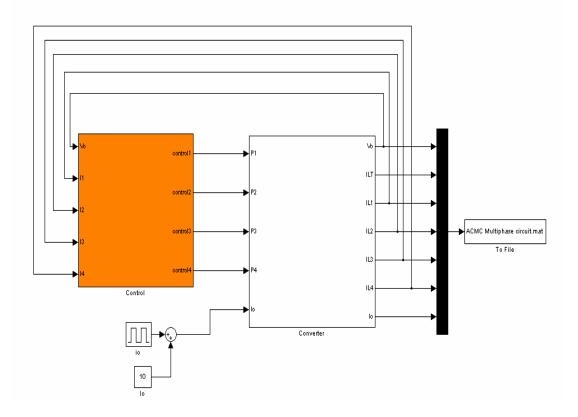

| Fig. A.17  | Overall simulation diagram used for ACMC in the multiphase converter                                                                  | 167 |

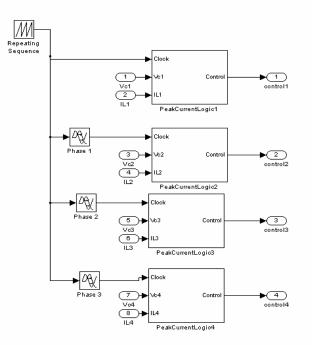

| Fig. A.18  | PCMC logic diagram used in the multiphase converter                                                                                   | 167 |

| Fig. A.19  | PCMC Control diagram used in the multiphase converter                                                                                 | 168 |

| Fig. A.20  | Overall simulation diagram used for PCMC in the multiphase converter                                                                  | 168 |

| Fig. A.21  | Single phase buck converter circuit with a CT in series with the high side switch. | 169 |

|------------|------------------------------------------------------------------------------------|-----|

| Fig. A. 22 | Switch current estimation circuit diagram                                          | 169 |

| Fig. B.1   | Inductor Current estimation circuit diagram                                        | 170 |

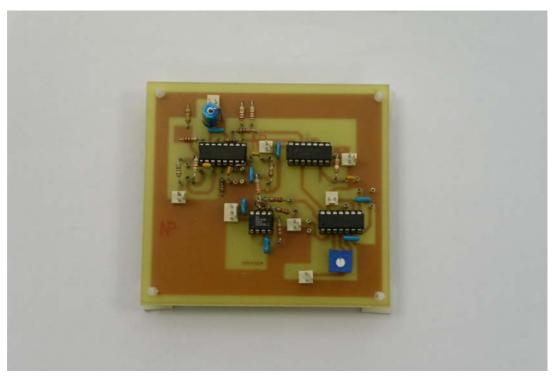

| Fig. B. 2  | Inductor current estimation PCB circuit                                            | 171 |

| Fig. B.3   | PCMC circuit diagram                                                               | 171 |

| Fig. B.4   | PCMC PCB circuit                                                                   | 172 |

| Fig. B.5   | Single phase buck converter PCB circuit with load                                  | 172 |

## List of Tables

| Table 2.1  | Power loss evaluation formulas for a synchronous derived converter                                                                  | 26  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2. 2 | Four phase converter characteristics used in this thesis                                                                            | 29  |

| Table 2.3  | Controller gain and zero selection for different inductances                                                                        | 44  |

| Table 2.4  | Simulation results for a 90A step up and step down in load                                                                          | 46  |

| Table 3.1  | Current controller characteristics and output voltage overshoot for<br>a load step down of 90 A for different inductance values     | 77  |

| Table 3.2  | Peak current controller characteristics and output voltage overshoot for<br>a load step down of 90A for different inductance values | 96  |

| Table 3.3  | Four-phase converter characteristics for the three kinds of control methods                                                         | 100 |

| Table 4.1  | Comparative overview of VRM current sensing techniques                                                                              | 114 |

# CHAPTER 1 INTRODUCTION

#### 1.0 Background

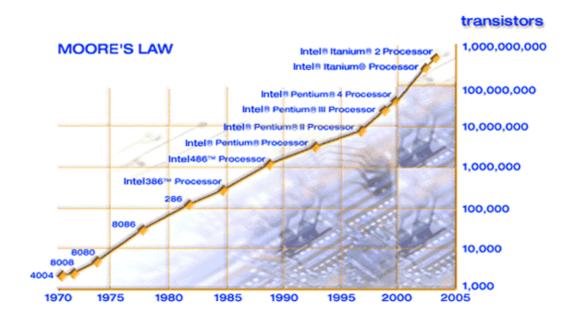

With advances made in Very Large Scale Integration techniques (VLSI), the microprocessor has continuously gained in speed and compactness over the past 40 years. As predicted by Moore's law, the number of transistors in a single chip has consistently increased over this time period in an exponential way [1]-[2] (see Fig. 1.1). The current Pentium 4 contains several million transistors, and Intel is even planning to reach the billion transistor mark for the next generation of the processor.

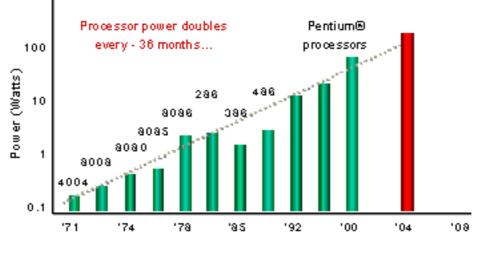

However, with the multiplication of the number of transistors integrated into the microprocessor, the power requirements of such an IC have also shot up [3]-[4]. The dramatic increase in the power required to drive the microprocessor may be seen from Fig. 1.2.

Fig.1.1 Exponential increase of the number of transistors integrated in a single chip (http://www.intel.com/technology/silicon/mooreslaw/)

Fig.1.2 Evolution of power consumption in the microprocessor [5]

As may be noted, the current high speed processor is consuming more than a hundred watts of power and this may be compared to the low value of only several milli-watts dissipated in the early days. At the same time, current CPUs are also demanding an increasingly superior performance, such as ability to handle very fast current transients within a very tight voltage tolerance.

Indeed, for the CPU to work, a constant voltage  $V_{cc}$ , called core voltage has to be applied across it. Initially,  $V_{cc}$  was fixed at 5 V. However, with a large clock frequency  $f_{clock}$ , the dynamic power loss  $P_L$  can become substantial since

$$P_L \alpha C_L V_{cc}^2 f_{clock}, \tag{1.1}$$

where  $C_L$  is the capacitive loading of a single CMOS cell [6].

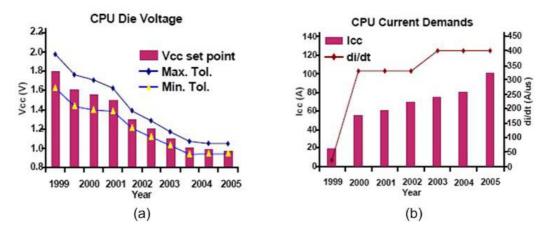

Consequently, to limit this power loss, and thereby the heat stress on the CPU, the core voltage has been considerably decreased in recent years, as shown in Fig. 1.3(a). In today's Pentium IV, the core voltage is kept to a range of 0.8 V to 1.8 V, and this trend of decreasing core voltage is expected to continue. Furthermore, the smaller voltage goes with an even tighter tolerance band, as shown in Fig. 1.3(a). The tolerance band was 5 % for the 3.3 V-Pentium II, whereas it has been reduced to only 1.2% for the current 1.8 V-Pentium IV [6].

Fig.1.3 Intel roadmap of the 32-bit CPU load at CPU-system connector [5](a) CPU die voltage(b) CPU current demands

Hence, the microprocessor has become increasingly sensitive to voltage fluctuations requiring the core voltage to be controlled within a tight window, should a load perturbation occur.

Moreover, since the required power to drive the CPU is considerable, reduction in core voltage means a significant increase in the demanded current, as shown in Fig. 1.3(b). In today's CPU, the peak current demand is as high as 120 A, and this value may even reach several hundred amperes in the next generation processor [4], [5]. This complicates the circuit design and thermal management very much, since even low values of parasitic resistances in the circuit will lead to significant power loss [3], [5].

Meanwhile, another aspect of modern day CPUs is their power adaptability to the working load. Indeed, in order to comply with new environmental rules such as "Energy Star" norms, and/or extend the battery life for laptops, modern CPU goes through different power stages depending on the running task [7], [8]. Therefore, the performance is maximized while the expenditure of energy is minimized. Microprocessors, which used to work either fully or not, have been replaced since 1989 by new processors, in which parts of them are able to go into a sleep mode, when not used [7]. In such a processor, both the voltage to be supplied, and the current drawn, vary according to the load. In fact, the microprocessor acts as a variable current sink requiring a specific and adjustable input voltage,  $V_{cc}$  [9]. The desired reference voltage  $V_{ccref}$  is communicated to the supply via a number of bits called 'Voltage Identification' (VID).

However, as mentioned earlier, the power loss is proportional to  $V_{cc}^2$  and the clock frequency. In spite of the fact that the core voltage varies with the power level, it is still kept low and within a relatively small range (for example, from 0.8 V to 1.8 V in the current Pentium IV). Consequently, the power saving scheme results mainly in large variations in the current drawn by the processor. In the present day processor, the load varies thus from a few amperes to 120 A [9]. Moreover, this new CPU architecture comes with an expected high speed performance. Thus, the user expects his computer to be able to recover from standby quickly, or even to switch in no time from a relatively non-power consuming task, such as writing a memo, to a higher demanding application such as playing a movie from a hard disk. It is therefore required for the CPU to toggle between two different power stages in a very rapid manner. As a result, manufacturers have designed today fast reactive CPUs, where the current drawn can vary suddenly over a magnitude of 100 A, with a rate which may be as high as 930 A/µs [9].

Hence, to summarize, depending on the running task, the microprocessor draws or switches off a huge amount of current from its power supply in a very short period of time. Usually, the power supply does not react that fast, and though a considerable number of high frequency decoupling capacitors are connected across the CPU, large variations in load current still cause significant disturbances in  $V_{cc}$ , which may lead to

system failure. Nevertheless, modern processors allow the voltage to exceed the tolerance band within certain boundaries for a short time period. But this transient time period is relatively small, and the transient voltage range is also low. For example, these values are, respectively, less than 25  $\mu$ s and 50 mV in the current Pentium IV [9]. Therefore, a fast power supply is required so that the core voltage perturbation during a step load is contained within the tight window fixed by processor requirements.

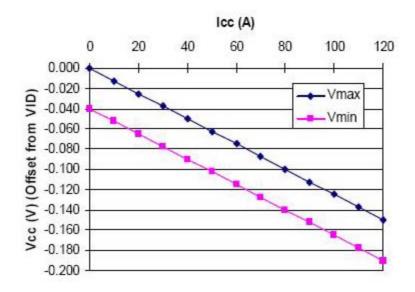

To help in this task, most of today's processors have adopted the Adaptive Voltage Positioning (AVP) method, where  $V_{cc}$  varies depending on the load (Fig. 1.4) [9]. Here, the final  $V_{cc}$  voltage presented to the microprocessor is lower than  $V_{ccref}$ , with the difference varying according to the load as shown in Fig. 1.4. This difference can then be used to limit the voltage jump or drop beyond the allowable limits during the load transients. The voltage perturbation amplitude is hence considerably reduced, as is the settling time ( $\Delta t$ ) during step load, as can be seen in Fig. 1.5. Different methods exist to implement such a scheme and are commonly used in today's CPU power supply [10]-[16].

Therefore, to summarize, the CPU power supply of today must be able to identify the VID codes, continuously sense the load current, deduce from Fig. 1.4 the correct core voltage to be supplied, and finally manage to present the desired voltage in spite of large load variations within a tight settling time of 25 µs for the current Pentium IV. The CPU power management has thus become increasingly complex and stringent. As a result, a dedicated module, called a Voltage Regulator Module (VRM) is needed to control accurately and rapidly the core voltage in spite of large load variations, or other disturbances. In the following, before investigating the VRM in detail, the overall power delivery architecture is first presented briefly.

Fig. 1.4 Processor equipped with AVP load line [9]

Fig. 1.5 Comparison of voltage fluctuations during a step load increase between processors with and without AVP

#### 1.1 Computer power delivery architecture

The power delivery architecture used to be relatively simple in the early days. The 110 V or 220 V main AC source was simply converted via a "silver box" to a fairly constant 5 V. The microprocessor and all the other electronic systems were then drawing power directly from this 5 V plane present in the motherboard [5].

However, with the increase in the number of peripherals in the computer, besides the power demand rising tremendously, the different peripherals also require different voltage inputs. Hence, in today's PC, typically, three different voltages are supplied by the silver box; 3.3 V, 5 V and 12 V. The 3.3 V and 5 V output are usually used by the digital circuits, while the 12 V is used mainly to run motors in disk drives and fans. A forward converter fed from an AC to DC front end rectifier is commonly used in these cases.

Due to the stringent voltage requirements and large load variations, a dedicated DC-DC converter called Voltage Regulator Module (VRM) is used to regulate the voltage supplied to the microprocessor from one of the silver box output. The 5V output was initially used for this purpose until the Pentium IV and its equivalents were introduced. With the dramatic increase in the power delivered to the CPU, the distribution loss in the 5 V bus was becoming increasingly significant. Therefore, to reduce this additional loss, the source voltage of the VRM has been switched to the higher voltage of 12 V, also available at the output of the silver box. This power delivery architecture presented in Fig. 1.6 is the most commonly used in today's desktop [17].

Nevertheless, to reduce further the loss in the 12 V voltage bus, the industry is currently considering switching to an even higher voltage of 48 V in the next

generation microprocessors, including multi-processor system. In such a case, the silver box will deliver only a constant DC voltage of 48 V. Each peripheral will then be preceded by a dedicated DC-DC converter, which will convert the applied 48 V into the required voltages [18]-[19].

In the laptops, heat management is a major concern. Here, the silver box is substituted by an AC/DC adapter placed outside and delivering only one DC constant output voltage in the range of 14 to 18 V. Different DC-DC converters are then placed inside, to convert this voltage into other suitable voltages as needed.

This thesis will mainly focus on the microprocessor voltage regulator module. The constant 12 V output delivered by the silver box will be considered for the VRM source. In the following, an introduction to VRM topologies is presented.

Fig. 1.6 Power system architecture commonly used in current desktops The current values shown are estimated based on AMD technical documents.

#### **1.2 VRM topologies**

From the power requirements for present-day microprocessors given by Intel [9], as seen earlier, today's VRM has to be accurate with fast response, and be able to accommodate large changes in load current in a very short time without great disturbance in the  $V_{cc}$  voltage. Also, the VRM is placed in close proximity to the microprocessor, in order to minimize the parasitic inductances and resistances which affect greatly the transient characteristics [20]-[22]. Since the motherboard is limited in space, the VRM has to be small in size. Last but not least, to comply with tight regulation regarding energy saving, efficiency is an essential criterion that modern VRMs have to take into account.

From the early days, buck converter topologies have been widely used in VRMs, since they meet most of the above requirements in terms of efficiency, size, and control. Fig. 1.7 shows a conventional buck converter feeding a current-sink-modeled CPU [23]. The converter consists of two stages. In the first stage, a switching circuit connects the indicated point A to the source or to the ground. Since the current in this circuit loop has high di/dt's due to the switching, the inductance in the loop should be kept as small as possible [24]. In the second stage, there is an LC low pass filter which is designed to pass only the average of  $V_A$  to the load. By turning on the MOSFET Q<sub>1</sub> during a fraction *d* of the period, called duty cycle, and turning off during the rest of the period, the voltage across the load can ideally be maintained to be  $V_{in}d$ , with a small ripple depending on *L* and *C* values. The load voltage is thus directly controlled by adjusting the duty cycle. If the inductor current does not hit zero in a period, the circuit is said to work in Continuous Conduction Mode (CCM). Besides, in the VRM, the power supply for the control box is derived directly from the 12V or 5V plane present in the motherboard [15], [16].

Fig.1.7 Conventional buck converter

Fig.1.8 Synchronous buck converter with fast recovery diode

However, VRMs are expected to carry a large amount of current, which leads to significant diode power loss in the conventional buck converter. For this reason, the synchronous buck converter, where the diode is replaced by a MOSFET as shown in Fig. 1.8, is preferred in a VRM [4] ,[25]-[26]. In such a scheme,  $Q_1$  is called the high side or the control switch and  $Q_2$  is called the low side or the synchronous switch. Also, the presence of  $Q_2$  allows a negative current to flow through the inductor, which avoids the discontinuous conduction mode (DCM) of operation [23]. Therefore, the output voltage is proportional to the input voltage and the duty cycle even under very low load.

In practice, a MOSFET takes a finite time to turn on or off. Hence, to avoid a short circuit across  $V_{in}$  during switch transitions, a dead-time has to be provided before turning on Q<sub>2</sub> or Q<sub>1</sub>, during which the inductor current flows through the internal diode of Q<sub>2</sub>. Due to the usual poor characteristics of this diode, a fast recovery diode or Schottky diode is commonly placed in parallel, as shown in Fig. 1.8.

This topology was widely used in VRMs, until the introduction of Pentium III and its equivalents. Indeed, in that processor, the operating voltage was drastically reduced from 2.5 V to 1.5 V, and the tolerance band was decreased from 85 mV to 75 mV. Also, the current to be supplied was increased to a larger value of 30 A instead of 10 A, and its slope could attain 8 A/ns instead of 1 A/ns [27]. With such tight steady state and transient requirements, the design of a suitable synchronous buck converter became highly problematic [4], [26]-[27]. The reasons will be explained in the following.

First, with a large load current, the stress endured by each component in the converter is considerable. The power loss in the switches becomes significant; the inductor size also becomes greater with the increase in current [23], [28].

Secondly, the dynamic and steady state requirements of the microprocessor lead to contradictory design choice for the inductance value. Thus, during a load transition, as VRM is inherently slow, the current is first provided by the output capacitors, causing a voltage fluctuation. In response, the VRM has to charge or discharge the capacitor so that the default reference voltage could be met. However, the charging or discharging current  $I_L$  flowing into the capacitor has its slew rate limited by the output inductance. Fig. 1.9 shows a typical inductor and load current waveforms during transient.

Fig.1.9 Large unbalanced charges during load transient

As can be seen in that figure, the difference between the inductor current and the load current during transient causes vast imbalance in the charge that has to be provided by the output capacitor. The inductor current will generally rise beyond the load current value in order to compensate the capacitor discharge, and to recover from the output voltage deviation caused by the discharge from the capacitor. Hence, by decreasing the inductance value and therefore increasing the inductor current slope, both the settling time and the output voltage deviation can be reduced. But, a small inductance leads to high current ripple, which increases the switching loss. Furthermore, with high current ripple, the capacitance required to keep the voltage ripple within the small window allowed by the processor can also become considerable. Such high value capacitors are large in size and the motherboard real estate is expensive.

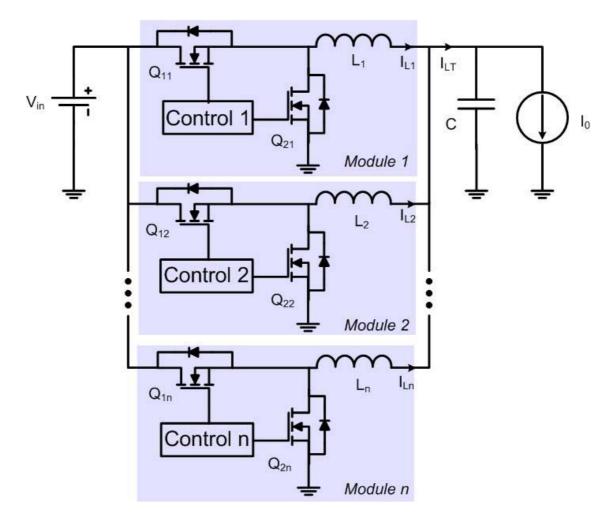

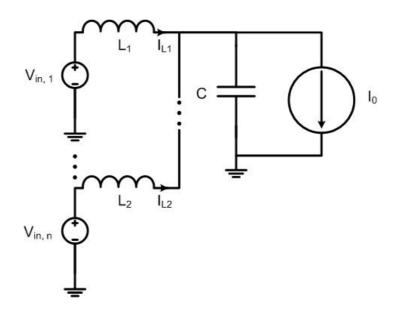

As it was getting impossible to meet the microprocessor's requirement using classical methods without increasing the VRM size greatly, a new topology was needed for future processors. In 1999, a novel VRM, called multiphase interleaved converter [4], [20]-[22], [27], [29]-[33], was utilized to power the new Pentium III. Such an n-phase interleaved converter is shown in Fig. 1.10.

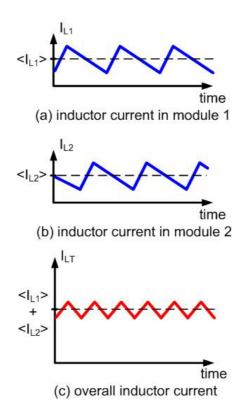

In this scheme, in order to reduce the increased current stress endured by each converter component, several complete buck converter modules are paralleled, as shown in Fig. 1.10. In each module, called a channel or a phase, the inductance is chosen to be the same, and as in a classical buck converter each inductor carries a triangular shape current. Through appropriate control, these waveforms are phase shifted in such a way that the ripple in the overall current  $I_0$  is reduced, as can be seen in Fig. 1.11 for a two phase converter.

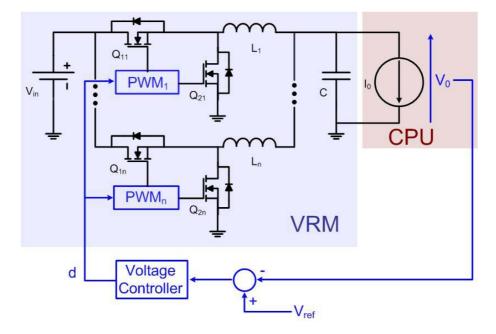

Fig. 1.10 n-phase interleaved converter

Fig. 1.11 Each inductor and overall inductor current in a two phase buck converter

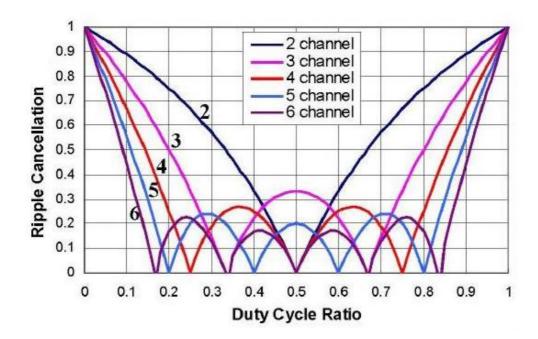

Fig. 1.12 Overall current ripple cancellation for a 2-6 phase buck converter [34]

Hence, a smaller inductance value can be chosen when compared to a single phase VRM, without increasing the overall current ripple. Besides, the use of several modules helps to spread the power dissipation, and hence facilitate the heat management, which is critical in motherboards. Finally, the phase shift in the control offers the additional advantage of increasing the fundamental frequency of the overall inductor current,  $I_{LT}$ . Therefore, as a side benefit, a smaller capacitor can be selected for the same voltage ripple, reducing in a way the VRM size. Though it requires more space and components, the multiphase topology presents an affordable solution for present day and future processors.

The ripple reduction depends actually on the number of phases and the operating duty cycle, as shown in Fig. 1.12 [34]. Currently, the steady state duty cycle is around 0.16. Therefore, a six phase converter may be used to minimize the current ripple. However, four channel interleaved converters are presently widely used, as a compromise between cost, size, and efficiency [35]-[36]. Yet, for the next generation of processors, a higher number of phases will most likely be selected to cater to the constant increase in power requirements.

One of the important issues in this topology is the load current sharing among the phases [32]. Indeed, should a current unbalance occur among the channels, the system will become less effective, and the steady state and transient characteristics of the system will greatly suffer. Hence, in present and future VRMs, in which the power and heat management is getting to be increasingly critical, a current sharing process must be included in the control scheme.

Another difficulty in using this topology is with regard to its size. In order to reduce the space occupied, the different inductances of the multiphase converter may be integrated into one unique core [34]-[35], [37]-[39]. In such a circuit, called the

multiphase coupled converter, the mode of operation is completely changed, since all the inductors are coupled together. Nevertheless, the coupling may be optimized so that it offers several other advantages, such as better dynamic response under a loadinduced transient, smaller current ripple in each channel, and less inductor core losses. However, the coupled inductor makes the core structure complex, especially when more than two phases are used. Also, phase shifts are no more introduced in the phase inductor currents, which compromises some of the benefits associated with the multiphase structure. Therefore, so far, the normal multiphase converter is still more popular.

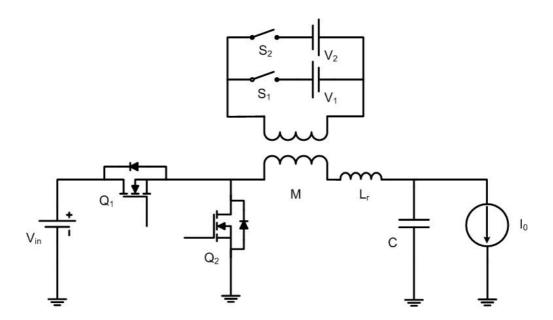

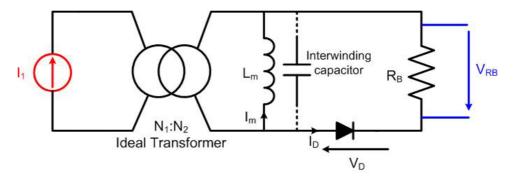

Another VRM candidate proposed currently in the literature is the stepping inductance scheme [40]-[42]. It consists of a classical synchronous buck converter in which the filter inductor is replaced by a transformer M in series with an inductance  $L_r$ , as shown in Fig. 1.13.

Fig.1.13 Basic configuration of stepping inductance based VRM

The secondary side of the transformer is here connected to the voltage sources  $V_1$  and  $V_2$ , through the switches  $S_1$  and  $S_2$ . These sources are derived from the supply voltage  $V_{in}$  through appropriate arrangement of auxiliary switches and transformer windings, not shown here. Also,  $L_r$ , which could be the leakage inductance of the transformer, is chosen to be very small compared to the primary inductance  $L_1$  of M.

In the control scheme given in [42], during steady state, the switches  $S_1$  and  $S_2$  are fully off, so that the output inductance is the sum of  $L_1$  and  $L_r$ . Due to this relatively large inductance value, the inductor current ripple is very low, and so is the output voltage ripple. When a large load step occurs, the transformer primary inductance is then shorted by turning on  $S_1$  or  $S_2$ . Consequently, the filter inductance is reduced to  $L_r$ , and therefore a faster variation in inductor current is permitted. Also, at the same time, the voltage source  $V_1$  or  $V_2$  will charge or discharge the transformer's secondary. The switch  $S_1$  or  $S_2$  is finally turned off only when the resulting primary current would be equal to the current already flowing through  $L_r$ , in order to ensure a smooth transition.

Though having fewer components, this scheme's main drawback is the control and circuit design complexity. Also, during transient, the reflected voltage of  $V_2$  or  $V_1$ affects the slope of variation of the inductor current. This must be taken into account in the design of the transformer. Furthermore, usually it takes a long time to charge or discharge the transformer to the desired value. As a result, there is a significant time period, in which the output filter inductor is limited to the very small value of  $L_r$ , and hence the current ripple will be very large during this time. To limit the resulting voltage ripple to reasonable values without using large capacitance, a hysteresis current mode control is employed [42]. This control, however, complicates the design of the converter because of the varying switching frequency. Moreover, a highly accurate and efficient current sensor is needed to sense the inductor current. Consequently, this scheme, though promising, is not yet widely used in VRM.

Therefore, the great majority of today's VRMs use the four phase interleaved converter topology, which is the main focus in this thesis. For more information regarding the stepping inductance system, [40]-[42] may be referred to.

In the following, a brief introduction to the several issues covered in this thesis as well as the scope of this thesis are presented.

#### **1.3** Thesis motivation and outline

The multiphase converter has gained its popularity based on superior power and heat management. The dynamic and steady state requirements of the CPU are fulfilled relatively easily without using bulky capacitors, by simply decreasing the inductance value in each phase, thus, allowing higher current slope. However, during transient, the inductor current's rate of rise or fall does not only depend on the inductance value, but also on the controller characteristics. In other words, below a certain limit, which depends on the selected control scheme, decreasing the inductance value further does not improve the transient response, but only affects the converter's steady state performance including efficiency. In this thesis, ways to optimize the inductor value in order to have the best transient response with minimum steady state voltage ripple will be investigated for the three kinds of control schemes mostly used in today's VRM; Voltage Mode Control (VMC), Average Current Mode Control (ACMC), and Peak Current Mode Control (PCMC). These studies are carried out both analytically and through simulations. The studies bring out the superiority of a PCMC scheme over the ACMC scheme and the currently popular VMC scheme.

Another topic covered in this thesis is current sensors in buck derived topologies for use in high performance control schemes, such as the PCMC scheme. As mentioned earlier, the numerous advantages of the multiphase converter are in fact effective only if the load current is shared correctly among the phases. Therefore, in order to prevent system failures, the converter control circuit must include a current sharing scheme. By controlling directly each inductor current, current mode control offers an easy solution to this load sharing problem in steady state as well as during transients. However, in order to implement a current mode control of maximum bandwidth, a fast and accurate current sensor is needed. Yet, in current sensors for DC-DC converters existing today, accuracy and rapidness come always with a price in cost and efficiency. Therefore, voltage mode control scheme had been preferred in practice, though it results in a poor current sharing. However, given the Intel voltage/current road map, current mode control scheme is gathering popularity, and presently, there is a need for developing high performance current sensors for use in converters such as the multiphase converter. This thesis proposes a novel, highly accurate and efficient current sensing method based on the use of current transformers. Analytical design and experimental studies have been performed on the proposed current sensor technique and on a single phase synchronous buck converter using these sensors.

These different issues will be presented as follows:

• **Chapter 2**: In this chapter, the selection of the different components of the multiphase converter is first presented. The converter equipped with a voltage mode control is then analyzed and a large signal model of the system is proposed. This model will next be used for the design of the voltage controller, and for the inductance optimization. Finally, the complete system equipped

with the optimized inductance is simulated in order to investigate the current sharing among the channels in steady state as well as during step load changes.

- Chapter 3: In this chapter, the two most popular current mode controls are investigated: average current mode control and peak current mode control. For each case, a large signal model is derived, the controller design procedure is presented, and methods to optimize the inductance values are investigated. Simulations under maximum load step for each case is also provided to verify and confirm the theoretical results. The results in Chapter 2 & Chapter 3 confirm the potential superiority of the peak current mode control scheme. This also makes the need for an accurate, fast, small, and efficient current sensor for the VRM application apparent.

- Chapter 4: In this chapter, a literature survey is conducted on existing current sensors used in DC-DC converters for control purposes. Firstly, the difficulties in sensing the current in actual VRM are presented; then, for each sensor, its efficiency, accuracy and speed of response are investigated. This chapter is actually an introduction to the chapter 5, where a new current sensing method, which overcomes most of the discussed difficulties, will be introduced.

- Chapter 5: In this chapter, a novel current sensing technique based on current transformers and capable of high performance is proposed. The requirements and the design of the current transformer to be used are presented. The accuracy of the sensing method is also analyzed. Finally, experimental results on a step down buck converter, controlled with peak current control using such a sensor, are provided to confirm its performance. The proposed technique can also be applied to several other types of power converters besides the multiphase buck converter.

## **1.4 Thesis Contributions**

The major contributions of this thesis are as follows:

- Large signal models of the four phase converter with VMC, ACMC and PCMC have been proposed. These models have been verified using simulation results. The models are useful in the design of the controllers and for an accurate analysis of the dynamic performance of the converter, which will be used later on.

- Critical inductance analyses have been carried out for the system with ACMC and PCMC using the proposed large signal models. Analytical methods to estimate the critical inductance value are presented and these are verified with simulation results.

- A novel current sensing technique based on current transformers and capable of high performance is proposed. Experimental results based on the use of such a sensor in PCMC on a single phase buck converter are also provided.

## CHAPTER 2

## **VOLTAGE MODE CONTROL METHOD**

### 2.0 Introduction

The Voltage Regulator Module (VRM) concept and the multiphase interleaved buck topology have been introduced in Section 1.2. Several ways exist to control such a complex converter, the most popular among them being the Voltage Mode Control (VMC), the Average Current Mode Control (ACMC) and the Peak Current Mode Control (PCMC) [43]-[45]. In this thesis, the design issues regarding these control schemes are investigated and compared for a four phase converter.

The present chapter is mainly focused on the VMC scheme, which offers the advantage of a simpler control structure as opposed to schemes employing current mode control techniques. Moreover, as mentioned earlier, the output voltage, which is the only variable used in the feedback loop in VMC, has an increased ripple frequency due to the adoption of the interleaving method. As a result, the allowable bandwidth is also increased using this control method. However, the scheme's main drawback is the absence of a current sharing feature, as will be shown in this chapter. Therefore, though this control method was popular in earlier VRMs, it is no longer preferred for the current and future VRMs, where the load sharing capability is critical.

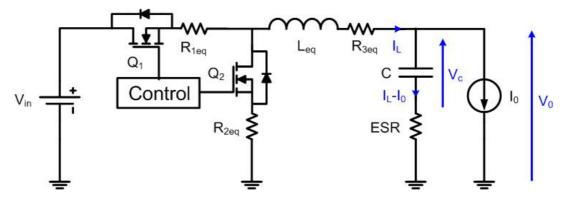

The VMC scheme has been investigated in the past, especially the issue of optimizing the control design as well as the system design, in order to have the best transient response with minimum steady state voltage ripple [45]-[48]. However, in most of the cases, the switch resistances are conveniently ignored in the circuit analysis [46]-[48], or arbitrarily added to the resistance of the inductor [45], in order

to be able to derive a large signal model. The limitations of such an approximation are brought out in this chapter, and a more accurate large signal model is proposed. The design methodology, in particular the inductance optimization method, is then investigated in the present chapter for such a control scheme. These analytical methods will be extended for application to the current mode control schemes in the next chapter.

The first part of this chapter discusses issues regarding the selection of the main components to be used in the four phase converter. This part, in fact, is applicable to the VRM module in general irrespective of the control scheme adopted.

Following this, in the second part of the chapter, the implementation of the VMC scheme in the multiphase converter is presented and analyzed. The limitations of the linear model derived by ignoring the switch resistances are particularly highlighted. A more accurate large signal model taking into account the MOSFET onstate resistances and the loss resistances of the inductors and the capacitors is then proposed and verified and compared to other models using simulation results. Using the proposed large signal model, the design of the voltage controller is carried out. The dynamic performance of the converter is then studied for different inductance values. A critical inductance value, for which the transient response is optimized with minimum steady state voltage ripple, is identified. This critical inductance concept is based on that presented in [45]. A method to estimate the critical inductance using the proposed large signal model is presented. The critical inductance estimation method presented in this chapter for the VMC scheme will be extended to the ACMC and PCMC schemes in the next chapter. Finally, the four phase converter equipped with the critical inductance and the designed voltage controller is simulated, and its current sharing capability discussed.

## 2.1 Selection of power stage components