# Synthesis of Multiprocessor Architectures for Multimedia Applications

## **Dinesh Kunchamwar**

(B.E. (Hons.) Computer Science)

Supervised by

Samarjit Chakraborty

Weng Fai Wong

A THESIS SUBMITTED FOR A DEGREE OF MSC(BY RESEARCH) COMPUTER SCIENCE

## SCHOOL OF COMPUTING

NATIONAL UNIVERSITY OF SINGAPORE

2006

#### Abstract

Streaming applications typically consist of a large number of tasks, each of which can be mapped onto a different processor on a Multi-processor System on Chip (MPSoC) platform. This gives rise to a large design space (whose size can be exponential in the number of tasks in the application). Previous work on design space exploration for this problem use evolutionary algorithms which do not guarantee optimality and are too time-consuming because of the need for full-system simulation. This problem has also been formulated as Integer Linear Programming problem assuming constant execution requirements. However high degree of burstiness in the arrival rate of streams and high variability in the execution demand of the data items, make those approaches inadequate. In this work we present a depth-first design space exploration technique which breaks down the process of system simulation into many task level simulations. The results of the task level simulations are represented using Variability Characterization Curves (VCCs) which are based on theory of network calculus. We formulated an algorithm which explores the design space in a depth first manner and combines the VCCs of task mappings along the explored path using purely analytical methods. The algorithm avoids exhaustive searching of the design space by using certain timing conditions and upper bounds on the costs to prune some portions of design space. We take the multi-objective optimization approach for this problem and device a technique that is capable of finding a pareto optimal front. This allows the designer to make trade-offs among various design goals to quickly narrow down the choice of various architecture design parameters. We implemented our scheme and performed a case study based on the MPEG-2 decoder application. We demonstrated the usefulness of our multi-objective technique using two objectives: the silicon area required to realize the MPSoC system and power requirements of the system. For this case study, 76% of the design space was pruned due to the timing and upper bound conditions which translated into 74% saving in the running time of the algorithm.

#### **ACKNOWLEDGEMENTS**

I feel deeply indebted to my supervisors Dr. Weng Fai Wong and Dr. Samarjit Chakraborty, without their support, guidance and constant motivation this thesis would not have been possible. I would like to sincerely thank them for allowing me to learn from their knowledge and experience and for their patience and encouragement which helped me to get through difficult times.

I thank my thesis committee members: Dr. Tulika Mitra and Dr. Wei Tsang Ooi, who evaluated my Graduate Research Paper and provided valuable suggestions during thesis proposal presentation.

Special thanks to all fellow students in the Embedded Systems Lab who shared their expertise and helped me in times of need. Thanks to Yanhong and Balaji for help on SimpleScalar, Priya, specially for help on latex, Unmesh, Yuan Yi, and Ramkumar for sharing their thoughts and experiences and Linh for her kind words.

Thanks to all my friends at hong leong for all the happiness and fun that we shared. I deeply appreciate all the moral support Laura provided and thank her for being with me. I express my sincere gratitude towards my parents for being constant source of motivation and for the values they have inculcated in me.

# CONTENTS

| 1. | Intro | duction                                            | 8  |

|----|-------|----------------------------------------------------|----|

|    | 1.1   | Related Work                                       | 12 |

|    | 1.2   | Contributions                                      | 13 |

|    | 1.3   | Organization of the thesis                         | 15 |

| 2. | Cho   | ce of Application Model                            | 17 |

|    | 2.1   | Task Precedence Graph                              | 17 |

|    | 2.2   | Process Networks                                   | 19 |

| 3. | Varia | ability Characterization of Streaming Applications | 20 |

| 4. | Desi  | gn Space Exploration                               | 23 |

|    | 4.1   | Problem Description                                | 23 |

|    | 4.2   | Analytical Framework                               | 25 |

|    | 4.3   | Estimating buffer size requirements                | 27 |

|    | 4.4   | Conditions for pruning design space                | 28 |

| 5. | MPE   | G2 Case Study                                      | 30 |

|    | 5.1   | Candidate architectures                            | 32 |

|    | 5.2   | Initial Simulation                                 | 34 |

|    | 5.3   | Obtaining service curves from simulation trace     | 34 |

|    | 5.4   | Overview of Depth First DSE algorithm              | 35 |

|    | 5.5   | Choice of objective functions                      | 37 |

|    |       | 5.5.1 Cost model for Chip-space requirements       | 40 |

|    |       | 5.5.2 Chip-space estimation for on-chip buffers    | 41 |

|    | Contents                                                                         | 5        |

|----|----------------------------------------------------------------------------------|----------|

|    | <ul> <li>5.5.3 Estimating Power consumption of candidate architectures</li></ul> | 43<br>45 |

| 6. | Conclusions and Future Work                                                      | 49       |

| Ap | opendix                                                                          | 55       |

| Α. | Config file parameters for ppc604 like processor (source:SimScal)                | 56       |

| В. | Microarchitectural Configurations                                                | 58       |

| С. | Base configuration file                                                          | 63       |

| D. | Scripts for running the SimpleScalar simulations                                 | 65       |

| E. | Scripts for running the Wattch simulations                                       | 67       |

| F. | Details of Pareto Optimal Solutions                                              | 68       |

# LIST OF FIGURES

| 1.1 | Streaming Application                                                                   | 9  |

|-----|-----------------------------------------------------------------------------------------|----|

| 1.2 | Overview of DSE technique                                                               | 14 |

| 2.1 | Task Precedence Graph                                                                   | 18 |

| 2.2 | Kahn Process Network                                                                    | 19 |

| 3.1 | Application Model                                                                       | 20 |

| 4.1 | Example Design Space                                                                    | 27 |

| 5.1 | Experimental Framework                                                                  | 31 |

| 5.2 | MPEG2 Application Model                                                                 | 31 |

| 5.3 | Depth First DSE pseudo code                                                             | 36 |

| 5.4 | Depth First DSE program flow                                                            | 38 |

| 5.5 | Pareto Optimal Front creation                                                           | 39 |

| 5.6 | Points connected by line represent the Pareto Optimal front. Other points shown by tri- |    |

|     | angles are other feasible solutions dominated by some solution on the pareto-optimal    |    |

|     | front. Silicon costs are on horizontal axis and power costs on vertical axis            | 45 |

| 5.7 | Pareto Optimal Solution H                                                               | 47 |

| 5.8 | Pareto Optimal Solution K                                                               | 48 |

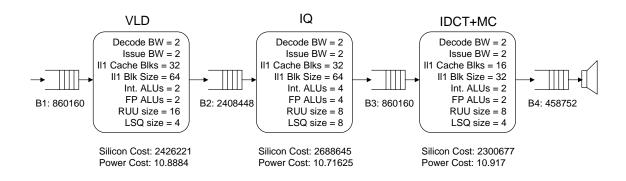

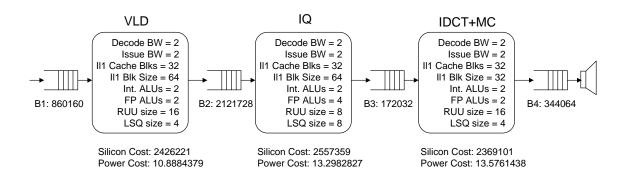

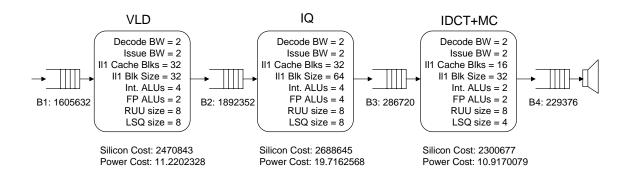

| F.1 | Pareto Optimal Solution B                                                               | 68 |

| F.2 | Pareto Optimal Solution J                                                               | 69 |

| F.3 | Pareto Optimal Solution P                                                               | 69 |

# LIST OF TABLES

| 5.1         | Microarchitectural parameters and their different values | 33 |

|-------------|----------------------------------------------------------|----|

| 5.2         | Transistor counts of different candidate architectures   | 42 |

| 5.3         | Power costs of different candidate architectures         | 44 |

| 5.4         | Performance statistics for MPEG2 case study              | 46 |

|             |                                                          |    |

| <b>B</b> .1 | Microarchitectral Configurations                         | 59 |

| B.2         | Microarchitectral Configurations (Cont.)                 | 60 |

| B.3         | Microarchitectral Configurations (Cont.)                 | 61 |

| <b>B</b> .4 | Microarchitectral Configurations (Cont.)                 | 62 |

#### 1. INTRODUCTION

Streaming application domain consists of a wide variety of applications from embedded systems (e.g. cell phones, hand held computers), desktop applications (e.g. real-time encryption, software radio, graphics packages) and high performance servers (e.g. network packet processors, cell phone base stations, software routers). Designing and implementing efficient HW/SW systems for these applications has been the focus of research for many researchers due to the huge commercial impact these systems create. With the increasing use of streaming media in hand held devices and increasing performance demand of applications running on these devices, it becomes more important for a system designer to utilize the system resources to the fullest. Although existing design methodologies for the HW/SW co-design of embedded systems can be applied to these systems, due to the ever growing complexity of the applications they may not be as efficient. Many multimedia streaming applications have to handle a highly compressed stream of media content. Most of the compression techniques exploit the similarity between successive frames in order to achieve more compression, and this similarity is not constant throughout the length of media. Highly compressed portions of the media need more processing for decoding and less compressed portions the less. Thus, for such media the decoder has to face the variable processing demand of the different portions of the stream. The system design methodologies can exploit this variability to optimize the system performance and resource utilization. Traditional design methodologies, hence, must be upgraded by taking into account these changing nature of applications.

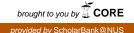

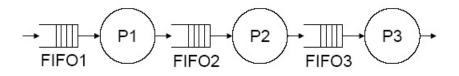

In a streaming application, a potentially infinite stream of data items enters the system, a number of tasks are performed on each data item before the output is sent to an output device. Typically the tasks performed on data items are independent and communicate with each other by FIFO channels. Each task reads data items from its input channel in a FIFO order, does some processing and writes the resulting data into the input channel of the next task. Due to this data dependent behavior of tasks, they can be mapped to a different processing element (PE) in a multiprocessor system. Portions of

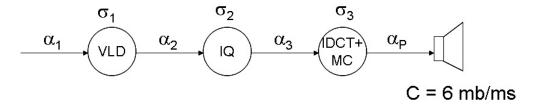

Fig. 1.1: Streaming Application

memory can be allocated as the FIFO channels. Both, the PE which writes to a channel and the PE which reads from the channel should share the memory allocated to the channel.

System-on-chip multiprocessors are widely used to implement these streaming applications due to their advantages in terms of performance, power, cost, and design turn-around time. In order to realize these advantages to the fullest, it is necessary to have an efficient design methodology which addresses the two aspects of the system design. First, efficiently mapping of tasks in the application to available computation units and second, designing an optimal communication network. In this work we concentrate on the first aspect.

Typically, a number of different processing tasks constitute a streaming application. Every task may have different processing requirements in terms of sheer processing power or control-intensiveness and computation intensiveness. Depending on these requirements, different processing architectures may be suitable for different tasks. For example, DSP's are most suitable for tasks which have regular computational loops where as general purpose processors are best for control intensive tasks. Further, in some streaming applications (e.g multimedia decoders) processing requirements are input dependent, in which case the processing requirements vary for different portions of the stream. For example the execution time required for decoding different frames of a mpeg2 decoder is highly variable. Further, with the advances in processor technology, ever growing number of processors are becoming available for mapping of tasks. Thus the system designer is faced with the difficult task of mapping the tasks on processing units in order to optimize overall system performance. In order to make the systems commercially feasible, cost of the overall system (in terms of silicon area and/or power consumption) must also be taken into account. This problem has been addressed mainly in 2 different aspects: 1) Given fixed amount of silicon resources, find the mapping such that system performance is maximized and overall system can be implemented on given amount of silicon. 2) Given an application specification with minimum performance requirements, find the mapping such that overall system can be implemented with minimum cost (silicon area or power). In first, the cost of resources acts the constraint and performance as the goal function. This approach is most suitable for network packet processors, or cell phone base stations etc. since network traffic might go up in future and it is desirable to push as much traffic as possible. However in this work, we take the second approach, where performance requirements act as constraints and overall costs of the system acts as the optimization function. This approach is more suitable for multimedia applications for which the output performance requirements are fixed (e.g. 20 frames/sec for video decoders).

Our technique uses initial simulation of tasks on individual processor types in order to estimate the worst case bounds on the execution requirements of the application. Using some results from the theory of network calculus, it is possible to combine the worst case bounds for many task-processor mappings to find the effective worst case bounds. This results in significant simulation time savings as follows. If T is the number of tasks in the application and n is the number of candidate architectures, the total simulation time required is:  $\sum_{0 < i < T} \sum_{0 < j < n} t_{ij}$ , where  $t_{ij}$  is the time required for simulating  $i^{th}$  task on  $j^{th}$  processor. Let  $t_{max} = max(t_{ij}) \forall i$ ,  $\forall j$ . Then  $\sum_{0 < i < T} \sum_{0 < j < n} t_{ij} \le t_{max} \times T \times n$ , which is O(nT). On the other hand if we explore the design space exhaustively and perform system level simulation for each design point, then  $total \ simulation \ time \le t_{max} \times T \times n^T$  which is  $O(Tn^T)$ . However the designer, with his experience, may be able to quickly eliminate some processors which are not suitable for some tasks. After such elimination, let  $n_i < n$  be the number of processors on which task  $T_i$  can be mapped. In this case the design space exploration with full system

level simulation. However with the task level simulation approach simulation time  $\leq t_{max} \times \sum n_i$ . It should be noted, however, that a full system simulation allows a more accurate estimation of performance as well as communication delays. The task level simulations are aimed only at performance estimation and are based on the assumption that once task mapping is done, a suitable communication network can be designed. This approach of independently exploring computation and communication architectures has been followed by many researchers as mentioned in Section 1.1.

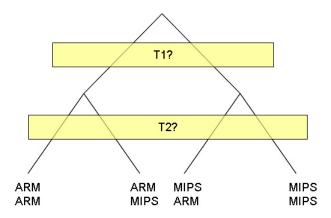

We used a depth-first approach for design space exploration, with every level in the design tree representing a mapping decision for a task and the number branches at every level representing the number of possible mappings. The cost of the explored path is computed by adding the costs of the candidate architectures chosen for tasks on the path. By candidate architecture we mean a processor with some microarchitectural properties like cache sizes, decode/issue widths etc. All commercial processors can be uniquely described by these microarchitectural properties. Hence we find it is more convenient to define the candidate architectures using their microarchitectural details.

A MPSoC designer is often faced with the challenge of designing systems with more than one design goals in mind. For example, in [31] performance of access network, performance of backbone network, and cost savings are used as objective functions. In [7] silicon cost of the system has been used as the objective function. One could imagine many more objectives like power, threshold etc. which could be of practical use to the designer. Further these objectives may be conflicting with each other, optimizing on one objective may result in degradation on the other objectives. In such a situation, it is essential for the designer to be able to evaluate trade-offs between different design points. Our DSE technique is capable of handling this multi-objective scenario and can produce a Pareto-Optimal front for a given set of objectives.

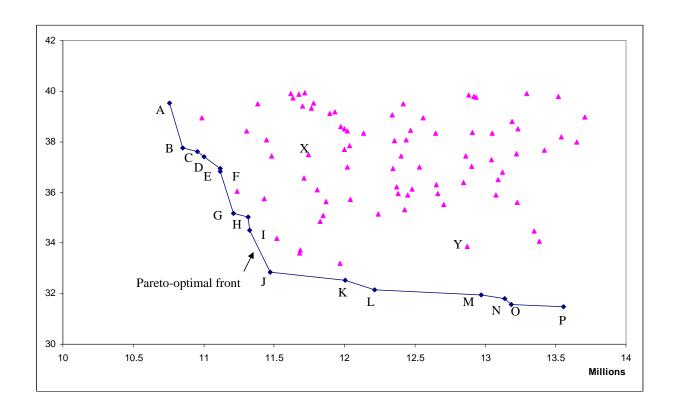

We used MPEG2 decoder application as the target application and implemented our scheme to find the pareto optimal front with mainly two objectives in mind: the architecture cost of the system and the average power consumption of the system. The architecture costs for different candidate architectures were derived from an empirical cost model described in [30] and the power numbers were obtained from Wattch simulator [2]. Our experiments prove the usefulness of the scheme.

#### 1.1 Related Work

Traditionally, most commercial SoCs are platform based [26, 16]. PROPHID [15] multiprocessor architecture, for example, is a bus based architecture with a general purpose processor for control processes and a number of Application Domain Specific (ADS) processors for performing tasks in the applications. ECLIPSE [26, 27] is another such heterogeneous SoC platform aimed at implementation of multimedia applications. They consist of a predefined communication architecture with a possibility of customizations in terms of choice of processing units, scheduling policies on the processing units, and on-chip buffer size requirements. One of the popular approaches for application design for platform based systems has been a cyclic process of performance estimation and tuning the platform for the application. Many evolutionary algorithm based techniques are developed for this purpose[31]. Many of these perform full system-level simulation [25] which makes them very timeconsuming. Many trace-based simulation techniques are developed in order to reduce the simulation time [17, 34]. SPADE [33] is a method and a tool in which applications and architectures are modeled in such a way that mapping of applications onto architectures, prior to architecture/application co-simulation, can be easily done. The co-simulation is trace-driven. The execution of the application generates traces of symbolic instructions, and these instructions are interpreted by the architecture thus revealing timing behavior. The TD cosimulation is fast because the architecture does not process the actual data. However the evolutionary approach does not guarantee optimality of the solution.

In DSE of multiprocessor SoC systems, many possible mappings of tasks onto different processors (e.g. GP, DSP, ASIC, FPGA) is possible. In order to find out *how good* a particular mapping is, there is a need for metrics which characterize each type of PE. In this context, the work in [28] finds out the *affinity* of each task toward different types of processors. An affinity of 1 indicates a perfect matching and 0 indicates no match. Given the source code for a task, they perform static analysis to find out metrics like *Control Flow Complexity (CFC), Loop Ratio (LR)* etc. A high value of CFC identifies a task which has lot of control flow and less computation. These tasks are suitable for GPPs. On the other hand a high value of LR indicates that the task is computationally intensive with lot of regular computations. These tasks are more suitable for DSPs. There are many more such metrics and weighted average of all metrics is taken to arrive at a global affinity value.

Ever growing demand of system performance forces the system designers to integrate more and

more processing elements in a single SoC to meet the performance requirement. Many researchers [12, 24, 14, 11] have proposed a new system design paradigm for such high performance SoCs, which involves separation between (1) function and architecture and (2) between communication and computation. Adopting this paradigm, design methodology proposed in [12], models the system behavior as a composition of function blocks and maps the function blocks to the processing elements of predefined target architecture. Separation between computation and communication in system design allows the system designer to explore the communication architecture independently of component selection and mapping.

An important aspect of system design is the representation of application using appropriate application model. Most of the work in the direction of HW/SW co-design [13, 4, 3, 18, 29] treats the application as a Task Graph [13, 3]. The tasks in such a task graph have data dependencies and a task can execute only when all its dependencies are satisfied. SoC design for such task graphs is typically solved as a scheduling problem. However as the applications become more and more complex, the number of tasks in the task graph grows rapidly. Representation of the applications using task-graphs thus becomes more cumbersome. Of late, Kahn Process Networks [10] have been used more popularly as the Model of Computation (MoC).

Synthesis of multiprocessor architecture for KPNs has been addressed in [8, 7, 6, 23, 19, 5]. The mapping problem is formulated as an ILP [8, 7] and thus produces optimal solution. However they assume fixed processing requirements for the tasks and regular memory access pattern, which may not be realistic in case of multimedia applications.

#### 1.2 Contributions

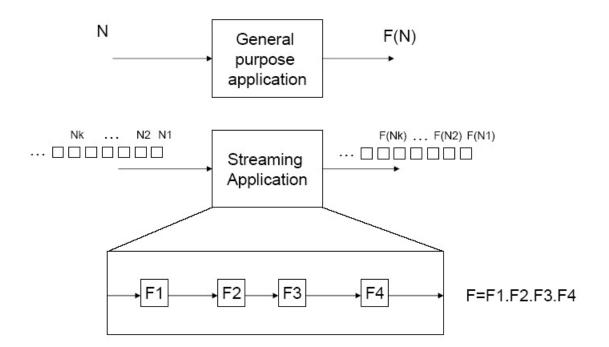

In this thesis, we present an innovative design space exploration (DSE) method using depth first exploration approach. Figure 1.2 depicts an overview of our method. We use Kahn Process Networks to model the applications. The aim of the DSE is to find the optimal mapping of processes (or tasks) to processing units (or candidate architectures). Our technique can handle multi-objective optimization scenario and produces a Pareto-Optimal front. The designer can use the pareto-optimal front to choose trade-offs between different objective functions. We use a simulation based performance estimation, which is not a new technique. However our approach is novel in that we perform simulation at the

Fig. 1.2: Overview of DSE technique

task level rather than system level. This gives the system designer flexibility of modifying a task and simulating only that task again. In this thesis, we used variability characterization curves or VCCs [21] to model the variability in the execution demand of multimedia applications. An overview of VCCs is also given in Chapter 3. Thus the mapping found by our algorithm is more accurate as compared to previous techniques which assume constant execution demand. The execution trace obtained from simulation, which essentially records the number of processor cycles required for each activation of a task, is used to find the VCCs for each (Task, Processor) pair. Once these individual curves are obtained, we use purely analytical methods from the theory of Network Calculus [1] to combine the individual VCCs for each task in order to estimate the overall system performance. Our depthfirst approach for searching the design space allows us to incrementally combine VCCs depending on which path is chosen for further searching. We show that it is possible to prune away certain portions of the design space using conditions specified in terms of timing constraint of the application which is another important contribution of this work. This leads to faster design space exploration without compromising the optimality of the solution. Thus our technique combines the advantages of ILP based techniques which guarantee optimality and the full system simulation based evolutionary techniques which are more accurate in performance estimation. We also compute the minimum buffer sizes required to prevent buffer overflows. Thus the optimal solution found by our DSE technique not only guarantees required output rate but also guarantees that none of the buffers overflow.

#### 1.3 Organization of the thesis

The two most common models of computation (MoCs), the Task Precedence Graph and Kahn Process Networks are discussed in Chapter 2. This chapter also discusses the advantages and disadvantages of the two MoCs and why we choose the later in this work. Chapter 3 describes the Variability Characterization Curves (VCCs) and how they can be used to represent the worst case characteristics of the on-chip traffic of data items created by the execution of different tasks. In Chapter 4, we develop an analytical framework using the VCCs for our design space exploration problem and provide some conditions which help us in pruning of the design space. Chapter 5 describes the experiments we performed in order to validate the usefulness of our DSE technique. We performed two sets of experiments, one using different cache configurations of the MIPS processor and another using different frequencies for the same processor. However it should be noted that our technique is fairly generic and can be applied to any processor architecture, subject to the availability of a simulation framework for that architecture. Chapter 6 summarizes the main contributions of this thesis and concludes.

#### 2. CHOICE OF APPLICATION MODEL

The main goal of application modeling is to use suitable Models of Computation (MoCs) for specifying a multi-media applications. Ideally, the MoC should allow a succinct representation of the application so that the inherent parallelism is exposed and can be exploited when mapping it an architecture. Two distinct models are generally used to describe streaming applications or parallel applications - Task Precedence Graph (or directed acyclic graphs) and Process Networks. Synthesis of optimal application specific multiprocessor architectures for DAG based periodic task graphs with real time processing requirements has been extensively studied in literature [4, 3, 18, 29] from cost as well as power optimization point of view. However, synthesis for process networks is not widely explored. The approaches for DAG based task graphs rely on static scheduling and solve the synthesis problem which essentially consists of architectural resource allocation, binding of application components to architecture, and scheduling. This approach can also be used for process networks as well by unrolling inner loops of processes and decomposing it in the form of a periodic DAG based task graph. Such an approach might lead to a very large size graph for most of the real life applications making the approach impractical.

#### 2.1 Task Precedence Graph

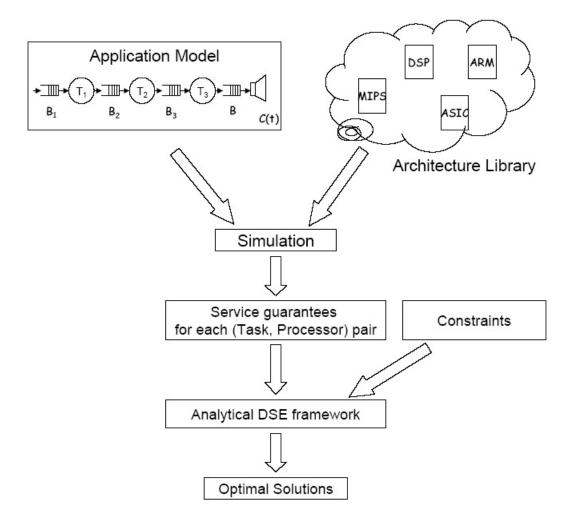

In a task precedence graph, nodes represent the tasks and the directed edges represent the execution dependencies as well as the amount of communication. DAGs are commonly used in static scheduling of a parallel program with tightly coupled tasks on multiprocessors. For example, in the task precedence graph shown in Figure 2.1, task n4 cannot commence execution before tasks n1 and n2 finish execution and gathers all the communication data from n2 and n3. For most applications, a task precedence graph can model the program more accurately because it captures the temporal dependencies among tasks.

Fig. 2.1: Task Precedence Graph

Formally, A parallel program can be represented by a directed acyclic graph (DAG) G = (V, E), where V is a set of v nodes and E is a set of e directed edges. A node in the DAG represents a task which in turn is a set of instructions which must be executed sequentially without preemption in the same processor. The weight of a node  $n_i$  is called the computation cost and is denoted by  $w(n_i)$ . The edges in the DAG, each of which is denoted by  $(n_i, n_j)$ , correspond to the communication messages and precedence constraints among the nodes. The weight of an edge is called the communication cost of the edge and is denoted by  $c(n_i, n_j)$ .

Synthesis of application specific architecture for an application described using DAG has been solved as resource allocation, binding of application components to resources and scheduling problem in [13].

The objective of scheduling is to minimize the completion time of a concurrent application (such as streaming) by properly allocating the tasks to the processors. In a broad sense, the scheduling problem exists in two forms: *static* and *dynamic*. In static scheduling, which is usually done at compile time, the characteristics of a parallel program (such as task processing times, communication, data

Fig. 2.2: Kahn Process Network

dependencies, and synchronization requirements) are known before program execution. A parallel program, therefore, can be represented by a node- and edge-weighted directed acyclic graph (DAG), in which the node weights represent task processing times and the edge weights represent data dependencies as well as the communication times between tasks.

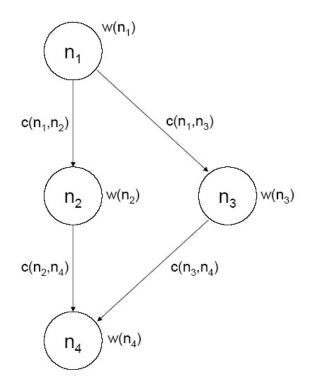

#### 2.2 Process Networks

We specify media-processing applications as a set of concurrently executing tasks that exchange information solely by unidirectional streams of data. A directed graph with a node for each task and an edge for each data stream represents the structure of the application. Process network, introduced by Kahn in [10], is popularly used as the model of computation (MoC) for specifying these kind of applications. A Kahn process network (KPN) consists of executable *processes* that communicate point-to-point over unbounded FIFO *channels* and synchronize by means of blocking reads. Figure 2.2 shows an example of KPN.

We chose Kahn Process Networks as application model due to the fact that Kahn models nicely fit with the dataflow application domain (to which most of multimedia applications belong) and that they are *deterministic*. The latter means that the same application input always results in the same application output. So, the functionality of a Kahn application is not affected by architectural latencies, i.e. the application behavior is architecture independent.

#### 3. VARIABILITY CHARACTERIZATION OF STREAMING APPLICATIONS

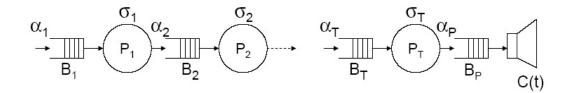

We model streaming applications using the model depicted in Figure 3.1. The application consists of T tasks (or processes),  $P_1$ ,  $P_2$ , ...,  $P_T$ . Each task  $P_i$  has an input buffer  $B_i$  which is a FIFO channel of fixed capacity. These buffers are used to store the input stream temporarily until it is consumed by the processor. Each task  $P_i$  can be imagined as an infinite loop. At the beginning of each iteration it reads a data item from its input buffer  $B_i$ . The body of the loop performs some processing on this data item and finally the output data item is written to the input buffer of the next task i.e  $B_{i+1}$ . The output of the last task is written to the *playout buffer* B. A real-time client (RTC) such as a audio or video output device consumes data items from playout buffer at a fixed rate C (e.g. 20 fps for a video device).

For the sake of generality, we consider any multimedia stream to be made up of a sequence of *stream objects*. A stream object might be a bit belonging to a compressed bit stream representing a coded video clip, or a macroblock, or a video frame, or an audio sample—depending on where in the architecture the stream exists. For example, in case of an MPEG-2 decoder the stream objects are nothing but the macroblocks which constitute the frames in the video.

Variability characterization curves (VCCs) are used to quantify best-case and worst-case characteristics of *sequences*. These can be sequences of consecutive stream objects belonging to a stream, sequences of consecutive executions of a task implemented on a PE while processing a stream, or sequences of consecutive time intervals of some specified length. A VCC  $\mathcal{V}$  is composed of a tuple

Fig. 3.1: Application Model

$(\mathcal{V}^{l}(k), \mathcal{V}^{u}(k))$ . Both these functions take an integer k as the input parameter, which represents the *length* of a sequence.  $\mathcal{V}^{l}(k)$  then returns a *lower bound* on some property that holds for *all* subsequences of length k within some larger sequence. Similarly,  $\mathcal{V}^{u}(k)$  returns the corresponding *upper bound* that holds for *all* subsequences of length k within the larger sequence. Let the function P be a *measure* of some property over a sequence  $1, 2, \ldots$ . If P(n) denotes the measure of this property for the first n items of the sequence (i.e.  $1, \ldots, n$ ), then  $\mathcal{V}^{l}(k) \leq P(i+k) - P(i) \leq \mathcal{V}^{u}(k)$  for all  $i, k \geq 1$ .

For every input buffer  $B_i$ , let  $x_i(t)$  which represent the number of data items arriving in the buffer in an interval of time from 0 to t. We define arrival curve  $\alpha_i = (\alpha_i^u, \alpha_i^l)$  for  $i^{th}$  task as:

$$\alpha_i^u(\Delta) = \sup_{t \ge 0} \{x_i(t+\Delta) - x_i(t)\} \forall \Delta \ge 0$$

$$\alpha_i^l(\Delta) = \inf_{t \ge 0} \{x_i(t+\Delta) - x_i(t)\} \forall \Delta \ge 0$$

$\alpha_i^u(\Delta)$  (upper arrival curve) denotes the maximum number of data items arriving in  $B_i$  during any interval of length  $\Delta$  and  $\alpha_i^l(\Delta)$  (lower arrival curve) denotes the minimum. Thus using arrival curves we can capture the worst case burstiness of the streams arriving in the buffers.

Similarly with every task  $P_i$  we associate  $y_i(t)$  which represents the number of data items processed by the task in an interval of time from 0 to t. And the service curve  $\sigma_i = (\sigma_i^u, \sigma_i^l)$  is defined as:

$$\sigma_i^u(\Delta) = \sup_{t \ge 0} \{y_i(t + \Delta) - y_i(t)\} \forall \Delta \ge 0$$

$$\sigma_i^l(\Delta) = \inf_{t \ge 0} \{y_i(t + \Delta) - y_i(t)\} \forall \Delta \ge 0$$

$\sigma_i^u(\Delta)$  (upper service curve) denotes the maximum number of data items processed within any interval of length  $\Delta$  and  $\sigma_i^l(\Delta)$  (lower service curve). Thus using service curves we can estimate worst case service guarantees for an incoming stream.

In this work, we want to ensure that the streaming application produces its expected real-time output even in the presence of the worst case arrival rate  $\alpha_i^l$  and worst case service rate  $\sigma_i^l$ . Thus we use only the lower arrival curves and service curves in the rest of the paper. And for the simplicity of notation we use  $\alpha_i$  and  $\sigma_i$  instead of  $\alpha_i^l$  and  $\sigma_i^l$  respectively.

Using standard results from the theory of network calculus[1], we compute  $\alpha_{i+1}(\Delta)$  as:

$$\alpha_{i+1}(\Delta) = (\alpha_i \otimes \sigma_i)(\Delta) \forall i$$

(3.1)

where, for any two functions f and g, the min-plus convolution of f and g is given by  $(f \otimes g)(t) = \inf_{s:0 \le s \le t} \{f(s) + g(t-s)\}.$

The minimum buffer size required to prevent the input buffer of  $i^{th}$  task from overflowing can be calculated as:

$$B_i = \sup_{\Delta \ge 0} \{ \alpha_i(\Delta) - \alpha_{i+1}(\Delta) \}$$

(3.2)

And the minimum playout buffer size required to prevent overflow can be calculated as:

$$B_p = \sup_{\Delta \ge 0} \{ \alpha_p(\Delta) - C(\Delta) \}$$

(3.3)

Please refer to [1] and [21] for the detailed derivation of these results. Thus the total on-chip buffer required to prevent any of the buffers from overflowing is computed as:

$$B = \sum_{1}^{T} B_i \tag{3.4}$$

These Variability Characterization Curves (VCCs) have been used [21] in order to identify system level design trade-offs for multimedia processing SoC platforms. We use VCCs to characterize each task when mapped to different processing units, and identify the optimal mapping of tasks to processing units.

#### 4. DESIGN SPACE EXPLORATION

#### 4.1 Problem Description

Streaming applications consist of a sequence of tasks, each of which has a different processing requirements. Some tasks are control intensive for which general purpose processors like MIPS or ARM are most suitable. On the other hand DSPs are more suitable for tasks which are computationally intensive. At a much lower level, each processor is characterized by some microarchitectural parameters like issue and decode width, number of integer and floating point ALUs, instruction and data cache sizes, RUUs, LSOs etc. A task in a streaming application may run more efficiently one setting of these microarchitectural parameters and less for another setting. Further, the designer of a SoC system can choose to run the processors at different frequencies in order to save power and at the same time meet the execution requirements of the application. This gives rise to a design space which has a size  $n^T$ , if T is the number of tasks and n the number of different candidate architectures on which they can be mapped to. For the sake of generality, we define each candidate architecture by using the microarchitectural parameters mentioned above, rather than using names of the processors. It should be noted that, almost all commercial processors can be represented using these microarchitectural parameters. For example, Appendix A shows the parameters that describe a processor similar to PowerPC604 (source: simscal [30]). None of the previous works [8, 7, 31] in this direction have considered the microarchitectural details. In Section 5.5 we describe how these microarchitectural properties help us in accurately estimating the costs associated with each candidate architecture.

The goal of this work is to propose a design space exploration method which finds the optimal mapping of T tasks onto any of the n candidate architectures in the architecture library. Potentially there could be more than one optimality criteria, each optimality criteria being one of the objective functions of our multi-objective framework. One of the outcomes of our DSE is a Pareto-Optimal front of solutions, which is nothing but the set of all design points which are not *dominated* by any

other design point. The formal definition of Pareto-optimality is as follows:

If C is a set of all cost vectors  $c \in R^k$  where is k is the number of objectives, then a cost vector  $c \in C$  dominates  $d \in C$ , if  $c_i \leq d_i$ ,  $\forall i \in (0, k - 1)$  and  $c_j < d_j$  for at least one  $j \in (0, k - 1)$ . A cost vector is Pareto-Optimal if it is not dominated by any other cost vector.

The pareto-optimal front allows a system designer to identify trade-offs between different design objectives like cost, power, on-chip buffer size etc. It should be noted that to be a candidate for inclusion in the pareto-optimal front, the solution has to first satisfy the timing requirements of the application.

The target SoC platforms are assumed to consist of a number of processing elements (PEs) connected by a point-to-point communication network (e.g. RAW [22]) so that the communication conflicts are minimized. The PEs are assumed to have local memories that can fit the input FIFO buffers for the tasks mapped to them thus memory access conflicts are minimized. Thus the mapping problem of tasks to processing units can be addressed independently of the design of communication or memory architecture. Extensive research [12, 24, 14, 11] in the the direction of communication and memory architecture for SoCs shows that these assumptions are safe. They are also in keeping with the latest trends in SoC design methodology which divide the system design in two phases: 1)Mapping of tasks to processing units, and, 2) design of memory and communication architecture, of which we address the first in this work.

In summary, our problem setup consists of an *application* modeled as a Process Network along with the desired output rate C for that application, and *Architecture Library* of all types of processors available for mapping along with the cost of each type of processor. It should be noted that the service curves  $\sigma_{ij}$  for each  $(Task_i, Processor_j)$  pair are available in advance through initial simulation of tasks on processors. Each *candidate solution* is a n-tuple of the form  $(M_1, M_2, ..., M_T)$ , where the value of each mapping variable  $M_i$  points to a candidate architecture in the architecture library, clearly  $1 \le M_i \le n$ ,  $\forall i$ . Each candidate solution refers to a leaf node in the design space. We refer to intermediate nodes (non-leaf) as partial solutions. A *partial solution* is essentially a n-tuple of the form  $(M_1, M_2, ..., M_T)$  with  $1 \le M_i \le n$ ,  $\forall i \le t$ , for some t < T and  $M_i = 0$ ,  $\forall i > t$ .

VLSI technology dependent factors such as total maximum silicon area  $(C_{max})$  available for system implementation and total maximum power  $(P_{max})$  available to the system, are taken as external

inputs to our framework. We use  $C_{max}$  and  $P_{max}$  as conditions for pruning certain portions of the design space. Every time we go one step deeper in the design space, we apply these conditions to the partial solution. If the cost of the partial solution exceeds  $C_{max}$  or the total power consumption exceeds  $P_{max}$  then the search along that path is abandoned. These upper bounds can be used to restrict the search within practical limits of realizing the MPSoC.

#### 4.2 Analytical Framework

Using the result 3.1 recursively we compute  $\alpha_p$ , the rate of arrival of data items at the playout buffer, as:

$$\alpha_p(\Delta) = ((\dots(\alpha_1 \otimes \sigma_1) \otimes \sigma_2) \dots \otimes \sigma_T)(\Delta)$$

(4.1)

The timing constraint for successful execution of this application can be specified as:

$$\alpha_p(\Delta) \ge C.\Delta, \ \forall \ \Delta > 0 \tag{4.2}$$

We define:

- Infeasible Solution: A mapping for which above timing constraint is not satisfied.

- Feasible Solution: A mapping for which above timing constraint is satisfied.

- Optimal Solution: A Feasible solution which has the least cost.

In the above discussion, the service curves depend on the mapping of a task on a processing unit. For example,  $\sigma_{11}$  (in case  $T_1$  is mapped to processor type 1) is not the same as  $\sigma_{12}$  (in case  $T_1$  is mapped to processor type 2). We use binary decision variables  $x_{ij}$ , which is true when  $i^{th}$  task is mapped to  $j^{th}$  processor type. We write the above equations as :

$$\alpha_{i+1}(\Delta) = (\alpha_i \otimes \sigma_{i1})(\Delta).x_{i1} + \dots + (\alpha_i \otimes \sigma_{in})(\Delta).x_{in}$$

$$= (\alpha_i \otimes (\sigma_{i1}.x_{i1} + \dots + \sigma_{in}.x_{in}))(\Delta)$$

And the rate of arrival of data items in the playout buffer can be expressed as:

$$\alpha_{p}(\Delta) = ((...(\alpha_{1} \otimes (\sigma_{11}.x_{11} + \sigma_{12}.x_{12} + ... + \sigma_{1n}.x_{1n}) \\ \otimes (\sigma_{21}.x_{21} + \sigma_{22}.x_{22} + ... + \sigma_{2n}.x_{2n})) \\ ... \\ \otimes (\sigma_{t1}.x_{t1} + \sigma_{t2}.x_{t2} + ... + \sigma_{tn}.x_{tn}))(\Delta) \\ > C(\Delta), \ \forall \ \Delta > 0$$

This serves as a feasibility condition for solutions. Any design space exploration method can use this condition to evaluate candidate solutions from the design space. We discuss the advantages and disadvantages of several search techniques and propose our depth-first-search algorithm.

- Evolutionary Algorithms: They have mainly two parts, a mechanism for choosing potential solutions from the entire population of solutions, and a mechanism that evaluates the 'fitness' of these potential solutions. The feasibility condition mentioned above can serve as the mechanism to evaluate the fitness of a design point. However the mechanism for choosing the potential solutions is ad-hoc and may not lead to the optimal solution.

- ILP: There have been attempts to come up with an ILP formulation for this mapping problem. However the ILP formulation is made possible due to the assumption that the tasks have fixed execution requirement. Also they assume a regular memory access pattern. However the execution requirement for most multimedia applications has a lot of variability. The above feasibility condition accounts for variability through the use of variability characterization curves such as arrival curves and service curves. Due to the non-linear nature of the variability curves, an ILP formulation becomes impossible.

- Proposed Algorithm (DepthFirstDSE): The design space can be represented as a tree of height *T* (number of tasks), with *n* (number of different processing units) child nodes per node except the leaf nodes. Every level in the tree represents a mapping decision for a task. Due to the sequential flow of data items through the application, the mapping of a task determines the arrival curve of data items for the next task which in turn decides the mapping for that task and so on. Thus a depth-first approach for searching this design space is the most suitable.

Fig. 4.1: Example Design Space

For example, using T = 2, n = 2 in the feasibility condition above and re-arranging the terms, we get:

$$\alpha_p(\Delta) = ((\alpha_1 \otimes \sigma_{11} \otimes \sigma_{21}).x_{11}.x_{21} + (\alpha_1 \otimes \sigma_{11} \otimes \sigma_{22}).x_{11}.x_{22} + (\alpha_1 \otimes \sigma_{12} \otimes \sigma_{21}).x_{12}.x_{21} + (\alpha_1 \otimes \sigma_{12} \otimes \sigma_{22}).x_{12}.x_{22})(\Delta) > C(\Delta), \forall \Delta > 0$$

It can be seen that  $\alpha_p$  is made of 4 terms, each corresponding to a path in the tree which also represents a solution in the search space. It is easy to see that, in case of T tasks and n processor types,  $\alpha_p$  is made of  $n^T$  terms, each corresponding to a unique path in the design space and representing a possible mapping instance. It should be noted that, mapping for a task decides the Arrival Curve of data items for the next task. This indicates the suitability of our depth-first approach for design space exploration.

#### 4.3 Estimating buffer size requirements

Using the results from theory of network calculus, the minimum buffer size required to prevent the input channel of  $T_i$  from overflowing can be calculated as:

$$B_i = \sup_{\Delta \ge 0} \{ \alpha_i(\Delta) - \alpha_{i+1}(\Delta) \}$$

(4.3)

where  $\alpha_i$  is the arrival rate of streaming objects at the input channel of  $T_i$  and it depends on which processor the task is mapped to. And the minimum playout buffer size required to prevent overflow can be calculated as:

$$B_p = \sup_{\Delta > 0} \{ \alpha_p(\Delta) - C(\Delta) \}$$

(4.4)

Thus the total buffer cost of a solution is:

$$B = B_p + \sum_{1}^{T} B_i \tag{4.5}$$

This buffer size estimate depends on service rates for the tasks which depend on the type of processor the task is mapped to. This buffer size can used to measure the *goodness* of a mapping, less the buffer size better is the mapping. It is well known that SRAM based components such as caches etc. occupy significant portion of silicon chip in modern processors. In a MPSoC with many processing units on a single die of silicon, it becomes even more important to minimize the buffer sizes. Later in Section 5.5.1 we describe how estimates from Equation 4.5 are used as part of the overall silicon chip-space requirements of the system.

The actual chip area numbers  $(C_j$ 's) can be obtained from the data sheets of the processors or can be derived from a well defined cost model. We have discussed some of these cost models in Section 5.5. The cost model for our second objective function: power consumption of the system is also discussed in the same section.

#### 4.4 Conditions for pruning design space

As we explore the design space with a depth first approach, it is possible to eliminate some portions of the tree without having to go down to the leaf nodes. We introduced some conditions at each level in the design tree. If these conditions are satisfied at any node in the tree then part of the tree rooted at that node is eliminated. This may improve the running time of the algorithm significantly.

We used mainly two types of conditions at each level in the design space. The first is based on timing properties of the stream. We check if  $\alpha(\Delta) < C.\Delta$ ,  $\forall \Delta > 0$ . This condition implies that the output rates of processors along this path of the design space are too weak to satisfy the overall performance requirement of the application i.e  $\alpha_p(\Delta) \ge C.\Delta, \forall \Delta > 0$ . Thus all the solutions in the part of the design space rooted at this node can be safely eliminated in order to save running time.

The second type of conditions we used were based on certain technology dependent upper bounds on the overall costs of the solutions. Our multiobjective approach considers many types of costs like silicon chip area, power consumption etc. Each of these costs has a upper limit, for example, silicon requirements of the MPSoC are limited by the maximum number of transistors that can fit on a single die of silicon (*max\_silicon\_cost*) or availability of maximum power supply for the system (*max\_power\_cost*). At each level in the design tree we check if the costs of path explored so far are greater than the upper bounds and in that case we abandone the search along that path.

As will be discussed in the experimental results, these conditions cause significant improvement in the running time of the algorithm.

#### 5. MPEG2 CASE STUDY

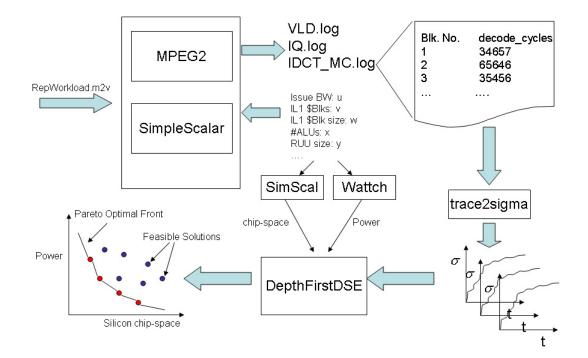

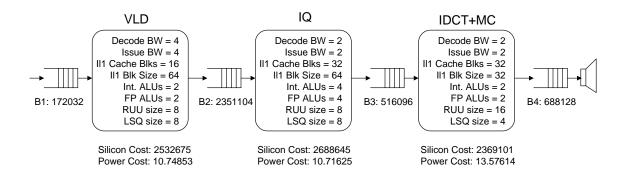

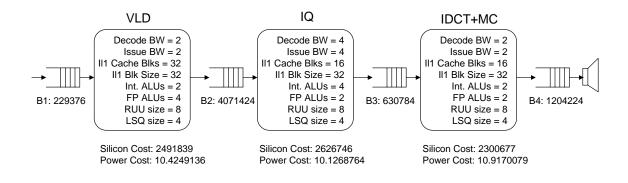

Our experimental setup is as shown in Figure 5.1. We used MPEG2 decoder as an example multimedia application for our experiments. We partitioned the application into 3 tasks: VLD, IQ, and IDCT+MC as the third task. Each task is simulated on different candidate architectures using SimpleScalar simulator and a simulation trace is obtained. For the experimental verification of our technique, we choose different microarchitectural configurations as the candidate architectures, described in more detail in Section 5.1. The *simulation trace* is essentially contains the the number of processor cycles required for each activation of the tasks. It should be noted that, although we need to simulate the tasks on each of the candidate architectures, this has to be done only once. Moreover in the context of industrial development of applications which happens in an incremental fashion with small changes to some of the tasks in the application, this simulation has to be carried out only on the modified tasks. Thus this technique will save valuable simulation time, as compared to other DSE techniques which require full system simulation.

Simulation traces are then passed on to the trace2sigma utility that we implemented which converts the traces into the service curves by counting the number of macroblocks decoded per unit of time. If service curves for different frequencies need to be obtained, then trace2sigma should be run many times with different frequency parameters.

Each candidate architecture is associated with two types of costs - silicon chip space required and the power consumed. These two act as the two objective functions of our multi objective optimization. We used a chip-space estimation model described in [30] to evaluate the first cost function and Wattch [2] to evaluate the second cost function. The designer's goal is to minimize both types of costs. However it may not always be possible to minimize both costs, which results in many trade-offs between the two costs. Our search algorithm keeps track of all these trade-offs and represents them in the form of a Pareto-optimal front. Section 5.5 describes the cost models in more details.

The service curves and the cost numbers from the cost functions are then passed on to the Depth-

Fig. 5.1: Experimental Framework

Fig. 5.2: MPEG2 Application Model

FirstDSE algorithm. This algorithm uses feasibility condition mentioned in Section 4.2 to ascertain if one of the  $n^T$  possible mappings of tasks on to the candidate architectures satisfies the performance requirements of the application (mpeg2 in this case). Once a mapping is found to satisfy the performance constraint, the costs associated with the mapping are computed by adding the costs of each individual candidate architecture which constitutes the mapping. Each mapping that satisfies the performance constraint is evaluated using multiple objective functions. The algorithm checks for the pareto-optimality of the mapping using the multiple objective functions. The final outcome of the algorithm is the pareto-optimal front which allows one to decide trade-offs between many types of costs associated with the MPSoC system. All the necessary information about the performance requirements of the application is available in the form of the service curves. The system designer has to provide the information about the cost of each architecture in the architecture library and the desired output rate (C) at the playout buffer. All this information is then passed on to the DepthFirstDSE algorithm, which finds the least cost mapping for each task such that the application as a whole produces output at the desired rate C.

## 5.1 Candidate architectures

Having decided to use SimpleScalar for our simulations, which allows microarchitectural customizations through a configuration file, simulating different candidate architectures could be easily done by setting different microarchitectural parameters in the configuration file. Some of these parameters are listed below:

- *fetch:ifqsize <size>* Instruction fetch queue size

- *decode:width <#instructions>* Decode bandwidth

- *issue:width <#instructions>* Issue bandwidth

- *ruu:size <size>* size of the Register Update Unit

- *lsq:size <size>* size of Load Store Queue

- cache:il1 <#blks>:<blksize>:<assoc>:<repl\_policy> Level 1 instruction cache configuration

- <#blks> : Number of cache blocks

- <blksize> : Cache block size (bytes)

- <assoc> : Cache associativity

- <repl\_policy>: Replacement policy (e.g least recently used (LRU))

#### [Similarly for il2, dl1, dl2 caches]

- *res:ialu* <*#ialu>* number of integer ALUs

- *res:imult* <*#imul>* number of integer multiplier/dividers

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ | Il1Cacheblks | Il 1blksize | IntALUs | FPALUs | RUUSize | LSQsize |

|-------------------------------------------------------|--------------|-------------|---------|--------|---------|---------|

| 2:2                                                   | 16           | 32          | 2       | 2      | 16      | 8       |

| 4:4                                                   | 32           | 64          | 4       | 4      | 8       | 4       |

Tab. 5.1: Microarchitectural parameters and their different values

- *res:fpalu* <*#fpalu>* number of floating point ALUs

- *res:fpmult* <#fpmul> number of floating point multiplier/dividers

- ...

Many real processors can be emulated by setting appropriate values for the parameters in the configuration file. For example, Appendix A shows a configuration file which emulates PowerPC604 like processor.

From the microarchitectural parameters mentioned above, we chose some parameters which we feel are closely related to the performance of the task. We defined our candidate architectures using different combinations of values for the chosen set of parameters. Table 5.1 shows the parameters and their different values. Allowing two different values for each parameter results in 128 ( $2 \times 2 \times 2 \times 2 \times 2$  $2 \times 2 \times 2$ ) different microarchitectural configurations. The possible values of parameters were chosen by looking at some existing processor architectures. For example, most superscalars have decode and issue width of 2 or 4 ([22]). Similarly we were conservative in choosing the size and number of Icache blocks, due to small size of the application in question, the MPEG2 decoder, and the presence of regular loops in the code. We believe that choosing bigger I-cache sizes might result in almost all code being able to fit into the I-cache and if that happens there will not be significant performance difference between two configurations. Number of integer and floating point ALUs and RUU and LSQ sizes were also chosen after looking at configurations of some real processors (Appendix A). Detailed listing of configurations is attached in Appendix B. Appendix C shows an example of a SimpleScalar configuration file. Configuration files for all of the 128 candidates can be reproduced by using data from appendix B. We feel that this design space is big enough for validating the usefulness of our technique. It is worth mentioning here that in [31] only four architectures (ARM, PowerPC,  $\mu$ engine, DSP) were considered. Another work in this direction [7] also considers 4 arbitrary architectures, and does not even mention any of the microarchitectural details.

#### 5.2 Initial Simulation

Any design technique that relies on simulation as a means of performance estimation, is faced with the problem of selecting *representative workload*, which is a well recognized problem in the domain of multiprocessor SoC design. Ideally, each implementation of an application on a MPSoC architecture has to be evaluated for a large number of possible inputs. However, this is an expensive process since the simulation involved for each input might require a considerable amount of time [32]. It is necessary for the designer to able to choose small *representative* set of inputs from a large library. A systematic solution for this is proposed in [20]. This work is based on the hypothesis that all the characteristics of multimedia streams that influence the performance of a MPSoC platform architecture, are related to their *variability*. Given a library of multimedia streams, they classify two streams as *similar* if both of them exhibit the same kind of variability with respect to execution time requirements and input/output rates as mentioned above. Once all similar workloads have been recognized, it is enough only to simulate one of these workloads. Following the rigorous workload selection process mentioned in this work is beyond the scope of this thesis, hence we use a sample video clip for our experiments. However it should be noted that the clip used is long enough and is representative of the behavior of all video clips as far as the worst case properties like service curves are concerned.

#### 5.3 Obtaining service curves from simulation trace

Service curves of each candidate architecture are obtained using the trace2sigma utility that we implemented. It takes as input the simulation trace and produces the number of macroblocks processed per unit of time. Since trace2sigma allows us to specify the processor frequency, the service curves for different frequencies can be derived easily. For example, if frequency specified is 10 MHz then we count the number of macroblocks that are processed in first 10<sup>7</sup> processor cycles, next 2 \* 10<sup>7</sup> cycles and so on (assuming a second as the unit time, however if a ms is used as the unit then trace2sigma samples the trace at every 10<sup>4</sup> processor cycles). This gives us  $y_i(t)$  as mentioned in Chapter 3. And the derivation of  $\sigma(\Delta)$  is straightforward as described in the same chapter.

We assume that the output device consumes data from the playout buffer at 20 frames per second, which is the value of C in this case. According to MPEG2 standard, each macroblock is of size

$16 \times 16$  pixels. For a MPEG2 video clip with resolution  $W \times H$  pixels, the number of macroblocks per frame is  $\frac{W \times H}{16 \times 16}$ . Thus an output rate of 20 fps translates to  $\frac{W \times H}{16 \times 16} \times 20$  macroblocks per sec. All our experiments were performed using this output rate.

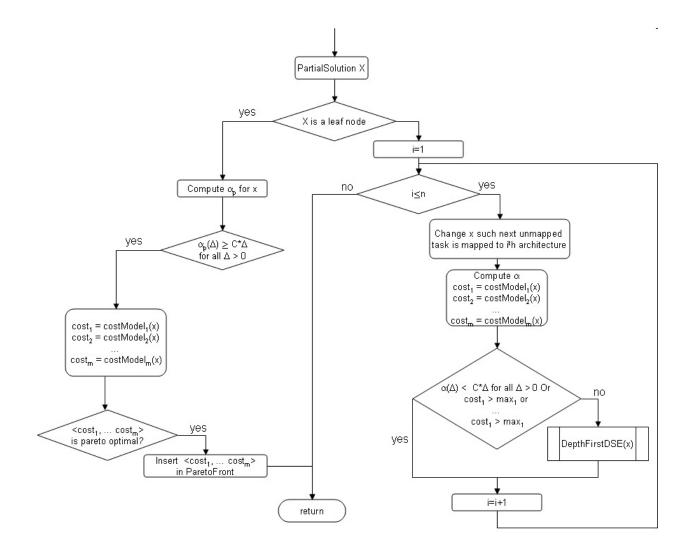

#### 5.4 Overview of Depth First DSE algorithm

Central to our DSE technique is a simple depth-first DSE algorithm that we implemented. Figure 5.3 shows the pseudo-code for this algorithm. This is a recursive depth-first search algorithm which takes as input a *PartialSolution* data structure, which stores the mapping of some or all of the tasks. This data structure is nothing but an array of size equal to the number of tasks. The value of each element in the array indicates the mapping for that tasks. For example, if x[i] = j then  $i^{th}$  task is mapped to  $j^{th}$  candidate architecture. x[i] = 0 means mapping decision for  $i^{th}$  task has not been made. First call to DepthFirstDSE is made by the *main* function with  $x[i] = 0 \forall i$ , which means none of the tasks have been mapped.

DepthFirstDSE first checks if the *PartialSolution* x is a leaf node in the design space (i.e.  $x[i] = 0 \forall i$ ). If it is then it computes the  $\alpha$ 's at the input of each FIFO buffer by using the  $\sigma$ 's corresponding to the candidate architectures chosen by the solution and applying the analytical results mentioned in Chapter 4. Once the  $\alpha$  at the input of *playout buffer* is calculated, it checks if the application satisfies the real-time output constraint ( $\alpha(\Delta) \ge C \times \Delta$ ,  $\forall \Delta > 0$ ), where *C* is the rate at which real-time output device consumes streaming objects (macroblocks in this case) from the playout buffer. If this condition is satisfied, which means that this is a feasible solution, then the costs of this solution are computed. A solution is made of mapping of tasks to candidate architectures and each candidate architecture may have different types of costs associated with it. The costs which are specific to candidates are calculated by invoking the cost models for each of them and adding up the results. As described in Section 5.5.2 later, the on-chip buffers used for communication between processing units also contribute to certain costs such as silicon chip space requirements. The estimated buffer cost is computed by function *bufferCost()* and added to the overall silicon cost.

If the PartialSolution x is not a leaf node in the design space (not all the tasks are mapped) then it tries to map the next unmapped task onto all possible candidate architectures. For every possible mapping of the next task, first it checks for a timing condition. The function TimingCondition()

```

Void DepthFirstDSE(PartialSolution x) {

If x is a leaf node in the design space {

// x[j] > 0 for all j

Compute the arrival rate \alpha at the playout buffer;

If (\alpha_n(\Delta)) \ge C^*\Delta for all \Delta > 0 ) // solution satisfies performance constraint

cost_1 = costModel_1(x); // invokes costModel1 for x[1], ..., x[T] and returns sum

cost_m = costModel_m (x); // invokes costModelm for x[1], ..., x[T] and returns sum

// above costs depend on costs of individual candidate architectures

// some other costs like buffer costs depend on mapping of two consecutive tasks

cost buff = bufferCost(x);

// buffers contribute to silicon chip-space requirements

// assuming cost1 is silicon chip-space requirement of candidate architectures

cost_1 += cost buff:

if(isParetoOptimal(cost<sub>1</sub>, cost<sub>2</sub>, ..., cost<sub>m</sub>))

// checks if the cost vector is pareto-optimal

// if yes, it is inserted to Pareto Front

insertIntoParetoFront(x, cost<sub>1</sub>, cost<sub>2</sub>, ..., cost<sub>m</sub>);

}

}

else { // x is a partial solution; x[j] > 0 for 0 \le j \le k; x[j] = 0 for k \le j \le n

for(i=1;i<=nArchitectures;i++) {</pre>

update x such that next unmapped task is mapped to ith candidate architecture;

if(TimingCondition(x))

; // this path will not lead to a solution that satisfies the output rate requirements

else {

cost<sub>1</sub> = costModel<sub>1</sub> (x); // invokes costModel1 for x[1], ..., x[k] and returns sum

...

cost_m = costModel_m (x); // invokes costModelm for x[1], ..., x[k] and returns sum

// since x is a partial solution, compute buffer costs for tasks which are mapped

cost_buff = bufferCost(x);

// assuming cost_1 is the silicon chip space

cost_1 += cost\_buff;

if(cost_1 > max_1 OR cost_2 > max_2 ... OR cost_m > max_m)

; // Costs of solutions along this path exceed some technology dependent

// upper bounds though these solutions satisfy timing requirements,

// they can not be implemented using prevalent fabrication technology

}

else

// call recursively with updated solution

DepthFirstDSE(x);

}

}

}

}

```

essentially implements the check  $\alpha(\Delta) < C.\Delta, \forall \Delta > 0$  mentioned earlier in Section 4.4. Next, the costs of the *PartialSolution* are computed and compared against some technology dependent upper limits, which is the second condition mentioned in Section 4.4. If any of these costs exceed these upper bounds then search along this path is abandoned. These upper bounds give the designer a way of eliminating solutions which are too costly to be implemented. It should be noted that these upper bounds are external inputs to this algorithm and represent some industrial cost constraints. For example, maximum number of transistors that can fit on a single die of silicon using a particular fabrication technology or maximum power usage allowed for the system. With these two conditions, timing condition and upper bounds on costs, exhaustive exploration of the design space can be avoided. The first condition helps us eliminate solutions that are not powerful enough to match the performance requirements of the application where as the second conditions eliminates solutions that are too costly. Figure 5.4 shows flowchart representation of the same algorithm. As the algorithm explores the design space it finds pareto-optimal solutions and adds them to the pareto optimal front. Figure 5.5 outlines the pseudo-code for two functions, first, *isParetoOptimal()* which checks if a new solution is pareto-optimal and second, insertIntoParetoFront() which actually inserts the solution into the pareto-front. *insertIntoParetoFront()* has mainly two parts, first part simply adds the new solution to the existing set of pareto-optimal solution. The second and equally important part checks if there are any solutions in the set which are dominated by the newly added solution. If any such solution is found then it is removed from the set. This is necessary because a solution which is dominated by another solution can no longer be part of the pareto-optimal front.

#### 5.5 Choice of objective functions

Some researchers have formulated the mapping of tasks to processors as an ILP [7] using silicon chip area as the single objective function. This single objective approach may not be adequate since system design for MPSoCs often involves many design objectives. The objectives could be conflicting such that optimizing on one objective compromises the other design objectives. Keeping this in mind we decided to take the multi-objective approach in this thesis. Researchers [31] working in the direction of DSE of MPSoCs have used different objectives like network performance and cost savings. Many more objectives that are critical to the system design are throughput, power usage of the

| n                 | Number of candidate architectures                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Т                 | Number of tasks in the application                                                                                                                                                           |

| PartialSolution x | A data structure which stores the mapping of tasks to candidate architectures i.e. $1 \le x[i] \le n, \forall i \in [0,j]$ for some j <t <math="" and="">x[i] = 0 \forall i \in [j+1, T]</t> |

| Leaf Node         | Refers to a complete solution i.e. 1<=x[i]<=n, $\forall i \in [0,T]$                                                                                                                         |

Fig. 5.4: Depth First DSE program flow

```

struct ParetoSolution {

PartialSolution *x;

int cost_1;

int cost 2;

...

int cost_m;

struct ParetoSolution *next;

};

ParetoFront is the set of pareto optimal solutions;

int isParetoOptimal( <cost_1, cost_2, ... cost_m>) {

ParetoSolution ps;

If( ParetoFront is empty) // this means any solution is pareto optimal

return 1;

ps = first solution in ParetoFront;

while(there are more solutions in ParetoFront){

if( ps dominates <cost_1, cost_2, ... cost_m>) {

//Dominated by some solution already in the pareto-optimal front

// this means input vector can not be pareto-optimal

return 0;

}

ps = next solution in ParetoFront;

}

return 1;

}

void insertPareto(PartialSolution x, <cost_1, cost_2, ... cost_m>) {

ParetoSolution ps1, ps2;

ParetoSolution ps = new ParetoSolution(x, <cost 1, cost 2, ... cost m>);

Add ps to ParetoFront;

//New solution inserted to ParetoFront

// following code removes all solutions in the ParetoFront which are dominated

// by newly added solution

// this is necessary to maintain the pareto-optimality of each solution in ParetoFront

ps1 = first solution in ParetoFront;

while(there are more solutions in Pareto Front){

if(ps dominates ps1){

remove ps1 from ParetoFront;

ł

ps1 = next solution in ParetoFront;

}

}

```

system etc. In order to demonstrate our multi-objective approach we narrowed down to two objective functions: silicon chip-space requirements and the power usage of the system. It should be noted however that our technique in general can handle any number of objectives, subject to the availability of appropriate cost models for those objectives.

#### 5.5.1 Cost model for Chip-space requirements

For one of the objective functions, silicon chip area, we must estimate the chip-space requirements of MPSoC including the processing elements and the communication elements such as the buffers. We considered many ways to estimate the chip-space requirements for processing elements, including information from datasheets of real processors. However it was found that many manufacturers do not mention this information, probably because the chip area varies depending on the fabrication technology used. For example, chip area required for a processor on a 0.5 micron technology is different from area required for the same processor on 0.18 micron technology. We also considered some empirical cost models like SimpleFit [22], which are based on chip areas of some commercial processors. By fitting a quadratic function to the data for real processors, this model defines the silicon cost as a function of issue width. However sophisticated, this model is not of much use because of following reasons: first, its based only on one microarchitectural parameter i.e issue width, and second, the possible values of issue width are limited to 1, 2, or 4 even for latest superscalars.

It should be noted that building a cost model which takes into consideration all the microarchitectural parameters mentioned in Section 5.1 is not a simple task. Among all the components that account for chip area, some are SRAM based and have a well known implementation. For example, data and instruction caches, register sets, etc. It is easy to estimate the chip area for these components using analytical models. Since the chip area for 1 bit of SRAM is known, total area can be easily computed by multiplying it with the memory size of the component and adding some fixed cost for the structural implementation. However, some other components such as functional modules (adders and multipliers etc.) are much complex in implementation. Chip area for these components can only be computed using empirical methods, i.e. by using transistor counts for some well known implementations and extrapolating using word width as a parameter. Naturally these estimations are not as accurate as the analytical models. Another set of components, like buses and arbiters, it is even more difficult to estimate the chip area because it depends on the actual layout of the other components on the chip. The chip space requirements for these components can best be estimated as a percentage overhead after adding chip space for all other components.

Considering these difficulties a hardware complexity estimation model, SimScal [30] has been developed. SimScal is based on sim-outorder simulator of SimpleScalar. It takes as input SimpleScalar microarchitectural parameters like cache size, decode and issue width, number of integer and floating point ALUs, RUU and LSQ sizes, branch predictors and memory ports, and estimates the transistor count and the chip area required. To the best of our knowledge, this is the only chip space estimator which takes into account such a wide range of microarchitectural parameters and is proved to be fairly accurate.

We estimated the silicon chip-space for each of our candidate architectures using SimScal estimation model. Appendix B summarizes the microarchitectural parameters that define our candidate architectures and Table 5.2 shows the corresponding silicon cost measured in transistor counts.

#### 5.5.2 Chip-space estimation for on-chip buffers

On-chip buffer also contribute significantly to silicon chip-space requirements of an MPSoC. In the context of streaming applications these buffers are first-in-first-out buffers with one processor reading from it and another writing to it. Analytical model for estimating transistor counts of such FIFO buffers can be easily constructed using an approach similar to SimScal's analytical model for I-cache transistor count estimation. SimScal assumes four transistors per SRAM bit of memory (TransSRBit = 4), two transistors per write port (TransWP = 2) and one transistor per read port (TransRP = 1). Assuming one read and one write port per buffer bit, the transistor count per buffer bit can be calculated as: TransBuffBit = TransSRBit + TransWP + TransRP.

Buffer size calculated by Equation 4.5 is measured in terms of numbers of data items, for example macro-blocks in case of MPEG2 decoder. The size of MPEG2 pixel is  $16 \times 16$  pixels. Each macro-block occupies  $16 \times 16 \times ColorDepth$  bits of buffer space, where ColorDepth is the number of bits required to represent each pixel. Using this data, the total transistor count for on-chip buffers can be estimated as:  $TransBuff = TransBuffBit \times B \times 16 \times 16 \times ColorDepth$ , where B is the buffer size calculated by Equation 4.5. Here all the terms except B are constants. The proposed algorithm

| no.      | Trans.count        | no.      | Trans.count        | no.      | Trans.count        | no.        | Trans.count        |

|----------|--------------------|----------|--------------------|----------|--------------------|------------|--------------------|

| 1        | 2345125            | 33       | 2307957            | 65       | 2337741            | 97         | 2300677            |

| 2        | 2551155            | 34       | 2504115            | 66       | 2543203            | 98         | 2496275            |

| 3        | 2373685            | 35       | 2336517            | 67       | 2366301            | 99         | 2329237            |

| 4        | 2579715            | 36       | 2532675            | 68       | 2571763            | 100        | 2524835            |

| 5        | 2376485            | 37       | 2339317            | 69       | 2369101            | 100        | 2324033            |

| 6        | 2582515            | 38       | 2535475            | 70       | 2574563            | 101        | 2532037            |

| 7        | 2433605            | 39       | 2396437            | 70       | 2426221            | 102        | 2327055            |

| 8        | 2433605            | 40       | 2592595            | 71       | 2631683            | 103        | 2584755            |

| 9        | 2484363            | 40       | 2392393            | 72       | 2475843            | 104        | 2431083            |

| 10       | 2484303            | 41       | 2635705            | 73       | 2681433            | 105        | 2626745            |

| 10       | 2512923            | 42       | 2468043            | 74       | 2504403            | 100        | 2459643            |