## **CHARACTERIZATION AND MODELING OF MOSFETS**

## FOR RF APPLICATIONS

## MAHALINGAM UMASHANKAR

(B. E. (Hons.), Birla Institute of Technology and Science, Pilani)

## A THESIS SUBMITTED

# FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

## NATIONAL UNIVERSITY OF SINGAPORE

2005

## Acknowledgements

I am grateful to my supervisors Assoc. Prof. Ganesh Shankar Samudra, National University of Singapore and Dr. Subhash Chander Rustagi, Institute of Microelectronics, for providing me with the valuable opportunity of conducting research under their supervision. I sincerely thank them for their able guidance, support and help throughout the course.

I would like to thank Mr. Navab Singh, Institute of Microelectronics, for his help in process simulations and Mr. Arivazhagan Nagarajan, Institute of Microelectronics, for assisting me with workstation and software requirements. I would like to thank Ms. Tan Shane Yin Selina, Institute of Microelectronics, for helping me with the die bonding process. I would like to thank Mr. Teo Seow Miang and Ms. Zheng Huan Qun, Signal Processing and VLSI design laboratory, National University of Singapore, for helping me with workstation requirements to carry out simulations.

Special thanks to the National University of Singapore for supporting me with a graduate research scholarship and to the Institute of Microelectronics, Singapore, for granting me an attachment and providing me with the requisite lab facilities for conducting this research.

I thank my friends in the Signal Processing and VLSI design laboratory, National University of Singapore, whose association made for an enjoyable research experience. Finally, I thank my parents, for their constant encouragement, understanding and blessings towards my endeavor.

## **Table of Contents**

| Acknowledgements                                         | i    |

|----------------------------------------------------------|------|

| Table of Contents                                        | ii   |

| Summary                                                  | vi   |

| List of Figures                                          | viii |

| List of Abbreviations and Symbols                        | xii  |

| List of Abbreviations and Symbols                        | xii  |

| Chapter 1: Introduction                                  |      |

| 1.1 Motivation                                           | 2    |

| 1.2 Challenges in MOSFET modeling for RF IC design       | 2    |

| 1.3 The need for three-port characterization of a MOSFET | 4    |

| 1.4 Issues in RF characterization                        |      |

| 1.4.1 Multi-port vector network analyzers                | 6    |

| 1.4.2 Two-port vector network analyzers                  | 7    |

| 1.5 Scope of the work                                    |      |

| 1.6 An outline of this work                              | 9    |

| 1.7 List of publications                                 |      |

| Chapter 2: Overview of Past Work and Network Theory      |      |

| 2.1 Prior work in MOSFET characterization                |      |

| 2.2 MOS admittance network theory                        |      |

| 2.2.1 Redundancy of the main diagonal elements           |      |

| Chapter 3: Test Structures and Measurement               |      |

| 3.1 Measurement Setup                                    |      |

| 3.1.1 A note on IC-CAP                                     |    |

|------------------------------------------------------------|----|

| 3.1.2 Calibration of the Vector Network Analyzer           |    |

| 3.2 Device specifications                                  |    |

| 3.2.1 The SD-R test structure                              |    |

| 3.3 The GPG probe                                          |    |

| 3.4 Parasitic De-embedding of measured data                |    |

| 3.4.1 Eliminating the third port parasitic                 |    |

| 3.5 Effect of the GPG probe on device measurements         |    |

| 3.6 Summary                                                |    |

| Chapter 4: De-embedding of the GPG Probe Impedance         |    |

| 4.1 Equivalent circuit representation of the MOS device    |    |

| 4.1.1 Interpreting the equivalent circuit model parameters |    |

| 4.2 Equivalent circuit representation of the SD-R device   | 41 |

| 4.2.1 Parameter extraction of the SD-R device              | 44 |

| 4.3 MOS device model analysis and extraction               |    |

| 4.3.1 Analysis of the GD Configuration                     |    |

| 4.3.2 Parameter extraction for the GD configuration        |    |

| 4.3.3 Analysis of the GS Configuration                     | 49 |

| 4.3.4 Parameter extraction for the GS configuration        | 51 |

| 4.3.5 Analysis of the SD Configuration                     | 53 |

| 4.3.6 Parameter extraction for the SD configuration        | 55 |

| 4.4 Off-state analysis and parameter extraction            | 57 |

| 4.5 Probe de-embedding and generation of three-port data   | 61 |

| 4.5.1 Three port capacitance and conductance coefficients    |     |

|--------------------------------------------------------------|-----|

| 4.5.2 Terminal charge extraction                             |     |

| 4.6 Summary                                                  |     |

| Chapter 5: Device Simulation                                 |     |

| 5.1 Overview of TSUPREM-4 and Medici                         |     |

| 5.2 Simulation of a 0.35µm NMOS structure                    |     |

| 5.3 DC and RF Simulations of the MOSFET and SD-R structure   |     |

| 5.4 Extracted results from SD-R simulations and measurements |     |

| 5.5 Summary                                                  | 80  |

| 6.1 Consistency of the extraction scheme                     |     |

| 6.1.1 Comparison of extrinsic model parameters               | 86  |

| 6.2 Validation of the three-port characterization            |     |

| 6.3 Three-port terminal capacitance and conductance          |     |

| 6.3.1 Differences in measured terminal capacitances          |     |

| 6.3.2 NQS effect on device trans-conductance                 |     |

| 6.4 Terminal charges                                         |     |

| 6.4.1 Frequency dependence of terminal charges               |     |

| 6.5 Summary                                                  | 113 |

| Chapter 7: Conclusion and Future Work                        |     |

| 7.1 Conclusion                                               |     |

| 7.2 Future work                                              |     |

| References                                                   |     |

| Appendix A: TSUPREM-4 input files for 0.35µm process         |     |

| A.1 Generation of initial process mesh                                 | . 124 |

|------------------------------------------------------------------------|-------|

| A.2 Generation of final structure                                      | . 128 |

| Appendix B: Simulated Test structure of a 0.35µm MOSFET from TSUPREM-4 | . 139 |

| Appendix C: Medici input files for device simulations                  | . 140 |

| C.1 Initial mesh and zero carrier solution                             | . 140 |

| C.2 Two-carrier solutions to build up gate bias                        | . 141 |

| C.3 Building the drain bias and performing RF simulations              | . 144 |

### Summary

Concomitant with a lack of reliable pure-mode multi-port measurement techniques, the conventional characterization of MOSFETs has been carried out in two-port form by tying the bulk and source terminals together to ground. This is found to be an incomplete description of device behavior, as it fails to capture the effect of non-zero body bias and substrate signal coupling at RF, which affects the accuracy of RF device modeling. Moreover, an accurate description of the terminal charges is not possible from two-port characterization involving only the gate and drain terminals. A three-port characterization is thus required to fully describe the electrical behavior of a MOSFET.

This work describes the complete three-port characterization of a MOSFET valid up to 15GHz in all regions of operation, from two-port S-parameter measurements. The approach is to obtain accurate two-port Y-parameters in three different configurations (GD, GS and SD) and appropriately assemble them to generate three-port data. The work reports the characterization of the GPG probe used for bias feed at the un-calibrated third port and identifies the undesirable effect of the probe's 'lossy' and inductive behavior on two-port measurements of the MOSFET at RF. Such a behavior necessitates the deembedding of the GPG probe's parasitic impedance from the measured two-port Y-parameters of the device. To this effect, a generic RF small-signal equivalent circuit and model-based parameter extraction scheme is developed for the MOSFET. The scheme utilizes the measured probe impedance and three physical parameters extracted from a novel test structure named SD-R. The extracted equivalent circuit model parameters are used to generate the accurate two-port Y-parameters after removing the probe impedance. These two-port Y-parameters are then used to assemble the three-port data.

The same equivalent circuit model parameters obtained uniquely from different twoport configurations are found to match very well, thus establishing the consistency of the extraction scheme. An excellent match is observed in each of the redundant main diagonal elements of the three-port admittance matrix, obtained from two different twoport configurations. This confirms the effective de-embedding of the probe's impedance and establishes the accuracy of three-port characterization. The extracted junction admittances in the on-state, from the measured and simulated SD-R device data are shown here for the first time at different bias and frequency and their behavior is explained with the help of device physics. The general utility of this novel SD-R device towards RF MOSFET modeling and extraction is also discussed.

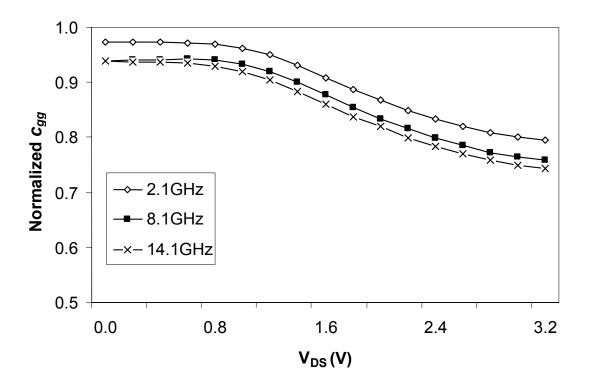

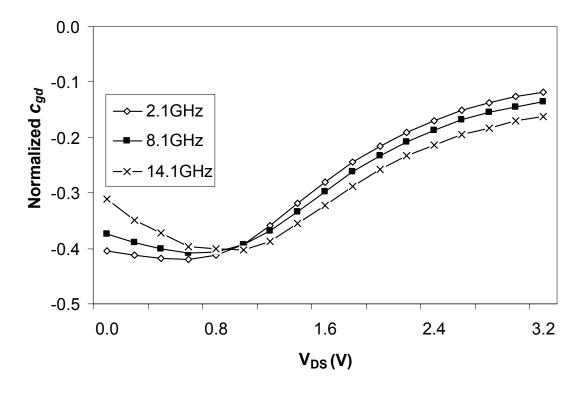

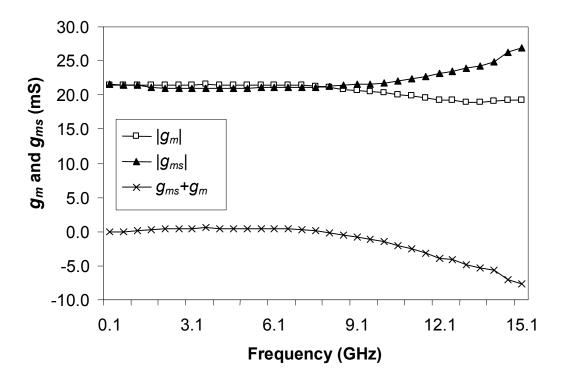

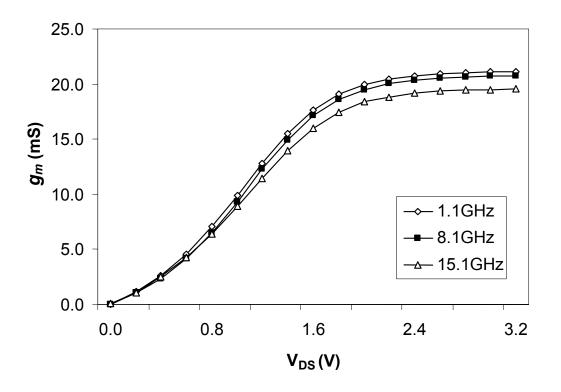

The measured three-port terminal capacitances of the MOSFET obtained as functions of bias and frequency are reported here for the first time along with 2-dimensional device simulation results to validate the characterization. The non-quasi-static effect is shown to manifest as the increasing difference between the magnitudes of trans-conductance obtained from the common-source configuration and of that obtained from the commondrain configuration.

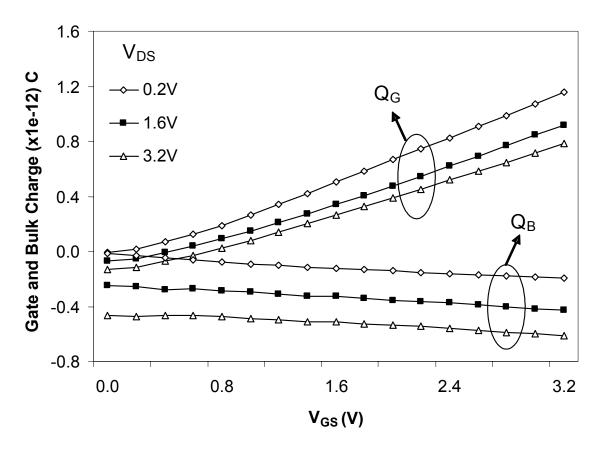

This work reports the bias and frequency dependence of all terminal charges of the MOSFET, extracted from its measured three-port capacitances, for the first time and discusses its implications towards RF MOSFET modeling and circuit simulation.

## List of Figures

| Figure 2. 1 On-wafer termination for two-port S-parameter measurements            | 13 |

|-----------------------------------------------------------------------------------|----|

| Figure 2. 2 GD configuration                                                      | 16 |

| Figure 2. 3 GS configuration                                                      | 17 |

| Figure 2. 4 SD configuration                                                      | 17 |

| Figure 2. 5 Redundancy of main diagonal elements                                  | 18 |

| Figure 3. 1 Multi-finger architecture of the measured MOSFET                      | 23 |

| Figure 3. 2 SD-R test structure (in SD configuration)                             | 24 |

| Figure 3. 3 GPG probe characterization                                            | 25 |

| Figure 3. 4 $s_{11}$ of the GPG probe ( $s_{GPG.11}$ )                            | 26 |

| Figure 3. 5 The MOSFET test structure                                             | 27 |

| Figure 3. 6 Two-port parasitic representation for the MOSFET in GD configuration  | 27 |

| Figure 3. 7 Two-port equivalent parasitic representation of the pads              | 28 |

| Figure 3. 8 Lead interconnect dummy and its equivalent parasitic representation   | 29 |

| Figure 3. 9 Third port parasitic (GD configuration)                               | 31 |

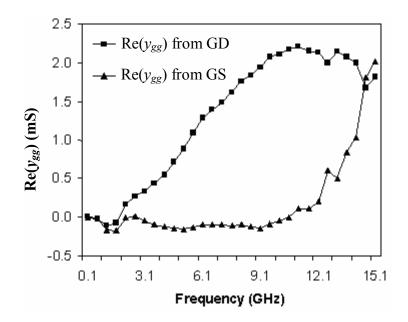

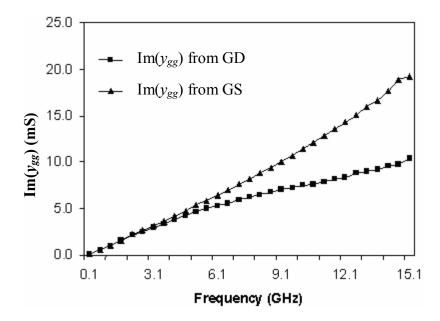

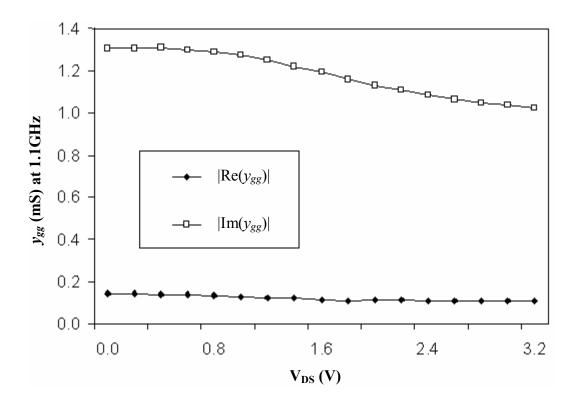

| Figure 3. 10 Effect of GPG probe on real part of $y_{gg}$                         | 34 |

| Figure 3. 11 Effect of GPG probe on imaginary part of $y_{gg}$                    | 34 |

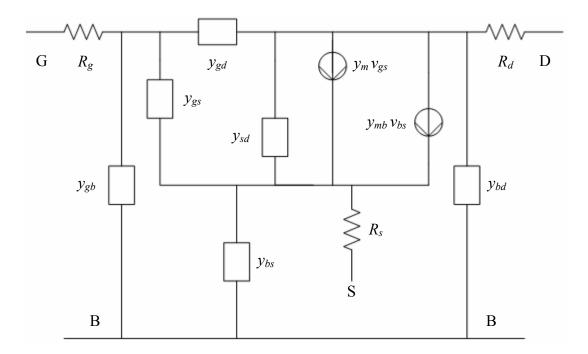

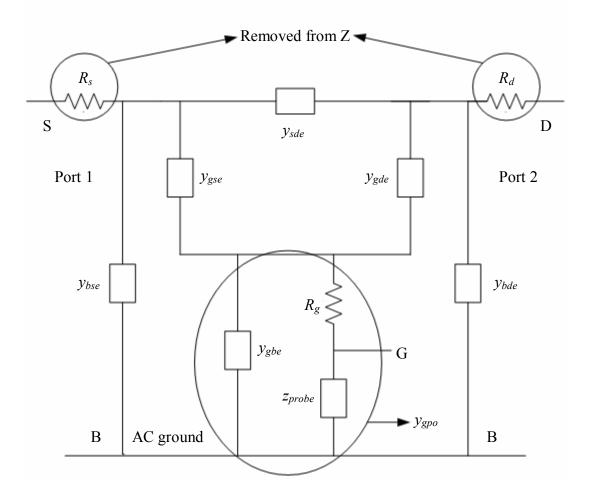

| Figure 4. 1 RF Equivalent circuit model for the MOS device                        | 38 |

| Figure 4. 2(a) RF Equivalent circuit of the SD-R device (SD configuration)        | 42 |

| Figure 4. 2(b) Practical Equivalent circuit of the SD-R device (SD configuration) | 43 |

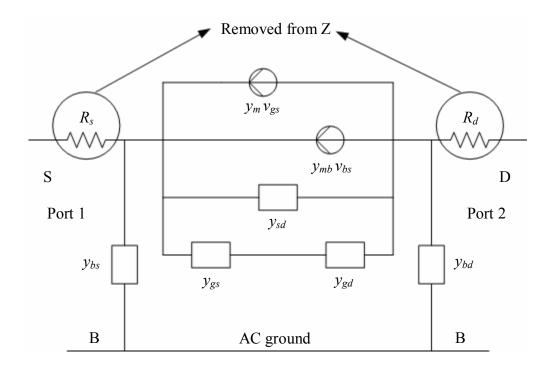

| Figure 4. 3 RF Equivalent circuit of the MOSFET in GD configuration               | 47 |

| Figure 4. 4 RF Equivalent circuit of the MOSFET in GS configuration               | 50 |

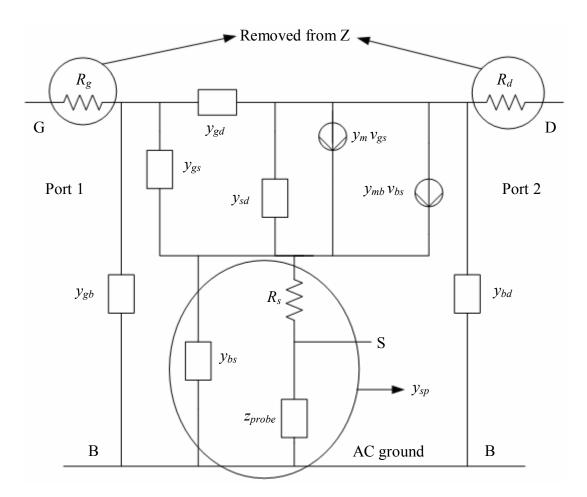

| Figure 4. 5 RF Equivalent circuit of the MOSFET in SD configuration               | 54 |

| Figure 4. 6 RF Equivalent circuit of the MOSFET in off-state (GD configuration) 57                                             |

|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 4. 7 RF Equivalent circuit of the MOSFET in off-state (GS configuration) 59                                             |

| Figure 4. 8 RF Equivalent circuit of the MOSFET in off-state (SD configuration) 60                                             |

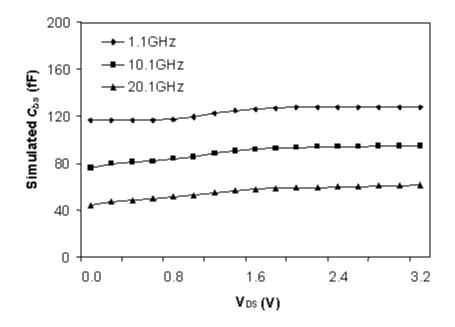

| Figure 5. 1(a) Simulated bulk-source capacitance ( $V_{GS}=3V$ and $V_{BS}=0V$ )                                               |

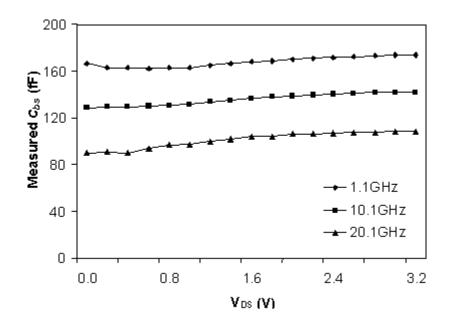

| Figure 5. 1(b) Measured bulk-source capacitance ( $V_{GS}=3V$ and $V_{BS}=0V$ )                                                |

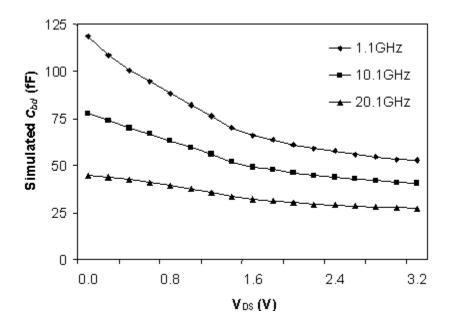

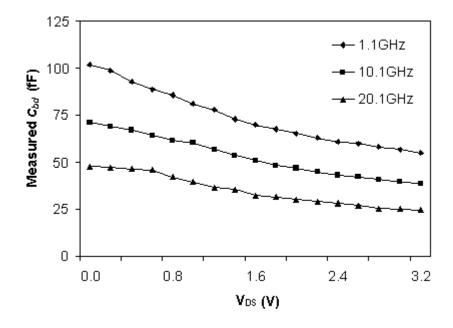

| Figure 5. 2(a) Simulated bulk-drain capacitance ( $V_{GS}$ =3V and $V_{BS}$ =0V)74                                             |

| Figure 5. 2(b) Measured bulk-drain capacitance ( $V_{GS}$ =3V and $V_{BS}$ =0V)74                                              |

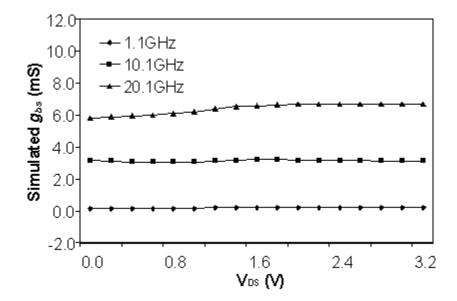

| Figure 5. 3(a) Simulated bulk-source conductance ( $V_{GS}$ =3V and $V_{BS}$ =0V)                                              |

| Figure 5. 3(b) Measured bulk-source conductance ( $V_{GS}$ =3V and $V_{BS}$ =0V)76                                             |

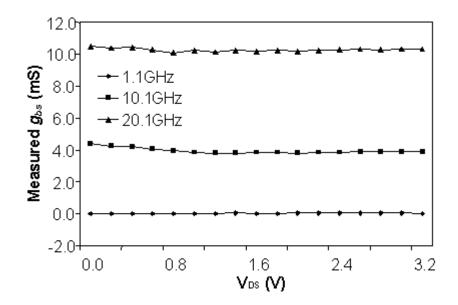

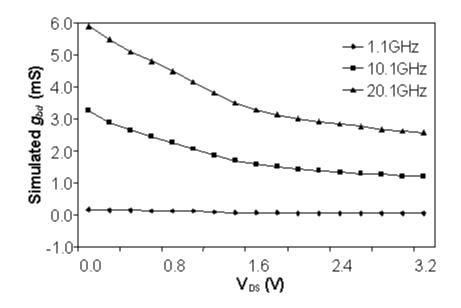

| Figure 5. 4(a) Simulated bulk-drain conductance ( $V_{GS}$ =3V and $V_{BS}$ =0V)76                                             |

| Figure 5. 4(b) Measured bulk-drain conductance ( $V_{GS}=3V$ and $V_{BS}=0V$ )                                                 |

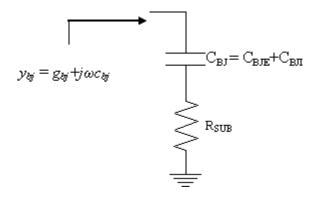

| Figure 5. 5 Simple equivalent circuit for the junction admittance                                                              |

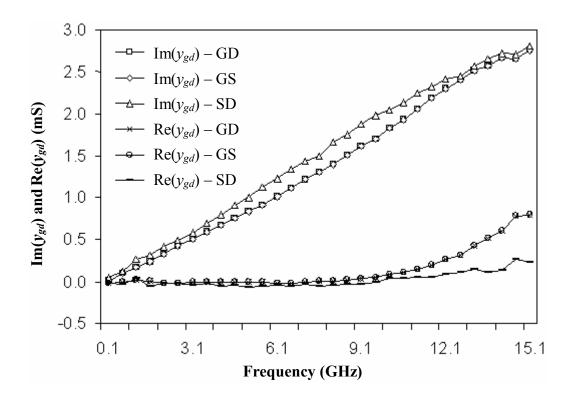

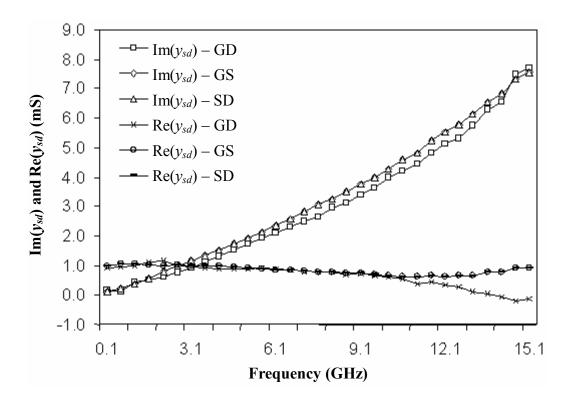

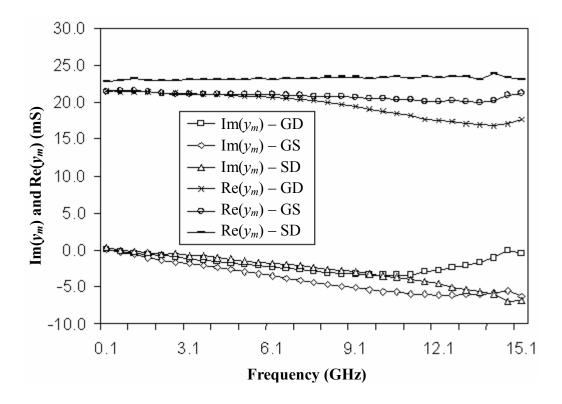

| Figure 6. 1 Model-based $y_{gd}$ (V <sub>GS</sub> =3V, V <sub>DS</sub> =3.2V and V <sub>BS</sub> =0V)                          |

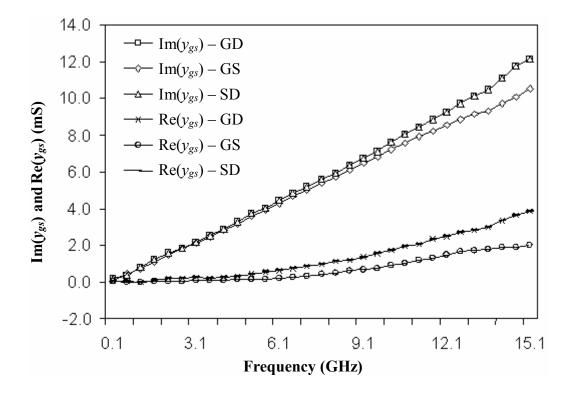

| Figure 6. 2 Model-based $y_{gs}$ (V <sub>GS</sub> =3V, V <sub>DS</sub> =3.2V and V <sub>BS</sub> =0V)                          |

| Figure 6. 3 Model-based $y_{sd}$ (V <sub>GS</sub> =3V, V <sub>DS</sub> =3.2V and V <sub>BS</sub> =0V)                          |

| Figure 6. 4 Model-based $y_m$ (V <sub>GS</sub> =3V, V <sub>DS</sub> =3.2V and V <sub>BS</sub> =0V)                             |

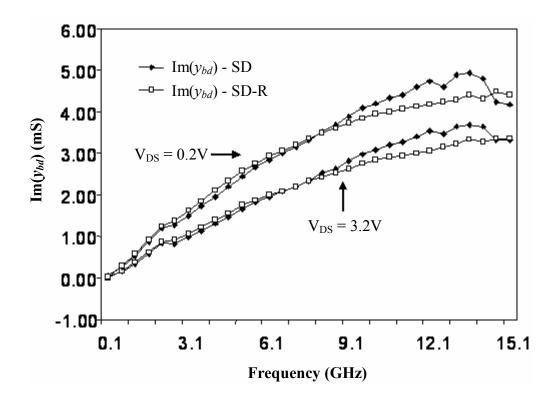

| Figure 6. 5 Plot of $y_{bd}$ from SD and SD-R in off-state (V <sub>GS</sub> =0V and V <sub>BS</sub> =0V)                       |

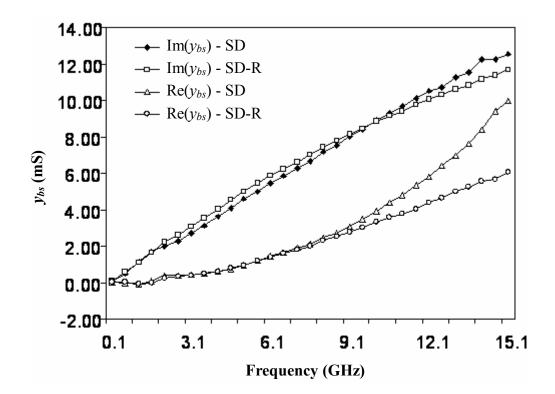

| Figure 6. 6 Plot of $y_{bs}$ from SD and SD-R in off-state (V <sub>GS</sub> =V <sub>BS</sub> =0V and V <sub>DS</sub> =3.2V) 87 |

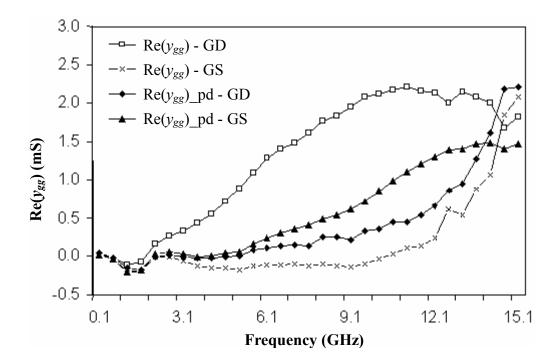

| Figure 6. 7 Real part of $y_{gg}$ from GD and GS ("_pd" indicates probe de-embedded data)88                                    |

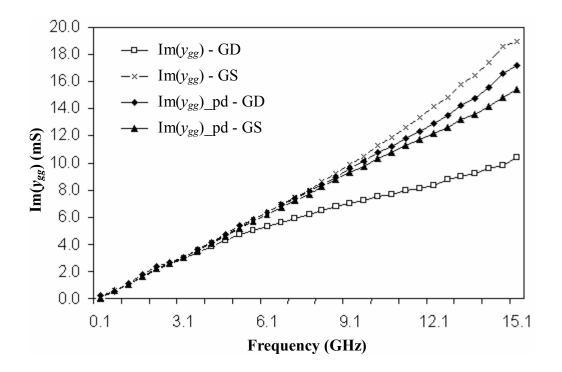

| Figure 6. 8 Imaginary part of $y_{gg}$ from GD and GS ("_pd" - probe de-embedded data) 89                                      |

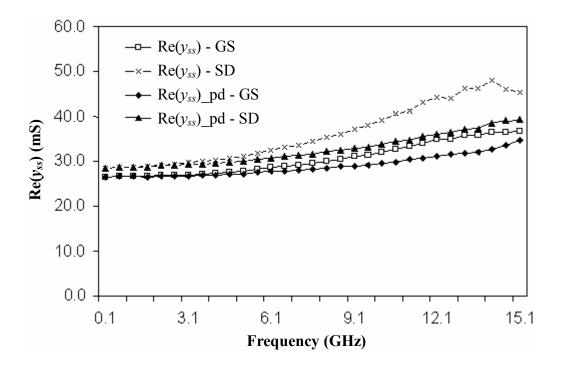

| Figure 6. 9 Real part of $y_{ss}$ from GS and SD ("_pd" - probe de-embedded data)                                              |

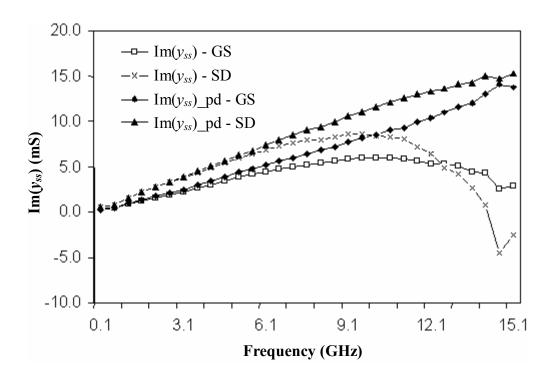

| Figure 6. 10 Imaginary part of $y_{ss}$ from GS and SD ("_pd" - probe de-embedded data) 91                                     |

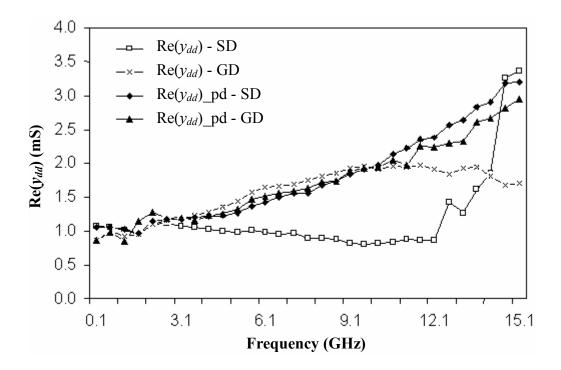

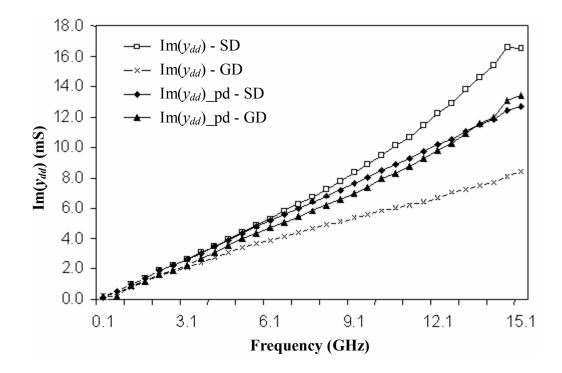

| Figure 6. 11 Real part of $y_{dd}$ from SD and GD ("_pd" - probe de-embedded data)                                             |

| Figure 6. 12 Imaginary part of $y_{dd}$ from SD and GD ("_pd" - probe de-embedded data) 92                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6. 13 Normalized $c_{gg}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

| Figure 6. 14 Normalized $c_{gd}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

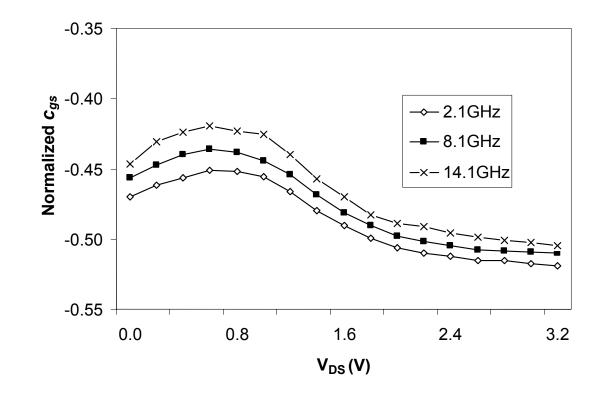

| Figure 6. 15 Normalized $c_{gs}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

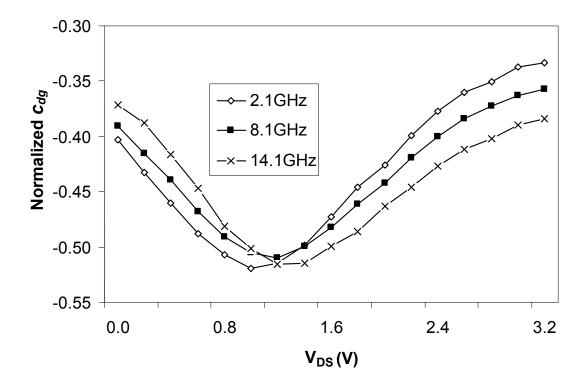

| Figure 6. 16 Normalized $c_{dg}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

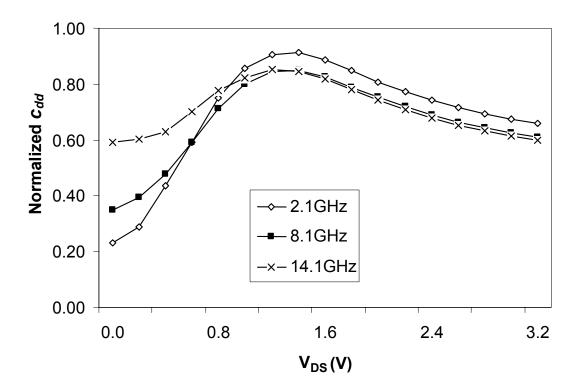

| Figure 6. 17 Normalized $c_{dd}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

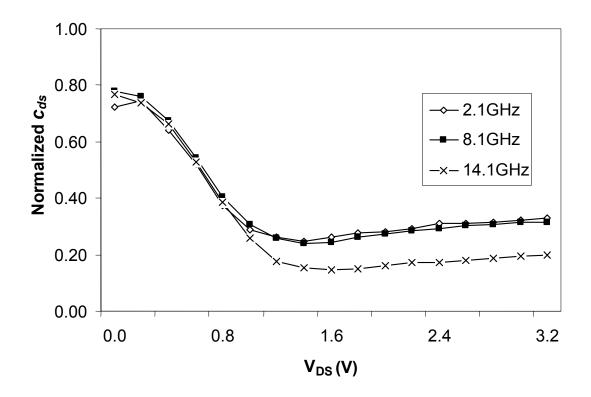

| Figure 6. 18 Normalized $c_{ds}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

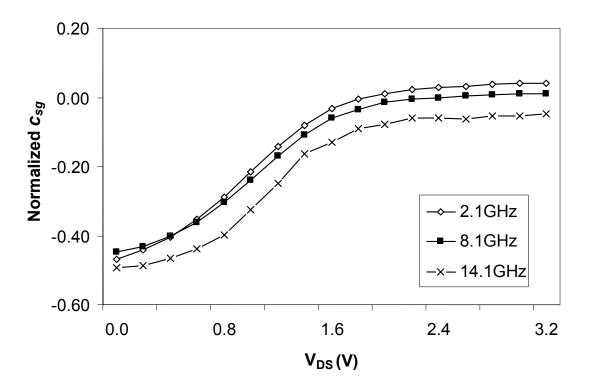

| Figure 6. 19 Normalized $c_{sg}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

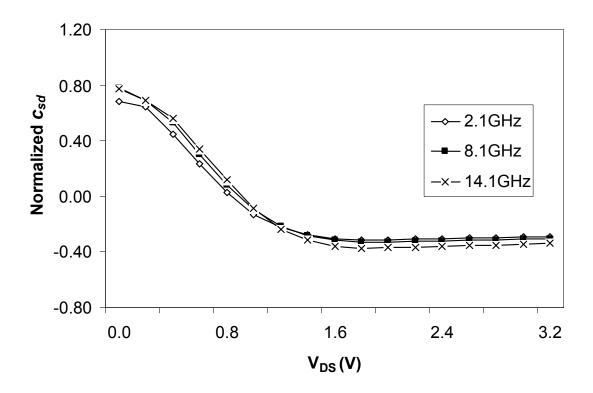

| Figure 6. 20 Normalized $c_{sd}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

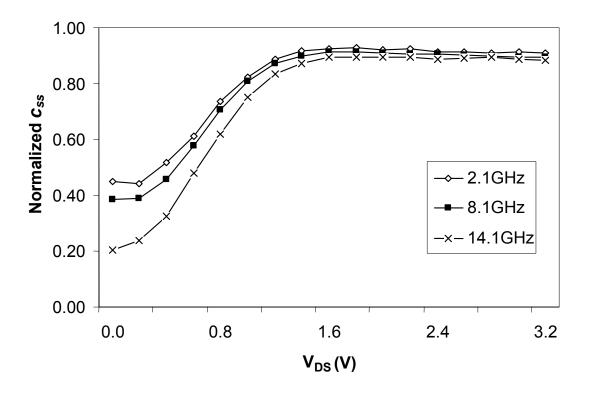

| Figure 6. 21 Normalized $c_{ss}$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                        |

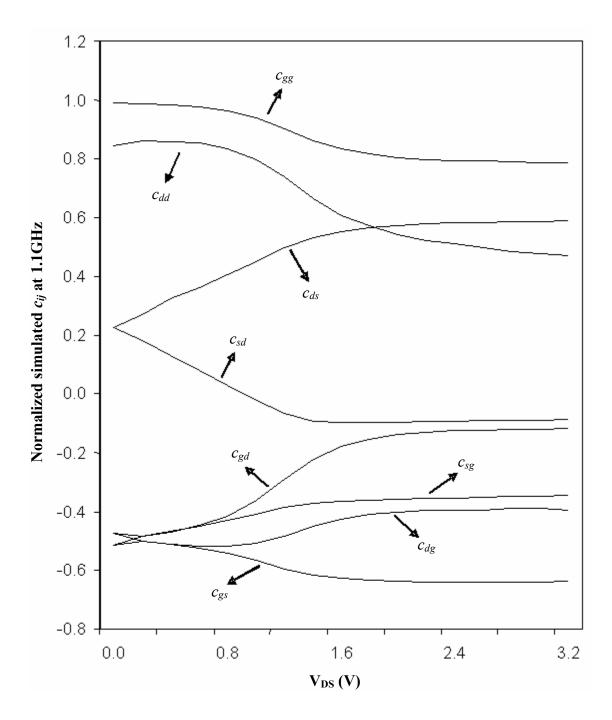

| Figure 6. 22 Normalized $c_{ij}$ of a 0.35µm MOSFET from Medici simulations (V <sub>GS</sub> =3V,                                                                                                                                                                                                                                                                                                  |

| V <sub>SB</sub> =0V)                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                    |

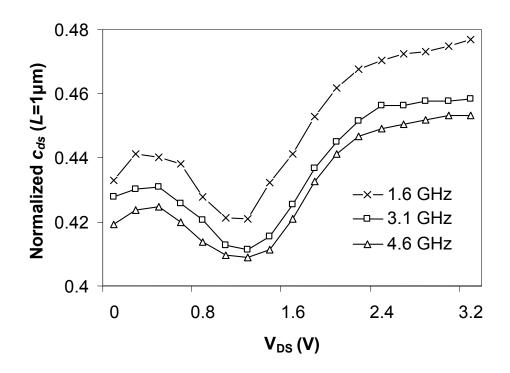

| Figure 6. 23 Normalized $c_{ds}$ measured from 1µm device (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)100                                                                                                                                                                                                                                                                                            |

| Figure 6. 23 Normalized $c_{ds}$ measured from 1µm device (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V) 100<br>Figure 6. 24 Magnitude of measured Re( $y_{dg}$ ) and Im( $y_{dg}$ ) (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V)                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                    |

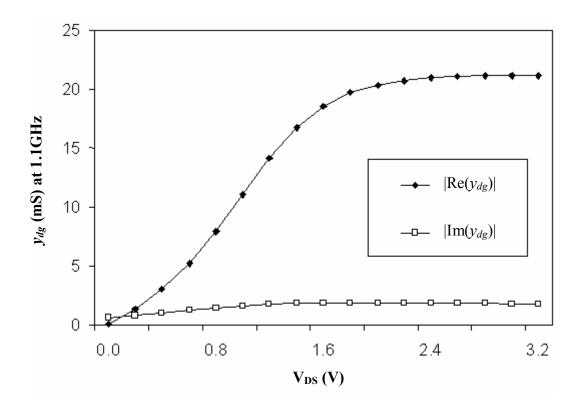

| Figure 6. 24 Magnitude of measured $\text{Re}(y_{dg})$ and $\text{Im}(y_{dg})$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V) 102                                                                                                                                                                                                                                                                      |

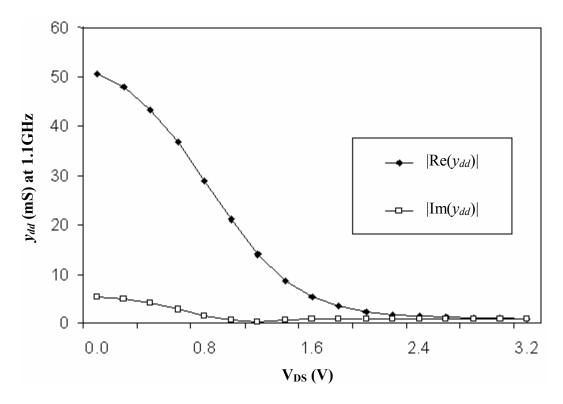

| Figure 6. 24 Magnitude of measured $\text{Re}(y_{dg})$ and $\text{Im}(y_{dg})$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V) 102<br>Figure 6. 25 Magnitude of measured $\text{Re}(y_{dd})$ and $\text{Im}(y_{dd})$ (V <sub>GS</sub> =3V, V <sub>SB</sub> =0V) 102                                                                                                                                     |

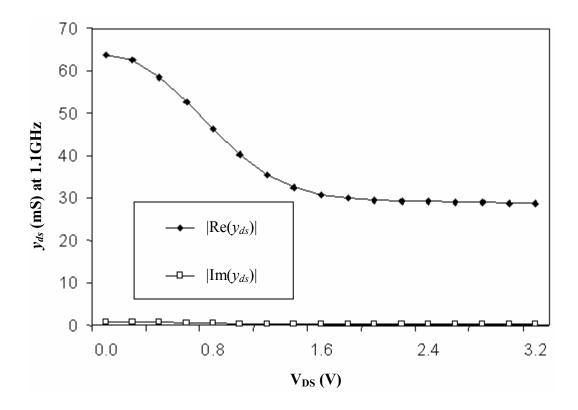

| Figure 6. 24 Magnitude of measured $\text{Re}(y_{dg})$ and $\text{Im}(y_{dg})$ ( $V_{\text{GS}}=3V$ , $V_{\text{SB}}=0V$ ) 102<br>Figure 6. 25 Magnitude of measured $\text{Re}(y_{dd})$ and $\text{Im}(y_{dd})$ ( $V_{\text{GS}}=3V$ , $V_{\text{SB}}=0V$ ) 102<br>Figure 6. 26 Magnitude of measured $\text{Re}(y_{ds})$ and $\text{Im}(y_{ds})$ ( $V_{\text{GS}}=3V$ , $V_{\text{SB}}=0V$ ) 103 |

| Figure 6. 24 Magnitude of measured $\text{Re}(y_{dg})$ and $\text{Im}(y_{dg})$ ( $V_{GS}=3V$ , $V_{SB}=0V$ )                                                                                                                                                                                                                                                                                       |

| Figure 6. 24 Magnitude of measured $\text{Re}(y_{dg})$ and $\text{Im}(y_{dg})$ ( $V_{GS}=3V$ , $V_{SB}=0V$ )                                                                                                                                                                                                                                                                                       |

| Figure 6. 24 Magnitude of measured $\text{Re}(y_{dg})$ and $\text{Im}(y_{dg})$ ( $V_{GS}=3V$ , $V_{SB}=0V$ )                                                                                                                                                                                                                                                                                       |

| Figure 6. 24 Magnitude of measured $\operatorname{Re}(y_{dg})$ and $\operatorname{Im}(y_{dg})$ ( $V_{GS}=3V$ , $V_{SB}=0V$ )                                                                                                                                                                                                                                                                       |

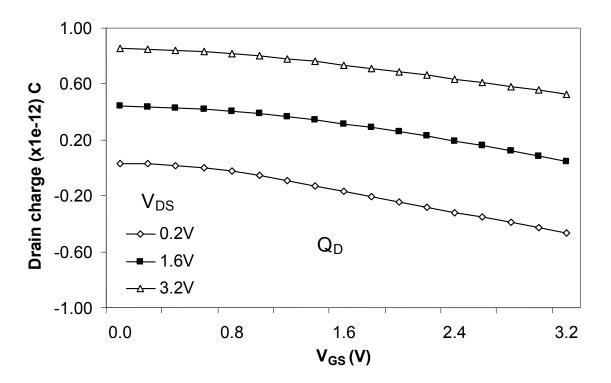

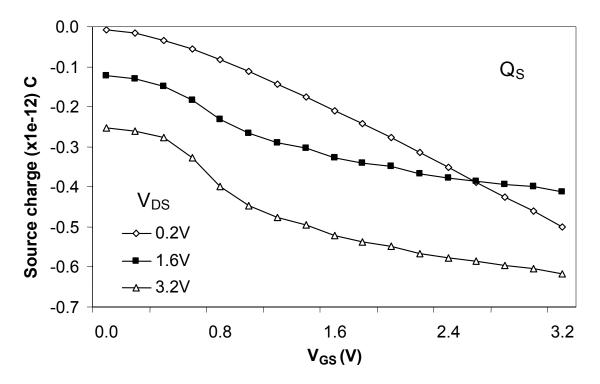

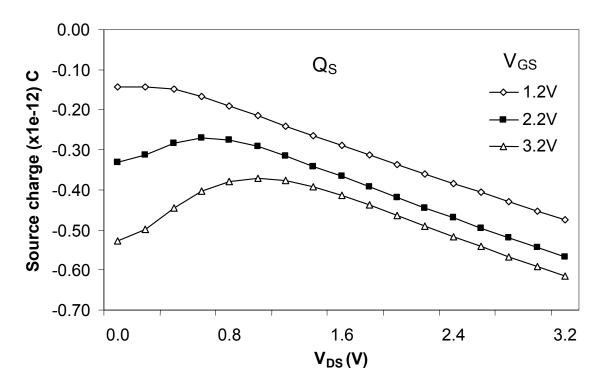

| Figure 6. 33 Source terminal charge ( $V_{SB}=0V$ ) at 2.1GHz                                   | 110 |

|-------------------------------------------------------------------------------------------------|-----|

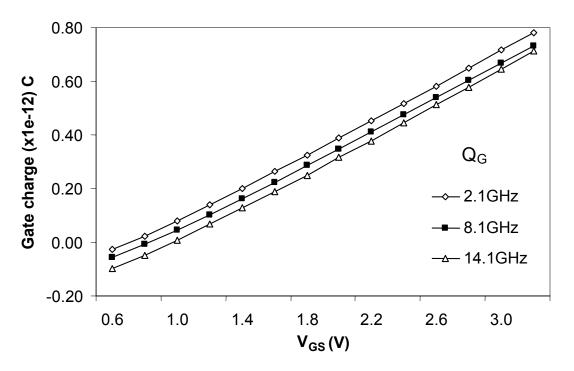

| Figure 6. 34 Frequency dependence of Gate charge ( $V_{DS}$ =3.2V, $V_{SB}$ =0V)                | 111 |

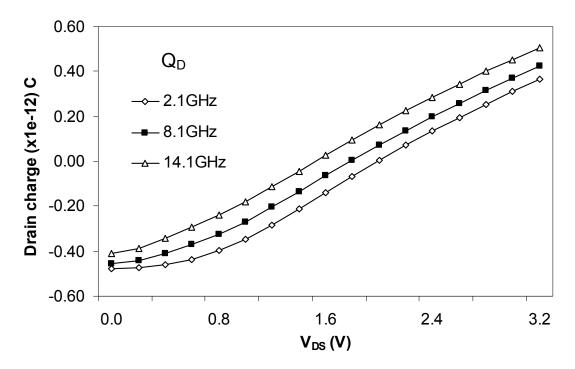

| Figure 6. 35 Frequency dependence of drain charge ( $V_{GS}$ =3.2V, $V_{SB}$ =0V)               | 112 |

| Figure 6. 36 Frequency dependence of source charge (V <sub>GS</sub> =3.2V, V <sub>SB</sub> =0V) | 112 |

## List of Abbreviations and Symbols

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

|--------|---------------------------------------------------|

| MOS    | Metal Oxide Semiconductor                         |

| CMOS   | Complementary MOS                                 |

| RF     | Radio Frequency                                   |

| IC     | Integrated Circuits                               |

| DC     | Direct Current                                    |

| AC     | Alternating Current                               |

| BSIM   | Berkeley Short-channel IGFET Model                |

| EKV    | Enz-Krummenacher-Vittoz MOS model                 |

| NQS    | Non-Quasi-Static effect                           |

| VNA    | Vector Network Analyzer                           |

| DUT    | Device Under Test                                 |

| EMI    | Electro-Magnetic Interference                     |

| GSG    | Ground-Signal-Ground                              |

| GSGSG  | Ground-Signal-Ground-Signal-Ground                |

| GPG    | Ground-Power-Ground                               |

| ISS    | Impedance Standard Substrate                      |

| LRRM   | Load-Reflect-Reflect-Match                        |

| LRM    | Load-Reflect-Match                                |

| TRL    | Thru-Reflect-Line                                 |

| SOLT   | Short-Open-Load-Thru                              |

| TCAD   | Technology Computer-Aided Design                  |

| GPIB                    | General Purpose Interface Bus                                 |

|-------------------------|---------------------------------------------------------------|

| IC-CAP                  | Integrated Circuit - Characterization and Analysis Program    |

| PEL                     | Parameter Extraction Language                                 |

| LDD                     | Lightly Doped Diffusion                                       |

| RTA                     | Rapid Thermal Anneal                                          |

| S-parameters            | Scattering parameters                                         |

| Y-parameters            | Admittance parameters                                         |

| GD                      | Gate-Drain (common source) configuration                      |

| GS                      | Gate-Source (common drain) configuration                      |

| SD                      | Source-Drain (common gate) configuration                      |

| SD-R                    | New test structure with large resistance on the gate          |

| S                       | Sub-threshold slope of the MOSFET in mV/decade                |

| V <sub>th</sub>         | Threshold voltage of the MOSFET in V                          |

| L                       | Channel Length of the MOSFET in $\mu m$                       |

| W                       | Width of the MOSFET in $\mu m$                                |

| <i>t</i> <sub>ox</sub>  | Gate oxide thickness of the MOSFET in nm                      |

| <i>Y</i> ij             | Admittance parameter at port ' $i$ ' due to port ' $j$ '      |

| C <sub>ij</sub>         | Capacitance at port 'i' due to port 'j'                       |

| $\operatorname{Re}(y)$  | <u>Real part of a complex number <math>y</math></u>           |

| $\operatorname{Im}(y)$  | Imaginary part of a complex number y                          |

| $f_t$                   | Cut-off frequency of the MOSFET at a given bias               |

| R <sub>gsh</sub>        | Sheet resistance of the gate poly silicon in $\Omega$ /square |

| <i>R</i> <sub>dsw</sub> | Drain-to-source resistance in $\Omega$ - $\mu$ m              |

## **Chapter 1: Introduction**

The advancement in CMOS technology has resulted in rapid downscaling in the size of the MOS transistor. The minimum possible MOS channel length (feature size) for a given technology, also referred to as the technology node, has reached well into the deep sub-micron/nano-meter range. Commercially, the 90nm technology node is already in production and the industry is expected to move on to the 65nm node very soon. In consonance with this trend, the cut-off frequency  $(f_t)$  of operation of the MOSFETs has also increased tremendously. This is attributed to the reduced transit time of injected electrons from the source to reach the drain due to reduced channel length, which also gives rise to very high drain fields leading to velocity saturation of carriers. Apart from favoring high-speed digital design applications, this has served as a boon for the RF IC design community, for it has enhanced the prospects of RF design using bulk-CMOS technology [1, 2]. Complete RF circuits and systems implemented with CMOS technology, operating at frequencies up to several Giga Hertz have already been reported [3]. Bulk Silicon CMOS technology is even viewed as a strong contender for emerging wireless millimeter wave applications [4-5].

The requirements of RF design have laid more stress on compact and accurate modeling of circuit elements to increase the capabilities of current RF circuit simulators. The challenges in MOSFET modeling are greatly enhanced with advancing technology as one needs to consider more complex physical issues (quantum effects, poly depletion, stress induced leakage etc) for smaller transistors. Further, the high frequency behavior of a device is significantly affected by all these physical effects and related parasitic. In

order to understand and accurately model the RF behavior of the MOSFET, a comprehensive electrical characterization of the device is indispensable.

#### 1.1 Motivation

The motive behind this work is to find a reliable and cost-effective way to achieve the complete characterization of the MOSFET in the three-port form, extract its terminal charges as a function both bias and frequency and thus facilitate its large-signal modeling for RF applications. The lack of reliable multi-port characterization tools for active devices further fueled the need to provide a solution using conventional two-port measurement techniques. This in turn required the development of a generic small-signal RF MOSFET model and suitable techniques for its parameter extraction. In the following sub-sections, the inadequacies and problems faced in current RF modeling as well as measurement and characterization of the MOSFET are discussed. The next section elucidates some of the problems in today's high frequency MOS models.

### 1.2 Challenges in MOSFET modeling for RF IC design

The success of RF design depends heavily on the accuracy of circuit simulation tools. This requires efficient and compact models for the active and passive circuit elements. As the MOS transistor is the most important circuit element, a lot of effort has been undertaken to accurately model its DC and AC behavior. The BSIM, EKV and Philips compact models for the MOSFETs are widely used in the industry. Of these, the BSIM model is being regarded as the industry standard. Though these models are very good for predicting DC and lower frequency AC behavior, there are issues in the RF regime of device operation. Especially when one approaches the device cut-off frequency, the nonquasi-static (NQS) effect becomes significant and the models are not accurate, as they fail to take into account the frequency dependence of the channel charge [6]. The computed terminal charges are thus in error at high frequencies.

The NQS effect has been attributed to the inability of the channel carriers to immediately respond to the applied terminal signal on account of their inertia. This results in temporary storage of transient charge in the channel. The NQS effect is more pronounced in longer channel transistors. They can be analyzed by dividing the channel into multiple small quasi-static sub-sections. As the device channel length comes down, the NQS effect is visible only at higher frequencies. The onset frequency of the non-quasi-static effect is given by [6, 7],

$$2\pi f_{NQS} = n2\pi f_t = n \frac{\mu_{eff} \left( V_G - V_T \right)}{L_{eff}^2}.$$

(1.1)

In (1.1),  $f_{NQS}$  is the onset frequency of the NQS effect,  $f_t$  is the device cut-off frequency and n is a small fraction chosen to be much less than unity for good simulation accuracy. Current industry models are all Quasi-static implementations and they are valid only up to a third of  $f_t$ . The BSIM4 model [8] provides a charge-deficit NQS model for AC and transient simulations using an Elmore equivalent circuit to model channel charge buildup. The relaxation time depends on the intrinsic input resistance of the channel [9-12]. But this results in complex expressions for trans-conductance and trans-capacitances that are not physically correct. This may affect model scalability.

Further, in smaller devices, device parasitic like junction, overlap and fringing capacitances and conductance – all of which show frequency dependence - become increasingly important. The substrate itself introduces some frequency dependence

through signal coupling as will be discussed in the next section. This implies that the terminal capacitances and conductance and thus the charges themselves are bound to be frequency dependent.

A major issue in today's bulk MOS models is in the treatment of the substrate. The substrate in bulk MOS devices plays a significant role in determining the RF performance of a device. Some of the models like BSIM4 take a sub-circuit approach to include effects of the substrate network [8]. Various techniques for substrate network modeling have also been reported in the literature [13-15]. But, this sub-circuit approach makes the resulting RF model non-scalable in nature. A scalable substrate model has been reported in [16] but is valid only up to 10GHz.

To overcome these limitations, a more holistic description of the device is required, which gives an insight into the actual behavior of the substrate and also the bias and frequency dependence of all its terminal capacitances, conductance and charges. The next section presents the conventional incomplete MOS description in its two-port form and brings out the need for a three-port characterization.

#### 1.3 The need for three-port characterization of a MOSFET

The MOS transistor is essentially a four-terminal device. However MOSFET modeling in the RF regime has been guided by the data collected by treating it as a three-terminal device. This means only a two-port characterization and analysis of the device is attempted [11-25], where the source is shorted to the substrate (bulk) to serve as the common terminal. Such an approach gives an incomplete description of the device. The effect of the substrate terminal on the device operation is unaccounted. This is because

charges induced in the substrate terminal are in turn coupled to other terminals and the signal coupling gets more significant at high frequencies.

In a conventional two-port characterization the small-signal current at the source and substrate terminals cannot be isolated from each other because the two terminals are tied together during measurement. Two-port characterization makes it impossible to predict the individual source and substrate terminal small-signal currents. But in reality, the source and substrate currents are distinctly different. And in many practical cases, the Source and Bulk terminals of the MOSFET are not tied together and both AC and DC potentials do exist between them. This means that signals and charges induced on the two terminals are different, e.g. - in a cascode amplifier stage, the Source and Bulk terminals of the MOSFET in common-source configuration are at different potentials. Only a three-port characterization yields each terminal small-signal current of the device distinctly, thus enabling accurate modeling and circuit simulation.

Thus, a complete three-port characterization of the MOSFET is essential for modeling the substrate effects at RF. The next section explores the various means to achieve RF characterization in general. It brings out the relative merits of two-port measurements as against multi-port measurements at RF.

#### 1.4 Issues in RF characterization

Device characterization using direct admittance (Y) or impedance (Z) measurements requires ideal short and open conditions. Such conditions are difficult to achieve at higher frequencies and, open and short ports affect device stability at high frequencies. Sparameter measurements, carried when the ports are terminated in the characteristic impedances are most accurate and reliable at RF and microwave frequencies. Once the S- parameter data is available, it can be converted to Y, Z or H parameters using simple matrix manipulation, for ease of analysis and parameter extraction.

#### 1.4.1 Multi-port vector network analyzers

The RF characterization of MOS devices is best done using a Vector Network Analyzer (VNA) as it employs direct S-parameter measurements. The aim of this work is to achieve a three-port characterization of the MOSFET. It may seem that a multi-port VNA can offer a solution to this requirement. However, a Pure-mode Multi-port VNA still remains a research concept and is yet to be made commercially available. This is because of the challenge involved in maintaining the signals perfectly aligned to the reference planes (probe tips).

Mixed-mode multi-port VNA are commercially available today. But they have some serious disadvantages [26]. In such an instrument, a four-port network is treated as a two-port network with two modes per port, namely, differential and common modes [27, 28]. Sub-matrices have to be generated for each combination of these modes with stimulus and response signals. The differential sub-matrix is itself evaluated mathematically from single-ended measurements (A single port is excited at a time.), subject to superposition principle. Thus, it requires that the DUT must be linear for accurate computation of the mixed-mode terms.

In case of a purely differential measurement, it is very difficult to get exactly matched (common-mode) or opposite phase (differential) signals. One requires additional equipments like 'baluns' to achieve the phase requirements. Even these, are not very accurate and can introduce phase changes. A slight phase mismatch results in mode conversions and Electro-Magnetic Interference (EMI) related problems. The choice of probes is very important to prevent signal coupling or cross-talks. To ensure proper isolation of RF signals, the multi-port measurement requires very complex probes like GSSG (Ground-Signal-Signal-Ground) and GSGSG (Ground-Signal-Ground-Signal-Ground), which are much more expensive when compared to normal GSG (Ground-Signal-Ground) probes required for two-port measurements.

The calibration of a four-port Network Analyzer is a very tedious process. It has to be done using multiple two-port calibrations. Some methods require short, open and load measurements at each port and all combinations of ideal thru connect [26, 27]. Thus, the required Impedance Standard Substrate (ISS) is quite complex and expensive. The calibration procedure itself is not yet standardized for on-wafer measurements. The reliability of the multi-port calibration is still a subject of investigation. There are no standardized four-port calibration tool-kits available as yet in the market. Further, techniques for multi-port de-embedding of on-wafer parasitic are still being developed and remain a research topic in itself. As the de-embedding techniques are not yet standardized, designing a suitable set of dummy test structures to characterize the parasitic also needs to be investigated. Without complete de-embedding of on-wafer parasitic, the multi-port characterization data is not expected to be meaningful.

#### 1.4.2 Two-port vector network analyzers

The two-port VNA is much simpler and efficient to use than its multi-port counterpart. It is also the least expensive of them all. The two-port calibration techniques are quite well established and standardized – TRL (Thru-Reflect-Line), LRM (Load-Reflect-Match), SOLT (Short-Open-Load-Thru) and LRRM (Load-Reflect-Reflect-Match), to name a few. There are several software tools like WinCal and Nucleus dedicated to twoport calibration. Signal isolation is not a problem, and the probes (GSG) required are also simpler and cheaper. Considering all the problems in a Multi-port VNA, it can be concluded that two-port VNA measurements are much easier to perform and are more reliable when compared with multi-port measurements. Therefore, carrying out two-port measurements in different permutations and appropriately relating them to the three-port parameters is an excellent option to explore for multi-port characterization.

#### 1.5 Scope of the work

This work evolves a method to obtain the complete three-port characterization of the MOS transistor valid in all regions of operation, up to about 15GHz, with the help of simple two-port RF measurements to overcome issues mentioned in Section 1.4. The method and the techniques presented here are quite generic and can be useful even for millimeter wave applications provided a valid equivalent circuit representation is available. The new test structure (SD-R) developed for this work directly yields the MOSFET junction admittances at all biases and frequencies, which can be used for RF modeling of junction and substrate behavior. The measured three-port terminal capacitances as functions of bias and frequency are presented here for the first time. The terminal charge extraction method presented here is quite efficient and general. All four MOSFET terminal charges obtained as functions of bias and frequency from measured three-port data are reported here for the first time. They are extremely useful for largesignal device modeling and circuit simulations. The many modeling problems presented in Section 1.2 and 1.3 can be effectively addressed with the knowledge of these terminal charges. The next section provides a brief outline of the contents of this thesis.

#### 1.6 An outline of this work

This chapter focused on the motivation and scope of this work along with some of the problems faced in RF modeling and characterization. Chapter 2 gives an overview of past work towards three-port characterization from two-port measurements. It elaborates the limitations of the existing methods. It brings out the practical problems reported in one of the latest papers [32], by a study of the non-ideal behavior of the GPG (Ground-Power-Ground) probe used at the un-calibrated third-port for bias feed, while carrying out two-port measurements. This chapter proceeds to develop the theoretical background required to realize three-port MOSFET characterization from two-port measurements. It provides a detailed description of the MOSFET Admittance Network theory and its application towards the characterization of the device. It also illustrates the three different two-port permutations to be used, along with their equivalent admittance matrix representations.

Chapter 3 and 4 provide a detailed solution to the problem posed by the GPG probe. Chapter 3 describes the measurement set-ups, device characterization and parasitic deembedding procedures used. It proposes a new test structure (SD-R) to directly extract a set of model parameters, which are of special use in the MOSFET parameter extraction, employed for de-embedding the probe's impedance. It proceeds to explain the RF characterization of the GPG probe using one-port S-parameter measurements, and the undesirable effect of the probe's impedance on two-port measurements of the MOSFET. It stresses the need for de-embedding the probe's impedance from the RF measurements.

Chapter 4 is dedicated towards the de-embedding of the probe impedance using RF MOSFET modeling and parameter extraction techniques for both on-state and off-state behavior of the device. The given method employs small-signal modeling techniques to

develop a general RF equivalent circuit for the MOSFET. Using the general RF equivalent circuit, this chapter demonstrates the use of the SD-R test structure through the extraction of some important physical parameters like junction admittances and the body-effect trans-conductance (which are also useful for RF modeling in general). The work presents a novel parameter extraction scheme, utilizing the physical parameters extracted from the SD-R device, to accurately de-embed the effect of the probe impedance at the un-calibrated third port, from the two-port data of the MOS device. It proceeds to describe the generation of the three-port Y-parameters and terminal capacitances from the corrected two-port data. The chapter concludes with a derivation of expressions for the terminal charges of the device using the three-port terminal capacitances.

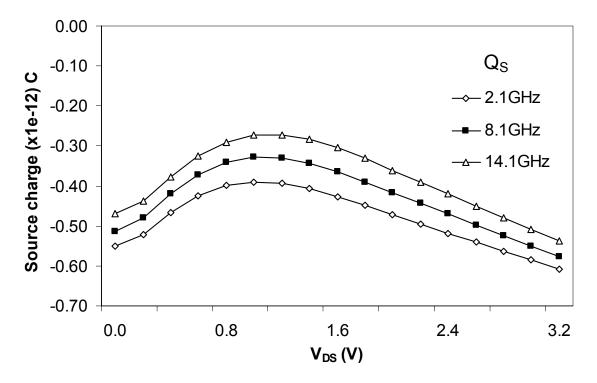

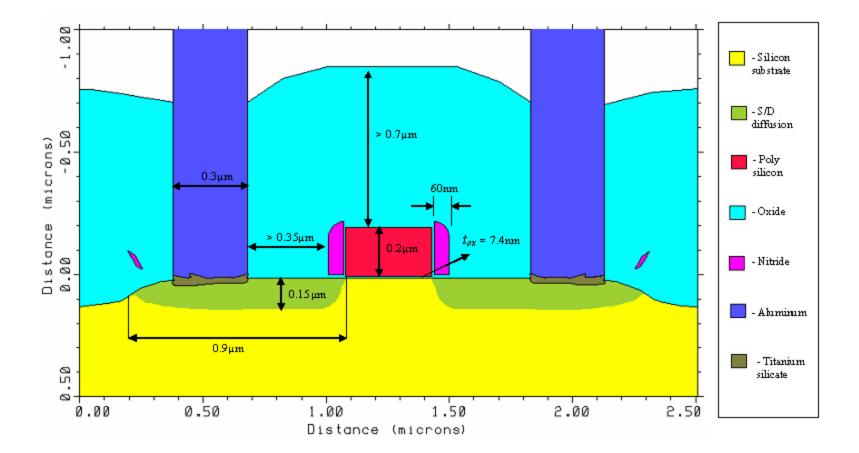

Chapter 5 presents the two-dimensional device simulations carried out using TCAD simulators, to serve as a guideline to validate the three-port characterization data of the MOSFET, as well as to verify functionality of the SD-R device and its parameter extraction. It describes the process simulation of a 0.35µm NMOS device in CMOS technology using Synopsys TSUPREM-4 along with DC and RF simulations of the simulated NMOS structure in Synopsys Medici. It gives an overview of the process flow, development of the simulation mesh, adaptive re-grid procedures and the device models used in the simulations. It reports the junction capacitance and conductance of the device extracted from both simulations and measurements of the SD-R structure and verifies its functionality. It provides explanations for both the bias and frequency dependence of the extracted junction admittances.

Chapter 6 illustrates the consistency of the MOS parameter extraction scheme and validates the three-port characterization data by exhibiting the match of the redundant

10

admittances obtained from different two-port configurations after probe de-embedding. It also verifies the correctness of the extrinsic parameters, by comparing junction admittances extracted from both the normal device and SD-R structure measurements. It presents the three-port capacitances and trans-conductance obtained from measurements for the first time, along with capacitances obtained from simulations and discusses their overall trends. The work presents the NQS effect manifested as the increasing divergence between the gate-to-drain ( $g_m$ ) and gate-to-source ( $g_{ms}$ ) trans-conductance obtained from the three-port data for the first time. This chapter depicts the terminal charges of the MOSFET, extracted from its measured three-port capacitances, as functions of both bias and frequency for the first time. It also discusses the bias dependence of the charges using device physics. Chapter 7 presents the conclusions of this work. It also presents some suggestions for future enhancements of this work. The list of publications associated with this work is given in the next section.

### 1.7 List of publications

- 1. U. Mahalingam, S. C. Rustagi, and G. S. Samudra, "Three-Port RF Characterization of MOS Transistors," 65th Automated Radio Frequency Techniques Group (ARFTG) Conference Digest, June 2005.

- U. Mahalingam, S. C. Rustagi, and G. S. Samudra, "Direct Extraction of Substrate Network for RF MOSFET Modeling Using a Simple Test Structure," *IEEE Electron Device Letters*, vol. 27, no. 2, pp. 130-132, Feb. 2006.

- U. Mahalingam, S. C. Rustagi and G. S. Samudra, "Frequency and Bias Dependent Terminal Charge Extraction for a MOSFET using Three-port RF Characterization", draft under preparation.

## **Chapter 2: Overview of Past Work and Network Theory**

This chapter provides a brief study of the various methods developed for active device characterization. It analyzes the limitations of these works and proposes an effective solution to the problem faced in one of the latest reports in literature [32] on three-port MOSFET characterization. The latter portion of this chapter develops the theoretical background needed for the succeeding chapters on measurement and extraction. The general admittance theory of the MOSFET and its abstractions into different two-port configurations has been presented.

#### 2.1 Prior work in MOSFET characterization

Several attempts to obtain a three-port RF characterization from two-port S-parameter measurements have been reported in the literature [29-32]. In one of the methods, the third port is terminated on-wafer with the characteristic impedance. Thus, the two-port S-parameters directly correspond to the elements of a three-by-three S-parameter matrix. The methods in [29-31] employ multiple test structures for the measurements. As device level variations can be significant, the accuracy of the characterization is affected by these variations. Further, de-embedding of shunt and series parasitic is very important at RF regime, and so the use of multiple structures may yield inaccurate data. Some of the methods are also very involved in their analysis. A serious disadvantage in such methods is that the terminating impedance interferes with the DC biasing of the device at the third port [29]. This approach is shown in Figure 2.1.

Figure 2. 1 On-wafer termination for two-port S-parameter measurements

Alternatively, to perform a similar experiment with Z-parameters, large impedance in the form of a series inductance is required at the third port probe-tip (so that the third port is practically "open-circuit"). Obtaining sufficiently large impedance to obtain ideal open-circuit conditions is again laced with practical difficulties.

Jha et al [32] had proposed a method to obtain three-port characterization of a MOSFET using two-port measurements in three different configurations of the device. The difference in this case is that, instead of terminating the third port with the characteristic impedance, an external AC short is attempted at the third port. Here, the correspondence to three-port characteristics is established via Y-parameters and not the S-parameters. The measured S-parameters are converted to two-port Y-parameters. The two-port Y-parameters obtained from the three different configurations are properly assembled to yield the three-port Y-parameters of the device. This method proposes a single test structure and thus avoids problems of device-level variation. For on-wafer measurements, a Ground-Power-Ground (GPG) probe is employed to provide the external AC short and the third port DC-feed. In the absence of terminating impedance

the biasing problems mentioned before are also avoided. A large on-probe capacitance serves to bring the AC short close to the probe-tip.

This method is valid only if the GPG probe provides an ideal AC ground at the third port. However, the GPG probe provides an AC short only at low frequencies (up to 1.1GHz as indicated by measurements on GPG probe, which will be discussed later). The probe is 'lossy' and also exhibits a strong inductive behavior at higher frequencies (see Chapter 3). So, the two-port Y-parameters obtained from S-parameter measurement do not correspond to the three-port parameters of the device. The work reported in [32] is valid only up to about 1.1GHz. Thus the effect of this non-ideal AC short, i.e. the probe impedance, must be properly de-embedded to get the correct three-port characteristics of the MOSFET at RF.

The behavior of the GPG probe and its detrimental effect on the device measurements is addressed in Chapter 3 and the probe de-embedding solution is formally evolved in Chapter 4, which paves the way for accurate three-port characterization of the MOSFET. The next section builds up the theoretical background for the MOS device description. The device is described by its admittance matrices in its complete form as well as, by the various two-port configurations in its partial forms. The relation between the three twoport forms and the larger matrix is brought out. The advantages of such a Y-parameter representation towards RF characterization are also clearly established.

#### 2.2 MOS admittance network theory

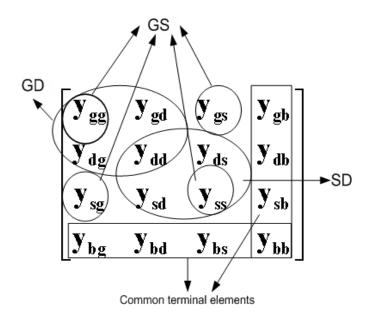

Any *n*-port device (i.e. a device having 'n+1' terminals) can be described completely by its corresponding *n*-port S, Y, H or Z parameters. As the MOSFET is a four terminal device, it is completely characterized by its three-port parameters. The different parameter sets are inter-convertible using simple matrix manipulation techniques [33]. RF measurements using a Network Analyzer yield the S-parameters of the device. These are then converted to Y- or Z-parameters for ease of analysis and parameter extraction. The general 4x4 admittance matrix describes the complete device as given by (2.1).

$$\begin{bmatrix} i_{g} \\ i_{d} \\ i_{s} \\ i_{b} \end{bmatrix} = \begin{bmatrix} y_{gg} & y_{gd} & y_{gs} & y_{gb} \\ y_{dg} & y_{dd} & y_{ds} & y_{db} \\ y_{sg} & y_{sd} & y_{ss} & y_{sb} \\ y_{bg} & y_{bd} & y_{bs} & y_{bb} \end{bmatrix} \begin{bmatrix} v_{g} \\ v_{d} \\ v_{s} \\ v_{b} \end{bmatrix}$$

(2.1)

As explained earlier, this description covers the effect of the signal coupling to the bulk terminal as well as charges induced at all terminals due to applied DC potential. The well-known admittance conservation principle [7] states that the sum total of the row or column entries of an '*n*-by-*n*' admittance matrix of an *n*-port device, add up to zero. For example considering the first row elements of (2.1), we can conclude that,

$$y_{gg} + y_{gd} + y_{gs} + y_{gb} = 0. (2.2)$$

This means that the complete 4x4 Y-matrix can be generated with the knowledge of any 9 of the 16 elements in (2.1). This can be achieved by taking one of the terminals as being common to all other terminals involved in the three-port description. It is convenient to take the bulk as the common terminal at AC ground ( $v_b$ =0). The MOSFET thus has three ports, namely, Gate-Bulk, Drain-Bulk and Source-Bulk. Thus we can eliminate the final row and column entries of the 4x4 Y-matrix and reduce the problem to a 3x3 Y-matrix as given in (2.3).

$$\begin{bmatrix} i_g \\ i_d \\ i_s \end{bmatrix} = \begin{bmatrix} y_{gg} & y_{gd} & y_{gs} \\ y_{dg} & y_{dd} & y_{ds} \\ y_{sg} & y_{sd} & y_{ss} \end{bmatrix} \begin{bmatrix} v_g \\ v_d \\ v_s \end{bmatrix}$$

(2.3)

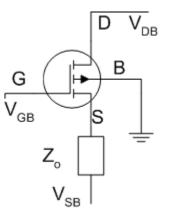

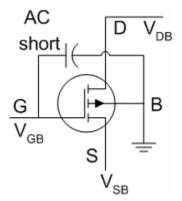

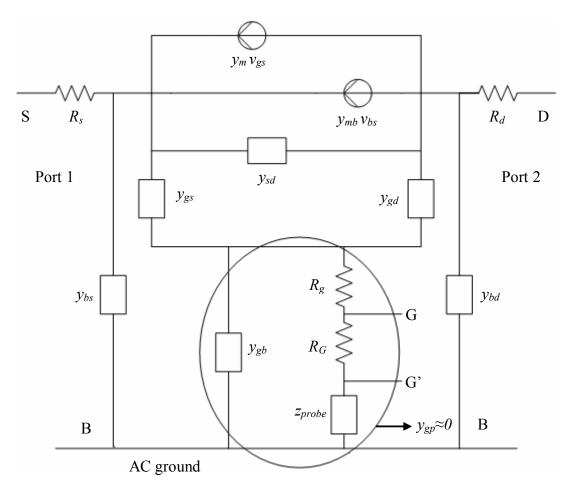

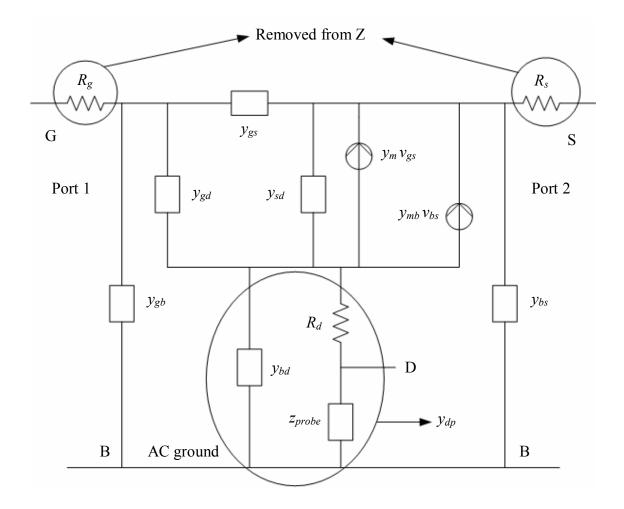

The nine elements in (2.3) can be individually generated by three unique two-port configurations [32] in which the third-port is AC shorted. The GD configuration is the common-source configuration where the two RF ports are Gate-Bulk and Drain-Bulk while the Source is AC shorted to the Bulk ( $v_s$ =0) as shown in Figure 2.2. The bulk itself is always at AC ground, serving as the common terminal. The corresponding GD admittance matrix is given in (2.4).

Figure 2. 2 GD configuration

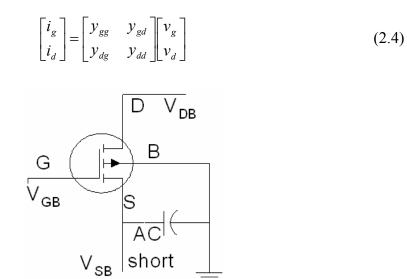

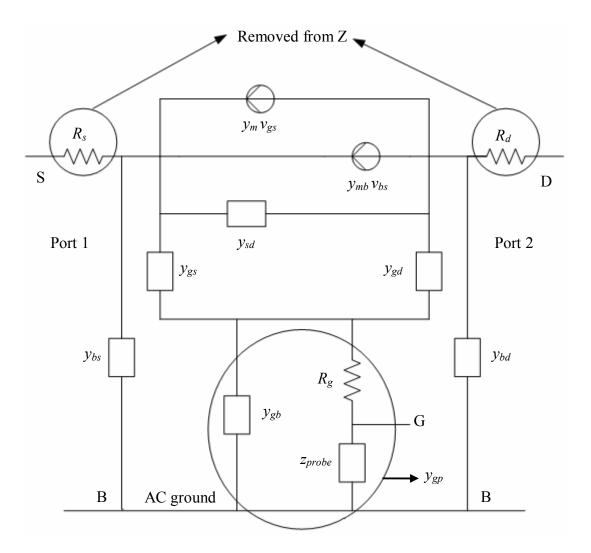

The GS configuration is the common-drain configuration where the two RF ports are Gate-Bulk and Source-Bulk while the Drain is AC shorted to the Bulk ( $v_d$ =0) as shown in Figure 2.3. The corresponding admittance matrix is given in (2.5).

$$\begin{bmatrix} i_g \\ i_s \end{bmatrix} = \begin{bmatrix} y_{gg} & y_{gs} \\ y_{sg} & y_{ss} \end{bmatrix} \begin{bmatrix} v_g \\ v_s \end{bmatrix}$$

(2.5)

Figure 2. 3 GS configuration

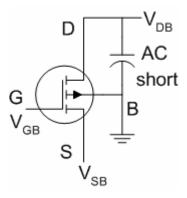

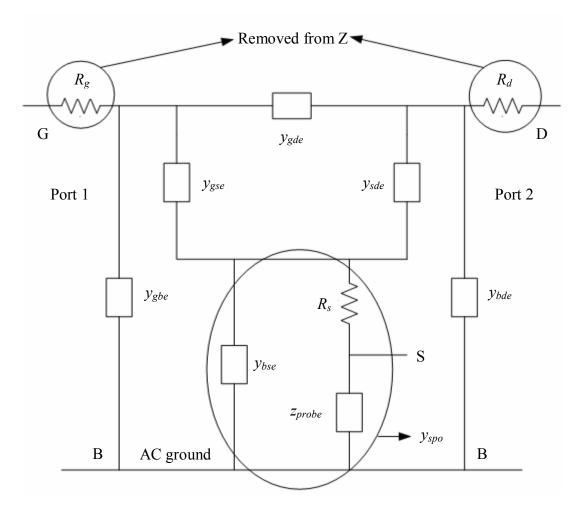

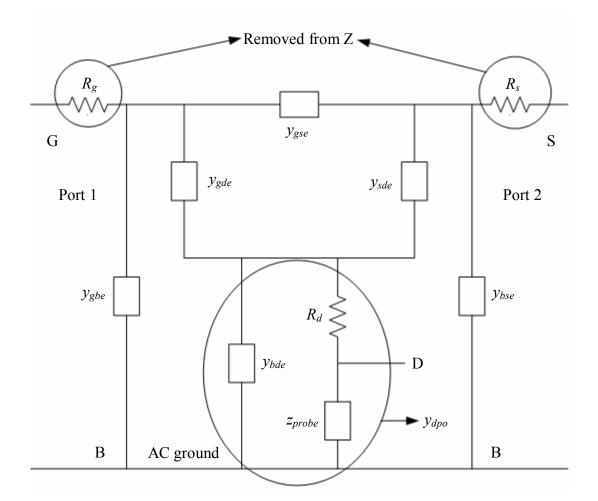

Similarly, the SD (common-gate) configuration is defined, where the two RF ports are Gate-Bulk and Source-Bulk, while the Gate is AC shorted to the Bulk ( $v_g=0$ ) as shown in Figure 2.4. The corresponding admittance matrix is given in (2.6).

$$\begin{bmatrix} i_s \\ i_d \end{bmatrix} = \begin{bmatrix} y_{ss} & y_{sd} \\ y_{ds} & y_{dd} \end{bmatrix} \begin{bmatrix} v_s \\ v_d \end{bmatrix}$$

(2.6)

Figure 2. 4 SD configuration

The two-port matrices of (2.4)-(2.6) provide some redundancy as some of the elements are obtained from two different configurations. The next section examines the relevance of this redundancy in validating the device characterization, through an illustration.

#### 2.2.1 Redundancy of the main diagonal elements

Figure 2.5 depicts a consolidated picture of the admittance matrix with contributions from the individual configurations also being highlighted. In the figure, the main diagonal elements of the upper 3x3 Y-matrix (excluding the common terminal elements), namely  $y_{gg}$ ,  $y_{dd}$  and  $y_{ss}$ , are each obtained uniquely from two different measurement configurations. The  $y_{11}$  of GD and GS configurations yield  $y_{gg}$ , while  $y_{22}$  of GD and SD configurations yield  $y_{dd}$  of the device. Similarly,  $y_{22}$  of GS and  $y_{11}$  of SD both yield  $y_{ss}$ .

Figure 2. 5 Redundancy of main diagonal elements

As all three configurations are for the same device, any main diagonal element obtained from two different configurations should also be equal. Otherwise, the measured two-port Y parameters do not reflect the true characteristics of the device. Thus, such an agreement of the main diagonal elements serves to validate the entire three-port characterization. We will use this test to confirm the veracity of the three-port data obtained after probe de-embedding, in Chapter 6. The two-port Y-parameters defined by (2.4)-(2.6) directly correspond to the entries in (2.3) and thus the three-port Y-parameters can be easily assembled from them. The Sparameter measurements for these two-port configurations are carried out by providing an external AC short at the third port at RF. These S-parameters do not enjoy a similar correspondence to the three-port S-parameter matrix of the MOSFET. So, they are not the actual two-port S-parameters of the device. To establish a similar correspondence between two-port S-parameters and the three-port S-parameters, one must terminate the third port of the above-mentioned two-port configurations with the characteristic impedance of the network (e.g.  $Z_0=50\Omega$ ). But, the practical difficulties like DC bias interference make this approach infeasible. However, the measured S-parameters are converted to Y-parameters, which are indeed the actual two-port Y-parameters of the device. So they directly map to the three-port Y-parameter matrix in (2.3). Thus we find that Y-parameters provide the easiest way to get the three-port characteristics of the MOSFET.

This completes the theoretical description of the MOS terminal admittances. The next chapter describes the new test structures, measurement setups and parasitic de-embedding methods used for the MOSFET characterization. It develops a method to characterize the GPG probe and identifies its significant degrading effect on device measurements at RF.

### **Chapter 3: Test Structures and Measurement**

This chapter describes the measurement set-ups and device structures employed for the characterization. It introduces a novel test structure, named the SD-R device and highlights its utility towards physical parameter extraction for RF modeling. It presents a newly developed method for the characterization of the GPG probe and reports its measured RF behavior for the first time. It explains the two-step de-embedding of onwafer parasitic from the measured data. It also proposes a new approach to eliminate the on-wafer parasitic at the third port. The chapter concludes with an account of the effect of the non-ideal short provided by the GPG probe at the third port, on the two-port device measurements. The effect of probes used at un-calibrated ports of a device, on measured data at RF, has been studied here for the first time.

### 3.1 Measurement Setup

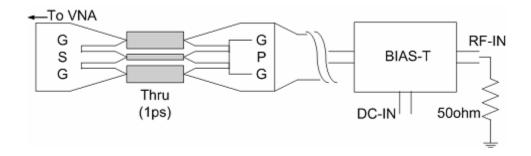

A two-port Vector Network Analyzer (HP8510c VNA) and a DC source-measure unit (HP4142) were used for the measurements. The measurement system was controlled with the help of a 'UNIX' workstation through a standard GPIB (General Purpose Interface Bus). Two RF GSG (Ground-Signal-Ground) probes (CASCADE-Infinity probes) were used for the RF signal ports while a GPG (Ground-Power-Ground) probe (GGB Industries) was used at the third port to provide DC feed along-with an external AC-short. The RF signal was coupled with DC bias using appropriate Bias Tees (HP 11612B Bias Network). Though the DC source itself can provide the AC-short at the third port, the GPG probe actually helps to bring the short closer to the device through a large on-probe capacitance. This is very important because the third port is un-calibrated and the

cables leading to the DC source can insert significant parasitic impedance before being shorted inside the instrument. A Bias Tee is employed at the third port, whose RF-in terminal is terminated by the characteristic impedance of  $50\Omega$  and DC-in is connected to the HP4142. The IC-CAP software tool was used to transfer and store the measured data for future analysis.

#### 3.1.1 A note on IC-CAP

The "Integrated Circuit-Characterization and Analysis Program" – IC-CAP is a stateof-the-art device modeling software from Agilent technologies. It provides powerful characterization and analysis capabilities for semiconductor modeling applications. This work has relied on IC-CAP's capabilities in data acquisition, simulation, and graphical analysis. The special Parameter Extraction Language (PEL) utility of IC-CAP has been extensively exploited in this work to construct efficient transforms (extraction programs) for direct parameter extractions at RF [34]. The huge amount of data generated from RF S-parameter measurements have been efficiently de-embedded and processed using these transforms to achieve the accurate three-port capacitance and conductance coefficients of the MOS device up to several GHz.

#### 3.1.2 Calibration of the Vector Network Analyzer

The VNA ports were calibrated using the Load-Reflect-Reflect-Match (LRRM) technique [35] on the Impedance Standard Substrate (ISS). This requires a golden device for the short, load (50 $\Omega$ ) and thru conditions. The thru is a loss-less delay line with an electrical delay of 1ps for the GD configuration i.e. the normal scenario in which the two RF signal probes are oriented opposite to each other. For the GS and SD case, the RF

signal probes are oriented at right angles to each other, which require a special L-shaped thru line with electrical delay of 3ps. For the LRRM method, measuring load for one of the ports is sufficient. The open and short are measured for both the ports. The source power levels were set at -10dBm and noise tolerance for the calibration is set to within 0.05dB to ensure quality measurements at RF. The PC-based WinCal software [36], a two-port calibration tool-kit, was used for this purpose.

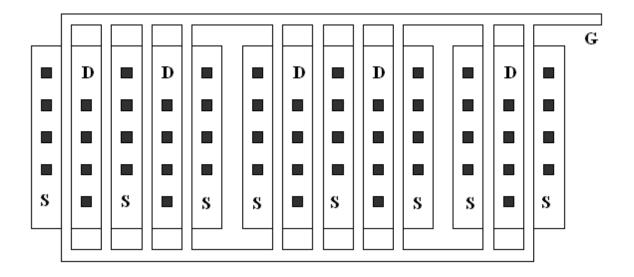

#### 3.2 Device specifications

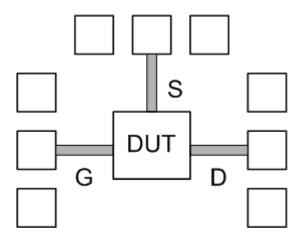

Enhancement type NMOS devices were fabricated in a local fabrication company, using standard 0.35 micron CMOS technology with single poly and four metal layers. Measurements were carried out on devices with three different channel lengths - 1 $\mu$ m, 0.5 $\mu$ m and 0.35 $\mu$ m respectively. Each device is comprised of 10 fingers of 10 $\mu$ m width each (total W=100 $\mu$ m). Figure 3.1 gives a simplistic view of the measured device's multi-finger architecture (the metal layers used to establish source and drain contacts are not shown here) with shared drain and source diffusion regions. Figure 3.1 shows that the measured ten-finger MOS device is comprised of two four-finger sections and one two-finger section with a focus to minimize the number of drain diffusions. In all, there are eight source diffusion regions and five drain diffusion regions. The gate of each the finger is contacted from both sides to reduce resistance [40].

Figure 3. 1 Multi-finger architecture of the measured MOSFET

The measurements covered the entire operational range of the MOS devices with the terminal biases  $V_{GB}$ ,  $V_{DB}$  and  $V_{SB}$  each ranging from 0V to 3.2V in steps of 0.2V ( $V_B$ =0) and the signal frequency ranging from a 100MHz to 25.1GHz in steps of 500MHz. It may be noted that the maximum acceptable potential at any terminal with respect to the source is 3.3V for the 0.35 micron technology. The two-port S-parameter measurements were repeated as above for the GD, GS and SD configurations.

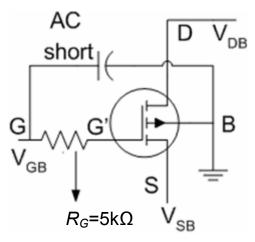

#### 3.2.1 The SD-R test structure

In addition to the normal devices mentioned in the previous section, a special device structure has been conceptualized to aid the RF parameter extraction of the MOSFET, to be elaborated in Chapter 4. This structure employs a huge resistance ( $R_G$ ) of about 5k $\Omega$  at the Gate terminal of the MOS device. Other features of this device are exactly the same as those of a normal device. The measurements on this structure are carried out in the SD configuration alone. The purpose of the huge gate resistance is to kill any small-signal at the external Gate terminal (Figure 3.2). This enables us to directly extract the junction admittances of the device in on-state (see Chapter 4). This structure will be henceforth referred to as the SD-R device. It should be noted that, as the gate DC current is negligibly small, the  $R_G$  does not in any way hamper the device biasing. Thus, the DC behavior of such a device is exactly the same as that of a normal device.

Figure 3. 2 SD-R test structure (in SD configuration)

## 3.3 The GPG probe

The GPG probe is used at the third port for DC bias feed and for providing the ACshort. The probe has a large mounted capacitance (120pF), which provides an ideal AC ground at low frequencies. A 1-port S-parameter characterization of the GPG probe was carried for frequencies 100MHz to 25.1GHz in steps of 500MHz. A GSG probe was used to measure the  $s_{11}$  of the GPG probe through a lossless 'thru' line (electrical delay=1ps). The GPG probe was terminated by 50 $\Omega$  impedance through an RF cable and Bias-Tee (similar to experimental set-up for device measurement). The characterization set-up is shown in Figure 3.3.

Figure 3. 3 GPG probe characterization

The measured  $s_{11}$  ( $s_{MS.11}$ ) of the GPG probe is corrected for electrical delay ( $T_D$ =1ps) of the through line as given in (3.1).

$$s_{GPG,11} = s_{MS,11} * e^{j2\pi f(2T_D)}$$

(3.1)

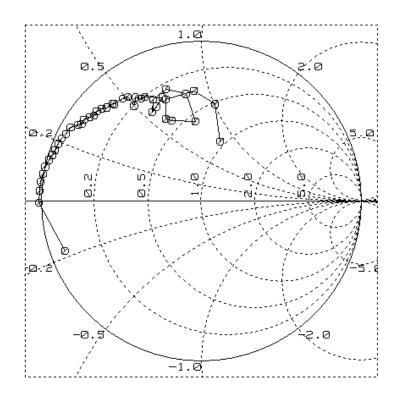

The corrected  $s_{11}$  of the probe ( $s_{GPG,11}$ ) is shown in Figure 3.4. As expected, the capacitive effect dominates at very low frequencies. But at higher frequencies, especially beyond 1.1GHz, the probe exhibits an increasing loss and significantly large inductive characteristic. The S-parameters are converted to 1-port Z-parameter as given in (3.2).

$$z_{GPG} = 50*(1+s_{GPG,11})/(1-s_{GPG,11})$$

(3.2)

It is clear from Figure 3.4 that the GPG probe exhibits a non-ideal behavior and thus its effect must be completely removed from the two-port measurements of the MOSFET. The disparity produced by the GPG probe impedance on the measured Y-parameters is discussed in the following sections.

Figure 3. 4 s<sub>11</sub> of the GPG probe (s<sub>GPG.11</sub>)

# 3.4 Parasitic De-embedding of measured data

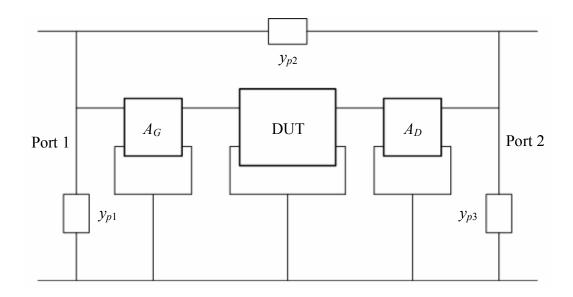

The conventional one-step de-embedding technique is not valid for frequencies beyond 10GHz as the serial parasitic of leading interconnects become significant [37]. The two-step de-embedding approach given in [37] is also not adequate as it makes a lumped approximation of the serial parasitic. To consider the distributed effects of the serial parasitic, the cascaded matrix approach presented in [38] is adopted after removing the pad parasitic. Dummy Test structures were laid out for the de-embedding of on-chip parasitic – both pad and interconnect. Figure 3.5 depicts the DUT with its pads and leading interconnects. The pad parasitic is a parallel component, which can be simply removed from the DUT Y-parameters. The interconnect exhibits a distributed behavior at RF which hinders the possibility of its separation into serial and parallel components. The

best way to handle them is to obtain their two-port characteristics separately and deembed them from the DUT using the ABC-matrices [38].

Figure 3. 5 The MOSFET test structure

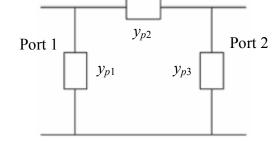

Figure 3.6 shows the DUT with both its pad  $(y_{p1}, y_{p2} \text{ and } y_{p3})$  and interconnect (represented by ABC matrices  $A_G$  and  $A_D$ ) parasitic components considering only the two RF signal ports at a time.

Figure 3. 6 Two-port parasitic representation for the MOSFET in GD configuration

The parasitic associated with the un-calibrated third port is combined with the GPG probe impedance and removed together. The third port parasitic de-embedding is considered in detail in Section 3.4.1.

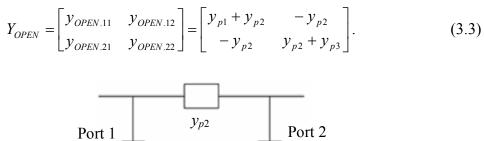

A dummy containing only the pads was measured to get the parallel parasitic in each two-port configuration. Figure 3.7 depicts the two-port equivalent parasitic admittance elements ( $y_{p1}$ ,  $y_{p2}$  and  $y_{p3}$ ) representing the pads. The measured two-port S-parameters are converted to Y-parameters. The open parasitic is given by,

Figure 3. 7 Two-port equivalent parasitic representation of the pads

The measured S-parameters of the MOSFET are converted to Y-parameters ( $Y_{DUT, MS}$ ) and the pad parasitic is first removed. This yields the pad de-embedded Y-parameters ( $Y_{MS-PD}$ ) of the structure.

$$Y_{MS-PD} = Y_{DUT, MS} - Y_{OPEN}$$

(3.4)

Considering the Common-Source two-port configuration for the DUT in Figure 3.5 and discounting the gate and drain pads, we are now left with the Gate-side leading interconnect followed by the actual DUT and the Drain-side leading interconnect – all

three in a serially cascaded form. The ABC-matrix by virtue of its mathematical property is best-suited to describe such a chain of two-ports [38]. Thus, we have,

$$A_{MS-PD} = A_G * A_{DUT} * A_D, (3.5)$$

In (3.5), the two-port ABC-matrices denote the pad de-embedded characteristics ( $A_{MS-PD}$ ), the gate interconnect ( $A_G$ ), the actual device ( $A_{DUT}$ ) and the drain interconnect ( $A_D$ ) respectively.

Each of the leading interconnects was laid out as a 'thru' set-up and measured in twoport form. Figure 3.8 shows the 'thru' setup of the Gate terminal lead interconnect and the corresponding parasitic. It should be noted that this dummy as such includes the pad parasitic also. A pad dummy similar in geometry to the dummy shown in Figure 3.8, without interconnect, is first measured. Its S-parameters are converted to Y-parameters  $(Y_{OPEN})$ . The measured interconnect dummy S-parameters are also converted to Yparameters  $(Y_{INTERCON, MS})$  and de-embedded of the pad parasitic  $(Y_{OPEN})$ , before being converted to ABC-parameters. The  $A_G$  so obtained is given in (3.6).

Port 1

Port 2

$$A_G$$

$y_{p1}$

$$A_G = A \left[ Y_{INTERCON, MS} - Y_{OPEN} \right]$$

(3.6)

$y_{p3}$

Figure 3. 8 Lead interconnect dummy and its equivalent parasitic representation

Similarly, we obtain  $A_D$  and  $A_S$  for the drain and source leading interconnects. Through simple matrix manipulations like post multiplication and pre-multiplication by the inverse of the respective interconnect ABC matrices, we obtain the accurate DUT characteristics, which are converted back to Y-parameters for analysis.

$$A_{DUT} = A_{G}^{-1} * A_{MS-PD} * A_{D}^{-1}$$

(3.7)

$$Y_{DUT} = Y \Big[ A_{DUT} \Big] \tag{3.8}$$

Similarly, for the GS and SD configurations, the respective interconnects are removed using the cascading ABC matrices after de-embedding the pad parasitic.

But it must be re-emphasized that the pad and series parasitic at the third port are still left to be de-embedded from the measured two-port data. The next section demonstrates a new approach to eliminate the third port parasitic.

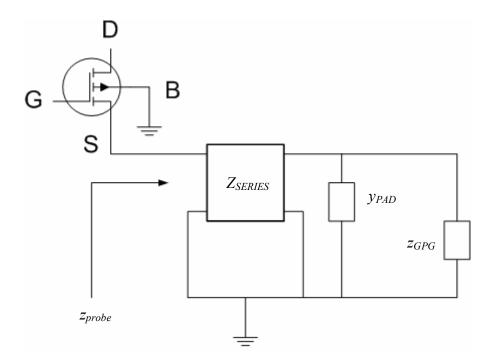

### 3.4.1 Eliminating the third port parasitic

The best way to eliminate the parasitic at the third port is to combine them with the larger parasitic impedance of the GPG probe and remove them together. Figure 3.9 shows the third port parasitic along with the probe impedance for the GD configuration of the MOSFET. Here the gate-bulk and drain-bulk ports have been de-embedded of their parasitic as mentioned in the previous section. Looking into the parasitic and probe impedance network at the source terminal of the MOSFET, we define the total impedance at the third port as " $z_{probe}$ ", for ease of understanding and analysis. This impedance is calculated using the reflection co-efficient of the parasitic network as explained next. It must be mentioned here that none of the earlier works on two-port measurements reported in literature so far, have succeeded in completely eliminating the parallel and

series parasitic at the un-calibrated third port of the device. The approach presented here is quite general and can be used for parasitic removal at un-calibrated ports for other RF applications as well.

Figure 3. 9 Third port parasitic (GD configuration)

First, the shunting pad admittance at the third port is calculated from the pad dummy measurements. For example, to find the parasitic associated with the source pad (represented as  $y_{PAD}$  in Figure 3.9), two-port measurements of the pad dummy ( $Y_{OPEN}$ ) carried out in the SD configuration (defined with respect to device orientation on the wafer) can be used. Considering the equivalent circuit representation of the pad parasitic provided in Figure 3.7, the source pad parasitic would be given by  $y_{p1}$ . This can be directly obtained from the measured  $Y_{OPEN}$  using the relation specified in (3.3), as given here in (3.9).

$$y_{PAD} = y_{OPEN.11} + y_{OPEN.12} = y_{p1}$$

(3.9)

For convenience of analysis here, the impedance of the GPG probe and the pad are combined together and denoted as  $z_P$ .

$$z_P = (z_{GPG}^{-1} + y_{PAD})^{-1}$$

(3.10)

The reflection co-efficient  $\rho_p$  of this network with the characteristic impedance Zo=50 $\Omega$ , is defined as,

$$\rho_P = \frac{z_P - 50}{z_P + 50}.\tag{3.11}$$

The  $Z_{SERIES}$  of the third port inter-connect parasitic is a two-port matrix. It is therefore converted to the corresponding S-parameters ( $S_{int}$ ).

$$S_{\text{int}} = S[Z_{\text{SERIES}}] = \begin{bmatrix} s_{\text{int},11} & s_{\text{int},12} \\ s_{\text{int},21} & s_{\text{int},22} \end{bmatrix}$$

(3.12)

The reflection co-efficient of the combined network  $\rho_{probe}$  is obtained as given in [33].

$$\rho_{probe} = s_{\text{int.11}} + \frac{s_{\text{int.12}} s_{\text{int.21}} \rho_P}{1 - s_{\text{int.22}} \rho_P}$$

(3.13)

The reflection co-efficient is converted into the effective impedance looking into the network i.e.  $z_{probe}$  as given in (3.14).

$$z_{probe} = 50 \frac{\left(1 + \rho_{probe}\right)}{\left(1 - \rho_{probe}\right)}$$

(3.14)

This impedance must be removed to get the ideal two-port characteristics of the device in each configuration. The next section shows the effect of this probe impedance on actual device measurements.

### 3.5 Effect of the GPG probe on device measurements

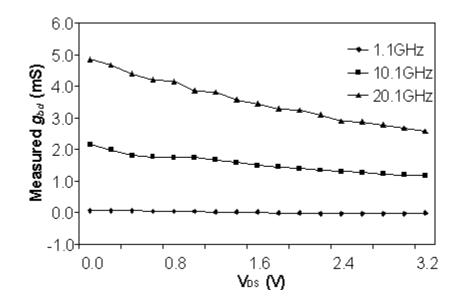

The probe impedance at the third port has a significant effect on the two-port device measurements at RF. The effect of the GPG probe on RF device measurements has not been reported in literature. This is because most of the works on two-port RF characterization [11-25] use a MOSFET with the source and bulk nodes tied together. This makes it impossible to give any DC biasing between the source and bulk nodes and thus the works do not require a GPG probe for the measurements. In [32], a GPG probe has been used for the measurements but only low frequency data (up to 1.1GHz) was reported. This work concentrates on the RF regime and thus has identified the significant problem posed by the GPG probe. In this section, we report the undesirable effects of this probe (used at the un-calibrated third port for biasing) on the measured two-port admittances of the MOSFET. The MOSFET admittance network theory is applied to the measurements here to clearly gauge the magnitude of the problem.